## 特長

- 集積化されたデュアル14ビットADC

- サンプル・レート:125Msps

- 単一3V電源(2.85V~3.4V)

- 低消費電力:790mW

- SNR:72.4dB、SFDR:88dB

- 100MHzでのチャネル間分離:110dB

- 柔軟な入力:1V<sub>P-P</sub>~2V<sub>P-P</sub>

- 640MHzのフルパワー帯域幅S/H

- クロック・デューティ・サイクル・スタビライザ

- シャットダウン・モードとナップ・モード

- データ・レディ出力クロック

- ピン互換ファミリ

- 125Msps:LTC2283(12ビット), LTC2285(14ビット)

- 105Msps:LTC2282(12ビット), LTC2284(14ビット)

- 80Msps:LTC2294(12ビット), LTC2299(14ビット)

- 65Msps:LTC2293(12ビット), LTC2298(14ビット)

- 40Msps:LTC2292(12ビット), LTC2297(14ビット)

- 64ピン9mm×9mm QFNパッケージ

## アプリケーション

- 無線および有線の広帯域通信

- イメージング・システム

- スペクトル分析

- 携帯用計測器

## 概要

LTC<sup>®</sup>2285は、高周波の広いダイナミック・レンジの信号をデジタル化する14ビット、125Msps、低消費電力、デュアル3V A/Dコンバータです。SNRが72.2 dB、ナイキスト周波数での信号に対するSFDRが82dBという優れたAC特性を備えているため、要求の厳しいイメージングや通信アプリケーションに最適です。

DC仕様では、±1.5 LSBのINLと±0.6LSBのDNLが規定されています。遷移ノイズは1.3LSBRMSと低く抑えられています。

単一3V電源により、低消費電力動作が可能です。個別の出力電源により、0.5V~3.6Vロジックをドライブする出力が可能です。

シングルエンドCLK入力によってコンバータ動作を制御します。また、オプションのクロック・デューティ・サイクル・スタビライザにより、広範なクロック・デューティ・サイクルに対してフルスピードで高性能を達成できます。データラッチ出力クロック(CLKOUT)を使用して出力データをラッチすることができます。

**L**、**LT**、**LTC**、**LTM**はリニアテクノロジー社の登録商標です。

他のすべての商標はそれぞれの所有者に所有権があります。

## 標準的応用例

## 絶対最大定格

OV<sub>DD</sub> = V<sub>DD</sub> (Note 1, 2)

|                         |       |                                 |

|-------------------------|-------|---------------------------------|

| 電源電圧 (V <sub>DD</sub> ) | ..... | 4V                              |

| デジタル出力のグランド電圧 (OGND)    | ..... | -0.3V~1V                        |

| アナログ入力電圧 (Note 3)       | ..... | -0.3V~(V <sub>DD</sub> + 0.3V)  |

| デジタル入力電圧                | ..... | -0.3V~(V <sub>DD</sub> + 0.3V)  |

| デジタル出力電圧                | ..... | -0.3V~(OV <sub>DD</sub> + 0.3V) |

| 消費電力                    | ..... | 1500mW                          |

| 動作温度範囲                  |       |                                 |

| LTC2285C                | ..... | 0°C~70°C                        |

| LTC2285I                | ..... | -40°C~85°C                      |

| 保存温度範囲                  | ..... | -65°C~150°C                     |

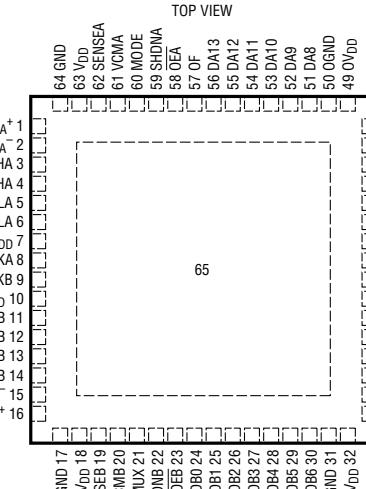

## パッケージ/発注情報

|                                                                                                                                                                                                                                 |                                                                                                                                                                                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|  <p>TOP VIEW</p>                                                                                                                              | <b>UP PACKAGE</b><br>64-LEAD (9mm x 9mm) PLASTIC QFN<br>$T_{JMAX} = 150^{\circ}\text{C}$ , $\theta_{JA} = 20^{\circ}\text{C/W}$<br>EXPOSED PAD (PIN 65) IS GND AND MUST BE SOLDERED TO PCB |  |

|                                                                                                                                                                                                                                 | <b>ORDER PART NUMBER</b> <b>QFN PART* MARKING</b><br>LTC2285CUP      LTC2285UP<br>LTC2285IUP                                                                                               |  |

| <b>Order Options</b> Tape and Reel: Add #TR<br>Lead Free: Add #PBF   Lead Free Tape and Reel: Add #TRPBF<br>Lead Free Part Marking: <a href="http://www.linear-tech.co.jp/leadfree/">http://www.linear-tech.co.jp/leadfree/</a> |                                                                                                                                                                                            |  |

さらに広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。

\*温度グレードは出荷時のコンテナのラベルで識別されます。

## コンバータ特性

●は全動作温度範囲の規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。(Note 4)

| PARAMETER                     | CONDITIONS                         | MIN | TYP  | MAX  | UNITS                          |     |

|-------------------------------|------------------------------------|-----|------|------|--------------------------------|-----|

| Resolution (No Missing Codes) |                                    | ●   | 14   |      | Bits                           |     |

| Integral Linearity Error      | Differential Analog Input (Note 5) |     |      | ±1.5 | LSB                            |     |

| Differential Linearity Error  | Differential Analog Input          | ●   | -1   | ±0.6 | 1.1                            | LSB |

| Offset Error                  | (Note 6)                           | ●   | -12  | ±2   | 12                             | mV  |

| Gain Error                    | External Reference                 | ●   | -2.5 | ±0.5 | 2.5                            | %FS |

| Offset Drift                  |                                    |     |      | ±10  | $\mu\text{V}/^{\circ}\text{C}$ |     |

| Full-Scale Drift              | Internal Reference                 |     |      | ±30  | ppm/°C                         |     |

|                               | External Reference                 |     |      | ±5   | ppm/°C                         |     |

| Gain Matching                 | External Reference                 |     |      | ±0.3 | %FS                            |     |

| Offset Matching               |                                    |     |      | ±2   | mV                             |     |

| Transition Noise              | SENSE = 1V                         |     |      | 1.3  | LSB <sub>RMS</sub>             |     |

## アナログ入力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL       | PARAMETER                                            | CONDITIONS                                                             | MIN    | TYP                    | MAX      | UNITS          |

|--------------|------------------------------------------------------|------------------------------------------------------------------------|--------|------------------------|----------|----------------|

| $V_{IN}$     | Analog Input Range ( $A_{IN}^+ - A_{IN}^-$ )         | $2.85V < V_{DD} < 3.4V$ (Note 7)                                       | ●      | $\pm 0.5V$ to $\pm 1V$ |          | V              |

| $V_{IN,CM}$  | Analog Input Common Mode ( $A_{IN}^+ + A_{IN}^-$ )/2 | Differential Input Drive (Note 7)<br>Single Ended Input Drive (Note 7) | ●<br>● | 1<br>0.5               | 1.5<br>2 | V              |

| $I_{IN}$     | Analog Input Leakage Current                         | $0V < A_{IN}^+, A_{IN}^- < V_{DD}$                                     | ●      | -1                     | 1        | $\mu\text{A}$  |

| $I_{SENSE}$  | SENSEA, SENSEB Input Leakage                         | $0V < SENSEA, SENSEB < 1V$                                             | ●      | -3                     | 3        | $\mu\text{A}$  |

| $I_{MODE}$   | MODE Input Leakage Current                           | $0V < MODE < V_{DD}$                                                   | ●      | -3                     | 3        | $\mu\text{A}$  |

| $t_{AP}$     | Sample-and-Hold Acquisition Delay Time               |                                                                        |        | 0                      |          | ns             |

| $t_{JITTER}$ | Sample-and-Hold Acquisition Delay Time Jitter        |                                                                        |        | 0.2                    |          | $\text{psRMS}$ |

| CMRR         | Analog Input Common Mode Rejection Ratio             |                                                                        |        | 80                     |          | dB             |

|              | Full Power Bandwidth                                 | Figure 8 Test Circuit                                                  |        | 640                    |          | MHz            |

## ダイナミック精度

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ 。(Note 4)

| SYMBOL          | PARAMETER                                             | CONDITIONS                            | MIN | TYP  | MAX  | UNITS |

|-----------------|-------------------------------------------------------|---------------------------------------|-----|------|------|-------|

| SNR             | Signal-to-Noise Ratio                                 | 5MHz Input                            |     | 72.4 |      | dB    |

|                 |                                                       | 30MHz Input                           |     | 72.3 |      | dB    |

|                 |                                                       | 70MHz Input                           | ●   | 68.9 | 72.2 | dB    |

|                 |                                                       | 140MHz Input                          |     | 71.7 |      | dB    |

| SFDR            | Spurious Free Dynamic Range<br>2nd or 3rd Harmonic    | 5MHz Input                            |     | 88   |      | dB    |

|                 |                                                       | 30MHz Input                           |     | 85   |      | dB    |

|                 |                                                       | 70MHz Input                           | ●   | 70   | 82   | dB    |

|                 |                                                       | 140MHz Input                          |     | 78   |      | dB    |

| SFDR            | Spurious Free Dynamic Range<br>4th Harmonic or Higher | 5MHz Input                            |     | 90   |      | dB    |

|                 |                                                       | 30MHz Input                           |     | 90   |      | dB    |

|                 |                                                       | 70MHz Input                           | ●   | 77   | 90   | dB    |

|                 |                                                       | 140MHz Input                          |     | 90   |      | dB    |

| S/(N+D)         | Signal-to-Noise Plus Distortion Ratio                 | 5MHz Input                            |     | 72.2 |      | dB    |

|                 |                                                       | 30MHz Input                           |     | 72   |      | dB    |

|                 |                                                       | 70MHz Input                           | ●   | 67   | 71.9 | dB    |

|                 |                                                       | 140MHz Input                          |     | 70.2 |      | dB    |

| I <sub>MD</sub> | Intermodulation Distortion                            | $f_{IN} = 40\text{MHz}, 41\text{MHz}$ |     | 85   |      | dB    |

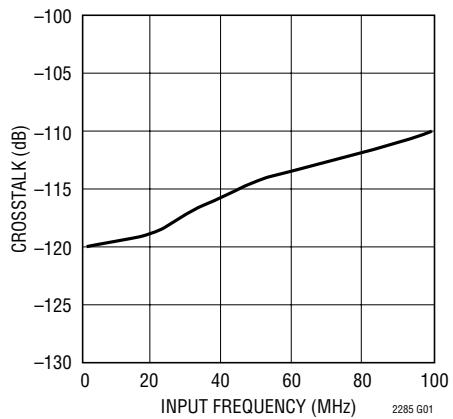

|                 | Crosstalk                                             | $f_{IN} = 100\text{MHz}$              |     | -110 |      | dB    |

## 内部リファレンス特性 (Note 4)

| PARAMETER                  | CONDITIONS              | MIN   | TYP      | MAX   | UNITS  |

|----------------------------|-------------------------|-------|----------|-------|--------|

| $V_{CM}$ Output Voltage    | $I_{OUT} = 0$           | 1.475 | 1.500    | 1.525 | V      |

| $V_{CM}$ Output Tempco     |                         |       | $\pm 25$ |       | ppm/°C |

| $V_{CM}$ Line Regulation   | $2.85V < V_{DD} < 3.4V$ |       | 3        |       | mV/V   |

| $V_{CM}$ Output Resistance | $ I_{OUT}  < 1mA$       |       | 4        |       | Ω      |

## デジタル入力とデジタル出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL                                                           | PARAMETER                 | CONDITIONS                                        | MIN | TYP   | MAX  | UNITS |

|------------------------------------------------------------------|---------------------------|---------------------------------------------------|-----|-------|------|-------|

| <b>LOGIC INPUTS (CLK, <math>\overline{OE}</math>, SHDN, MUX)</b> |                           |                                                   |     |       |      |       |

| $V_{IH}$                                                         | High Level Input Voltage  | $V_{DD} = 3V$                                     | ●   | 2     |      | V     |

| $V_{IL}$                                                         | Low Level Input Voltage   | $V_{DD} = 3V$                                     | ●   |       | 0.8  | V     |

| $I_{IN}$                                                         | Input Current             | $V_{IN} = 0V$ to $V_{DD}$                         | ●   | -10   | 10   | μA    |

| $C_{IN}$                                                         | Input Capacitance         | (Note 7)                                          |     | 3     |      | pF    |

| <b>LOGIC OUTPUTS</b>                                             |                           |                                                   |     |       |      |       |

| <b><math>0V_{DD} = 3V</math></b>                                 |                           |                                                   |     |       |      |       |

| $C_{OZ}$                                                         | Hi-Z Output Capacitance   | $\overline{OE} = \text{High}$ (Note 7)            |     | 3     |      | pF    |

| $I_{SOURCE}$                                                     | Output Source Current     | $V_{OUT} = 0V$                                    |     | 50    |      | mA    |

| $I_{SINK}$                                                       | Output Sink Current       | $V_{OUT} = 3V$                                    |     | 50    |      | mA    |

| $V_{OH}$                                                         | High Level Output Voltage | $I_O = -10\mu\text{A}$<br>$I_O = -200\mu\text{A}$ | ●   | 2.995 |      | V     |

| $V_{OL}$                                                         | Low Level Output Voltage  | $I_O = 10\mu\text{A}$<br>$I_O = 1.6\text{mA}$     | ●   | 2.7   | 2.99 | V     |

|                                                                  |                           |                                                   |     | 0.005 |      | V     |

|                                                                  |                           |                                                   | ●   | 0.09  | 0.4  | V     |

| <b><math>0V_{DD} = 2.5V</math></b>                               |                           |                                                   |     |       |      |       |

| $V_{OH}$                                                         | High Level Output Voltage | $I_O = -200\mu\text{A}$                           |     | 2.49  |      | V     |

| $V_{OL}$                                                         | Low Level Output Voltage  | $I_O = 1.6\text{mA}$                              |     | 0.09  |      | V     |

| <b><math>0V_{DD} = 1.8V</math></b>                               |                           |                                                   |     |       |      |       |

| $V_{OH}$                                                         | High Level Output Voltage | $I_O = -200\mu\text{A}$                           |     | 1.79  |      | V     |

| $V_{OL}$                                                         | Low Level Output Voltage  | $I_O = 1.6\text{mA}$                              |     | 0.09  |      | V     |

## 電源条件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 8)

| SYMBOL     | PARAMETER                     | CONDITIONS                              | MIN | TYP  | MAX | UNITS |    |

|------------|-------------------------------|-----------------------------------------|-----|------|-----|-------|----|

| $V_{DD}$   | Analog Supply Voltage         | (Note 9)                                | ●   | 2.85 | 3   | 3.4   | V  |

| $OV_{DD}$  | Output Supply Voltage         | (Note 9)                                | ●   | 0.5  | 3   | 3.6   | V  |

| $IV_{DD}$  | Supply Current                | Both ADCs at $f_S(\text{MAX})$          | ●   |      | 263 | 305   | mA |

| $P_{DISS}$ | Power Dissipation             | Both ADCs at $f_S(\text{MAX})$          | ●   |      | 790 | 915   | mW |

| $P_{SHDN}$ | Shutdown Power (Each Channel) | $SHDN = H, \bar{OE} = H, \text{No CLK}$ |     |      | 2   |       | mW |

| $P_{NAP}$  | Nap Mode Power (Each Channel) | $SHDN = H, \bar{OE} = L, \text{No CLK}$ |     |      | 15  |       | mW |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL           | PARAMETER                                    | CONDITIONS                         | MIN | TYP  | MAX | UNITS  |    |

|------------------|----------------------------------------------|------------------------------------|-----|------|-----|--------|----|

| $t_s$            | Sampling Frequency                           | (Note 9)                           | ●   | 1    | 125 | MHz    |    |

| $t_L$            | CLK Low Time                                 | Duty Cycle Stabilizer Off (Note 7) | ●   | 3.8  | 4   | 500    | ns |

|                  |                                              | Duty Cycle Stabilizer On (Note 7)  | ●   | 3    | 4   | 500    | ns |

| $t_H$            | CLK High Time                                | Duty Cycle Stabilizer Off (Note 7) | ●   | 3.8  | 4   | 500    | ns |

|                  |                                              | Duty Cycle Stabilizer On (Note 7)  | ●   | 3    | 4   | 500    | ns |

| $t_{AP}$         | Sample-and-Hold Aperture Delay               |                                    |     | 0    |     | ns     |    |

| $t_D$            | CLK to DATA Delay                            | $C_L = 5\text{pF}$ (Note 7)        | ●   | 1.4  | 2.7 | 5.4    | ns |

| $t_c$            | CLK to CLKOUT Delay                          | $C_L = 5\text{pF}$ (Note 7)        | ●   | 1.4  | 2.7 | 5.4    | ns |

|                  | DATA to CLKOUT Skew                          | $(t_D - t_c)$ (Note 7)             | ●   | -0.6 | 0   | 0.6    | ns |

| $t_{MD}$         | MUX to DATA Delay                            | $C_L = 5\text{pF}$ (Note 7)        | ●   | 1.4  | 2.7 | 5.4    | ns |

|                  | Data Access Time After $\bar{OE} \downarrow$ | $C_L = 5\text{pF}$ (Note 7)        | ●   |      | 4.3 | 10     | ns |

|                  | BUS Relinquish Time                          | (Note 7)                           | ●   |      | 3.3 | 8.5    | ns |

| Pipeline Latency |                                              |                                    |     |      | 5   | Cycles |    |

**Note 1:** 絶対最大定格はそれを超えるとデバイスに永続的な損傷を与える可能性がある値。また、絶対最大定格状態が長時間続くと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

**Note 2:** すべての電圧値は(注記がない限り)GNDと0GNDを接続したグランドを基準にしている。

**Note 3:** これらのピンの電圧をGNDより低くするか $V_{DD}$ より高くすると、内部のダイオードによってクランプされる。この製品はGNDより低い、または $V_{DD}$ より高い電圧で、ラッピングアップを起こさずに100mA以上の入力電流を処理することができる。

**Note 4:** 注記がない限り、 $V_{DD} = 3\text{V}$ 、 $f_{\text{SAMPLE}} = 125\text{MHz}$ 、入力レンジ = 差動ドライブで $2\text{V}_{\text{p-p}}$ 。

**Note 5:** 積分非直線性は、伝達曲線の実際のエンドポイントを通過する直線からのコードの偏差として定義されている。偏差は量子化帯域の中心から測定される。

**Note 6:** オフセット誤差は、出力コードが00 0000 0000 0000と11 1111 1111 1111の間を行ったり来たりするときに、-0.5LSBから測定したオフセット電圧。

**Note 7:** 設計によって保証されているが、テストされていない。

**Note 8:**  $V_{DD} = 3\text{V}$ 、 $f_{\text{SAMPLE}} = 125\text{MHz}$ 、入力レンジ = 差動ドライブで $1\text{V}_{\text{p-p}}$ 。消費電流と消費電力は、両チャネルがアクティブなときの両チャネルの合計。

**Note 9:** 推奨動作条件。

## 標準的性能特性

クロストークと入力周波数

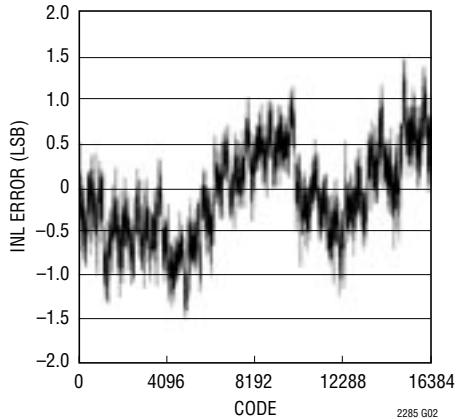

標準INL、2Vレンジ、125Msps

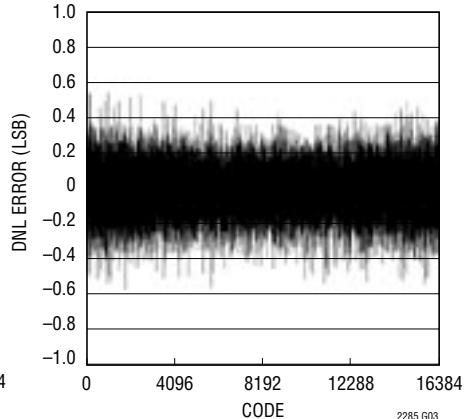

標準DNL、2Vレンジ、125Msps

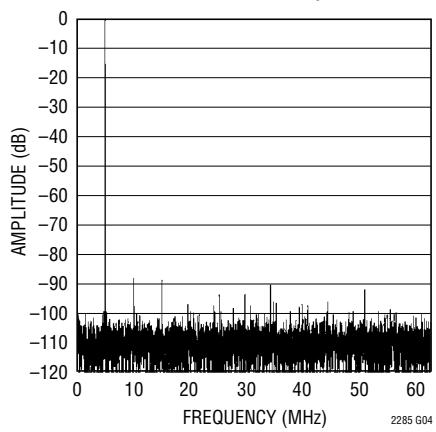

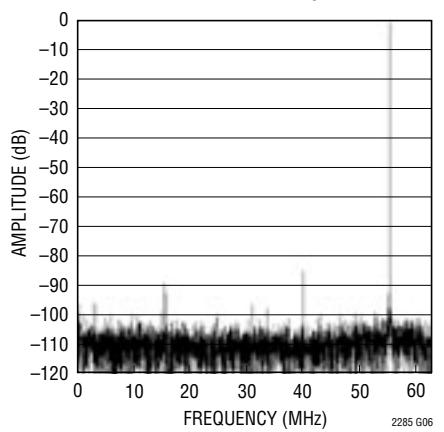

8192ポイントのFFT、 $f_{IN} = 5\text{MHz}$ 、

-1dB、2Vレンジ、125Msps

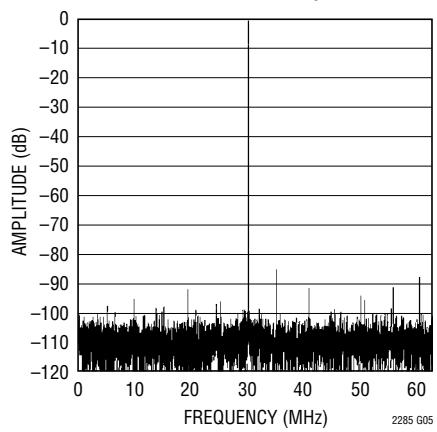

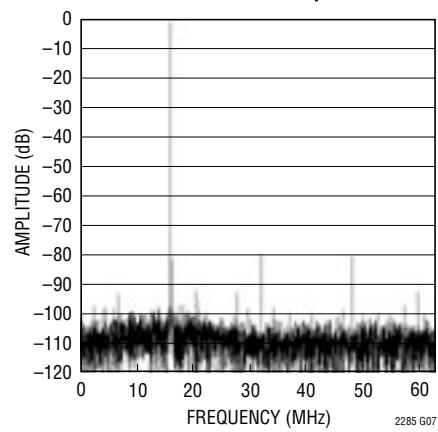

8192ポイントのFFT、 $f_{IN} = 30\text{MHz}$ 、

-1dB、2Vレンジ、125Msps

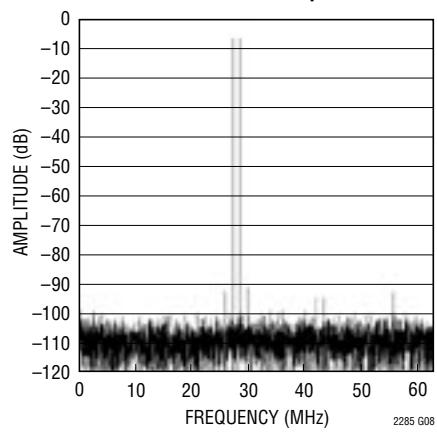

8192ポイントのFFT、 $f_{IN} = 70\text{MHz}$ 、

-1dB、2Vレンジ、125Msps

8192ポイントのFFT、 $f_{IN} = 140\text{MHz}$ 、

-1dB、2Vレンジ、125Msps

8192ポイントの2トーンFFT、

$f_{IN} = 28.2\text{MHz}$ および $26.8\text{MHz}$ 、

-1dB、2Vレンジ、125Msps

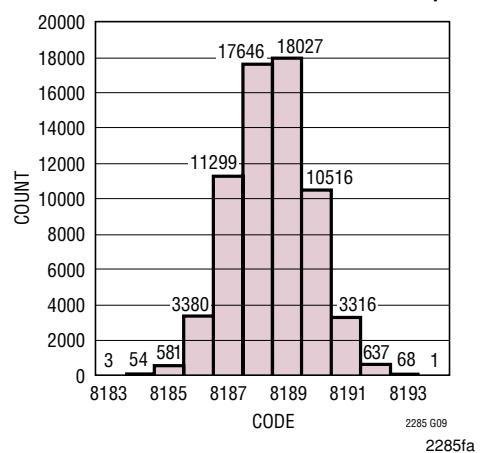

入力接地のヒストグラム、125Msps

## 標準的性能特性

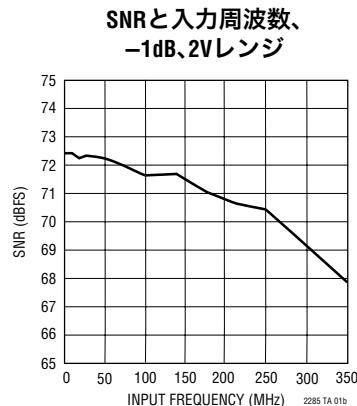

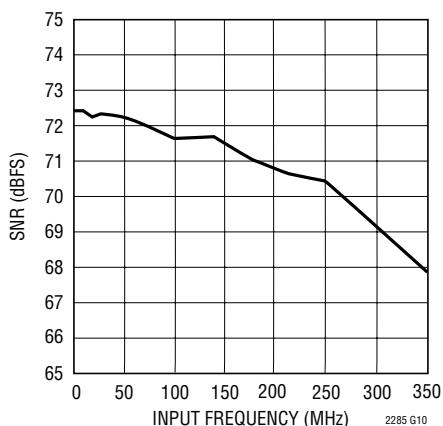

SNRと入力周波数、

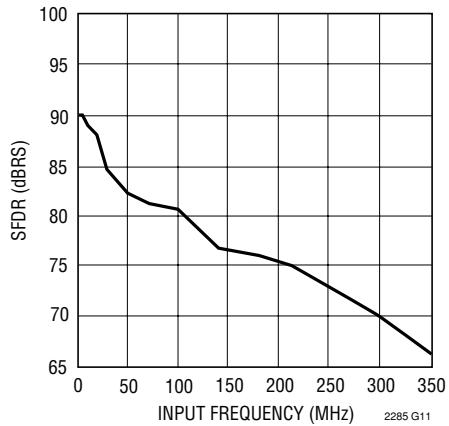

-1dB、2Vレンジ、125MspsSFDRと入力周波数、

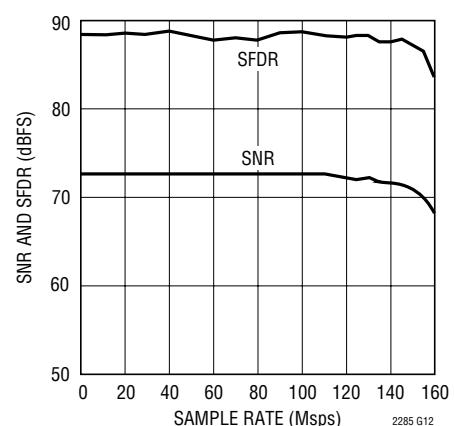

-1dB、2Vレンジ、125MspsSNRおよびSFDRとサンプリング・

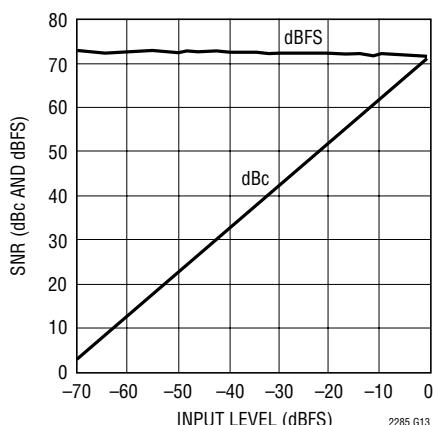

レート、2Vレンジ、 $f_{IN} = 5\text{MHz}$ 、-1dBSNRと入力レベル、 $f_{IN} = 70\text{MHz}$ 、

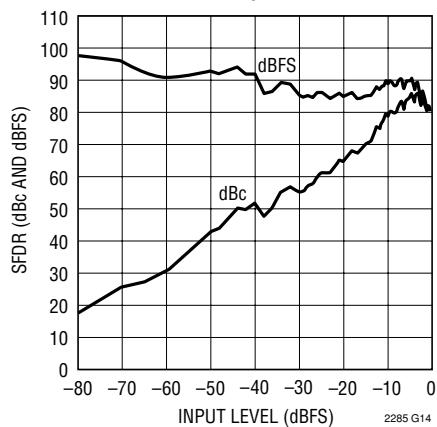

2Vレンジ、125MspsSFDRと入力レベル、 $f_{IN} = 70\text{MHz}$ 、

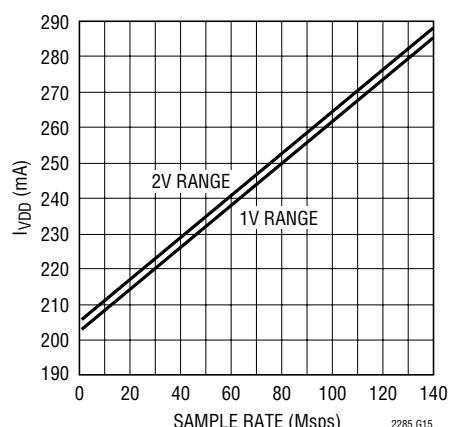

2Vレンジ、125MspsI<sub>VDD</sub>とサンプリング・レート、

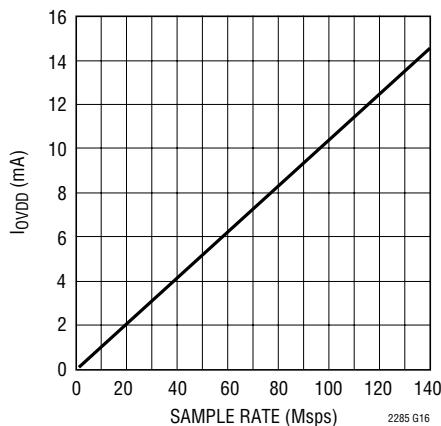

5MHzの正弦波入力、-1dBI<sub>VDD</sub>とサンプリング・レート、

5MHzの正弦波入力、-1dB、

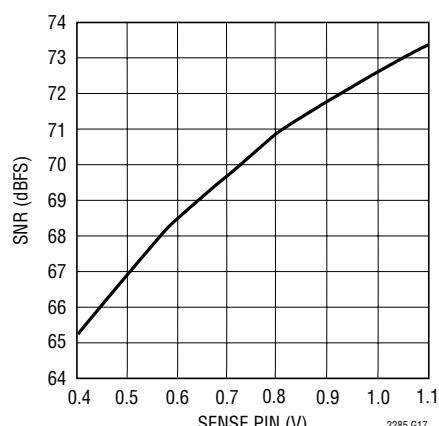

OV<sub>DD</sub> = 1.8VSNRとSENSE、 $f_{IN} = 5\text{MHz}$ 、-1dB

## ピン機能

**A<sub>INA</sub><sup>+</sup>(ピン1):**チャネルAの正の差動アナログ入力。

**A<sub>INA</sub><sup>-</sup>(ピン2):**チャネルAの負の差動アナログ入力。

**REFHA(ピン3、4):**チャネルAの“H”リファレンス。一緒に短絡し、ピンのできるだけ近くで0.1 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン5とピン6にバイパスしてください。さらに、追加の2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン5とピン6にバイパスし、1 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスしてください。

**REFLA(ピン5、6):**チャネルAの“L”リファレンス。一緒に短絡し、ピンのできるだけ近くで0.1 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン3とピン4にバイパスしてください。さらに、追加の2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン3とピン4にバイパスし、1 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスしてください。

**V<sub>DD</sub>(ピン7、10、18、63):**アナログ3V電源。0.1 $\mu$ Fのセラミック・チップ・コンデンサを使用してGNDにバイパスしてください。

**CLKA(ピン8):**チャネルAのクロック入力。立ち上がりエッジで入力のサンプリングが開始されます。

**CLKB(ピン9):**チャネルBのクロック入力。立ち上がりエッジで入力のサンプリングが開始されます。

**REFLB(ピン11、12):**チャネルBの“L”リファレンス。一緒に短絡し、ピンのできるだけ近くで0.1 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン13とピン14にバイパスしてください。さらに、追加の2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン13とピン14にバイパスし、1 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスしてください。

**REFHB(ピン13、14):**チャネルBの“H”リファレンス。一緒に短絡し、ピンのできるだけ近くで0.1 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン11とピン12にバイパスしてください。さらに、追加の2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン11とピン12にバイパスし、1 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスしてください。

**A<sub>INB</sub><sup>-</sup>(ピン15):**チャネルBの負の差動アナログ入力。

**A<sub>INB</sub><sup>+</sup>(ピン16):**チャネルBの正の差動アナログ入力。

**GND(ピン17、64):**ADCの電源グランド。

**SENSEB(ピン19):**チャネルBのリファレンス・プログラミング・ピン。SENSEBをV<sub>CMB</sub>に接続すると、内部リファレンスと±0.5Vの入力レンジが選択されます。V<sub>DD</sub>に接続すると、内部リファレンスと±1Vの入力レンジが選択され

ます。0.5Vより大きく1Vより小さい外部リファレンスをSENSEBに印加すると、±VSENSEBの入力レンジが選択されます。±1Vが最大有効入力レンジです。

**V<sub>CMB</sub>(ピン20):**チャネルBの出力と入力の1.5V同相バイアス。2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスしてください。V<sub>CMA</sub>に接続してはなりません。

**MUX(ピン21):**デジタル出力のマルチプレクサ制御。MUXが“H”的とき、チャネルAはDA0～DA13に出力され、チャネルBはDB0～DB13に出力されます。MUXが“L”的とき、出力バスが入れ替わり、チャネルAはDB0～DB13に出力され、チャネルBはDA0～DA13に出力されます。両方のチャネルを1本の出力バスに多重化するには、MUX、CLKAおよびCLKBと一緒に接続します。(これは、80Mspsを上回るクロック周波数には推奨できません。)

**SHDNE(ピン22):**チャネルBのシャットダウン・モード選択ピン。SHDNEとOEBをGNDに接続すると通常動作になります。SHDNEをGNDに接続し、OEBをV<sub>DD</sub>に接続すると通常動作になります。出力がハイ・インピーダンスになります。SHDNEをV<sub>DD</sub>に接続し、OEBをGNDに接続するとナップ・モードになります。出力がハイ・インピーダンスになります。SHDNEとOEBをV<sub>DD</sub>に接続するとスリープ・モードになります。出力がハイ・インピーダンスになります。

**OEB(ピン23):**チャネルBの出力イネーブル・ピン。SHDNEピンの機能を参照してください。

**DB0-DB13(ピン24～30、33～39):**チャネルBのデジタル出力。DB13がMSBです。

**OGND(ピン31、50):**出力ドライバのグランド。

**OV<sub>DD</sub>(ピン32、49):**出力ドライバの正電源。0.1 $\mu$ Fのセラミック・チップ・コンデンサを使用してGNDにバイパスしてください。

**CLKOUT(ピン40):**データ・レディ・クロック出力。CLKOUTの立ち下がりエッジでデータをラッチします。CLKOUTはCLKBから得られます。同時動作をさせるにはCLKAをCLKBに接続します。

**DA0～DA13(ピン41～48、51～56):**チャネルAのデジタル出力。DA13がMSBです。

**OF(ピン57):**オーバーフロー/アンダーフロー出力。チャネルAまたはチャネルBのいずれかでオーバーフローまたはアンダーフローが発生した場合、“H”になります。

**OEA(ピン58):**チャネルAの出力イネーブル・ピン。SHDNAピンの機能を参照してください。

## ピン機能

**SHDNA(ピン59):** チャネルAのシャットダウン・モード選択ピン。SHDNAと $\overline{OEA}$ をGNDに接続すると通常動作になり、出力がイネーブルされます。SHDNAをGNDに接続し、 $\overline{OEA}$ を $V_{DD}$ に接続すると通常動作になり、出力がハイ・インピーダンスになります。SHDNAを $V_{DD}$ に接続し、 $OEA$ をGNDに接続するとナップ・モードになり、出力がハイ・インピーダンスになります。SHDNAと $\overline{OEA}$ を $V_{DD}$ に接続するとスリープ・モードになり、出力がハイ・インピーダンスになります。

**MODE(ピン60):** 出力のフォーマットとクロック・デューティ・サイクル・スタビライザの選択ピン。MODEは両方のチャネルを制御することに注意してください。MODEをGNDに接続すると、オフセット・バイナリの出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオフします。1/3 $V_{DD}$ に接続すると、オフセット・バイナリの出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオンします。2/3 $V_{DD}$ に接続すると、2の補数の出力フォーマットが選択

され、クロック・デューティ・サイクル・スタビライザがオンします。 $V_{DD}$ に接続すると、2の補数の出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオフします。

**$V_{CMA}$ (ピン61):** チャネルAの出力と入力の1.5V同相バイアス。2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスしてください。 $V_{CMB}$ に接続してはなりません。

**SENSEA(ピン62):** チャネルAのリファレンス・プログラミング・ピン。SENSEAを $V_{CMA}$ に接続すると、内部リファレンスと $\pm 0.5V$ の入力レンジが選択されます。 $V_{DD}$ に接続すると、内部リファレンスと $\pm 1V$ の入力レンジが選択されます。0.5Vより大きく1Vより小さい外部リファレンスをSENSEAに印加すると、 $\pm V_{SENSEA}$ の入力レンジが選択されます。 $\pm 1V$ が最大有効入力レンジです。

**GND(露出パッド)(ピン65):** ADCの電源グランド。パッケージ底面の露出パッドはグランドに半田付けする必要があります。

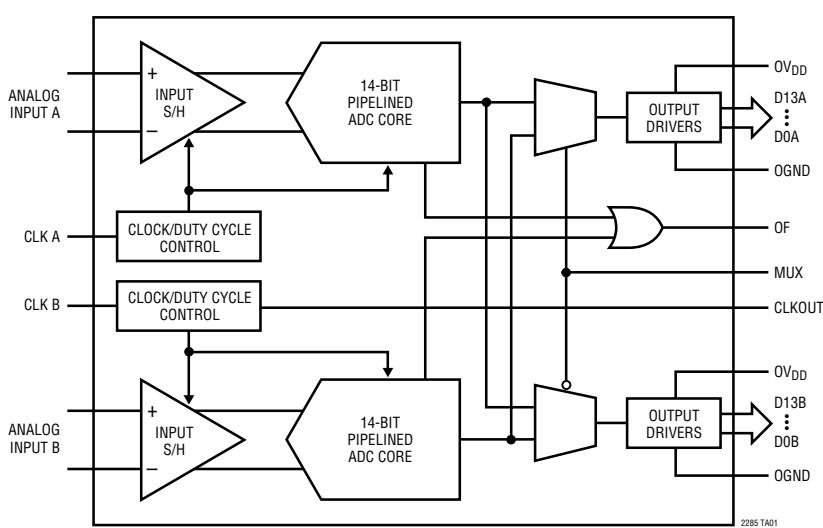

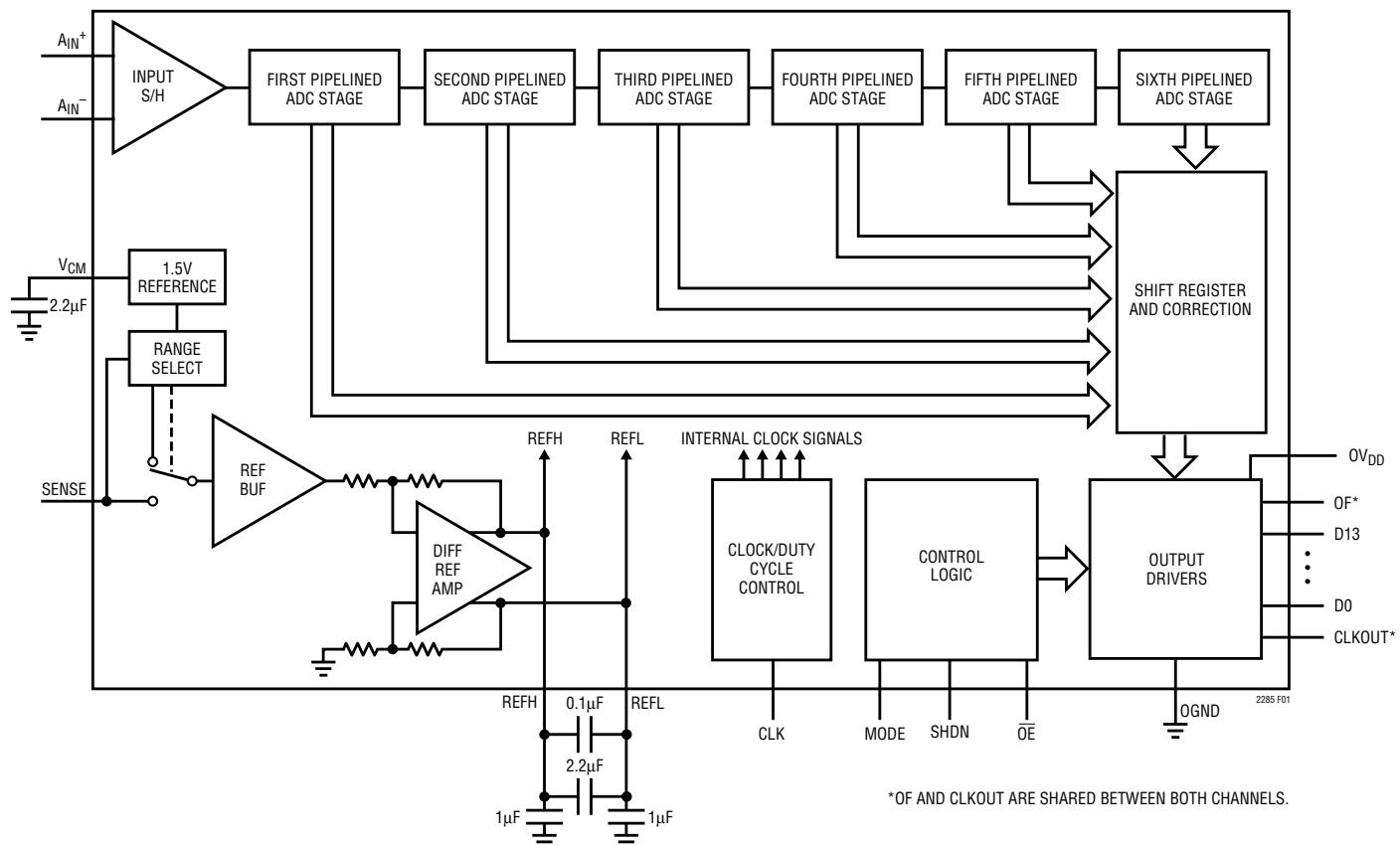

## 機能ブロック図

図1. 機能ブロック図(1チャネルのみ表示)

2285f01

\*OF AND CLKOUT ARE SHARED BETWEEN BOTH CHANNELS.

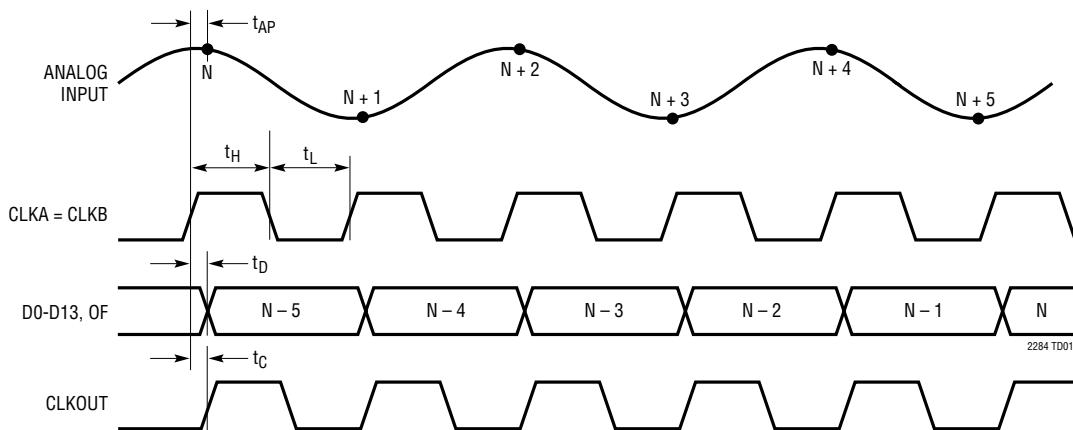

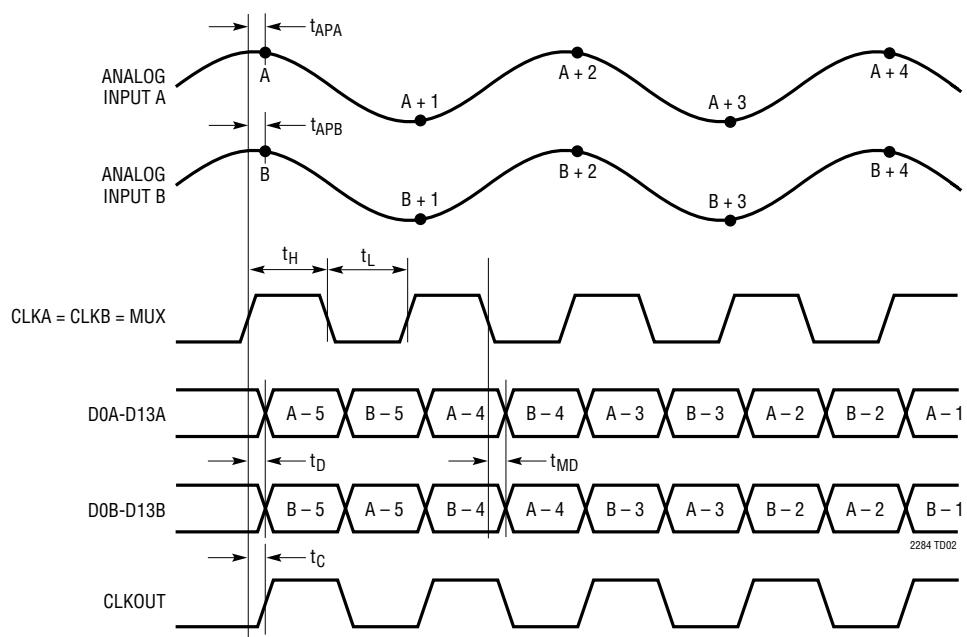

## タイミング図

デュアル・デジタル出力バスのタイミング

(1チャネルのみ表示)

多重化されたデジタル出力バスのタイミング

## アプリケーション情報

### ダイナミック特性

#### 信号とノイズ+歪みの比

信号とノイズ+歪みの比[S/(N+D)]は、ADC出力での基本入力周波数のRMS振幅と他のすべての周波数成分のRMS振幅の比です。出力は、DCからサンプリング周波数の1/2までの周波数帯域に制限されます。

#### SN比(SNR)

信号とノイズの比(SNR)は基本入力周波数のRMS振幅と、最初の5つの高調波およびDCを除く他のすべての周波数成分のRMS振幅の比です。

#### 全高調波歪み

全高調波歪みは、入力信号のすべての高調波のRMS値の合計と基本波のRMS値の比です。帯域外高調波は、DCからサンプリング周波数の1/2までの周波数帯域に限定されます。THDは次式で表されます。

$$THD = 20 \log (\sqrt{V2^2 + V3^2 + V4^2 + \dots + Vn^2} / V1)$$

ここで、V1は基本周波数のRMS振幅であり、V2からVnは2次高調波からn次高調波までの振幅です。このデータシートで計算されているTHDには、5次までの高調波がすべて使用されています。

#### 混変調歪み

ADCの入力信号が複数のスペクトル成分から構成される場合、ADCの伝達関数の非直線性によって、THDに加えて混変調歪み(IMD)が生じる可能性があります。IMDは、周波数が異なる別の正弦波入力が現れたときに、ある正弦波入力に生じる変化です。

周波数がfaとfbの2つの純粋な正弦波がADCの入力に供給されると、ADCの伝達関数の非直線性によって  $mfa \pm nfb$  の和と差の周波数で歪み積を生じる可能性があります。ここで、mとnは0、1、2、3などです。3次の混変調積は  $2fa + fb$ 、 $2fb + fa$ 、 $2fa - fb$  および  $2fb - fa$  です。混変調歪みは、最大3次混変調積のRMS値に対する、どちらかの入力トーンのRMS値の比として定義されます。

#### スプリアスフリー・ダイナミックレンジ(SFDR)

スプリアスフリー・ダイナミックレンジは、入力信号とDC

を除いた最大のスペクトル成分であるピーク高調波、つまりスプリアス・ノイズです。この値は、フルスケール入力信号のRMS値を基準にしたデシベル値で表されます。

#### 入力帯域幅

入力帯域幅は、フルスケール入力信号に対して、再生される基本成分の振幅が3dBだけ減少する入力周波数です。

#### アーチャ遅延時間

CLKが電源電圧の中点に達したときから入力信号がサンプル・ホールド回路によってホールドされる瞬間までの時間。

#### アーチャ遅延ジッタ

変換ごとのアーチャ遅延時間の変動。このランダムな変動によって、AC入力のサンプリング時にノイズが生じます。ジッタだけによるSNRは次のようにになります。

$$SNR_{JITTER} = -20 \log (2\pi \cdot f_{IN} \cdot t_{JITTER})$$

#### クロストーク

クロストークは、(フルスケール信号でドライブされている)一方のチャネルから(-1dBFSの信号でドライブされている)他方のチャネルへのカップリングです。

#### コンバータの動作

図1に示すように、LTC2285はデュアルCMOSのパイプライン構成の多段コンバータです。このコンバータはパイプライン構成の6つのADC段を備えており、サンプリングされたアナログ入力は5サイクル後にデジタル値になります(「タイミング図」の項目を参照)。最適なAC特性を得るために、アナログ入力を差動でドライブする必要があります。コストに敏感なアプリケーションでは、アナログ入力をシングルエンドでドライブすることができますが、高調波歪みがわずかに増加します。CLK入力はシングルエンドです。LTC2285はCLK入力ピンの状態によって決定される2つのフェーズで動作します。

図1に示すパイプライン構成の各段は、ADC、再生DAC、および段間残余アンプを備えています。動作時、ADCは段への入力を量子化し、量子化された値はDACによって入力から差し引かれ、残余を生じます。残余は、残余アンプによって増幅されて出力されます。奇数段が残余を出力

## アプリケーション情報

しているとき偶数段がその残余を取得するように、またその逆になるように、後に続く段は位相がずれて動作します。

CLKが“L”的とき、アナログ入力はブロック図に示す「入力S/H」内部の入力サンプル・ホールド・コンデンサに差動で直接サンプリングされます。CLKが“L”から“H”に遷移する瞬間、サンプリングされた入力がホールドされます。CLKが“H”的間、ホールドされた入力電圧は、パイプライン構成の最初のADC段をドライブするS/Hアンプによってバッファれます。最初の段は、CLKがこの“H”的間にS/Hの出力を取得します。CLKが“L”に戻ると最初の段はその残余を生成し、この残余が2番目の段によって取得されます。同時に、入力のS/Hは再度アナログ入力を取得します。CLKが“H”に戻ると2番目の段はその残余を生成し、この残余が3番目の段によって取得されます。同様の過程が3番目、4番目、さらに5番目の段で繰り返され、5番目の段の残余は最終評価のために6番目の段のADCに送られます。

最初の段に続く各ADC段には、フラッシュ誤差とアンプのオフセット誤差を調節するための追加範囲があります。ADCの全段からの結果は、出力バッファに送る前にそれらの結果を補正ロジックで適切に結合できるように、デジタル動作で同期させます。

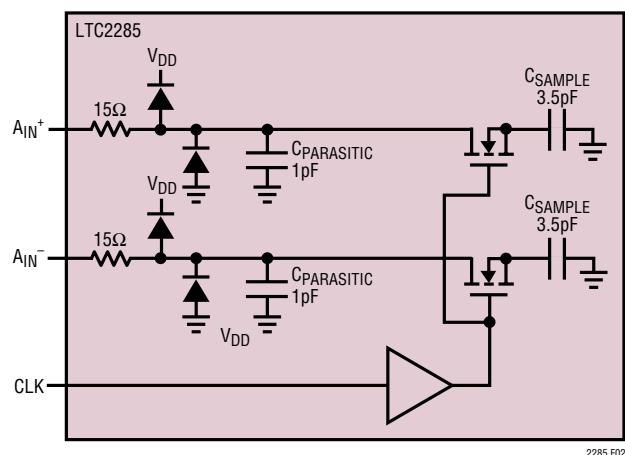

### サンプル/ホールド動作と入力ドライブ

#### サンプル/ホールド動作

LTC2285のCMOS差動サンプル・ホールドの等価回路を図2に示します。アナログ入力は、NMOSトランジスタを介してサンプリング・コンデンサ( $C_{SAMPLE}$ )に接続されています。各入力のところに示されているコンデンサ( $C_{PARASITIC}$ )は、各入力に関連した他のすべての容量の和です。

CLKが“L”的とき、サンプル・フェーズの間トランジスタはアナログ入力をサンプリング・コンデンサに接続するので、これらのコンデンサは差動入力電圧まで充電され、さらにこの電圧を追尾します。CLKが“L”から“H”に遷移するとき、サンプリングされた入力電圧はサンプリング・コンデンサにホールドされます。CLKが“H”的とき、ホールド・フェーズの間サンプリング・コンデンサは入力から切り離され、ホールドされた電圧はADCコアに渡されて処理されます。CLKが“H”から“L”に遷移すると、入力はサンプリング・コンデンサに再度接続され、新しいサンプルを収集します。サンプリング・コンデンサには直前のサンプルがまだホールドされているので、サンプル間の電圧変化に比例した充電グリッチがこのときに見られます。直前のサンプルと新しいサンプル間の変化が小さいと、入力に見られる充電グリッチは小さくなります。ナイ

図2. 等価入力回路

## アプリケーション情報

キスト周波数の近くの入力周波数で見られる変化のように入力の変化が大きければ、さらに大きな充電グリッチが見られます。

### シングルエンド入力

コストに敏感なアプリケーションでは、アナログ入力をシングルエンドでドライブすることができます。シングルエンド入力では高調波歪みとINLが増加しますが、SNRとDNLは変化しません。シングルエンド入力の場合、 $A_{IN^+}$ を入力信号でドライブし、 $A_{IN^-}$ を1.5Vまたは $V_{CM}$ に接続する必要があります。

### 同相バイアス

最適な特性を得るために、アナログ入力を差動でドライブする必要があります。各入力は1.5Vの同相電圧を中心として、2Vレンジでは $\pm 0.5V$ 、1Vレンジでは $\pm 0.25V$ の振幅が必要です。 $V_{CM}$ 出力ピンを使用して同相バイアス・レベルを与えることができます。 $V_{CM}$ は、トランスのセンタータップに直接接続してDC入力レベルを設定するか、またはオペアンプの差動ドライブ回路へのリファレンス・レベルとして設定することができます。 $V_{CM}$ ピンは、2.2 $\mu$ F以上のコンデンサを使用してADCの近くのグランドにバイパスする必要があります。

### 入力ドライブ・インピーダンス

すべての高性能高速ADCの場合と同様に、LTC2285のダイナミック性能は入力ドライブ回路(特に2次と3次の高調波)の影響を受けることがあります。ソース・インピーダンスとリアクタンスはSFDRに影響を与えることがあります。サンプル・ホールド回路は、CLKの立ち下がりエッジで3.5pFのサンプリング・コンデンサを入力ピンに接続してサンプリング周期を開始します。サンプリング周期はCLKが立ち上がるとき終了し、サンプリングされた入力をサンプリング・コンデンサにホールドします。入力回路は、理想的にはサンプリング周期 $1/(2F_{ENCODE})$ の間、サンプリング・コンデンサを完全に充電するのに十分なだけ高速である必要があります。ただし、これが常に可能だとは限らず、不完全なセトリングのためにSFDRが低下することがあります。不完全なセトリングの影響を最小限に抑えるため、サンプリング・グリッチができるだけリニアになるように設計されています。

最高性能を得るために、各入力のソース・インピーダンスを100 $\Omega$ 以下にすることを推奨します。差動入力のソース・インピーダンスは整合させる必要があります。よく整合していないと、偶数次高調波、特に2次高調波が大きくなります。

### 入力ドライブ回路

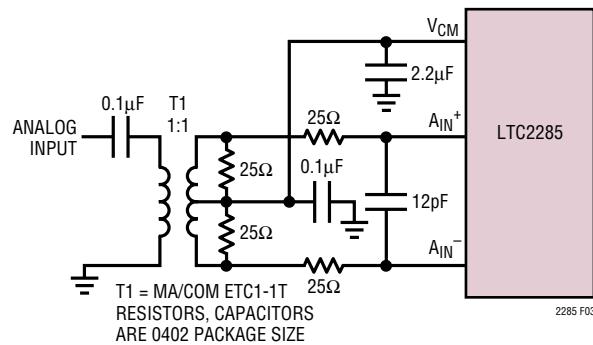

2次側にセンタータップを備えたRFトランスによってドライブされるLTC2285を図3に示します。2次側センタータップは $V_{CM}$ でDCバイアスされており、ADCの入力信号を最適DCレベルに設定します。トランスの2次側を終端するのは望ましいことです。これによりサンプル・ホールドによって生じる充電グリッチの同相経路が確保されるからです。図3は巻数比が1:1のトランスを示します。ADCから見たソース・インピーダンスが各ADC入力で100 $\Omega$ を超えないように、別の巻数比を使用することもできます。トランスを使用する場合の不利な点は低周波数応答の低下です。ほとんどの小型RFトランスは、1MHzより低い周波数での性能が良くありません。

図3. トランスを使用したシングルエンドから差動への変換

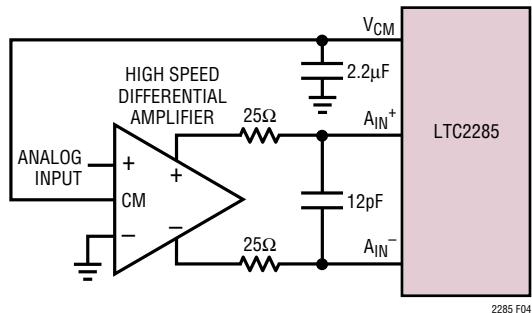

差動アンプを使用してシングルエンド入力信号を差動入力信号に変換する例を図4に示します。この方法の利点は低い周波数の入力応答が確保できることです。ただし、ほとんどのオペアンプでは利得帯域幅の制限により、高い入力周波数でのSFDRが制限されます。

# LTC2285

## アプリケーション情報

図4. アンプを使用した差動ドライブ

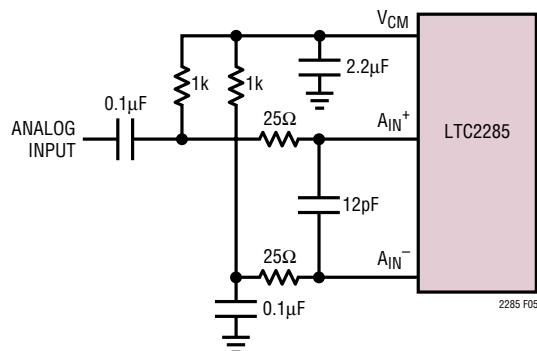

シングルエンドの入力回路を図5に示します。アナログ入力から見たインピーダンスを整合させる必要があります。歪みを低く抑える必要がある場合、この回路は推奨できません。

図5. シングルエンドのドライブ

アナログ入力に接続されている25Ωの抵抗と12pFのコンデンサは2つの役目を果たします。サンプル・ホールドの充電グリッッチからドライブ回路を絶縁し、コンバータの入力の広帯域ノイズを制限します。

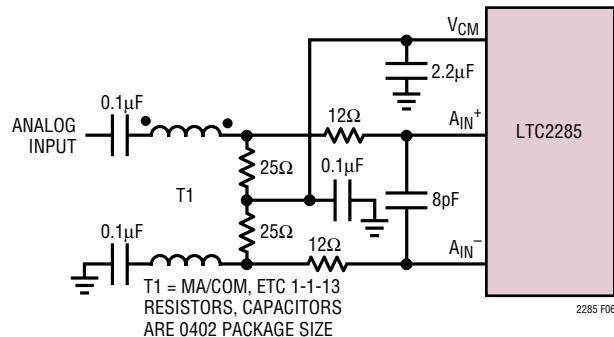

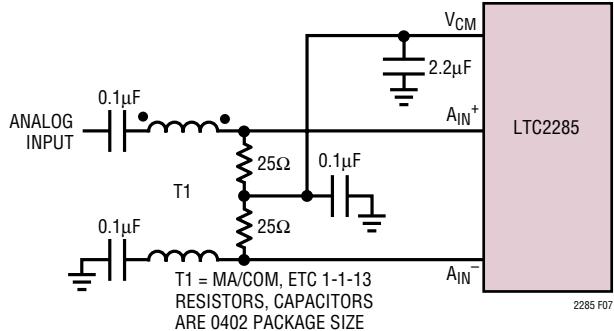

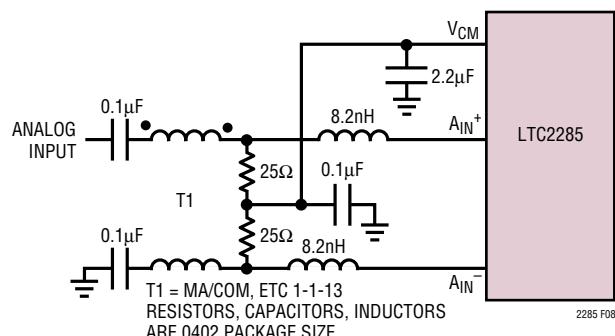

70MHzを超す入力周波数では、図6、図7、および図8の入力回路を推奨します。センター・タップ付き磁束結合型トランジスに比べて、バラン・トランジスは高周波数応答が優れています。カップリング・コンデンサにより、アナログ入力を1.5VにDCバイアスすることができます。図8の直列インダクタはインピーダンス整合用素子で、ADCの帯域幅を最大にします。

図6. 70MHz～170MHzの入力周波数用の推奨フロントエンド回路

図7. 170MHz～300MHzの入力周波数用の推奨フロントエンド回路

図8. 300MHzを超える入力周波数用の推奨フロントエンド回路

## アプリケーション情報

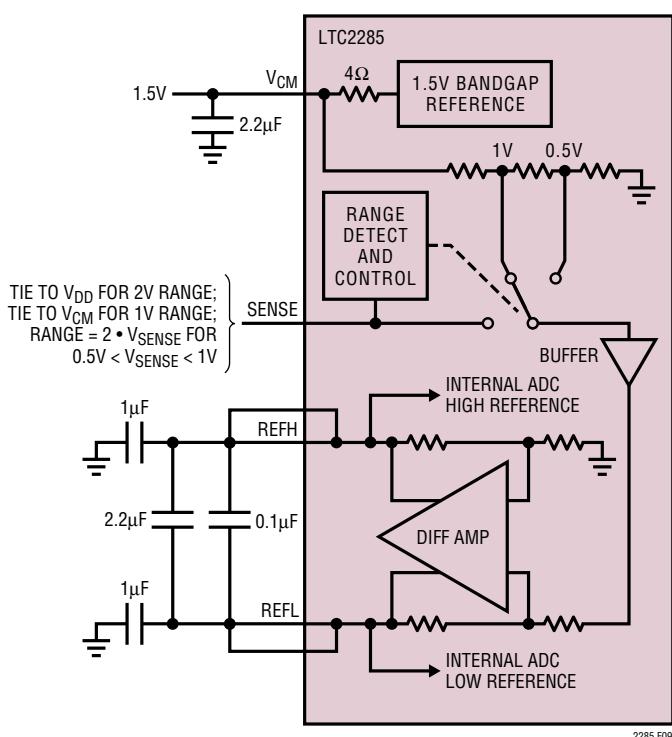

### リファレンスの動作

1.5Vのバンドギャップ・リファレンス、差動アンプ、スイッチングと制御の回路で構成されるLTC2285のリファレンス回路を図9に示します。内部電圧リファレンスは、ピンで選択可能な2V(差動±1V)または1V(差動±0.5V)の2つの入力レンジに設定することができます。SENSEピンをV<sub>DD</sub>に接続すると2Vレンジが選択され、SENSEピンをV<sub>CM</sub>に接続すると1Vレンジが選択されます。

1.5Vのバンドギャップ・リファレンスは2つの機能を果たします。このリファレンスの出力は、任意の外部入力回路の同相電圧を設定するためのDCバイアス点を提供します。さらに、このリファレンスは差動アンプと一緒に使用され、内部のADC回路が必要とする差動リファレンス・レベルを生成します。1.5Vリファレンスの出力(V<sub>CM</sub>)には外付けのバイパス・コンデンサが必要です。このコンデンサは、内部回路と外部回路のための、グランドへの高周波で低インピーダンスの経路として機能します。

差動アンプはADCの“H”リファレンスと“L”リファレンスを生成します。高速スイッチング回路がこれらの出力に接続されています。

図9. 等価リファレンス回路

続されているので、これらの出力は外部でバイパスする必要があります。各出力には2つのピンが備わっています。複数の出力ピンは、パッケージのインダクタンスを減らすために必要です。図9に示すように、バイパス・コンデンサを接続する必要があります。各ADCチャネルは、それぞれにバイパス・コンデンサが接続された独立したリファレンスを備えています。2つのチャネルは同じ入力レンジまたは異なる入力レンジで使用することができます。

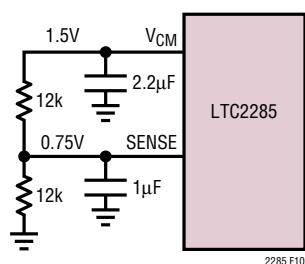

ピンで選択可能なレンジの間の他の電圧レンジは、図10に示すように、2つの外付け抵抗を使用して設定することができます。外部リファレンスを使用し、その出力を直接または抵抗分割器を介してSENSEに印加することができます。ロジック・デバイスを使用してSENSEピンをドライブすることは推奨できません。SENSEピンは、できるだけコンバータの近くで適切なレベルに接続してください。SENSEピンを外部からドライブする場合、1μFのセラミック・コンデンサを使用してデバイスのできるだけ近くでグランドにバイパスしてください。チャネルの整合を最良にするためには、外部リファレンスをSENSEAとSENSEBに接続します。

図10. 1.5VレンジのADC

### 入力レンジ

入力レンジはアプリケーションに基づいて設定することができます。2V入力レンジは、優れたSFDRを保ったまま最良のSNRを実現します。1V入力レンジのSFDR性能はさらに優れていますが、SNRが5.7dBだけ低下します。「標準的性能特性」の項目を参照してください。

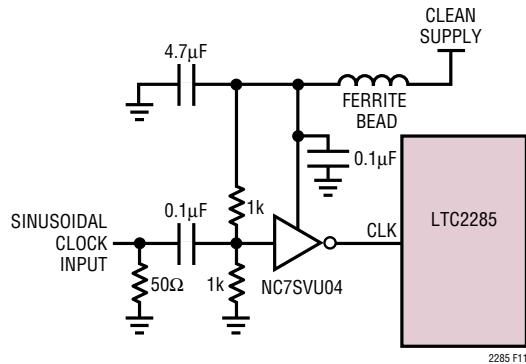

### クロック入力のドライブ

CLK入力はCMOSまたはTTLレベルの信号で直接ドライブすることができます。CLKピンの前にジッタが小さい方形波発生回路を置いて、正弦波のクロックを使用することもできます(図11)。

# LTC2285

## アプリケーション情報

図11. 正弦波のシングルエンドCLKドライブ

LTC2285のノイズ特性は、アナログ入力に依存するのと同程度にクロック信号の品質に依存することがあります。クロック信号に含まれるすべてのノイズは新たなアーチャ・ジッタを生じ、このジッタは本来のADCアーチャ・ジッタにRMSとして加算されます。

高い入力周波数をデジタル変換する場合など、ジッタが致命的なアプリケーションではできるだけ大きな振幅を使用してください。また、正弦波信号でADCをクロック駆動する場合、クロック信号にフィルタをかけてソースから生じる広帯域ノイズと歪み積を減らします。

CLKAとCLKBを短絡して同じクロック・ソースでドライブすることを推奨します。2つのチャネルがアナログ入力をサンプリングする間に小さな遅延時間が必要な場合、CLKAとCLKBを2つの異なった信号でドライブすることができます。この遅延が1nsを超えると、デバイスの性能が低下することがあります。CLKAとCLKBは非同期の信号でドライブしてはなりません。

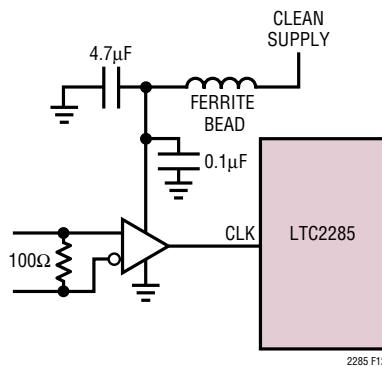

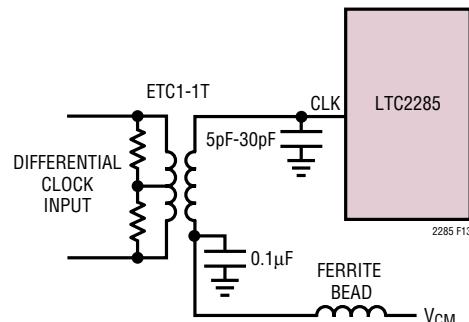

差動クロックをシングルエンドCLK入力に変換する別の方法を、図12と図13に示します。トランスを使用した場合、位相ノイズへの効果は期待できません。LVDSまたはPECLからCMOSへの変換器の場合、70MHz以下ではほとんど劣化しませんが、140MHzではトランスを使用した場合に比べてSNRが劣化します。受信信号には、SNRがどれだけ劣化しても十分に耐えることができる性質も備わっています。WCDMAやOFDMなどの(公称パワーレベルがフルスケールよりも少なくとも6dB～8dB低くなければならない)波高率が大きい信号では、これらの変換器を使用してもあまり影響はありません。

IF LVDS USE FIN1002 OR FIN1018.

FOR PECL, USE AZ1000ELT21 OR SIMILAR

図12. LVDSまたはPECLからCMOSへの

変換器を使用したCLKドライブ

図13. トランスを使用したLVDSまたはPECLのCLKドライブ

この例のトランスは、使用する信号に適した終端器を使用して終端することができます。低電圧の差動信号を考慮すると、1:4のインピーダンス比のトランスを使用することが望ましい場合があります。差動信号が異なるブレーンで始まる場合、センタータップはコンデンサを介してADCの近くでグランドにバイパスすることができます。入力にコンデンサを使用するとピーピングを生じることがあり、また伝送ラインの長さによって10Ω～20Ωの直列抵抗が必要になります。この抵抗は、隣接するデジタル信号によってクロック・ラインに誘導される可能性のある高周波ノイズのローパス・フィルタおよび反射の減衰メカニズムとして機能します。

### 最大変換レートと最小変換レート

LTC2285の最大変換レートは125Mspsです。LTC2285のサンプリング・レートの下限は、サンプル・ホールド回路のドリープによって決定されます。このADCのパイプライン

## アプリケーション情報

ン構成のアーキテクチャでは、アナログ信号を小さな値のコンデンサに保存することが基本です。接合部のリーク電流によってコンデンサを放電します。LTC2285の規定最小動作周波数は1Mspsです。

### クロック・デューティ・サイクル・スタビライザ

入力クロックのデューティ・サイクルが50%でない場合でも、オプションのクロック・デューティ・サイクル・スタビライザ回路によって高性能を確保することができます。多くのアプリケーションでクロック・デューティ・サイクル・スタビライザの使用が推奨されています。クロック・デューティ・サイクル・スタビライザを使用するには、外付け抵抗を使ってMODEピンを1/3V<sub>DD</sub>または2/3V<sub>DD</sub>に接続します。

この回路は、CLKピンの立ち上がりエッジを使用してアナログ入力をサンプリングします。CLKの立ち下がりエッジは無視され、フェーズロック・ループによって内部立ち下がりエッジが作られます。入力クロックのデューティ・サイクルは40%～60%の範囲で変えることができ、クロック・デューティ・サイクル・スタビライザは内部デューティ・サイクルを50%に保ちます。クロックが長時間オフすると、デューティ・サイクル・スタビライザ回路のPLLが入力クロックにロックするのに100クロック・サイクルを必要とします。

サンプリング・レートを即座に変化させる必要があるアプリケーションでは、クロック・デューティ・サイクル・スタビライザをディスエーブルすることができます。デューティ・サイクル・スタビライザをディスエーブルする場合には、サンプリング・クロックのデューティ・サイクルが50%( $\pm 5\%$ )になるように注意してください。

表1. 出力コードと入力電圧

| $A_{IN^+} - A_{IN^-}$<br>(2V Range) | OF | D13 - D0<br>(Offset Binary) | D13 - D0<br>(2's Complement) |

|-------------------------------------|----|-----------------------------|------------------------------|

| >+1.000000V                         | 1  | 11 1111 1111 1111           | 01 1111 1111 1111            |

| +0.999878V                          | 0  | 11 1111 1111 1111           | 01 1111 1111 1111            |

| +0.999756V                          | 0  | 11 1111 1111 1110           | 01 1111 1111 1110            |

| +0.000122V                          | 0  | 10 0000 0000 0001           | 00 0000 0000 0001            |

| 0.000000V                           | 0  | 10 0000 0000 0000           | 00 0000 0000 0000            |

| -0.000122V                          | 0  | 01 1111 1111 1111           | 11 1111 1111 1111            |

| -0.000244V                          | 0  | 01 1111 1111 1110           | 11 1111 1111 1110            |

| -0.999878V                          | 0  | 00 0000 0000 0001           | 10 0000 0000 0001            |

| -1.000000V                          | 0  | 00 0000 0000 0000           | 10 0000 0000 0000            |

| <-1.000000V                         | 1  | 00 0000 0000 0000           | 10 0000 0000 0000            |

### デジタル出力

表1は、アナログ入力電圧、デジタル・データ・ビット、およびオーバーフロー・ビット間の相関を示します。OFは、チャネルAまたはチャネルBのいずれかでオーバーフローまたはアンダーフローが発生した場合に“H”になります。

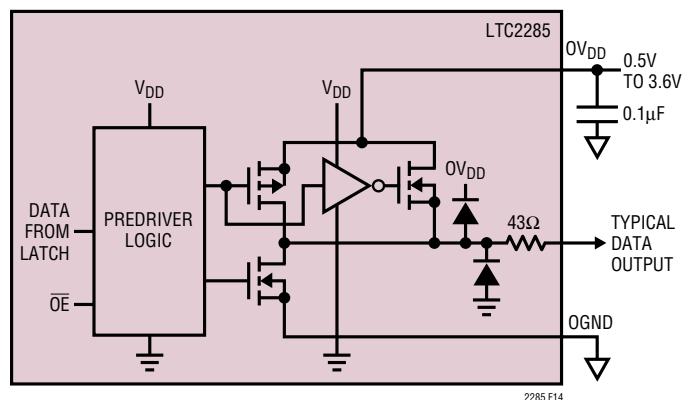

### デジタル出力バッファ

1つの出力バッファの等価回路を図14に示します。各バッファはOV<sub>DD</sub>とOGNDから電力を供給され、ADCの電源とグランドから絶縁されています。出力ドライバにNチャネル・トランジスタが追加されているので、低い電圧まで動作可能です。出力に直列接続された内部抵抗によって、外部回路から見ると出力が50Ωに見えるので、外付けの減衰抵抗が不要な場合があります。

すべての高速/高分解能コンバータの場合と同様、デジタル出力負荷が性能に影響を与えることがあります。デジタル出力と敏感な入力回路の間に生じるおそれのある相互反応を抑えるため、LTC2285のデジタル出力はできるだけ小さな容量性負荷をドライブするようにします。全速動作では、容量性負荷を10pF未満に保つ必要があります。

OV<sub>DD</sub>電圧を低くすることも、デジタル出力からの干渉を減らすのに役立ちます。

図14. デジタル出力バッファ

## アプリケーション情報

### データのフォーマット

LTC2285のパラレル・デジタル出力は、MODEピンを使用して、オフセット・バイナリ形式または2の補数形式に設定できます。MODEをGNDまたは $1/3V_{DD}$ に接続すると、オフセット・バイナリの出力フォーマットが選択されます。MODEを $2/3V_{DD}$ または $V_{DD}$ に接続すると、2の補数の出力フォーマットが選択されます。外付け抵抗分割器を使用して、 $1/3V_{DD}$ または $2/3V_{DD}$ のロジック値を設定することができます。MODEピンのロジック状態を表2に示します。

表2. MODEピンの機能

| MODE Pin    | Output Format  | Clock Duty Cycle Stabilizer |

|-------------|----------------|-----------------------------|

| 0           | Offset Binary  | Off                         |

| $1/3V_{DD}$ | Offset Binary  | On                          |

| $2/3V_{DD}$ | 2's Complement | On                          |

| $V_{DD}$    | 2's Complement | Off                         |

### オーバーフロー・ビット

OFがロジック“H”を出力しているとき、チャネルAまたはチャネルBのコンバータはオーバーレンジまたはアンダーレンジ状態です。両方のチャネルがOFピンを共有していますが、これはLTC2284やLTC2299などの低速のピン互換デバイスでは対応していません。チャネルAがスリープ・モードまたはナップ・モード状態では、OFはディスエーブルされます。

### 出力クロック

ADCには、デジタル出力(CLKOUT)として使用できる、CLKB入力を遅延させた信号が備わっています。CLKOUTピンの立ち下がりエッジはデジタル出力データのラッチに使用できます。チャネルBがスリープ・モードまたはナップ・モード状態では、CLKOUTはディスエーブルされます。

### 出力ドライバの電源

出力専用の電源ピンとグランド・ピンが備わっているので、出力ドライバをアナログ回路から絶縁することができます。デジタル出力バッファの電源(OV<sub>DD</sub>)は、ドライブされるロジックと同じ電源に接続する必要があります。たとえば、1.8V電源から電力を供給されるDSPをコンバータがドライブする場合、OV<sub>DD</sub>は同じ1.8V電源に接続します。

OV<sub>DD</sub>は、500mV～3.6Vの任意の電圧で電力供給を受けることができます。OGNDはGND～1Vの任意の電圧で電力供給を受けることができ、OV<sub>DD</sub>より低くなければなりません。ロジック出力はOGNDとOV<sub>DD</sub>の間で振幅します。

### 出力イネーブル

出力イネーブル・ピン( $\overline{OE}$ )を使用して出力をディスエーブルすることができます。 $\overline{OE}$ を“H”にすると、OFを含むすべてのデータ出力がディスエーブルされます。データのアクセス時間やバスの解放時間は、全速動作時に出力のイネーブルやディスエーブルをするには長すぎます。出力のハイ・インピーダンス状態は、長期の休止時の使用を意図したものです。チャネルAとチャネルBには、独立した出力イネーブル・ピン( $\overline{OEA}$ 、 $\overline{OEB}$ )が備わっています。

### スリープ・モードとナップ・モード

節電のため、コンバータをシャットダウン・モードまたはナップ・モードに設定することができます。SHDNをGNDに接続すると正常動作になります。SHDNを $V_{DD}$ に接続し、 $\overline{OE}$ を $V_{DD}$ に接続するとスリープ・モードになり、リファレンスを含むすべての回路をパワーダウンし、消費電力は標準で1mWになります。スリープ・モードを抜け出すとき、リファレンス・コンデンサを再充電して安定化する必要があるので、出力データが有効になるまで数ミリ秒かかります。SHDNを $V_{DD}$ に接続し、 $\overline{OE}$ をGNDに接続するとナップ・モードになり、消費電力は標準で30mWになります。ナップ・モードでは内蔵リファレンス回路はオンのままなので、ナップ・モードからの回復はスリープ・モードからの回復よりも早く、標準で100クロック・サイクルかかります。スリープとナップの両方のモードで、すべてのデジタル出力がディスエーブルされ、ハイ・インピーダンス状態になります。

チャネルAとチャネルBには、独立したSHDNピン(SHDNA、SHDNB)が備わっています。チャネルAはSHDNAと $\overline{OEA}$ によって制御され、チャネルBはSHDNBと $\overline{OEB}$ によって制御されます。2つのチャネルのナップ・モード、スリープ・モードおよび出力イネーブル・モードは完全に独立しているので、一方のチャネルがナップ・モードまたはスリープ・モード時に、他方のチャネルを動作させることができます。

### デジタル出力のマルチプレクサ

サンプリング・レートが80Msps以下の場合、LTC2285のデジタル出力は1つのデータバスに多重化することができます。MUXピンは2つのデータバスを入れ替えるデジタル入力です。MUXが“H”的とき、チャネルAはDA0～DA13に出力され、チャネルBはDB0～DB13に出力されます。MUXが“L”的とき、出力バスが入れ替わり、チャネルAはDB0～DB13に出力され、チャネルBはDA0～DA13に出力されます。両方のチャネルを1つの出力バスに多重化するには、MUX、CLKAおよびCLKBと一緒に接続します(「タ

## アプリケーション情報

イミング図」の多重化モードを参照)。多重化されたデータはどちらのデータバスでも利用できます(使用しないデータバスは対応する $\overline{OE}$ ピンを使用してディスエーブルすることができます)。

### 接地とバイパス

LTC2285は切れ目のないクリーンなグランド・プレーンを備えたPCボードを必要とします。内部グランド・プレーンを備えた多層基板を推奨します。PCボードのレイアウトでは、デジタル信号ラインとアナログ信号ラインをできるだけ離す必要があります。特に、アナログ信号トラックの横やADCの下にデジタル・トラックを走らせないように注意してください。

$V_{DD}$ 、 $OV_{DD}$ 、 $V_{CM}$ 、 $REFH$ 、 $REFL$ の各ピンには、高品質のセラミック・バイパス・コンデンサを使用してください。バイパス・コンデンサは、できるだけピンの近くに配置する必要があります。特に重要なのは、 $REFH$ と $REFL$ の間の $0.1\mu F$ のコンデンサです。このコンデンサは、できるだけデバイスの近く(1.5mm以内)に配置してください。サイズが0402のセラミック・コンデンサを推奨します。 $REFH$ と $REFL$ の間の大きな $2.2\mu F$ のコンデンサは、これよりいくらか離れてもかまいません。ピンとバイパス・コンデンサを接続するトレースは短くし、できるだけ幅を広くします。

LTC2285の差動入力は互いに並行にし、できるだけ近づけて配置してください。入力トレースはできるだけ短くして容量を最小限に抑え、ノイズを拾わないようにする必要があります。

### 熱伝達

LTC2285が発生する熱の大部分は、ダイから底面の露出パッドとパッケージのピンを通ってPCボードに伝わります。優れた電気的特性と熱特性を得るために、露出パッドをPCボードの大きな接地されたパッドに半田付けする必要があります。すべてのグランド・ピンを面積が十分大きいグランド・プレーンに接続することが重要です。

### アンダーサンプリング用クロック・ソース

アンダーサンプリングではクロック・ソースに対する要求が厳しく、入力周波数が高いほどクロックのジッタや位相ノイズに影響されやすくなります。フルスケール信号のSNRを70MHzで1dB劣化させるクロック・ソースの場合、SNRを140MHzで3dB、190MHzで4.5dB劣化させます。

クロック周波数の絶対精度が比較的重要ではなく、必要なADCが1個だけの場合、SaronixやVectronなどの販売元

の3V缶タイプ発振器をADCの近くに配置し、直接ADCに接続することができます。ADCまである程度の距離がある場合には、なんらかのソース終端によって、数分の1インチの距離でも生じる可能性のあるリンギングを抑えることを推奨します。クロックは電源の値をオーバーシュートしないようにする必要があります。オーバーシュートすると性能が低下します。正弦波のクロック・ソースを使用している場合を除き、クロック信号は狭帯域フィルタを通さないでください。フィルタを通すと、標準的なデジタル・クロック信号に含まれる立ち上がり時間と立ち下り時間のアーチファクトが位相ノイズに変換されるからです。

位相ノイズが最も小さい発振器は出力がシングルエンドの正弦波であり、これらのデバイスではADCの近くにフィルタを使用すると効果的な場合があります。往復の反射時間を短くするとともに、フィルタとADC間のトレースへの影響を低減するために、このフィルタはADCに近接させる必要があります。回路が近接位相ノイズの影響を受けやすい場合、発振器の電源とすべてのバッファは安定性の高いものでなければなりません。電源が安定していないと、電源による伝播遅延の変動によって位相ノイズが生じます。これらのクロック・ソースはデジタル・デバイスとみなされるかもしれません、デジタル電源で動作させではありません。そのクロックをFPGAなどのデジタル・デバイスのドライブにも使用する場合には、発振器およびすべてのクロック・ファンアウト・デバイスをADCの近くに配置し、ADCへの配線を優先する必要があります。FPGAへのクロック信号はドライバに直列終端を使用し、FPGAが生成する高周波ノイズがクロック・ファンアウト・デバイスの基板に妨害を与えないようにする必要があります。FPGAをプログラム可能な分割器として使用する場合、元の発振器を使用して信号の時間合わせを行い、また、タイミング調整用フリップフロップと発振器をADCの近くに配置し、十分に安定した電源で電力を供給する必要があります。

複数のADCがある場合、またはクロック・ソースがある程度離れている場合には、クロックを差動で分配することを推奨します。これはEMIの観点から望ましいだけでなく、デジタル・ソースからの放射ノイズや多層PCボードの層間に存在する導波路内を伝播するノイズを防ぐ観点からも推奨します。差動ペアは互いに近接させ、他の信号から離さなければなりません。差動ペアは、両側にトレース間隔の少なくとも3倍の距離をとって銅でガードを設け、1/4インチ以下の間隔のビアによってグランドに接続する必要があります。

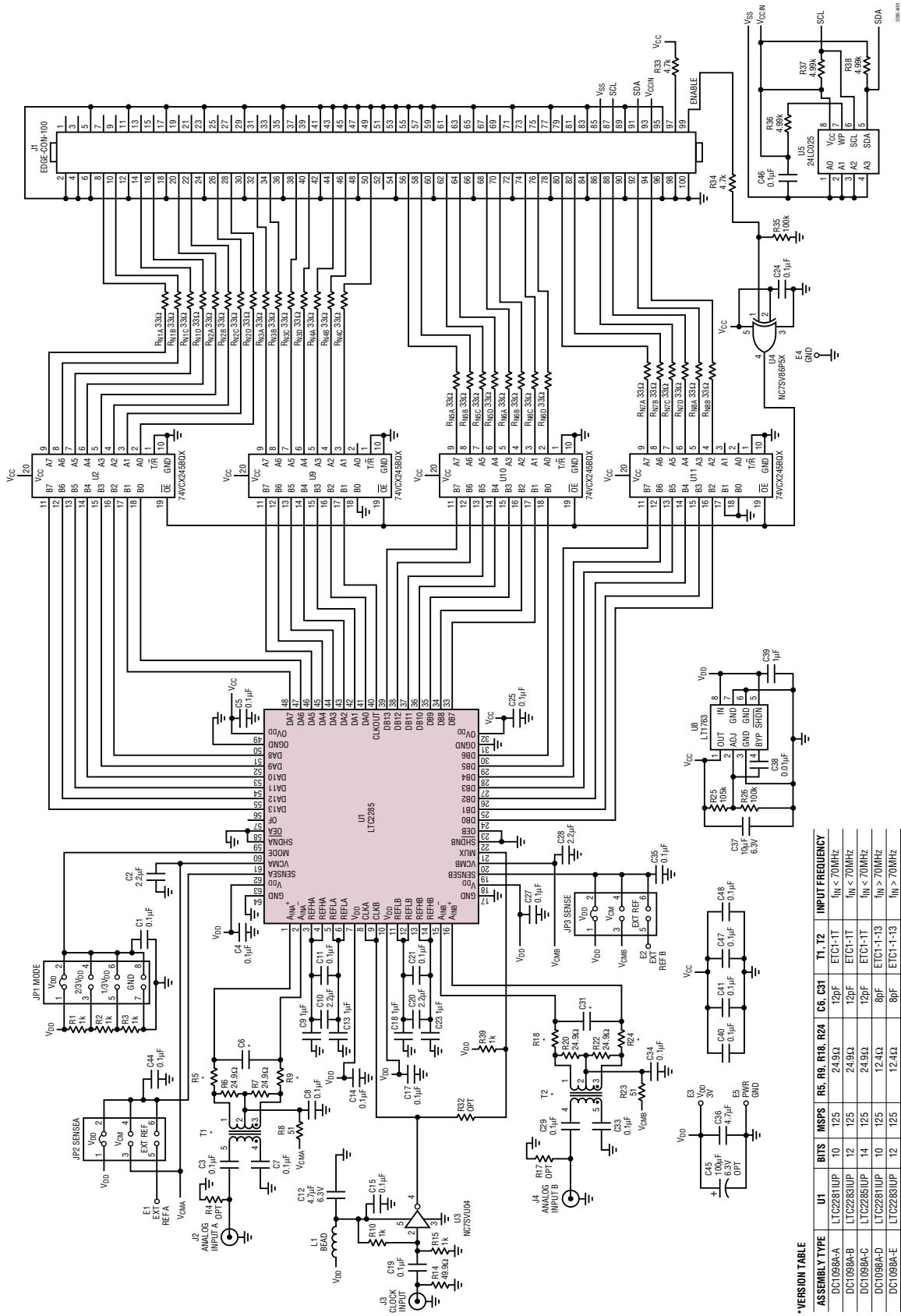

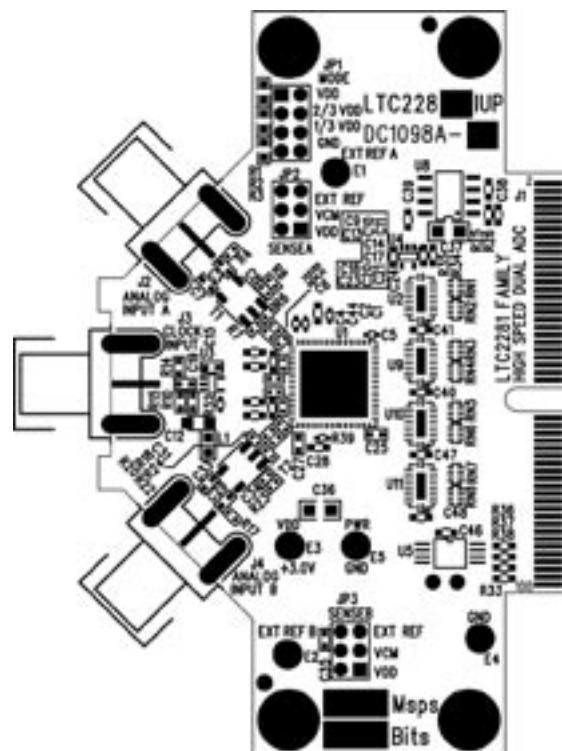

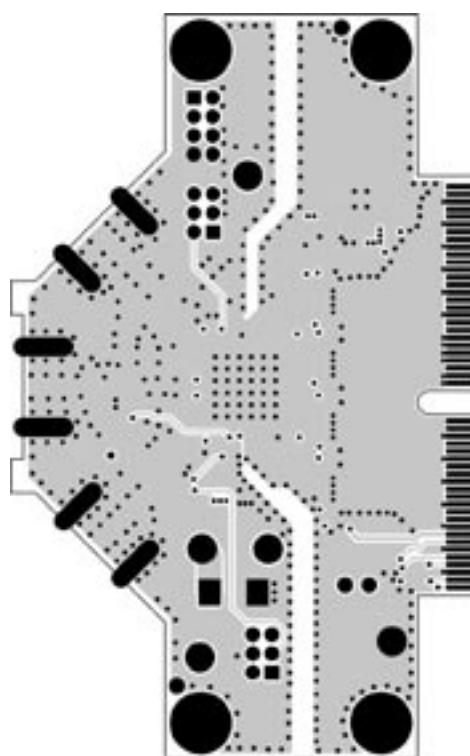

## LTC2285の評価回路図

\*VERSION TABLE

## アプリケーション情報

## シルクスクリーンの上面

上面

2285fa

# LTC2285

---

## アプリケーション情報

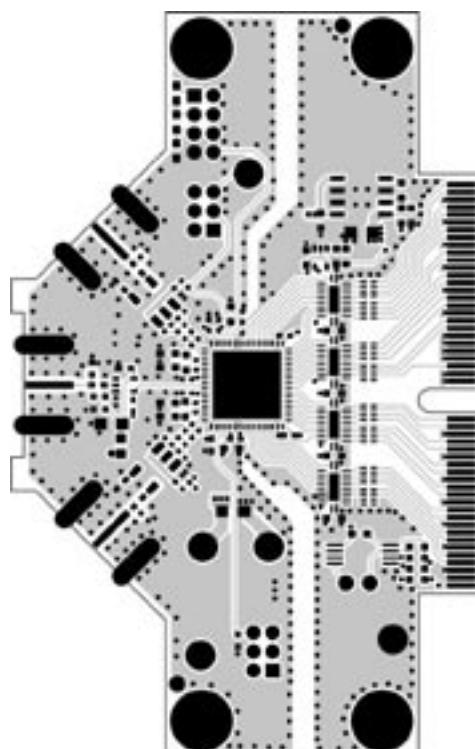

内部第2層GND

内部第3層電源

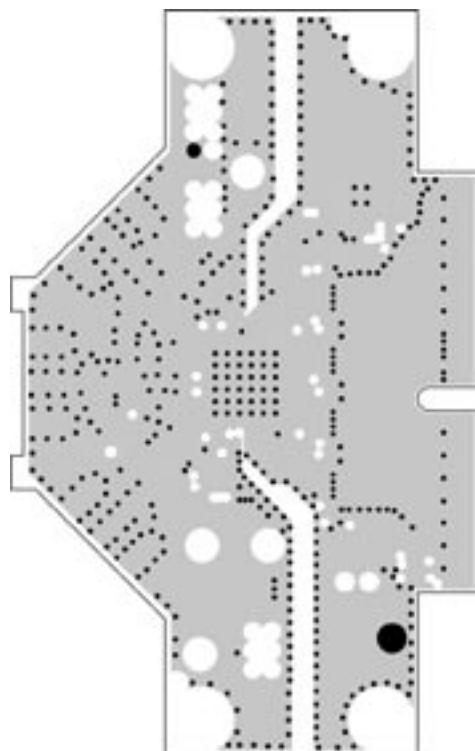

底面

2285fa

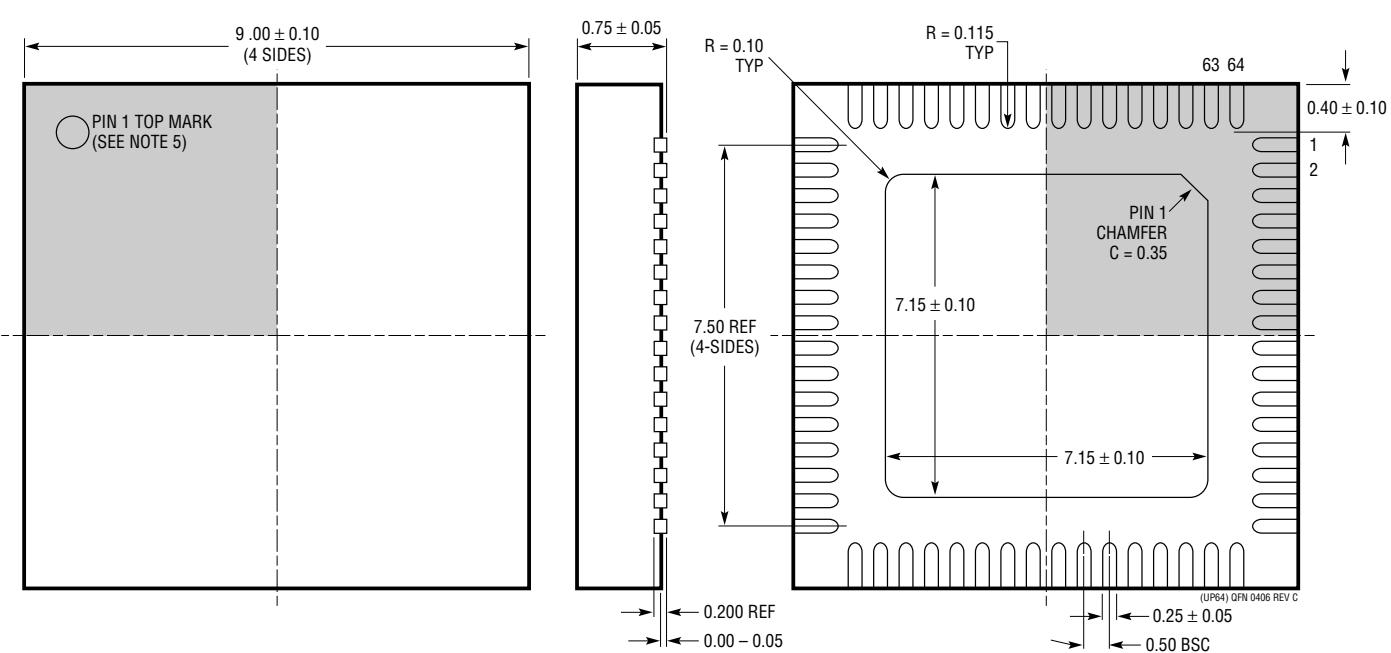

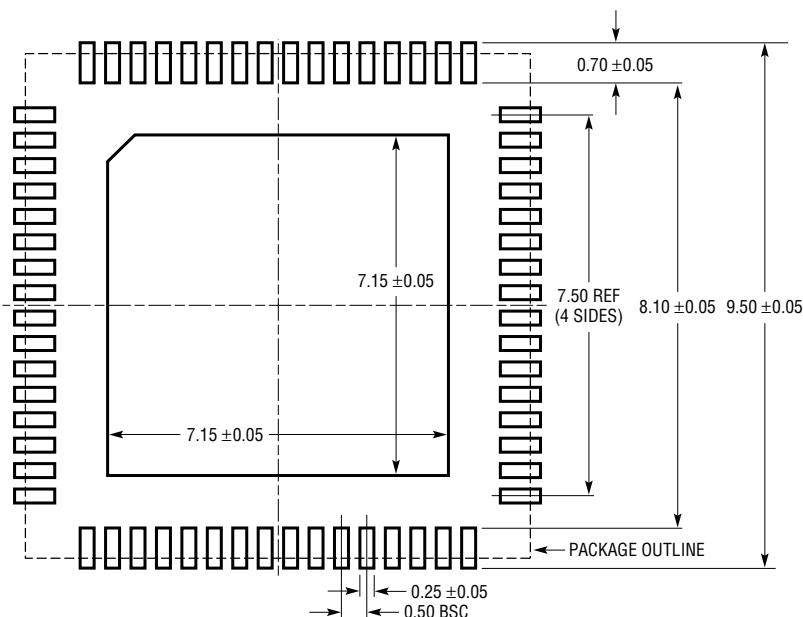

## パッケージ寸法

UPパッケージ

64ピン・プラスチックQFN (9mm x 9mm)

(Reference LTC DWG # 05-08-1705)

## NOTE:

1. 図はJEDECのパッケージ外形MO-220のバリエーションWNJR-5に適合

2. すべての寸法はミリメートル

3. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリは(もしあれば)各サイドで0.20mmを超えないこと

4. 露出パッドは半田メッキとする

5. 網掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

6. 図は実寸とは異なる

2285fa

## 関連製品

| 製品番号       | 説明                                | 注釈                                                                |

|------------|-----------------------------------|-------------------------------------------------------------------|

| LTC1748    | 14ビット、80Msps、5V ADC               | SNR:76.3dB、SFDR:90dB、48ピンTSSOPパッケージ                               |

| LTC1750    | 14ビット、80Msps、5V広帯域ADC             | 最大500MHzのIFアンダーサンプリング、SFDR:90dB                                   |

| LT1993-2   | 高速差動オペアンプ                         | BW:800MHz、歪み:70dBc(70MHz)、利得:6dB                                  |

| LT1994     | 低ノイズ、低歪みの完全差動入出力アンプ/ドライバ          | 低歪み:-94dBc(1MHz)                                                  |

| LTC2208    | 16ビット、130Msps、3.3V ADC、LVDS出力     | 1250mW、SNR:77.1dB、SFDR:100dB、64ピンQFN                              |

| LTC2220    | 12ビット、170Msps、3.3V ADC、LVDS出力     | 890mW、SNR:67.7dB、SFDR:84dB、64ピンQFNパッケージ                           |

| LTC2224    | 12ビット、135Msps、3.3V ADC、高IFサンプリング  | 630mW、SNR:67.6dB、SFDR:84dB、48ピンQFNパッケージ                           |

| LTC2242-12 | 12ビット、250Msps、2.5V ADC、LVDS出力     | 740mW、SNR:65.4dB、SFDR:84dB、64ピンQFNパッケージ                           |

| LTC2254    | 14ビット、105Msps、3V ADC、最低消費電力       | 320mW、SNR:72.4dB、SFDR:88dB、32ピンQFNパッケージ                           |

| LTC2255    | 14ビット、125Msps ADC、3V ADC、最低消費電力   | 395mW、SNR:72.5dB、SFDR:88dB、32ピンQFNパッケージ                           |

| LTC2280    | 10ビット、デュアル、105Msps、3V ADC、低クロストーク | 320mW、SNR:61.6dB、SFDR:85dB、64ピンQFNパッケージ                           |

| LTC2282    | 12ビット、デュアル、105Msps、3V ADC、低クロストーク | 540mW、SNR:70.1dB、SFDR:88dB、64ピンQFNパッケージ                           |

| LTC2284    | 14ビット、デュアル、105Msps、3V ADC、低クロストーク | 540mW、SNR:72.4dB、SFDR:88dB、64ピンQFNパッケージ                           |

| LTC2286    | 10ビット、デュアル、25Msps、3V ADC、低クロストーク  | 150mW、SNR:61.8dB、SFDR:85dB、64ピンQFNパッケージ                           |

| LTC2287    | 10ビット、デュアル、40Msps、3V ADC、低クロストーク  | 235mW、SNR:61.8dB、SFDR:85dB、64ピンQFNパッケージ                           |

| LTC2288    | 10ビット、デュアル、65Msps、3V ADC、低クロストーク  | 400mW、SNR:61.8dB、SFDR:85dB、64ピンQFNパッケージ                           |

| LTC2289    | 10ビット、デュアル、80Msps、3V ADC、低クロストーク  | 422mW、SNR:61.6dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2290    | 12ビット、デュアル、10Msps、3V ADC、低クロストーク  | 120mW、SNR:71.3dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2291    | 12ビット、デュアル、25Msps、3V ADC、低クロストーク  | 150mW、SNR:71.4dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2292    | 12ビット、デュアル、40Msps、3V ADC、低クロストーク  | 235mW、SNR:71.4dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2293    | 12ビット、デュアル、65Msps、3V ADC、低クロストーク  | 400mW、SNR:71.3dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2294    | 12ビット、デュアル、80Msps、3V ADC、低クロストーク  | 422mW、SNR:70.6dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2295    | 14ビット、デュアル、10Msps、3V ADC、低クロストーク  | 120mW、SNR:74.4dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2296    | 14ビット、デュアル、25Msps、3V ADC、低クロストーク  | 150mW、SNR:74.5dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2297    | 14ビット、デュアル、40Msps、3V ADC、低クロストーク  | 235mW、SNR:74.4dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2298    | 14ビット、デュアル、65Msps、3V ADC、低クロストーク  | 400mW、SNR:74.3dB、SFDR:90dB、64ピンQFNパッケージ                           |

| LTC2299    | 14ビット、デュアル、80Msps、3V ADC、低クロストーク  | 444mW、SNR:73dB、SFDR:90dB、64ピンQFNパッケージ                             |

| LT5512     | DC~3GHz高信号レベル・ダウンコンバーティング・ミキサ     | DC~3GHz、IIP3:21dBm、内蔵LOバッファ                                       |

| LT5514     | デジタル利得制御付き超低歪みIFアンプ/ADCドライバ       | 1dB BW:450MHz、OIP3:47dB、デジタル利得制御:1.5dB/ステップで10.5dB~33dB           |

| LT5515     | 1.5GHz~2.5GHz直接変換直交復調器            | 高いIIP3:1.9GHzで20dBm、内蔵LO直交ジェネレータ                                  |

| LT5516     | 800MHz~1.5GHz直接変換直交復調器            | 高いIIP3:900MHzで21.5dBm、内蔵LO直交ジェネレータ                                |

| LT5517     | 40MHz~900MHz直接変換直交復調器             | 高いIIP3:800MHzで21dBm、内蔵LO直交ジェネレータ                                  |

| LT5522     | 600MHz~2.7GHz高直線性ダウンコンバーティング・ミキサ  | 4.5V~5.25V電源、IIP3:900MHzで25dBm、NF = 12.5dB、50ΩシングルエンドのRFポートとLOポート |