## 特長

- 高速シリアル・インターフェース (JESD204)

- サンプル・レート: 105Msps

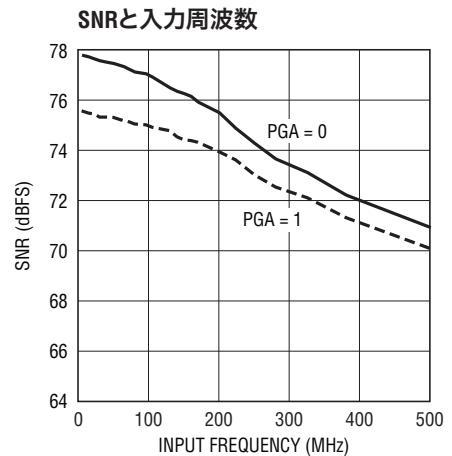

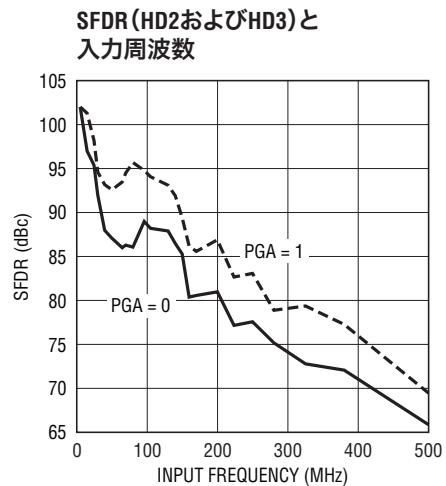

- ノイズフロア: 77.7dBFS

- SFDR: 100dB

- SFDR: 250MHzで > 82dB (入力範囲1.5 V<sub>P-P</sub>)

- PGAフロントエンド (入力範囲2.25V<sub>P-P</sub>または1.5V<sub>P-P</sub>)

- 700MHzのフルパワー帯域幅S/H

- オプションの内部ディザイナー

- 単一3.3V電源

- 低消費電力: 1300mW

- クロック・デューティ・サイクル・スタビライザ

- ピン互換ファミリー

- 105Msps: LTC2274

- 80Msps: LTC2273

- 65Msps: LTC2272

- 40ピン(6mm×6mm)QFNパッケージ

## アプリケーション

- テレコム

- 受信機

- 携帯電話基地局

- スペクトル分析

- イメージング・システム

- ATE

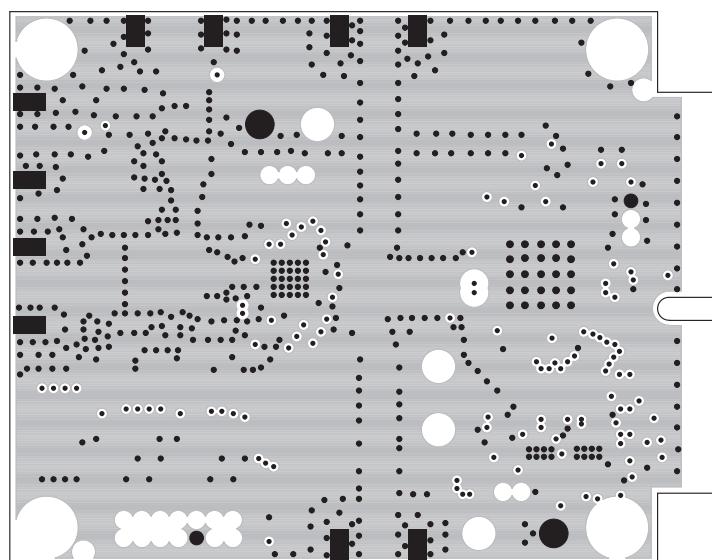

## 標準的応用例

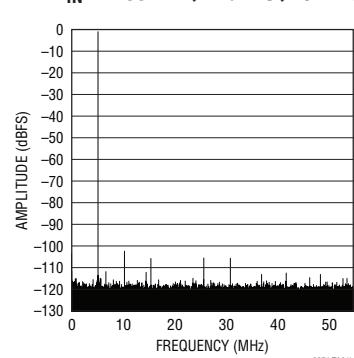

128kポイントのFFT、

$f_{IN} = 4.93\text{MHz}$ ,  $-1\text{dBFS}$ ,  $\text{PGA} = 0$

2274 TA01

2274fb

## 絶対最大定格

$OV_{DD} = V_{DD}$  (Note 1, 2)

|                          |                            |

|--------------------------|----------------------------|

| 電源電圧 ( $V_{DD}$ )        | -0.3V~4V                   |

| アナログ入力電圧 (Note 3)        | -0.3V~( $V_{DD} + 0.3V$ )  |

| デジタル入力電圧                 | -0.3V~( $V_{DD} + 0.3V$ )  |

| デジタル出力電圧                 | -0.3V~( $OV_{DD} + 0.3V$ ) |

| 電力損失                     | 2000mW                     |

| 動作温度範囲                   |                            |

| LTC2274C                 | 0°C~70°C                   |

| LTC2274I                 | -40°C~85°C                 |

| 保存温度範囲                   | -65°C~150°C                |

| デジタル出力電源電圧 ( $OV_{DD}$ ) | -0.3V~4V                   |

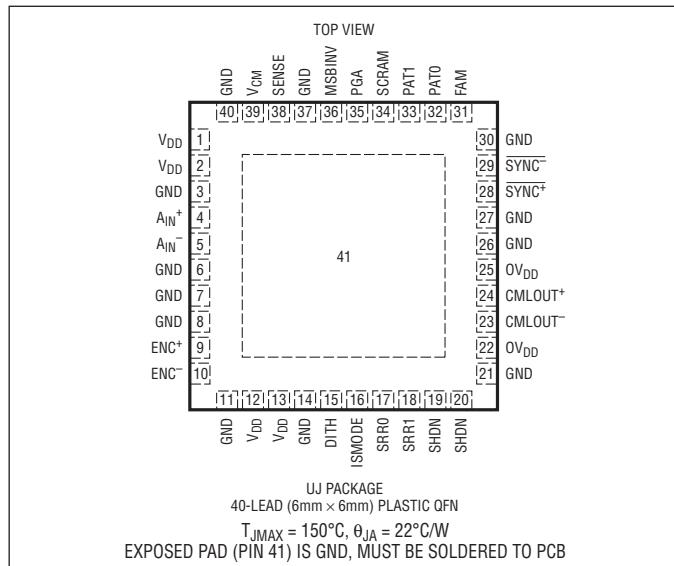

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープアンドリール        | 製品マーキング*  | パッケージ                           | 温度範囲          |

|----------------|------------------|-----------|---------------------------------|---------------|

| LTC2274CUJ#PBF | LTC2274CUJ#TRPBF | LTC2274UJ | 40-Lead (6mm x 6mm) Plastic QFN | 0°C to 70°C   |

| LTC2274IUJ#PBF | LTC2274IUJ#TRPBF | LTC2274UJ | 40-Lead (6mm x 6mm) Plastic QFN | -40°C to 85°C |

| 鉛ベース仕様         | テープアンドリール        | 製品マーキング*  | パッケージ                           | 温度範囲          |

| LTC2274CUJ     | LTC2274CUJ#TR    | LTC2274UJ | 40-Lead (6mm x 6mm) Plastic QFN | 0°C to 70°C   |

| LTC2274IUJ     | LTC2274IUJ#TR    | LTC2274UJ | 40-Lead (6mm x 6mm) Plastic QFN | -40°C to 85°C |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。 \*温度等級は出荷時のコンテナのラベルで識別されます。

鉛フリー製品のマーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandree/> をご覧ください。

## コンバータ特性

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。(Note 4)

| SYMBOL                       | CONDITIONS                                                  | MIN | TYP                  | MAX       | UNITS                        |

|------------------------------|-------------------------------------------------------------|-----|----------------------|-----------|------------------------------|

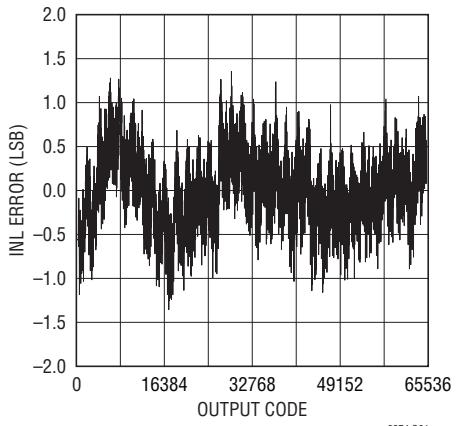

| Integral Linearity Error     | Differential Analog Input (Note 5) $T_A = 25^\circ\text{C}$ |     | $\pm 1.2$            | $\pm 4$   | LSB                          |

| Integral Linearity Error     | Differential Analog Input (Note 5)                          | ●   | $\pm 1.5$            | $\pm 4.5$ | LSB                          |

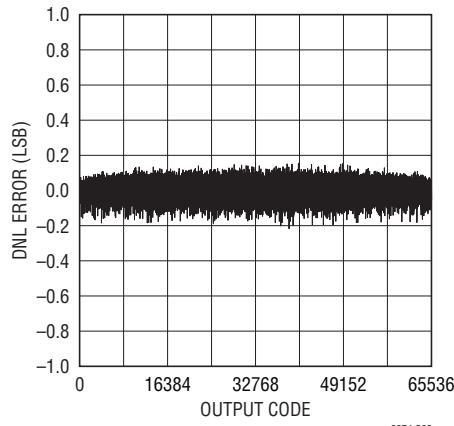

| Differential Linearity Error | Differential Analog Input                                   | ●   | $\pm 0.3$            | $\pm 1$   | LSB                          |

| Offset Error                 | (Note 6)                                                    | ●   | $\pm 1$              | $\pm 8.5$ | mV                           |

| Offset Drift                 |                                                             |     | $\pm 10$             |           | $\mu\text{V}/^\circ\text{C}$ |

| Gain Error                   | External Reference                                          | ●   | $\pm 0.2$            | $\pm 1.5$ | %FS                          |

| Full-Scale Drift             | Internal Reference<br>External Reference                    |     | $\pm 30$<br>$\pm 15$ |           | ppm/°C<br>ppm/°C             |

| Transition Noise             |                                                             |     | 3                    |           | LSB <sub>RMS</sub>           |

## アナログ入力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL       | PARAMETER                                        | CONDITIONS                                                | MIN | TYP         | MAX  | UNITS                      |

|--------------|--------------------------------------------------|-----------------------------------------------------------|-----|-------------|------|----------------------------|

| $V_{IN}$     | Analog Input Range ( $A_{IN^+} - A_{IN^-}$ )     | $3.135\text{V} \leq V_{DD} \leq 3.465\text{V}$            | ●   | 1.5 or 2.25 |      | $V_{P-P}$                  |

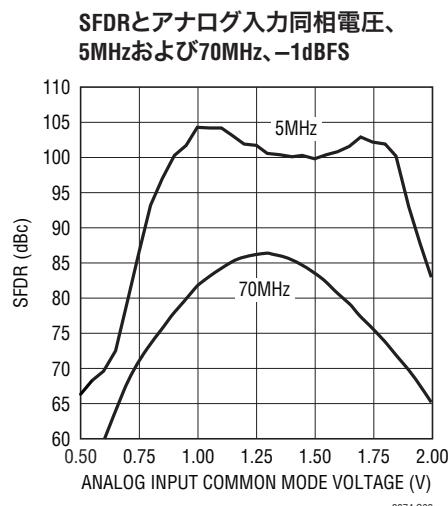

| $V_{IN, CM}$ | Analog Input Common Mode                         | Differential Input (Note 7)                               | ●   | 1           | 1.25 | 1.5                        |

| $I_{IN}$     | Analog Input Leakage Current                     | $0\text{V} \leq A_{IN^+}, A_{IN^-} \leq V_{DD}$ (Note 10) | ●   | -1          | 1    | $\mu\text{A}$              |

| $I_{SENSE}$  | SENSE Input Leakage Current                      | $0\text{V} \leq SENSE \leq V_{DD}$ (Note 11)              |     | -3          | 3    | $\mu\text{A}$              |

| $C_{IN}$     | Analog Input Capacitance                         | Sample Mode $ENC^+ < ENC^-$<br>Hold Mode $ENC^+ > ENC^-$  |     | 6.7<br>1.8  |      | $\text{pF}$<br>$\text{pF}$ |

| $t_{AP}$     | Sample-and-Hold<br>Acquisition Delay Time        |                                                           |     | 1           |      | $\text{ns}$                |

| $t_{JITTER}$ | Sample-and-Hold<br>Acquisition Delay Time Jitter |                                                           |     | 80          |      | $\text{fs}_{\text{RMS}}$   |

| CMRR         | Analog Input<br>Common Mode Rejection Ratio      | $1\text{V} < (A_{IN^+} = A_{IN^-}) < 1.5\text{V}$         |     | 80          |      | $\text{dB}$                |

| BW-3dB       | Full Power Bandwidth                             | $R_S \leq 25\Omega$                                       |     | 700         |      | $\text{MHz}$               |

## ダイナミック精度

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ 。(Note 4)

| SYMBOL | PARAMETER                                                                  | CONDITIONS                                                                                                                                | MIN | TYP                  | MAX                  | UNITS                                           |

|--------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|----------------------|-------------------------------------------------|

| SNR    | Signal-to-Noise Ratio                                                      | 5MHz Input (2.25V Range, PGA = 0)<br>5MHz Input (1.5V Range, PGA = 1)                                                                     |     | 77.6<br>75.4         |                      | $\text{dBFS}$<br>$\text{dBFS}$                  |

|        |                                                                            | 15MHz Input (2.25V Range, PGA = 0), $T_A = 25^\circ\text{C}$<br>15MHz Input (2.25V Range, PGA = 0)<br>15MHz Input (1.5V Range, PGA = 1)   | ●   | 76.5<br>76.2<br>75.3 | 77.5<br>77.2<br>75.3 | $\text{dBFS}$<br>$\text{dBFS}$<br>$\text{dBFS}$ |

|        |                                                                            | 70MHz Input (2.25V Range, PGA = 0)<br>70MHz Input (1.5V Range, PGA = 1)                                                                   |     | 77.2<br>75.1         |                      | $\text{dBFS}$<br>$\text{dBFS}$                  |

|        |                                                                            | 140MHz Input (2.25V Range, PGA = 0)<br>140MHz Input (1.5V Range, PGA = 1), $T_A = 25^\circ\text{C}$<br>140MHz Input (1.5V Range, PGA = 1) | ●   | 73.8<br>73.4         | 76.3<br>74.5<br>74.2 | $\text{dBFS}$<br>$\text{dBFS}$<br>$\text{dBFS}$ |

|        |                                                                            | 170MHz Input (2.25V Range, PGA = 0)<br>170MHz Input (1.5V Range, PGA = 1)                                                                 |     | 75.9<br>74.3         |                      | $\text{dBFS}$<br>$\text{dBFS}$                  |

|        |                                                                            | 5MHz Input (2.25V Range, PGA = 0)<br>5MHz Input (1.5V Range, PGA = 1)                                                                     |     | 100<br>100           |                      | $\text{dBc}$<br>$\text{dBc}$                    |

|        |                                                                            | 15MHz Input (2.25V Range, PGA = 0), $T_A = 25^\circ\text{C}$<br>15MHz Input (2.25V Range, PGA = 0)<br>15MHz Input (1.5V Range, PGA = 1)   | ●   | 85<br>84<br>100      | 95<br>95<br>100      | $\text{dBc}$<br>$\text{dBc}$<br>$\text{dBc}$    |

|        |                                                                            | 70MHz Input (2.25V Range, PGA = 0)<br>70MHz Input (1.5V Range, PGA = 1)                                                                   |     | 86<br>94             |                      | $\text{dBc}$<br>$\text{dBc}$                    |

|        |                                                                            | 140MHz Input (2.25V Range, PGA = 0)<br>140MHz Input (1.5V Range, PGA = 1), $T_A = 25^\circ\text{C}$<br>140MHz Input (1.5V Range, PGA = 1) | ●   | 81<br>80             | 85<br>89             | $\text{dBc}$<br>$\text{dBc}$                    |

|        |                                                                            | 170MHz Input (2.25V Range, PGA = 0)<br>170MHz Input (1.5V Range, PGA = 1)                                                                 |     | 80<br>85             |                      | $\text{dBc}$<br>$\text{dBc}$                    |

| SFDR   | Spurious Free Dynamic Range<br>2 <sup>nd</sup> or 3 <sup>rd</sup> Harmonic | 5MHz Input (2.25V Range, PGA = 0)<br>5MHz Input (1.5V Range, PGA = 1)                                                                     |     | 100<br>100           |                      | $\text{dBc}$<br>$\text{dBc}$                    |

|        |                                                                            | 15MHz Input (2.25V Range, PGA = 0), $T_A = 25^\circ\text{C}$<br>15MHz Input (2.25V Range, PGA = 0)<br>15MHz Input (1.5V Range, PGA = 1)   | ●   | 85<br>84<br>100      | 95<br>95<br>100      | $\text{dBc}$<br>$\text{dBc}$<br>$\text{dBc}$    |

|        |                                                                            | 70MHz Input (2.25V Range, PGA = 0)<br>70MHz Input (1.5V Range, PGA = 1)                                                                   |     | 86<br>94             |                      | $\text{dBc}$<br>$\text{dBc}$                    |

|        |                                                                            | 140MHz Input (2.25V Range, PGA = 0)<br>140MHz Input (1.5V Range, PGA = 1), $T_A = 25^\circ\text{C}$<br>140MHz Input (1.5V Range, PGA = 1) | ●   | 81<br>80             | 85<br>89             | $\text{dBc}$<br>$\text{dBc}$                    |

|        |                                                                            | 170MHz Input (2.25V Range, PGA = 0)<br>170MHz Input (1.5V Range, PGA = 1)                                                                 |     | 80<br>85             |                      | $\text{dBc}$<br>$\text{dBc}$                    |

## ダイナミック精度

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $A_{IN} = -1\text{dBFS}$ 。(Note 4)

| SYMBOL  | PARAMETER                                                      | CONDITIONS                                                    | MIN | TYP  | MAX  | UNITS |

|---------|----------------------------------------------------------------|---------------------------------------------------------------|-----|------|------|-------|

| SFDR    | Spurious Free Dynamic Range 4 <sup>th</sup> Harmonic or Higher | 5MHz Input (2.25V Range, PGA = 0)                             |     | 100  |      | dBc   |

|         |                                                                | 5MHz Input (1.5V Range, PGA = 1)                              |     | 100  |      | dBc   |

|         |                                                                | 15MHz Input (2.25V Range, PGA = 0)                            | ●   | 90   | 100  | dBc   |

|         |                                                                | 15MHz Input (1.5V Range, PGA = 1)                             |     | 100  |      | dBc   |

|         |                                                                | 70MHz Input (2.25V Range, PGA = 0)                            |     | 100  |      | dBc   |

|         |                                                                | 70MHz Input (1.5V Range, PGA = 1)                             |     | 100  |      | dBc   |

| S/(N+D) | Signal-to-Noise Plus Distortion Ratio                          | 140MHz Input (2.25V Range, PGA = 0)                           |     | 95   |      | dBc   |

|         |                                                                | 140MHz Input (1.5V Range, PGA = 1)                            | ●   | 85   | 100  | dBc   |

|         |                                                                | 170MHz Input (2.25V Range, PGA = 0)                           |     | 90   |      | dBc   |

|         |                                                                | 170MHz Input (1.5V Range, PGA = 1)                            |     | 95   |      | dBc   |

|         |                                                                | 5MHz Input (2.25V Range, PGA = 0)                             |     | 77.5 |      | dBFS  |

|         |                                                                | 5MHz Input (1.5V Range, PGA = 1)                              |     | 75.3 |      | dBFS  |

| SFDR    | Spurious Free Dynamic Range at -25dBFS Dither "OFF"            | 15MHz Input (2.25V Range, PGA = 0), $T_A = 25^\circ\text{C}$  |     | 76.3 | 77.4 | dBFS  |

|         |                                                                | 15MHz Input (2.25V Range, PGA = 0)                            | ●   | 75.9 | 77   | dBFS  |

|         |                                                                | 15MHz Input (1.5V Range, PGA = 1)                             |     | 75.2 |      | dBFS  |

|         |                                                                | 70MHz Input (2.25V Range, PGA = 0)                            |     | 76.7 |      | dBFS  |

|         |                                                                | 70MHz Input (1.5V Range, PGA = 1)                             |     | 74.2 |      | dBFS  |

|         |                                                                | 140MHz Input (2.25V Range, PGA = 0), $T_A = 25^\circ\text{C}$ |     | 75.3 |      | dBFS  |

| SFDR    | Spurious Free Dynamic Range at -25dBFS Dither "ON"             | 140MHz Input (1.5V Range, PGA = 1)                            |     | 73.6 | 74.3 | dBFS  |

|         |                                                                | 140MHz Input (1.5V Range, PGA = 1)                            | ●   | 73.2 | 74   | dBFS  |

|         |                                                                | 170MHz Input (2.25V Range, PGA = 0)                           |     | 73.4 |      | dBFS  |

|         |                                                                | 170MHz Input (1.5V Range, PGA = 1)                            |     | 73.4 |      | dBFS  |

|         |                                                                | 5MHz Input (2.25V Range, PGA = 0)                             |     | 105  |      | dBFS  |

|         |                                                                | 5MHz Input (1.5V Range, PGA = 1)                              |     | 105  |      | dBFS  |

| SFDR    | Spurious Free Dynamic Range at -25dBFS Dither "ON"             | 15MHz Input (2.25V Range, PGA = 0)                            |     | 105  |      | dBFS  |

|         |                                                                | 15MHz Input (1.5V Range, PGA = 1)                             |     | 105  |      | dBFS  |

|         |                                                                | 70MHz Input (2.25V Range, PGA = 0)                            |     | 105  |      | dBFS  |

|         |                                                                | 70MHz Input (1.5V Range, PGA = 1)                             |     | 105  |      | dBFS  |

|         |                                                                | 140MHz Input (2.25V Range, PGA = 0)                           |     | 100  |      | dBFS  |

|         |                                                                | 140MHz Input (1.5V Range, PGA = 1)                            |     | 100  |      | dBFS  |

| SFDR    | Spurious Free Dynamic Range at -25dBFS Dither "ON"             | 170MHz Input (2.25V Range, PGA = 0)                           |     | 100  |      | dBFS  |

|         |                                                                | 170MHz Input (1.5V Range, PGA = 1)                            |     | 100  |      | dBFS  |

|         |                                                                | 5MHz Input (2.25V Range, PGA = 0)                             |     | 115  |      | dBFS  |

|         |                                                                | 5MHz Input (1.5V Range, PGA = 1)                              |     | 115  |      | dBFS  |

|         |                                                                | 15MHz Input (2.25V Range, PGA = 0)                            | ●   | 97   | 115  | dBFS  |

|         |                                                                | 15MHz Input (1.5V Range, PGA = 1)                             |     | 115  |      | dBFS  |

| SFDR    | Spurious Free Dynamic Range at -25dBFS Dither "ON"             | 70MHz Input (2.25V Range, PGA = 0)                            |     | 115  |      | dBFS  |

|         |                                                                | 70MHz Input (1.5V Range, PGA = 1)                             |     | 115  |      | dBFS  |

|         |                                                                | 140MHz Input (2.25V Range, PGA = 0)                           |     | 110  |      | dBFS  |

|         |                                                                | 140MHz Input (1.5V Range, PGA = 1)                            |     | 110  |      | dBFS  |

|         |                                                                | 170MHz Input (2.25V Range, PGA = 0)                           |     | 105  |      | dBFS  |

|         |                                                                | 170MHz Input (1.5V Range, PGA = 1)                            |     | 105  |      | dBFS  |

## 同相バイアス特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| PARAMETER                  | CONDITIONS                                     | MIN  | TYP  | MAX  | UNITS                 |

|----------------------------|------------------------------------------------|------|------|------|-----------------------|

| $V_{CM}$ Output Voltage    | $I_{OUT} = 0$                                  | 1.15 | 1.25 | 1.35 | V                     |

| $V_{CM}$ Output Tempco     | $I_{OUT} = 0$                                  | ●    | 40   |      | ppm/ $^\circ\text{C}$ |

| $V_{CM}$ Line Regulation   | $3.135\text{V} \leq V_{DD} \leq 3.465\text{V}$ | ●    | 1    |      | mV/V                  |

| $V_{CM}$ Output Resistance | $-1\text{mA} \leq  I_{OUT}  \leq 1\text{mA}$   | ●    | 2    |      | $\Omega$              |

## デジタル入力とデジタル出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL | PARAMETER | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------|-----------|------------|-----|-----|-----|-------|

|--------|-----------|------------|-----|-----|-----|-------|

エンコード入力( $ENC^+$ 、 $ENC^-$ )

|           |                            |                                           |   |     |            |                  |

|-----------|----------------------------|-------------------------------------------|---|-----|------------|------------------|

| $V_{ID}$  | Differential Input Voltage | (Note 7)                                  | ● | 0.2 |            | V                |

| $V_{ICM}$ | Common Mode Input Voltage  | Internally Set<br>Externally Set (Note 7) |   | 1.4 | 1.6<br>3.0 | V                |

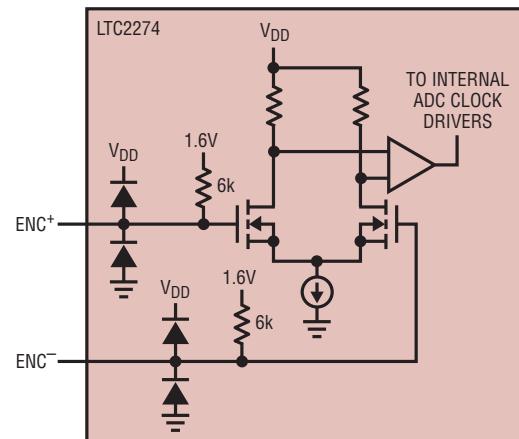

| $R_{IN}$  | Input Resistance           | (See Figure 2)                            |   |     | 6          | $\text{k}\Omega$ |

| $C_{IN}$  | Input Capacitance          |                                           |   |     | 3          | pF               |

SYNC入力( $SYNC^+$ 、 $SYNC^-$ )

|            |                                 |                                           |   |     |            |                  |

|------------|---------------------------------|-------------------------------------------|---|-----|------------|------------------|

| $V_{SID}$  | SYNC Differential Input Voltage | (Note 7)                                  | ● | 0.2 |            | V                |

| $V_{SICM}$ | SYNC Common Mode Input Voltage  | Internally Set<br>Externally Set (Note 7) |   | 1.1 | 1.6<br>2.2 | V                |

| $R_{SIN}$  | SYNC Input Resistance           |                                           |   |     | 16.5       | $\text{k}\Omega$ |

| $C_{SIN}$  | SYNC Input Capacitance          |                                           |   |     | 3          | pF               |

## ロジック入力(DITH、PGA、MSBINV、SCRAM、FAM、SHDN、SRR1、SRR0、ISMODE、PAT1、PATO)

|          |                          |                                  |   |   |          |               |

|----------|--------------------------|----------------------------------|---|---|----------|---------------|

| $V_{IH}$ | High Level Input Voltage | $V_{DD} = 3.3\text{V}$           | ● | 2 |          | V             |

| $V_{IL}$ | Low Level Input Voltage  | $V_{DD} = 3.3\text{V}$           | ● |   | 0.8      | V             |

| $I_{IN}$ | Input Current            | $V_{IN} = 0\text{V}$ to $V_{DD}$ | ● |   | $\pm 20$ | $\mu\text{A}$ |

| $C_{IN}$ | Input Capacitance        |                                  |   |   | 1.5      | pF            |

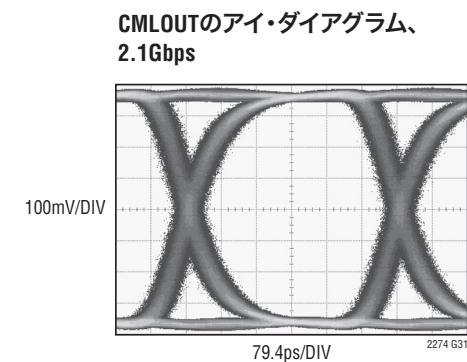

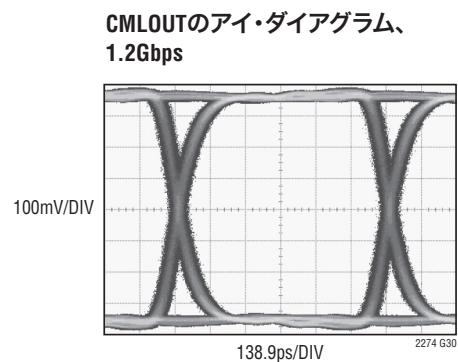

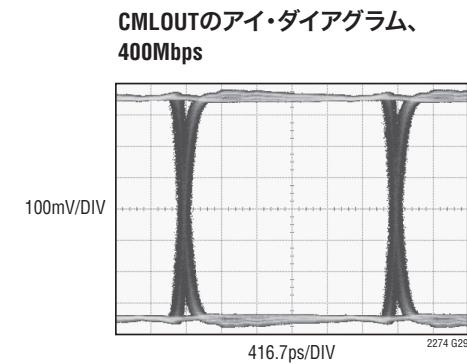

高速シリアル出力(CMLOUT<sup>+</sup>、CMLOUT<sup>-</sup>)

|           |                            |                                                                                                       |   |                                                       |    |          |

|-----------|----------------------------|-------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------|----|----------|

| $V_{OH}$  | Output High Level          | Directly-Coupled 50 $\Omega$ to $0V_{DD}$<br>Directly-Coupled 100 $\Omega$ Differential<br>AC-Coupled |   | $0V_{DD}$<br>$0V_{DD} - 0.2$<br>$0V_{DD} - 0.2$       |    | V        |

| $V_{OL}$  | Output Low Level           | Directly-Coupled 50 $\Omega$ to $0V_{DD}$<br>Directly-Coupled 100 $\Omega$ Differential<br>AC-Coupled |   | $0V_{DD} - 0.4$<br>$0V_{DD} - 0.6$<br>$0V_{DD} - 0.6$ |    | V        |

| $V_{OCM}$ | Output Common Mode Voltage | Directly-Coupled 50 $\Omega$ to $0V_{DD}$<br>Directly-Coupled 100 $\Omega$ Differential<br>AC-Coupled |   | $0V_{DD} - 0.2$<br>$0V_{DD} - 0.4$<br>$0V_{DD} - 0.4$ |    | V        |

| $R_{OUT}$ | Output Resistance          | Single-Ended Differential                                                                             | ● | 35<br>50<br>100                                       | 65 | $\Omega$ |

## 電源条件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ 。(Note 4)

| SYMBOL     | PARAMETER             | CONDITIONS                                                                                                                                          |             | MIN               | TYP                              | MAX   | UNITS |

|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|----------------------------------|-------|-------|

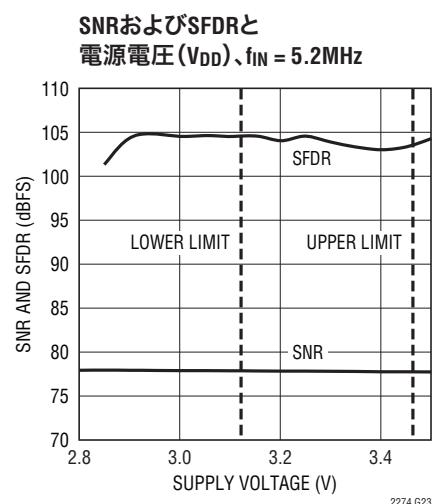

| $V_{DD}$   | Analog Supply Voltage |                                                                                                                                                     | ●           | 3.135             | 3.3                              | 3.465 | V     |

| $P_{SHDN}$ | Shutdown Power        | $SHDN$ Pins = $V_{DD}$                                                                                                                              |             |                   | 5                                |       | mW    |

| $0V_{DD}$  | Output Supply Range   | CMLOUT Directly-Coupled $50\Omega$ to $0V_{DD}$ (Note 7)<br>CMLOUT Directly-Coupled $100\Omega$ Differential (Note 7)<br>CMLOUT AC-Coupled (Note 7) | ●<br>●<br>● | 1.2<br>1.4<br>1.4 | $V_{DD}$<br>$V_{DD}$<br>$V_{DD}$ |       | V     |

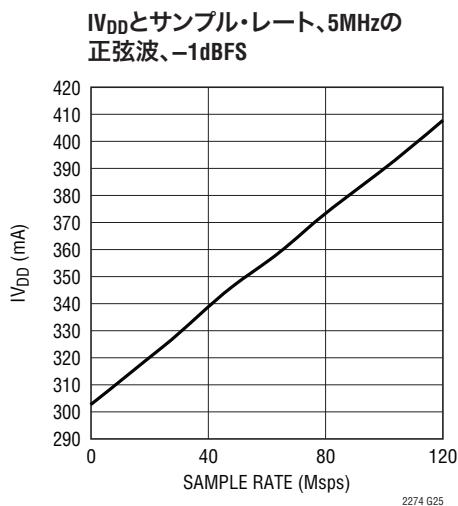

| $I_{VDD}$  | Analog Supply Current | DC Input                                                                                                                                            | ●           |                   | 394                              | 450   | mA    |

| $I_{0VDD}$ | Output Supply Current | CMLOUT Directly-Coupled, $50\Omega$ to $0V_{DD}$<br>CMLOUT Directly-Coupled $100\Omega$ Differential<br>CMLOUT AC-Coupled                           |             |                   | 8<br>16<br>16                    |       | mA    |

| $P_{DIS}$  | Power Dissipation     | DC Input                                                                                                                                            | ●           |                   | 1300                             | 1485  | mW    |

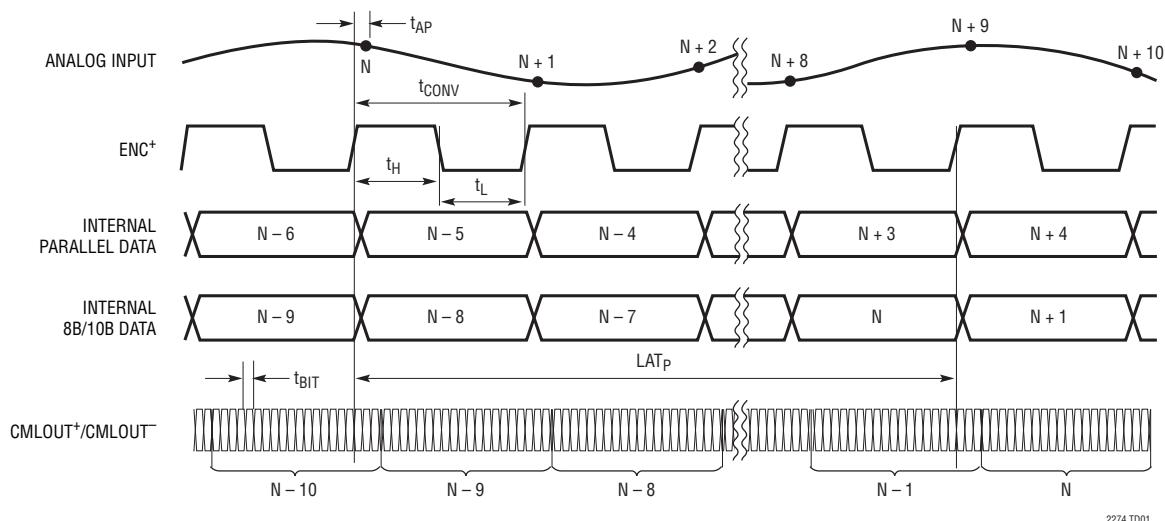

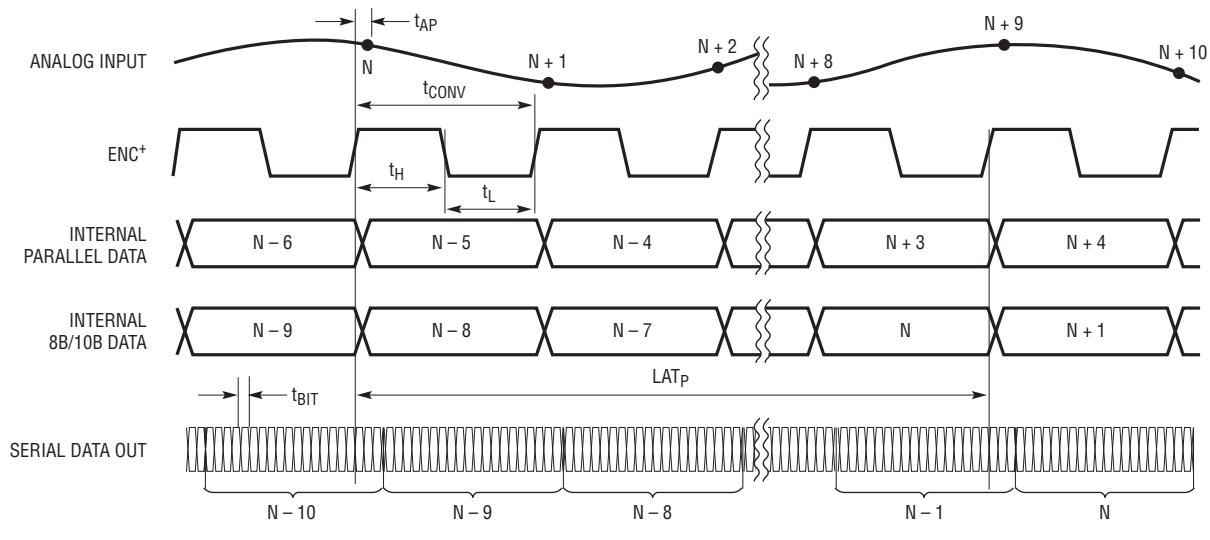

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL        | PARAMETER                                                    | CONDITIONS                                          |   | MIN      | TYP           | MAX                 | UNITS  |

|---------------|--------------------------------------------------------------|-----------------------------------------------------|---|----------|---------------|---------------------|--------|

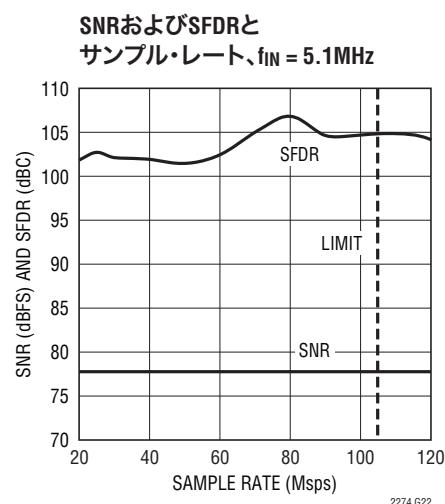

| $f_S$         | Sampling Frequency                                           | (Note 9)                                            | ● | 20       | 105           |                     | MHz    |

| $t_{CONV}$    | Conversion Period                                            |                                                     |   |          | $1/f_S$       |                     | s      |

| $t_L$         | ENC Clock Low Time                                           | (Note 7)                                            | ● | 3.1      | 4.762         | 25                  | ns     |

| $t_H$         | ENC Clock High Time                                          | (Note 7)                                            | ● | 3.1      | 4.762         | 25                  | ns     |

| $t_{AP}$      | Sample-and-Hold Aperture Delay                               |                                                     |   |          | 0.7           |                     | ns     |

| $t_{BIT, UI}$ | Period of a Serial Bit                                       |                                                     |   |          | $t_{CONV}/20$ |                     | s      |

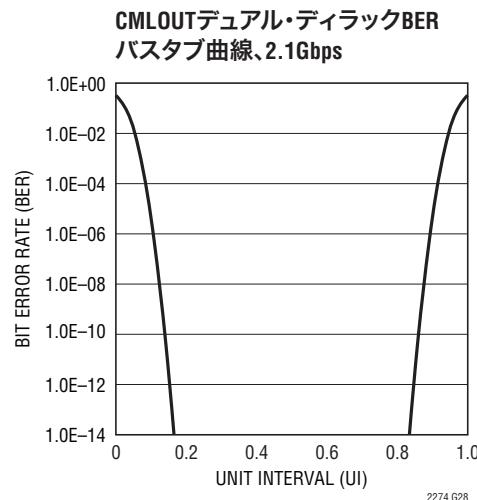

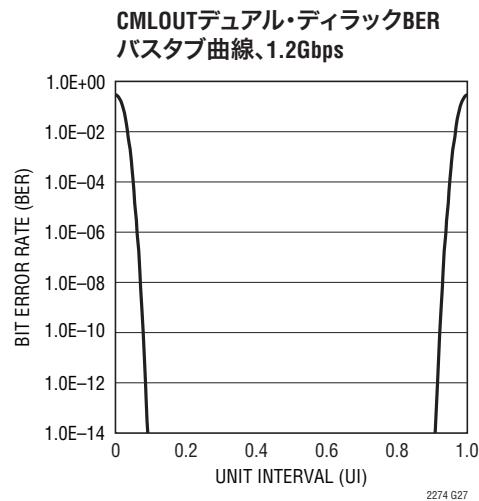

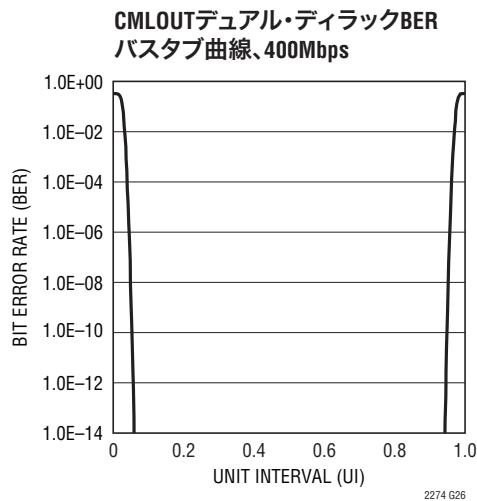

| $t_{JIT}$     | Total Jitter of CMLOUT $\pm$ (P-P)                           | BER = 1E-12 (Note 7)                                | ● |          |               | 0.35                | UI     |

| $t_R, t_F$    | Differential Rise and Fall Time of CMLOUT $\pm$ (20% to 80%) | $R_{TERM} = 50\Omega, C_L = 2\text{pF}$<br>(Note 7) | ● | 50       | 110           |                     | ps     |

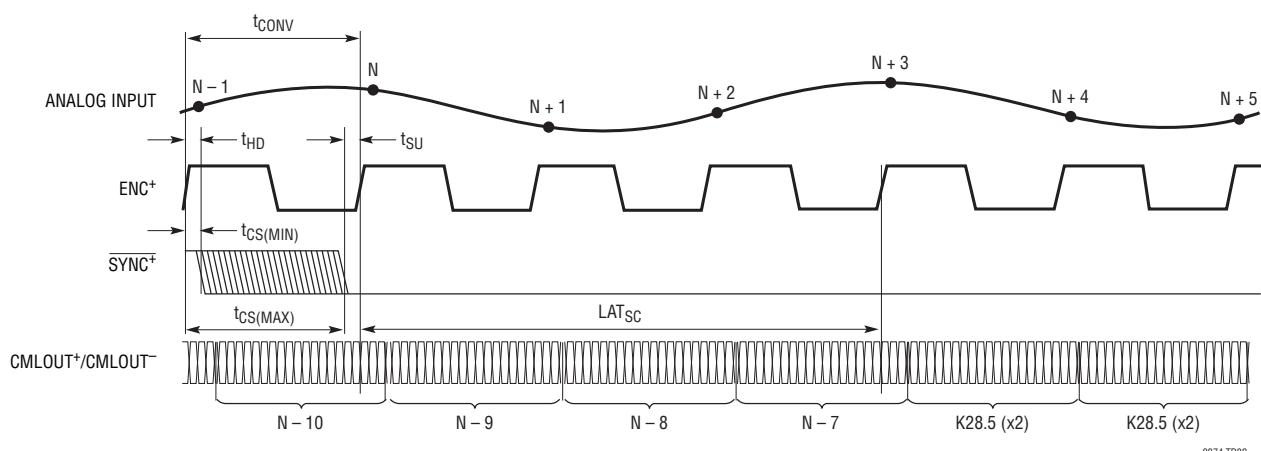

| $t_{SU}$      | SYNC to ENC Clock Setup Time                                 | (Note 7)                                            | ● | 2        |               |                     | ns     |

| $t_{HD}$      | ENC Clock to SYNC Hold Time                                  | (Note 7)                                            | ● | 2.5      |               |                     | ns     |

| $t_{CS}$      | ENC Clock to SYNC Delay                                      | (Note 7)                                            | ● | $t_{HD}$ |               | $t_{CONV} - t_{SU}$ | ns     |

| $LAT_P$       | Pipeline Latency                                             |                                                     |   |          | 9             |                     | Cycles |

| $LAT_{SC}$    | Latency from SYNC Active to COMMA Out                        |                                                     |   |          | 3             |                     | Cycles |

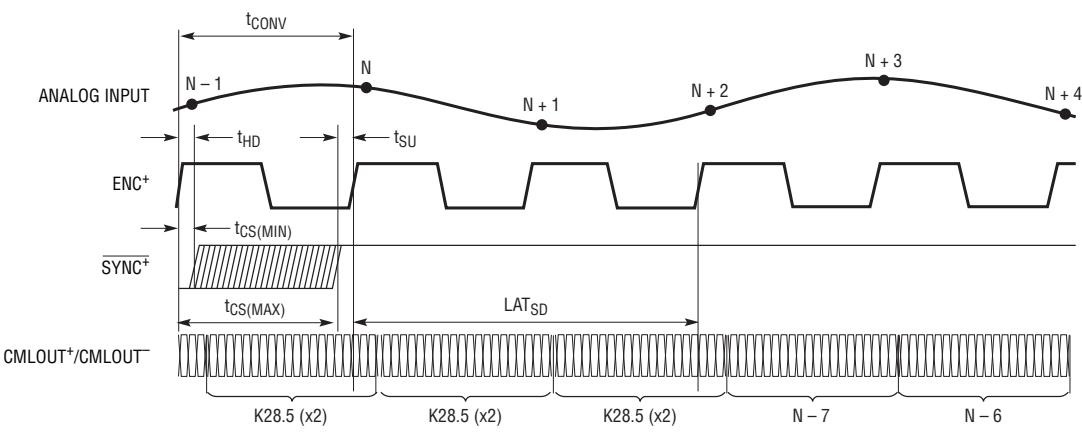

| $LAT_{SD}$    | Latency from SYNC Release to DATA Out                        |                                                     |   |          | 2             |                     | Cycles |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**全ての電圧値は(注記がない限り)GNDを基準にしている。

**Note 3:**これらのピンの電圧がGNDより下に引き下げられるか、 $V_{DD}$ より上に引き上げられると、内部のダイオードによってクランプされる。この製品は、GNDより低いか、または $V_{DD}$ より高い電圧でラッピングアップを生じることなしに100mAを超える入力電流を処理することができる。

**Note 4:**注記がない限り、 $V_{DD} = 3.3\text{V}$ 、 $f_{SAMPLE} = 105\text{MHz}$ 、差動 $ENC^+/ENC^- = 2\text{V}_{\text{P-P}}$ の正弦波(1.6Vの同相電圧)、入力範囲 = 差動ドライブで $2.25\text{V}_{\text{P-P}}$ ( $\text{PGA} = 0$ )。

**Note 5:**積分非直線性は、伝達曲線に「最もよく合致する直線」からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 6:**オフセット誤差は、2の補数出力モードで出力コードが0000 0000 0000 0000と1111 1111 1111の間を行ったり来たりするとき、-1/2 LSBから測定したオフセット電圧である。

**Note 7:**設計によって保証されているが、テストされない。

**Note 8:** $V_{DD} = 3.3\text{V}$ 、 $f_{SAMPLE} = 105\text{MHz}$ 、入力範囲 = 差動ドライブで $2.25\text{V}_{\text{P-P}}$ 。

**Note 9:**推奨動作条件。

**Note 10:**スイッチト・キャバシタのアナログ入力のダイナミック電流はリーク電流に比べて大きくなることがあり、サンプル・レートによって変化する。

**Note 11:**リーク電流の過渡電流は起動時に高くなる。ドライブ抵抗は1k以下に保つ。

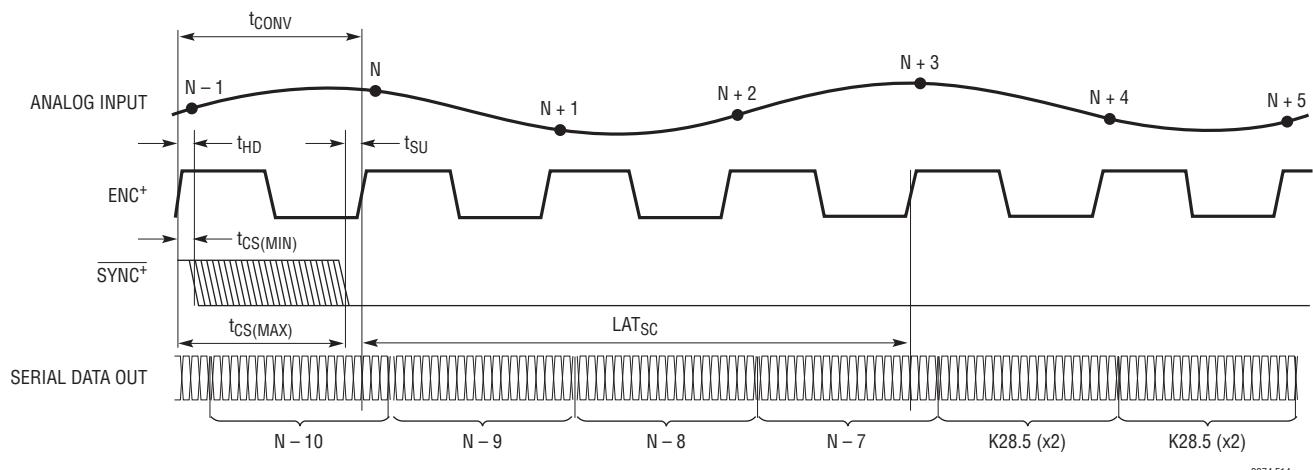

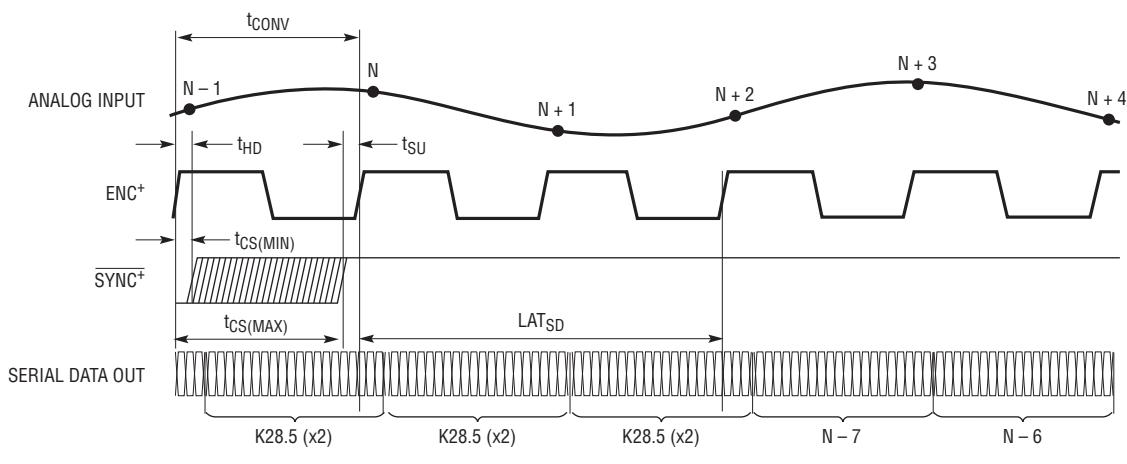

## タイミング図

アナログ入力からシリアルデータ出力のタイミング

SYNC<sup>+</sup>の立下りエッジからコンマ(K28.5)のタイミングSYNC<sup>+</sup>の立上りエッジからデータのタイミング

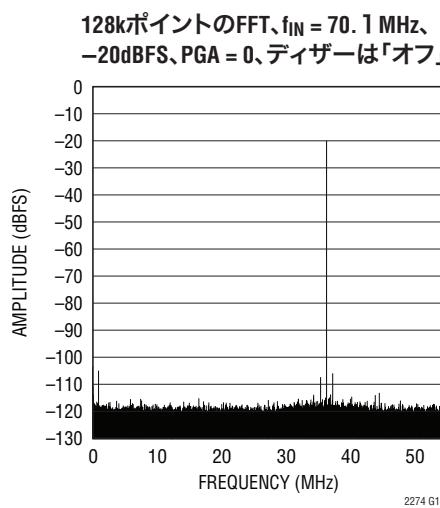

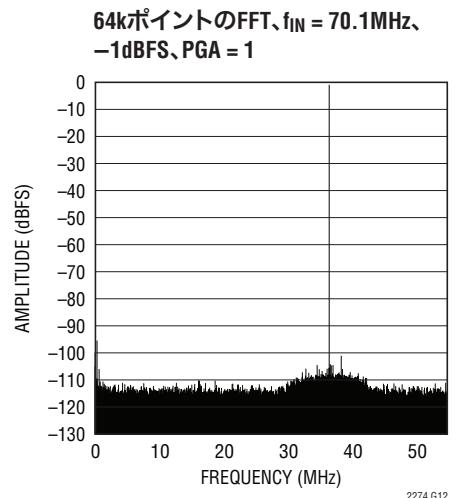

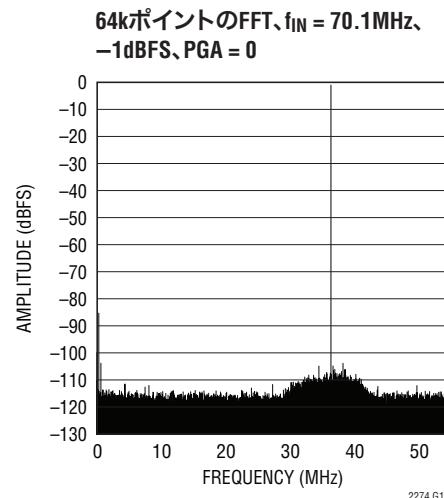

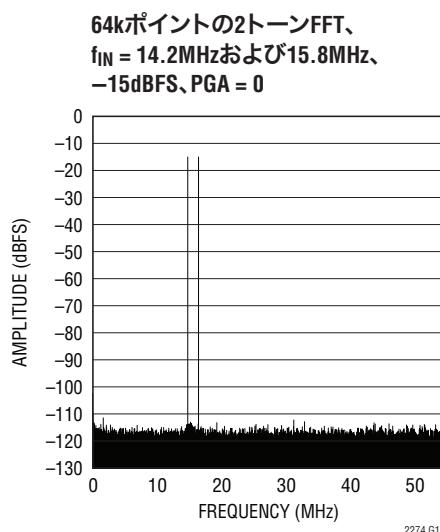

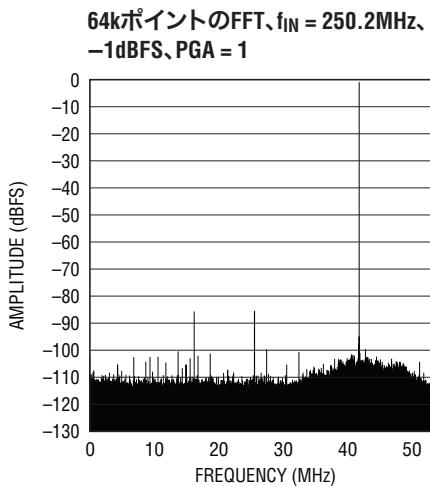

標準的性能特性 注記がない限り、 $V_{DD} = 3.3V$ 、 $0V_{DD} = 1.5V$ 、 $T_A = 25^\circ C$ 、 $F_S = 105Msps$ 。

積分非直線性(INL)と出力コード

微分非直線性(DNL)と出力コード

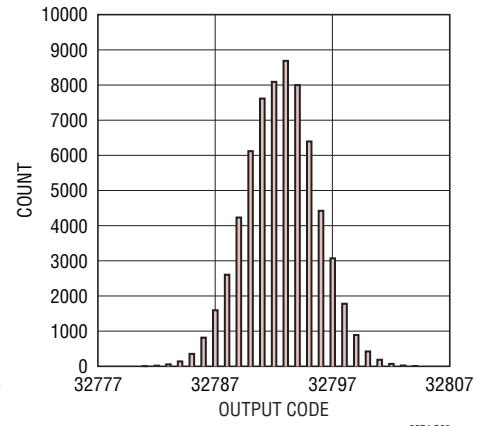

接地した入力のヒストグラム

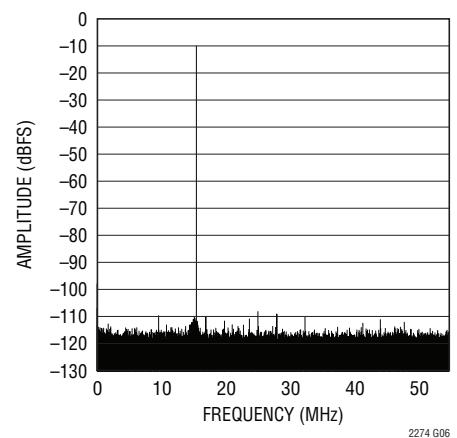

128kポイントのFFT、 $f_{IN} = 4.93MHz$ 、

-1dBFS、PGA = 0

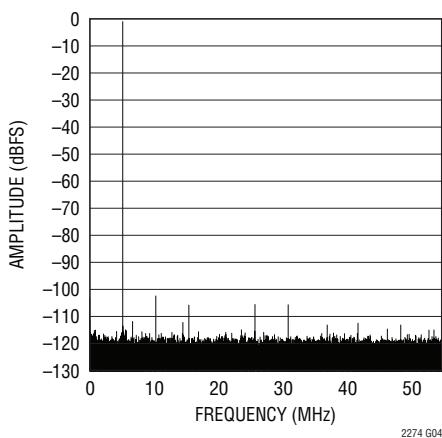

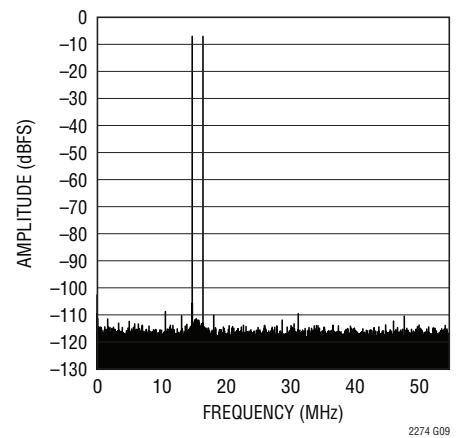

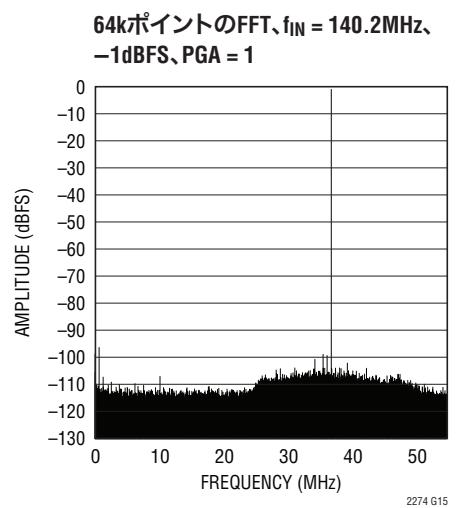

64kポイントのFFT、 $f_{IN} = 14.8MHz$ 、

-1dBFS、PGA = 0

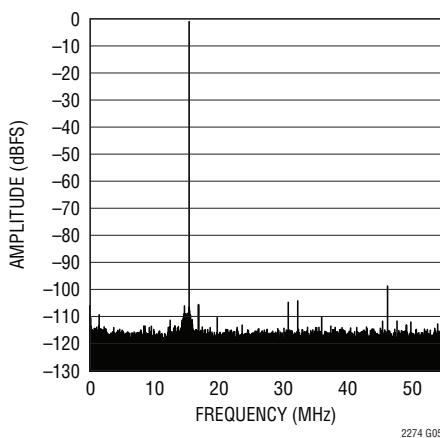

64kポイントのFFT、 $f_{IN} = 14.8MHz$ 、

-10dBFS、PGA = 0

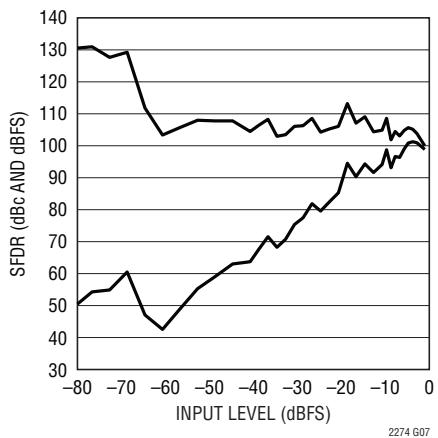

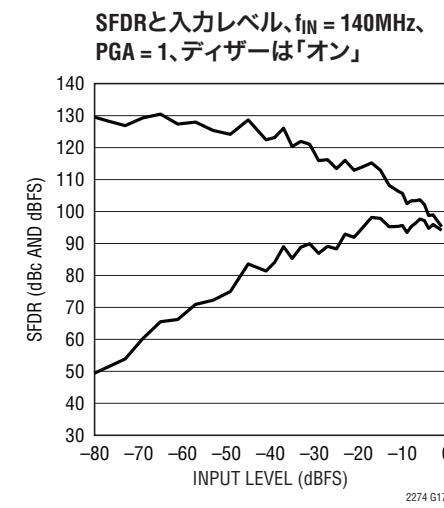

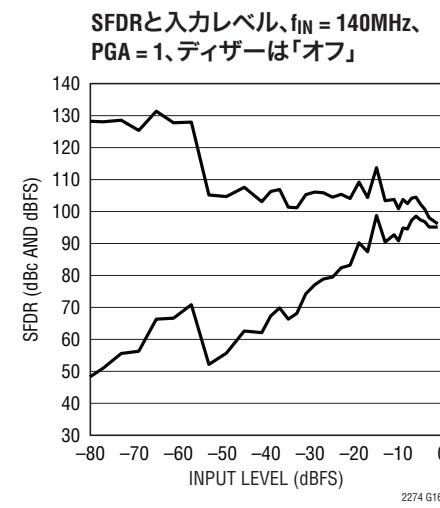

SFDRと入力レベル、 $f_{IN} = 15MHz$ 、

PGA = 0、ディザーは「オフ」

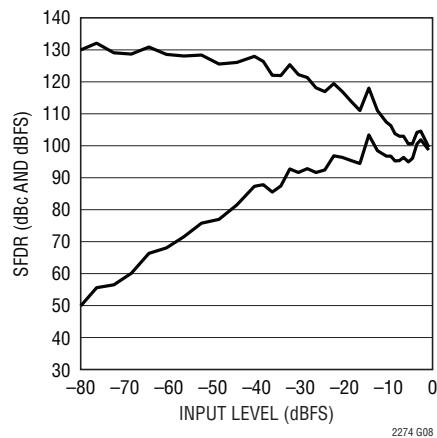

SFDRと入力レベル、 $f_{IN} = 15MHz$ 、

PGA = 0、ディザーは「オン」

64kポイントの2トーンFFT、

$f_{IN} = 14.2MHz$ および $15.8MHz$ 、

-7dBFS、PGA = 0

2274fb

標準的性能特性 注記がない限り、 $V_{DD} = 3.3V$ 、 $0V_{DD} = 1.5V$ 、 $T_A = 25^\circ C$ 、 $F_S = 105Msps$ 。

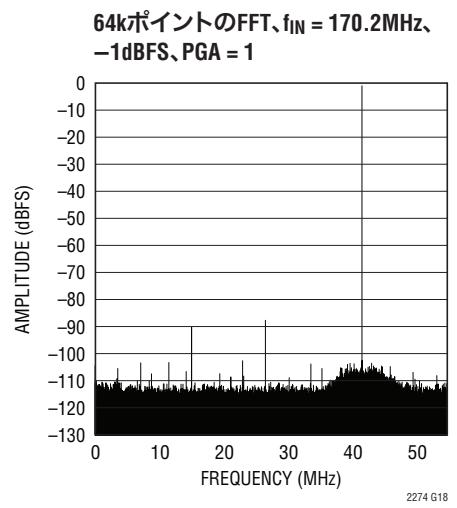

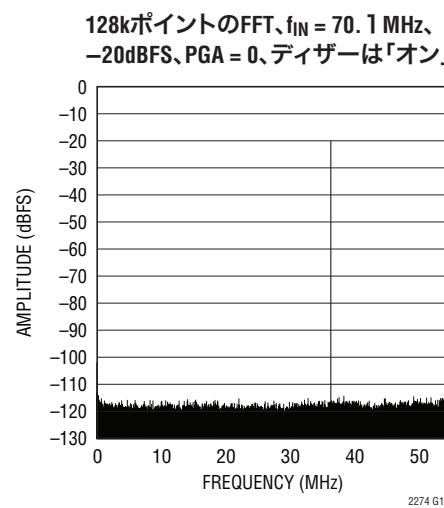

## 標準的性能特性 注記がない限り、 $V_{DD} = 3.3V$ 、 $OV_{DD} = 1.5V$ 、 $T_A = 25^\circ C$ 、 $F_S = 105Msps$ 。

2274fb

**標準的性能特性** 注記がない限り、 $V_{DD} = 3.3V$ 、 $OV_{DD} = 1.5V$ 、 $T_A = 25^\circ C$ 、 $F_S = 105Msps$ 。

## ピン機能

**V<sub>DD</sub>(ピン1、2、12、13)**: アナログ3.3V電源。0.1μFのセラミック・チップ・コンデンサを使ってGNDにバイパスします。

**GND(ピン3、6、7、8、11、14、21、26、27、30、37、40)**: ADCの電源グランド。

**A<sub>IN</sub><sup>+</sup>(ピン4)**: 正の差動アナログ入力。

**A<sub>IN</sub><sup>-</sup>(ピン5)**: 負の差動アナログ入力。

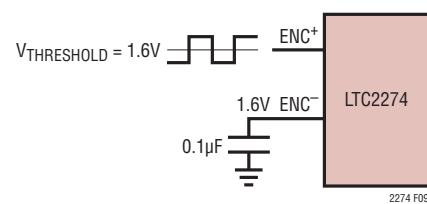

**ENC<sup>+</sup>(ピン9)**: 正の差動エンコード入力。サンプリングされたアナログ入力はENC<sup>+</sup>の立上りエッジで保持されます。このピンは6.2kΩ抵抗を通して内部で1.6Vにバイアスされています。出力電圧はENC<sup>+</sup>の立下りエッジでラッチすることができます。

**ENC<sup>-</sup>(ピン10)**: 負の差動エンコード入力。サンプリングされたアナログ入力はENC<sup>-</sup>の立下りエッジで保持されます。このピンは6.2kΩ抵抗を通して内部で1.6Vにバイアスされています。シングルエンドのエンコード信号の場合、0.1μFのコンデンサを使ってグランドにバイパスします。

**DITH(ピン15)**: 内部ディザイナー・イネーブル・ピン。DITHを“L”にすると、内部ディザイナーがディスエーブルされます。DITHを“H”にすると、内部ディザイナーがイネーブルされます。ディザイナー動作の詳細については、このデータシートの「内部ディザイナー」のセクションを参照してください。

**ISMODE(ピン16)**: アイドル同期モード。ISMODEがアサートされていないとき、同期は一連のコンマ符号(K28.5)によって行われます。ISMODEがアサートされているときは、特殊なアイドル同期モードがイネーブルされ、同期後の最初のデータ・コードに負のランニング・ディスペリティを設定するために、1つのコンマ符号(K28.5)とそれに続く適当なデータ・コード・グループ(D5.6またはD16.2)を送って同期が行われます。

**SRR0(ピン17)**: サンプル・レートの範囲選択ビット0。サンプル・レートの動作範囲を選択するのに、SRR1ピンと一緒に使います。

**SRR1(ピン18)**: サンプル・レートの範囲選択ビット1。サンプル・レートの動作範囲を選択するのに、SRR0ピンと一緒に使います。

**SHDN(ピン19、20)**: シャットダウン・ピン。両方のピンを“H”にするとデバイスがシャットダウンします。

**OV<sub>DD</sub>(ピン22、25)**: 出力ドライバの正電源。この電源の範囲は、直接結合されたCML出力では1.2V～V<sub>DD</sub>であり、AC結合された、または差動終端されたCML出力では1.4V～OV<sub>DD</sub>です。0.1μFのセラミック・チップ・コンデンサを使ってグランドにバイパスします。

**CMLOUT<sup>-</sup>(ピン23)**: 負の高速CML出力。

**CMLOUT<sup>+</sup>(ピン24)**: 正の高速CML出力。

**SYNC<sup>+</sup>(ピン28)**: 同期リクエストの正入力(JESD204との互換性のためアクティブ“L”)。このピンを少なくとも2サンプル・クロック・サイクルの間“L”レベルにすると、フレームの同期が開始されます。

**SYNC<sup>-</sup>(ピン29)**: 同期リクエストの負入力。このピンを少なくとも2サンプル・クロック・サイクルの間“H”レベルにすると、フレームの同期が開始されます。シングルエンド動作の場合、0.1μFのコンデンサを使ってグランドにバイパスし、SYNC<sup>+</sup>ポイントとしてSYNC<sup>+</sup>を使います。

**FAM(ピン31)**: フレーム・アラインメント・モニタ・イネーブル。“H”レベルにすると、フレーム・アラインメントのモニタのために、フレームの末尾の予め決められたデータをK28.7符合で置換することをイネーブルします。

**PAT0(ピン32)**: パターン選択ビット0。シリアル・インターフェースのテストパターンを選択するのに、PAT1と一緒に使います。

**PAT1(ピン33)**: パターン選択ビット1。シリアル・インターフェースのテストパターンを選択するのに、PAT0と一緒に使います。

**SCRAM(ピン34)**: データ・スクランブリングのイネーブル。このピンを“H”レベルにすると、ADCの各データ・サンプルのスクランブリングで多項式 $1+x^{14}+x^{15}$ が適用されます。スクランブリングは8B/10Bエンコーディングの前に行われます。

**PGA(ピン35)**: プログラム可能な利得アンプ制御ピン。“L”にすると、1のフロントエンド利得および2.25V<sub>P-P</sub>の入力範囲が選択されます。“H”にすると、1.5のフロントエンド利得および1.5V<sub>P-P</sub>の入力範囲が選択されます。

**MSBINV(ピン36)**: MSBの反転。“H”レベルにすると、MSBを反転させ、2の補数形式をイネーブルします。

## ピン機能

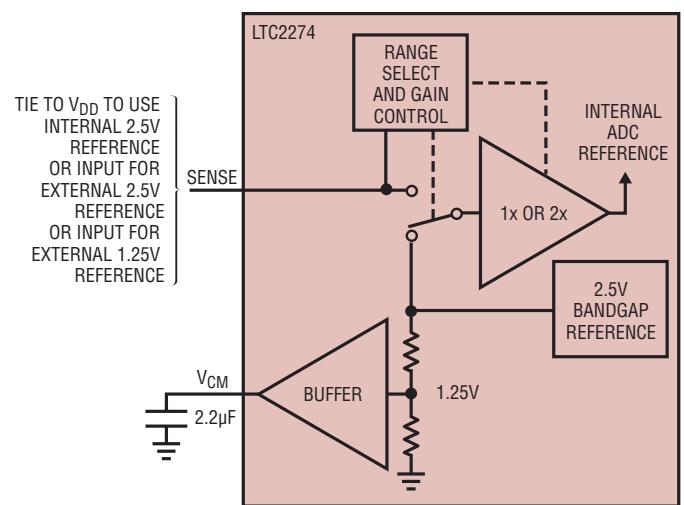

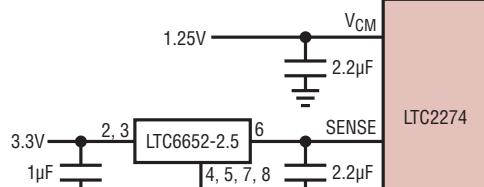

**SENSE(ピン38)**:リファレンス・モードの選択および外部リファレンス入力。内部2.5Vバンドギャップ・リファレンスを選択するには、SENSEをV<sub>DD</sub>に接続します。2.5Vまたは1.25Vの外部リファレンスを使うことができます。両方のリファレンス値とも2.25VのフルスケールADCレンジを設定します(PGA = 0)。

**V<sub>CM</sub>(ピン39)**:1.25Vの出力。入力同相電圧の最適電圧。最小2.2μFでグランドにバイパスする必要があります。セラミック・チップ・コンデンサを推奨します。

**GND(露出パッド)(ピン41)**:ADCの電源グランド。パッケージの底面の露出パッドはグランドに半田付けする必要があります。

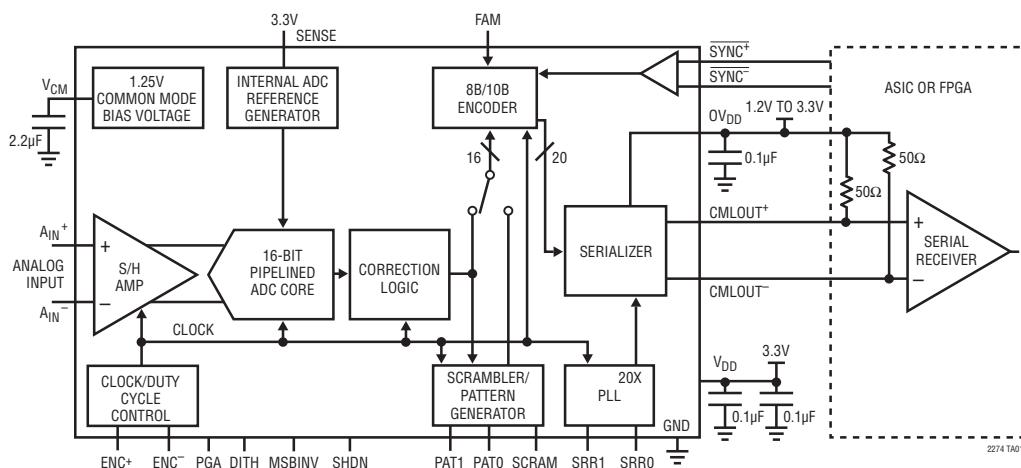

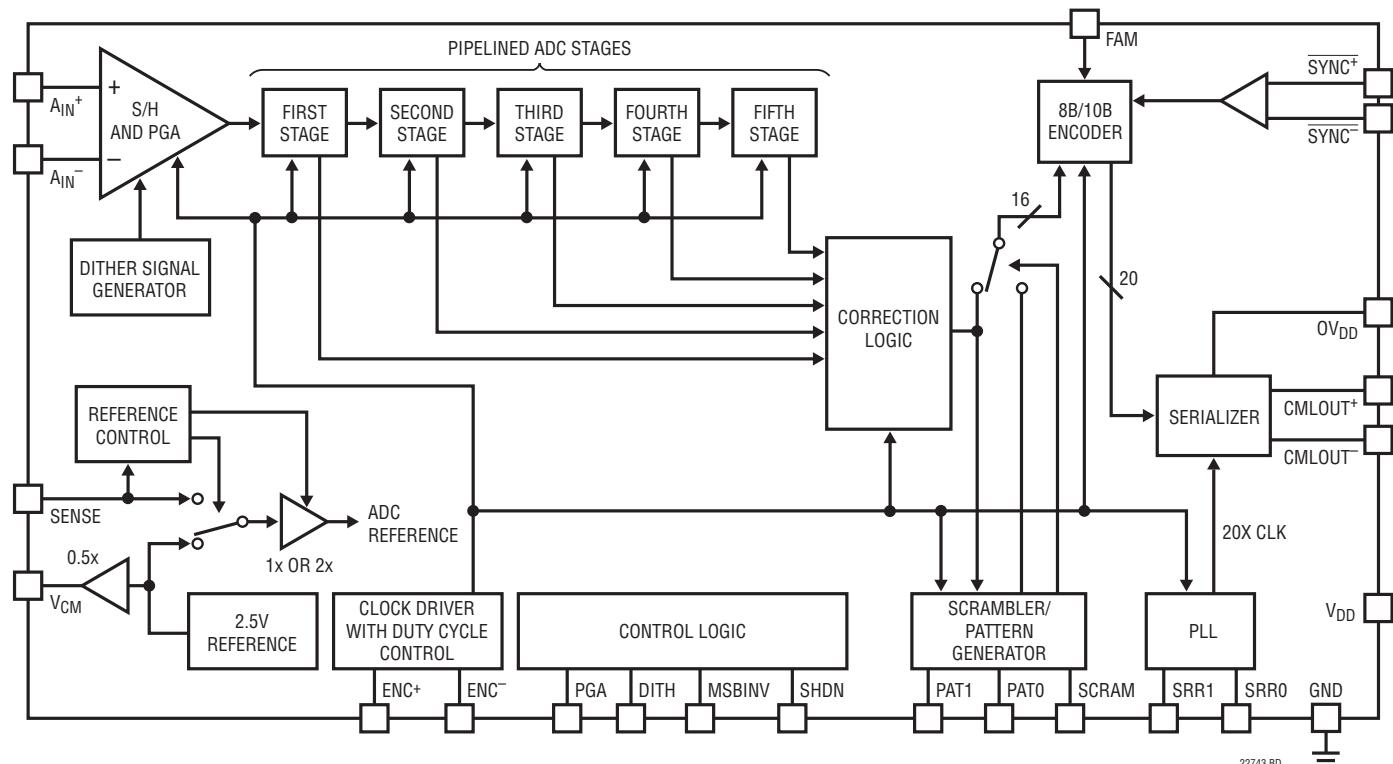

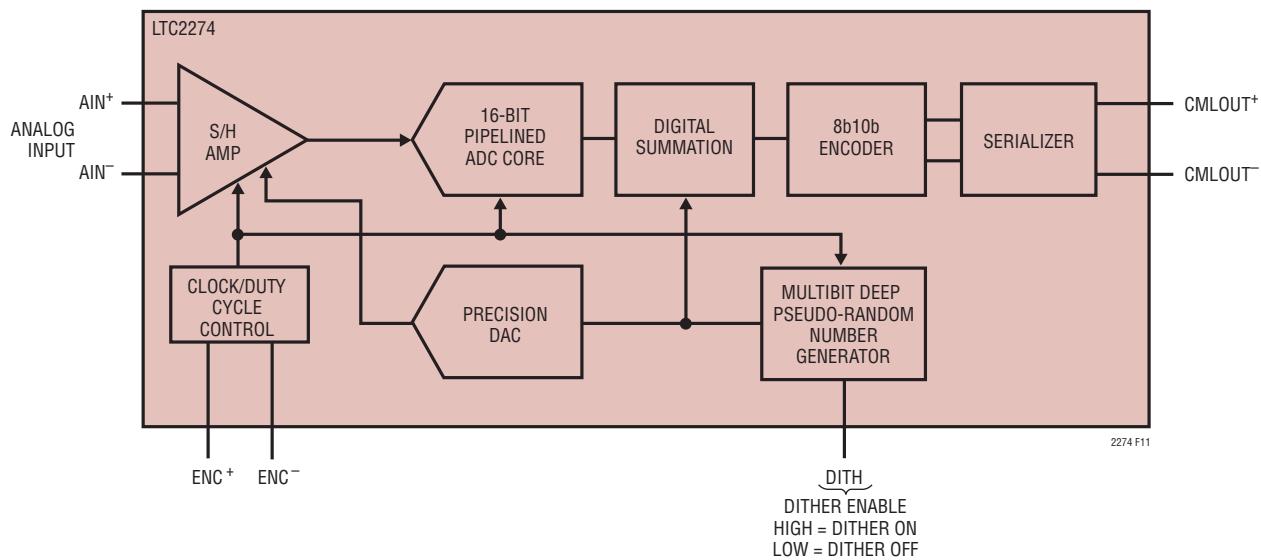

## ブロック図

図1. 機能ブロック図

## 定義

### ダイナミック性能に関する用語

#### 信号と雑音+歪みの比

信号と雑音+歪みの比S/(N+D)は、ADCの出力での基本入力周波数のRMS振幅と他の全ての周波数成分のRMS振幅の比です。出力の帯域はDCからサンプリング周波数の半分より低い周波数に制限されます。

#### 信号対雑音比

信号対雑音比(SNR)は基本入力周波数のRMS振幅と、最初の5つの高調波を除く他の全ての周波数成分のRMS振幅の比です。

#### 全高調波歪み

全高調波歪みは入力信号の全高調波のRMS和の基本周波数に対する比です。帯域外高調波はDCとサンプリング周波数の半分の間の周波数帯域でエイリアスを生じます。THDは次のように表されます。

$$\text{THD} = -20 \log (\sqrt{V_2^2 + V_3^2 + V_4^2 + \dots + V_N^2} / V_1)$$

ここで、 $V_1$ は基本波のRMS振幅で、 $V_2 \sim V_N$ は2次～N次の高調波の振幅です。

#### 混変調歪み

ADCの入力信号に複数のスペクトル成分が含まれていると、ADCの伝達関数の非直線性により、THDに加えて混変調歪み(IMD)が生じることがあります。IMDは周波数の異なる別の正弦波入力が存在するためにある正弦波入力に生じる変化です。

周波数がfaとfbの2つの純粋な正弦波がADCの入力に与えられると、ADCの伝達関数の非直線性により $mfa \pm nfb$ の和と差の周波数で歪み積を生じることがあります。ここで、mとnは0、1、2、3などです。たとえば、3次IMD項には $2fa+fb$ 、 $fa+2fb$ 、 $2fa-fb$ および $fa-2fb$ が含まれます。3次のIMDは、最大の3次IMD積のRMS値に対する、どちらかの入力トーンのRMS値の比として定義されます。

#### スプリアスフリー・ダイナミックレンジ(SFDR)

dBcで表したピーク・スプリアス・スペクトル成分のRMS値に対する、入力信号のRMS振幅の比。SFDRはフルスケールを基準にして計算し、dBFSで表すこともできます。

#### フルパワー帯域幅

フルパワー帯域幅はフルスケールの入力信号から再構成された基本波の振幅が3dBだけ減少する入力周波数です。

#### アーチャ遅延時間

立ち上がりつつあるENC<sup>+</sup>の電圧がENC<sup>-</sup>の電圧に等しくなったときから、入力信号がサンプル・ホールド回路によってホールドされる瞬間までの時間。

#### アーチャ遅延ジッタ

変換ごとのアーチャ遅延時間の変動。このランダムな変動により、AC入力のサンプリング時にノイズが生じます。ジッタだけによるSNRは次のようになります。

$$\text{SNR}_{\text{JITTER}} = -20 \log (2\pi \cdot f_{IN} \cdot t_{JITTER})$$

### シリアル・インターフェースに関する用語

#### 8B/10Bエンコーディング

8ビットのデータ・ワード(オクテット)をシリアル伝送に適したものにするために考案されたデータ・エンコーディング方法。得られる10ビット・ワード(コード・グループ)には2つの基本的長所があります。1) レシーバはデータを捕捉するのに高速クロックを必要としません。これは、出力されるコード・グループはランレングスが制限されるので、レシーバがデータにロックして高速クロックを再生するのに十分な遷移箇所がビットストリームに含まれることを保証するからです。2) データ・ストリームのDCバランスが保たれるようにコード・グループが生成されるのでAC結合が可能です(「ランニング・ディスペリティ」を参照)。

可能な256の入力オクテットと生成される10ビット・コード・グループの表がIEEE Std 802.3-2002のパート3の表36-1に与えられています。256のデータ・コード・グループのそれぞれに関連した名称がDx,yの形式で定められており、xは0～31、yは0～7の範囲の値をとります。同標準規格の表36-2はコンマなどデータ文字ではない12の特殊コード・グループの追加セットを定義しています。

## 定義

特殊コード・グループの名称はDではなくKで始まります。8B/10Bに関する完全な記述はIEEE Std 802.3-2002のパート3のClause 36.2に与えられています。

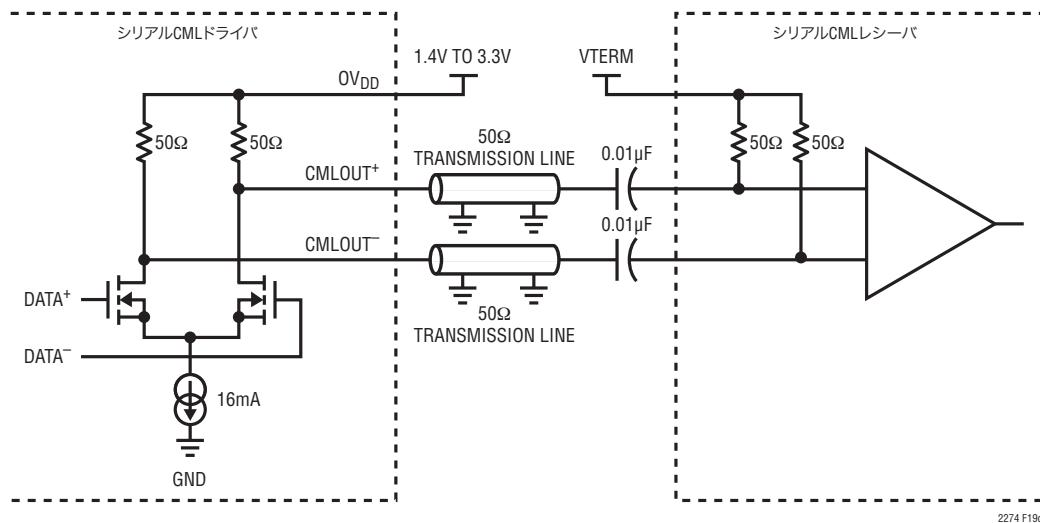

### 電流モード・ロジック(CML)

差動高速ロジックを実現するのに使われる手法。CMLは差動対(通常nタイプ)を使って、抵抗性負荷への電流を制御します。どんなロジック機能でもCMLを使って実現することができます。出力の振幅とオフセットは、バイアス電流、負荷抵抗、および終端抵抗に依存します。

この製品ファミリーはCMLドライバを使って高速シリアル・データを外部世界に伝送します。出力ドライバのバイアス電流は標準16mAで、各出力の $25\Omega$ の結合された内部と外部の終端抵抗両端に $400\text{mV}_{\text{P-P}}$ (差動で $800\text{mV}_{\text{P-P}}$ )の信号振幅を発生します。

### コード・グループ

8B/10Bエンコーダからの10ビット出力、または8B/10Bデコーダへの10ビット入力。

### コンマ

バイナリ・シーケンスの“0011111”または“1100000”を含む特殊8B/10Bコード・グループ。コンマ・シーケンスは(ビット・エラーが発生しない限り)どの通常のコード・グループによつても発生することができないので、コンマはフレームのアラインメントおよび同期に使われます。コンマを含んでいる3つの特殊コード・グループがあります(K28.1、K28.5、およびK28.7)。

簡単のため、これら3つの特殊コード・グループのそれぞれは多くの場合「コンマ」と呼ばれますが、厳密な意味では、コンマに指定されているのはこれらのコード・グループの最初の7ビットです。

### DCバランスのとれた信号

信号の最小の劣化でAC結合することができるように特に前処理した信号。DCバランスは1と0の平均個数が等しいとき達成され、カップリング・コンデンサの受信側に対してDCがふらつく望ましくない影響を除去します。8B/10Bコーディングを使うと、DCバランスが下のディスパリティ規則によって実現されます(「ランニング・ディスパリティ」を参照)。

### デスクランブル

スクランブルされたデータをスクランブルされる前の状態に復元するロジック・ブロック。セルフアライニング・デスクランブルはスクランブルと同じ疑似ランダム・ビット・シーケンスに基づいていますので、アラインメント信号は不要です。この製品ファミリーでは、スクランブルは $1+x^{14}+x^{15}$ の多項式をベースにしており、セルフアライニング・プロセスにより、最初の1個のADCサンプルが失われます。

### フレーム

完全なワードを形成するオクテットまたはコード・グループのグループ。この製品ファミリーでは、1フレームは2個のオクテットまたはコード・グループで構成され、1個のADCサンプルを構成します。

### フレーム・アラインメント・モニタ(FAM)

初期フレーム同期が確立された後、フレーム・アラインメント・モニタにより、レシーバはデータの損失なしにコード・グループのアラインメントが維持されていることを検証することができます。これは、特定の条件が満たされたとき、フレームの最後のコード・グループをK28.7コンマで置き換えて行われます。レシーバは、アラインメント検証のために、このコンマをフレーム内の位置マーカーとして使います。データをデコードした後、レシーバはK28.7コンマを元のデータに置き換えます。

### アイドル・フレーム同期モード(ISMODE)

K28.5の代わりにアイドル順序セットを使って初期フレーム同期を確立する特殊な同期モード。

「アイドル順序セット」は、IEEE Std 802.3-2002のパート3、Clause 36.2.4.12で定義されています。一般に、これはK28.5コンマにD5.6またはD16.2が1つ続きます。

## 定義

K28.5コンマを送った後のランニング・ディスパリティが正であれば、コンマの後にD16.2が送られ、そうでなければD5.6が送られます。その結果、アイドル順序セットのエンディング・ディスパリティは常に負になります。

## 初期フレーム同期

レシーバからのリクエストに対してフレーム同期情報をレシーバに知らせるプロセス。JESD204に準拠するため、K28.5コンマがプリアンブルとして送られます。プリアンブルが検出されるとレシーバは同期リクエストを終了し、プリアンブルの伝送がフレームの最後まで続きます。レシーバはプリアンブルの後の最初の通常データ・ワードをデータ・フレームの始点に指定します。

## オクテット

8B/10Bエンコーダへの8ビット入力、または8B/10Bデコーダからの8ビット出力。

## ランレンジングスリミテッド(RLL)

シリアル伝送前にデータをエンコードすることにより、データ・ストリーム内の連続した1または0の個数を制限すること。

このプロセスは、レシーバがフェーズロック・ループを使ってロックして高速クロックを再生するのに十分な個数の遷移箇所がシリアル・データ内に存在することを保証します。

## ランニング・ディスパリティ

DCバランスを維持するために、各入力オクテットに対して2種類の可能な8B/10B出力コード・グループがあります。ランニング・ディスパリティが計算され、DCバランスを維持するため2つのコード・グループのどちらを伝送するか決定します。

コード・グループのディスパリティがサブブロックと呼ばれる2つのセグメントで解析されます。サブブロック1はコード・グループの最初の6ビットで構成され、サブブロック2はコード・グループの最後の4ビットで構成されます。サブブロック内の1の個数が0の個数より多いとき、ランニング・ディスパリティは正であり0の個数が1の個数より多いとき、ランニング・ディスパリティは負です。サブブロック内で1と0の個数が等しいとき、ランニング・ディスパリティは変化せず保たれます。

現在のランニング・ディスパリティの極性により、DCバランスを維持するため2つのコード・グループのどちらを送るかが決まります。ディスパリティの規則の詳細に関しては、IEEE Std 802.3-2002のパート3、Clause 36.2.4.4を参照してください。

## 疑似ランダム・ビット・シーケンス(PRBS)

有限のインターバルでランダムな性質を持つデータ・シーケンス。最も一般的に使用されるPRBSテストパターンは $1+x^m+x^n$ の形の多項式によって記述することができ、 $2^n-1$ ビットの長さでランダムな性質を有します。ここで、nはPRBS多項式の次数を表し、mはランダム・シーケンスの長さを最大化する役目を果たします。

## スクランブラー

疑似ランダム・ビット・シーケンスを入力オクテットに適用し、高速シリアル・ビット・ストリームの総内容を最小化するロジック・ブロック。

## アプリケーション情報

### コンバータの動作

LTC2274はパイプライン構成のCMOSマルチステップ・コンバータで、フロントエンドPGAを備えています。図1に示されているように、このコンバータはパイプライン構成の5段のADCを備えています。サンプリングされたアナログ入力は9サイクル後にデジタル値になります（「タイミング図」を参照）。アナログ入力( $A_{IN}^+$ 、 $A_{IN}^-$ )は同相ノイズ耐性を改善して入力範囲を広げるため差動です。さらに、差動入力ドライブを使うと、サンプル・ホールド回路の偶数次高調波が減少します。エンコード・クロック入力( $ENC^+$ 、 $ENC^-$ )も同相ノイズ耐性を改善するため差動です。

図1に示されているパイプライン構成の各段は、1個のADC、再構成DAC、および誤差残余アンプを備えています。各段の機能は各段の入力電圧のデジタル表現を（結果として生じるアナログ誤差残余とともに）生成することです。各段のADCは量子化を行い、残余は入力電圧と再構成DACの出力との差をとて発生します。残余は残余アンプによって増幅されて後続段に渡されます。パイプラインに構成された各段はクロックの交替する位相で動作するので、奇数段がそれらの残余を出力しているとき偶数段がそれらの残余を取得するように、またその逆になるように動作します。

LTC2274のパイプライン構成のADCは差動の $ENC^+$ / $ENC^-$ 入力ピンの状態で定まる2つのフェーズで動作します。簡単にするために、この説明では、 $ENC^+$ が $ENC^-$ より大きいとき $ENC$ は“H”であると表現し、 $ENC^+$ が $ENC^-$ より小さいとき $ENC$ は“L”であると表現します。

$ENC$ が“L”的とき、アナログ入力は図1の「S/HとPGA」ブロック内部の入力サンプル・ホールド・コンデンサに差動でサンプリングされます。 $ENC$ の立上りエッジで、サンプル・コンデンサの電圧がホールドされます。 $ENC$ が“H”的間、ホールドされた入力電圧はS/Hアンプによってバッファされます。このS/Hアンプはパイプライン構成の最初のADC段をドライブします。最初の段は $ENC$ の“H”フェーズの間にS/Hアンプの出力を取得します。 $ENC$ の立下りエッジで最初の段はその残余を出力し、この残余が2番目の段によって取得されます。このプロセスがパイプラインの終点まで続きます。

初段に続く各ADC段にはフラッシュ誤差とアンプのオフセット誤差を調節するための追加誤差補正範囲があります。ADCの全段からの結果はデジタル動作で遅延させ、エンコードされ、シリアル化され、出力バッファに送られる前にそれらの結果を補正ロジックで適切に結合できるようにします。

## アプリケーション情報

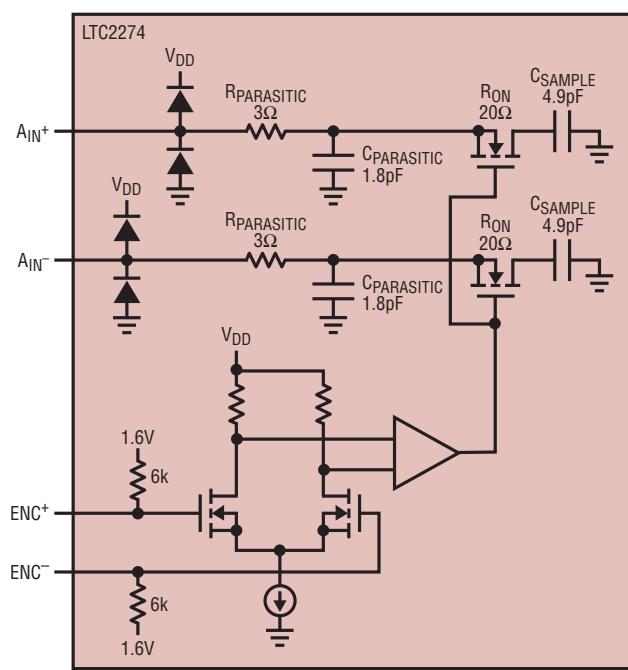

### サンプル/ホールド動作と入力ドライブ

#### サンプル/ホールド動作

LTC2274のCMOS差動サンプル・ホールドの等価回路を図2に示します。差動アナログ入力はNMOSトランジスタを通してサンプリング・コンデンサ( $C_{SAMPLE}$ )に直接サンプルされます。各入力のところに示されているコンデンサ( $C_{PARASITIC}$ )は各入力に関連した他の全ての容量の和です。

ENCが”L”のとき、サンプリング・フェーズの間NMOSトランジスタはアナログ入力をサンプリング・コンデンサに接続するので、これらのコンデンサは差動入力電圧まで充電され、さらにこの電圧を追尾します。ENCの立上りエッジで、サンプルされた入力電圧がサンプリング・コンデンサにホールドされます。ENCが”H”的とき、ホールド・フェーズの間サンプリング・コンデンサは入力から切り離され、ホールドされた電圧はADCコアに渡されて処理されます。ENCが”H”から”L”に遷移すると、入力はサンプリング・コンデンサに再度接続され、新しいサンプルを収集します。サンプリング・コンデンサには直前のサンプルがまだホールドされているので、隣接するサンプル間の電圧変化に比例した充電グリッチがこのとき見られます。直前のサンプルと新しいサンプルの間の変化が小さいと、入力に見られる充電グリッチは小さくなります。ナイキスト周波数の近くの入力周波数で見られる変化のように、入力の変化が大きければ、さらに大きな充電グリッチが見られます。

#### 同相バイアス

規定性能を達成するには、ADCのサンプル・ホールド回路には差動ドライブが必要です。各入力は、2.25Vレンジでは(PGA = 0) 1.25Vの同相電圧を中心にして $\pm 0.5625V$ 振幅させ、1.5Vレンジでは(PGA = 1)  $\pm 0.375V$ 振幅させます。V<sub>CM</sub>出力ピン(ピン39)は同相バイアス・レベルを与えるように設計されています。V<sub>CM</sub>はトランジスタのセンタータップに直接接続してDC入力レベルを設定するか、またはオペアンプ差動ドライバ回路の基準レベルとして接続することができます。V<sub>CM</sub>ピンは2.2 $\mu$ F以上でADCの近くのグランドにバイパスする必要があります。

#### 入力ドライブのインピーダンス

全ての高性能高速ADCの場合と同様、LTC2274のダイナミック動作は入力ドライブ回路(特に2次と3次の高調波)の影響を受けることがあります。ソース・インピーダンスと入力アクタンスはSFDRに影響を与えることがあります。ENCの立下りエッジで、サンプル・ホールド回路は4.9pFのサンプリング・コンデンサを入力ピンに接続してサンプリング周期を開始します。サンプリング周期はENCが立ち上ると終了し、サンプルされた入力をサンプリング・コンデンサにホールドします。入力回路は理想的にはサンプリング周期1/(2F<sub>ENCODE</sub>)の間にサンプリング・コンデンサを完全に充電するのに十分なだけ高速である必要があります。ただし、これが常に可能だとは限らず、不完全なセトリングのためにSFDRが減少することがあります。不十分なセトリングの影響を小さくするため、サンプリング・グリッチができるだけリニアになるように設計されています。

最適動作のため、各入力のソース・インピーダンスを100 $\Omega$ 以下にすることを推奨します。差動入力のソース・インピーダンスは整合させる必要があります。よく整合していないと、偶数次高調波、特に2次高調波が高くなります。

図2. 等価入力回路

## アプリケーション情報

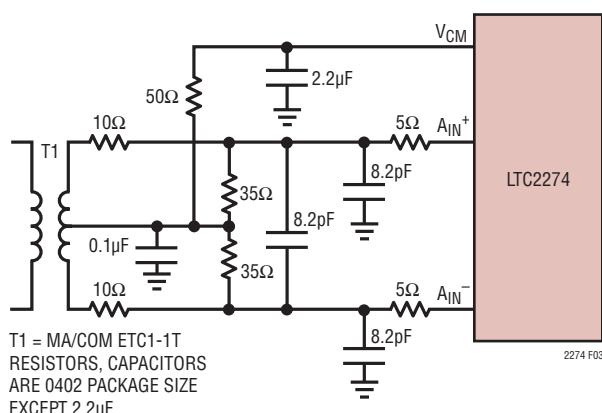

### 入力ドライブ回路

#### 入力のフィルタリング

ADCの入力の1次RCローパス・フィルタは2つの機能を果たすことができます。入力回路からのノイズを制限し、ADCのS/Hのスイッチングから絶縁します。LTC2274は非常に広い帯域幅のS/H回路(DC~700MHz)を備えており、広い範囲のアプリケーションで使うことができますので、唯1つのRCフィルタを推奨することは不可能です。

図3、図4aおよび図4bは入力周波数の3つの範囲の入力RCフィルタリングの3つの例を示しています。一般に、耐えられる限りコンデンサを大きくするのが望ましいと言えます。これは、デジタル回路から結合したノイズとともに、ランダムノイズを抑えるのに役立ちます。LTC2274はデータシートの仕様を満たすのにどんな入力フィルタも必要としませんが、フィルタリングがないと、入力ドライブ回路に対するノイズ要件が厳しくなります。

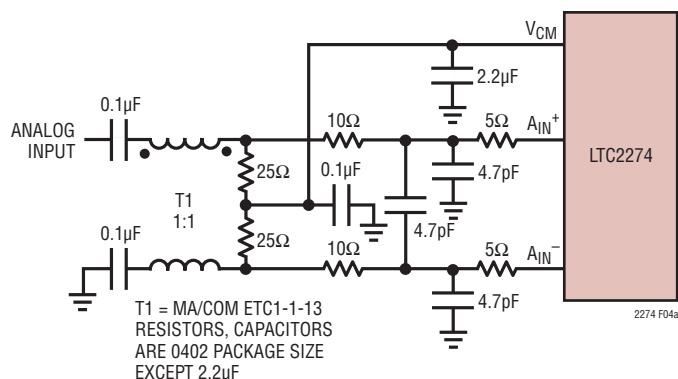

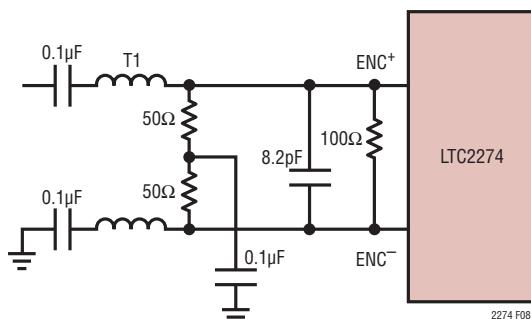

#### トランス結合回路

2次側にセンタタップを備えたRF変圧器によってドライブされるLTC2274を図3に示します。2次側センタタップはV<sub>CM</sub>でDCバイアスされており、ADCの入力信号を最適DCレベルに設定します。図3には巻数比が1:1のトランスが示されています。他の巻数比を使うこともできますが、巻数比が増加するにつれ、ADCから見込むインピーダンスも増加します。ソース・

図3. トランスを使ったシングルエンドから差動への変換。5MHz~150MHzの入力周波数に対して推奨

インピーダンスが50Ωを超えると、入力帯域幅が減少し、高周波数の歪みが増加することがあります。トランスを使う場合の不利な点は低周波応答の低下です。ほとんどの小型RFトランスは1MHzより低い周波数での性能が良くありません。

センタタップ付きトランスは2次側のDCバイアスの手段として便利ですが、高い入力周波数ではバランスが悪くなることが多い、大きな2次高調波を生じます。

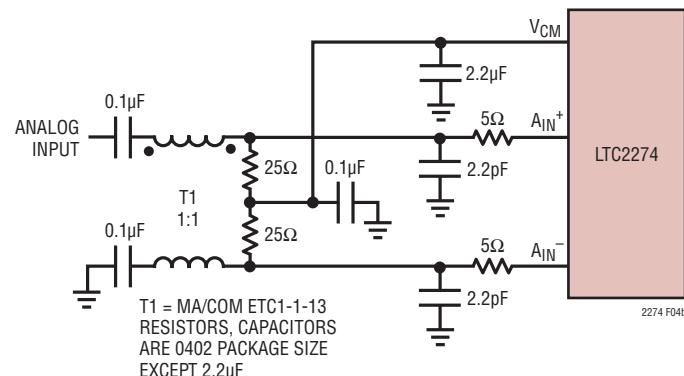

伝送ラインのバラン・トランスを使ったトランス結合を図4aに示します。このタイプのトランスの高周波応答とバランスは、磁束結合されたセンタタップ付きトランスに比べてはるかに優れています。カップリング・コンデンサがグランド端子と入力の1次側端子に追加されるので、2次側端子を1.25Vにバイアスすることができます。もっと高い入力周波数に適した部品を使った同じ回路を図4bに示します。

図4a. 伝送ライン・バラン・トランスの使用

100MHz~250MHzの入力周波数に推奨

図4b. 伝送ライン・バラン・トランスの使用

250MHz~500MHzの入力周波数に推奨

## アプリケーション情報

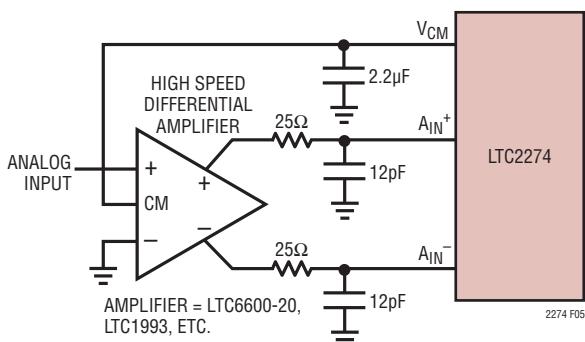

### 直接結合回路

差動アンプを使ってシングルエンド入力信号を差動入力信号に変換する例を図5に示します。この方法の利点は低い入力周波数に対する応答が良いことです。ただし、どんなオペアンプや閉ループ・アンプも利得帯域幅が制限されているので、高い入力周波数ではADCのSFDRが劣化します。さらに、広帯域のオペアンプや差動アンプはノイズが高くなる傾向があります。その結果、ADCの入力の前でノイズ帯域幅が制限されていない限り、SNRが劣化します。

### リファレンスの動作

2.5Vのバンドギャップ・リファレンス、利得をプログラム可能なアンプおよび制御回路で構成されるLTC2274のリファレンス回路を図6に示します。LTC2274にはリファレンス動作の3つのモードが備わっています。内部リファレンス、1.25Vの外部リファレンスまたは2.5Vの外部リファレンスです。内部リファレンスを使用するには、SENSEピンをV<sub>DD</sub>に接続します。外部リファレンスを使用するには、単純に1.25Vまたは2.5Vのリファレンス電圧をSENSE入力ピンに与えます。SENSEに1.25Vまたは2.5Vを与えると、どちらの場合も2.25V<sub>P-P</sub>のフルスケール・レンジになります(PGA = 0)。1.25Vの出力V<sub>CM</sub>が入力のドライブ回路の同相バイアスのために与えられます。V<sub>CM</sub>出力には外部バイパス・コンデンサが必要です。このコンデンサは、内部回路と外部回路に、高周波領域で低インピーダンスのグランド経路を与えます。これはリファレンスの補償コンデンサとし

図5. 差動アンプを使ったDC結合による入力

ても機能します。このコンデンサがないとリファレンスは安定しません。安定性のために必要な最小値は2.2μFです。

利得をプログラム可能な内部アンプはADCの内部リファレンス電圧を与えます。このアンプのセッティングの要件は非常に厳しく、外部で使用するためにアクセスすることはできません。

SENSEピンは公称2.5Vまたは1.25Vの外部リファレンス入力を中心にして±5%ドライブすることができます。この調整範囲を使って、ADCの利得誤差や他のシステム利得誤差を調整することができます。内部リファレンスを選択するときは、SENSEピンをできるだけコンバータの近くでV<sub>DD</sub>に接続します。SENSEピンを外部からドライブする場合、1μF(以上)のセラミック・コンデンサを使ってデバイスのできるだけ近くでグランドにバイパスします。

### PGAピン

PGAピンはADCのフロントエンドの2つの利得設定のどちらかを選択します。PGA = 0は2.25V<sub>P-P</sub>の入力範囲を選択し、PGA = 1は1.5V<sub>P-P</sub>の入力範囲を選択します。2.25Vの入力範囲は最良のSNRを与えますが、100MHzを超える入力周波数では歪みが大きくなります。入力周波数が高いアプリケーションでは、低い入力範囲は歪みを改善しますが、SNRが2.4dB悪くなります。このデータシートの「標準的性能特性」のセクションを参照してください。

図6 リファレンス回路

## アプリケーション情報

2274 F07

2274 F08a

図7. 外部2.5Vリファレンス付きの

2.25VレンジのADC

T1 = MA/COM ETC1-1-13

RESISTORS AND CAPACITORS

ARE 0402 PACKAGE SIZE

2274 F08b

図8b. トランスでドライブされるエンコード

図8a. エンコード入力の等価回路

2274 F09

図9. シングルエンドのENCドライブ

(低ジッタには推奨できない)

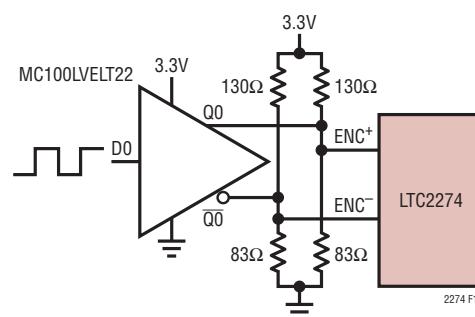

図10. CMOSからPECLへの変換器を使ったENCドライブ

## アプリケーション情報

### エンコード入力のドライブ

LTC2274のノイズ特性は、アナログ入力に依存するのと同程度にエンコード信号の質の良し悪しに依存することがあります。エンコード入力は、主に同相ノイズ源に対する耐性のため、差動でドライブするように意図されています。各入力は6kΩの抵抗を通して1.6Vにバイアスされています。これらのバイアス抵抗はトランジスタ結合のドライブ回路のDC動作点を設定し、シングルエンドのドライブ回路のロジック・スレッショルドを設定することができます。

エンコード信号に含まれるどんなノイズも新たなアーチャ・ジッタを生じ、このジッタは本来のADCアーチャ・ジッタにRMSとして追加されます。

ジッタが重要な問題となる(高入力周波数)アプリケーションでは、以下の配慮が必要です。

1. 差動ドライブを使います。

2. できるだけ大きな振幅を使います。トランジスタ結合を使うなら、大きな巻数比を使って振幅を大きくします。

3. 固定周波数の正弦波信号でADCをクロック駆動する場合、エンコード信号にフィルタをかけて広帯域ノイズを減らします。

4. 両方のエンコード入力で容量と直列抵抗値をバランスさせ、どの結合ノイズも同相ノイズとして両方の入力に現われるようにします。

エンコード入力の同相範囲は1.2V～V<sub>DD</sub>です。シングルエンドのドライブの場合、各入力はグランド～V<sub>DD</sub>の範囲でドライブすることができます。

### 最大変換レートと最小変換レート

LTC2274の最大変換レートは105Mspsです。

LTC2274のサンプリング・レートの下限は20MspsのPLL最小動作周波数によって決まります。

ADCが正常に動作するには、内部CLK信号のデューティ・サイクルを50%にする必要があります。デューティ・サイクル・スタビライザ回路がデバイスに実装されており、50%から外れたENCデューティ・サイクルを使えるようにします。

### データのフォーマット

MSBINVピンはADCのデータ・フォーマットを選択します。“L”レベルはオフセット・バイナリ形式を選択します(コード0が-FSに対応し、コード65535が+FSに対応します)。MSBINVを“H”レベルにすると、2の補数形式を選択します(コード-32768が-FSに対応し、コード32767が+FSに対応します)。

### シャットダウン機能

両方のSHDNピンを“H”レベルにすると、ADCとシリアル・インターフェースがシャットダウンし、デバイスは低電流状態になります。

### 内部ディザイナー

LTC2274は伝達関数が非常にリニアな16ビットADCですが、低い入力レベルでは、伝達関数のわずかな不完全性でも不要のトーンを生じます。伝達関数の小さな誤差は通常ADCの素子の不整合によって生じます。オプションの内部ディザイナー・モードをイネーブルして、ADCの伝達曲線の入力位置をランダム化することができますので、低信号レベルのSFDRが改善されます。

図11に示されているように、サンプル・ホールド・アンプの出力はディザイナーDACの出力に加算されます。ディザイナーDACは長いシーケンスの疑似ランダム数発生器によってドライブされます。また、ディザイナーDACに与えられるランダム数は、デジタル処理でADCの結果から差し引かれます。ディザイナーDACがADCに対して精密に較正されていると、ディザイナー信号はほとんど出力に現れません。漏れ出るディザイナー信号は白色ノイズのように見えます。ディザイナーDACは、ディザイナーをオフしたときのノイズフロアに比べて、ADCのノイズフロアの上昇が0.5dBより小さくなるように較正されています。

## アプリケーション情報

図11. 内部ディザイナ回路の等価機能のブロック図

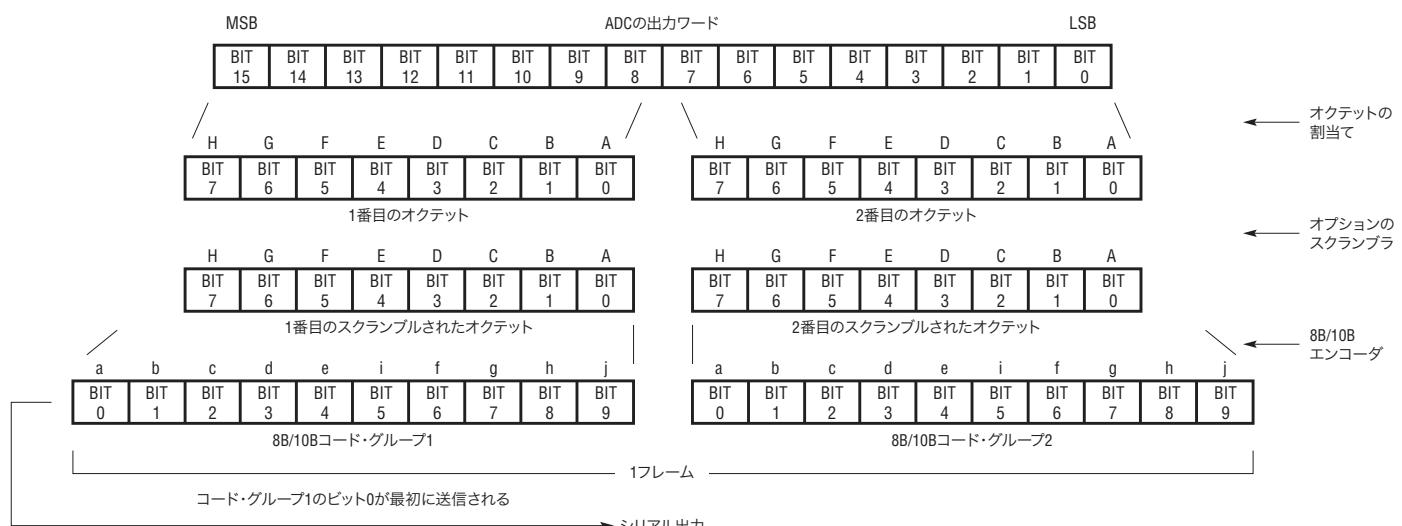

## シリアル化されたデータ・フレーム

シリアル化する前に、ADCの電圧は8B/10Bフォーマットにエンコードされます。これはDCバランスがとれています。ランレンジスが制限されています。レシーバはPLLを使ってデータにロックし、クロックを再生する必要があります。8B/10BフォーマットはADCデータが8ビットのブロック(オクテット)に分割されることを要求します。このブロックは8B/10Bの規則を適用して10ビットのコード・グループにエンコードされます(8B/10Bの詳細に関しては、IEEE Std 802.3-2002のパート3を参照)。

完全な1個の8B/10Bフレームの生成を図12に示します。ADCの最上位8ビットはフレームの前半分に割り当てられ、残りの8ビットはフレームの後半分に割り当てられます。その結果得られる2個のオクテットは次いでオプションでスクランブルされ、それぞれ対応する8B/10Bコードにエンコードされます。最後に2つの10ビット・グループがシリアル化され、コード・グループ1のビット0を先頭にして送信されます。

図12. 送信される1フレームの展開(IEEE Std 802.3-2002のパート3、図36-3と比較)

## アプリケーション情報

2274 F13

図13. アナログ・サンプルとシリアル・データ出力の関係

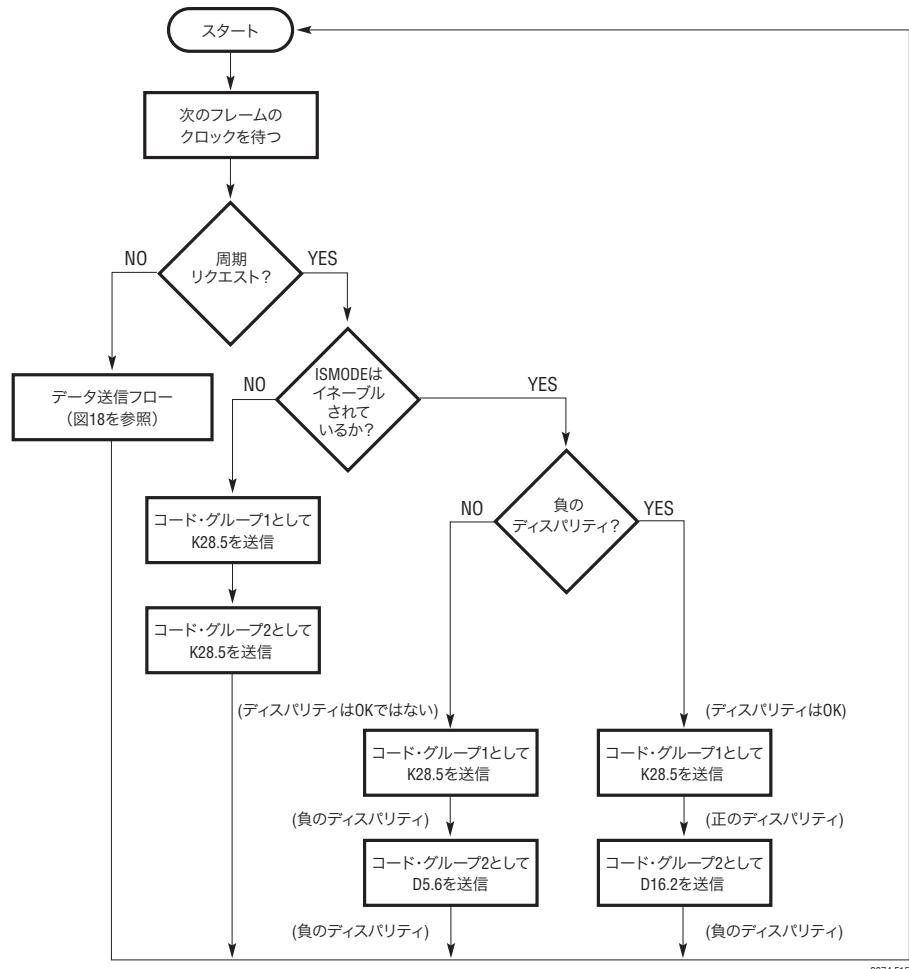

### 初期フレーム同期

フレーム・クロックが存在しないと、同期過程を通して各フレームの始点を決定する必要があります。フレーム同期を確立するための以下のシーケンスが図14と図15に示されています。

- レシーバは同期インターフェースを介して同期リクエストを発信します。

- 同期リクエストが1ENCクロック・サイクルを超えてアクティブであると、LTC2274は同期プリアンブルを送ります。ISMODEピンが“L”だと、送られたプリアンブルは、JESD204仕様に適合する連続K28.5コンマ符号で構成されます。ISMODEピンが“H”だと、一連のアイドル順序セットが送られます。アイドル順序セットは、IEEE Std 802.3-2002のパート3、Clause 36.2.4.12で定義されているように、1個のK28.5コンマとそれに続くD5.6またはD16.2のどちらかによって構成されます。

- レシーバは期待するプリアンブルを探し、適切な個数のプリアンブル文字が正しく受け取られるのを待ちます。

- レシーバは同期リクエストを終了します。

- 同期リクエストの終了を検出すると、LTC2274はフレームの終点まで同期プリアンブルを送信します。

- 次のフレームの始点で、LTC2274はデータ文字の送信を開始します。

- レシーバはプリアンブル送信後受け取った最初のデータ文字をフレームの始点に指定します。フレームの最初のオクテットにはADCの出力ワードの最上位バイトが含まれます。

## アプリケーション情報

2274 F14a

図14a. SYNC+の”L”への遷移からコンマ出力までのタイミング (ISMODEは”L”)

2274 F14b

図14b. SYNC+の”H”への遷移からデータ出力までのタイミング (ISMODEは”L”)

図15. 初期同期のフロー・ダイアグラム

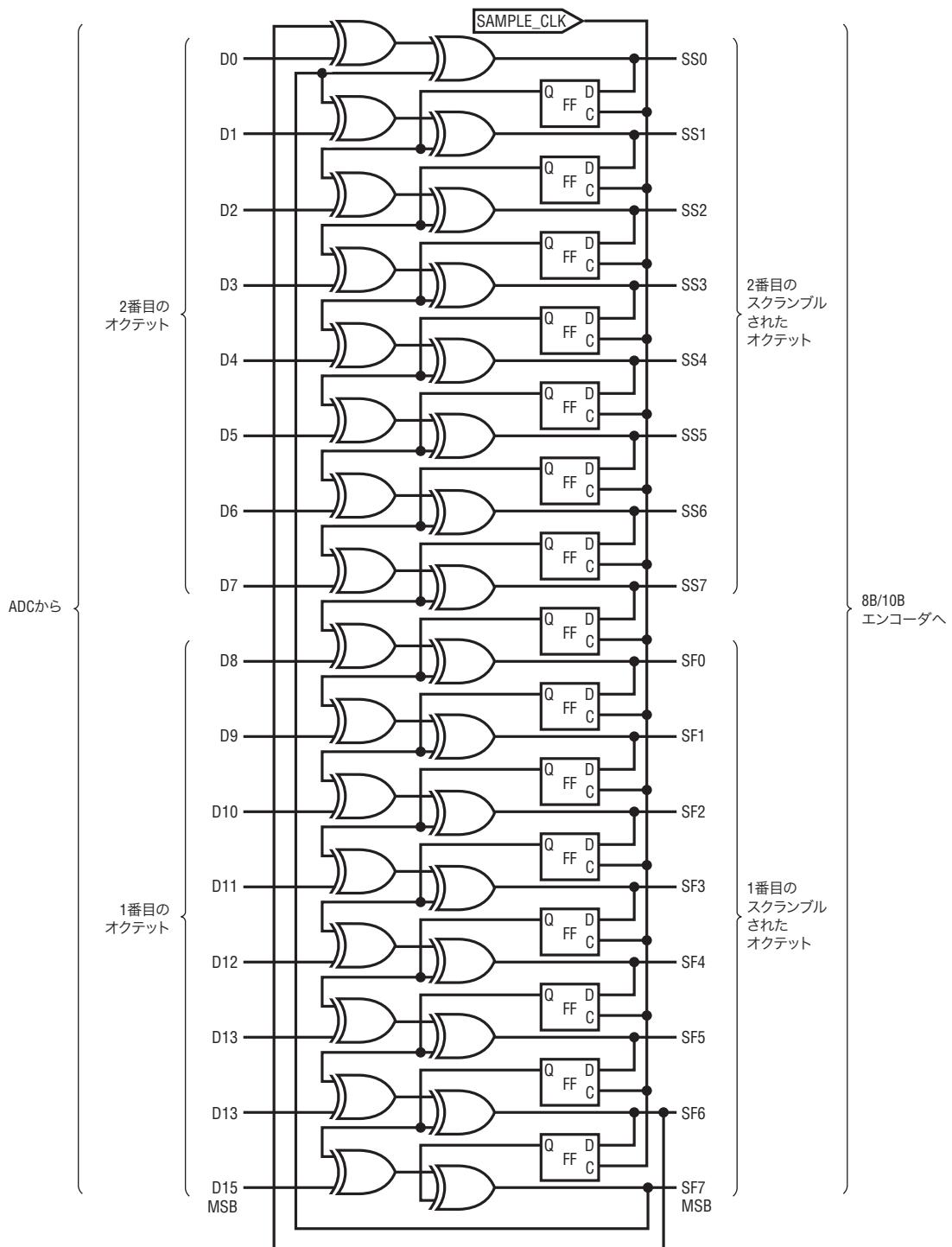

### スクランブリング

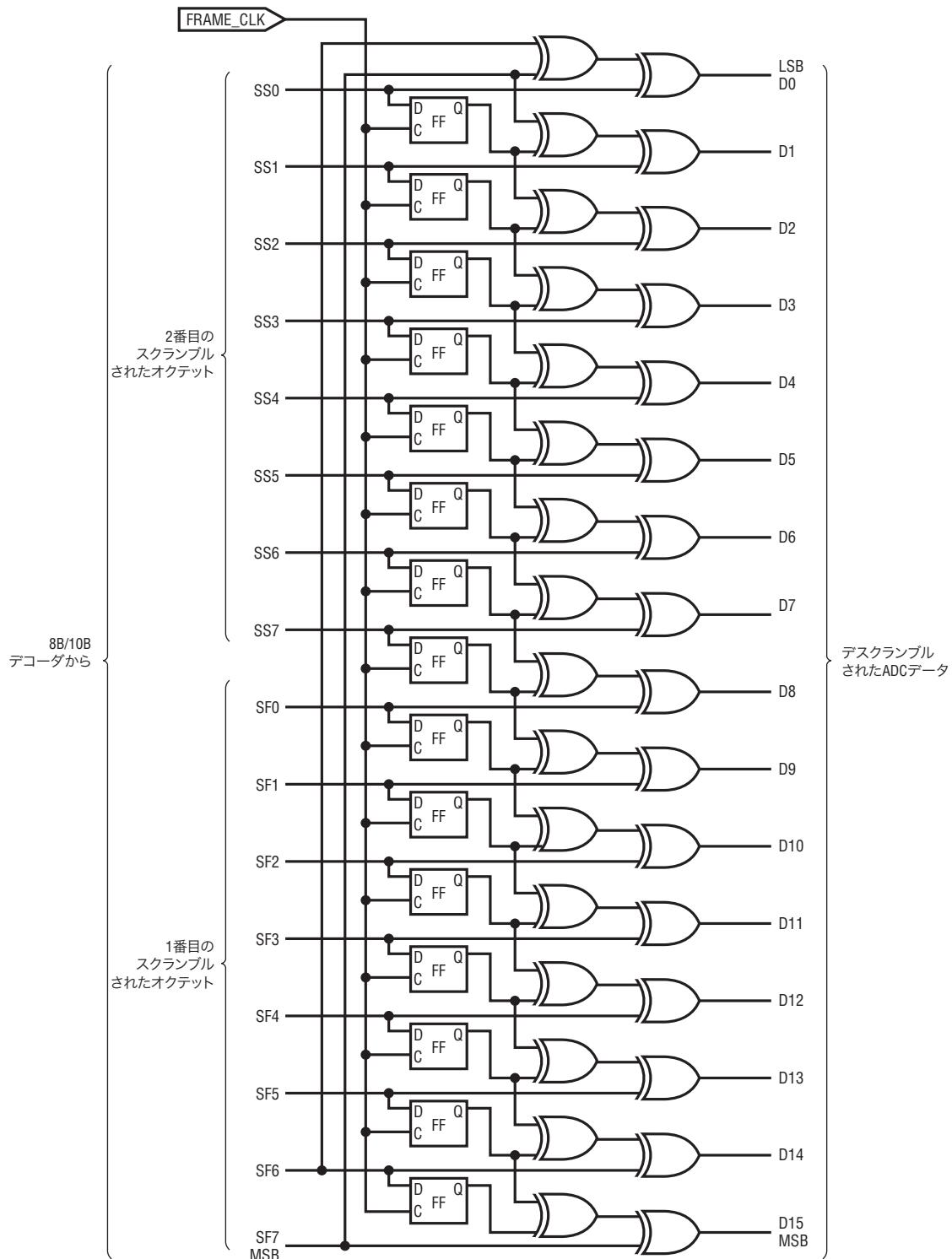

シリアル・データ出力からのスペクトル干渉を避けるため、オプションのデータ・スクランブラーがADCデータと8B/10Bエンコーダの間に追加され、シリアル・リンクのスペクトルをランダム化します。スクランブラーはSCRAMピンをロジック・レベル“H”に設定することによりイネーブルされます。スクランブラーに使われる多項式は $1+x^{14}+x^{15}$ です。これは $2^{15}-1$ 回ごとに自己を反復する疑似ランダム・パターンです。LTC2274によるこの多項式の並列形式での実装を図16に示します。

スクランブルされたデータは2つの有効な8B/10Bコード・グループに変換され、完全なフレームを構成します。8B/10Bコード・グループは次いでシリализされ送信されます。

レシーバはデータをデシリализし、コード・グループをオクテットにデコードし、さらに、図17に示されているセルフ・アライニング・デスクランブラーを使ってそれらを元のオクテットにデスクランブルする必要があります。このデスクランブラーは16ビットの並列形式で示されており、多項式 $1+x^{14}+x^{15}$ の効率的な実装であり、フレーム・クロック・レート(ADCのサンプル・レート)で動作します。

## アプリケーション情報

2274 F16

図16. LTC2274の16ビット $1+x^{14}+x^{15}$ 並列スクランブラー

2274 F17

図17. 必要な16ビット $1+x^{14}+x^{15}$ 並列デスクランブラー

## アプリケーション情報

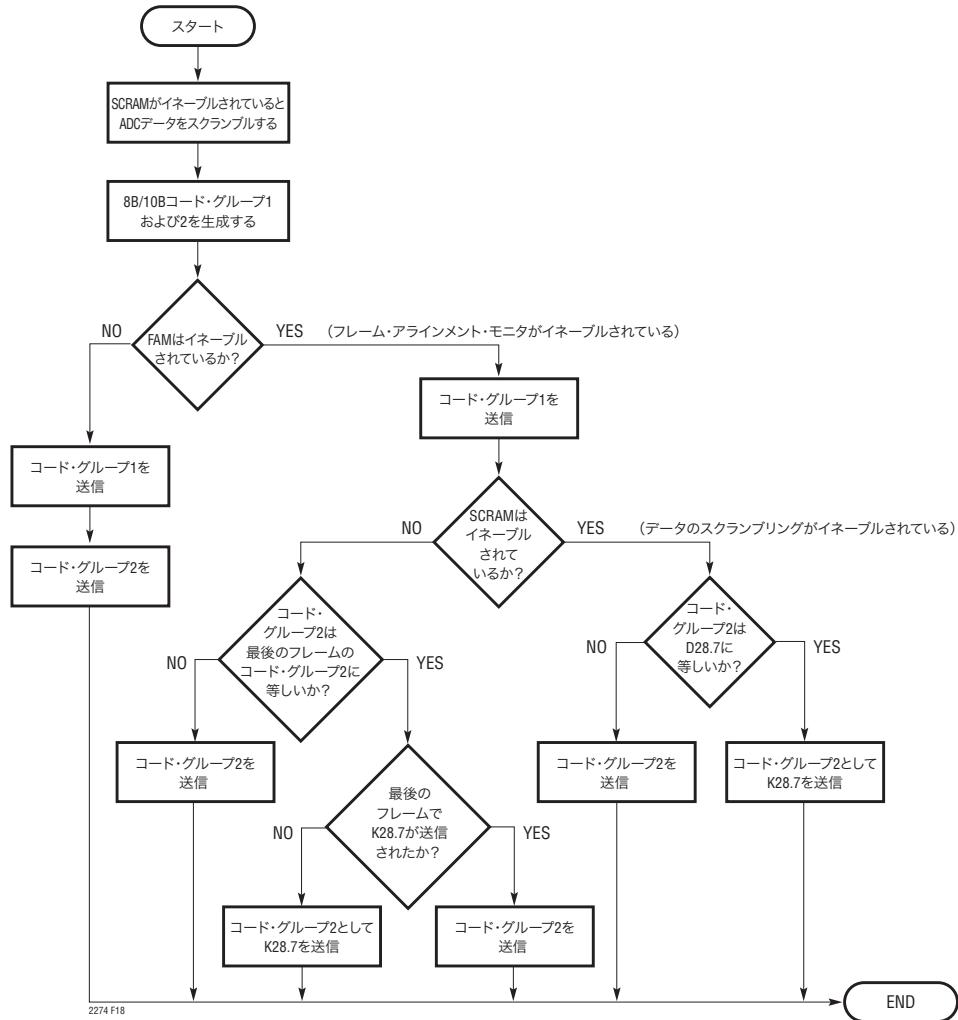

### フレーム・アラインメント・モニタ

初期同期が確立された後、フレーム・アラインメントが保たれていることを定期的に検証するのが望ましいでしょう。レシーバはいつでも同期リクエストを発することができますが、再同期の期間はデータが失われます。

データを失わずにフレーム・アラインメントを検証するには、FAMピンを“H”レベルに設定して、フレーム・アラインメント・モニタをイネーブルします。このモードでは、フレームの2番目のコード・グループの予め決められたデータが制御文字K28.7によって置き換えられます。レシーバはK28.7文字を検出して、それを元のデータで置き換える必要があります。このようにして、2番目のコード・グループを1番目と識別することができます。レシーバは、データを失うことなく、定期的にフレーム・アラインメントを検証することができます（表1と図18のフロー・ダイアグラムを参照）。表1にまとめられている2つのフレーム・アラインメント・モードがあります。

FAMモード1はFAMが“H”、SCRAMが“L”的き実現されます。

- 現在のフレームの2番目のコード・グループのデータが前のフレームの2番目のコード・グループのデータに等しいとき、

LTC2274はシリアル化する前に2番目のコード・グループを制御文字K28.7で置き換えます。ただし、K28.7符合が前のフレームで既に送信されていれば、実際のコード・グループが送信されます。

- K28.7符合を受け取ると、レシーバはそれを前のフレームの同じ位置でデコードされたデータと置き換える必要があります。

FAMモード2はFAMが“H”、SCRAMが“H”的き実現されます。

- 現在のフレームの2番目のコード・グループのデータがD28.7に等しいとき、LTC2274はシリアル化する前にこのデータをK28.7で置き換えます。

- K28.7符合を受け取ると、レシーバはそれをD28.7で置き換える必要があります。

FAMがイネーブルされているとき、レシーバはデータ・ストリームの中にK28.7符合が存在するか探す必要があります。2つの連続したK28.7符号がフレームの終点と想定されるところ以外の同じ位置に検出されると、レシーバはそのフレーム境界を新しい位置に揃え直します。

表1. フレーム・アラインメント・モニタ・モード

|            | SCRAM PIN | DDSYNC PIN | アクション                                                    |

|------------|-----------|------------|----------------------------------------------------------|

| FAM Mode 1 | Low       | High       | 2番目のコード・グループは、それが前のフレームの2番目のコード・グループに等しければ、K28.7で置き換えられる |

| FAM Mode 2 | High      | High       | 2番目のコード・グループは、それがD28.7に等しければ、K28.7で置き換えられる               |

| FAM OFF    | X         | Low        | K28.7の置換は行われない                                           |

## アプリケーション情報

図18. データ送信のフロー・ダイアグラム

### PLL動作

PLLは広い範囲のサンプル・レートに適応するように設計されています。SRR0ピンとSRR1ピンを使って、意図するサンプル・レートの範囲にPLLを構成設定します。ユーザーが利用可能なサンプリング・クロックの範囲が表2にまとめてあります。

表2. サンプル・レートの範囲

| SRR1 | SRR0 | サンプル・レートの範囲           |

|------|------|-----------------------|

| 0    | X    | 20Msps < FS ≤ 35Msps  |

| 1    | 0    | 30Msps < FS ≤ 65Msps  |

| 1    | 1    | 60Msps < FS ≤ 105Msps |

### シリアル・テストパターン

シリアル・インターフェースのテストをしやすくするため、PAT0とPAT1を介して3種類のテストパターンを選択することができます。利用可能なテストパターンを表3に示します。 $\overline{\text{SYNC}^+}$ ピン/ $\overline{\text{SYNC}^-}$ ピンを使って同期をリクエストすることにより、K28.5コマを4番目のテストパターンとして使うことができます。

表3. テストパターン

| PAT1 | PAT0 | テストパターン                                 |

|------|------|-----------------------------------------|

| 0    | 0    | ADCデータ                                  |

| 0    | 1    | 1010101010パターン<br>(8B/10Bコード・グループD21.5) |

| 1    | 0    | $1+x^9+x^{11}$ 疑似ランダム・パターン              |

| 1    | 1    | $1+x^{14}+x^{15}$ 疑似ランダム・パターン           |

## アプリケーション情報

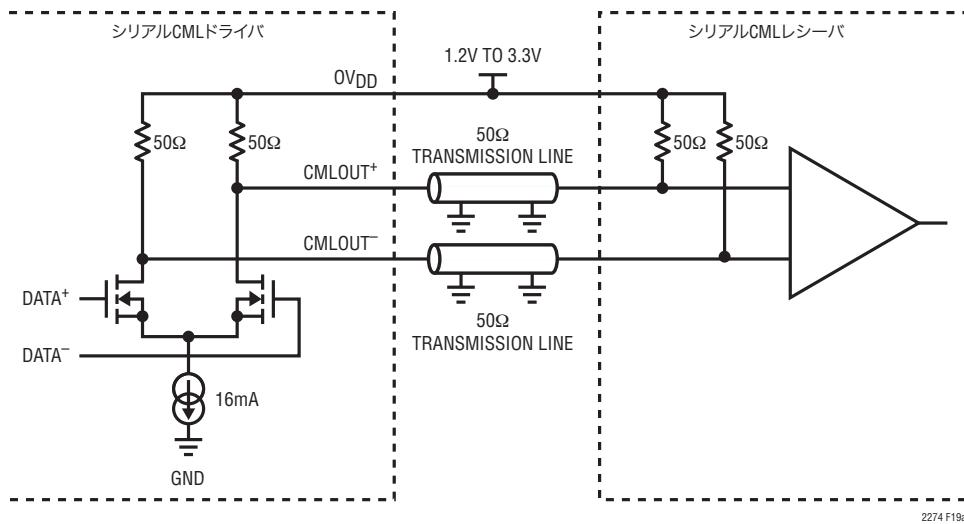

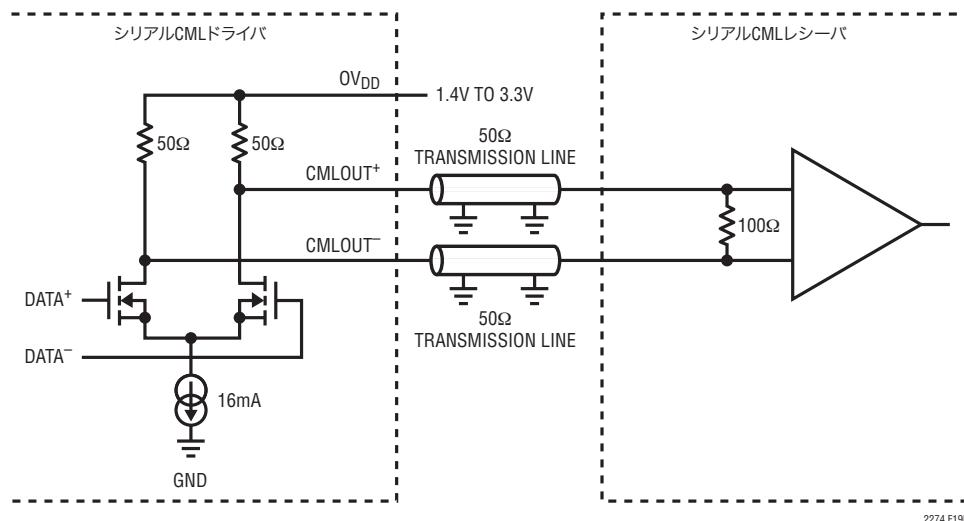

### 高速CML出力

CML出力は正しく動作するために終端する必要があります。OV<sub>DD</sub>電源電圧と終端電圧によりCML出力の同相出力レベルが決まります。CMLドライバが正しく動作するように、出力同相電圧を1Vより大きくします。

レシーバの終端電圧が1.2V～3.3Vの範囲内のときは、図19aの直接結合終端モードを推奨します。CML出力が50Ω終端抵抗に直接接続されると、OV<sub>DD</sub>電源電圧はレシーバの終端電圧として機能し、出力同相電圧はOV<sub>DD</sub>より約200mV低くなります。

必要な範囲内にレシーバの終端電圧が存在しない場合、図19bの直接接続された差動終端を使うことができます。この場合、同相電圧はOV<sub>DD</sub>の下約400mVにシフトし、1.4V～3.3Vの範囲のOV<sub>DD</sub>が必要です。

シリアル・レシーバの同相入力の要件が直接接続終端モードに適合しない場合、DCバランスされた8B/10Bエンコード・データは、図19cに示されているように、DCブロッキング・コンデンサの追加を許容します。このAC結合モードでは、終端電圧はレシーバの要件によって決定されます。カップリング・コンデンサは目的の動作ビット・レートに対して適切に選択します。通常は1nF～10nFです。AC結合モードでは、出力同相電圧はOV<sub>DD</sub>の約400mV下なので、OV<sub>DD</sub>電源電圧は1.4V～3.3Vの範囲にします。

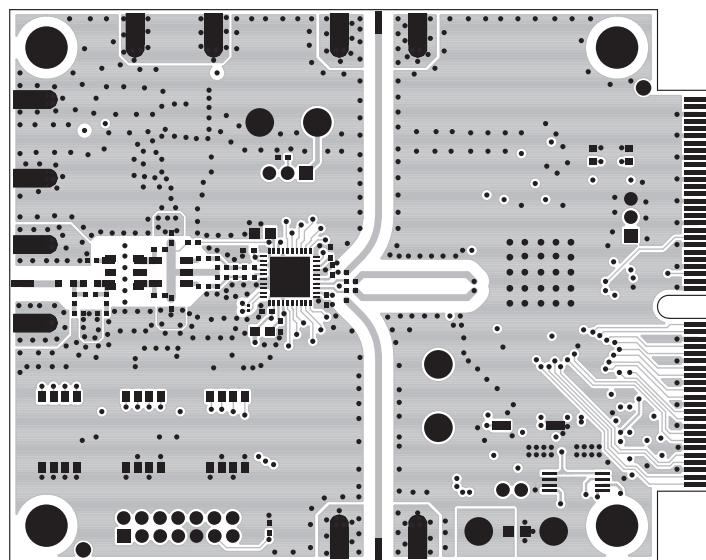

### 接地とバイパス

LTC2274には全く切れ目の無いグランド・プレーンを備えたプリント基板が必要です。内部グランド・プレーンを備えた多層基板を推奨します。LTC2274のピン配置はフロースルー・レイアウトに最適化されているので、入力とデジタル出力間の相互反応が最小に抑えられています。プリント回路基板のレイアウトでは、デジタル信号ラインとアナログ信号ラインをできるだけ分離します。特に、どのデジタル・トラックもアナログ信号トラックに沿って配置しないように、またADCの下に配置しないように注意します。

高品質のセラミック・バイパス・コンデンサを、V<sub>DD</sub>、V<sub>CM</sub>およびOV<sub>DD</sub>の各ピンに使います。バイパス・コンデンサはできるだけピンに近づけて配置してください。ピンやバイパス・コンデンサを接続するトレースは短くし、できるだけ幅を広くします。

LTC2274の差動入力は互いに並行にできるだけ近づけて配置します。入力トレースはできるだけ短くして容量を小さくし、ノイズを拾わないようにします。

### 熱伝達

LTC2274が発生する熱の大部分はダイから底面の露出パッドに伝わります。すぐれた電気特性と熱特性を得るには、露出パッドをPCボードの大きな接地されたパッドに半田付けする必要があります。露出パッドと全てのグランド・ピンを面積が十分大きなグランド・プレーンにできるだけ多くのビアを使って接続することが重要です。

## アプリケーション情報

図19a. CMLの終端、直接接続モード(望ましい)

図19b. CMLの終端、直接接続差動モード

## アプリケーション情報

図19c. CMLの終端、AC接続モード

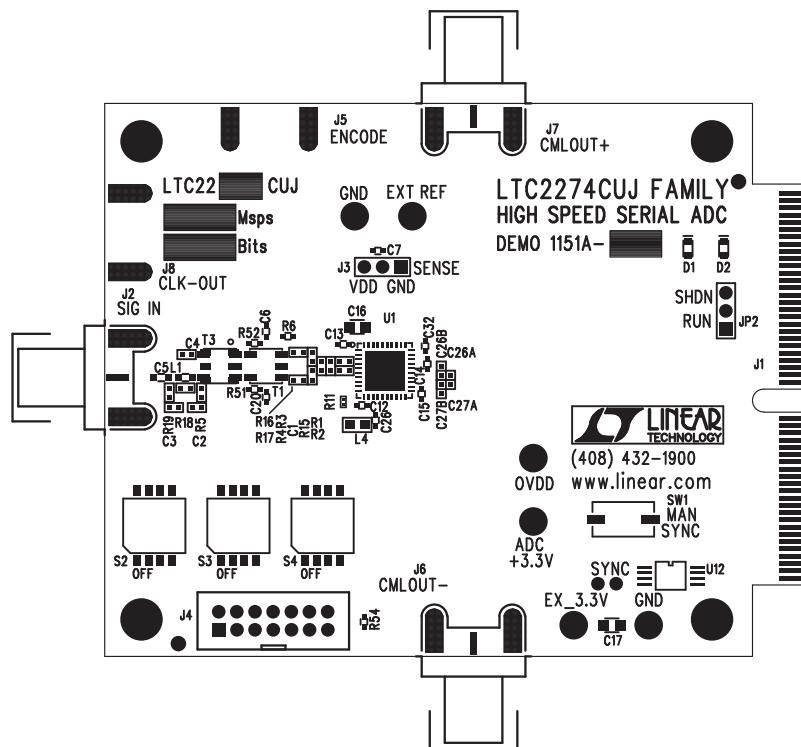

# LTC2274

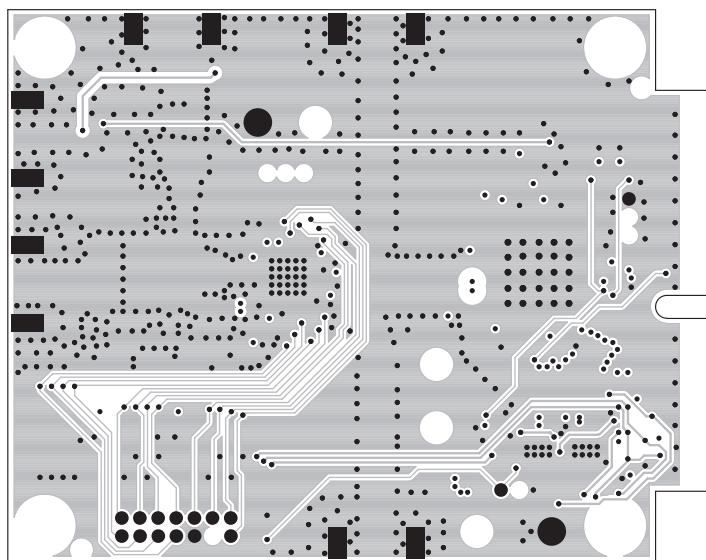

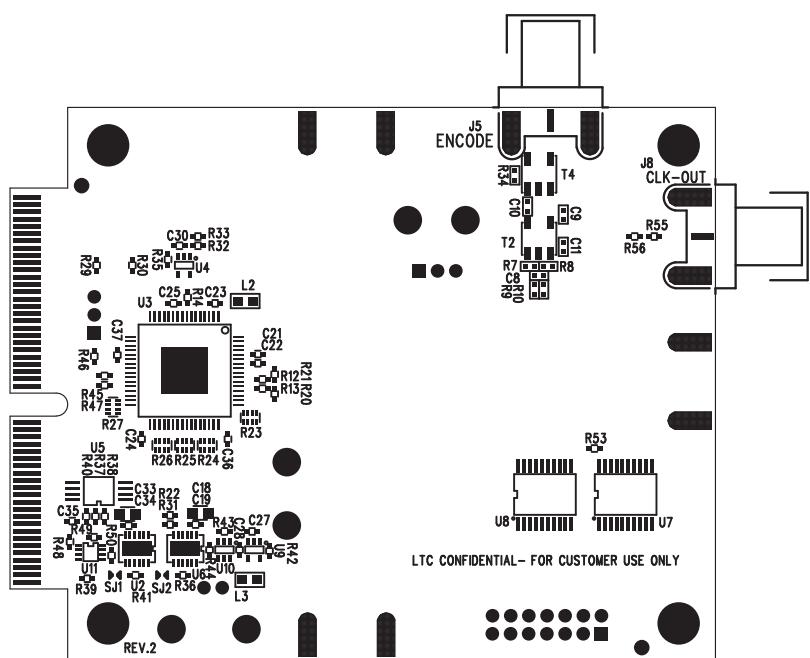

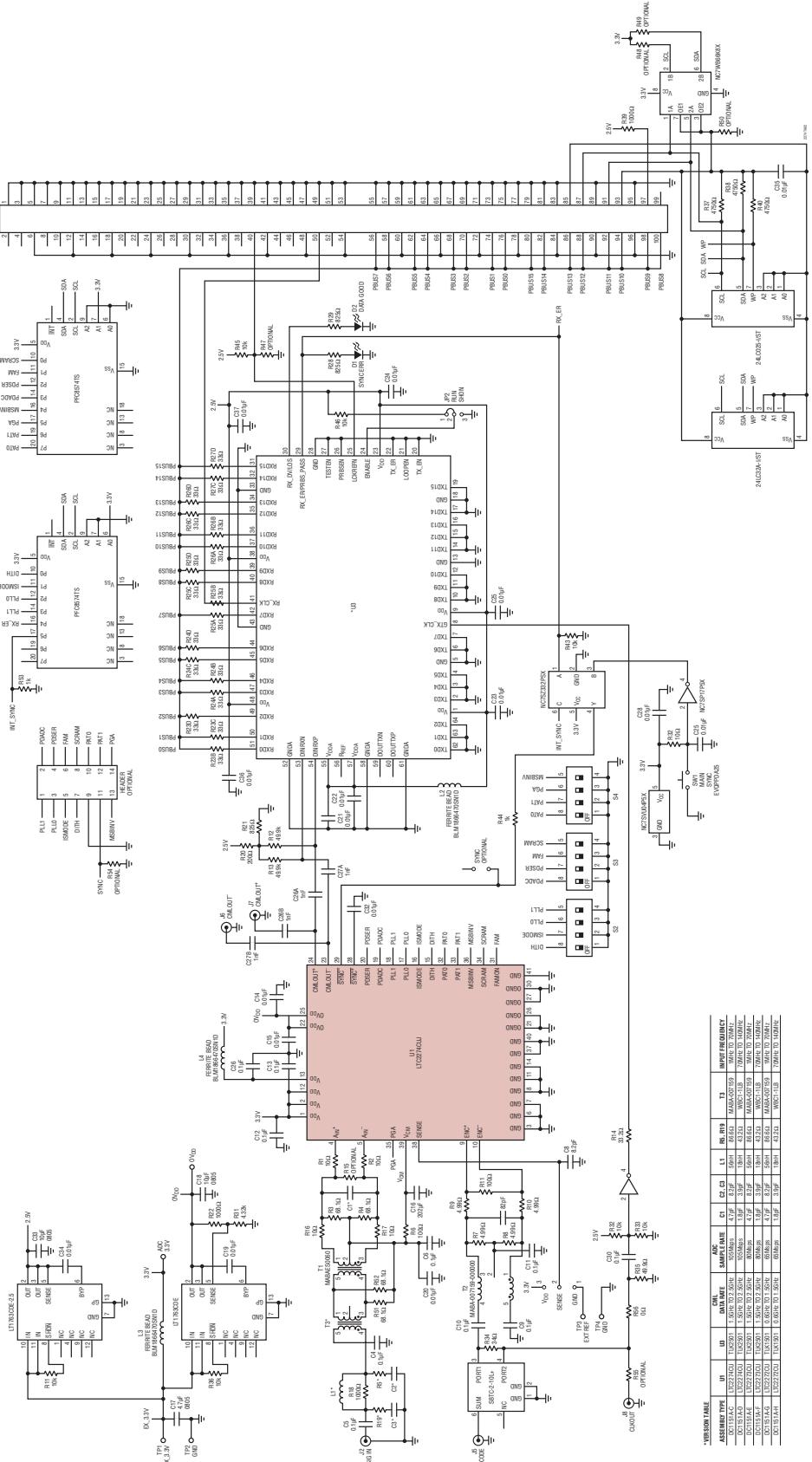

## 標準的応用例

シルクスクリーンのトップ

トップサイド

2274fb

標準的応用例

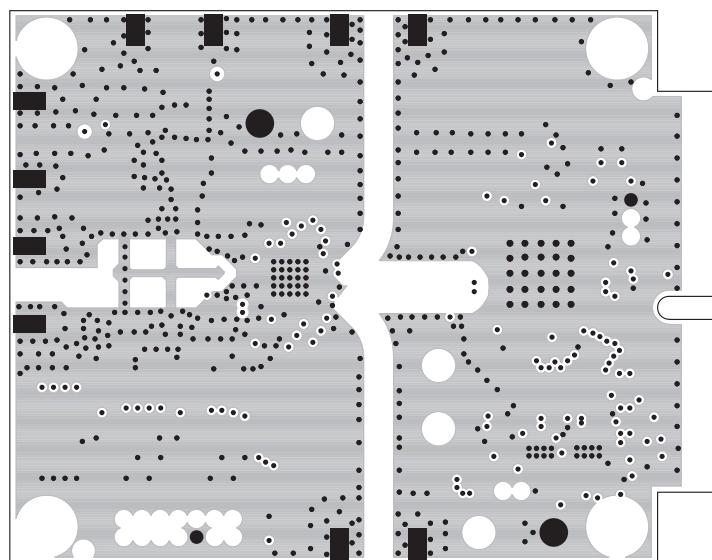

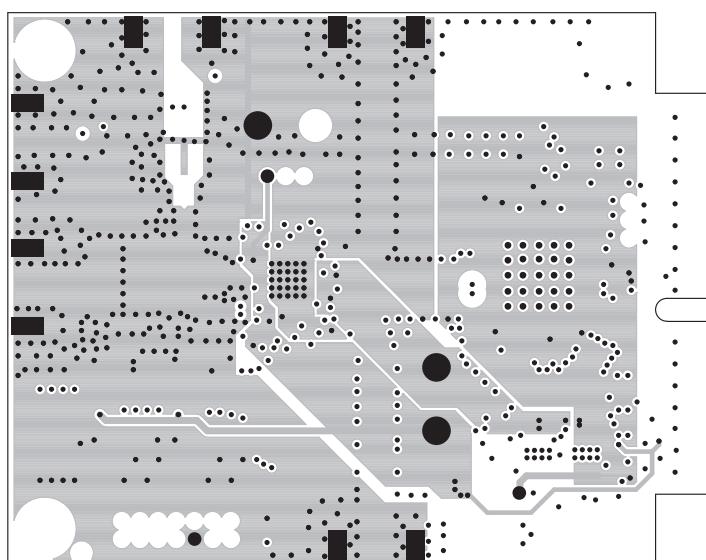

内部レイヤ2

内部レイヤ3

# LTC2274

## 標準的応用例

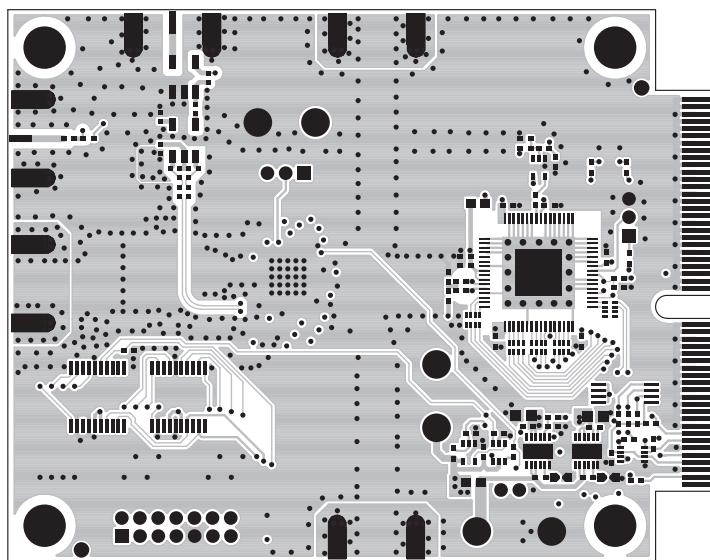

内部レイヤ4

内部レイヤ5

## 標準的應用例

ボトムサイド

## シリクスクリーンのボトム

## 標準的應用例

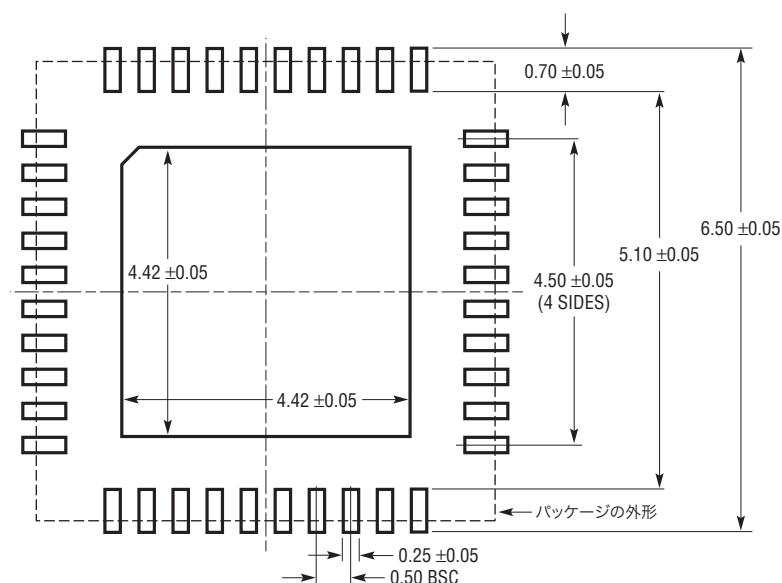

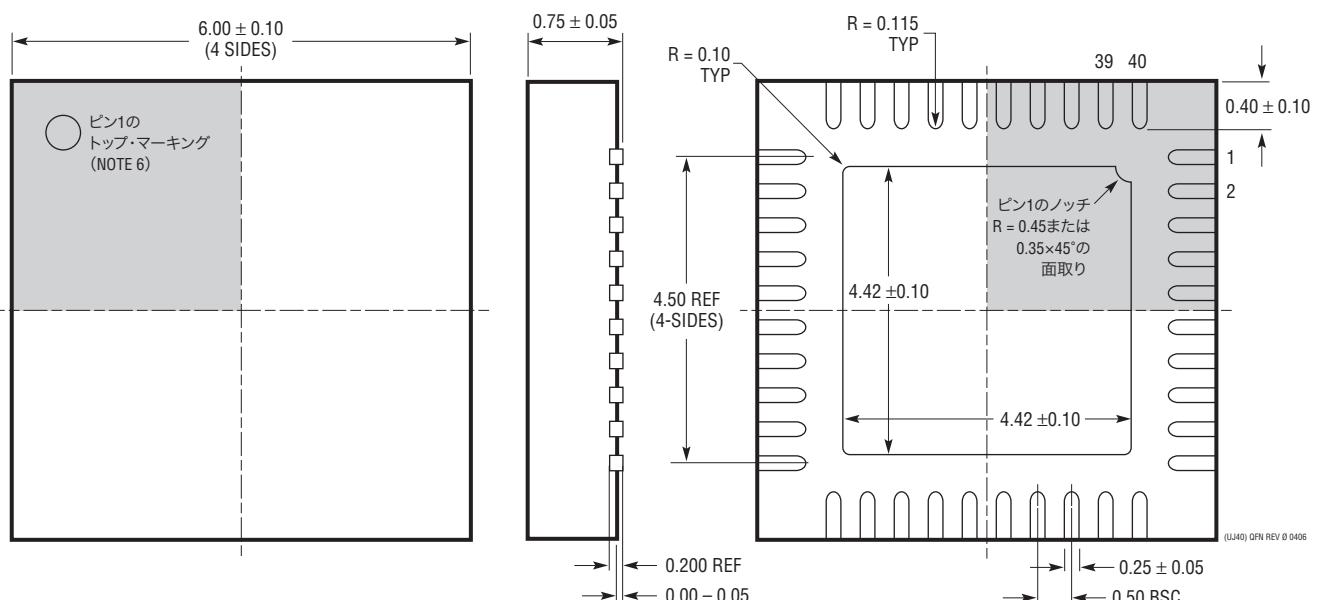

## パッケージ

UJパッケージ

40ピン・プラスチックQFN (6mm×6mm)

(Reference LTC DWG # 05-08-1728 Rev Ø)

推奨する半田パッドのピッチと寸法

半田付けされない領域には半田マスクを使用する

## NOTE:

1. 図面はJEDECのパッケージ外形バリエーション(WJJD-2)

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリは(もしあれば)各サイドで0.20mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージのトップとボトムのピン1の位置の参考に過ぎない

底面図一露出パッド

## 関連製品

| 製品番号       | 説明                                       | 注釈                                                                      |

|------------|------------------------------------------|-------------------------------------------------------------------------|

| LTC1993-2  | 高速差動オペアンプ                                | BW:800MHz、歪み:70dBc(70MHz)、利得:6dB                                        |

| LTC1994    | 低ノイズ、低歪みの完全差動入出力アンプ/ドライバ                 | 低歪み:-94dBc(1MHz)                                                        |

| LTC2215    | 16ビット、65Msps、低ノイズADC                     | 700mW、SNR:81.5dB、SFDR:100dB、64ピンQFN                                     |

| LTC2216    | 16ビット、80Msps、低ノイズADC                     | 970mW、SNR:81.3dB、SFDR:100dB、64ピンQFN                                     |

| LTC2217    | 16ビット、105Msps、低ノイズADC                    | 1190mW、SNR:81.2dB、SFDR:100dB、64ピンQFN                                    |

| LTC2202    | 16ビット、10Msps、3.3V ADC、低ノイズ               | 140mW、SNR:81.6dB、SFDR:100dB、48ピンQFN                                     |

| LTC2203    | 16ビット、25Msps、3.3V ADC、低ノイズ               | 220mW、SNR:81.6dB、SFDR:100dB、48ピンQFN                                     |

| LTC2204    | 16ビット、40Msps、3.3V ADC                    | 480mW、SNR:79dB、SFDR:100dB、48ピンQFN                                       |

| LTC2205    | 16ビット、65Msps、3.3V ADC                    | 590mW、SNR:79dB、SFDR:100dB、48ピンQFN                                       |

| LTC2206    | 16ビット、80Msps、3.3V ADC                    | 725mW、SNR:77.9dB、SFDR:100dB、48ピンQFN                                     |

| LTC2207    | 16ビット、105Msps、3.3V ADC                   | 900mW、SNR:77.9dB、SFDR:100dB、48ピンQFN                                     |

| LTC2208    | 16ビット、130Msps、3.3V ADC、LVDS出力            | 1250mW、SNR:77.7dB、SFDR:100dB、64ピンQFN                                    |

| LTC2209    | 16ビット、160Msps、ADC、LVDS出力                 | 1.45W、SNR:77.1dB、SFDR:100dB、64ピンQFN                                     |

| LTC2220    | 12ビット、170Msps ADC                        | 890mW、SNR:67.5dB、9mm×9mm QFNパッケージ                                       |

| LTC2220-1  | 12ビット、185Msps、3.3V ADC、LVDS出力            | 910mW、SNR:67.7dB、SFDR:80dB、64ピンQFN                                      |

| LTC2224    | 12ビット、135Msps、3.3V ADC、高IFサンプリング         | 630mW、SNR:67.6dB、SFDR:84dB、48ピンQFN                                      |

| LTC2249    | 14ビット、80Msps ADC                         | 230mW、SNR:73dB、5mm×5mm QFNパッケージ                                         |

| LTC2250    | 10ビット、105Msps ADC                        | 320mW、SNR:61.6dB、5mm×5mm QFNパッケージ                                       |

| LTC2251    | 10ビット、125Msps ADC                        | 395mW、SNR:61.6dB、5mm×5mm QFNパッケージ                                       |

| LTC2252    | 12ビット、105Msps ADC                        | 320mW、SNR:70.2dB、5mm×5mm QFNパッケージ                                       |

| LTC2253    | 12ビット、125Msps ADC                        | 395mW、SNR:70.2dB、5mm×5mm QFNパッケージ                                       |

| LTC2254    | 14ビット、105Msps ADC                        | 320mW、SNR:72.5dB、5mm×5mm QFNパッケージ                                       |

| LTC2255    | 14ビット、125Msps、3V ADC、低消費電力               | 395mW、SNR:72.5dB、SFDR:88dB、32ピンQFN                                      |

| LTC2284    | 14ビット、デュアル、105Msps、3V ADC、低クロストーク        | 540mW、SNR:72.4dB、SFDR:88dB、64ピンQFN                                      |

| LTC2299    | デュアルの14ビット、80Msps ADC                    | 230mW、SNR:71.6dB、5mm×5mm QFNパッケージ                                       |

| LTC5512    | DC～3GHz高信号レベル・<br>ダウンコンバーティング・ミキサ        | DC～3GHz、IIP3:21dBm、内蔵LOバッファ                                             |

| LTC5515    | 1.5 GHz～2.5GHz直接変換直交復調器                  | 高いIIP3:1.9GHzで20dBm、内蔵LO直交ジェネレータ                                        |

| LTC5516    | 800MHz～1.5GHz直接変換直交復調器                   | 高いIIP3:900MHzで21.5dBm、内蔵LO直交ジェネレータ                                      |

| LTC5517    | 40MHz～900MHz直接変換直交復調器                    | 高いIIP3:800MHzで21dBm、内蔵LO直交ジェネレータ                                        |

| LTC5522    | 600MHz～2.7GHz高直線性<br>ダウンコンバーティング・ミキサ     | 4.5V～5.25Vの電源、IIP3:900MHzで25dBm、<br>NF = 12.5dB、50ΩシングルエンドのRFポートとLOポート  |

| LTC5527    | 400MHz～3.7GHz高信号<br>レベル・ダウンコンバーティング・ミキサ  | 4.5V～5.25V電源、IIP3:1900MHzで23.5dBm、<br>I <sub>CC</sub> = 78mA、変換利得 = 2dB |

| LTC5579    | 1.5GHz～3.8GHz 高直線性<br>アップコンバーティング・ミキサ    | 3.3V電源、OIP3:2.14GHzで27.3dBm、<br>変換利得 = 2.14GHzで2.6dB                    |

| LTC6400-20 | 300MHz IF向け、1.8GHz、低ノイズ、<br>低歪み差動ADCドライバ | 固定利得:10V/V、合計入力ノイズ:2.1nV $\sqrt{\text{Hz}}$ 、<br>3mm×3mm QFN-16パッケージ    |