## 特長

- サンプル・レート:125Msps/105Msps

- 単一3V電源(2.85V～3.4V)

- 低消費電力:395mW/320mW

- SNR:70.2dB

- SFDR:88dB

- 欠落コードなし

- 柔軟な入力:1V<sub>P-P</sub>～2V<sub>P-P</sub>の範囲

- フルパワー帯域幅が640MHzのサンプル/ホールド

- クロック・デューティ・サイクル・スタビライザ

- シャットダウン・モードとナップ・モード

- ピン互換ファミリ

- 125Msps:LTC2253(12ビット)、LTC2255(14ビット)

- 105Msps:LTC2252(12ビット)、LTC2254(14ビット)

- 80Msps:LTC2229(12ビット)、LTC2249(14ビット)

- 65Msps:LTC2228(12ビット)、LTC2248(14ビット)

- 40Msps:LTC2227(12ビット)、LTC2247(14ビット)

- 25Msps:LTC2226(12ビット)、LTC2246(14ビット)

- 10Msps:LTC2225(12ビット)、LTC2245(14ビット)

- 32ピン(5mm×5mm)QFNパッケージ

## アプリケーション

- 無線および有線の広帯域通信

- 画像処理システム

- 超音波

- スペクトル分析

- ポータブル機器

## 標準的応用例

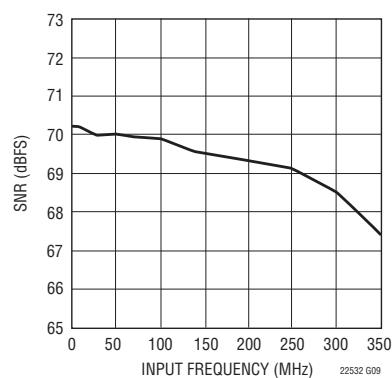

**LTC2253:SNRと入力周波数、-1dB、2Vレンジ、125Msps**

# LTC2253/LTC2252

## 絶対最大定格

$0V_{DD} = V_{DD}$  (Note 1, 2)

電源電圧 ( $V_{DD}$ ) ..... 4V

デジタル出力のグランド電圧 (0GND) ..... -0.3V ~ 1V

アナログ入力電圧 (Note 3) ..... -0.3V ~ ( $V_{DD} + 0.3V$ )

デジタル入力電圧 ..... -0.3V ~ ( $V_{DD} + 0.3V$ )

デジタル出力電圧 ..... -0.3V ~ ( $0V_{DD} + 0.3V$ )

電力損失 ..... 1500mW

動作温度範囲

LTC2253C, LTC2252C ..... 0°C ~ 70°C

LTC2253I, LTC2252I ..... -40°C ~ 85°C

保存温度範囲 ..... -65°C ~ 125°C

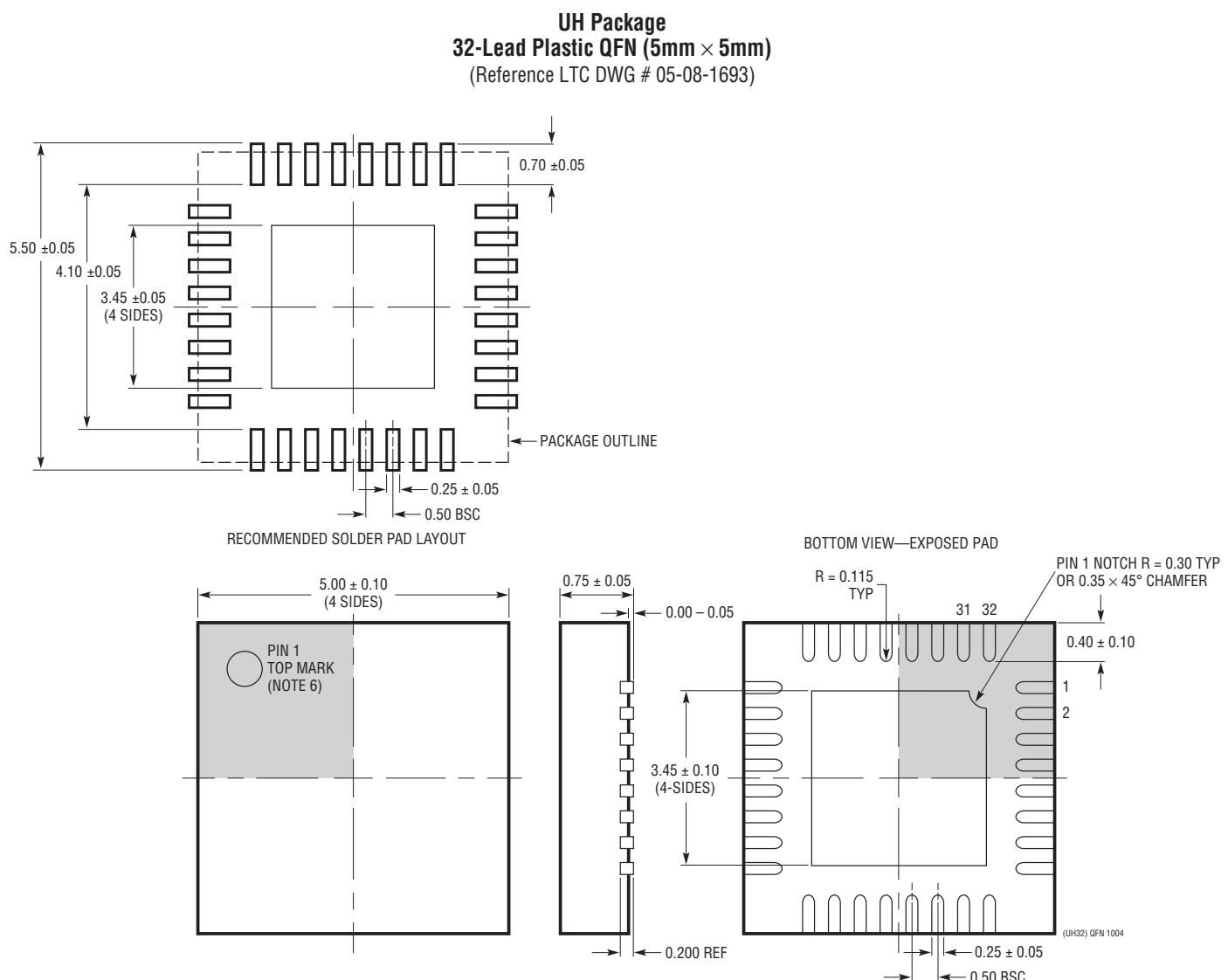

## パッケージ/発注情報

| ORDER PART NUMBER |

|-------------------|

| LTC2253CUH        |

| LTC2253IUH        |

| LTC2252CUH        |

| LTC2252IUH        |

| QFN PART* MARKING |

| 2253              |

| 2252              |

TOP VIEW

TOP VIEW

UH PACKAGE

32-LEAD (5mm x 5mm) PLASTIC QFN

$T_{JMAX} = 125^{\circ}\text{C}$ ,  $\theta_{JA} = 34^{\circ}\text{C/W}$

EXPOSED PAD (PIN 33) IS GND

MUST BE SOLDERED TO PCB

発注オプション テープ・アンド・リール:#TRを付加

無鉛仕上げ:#PBFを付加 無鉛仕上げのテープ・アンド・リール:#TRPBFを付加

無鉛仕上げの製品マーキング: <http://www.linear-tech.co.jp/leadfree/>

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

\* 温度グレードは出荷時のコンテナのラベルで識別されます。

## コンバータ特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^{\circ}\text{C}$  での値 (Note 4)。

| PARAMETER                     | CONDITIONS                               | LTC2253 |      |                     | LTC2252 |      |                     | UNITS                                              |     |

|-------------------------------|------------------------------------------|---------|------|---------------------|---------|------|---------------------|----------------------------------------------------|-----|

|                               |                                          | MIN     | TYP  | MAX                 | MIN     | TYP  | MAX                 |                                                    |     |

| Resolution (No Missing Codes) |                                          | ●       | 12   |                     | 12      |      |                     | Bits                                               |     |

| Integral Linearity Error      | Differential Analog Input (Note 5)       | ●       | -1.5 | $\pm 0.3$           | 1.5     | -1.5 | $\pm 0.3$           | 1.5                                                | LSB |

| Differential Linearity Error  | Differential Analog Input                | ●       | -0.7 | $\pm 0.15$          | 0.7     | -0.7 | $\pm 0.15$          | 0.7                                                | LSB |

| Offset Error                  | (Note 6)                                 | ●       | -12  | $\pm 2$             | 12      | -12  | $\pm 2$             | 12                                                 | mV  |

| Gain Error                    | External Reference                       | ●       | -2.5 | $\pm 0.5$           | 2.5     | -2.5 | $\pm 0.5$           | 2.5                                                | %FS |

| Offset Drift                  |                                          |         |      | $\pm 10$            |         |      | $\pm 10$            | $\mu\text{V}/^{\circ}\text{C}$                     |     |

| Full-Scale Drift              | Internal Reference<br>External Reference |         |      | $\pm 30$<br>$\pm 5$ |         |      | $\pm 30$<br>$\pm 5$ | ppm/ $^{\circ}\text{C}$<br>ppm/ $^{\circ}\text{C}$ |     |

| Transition Noise              | SENSE = 1V                               |         |      | 0.32                |         |      | 0.32                | LSBRMS                                             |     |

## アナログ入力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 4)。

| SYMBOL       | PARAMETER                                     | CONDITIONS                                     | MIN | TYP          | MAX | UNITS          |               |

|--------------|-----------------------------------------------|------------------------------------------------|-----|--------------|-----|----------------|---------------|

| $V_{IN}$     | Analog Input Range ( $A_{IN}^+ - A_{IN}^-$ )  | $2.85\text{V} < V_{DD} < 3.4\text{V}$ (Note 7) | ●   | ±0.5V to ±1V |     | V              |               |

| $V_{IN,CM}$  | Analog Input Common Mode                      | Differential Input (Note 7)                    | ●   | 1            | 1.5 | 1.9            | V             |

| $I_{IN}$     | Analog Input Leakage Current                  | $0\text{V} < A_{IN}^+, A_{IN}^- < V_{DD}$      | ●   | -1           |     | 1              | $\mu\text{A}$ |

| $I_{SENSE}$  | SENSE Input Leakage                           | $0\text{V} < \text{SENSE} < 1\text{V}$         | ●   | -3           |     | 3              | $\mu\text{A}$ |

| $I_{MODE}$   | MODE Pin Leakage                              |                                                | ●   | -3           |     | 3              | $\mu\text{A}$ |

| $t_{AP}$     | Sample-and-Hold Acquisition Delay Time        |                                                |     | 0            |     | ns             |               |

| $t_{JITTER}$ | Sample-and-Hold Acquisition Delay Time Jitter |                                                |     | 0.2          |     | $\text{psRMS}$ |               |

| CMRR         | Analog Input Common Mode Rejection Ratio      |                                                |     | 80           |     | dB             |               |

|              | Full Power Bandwidth                          | Figure 8 Test Circuit                          |     | 640          |     | MHz            |               |

## ダイナミック精度

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ 。(Note 4)

| SYMBOL  | PARAMETER                                             | CONDITIONS                                                 | LTC2253 |     |      | LTC2252 |      |      | UNITS |

|---------|-------------------------------------------------------|------------------------------------------------------------|---------|-----|------|---------|------|------|-------|

|         |                                                       |                                                            | MIN     | TYP | MAX  | MIN     | TYP  | MAX  |       |

| SNR     | Signal-to-Noise Ratio                                 | 5MHz Input                                                 |         |     | 70.2 |         |      | 70.2 | dB    |

|         |                                                       | 30MHz Input                                                |         |     | 70.1 |         |      | 70.2 |       |

|         |                                                       | 70MHz Input                                                | ●       | 68  | 70   | 68.5    | 70.1 |      |       |

|         |                                                       | 140MHz Input                                               |         |     | 69.6 |         |      | 69.8 |       |

| SFDR    | Spurious Free Dynamic Range<br>2nd or 3rd Harmonic    | 5MHz Input                                                 |         |     | 88   |         |      | 88   | dB    |

|         |                                                       | 30MHz Input                                                |         |     | 85   |         |      | 88   |       |

|         |                                                       | 70MHz Input                                                | ●       | 72  | 82   | 71      | 84   |      |       |

|         |                                                       | 140MHz Input                                               |         |     | 78   |         |      | 79   |       |

| SFDR    | Spurious Free Dynamic Range<br>4th Harmonic or Higher | 5MHz Input                                                 |         |     | 90   |         |      | 90   | dB    |

|         |                                                       | 30MHz Input                                                |         |     | 90   |         |      | 90   |       |

|         |                                                       | 70MHz Input                                                | ●       | 77  | 90   | 78      | 90   |      |       |

|         |                                                       | 140MHz Input                                               |         |     | 90   |         |      | 90   |       |

| S/(N+D) | Signal-to-Noise Plus<br>Distortion Ratio              | 5MHz Input                                                 |         |     | 69.8 |         |      | 70.1 | dB    |

|         |                                                       | 30MHz Input                                                |         |     | 69.7 |         |      | 70.1 |       |

|         |                                                       | 70MHz Input                                                | ●       | 67  | 69.6 | 67.5    | 70   |      |       |

|         |                                                       | 140MHz Input                                               |         |     | 68.5 |         |      | 68.7 |       |

| IMD     | Intermodulation Distortion                            | $f_{IN1} = 28.2\text{MHz}$ ,<br>$f_{IN2} = 26.8\text{MHz}$ |         |     | 85   |         |      | 85   | dB    |

# LTC2253/LTC2252

## 内部リファレンスの特性 (Note 4)

| PARAMETER                  | CONDITIONS              | MIN   | TYP      | MAX   | UNITS  |

|----------------------------|-------------------------|-------|----------|-------|--------|

| $V_{CM}$ Output Voltage    | $I_{OUT} = 0$           | 1.475 | 1.500    | 1.525 | V      |

| $V_{CM}$ Output Tempco     |                         |       | $\pm 25$ |       | ppm/°C |

| $V_{CM}$ Line Regulation   | $2.85V < V_{DD} < 3.4V$ |       | 3        |       | mV/V   |

| $V_{CM}$ Output Resistance | $-1mA < I_{OUT} < 1mA$  |       | 4        |       | Ω      |

## デジタル入力とデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 4)。

| SYMBOL                             | PARAMETER                | CONDITIONS                | MIN | TYP | MAX | UNITS |

|------------------------------------|--------------------------|---------------------------|-----|-----|-----|-------|

| ロジック入力(CLK, $\overline{OE}$ 、SHDN) |                          |                           |     |     |     |       |

| $V_{IH}$                           | High Level Input Voltage | $V_{DD} = 3V$             | ●   | 2   |     | V     |

| $V_{IL}$                           | Low Level Input Voltage  | $V_{DD} = 3V$             | ●   |     | 0.8 | V     |

| $I_{IN}$                           | Input Current            | $V_{IN} = 0V$ to $V_{DD}$ | ●   | -10 | 10  | μA    |

| $C_{IN}$                           | Input Capacitance        | (Note 7)                  |     |     | 3   | pF    |

## ロジック出力

### $0V_{DD} = 3V$

|              |                           |                                                   |   |               |             |    |

|--------------|---------------------------|---------------------------------------------------|---|---------------|-------------|----|

| $C_{OZ}$     | Hi-Z Output Capacitance   | $\overline{OE} = \text{High}$ (Note 7)            |   | 3             |             | pF |

| $I_{SOURCE}$ | Output Source Current     | $V_{OUT} = 0V$                                    |   | 50            |             | mA |

| $I_{SINK}$   | Output Sink Current       | $V_{OUT} = 3V$                                    |   | 50            |             | mA |

| $V_{OH}$     | High Level Output Voltage | $I_O = -10\mu\text{A}$<br>$I_O = -200\mu\text{A}$ | ● | 2.995<br>2.7  | 2.99<br>2.9 | V  |

| $V_{OL}$     | Low Level Output Voltage  | $I_O = 10\mu\text{A}$<br>$I_O = 1.6\text{mA}$     | ● | 0.005<br>0.09 | 0.09<br>0.4 | V  |

### $0V_{DD} = 2.5V$

|          |                           |                         |  |      |  |   |

|----------|---------------------------|-------------------------|--|------|--|---|

| $V_{OH}$ | High Level Output Voltage | $I_O = -200\mu\text{A}$ |  | 2.49 |  | V |

| $V_{OL}$ | Low Level Output Voltage  | $I_O = 1.6\text{mA}$    |  | 0.09 |  | V |

### $0V_{DD} = 1.8V$

|          |                           |                         |  |      |  |   |

|----------|---------------------------|-------------------------|--|------|--|---|

| $V_{OH}$ | High Level Output Voltage | $I_O = -200\mu\text{A}$ |  | 1.79 |  | V |

| $V_{OL}$ | Low Level Output Voltage  | $I_O = 1.6\text{mA}$    |  | 0.09 |  | V |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 8)。

| SYMBOL     | PARAMETER             | CONDITIONS                              | LTC2253 |      |     | LTC2252 |      |     | UNITS |    |

|------------|-----------------------|-----------------------------------------|---------|------|-----|---------|------|-----|-------|----|

|            |                       |                                         | MIN     | TYP  | MAX | MIN     | TYP  | MAX |       |    |

| $V_{DD}$   | Analog Supply Voltage | (Note 9)                                | ●       | 2.85 | 3   | 3.4     | 2.85 | 3   | 3.4   | V  |

| $OV_{DD}$  | Output Supply Voltage | (Note 9)                                | ●       | 0.5  | 3   | 3.6     | 0.5  | 3   | 3.6   | V  |

| $I_{VDD}$  | Supply Current        |                                         | ●       |      | 132 | 156     |      | 107 | 126   | mA |

| $P_{DISS}$ | Power Dissipation     |                                         | ●       |      | 395 | 468     |      | 320 | 378   | mW |

| $P_{SHDN}$ | Shutdown Power        | $SHDN = H$ ,<br>$\bar{OE} = H$ , No CLK |         |      | 2   |         |      | 2   |       | mW |

| $P_{NAP}$  | Nap Mode Power        | $SHDN = H$ ,<br>$\bar{OE} = L$ , No CLK |         |      | 15  |         |      | 15  |       | mW |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 4)。

| SYMBOL           | PARAMETER                                    | CONDITIONS                                                        | LTC2253 |          |        | LTC2252    |          |              | UNITS      |          |

|------------------|----------------------------------------------|-------------------------------------------------------------------|---------|----------|--------|------------|----------|--------------|------------|----------|

|                  |                                              |                                                                   | MIN     | TYP      | MAX    | MIN        | TYP      | MAX          |            |          |

| $f_s$            | Sampling Frequency                           | (Note 9)                                                          | ●       | 1        | 125    | 1          | 105      |              | MHz        |          |

| $t_L$            | CLK Low Time                                 | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On<br>(Note 7) | ●<br>●  | 3.8<br>3 | 4<br>4 | 500<br>500 | 4.5<br>3 | 4.76<br>4.76 | 500<br>500 | ns<br>ns |

| $t_H$            | CLK High Time                                | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On<br>(Note 7) | ●<br>●  | 3.8<br>3 | 4<br>4 | 500<br>500 | 4.5<br>3 | 4.76<br>4.76 | 500<br>500 | ns<br>ns |

| $t_{AP}$         | Sample-and-Hold Aperture Delay               |                                                                   |         |          | 0      |            |          | 0            | ns         |          |

| $t_D$            | CLK to DATA Delay                            | $C_L = 5\text{pF}$ (Note 7)                                       | ●       | 1.4      | 2.7    | 5.4        | 1.4      | 2.7          | 5.4        | ns       |

|                  | Data Access Time After $\bar{OE} \downarrow$ | $C_L = 5\text{pF}$ (Note 7)                                       | ●       |          | 4.3    | 10         |          | 4.3          | 10         | ns       |

|                  | BUS Relinquish Time                          | (Note 7)                                                          | ●       |          | 3.3    | 8.5        |          | 3.3          | 8.5        | ns       |

| Pipeline Latency |                                              |                                                                   |         |          | 5      |            |          | 5            | Cycles     |          |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

**Note 2:** 全ての電圧値は(注記がない限り)GNDとOGNDを結線したグランドを基準にしている。

**Note 3:** これらのピンの電圧をGNDより低くするか、 $V_{DD}$ より高くすると、その電圧は内部のダイオードによってクランプされる。この製品は、GNDより低いか、または $V_{DD}$ より高い電圧で、ラッピングを生じることなしに100mAを超える入力電流を処理することができる。

**Note 4:** 注記がない限り、 $V_{DD} = 3\text{V}$ 、 $f_{SAMPLE} = 125\text{MHz}$  (LTC2253) または  $105\text{MHz}$  (LTC2252)、入力範囲 = 差動ドライブで $2\text{V}_{\text{P-P}}$ 、クロック・デューティ・サイクル・スタビライザはオン。

**Note 5:** 積分非直線性は、実際の伝達曲線の端点を通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 6:** オフセット誤差は、出力コードが0000 0000 0000と1111 1111 1111の間を往復しているときに、 $-0.5\text{LSB}$ から測定されたオフセット電圧である。

**Note 7:** 設計によって保証されており、テストされない。

**Note 8:**  $V_{DD} = 3\text{V}$ 、 $f_{SAMPLE} = 125\text{MHz}$  (LTC2253) または  $105\text{MHz}$  (LTC2252)、入力範囲 = 差動ドライブで $1\text{V}_{\text{P-P}}$ 。

**Note 9:** 推奨動作条件。

# LTC2253/LTC2252

## 標準的性能特性

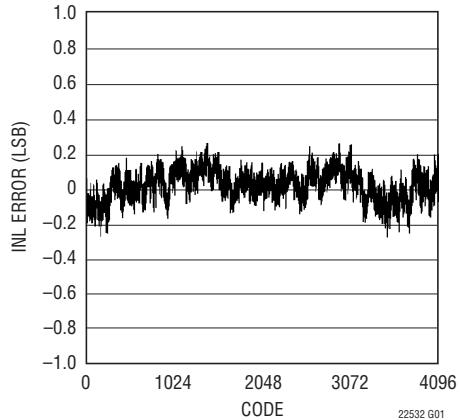

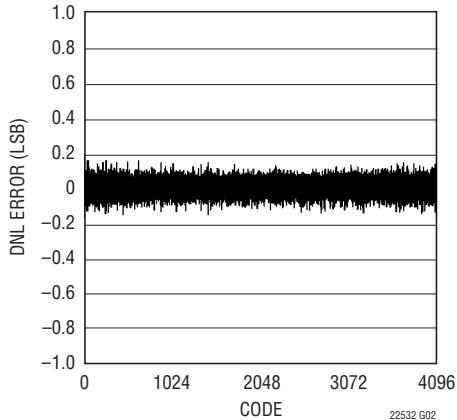

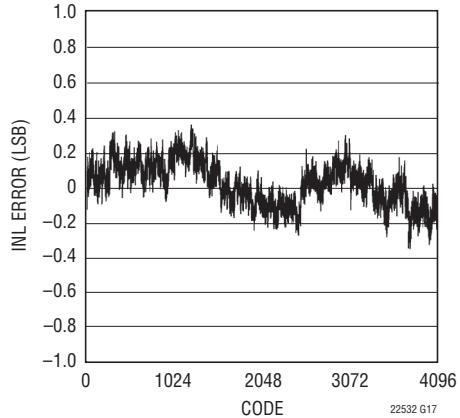

LTC2253: 標準的な INL、2V レンジ、125Msps

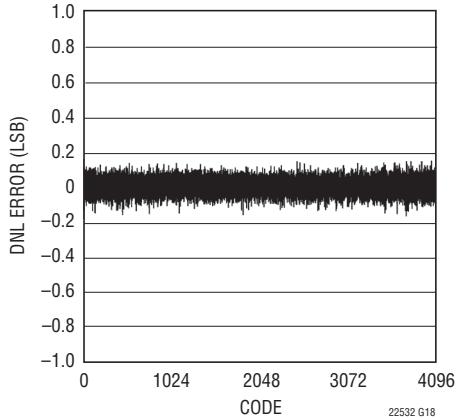

LTC2253: 標準的な DNL、2V レンジ、125Msps

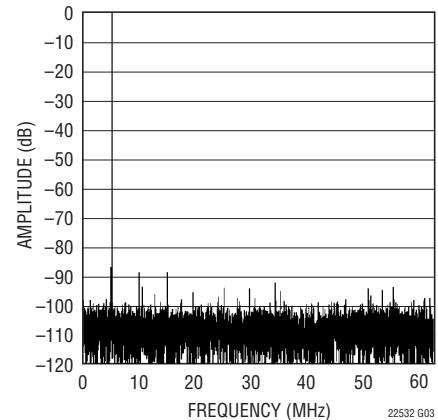

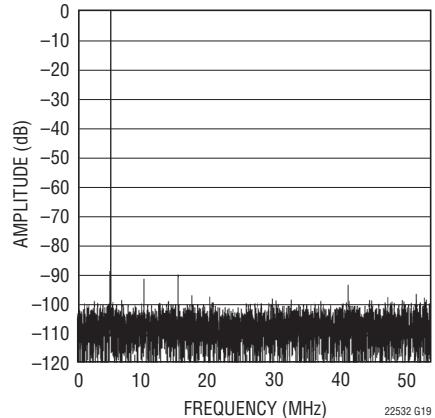

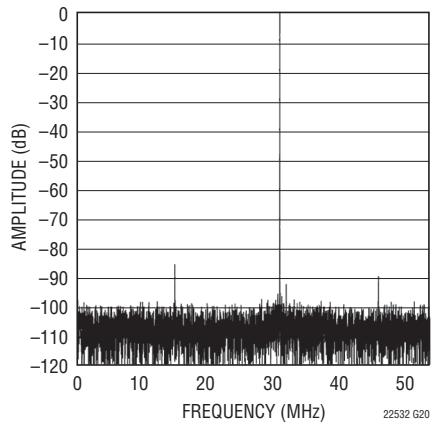

LTC2253: 8192 ポイントの FFT、

$f_{IN} = 5\text{MHz}$ 、-1dB、2V レンジ、125Msps

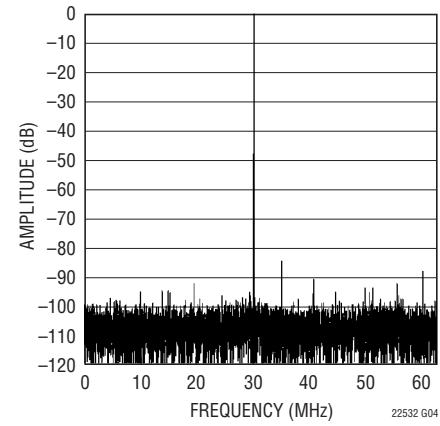

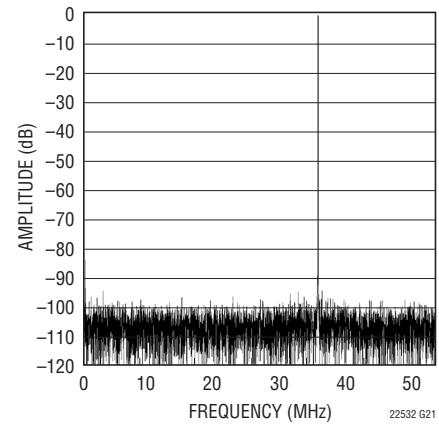

LTC2253: 8192 ポイントの FFT、

$f_{IN} = 30\text{MHz}$ 、-1dB、2V レンジ、125Msps

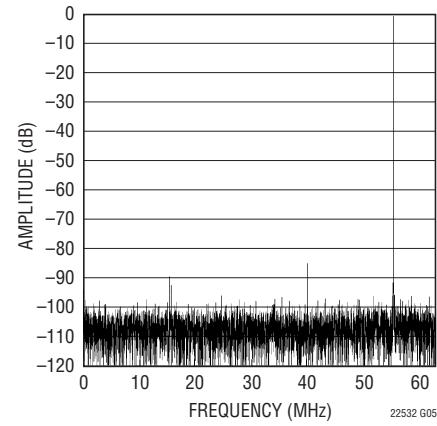

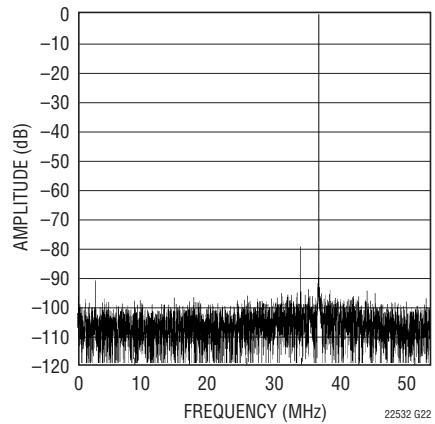

LTC2253: 8192 ポイントの FFT、

$f_{IN} = 70\text{MHz}$ 、-1dB、2V レンジ、125Msps

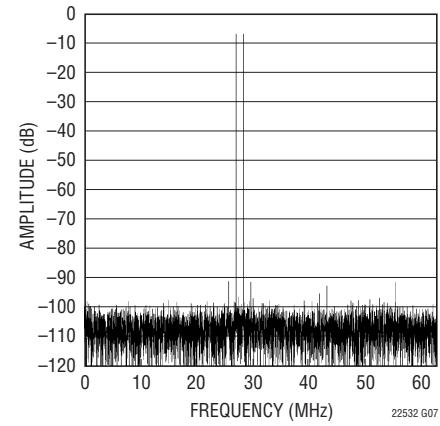

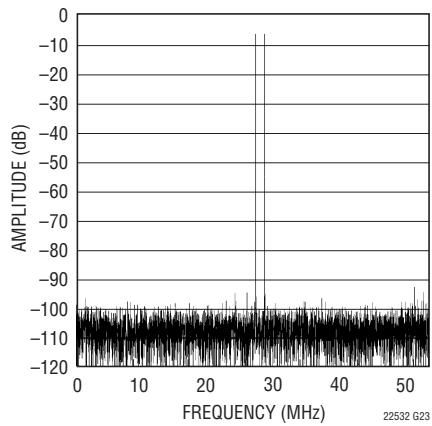

LTC2253: 8192 ポイントの FFT、

$f_{IN} = 140\text{MHz}$ 、-1dB、2V レンジ、125Msps

LTC2253: 8192 ポイントの 2 トーン FFT、 $f_{IN} = 28.2\text{MHz}$  および  $26.8\text{MHz}$ 、-1dB、2V レンジ、125Msps

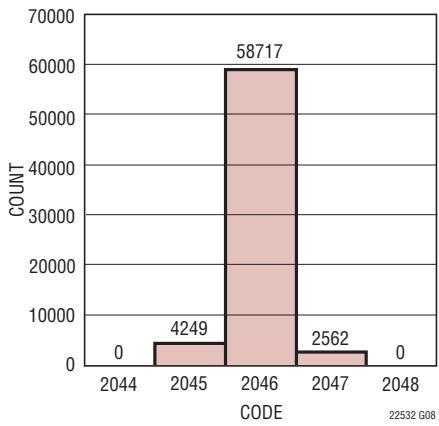

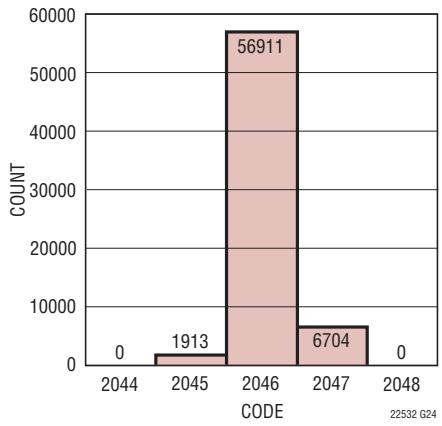

LTC2253: 接地入力時の

ヒストグラム、125Msps

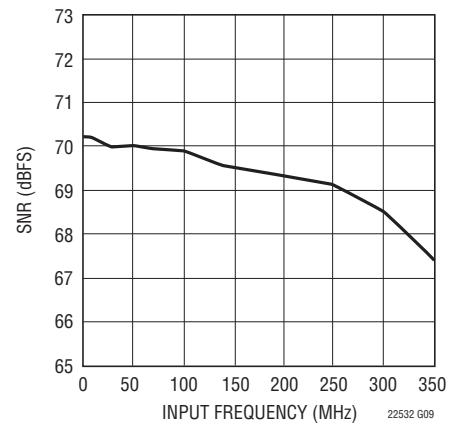

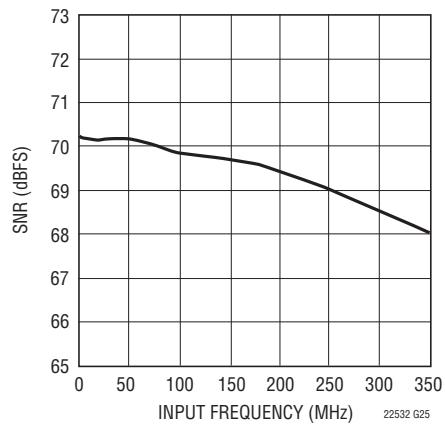

LTC2253: SNR と 入力周波数、-1dB、2V レンジ、125Msps

## 標準的性能特性

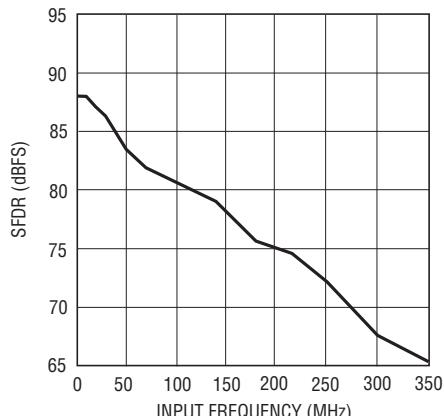

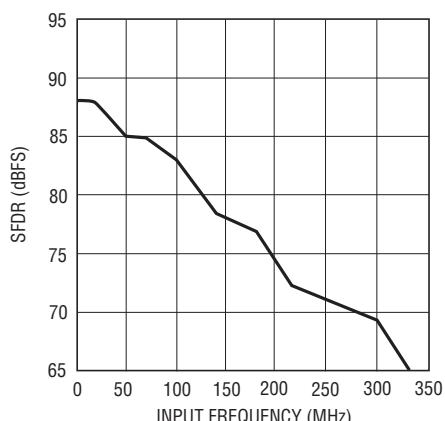

LTC2253: SFDRと入力周波数、-1dB、2Vレンジ、125Msps

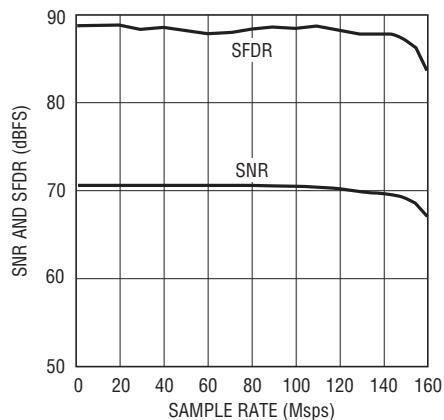

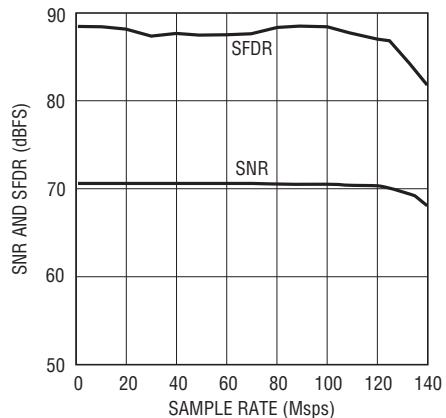

LTC2253: SNRおよびSFDRとサンプル・レート、2Vレンジ、 $f_{IN} = 5\text{MHz}$ 、-1dB

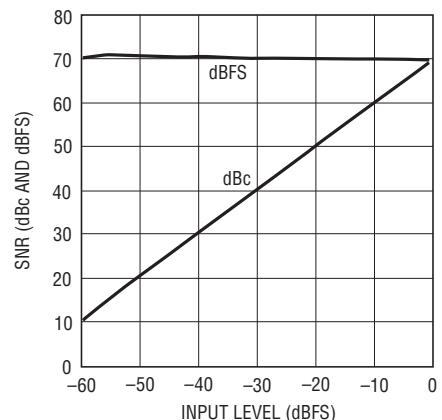

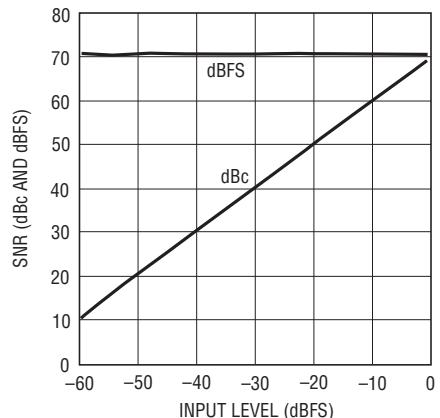

LTC2253: SNRと入力レベル、 $f_{IN} = 70\text{MHz}$ 、2Vレンジ、125Msps

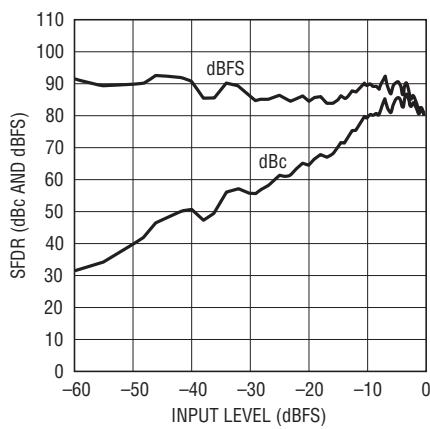

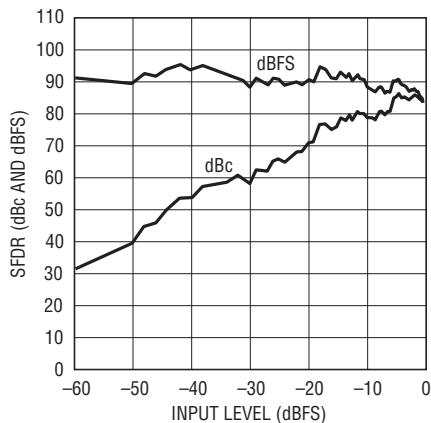

LTC2253: SFDRと入力レベル、 $f_{IN} = 70\text{MHz}$ 、2Vレンジ、125Msps

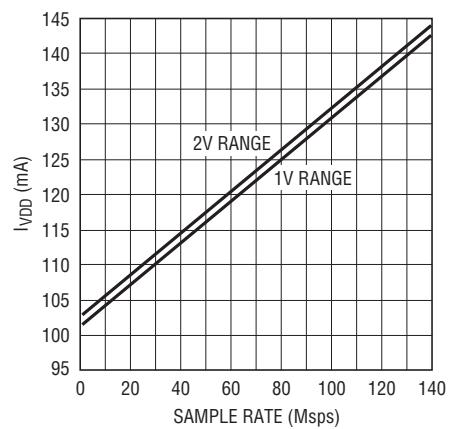

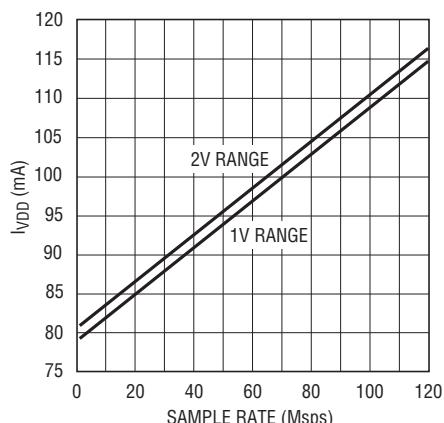

LTC2253:  $I_{VDD}$ とサンプル・レート、5MHzの正弦波入力、-1dB

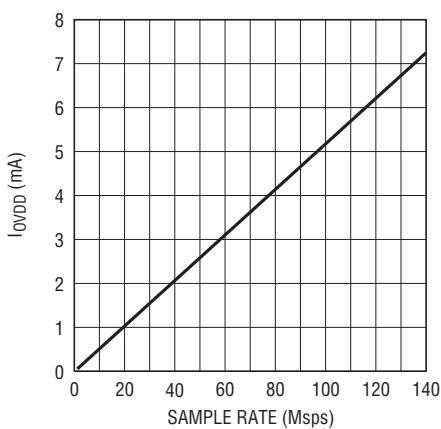

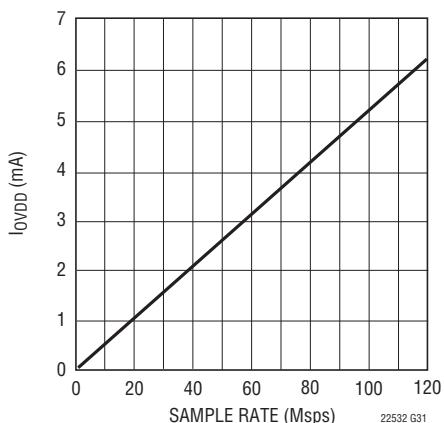

LTC2253:  $I_{OVDD}$ とサンプル・レート、5MHzの正弦波入力、-1dB、 $0V_{DD} = 1.8\text{V}$

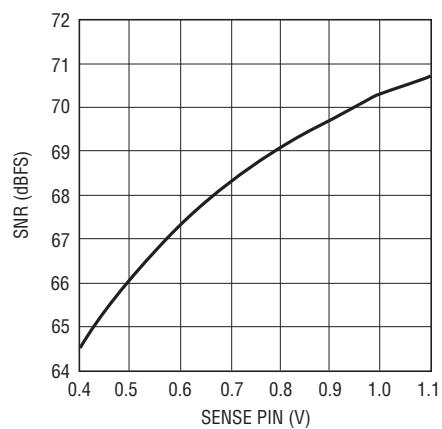

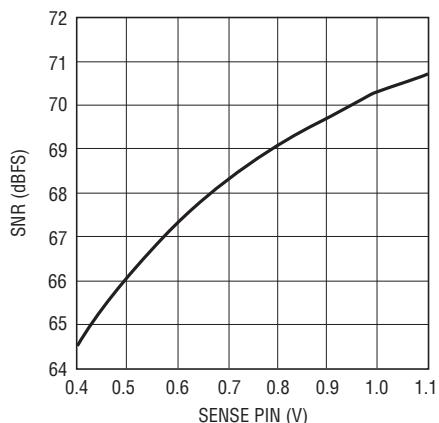

LTC2253: SNRとSENSEの電圧、 $f_{IN} = 5\text{MHz}$ 、-1dB

# LTC2253/LTC2252

## 標準的性能特性

LTC2252: 標準的な INL、2V レンジ、105Msps

LTC2252: 標準的な DNL、2V レンジ、105Msps

LTC2252: 8192 ポイントの FFT、

$f_{IN} = 5\text{MHz}$ 、-1dB、2V レンジ、105Msps

LTC2252: 8192 ポイントの FFT、

$f_{IN} = 30\text{MHz}$ 、-1dB、2V レンジ、105Msps

LTC2252: 8192 ポイントの FFT、

$f_{IN} = 70\text{MHz}$ 、-1dB、2V レンジ、105Msps

LTC2252: 8192 ポイントの FFT、

$f_{IN} = 140\text{MHz}$ 、-1dB、2V レンジ、105Msps

LTC2252: 8192 ポイントの 2 トーン FFT、 $f_{IN} = 28.2\text{MHz}$  および  $26.8\text{MHz}$ 、-1dB、2V レンジ、105Msps

LTC2252: 接地入力時の

ヒストグラム、105Msps

LTC2252: SNR と 入力周波数、-1dB、2V レンジ、105Msps

## 標準的性能特性

LTC2252:SFDRと入力周波数、

-1dB、2Vレンジ、105Msps

22532 G26

LTC2252:SNRおよびSFDRと

サンプル・レート、2Vレンジ、

$f_{IN} = 5\text{MHz}$ 、-1dB

22532 G27

LTC2252:SNRと入力レベル、

$f_{IN} = 70\text{MHz}$ 、2Vレンジ、105Msps

22532 G28

LTC2252:SFDRと入力レベル、

$f_{IN} = 70\text{MHz}$ 、2Vレンジ、105Msps

22532 G29

LTC2252: $I_{OVDD}$ とサンプル・レート、

5MHzの正弦波入力、-1dB、

$0V_{DD} = 1.8\text{V}$

22532 G31

LTC2252: $I_{OVDD}$ とサンプル・レート、

5MHzの正弦波入力、-1dB

22532 G30

LTC2252:SNRとSENSEの電圧、

$f_{IN} = 5\text{MHz}$ 、-1dB

22532 G32

## ピン機能

**A<sub>IN+</sub>(ピン1)**: 正の差動アナログ入力。

**A<sub>IN-</sub>(ピン2)**: 負の差動アナログ入力。

**REFH(ピン3、4)**: A/Dコンバータの“H”リファレンス。これらのピンを相互に短絡させて、0.1 $\mu$ Fのセラミック・チップ・コンデンサをピンにできるだけ近づけて使用して、ピン5、6にバイパスします。また、さらに2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン5、6にバイパスし、1 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスします。

**REFL(ピン5、6)**: A/Dコンバータの“L”リファレンス。これらのピンを相互に短絡させて、0.1 $\mu$ Fのセラミック・チップ・コンデンサをピンにできるだけ近づけて使用して、ピン3、4にバイパスします。また、さらに2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してピン3、4にバイパスし、1 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスします。

**V<sub>DD</sub>(ピン7、32)**: 3V電源。0.1 $\mu$ Fのセラミック・チップ・コンデンサを使用してGNDにバイパスします。

**GND(ピン8)**: A/Dコンバータの電源グランド。

**CLK(ピン9)**: クロック入力。立ち上がりエッジで入力のサンプリングが開始されます。

**SHDN(ピン10)**: シャットダウン・モードの選択ピン。SHDNと $\overline{OE}$ をGNDに接続すると通常動作になり、出力がイネーブルされます。SHDNをGNDに接続し、 $\overline{OE}$ をV<sub>DD</sub>に接続すると通常動作になり、出力が高インピーダンスになります。SHDNをV<sub>DD</sub>に接続し、 $\overline{OE}$ をGNDに接続するとナップ・モードになり、出力が高インピーダンスになります。SHDNと $\overline{OE}$ をV<sub>DD</sub>に接続するとスリープ・モードになり、出力が高インピーダンスになります。

**$\overline{OE}$ (ピン11)**: 出力イネーブル・ピン。SHDNピンの機能を参照してください。

**NC(ピン12、13)**: これらのピンは接続しないでください。

**D0～D11(ピン14、15、16、17、18、19、22、23、24、25、26、27)**: デジタル出力。D11がMSBです。

**0GND(ピン20)**: 出力ドライバのグランド。

**0V<sub>DD</sub>(ピン21)**: 出力ドライバの正電源。0.1 $\mu$ Fのセラミック・チップ・コンデンサを使ってグランドにバイパスします。0V<sub>DD</sub>は0.5V～3.6Vの範囲に設定できます。

**OF(ピン28)**: オーバーフロー/アンダーフロー出力。オーバーフローとアンダーフローが生じると“H”になります。

**MODE(ピン29)**: 出力形式とクロック・デューティ・サイクル・スタビライザの選択ピン。MODEをGNDに接続すると、オフセット・バイナリの出力形式が選択され、クロック・デューティ・サイクル・スタビライザがオフします。1/3 V<sub>DD</sub>に接続すると、オフセット・バイナリの出力形式が選択され、クロック・デューティ・サイクル・スタビライザがオンします。2/3 V<sub>DD</sub>に接続すると、2の補数の出力形式が選択され、クロック・デューティ・サイクル・スタビライザがオンします。V<sub>DD</sub>に接続すると、2の補数の出力形式が選択され、クロック・デューティ・サイクル・スタビライザがオフします。

**SENSE(ピン30)**: リファレンスのプログラミング・ピン。SENSEをV<sub>CM</sub>に接続すると、内部リファレンスと±0.5Vの入力範囲が選択されます。V<sub>DD</sub>に接続すると、内部リファレンスと±1Vの入力範囲が選択されます。0.5Vより大きく1Vより小さい外部リファレンスをSENSEに印加すると、±V<sub>SENSE</sub>の入力範囲が選択されます。±1Vが最大有効入力範囲です。

**V<sub>CM</sub>(ピン31)**: 出力と入力の1.5V同相バイアス。2.2 $\mu$ Fのセラミック・チップ・コンデンサを使用してグランドにバイパスします。

**GND(露出パッド)(ピン33)**: A/Dコンバータの電源グランド。パッケージの底面の露出パッドはグランドに半田付けする必要があります。

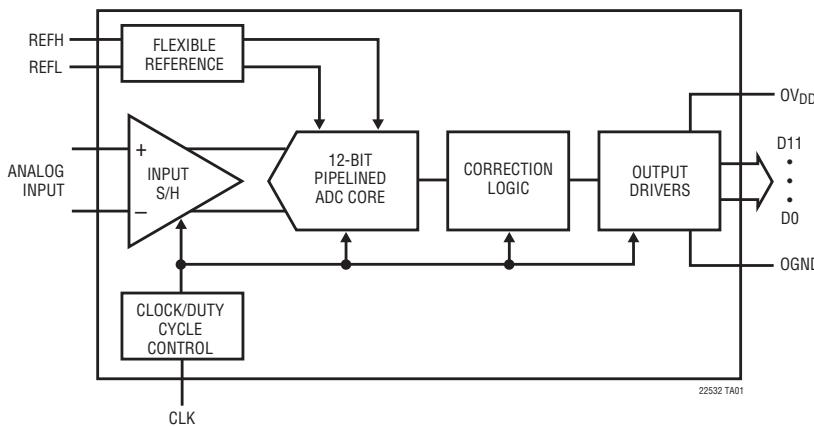

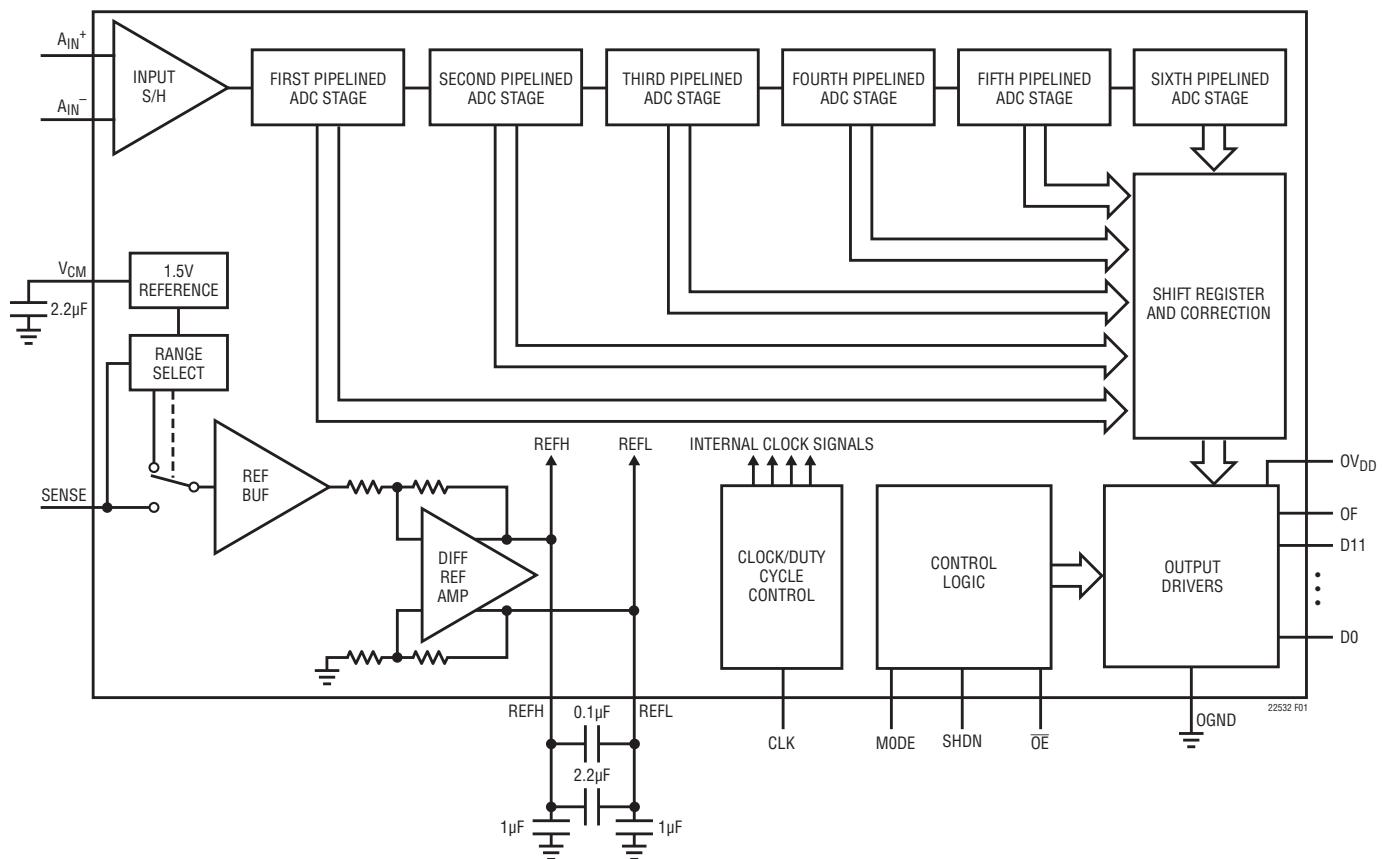

## 機能ブロック図

図1. 機能ブロック図

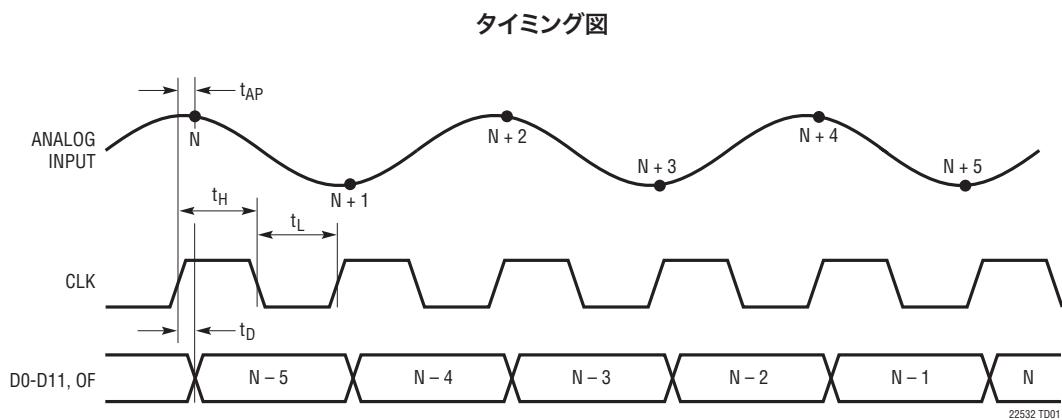

## タイミング図

## アプリケーション情報

### ダイナミック性能

#### 信号対ノイズ+歪み比

信号対ノイズ+歪み比[S/(N+D)]は、ADC出力における基本入力周波数のRMS振幅と、他の全ての周波数成分のRMS振幅の比です。出力の帯域はDCからサンプリング周波数の半分より低い周波数に制限されています。

#### 信号対ノイズ比

信号対ノイズ比(SNR)は、基本入力周波数のRMS振幅と、最初の5つの高調波とDCを除く他の全ての周波数成分のRMS振幅の比です。

#### 全高調波歪み

全高調波歪み(THD)は入力信号の全高調波の実効値の和と、入力信号の基本波の実効値との比です。帯域外高調波はDCからサンプリング周波数の半分までの周波数帯域でエイリアスを生じます。THDは次のように表されます。

$$THD = 20 \log (\sqrt{(V2^2 + V3^2 + V4^2 + \dots + Vn^2)}/V1)$$

ただし、V1は基本周波数のRMS振幅、V2～Vnは2次～n次の高調波の振幅です。このデータシートで計算されているTHDには5次までの高調波が全て使用されています。

#### 混変調歪み

A/Dコンバータの入力信号が複数のスペクトル成分で構成されていると、A/Dコンバータの伝達関数の非直線性により、THDに加えて混変調歪み(IMD)が生じことがあります。IMDは周波数の異なる別の正弦波入力が存在するためにある正弦波入力に生じる変化です。

周波数がfaとfbの2つの純粋な正弦波がADCの入力に与えられると、ADCの伝達関数の非直線性により  $mfa \pm nfb$  の和と差の周波数で歪み積を生じことがあります。ここで、mとnは0、1、2、3などです。3次の混変調歪み積は  $2fa + fb$ 、 $2fb + fa$ 、 $2fa - fb$  および  $2fb - fa$  です。混変調歪みは、最大の3次混変調積の実効値に対する、どちらかの入力トーンの実効値の比として定義されます。

#### スプリアス・フリー・ダイナミック・レンジ(SFDR)

スプリアスフリー・ダイナミックレンジは、入力信号とDCを除いた最大のスペクトル成分であるピーク高調波またはスプリアス・ノイズです。この値は、フルスケール入力信号の実効値を基準にしたデシベル値で表されます。

#### 入力帯域幅

入力帯域幅はフルスケールの入力信号から再構成された基本波の振幅が3dBだけ減少する入力周波数です。

#### アーチャ遅延時間

CLKが電源電圧の中間値に達した時点から、入力信号がサンプル・ホールド回路によって保持される瞬間までの時間です。

#### アーチャ遅延ジッタ

変換間でのアーチャ遅延時間の変動のことです。このランダムな変動により、AC入力のサンプリング時にノイズが生じます。ジッタだけを要因とした場合の信号対ノイズ比は次のようにになります。

$$SNR_{JITTER} = -20 \log (2\pi \cdot f_{IN} \cdot t_{JITTER})$$

#### コンバータの動作

図1に示すように、LTC2253/LTC2252はCMOSパイプライン構成の多段コンバータです。パイプライン構成の6個のADC段を備えており、サンプリングされたアナログ入力は5サイクル後にデジタル値になります(「タイミング図」を参照)。最適なAC性能を得るにはアナログ入力を差動でドライブします。コストが重視されるアプリケーションの場合、高調波歪みがわずかに悪化するシングルエンドでアナログ入力をドライブすることができます。CLK入力はシングルエンドです。LTC2253/LTC2252は、CLK入力ピンの状態で定まる2つのフェーズで動作します。

図1に示すパイプライン構成の各段は、1個のADC、再構成DAC、および段間残差アンプを備えています。動作時、ADCは各段の入力を量子化し、量子化された値はDACによって入力から差し引かれ、残差を生じます。残差は残差アンプによって増幅されて出力されます。奇数段がその残差を出力しているとき偶数段がその残差を取得するように、またその逆になるように、後続段は先行段から位相がずれて動作します。

## アプリケーション情報

CLKが“L”的とき、アナログ入力は差動式に直接サンプリングされ、ブロック図に示す「INPUT S/H」(入力サンプル/ホールド)の内部で、入力サンプル・ホールド・コンデンサに移されます。CLKが“L”から“H”に遷移する瞬間、サンプリングされた入力がホールドされます。CLKが“H”的間、ホールドされた入力電圧はサンプル/ホールド・アンプによってバッファされます。このアンプはパイプライン構成の最初のADC段をドライブします。最初の段はCLKの“H”フェーズの間にサンプル/ホールドの出力を取得します。CLKが“L”に戻ると、第1段から残差が生じ、第2段がその残差を取り込みます。同時に、入力S/Hは再度アナログ入力を取り込みます。CLKが“H”に戻ると2番目の段はその残差を出力し、この残差が3番目の段によって取得されます。同様の過程が3番目、4番目、および5番目の段で繰り返され、5番目の段の残差は最終評価のために6番目のADCに送られます。

最初の段に続く各ADC段にはフラッシュ誤差とアンプのオフセット誤差を調節するための追加範囲があります。ADCの全段からの結果は、出力バッファに送る前に、それらの結果を補正ロジックで適切に結合できるようにデジタル動作で同期させます。

## サンプル/ホールド動作と入力ドライブ

### サンプル/ホールド動作

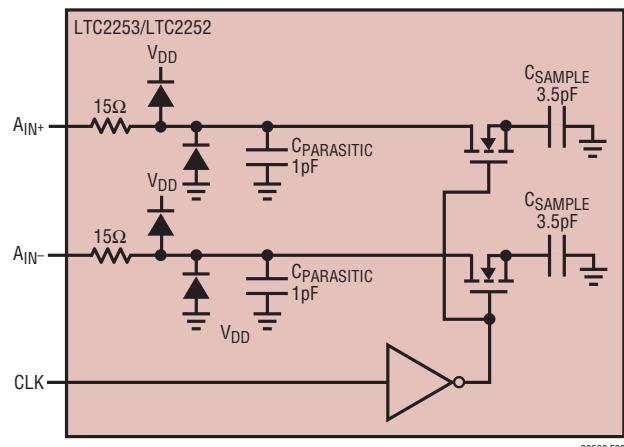

LTC2253/LTC2252のCMOS差動サンプル・ホールドの等価回路を図2に示します。アナログ入力はNMOSトランジスタを介してサンプリング・コンデンサ( $C_{SAMPLE}$ )に接続されています。各入力に接続されているコンデンサ( $C_{PARASITIC}$ )は、各入力に関連した他の全ての容量を合計したものです。

CLKが“L”的とき、サンプリング・フェーズの間トランジスタはアナログ入力をサンプリング・コンデンサに接続するので、これらのコンデンサは差動入力電圧まで充電され、さらにこの電圧をトラッキングします。CLKが“L”から“H”に移行するとき、サンプリングされた入力電圧はサンプリング・コンデンサにホールドされます。CLKが“H”になっているホールド・フェーズの間、サンプリング・コンデンサは入力から切り離され、ホールドされた電圧はADCコアに送られて処理されます。CLKが“H”から“L”に遷移すると、入力はサンプリング・コンデンサに再度接続され、新しいサンプルを収集します。サンプリング・コンデンサには直前のサンプルが引き続きホールドされているので、隣接するサンプル間の電圧変化に比例した充電グリッ

チがこのときに見られます。直前のサンプルと新しいサンプル間の変化が小さいと、入力で見受けられる充電グリッチは小さくなります。ナイキスト周波数の近くの入力周波数で見られる変化のように、入力の変化が大きいと、さらに大きな充電グリッチが見られます。

### シングルエンド入力

コストが重視されるアプリケーションの場合、アナログ入力をシングルエンドでドライブすることができます。シングルエンド入力を用いると、高調波歪みが増加しINLが低下しますが、SNRとDNLは変化しません。シングルエンド入力の場合、入力信号を使用して  $A_{IN^+}$  をドライブし、 $A_{IN^-}$  を1.5Vまたは  $V_{CM}$  に接続する必要があります。

### 同相バイアス

最適な性能を得るには、アナログ入力を差動でドライブします。各入力は1.5Vの同相電圧を中心として、2Vレンジでは $\pm 0.5V$ 、1Vレンジでは $\pm 0.25V$ の振幅が必要です。  $V_{CM}$ 出力ピン(ピン31)を使って同相バイアス・レベルを供給することができます。 $V_{CM}$ はトランジスタのセンタータップに直接接続してDC入力レベルを設定するか、またはオペアンプの差動ドライバ回路のリファレンス・レベルとして接続することができます。 $V_{CM}$ ピンは、 $2.2\mu F$ 以上のコンデンサを使って、ADCに近いグランドにバイパスする必要があります。

図2. 等価入力回路

## アプリケーション情報

### 入力ドライブのインピーダンス

全ての高性能高速ADCの場合と同様、LTC2253/LTC2252のダイナミック性能は入力ドライブ回路、特に2次と3次の高調波の影響を受けることがあります。ソース・インピーダンスと入力リアクタンスはSFDRに影響を及ぼすことがあります。サンプル・ホールド回路はCLKの立ち下がりエッジで3.5pFのサンプリング・コンデンサを入力ピンに接続してサンプリング期間を開始します。サンプリング期間はCLKが立ち上がるまで終了し、サンプリングされた入力をサンプリング・コンデンサにホールドします。入力回路は理想的にはサンプリング期間1/(2FENCODE)の間にサンプリング・コンデンサを完全に充電するのに十分なだけ高速である必要があります。ただし、これが常に可能とは限らず、不十分なセトリングのためにSFDRが低下することがあります。不十分なセトリングの影響を最小限に抑えるため、サンプリング・グリッチはできるだけ直線状になるように設計されています。

最高の性能を得るために各入力のソース・インピーダンスを100Ω以下にすることを推奨します。差動入力のソース・インピーダンスは整合させる必要があります。よく整合していないと、偶数次高調波、特に2次高調波が大きくなります。

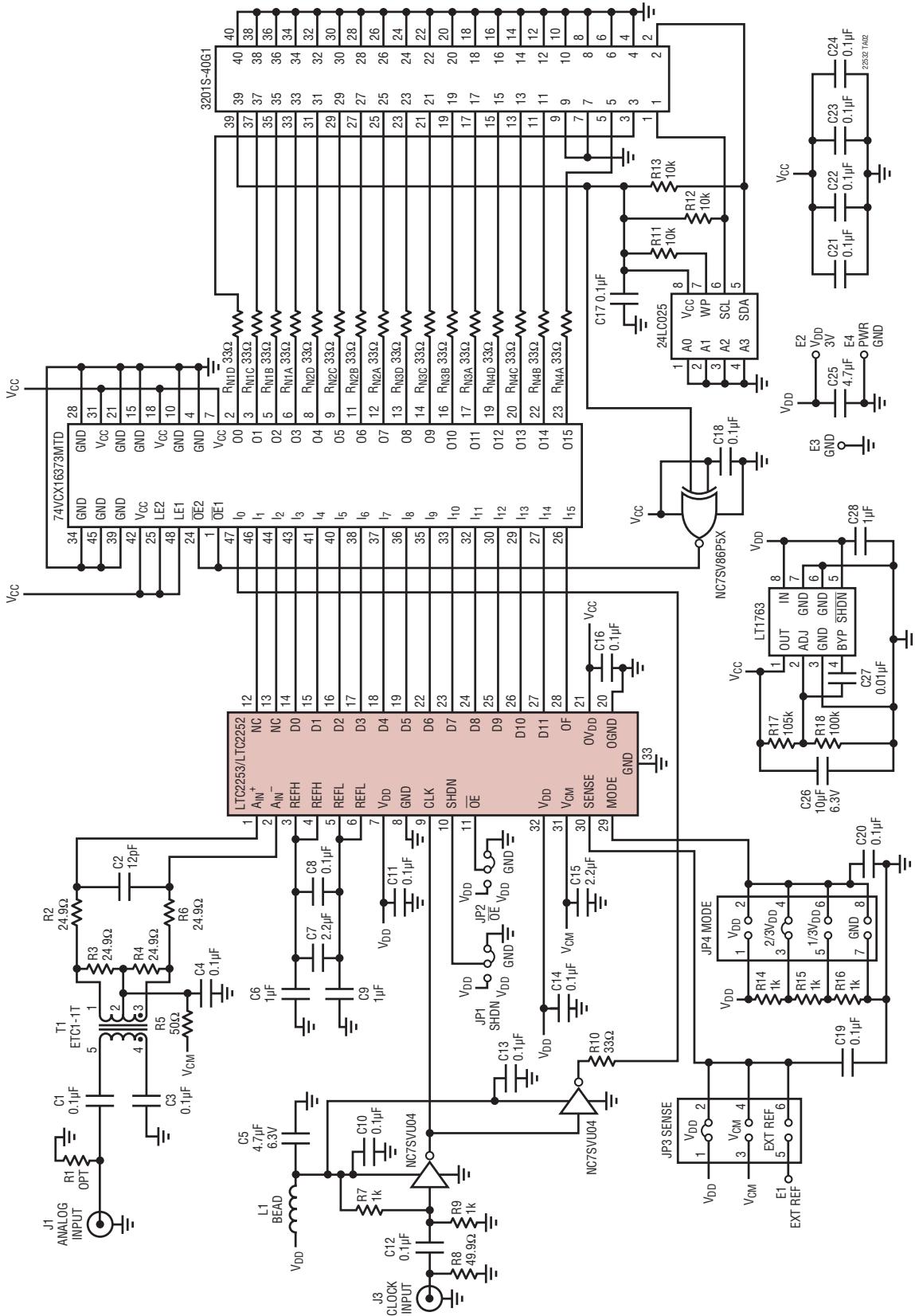

### 入力ドライブ回路

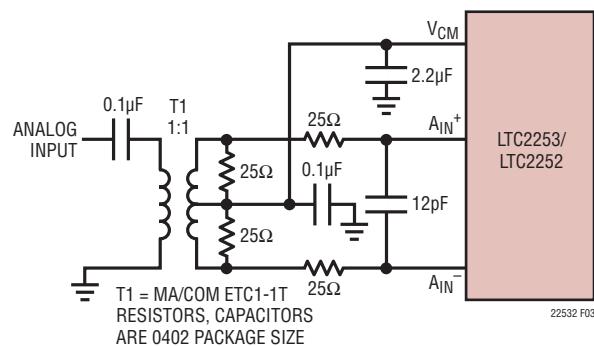

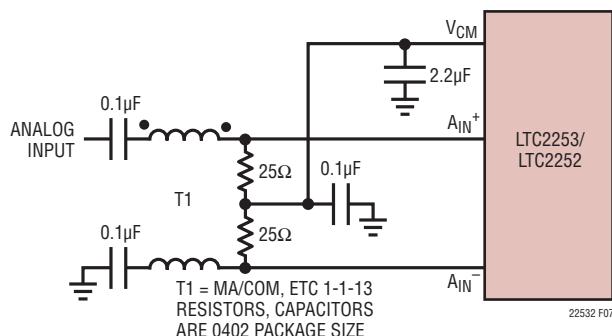

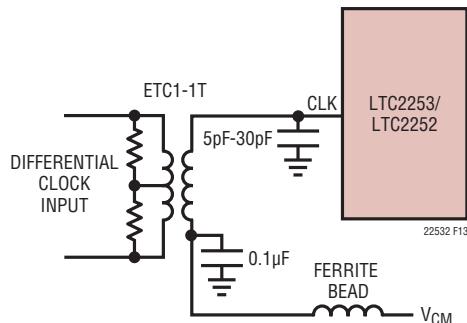

2次側にセンタータップを備えたRFトランスによってドライブされるLTC2253/LTC2252を図3に示します。2次側のセンタータップはV<sub>CM</sub>でDCバイアスされており、ADCの入力信号を最適なDCレベルに設定します。トランスの2次側を終端するのは望ましいことです。これにより、サンプル・ホールドによって生じる充電グリッチの同相経路が確保されるからです。図3には巻数比が1:1のトランスが示されています。ADCから見たソース・インピーダンスが各ADC入力で100Ωを超えないように、他の巻数比を使用することもできます。トランスを使う場合の不利な点は低周波応答の低下です。ほとんどの小型RFトランスは1MHzより低い周波数では性能が低下します。

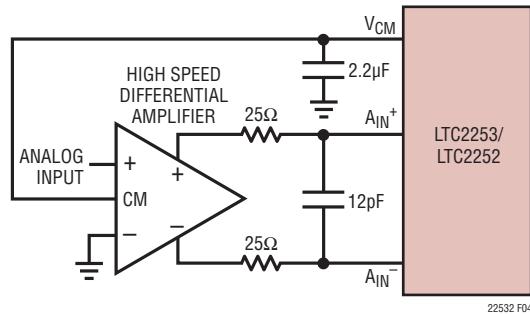

差動アンプを使ってシングルエンド入力信号を差動入力信号に変換する例を図4に示します。この方法の利点は低い入力周波数に対する応答が良いことです。ただし、ほとんどのオペアンプでは、利得帯域幅の制限により、高い入力周波数でのSFDRが制限されます。

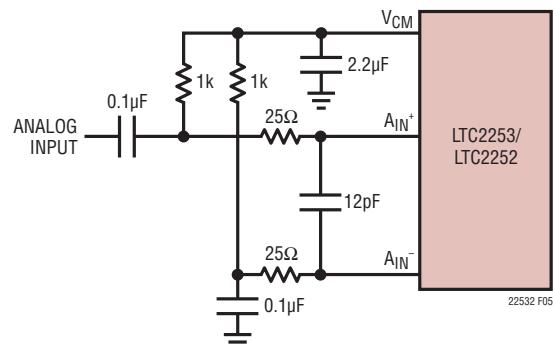

シングルエンド入力回路を図5に示します。アナログ入力から見たインピーダンスを整合させる必要があります。歪みが少ない必要がある場合、この回路は推奨されません。

アナログ入力に接続されている25Ωの抵抗と12pFのコンデンサは2つの役目を果たします。サンプル・ホールドの充電グリッチからドライブ回路を絶縁し、コンバータの入力の広帯域ノイズを制限します。

図3. トランスを使用したシングルエンド入力から差動入力への変換

図4. アンプを使った差動ドライブ

図5. シングルエンドのドライブ

## アプリケーション情報

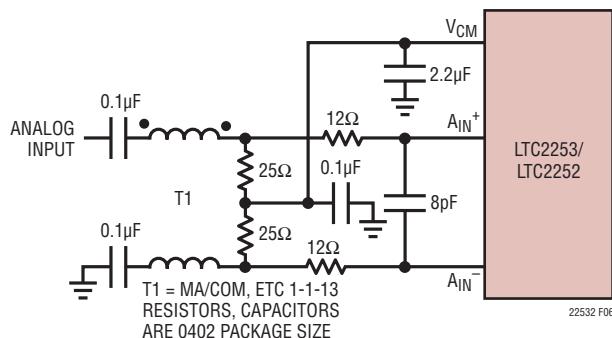

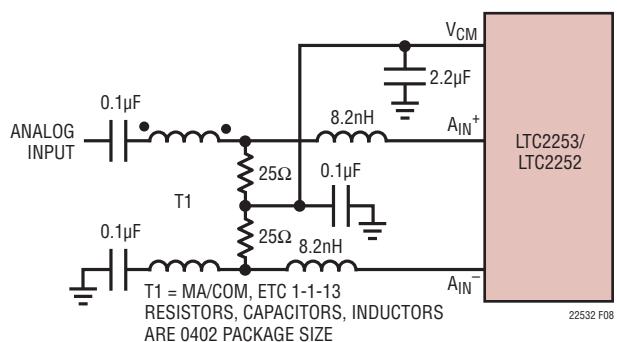

70MHzを超える入力周波数では、図6、図7、および図8の入力回路を推奨します。センタータップ付き磁束結合型トランジスタに比べて、バラン・トランジスは高周波数応答が優れています。カップリング・コンデンサにより、アナログ入力を1.5VにDCバイアスすることができます。図8の直列インダクタはインピーダンス整合用素子で、ADCの帯域幅を最大にします。

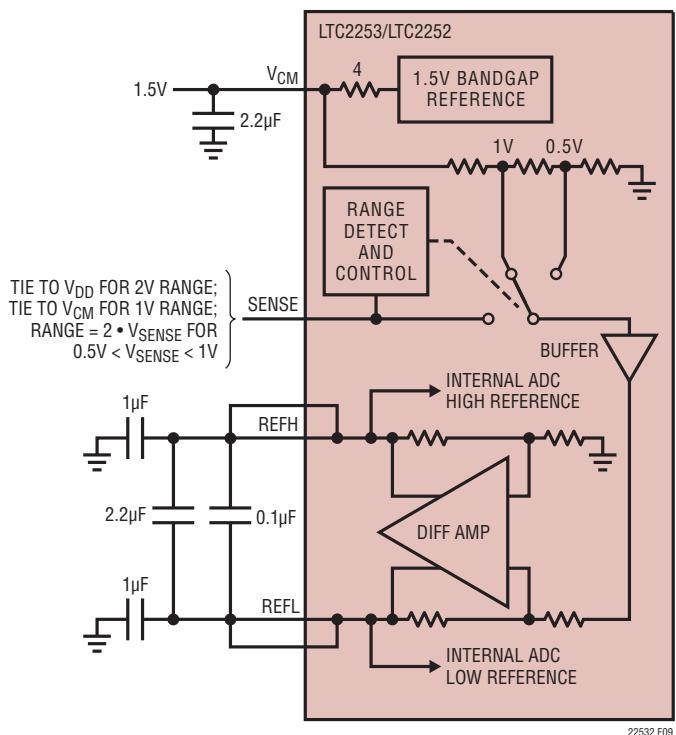

### リファレンスの動作

1.5Vのバンドギャップ・リファレンス、差動アンプ、およびスイッチングと制御の回路で構成されるLTC2253/LTC2252のリファレンス回路を図9に示します。内部電圧リファレンスはピンで選択可能な2V(差動±1V)または1V(差動±0.5V)の2つの入力レンジに設定することができます。SENSEピンをV<sub>DD</sub>に接続すると2Vの範囲が選択され、SENSEピンをV<sub>CM</sub>に接続すると1Vの範囲が選択されます。

図6. 入力周波数が70MHz～170MHzの場合の推奨フロントエンド回路

図7. 入力周波数が170MHz～300MHzの場合の推奨フロントエンド回路

1.5Vのバンドギャップ・リファレンスは2つの機能を果たします。このリファレンスの出力は任意の外部入力回路の同相電圧を設定するためのDCバイアス点を提供します。さらに、差動アンプと一緒に使用されて、内部のADC回路が必要とする差動リファレンス・レベルを生成します。1.5Vリファレンスの出力V<sub>CM</sub>には外付けのバイパス・コンデンサが必要です。このコンデンサは、内部回路と外部回路に対して高周波で低インピーダンスのグランド経路を確保します。

図8. 入力周波数が300MHzを超える場合の推奨フロントエンド回路

図9. 等価リファレンス回路

# LTC2253/LTC2252

## アプリケーション情報

差動アンプはADCの“H”リファレンスと“L”リファレンスを生成します。高速スイッチング回路がこれらの出力に接続されているので、これらの出力は外部でバイパスする必要があります。各出力には2つのピンがあります。パッケージのインダクタンスを減らすために複数の出力ピンを必要とします。バイパス・コンデンサは図9に示すように接続する必要があります。

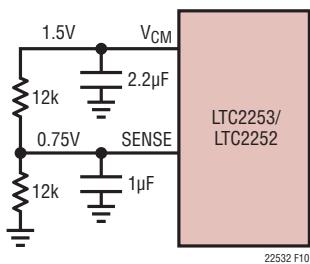

ピンで選択可能な範囲の間にくる他の電圧範囲は、図10に示すように、2つの外付け抵抗を使って設定することができます。外部リファレンスを使って、その出力を直接または抵抗分割器を通してSENSEに与えることができます。ロジック・デバイスを使ってSENSEピンをドライブすることは推奨しません。SENSEピンはできるだけコンバータの近くで適切なレベルに接続します。SENSEピンを外部からドライブする場合、 $1\mu\text{F}$ のセラミック・コンデンサを使ってデバイスのできるだけ近くでグランドにバイパスします。

図10. 1.5VレンジのADC

## 入力範囲

入力範囲はアプリケーションに基づいて設定することができます。2Vの入力範囲では優れたSFDRを保ったまま最良のSNRが得られます。1Vの入力範囲のSFDR性能はさらに優れていますが、SNRは4.2dBだけ低下します。

## クロック入力のドライブ

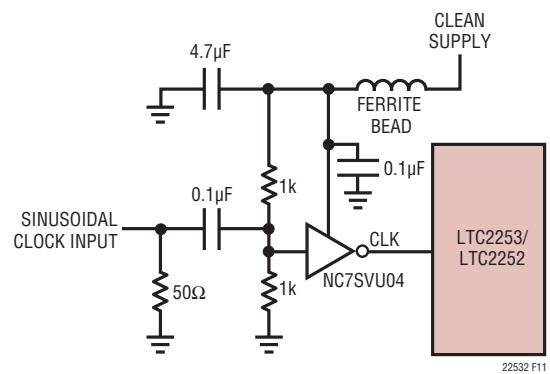

CLK入力はCMOSまたはTTLレベルの信号で直接ドライブすることができます。CLKピンの前にジッタの小さな方形波発生回路を置いて正弦波のクロックを使うこともできます(図11)。

LTC2253/LTC2252のノイズ特性はアナログ入力に依存しますが、同程度にクロック信号の品質に依存することがあります。クロック信号に何らかのノイズがあると、追加のアーチャ・ジッタが生じ、本来のADCアーチャ・ジッタにRMSとして加算されます。

高い入力周波数をデジタル変換する場合など、ジッタに対する要求が厳しいアプリケーションではできるだけ大きな振幅を使います。また、正弦波信号でADCをクロック駆動する場合は、クロック信号にフィルタをかけて広帯域ノイズとソースによって生じた歪み積を減らします。

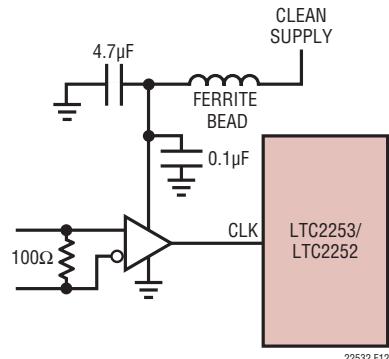

図12および13に、差動クロックをシングルエンドCLK入力に変換するための代替手段を示します。トランジスタを使用すること

図11. 正弦波シングルエンドCLKドライブ

IF LVDS USE FIN1002 OR FIN1018.

FOR PECL, USE AZ1000ELT21 OR SIMILAR

図12. LVDSまたはPECLからCMOSへのコンバータを使用したCLKのドライブ

図13. トランジスタを使用したLVDSまたはPECL CLKのドライブ

22532fa

## アプリケーション情報

で、位相ノイズへの寄与が増えることはありません。LVDS または PECL から CMOS への変換器は、トランジスタを使用する解決策と比較して、70MHz 未満では性能の低下がわずかですが、140MHz では SNR が劣化します。受信される信号の特性も、SNR が劣化する程度に大きく影響します。公称電力レベルがフルスケールを少なくとも 6dB ~ 8dB 下回る必要がある WCDMA や OFDM などの波高率の高い信号の場合、これらの変換器の使用が与える影響は少なくなります。

例におけるトランジスタは、使用している信号に適した終端を使用して終端することができます。電圧の低い差動信号が検討されている場合、1:4 のインピーダンス比を持つトランジスタを使用することを推奨します。差動信号が異なるプレーン上で発生する場合、A/D コンバータに近づけたコンデンサを介して、センタータップをグランドにバイパスすることができます。入力にコンデンサを使用すると、ピーピングが発生する場合があり、伝送線路の長さによっては、 $10\Omega$  ~  $20\Omega$  の直列抵抗が必要になることがあります。この直列抵抗は、隣接するデジタル信号によってクロック・ラインに発生する可能性のある高周波ノイズを除去するためのローパス・フィルタ、および反射の減衰メカニズムの両方として機能します。

### 最大変換レートと最小変換レート

LTC2253/LTC2252 の最大変換レートは 125Msps (LTC2253) および 105Msps (LTC2252) です。LTC2253/LTC2252 のサンプル・レートの下限はサンプル・ホールド回路の電圧低下によって決まります。この ADC のパイプライン・アーキテクチャでは、アナログ信号を小容量のコンデンサに保存することに依存しています。コンデンサは接合部の漏れ電流によって放電します。LTC2253/LTC2252 の規定最小動作周波数は 1Msps です。

### クロック・デューティ・サイクル・スタビライザ

入力クロックのデューティ・サイクルが 50% でない場合でも、オプションのクロック・デューティ・サイクル・スタビライザ回路により、高性能が確保されます。ほとんどのアプリケーションでは、クロック・デューティ・サイクル・スタビライザの使用を推奨します。クロック・デューティ・サイクル・スタビライザを使用するには、外付け抵抗を使って MODE ピンを  $1/3V_{DD}$  または  $2/3V_{DD}$  に接続します。

この回路は CLK ピンの立ち上がりエッジを使って、アナログ入力をサンプリングします。CLK の立ち下がりエッジは無視され、フェーズロック・ループにより内部で立ち下がりエッジが生成されます。入力クロックのデューティ・サイクルは 40% ~ 60% の範囲で変化することができ、クロック・デューティ・サイクル・スタビライザは内部デューティ・サイクルを 50% に保ちます。クロックが長時間オフする場合、デューティ・サイクル・スタビライザ回路の PLL が入力クロックにロックするのに 100 クロック・サイクルを必要とします。

サンプル・レートを迅速に変更する必要のあるアプリケーションでは、クロック・デューティサイクル・スタビライザをディスエーブルすることができます。デューティ・サイクル・スタビライザをディスエーブルする場合は、サンプリング・クロックのデューティ・サイクルが 50% ( $\pm 5\%$ ) になるように注意してください。

### デジタル出力

アナログ入力電圧、デジタル・データ・ビット、およびオーバーフロー・ビットの相互関係を表 1 に示します。

表 1. 出力コードと入力電圧

| $A_{IN^+} - A_{IN^-}$<br>(2V レンジ) | OF | $D_{11} \sim D_0$<br>(オフセット・バイナリ) | $D_{11} \sim D_0$<br>(2 の補数) |

|-----------------------------------|----|-----------------------------------|------------------------------|

| >+1.000000V                       | 1  | 1111 1111 1111                    | 0111 1111 1111               |

| +0.999512V                        | 0  | 1111 1111 1111                    | 0111 1111 1111               |

| +0.999024V                        | 0  | 1111 1111 1110                    | 0111 1111 1110               |

| +0.000488V                        | 0  | 1000 0000 0001                    | 0000 0000 0001               |

| 0.000000V                         | 0  | 1000 0000 0000                    | 0000 0000 0000               |

| -0.000488V                        | 0  | 0111 1111 1111                    | 1111 1111 1111               |

| -0.000976V                        | 0  | 0111 1111 1110                    | 1111 1111 1110               |

| -0.999512V                        | 0  | 0000 0000 0001                    | 1000 0000 0001               |

| -1.000000V                        | 0  | 0000 0000 0000                    | 1000 0000 0000               |

| <-1.000000V                       | 1  | 0000 0000 0000                    | 1000 0000 0000               |

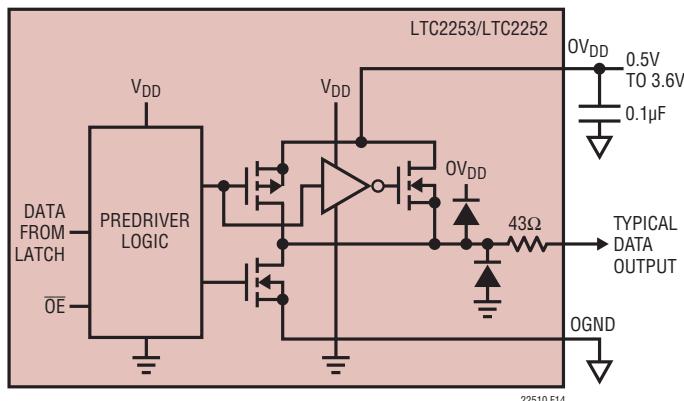

### デジタル出力バッファ

1 個の出力バッファの等価回路を図 14 に示します。各バッファは  $OV_{DD}$  と  $OGND$  から給電され、ADC 電源とグランドからは分離されています。出力ドライバに N チャネル・トランジスタが追加されているので低電圧まで動作可能です。出力に直列接続された内部抵抗により、外部回路から見ると出力は  $50\Omega$  に見えるので、外部の減衰抵抗が不要になることがあります。

## アプリケーション情報

図14. デジタル出力バッファ

全ての高速/高分解能コンバータの場合と同様、デジタル出力負荷が性能に影響を与えることがあります。デジタル出力と敏感な入力回路の間に生じる恐れのある相互反応を抑えるため、LTC2253/LTC2252のデジタル出力はできるだけ小さな容量性負荷をドライブするようにします。フルスピード動作を行う場合は、容量性負荷を10pF以下に抑えます。

OV<sub>DD</sub>電圧を低くすることも、デジタル出力からの干渉を減らすのに役立ちます。

### データ形式

LTC2253/LTC2252のパラレル・デジタル出力は、MODEピンを使用して、オフセット・バイナリまたは2の補数の形式を選択できます。MODEをGNDまたは1/3V<sub>DD</sub>に接続すると、オフセット・バイナリの出力形式が選択されます。MODEを2/3V<sub>DD</sub>ま

表2. MODEピンの機能

| MODEピン             | 出力形式       | クロック・デューティ・サイクル・スタビライザ |

|--------------------|------------|------------------------|

| 0                  | オフセット・バイナリ | オフ                     |

| 1/3V <sub>DD</sub> | オフセット・バイナリ | オン                     |

| 2/3V <sub>DD</sub> | 2の補数       | オン                     |

| V <sub>DD</sub>    | 2の補数       | オフ                     |

たはV<sub>DD</sub>に接続すると、2の補数の出力形式が選択されます。外付け抵抗分割器を使って1/3V<sub>DD</sub>または2/3V<sub>DD</sub>のロジック値を設定することができます。MODEピンのロジック状態を表2に示します。

### オーバーフロー・ビット

OFがロジック“H”を出力すると、コンバータにはオーバーレンジまたはアンダーレンジのいずれかが生じます。

### 出力ドライバの電源

出力専用の電源ピンとグランド・ピンが備わっているので、出力ドライバをアナログ回路から分離することができます。デジタル出力バッファの電源OV<sub>DD</sub>は、ロジックをドライブするのと同じ電源に接続します。例えば、1.8V電源から電力を供給されているDSPをコンバータがドライブする場合、OV<sub>DD</sub>は同じ1.8V電源に接続します。

500mV～3.6Vの任意の電圧でOV<sub>DD</sub>に給電できます。OGNDはGND～1Vの任意の電圧で電力供給を受けることができ、OV<sub>DD</sub>より低くなければなりません。ロジック出力は、OGNDからOV<sub>DD</sub>までの範囲で振幅します。

### 出力イネーブル

出力イネーブル・ピン $\overline{OE}$ を使って出力をディスエーブルすることができます。 $\overline{OE}$ を“H”にすると、OFを含む全てのデータ出力がディスエーブルされます。データのアクセス時間やバスの解放時間は、フルスピード動作時に出力のイネーブルやディスエーブルをするには長すぎます。出力の“Hi-Z”状態は長期の休止時に使用することを意図しています。

### スリープ・モードとナップ・モード

節電のため、コンバータをシャットダウン・モードまたはナップ・モードにすることができます。SHDNをGNDに接続すると通常動作になります。SHDNをV<sub>DD</sub>に接続し、 $\overline{OE}$ をV<sub>DD</sub>に接続するとスリープ・モードになります、リファレンスを含む全ての回路をパワーダウンし、電力損失は標準で1mWになります。スリープ・モードから回復するとき、リファレンスのコンデンサを再充電して安定化する必要があるので、出力データが有効になるまで数ミリ秒かかります。SHDNをV<sub>DD</sub>に接続し、 $\overline{OE}$ をGNDに接続するとナップ・モードになります、電力損失は標準で15mWになります。ナップ・モードでは内蔵リファレンス回路はオンしたままなので、ナップ・モードからの回復はスリープ・モードからの回復よりも速く、標準で100クロック・サイクルしかかかりません。スリープとナップの両方のモードで全てのデジタル出力はディスエーブルされ、“Hi-Z”状態になります。

## アプリケーション情報

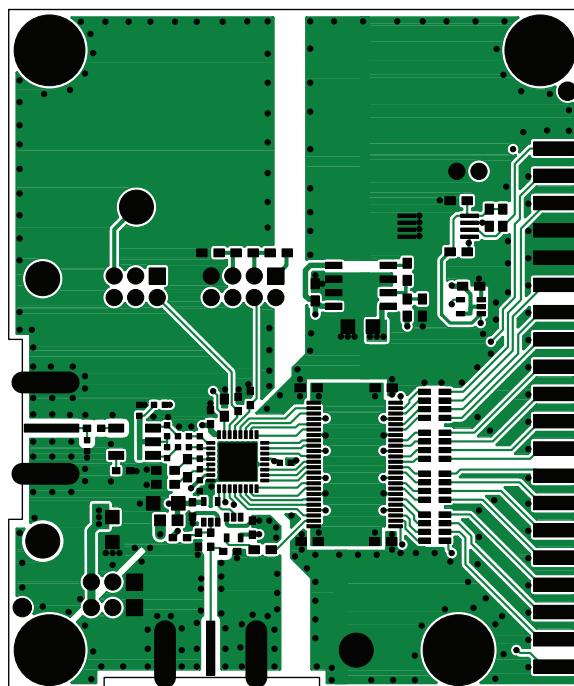

### 接地とバイパス

LTC2253/LTC2252には、切れ目のないきれいなグランド・プレーンを備えたプリント回路基板が必要です。内部グランド・プレーンを備えた多層基板を推奨します。プリント回路基板のレイアウトでは、デジタル信号線とアナログ信号線をできるだけ離すようにします。特に、デジタル・トラックをアナログ信号トラックと並べて配置したり、ADCの下に配置したりしないように注意してください。

V<sub>DD</sub>、OV<sub>DD</sub>、V<sub>CM</sub>、REFH、REFLの各ピンには、高品質のセラミック・バイパス・コンデンサを使用します。バイパス・コンデンサは、できるだけピンの近くに配置する必要があります。特に重要なのは、REFHとREFLの間に配置する0.1 $\mu$ Fのコンデンサです。このコンデンサはできるだけデバイスに近づけて(1.5mm以内)配置してください。0402サイズのセラミック・コンデンサを推奨します。REFHとREFLの間の大きい2.2 $\mu$ Fコンデンサはこれよりいくらか離れてもかまいません。ピンとバイパス・コンデンサを接続するトレースは短くする必要があり、幅はできるだけ広くします。

LTC2253/LTC2252の差動入力は平行に配線し、互いに近づけるようにします。入力トレースはできるだけ短くして容量を小さくし、ノイズを拾わないようにします。

### 熱伝達

LTC2253/LTC2252が発生する熱の大部分はダイから底面の露出パッドとパッケージのピンを通ってプリント回路基板に伝わります。優れた電気的性能と熱性能を得るには、露出パッドをPC基板の大きな接地されたパッドに半田付けします。全てのグランド・ピンを面積が十分大きなグランド・プレーンに接続することが重要です。

### アンダーサンプリングのクロック・ソース

アンダーサンプリングでは、クロック・ソースに対する要求レベルが高くなり、入力周波数が高いほどクロックのジッタや位相ノイズに対して敏感になります。フルスケール信号のSNRを70MHzで1dBだけ低下させるクロック・ソースは、SNRを140MHzでは3dB、190MHzでは4.5dBだけ低下させます。

クロック周波数の絶対精度が比較的重要ではなく、1つのADCだけが必要とされる場合、SaronixやVectronなどのメー

カーの3Vメタルキャン発振器をADCの近くに配置してADCに直接接続することができます。ADCまでいくらかでも距離がある場合、何らかのソース終端を行つて、たとえ数分の1インチでも生じる可能性のあるリングングを抑えます。クロックが電源の値をオーバーシュートしないようにする必要があります。オーバーシュートすると性能が低下します。正弦波のクロック・ソースでない限り、クロック信号は狭帯域のフィルタを通さないでください。狭帯域のフィルタを通すと、標準的なデジタル・クロック信号に含まれる立ち上がり時間と立ち下がり時間の影響が位相ノイズに反映されるからです。

位相ノイズが最も小さい発振器は出力がシングルエンドの正弦波であり、これらのデバイスの場合は、ADCの近くにフィルタを使用すると効果的な場合があります。このフィルタはADCに近づけて配置して、往復の反射時間を短くするとともに、フィルタとADCの間のトレースが外部の影響を受けにくくします。近接位相ノイズの影響を受けやすい場合、発振器の電源と全てのバッファは非常に安定したものでなければなりません。電源が安定していないと、電源による伝播遅延の変動によって位相ノイズが生じます。これらのクロック・ソースはデジタル・デバイスと見なされるかもしれません、それらをデジタル電源で動作させないでください。そのクロックがFPGAなどのデジタル・デバイスをドライブするのにも使用される場合、発振器と全てのクロックのファンアウト・デバイスをADCの近くに配置し、ADCへの配線を優先させます。FPGAへのクロック信号は信号源で直列終端を行い、FPGAからの高周波ノイズがクロックのファンアウト・デバイスのサブストレートの状態を乱さないようにします。FPGAをプログラム可能な分割器として使用する場合、元の発振器を使って信号の時間合せを行う必要があります、タイミング調整用フリップ・フロップと発振器をADCに近づけて配置し、十分に安定した電源から電力を供給します。

複数のADCが存在する場合、またはクロック・ソースがいくらか離れている場合、クロックを差動で分配することを推奨します。これは、EMIの観点からだけでなく、デジタル・ソースからの放射ノイズや多層PCBの層間に存在する導波路内を伝播するノイズを防ぐ観点からも推奨します。この差動ペアは互いに近接させ、他の信号から離す必要があります。差動ペアは、両側にトレース間隔の少なくとも3倍の距離をとって銅でガードを設け、1/4インチ以下の間隔でビアを使って接地します。

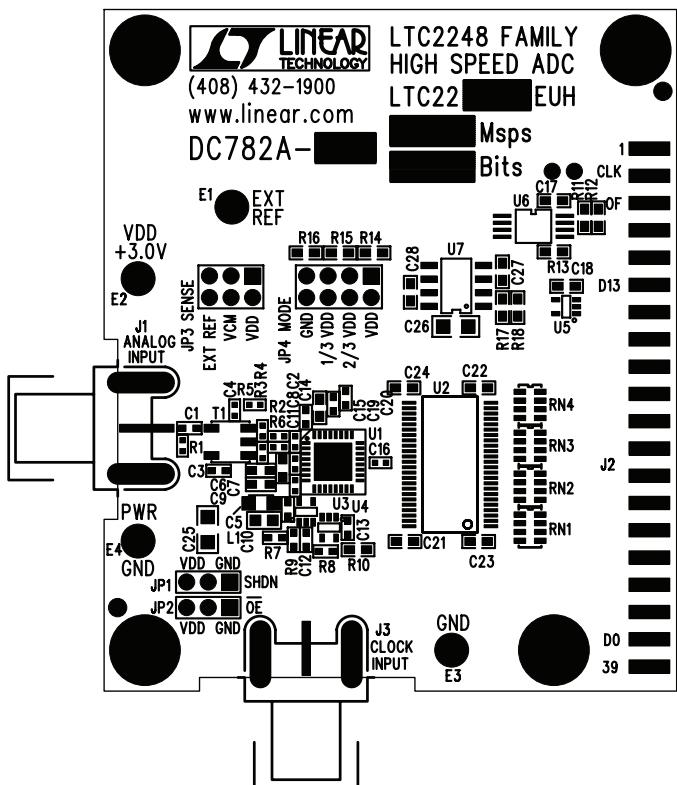

# LTC2253/LTC2252

## アプリケーション情報

## アプリケーション情報

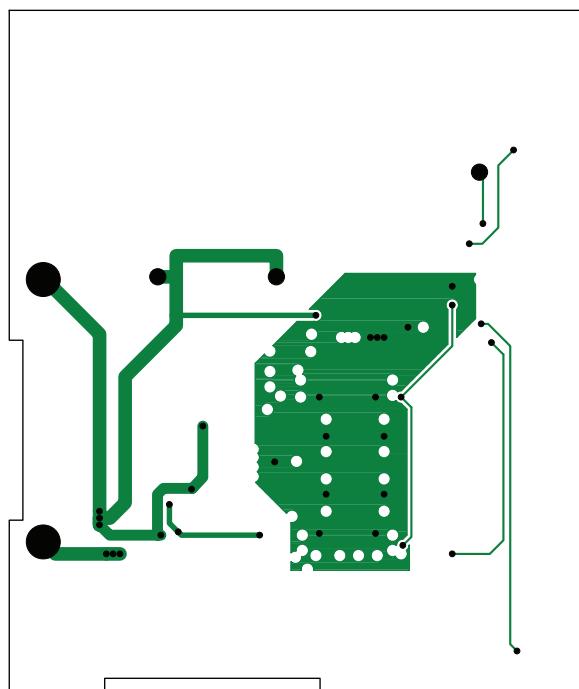

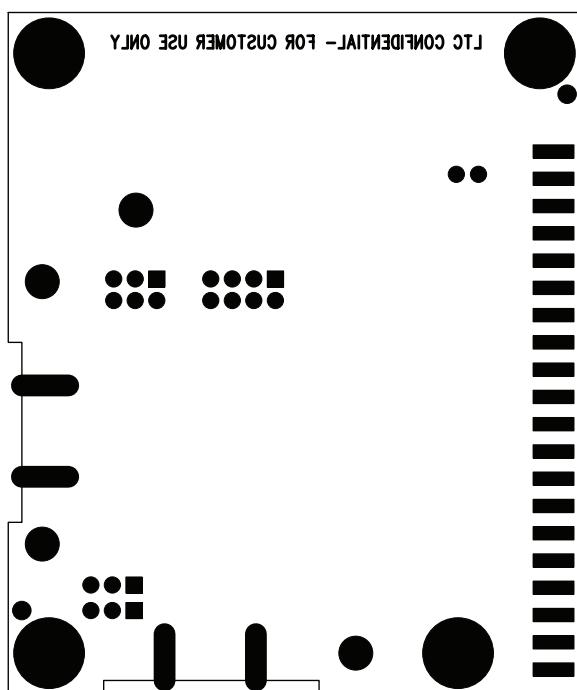

部品面シルク

上面

中間層 2 GND

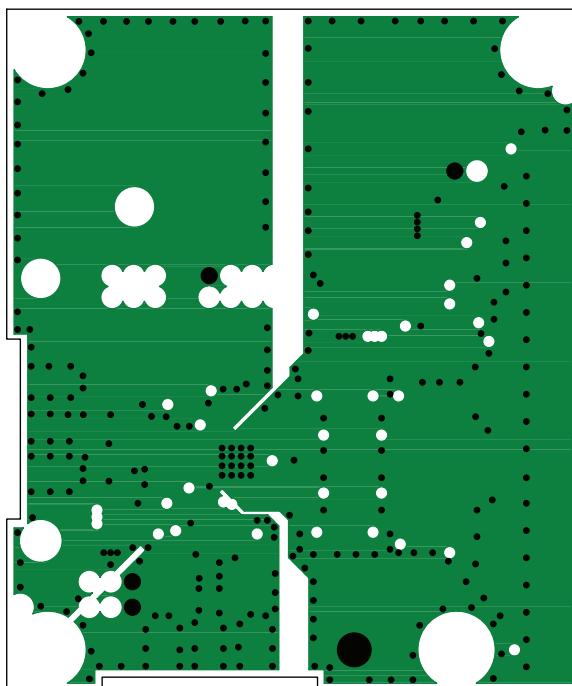

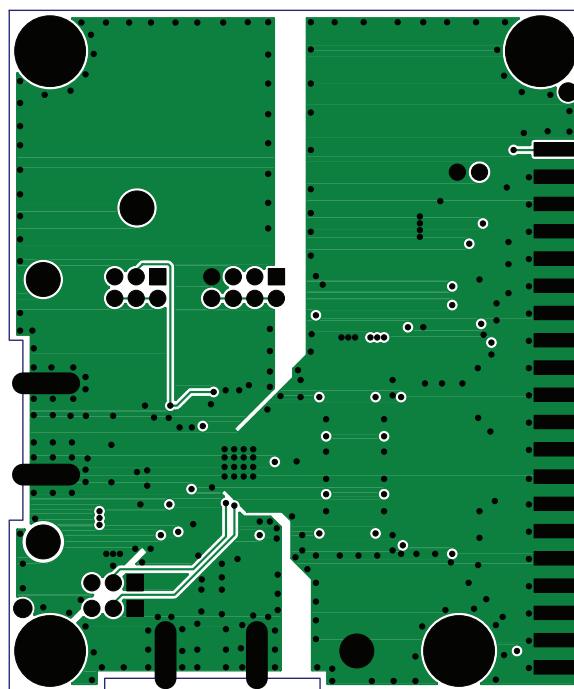

# LTC2253/LTC2252

## アプリケーション情報

中間層3 電源

上面

はんだ面シルク

22532fa

## パッケージ

## 注記 :

1. 図は JEDEC のパッケージ外形 M0-220 のバリエーション(WHHD-(X))に含めるよう提案されている(承認待ち)

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのパリを含まない。モールドのパリは(もしあれば)各サイドで 0.20mm を超えないこと

5. 露出パッドは半田メッキとする

6. 灰色の部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

# LTC2253/LTC2252

## 関連製品

| 製品番号      | 概要                               | 注釈                                                                |

|-----------|----------------------------------|-------------------------------------------------------------------|

| LTC1747   | 12ビット、80Msps ADC                 | SNR:72dB、SFDR:87dB、48ピンTSSOPパッケージ                                 |

| LTC1748   | 14ビット、80Msps ADC                 | SNR:76.3dB、SFDR:90dB、48ピンTSSOPパッケージ                               |

| LTC1749   | 12ビット、80Msps、広帯域ADC              | 最大500MHzのIFアンダーサンプリング、SFDR:87dB                                   |

| LTC1750   | 14ビット、80Msps、広帯域ADC              | 最大500MHzのIFアンダーサンプリング、SFDR:90dB                                   |

| LT1993    | 高速差動オペアンプ                        | BW:600MHz、歪み:75dBc(70MHz)                                         |

| LTC2220   | 12ビット、170Msps ADC                | 890mW、SNR:67.5dB、9mm×9mm QFNパッケージ                                 |

| LTC2220-1 | 12ビット、185Msps ADC                | 910mW、SNR:67.5dB、9mm×9mm QFNパッケージ                                 |

| LTC2221   | 12ビット、135Msps ADC                | 660mW、SNR:67.5dB、9mm×9mm QFNパッケージ                                 |

| LTC2222   | 12ビット、105Msps ADC                | 475mW、SNR:67.9dB、7mm×7mm QFNパッケージ                                 |

| LTC2223   | 12ビット、80Msps ADC                 | 366mW、SNR:68dB、7mm×7mm QFNパッケージ                                   |

| LTC2224   | 12ビット、135Msps ADC                | 660mW、SNR:67.5dB、7mm×7mm QFNパッケージ                                 |

| LTC2225   | 12ビット、10Msps ADC                 | 60mW、SNR:71.4dB、5mm×5mm QFNパッケージ                                  |

| LTC2228   | 12ビット、65Msps ADC                 | 210mW、SNR:71dB、5mm×5mm QFNパッケージ                                   |

| LTC2229   | 12ビット、80Msps ADC                 | 230mW、SNR:71.6dB、5mm×5mm QFNパッケージ                                 |

| LTC2248   | 14ビット、65Msps ADC                 | 210mW、SNR:74dB、5mm×5mm QFNパッケージ                                   |

| LTC2249   | 14ビット、80Msps ADC                 | 230mW、SNR:73dB、5mm×5mm QFNパッケージ                                   |

| LTC2250   | 10ビット、105Msps ADC                | 320mW、SNR:61.6dB、5mm×5mm QFNパッケージ                                 |

| LTC2251   | 10ビット、125Msps ADC                | 395mW、SNR:61.6dB、5mm×5mm QFNパッケージ                                 |

| LTC2254   | 14ビット、105Msps ADC                | 320mW、SNR:72.5dB、5mm×5mm QFNパッケージ                                 |

| LTC2255   | 14ビット、125Msps ADC                | 395mW、SNR:72.4dB、5mm×5mm QFNパッケージ                                 |

| LTC2292   | デュアル12ビット、40Msps ADC             | 240mW、SNR:71dB、9mm×9mm QFNパッケージ                                   |

| LTC2293   | デュアル12ビット、65Msps ADC             | 410mW、SNR:71dB、9mm×9mm QFNパッケージ                                   |

| LTC2294   | デュアル12ビット、80Msps ADC             | 445mW、SNR:70.6dB、9mm×9mm QFNパッケージ                                 |

| LTC2297   | デュアル14ビット、40Msps ADC             | 240mW、SNR:74dB、9mm×9mm QFNパッケージ                                   |

| LTC2298   | デュアル14ビット、65Msps ADC             | 410mW、SNR:74dB、9mm×9mm QFNパッケージ                                   |

| LTC2299   | デュアル14ビット、80Msps ADC             | 445mW、SNR:73dB、9mm×9mm QFNパッケージ                                   |

| LT5512    | DC～3GHz高信号レベル・ダウンコンバーティング・ミキサ    | DC～3GHz、IIP3:21dBm、LOバッファ内蔵                                       |

| LT5514    | デジタル利得制御付き超低歪みIFアンプ/ADCドライバ      | 1dB BW:450MHz、OIP3:47dB、デジタル利得制御:1.5dB/ステップで10.5dB～33dB           |

| LT5522    | 600MHz～2.7GHz高直線性ダウンコンバーティング・ミキサ | 4.5V～5.25V電源、IIP3:900MHzで25dBm、NF = 12.5dB、50ΩシングルエンドのRFポートとLOポート |

22532fa