## 特長

- 2チャネル同時サンプリングADC

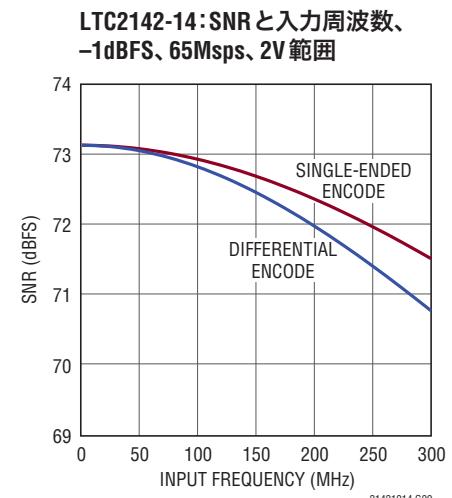

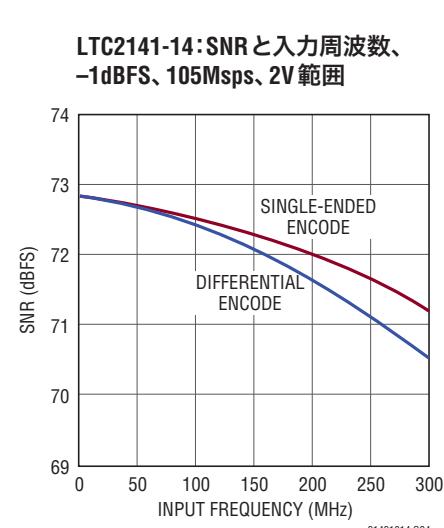

- SNR:73.2dB

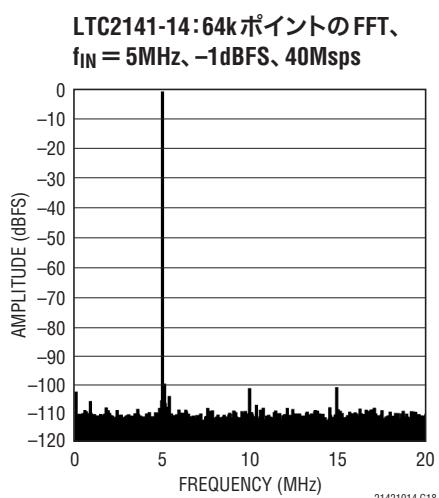

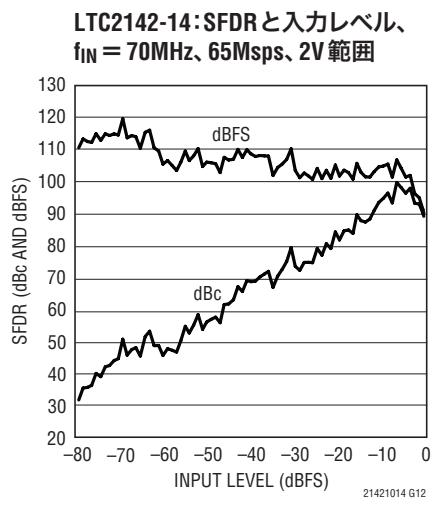

- SFDR:90dB

- 低消費電力:95mW/67mW/50mW(合計)、

48mW/34mW/25mW(チャネル当たり)

- 単一1.8V電源

- CMOS、DDR CMOSまたはDDR LVDS出力

- 選択可能な入力範囲:1V<sub>P-P</sub>~2V<sub>P-P</sub>

- 750MHzのフルパワー帯域幅サンプル/ホールド

- オプションのデータ出力ランダマイザ

- オプションのクロック・デューティ・サイクル・スタビライザ

- スリープ・モードとナップ・モード

- 設定用のシリアルSPIポート

- 64ピン(9mm×9mm)QFNパッケージ

## アプリケーション

- 通信

- セルラー基地局

- ソフトウェア無線

- 携帯型の医療用画像処理

- マルチチャネル・データ収集

- 非破壊試験

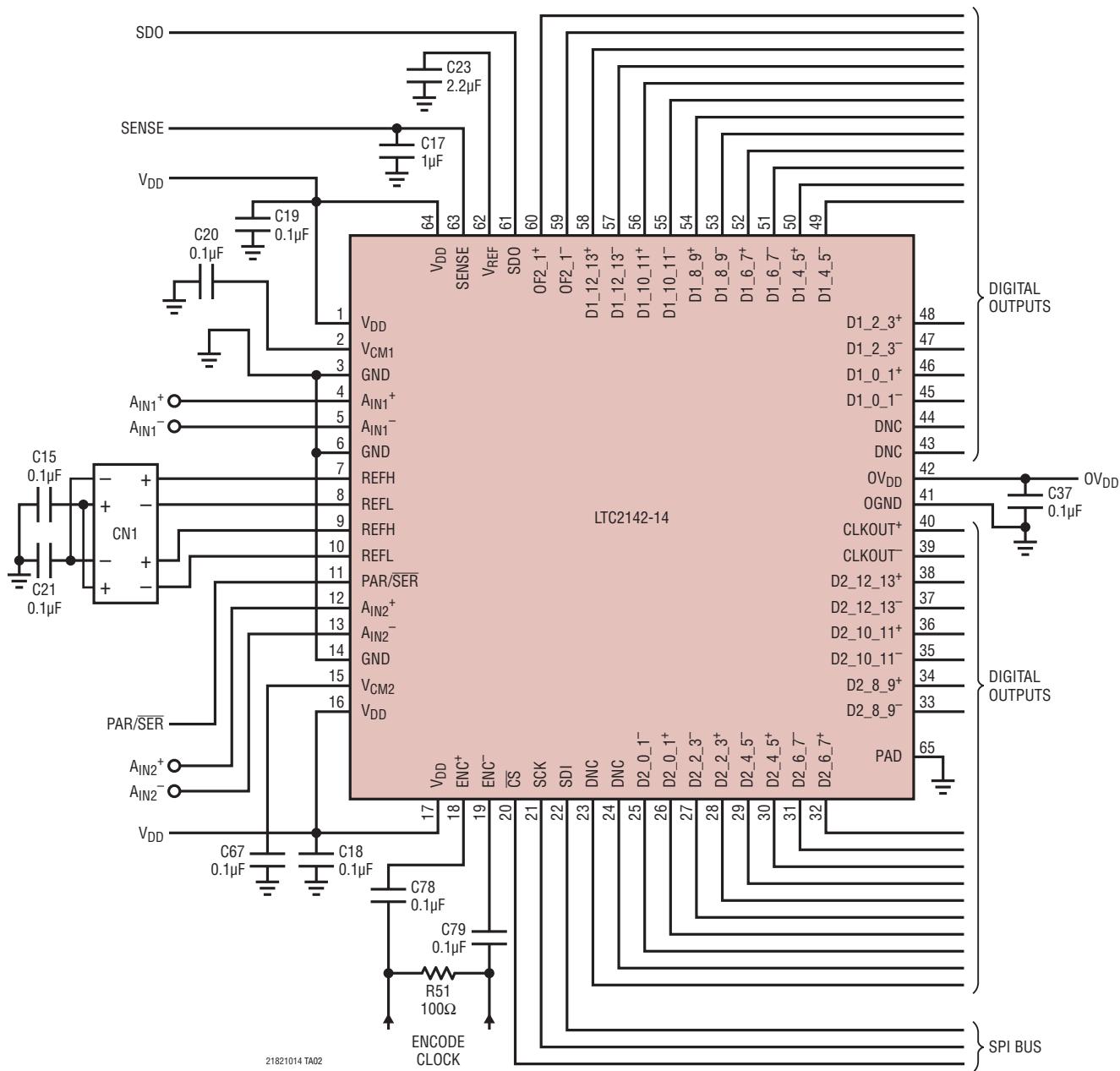

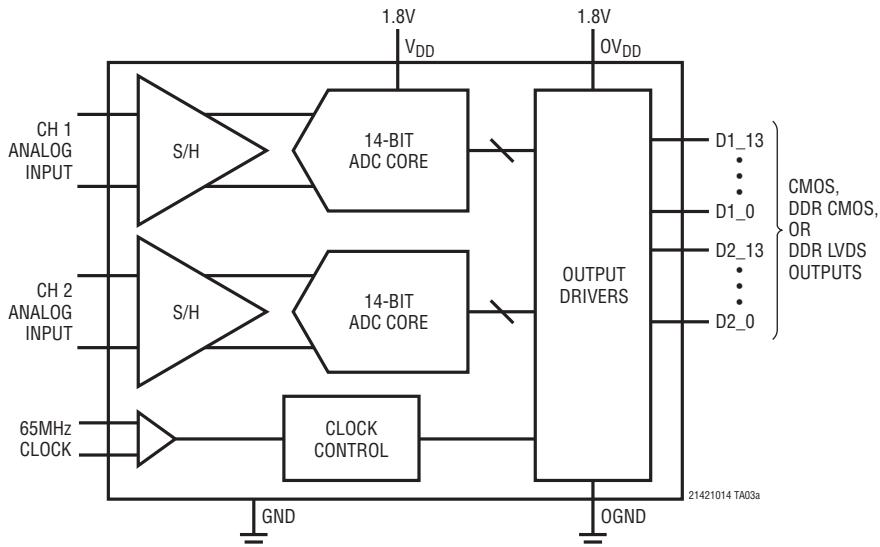

## 標準的応用例

## 概要

LTC®2142-14/LTC2141-14/LTC2140-14は、広いダイナミック・レンジの高周波信号をデジタル化する2チャネル同時サンプリング14ビットA/Dコンバータです。SNRが73.2dB、SFDRが90dBという優れたAC特性を備えているため、要求の厳しい通信アプリケーションに最適です。また、ジッタがわずか0.08psRMSなので、優れたノイズ性能を維持しながらIF周波数をアンダーサンプリングできます。

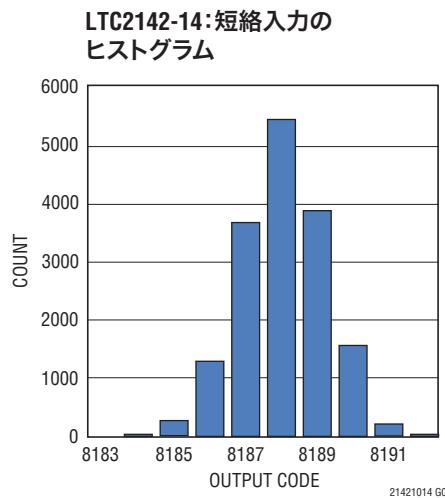

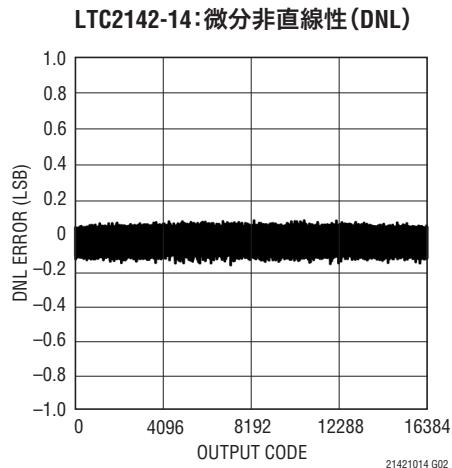

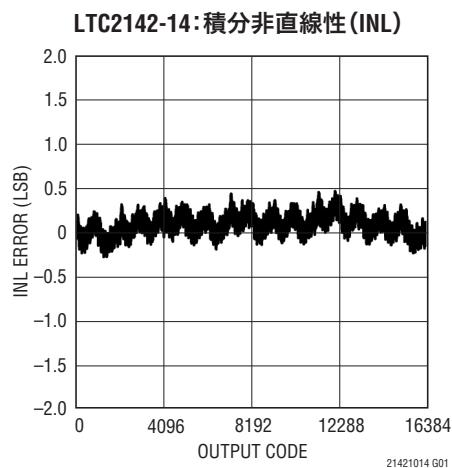

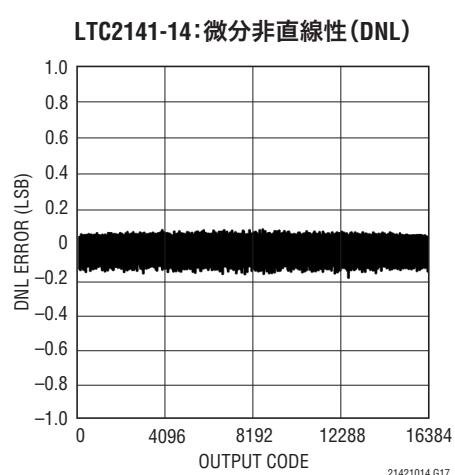

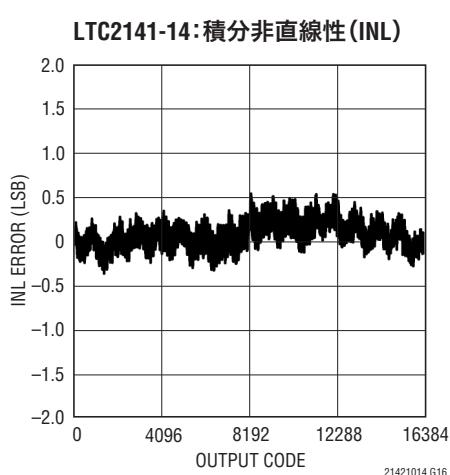

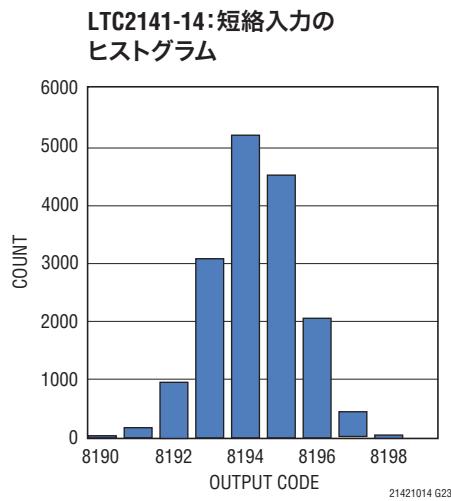

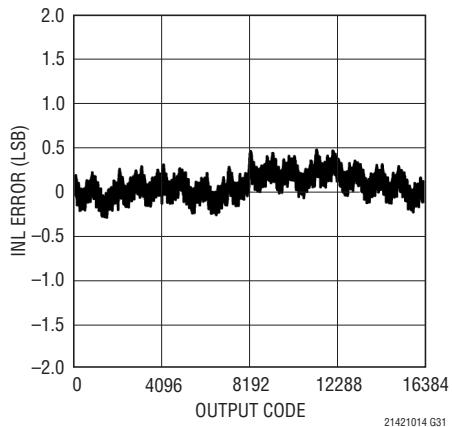

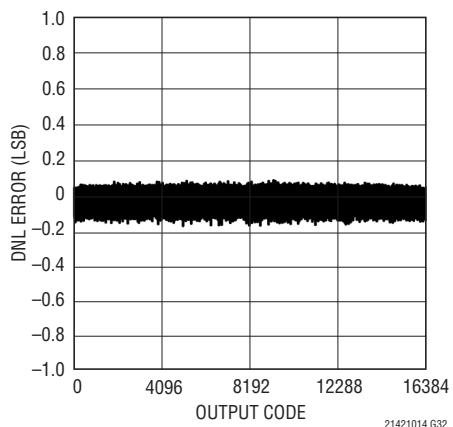

DC仕様では、±1LSB(標準)INL、±0.3LSB(標準)のDNL、およびミッシング・コードがないことが全温度範囲で規定されています。遷移ノイズは1.2LSBRMSです。

デジタル出力は、フルレートCMOS、ダブルデータレートCMOS、ダブルデータレートLVDSのいずれかに設定可能です。独立した出力電源により、1.2V~1.8VのCMOS出力振幅が可能です。

ENC+およびENC-入力は、正弦波、PECL、LVDS、TTL、またはCMOS入力により、差動またはシングルエンドでドライブできます。また、オプションのクロック・デューティ・サイクル・スタビライザにより、広範なクロック・デューティ・サイクルにおいてフルスピードで高性能を実現できます。

**LT**、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴは、リニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

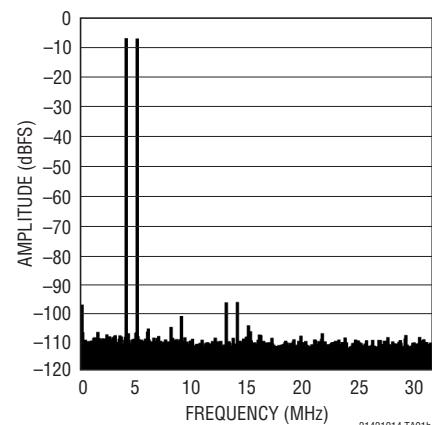

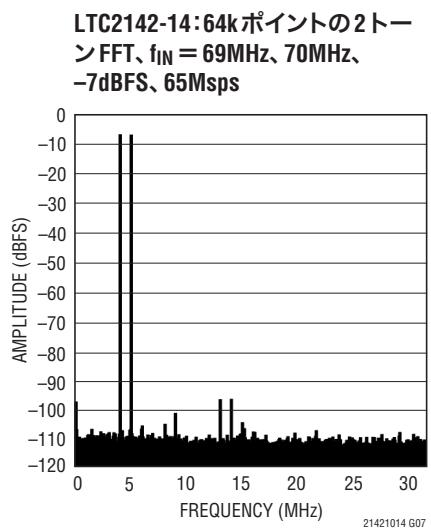

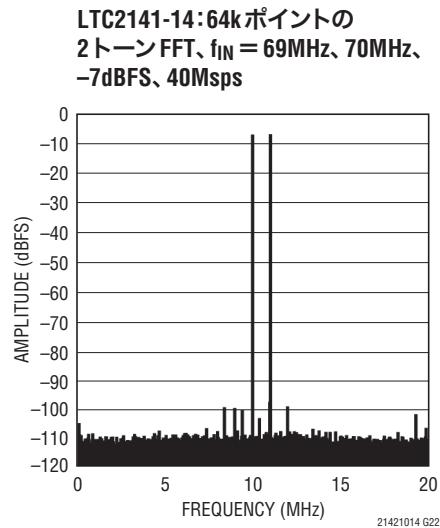

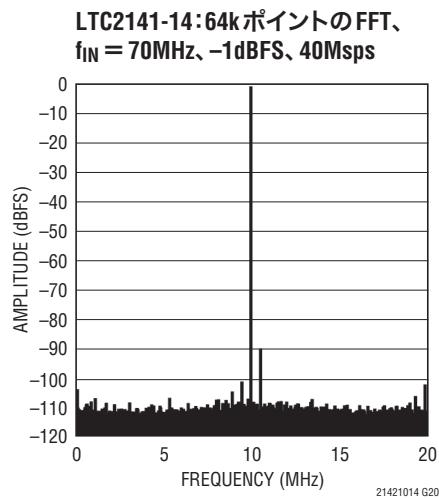

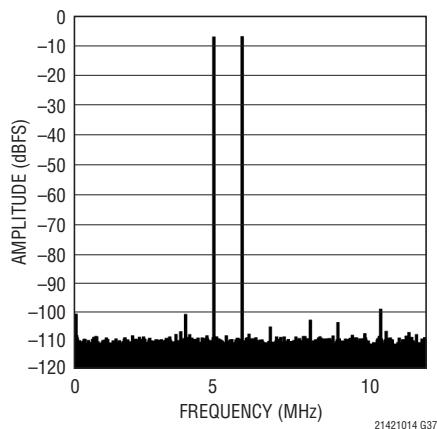

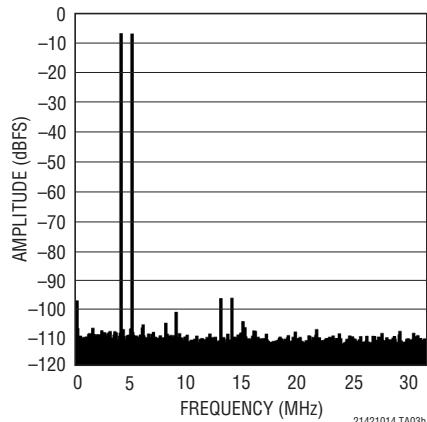

2トーンFFT、f<sub>IN</sub> = 70MHzおよび69MHz

# LTC2142-14/ LTC2141-14/LTC2140-14

## 絶対最大定格 (Note 1, 2)

|                                                                           |                            |

|---------------------------------------------------------------------------|----------------------------|

| 電源電圧 ( $V_{DD}$ , $0V_{DD}$ )                                             | -0.3V ~ 2V                 |

| アナログ入力電圧 ( $A_{IN}^+$ , $A_{IN}^-$ ,<br>PAR/SER, SENSE) (Note 3)          | -0.3V ~ ( $V_{DD}$ + 0.2V) |

| デジタル入力電圧 (ENC <sup>+</sup> , ENC <sup>-</sup> ,<br>CS, SDI, SCK) (Note 4) | -0.3V ~ 3.9V               |

| SDO (Note 4)                                                              | -0.3V ~ 3.9V               |

|                              |                             |

|------------------------------|-----------------------------|

| デジタル出力電圧                     | -0.3V ~ ( $0V_{DD}$ + 0.3V) |

| 動作温度範囲                       | 0°C ~ 70°C                  |

| LTC2142C, LTC2141C, LTC2140C | 0°C ~ 70°C                  |

| LTC2142I, LTC2141I, LTC2140I | -40°C ~ 85°C                |

| 保存温度範囲                       | -65°C ~ 150°C               |

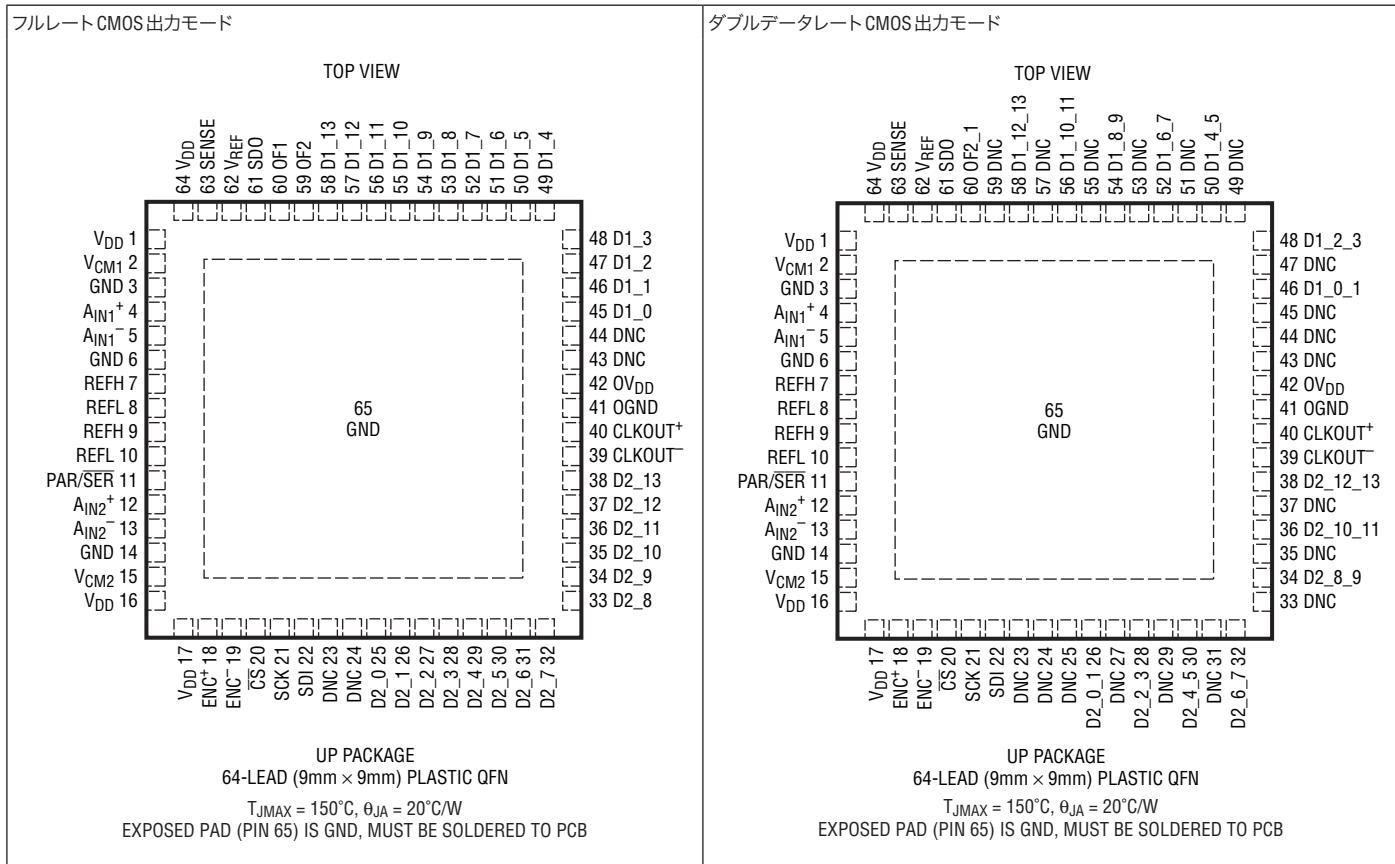

## ピン配置

21421014fa

## ピン配置

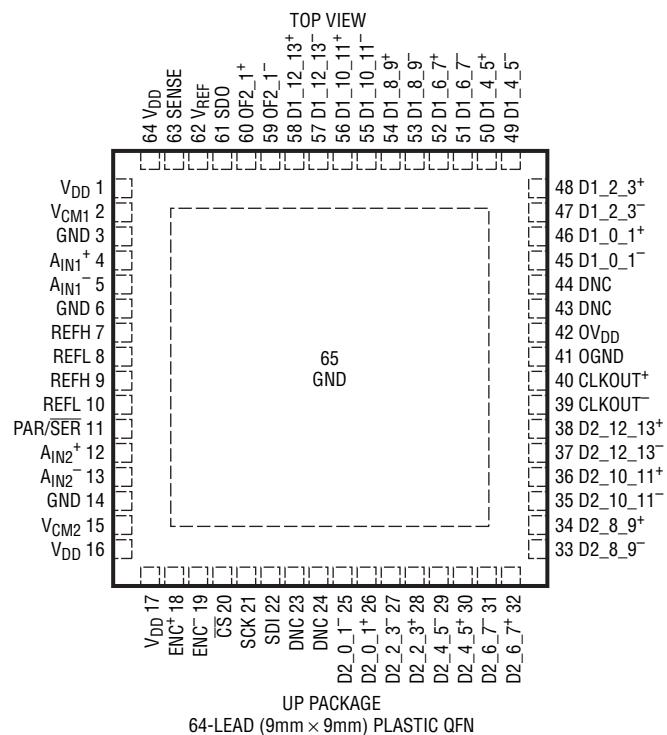

ダブルデータレートLVDS出力モード

T<sub>JMAX</sub> = 150°C, θ<sub>JA</sub> = 20°C/W

EXPOSED PAD (PIN 65) IS GND, MUST BE SOLDERED TO PCB

## 発注情報

| 無鉛仕上げ             | テープアンドリール           | 製品マーキング*     | パッケージ                           | 温度範囲          |

|-------------------|---------------------|--------------|---------------------------------|---------------|

| LTC2142CUP-14#PBF | LTC2142CUP-14#TRPBF | LTC2142UP-14 | 64-Lead (9mm × 9mm) Plastic QFN | 0°C to 70°C   |

| LTC2142IUP-14#PBF | LTC2142IUP-14#TRPBF | LTC2142UP-14 | 64-Lead (9mm × 9mm) Plastic QFN | -40°C to 85°C |

| LTC2141CUP-14#PBF | LTC2141CUP-14#TRPBF | LTC2141UP-14 | 64-Lead (9mm × 9mm) Plastic QFN | 0°C to 70°C   |

| LTC2141IUP-14#PBF | LTC2141IUP-14#TRPBF | LTC2141UP-14 | 64-Lead (9mm × 9mm) Plastic QFN | -40°C to 85°C |

| LTC2140CUP-14#PBF | LTC2140CUP-14#TRPBF | LTC2140UP-14 | 64-Lead (9mm × 9mm) Plastic QFN | 0°C to 70°C   |

| LTC2140IUP-14#PBF | LTC2140IUP-14#TRPBF | LTC2140UP-14 | 64-Lead (9mm × 9mm) Plastic QFN | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社へお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/designtools/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

# LTC2142-14/ LTC2141-14/LTC2140-14

コンバータ特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5)。

| PARAMETER                     | CONDITIONS                               | LTC2142-14 |      |           | LTC2141-14 |      |           | LTC2140-14 |      |           | UNITS |                                                            |

|-------------------------------|------------------------------------------|------------|------|-----------|------------|------|-----------|------------|------|-----------|-------|------------------------------------------------------------|

|                               |                                          | MIN        | TYP  | MAX       | MIN        | TYP  | MAX       | MIN        | TYP  | MAX       |       |                                                            |

| Resolution (No Missing Codes) |                                          | ●          | 14   |           | 14         |      |           | 14         |      |           | Bits  |                                                            |

| Integral Linearity Error      | Differential Analog Input (Note 6)       | ●          | -2.4 | $\pm 1$   | 2.4        | -2.4 | $\pm 1$   | 2.4        | -2.4 | $\pm 1$   | 2.4   | LSB                                                        |

| Differential Linearity Error  | Differential Analog Input                | ●          | -0.8 | $\pm 0.3$ | 0.8        | -0.8 | $\pm 0.3$ | 0.8        | -0.8 | $\pm 0.3$ | 0.8   | LSB                                                        |

| Offset Error                  | (Note 7)                                 | ●          | -9   | $\pm 1.5$ | 9          | -9   | $\pm 1.5$ | 9          | -9   | $\pm 1.5$ | 9     | mV                                                         |

| Gain Error                    | Internal Reference<br>External Reference | ●          |      | $\pm 1.5$ |            |      | $\pm 1.5$ |            |      | $\pm 1.5$ |       | %FS<br>%FS                                                 |

| Offset Drift                  |                                          |            |      | $\pm 10$  |            |      | $\pm 10$  |            |      | $\pm 10$  |       | $\mu\text{V}/^\circ\text{C}$                               |

| Full-Scale Drift              | Internal Reference<br>External Reference |            |      | $\pm 30$  |            |      | $\pm 30$  |            |      | $\pm 30$  |       | $\text{ppm}/^\circ\text{C}$<br>$\text{ppm}/^\circ\text{C}$ |

|                               |                                          |            |      | $\pm 10$  |            |      | $\pm 10$  |            |      | $\pm 10$  |       |                                                            |

| Gain Matching                 |                                          |            |      | $\pm 0.2$ |            |      | $\pm 0.2$ |            |      | $\pm 0.2$ |       | %FS                                                        |

| Offset Matching               |                                          |            |      | $\pm 1.5$ |            |      | $\pm 1.5$ |            |      | $\pm 1.5$ |       | mV                                                         |

| Transition Noise              |                                          |            |      | 1.23      |            |      | 1.31      |            |      | 1.19      |       | LSBRMS                                                     |

アナログ入力 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5)。

| SYMBOL       | PARAMETER                                            | CONDITIONS                                            | MIN | TYP   | MAX            | UNITS                                           |   |

|--------------|------------------------------------------------------|-------------------------------------------------------|-----|-------|----------------|-------------------------------------------------|---|

| $V_{IN}$     | Analog Input Range ( $A_{IN}^+ - A_{IN}^-$ )         | $1.7\text{V} < V_{DD} < 1.9\text{V}$                  | ●   |       | 1 to 2         | $V_{P-P}$                                       |   |

| $V_{IN(CM)}$ | Analog Input Common Mode ( $A_{IN}^+ + A_{IN}^-$ )/2 | Differential Analog Input (Note 8)                    | ●   | 0.7   | $V_{CM}$       | 1.25                                            | V |

| $V_{SENSE}$  | External Voltage Reference Applied to SENSE          | External Reference Mode                               | ●   | 0.625 | 1.250          | 1.300                                           | V |

| $I_{INCM}$   | Analog Input Common Mode Current                     | Per Pin, 65Msps<br>Per Pin, 40Msps<br>Per Pin, 25Msps |     |       | 81<br>50<br>31 | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |   |

| $I_{IN1}$    | Analog Input Leakage Current (No Encode)             | $0 < A_{IN}^+, A_{IN}^- < V_{DD}$                     | ●   | -1.5  | 1.5            | $\mu\text{A}$                                   |   |

| $I_{IN2}$    | PAR/SER Input Leakage Current                        | $0 < PAR/\bar{SER} < V_{DD}$                          | ●   | -3    | 3              | $\mu\text{A}$                                   |   |

| $I_{IN3}$    | SENSE Input Leakage Current                          | $0.625 < SENSE < 1.3\text{V}$                         | ●   | -3    | 3              | $\mu\text{A}$                                   |   |

| $t_{AP}$     | Sample-and-Hold Acquisition Delay Time               |                                                       |     |       | 0              | ns                                              |   |

| $t_{JITTER}$ | Sample-and-Hold Acquisition Delay Jitter             | Single-Ended Encode<br>Differential Encode            |     |       | 0.08<br>0.10   | $\text{psRMS}$<br>$\text{psRMS}$                |   |

| CMRR         | Analog Input Common Mode Rejection Ratio             |                                                       |     |       | 80             | dB                                              |   |

| BW-3B        | Full-Power Bandwidth                                 | Figure 6 Test Circuit                                 |     |       | 750            | MHz                                             |   |

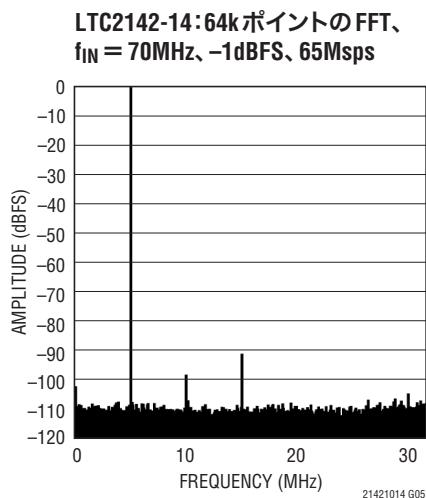

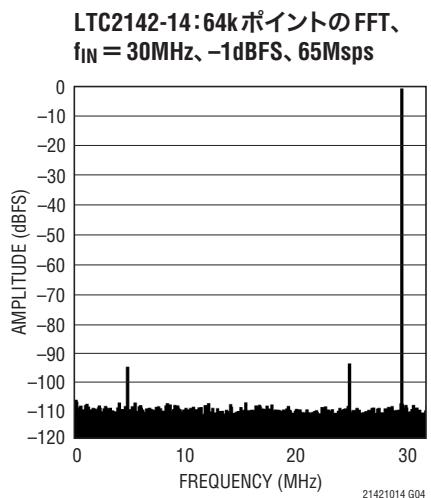

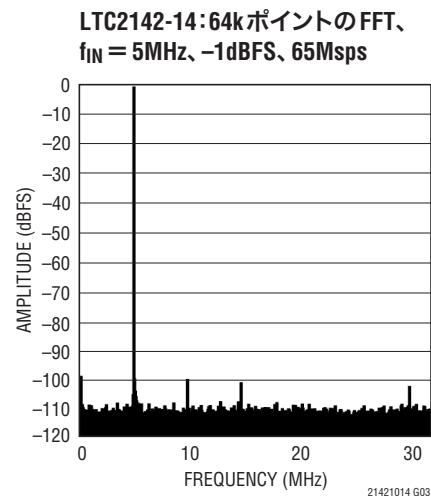

**ダイナミック精度** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ (Note 5)。

| SYMBOL  | PARAMETER                                             | CONDITIONS                                               | LTC2142-14 |                              |                              | LTC2141-14 |                              |                              | LTC2140-14                   |                              |                              | UNITS |

|---------|-------------------------------------------------------|----------------------------------------------------------|------------|------------------------------|------------------------------|------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|-------|

|         |                                                       |                                                          | MIN        | TYP                          | MAX                          | MIN        | TYP                          | MAX                          | MIN                          | TYP                          | MAX                          |       |

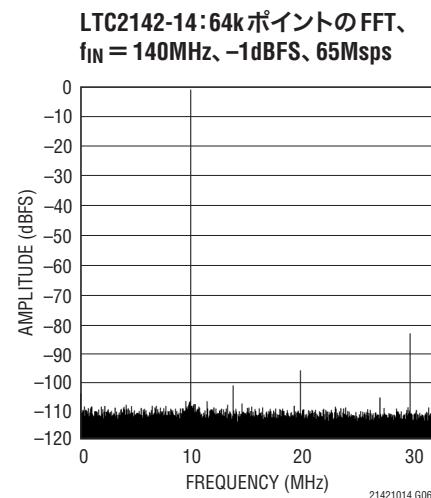

| SNR     | Signal-to-Noise Ratio                                 | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | ● 71.8     | 73.2<br>73.2<br>73.1<br>72.7 | 72.8<br>72.8<br>72.7<br>72.4 | 71.5       | 72.8<br>72.8<br>72.7<br>72.4 | 72.8<br>72.7<br>73.6<br>73.2 | 73.7<br>73.7<br>73.6<br>73.2 | 73.7<br>73.7<br>73.6<br>73.2 | dBFS<br>dBFS<br>dBFS<br>dBFS |       |

| SFDR    | Spurious Free Dynamic Range<br>2nd Harmonic           | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | ● 79       | 90<br>90<br>89<br>84         | 90<br>90<br>89<br>84         | 81         | 90<br>90<br>89<br>84         | 90<br>90<br>89<br>84         | 90<br>90<br>89<br>84         | 90<br>90<br>89<br>84         | dBFS<br>dBFS<br>dBFS<br>dBFS |       |

|         | Spurious Free Dynamic Range<br>3rd Harmonic           | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | ● 82       | 90<br>90<br>89<br>84         | 90<br>90<br>89<br>84         | 82         | 90<br>90<br>89<br>84         | 90<br>90<br>89<br>84         | 90<br>90<br>89<br>84         | 90<br>90<br>89<br>84         | dBFS<br>dBFS<br>dBFS<br>dBFS |       |

|         | Spurious Free Dynamic Range<br>4th Harmonic or Higher | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | ● 86       | 95<br>95<br>95<br>95         | 95<br>95<br>95<br>95         | 86         | 95<br>95<br>95<br>95         | 95<br>95<br>95<br>95         | 95<br>95<br>95<br>95         | 95<br>95<br>95<br>95         | dBFS<br>dBFS<br>dBFS<br>dBFS |       |

| S/(N+D) | Signal-to-Noise Plus Distortion<br>Ratio              | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | ● 71.5     | 73.1<br>73.1<br>72.9<br>72.2 | 72.7<br>72.7<br>72.5<br>72   | 71.1       | 72.7<br>72.7<br>72.5<br>72   | 72.7<br>72.7<br>72.5<br>72   | 73.5<br>73.5<br>73.4<br>72.7 | 73.5<br>73.5<br>73.4<br>72.7 | dBFS<br>dBFS<br>dBFS<br>dBFS |       |

|         | Crosstalk                                             | 10MHz Input                                              |            | -110                         | -110                         |            | -110                         | -110                         | -110                         | -110                         | dBc                          |       |

**内部リファレンスの特性** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5)。

| PARAMETER                          | CONDITIONS                               | MIN                              | TYP                | MAX                              | UNITS                       |

|------------------------------------|------------------------------------------|----------------------------------|--------------------|----------------------------------|-----------------------------|

| $V_{CM}$ Output Voltage            | $I_{OUT} = 0$                            | $0.5 \cdot V_{DD} - 25\text{mV}$ | $0.5 \cdot V_{DD}$ | $0.5 \cdot V_{DD} + 25\text{mV}$ | V                           |

| $V_{CM}$ Output Temperature Drift  |                                          |                                  | $\pm 25$           |                                  | $\text{ppm}/^\circ\text{C}$ |

| $V_{CM}$ Output Resistance         | $-600\mu\text{A} < I_{OUT} < 1\text{mA}$ |                                  | 4                  |                                  | $\Omega$                    |

| $V_{REF}$ Output Voltage           | $I_{OUT} = 0$                            | 1.225                            | 1.250              | 1.275                            | V                           |

| $V_{REF}$ Output Temperature Drift |                                          |                                  | $\pm 25$           |                                  | $\text{ppm}/^\circ\text{C}$ |

| $V_{REF}$ Output Resistance        | $-400\mu\text{A} < I_{OUT} < 1\text{mA}$ |                                  | 7                  |                                  | $\Omega$                    |

| $V_{REF}$ Line Regulation          | $1.7\text{V} < V_{DD} < 1.9\text{V}$     |                                  | 0.6                |                                  | $\text{mV/V}$               |

# LTC2142-14/ LTC2141-14/LTC2140-14

デジタル入力とデジタル出力 ●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 5)。

| SYMBOL                                                          | PARAMETER                          | CONDITIONS                                                                | MIN | TYP        | MAX            | UNITS    |

|-----------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|-----|------------|----------------|----------|

| エンコード入力(ENC <sup>+</sup> 、ENC <sup>-</sup> )                    |                                    |                                                                           |     |            |                |          |

| 差動エンコード・モード(ENC <sup>-</sup> はGNDに接続されていない)                     |                                    |                                                                           |     |            |                |          |

| V <sub>ID</sub>                                                 | Differential Input Voltage         | (Note 8)                                                                  | ●   | 0.2        |                | V        |

| V <sub>ICM</sub>                                                | Common Mode Input Voltage          | Internally Set<br>Externally Set (Note 8)                                 | ●   | 1.1        | 1.2<br>1.6     | V        |

| V <sub>IN</sub>                                                 | Input Voltage Range                | ENC <sup>+</sup> , ENC <sup>-</sup> to GND                                | ●   | 0.2        | 3.6            | V        |

| R <sub>IN</sub>                                                 | Input Resistance                   | (See Figure 10)                                                           |     | 10         |                | kΩ       |

| C <sub>IN</sub>                                                 | Input Capacitance                  | (Note 8)                                                                  |     | 3.5        |                | pF       |

| シングルエンド・エンコード・モード(ENC <sup>-</sup> はGNDに接続されている)                |                                    |                                                                           |     |            |                |          |

| V <sub>IH</sub>                                                 | High Level Input Voltage           | V <sub>DD</sub> = 1.8V                                                    | ●   | 1.2        |                | V        |

| V <sub>IL</sub>                                                 | Low Level Input Voltage            | V <sub>DD</sub> = 1.8V                                                    | ●   |            | 0.6            | V        |

| V <sub>IN</sub>                                                 | Input Voltage Range                | ENC <sup>+</sup> to GND                                                   | ●   | 0          | 3.6            | V        |

| R <sub>IN</sub>                                                 | Input Resistance                   | (See Figure 11)                                                           |     | 30         |                | kΩ       |

| C <sub>IN</sub>                                                 | Input Capacitance                  | (Note 8)                                                                  |     | 3.5        |                | pF       |

| デジタル入力(CS、SDI、SCKはシリアルまたはパラレル・プログラミング・モード。SDOはパラレル・プログラミング・モード) |                                    |                                                                           |     |            |                |          |

| V <sub>IH</sub>                                                 | High Level Input Voltage           | V <sub>DD</sub> = 1.8V                                                    | ●   | 1.3        |                | V        |

| V <sub>IL</sub>                                                 | Low Level Input Voltage            | V <sub>DD</sub> = 1.8V                                                    | ●   |            | 0.6            | V        |

| I <sub>IN</sub>                                                 | Input Current                      | V <sub>IN</sub> = 0V to 3.6V                                              | ●   | -10        | 10             | μA       |

| C <sub>IN</sub>                                                 | Input Capacitance                  | (Note 8)                                                                  |     | 3          |                | pF       |

| SDOの出力(シリアル・プログラミング・モード。オープン・ドレイン出力。SDOを使用する場合は2kΩのプルアップ抵抗が必要)  |                                    |                                                                           |     |            |                |          |

| R <sub>OL</sub>                                                 | Logic Low Output Resistance to GND | V <sub>DD</sub> = 1.8V, SDO = 0V                                          |     |            | 200            | Ω        |

| I <sub>OH</sub>                                                 | Logic High Output Leakage Current  | SDO = 0V to 3.6V                                                          | ●   | -10        | 10             | μA       |

| C <sub>OUT</sub>                                                | Output Capacitance                 | (Note 8)                                                                  |     | 3          |                | pF       |

| デジタル・データ出力(CMOSモード:フルデータレートとダブルデータレート)                          |                                    |                                                                           |     |            |                |          |

| <b>OV<sub>DD</sub> = 1.8V</b>                                   |                                    |                                                                           |     |            |                |          |

| V <sub>OH</sub>                                                 | High Level Output Voltage          | I <sub>O</sub> = -500μA                                                   | ●   | 1.750      | 1.790          | V        |

| V <sub>OL</sub>                                                 | Low Level Output Voltage           | I <sub>O</sub> = 500μA                                                    | ●   | 0.010      | 0.050          | V        |

| <b>OV<sub>DD</sub> = 1.5V</b>                                   |                                    |                                                                           |     |            |                |          |

| V <sub>OH</sub>                                                 | High Level Output Voltage          | I <sub>O</sub> = -500μA                                                   |     |            | 1.488          | V        |

| V <sub>OL</sub>                                                 | Low Level Output Voltage           | I <sub>O</sub> = 500μA                                                    |     |            | 0.010          | V        |

| <b>OV<sub>DD</sub> = 1.2V</b>                                   |                                    |                                                                           |     |            |                |          |

| V <sub>OH</sub>                                                 | High Level Output Voltage          | I <sub>O</sub> = -500μA                                                   |     |            | 1.185          | V        |

| V <sub>OL</sub>                                                 | Low Level Output Voltage           | I <sub>O</sub> = 500μA                                                    |     |            | 0.010          | V        |

| デジタル・データ出力(LVDSモード)                                             |                                    |                                                                           |     |            |                |          |

| V <sub>OD</sub>                                                 | Differential Output Voltage        | 100Ω Differential Load, 3.5mA Mode<br>100Ω Differential Load, 1.75mA Mode | ●   | 247<br>175 | 350<br>175     | mV<br>mV |

| V <sub>OS</sub>                                                 | Common Mode Output Voltage         | 100Ω Differential Load, 3.5mA Mode<br>100Ω Differential Load, 1.75mA Mode | ●   | 1.125      | 1.250<br>1.250 | V<br>V   |

| R <sub>TERM</sub>                                               | On-Chip Termination Resistance     | Termination Enabled, OV <sub>DD</sub> = 1.8V                              |     |            | 100            | Ω        |

**電源要件** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 9)。

| SYMBOL                              | PARAMETER                                                                                    | CONDITIONS                                           | LTC2142-14 |               |     | LTC2141-14 |              |     | LTC2140-14 |              |     | UNITS    |   |

|-------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------|------------|---------------|-----|------------|--------------|-----|------------|--------------|-----|----------|---|

|                                     |                                                                                              |                                                      | MIN        | TYP           | MAX | MIN        | TYP          | MAX | MIN        | TYP          | MAX |          |   |

| <b>CMOS出力モード:フルデータレートとダブルデータレート</b> |                                                                                              |                                                      |            |               |     |            |              |     |            |              |     |          |   |

| V <sub>DD</sub>                     | Analog Supply Voltage                                                                        | (Note 10)                                            | ●          | 1.7           | 1.8 | 1.9        | 1.7          | 1.8 | 1.9        | 1.7          | 1.8 | 1.9      | V |

| OV <sub>DD</sub>                    | Output Supply Voltage                                                                        | (Note 10)                                            | ●          | 1.1           | 1.8 | 1.9        | 1.1          | 1.8 | 1.9        | 1.1          | 1.8 | 1.9      | V |

| I <sub>VDD</sub>                    | Analog Supply Current                                                                        | DC Input<br>Sine Wave Input                          | ●          | 52.7<br>53    | 59  |            | 37.1<br>37.3 | 42  |            | 27.9<br>28.1 | 33  | mA<br>mA |   |

| I <sub>OVDD</sub>                   | Digital Supply Current                                                                       | Sine Wave Input, OV <sub>DD</sub> = 1.2V             |            | 4.4           |     |            | 2.7          |     |            | 1.7          |     | mA       |   |

| P <sub>DISS</sub>                   | Power Dissipation                                                                            | DC Input<br>Sine Wave Input, OV <sub>DD</sub> = 1.2V | ●          | 94.9<br>100.7 | 107 |            | 66.8<br>70.4 | 76  |            | 50.2<br>52.6 | 60  | mW<br>mW |   |

| <b>LVDS出力モード</b>                    |                                                                                              |                                                      |            |               |     |            |              |     |            |              |     |          |   |

| V <sub>DD</sub>                     | Analog Supply Voltage                                                                        | (Note 10)                                            | ●          | 1.7           | 1.8 | 1.9        | 1.7          | 1.8 | 1.9        | 1.7          | 1.8 | 1.9      | V |

| OV <sub>DD</sub>                    | Output Supply Voltage                                                                        | (Note 10)                                            | ●          | 1.7           | 1.8 | 1.9        | 1.7          | 1.8 | 1.9        | 1.7          | 1.8 | 1.9      | V |

| I <sub>VDD</sub>                    | Analog Supply Current                                                                        | Sine Input, 1.75mA Mode<br>Sine Input, 3.5mA Mode    | ●          | 54.4<br>55.8  | 63  |            | 38.7<br>40.2 | 46  |            | 29.5<br>30.9 | 37  | mA<br>mA |   |

| I <sub>OVDD</sub>                   | Digital Supply Current<br>(OV <sub>DD</sub> = 1.8V)                                          | Sine Input, 1.75mA Mode<br>Sine Input, 3.5mA Mode    | ●          | 34.3<br>65.7  | 75  |            | 33.9<br>65.3 | 75  |            | 33.7<br>65.1 | 75  | mA<br>mA |   |

| P <sub>DISS</sub>                   | Power Dissipation                                                                            | Sine Input, 1.75mA Mode<br>Sine Input, 3.5mA Mode    | ●          | 160<br>219    | 249 |            | 131<br>190   | 218 |            | 114<br>173   | 202 | mW<br>mW |   |

| <b>すべての出力モード</b>                    |                                                                                              |                                                      |            |               |     |            |              |     |            |              |     |          |   |

| P <sub>SLEEP</sub>                  | Sleep Mode Power                                                                             |                                                      |            | 1             |     |            | 1            |     |            | 1            |     | mW       |   |

| P <sub>NAP</sub>                    | Nap Mode Power                                                                               |                                                      |            | 10            |     |            | 10           |     |            | 10           |     | mW       |   |

| P <sub>DIFFCLK</sub>                | Power Increase with Differential Encode Mode Enabled<br>(No Increase for Nap or Sleep Modes) |                                                      |            | 20            |     |            | 20           |     |            | 20           |     | mW       |   |

**タイミング特性** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5)。

| SYMBOL                                         | PARAMETER                                 | CONDITIONS                                            | LTC2142-14 |          |              | LTC2141-14 |            |              | LTC2140-14 |         |          | UNITS            |          |

|------------------------------------------------|-------------------------------------------|-------------------------------------------------------|------------|----------|--------------|------------|------------|--------------|------------|---------|----------|------------------|----------|

|                                                |                                           |                                                       | MIN        | TYP      | MAX          | MIN        | TYP        | MAX          | MIN        | TYP     | MAX      |                  |          |

| f <sub>s</sub>                                 | Sampling Frequency                        | (Note 10)                                             | ●          | 1        | 65           | 1          |            | 40           | 1          |         | 25       | MHz              |          |

| t <sub>L</sub>                                 | ENC Low Time (Note 8)                     | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On | ●<br>●     | 7.3<br>2 | 7.69<br>7.69 | 500<br>500 | 11.88<br>2 | 12.5<br>12.5 | 500<br>500 | 19<br>2 | 20<br>20 | 500<br>500       | ns<br>ns |

| t <sub>H</sub>                                 | ENC High Time (Note 8)                    | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On | ●<br>●     | 7.3<br>2 | 7.69<br>7.69 | 500<br>500 | 11.88<br>2 | 12.5<br>12.5 | 500<br>500 | 19<br>2 | 20<br>20 | 500<br>500       | ns<br>ns |

| t <sub>AP</sub>                                | Sample-and-Hold<br>Acquisition Delay Time |                                                       |            | 0        |              |            | 0          |              |            | 0       |          | ns               |          |

| SYMBOL                                         | PARAMETER                                 | CONDITIONS                                            |            |          |              | MIN        | TYP        | MAX          |            |         |          | UNITS            |          |

| <b>デジタル・データ出力(CMOS モード:フルデータレートとダブルデータレート)</b> |                                           |                                                       |            |          |              |            |            |              |            |         |          |                  |          |

| t <sub>D</sub>                                 | ENC to Data Delay                         | C <sub>L</sub> = 5pF (Note 8)                         | ●          | 1.1      |              | 1.7        |            | 3.1          |            |         |          | ns               |          |

| t <sub>C</sub>                                 | ENC to CLKOUT Delay                       | C <sub>L</sub> = 5pF (Note 8)                         | ●          | 1        |              | 1.4        |            | 2.6          |            |         |          | ns               |          |

| t <sub>SKEW</sub>                              | DATA to CLKOUT Skew                       | t <sub>D</sub> - t <sub>C</sub> (Note 8)              | ●          | 0        |              | 0.3        |            | 0.6          |            |         |          | ns               |          |

|                                                | Pipeline Latency                          | Full Data Rate Mode<br>Double Data Rate Mode          |            |          |              |            | 6          |              | 6.5        |         |          | Cycles<br>Cycles |          |

21421014fa

# LTC2142-14/ LTC2141-14/LTC2140-14

**タイミング特性** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5)。

| SYMBOL                      | PARAMETER           | CONDITIONS                  |   | MIN | TYP | MAX | UNITS  |

|-----------------------------|---------------------|-----------------------------|---|-----|-----|-----|--------|

| <b>デジタル・データ出力(LVDS モード)</b> |                     |                             |   |     |     |     |        |

| $t_D$                       | ENC to Data Delay   | $C_L = 5\text{pF}$ (Note 8) | ● | 1.1 | 1.8 | 3.2 | ns     |

| $t_C$                       | ENC to CLKOUT Delay | $C_L = 5\text{pF}$ (Note 8) | ● | 1   | 1.5 | 2.7 | ns     |

| $t_{SKew}$                  | DATA to CLKOUT Skew | $t_D - t_C$ (Note 8)        | ● | 0   | 0.3 | 0.6 | ns     |

|                             | Pipeline Latency    |                             |   |     | 6.5 |     | Cycles |

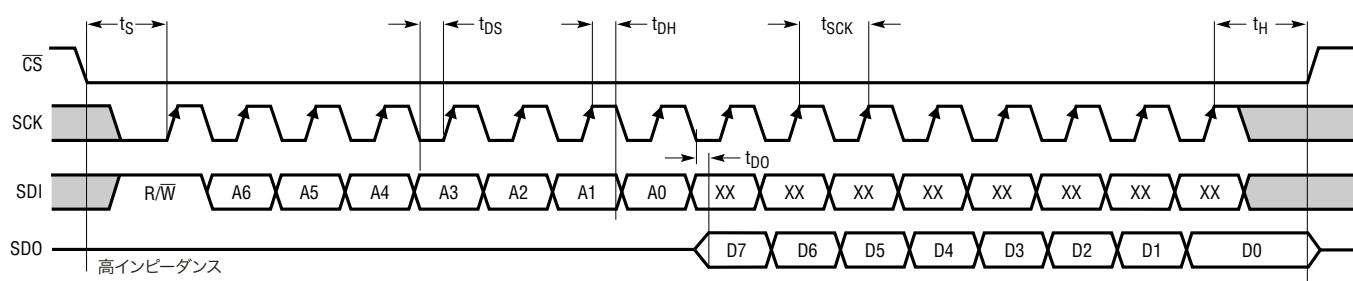

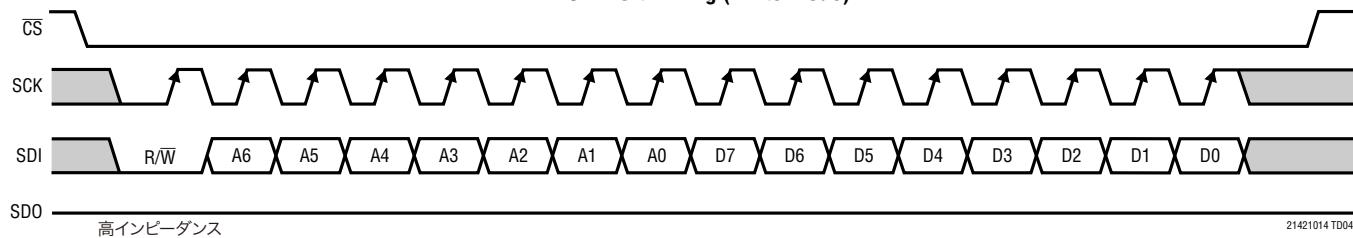

## SPIポートのタイミング (Note 8)

|           |                                          |                                                                                       |        |           |  |     |          |

|-----------|------------------------------------------|---------------------------------------------------------------------------------------|--------|-----------|--|-----|----------|

| $t_{SCK}$ | SCK Period                               | Write Mode<br>Readback Mode, $C_{SDO} = 20\text{pF}$ , $R_{PULLUP} = 2\text{k}\Omega$ | ●<br>● | 40<br>250 |  |     | ns<br>ns |

| $t_S$     | $\overline{\text{CS}}$ to SCK Setup Time |                                                                                       | ●      | 5         |  |     | ns       |

| $t_H$     | SCK to $\overline{\text{CS}}$ Setup Time |                                                                                       | ●      | 5         |  |     | ns       |

| $t_{DS}$  | SDI Setup Time                           |                                                                                       | ●      | 5         |  |     | ns       |

| $t_{DH}$  | SDI Hold Time                            |                                                                                       | ●      | 5         |  |     | ns       |

| $t_{DO}$  | SCK Falling to SDO Valid                 | Readback Mode, $C_{SDO} = 20\text{pF}$ , $R_{PULLUP} = 2\text{k}\Omega$               | ●      |           |  | 125 | ns       |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** すべての電圧値は(注記がない限り) GND と OGND を短絡した状態の GND を基準にしている。

**Note 3:** これらのピンの電圧を GND より低くすると、内部のダイオードによってクランプされる。この製品は、GND より低いか、または  $V_{DD}$  より高い電圧でラッチアップを生じることなしに 100mA を超える入力電流を処理することができる。

**Note 4:** これらのピンの電圧を GND より低くすると、その電圧は内部のダイオードによってクランプされる。これらのピンの電圧を  $V_{DD}$  より高くすると、その電圧は内部のダイオードによってクランプされない。この製品は、GND より低い電圧で、ラッチアップを生じることなく 100mA を超える入力電流を処理することができる。

**Note 5:** 注記がない限り、 $V_{DD} = 0V$ ,  $V_{DD} = 1.8V$ ,  $f_{SAMPLE} = 65\text{MHz}$  (LTC2142),  $40\text{MHz}$  (LTC2141)、または  $25\text{MHz}$  (LTC2140)、CMOS 出力、 $ENC^+ = \text{シングルエンドの } 1.8\text{V 方形波}$ 、 $ENC^- = 0\text{V}$ 、入力範囲 = 差動ドライブで  $2\text{V}_{\text{p-p}}$ 、各デジタル出力に  $5\text{pF}$  の負荷。電源電流および電力損失の規格値はデバイス全体の合計値であり、1 チャンネルあたりの値ではない。

**Note 6:** 積分非直線性は、伝達曲線に最もよく合致する直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 7:** オフセット誤差は、2 の補数出力モードで出力コードが 00 0000 0000 0000 と 11 1111 1111 の間を行ったり来たりするとき、 $-0.5\text{LSB}$  から測定したオフセット電圧である。

**Note 8:** 設計によって保証されているが、テストされない。

**Note 9:** 注記がない限り、 $V_{DD} = 1.8V$ ,  $f_{SAMPLE} = 65\text{MHz}$  (LTC2142)、 $40\text{MHz}$  (LTC2141)、または  $25\text{MHz}$  (LTC2140)、CMOS 出力、 $ENC^+ = \text{シングルエンドの } 1.8\text{V 方形波}$ 、 $ENC^- = 0\text{V}$ 、入力範囲 = 差動ドライブで  $2\text{V}_{\text{p-p}}$ 、各デジタル出力に  $5\text{pF}$  の負荷。電源電流および電力損失の規格値はデバイス全体の合計値であり、1 チャンネルあたりの値ではない。

**Note 10:** 推奨動作条件。

## 標準的性能特性

# LTC2142-14/ LTC2141-14/LTC2140-14

## 標準的性能特性

## 標準的性能特性

# LTC2142-14/ LTC2141-14/LTC2140-14

## 標準的性能特性

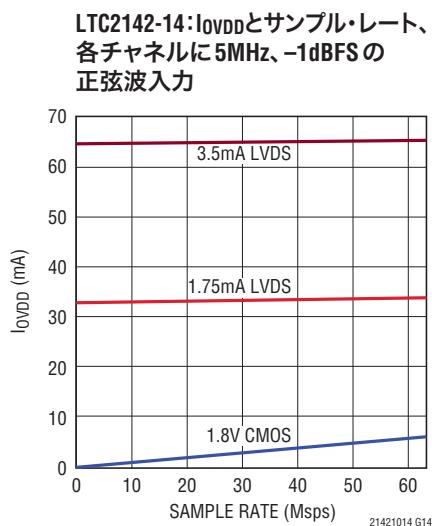

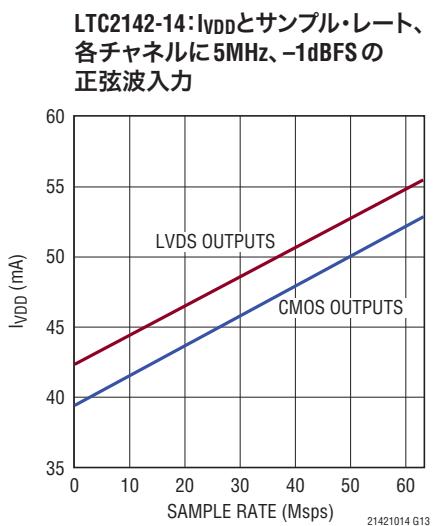

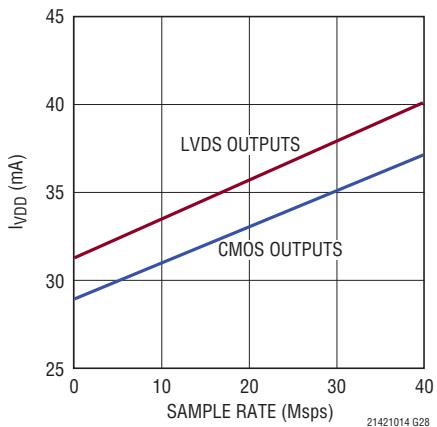

**LTC2141-14:**  $I_{VDD}$ とサンプル・レート、各チャネルに5MHz、-1dBFSの正弦波入力

**LTC2141-14:**  $I_{VDD}$ とサンプル・レート、各チャネルに5MHz、-1dBFSの正弦波入力

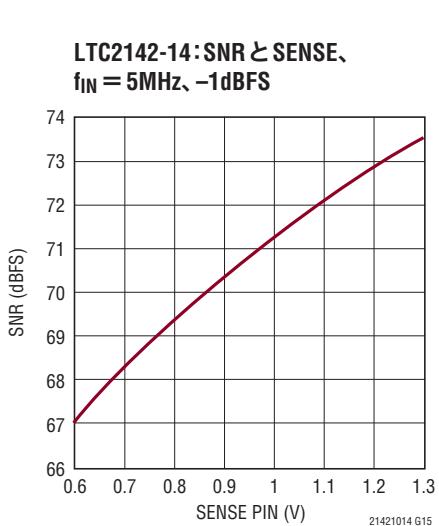

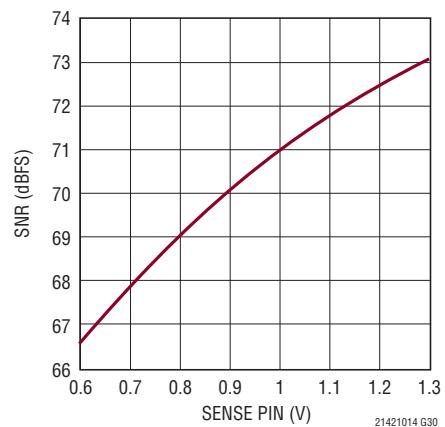

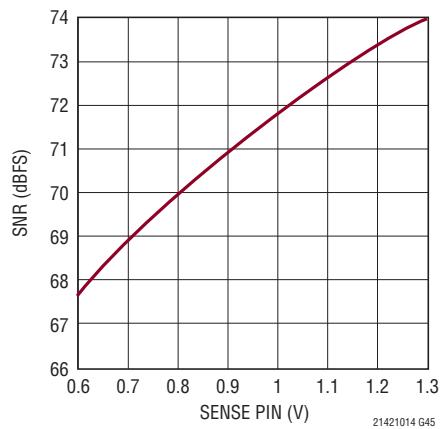

**LTC2141-14:** SNRとSENSE、 $f_{IN} = 5\text{MHz}$ 、-1dBFS

**LTC2140-14:** 積分非直線性(INL)

**LTC2140-14:** 微分非直線性(DNL)

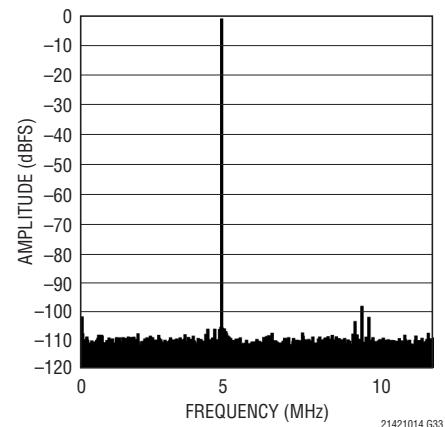

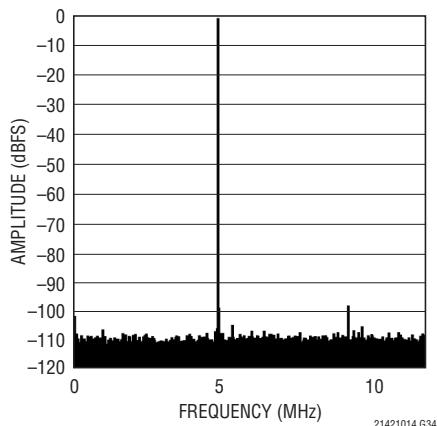

**LTC2140-14:** 64k ポイントのFFT、 $f_{IN} = 5\text{MHz}$ 、-1dBFS、25Mps

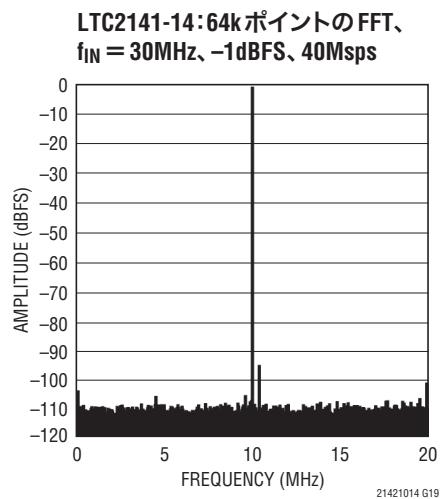

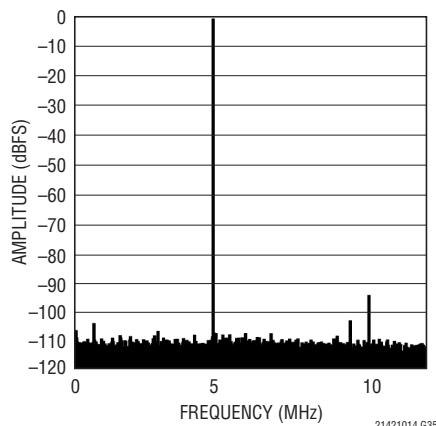

**LTC2140-14:** 64k ポイントのFFT、 $f_{IN} = 30\text{MHz}$ 、-1dBFS、25Mps

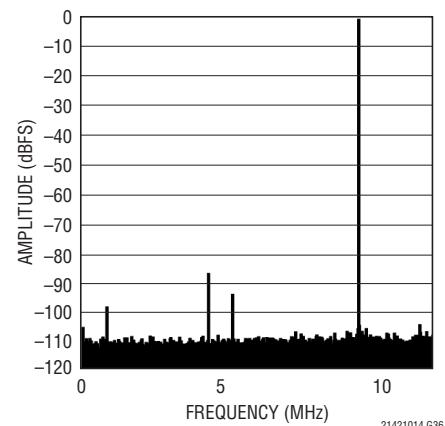

**LTC2140-14:** 64k ポイントのFFT、 $f_{IN} = 70\text{MHz}$ 、-1dBFS、25Mps

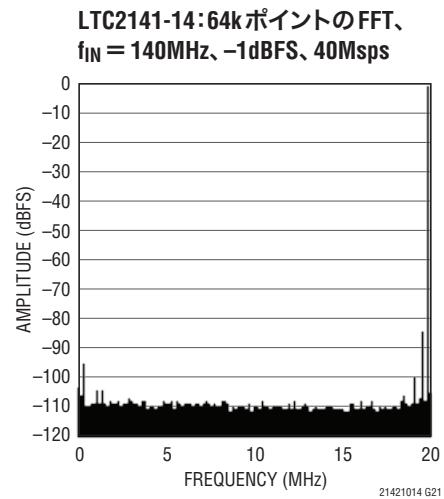

**LTC2140-14:** 64k ポイントのFFT、 $f_{IN} = 140\text{MHz}$ 、-1dBFS、25Mps

## 標準的性能特性

LTC2140-14: 64k ポイントの

2トーン FFT、 $f_{IN} = 69\text{MHz}$ 、 $70\text{MHz}$ 、

$-7\text{dBFS}$ 、 $25\text{Msps}$

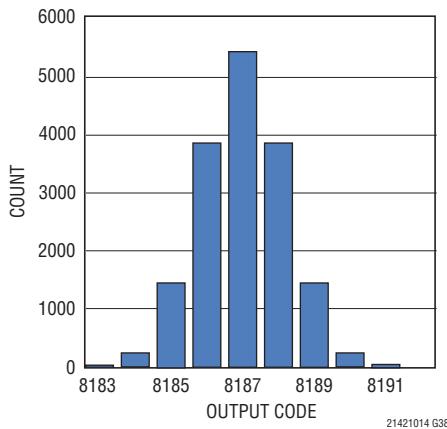

LTC2140-14: 短絡入力の

ヒストグラム

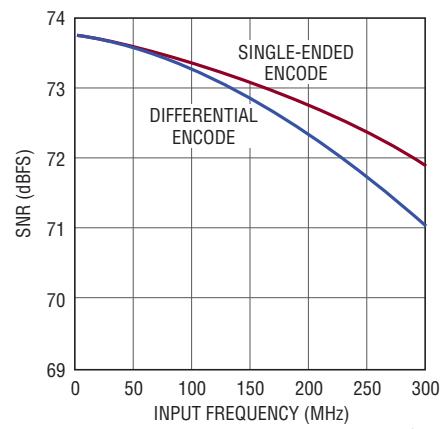

LTC2140-14: SNR と 入力周波数、

$-1\text{dBFS}$ 、 $25\text{Msps}$ 、 $2\text{V}$ 範囲

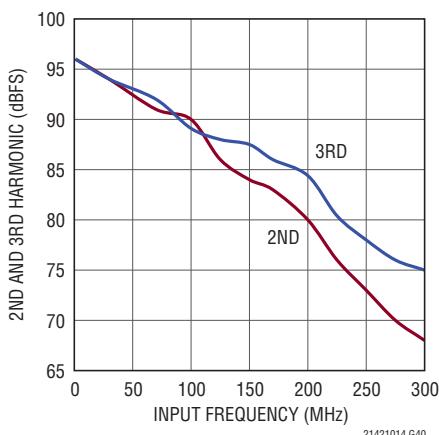

LTC2140-14: 2 次および 3 次高調波と

入力周波数、 $-1\text{dBFS}$ 、 $25\text{Msps}$ 、 $2\text{V}$ 範囲

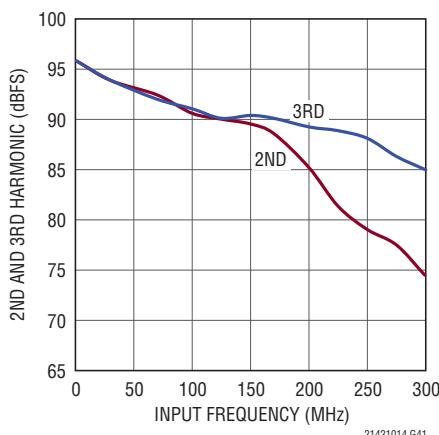

LTC2140-14: 2 次および 3 次高調波と

入力周波数、 $-1\text{dBFS}$ 、 $25\text{Msps}$ 、 $1\text{V}$ 範囲

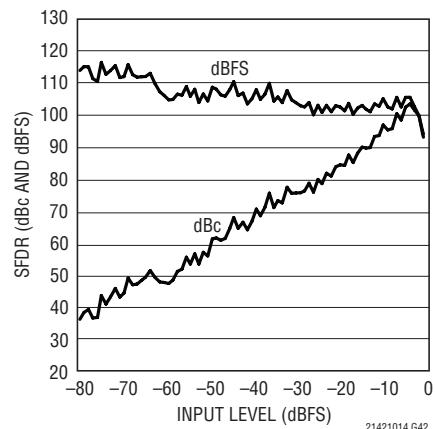

LTC2140-14: SFDR と 入力レベル、

$f_{IN} = 70\text{MHz}$ 、 $25\text{Msps}$ 、 $2\text{V}$ 範囲

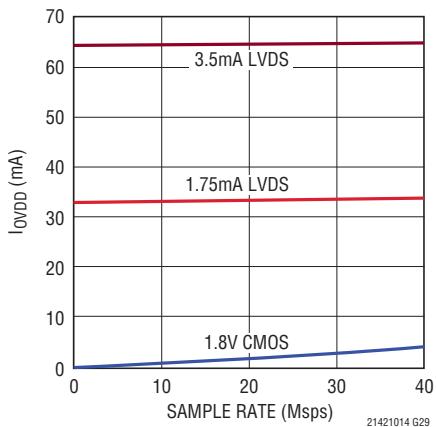

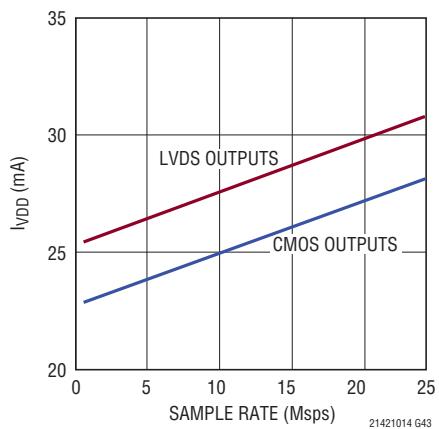

LTC2140-14:  $I_{VDD}$  と サンプル・レート、

各チャネルに  $5\text{MHz}$ 、 $-1\text{dBFS}$  の

正弦波入力

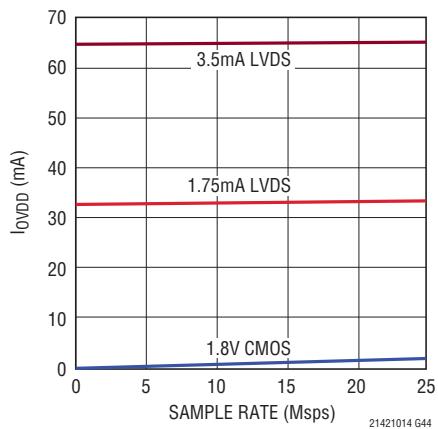

LTC2140-14:  $I_{VDD}$  と サンプル・レート、

各入力に  $5\text{MHz}$ 、 $-1\text{dBFS}$  の正弦波

LTC2140-14: SNR と SENSE、

$f_{IN} = 5\text{MHz}$ 、 $-1\text{dBFS}$

# LTC2142-14/ LTC2141-14/LTC2140-14

## ピン機能

### ピンはすべてのデジタル出力モードで同一

**V<sub>DD</sub>(ピン1、16、17、64)**: 1.7V～1.9Vのアナログ電源。0.1μFのセラミック・コンデンサを使用してグランドにバイパスします。隣接するピンはバイパス・コンデンサを共有することができます。

**V<sub>CM1</sub>(ピン2)**: 同相バイアス出力。公称値はV<sub>DD</sub>/2に等しい。V<sub>CM1</sub>は、チャネル1へのアナログ入力の同相電圧をバイアスするために使用します。0.1μFのセラミック・コンデンサを使ってグランドにバイパスします。

**GND(ピン3、6、14)**: ADCの電源グランド。

**A<sub>IN1</sub>+ (ピン4)**: チャネル1の正の差動アナログ入力。

**A<sub>IN1</sub>- (ピン5)**: チャネル1の負の差動アナログ入力。

**REFH (ピン7、9)**: ADCの“H”リファレンス。REFHおよびREFLの推奨バイパス回路については「アプリケーション情報」のセクションを参照してください。

**REFL (ピン8、10)**: ADCの“L”リファレンス。REFHおよびREFLの推奨バイパス回路については「アプリケーション情報」のセクションを参照してください。

**PAR/SER (ピン11)**: プログラミング・モード選択ピン。シリアル・プログラミング・モードをイネーブルするにはグランドに接続します。CS、SCK、SDI、SDOはA/Dコンバータの動作モードを制御するシリアル・インターフェースになります。パラレル・プログラミング・モードをイネーブルするにはV<sub>DD</sub>に接続します。この場合、CS、SCK、SDI、SDOは、A/Dコンバータの(種類が限定された)動作モードを制御するパラレル・ロジック入力になります。PAR/SERはグランドまたはV<sub>DD</sub>に直接接続し、ロジック信号ではドライブしないようにします。

**A<sub>IN2</sub>+ (ピン12)**: チャネル2の正の差動アナログ入力。

**A<sub>IN2</sub>- (ピン13)**: チャネル2の負の差動アナログ入力。

**V<sub>CM2</sub>(ピン15)**: 同相バイアス出力。公称値はV<sub>DD</sub>/2に等しい。V<sub>CM2</sub>は、チャネル2へのアナログ入力の同相電圧をバイアスするために使用します。0.1μFのセラミック・コンデンサを使ってグランドにバイパスします。

**ENC+ (ピン18)**: エンコード入力。立ち上がりエッジで変換が開始されます。

**ENC- (ピン19)**: エンコード相補入力。立ち下がりエッジで変換が開始されます。シングルエンド・エンコード・モードの場合はGNDに接続します。

**CS (ピン20)**: シリアル・プログラミング・モード(PAR/SER=0V)では、CSはシリアル・インターフェースのチップ選択入力です。CSが“L”になると、SCKがイネーブルされ、SDIのデータがモード制御レジスタにシフトされます。パラレル・プログラミング・モード(PAR/SER=V<sub>DD</sub>)では、CSはクロック・デューティ・サイクル・スタビライザを制御します(表2を参照)。CSは1.8V～3.3Vのロジックでドライブすることができます。

**SCK (ピン21)**: シリアル・プログラミング・モード(PAR/SER=0V)では、SCKはシリアル・インターフェースのクロック入力です。パラレル・プログラミング・モード(PAR/SER=V<sub>DD</sub>)では、SCKはデジタル出力モードを制御します(表2を参照)。SCKは1.8V～3.3Vのロジックでドライブすることができます。

**SDI (ピン22)**: シリアル・プログラミング・モード(PAR/SER=0V)では、SDIはシリアル・インターフェースのデータ入力です。SDIのデータは、SCKの立ち上がりエッジで同期してモード制御レジスタに入ります。パラレル・プログラミング・モード(PAR/SER=V<sub>DD</sub>)では、SDIをSDOと一緒に使ってデバイスをパワーダウンすることができます(表2を参照)。SDIは1.8V～3.3Vのロジックでドライブすることができます。

**OGND (ピン41)**: 出力ドライバのグランド。インダクタンスがきわめて低い経路でグランド・プレーンに短絡する必要があります。このピンの近くに複数のビアを使用します。

**0V<sub>DD</sub> (ピン42)**: 出力ドライバの電源。0.1μFのセラミック・コンデンサを使ってグランドにバイパスします。

**SDO (ピン61)**: シリアル・プログラミング・モード(PAR/SER=0V)では、SDOはシリアル・インターフェースのオプションのデータ出力です。SDOのデータは、モード制御レジスタから読み出してSCKの立ち下がりエッジでラッチすることができます。SDOはオープンドレインのNMOS出力で、2kの外付けプルアップ抵抗を1.8V～3.3Vに接続する必要があります。モード制御レジスタから読み出す必要がない場合は、プルアップ抵抗は不要であり、SDOは未接続のままでかまいません。パラレル・プログラミング・モード(PAR/SER=V<sub>DD</sub>)では、SDOをSDIと一緒に使ってデバイスをパワーダウンすることができます(表2を参照)。SDOを入力として使用する場合には、1kの直列抵抗を介して1.8V～3.3Vのロジックでドライブすることができます。

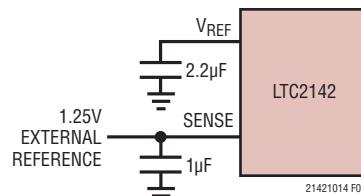

**V<sub>REF</sub> (ピン62)**: リファレンス電圧出力。2.2μFのセラミック・コンデンサを使ってグランドにバイパスします。出力電圧は公称1.25Vです。

## ピン機能

**SENSE(ピン63)**: リファレンス・プログラミング・ピン。SENSEをV<sub>DD</sub>に接続すると、内部リファレンスと±1Vの入力範囲が選択されます。SENSEをグランドに接続すると、内部リファレンスと±0.5Vの入力範囲が選択されます。0.625V～1.3Vの外部リファレンスをSENSEに印加すると、±0.8・V<sub>SENSE</sub>の入力範囲が選択されます。

**グランド(背面パッド・ピン65)**: 背面パッドはプリント回路基板のグランドに半田付けする必要があります。

### フルレートCMOS出力モード

以降のすべてのピンはCMOS出力レベル(0V<sub>GND</sub>～0V<sub>DD</sub>)を備えています。

**D2\_0～D2\_13(ピン25、26、27、28、29、30、31、32、33、34、35、36、37、38)**: チャネル2のデジタル出力。D2\_13がMSBです。

**DNC(ピン23、24、43、44)**: これらのピンは接続しないでください。

**CLKOUT~(ピン39)**: CLKOUT<sup>+</sup>の反転タイプ。

**CLKOUT<sup>+</sup>(ピン40)**: データ出力クロック。デジタル出力は通常CLKOUT<sup>+</sup>の立ち下がりエッジと同時に遷移します。CLKOUT<sup>+</sup>の位相は、モード制御レジスタをプログラムすることにより、デジタル出力に対して遅らせることもできます。

**D1\_0～D1\_13(ピン45、46、47、48、49、50、51、52、53、54、55、56、57、58)**: チャネル1のデジタル出力。D1\_13がMSBです。

**OF2(ピン59)**: チャネル2のオーバーフロー/アンダーフロー・デジタル出力。オーバーフローまたはアンダーフローが生じるとOF2は“H”になります。

**OF1(ピン60)**: チャネル1のオーバーフロー/アンダーフロー・デジタル出力。オーバーフローまたはアンダーフローが生じるとOF1は“H”になります。

### ダブルデータレートCMOS出力モード

以降のすべてのピンはCMOS出力レベル(0V<sub>GND</sub>～0V<sub>DD</sub>)を備えています。

**D2\_0\_1～D2\_12\_13(ピン26、28、30、32、34、36、38)**: チャネル2のダブルデータレート・デジタル出力。2つのデータ・ビットが各出力ピンに多重化されます。CLKOUT<sup>+</sup>が“L”的ときは、偶数データ・ビット(D0、D2、D4、D6、D8、D10、D12)が現れます。CLKOUT<sup>+</sup>が“H”的ときは、奇数データ・ビット(D1、D3、D5、D7、D9、D11、D13)が現れます。

**DNC(ピン23、24、25、27、29、31、33、35、37、43、44、45、47、49、51、53、55、57、59)**: これらのピンは接続しないでください。

**CLKOUT~(ピン39)**: CLKOUT<sup>+</sup>の反転タイプ。

**CLKOUT<sup>+</sup>(ピン40)**: データ出力クロック。デジタル出力は通常CLKOUT<sup>+</sup>の立ち下がりエッジおよび立ち上がりエッジと同時に遷移します。CLKOUT<sup>+</sup>の位相は、モード制御レジスタをプログラムすることにより、デジタル出力に対して遅らせることもできます。

**D1\_0\_1～D1\_12\_13(ピン46、48、50、52、54、56、58)**: チャネル1のダブルデータレート・デジタル出力。2つのデータ・ビットが各出力ピンに多重化されます。CLKOUT<sup>+</sup>が“L”的ときは、偶数データ・ビット(D0、D2、D4、D6、D8、D10、D12)が現れます。CLKOUT<sup>+</sup>が“H”的ときは、奇数データ・ビット(D1、D3、D5、D7、D9、D11、D13)が現れます。

**OF2\_1(ピン60)**: オーバーフロー/アンダーフロー・デジタル出力。オーバーフローまたはアンダーフローが生じるとOF2\_1は“H”になります。両方のチャネルのオーバーフロー/アンダーフローがこのピンに多重化されます。CLKOUT<sup>+</sup>が“L”的ときはチャネル2が現れ、CLKOUT<sup>+</sup>が“H”的ときはチャネル1が現れます。

### ダブルデータレートLVDS出力モード

以降のすべてのピンはLVDS出力レベルを備えています。出力電流レベルはプログラム可能です。各LVDS出力対のピン間にはオプションの内部100Ω終端抵抗があります。

**D2\_0\_1~/D2\_0\_1+～D2\_12\_13~/D2\_12\_13+(ピン25/26、27/28、29/30、31/32、33/34、35/36、37/38)**: チャネル2のダブルデータレート・デジタル出力。2つのデータ・ビットが各差動出力対に多重化されます。CLKOUT<sup>+</sup>が“L”的ときは、偶数データ・ビット(D0、D2、D4、D6、D8、D10、D12)が現れます。CLKOUT<sup>+</sup>が“H”的ときは、奇数データ・ビット(D1、D3、D5、D7、D9、D11、D13)が現れます。

**CLKOUT~/CLKOUT<sup>+</sup>(ピン39/40)**: データ出力クロック。デジタル出力は通常CLKOUT<sup>+</sup>の立ち下がりエッジおよび立ち上がりエッジと同時に遷移します。CLKOUT<sup>+</sup>の位相は、モード制御レジスタをプログラムすることにより、デジタル出力に対して遅らせることもできます。

**DNC(ピン23、24、43、44)**: これらのピンは接続しないでください。

# LTC2142-14/ LTC2141-14/LTC2140-14

## ピン機能

**D1\_0\_1-/D1\_0\_1+ ~ D1\_12\_13-/D1\_12\_13+**(ピン45/46、47/48、49/50、51/52、53/54、55/56、57/58)：チャネル1のダブルデータレート・デジタル出力。2つのデータ・ビットが各差動出力対に多重化されます。CLKOUT<sup>+</sup>が“L”的ときは、偶数データ・ビット(D0、D2、D4、D6、D8、D10、D12)が現れます。CLKOUT<sup>+</sup>が“H”的ときは、奇数データ・ビット(D1、D3、D5、D7、D9、D11、D13)が現れます。

**OF2\_1-/OF2\_1+**(ピン59/60)：オーバーフロー/アンダーフロー・デジタル出力。オーバーフローまたはアンダーフローが生じると、OF2\_1+は“H”になります。両方のチャネルのオーバーフロー/アンダーフローがこのピンに多重化されます。CLKOUT<sup>+</sup>が“L”的ときはチャネル2が現れ、CLKOUT<sup>+</sup>が“H”的ときはチャネル1が現れます。

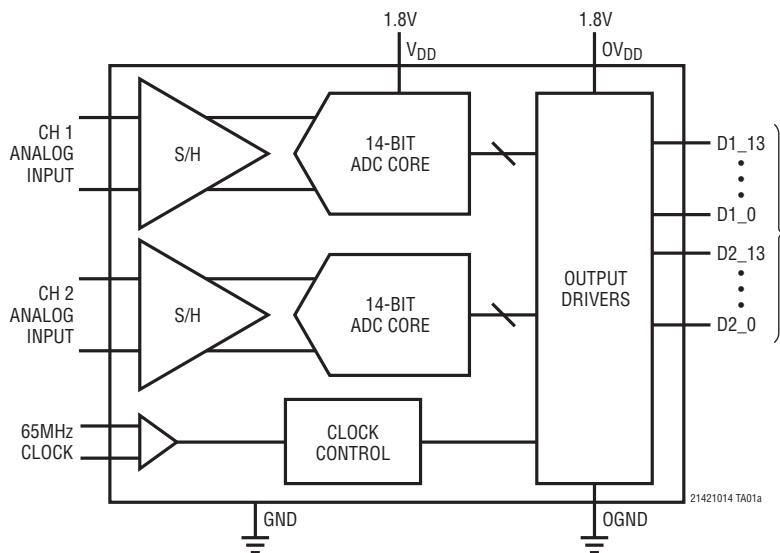

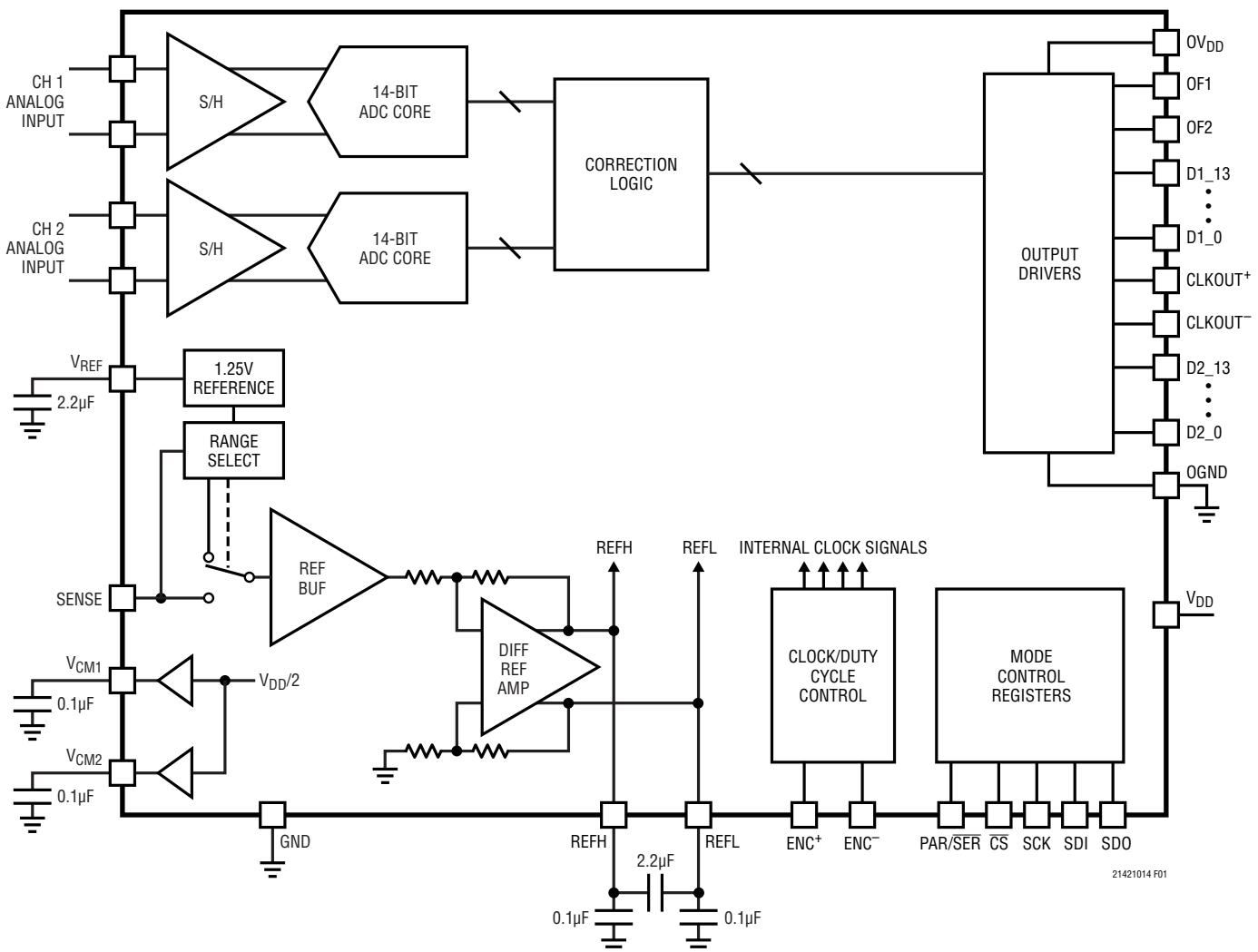

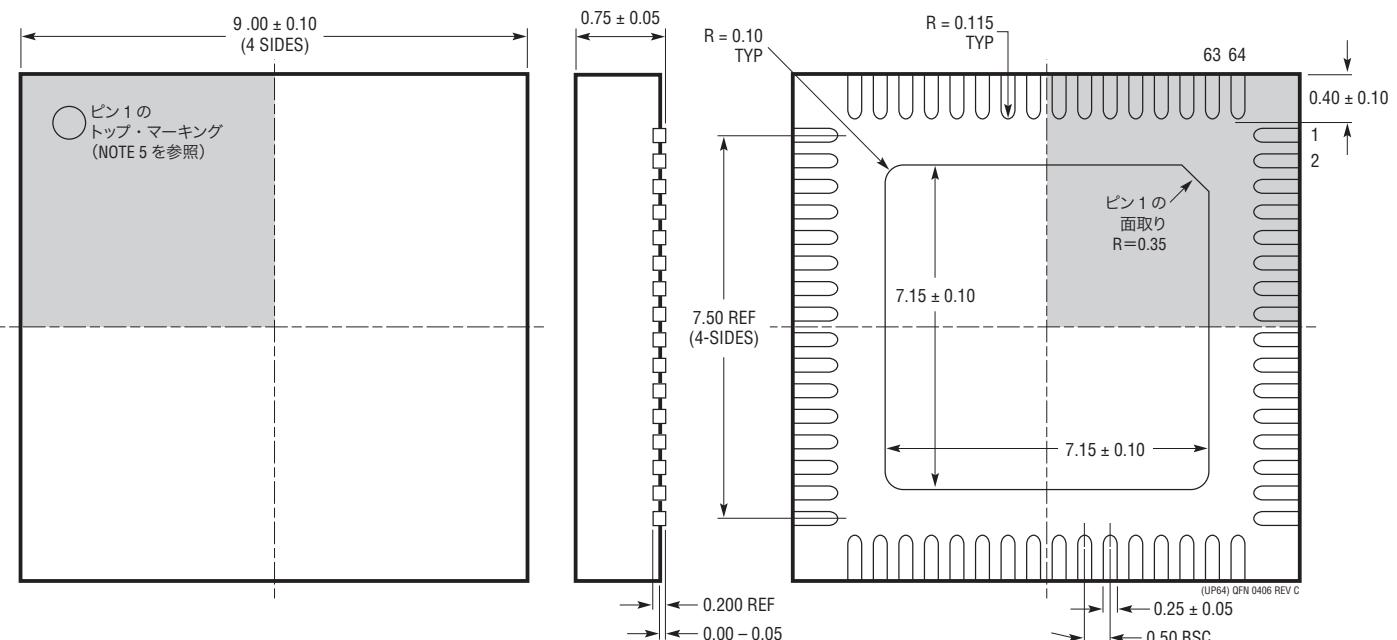

## 機能ブロック図

図1. 機能ブロック図

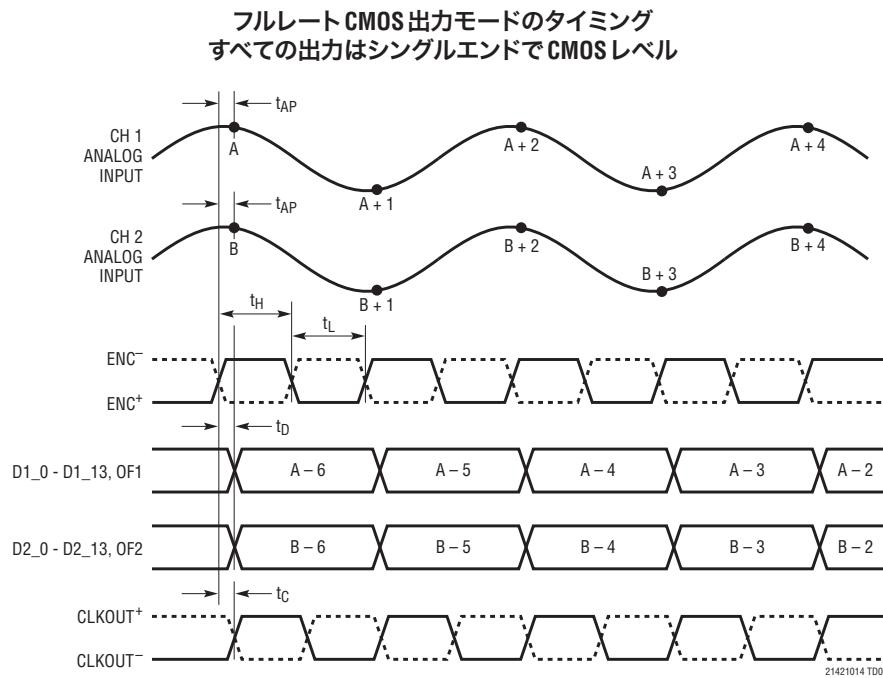

## タイミング図

## タイミング図

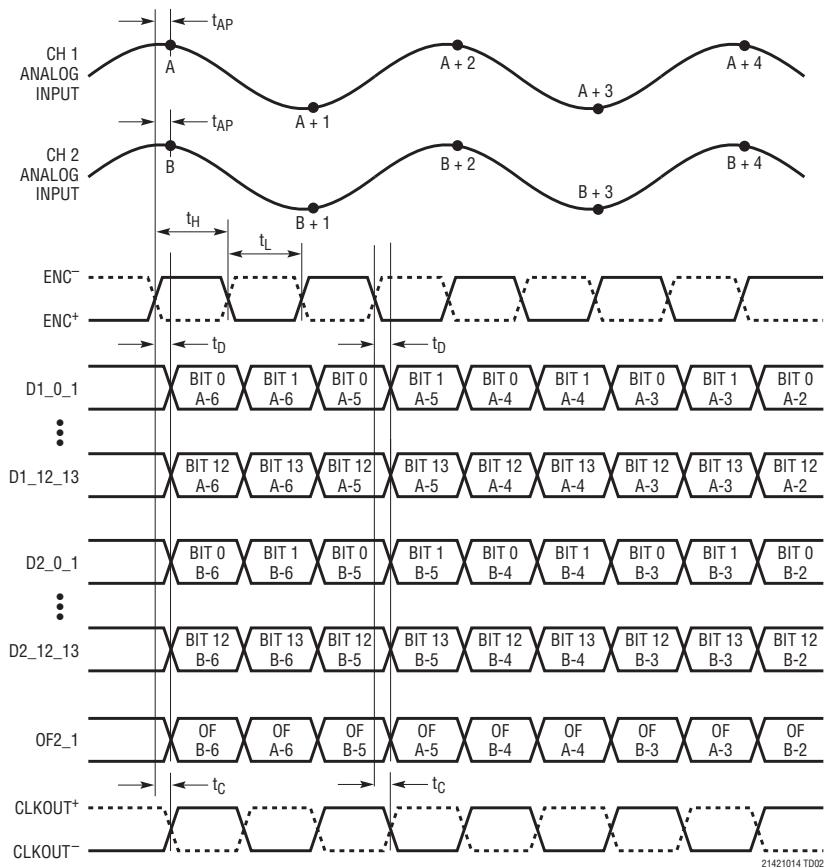

ダブルデータレート CMOS 出力モードのタイミング

すべての出力はシングルエンドで CMOS レベル

21421014 TD02

21421014fa

## タイミング図

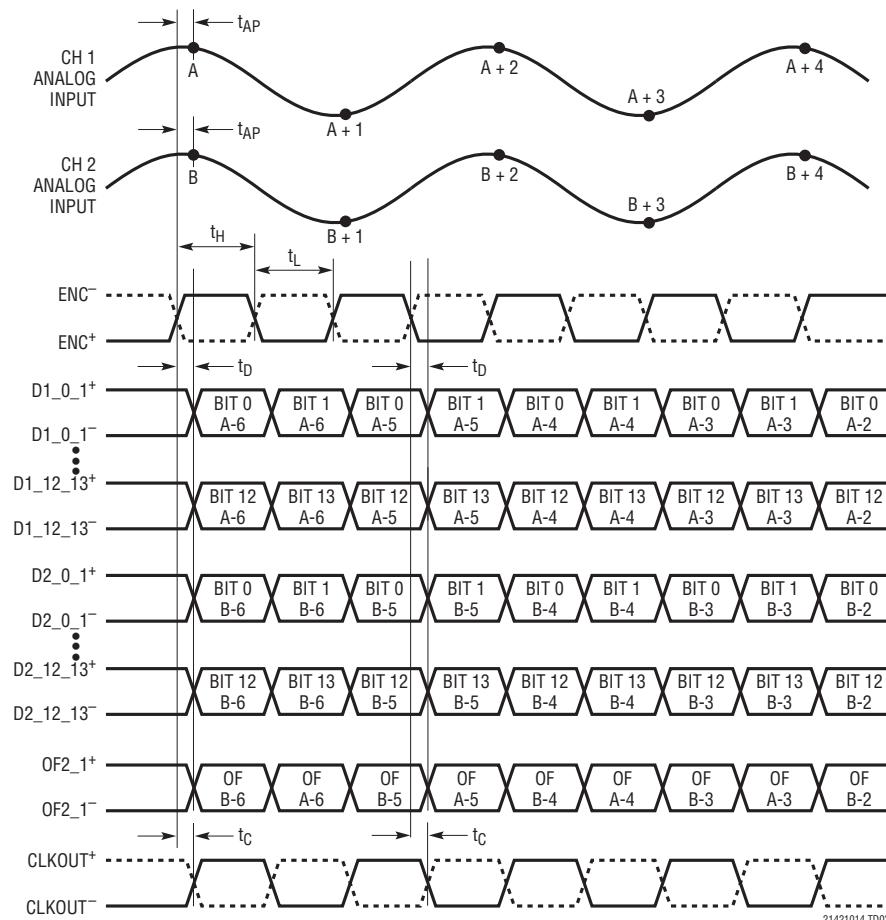

ダブルデータレートLVDS出力モードのタイミング

すべての出力は差動でLVDSレベル

SPIポートのタイミング(リードバック・モード)

SPI Port Timing (Write Mode)

# LTC2142-14/ LTC2141-14/LTC2140-14

## アプリケーション情報

### コンバータの動作

LTC2142-14/LTC2141-14/LTC2140-14は、1.8V 単一電源で動作する、低消費電力、2チャネル、14ビット、65Msps/40Msps/25Msps のA/Dコンバータです。アナログ入力は差動でドライブします。エンコード入力は差動でドライブできますが、消費電力を抑えるためにシングルエンドでドライブすることもできます。デジタル出力は、CMOSモード、(出力ラインの数を半減するため)ダブルデータレートCMOSモード、または(システム内のデジタル・ノイズを減らすため)ダブルデータレートLVDSモードにすることができます。シリアルSPIポートを介してモード制御レジスタをプログラムすることにより、多くの追加機能を選択することができます。

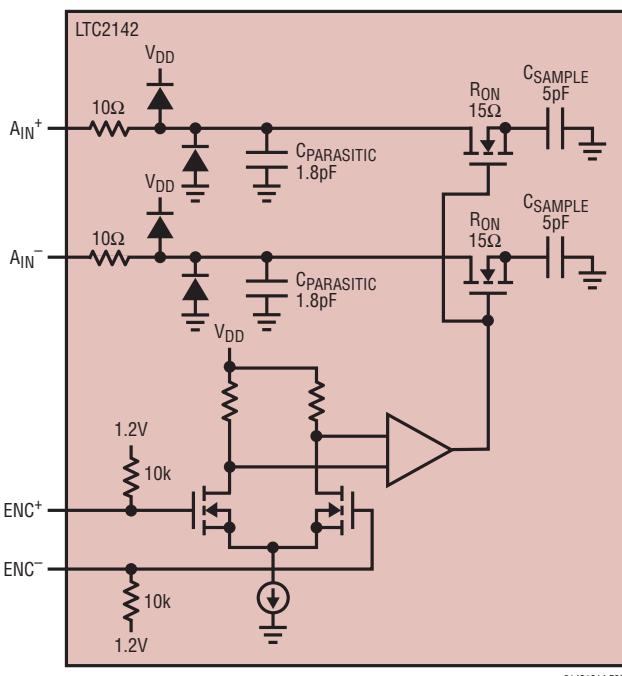

### アナログ入力

アナログ入力は差動CMOSサンプル&ホールド回路です(図2)。入力は $V_{CM1}$ または $V_{CM2}$ 出力ピンによって設定される同相電圧(通常は公称値である $V_{DD}/2$ )を中心に差動でドライブします。2Vの入力範囲の場合、入力の振幅範囲は $V_{CM} - 0.5V$ から $V_{CM} + 0.5V$ にします。入力間には $180^\circ$ の位相差が必要です。

2つのチャネルは共有のエンコード回路(図2)によって同時にサンプリングされます。

### シングルエンド入力

高調波歪みの影響を受けにくいアプリケーションでは、 $V_{CM}$ を中心とした1VP-Pの信号を使って $A_{IN^+}$ 入力をシングルエンドでドライブすることができます。 $A_{IN^-}$ 入力は $V_{CM}$ に接続し、 $V_{CM}$ バイパス・コンデンサを $2.2\mu F$ に増やします。シングルエンド入力では、高調波歪みが増加してINLが低下しますが、ノイズとDNLは変化しません。

### 入力ドライブ回路

#### 入力フィルタリング

可能であれば、アナログ入力のすぐ近くにRCローパス・フィルタを接続します。このローパス・フィルタがあると、A/Dコンバータのサンプル&ホールド・スイッチングからドライブ回路が分離され、さらにドライブ回路からの広帯域ノイズも制限されます。入力RCフィルタの一例を図3に示します。RC部品の値はアプリケーションの入力周波数に基づいて選択します。

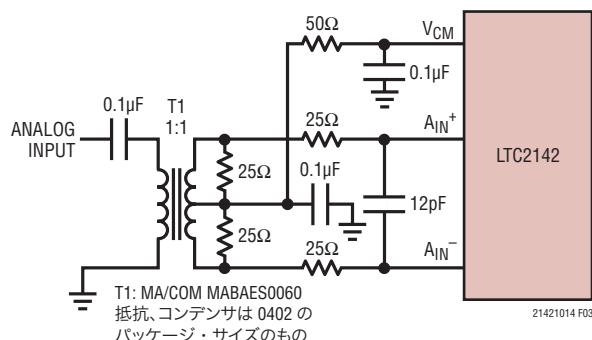

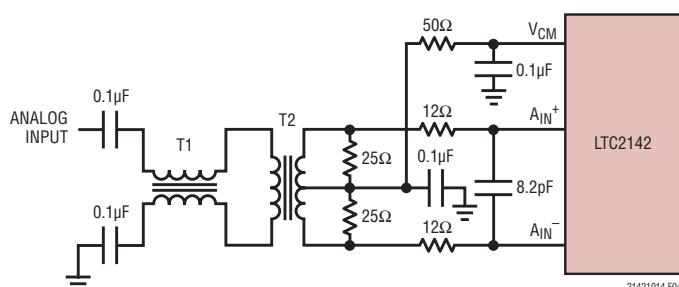

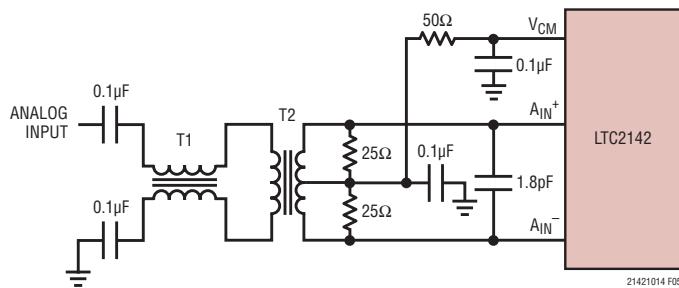

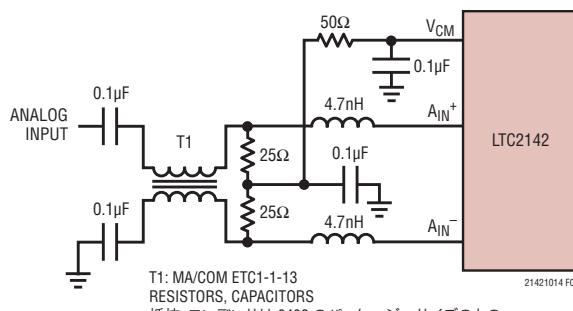

### トランスマルチピット回路

2次側にセンタータップを備えたRFトランスマルチピットによってドライブされるアナログ入力を図3に示します。センタータップは $V_{CM}$ でバイアスされており、A/Dコンバータの入力を最適なDCレベルに設定します。入力周波数が高いときは、伝送ラインのバランス・トランスマルチピット(図4～図6)のバランスが良くなるので、A/D変換の歪みが小さくなります。

図2. 等価入力回路。2つのアナログ・チャネルのうち1つのみを示す。

図3. トランスマルチピットを使用したアナログ入力回路。入力周波数が5MHz～70MHzの場合に推奨

## アプリケーション情報

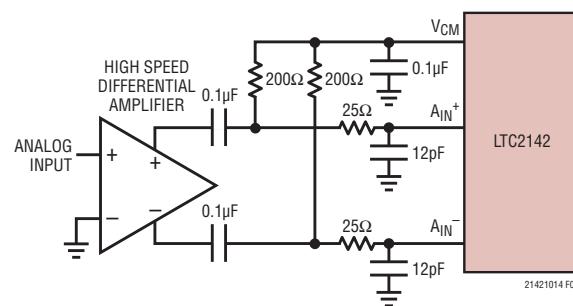

### アンプ回路

高速差動アンプによってドライブされるアナログ入力を図7に示します。アンプの出力はA/DコンバータにAC結合されているので、アンプの出力の同相電圧を最適に設定して歪みを最小限に抑えることができます。

非常に高い周波数では、多くの場合、RF利得ブロックの方が差動アンプよりも歪みが小さくなります。利得ブロックがシングルエンドである場合は、A/Dコンバータをドライブする前にトランス回路(図4～図6)で信号を差動に変換します。

T1: MA/COM MABA-007159-000000

T2: COILCRAFT WBC1-1TL

抵抗、コンデンサは0402のパッケージ・サイズのもの

図4. 入力周波数が5MHz～150MHzの場合の推奨フロントエンド回路

T1: MA/COM MABA-007159-000000

T2: COILCRAFT WBC1-1TL

抵抗、コンデンサは0402のパッケージ・サイズのもの

図5. 入力周波数が150MHz～250MHzの場合の推奨フロントエンド回路

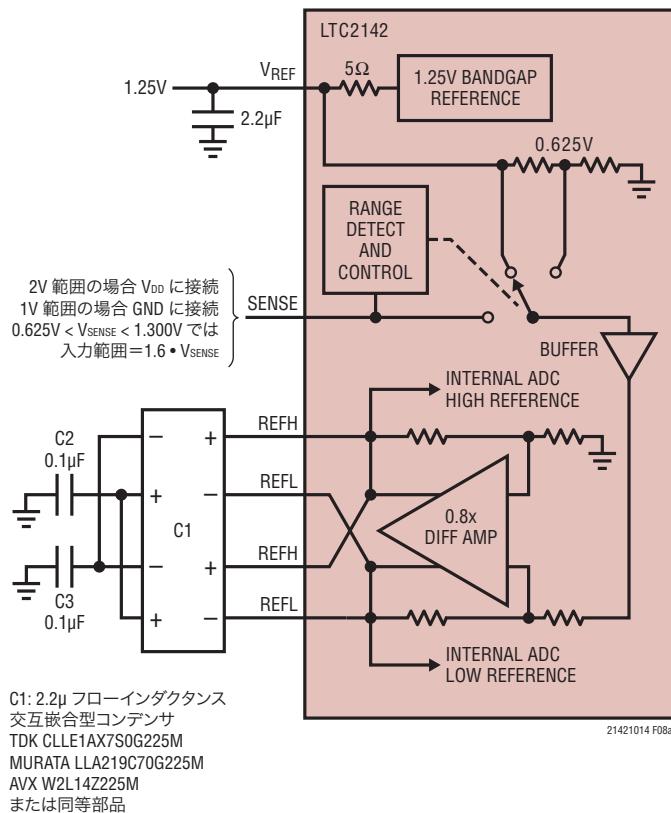

### リファレンス

LTC2142-14/LTC2141-14/LTC2140-14は1.25Vの電圧リファレンスを内蔵しています。内部リファレンスを使用する2Vの入力範囲の場合は、SENSEをV<sub>DD</sub>に接続します。内部リファレンスを使用する1Vの入力範囲の場合は、SENSEをグランドに接続します。外部リファレンスを使用する2Vの入力範囲の場合は、1.25Vのリファレンス電圧をSENSEに加えます(図9)。

0.625V～1.30Vの電圧をSENSEに印加することによって入力範囲を調整することができます。これにより、入力範囲は1.6・V<sub>SENSE</sub>になります。

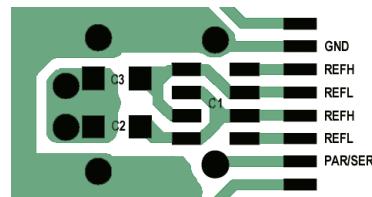

V<sub>REF</sub>、REFH、REFLの各ピンは図8に示すようにバイパスします。REFHとREFLの間のバイパス・コンデンサには、低インダクタンスの2.2μF交互嵌合型コンデンサを推奨します。このタイプのコンデンサは複数のメーカーから低価格で販売されています。

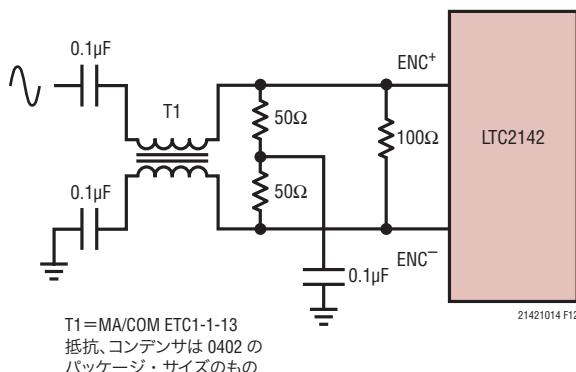

T1: MA/COM ETC1-1-13

RESISTORS, CAPACITORS

21421014 F06

図6. 入力周波数が250MHzを超える場合の推奨フロントエンド回路

図7. 高速差動アンプを使ったフロントエンド回路

21421014fa

# LTC2142-14/ LTC2141-14/LTC2140-14

## アプリケーション情報

図8a. リファレンス回路

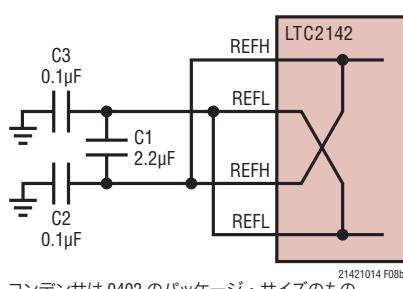

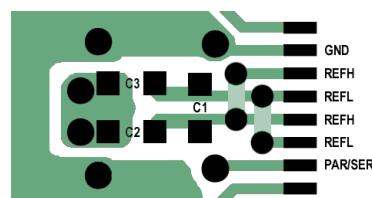

代わりに、REFHとREFLの間のC1を標準の2.2 $\mu$ Fコンデンサで置き換えるかもしれません(図8bを参照)。コンデンサは(回路基板の裏面ではなく)これら2つのピンにできるだけ近づけます。

REFH/REFLのバイパス・コンデンサの推奨回路基板レイアウトを図8cおよび図8dに示します。図8cでは、メーカーによつては交互嵌合型コンデンサ(C1)のピンが内部で接続されていないため、C1のすべてのピンを接続していることに注意してください。図8dでは、内部層に設けた短いジャンパによってREFHピンとREFLピンを接続しています。これらのジャンパの

図8b. REFH/REFLの代替バイパス回路

インダクタンスを最小に抑えるため、ジャンパは別の基板層のグランド・プレーン内の小さい穴に配置することができます。

図8c. 図8aのREFH/REFLのバイパス回路の推奨レイアウト

図8d. 図8bのREFH/REFLのバイパス回路の推奨レイアウト

図9. 1.25Vの外部リファレンスを使用する場合

## エンコード入力

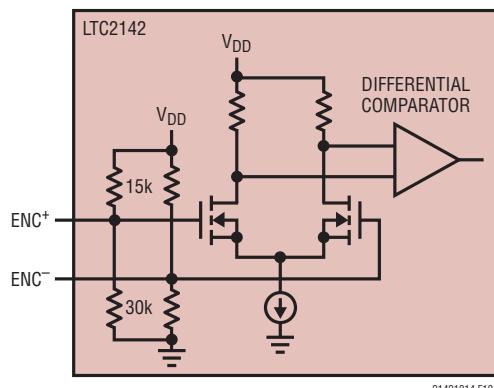

エンコード入力の信号品質は、A/Dコンバータのノイズ性能に強く影響します。エンコード入力はアナログ信号として扱います。このため、回路基板上のデジタル・トレースに隣接して配線しないようにしてください。エンコード入力の動作モードには、差動エンコード・モード(図10)とシングルエンド・エンコード・モード(図11)の2つがあります。

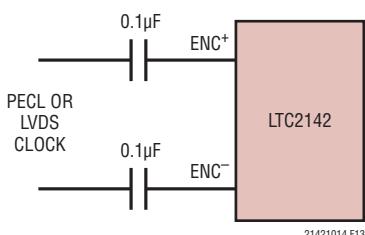

正弦波、PECLまたはLVDSのエンコード入力には、差動エンコード・モードを推奨します(図12および図13)。エンコード入力は内部で10k $\Omega$ の等価抵抗を介して1.2Vにバイアスされています。エンコード入力はV<sub>DD</sub>より高くすることができます(最大3.6V)、同相範囲は1.1V～1.6Vです。差動エンコード・モードでは、ENC<sup>+</sup>をグランドより200mV以上高い電圧に維持して、シングルエンド・エンコード・モードを誤って作動させないようにします。良好なジッタ性能を得るために、ENC<sup>+</sup>とENC<sup>-</sup>の立ち上がり時間と立ち下がり時間は短くします。

21421014fa

## アプリケーション情報

図10. 差動エンコード・モードでの等価エンコード入力回路

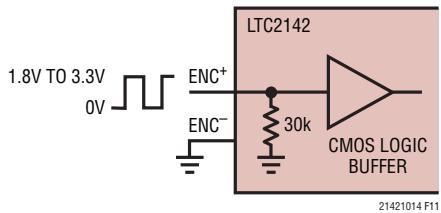

図11. シングルエンド・エンコード・モードでの等価エンコード入力回路

図12. 正弦波によるエンコード入力のドライブ

図13. PECL または LVDS によるエンコード入力のドライブ

シングルエンド・エンコード・モードは、CMOS エンコード入力と組み合わせて使用します。このモードを選択するには、ENC<sup>-</sup>をグランドに接続し、ENC<sup>+</sup>を方形波のエンコード入力でドライブします。ENC<sup>+</sup>はV<sub>DD</sub>より高くすることができるので(最大3.6V)、1.8V～3.3VのCMOSロジック・レベルを使用することができます。ENC<sup>+</sup>のしきい値は0.9Vです。良好なジッタ性能を得るため、ENC<sup>+</sup>の立ち上がり時間と立ち下がり時間は短くします。

エンコード信号がオフするか、または約500kHzより低い周波数になると、A/Dコンバータはナップ・モードになります。

### クロック・デューティ・サイクル・スタビライザ

良好な性能を得るために、エンコード信号のデューティ・サイクルは50%( $\pm 5\%$ )にします。オプションのクロック・デューティ・サイクル・スタビライザ回路がイネーブルされていると、エンコードのデューティ・サイクルは30%～70%の間で変化することができ、デューティ・サイクル・スタビライザは内部のデューティ・サイクルを一定の50%に保ちます。エンコード信号の周波数が変わると、デューティ・サイクル・スタビライザ回路は入力クロックにロックするのに100クロック・サイクルを要します。デューティ・サイクル・スタビライザはモード制御レジスタA2(シリアル・プログラミング・モード)またはCS(パラレル・プログラミング・モード)によってイネーブルされます。

サンプル・レートを迅速に変更する必要のあるアプリケーションでは、クロック・デューティ・サイクル・スタビライザをディスエーブルすることができます。デューティ・サイクル・スタビライザをディスエーブルする場合は、サンプリング・クロックのデューティ・サイクルが50%( $\pm 5\%$ )になるように注意してください。デューティ・サイクル・スタビライザは5Mspsより低いレートでは使わないでください。

### デジタル出力

#### デジタル出力モード

LTC2142-14/LTC2141-14/LTC2140-14は、フルレートCMOSモード、(出力ラインの数を半減するための)ダブルデータレートCMOSモード、(システム内のデジタル・ノイズを減らすための)ダブルデータレートLVDSモードという3つのデジタル出力モードで動作できます。出力モードはモード制御レジスタA3(シリアル・プログラミング・モード)、またはSCK(パラレル・プログラミング・モード)によって設定されます。ダブルデータレートCMOSモードはパラレル・プログラミング・モードでは選択できないことに注意してください。

21421014fa

## アプリケーション情報

### フルレート CMOS モード

フルレート CMOS モードでは、データ出力(D1\_0～D1\_13 および D2\_0～D2\_13)、オーバーフロー(OF2、OF1)、およびデータ出力クロック(CLKOUT<sup>+</sup>、CLKOUT<sup>-</sup>)が CMOS 出力レベルになります。出力は OV<sub>DD</sub> と OGND から電力を供給され、A/D コアの電源とグランドからは分離されています。OV<sub>DD</sub> は 1.1V～1.9V の範囲をとることができますので、1.2V～1.8V の CMOS ロジック出力が可能です。

良好な性能を得るために、デジタル出力がドライブする容量性負荷は最小限に抑えます。負荷容量が 10pF より大きい場合は、デジタル・バッファを使用します。

### ダブルデータレート CMOS モード

ダブルデータレート CMOS モードでは、2つのデータ・ビットが多重化されて各データ・ピンに出力されます。これにより、デジタル・ラインの数が 15 減るので、基板配線が簡単になり、データを受け取るのに必要な入力ピンの数が減ります。データ出力(D1\_0\_1、D1\_2\_3、D1\_4\_5、D1\_6\_7、D1\_8\_9、D1\_10\_11、D1\_12\_13、D2\_0\_1、D2\_2\_3、D2\_4\_5、D2\_6\_7、D2\_8\_9、D2\_10\_11、D2\_12\_13)、オーバーフロー(OF2\_1)、およびデータ出力クロック(CLKOUT<sup>+</sup>、CLKOUT<sup>-</sup>)は CMOS 出力レベルになります。出力は OV<sub>DD</sub> と OGND から電力を供給され、A/D コアの電源とグランドからは分離されています。OV<sub>DD</sub> は 1.1V～1.9V の範囲をとることができますので、1.2V～1.8V の CMOS ロジック出力が可能です。A/D コンバータのどちらのチャネルのオーバーフローも OF2\_1 ピンに多重化されることに注意してください。

良好な性能を得るために、デジタル出力がドライブする容量性負荷は最小限に抑えます。負荷容量が 10pF より大きい場合は、デジタル・バッファを使用します。

### ダブルデータレート LVDS モード

ダブルデータレート LVDS モードでは、2つのデータ・ビットが多重化されて各差動出力対に出力されます。デジタル出力データについては、A/D コンバータのチャネルごとに 7つの LVDS 出力対(D1\_0\_1<sup>+</sup>/D1\_0\_1<sup>-</sup>～D1\_12\_13<sup>+</sup>/D1\_12\_13<sup>-</sup> と D2\_0\_1<sup>+</sup>/D2\_0\_1<sup>-</sup>～D2\_12\_13<sup>+</sup>/D2\_12\_13<sup>-</sup>) があります。オーバーフロー(OF2\_1<sup>+</sup>/OF2\_1<sup>-</sup>) およびデータ出力クロック(CLKOUT<sup>+</sup>

CLKOUT<sup>-</sup>) には、それぞれ LVDS 出力対があります。A/D コンバータのどちらのチャネルのオーバーフローも OF2\_1<sup>+</sup>/OF2\_1<sup>-</sup> 出力対に多重化されることに注意してください。

デフォルトでは、出力は標準 LVDS レベルです。すなわち、出力電流が 3.5mA、出力同相電圧が 1.25V です。各 LVDS 出力対には外付けの 100Ω 差動終端抵抗が必要です。終端抵抗は、LVDS レシーバのできるだけ近くに配置してください。

出力は OV<sub>DD</sub> と OGND から電力を供給され、A/D コアの電源とグランドからは分離されています。LVDS モードでは、OV<sub>DD</sub> を 1.8V にする必要があります。

### 設定可能な LVDS 出力電流

LVDS モードでは、デフォルトの出力ドライバ電流は 3.5mA です。この電流は、モード制御レジスタ A3 を連続的にプログラムすることにより調整できます。設定可能な電流レベルは、1.75mA、2.1mA、2.5mA、3mA、3.5mA、4mA および 4.5mA です。

### オプションの LVDS ドライバの内部終端

ほとんどの場合は、100Ω の外付け終端抵抗を使用するだけで LVDS の優れた信号品位が得られます。さらに、モード制御レジスタ A3 を連続的にプログラムすることにより、オプションの 100Ω 内部終端抵抗をイネーブルすることができます。内部終端には、レシーバ側の不完全な終端によって生じる反射を吸収する効果があります。内部終端がイネーブルされると、同じ出力電圧振幅を維持するために、出力ドライバ電流は 2 倍になります。

### オーバーフロー・ビット

アナログ入力にオーバーレンジまたはアンダーレンジが生じると、オーバーフロー出力ビットはロジック “H” を出力します。オーバーフロー・ビットにはデータ・ビットと同じパイプライン待ち時間があります。フルレート CMOS モードでは、A/D コンバータの各チャネルに固有のオーバーフロー・ピン(チャネル 1:OF1、チャネル 2:OF2)があります。DDR CMOS モードまたは DDR LVDS モードでは、A/D コンバータのどちらのチャネルのオーバーフローも OF2\_1 出力に多重化されます。

## アプリケーション情報

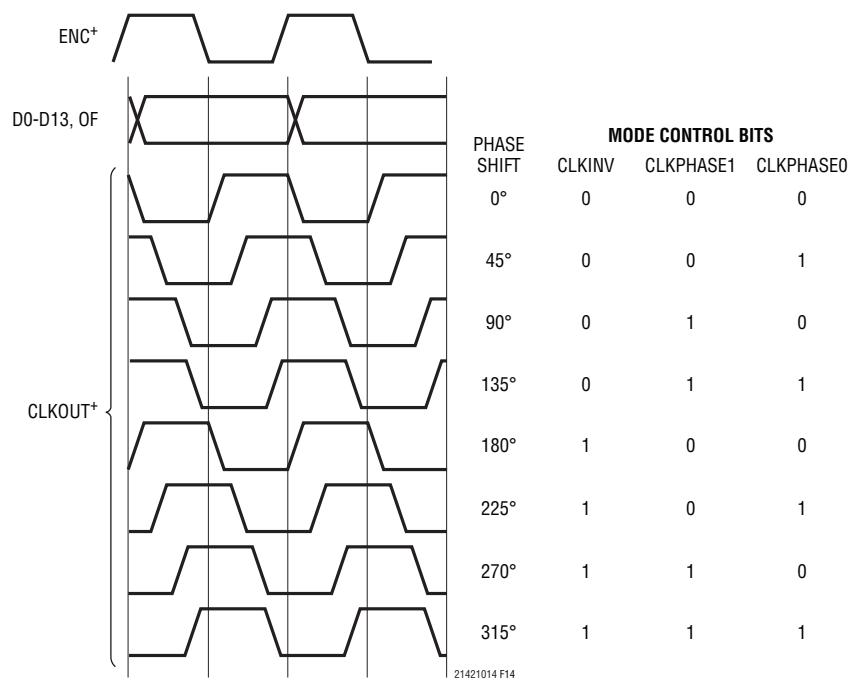

### 出力クロックの位相シフト

フルレートCMOSモードでは、データ出力ビットは通常 CLKOUT<sup>+</sup> の立ち下がりエッジと同時に変化するので、CLKOUT<sup>+</sup> の立ち上がりエッジを使って出力データをラッチすることができます。ダブルデータレートのCMOSモードおよびLVDSモードでは、データ出力ビットは通常 CLKOUT<sup>+</sup> の立ち下がりエッジおよび立ち上がりエッジと同時に変化します。データをラッチするとき適切なセットアップ時間とホールド時間を与えるには、データ出力ビットに対して CLKOUT<sup>+</sup> 信号の位相をシフトさせることができます。ほとんどのFPGAはこの機能を備えており、これが一般にタイミングを調整する最良のポイントです。

LTC2142-14/LTC2141-14/LTC2140-14 は、モード制御レジスタ A2 を連続的にプログラムすることにより、CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup> 信号の位相をシフトすることもできます。出力クロックは 0°、45°、90° または 135° の単位でシフトすることができます。位相シフト機能を使うには、クロック・デューティ・サイクル・スタビライザをオンする必要があります。もう 1 つの制御レジスタ・ビットは、位相シフトとは関係なく、CLKOUT<sup>+</sup> と CLKOUT<sup>-</sup> の極性を反転させることができます。これら 2 つの機能を組み合わせると、45° から 315° までの位相シフトが可能になります(図 14)。

### データ形式

アナログ入力電圧、デジタル・データ出力ビット、およびオーバーフロー・ビットの相互関係を表 1 に示します。デフォルトでは、出力のデータ形式はオフセット・バイナリです。モード制御レジスタ A4 を連続的にプログラムすることにより、2 の補数形式を選択することができます。

表 1. 出力コードと入力電圧

| $A_{IN^+} - A_{IN^-}$<br>(2V範囲) | OF | D13 ~ D0<br>(オフセット・バイナリ) | D13 ~ D0<br>(2の補数) |

|---------------------------------|----|--------------------------|--------------------|

| >1.000000V                      | 1  | 11 1111 1111 1111        | 01 1111 1111 1111  |

| +0.999878V                      | 0  | 11 1111 1111 1111        | 01 1111 1111 1111  |

| +0.999756V                      | 0  | 11 1111 1111 1110        | 01 1111 1111 1110  |

| +0.000122V                      | 0  | 10 0000 0000 0001        | 00 0000 0000 0001  |

| +0.000000V                      | 0  | 10 0000 0000 0000        | 00 0000 0000 0000  |

| -0.000122V                      | 0  | 01 1111 1111 1111        | 11 1111 1111 1111  |

| -0.000244V                      | 0  | 01 1111 1111 1110        | 11 1111 1111 1110  |

| -0.999878V                      | 0  | 00 0000 0000 0001        | 10 0000 0000 0001  |

| -1.000000V                      | 0  | 00 0000 0000 0000        | 10 0000 0000 0000  |

| ≤-1.000000V                     | 1  | 00 0000 0000 0000        | 10 0000 0000 0000  |

図 14. CLKOUT の位相シフト

# LTC2142-14/ LTC2141-14/LTC2140-14

## アプリケーション情報

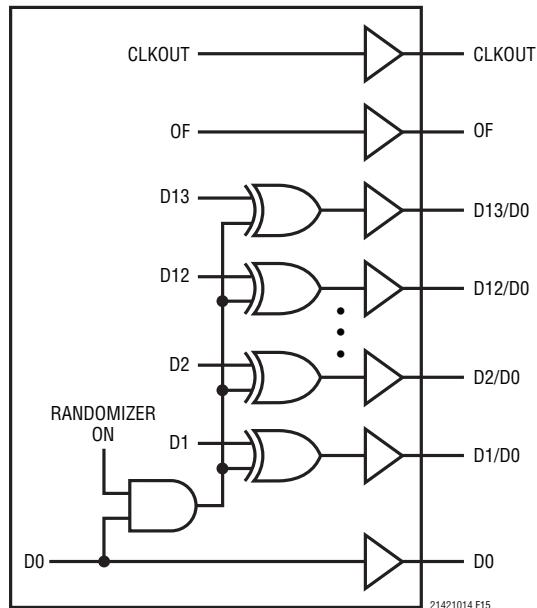

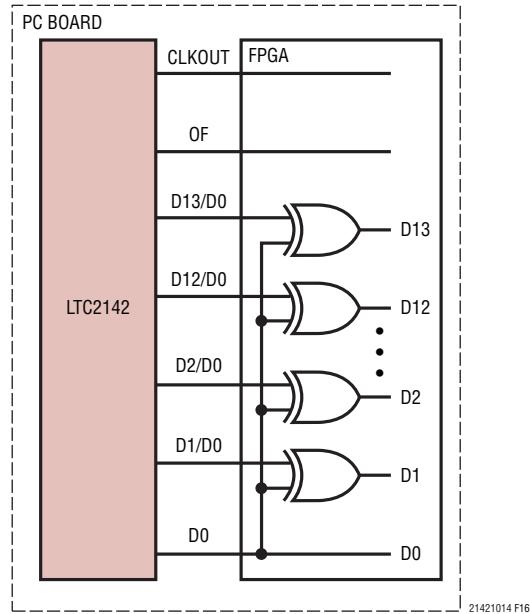

### デジタル出力ランダマイザ

A/Dコンバータのデジタル出力からの干渉は、場合によっては避けられません。デジタルの干渉は、容量性や誘導性の結合またはグランド・プレーンを介した結合から生じる可能性があります。結合係数がきわめて小さい場合でも、A/Dコンバータの出力スペクトルに不要なトーンが発生することがあります。デジタル出力をデバイスから伝送する前にランダム化することにより、これらの不要なトーンをランダム化し、それによって不要なトーン振幅を減少させることができます。

デジタル出力は、LSBと他のすべてのデータ出力ビットとの間で排他的論理和演算を行うことによってランダム化されます。デコードするには逆の演算を行います。つまり、LSBと他のすべてのビットとの間で排他的論理和演算を行います。LSB、OF、およびCLKOUTの各出力は影響を受けません。モード制御レジスタA4を連続的にプログラムすることにより、出力ランダマイザをイネーブルすることができます。

### 交互ビット極性

回路基板のデジタル帰還を減らすもうひとつの機能は交互ビット極性モードです。このモードがイネーブルされると、すべての奇数ビット(D1、D3、D5、D7、D9、D11、D13)が出力バッファの前で反転します。偶数ビット(D0、D2、D4、D6、D8、D10、D12)、OFおよびCLKOUTは影響を受けません。これにより、回路基板のグランド・プレーンのデジタル電流を減らし、(特に非常に小さなアナログ入力信号の場合)デジタル・ノイズを減らすことができます。

A/Dコンバータの入力にミッドスケール付近を中心とした微小信号があると、デジタル出力はほとんどのビットが1の状態とほとんどのビットが0の状態との間で切り換わります。このようにほとんどのビットが同時に切り換わると、大電流がグランド・プレーンに流れます。交互ビット極性モードでは、ビットを1つおきに反転することにより、全ビットの半数が“H”に遷移し、同時に全ビットの半数が“L”に遷移します。これにより、グランド・プレーンの電流が打ち消され、デジタル・ノイズが減少します。

デジタル出力は、奇数ビット(D1、D3、D5、D7、D9、D11、D13)を反転することにより、レシーバでデコードされます。交互ビット極性モードはデジタル出力ランダマイザからは独立しています。つまり、どちらか一方の機能をオンすることも、両方の機能を同時にオンすることも、両方の機能を同時にオフすることも可能です。交互ビット極性モードは、モード制御レジスタA4を連続的にプログラムすることによってイネーブルされます。

図15. デジタル出力ランダマイザの等価機能

図16. ランダム化されたデジタル出力信号の復元

## アプリケーション情報

### デジタル出力のテストパターン

A/Dコンバータへのデジタル・インターフェースを回路内でテストできるようにするために、A/Dコンバータのデータ出力(OF、D13～D0)を強制的に既知の値にするいくつかのテスト・モードがあります。

オール1:すべての出力が1

オール0:すべての出力が0

交互:サンプルの出力がオール1からオール0に交互に変化する。

格子縞:サンプルの出力が101010101010101から0101010101010に交互に変化する。

デジタル出力のテスト・パターンは、モード制御レジスタA4を連続的にプログラムすることによってイネーブルされます。テスト・パターンがイネーブルされると、その他の形式設定モード(2の補数、ランダマイザ、交互ビット極性)はすべて無効になります。

### 出力のディスエーブル

デジタル出力はモード制御レジスタA3を連続的にプログラムすることによってディスエーブルすることができます。OFおよびCLKOUTを含むすべてのデジタル出力がディスエーブルされます。高インピーダンスのディスエーブル・ステートは、インサーキット・テストまたは長期間の休止状態のためのものであり、複数のコンバータ間でデータ・バスをフルスピードで多重化するには遅すぎて使えません。出力をディスエーブルするときは、両方のチャネルをスリープ・モードまたはナップ・モードにしてください。

### スリープ・モードとナップ・モード

節電のため、A/Dコンバータをスリープ・モードまたはナップ・モードにすることができます。スリープ・モードでは、デバイス全体がパワーダウンし、消費電力は1mWになります。スリープ・モードから復帰するために必要な時間は、V<sub>REF</sub>、REFH、およびREFLのバイパス・コンデンサのサイズによって異なります。図8の推奨値の場合、A/Dコンバータは2ms後に安定します。

ナップ・モードでは、A/Dコンバータのコアはパワーダウンしますが、内部リファレンス回路はアクティブなままで、スリープ・モードより素早く起動することができます。ナップ・モードからの復帰には、少なくとも100クロック・サイクルが必要です。非常に正確なDCセトリングが必要なアプリケーションの場合は、

50μsを追加することにより、A/Dコンバータがナップ・モードから移行するときの電源電流の変化によって生じるわずかな温度変化に対して、内蔵リファレンスが安定状態に戻ることができます。チャネル2または両方のチャネルをナップ・モードにすることはできますが、チャネル1をナップ・モードにしてチャネル2を通常動作させることはできません。

スリープ・モードとナップ・モードは、モード制御レジスタA1(シリアル・プログラミング・モード)またはSDIとSDO(パラレル・プログラミング・モード)によってイネーブルされます。

### デバイスのプログラミング・モード

LTC2142-14/LTC2141-14/LTC2140-14の動作モードは、パラレル・インターフェースと簡素なシリアル・インターフェースのいずれでもプログラムできます。シリアル・インターフェースの方が柔軟性が高く、選択可能なすべてのモードをプログラムできます。パラレル・インターフェースには制限が多く、プログラムできるのはよく使用される一部のモードのみです。

### パラレル・プログラミング・モード

パラレル・プログラミング・モードを使用するには、PAR/SERをV<sub>DD</sub>に接続します。CS、SCK、SDIおよびSDOの各ピンは、特定の動作モードを設定するバイナリ・ロジック入力です。これらのピンはV<sub>DD</sub>またはグランドに接続するか、あるいは1.8V、2.5V、または3.3VのCMOSロジックでドライブすることができます。入力として使用する場合、SDOは1kの直列抵抗を介してドライブします。CS、SCK、SDI、およびSDOで設定されるモードを表2に示します。

表2. パラレル・プログラミング・モード制御ビット

(PAR/SER = V<sub>DD</sub>)

| ピン      | 説明                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------|

| CS      | クロック・デューティ・サイクル・スタビライザ制御ビット<br>0=クロック・デューティ・サイクル・スタビライザをオフ<br>1=クロック・デューティ・サイクル・スタビライザをオン                      |

| SCK     | デジタル出力モード制御ビット<br>0=フルレート CMOS 出力モード<br>1=ダブルデータレート LVDS 出力モード<br>(LVDS 電流は3.5mA、内部終端はオフ)                      |

| SDI/SDO | パワーダウン制御ビット<br>00=通常動作<br>01=チャネル1は通常動作、チャネル2はナップ・モード<br>10=チャネル1、チャネル2ともナップ・モード<br>11=スリープ・モード(デバイス全体がパワーダウン) |

## アプリケーション情報

### シリアル・プログラミング・モード

シリアル・プログラミング・モードを使用するには、PAR/SERをグランドに接続します。CS、SCK、SDIおよびSDOの各ピンは、A/Dコンバータのモード制御レジスタをプログラムするシリアル・インターフェースになります。データは16ビットのシリアル・ワードでレジスタに書き込まれます。レジスタの内容を検証するため、データをレジスタから読み出すこともできます。

シリアル・データ転送はCSが“L”になると開始されます。SDIピンのデータは、SCKの先頭から16番目までの立ち上がりエッジでラッチされます。先頭から16番目より後のSCK立ち上がりエッジは無視されます。データ転送はCSが再度“H”になると終了します。

16ビットの入力ワードの先頭ビットはR/Wビットです。次の7ビットはレジスタのアドレス(A6:A0)です。最後の8ビットはレジスタのデータ(D7:D0)です。

R/Wビットが“L”的場合、シリアル・データ(D7:D0)はアドレス・ビット(A6:A0)で設定されるレジスタに書き込まれます。R/Wビットが“H”的場合は、アドレス・ビット(A6:A0)によって設定されるレジスタ内のデータがSDOピンで読み出されます(タイミング図を参照)。読み出しコマンドの実行中、レジスタは更新されず、SDIのデータは無視されます。

SDOピンはオープン・ドレイン出力で、 $200\Omega$ のインピーダンスでグランド電位まで引き込みます。SDOを介してレジスタのデータを読み出す場合は、2kの外付けプルアップ抵抗が必要です。シリアル・データが書き込み専用で読み出す必要がない場合は、SDOをフロート状態のままにしてもかまわないと、プルアップ抵抗は不要です。

モード制御レジスタのマップを表3に示します。

### ソフトウェア・リセット

シリアル・プログラミングを使用する場合には、電源を投入して安定した後できるだけ早くモード制御レジスタをプログラムします。最初のシリアル・コマンドは、すべてのレジスタのデータ・ビットをロジック0にリセットするソフトウェア・リセットにする必要があります。ソフトウェア・リセットを実行するため、リセット・レジスタのビットD7にはロジック1を書き込みます。リセットSPI書き込みコマンドの完了後、ビットD7は自動的に0に戻ります。

### 接地とバイパス

LTC2142-14/LTC2141-14/LTC2140-14には、切れ目のないきれいなグランド・プレーンを備えたプリント回路基板が必要です。A/Dコンバータの下の最初の層には内部グランド・プレーンを備えた多層基板を推奨します。プリント回路基板のレイアウトでは、デジタル信号線とアナログ信号線をできるだけ離すようにします。特に、デジタル・トラックをアナログ信号トラックと並べて配置したり、A/Dコンバータの下に配置したりしないように注意してください。

V<sub>DD</sub>、OV<sub>DD</sub>、V<sub>CIM</sub>、V<sub>REF</sub>、REFH、REFLの各ピンには、高品質のセラミック・バイпас・コンデンサを使用します。バイパス・コンデンサは、できるだけピンの近くに配置する必要があります。サイズが0402のセラミック・コンデンサを推奨します。ピンとバイパス・コンデンサを接続するトレースは短くしておく必要があります、幅はできるだけ広くします。

特に重要なのは、REFHとREFLの間に配置するコンデンサです。このコンデンサは、A/Dコンバータと同じ側の回路基板上で、できるだけデバイスの近くに配置します。

アナログ入力、エンコード信号、およびデジタル出力は互いに隣接しないように配線します。これらの信号を互いに分離するためのバリヤとして、グランド領域とグランド・ビアを使用します。

### 熱伝達

LTC2142-14/LTC2141-14/LTC2140-14によって発生する熱の大半は、ダイから底面の背面パッドとパッケージのリードを通じて、プリント回路基板に伝達されます。優れた電気的性能と熱性能を得るには、プリント回路基板上にある大きな接地パッドに背面パッドを半田付けする必要があります。このパッドは、多数のビアで内部のグランド・プレーンに接続します。

## アプリケーション情報

表3. シリアル・プログラミング・モードのレジスタ・マップ(**PAR/SER = GND**)

レジスタ A0:リセット・レジスタ(アドレス 00h)

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------|----|----|----|----|----|----|----|

| RESET | X  | X  | X  | X  | X  | X  | X  |

ビット7      **RESET**      ソフトウェア・リセット・ビット

0=不使用

1=ソフトウェア・リセット。すべてのモード制御レジスタが00hにリセットされる。A/Dコンバータは一時的にスリープ・モードになる。このビットはSPI書き込みコマンドの終了時に自動的にゼロに戻る。リセット・レジスタは書き込み専用。リセット・レジスタからのデータの読み出しがランダムとなる。

ビット6~0      使用されない、ドントケア・ビット

レジスタ A1:パワーダウン・レジスタ(アドレス 01h)

| D7 | D6 | D5 | D4 | D3 | D2 | D1      | D0      |

|----|----|----|----|----|----|---------|---------|

| X  | X  | X  | X  | X  | X  | PWR0FF1 | PWR0FF0 |

ビット7~2      使用されない、ドントケア・ビット

ビット1~0      **PWR0FF1:PWR0FF0**      パワーダウン制御ビット

00=通常動作

01=チャネル1は通常動作、チャネル2はナップ・モード

10=チャネル1、チャネル2ともナップ・モード

11=スリープ・モード

レジスタ A2:タイミング・レジスタ(アドレス 02h)

| D7 | D6 | D5 | D4 | D3     | D2        | D1        | D0  |

|----|----|----|----|--------|-----------|-----------|-----|

| X  | X  | X  | X  | CLKINV | CLKPHASE1 | CLKPHASE0 | DCS |

ビット7~4      使用されない、ドントケア・ビット

ビット3      **CLKINV**      出力クロック反転ビット

0=通常のCLKOUT極性(タイミング図参照)

1=反転したCLKOUT極性

ビット2~1      **CLKPHASE1:CLKPHASE0**      出力クロックの位相遅延ビット

00=CLKOUT遅延なし(タイミング図参照)

01=CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup>を45°(クロック周期・1/8)だけ遅延

10=CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup>を90°(クロック周期・1/4)だけ遅延

11=CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup>を135°(クロック周期・3/8)だけ遅延

注記: CLKOUT位相遅延機能を使う場合は、クロック・デューティ・サイクル・スタビライザもオンする必要がある

ビット0      **DCS**      クロック・デューティ・サイクル・スタビライザ・ビット

0=クロック・デューティ・サイクル・スタビライザをオフ

1=クロック・デューティ・サイクル・スタビライザをオン

# LTC2142-14/ LTC2141-14/LTC2140-14

---

## アプリケーション情報

### レジスタA3:出力モード・レジスタ(アドレス03h)

| D7 | D6     | D5     | D4     | D3     | D2     | D1       | D0       |

|----|--------|--------|--------|--------|--------|----------|----------|

| X  | ILVDS2 | ILVDS1 | ILVDS0 | TERMON | OUTOFF | OUTMODE1 | OUTMODE0 |

- ビット7 使用されない、ドントケア・ビット

- ビット6～4 **ILVDS2:ILVDS0** LVDS出力電流ビット

000 = 3.5mAのLVDS出力ドライバ電流

001 = 4.0mAのLVDS出力ドライバ電流

010 = 4.5mAのLVDS出力ドライバ電流

011 = 不使用

100 = 3.0mAのLVDS出力ドライバ電流

101 = 2.5mAのLVDS出力ドライバ電流

110 = 2.1mAのLVDS出力ドライバ電流

111 = 1.75mAのLVDS出力ドライバ電流

- ビット3 **TERMON** LVDS内部終端ビット

0 = 内部終端をオフ

1 = 内部終端をオン。LVDS出力ドライバ電流はILVDS2:ILVDS0によって設定される電流の2倍

- ビット2 **OUTOFF** 出力のディスエーブル・ビット

0 = デジタル出力をイネーブル

1 = デジタル出力をディスエーブルし、出力を高インピーダンスにする

注記: デジタル出力をディスエーブルする場合は、デバイスもスリープ・モードまたはナップ・モードにする(両チャネルとも)。

- ビット1～0 **OUTMODE1:OUTMODE0** デジタル出力モード制御ビット

00 = フルレートCMOS出力モード

01 = ダブルデータレートLVDS出力モード

10 = ダブルデータレートCMOS出力モード

11 = 不使用

### レジスタA4:データ・フォーマット・レジスタ(アドレス04h)

| D7 | D6 | D5       | D4       | D3       | D2  | D1   | D0       |

|----|----|----------|----------|----------|-----|------|----------|

| X  | X  | OUTTEST2 | OUTTEST1 | OUTTEST0 | ABP | RAND | TWOSCOMP |

- ビット7～6 使用されない、ドントケア・ビット

- ビット5～3 **OUTTEST2:OUTTEST0** デジタル出力のテスト・パターン・ビット

000 = デジタル出力のテスト・パターンをオフ

001 = すべてのデジタル出力 = 0

011 = すべてのデジタル出力 = 1

101 = 格子縞出力パターン。OF、D13～D0は101 0101 0101 0101と0 10 1010 1010 1010を交互に出力

111 = 交互出力パターン。OF、D13～D0は0 00 0000 0000 0000と1 11 1111 1111 1111を交互に出力

注記: 他のビットの組み合わせは使用されない

- ビット2 **ABP** 交互ビット極性モード制御ビット

0 = 交互ビット極性モードをオフ

1 = 交互ビット極性モードをオン。出力形式を強制的にオフセット・バイナリにする

- ビット1 **RAND** データ出力ランダマイザ・モード制御ビット

0 = データ出力ランダマイザ・モードをオフ

1 = データ出力ランダマイザ・モードをオン

- ビット0 **TWOSCOMP** 2の補数モード制御ビット

0 = オフセット・バイナリのデータ形式

1 = 2の補数のデータ形式

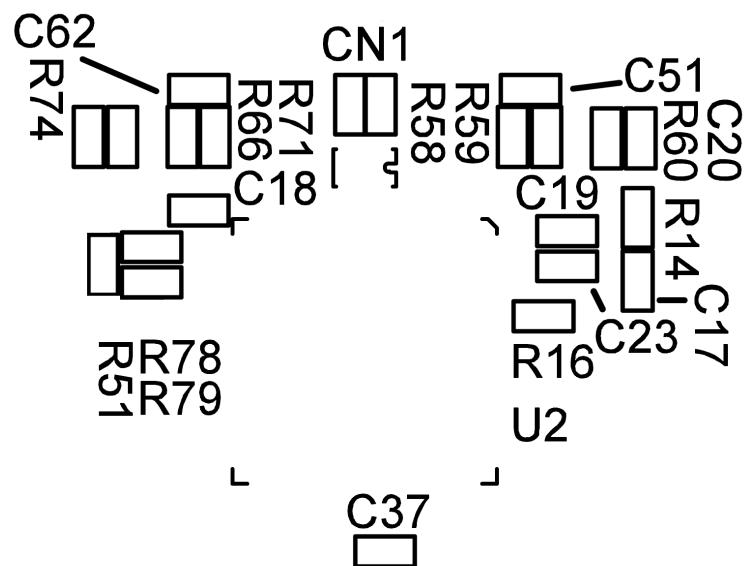

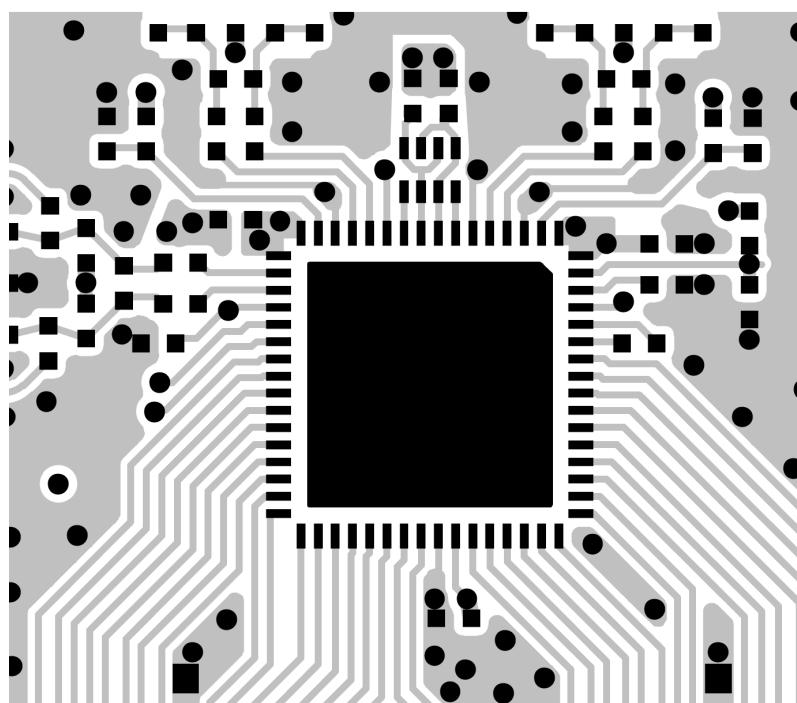

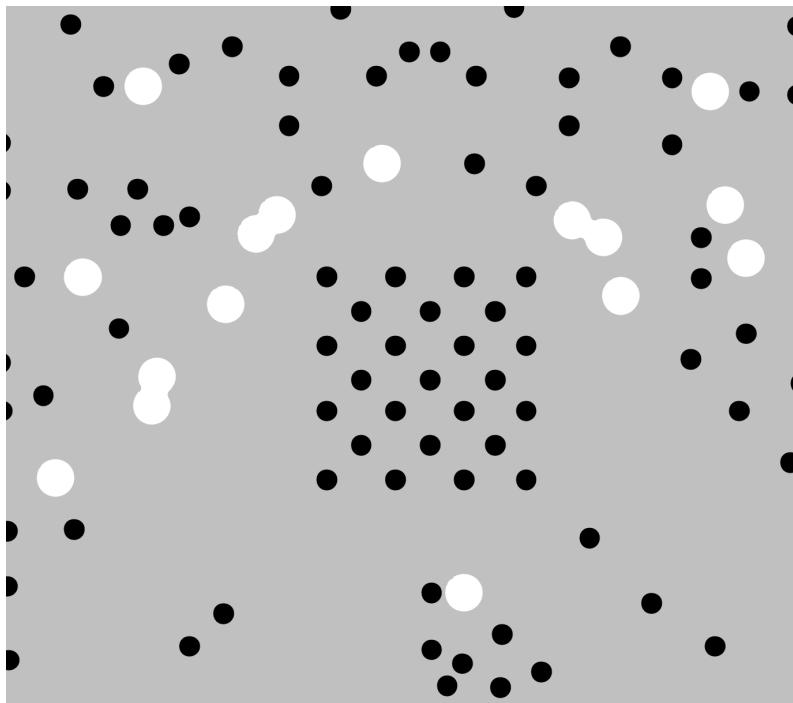

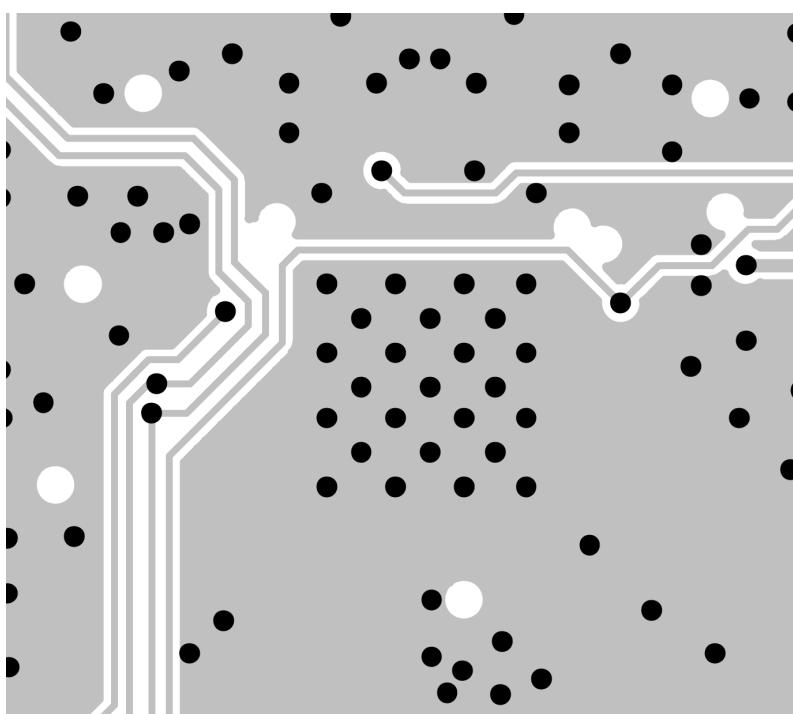

標準的応用例

部品面シルク

上面

21421014fa

標準的應用例

內部第2層(GND)

內部第3層

21421014fa

標準的應用例

內部第4層

內部第5層(電源)

21421014fa

標準的應用例

標準的應用例

LTC2142 回路図

LTC2142-14/

LTC2141-14/LTC2140-14

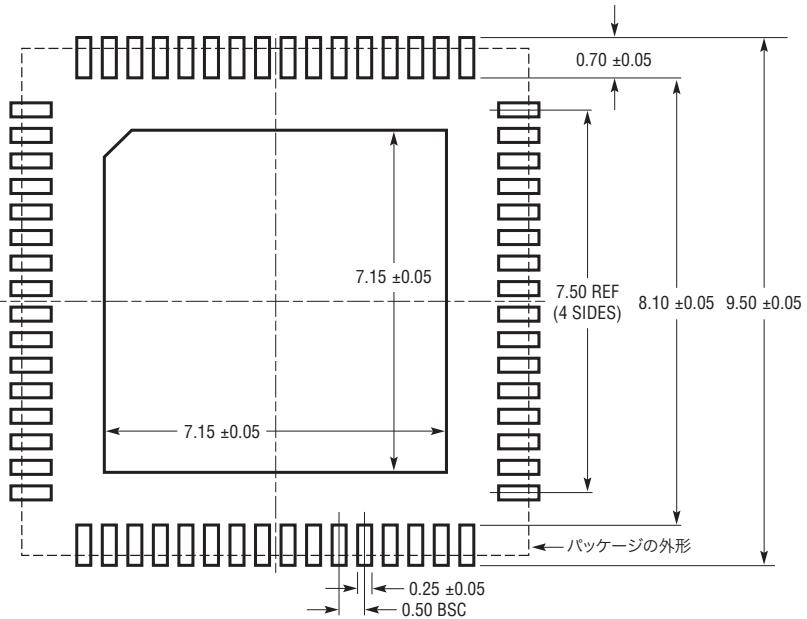

## パッケージ

**UPパッケージ

64ピン・プラスチックQFN(9mm×9mm)

(Reference LTC DWG # 05-08-1705 Rev C)**

推奨する半田パッドのピッチと寸法

半田付けされない領域には半田マスクを使用する

**NOTE:**

1. 図面は JEDEC のパッケージ外形 MO-220 のバリエーション(WNJR-5)に適合

2. 全ての寸法はミリメートル

3. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.20mm を超えないこと

4. 露出パッドは半田メッキとする

5. 網掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

6. 図は実寸とは異なる

### 底面図ー露出パッド

## 改訂履歴

| REV | 日付   | 概要                                 | ページ番号 |

|-----|------|------------------------------------|-------|

| A   | 7/12 | チャネル1データバス(D1_*)のピン説明で「チャネル1」に記述修正 | 16    |

# LTC2142-14/ LTC2141-14/LTC2140-14

## 標準的応用例

2トーンFFT、f<sub>IN</sub> = 70MHzおよび69MHz

## 関連製品

| 製品番号                                 | 説明                                                     | 注釈                                                                                  |

|--------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------|

| <b>A/Dコンバータ</b>                      |                                                        |                                                                                     |

| LTC2259-14/LTC2260-14/<br>LTC2261-14 | 14ビット、80Msps/105Msps/125Msps、<br>1.8V動作のADC、超低消費電力     | 89mW/106mW/127mW、SNR: 73.4dB、SFDR: 85dB、DDR LVDS/<br>DDR CMOS/CMOS出力、6mm×6mm QFN-40 |

| LTC2262-14                           | 14ビット、150Msps、1.8V動作のADC、<br>超低消費電力                    | 149mW、SNR: 72.8dB、SFDR: 88dB、DDR LVDS/DDR CMOS/<br>CMOS出力、6mm×6mm QFN-40            |

| LTC2266-14/LTC2267-14/<br>LTC2268-14 | 14ビット、80Msps/105Msps/125Msps、<br>1.8V動作のデュアルADC、超低消費電力 | 203mW/243mW/299mW、SNR: 73.1dB、SFDR: 88dB、<br>シリアルLVDS出力、6mm×6mm QFN-40              |

| LTC2266-12/LTC2267-12/<br>LTC2268-12 | 12ビット、80Msps/105Msps/125Msps、<br>1.8V動作のデュアルADC、超低消費電力 | 200mW/238mW/292mW、SNR: 70.6dB、SFDR: 88dB、<br>シリアルLVDS出力、6mm×6mm QFN-40              |

| <b>RFミキサ/復調器</b>                     |                                                        |                                                                                     |

| LT5517                               | 40MHz～900MHz直接変換直交復調器                                  | 高いIIP3: 800MHzで21dBm、LO直交ジェネレータ内蔵                                                   |

| LT5557                               | 400MHz～3.8GHz高直線性ダウントンバーティング・ミキサ                       | IIP3は2.6GHzで23.7dBm、3.5GHzで23.5dBm、NF = 13.2dB、<br>3.3V電源動作、トランジスタ内蔵                |

| LT5575                               | 800MHz～2.7GHz直接変換直交復調器                                 | 高いIIP3: 900MHzで28dBm、LO直交ジェネレータ内蔵、<br>RFおよびLOトランジスタ内蔵                               |

| <b>アンプ/フィルタ</b>                      |                                                        |                                                                                     |

| LTC6412                              | 800MHz、31dBレンジ、アナログ制御VGA                               | 連続調整可能な利得制御、240MHzでのOIP3: 35dBm、<br>ノイズフィギュア: 10dB、4mm×4mm QFN-24                   |

| LTC6605-7/LTC6605-10/<br>LTC6605-14  | ADCドライバ付きの整合したデュアル<br>7MHz/10MHz/14MHzフィルタ             | 差動ドライバ付きの整合された2個の2次ローパス・フィルタ、<br>ピンでプログラム可能な利得、6mm×3mm DFN-22                       |

| <b>シグナルチェーン・レシーバ</b>                 |                                                        |                                                                                     |

| LTM9002                              | 14ビット・デュアル・チャネルIF/<br>ベースバンド・レシーバ・サブシステム               | 高速ADC、パッシブ・フィルタ、固定利得差動アンプを内蔵                                                        |

21421014fa