## 特長

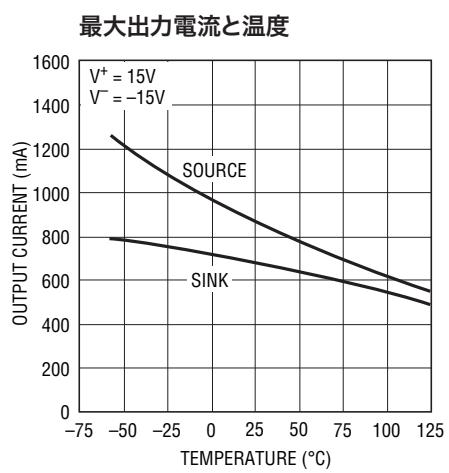

- 最小出力電流:  $\pm 500\text{mA}$

- 個別に調整可能なソースおよびシンク電流制限

- 電流制限精度: 2%

- 単一電源または両電源で動作

- シャットダウン/イネーブル制御入力

- オープン・コレクタ・ステータス・フラグ:

- シンク電流制限

- ソース電流制限

- サーマル・シャットダウン

- フェール・セーフ電流制限とサーマル・シャットダウン

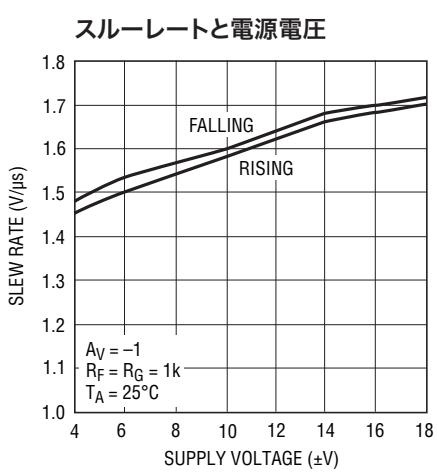

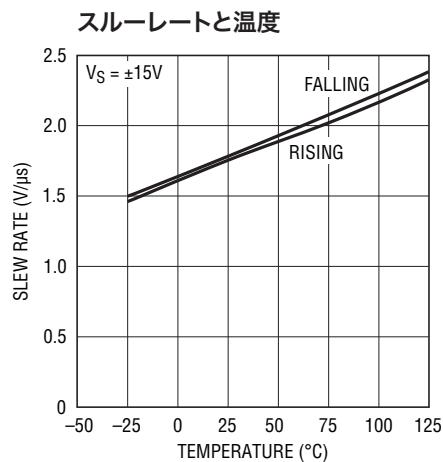

- スルーレート:  $1.6\text{V}/\mu\text{s}$

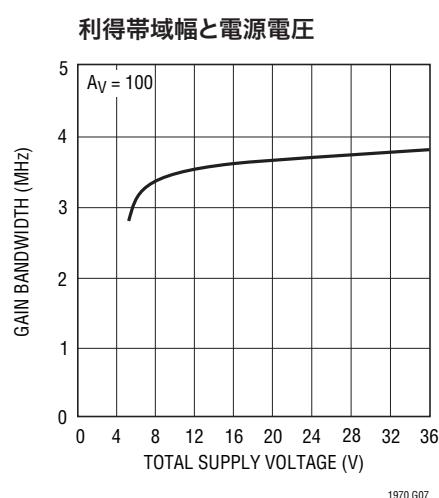

- 利得帯域幅積:  $3.6\text{MHz}$

- 速い電流制限応答:  $2\text{MHz}$  の帯域幅

- 規定温度範囲:  $-40^\circ\text{C} \sim 85^\circ\text{C}$

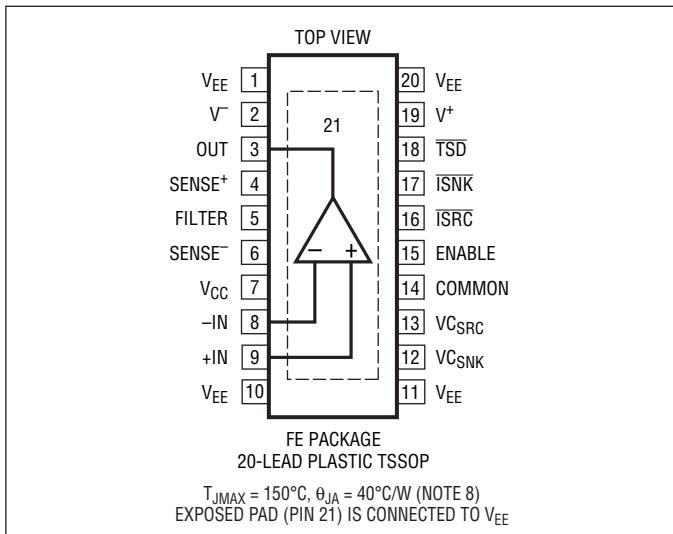

- 20ピンTSSOPパッケージで供給

## アプリケーション

- 自動テスト装置

- ラボ用電源

- モータ・ドライバ

- 熱電冷却器ドライバ

LT、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

## 概要

LT<sup>®</sup>1970は、外部制御の高精度電流制限機能を搭載した $\pm 500\text{mA}$ パワー・オペアンプです。個別の電流制御によって、ソースおよびシンク電流制限検知のスレッショルドを2%精度でプログラムします。外付けパワー・トランジスタを追加することにより、出力電流を増やすことができます。

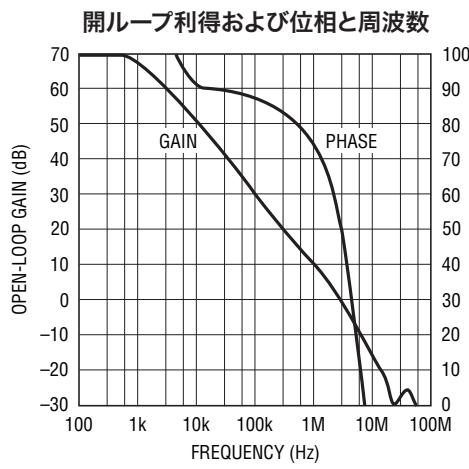

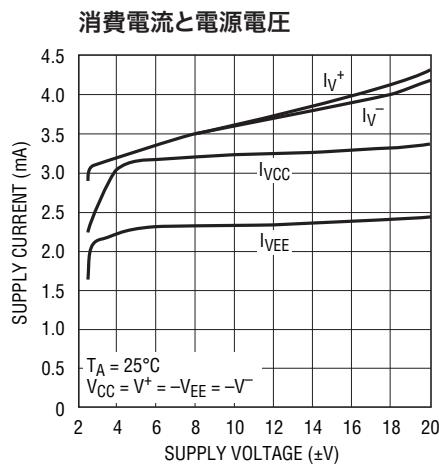

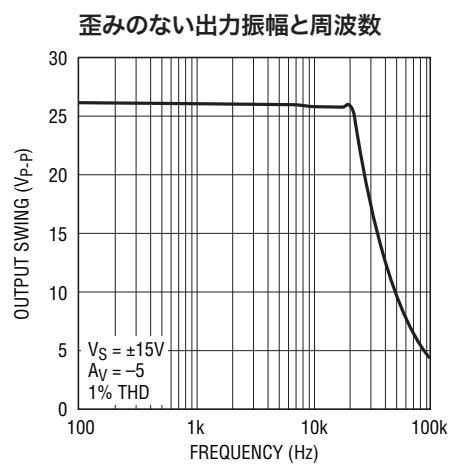

このデバイスは、総電源電圧が5V～36Vの単一または両電源で動作します。通常動作では、入力段の電源と出力段の電源が接続されています( $V_{CC}$ が $V^+$ に、 $V_{EE}$ が $V^-$ に接続)。より低電圧の独立電源から出力段( $V^+$ 、 $V^-$ )に電力を供給することで、消費電力を低減することができます。このアンプはユニティ・ゲイン安定で、利得帯域幅積が3.6MHz、スルーレートが $1.6\text{V}/\mu\text{s}$ です。電流制限回路は、 $VC_{SRC}$ または $VC_{SNK}$ 制御入力とアンプ出力との間の2MHz応答を実現します。

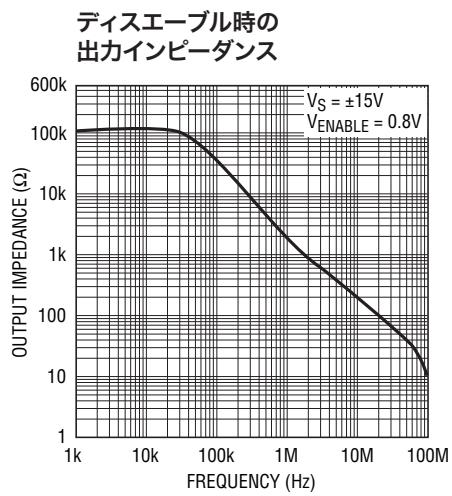

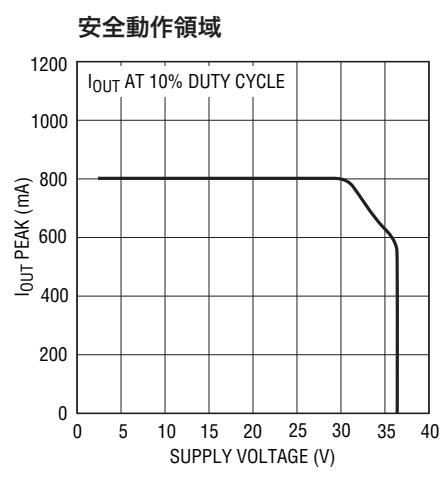

オープン・コレクタ・ステータス・フラグは、電流制限回路がアクティブになっていることと、アンプのサーマル・シャットダウンを知らせます。イネーブル・ロジック入力が "L" になると、アンプは低電力、高インピーダンス出力状態になります。サーマル・シャットダウンと $\pm 800\text{mA}$ 固定電流制限により、フォールト状態においてチップを保護できます。

LT1970は熱伝導銅底板によって放熱を容易にした20ピンTSSOPパッケージで供給されます。

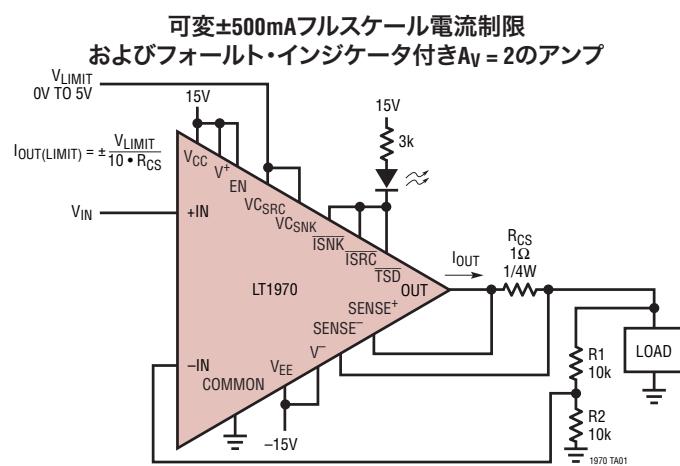

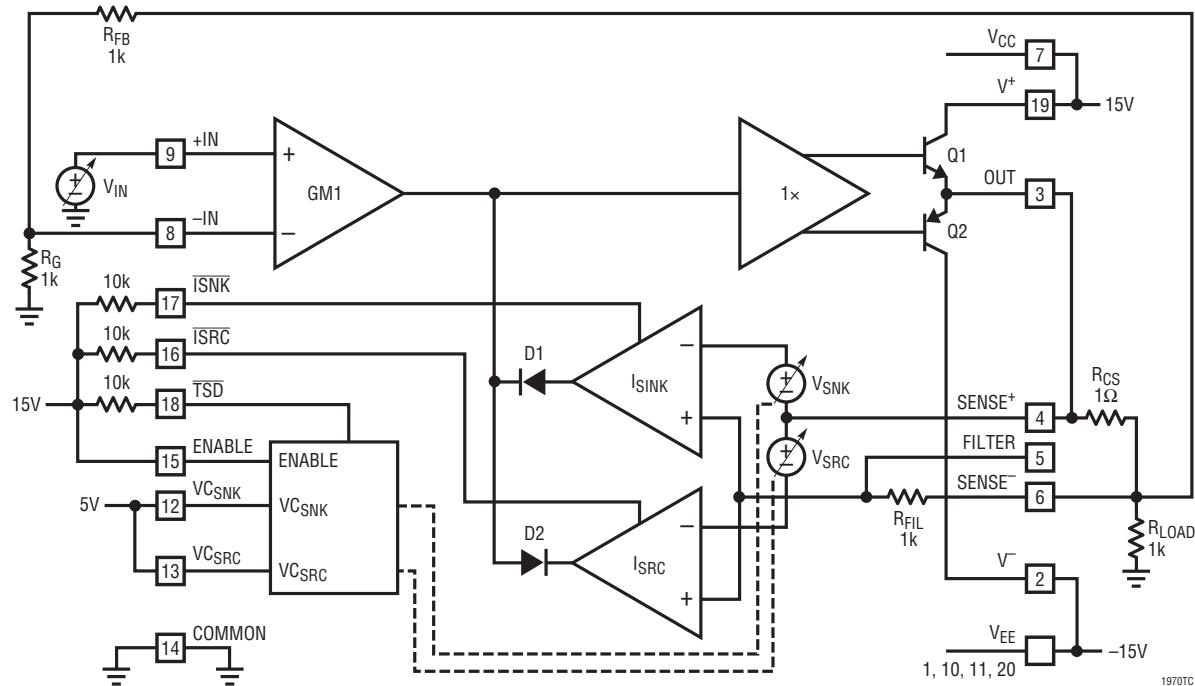

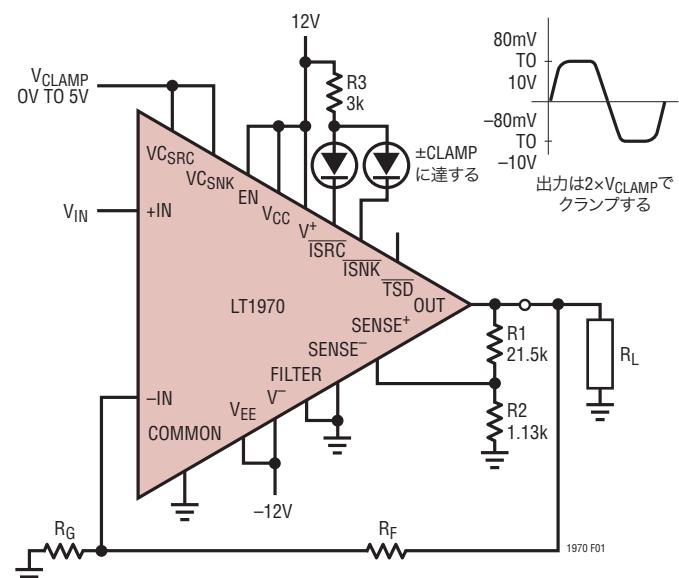

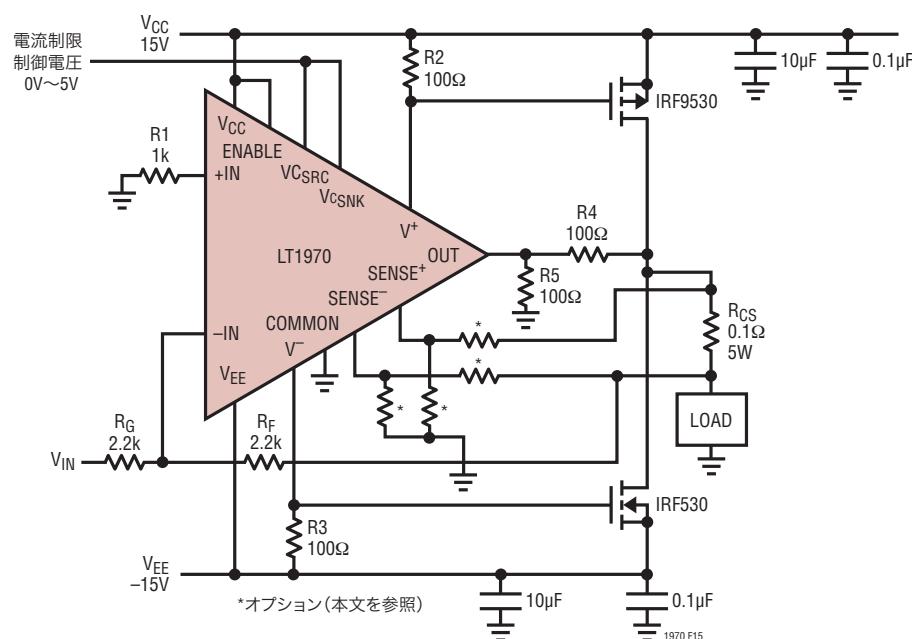

## 標準的応用例

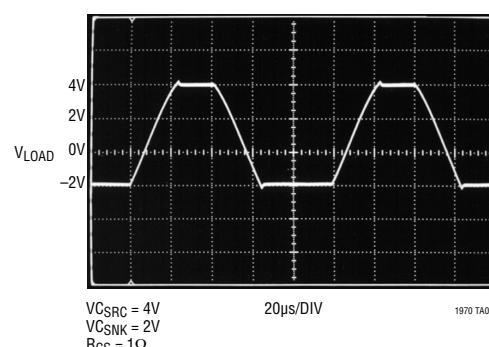

電流を制限された10Ω負荷への正弦波

## 絶対最大定格

(Note 1)

|                                                                     |                                   |

|---------------------------------------------------------------------|-----------------------------------|

| 電源電圧 ( $V_{CC}$ から $V_{EE}$ )                                       | 36V                               |

| 正高電流電源 ( $V^+$ )                                                    | $V^- \sim V_{CC}$                 |

| 負高電流電源 ( $V^-$ )                                                    | $V_{EE} \sim V^+$                 |

| アンプ出力 (OUT)                                                         | $V^- \sim V^+$                    |

| 電流検出ピン                                                              |                                   |

| (SENSE <sup>+</sup> 、SENSE <sup>-</sup> 、FILTER)                    | $V^- \sim V^+$                    |

| ロジック出力 ( $\overline{ISRC}$ 、 $\overline{ISNK}$ 、 $\overline{TSD}$ ) | COMMON～ $V_{CC}$                  |

| 入力電圧 (-IN、+IN)                                                      | $V_{EE} - 0.3V \sim V_{EE} + 36V$ |

| 入力電流                                                                | 10mA                              |

| 電流制御入力                                                              |                                   |

| ( $VC_{SRC}$ 、 $VC_{SNK}$ )                                         | COMMON～COMMON+7V                  |

| イネーブル・ロジック入力                                                        | COMMON～ $V_{CC}$                  |

| COMMON                                                              | $V_{EE} \sim V_{CC}$              |

| 出力短絡時間                                                              | 無期限                               |

| 動作温度範囲 (Note 2)                                                     | -40°C～85°C                        |

| 規定温度範囲 (Note 3)                                                     | -40°C～85°C                        |

| 最大接合部温度                                                             | 150°C                             |

| 保存温度範囲                                                              | -65°C～150°C                       |

| リード温度 (半田付け、10秒)                                                    | 300°C                             |

## ピン配置

## 発注情報

| 無鉛仕上げ        | テープアンドリール | 製品マーキング*  | パッケージ                 | 規定温度範囲        |

|--------------|-----------|-----------|-----------------------|---------------|

| LT1970#TRPBF | LT1970#TR | LT1970CFE | 20-Lead Plastic TSSOP | -40°C to 85°C |

| LT1970#TRPBF | LT1970#TR | LT1970IFE | 20-Lead Plastic TSSOP | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

\*温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$ での値。標準テスト条件についてはテスト回路を参照。

| SYMBOL              | PARAMETER                           | CONDITIONS                                                                                 | MIN    | TYP                 | MAX                 | UNITS                                           |

|---------------------|-------------------------------------|--------------------------------------------------------------------------------------------|--------|---------------------|---------------------|-------------------------------------------------|

| <b>パワー・オペアンプの特性</b> |                                     |                                                                                            |        |                     |                     |                                                 |

| $V_{OS}$            | Input Offset Voltage                | $0^\circ\text{C} < T_A < 70^\circ\text{C}$<br>$-40^\circ\text{C} < T_A < 85^\circ\text{C}$ | ●<br>● | 200<br>1000<br>1300 | 600<br>1000<br>1300 | $\mu\text{V}$<br>$\mu\text{V}$<br>$\mu\text{V}$ |

|                     | Input Offset Voltage Drift (Note 4) |                                                                                            | ●      | -10<br>-4           | 10                  | $\mu\text{V}/^\circ\text{C}$                    |

| $I_{OS}$            | Input Offset Current                | $V_{CM} = 0\text{V}$                                                                       | ●      | -100                | 100                 | nA                                              |

| $I_B$               | Input Bias Current                  | $V_{CM} = 0\text{V}$                                                                       | ●      | -600<br>-160        |                     | nA                                              |

|                     | Input Noise Voltage                 | 0.1Hz to 10Hz                                                                              |        |                     | 3                   | $\mu\text{V}_{\text{P-P}}$                      |

| $e_n$               | Input Noise Voltage Density         | 1kHz                                                                                       |        |                     | 15                  | $\text{nV}/\sqrt{\text{Hz}}$                    |

| $i_n$               | Input Noise Current Density         | 1kHz                                                                                       |        |                     | 3                   | $\text{pA}/\sqrt{\text{Hz}}$                    |

1970fc

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。標準テスト条件についてはテスト回路を参照。

| SYMBOL    | PARAMETER                    | CONDITIONS                                                                                                                                                                                                                                                                                                                      | MIN              | TYP                    | MAX                      | UNITS                                                    |                            |

|-----------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|--------------------------|----------------------------------------------------------|----------------------------|

| $R_{IN}$  | Input Resistance             | Common Mode<br>Differential Mode                                                                                                                                                                                                                                                                                                |                  | 500<br>100             |                          | $\text{k}\Omega$<br>$\text{k}\Omega$                     |                            |

| $C_{IN}$  | Input Capacitance            | Pin 8 and Pin 9 to Ground                                                                                                                                                                                                                                                                                                       |                  | 6                      |                          | $\text{pF}$                                              |                            |

| $V_{CM}$  | Input Voltage Range          | Typical<br>Guaranteed by CMRR Test                                                                                                                                                                                                                                                                                              | ●<br>●           | -14.5<br>-12.0         | 13.6<br>12.0             | $\text{V}$<br>$\text{V}$                                 |                            |

| CMRR      | Common Mode Rejection Ratio  | $-12\text{V} < V_{CM} < 12\text{V}$                                                                                                                                                                                                                                                                                             | ●                | 92                     | 105                      | $\text{dB}$                                              |                            |

| PSRR      | Power Supply Rejection Ratio | $V_{EE} = V^- = -5\text{V}, V_{CC} = V^+ = 3\text{V}$ to $30\text{V}$<br>$V_{EE} = V^- = -5\text{V}, V_{CC} = 30\text{V}, V^+ = 2.5\text{V}$ to $30\text{V}$<br>$V_{EE} = V^- = -3\text{V}$ to $-30\text{V}, V_{CC} = V^+ = 5\text{V}$<br>$V_{EE} = -30\text{V}, V^- = -2.5\text{V}$ to $-30\text{V}, V_{CC} = V^+ = 5\text{V}$ | ●<br>●<br>●<br>● | 90<br>110<br>90<br>110 | 100<br>130<br>100<br>130 | $\text{dB}$<br>$\text{dB}$<br>$\text{dB}$<br>$\text{dB}$ |                            |

| $A_{VOL}$ | Large-Signal Voltage Gain    | $R_L = 1\text{k}\Omega, -12.5\text{V} < V_{OUT} < 12.5\text{V}$                                                                                                                                                                                                                                                                 | ●                | 100<br>75              | 150                      | $\text{V}/\text{mV}$<br>$\text{V}/\text{mV}$             |                            |

|           |                              | $R_L = 100\Omega, -12.5\text{V} < V_{OUT} < 12.5\text{V}$                                                                                                                                                                                                                                                                       | ●                | 80<br>40               | 120                      | $\text{V}/\text{mV}$<br>$\text{V}/\text{mV}$             |                            |

|           |                              | $R_L = 10\Omega, -5\text{V} < V_{OUT} < 5\text{V}, V^+ = -V^- = 8\text{V}$                                                                                                                                                                                                                                                      | ●                | 20<br>5                | 45                       | $\text{V}/\text{mV}$<br>$\text{V}/\text{mV}$             |                            |

| $V_{OL}$  | Output Sat Voltage Low       | $V_{OL} = V_{OUT} - V^-$<br>$R_L = 100\Omega, V_{CC} = V^+ = 15\text{V}, V_{EE} = V^- = -15\text{V}$<br>$R_L = 10\Omega, V_{CC} = -V_{EE} = 15\text{V}, V^+ = -V^- = 5\text{V}$                                                                                                                                                 | ●                |                        | 1.9<br>0.8               | 2.5<br>$\text{V}$                                        |                            |

| $V_{OH}$  | Output Sat Voltage High      | $V_{OH} = V^+ - V_{OUT}$<br>$R_L = 100\Omega, V_{CC} = V^+ = 15\text{V}, V_{EE} = V^- = -15\text{V}$<br>$R_L = 10\Omega, V_{CC} = -V_{EE} = 15\text{V}, V^+ = -V^- = 5\text{V}$                                                                                                                                                 | ●                |                        | 1.7<br>1.0               | 2.3<br>$\text{V}$                                        |                            |

| $I_{SC}$  | Output Short-Circuit Current | Output Low, $R_{SENSE} = 0\Omega$<br>Output High, $R_{SENSE} = 0\Omega$                                                                                                                                                                                                                                                         |                  | 500<br>-1000           | 800<br>-800              | 1200<br>-500                                             | $\text{mA}$<br>$\text{mA}$ |

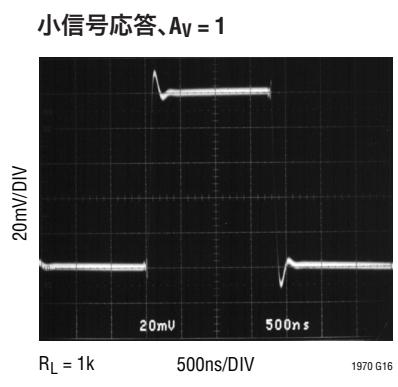

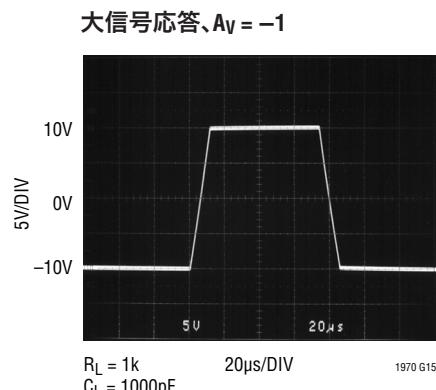

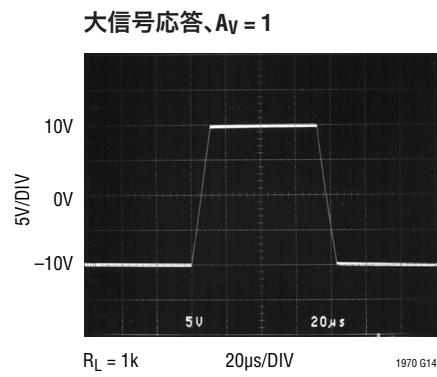

| SR        | Slew Rate                    | $-10\text{V} < V_{OUT} < 10\text{V}, R_L = 1\text{k}\Omega$                                                                                                                                                                                                                                                                     |                  | 0.7                    | 1.6                      |                                                          | $\text{V}/\mu\text{s}$     |

| FPBW      | Full Power Bandwidth         | $V_{OUT} = 10\text{V}_{\text{PEAK}}$ (Note 5)                                                                                                                                                                                                                                                                                   |                  | 11                     |                          |                                                          | $\text{kHz}$               |

| GBW       | Gain Bandwidth Product       | $f = 10\text{kHz}$                                                                                                                                                                                                                                                                                                              |                  |                        | 3.6                      |                                                          | $\text{MHz}$               |

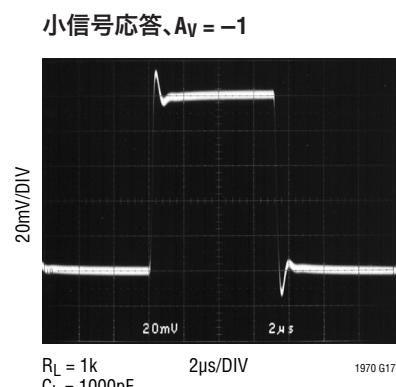

| $t_S$     | Settling Time                | $0.01\%, V_{OUT} = 0\text{V}$ to $10\text{V}, A_v = -1, R_L = 1\text{k}\Omega$                                                                                                                                                                                                                                                  |                  |                        | 8                        |                                                          | $\mu\text{s}$              |

## 電流検出の特性

|                                          |                                          |                                                      |        |            |            |            |               |  |

|------------------------------------------|------------------------------------------|------------------------------------------------------|--------|------------|------------|------------|---------------|--|

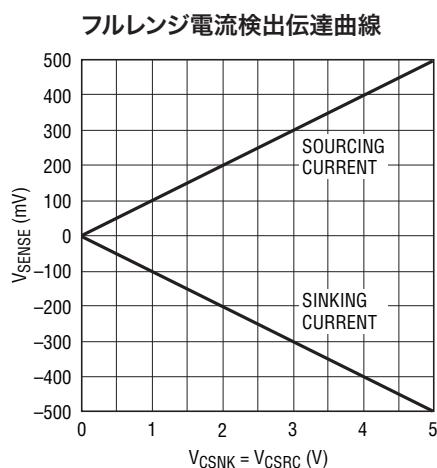

| $V_{SENSE(MIN)}$                         | Minimum Current Sense Voltage            | $V_{C_{SRC}} = V_{C_{SNK}} = 0\text{V}$              | ●<br>● | 0.1<br>0.1 | 4          | 7          | $\text{mV}$   |  |

| $V_{SENSE(4\%)}$                         | Current Sense Voltage 4% of Full Scale   | $V_{C_{SRC}} = V_{C_{SNK}} = 0.2\text{V}$            | ●      | 15         | 20         | 25         | $\text{mV}$   |  |

| $V_{SENSE(10\%)}$                        | Current Sense Voltage 10% of Full Scale  | $V_{C_{SRC}} = V_{C_{SNK}} = 0.5\text{V}$            | ●      | 45         | 50         | 55         | $\text{mV}$   |  |

| $V_{SENSE(FS)}$                          | Current Sense Voltage 100% of Full Scale | $V_{C_{SRC}} = V_{C_{SNK}} = 5\text{V}$              | ●<br>● | 490<br>480 | 500<br>500 | 510<br>520 | $\text{mV}$   |  |

| $I_{BI}$                                 | Current Limit Control Input Bias Current | $V_{C_{SRC}}, V_{C_{SNK}}$ Pins                      | ●      | -1         | -0.2       | 0.1        | $\mu\text{A}$ |  |

| $I_{SENSE^-}$                            | SENSE <sup>-</sup> Input Current         | $0\text{V} < (V_{C_{SRC}}, V_{C_{SNK}}) < 5\text{V}$ | ●      | -500       |            | 500        | $\text{nA}$   |  |

| $I_{FILTER}$                             | FILTER Input Current                     | $0\text{V} < (V_{C_{SRC}}, V_{C_{SNK}}) < 5\text{V}$ | ●      | -500       |            | 500        | $\text{nA}$   |  |

| $I_{SENSE^+}$                            | SENSE <sup>+</sup> Input Current         | $V_{C_{SRC}} = V_{C_{SNK}} = 0\text{V}$              | ●      | -500       |            | 500        | $\text{nA}$   |  |

|                                          |                                          | $V_{C_{SRC}} = 5\text{V}, V_{C_{SNK}} = 0\text{V}$   | ●      | 200        | 250        | 300        | $\mu\text{A}$ |  |

|                                          |                                          | $V_{C_{SRC}} = 0\text{V}, V_{C_{SNK}} = 5\text{V}$   | ●      | -300       | -250       | -200       | $\mu\text{A}$ |  |

|                                          |                                          | $V_{C_{SRC}} = V_{C_{SNK}} = 5\text{V}$              | ●      | -25        |            | 25         | $\mu\text{A}$ |  |

| Current Sense Change with Output Voltage |                                          |                                                      |        |            | $\pm 0.1$  |            | %             |  |

| Current Sense Change with Supply Voltage |                                          |                                                      |        |            | $\pm 0.05$ |            | %             |  |

|                                          |                                          |                                                      |        |            | $\pm 0.01$ |            | %             |  |

|                                          |                                          |                                                      |        |            | $\pm 0.05$ |            | %             |  |

|                                          |                                          |                                                      |        |            | $\pm 0.01$ |            | %             |  |

1970fc

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。標準テスト条件についてはテスト回路を参照。

| SYMBOL    | PARAMETER                   | CONDITIONS | MIN | TYP | MAX  | UNITS |          |

|-----------|-----------------------------|------------|-----|-----|------|-------|----------|

|           | Current Sense Bandwidth     |            |     | 2   |      | MHz   |          |

| $R_{CSF}$ | Resistance FILTER to SENSE- |            | ●   | 750 | 1000 | 1250  | $\Omega$ |

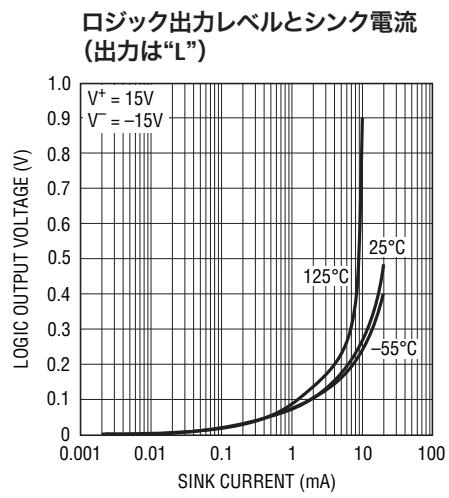

### ロジックI/Oの特性

|                              |                                                                                                    |                                                                                                  |   |     |     |               |   |

|------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---|-----|-----|---------------|---|

|                              | Logic Output Leakage $\overline{\text{ISRC}}$ , $\overline{\text{ISNK}}$ , $\overline{\text{TSD}}$ | $V = 15\text{V}$                                                                                 | ● | 1   |     | $\mu\text{A}$ |   |

|                              | Logic Low Output Level                                                                             | $I = 5\text{mA}$ (Note 6)                                                                        | ● | 0.2 | 0.4 | V             |   |

|                              | Logic Output Current Limit                                                                         |                                                                                                  |   | 25  |     | $\text{mA}$   |   |

| $V_{\text{ENABLE}}$          | Enable Logic Threshold                                                                             |                                                                                                  | ● | 0.8 | 1.9 | 2.5           | V |

| $I_{\text{ENABLE}}$          | Enable Pin Bias Current                                                                            |                                                                                                  | ● | -1  | 1   | $\mu\text{A}$ |   |

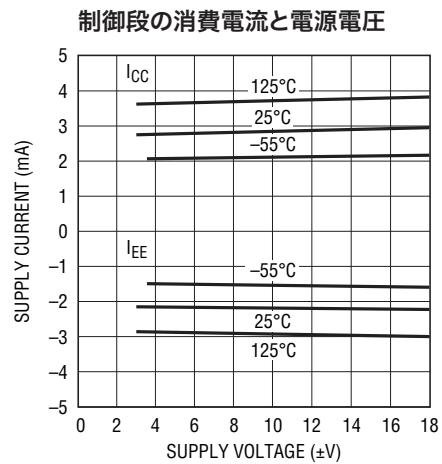

| $I_{\text{SUPPLY}}$          | Total Supply Current                                                                               | $V_{\text{CC}}, V^+$ and $V^-$ , $V_{\text{EE}}$ Connected                                       | ● | 7   | 13  | $\text{mA}$   |   |

| $I_{\text{CC}}$              | $V_{\text{CC}}$ Supply Current                                                                     | $V_{\text{CC}}, V^+$ and $V^-$ , $V_{\text{EE}}$ Separate                                        | ● | 3   | 7   | $\text{mA}$   |   |

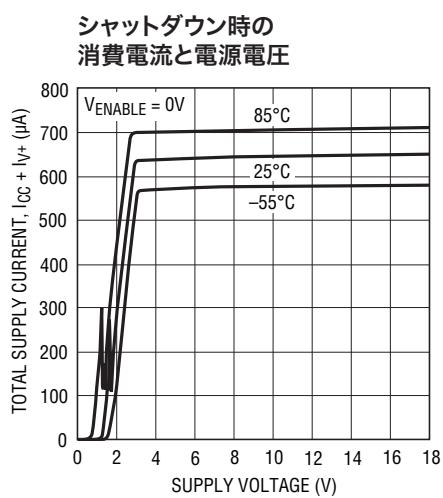

| $I_{\text{CC}(\text{STBY})}$ | Supply Current Disabled                                                                            | $V_{\text{CC}}, V^+$ and $V^-$ , $V_{\text{EE}}$ Connected, $V_{\text{ENABLE}} \leq 0.8\text{V}$ | ● | 0.6 | 1.5 | $\text{mA}$   |   |

| $t_{\text{ON}}$              | Turn-On Delay                                                                                      | (Note 7)                                                                                         |   |     | 10  | $\mu\text{s}$ |   |

| $t_{\text{OFF}}$             | Turn-Off Delay                                                                                     | (Note 7)                                                                                         |   |     | 10  | $\mu\text{s}$ |   |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

Note 2: LT1970Cは $-40^\circ\text{C}$ ～ $85^\circ\text{C}$ の動作温度範囲で動作することが保証されている。

Note 3: LT1970Cは $0^\circ\text{C}$ ～ $70^\circ\text{C}$ の温度範囲で性能仕様に適合することが保証されている。LT1970Cは $-40^\circ\text{C}$ ～ $85^\circ\text{C}$ の拡張温度範囲で性能仕様に適合するように設計され、特性が評価されており、性能仕様に適合すると予想されるが、これらの温度ではテストされないし、QAサンプリングも行われない。LT1970Iは $-40^\circ\text{C}$ ～ $85^\circ\text{C}$ の温度範囲で性能仕様に適合することが保証されている。

Note 4: このパラメータに対しては全数テストは実施されない。

Note 5: フルパワー帯域幅はスルーレートの測定値から、次のように計算される。

$$\text{FPBW} = \text{SR}/(2 \cdot \pi \cdot V_p)$$

Note 6:  $\overline{\text{TSD}}$ ピンのロジック“L”的出力レベルは $\overline{\text{ISRC}}$ ピンと $\overline{\text{ISNK}}$ ピンの出力レベルを全温度範囲で相関させることにより保証される。

Note 7: ターンオンとターンオフの遅延は、 $V_{\text{ENABLE}}$ が $1.6\text{V}$ を横切ってからOUTピンが正常な出力電圧の90%に達するまで測定される。

Note 8: 热抵抗はデバイスに接続されたPCボードのメタル量に依存して変化する。パッケージの最大熱放散を超えると、デバイスはサーマル・シャットダウン状態になり保護される。

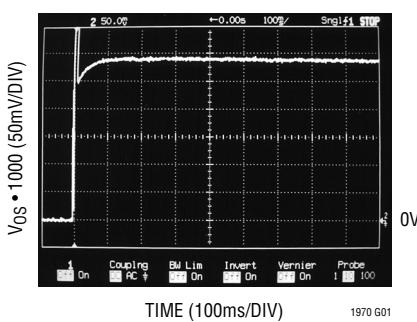

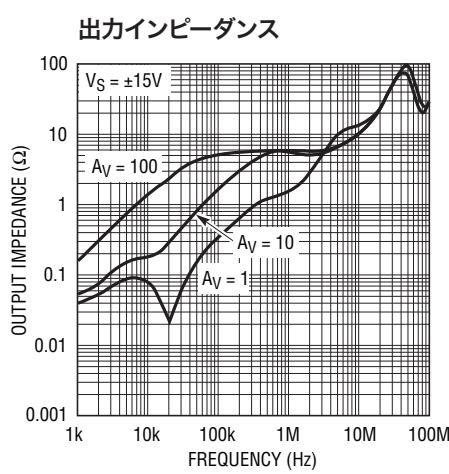

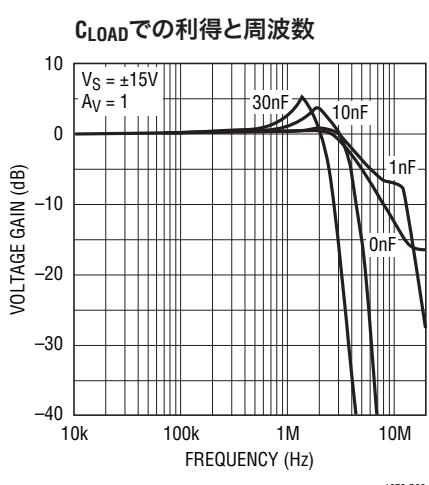

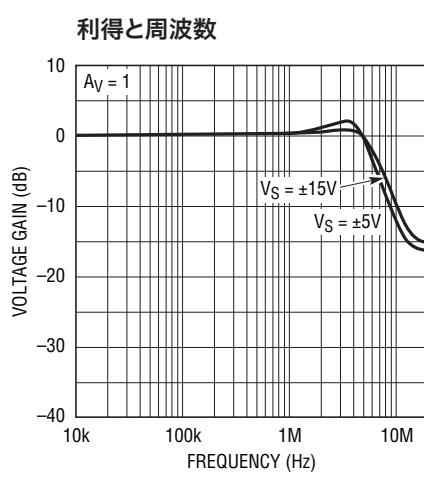

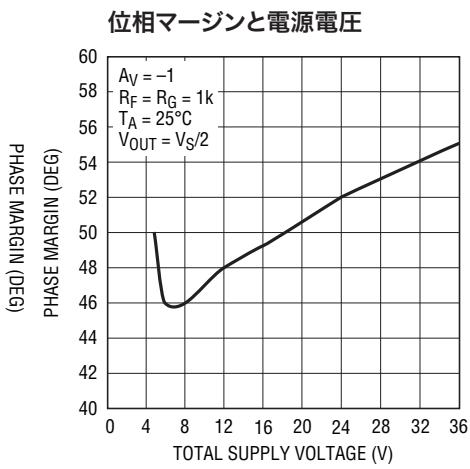

## 標準的性能特性

ウォームアップ・ドリフト $V_{IO}$ と時間

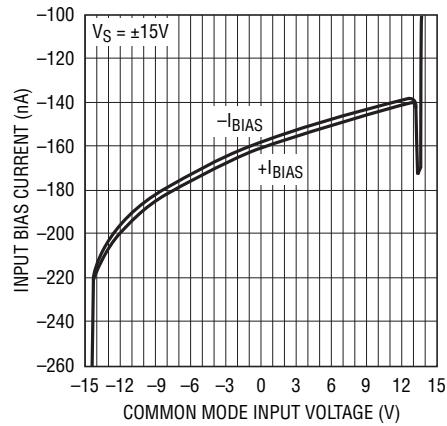

入力バイアス電流と $V_{CM}$

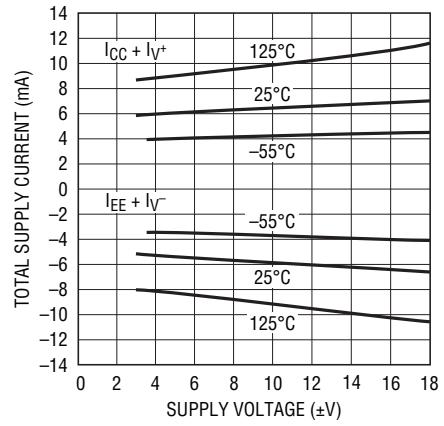

総消費電流と電源電圧

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

## ピン機能

**V<sub>EE</sub>(ピン1、10、11、20、パッケージのベース)**: 負電源電圧。V<sub>EE</sub>は集積回路のダイのサブストレートに接続されているので、常にデバイスに与えられる最も大きな負電圧でなければなりません。V<sub>EE</sub>は低ESRコンデンサでグランドにデカップリングします。V<sub>EE</sub>は負電圧またはグランド電位に等しくすることができます。V<sub>EE</sub>ピンのどれかまたは全てを使うことができます。使わないV<sub>EE</sub>ピンはオープンのままにしておく必要があります。

**V<sup>-</sup>(ピン2)**: 出力段の負電源。V<sup>-</sup>はV<sub>EE</sub>に等しくするか、またはもっと小さくすることができます。出力段の電流だけがV<sup>-</sup>から流れ出し、他の全ての電流はV<sub>EE</sub>から流れ出します。V<sup>-</sup>を使って外部のパワー・デバイスのベース/ゲートをドライブして、アンプの出力電流を内蔵出力デバイスの500mA定格を超えるレベルに増強することができます。ブースト・トランジスタをドライブするのに使わない限り、V<sup>-</sup>は低ESRコンデンサでグランドにデカップリングします。

**OUT(ピン3)**: アンプ出力。OUTピンはケルビン検出される負荷接続の一部として強制機能を与えます。OUTは通常は外部負荷電流センサ抵抗およびSENSE<sup>+</sup>ピンに直接接続されます。アンプ帰還は負荷および電流センサ抵抗の他端に直接接続されます。負荷電流をモニタするため、負荷接続はSENSE<sup>-</sup>ピンにも直接配線されます。

OUTピンの電流は標準±800mAに制限されます。この電流制限は、外部センス抵抗への接続のオープン状態または短絡状態が発生したとき(このとき精密電流制限機能は作動しません)出力トランジスタを保護します。

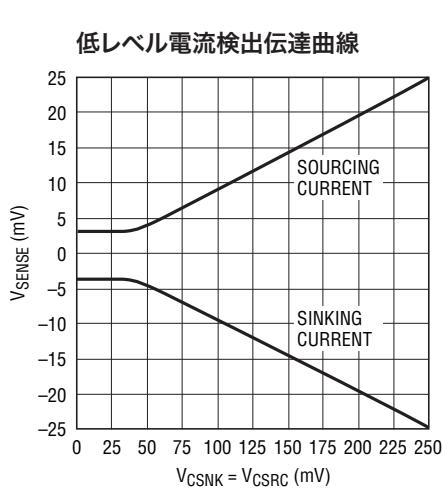

**SENSE<sup>+</sup>(ピン4)**: 正の電流検出ピン。このピンは通常外部センス抵抗のドライブされる側に接続されます。ソース電流制限動作は電圧V<sub>SENSE</sub>(V<sub>SENSE</sub><sup>+</sup>-V<sub>SENSE</sub><sup>-</sup>)がVC<sub>SRC</sub>(ピン13)プログラミング制御電圧の1/10に等しくなると起動します。シンク電流制限動作は電圧V<sub>SENSE</sub>がVC<sub>SNK</sub>(ピン12)プログラミング制御電圧の-1/10に等しくなると起動します。

**FILTER(ピン5)**: 電流検出フィルタ・ピン。このピンは通常使われず、オープンのままにするか、またはSENSE<sup>-</sup>ピンに短絡します。FILTERピンを使って、電流検出アンプの応答時間を、SENSE<sup>-</sup>入力に接続された1nF~100nFコンデンサで適応させることができます。内部の1k抵抗がフィルタの時定数を設定します。

**SENSE<sup>-</sup>(ピン6)**: 負の電流検出ピン。このピンは通常外部センス抵抗の負荷側に接続されます。ソース電流制限動作は電圧V<sub>SENSE</sub>(V<sub>SENSE</sub><sup>+</sup>-V<sub>SENSE</sub><sup>-</sup>)がVC<sub>SRC</sub>(ピン13)プログラミング制御電圧の1/10に等しくなると起動します。シンク電流制限動作は電圧V<sub>SENSE</sub>がVC<sub>SNK</sub>(ピン12)プログラミング制御電圧の-1/10に等しくなると起動します。

**V<sub>CC</sub>(ピン7)**: 正電源電圧。出力トランジスタを除く全ての回路がV<sub>CC</sub>から電力を供給されます。V<sub>CC</sub>からV<sub>EE</sub>までの総電源電圧は3.5V~36Vでなければなりません。V<sub>CC</sub>は常にV<sup>+</sup>以上でなければなりません。V<sub>CC</sub>は常に低ESRコンデンサでグランドにデカップリングします。

**-IN(ピン8)**: アンプの反転入力。-INはV<sub>EE</sub>-0.3V~V<sub>EE</sub>+36Vの電圧することができます。-INと+INは常に高インピーダンスに留まって、電流制限モードがアクティブなとき電流が入力に流れ込むのを防ぎます。過渡状態であっても-INまたは+INが決してV<sub>EE</sub>-0.3Vより下の電圧にならないように注意する必要があります。そうしないと回路が損傷を受けることがあります。回路内の他の素子が-INがV<sub>EE</sub>より下に下がるのを許す可能性がある場合、V<sub>EE</sub>から-INにショットキー・ダイオードを接続してクランプすることができます。

**+IN(ピン9)**: アンプの非反転入力。+INはV<sub>EE</sub>-0.3V~V<sub>EE</sub>+36Vの電圧することができます。-INと+INは常に高インピーダンスに留まって、電流制限モードがアクティブなとき電流が入力に流れ込むのを防ぎます。過渡状態であっても-INまたは+INが決してV<sub>EE</sub>-0.3Vより下の電圧にならないように注意する必要があります。そうしないと回路が損傷を受けることがあります。回路内の他の素子が+INがV<sub>EE</sub>より下に下がるのを許す可能性がある場合、V<sub>EE</sub>から+INにショットキー・ダイオードを接続してクランプすることができます。

## ピン機能

**VC<sub>SNK</sub>(ピン12)**: シンク電流制限御電圧の入力。電流シンク制限アンプは、SENSE<sup>+</sup>とSENSE<sup>-</sup>の間の検出電圧が $-1.0 \cdot V_{VCSNK}/10$ に等しいときアクティブになります。VC<sub>SNK</sub>はV<sub>COMMON</sub>～V<sub>COMMON</sub>+6Vに設定することができます。VC<sub>SNK</sub>とV<sub>SENSE</sub>の間の伝達関数は、 $VC_{SNK} < 60mV$ の非常に小さな入力電圧を除いてリニアです。シンク制限アンプとソース制限アンプが同時に動作しようとしないように、V<sub>SENSE</sub>は標準4mVの最小設定ポイントに制限されます。ゼロ出力電流を強制するには、ENABLEピンを“L”にします。

**VC<sub>SRC</sub>(ピン13)**: ソース電流制限御電圧の入力。電流ソース制限アンプは、SENSE<sup>+</sup>とSENSE<sup>-</sup>の間の検出電圧が $V_{VCSRC}/10$ に等しいときアクティブになります。VC<sub>SRC</sub>はV<sub>COMMON</sub>～V<sub>COMMON</sub>+6Vに設定することができます。VC<sub>SRC</sub>とV<sub>SENSE</sub>の間の伝達関数は、 $VC_{SRC} < 60mV$ の非常に小さな入力電圧を除いてリニアです。シンク制限アンプとソース制限アンプが同時に動作しようとしないように、V<sub>SENSE</sub>は標準4mVの最小設定ポイントに制限されます。ゼロ出力電流を強制するには、ENABLEピンを“L”にします。

**COMMON(ピン14)**: 制御入力とENABLE入力、およびフラグ出力はCOMMONピンを基準にします。COMMONはV<sub>EE</sub>～V<sub>CC</sub>-3Vの電位にすることができます。標準的アプリケーションでは、COMMONはグランドに接続します。

**ENABLE(ピン15)**: ENABLEデジタル入力制御。“L”に引き下げるとき、このTTLレベルのデジタル入力はアンプの出力をオフして、消費電流を1mA以下に下げます。出力電流をゼロに強制するにはENABLEピンを使います。VC<sub>SNK</sub> = VC<sub>SRC</sub> = 0Vに設定すると、I<sub>OUT</sub> = ±4mV/R<sub>SENSE</sub>がV<sub>OUT</sub>へ、またはV<sub>OUT</sub>から流れることを許します。

**ISRC(ピン16)**: ソース電流制限デジタル出力フラグ。ISRCはオープン・コレクタのデジタル出力です。ISRCはソース電流制限アンプが出力の制御を引き受けたとき“L”になります。このピンは最大10mAをシンクすることができます。ソース電流制限がアクティブでないとき電流制限フラグはオフします。そうした

ければ、ISRC、ISNKおよびTSDと一緒にワイヤーOR接続することができます。ISRCは、この機能をモニタしなければオープンのままにしておくことができます。

**ISNK(ピン17)**: シンク電流制限デジタル出力フラグ。ISNKはオープン・コレクタのデジタル出力です。ISNKはシンク電流制限アンプが出力の制御を引き受けたとき“L”になります。このピンは最大10mAをシンクすることができます。ソース電流制限がアクティブでないとき電流制限フラグはオフします。そうしたければ、ISRC、ISNKおよびTSDと一緒にワイヤーOR接続することができます。ISNKは、この機能をモニタしなければオープンのままにしておくことができます。

**TSD(ピン18)**: サーマル・シャットダウンのデジタル出力フラグ。TSDはオープン・コレクタのデジタル出力です。内部シャットダウン回路が(標準160°Cのダイ温度で)起動するとTSDは“L”になります。このピンは最大10mAの出力電流をシンクすることができます。ダイ温度が通常の動作温度内にあるときTSDフラグはオフになります。そうしたければ、ISRC、ISNKおよびTSDと一緒にワイヤーOR接続することができます。TSDは、この機能をモニタしなければオープンのままにしておくことができます。サーマル・シャットダウンの起動により、ユーザーは電気的負荷や周囲の熱的条件を調べるよう促されます。

**V<sup>+</sup>(ピン19)**: 出力段の正電源。V<sup>+</sup>はV<sub>CC</sub>に等しくするか、またはもっと小さくすることができます。出力段の電流だけがV<sup>+</sup>を通じて流れ、他の全ての電流はV<sub>CC</sub>に流れ込みます。V<sup>+</sup>を使って外部のパワー・デバイスのベース/ゲートをドライブして、アンプの出力電流を内蔵出力デバイスの500mA定格を超えるレベルに増強することができます。ブースト・トランジスタをドライブするのに使わない限り、V<sup>+</sup>は低ESRコンデンサでグランドにデカップリングします。

**パッケージ・ベース**: パッケージの露出した裏面はデバイスのダイでV<sub>EE</sub>ピンに電気的に接続されています。パッケージ・ベースは、V<sub>EE</sub>に電気的に接続されているPCボード上の熱拡散パッドに半田付けします。

## ブロック図とテスト回路

## アプリケーション情報

高精度制御可能電流制限付きLT1970パワー・オペアンプは柔軟性に富む電圧源および電流源モジュールです。このデータシートの表紙の図は代表的な基本応用回路ですが、回路の諸構成要素の機能を正しく理解することにより、他の様々な使い方が可能です。

## 回路の説明

## メイン・オペアンプ

下位回路ブロックGM1、1Xユニティゲイン電流バッファおよび出力トランジスタQ1とQ2が標準的オペアンプを形成しています。このアンプの電流出力能力は±500mA、利得帯域幅積は3.6MHzです。LT1970のほとんどのアプリケーションではこのアンプが主信号経路に使われます。オペアンプ回路の従来の全ての構成法がサポートされています。反転、非反転、フィルタ、加算、非線形などの回路を従来の方法で実現することができます。出力段には±800mAの電流制限が備わっており、フォールト状態に対して保護します。入力段の差動ブレーカダウンは高く、-INと+INの間が最小36Vです。差動入力電圧が与えられているとき、入力には電流が流れません。この特長

は、高精度電流検出アンプISINKとISRCがアクティブになると非常に重要です。

## 電流制限アンプ

アンプ段ISINKとISRCはトランスクンダクタンスが非常に高いアンプ段で、オフセット電圧は独立に制御されます。これらのアンプは、小さな外部電流センス抵抗両端の電圧を通常検出する入力ピンSENSE<sup>+</sup>とSENSE<sup>-</sup>の間の電圧をモニタします。トランスクンダクタンス・アンプの出力は、主力段GM1アンプと同じ高インピーダンス・ノードに接続されています。SENSE<sup>+</sup>とSENSE<sup>-</sup>の間の小さな(ユーザーが設定したVCSENK/10およびVCSRC/10よりも小さな)電圧差により、電流制限アンプは信号経路からデカップリングされます。これは、ブロック図ではダイオードD1とD2によって機能的に示されています。電圧VSENSEの大きさが十分増加して、オフセット電圧VCSENK/10またはVCSRC/10に等しくなるかまたはそれを上回ると、適切な電流制限アンプがアクティブになり、その非常に高いトランスクンダクタンスのため、入力段GM1から制御を引き継ぎます。

## アプリケーション情報

出力電流は  $I_{OUT} = V_{SENSE}/R_{SENSE} = (V_{CSRC} \text{または} V_{CSNK})/(10 \cdot R_{SENSE})$  の値に制御されます。電流制限アンプが出力の制御を引き継ぐのに要する時間は標準4μsです。

電流制限検出アンプは、 $V_{CC}-1.5V \sim V_{EE}+1.5V$  の範囲で変化する入力SENSE<sup>+</sup>と入力SENSE<sup>-</sup>に対してリニアに動作します。ほとんどのアプリケーションではSENSE<sup>+</sup>ピンとOUTピンと一緒に接続し、外部センス抵抗の反対側の負荷とSENSE<sup>-</sup>ピンを接続します。GM1の反転入力への帰還はSENSE<sup>-</sup>から-INに接続します。負荷電流をグランド側で検出するには、OUTピンとSENSE<sup>+</sup>ピンの間に負荷を接続することができます。この場合、SENSE<sup>-</sup>ピンはグランドに接続します。負荷電流は通常の接続と全く同様に安定化されます。ただし、R<sub>SENSE</sub>両端の電圧により、電圧モードの精度はこの場合低下します。

SENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピンが負荷電流以外のパラメータをモニタする創造的なアプリケーションが可能です。電流制限段の1つだけが同時にアクティブになることができ、アクティブになると電流制限段がGM1から出力の制御を引き継ぐという動作原理を、多くの異なる信号に利用することができます。

## 電流制限スレッショルド制御バッファ

入力ピンVC<sub>SNK</sub>とVC<sub>SRC</sub>を使って電流制限アンプI<sub>SINK</sub>とI<sub>SRC</sub>の応答スレッショルドを設定します。これらの入力のそれぞれは、COMMONリファレンス・ピンより0V～5V高い電圧によって独立にドライブすることができます。0V～5Vの入力電圧は1/10に減衰され、適切な電流制限アンプのオフセットとして与えられます。これらのピンにはAC信号を与えることができます。V<sub>C</sub>ピンから出力へのAC帯域幅は標準2MHzです。LT1970を正しく動作させるには、これらの制御入力をフロート状態のままにすることはできません。

低V<sub>CC</sub>電源のアプリケーションでは、最大入力制御電圧(VC<sub>SRC</sub>とVC<sub>SNK</sub>)をV<sub>CC</sub>の電位よりも2.5V下に保つことが重要です。これにより、電流制限スレッショルドのリニアな制御が保証されます。電流制限センス抵抗の値を小さくすると、小さな制御電圧で高い出力電流が可能になりますが、これはV<sub>CC</sub>電源が5Vしかないとき必要になります。

V<sub>C</sub>から関連したV<sub>os</sub>への伝達関数は約0.1V～5Vの入力(つまり電流制限アンプの入力では10mV～500mV)でリニアです。低レベルでは意図的に非直線性が伝達関数に組み込まれています。この非直線性によりシンク制限アンプとソース制限アンプが両方同時にアクティブにならないことが保証されます。制限アンプが同時にアクティブになると、出力の制御が失われるおそれがあります。「標準的性能特性」の曲線に示されているように、制御入力は「ホッケーのスティック」のような形をしており、各制限アンプの最小制限スレッショルドを4mVに保ちます。

電流検出入力ピンの興味深い使い方を図1に示します。ここでは、電流制限アンプを使って対称的に制限された出力電圧振幅を発生しています。出力電流のモニタの代わりに、出力電圧が1/20に分圧されてSENSE<sup>+</sup>入力に与えられ、SENSE<sup>-</sup>入力は接地されています。SENSE<sup>+</sup>とSENSE<sup>-</sup>の間のスレッショルド電圧(V<sub>CLAMP</sub>/10)に達すると、電流制限段が出力の制御を取り上げ、出力を±2×V<sub>CLAMP</sub>のレベルにクランプします。制御入力V<sub>CSRC</sub>とV<sub>CSNK</sub>と一緒に接続すると、單一の極性の入力電圧によって同一の+と-の出力制限電圧が設定され、対称的な制限が実現されます。この回路では、出力は標準800mAの組込みフェールセーフ・レベルで電流が制限されます。

図1. 対称出力電圧制限

## アプリケーション情報

### ENABLE制御

ENABLE入力ピンはLT1970を低消費電流、高インピーダンス出力の状態にします。ENABLEピンはCOMMONピンを基準にしたTTLスレッショルド・レベルに応答します。ENABLEピンを“L”に引き下げるのが、出力をゼロ電流に強制する最善の方法です。 $V_{CSNK} = V_{CSRC} = 0V$ に設定すると、出力電流を $\pm 4mV/R_{SENSE}$ に保つことができます。

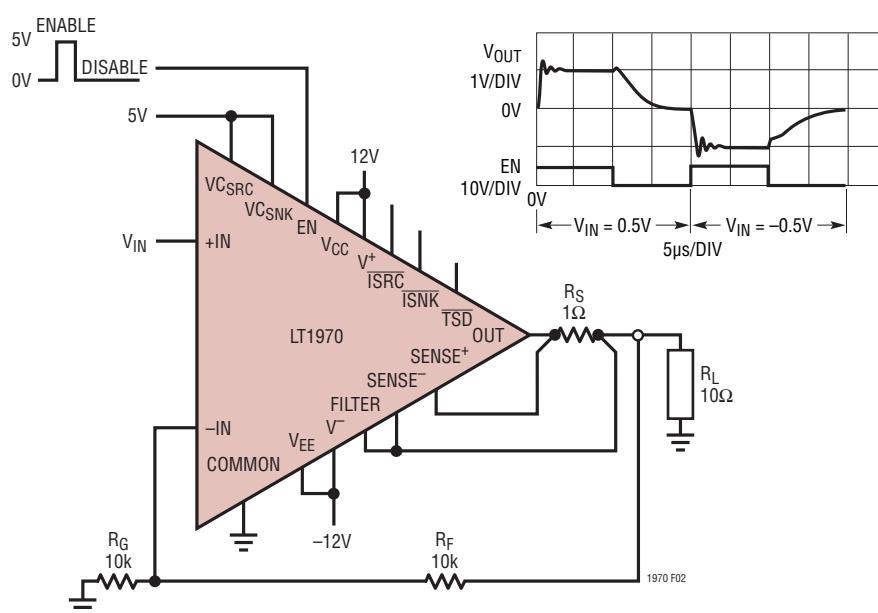

回路テスター(ATE)などのアプリケーションでは、予め定められたテスト電圧を予め定められた電流制限でテストノードに同時に適用するのが望ましいことがあります。図2に示されているように、ENABLEピンを使って、このゲーティング・アクションを行うことができます。LT1970がディスエーブルされている間、負荷は基本的にフロート状態であり、入力電圧と電流制限御電圧を設定して負荷のテスト・レベルを発生することができます。LT1970をイネーブルして負荷をドライブします。LT1970はわずか数マイクロ秒でイネーブルおよびディスエーブルします。負荷での実際のイネーブル時間とディスエーブル時間は負荷のリアクタンスの関数です。

### 動作状態フラグ

LT1970には3つのデジタル出力インジケータ( $\overline{TSD}$ ,  $\overline{ISRC}$ および $\overline{ISNK}$ )があります。これらの出力はCOMMONピンを基準にしたオープン・コレクタ・ドライバです。出力は36Vの能力があり、10mAを超えてシンクすることができます。 $\overline{ISRC}$ と $\overline{ISNK}$ は

関連した電流制限アンプの起動を表示します。 $\overline{TSD}$ 出力は、過度のダイ温度により回路がシャットダウン状態になったことを表示します。3つのデジタル出力は、一緒にワイヤーOR接続することも、個別にモニタすることも、オープンのままにしておくこともできます。これらの出力は回路動作には影響を与えませんが、デバイスの現在の動作状態を表示します。

ゆっくり変化する出力信号の場合、電流制限スレッショルドに達すると、電流制限出力フラグが低レベルにアサートします。LT1970の出力がスルーの限界(標準 $1.6V/\mu s$ )で変化する高速で変化する信号の場合、フラグが実際の電流制限値の標準75%でいくらか時期尚早にアサートすることがあります。

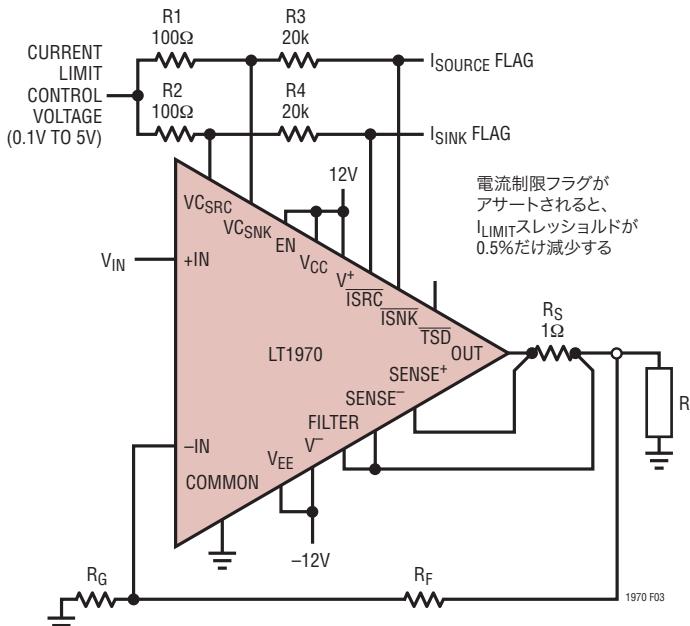

動作状態フラグはLEDをドライブして電流制限と熱的状態を視覚的に表示するように設計されています。このように、アクティブ“L”状態への遷移、またその状態からの遷移のエッジはそれほど鋭くなく、いくらかの不確実さを示すことがあります。電流制限御入力にいくらかの正帰還を加えると、これらの遷移を鋭くするのに役立ちます。

図3に示されている値では、どちらかの電流制限状態フラグが“L”になると電流制限スレッショルドが約0.5%減少します。鋭いロジック遷移により、これらの状態出力をシステムの制御ループに使って、電流制限状態が自動的に検出されるとき保護手段を講じることができます。

図2. ENABLEピンの使い方

1970fc

## アプリケーション情報

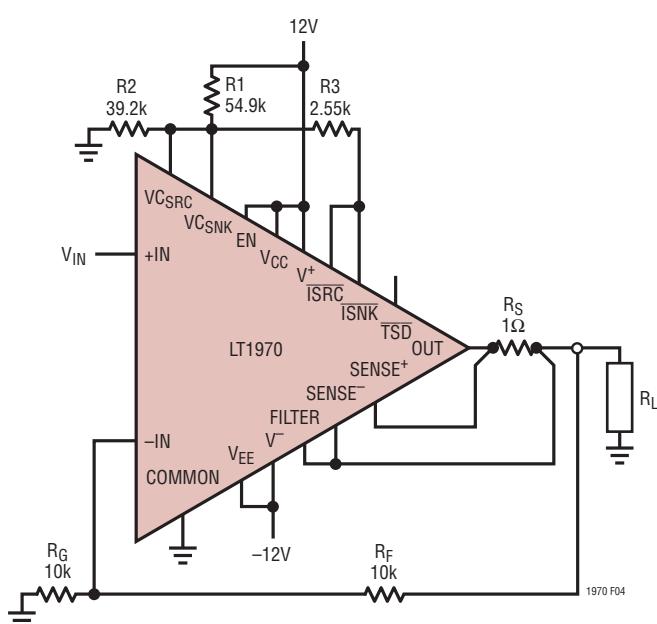

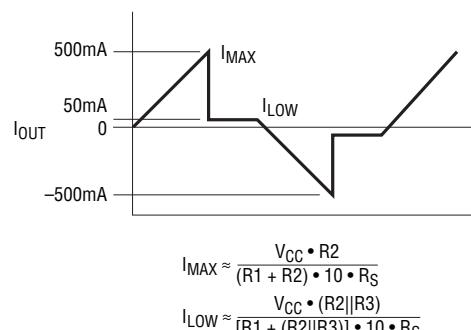

電流制限状態フラグを使ってアンプの電流制限値を大きく変えることもできます。「スナップバック」電流制限特性を図4に示します。電流制限のフラグが出力されると、ILIMITのスレッショルドが0.5%減少するこの回路では、簡単な抵抗ネットワークが最初に電流制限の高い値(500mA)を設定します。電流制限に入るほど信号が十分大きくなるまで回路は正常

に動作します。どちらかの電流制限フラグが“L”になると、電流制限御電圧は1/10に減少し、信号の大きさが減少するまで、低レベルの出力電流(50mA)が強制されます。負荷電流が低いレベルより下に下がると、電流制限は高い値に回復します。このアクションは、危険な高電流レベルでトリップし、安全にリセットできる状態になったらリセットする自己リセット可能なヒューズに似ています。

## 熱管理

### 電力損失の最小化

LT1970は最大36Vの総電源電圧、最大 $\pm 500$ mAの出力電流で動作可能です。デバイス内で消費される電力はワーストケース条件では18Wに近づくことがあります。この大きさの電力では、回路がサーマル・シャットダウンに入るまでダイの温度が上昇します。サーマル・シャットダウン機能は回路への損傷を防ぎますが、正常動作が妨げられます。LT1970の動作環境の熱設計は、回路を最大限使いこなすのに不可欠です。

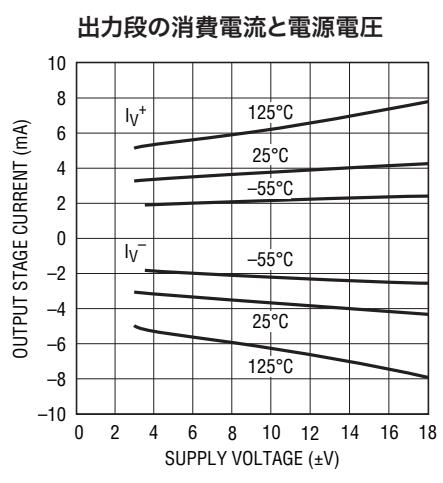

熱管理の最初の課題は、取り去る必要のある熱を最小に抑えることです。別個の電力ピン $V^+$ と $V^-$ はデバイス内の電力を最小化するのに大きく役立ちます。最大出力電流条件であっても、出力ピンは $V^+$ または $V^-$ の1.0V以内に振幅することができます。

図3. 電流制限状態フラグの遷移エッジを鋭くするための正帰還の追加

図4. 「スナップバック」電流制限

$$I_{MAX} \approx \frac{V_{CC} \cdot R_2}{(R_1 + R_2) \cdot 10 \cdot R_S}$$

$$I_{LOW} \approx \frac{V_{CC} \cdot (R_2 || R_3)}{[R_1 + (R_2 || R_3)] \cdot 10 \cdot R_S}$$

## アプリケーション情報

別個の電源または電圧レギュレータを使って $V^+$ と $V^-$ を必要な出力振幅のためのそれらの最小値に設定すると、電力損失が最小になります。電源 $V_{CC}$ と $V_{EE}$ も小さな値に減らすことができますが、これらの電源ピンは大きな電流は流さず、節約できる電力はずつと小さなものです。 $V_{CC}$ と $V_{EE}$ は最大出力振幅より1.5V以上大きくする必要があります。

$V_{CC}$ および $V_{EE}$ とは別に $V^-$ と $V^+$ が与えられる場合、 $V^-$ と $V^+$ の大きさが常に主電源より小さくなるように注意する必要があります。電源オン/オフの過渡時も含めて、あらゆる場合にこのことを保証するには、保護用ショットキー・ダイオードが必要になることがあります。

電圧を下げた $V^+$ 電源と $V^-$ 電源による動作は、最大出力振幅以外どんな性能パラメータにも影響を与えません。 $V_{CC} = V^+$ および $V_{EE} = V^-$ で保証されている全てのDC精度とAC性能の仕様は、減少した出力信号振幅範囲でも依然有効です。

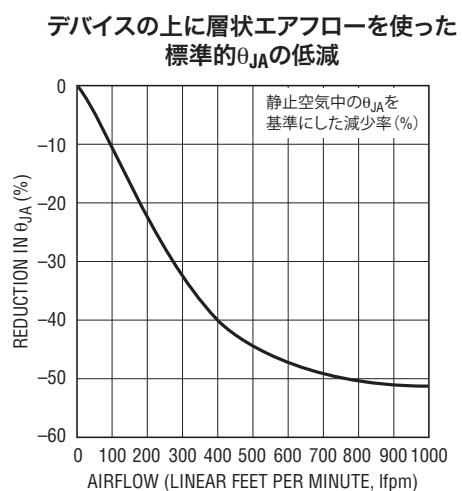

### ヒートシンク

LT1970のダイで消費される電力は環境への経路を必要とします。自由空気中でヒートシンクなしの条件での100°C/Wの熱抵抗では、パッケージの電力損失はわずか1Wに制限されます。底面に露出パッドを備えた20ピンTSSOPパッケージは、正しくPCボードに実装すると、効率の良い熱伝導体です。パッケージの底部をPCボード上の大きな銅パターンに半田付けすることにより、40°C/Wの熱抵抗が得られます。これにより、85°Cの動作では最大1.625Wの電力をLT1970で消費することができます。25°Cの動作では最大3.125Wの電力消費を達成できます。PCボードの熱拡散銅領域は $V_{EE}$ に接続する必要があります。

熱拡散に使われているPCBのメタルの例を図5に示します。これらは、PCBの異なる層のメタル領域の異なる組合せを使うと何を期待できるかを参考として示しています。これらは各層に1オンス銅を使った4層ボードの例です。熱を拡散するのに最も効果的な層はLT1970の接合部に最も近い層です。TSSOPパッケージの露出サーマル・パッドをボードに半田付けすると、接合部からケースへの熱抵抗は約3°C/Wになります。

少なくとも、PCBの全ての層のパッケージ直下の領域を熱拡散に使用することができます。ただし、領域をメタル・ヒートシンク・パッドの面積に限定すると効果はそれほどではなくなります。

ます。様々な層の領域を拡大すると、全体の熱抵抗が大きく減少します。全てのメタル層を接続するビア(小さな13ミルの孔で、PCBのメッキ工程で充填される)の追加もLT1970の動作温度を下げるのに役立ちます。これらも図5に示されています。

ヒートシンクに使われるメタル・プレーンは $V_{EE}$ に電気的に接続されることに注意するのは重要です。これらのプレーンはPCBデザインで使用される他のどの電力プレーンからも絶縁されている必要があります。

パワー・アンプの動作温度を制御する別の効果的な方法は基板に対してエアフローを使うことです。エアフローは、これも図5に示されているように、全体の熱抵抗を大きく減らすことができます。

### リアクティブな負荷のドライブ

#### 容量性負荷

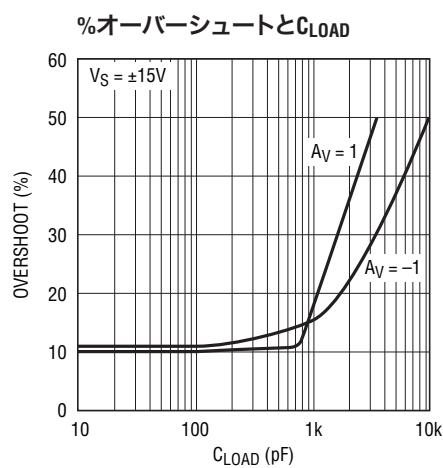

LT1970は大半のオペアンプに比べて容量性の負荷に対してはるかに耐性があります。電圧フォロワとしてのワーストケースの回路構成で、回路は2.5nF以下の容量性負荷に対して安定です。もっと利得の高い回路構成ではCLOADの処理が改善されます。非常に大きな容量性負荷をドライブする場合、アンプを容量性負荷から抵抗でデカップリングすると安定性の維持とピーピングの低減に効果的です。通常出力ピンと負荷の間に接続される電流センス抵抗は、デカップリング抵抗の一部として役立ちます。

#### 誘導性負荷

オペアンプの出力の負荷のインダクタンスは通常問題ではありませんが、LT1970は高出力インピーダンスの電流源として使うことができます。この状態を主要な動作モードにするか、または回路が保護的な電流制限モードのときの状態にすることができます。負荷容量が通常のオペアンプの位相マージンを劣化させるのと同じように、負荷インダクタンスは帰還制御された電流源のループ応答にピーピングを生じます。誘導性負荷はアンプの出力の長いリード線によって生じことがあります。アンプが誘導性負荷または(4インチを超える)長いリード線をドライブする場合、500pFのコンデンサをSENSE<sup>-</sup>ピンからグランド・プレーンに接続すると誘導性負荷をキャンセルして安定性を保証します。

## アプリケーション情報

| 静止空気中の $\theta_{JA}$ | パッケージ | トップ層 | 第2層 | 第3層 | ボトム層 |

|----------------------|-------|------|-----|-----|------|

| TSSOP<br>100°C/W     |       |      |     |     |      |

| TSSOP<br>50°C/W      |       |      |     |     |      |

| TSSOP<br>45°C/W      |       |      |     |     |      |

1970 F05a

1970 F05b

図5. 热拡散に使われているPCBのメタルの例。トップ層に実装されたドライバのパッケージ。

トップ層のメタルに半田付けされたヒートシンク・パッド。メタル領域はパッケージの寸法のスケールで描かれている

## アプリケーション情報

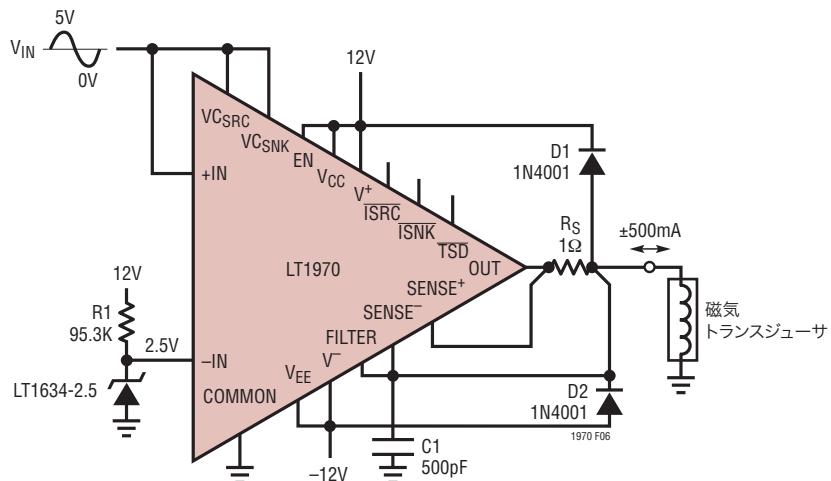

制御された電流量で誘導性負荷をドライブしているLT1970を図6に示します。この負荷は一般的磁気トランジスタとして示されており、これは磁界を発生したり変化させるのに使うことができます。電流制限入力をドライブすると、最大2MHzで変調可能な電流を直接負荷に強制します。入力段を変調信号の中点にバイアスすると、対称な双方向電流を負荷に流すことができます。高速のdi/dtの変化によって生じる大きな誘導性フライバック電位からLT1970の出力を保護するため、クランプ・ダイオードが追加されています。

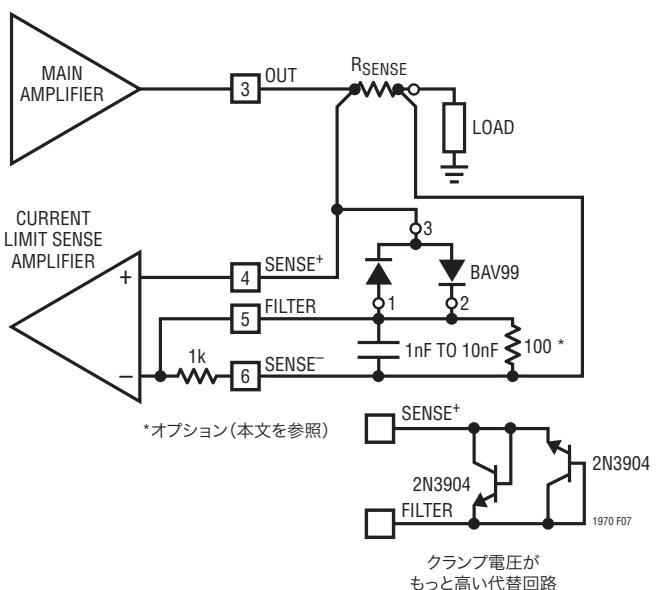

## 突発負荷短絡に対する保護

グランドや他の電源電位への(アクシデントなどによる偶然の)突発短絡はLT1970にとって最悪の負荷条件です。電流制限センスアンプはセンス抵抗両端の電圧に等しい入力電圧差で通常動作します。これは標準的アプリケーションでわずか最大500mVです。グランドへの突発負荷短絡の間、センス抵抗の負荷端は直ちにグランドに接続され、アンプの出力は正常な出力電圧に留まります。このため、大きな電圧差がセンスアンプの入力に短時間加わることがあります。この電圧差が $\pm 2V$ より大きくなる可能性がある場合、電流制限センスアンプの入力間にクランプを追加すると有益です。これらのクランプにより、発生しうる全ての短絡条件で、メイン・アンプの制御から電流制限アンプの制御へのスムーズな移行が保証されます。

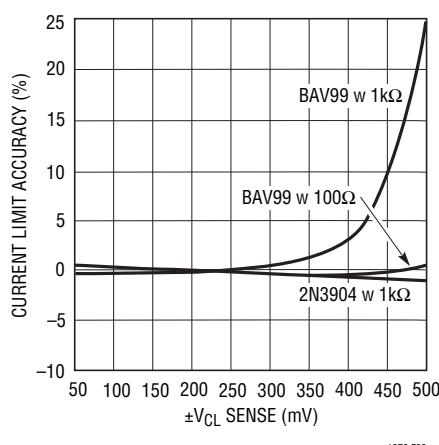

FILTERピンとSENSE<sup>+</sup>ピンの間のこれらのバック・トゥ・バック・クランプ・ダイオードの接続を図7に示します。この接続では、SENSE<sup>-</sup>ピンとFILTERピンの間の内部1k抵抗がダイオード電流を制限します。BAV99ダイオードは小型SOT-23パッケージの汎用シリコン・ダイオードです。最大電流制限検出電圧は今やダイオードの電圧降下であり、センス抵抗と1k内部抵抗の両端の電圧によって決まります。ダイオードが(約300mVの電圧降下で)電流を流し始めると、V<sub>DIODE</sub>がR<sub>SENSE</sub>両端の電圧より小さいので、制御の上端の予期される電流制限レベルの誤差が明らかになります。

図7. 突発負荷短絡に対する追加保護回路

図6. 磁気トランジスタの電流変調

1970fc

## アプリケーション情報

内部1k抵抗に並列にオプションの外部100Ω抵抗を追加すると、検出される電流制限電圧にダイオード電圧を強制的に近づけ、電流制限誤差を減少させます。

代わりに、バック・トゥ・バック2N3904 NPNトランジスタのベース-エミッタ接合がこのクランプ動作を与えることができます。これらのダイオードはもっと600mVに近い高い電圧レベルで導通を始めます。500mVの最大電流制限スレッショルドでは、誤差はほとんど気付かれません。クランプ保護を追加する3つの方法の標準的電流制限誤差の比較を図8に示します。電流センス抵抗と電流制限御電圧のスケールを下げて0V～300mVの電流制限検出電圧範囲にすると、突発短絡クランプ・ダイオードによって生じるこれらの精度誤差も防ぎます。

小さなフィルタ・コンデンサも図7に示されています。これも突発負荷短絡状態での追加制御手段を与えます。突発短絡はLT1970と負荷の間の全ての寄生配線インダクタンスを明らかにします。これらの分布寄生素子は短絡の発生または解消後の短時間に大きな過渡電圧スパイクを生じることがあります。これらの制御されない電圧過渡は実際に電流制限アンプに再結合し、ソース電流制限からシンク電流制限への極性反転、またはその逆の極性反転を引き起こすことがあります。

これは正帰還として機能があるので、電流制限アンプが誤った電流制限方向に進んでハンギングアップすることがあります。小さなフィルタ・コンデンサ(普通1nF～10nF)をSENSE-ピンとFILTERピンの間に追加すると、クランプ・ダイ

オードを通して充電し、負荷短絡の瞬間に正しい電流制限極性を強制します。これにより、コンデンサが内部1k抵抗を通して放電するまでアンプは電流リミットに保持され、過渡によって引き起こされる振舞いを防ぎ、スムーズに電流制限に移行します。

## 電源のバイパス

LT1970は電源から負荷に大きな電流を最大4MHzで供給することができます。電源のインピーダンスは、電源レールの垂下を生じることなくこれらの電流を供給するのに十分なだけ低く保つ必要があります。ピンの近くに配置した低ESRコンデンサ(0.1μFまたは1μFのセラミックなど)は全てのアプリケーションに不可欠です。大きな高速過渡電流が存在するとき、追加のコンデンサがデバイスの近くに必要になることがあります。オシロスコープを使って電源レールをチェックし、電源レールに信号に関係したリップルが見られたら、必要に応じてデカップリング・コンデンサを増やします。

LT1970の適切な起動バイパスを保証するには、起動時の電源電圧の変化率を6V/μsより速くならないように制限することを推奨します。

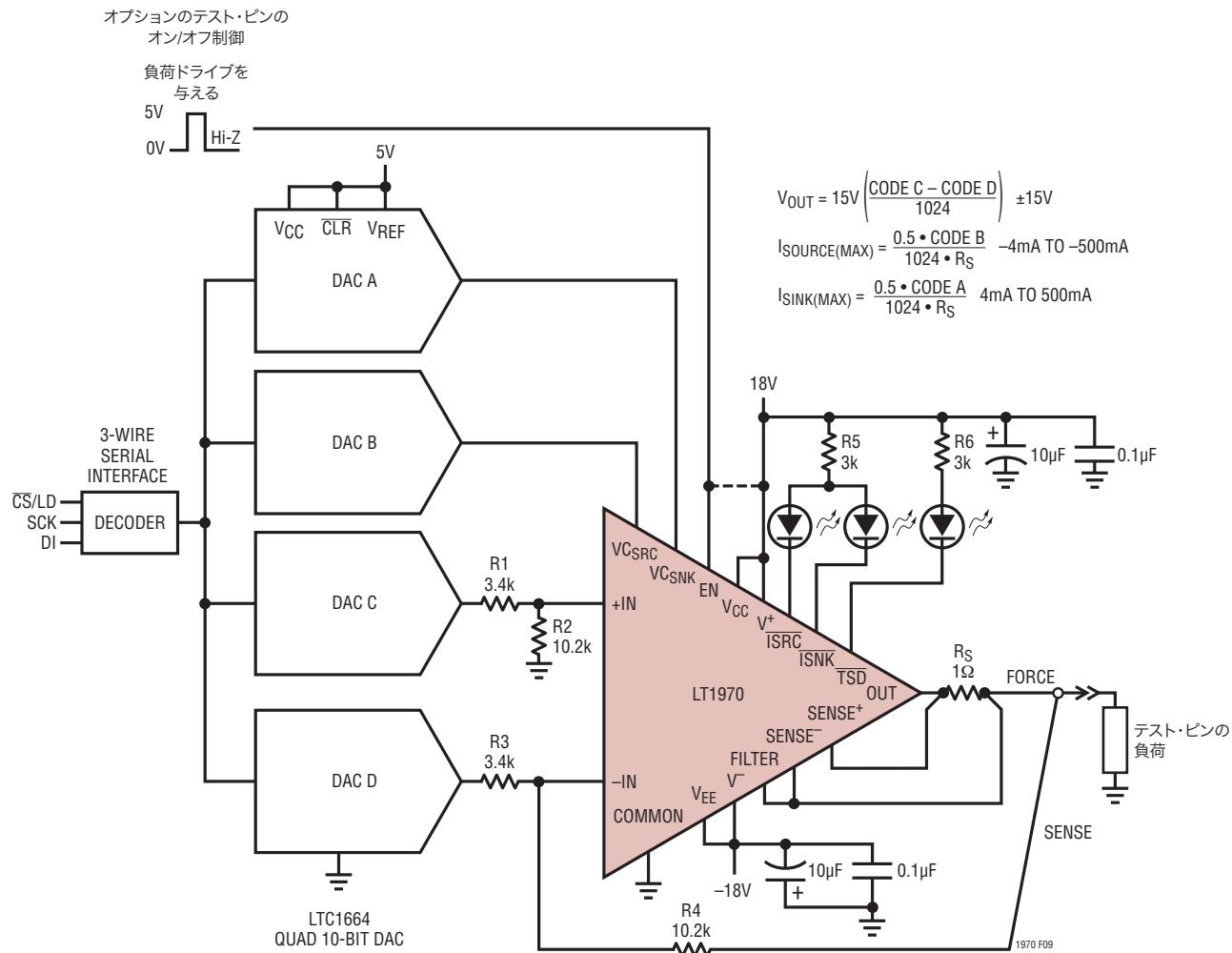

## 応用回路のアイデア

デジタルで制御されるアナログ・ピン・ドライバを図9に示します。全ての制御信号は、3線シリアル・インターフェースを介して、LTC<sup>®</sup>1664クワッド10ビットDACによって与えられます。LT1970は利得が3の簡単な差動アンプとして構成されています。この利得はDACのCとDからの0V～5Vの出力から±15Vを発生するのに必要です。電圧の空き高を与えるため、LT1970の電源は±18Vの最大値に設定されています。±18VはLT1970の電源電圧の絶対最大定格なので、電源電圧を増加させないように注意が必要です。DACのAとBは、負荷に対するシンク電流とソース電流のリミットを±4mA～±500mAの範囲で別々に制御します。ENABLE入力をを使ったピン・ドライバのオプションのオン/オフ制御を示します。常にイネーブルする場合、ENABLEピンをV<sub>CC</sub>に接続します。

図8. 異なったクランプによる電流制限精度

## アプリケーション情報

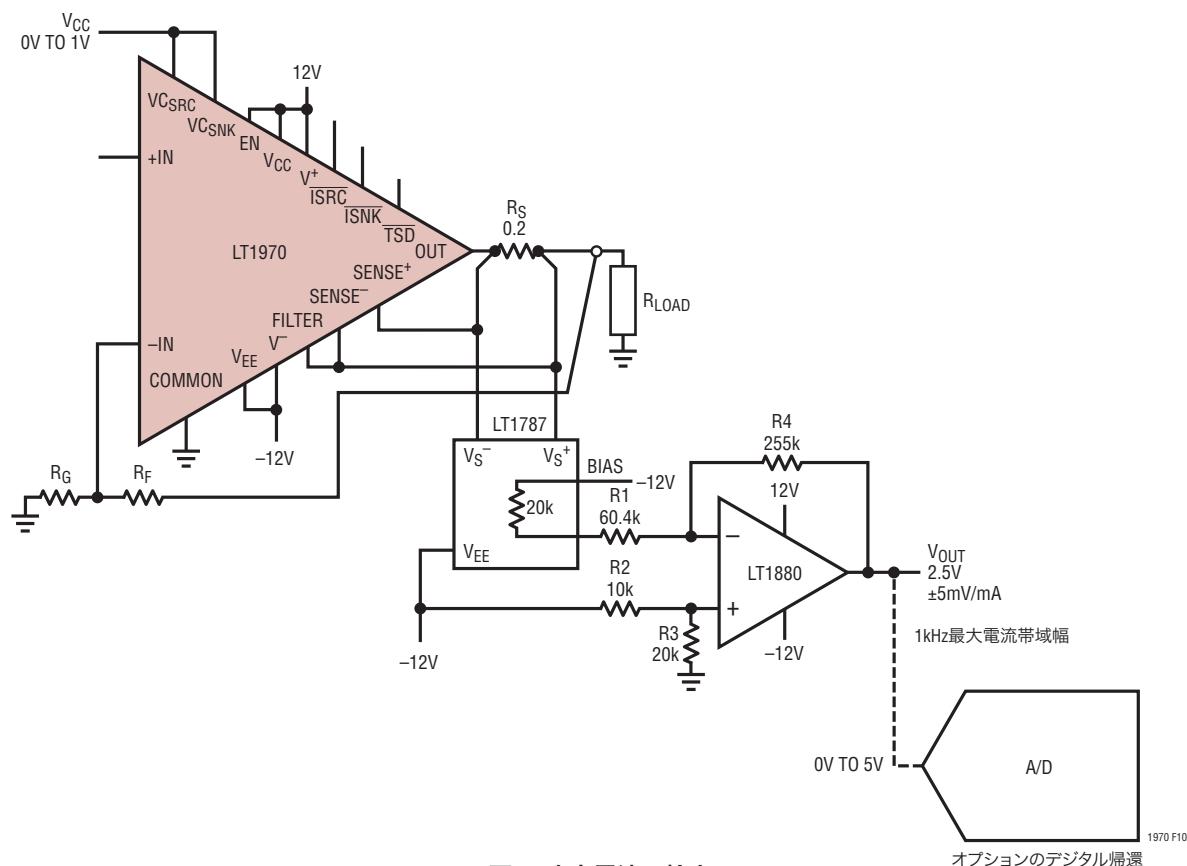

図9. デジタルで制御されるアナログ・ピン・ドライバ

アプリケーションによっては、いつでも負荷への電流が何であるかを知る必要があります。センス抵抗R<sub>S</sub>を流れる電流をモニタするLT1787ハイサイド電流センサアンプを図10に示します。LT1787は、±10Vの同相入力範囲を受け入れるためV<sub>EE</sub>電源からバイアスされます。最大100mVの差動信号を電流センサアンプに与えて直線性を維持するため、センス抵抗はスケールダウンされています。LT1880アンプは利得とレベルシフトを与え、最大1kHzのフルスケール帯域幅で0V～5Vの出力信号(2.5V DC ±5mV/mA)を発生します。次いでA/Dコンバータがこの瞬時電流値をデジタル化して回路からのデジタル帰還を与えることができます。

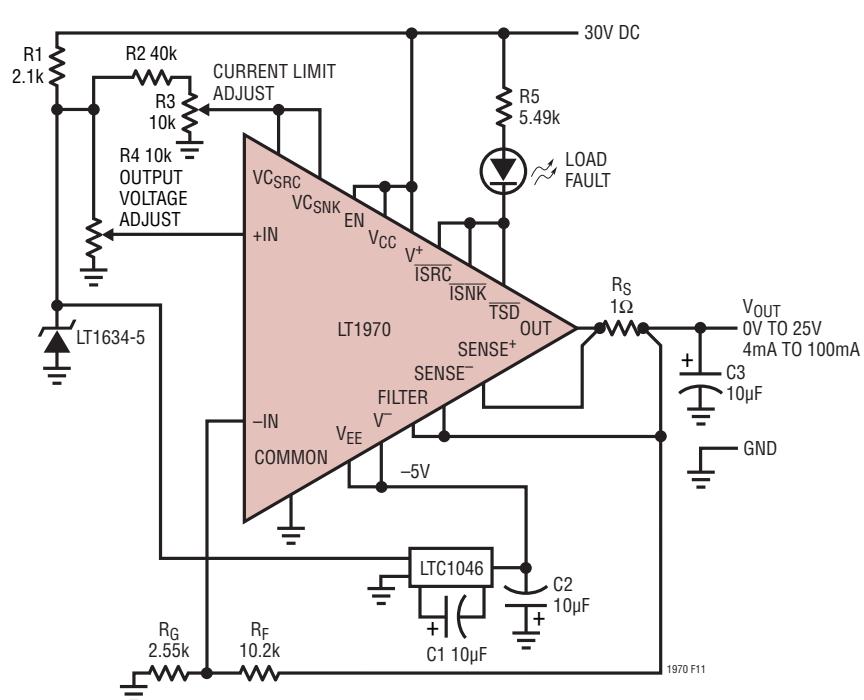

LT1970は標準的オペアンプと全く同様に簡単に使えます。図11に示されているように、高精度リファレンス電圧の基本的増幅により、非常に簡単なベンチ用DC電源が得られます。内蔵電力段が、4mA～100mAの出力電流で可変の0V～25Vを発生します。電圧と電流の調節はLT1634-5 5Vリファレンスから得られます。出力電流能力は500mAですが、この電源は電力損失のため100mAに制限されます。LT1970の出力段で最大電力が消費されるワーストケース出力電圧は、出力がグランドに短絡されるか、またはゼロに近い電圧に設定されるとき生じます。出力電流を100mAに制限すると、最大電力損失が3Wに設定されます。

## アプリケーション情報

## アプリケーション情報

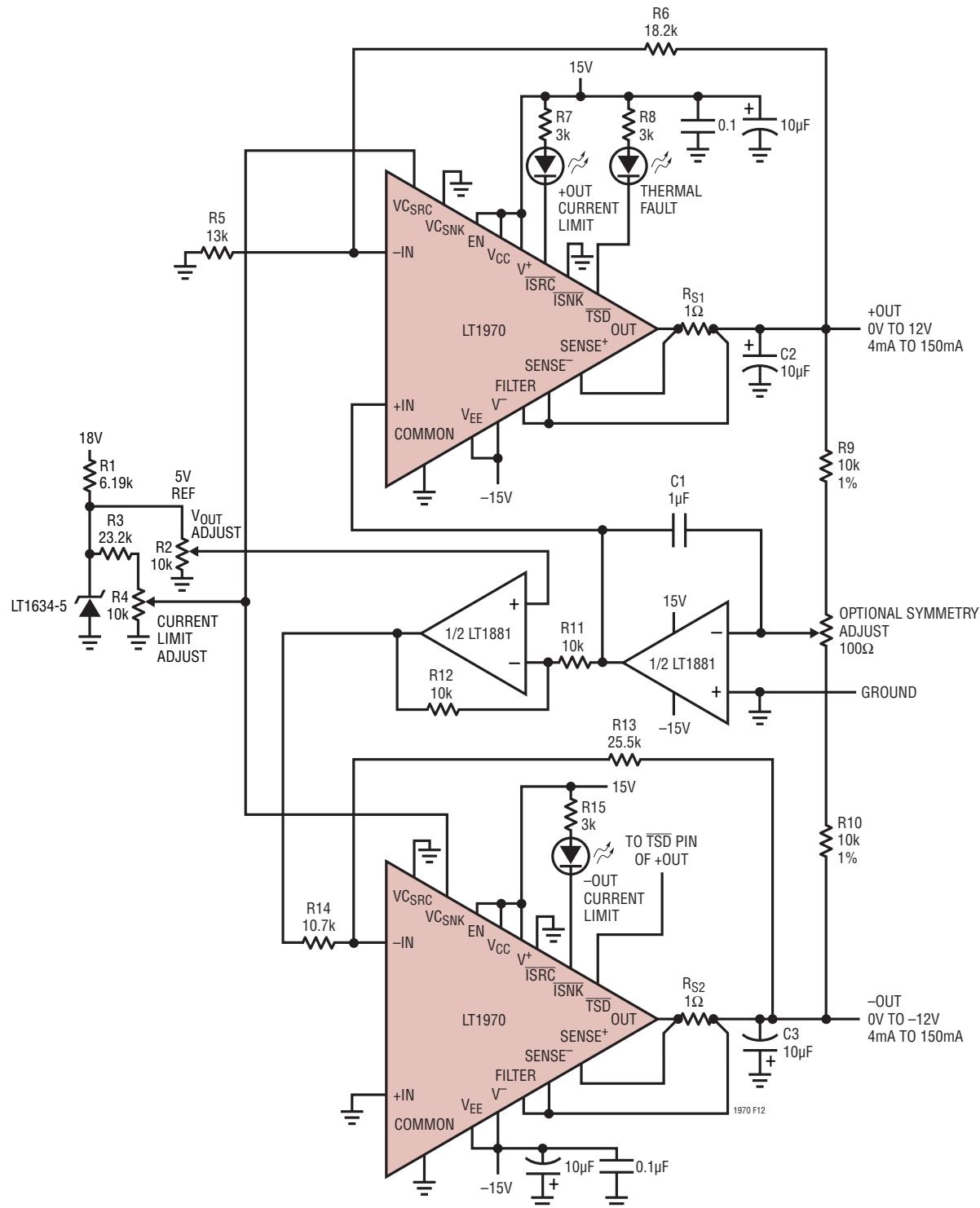

図12. デュアル・トラッキングのベンチ用電源

## アプリケーション情報

出力が完全に0Vまで変化できるように、LTC1046チャージポンプ・インバータを使って−5V電源を発生しています。これはLT1970の負レールを発生し、アンプの静止電流(標準7mA)だけをシンクする必要があります。

2番目のLT1970を使った、0V～±12Vのデュアル・トラッキング電源を図12に示します。+出力と−出力の間に接続された2個の10k抵抗の中点はLT1881デュアル・オペアンプのサーボ帰還ループによって0Vに保たれます。0Vを維持するには両方の出力は大きさが等しく極性が反対でなければならず、したがって相互にトラッキングします。一方の出力が電流リミットに達して電圧が低下すると、他方の出力が追従して共通負荷両端の対称な+電圧と−電圧を維持します。この場合も、出力電流制限は熱のためLT1970の最大能力よりも小さくなります。一方の出力は電流をソースするだけであり、他方の出力は電流をシンクするだけなので、別個の電流制限インジケータが各LT1970に使われています。出力フラグは一緒にOR接続できるので、両方のデバイスは同じサーマル・シャットダウン・インジケータを共有することができます。

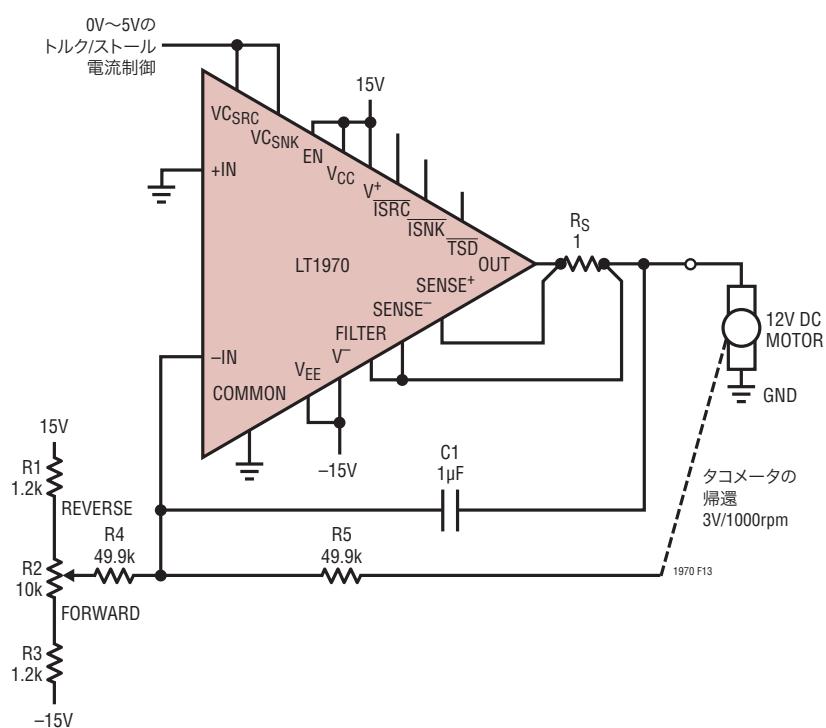

別の簡単なリニア・パワー・アンプ回路を図13に示します。これは、速度制御付きDCモーターのリニア・ドライバとして、LT1970を使います。同量の出力電流をソースおよびシンクする能力により、モーターの双方向回転が与えられます。速度制御はモーターに組み込まれたタコメータの出力を検出して行います。3V/1000rpmの標準的帰還信号は一組の望みの速度の入力電圧と比較されます。LT1970はユニティゲインで安定なので積分器として構成することができ、帰還速度信号を設定された入力信号と一致させるのに必要などんな電圧をもモーターに強制します。

さらに、アンプの電流リミットを調節して、モーターのトルクとストールの電流を制御することができます。信頼性のため、図4に示されている方式に似た帰還方式を使うことができます。ストールしたローターは電流制限状態を生じると想定すると、ストール電流制限を大きく減少させてモーターの巻線内の過度の電力消費を防ぐことができます。

図13. 簡単な双方向DCモーター速度コントローラ

## アプリケーション情報

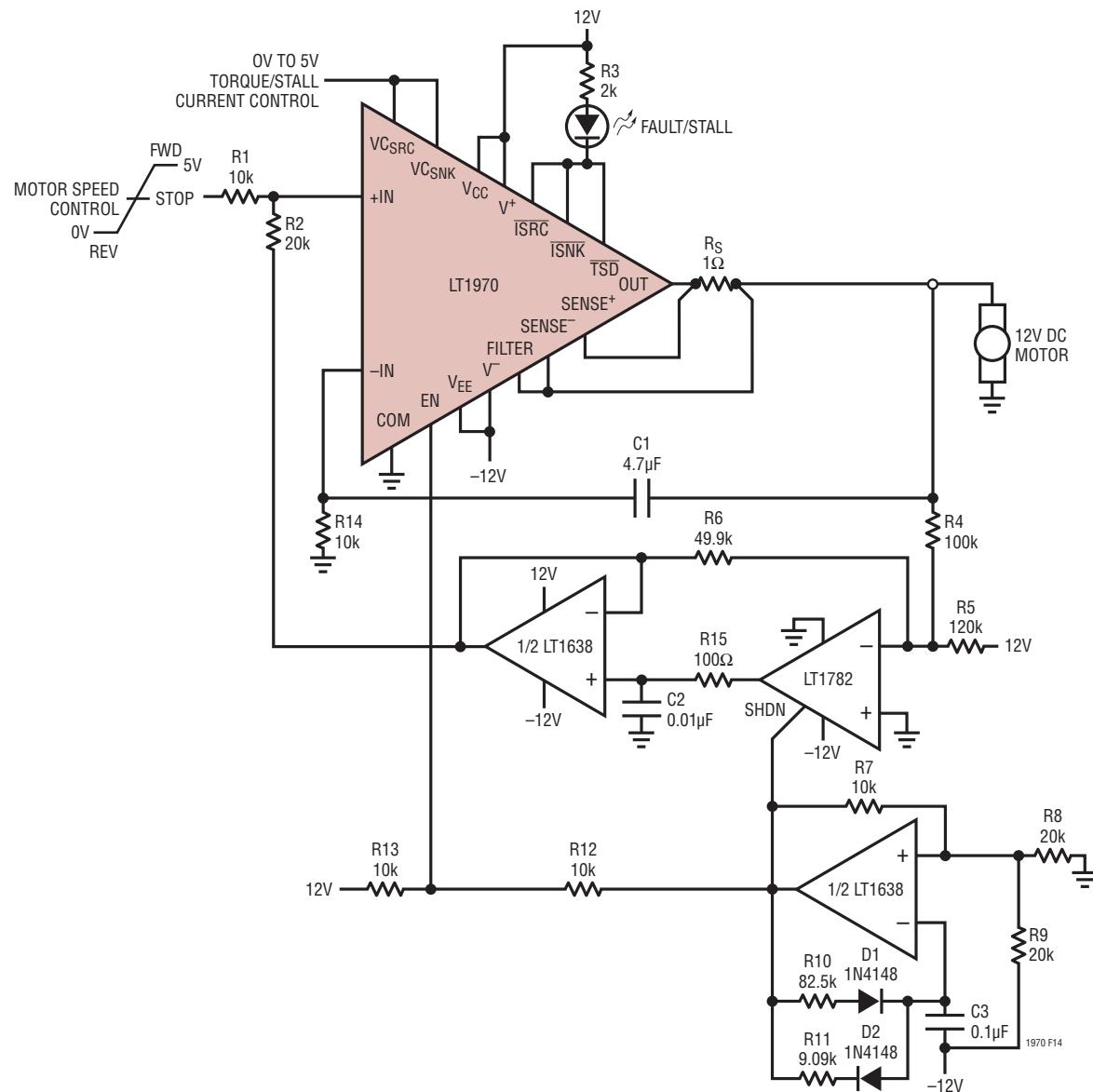

タコメータを使わないモーターの速度制御の場合、図14の回路が1つのアプローチを示しています。LT1970のイネーブル機能を使って、モーターへのドライブを周期的に停止することができます。ドライブが与えられないと、回転しているモーターはその回転速度に比例する逆EMF電圧を示します。LT1782はシャットダウン・ピンを備えた小型レール・トゥ・レール・アンプです。アンプはこの期間イネーブルされ、モーター両端の逆EMF電圧をサンプリングします。次いでこの電圧はLT1638デュアル・オペアンプの半分でバッファされ、LT1970積分器への帰還を与えるのに使われます。再度イネーブルされると、LT1970は、(速度設定入力電圧に比べた)速度帰還電圧が出力を固定値にセトリングするまで、モーターへのドライブを調整します。モーター速度入力の0V～5Vの信号は回転速度と回転方向の両方を制御します。

LT1638の他の半分は簡単なパルス発振器として使われ、モーターの逆EMFの周期的サンプリングを制御します。

図15は、LT1970の出力電流を増強するのがいかに容易であるかを示しています。この±5Aの電力段は相補的外部Nチャネル

およびPチャネルMOSFETを使って追加の電流を供給します。出力段の電源入力( $V^+$ と $V^-$ )は必要に応じてゲート・ドライブを供給するのに使われています。もっと高い出力電流では、センス抵抗 $R_{CS}$ の値を下げて、同じ簡単な電流制限御を維持します。

このクラスBの電力段は、高い周波数ではクロスオーバー歪みが明らかになるので、DCおよび低周波数(<1kHz)のアプリケーションを意図しています。

図15では、出力接続と電流検出入力の間にオプションの抵抗分割器がいくつか示されています。それらは、この電力段の負荷が取り去られる場合、または非常に低い電流レベルでだけ必要です。負荷が与えられていない大きなパワーデバイスは、飽和して出力電圧を電源レールの非常に近くまで引っ張ることがあります。電流センスアンプは、VCCとVEEの電源レールから少なくとも1V離れた入力電圧で適切に動作します。電流を増強したアプリケーションでは、検出入力ピンに接続する前に最大出力電圧レベルを1Vだけ減衰させる必要があるかもしれません。これは電流制限スレッショルドをわずかだけ下げます。

## アプリケーション情報

図14. タコメータを使わない簡単な双方向DCモーター速度コントローラ

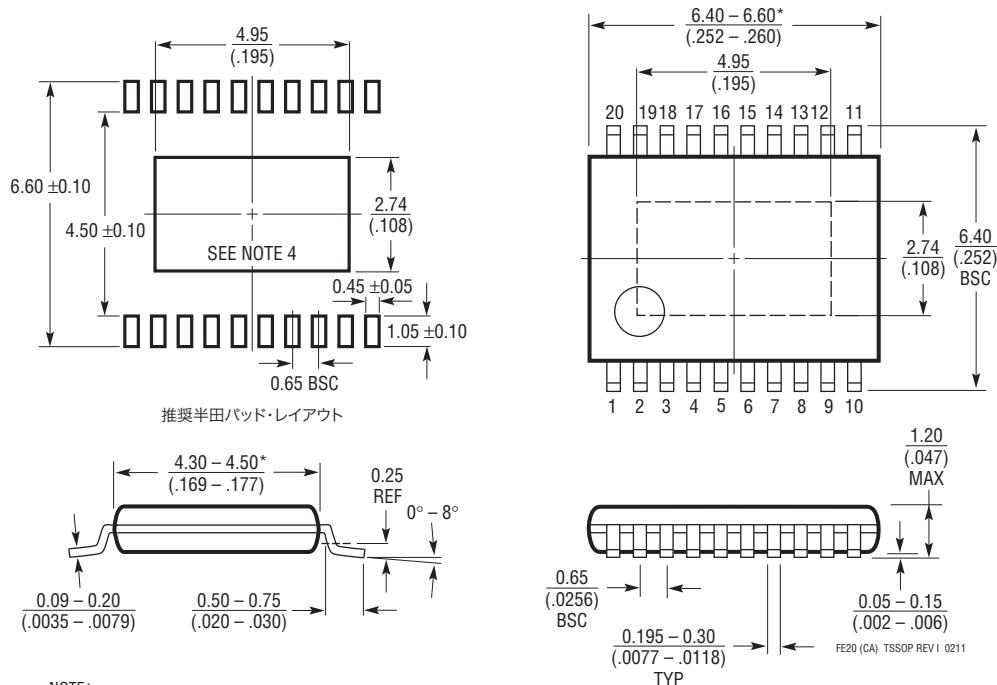

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> をご覧ください。

FEパッケージ

20ピン・プラスチックTSSOP (4.4mm)

(Reference LTC DWG # 05-08-1663 Rev I)

露出パッドのバリエーション CA

NOTE:

1. 標準寸法:ミリメートル

4. 露出パッド接着のための推奨最小PCBメタルサイズ

2. 寸法は  $\frac{\text{ミリメートル}}{(\text{インチ})}$

\*寸法にはモールドのバリを含まない。

モールドのバリは各サイドで0.150mm(0.006")を超えないこと

3. 図は実寸とは異なる

**改訂履歴** (改訂履歴は Rev C から開始)

| REV | 日付   | 概要                           | ページ番号    |

|-----|------|------------------------------|----------|

| C   | 7/12 | ロック図の修正<br>図14で電源電圧を変更、R6を追加 | 10<br>23 |

## アプリケーション情報

図15. ディスクリート・パワーデバイスを使って出力電流を5Aに増強する $A_v = -1$ のアンプ

## 関連製品

| 製品番号   | 説明                 | 注釈                              |

|--------|--------------------|---------------------------------|

| LT1010 | 高速±150mAパワーバッファ    | 帯域幅: 20MHz、スルーレート: 75V/ $\mu$ s |

| LT1206 | 250mA/60MHz電流帰還アンプ | シャットダウン・モード、調節可能な消費電流           |

| LT1210 | 1.1A/35MHz電流帰還アンプ  | $C_L = 10,000\text{pF}$ で安定     |