60ns、低消費電力

単一電源、グランド・センス

コンパレータ

1998年7月

## 特長

- 低消費電力 : 450 $\mu$ A

- 高速 : 20mVオーバードライブで60ns

5mVオーバードライブで85ns

- 低オフセット電圧 : 0.8mV

- 単一5V電源または $\pm$ 5V両電源で動作

- 負電源にまで拡張する入力同相範囲

- 最小入力スルーレート条件なし

- 相補TTL出力

- 位相反転を起こすことなく電源レールを超えて入力をドライブ可能

- LT1394、LT1016、およびLT1116とピン・コンパチブル

- 出力ラッチ機能

- SO-8パッケージで供給

## アプリケーション

- 高速A/Dコンバータ

- ゼロクロス検出器

- スイッチング・レギュレータ用電流センス

- 広範囲なV/Fコンバータ

- 高速パルス高/幅弁別器

- 高速トリガ

- ライン・レシーバ

- 高速サンプリング回路

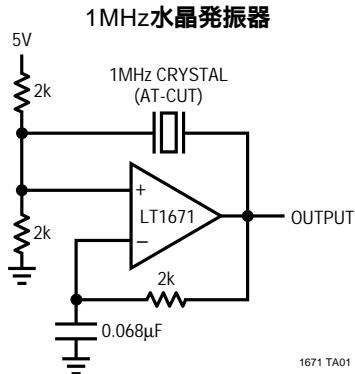

## 標準的応用例

## 概要

LT<sup>®</sup>1671は相補出力とラッチを備えた低消費電力、60nsのコンパレータです。入力同相範囲は、正電源より1.5V低い電位から負電源レールまでです。LT1394、LT1016、およびLT1116と同様、このコンパレータはTTLまたはCMOSロジックに直接インタフェースするように設計された相補出力を備えています。LT1671は単一5V電源または $\pm$ 5V両電源のどちらでも動作します。低オフセット電圧仕様と高利得により、高精度アプリケーションで使用できます。

LT1671は広範な動作条件で高速かつ安定して動作するように設計されています。出力段は最小の交差導通電流で、TTL、CMOS、または受動負荷を最大速度で両方向にアクティブにドライブします。他の高速コンパレータとは異なり、LT1671はアクティブ領域での低速遷移でも動作が安定しているので、最小入力スルーレートを規定する必要がありません。

LT1671には、出力でデータを保持するためのTTL/CMOS互換ラッチ機能が内蔵されています。ラッチはLATCHピンが“H”の間データを保持します。利得、オフセット、および負電源電流などのデバイス・パラメータが、負電源電圧の変動によって大きな影響を受けることはありません。

LT、LTC、LTはリニアテクノロジー社の登録商標です。

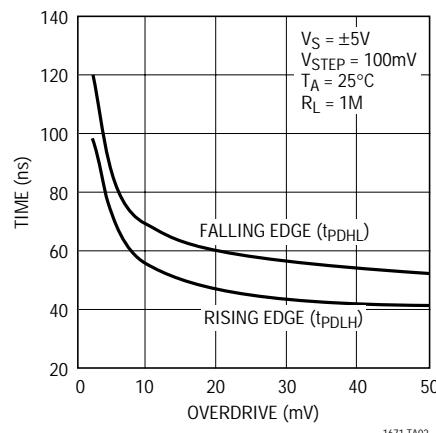

## 伝搬遅延とオーバードライブ

**絶対最大定格**

|                               |            |

|-------------------------------|------------|

| 正電源電圧 .....                   | 7V         |

| 負電源電圧 .....                   | - 7V       |

| 全電源電圧( $V^+ \sim V^-$ ) ..... | 12V        |

| 差動入力電圧 .....                  | $\pm 12V$  |

| 入力およびラッチ電流 .....              | $\pm 10mA$ |

| 出力電流( 連続 ) .....              | $\pm 20mA$ |

| 動作温度範囲 .....                  | 0 ~ 70     |

| 接合部温度 .....                   | 150        |

| 保存温度範囲 .....                  | - 65 ~ 150 |

| リード温度( 半田付け、10秒 ) .....       | 300        |

**パッケージ/発注情報**

| ORDER PART NUMBER |

|-------------------|

| LT1671CS8         |

| S8 PART MARKING   |

| 1671              |

TOP VIEW

S8 PACKAGE

8-LEAD PLASTIC SO

$T_{JMAX} = 150^\circ C$ ,  $\theta_{JA} = 190^\circ C/W$

ミリタリ・グレードに関してはお問い合わせください。

**電気的特性**注記がない限り、 $V^+ = 5V$ 、 $V^- = -5V$ 、 $V_{OUT}(Q) = 1.4V$ 、 $V_{LATCH} = V_{CM} = 0V$ 、 $T_A = 25$

| SYMBOL                           | PARAMETER                    | CONDITIONS                                     | MIN    | TYP          | MAX         | UNITS              |

|----------------------------------|------------------------------|------------------------------------------------|--------|--------------|-------------|--------------------|

| $V_{OS}$                         | Input Offset Voltage         | $R_S \leq 100\Omega$ (Note 1)                  | ●      | 0.8<br>4.0   | 2.5<br>4.0  | mV<br>mV           |

| $\frac{\Delta V_{OS}}{\Delta T}$ | Input Offset Voltage Drift   |                                                | ●      | 4            |             | $\mu V/C$          |

| $I_{OS}$                         | Input Offset Current         |                                                | ●      | 10<br>150    | 100         | nA<br>nA           |

| $I_B$                            | Input Bias Current           | (Note 2)                                       | ●      | 120<br>350   | 280         | nA<br>nA           |

| $V_{CMR}$                        | Input Voltage Range          | Single 5V Supply                               | ●<br>● | -5<br>0      | 3.5<br>3.5  | V<br>V             |

| CMRR                             | Common Mode Rejection Ratio  | $-5V \leq V_{CM} \leq 3.5V$                    | ●      | 55           | 100         | dB<br>dB           |

|                                  |                              | Single 5V Supply<br>$0V \leq V_{CM} \leq 3.5V$ | ●      | 55           | 100         | dB<br>dB           |

| PSRR                             | Power Supply Rejection Ratio | $4.6V \leq V^+ \leq 5.4V$                      | ●      | 50           | 85          | dB<br>dB           |

|                                  |                              | $-7V \leq V^- \leq -2V$                        | ●      | 60           | 90          | dB<br>dB           |

| $A_V$                            | Small Signal Voltage Gain    | $1V \leq V_{OUT} \leq 2V$                      |        | 2500<br>5000 |             | V/V                |

| $V_{OH}$                         | Output Voltage Swing High    | $V^+ \geq 4.6V$ , $I_{OUT} = 400\mu A$         | ●      | 2.7          | 3.1         | V                  |

|                                  |                              | $V^+ \geq 4.6V$ , $I_{OUT} = 4mA$              | ●      | 2.4          | 3.0         | V                  |

| $V_{OL}$                         | Output Voltage Swing Low     | $I_{OUT} = -400\mu A$                          | ●      | 0.3          | 0.5         | V                  |

|                                  |                              | $I_{OUT} = -4mA$                               | ●      | 0.4          |             | V                  |

| $I^+$                            | Positive Supply Current      |                                                | ●      | 450<br>1000  | 800<br>1000 | $\mu A$<br>$\mu A$ |

| $I^-$                            | Negative Supply Current      |                                                | ●      | 75<br>250    | 200<br>250  | $\mu A$<br>$\mu A$ |

## 電気的特性

注記がない限り、 $V^+ = 5V$ 、 $V^- = -5V$ 、 $V_{OUT}(Q) = 1.4V$ 、 $V_{LATCH} = V_{CM} = 0V$ 、 $T_A = 25^\circ C$

| SYMBOL          | PARAMETER                               | CONDITIONS                                | MIN | TYP | MAX  | UNITS |    |

|-----------------|-----------------------------------------|-------------------------------------------|-----|-----|------|-------|----|

| $V_{IH}$        | LATCH Pin High Input Voltage            |                                           | ●   | 2   |      | V     |    |

| $V_{IL}$        | LATCH Pin Low Input Voltage             |                                           | ●   |     | 0.8  | V     |    |

| $I_{IL}$        | LATCH Pin Current                       | $V_{LATCH} = 0V$                          | ●   |     | -250 | -1000 | nA |

| $t_{PD1}$       | Propagation Delay                       | $\Delta V_{IN} = 100mV$ , $V_{OD} = 20mV$ | ●   |     | 60   | 80    | ns |

|                 |                                         |                                           | ●   |     | 110  |       | ns |

| $t_{PD2}$       | Propagation Delay (Note 3)              | $\Delta V_{IN} = 100mV$ , $V_{OD} = 5mV$  | ●   |     | 85   | 100   | ns |

|                 |                                         |                                           | ●   |     | 130  |       | ns |

| $\Delta t_{PD}$ | Differential Propagation Delay (Note 3) | $\Delta V_{IN} = 100mV$ , $V_{OD} = 5mV$  |     |     | 15   | 30    | ns |

| $t_{LPD}$       | Latch Propagation Delay (Note 4)        |                                           |     |     | 60   |       | ns |

| $t_{SU}$        | Latch Setup Time (Note 4)               |                                           |     |     | -15  |       | ns |

| $t_H$           | Latch Hold Time (Note 4)                |                                           |     |     | 35   |       | ns |

| $t_{PW(D)}$     | Minimum Disable Pulse Width             |                                           |     |     | 30   |       | ns |

●は全動作温度範囲の規格値を意味する。

Note 1 : 入力オフセット電圧( $V_{OS}$ )は、一方の出力を1.4Vに強制して測定した電圧と、もう一方の出力を1.4Vに強制して測定した電圧の平均値として定義する。

Note 2 : 入力バイアス電流( $I_B$ )は、2つの入力電流の平均値として定義する。

Note 3 :  $t_{PD}$ および $\Delta t_{PD}$ は低いオーバードライブの自動計測装置で測定することはできない。LT1671は100mVのステップと20mVのオーバードライブによって100%テストされている。追加のDCテストが行われてすべての内部バイアスの条件が正しいことが保証されているならば、このテストで $t_{PD}$ および $\Delta t_{PD}$ のリミットを保証できることが相関テストによって確認されている。伝搬遅延( $t_{PD}$ )

は、実際の $V_{OS}$ にオーバードライブを加えて測定される。差動伝搬遅延は次式で定義される。

$$\Delta t_{PD} = t_{PD}^+ - t_{PD}^-$$

Note 4 : ラッチ伝搬遅延( $t_{LPD}$ )は、LATCHピンが解除されたときに出力が応答するまでの遅延時間である。ラッチ・セットアップ時間( $t_{SU}$ )は、ラッチ信号を行使する前に入力信号が安定していなければならない時間である。ラッチ・ホールド時間( $t_H$ )は、ラッチ信号が行使された後に入力信号が安定していなければならない時間である。

## 標準的性能特性

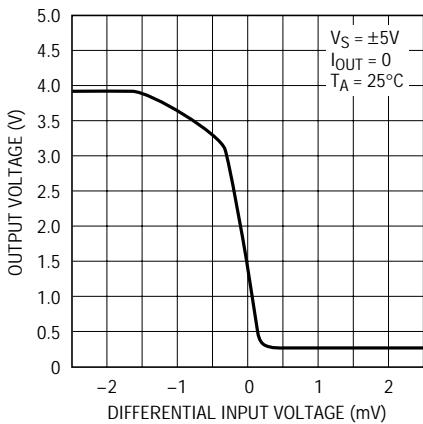

### 利得特性

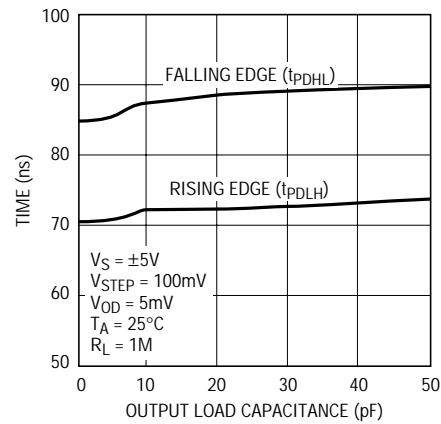

### 伝搬遅延と負荷容量

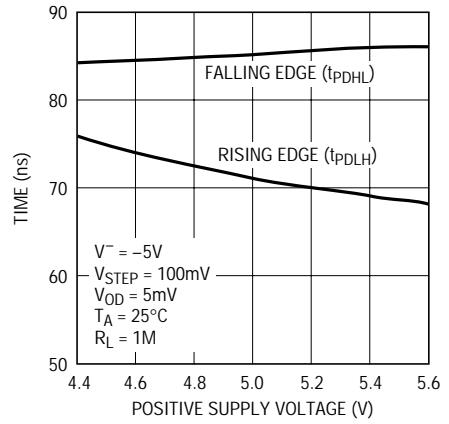

### 伝搬遅延と正電源電圧

## アプリケーション情報

### 同相モードに関する検討事項

LT1671は $\pm 5V$ 電源使用時には $-5V \sim 3.5V$ の同相範囲で、単一 $5V$ 電源使用時には $0V \sim 3.5V$ の同相範囲で仕様が規定されています。一般的に言えば、実際の電源電圧に関わらず、同相範囲は負電源より $0V$ 低いところから正電源より $1.5V$ 低いところまでです。同相モードのリミットの基準は、そこではまだ小さな差動入力信号に対して出力が正しく応答することです。

いずれかの入力信号が負の同相モード・リミットより低くなると、サブストレートとのあいだに形成される内部PNPダイオードがターンオンして、ダイを通して大きな電流が流れることができます。入力と負電源レールの間に外部ショットキ・クランプ・ダイオードを接続すると、内部ダイオードがターンオンするのを防止して、負方向のオーバードライブからの回復をスピードアップすることができます。

いずれの入力も正の同相モード・リミットを超えて上昇することができ、 $10mA$ を超す電流が流れるほど正電源を超えて高くならない限りコンパレータに損傷は与えません。他方の入力が許容同相範囲内にとどまる限り、機能は維持されます。ただし、入力信号が同相範囲内に戻るとき、伝搬遅延は増加します。

### 入力バイアス電流

入力バイアス電流は、出力を $1.4V$ に保って測定します。どのPNP差動入力段もそうであるように、LT1671のバイアス電流はデバイスから流れ出します。高い方の入力ではバイアス電流はゼロになり、低い方の入力では倍になります。

### LATCHピンのダイナミックス

LATCHピンの目的は、LATCHピンが'H'になるときの入力データを保持(出力をラッチ)することです。LATCHピンを接続しないとフロートして'H'状態になるので、フロースルー条件ではLATCHピンを接地することが必要です。

LATCHピンはTTLまたはCMOS出力でドライブするように設計されています。ヒステリシスは内蔵されていません。

### 高速設計技術

設計に多大な努力を払ったので、LT1671へ比較的使いやすくなりました。入力信号が遅いときでさえ、低速コンパレータよりもはるかに発振しにくくなっています。しかし、他の高速コンパレータと同様、PCボード・レイアウトおよび設計によって生じる問題が数多く存在します。最も一般的な問題として電源のバイパスがあります。低い電源インピーダンスを維持するためには、バイパスが必要です。電源ワイヤおよびPCトレースによる直流抵抗およびインダクタンスは、すぐに許容できないレベルにまで累積し、電源ラインは接続されているデバイスの内部電流レベルの変化とともに変動するようになります。ほとんどの場合、これで動作不良が生じます。また、隣接するデバイスがバイパスのない電源を通して接続されている場合は、有限の電源インピーダンスを通して相互作用する可能性があります。バイパス・コンデンサはデバイスの近くにエネルギーを蓄えることにより、電源インピーダンスを低くし、この問題を簡単に解決します。

バイパス・コンデンサは、できる限りLT1671の近くに配置してください。 $4.7\mu F$ のタンタル・コンデンサのような大きなコンデンサと並列に $0.1\mu F$ のセラミック・コンデンサのような質の良い高周波コンデンサを使用することを推奨します。

トレース配線の不備および高いソースインピーダンスも、同種の問題の原因となります。トレース長はできるだけ短くし、不要なカップリングを防ぐため、出力トレースは入力トレースと隣接して配置しないようにしてください。出力トレースが $4 \sim 5cm$ 以上あるときは、必ず抵抗で終端させ、発生する可能性のある反射をすべて除去できるようにしてください。抵抗値は、標準で $250 \sim 400$ です。また、ソースインピーダンスはできるだけ低く、なるべく $1k$ 以下にしておかなければなりません。

## 関連製品

| 製品番号   | 説明                       | 注釈                        |

|--------|--------------------------|---------------------------|

| LT1016 | UltraFast™高精度コンパレータ      | 業界標準 $10ns$ コンパレータ        |

| LT1116 | 12ns、単一電源グランド・センス・コンパレータ | LT1016の単一電源バージョン          |

| LT1394 | UltraFast単一電源コンパレータ      | $7ns$ 、 $6mA$ 、単一電源コンパレータ |

UltraFastはリニアテクノロジー社の商標です。