## 特長

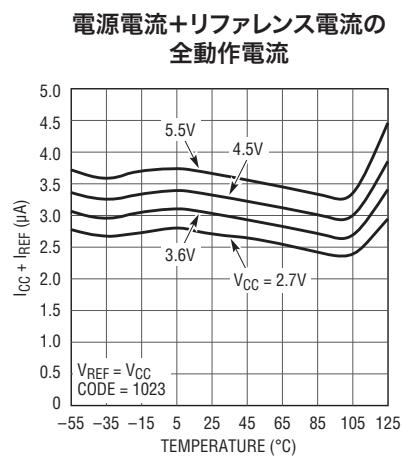

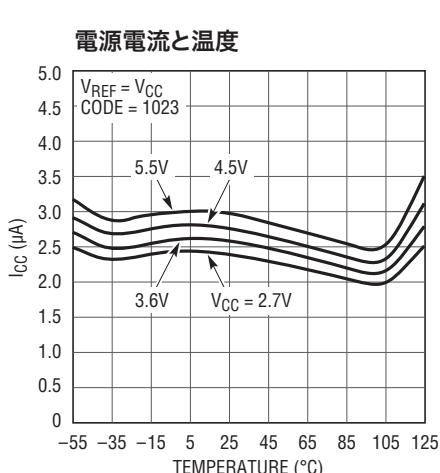

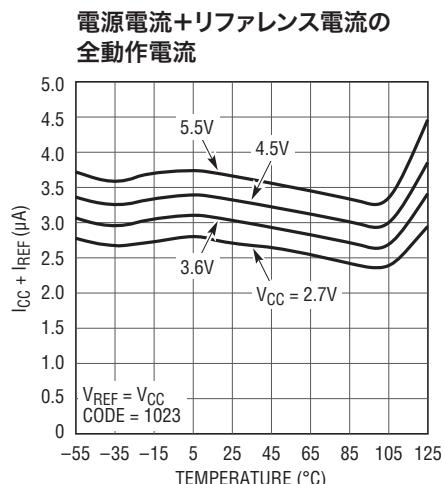

- 超低消費電流: バッテリ寿命を延長するDACあたり $1.5\mu\text{A}$ (標準)の $I_{CC}$ および $0.05\mu\text{A}$ のスリープ・モード

- 小型: 8リード MSOPに2個の10ビットDACを搭載—SO-8のボード・スペースの半分

- 2.7V～5.5Vの広い電源範囲で動作

- ダブル・バッファ構成により同時にDAC更新が可能

- $1000\text{pF}$ をドライブ可能なレール・トゥ・レール電圧出力

- リファレンス範囲には $0\text{V} \sim V_{CC}$ 比例出力のために電源が含まれる

- リファレンス入力インピーダンスはコードに無関係( $7.1\text{M}\Omega$ 標準)で、外部バッファが不要

- シュミットトリガ入力を備えた3線シリアル・インターフェース

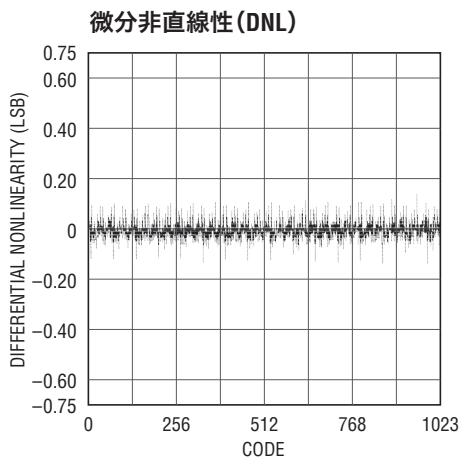

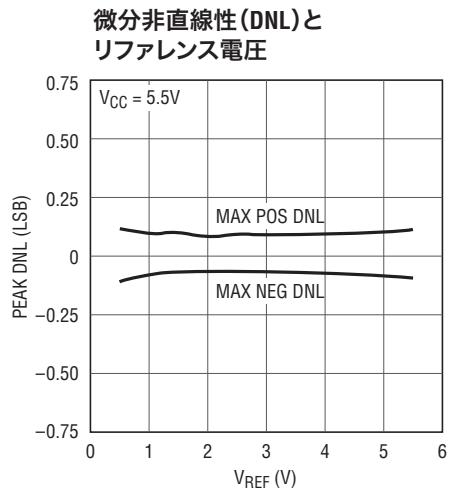

- 微分非直線性: $\pm 0.75\text{LSB}$ 最大

## アプリケーション

- モバイル通信

- 携帯用バッテリ駆動機器

- リモート機器またはアクセスできない機器の調整

- デジタル制御のアンプとアップテネータ

- 製造時またはフィールドでの較正

LT、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

## 概要

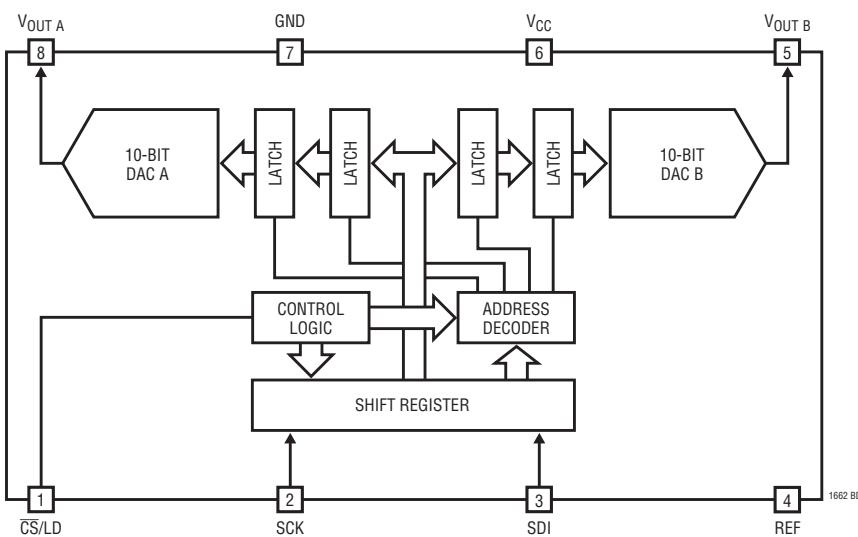

LTC<sup>®</sup>1662は、超低消費電流で、完全にバッファされた電圧出力を備えたデュアル10ビット・デジタル-アナログ・コンバータ(DAC)です。各DACは、計 $1.7\mu\text{A}$ (標準)の電源電流+リファレンス動作電流しか消費せず、 $1\text{mA}$ を超えるDC出力電流を供給し、最大 $1000\text{pF}$ の容量性負荷を確実にドライブ可能です。プログラム可能なスリープ・モードでは、さらに全動作電流は $0.05\mu\text{A}$ まで減少します。

リニアテクノロジー独自の固有単調性アーキテクチャは、優れた直線性ときわめて小さな外部フォーム・ファクタを実現します。ダブル・バッファされた入力ロジックは、同時更新機能を備えており、スリープ・モードを中断することなく、どちらのDACへの書き込みにも使用できます。

LTC1662は超低動作電流および小型サイズのため、電力が極度に制限される製品に最適です。ほとんどの設計では、消費電力への影響はほとんど確認されません。LTC1662は、消費電流がトリムポットと比べても数分の1である上、バッファされた低インピーダンス(標準 $0.5\Omega$ 、 $V_{CC} = 5\text{V}$ )のレール・トゥ・レール出力を与えます。

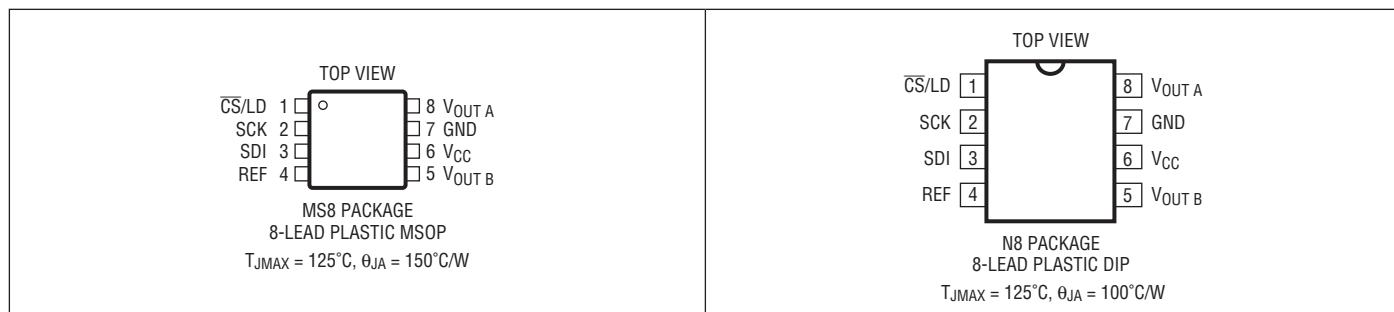

LTC1662は、LTC1661 60 $\mu\text{A}$ デュアル10ビットDACとピンおよびソフトウェア・コンパチブルです。8ピンMSOPおよびPDIPパッケージで供給されて、インダストリアル温度範囲で仕様が規定されています。

## ブロック図

## 絶対最大定格

(Note 1)

|                                                    |                               |                             |

|----------------------------------------------------|-------------------------------|-----------------------------|

| V <sub>CC</sub> からGND                              | -0.3V～7.5V                    | 動作温度範囲                      |

| ロジック入力からGND                                        | -0.3V～7.5V                    | LTC1662C ..... 0°C～70°C     |

| V <sub>OUT A</sub> , V <sub>OUT B</sub> , REFからGND | -0.3V～(V <sub>CC</sub> +0.3V) | LTC1662I ..... -40°C～85°C   |

| 最大接合部温度                                            | 125°C                         | リード温度(半田付け、10秒) ..... 300°C |

| 保存温度範囲                                             | -65°C～150°C                   |                             |

## ピン配置

## 発注情報

| 無鉛仕上げ           | テープアンドリール         | 製品マーキング    | パッケージ               | 温度範囲          |

|-----------------|-------------------|------------|---------------------|---------------|

| LTC1662CMS8#PBF | LTC1662CMS8#TRPBF | LTKB       | 8-Lead Plastic MSOP | 0°C to 70°C   |

| LTC1662IMS8#PBF | LTC1662IMS8#TRPBF | LTKC       | 8-Lead Plastic MSOP | -40°C to 85°C |

| LTC1662CN8#PBF  | LTC1662CN8#TRPBF  | LTC1662CN8 | 8-Lead Plastic DIP  | 0°C to 70°C   |

| LTC1662IN8#PBF  | LTC1662IN8#TRPBF  | LTC1662IN8 | 8-Lead Plastic DIP  | -40°C to 85°C |

| 鉛仕上げ            | テープアンドリール         | 製品マーキング    | パッケージ               | 温度範囲          |

| LTC1662CMS8     | LTC1662CMS8#TR    | LTKB       | 8-Lead Plastic MSOP | 0°C to 70°C   |

| LTC1662IMS8     | LTC1662IMS8#TR    | LTKC       | 8-Lead Plastic MSOP | -40°C to 85°C |

| LTC1662CN8      | LTC1662CN8#TR     | LTC1662CN8 | 8-Lead Plastic DIP  | 0°C to 70°C   |

| LTC1662IN8      | LTC1662IN8#TR     | LTC1662IN8 | 8-Lead Plastic DIP  | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲( $T_A = T_{MIN} \sim T_{MAX}$ )での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 2.7V \sim 5.5V$ 、 $V_{REF} \leq V_{CC}$ 、 $V_{OUT}$ に負荷なし。

| SYMBOL          | PARAMETER                          | CONDITIONS                                                                                                                              | MIN | TYP          | MAX      | UNITS                        |    |

|-----------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|----------|------------------------------|----|

| <b>精度</b>       |                                    |                                                                                                                                         |     |              |          |                              |    |

|                 | Resolution                         |                                                                                                                                         | ●   | 10           |          | Bits                         |    |

|                 | Monotonicity                       | (Note 2)                                                                                                                                | ●   | 10           |          | Bits                         |    |

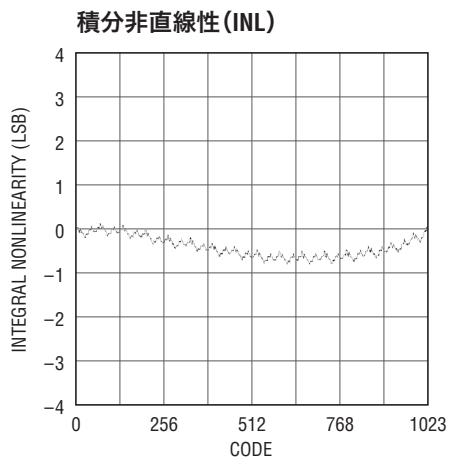

| DNL             | Differential Nonlinearity          | (Note 2)                                                                                                                                | ●   | ±0.12        | ±0.75    | LSB                          |    |

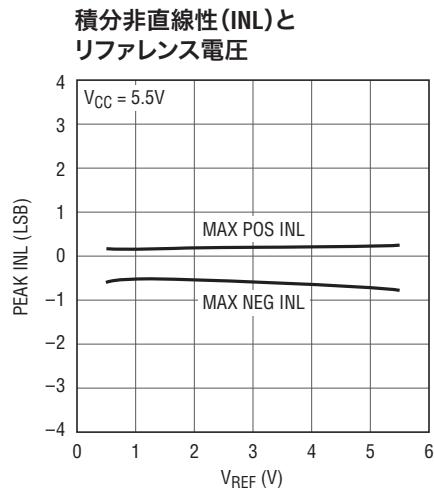

| INL             | Integral Nonlinearity              | (Note 2)                                                                                                                                | ●   | ±0.8         | ±4       | LSB                          |    |

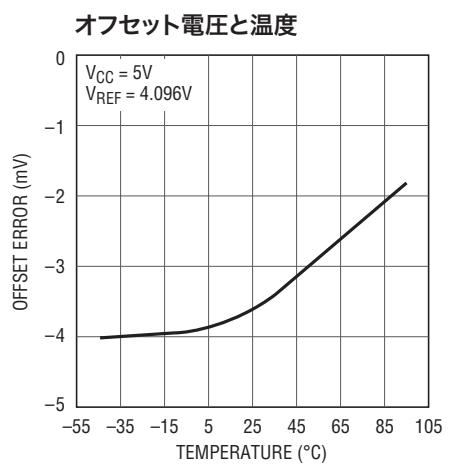

| Vos             | Offset Error                       | $V_{CC} = 5V$ , $V_{REF} = 4.096V$ , Measured at Code 20                                                                                | ●   | ±5           | ±25      | mV                           |    |

| Vos TC          | Vos Temperature Coefficient        |                                                                                                                                         |     | ±15          |          | $\mu\text{V}/^\circ\text{C}$ |    |

| GE              | Gain Error                         | $V_{CC} = 5V$ , $V_{REF} = 4.096V$                                                                                                      | ●   | ±1           | ±8       | LSB                          |    |

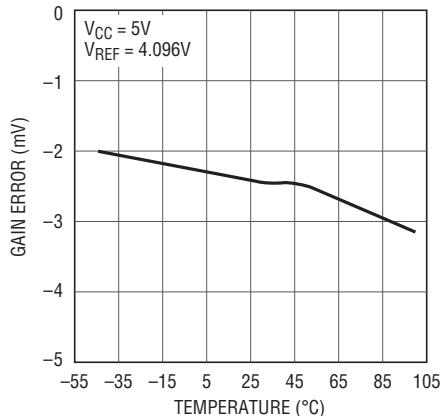

| GETC            | Gain Error Temperature Coefficient |                                                                                                                                         |     | ±12          |          | $\mu\text{V}/^\circ\text{C}$ |    |

| PSR             | Power Supply Rejection             | $V_{REF} = 2.5V$                                                                                                                        |     | 0.18         |          | LSB/V                        |    |

| <b>リファレンス入力</b> |                                    |                                                                                                                                         |     |              |          |                              |    |

|                 | Input Voltage Range                |                                                                                                                                         | ●   | 0            | $V_{CC}$ | V                            |    |

|                 | Input Resistance                   | Active Mode<br>Sleep Mode                                                                                                               | ●   | 3.9<br>2.5   | 7.1      | $M\Omega$<br>$G\Omega$       |    |

|                 | Input Capacitance                  |                                                                                                                                         |     | 10           |          | pF                           |    |

| <b>電源</b>       |                                    |                                                                                                                                         |     |              |          |                              |    |

| $V_{CC}$        | Positive Supply Voltage            | For Specified Performance                                                                                                               | ●   | 2.7          | 5.5      | V                            |    |

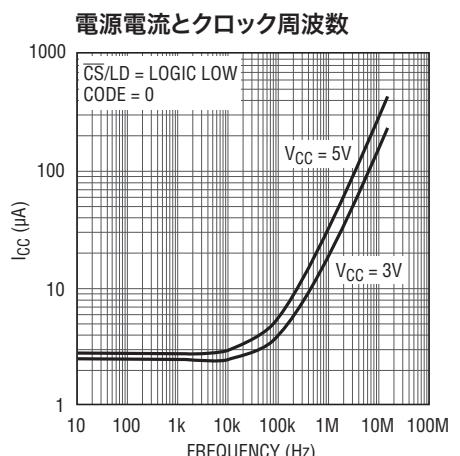

| $I_{CC}$        | Supply Current                     | $V_{CC} = 3V$ (Note 3)                                                                                                                  |     | 3.0          | 4.0      | $\mu\text{A}$                |    |

|                 |                                    | $V_{CC} = 5V$ (Note 3)                                                                                                                  |     | 3.5          | 4.5      | $\mu\text{A}$                |    |

|                 | Sleep Mode Operating Current       | $V_{CC} = 3V$ (Note 3)                                                                                                                  | ●   | 5.0          |          | $\mu\text{A}$                |    |

|                 |                                    | $V_{CC} = 5V$ (Note 3)                                                                                                                  | ●   | 5.5          |          | $\mu\text{A}$                |    |

|                 | Sleep Mode Operating Current       | Supply Plus Reference Current, $V_{CC} = V_{REF} = 5V$ (Note 3)                                                                         | ●   | 0.05         | 0.10     | $\mu\text{A}$                |    |

|                 |                                    |                                                                                                                                         | ●   | 0.18         |          | $\mu\text{A}$                |    |

| <b>DC性能</b>     |                                    |                                                                                                                                         |     |              |          |                              |    |

|                 | Short-Circuit Current Low          | $V_{OUT} = 0V$ , $V_{CC} = V_{REF} = 5V$ , Code = 1023 (Note 7)                                                                         | ●   | 5            | 12       | 70                           | mA |

|                 | Short-Circuit Current High         | $V_{OUT} = V_{CC} = V_{REF} = 5V$ , Code = 0 (Note 7)                                                                                   | ●   | 3            | 10       | 80                           | mA |

| <b>AC性能</b>     |                                    |                                                                                                                                         |     |              |          |                              |    |

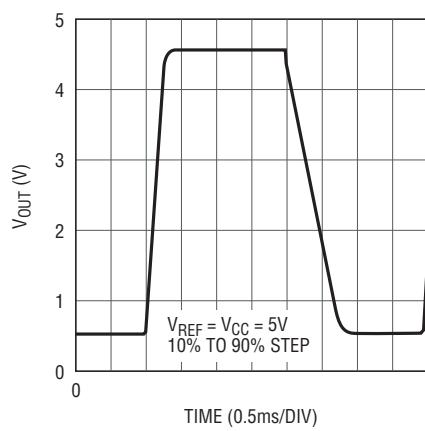

|                 | Voltage Output Slew Rate           | Rising (Notes 4, 5)<br>Falling (Notes 4, 5)                                                                                             |     | 20<br>7      |          | V/ms<br>V/ms                 |    |

|                 | Voltage Output Settling Time       | Rising $0.1V_{FS}$ to $0.9V_{FS} \pm 0.5\text{ LSB}$ (Notes 4, 5)<br>Falling $0.9V_{FS}$ to $0.1V_{FS} \pm 0.5\text{ LSB}$ (Notes 4, 5) |     | 0.40<br>0.75 |          | ms<br>ms                     |    |

|                 | Capacitive Load Driving            |                                                                                                                                         |     | 1000         |          | pF                           |    |

| <b>デジタルI/O</b>  |                                    |                                                                                                                                         |     |              |          |                              |    |

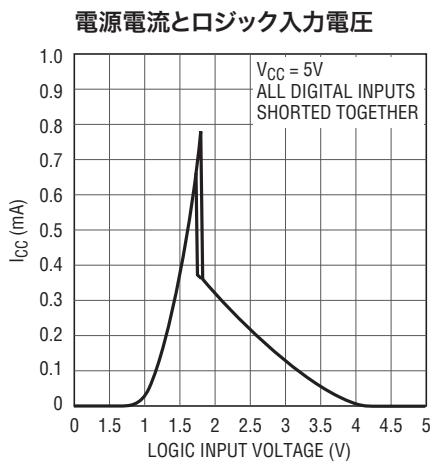

| $V_{IH}$        | Digital Input High Voltage         | $V_{CC} = 2.7V$ to $5.5V$                                                                                                               | ●   | 2.4          |          | V                            |    |

|                 |                                    | $V_{CC} = 2.7V$ to $3.6V$                                                                                                               | ●   | 2.0          |          | V                            |    |

| $V_{IL}$        | Digital Input Low Voltage          | $V_{CC} = 4.5V$ to $5.5V$                                                                                                               | ●   |              | 0.8      | V                            |    |

|                 |                                    | $V_{CC} = 2.7V$ to $5.5V$                                                                                                               | ●   |              | 0.6      | V                            |    |

| $I_{LK}$        | Digital Input Leakage              | $V_{IN} = \text{GND}$ to $V_{CC}$                                                                                                       | ●   | ±0.05        | ±1.0     | $\mu\text{A}$                |    |

| $C_{IN}$        | Digital Input Capacitance          |                                                                                                                                         |     | 1.5          |          | pF                           |    |

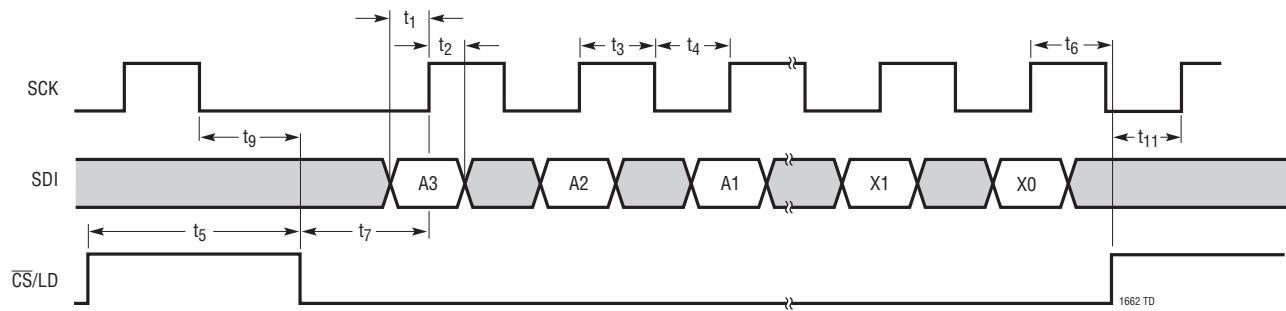

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。

| SYMBOL                                                    | PARAMETER                               | CONDITIONS                             |   | MIN | TYP | MAX  | UNITS |

|-----------------------------------------------------------|-----------------------------------------|----------------------------------------|---|-----|-----|------|-------|

| <b><math>V_{CC} = 4.5\text{V} \sim 5.5\text{V}</math></b> |                                         |                                        |   |     |     |      |       |

| $t_1$                                                     | SDI Setup                               | Relative to SCK Positive Edge          | ● | 55  |     |      | ns    |

| $t_2$                                                     | SDI Hold                                | Relative to SCK Positive Edge          | ● | 0   |     |      | ns    |

| $t_3$                                                     | SCK High Time                           | (Note 6)                               | ● | 30  |     |      | ns    |

| $t_4$                                                     | SCK Low Time                            | (Note 6)                               | ● | 30  |     |      | ns    |

| $t_5$                                                     | $\bar{CS}/LD$ Pulse Width               | (Note 6)                               | ● | 100 |     |      | ns    |

| $t_6$                                                     | LSB SCK High to $\bar{CS}/LD$ High      | (Note 6)                               | ● | 30  |     |      | ns    |

| $t_7$                                                     | $\bar{CS}/LD$ Low to SCK High           | (Note 6)                               | ● | 20  |     |      | ns    |

| $t_9$                                                     | SCK Low to $\bar{CS}/LD$ Low            | (Note 6)                               | ● | 0   |     |      | ns    |

| $t_{11}$                                                  | $\bar{CS}/LD$ High to SCK Positive Edge | (Note 6)                               | ● | 20  |     |      | ns    |

|                                                           | SCK Frequency                           | Square Wave (Note 6)                   | ● |     |     | 16.7 | MHz   |

| <b><math>V_{CC} = 2.7\text{V} \sim 5.5\text{V}</math></b> |                                         |                                        |   |     |     |      |       |

| $t_1$                                                     | SDI Setup                               | Relative to SCK Positive Edge (Note 6) | ● | 75  |     |      | ns    |

| $t_2$                                                     | SDI Hold                                | Relative to SCK Positive Edge (Note 6) | ● | 0   |     |      | ns    |

| $t_3$                                                     | SCK High Time                           | (Note 6)                               | ● | 50  |     |      | ns    |

| $t_4$                                                     | SCK Low Time                            | (Note 6)                               | ● | 50  |     |      | ns    |

| $t_5$                                                     | $\bar{CS}/LD$ Pulse Width               | (Note 6)                               | ● | 150 |     |      | ns    |

| $t_6$                                                     | LSB SCK High to $\bar{CS}/LD$ High      | (Note 6)                               | ● | 50  |     |      | ns    |

| $t_7$                                                     | $\bar{CS}/LD$ Low to SCK High           | (Note 6)                               | ● | 30  |     |      | ns    |

| $t_9$                                                     | SCK Low to $\bar{CS}/LD$ Low            | (Note 6)                               | ● | 0   |     |      | ns    |

| $t_{11}$                                                  | $\bar{CS}/LD$ High to SCK Positive Edge | (Note 6)                               | ● | 30  |     |      | ns    |

|                                                           | SCK Frequency                           | Square Wave (Note 6)                   | ● |     |     | 10   | MHz   |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

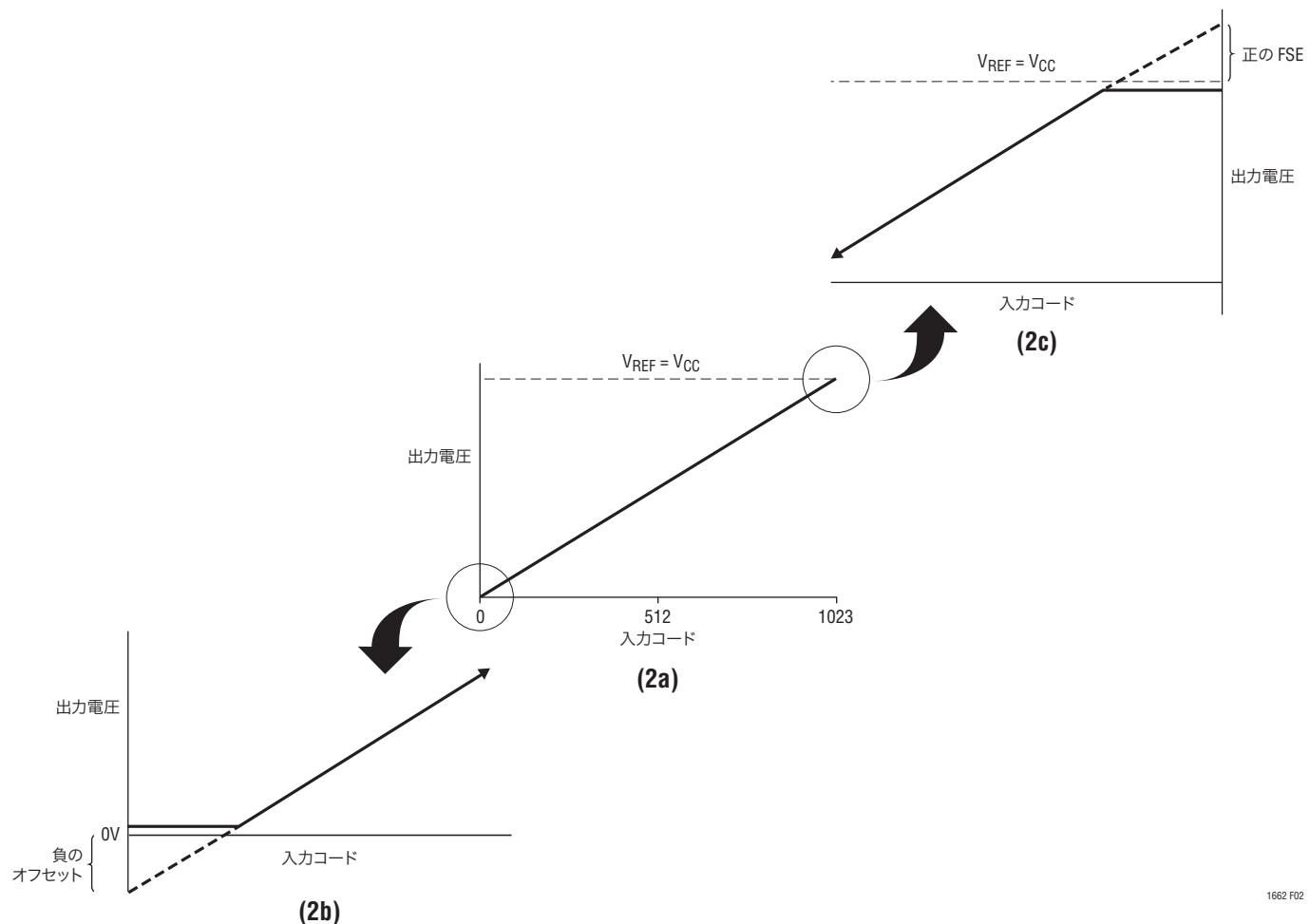

**Note 2:** 非直線性と単調性は  $V_{CC} = 5\text{V}$ ,  $V_{REF} = 4.096\text{V}$ , コード 20～コード 1023 で定義されており、テストされる。図2を参照。

**Note 3:** 0V または  $V_{CC}$  のデジタル入力。

**Note 4:** 負荷は  $100\text{pF}$  に並列接続された  $10\text{k}\Omega$ 。

**Note 5:**  $V_{CC} = V_{REF} = 5\text{V}$ 。DAC は  $0.1V_{FS}$  と  $0.9V_{FS}$  (つまり、コード  $k = 102$  とコード  $k = 922$ ) の間で切り替えられる。

**Note 6:** 設計によって保証されており、テストされない。

**Note 7:** 1つの DAC 出力に負荷が与えられる。

## 標準的性能特性

1662 G01

1662 G02

1662 G03

1662 G04

1662 G05

1662 G06

1662 G07

1662 G08

1662 G09

## 標準的性能特性

利得誤差と温度

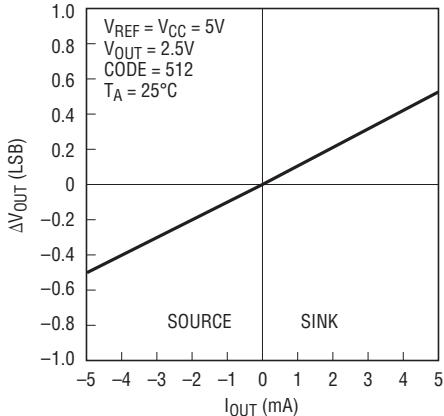

負荷レギュレーションと

出力電流(5V時)

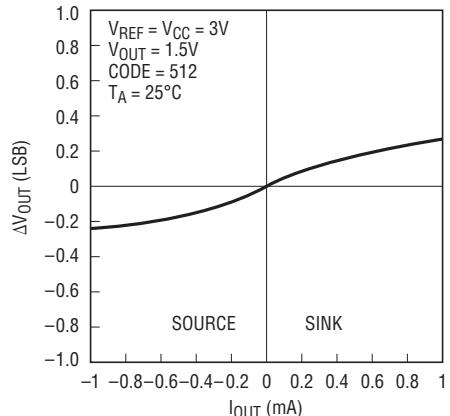

負荷レギュレーションと

出力電流(3V時)

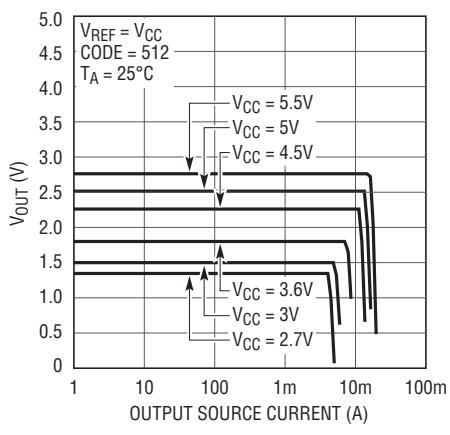

出力アンプ電流のソース能力

(ミッドスケール)

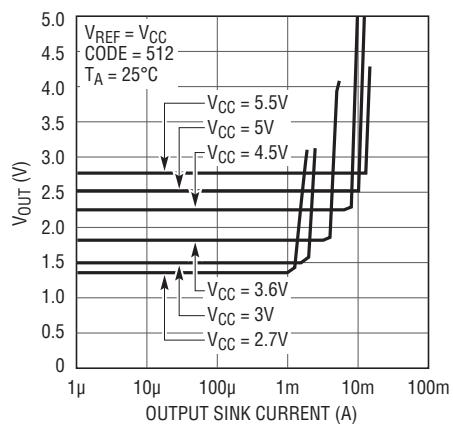

出力アンプ電流のシンク能力

(ミッドスケール)

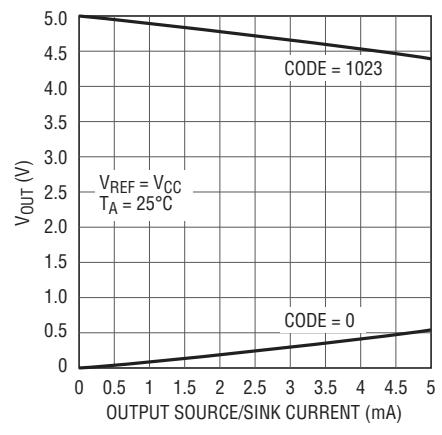

最大/最小出力電圧と

ソース/シンク出力電流( $V_{CC} = 5V$ )

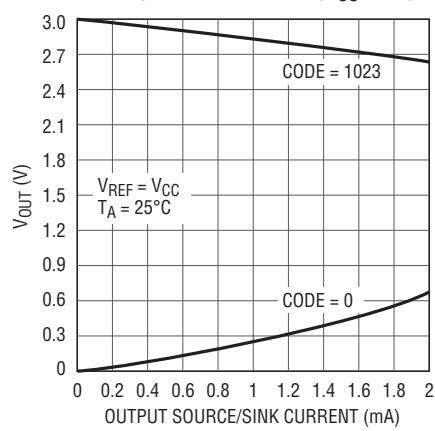

最大/最小出力電圧と

ソース/シンク出力電流( $V_{CC} = 3V$ )

大信号ステップ応答

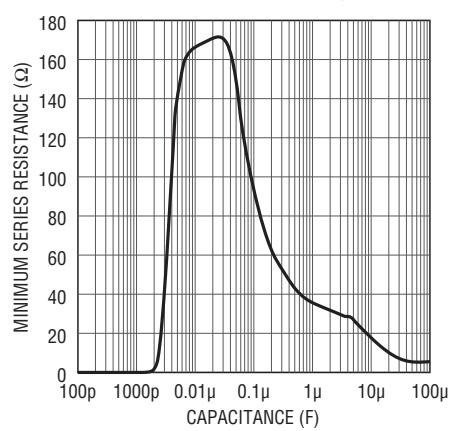

出力の最小直列抵抗と負荷容量

## ピン機能

**CS/LD(ピン1)**:シリアル・インターフェースのチップ・セレクト/負荷入力。 $\overline{CS}/LD$ が“L”的とき、SCKがイネーブルされ、SDIのデータをレジスタにシフトします。 $\overline{CS}/LD$ が“H”に引き上げられると、SCKがディスエーブルされ、制御コード(A3～A0)で指定される動作が実行されます。CMOSとTTLに対して互換性があります。

**SCK(ピン2)**:シリアル・インターフェースのクロック入力。CMOSとTTLに対して互換性があります。

**SDI(ピン3)**:シリアル・インターフェースのデータ入力。SDIピンの入力ワード・データは、SCKの立ち上がりエッジで16ビット・

レジスタにシフトされます。CMOSとTTLに対して互換性があります。

**REF(ピン4)**:リファレンス電圧入力。0V  $\leq V_{REF} \leq V_{CC}$ 。

**V<sub>OUT A</sub>, V<sub>OUT B</sub>(ピン8、ピン5)**:DACのアナログ電圧出力。出力範囲は次のとおりです。

$$0 \leq V_{OUTA}, V_{OUTB} \leq V_{REF} \left( \frac{1023}{1024} \right)$$

**V<sub>CC</sub>(ピン6)**:電源電圧入力。2.7V  $\leq V_{CC} \leq 5.5$ V。

**GND(ピン7)**:システム・グラウンド。

## 定義

**微分非直線性(DNL)**:任意の隣接する2つのコードで測定された変化と理想的な1 LSBの変化の間の差。任意の2つのコードの間のDNL誤差は次のように計算されます。

$$DNL = (\Delta V_{OUT} - LSB)/LSB$$

ここで、 $\Delta V_{OUT}$ は2つの隣接するコードの間の測定された電圧差です。

**フルスケール誤差(FSE)**:理想値からの実際のフルスケール電圧の偏差。FSEにはオフセットと利得誤差の影響が含まれます(図2を参照)。

**利得誤差(GE)**:理想的DACの伝達関数の勾配からの偏差を、フルスケールの LSB で表したもの。

**積分非直線性(INL)**:DACの伝達関数のエンドポイントを通る直線からの偏差(エンドポイントINL)。出力はゼロより下にはなれないで、直線性はフルスケールと、出力がゼロより大きくなることが保証されている最低コードの間で測定されます。与えられた入力コードでのINL誤差は次のように計算されます。

$$INL = [V_{OUT} - V_{OS} - (V_{FS} - V_{OS})(code/1023)]/LSB$$

ここで、 $V_{OUT}$ は与えられた入力コードで測定されたDACの出力電圧です。

**最下位ビット LSB**:2つの連続するコード間の理想電圧差。

$$LSB = V_{REF}/1024$$

**分解能(n)**:フルスケール範囲を分割するDAC出力の状態数( $2^n$ )を定めます。分解能には直線性の意味は含まれていません。

**電圧オフセット誤差(V<sub>OS</sub>)**:名目上は、DACにオールゼロが与えられたときの出力電圧。単一電源DACのオフセットは実際負になることがあります。出力はゼロより下になることができません(図2を参照)。

この理由で、単一電源DACのオフセットは、出力がゼロより大きくなることが保証されている最低コードで測定されます。

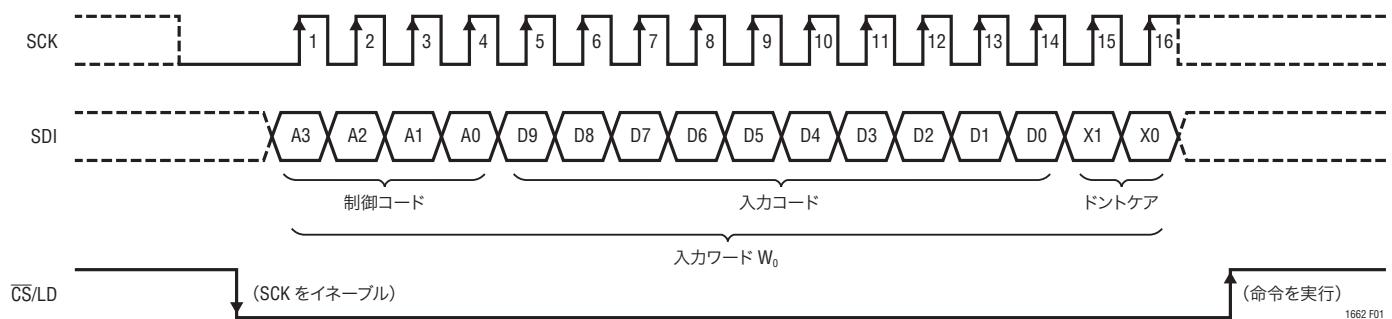

## タイミング図

## 動作

図1. レジスタへのロード・シーケンス

## 動作

表1. DACの制御機能

| 制御      |                                 | 入力レジスタの状態 | DACレジスタの状態 | パワーダウンの状態<br>(スリープ/ウェイク)                                                 | 注釈                                                                       |

|---------|---------------------------------|-----------|------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|

| A3      | A2 A1 A0                        |           |            |                                                                          |                                                                          |

| 0 0 0 0 | 変化なし                            | 更新なし      | 変化なし       | 変化なし                                                                     | 動作なし。パワーダウン状態の変化なし<br>(デバイスはウェイクまたはスリープ・モードに留まる)                         |

| 0 0 0 1 | DAC Aにロード                       | 更新なし      | 変化なし       | 変化なし                                                                     | 入力レジスタAにデータをロードDAC出力に変化なし。<br>パワーダウン状態に変化なし                              |

| 0 0 1 0 | DAC Bにロード                       | 更新なし      | 変化なし       | 変化なし                                                                     | 入力レジスタBにデータをロード。DAC出力に変化なし。<br>パワーダウン状態に変化なし                             |

| 1 0 0 0 | 変化なし                            | 出力を更新     | ウェイク       | 入力レジスタの既存の内容を両方のDACレジスタにロード。<br>出力を更新。デバイスがウェイクアップ                       | 入力レジスタの既存の内容を両方のDACレジスタにロード。<br>出力を更新。デバイスがウェイクアップ                       |

| 1 0 0 1 | DAC Aにロード                       | 出力を更新     | ウェイク       | 入力レジスタAにロード。DACレジスタに入力レジスタAの新しい内容とレジスタBの既存の内容をロード。出力を更新。<br>デバイスがウェイクアップ | 入力レジスタAにロード。DACレジスタに入力レジスタAの既存の内容とレジスタBの既存の内容をロード。出力を更新。<br>デバイスがウェイクアップ |

| 1 0 1 0 | DAC Bにロード                       | 出力を更新     | ウェイク       | 入力レジスタBにロード。DACレジスタに入力レジスタAの既存の内容とレジスタBの新しい内容をロード。出力を更新。<br>デバイスがウェイクアップ | 入力レジスタBにロード。DACレジスタに入力レジスタAの既存の内容とレジスタBの新しい内容をロード。出力を更新。<br>デバイスがウェイクアップ |

| 1 1 0 1 | 変化なし                            | 更新なし      | ウェイク       | デバイスがウェイクアップ入力およびDACレジスタに変化なし。<br>DAC出力はDACレジスタの既存の内容を反映。                | デバイスがウェイクアップ入力およびDACレジスタに変化なし。<br>DAC出力はDACレジスタの既存の内容を反映。                |

| 1 1 1 0 | 変化なし                            | 更新なし      | スリープ       | デバイスはスリープ状態になる。入力およびDACレジスタに変化なし。<br>DAC出力を高インピーダンス状態に設定。                | デバイスはスリープ状態になる。入力およびDACレジスタに変化なし。<br>DAC出力を高インピーダンス状態に設定。                |

| 1 1 1 1 | DACのAとBに同じ<br>10ビット・コードを<br>ロード | 出力を更新     | ウェイク       | 両方の入力レジスタにロード。入力レジスタの新しい内容を両方のDACレジスタにロード。出力を更新。デバイスがウェイクアップ             | 両方の入力レジスタにロード。入力レジスタの新しい内容を両方のDACレジスタにロード。出力を更新。デバイスがウェイクアップ             |

Note: 表に示されている以外のすべての制御コードは定義されておらず、テストされません。

## 伝達関数

LTC1662の伝達関数は次のとおりです。

$$V_{\text{OUT(IDEAL)}} = \left( \frac{k}{1024} \right) V_{\text{REF}}$$

ここで、kはDACの2進数の入力コードD9～D0に相当する10進数、V<sub>REF</sub>はREF(ピン4)の電圧です。

## パワーオン・リセット

LTC1662は、電源が最初に入れられたとき出力をゼロスケールにクリアして、システムの初期状態を一定に保ち、反復可能にします。

## 電源シーケンシング

REF(ピン4)の電圧は $-0.3V \leq V_{\text{REF}} \leq V_{\text{CC}} + 0.3V$  の範囲内に保つ必要があります(「絶対最大定格」を参照)。V<sub>CC</sub>(ピン6)の電圧が遷移している電源のターンオン・シーケンスとターンオフ・シーケンスの間は、特に注意が必要です。電源をシーケンス制御できないときは、ピン4(アノード)とピン6(カ

ソード)の間にショットキ・ダイオードを接続することによってREFの電圧をクランプしてください。

## シリアル・インターフェース

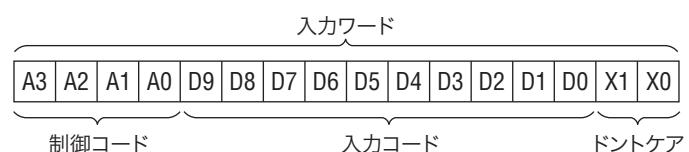

表2を参照してください。16ビットの入力ワードは4ビットの制御コード、10ビットの入力コードおよび2ビットのドントケアで構成されています。

表2. LTC1662の入力ワード

入力ワードは、レジスタにロードされた後(図1を参照)、内部でシリアルからパラレルの形式に変換されます。次いで、パラレルの10ビット幅の入力コードのデータ経路は2つのラッチ・レジスタによってバッファされます。

## 動作

これらのうちの最初のもの(入力レジスタ)は新しい入力コードをロードするのに使われます。2番目のバッファ(DACレジスタ)はDACの出力を更新するのに使われます。各DACには、10ビットの入力レジスタと10ビットのDACレジスタが備わっています。

適切な4ビット制御コードを選択することにより(表1を参照)、1つのDACにロードしたり、パワーダウン状態(スリープ/ウェイク)を変更するなどの単一動作を実行することができます。さらに、制御コードには一度に複数の動作を実行するものもあります。たとえば、このようなコードの1つはDAC Aにロードし、両方の出力を更新し、デバイスをウェイクアップします。DACは個別にまたは一緒にロードできますが、出力は常に一緒に更新されます。

### レジスタへのロード・シーケンス

図1を参照してください。 $\overline{CS/LD}$ が“L”に保たれていると、SDI入力のデータはSCKの立ち上がりエッジで16ビット・シフトレジスタにシフトされます。4ビットの制御コード(A3～A0)が最初にロードされ、次いで、10ビットの入力コード(D9～D0)がロードされます。いずれの場合もMSBからLSBへの順です。ドントケアの2ビット(X1とX0)は最後にロードされます。入力ワードの全16ビットがシフトされて取り込まれると、 $\overline{CS/LD}$ は“H”に引き上げられ、システムは表1に従って応答します。 $\overline{CS/LD}$ が“H”になるとクロックは内部でディスエーブルされます。注記： $\overline{CS/LD}$ が“L”に引き下げられるときSCKは“L”である必要があります。

### スリープ・モード

DACの制御コード1110<sub>b</sub>は特殊なスリープ命令のために予約されています(表1を参照)。このモードでは、静的な電力消費は大きく減少します。リファレンス入力とアナログ出力は高インピーダンス状態に設定され、DACのすべての設定はメモリに保存されるので、スリープ・モードから抜け出すと、ウェイク命令で更新されないDACの出力はそれらの最後のアクティブ状態に復元されます。

スリープ・モードは制御コード1110<sub>b</sub>を使ってロード・シーケンスを実行することにより開始されます(DAC入力コードD9～D0は無視されます)。

命令サイクルを節約するため、両方のDACをスリープの間に新しい入力コード(制御コードの0001<sub>b</sub>と0010<sub>b</sub>)で準備する

ことができます。次いで、1つのコマンド(1000<sub>b</sub>)を使って、デバイスのウェイクアップと出力値の更新の両方を実行することができます。

あるいは、スリープ時に片方のDACに新しい入力コードをロードすることもできます。次いで、1つのコマンドだけでもう一方のDACへのロード、デバイスのウェイクアップ、両方のDAC出力の更新を行います。

たとえば、スリープ時に制御コード0001<sub>b</sub>を使ってDAC Aへのロードを行います。次いで、制御コード0101<sub>b</sub>でDAC Bへのロード、デバイスのウェイクアップを行い、同時に両方のDAC出力を更新します。

### 電圧出力

LTC1662に内蔵されているレール・トゥ・レール出力アンプのそれぞれは、通常少なくとも1mA ( $V_{CC} = 5V$ )をソースまたはシンクすることができます。出力は負荷なしでどちらの電源レールからも数ミリボルト以内まで振幅し、レールへの負荷をドライブしているとき130Ω(標準)の等価出力抵抗を示します。出力アンプは最大1000pFの容量性負荷を安定してドライブします。

出力に直列に接続された小さな抵抗を使って、どんな負荷容量に対しても安定性を実現することができます。「標準的性能特性」のセクションの「出力の最小直列抵抗と負荷容量」の曲線を参照してください。

### レール・トゥ・レール出力に関する検討事項

どんなレール・トゥ・レールのDACでも、出力振幅は電源電圧範囲内に制限されます。

DACのオフセットが負であれば、図2bに示されているように、最小コードの出力が0Vに制限されます。

同様に、REFピンが $V_{CC}$ に接続されているとき、フルスケールの近くで出力が制限されることがあります。 $V_{REF} = V_{CC}$ で、DACのフルスケール誤差( $FSE = V_{OS} + GE$ )が正のとき、最高コードの出力が、図2cに示されているように、 $V_{CC}$ に制限されます。 $V_{REF}$ が $V_{CC} - FSE$ より小さいと、フルスケールの制限は生じません。

オフセットと直線性は、DACの伝達関数の(出力の制限が生じない)領域にわたって定義され、テストされます。

## 動作

図2. DAC伝達曲線に対するレール・トゥ・レール動作の影響。(a) 全体の伝達関数 (b) ゼロスケールに近いコードに対する負のオフセットの影響 (c)  $V_{REF} = V_{CC}$  のときのフルスケールに近い入力コードに対する正のフルスケール誤差の影響

# LTC1662

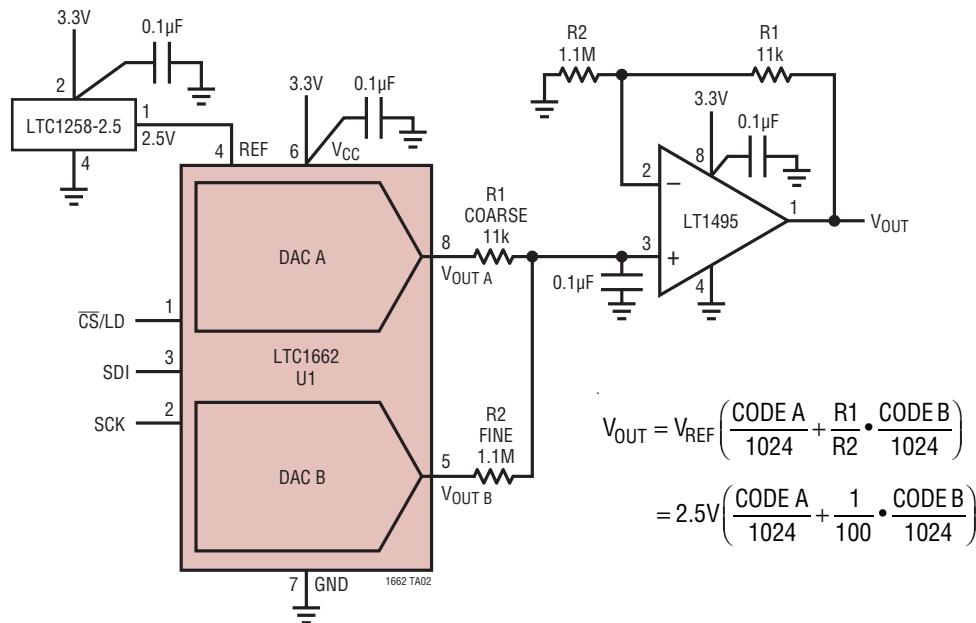

## 標準的応用例

粗調整/微調整付きマイクロパワー調整回路。全電源電流:9.5μA

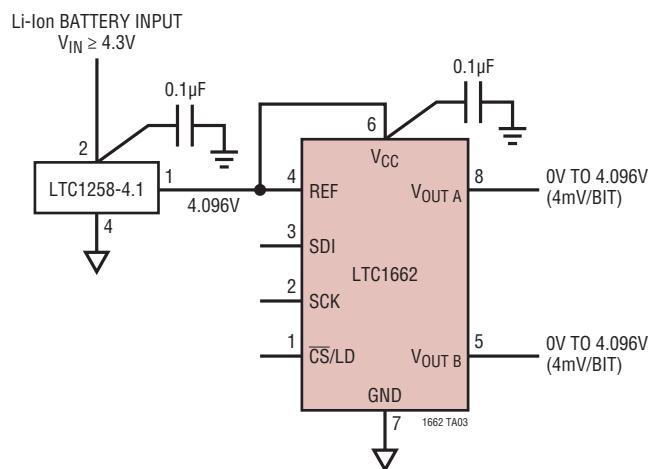

1個のリチウムイオン・バッテリで駆動される携帯アプリケーション

で使用したLTC1258およびLTC1662。全電源電流:8.2μA

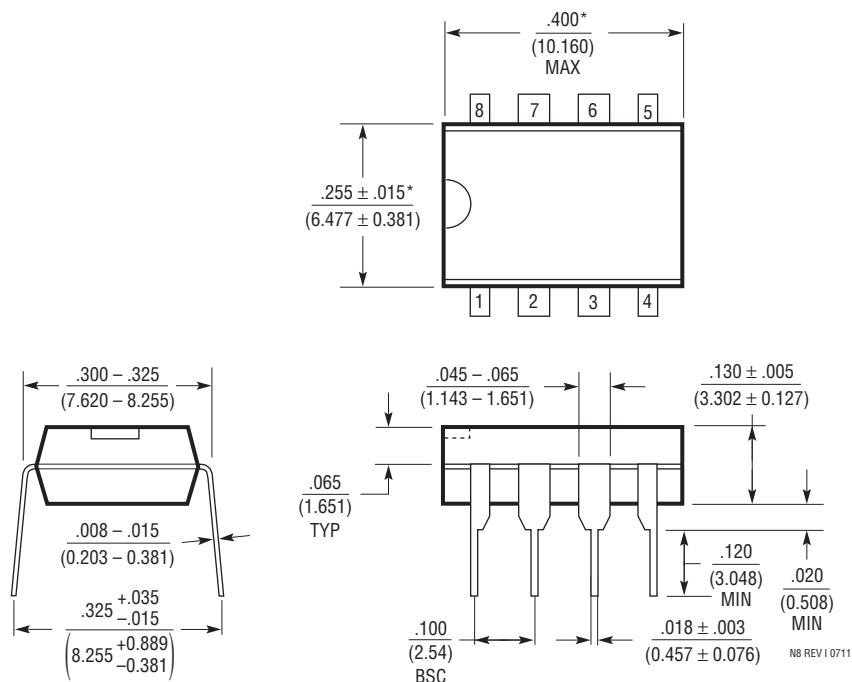

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/design-tools/packaging/> を参照してください。

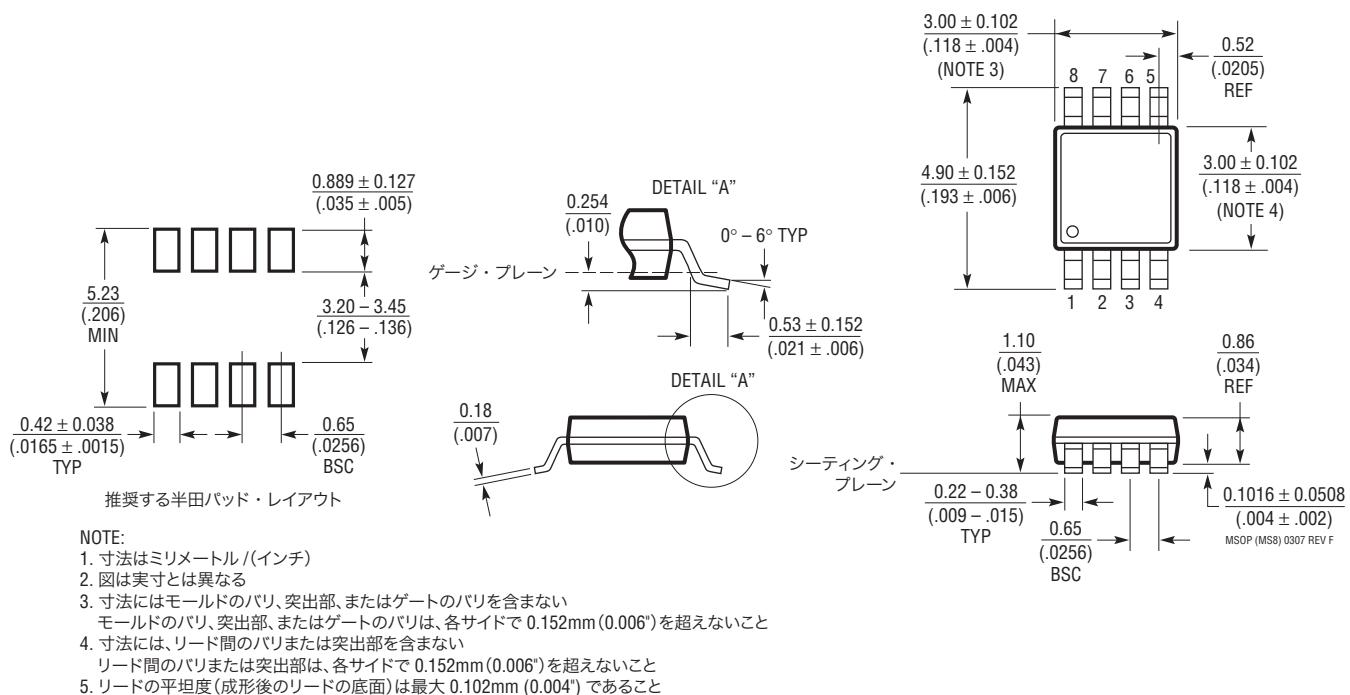

**MS8パッケージ

8ピン・プラスチック MSOP**

(Reference LTC DWG # 05-08-1660 Rev F)

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/design-tools/packaging/> を参照してください。

Nパッケージ

8ピンPDIP(細型0.300インチ)

(Reference LTC DWG # 05-08-1510 Rev I)

NOTE:

1. 尺法は インチ

ミリメートル

\*これらの寸法にはモールドのバリまたは突出部を含まない

モールドのバリまたは突出部は0.010インチ (0.254mm) を超えないこと

## 改訂履歴

| REV | 日付    | 概要                                                 | ページ番号   |

|-----|-------|----------------------------------------------------|---------|

| A   | 01/12 | 「タイミング特性」のセクションの標準値を削除。<br>「関連製品」の LTC1659 の情報を修正。 | 4<br>16 |

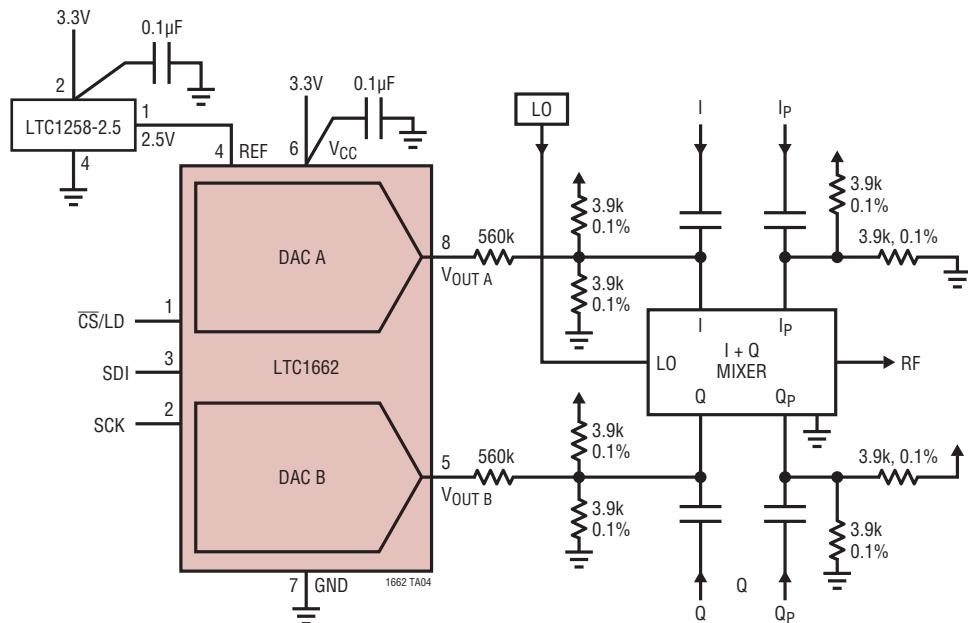

## 標準的応用例

ミキサの性能を最適化する超低消費電力DAC

## 関連製品

| 製品番号             | 説明                                                     | 注釈                                                                                                                              |

|------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| LTC1661          | デュアル10ビットV <sub>OUT</sub> DAC、8ピンMSOPパッケージ             | V <sub>CC</sub> =2.7V~5.5V、DAC当たり60μA、レール・トゥ・レール出力                                                                              |

| LTC1663          | 2線インターフェース付きのシングル10ビットV <sub>OUT</sub> DAC、SOT-23パッケージ | V <sub>CC</sub> =2.7V~5.5V、内部リファレンス、60μA                                                                                        |

| LTC1664          | 16ピン細型SSOPのクワッド10ビットV <sub>OUT</sub> DAC               | V <sub>CC</sub> =2.7V~5.5V、DAC当たり59μA、レール・トゥ・レール出力                                                                              |

| LTC1665/LTC1660  | 16ピン細型SSOPのオクタル8/10ビットV <sub>OUT</sub> DAC             | V <sub>CC</sub> =2.7V~5.5V、DAC当たり56μA、レール・トゥ・レール出力                                                                              |

| LTC1446/LTC1446L | 内部リファレンス付きデュアル12ビットV <sub>OUT</sub> DAC、SO-8パッケージ      | LTC1446:V <sub>CC</sub> =4.5V~5.5V、V <sub>OUT</sub> =0V~4.095V<br>LTC1446L:V <sub>CC</sub> =2.7V~5.5V、V <sub>OUT</sub> =0V~2.5V |

| LTC1448          | デュアル12ビットV <sub>OUT</sub> DAC、8ピンMSOPパッケージ             | V <sub>CC</sub> =2.7V~5.5V、外部リファレンスをV <sub>CC</sub> に接続可能                                                                       |

| LTC1454/LTC1454L | 追加機能付きデュアル12ビットV <sub>OUT</sub> DAC、SO-16パッケージ         | LTC1454:V <sub>CC</sub> =4.5V~5.5V、V <sub>OUT</sub> =0V~4.095V<br>LTC1454L:V <sub>CC</sub> =2.7V~5.5V、V <sub>OUT</sub> =0V~2.5V |

| LTC1458/LTC1458L | 追加機能付きクワッド12ビット・レール・トゥ・レール出力DAC                        | LTC1458:V <sub>CC</sub> =4.5V~5.5V、V <sub>OUT</sub> =0V~4.095V<br>LTC1458L:V <sub>CC</sub> =2.7V~5.5V、V <sub>OUT</sub> =0V~2.5V |

| LTC1659          | シングル、レール・トゥ・レール12ビットV <sub>OUT</sub> DAC、8ピンMSOPパッケージ  | V <sub>CC</sub> =2.7V~5.5V、低消費電力乗算型V <sub>OUT</sub> DAC。<br>GNDからREFの出力振幅。REF入力をV <sub>CC</sub> に接続可能                           |