## 特長

- 3V電源、分解能12ビット

- 低消費電流：160 $\mu$ A標準

- 自動シャットダウン時の消費電流：1nA

- 保証最大DNL：±3/4 LSB

- 2.7Vでの動作を保証

(5Vバージョンを用意：LTC1594/LTC1598)

- マルチブレクサ：4チャネルMUX (LTC1594L)

8チャネルMUX (LTC1598L)

- 独立したMUX出力およびADC入力ピン

- MUXとADCを別々に制御可能

- サンプリング・レート：10.5ksps

- QSPI、SPI、MICROWIRE™などに対応するI/O

- 小型パッケージ：16ピン細型SO (LTC1594L)

24ピンSSOP (LTC1598L)

## アプリケーション

- ペン・スクリーン・デジタイザ

- バッテリ駆動システム

- リモート・データ収集

- 絶縁型データ収集

- バッテリ監視

- 温度測定

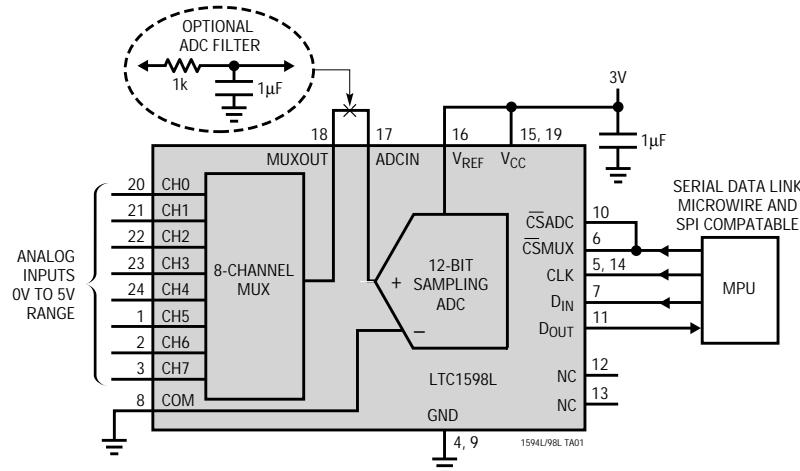

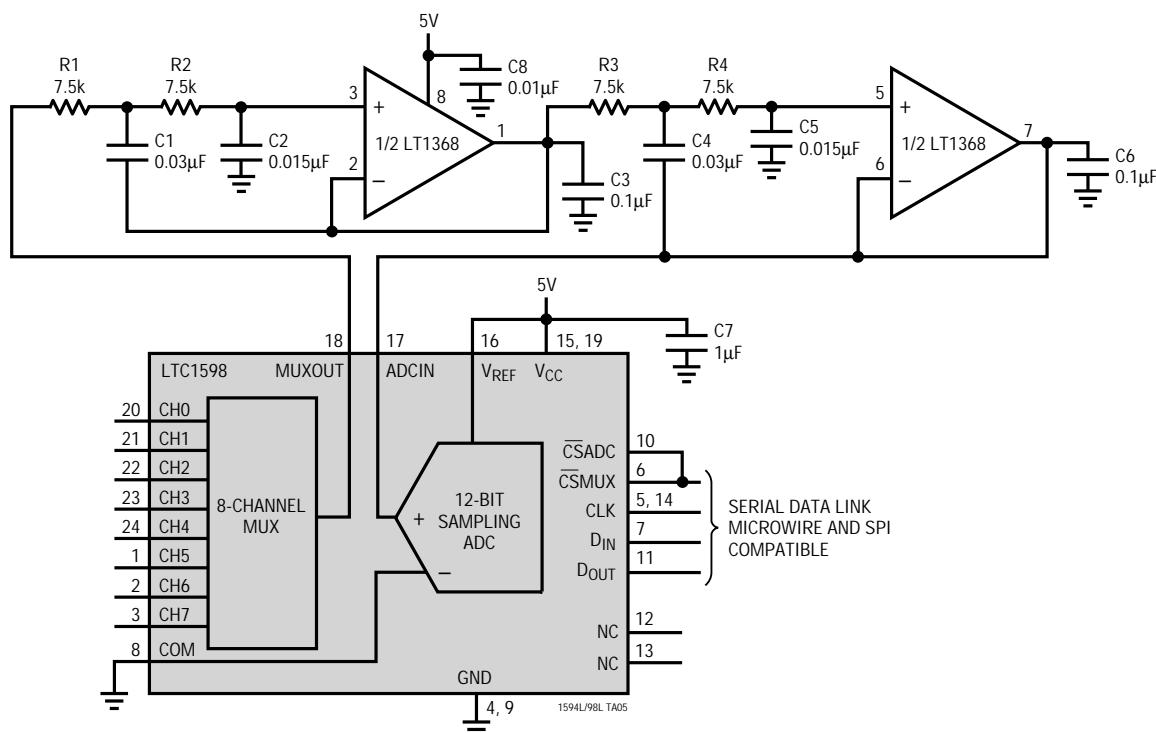

## 標準的応用例

3V電流で動作し、200Hzサンプリングの12 $\mu$ W、8チャネル、12ビットADC

## 概要

LTC®1594L/LTC1598Lは、それぞれ4チャネルおよび8チャネル・マルチブレクサの3Vマイクロパワー、12ビット・サンプリングA/Dコンバータです。変換実行時の消費電力はわずか標準160 $\mu$ Aですが、変換を行っていないときは自動的に標準1nAまでパワーダウンします。LTC1594Lは16ピンSOパッケージ、LTC1598Lは24ピンSSOPパッケージで供給されます。どちらも3V電源で動作します。これらの12ビット・スイッチト・キャパシタ逐次比較型ADCには、サンプル・ホールドが内蔵されています。

内蔵シリアル・ポートにより、3本または4本の伝送線を通してさまざまなマイクロプロセッサおよびマイクロコントローラへ効率よくデータ転送を行えます。このような伝送機能をマイクロパワー消費電力で実現しているため、リモート配置が可能であり、また絶縁バリアを通したデータ伝送も可能です。

この回路は計測アプリケーションで使用したり、外部リファレンス電圧を接続して使用することができます。また、高インピーダンスのアナログ入力および縮小スパン(1.5V以下のフルスケール)で動作可能なため、多くのアプリケーションでセンサやトランズデューサに直接接続でき、利得段を必要としません。

**L**、**LTC**、**LTI**はリニアテクノロジー社の登録商標です。

MICROWIREは、ナショナル・セミコンダクター社の商標です。

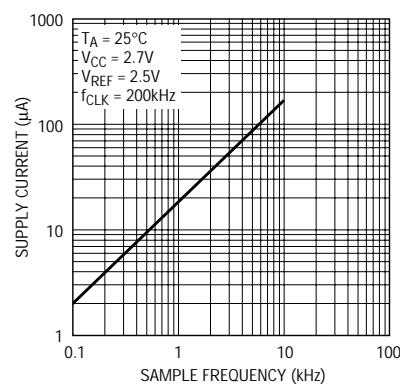

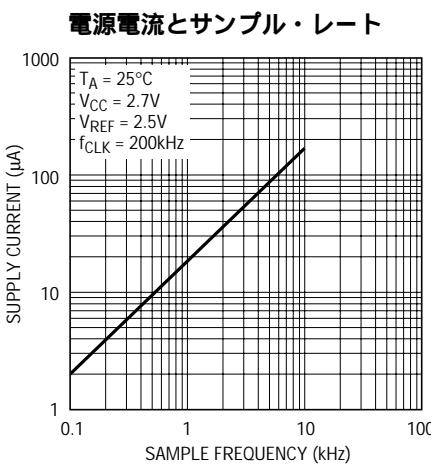

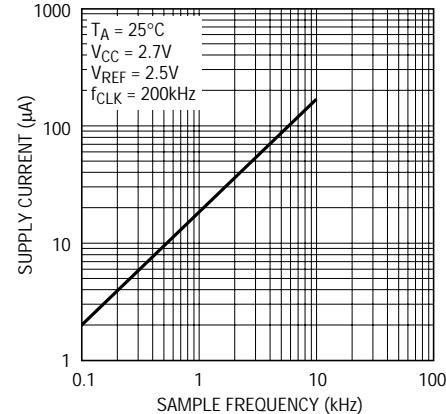

### 電源電流とサンプル・レート

## 絶対最大定格

(Notes 1, 2)

GNDに対する電源電圧(  $V_{CC}$  ) ..... 12V

### 電圧

アナログ・リファレンス ..... - 0.3V ~ (  $V_{CC}$  + 0.3V )

アナログ入力 ..... - 0.3V ~ (  $V_{CC}$  + 0.3V )

デジタル入力 ..... - 0.3V ~ 12V

デジタル出力 ..... - 0.3V ~ (  $V_{CC}$  + 0.3V )

消費電力 ..... 500mW

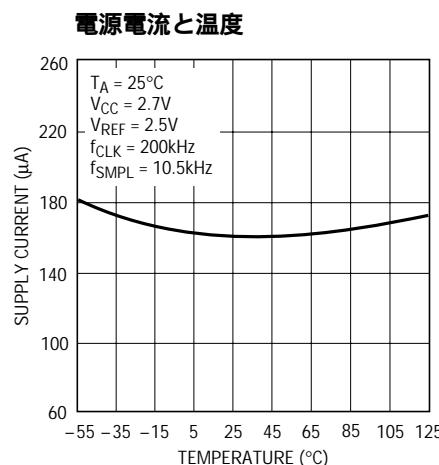

### 動作温度範囲

LTC1594LCS/LTC1598LCG ..... 0 ~ 70

LTC1594LIS/LTC1598LIG ..... - 40 ~ 85

保存温度範囲 ..... - 65 ~ 150

リード温度( 半田付け、10秒 ) ..... 300

## パッケージ/発注情報

| TOP VIEW                                             | ORDER PART NUMBER    | TOP VIEW            | ORDER PART NUMBER |

|------------------------------------------------------|----------------------|---------------------|-------------------|

|                                                      |                      |                     |                   |

| CH0 1                                                | 16 $V_{CC}$          | 24 CH4              | LTC1598LCG        |

| CH1 2                                                | 15 MUXOUT            | 23 CH3              | LTC1598LIG        |

| CH2 3                                                | 14 D <sub>IN</sub>   | 22 CH2              |                   |

| CH3 4                                                | 13 CS <sub>MUX</sub> | 21 CH1              |                   |

| ADCIN 5                                              | 12 CLK               | 20 CH0              |                   |

| V <sub>REF</sub> 6                                   | 11 $V_{CC}$          | 19 $V_{CC}$         |                   |

| COM 7                                                | 10 D <sub>OUT</sub>  | 18 MUXOUT           |                   |

| GND 8                                                | 9 CS <sub>SADC</sub> | 17 ADCIN            |                   |

| S PACKAGE<br>16-LEAD PLASTIC SO                      |                      | 16 V <sub>REF</sub> |                   |

| T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 120°C/W |                      | 15 $V_{CC}$         |                   |

|                                                      |                      | 14 CLK              |                   |

|                                                      |                      | 13 NC               |                   |

| G PACKAGE<br>24-LEAD PLASTIC SSOP                    |                      |                     |                   |

| T <sub>JMAX</sub> = 150°C, θ <sub>JA</sub> = 110°C/W |                      |                     |                   |

ミリタリ・グレードに関してはお問い合わせください。

## 推奨動作条件 ( Note 5 )

| SYMBOL           | PARAMETER                                                   | CONDITIONS                    | MIN | TYP | MAX | UNITS |

|------------------|-------------------------------------------------------------|-------------------------------|-----|-----|-----|-------|

| $V_{CC}$         | Supply Voltage ( Note 3 )                                   |                               | 2.7 | 3.6 |     | V     |

| $f_{CLK}$        | Clock Frequency                                             | $V_{CC}$ = 2.7V<br>( Note 4 ) |     | 200 |     | kHz   |

| $t_{CYC}$        | Total Cycle Time                                            | $f_{CLK}$ = 200kHz            | 95  |     |     | μs    |

| $t_{hDI}$        | Hold Time, D <sub>IN</sub> After CLK↑                       | $V_{CC}$ = 2.7V               | 450 |     |     | ns    |

| $t_{su\bar{CS}}$ | Setup Time CS↓ Before First CLK↑ ( See Operating Sequence ) | $V_{CC}$ = 2.7V               | 2   |     |     | μs    |

| $t_{suDI}$       | Setup Time, D <sub>IN</sub> Stable Before CLK↑              | $V_{CC}$ = 2.7V               | 600 |     |     | ns    |

| $t_{WHCLK}$      | CLK High Time                                               | $V_{CC}$ = 2.7V               | 1.5 |     |     | μs    |

| $t_{WLCLK}$      | CLK Low Time                                                | $V_{CC}$ = 2.7V               | 1.5 |     |     | μs    |

| $t_{WHCS}$       | CS High Time Between Data Transfer Cycles                   | $f_{CLK}$ = 200kHz            | 25  |     |     | μs    |

| $t_{WLCS}$       | CS Low Time During Data Transfer                            | $f_{CLK}$ = 200kHz            | 70  |     |     | μs    |

# LTC1594L/LTC1598L

## コンバータおよびマルチプレクサの特性 (Note 5)

| PARAMETER                         | CONDITIONS   | LTC1594LCS/LTC1598LCG |     |                            | LTC1594LIS/LTC1598LIG |     |      | UNITS |

|-----------------------------------|--------------|-----------------------|-----|----------------------------|-----------------------|-----|------|-------|

|                                   |              | MIN                   | TYP | MAX                        | MIN                   | TYP | MAX  |       |

| Resolution (No Missing Codes)     |              | ●                     | 12  |                            | 12                    |     |      | Bits  |

| Integral Linearity Error          | (Note 6)     | ●                     |     | ±3                         |                       |     | ±3   | LSB   |

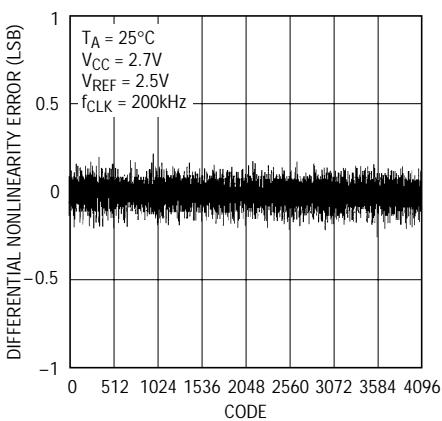

| Differential Linearity Error      |              | ●                     |     | ±3/4                       |                       |     | ±1   | LSB   |

| Offset Error                      |              | ●                     |     | ±3                         |                       |     | ±3   | LSB   |

| Gain Error                        |              | ●                     |     | ±8                         |                       |     | ±8   | LSB   |

| REF Input Range                   | (Notes 7, 8) |                       |     | 1.5V to $V_{CC}$ + 0.05V   |                       |     |      | V     |

| Analog Input Range                | (Notes 7, 8) |                       |     | −0.05V to $V_{CC}$ + 0.05V |                       |     |      | V     |

| MUX Channel Input Leakage Current | Off Channel  | ●                     |     | ±200                       |                       |     | ±200 | nA    |

| MUXOUT Leakage Current            | Off Channel  | ●                     |     | ±200                       |                       |     | ±200 | nA    |

| ADCIN Input Leakage Current       | (Note 9)     | ●                     |     | ±1                         |                       |     | ±1   | µA    |

## ダイナミック精度 (Note 5) $f_{SMPL} = 10.5\text{kHz}$

| SYMBOL    | PARAMETER                                      | CONDITIONS        | MIN | TYP | MAX | UNITS |

|-----------|------------------------------------------------|-------------------|-----|-----|-----|-------|

| S/(N + D) | Signal-to-Noise Plus Distortion Ratio          | 1kHz Input Signal |     | 68  |     | dB    |

| THD       | Total Harmonic Distortion (Up to 5th Harmonic) | 1kHz Input Signal |     | −78 |     | dB    |

| SFDR      | Spurious-Free Dynamic Range                    | 1kHz Input Signal |     | 80  |     | dB    |

|           | Peak Harmonic or Spurious Noise                | 1kHz Input Signal |     | −80 |     | dB    |

## デジタルおよびDC電気的特性 (Note 5)

| SYMBOL       | PARAMETER                  | CONDITIONS                                                                                                                                                                      | MIN    | TYP          | MAX          | UNITS    |

|--------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|--------------|----------|

| $V_{IH}$     | High Level Input Voltage   | $V_{CC} = 3.6\text{V}$                                                                                                                                                          | ●      | 2.0          |              | V        |

| $V_{IL}$     | Low Level Input Voltage    | $V_{CC} = 2.7\text{V}$                                                                                                                                                          | ●      |              | 0.8          | V        |

| $I_{IH}$     | High Level Input Current   | $V_{IN} = V_{CC}$                                                                                                                                                               | ●      |              | 2.5          | µA       |

| $I_{IL}$     | Low Level Input Current    | $V_{IN} = 0\text{V}$                                                                                                                                                            | ●      |              | −2.5         | µA       |

| $V_{OH}$     | High Level Output Voltage  | $V_{CC} = 2.7\text{V}, I_0 = 10\mu\text{A}$<br>$V_{CC} = 2.7\text{V}, I_0 = 360\mu\text{A}$                                                                                     | ●<br>● | 4.0<br>2.4   | 4.64<br>4.62 | V        |

| $V_{OL}$     | Low Level Output Voltage   | $V_{CC} = 2.7\text{V}, I_0 = 400\mu\text{A}$                                                                                                                                    | ●      |              | 0.4          | V        |

| $I_{OZ}$     | Hi-Z Output Leakage        | $\overline{CS} = \text{High}$                                                                                                                                                   | ●      |              | ±3           | µA       |

| $I_{SOURCE}$ | Output Source Current      | $V_{OUT} = 0\text{V}$                                                                                                                                                           |        |              | −10          | mA       |

| $I_{SINK}$   | Output Sink Current        | $V_{OUT} = V_{CC}$                                                                                                                                                              |        |              | 15           | mA       |

| $R_{REF}$    | Reference Input Resistance | $\overline{CS} = V_{IH}$<br>$\overline{CS} = V_{IL}$                                                                                                                            |        |              | 2700<br>60   | MΩ<br>kΩ |

| $I_{REF}$    | Reference Current          | $\overline{CS} = V_{CC}$<br>$t_{CYC} \geq 760\mu\text{s}, f_{CLK} \leq 25\text{kHz}$<br>$t_{CYC} \geq 60\mu\text{s}, f_{CLK} \leq 200\text{kHz}$                                | ●<br>● | 0.001<br>50  | 2.5<br>70    | µA<br>µA |

| $I_{CC}$     | Supply Current             | $\overline{CS} = V_{CC}, CLK = V_{CC}, D_{IN} = V_{CC}$<br>$t_{CYC} \geq 760\mu\text{s}, f_{CLK} \leq 25\text{kHz}$<br>$t_{CYC} \geq 60\mu\text{s}, f_{CLK} \leq 200\text{kHz}$ | ●<br>● | 0.001<br>160 | ±3<br>160    | µA<br>µA |

|              |                            |                                                                                                                                                                                 |        |              | 160          | 320      |

## AC特性 (Note 5)

| SYMBOL          | PARAMETER                                             | CONDITIONS                                                  | MIN | TYP          | MAX  | UNITS          |

|-----------------|-------------------------------------------------------|-------------------------------------------------------------|-----|--------------|------|----------------|

| $t_{SMPL}$      | Analog Input Sample Time                              | See Figure 1 in Applications Information                    | 1.5 |              |      | CLK Cycles     |

| $f_{SMPL(MAX)}$ | Maximum Sampling Frequency                            | See Figure 1 in Applications Information                    | ●   | 10.5         |      | kHz            |

| $t_{CONV}$      | Conversion Time                                       | See Figure 1 in Applications Information                    |     | 12           |      | CLK Cycles     |

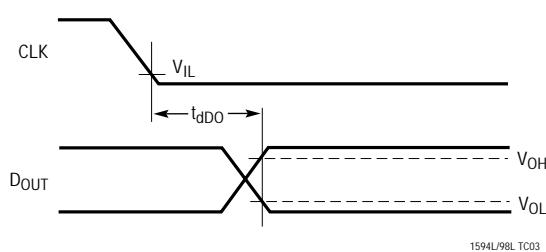

| $t_{dDO}$       | Delay Time, $CLK \downarrow$ to $D_{OUT}$ Data Valid  | See Test Circuits                                           | ●   | 600          | 1500 | ns             |

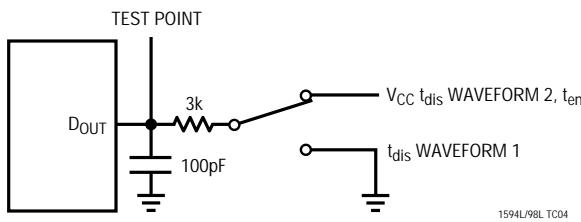

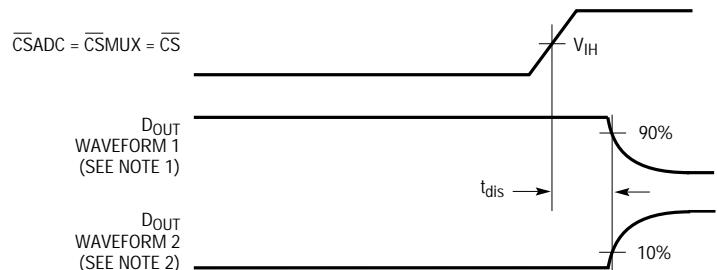

| $t_{dis}$       | Delay Time, $\bar{CS} \uparrow$ to $D_{OUT}$ Hi-Z     | See Test Circuits                                           | ●   | 220          | 600  | ns             |

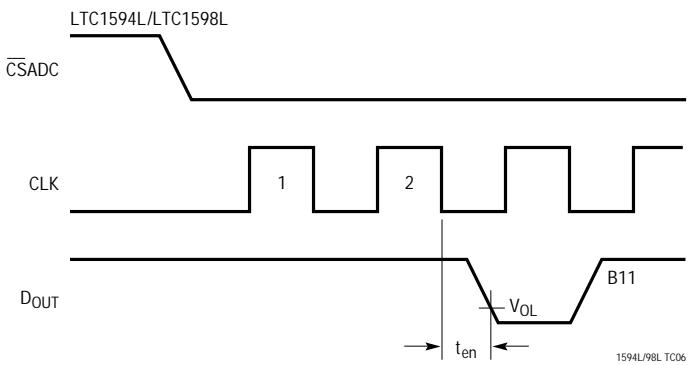

| $t_{en}$        | Delay Time, $CLK \downarrow$ to $D_{OUT}$ Enabled     | See Test Circuits                                           | ●   | 180          | 500  | ns             |

| $t_{hDO}$       | Time Output Data Remains Valid After $CLK \downarrow$ | $C_{LOAD} = 100pF$                                          |     | 520          |      | ns             |

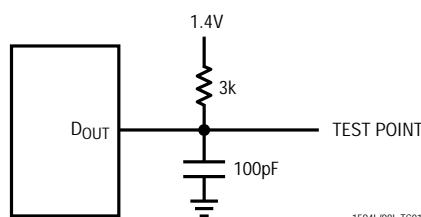

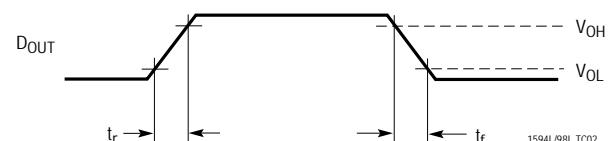

| $t_f$           | $D_{OUT}$ Fall Time                                   | See Test Circuits                                           | ●   | 60           | 180  | ns             |

| $t_r$           | $D_{OUT}$ Rise Time                                   | See Test Circuits                                           | ●   | 80           | 180  | ns             |

| $t_{ON}$        | Enable Turn-On Time                                   | See Figure 1 in Applications Information                    | ●   | 540          | 1200 | ns             |

| $t_{OFF}$       | Enable Turn-Off Time                                  | See Figure 2 in Applications Information                    | ●   | 190          | 500  | ns             |

| $t_{OPEN}$      | Break-Before-Make Interval                            |                                                             | ●   | 125          | 350  | ns             |

| $C_{IN}$        | Input Capacitance                                     | Analog Inputs<br>On-Channel<br>Off-Channel<br>Digital Input |     | 20<br>5<br>5 |      | pF<br>pF<br>pF |

は全動作温度範囲の規格値を意味する。

Note 1 : 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2 : すべての電圧値はGNDを基準にする。

Note 3 : これらのデバイスは3Vで仕様が規定されている。5V仕様のデバイス (LTC1594/LTC1598)については当社にお問い合わせください。

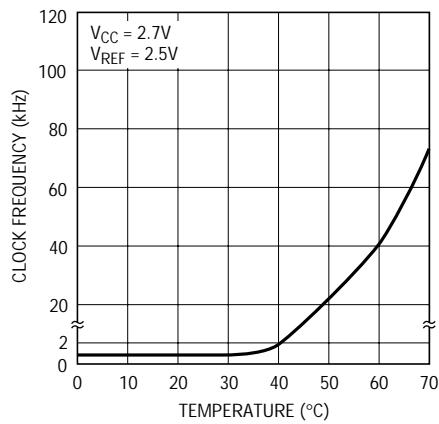

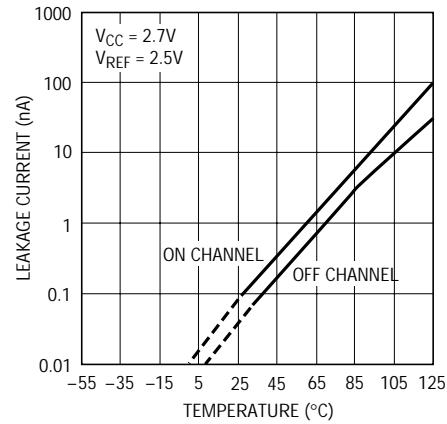

Note 4 : 高温でリーク電流が増加すると、S/Hが低下するため、85 $^{\circ}\text{C}$ では $f_{CLK} \geq 200\text{kHz}$ 、70 $^{\circ}\text{C}$ では $f_{CLK} \geq 75\text{kHz}$ 、25 $^{\circ}\text{C}$ では $f_{CLK} \geq 1\text{kHz}$ が推奨される。

Note 5 : 注記がない限り、 $V_{CC} = 2.7\text{V}$ 、 $V_{REF} = 2.5\text{V}$ 、および $CLK = 200\text{kHz}$ 、CSADCピンとCSMUXピンはテスト中には連結される。

Note 6 : 直線性誤差はA/D伝達曲線の実際のエンド・ポイント間で規定されている。

Note 7 : 各リファレンスとアナログ入力には2個の内蔵ダイオードが接続されている。これらのダイオードはリファレンスまたはアナログ入力電圧がGNDからダイオード1個分低いか、 $V_{CC}$ よりダイオード1個分高いと導通する。このスペックでは、 $2.7V \leq V_{CC} \leq 3.6V$ の場合に、いずれかのダイオードの50mV順バイアスが許容されている。これはリファレンスまたはアナログ入力が電源電圧を50mV以上超えない限り、出力コードが正しいことを意味する。したがって0V~3Vの絶対入力電圧範囲を達成するには、初期許容差、温度変動、および負荷に対して最小2.950Vの電源電圧が必要となる。

Note 8 : 推奨動作条件。

Note 9 : チャネル・リーク電流はチャンネル選択後に測定される。

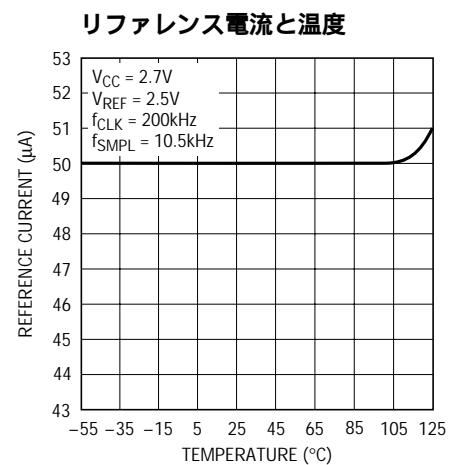

## 標準的性能特性

1594L/98L G01

1594L/98L G02

1594L/98L G03

## 標準的性能特性

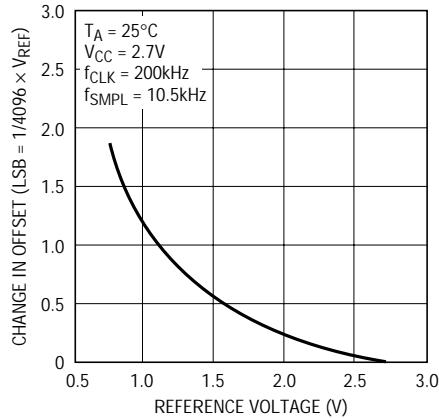

### オフセットの変動とリファレンス電圧

1594L/98L G04

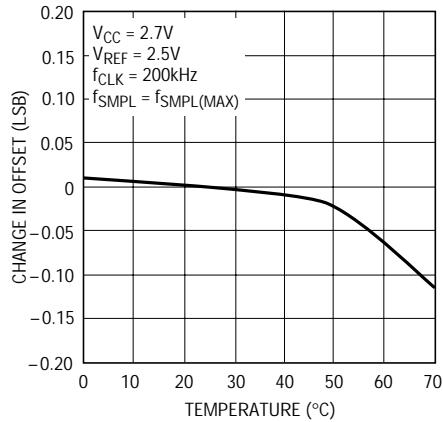

### オフセットの変動と温度

1594L/98L G05

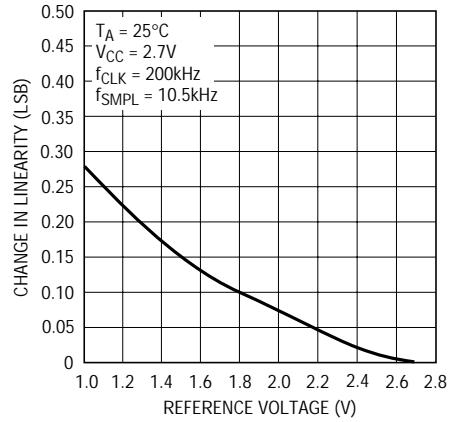

### 直線性の変動とリファレンス電圧

1594L/98L G06

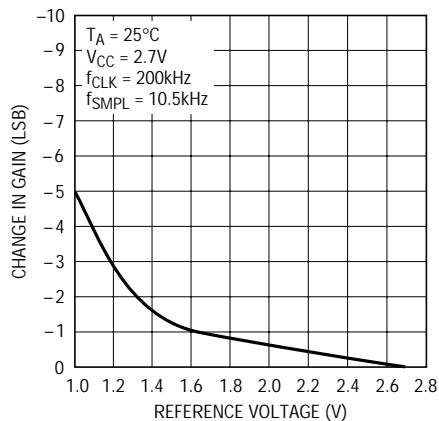

### 利得の変動とリファレンス電圧

1594L/98L G07

### 微分非直線性とコード

1594L/98L G08

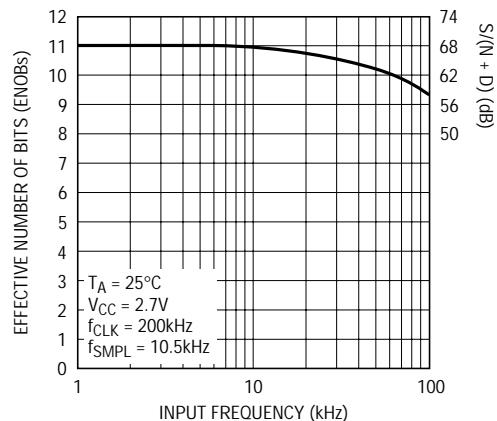

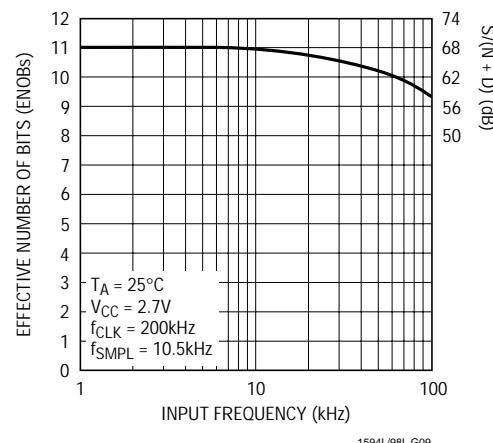

### 有効ビットおよびS/(N+D)と入力周波数

1594L/98L G09

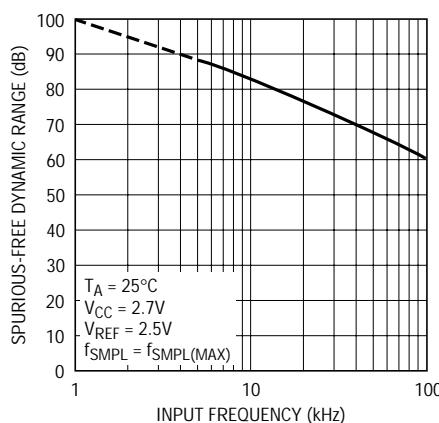

### スピアス・フリー・ダイナミック・レンジと周波数

1594L/98L G10

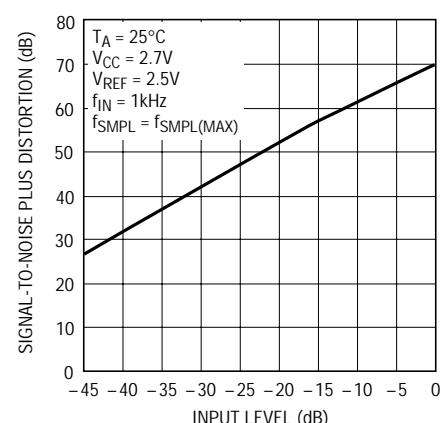

### S/(N+D)と入力レベル

1594L/98L G11

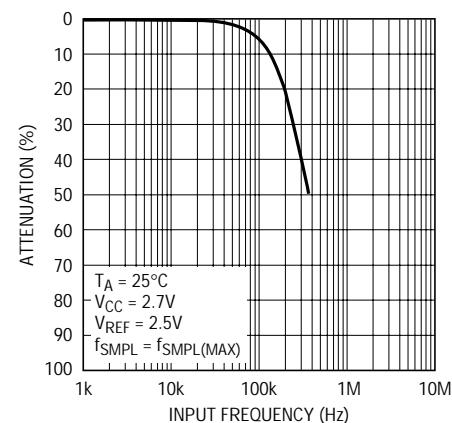

### 減衰と入力周波数

1594L/98L G12

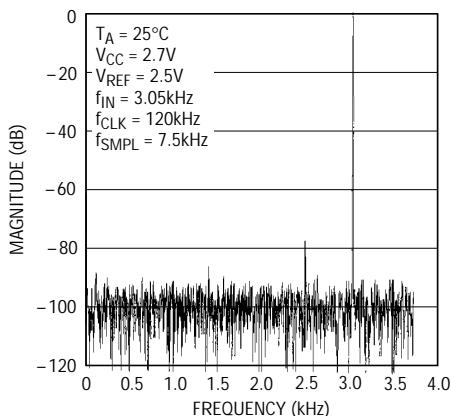

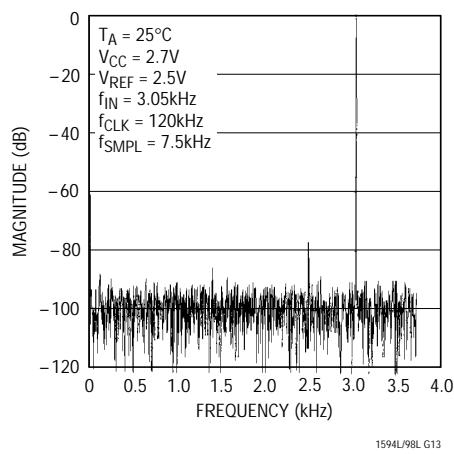

## 標準的性能特性

4096ポイントのFFTプロット

1594L/98L G13

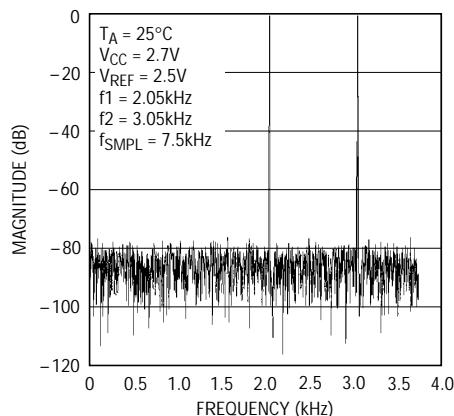

混変調歪み

1594L/98L G14

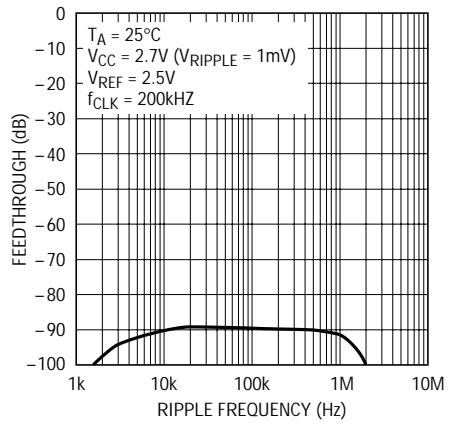

電源フィードスルーと

リップル周波数

1594L/98L G15

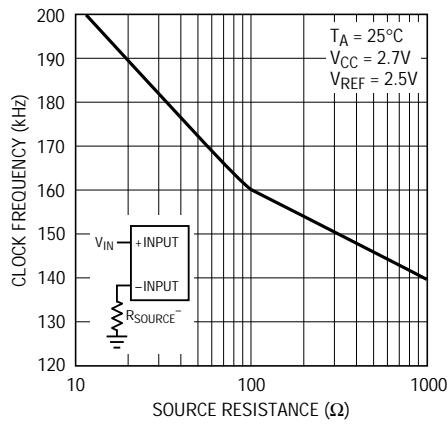

最大クロック周波数と

ソース抵抗

1594L/98L G16

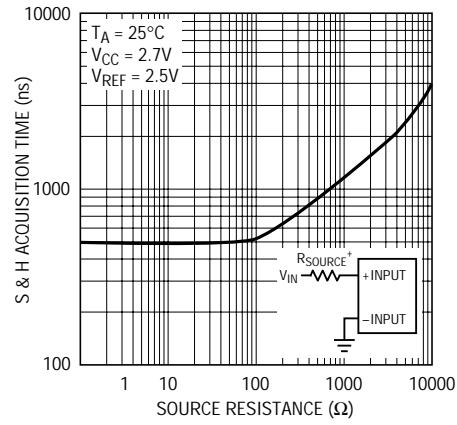

サンプル・ホールド・アクイジョン・

タイムとソース抵抗

1594L/98L G17

6

0.1LSB誤差に対する最小クロック

周波数と温度

1594L/98L G18

入力チャネル・リーク電流

と温度

1594L/98L G19

## ピン機能

### LTC1594L

CH0( ピン1 ): アナログ・マルチブレクサ入力

CH1( ピン2 ): アナログ・マルチブレクサ入力

CH2( ピン3 ): アナログ・マルチブレクサ入力

CH3( ピン4 ): アナログ・マルチブレクサ入力

ADCIN( ピン5 ): ADC入力。この入力はADCの正アナログ入力です。通常動作では、このピンはMUXOUTに接続します。

V<sub>REF</sub>( ピン6 ): リファレンス入力。リファレンス入力でA/Dコンバータの電圧スパンを決定します。

COM( ピン7 ): 負のアナログ入力。この入力はADCの負アナログ入力であり、GNDを基準としてノイズが入ってはなりません。

GND( ピン8 ): アナログ・グランド。GNDはアナログ・グランド・プレーンに直接接続しなければなりません。

CSADC( ピン9 ): ADCチップ・セレクト入力。この入力に“H”レベルがあると、ADCをパワーダウンし、D<sub>OUT</sub>をハイ・インピーダンスにします。この入力に“L”レベルがあると、ADCは選択されたチャネルをサンプリングして、変換を開始します。通常動作では、このピンはCSMUXと並列にドライブします。

### LTC1598L

CH5( ピン1 ): アナログ・マルチブレクサ入力

CH6( ピン2 ): アナログ・マルチブレクサ入力

CH7( ピン3 ): アナログ・マルチブレクサ入力

GND( ピン4 ): アナログ・グランド。GNDはアナログ・グランド・プレーンに直接接続しなければなりません。

CLK( ピン5 ): シフト・クロック。このクロックはシリアル・データ伝送をMUXとADCに同期させます。また、ADCの変換速度も決定します。

CSMUX( ピン6 ): MUXチップ・セレクト入力。この入力に“H”レベルがあると、MUXはチャネル・アドレスを受信することができます。この入力に“L”レベルがあると、選択されたMUXチャネルをイネーブルしてそれをMUXOUTピンに接続して、A/D変換を行うことができます。通常動作では、このピンをCSADCと並列にドライブします。

D<sub>IN</sub>( ピン7 ): デジタル・データ入力。マルチブレクサ・アドレスがこの入力にシフトインされます。

D<sub>OUT</sub>( ピン10 ): デジタル・データ出力。この出力からA/D変換結果がシフト・アウトされます。

V<sub>CD</sub>( ピン11 ): 電源電圧。このピンはA/Dコンバータに電力を供給します。アナログ・グランド・プレーンに直接バイパスしなければなりません。

CLK( ピン12 ): シフト・クロック。このクロックはシリアル・データ伝送をMUXとADCに同期させます。

CSMUX( ピン13 ): MUXチップ・セレクト入力。この入力に“H”レベルがあると、MUXはチャネル・アドレスを受信することができます。この入力に“L”レベルがあると、選択されたMUXチャネルをイネーブルしてそれをMUXOUTピンに接続して、A/D変換を行うことができます。通常動作では、このピンをCSADCと並列にドライブします。

D<sub>IN</sub>( ピン14 ): デジタル・データ入力。マルチブレクサ・アドレスがこの入力にシフトインされます。

MUXOUT( ピン15 ): MUX出力。このピンはマルチブレクサの出力です。通常動作ではADCINに接続します。

V<sub>CD</sub>( ピン16 ): 電源電圧。このピンはピン11に接続しなければなりません。

COM( ピン8 ): 負のアナログ入力。この入力はADCの負アナログ入力であり、GNDを基準としてノイズが入ってはなりません。

GND( ピン9 ): アナログ・グランド。GNDはアナログ・グランド・プレーンに直接接続しなければなりません。

CSADC( ピン10 ): ADCチップ・セレクト入力。この入力に“H”レベルがあると、ADCをパワーダウンし、D<sub>OUT</sub>をハイ・インピーダンスにします。この入力に“L”レベルがあると、ADCは選択されたチャネルをサンプリングして、変換を開始します。通常動作では、このピンはCSMUXと並列にドライブします。

D<sub>OUT</sub>( ピン11 ): デジタル・データ出力。この出力からA/D変換結果がシフト・アウトされます。

NC( ピン12 ): 無接続。

NC( ピン13 ): 無接続。

CLK( ピン14 ): シフト・クロック。この入力はピン5に接続してください。

## ピン機能

$V_{CC}$ ( ピン15 ): 電源電圧。このピンはA/Dコンバータに電源を供給します。アナログ・グランド・プレーンに直接バイパスしなければなりません。

$V_{REF}$ ( ピン16 ): リファレンス入力。リファレンス入力でA/Dコンバータの電圧スパンを決定します。

ADCIN( ピン17 ): ADC入力。この入力はADCの正アナログ入力です。通常動作では、このピンはMUXOUTに接続します。

MUXOUT( ピン18 ): MUX出力。このピンはマルチプレクサの出力です。通常動作ではADCINに接続します。

$V_{CC}$ ( ピン19 ): 電源電圧。このピンはピン15に接続しなければなりません。

CH0( ピン20 ): アナログ・マルチプレクサ入力

CH1( ピン21 ): アナログ・マルチプレクサ入力

CH2( ピン22 ): アナログ・マルチプレクサ入力

CH3( ピン23 ): アナログ・マルチプレクサ入力

CH4( ピン24 ): アナログ・マルチプレクサ入力

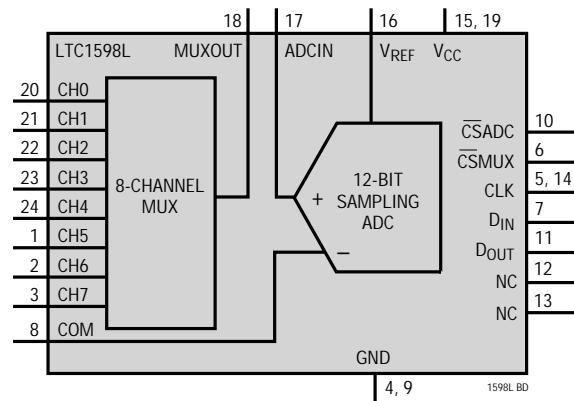

## ブロック図

LTC1594L

LTC1598L

6

## テスト回路

$t_{dDO}$ 、 $t_r$  および  $t_f$  の負荷回路

$D_{OUT}$  の立ち上りおよび立ち下り時間  $t_r$ 、 $t_f$  の電圧波形

## テスト回路

D<sub>OUT</sub>遅延時間、t<sub>dDO</sub>の電圧波形

t<sub>en</sub>の電圧波形

t<sub>dis</sub>およびt<sub>en</sub>の負荷回路

t<sub>dis</sub>の電圧波形

NOTE 1: WAVEFORM 1 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS HIGH UNLESS DISABLED BY THE OUTPUT CONTROL.

NOTE 2: WAVEFORM 2 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS LOW UNLESS DISABLED BY THE OUTPUT CONTROL.

## アプリケーション情報

### 概要

LTC1594L/LTC1598Lはそれぞれ4チャネルおよび8チャネル・マルチブレクサ付きのマイクロパワー、12ビット・サンプリングA/Dコンバータです。これらのADCは、サンプリング速度が10.5kHzのときに標準160 $\mu$ Aの電流を消費します。サンプリング速度が遅くなると、消費電流は直線的に低下します( 電源電流とサンプル・レートを参照 )。ADCは変換を行っていないときには自動的にパワーダウンし、リーク電流しか流しません。LTC1594Lは16ピン細型SOパッケージで供給され、LTC1598Lは24ピンSSOPパッケージで供給されます。両方のデバイスとも2.7V ~ 3.6Vの単一電源で動作します。

LTC1594L/LTC1598Lは、12ビットのスイッチ・キャバシタADC、サンプル・ホールド、シリアル・ポート、および外部リファレンス入力ピンを備えています。さらに、LTC1594Lは4チャネル・マルチブレクサ、LTC1598Lは8チャネル・マルチブレクサを備えています( ブロック図を参照 )。これら

はDCコモン・モード電圧でフロートしている信号を測定でき、1.5Vまでの縮小スパンで動作可能です。スパンを縮小すれば、366 $\mu$ Vの分解能を達成できます。

LTC1594L/LTC1598Lには独立したMUX出力およびADC入力ピンがあり、信号処理を経済的に行う理想的なMUXOUT/ADCINループを形成します。MUXとADCは独立したチップ・セレクトを通して個別に制御することができ、柔軟性が向上しています。

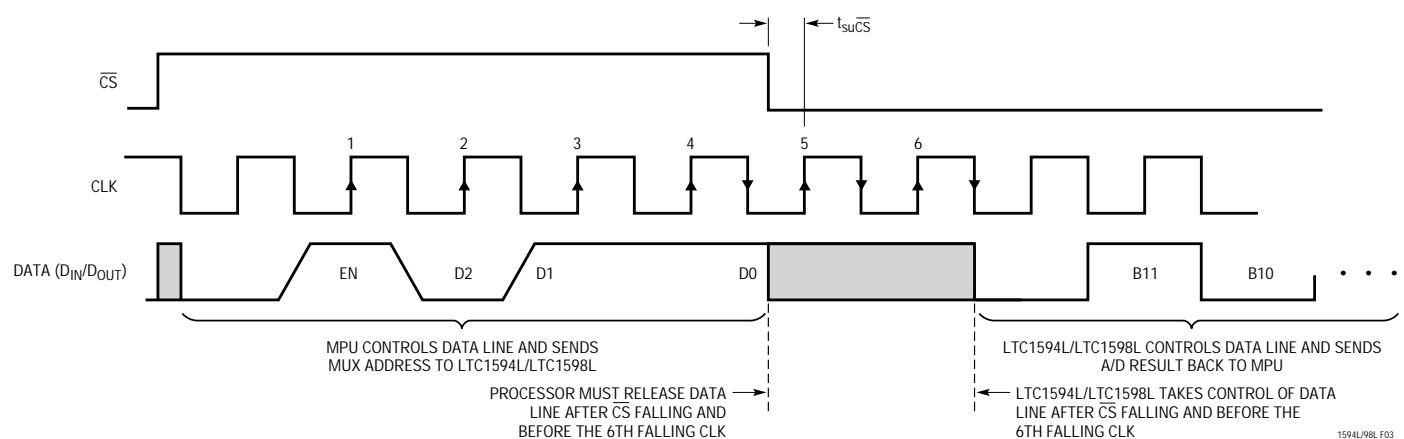

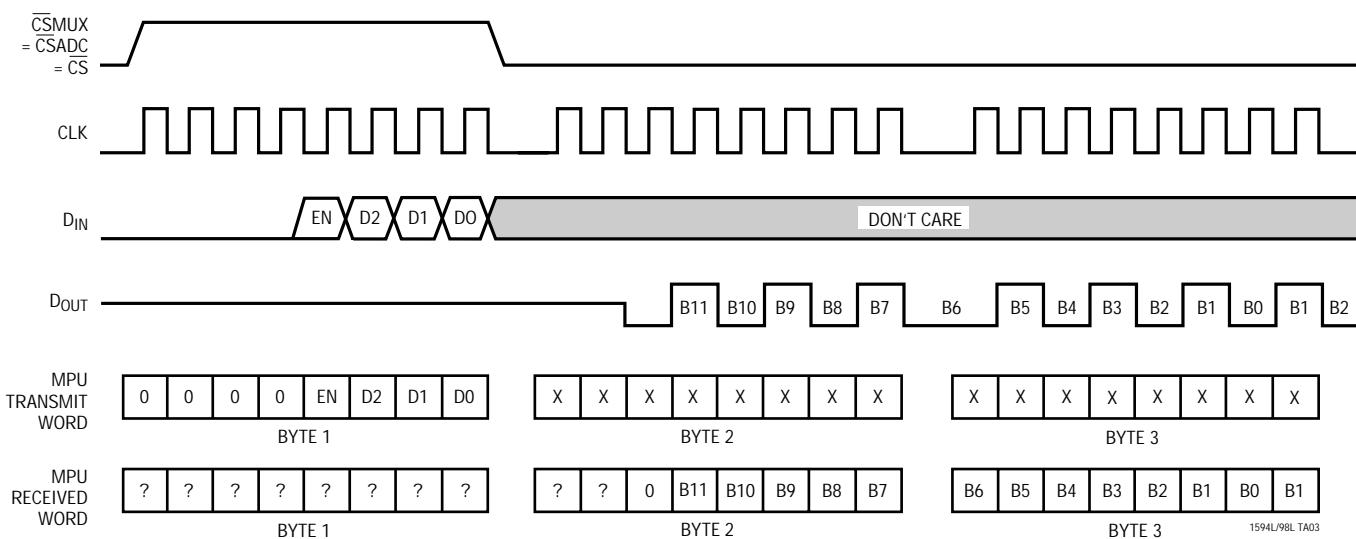

### シリアル・インターフェース

この説明では、注記がない限りCSMUXとCSADCが連結されていると仮定し、それを単にCSと呼ぶものとします。

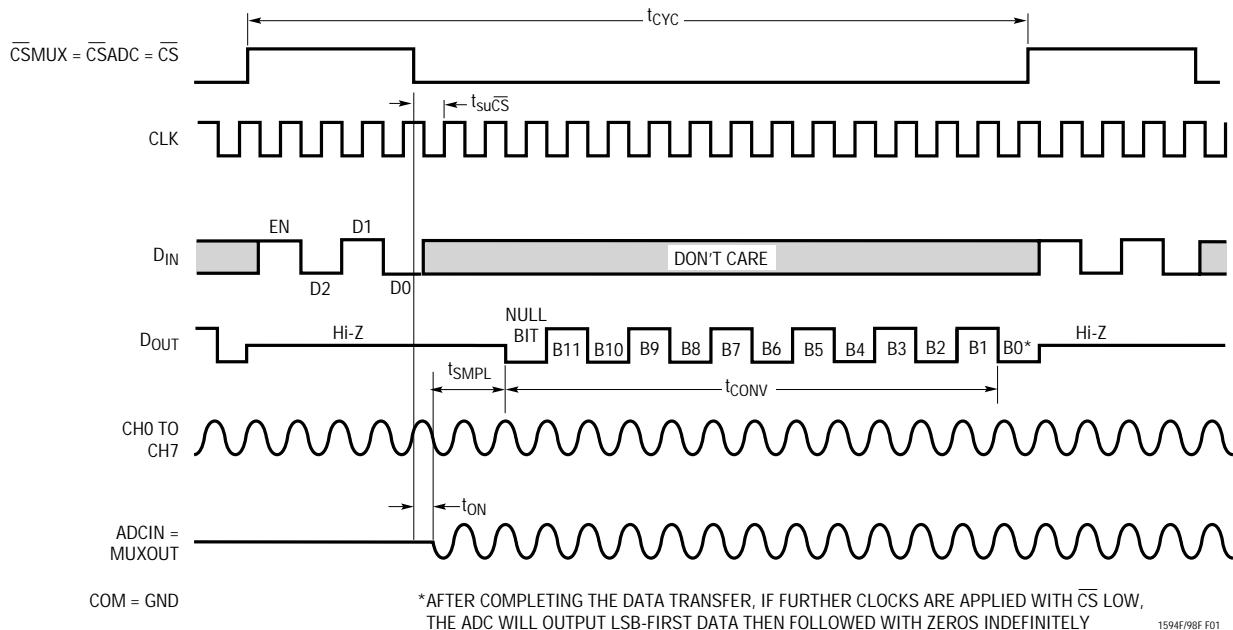

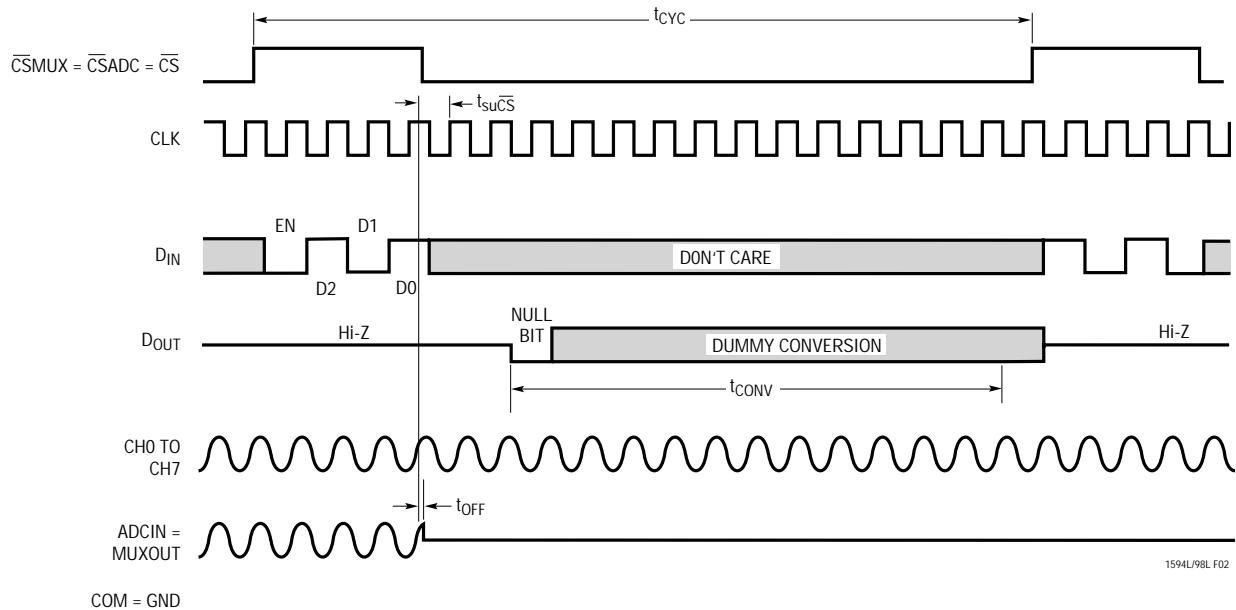

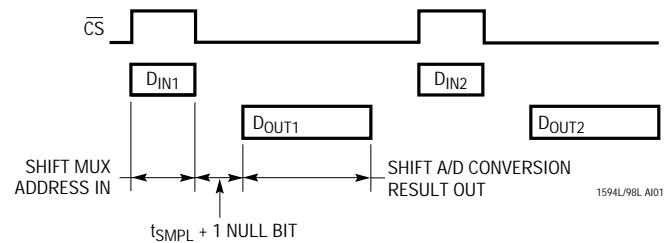

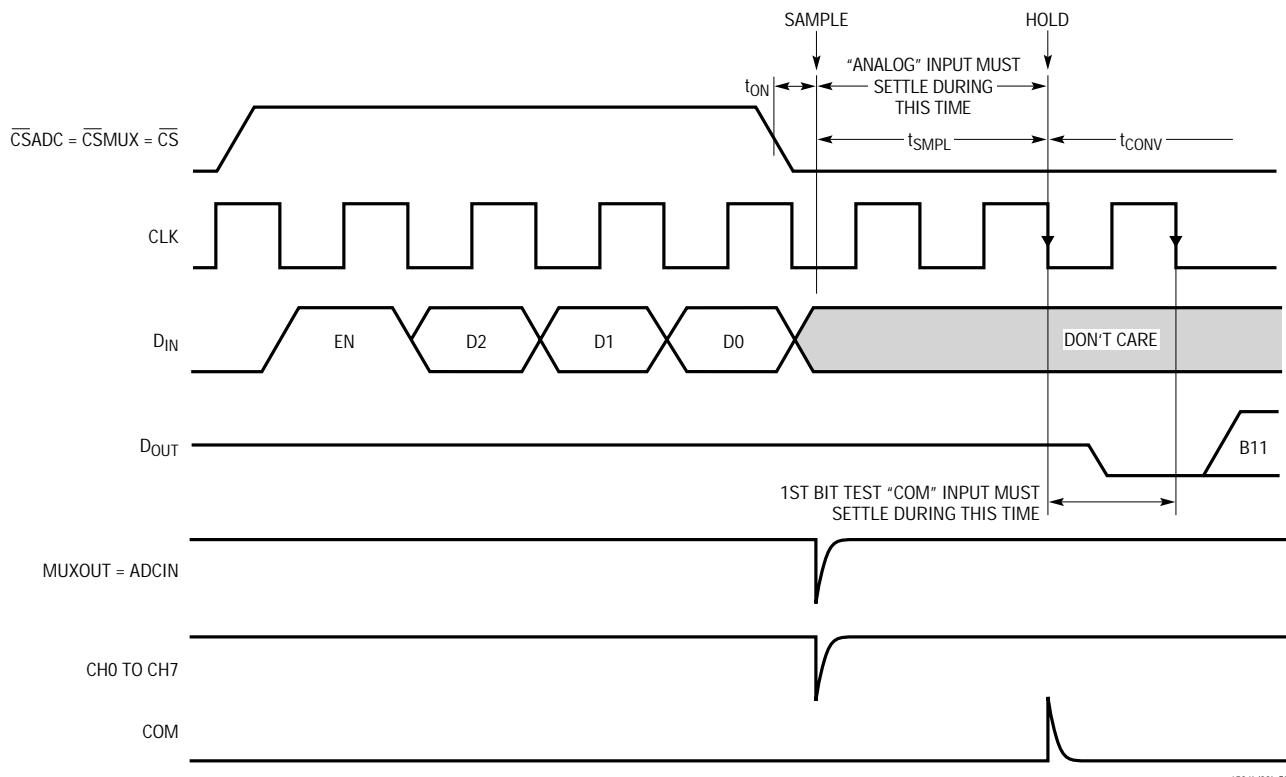

LTC1594L/LTC1598Lは、同期式、半二重、4線インターフェースを介して、マイクロプロセッサおよび他の外部回路と通信を行います( 図1および図2の動作シーケンスを参照 )。

図1. LTC1594L/LTC1598Lの動作シーケンス例 : CH2、GND

## アプリケーション情報

図2. LTC1594L/LTC1598Lの動作シーケンス例：全チャネル・オフ

### データ転送

CLKは、送信および受信の両システムにおいて、各ビットをCLKの立下りエッジで送信し、CLKエッジの立上がりで取り込んでデータ転送を同期化します。

LTC1594L/LTC1598Lは最初に入力データを受信し、次にA/D変換結果を送り返します(半二重)。半二重動作のため、D<sub>IN</sub>とD<sub>OUT</sub>を連結して、CS、CLK、およびDATA(D<sub>IN</sub>/D<sub>OUT</sub>)の3線だけで送信することが可能です。

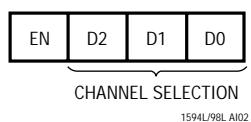

データ転送は立下りのチップ・セレクト(CS)信号によって開始されます。CSが立ち上がった後、D<sub>IN</sub>ピンの入力データはクロックの立上りエッジで4ビット・レジスタにラッチされます。5つ以上の入力ビットを、問題なくD<sub>IN</sub>ピンに送ることができます。CSが立ち下がる前にクロック・インされた最後の4ビットだけが4ビット・レジスタにストアされます。この4ビット入力データ・ワードは、マルチプレクサのチャネルを選択します(入力データ・ワードおよび表1、2を参照)。正しい動作を保証するために、CSはクロックの次の立上りエッジの前に“L”にしなければなりません。

CSを“L”にすると、ブレイク・ビフォア・メイク間隔t<sub>OPEN</sub>を確保するために、t<sub>OFF</sub>の遅延後にすべてのチャ

ネルが同時にオフに切り替わります。t<sub>ON</sub>(t<sub>OFF</sub> + t<sub>OPEN</sub>)の遅延後に、選択されたチャネルがオンに切り替わり、チップのADCは入力信号を獲得して、変換を開始することができます(図1および2を参照)。1ヌル・ビット後、変換の結果がD<sub>OUT</sub>ラインに出力されます。選択されたチャネルは、CSの次の立下りエッジまでオンのままでです。データ交換の終わりにCSを“H”にしなければなりません。これによって、LTC1594L/LTC1598Lをリセットし、次のデータ変換を開始します。

### ブレイク - ビフォア - メイク

LTC1594L/LTC1598Lは、CSが“L”になると、全チャネルを同時にオフにしてから次に選択したチャネルをオンに切り替えるブレイク - ビフォア - メイク間隔を提供します。言い換えると、CSが“L”になるとt<sub>OFF</sub>遅延後に、ブレイク - ビフォア - メイク間隔を確保するために、すべ

## アプリケーション情報

てのチャネルがオフに切り替わります。この間隔の後、選択されたチャネルがオンに切り替わり、信号の伝送が可能になります。選択されたチャネルは、 $\overline{CS}$ の次の立下りエッジまでオンのままで、プロセスは「EN」ビットがロジック“H”的ときに自身を繰り返します。「EN」ビットがロジック“L”的場合、 $\overline{CS}$ が“L”になった $t_{OFF}$ 遅延後に、すべてのチャネルは同時にオフに切り替わり、 $\overline{CS}$ の次の立下りエッジまでオフになったままです。

### 入力データ・ワード

$\overline{CS}$ が“H”的とき、LTC1594L/LTC1598Lはクロックの立上りエッジでデータを $D_{IN}$ 入力にクロック・インし、4ビット・レジスタにストアします。入力データ・ワードは次のとおり定義されています。

### 「EN」ビット

4ビット・レジスタの最初のビットは「EN」ビットです。図1に示すとおり、「EN」ビットがロジック“H”的場合、 $\overline{CS}$ が“L”になってから $t_{ON}$ 遅延後に、選択されたチャネルがイネーブルされます。図2に示すとおり、「EN」ビットがロジック“L”的場合、 $\overline{CS}$ が“L”になってから $t_{OFF}$ 遅延後に、すべてのチャネルがディスエーブルされます。

### マルチプレクサ(MUX)アドレス

「EN」ビットに続く入力ワードの3ビットは、要求された変換に対するMUXのチャネルを選択します。あるチャネル選択に対して、コンバータはCOMピンの電圧を基準にして、選択されたチャネル間の電圧を測定します。表1と2に、LTC1594L/LTC1598Lチャネル選択のための各種ビットの組合せを示します。

表1. LTC1594Lチャネル選択のための論理値表

| CHANNEL STATUS | EN | D2 | D1 | D0 |

|----------------|----|----|----|----|

| All Off        | 0  | X  | X  | X  |

| CH0            | 1  | 0  | 0  | 0  |

| CH1            | 1  | 0  | 0  | 1  |

| CH2            | 1  | 0  | 1  | 0  |

| CH3            | 1  | 0  | 1  | 1  |

表2. LTC1598Lチャネル選択のための論理値表

| CHANNEL STATUS | EN | D2 | D1 | D0 |

|----------------|----|----|----|----|

| All Off        | 0  | X  | X  | X  |

| CH0            | 1  | 0  | 0  | 0  |

| CH1            | 1  | 0  | 0  | 1  |

| CH2            | 1  | 0  | 1  | 0  |

| CH3            | 1  | 0  | 1  | 1  |

| CH4            | 1  | 1  | 0  | 0  |

| CH5            | 1  | 1  | 0  | 1  |

| CH6            | 1  | 1  | 1  | 0  |

| CH7            | 1  | 1  | 1  | 1  |

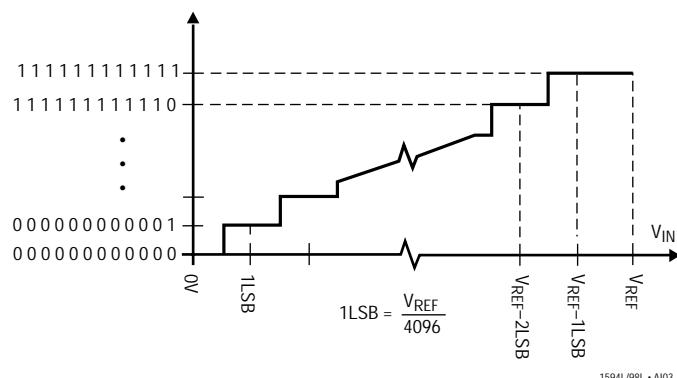

### 伝達曲線

LTC1594L/LTC1598Lはユニポーラ専用に固定されています。この変換タイプの入力スパンとコード割当てを以下の図に示します。

### 伝達曲線

6

### 出力コード

| OUTPUT CODE      | INPUT VOLTAGE    | ( $V_{REF} = 2.500V$ ) |

|------------------|------------------|------------------------|

| 1111111111111111 | $V_{REF} - 1LSB$ | 2.49939V               |

| 1111111111111110 | $V_{REF} - 2LSB$ | 2.49878V               |

| .                | .                | .                      |

| 0000000000000001 | 1LSB             | 0.00061V               |

| 0000000000000000 | 0V               | 0V                     |

1594L/98L • AI04

## アプリケーション情報

### $D_{IN}$ と $D_{OUT}$ を連結した場合の動作

LTC1594L/LTC1598Lは $D_{IN}$ と $D_{OUT}$ を連結した状態で動作できます。これによって、マイクロプロセッサ(MPU)との通信に必要なラインが1本節約されます。データは1本のワイヤで双方向に伝送されます。このデータ・ラインに接続されたプロセッサのピンは、入力または出力として構成できなければなりません。LTC1594L/LTC1598Lは $\overline{CS}$ が立ち下がった後6番目のCLKが立ち下がる前にデータ・ラインを制御し、プロセッサは $\overline{CS}$ が“H”的ときにデータ・ラインを制御します(図3を参照)。したがって、衝突を

回避するために、 $\overline{CS}$ が“L”的ときにプロセッサのポート・ラインを入力に切り替える必要があります。

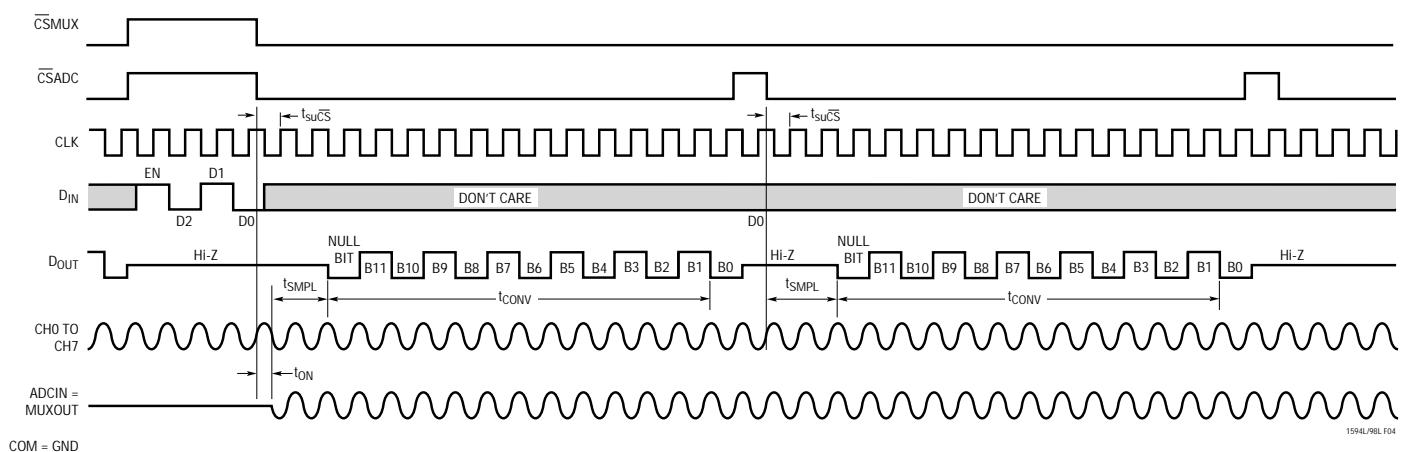

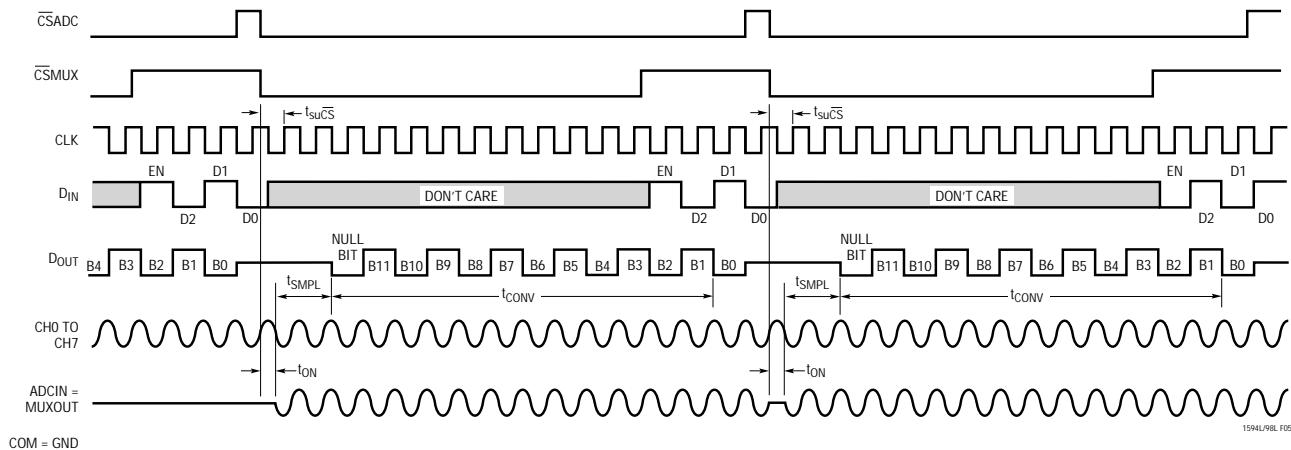

### MUXとADCのための別々のチップ・セレクト

LTC1594L/LTC1598LはMUXとADCを別々に制御するため、独立したチップ・セレクト、 $\overline{CS}_{MUX}$ と $\overline{CS}_{ADC}$ を提供します。この機能は複数の変換に対して特定のチャネルを1回だけ選択する柔軟性を提供するだけでなく(図4を参照)サンプリング・レートを最大20kspsに高めます(図5を参照)。

図3.  $D_{IN}$ と $D_{OUT}$ を連結した場合のLTC1594L/LTC1598Lの動作

図4. 複数の変換に対してチャネルを1回選択

## アプリケーション情報

図5. 別々のチップ・セレクトを使用して、サンプル・レートを最大にする

### MUXOUT/ADCINループによる経済的な信号調整

LTC1594L/LTC1598LのMUXOUTピンとADCINピンは、変換前にプログラム可能な利得アンプ(PGA)やアナログ入力信号の処理を可能にする非常に柔軟な外部ループを形成します。このループは各チャネルごとではなく、1つの回路しか必要ないため、調整を実行する経済的な方法です。

標準的応用例セクションには、MUXOUT/ADCINループを使用してしPGAを形成したり、複数のアナログ入力のアンチエイリア・フィルタリングを行ういくつかの例があります。

### マイクロパワー性能の達成

LTC1594L/LTC1598Lは標準動作電流が160 $\mu$ Aであり、また変換と変換の間の自動シャットダウン機能を備えているため、広い範囲のサンプリング・レートできわめて低い消費電力を実現できます(図6参照)。自動シャットダウン機能を備えているため、サンプリング・レートを遅くすれば、消費電流を減少させることができます。このような低消費電力を達成するには、いくつかの事項を検討する必要があります。

### シャットダウン

LTC1594L/LTC1598Lは自動シャットダウン機能を備えています。CSピンが“L”的ときに電力を消費します。各変換の終わりに、ADCのバイアス回路とコンパレータはパワーダウンし、リファレンス入力はハイ・インピーダンスになり、CLKは動作したままで、LSBファースト・データまたはゼロをクロック・アウトします(図1と図2を参照)。CSピンが“H”的とき、ADCは完全にパワー・ダウンして、CLKを動作状態

RAIL-TO-RAILは日本モトローラ(株)の登録商標です。

図6. 変換と変換の間の自動パワー・シャットダウンにより、サンプル・レートの低下に伴って消費電力も減少

にし入力データ・ワードをMUXにクロック・インします。CS、D\_IN、およびCLKがレール・トゥ・レールで動作していない場合には、入力ロジック・バッファに電流が流れます。これらの電流は標準消費電流よりも大きくなることがあります。消費電流を最小にするには、CS、D\_IN、およびCLKピンをレール・トゥ・レールで振幅させてください。

### D\_OUTの負荷特性

デジタル出力の容量性負荷によって消費電力が増大することがあります。D\_OUTピンに100pFのコンデンサを接続すると、クロック周波数200kHzで電源電流に50 $\mu$ A以上の電流が追加されます。この余分な50 $\mu$ Aほどの電流は、負荷容量の充・放電に使われます。ロジック回路によって高い周波数でドライブされるデジタル・ラインについても同じことがいえます。(C)(V)(f)電流を評価して、問題を最小限に抑えてください。

## アプリケーション情報

### ボード・レイアウトの検討

#### グランドとバイパス

LTC1594L/LTC1598Lは使いやすいデバイスですが、使用時に注意する点がいくつかあります。アナログ・グランド・プレーンおよび一点接地法を用いて使用しなければなりません。GNDピンは直接グランド・プレーンに接続してください。

$V_{CC}$ ピンは10 $\mu$ Fのタンタル・コンデンサをできる限りリードを短くして、グランドにバイパスしてください。電源がクリーンな場合、LTC1594L/LTC1598Lは小さな1 $\mu$ F以下の表面実装型またはセラミックのバイパス・コンデンサを接続しても動作させることができます。すべてのアナログ入力は一点接地を直接基準にしなければなりません。デジタル入力と出力は、リファレンス電圧およびアナログ回路からシールドするか、またはそれから離して配線してください。

### サンプル・ホールド

LTC1594L/LTC1598LはどちらもADCINピンとMUXOUTピンが連結されていると仮定して、選択されたチャネルを通して信号を獲得するビルトイン・サンプル・ホールド(S&H)機能を提供します。これらのデバイスのS&Hは、 $t_{SMPL}$ 期間中にCOM入力を基準にして、選択したチャネルを通して入力信号を収集します(図7参照)。

### シングルエンド入力

LTC1594L/LTC1598Lのサンプル・ホールドにより、高速で変化する信号を変換することができます。図7に示すように、入力電圧は $t_{SMPL}$ 期間中にサンプリングされます。サンプリング間隔は、 $\overline{CS}$ が“L”になり $t_{ON}$ 時間後に開始され、 $\overline{CS}$ が“L”になってから2番目のCLK立下りエッジまで続きます(図7参照)。この立下りCLKエッジで、S&Hはホールド・モードに入り変換が開始されま

図7. LTC1594L/LTC1598LのADCIN入力とCOM入力セトリング・ウィンドウ

## アプリケーション情報

す。「COM」入力の電圧は一定の状態を維持し、変換期間を通じてノイズとリップルがないようにしなければなりません。そうしないと、変換動作が正確に行われないことがあります。変換期間は12 CLKサイクルです。したがって、この期間に「COM」入力の電圧が変化すると、変換誤差が発生する可能性があります。「COM」入力に正弦波電圧が加えられた場合、この誤差は次のようになります。

$$V_{\text{ERROR}(\text{MAX})} = V_{\text{PEAK}} (2\pi f)(\text{「COM」}) 12/f_{\text{CLK}}$$

ここで、(「COM」)は「COM」入力電圧の周波数、 $V_{\text{PEAK}}$ は最大振幅、 $f_{\text{CLK}}$ はCLKの周波数です。ほとんどの場合、 $V_{\text{ERROR}}$ は大きくありません。コンバータが $\text{CLK} = 200\text{kHz}$ で動作しているときに、「COM」入力に60Hz信号を印加して、0.5LSB誤差(305μV)を発生するには、そのピーク値が5.266mVでなければなりません。

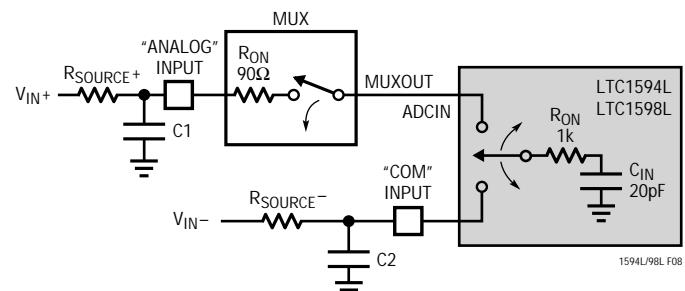

### アナログ入力

電荷再分布A/D変換技術を使用しているため、LTC1594L/LTC1598Lのアナログ入力には、容量性スイッチング入力電流スパイクが発生します。これらの電流スパイクは、瞬時に減衰するため問題は起こりません。しかし、大きなソース抵抗を使用したり、あるいは低速セトリング・オペアンプで入力をドライブする場合は、電流スパイクによって発生する過渡信号が、変換の開始前に完全にセトリングするよう配慮しなければなりません。

### 「アナログ」入力セトリング

LTC1594L/LTC1598Lの入力コンデンサは、 $t_{\text{SMPL}}$ 期間中に選択したチャネル入力に切り替えられ(図7参照)、その時間内に入力信号をサンプリングします。サンプル・フェーズは、変換開始前の最低1 1/2 CLKサイクルです。「アナログ」入力の電圧は $t_{\text{SMPL}}$ 期間内に完全にセトリングしなければなりません。 $R_{\text{SOURCE}}^+$ と $C_1$ を最小にすると、入力セトリング時間が改善されます。大きな「アナログ」入力ソース抵抗を使用しなければならない場合は、より低速なCLK周波数を使用すれば、サンプリング時間を長くすることができます。

### 「COM」入力セトリング

$t_{\text{SMPL}}$ の終わりに、入力コンデンサが「COM」入力に切り替わり変換が始まります(図1および図7参照)。変換中、「アナログ」入力電圧はサンプル・ホールドによって効果的に「ホールド」され、変換結果には影響を与えません。しかし、変換期間の最初のCLKサイクルの間「COM」入力電圧にノイズがなく、完全にセトリングすることが重要です。 $R_{\text{SOURCE}}^-$ および $C_2$ を最小にすれば、セトリング時間が改善されます。大きな「COM」入力ソース抵抗を使用しなければならない場合は、低いCLK周波数を使用すれば、セトリングの許容時間を延長できます。

### 入力オペアンプ

オペアンプでアナログ入力をドライブするときは、オペアンプが許容時間内にセトリングすることが重要です(図7参照)。また、上記で説明したように、低速オペアンプに対応するために、「アナログ」および「COM」入力のサンプリング時間を延長することができます。LT<sup>®</sup>1006およびLT1413単一電源オペアンプを含む大部分のオペアンプは、200kHzの最大クロック・レートで発生する7.5μsの最小セトリング・ウインドウ(「アナログ」入力)でも十分にセトリングするようになっています。

6

### ソース抵抗

LTC1594L/LTC1598Lのアナログ入力は、図8に示すように、20pFのコンデンサ( $C_{\text{IN}}$ )が1kの抵抗( $R_{\text{ON}}$ )および90Ωのチャネル抵抗と直列に接続されているように見えます。 $C_{\text{IN}}$ は各変換サイクル中に、「アナログ」および「COM」入力の間で一度だけ切り替えられます。外部ソース抵抗および容量が大きいと、入力のセトリングは減速されます。アナログ入力が許容時間内に完全にセトリングできるよう、全体のRC時定数を十分短くすることが重要です。

図8. アナログ入力等価回路

## アプリケーション情報

### 入力リーク電流

ソース抵抗が大きくなりすぎると、入力リーク電流によって誤差が発生します。たとえば、600 のソース抵抗に流れる200nAの最大入力リークのスペック( 85 の値 )では、120 $\mu$ Vつまり0.2LSBの電圧降下が発生します。リークが急速に低下するため、この誤差は低温度では非常に小さくなります(「入力チャネル・リーク電流と温度」の標準特性曲線を参照)。

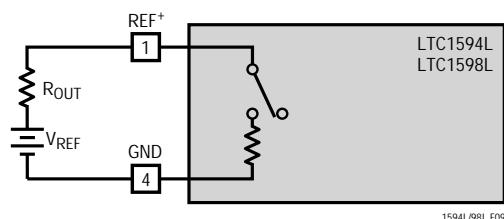

## リファレンス入力

LTC1594L/LTC1598Lのリファレンス入力は、 $CS$ が“L”に立ち下がってから変換の終了までは、実質的に50k抵抗となります。それ以外は、ハイ・インピーダンス・ノードとなっています(図9参照)。リファレンス入力の電圧がA/Dコンバータの電圧スパンを決定するため、リファレンス入力は低 $R_{OUT}$ のリファレンスIC( LTC1004、LTC1019、LTC1021など)または低 $R_{OUT}$ の電圧源でドライブしなければなりません。

図9. リファレンス入力等価回路

### 縮小リファレンス電圧での動作

LTC1594L/LTC1598Lの有効分解能は、コンバータの入力スパンを狭くすれば増大できます。LTC1594L/LTC1598Lは、広範なリファレンス電圧範囲にわたって良好な直線性および利得を示します(「直線性の変動とリファレンス電圧」および「利得の変動とリファレンス電圧」の標準特性曲線を参照)。ただし、コンバータの縮小LSBステップ・サイズおよびその結果要求される高精度特性のため、低い $V_{REF}$ の値で動作させる場合には注意が必要です。低 $V_{REF}$ 値で動作させる場合は、以下の項目について考慮する必要があります。

1. オフセット

2. ノイズ

3. 変換速度( CLK周波数 )

### 縮小V<sub>REF</sub>でのオフセット

ADCが縮小リファレンス電圧で動作しているときには、LTC1594L/LTC1598Lのオフセットの出力コードに対する影響はより大きくなります。 LSBのサイズが縮小されるため、オフセット(通常は固定電圧)はLSBの中で大きな部分を占めるようになります。「オフセットの変動とリファレンス電圧」の標準特性曲線は、 $V_{OS}$ の標準値に対するLSBのオフセットとリファレンス電圧の関係を示しています。たとえば、2.5Vのリファレンス電圧では0.2LSBである122 $\mu$ Vの $V_{OS}$ は、1Vのリファレンス電圧では0.5LSB、0.2Vのリファレンス電圧では2.5LSBになります。このオフセットが許容できなければ、受信側システムによってデジタル的に訂正するか、またはLTC1594L/LTC1598Lの「COM」入力をオフセットして訂正することができます。

### 縮小V<sub>REF</sub>でのノイズ

LTC1594L/LTC1598Lの全入力換算ノイズは、グランド・プレーンの使用、十分なバイパス、適切なレイアウト手法によって、リファレンス入力のノイズを最小限に抑えることによりピーク間で約400 $\mu$ Vまで低減することができます。このノイズは、5Vのリファレンス入力では問題になりませんが、 LSBのサイズが縮小されると LSBでより大きな部分を占めます。

2.5Vのリファレンス電圧による動作では、400μVのノイズはピーク間で0.66 LSBにすぎません。この場合、LTC1594L/LTC1598Lのノイズは出力コードに事実上まったく不確定さを与えません。縮小リファレンス電圧では、ノイズは LSBに対して大きな部分を占め、出力コードに不要なジッタが発生することがあります。たとえば、1.25Vのリファレンスでは、この同じ400μVノイズがピーク間で1.32 LSBになります。これにより、安定した出力コードを達成できる入力電圧範囲が1 LSBだけ縮小されます。リファレンス電圧がさらに1Vに低減されると、400μVノイズは1.65 LSBとなり、安定した出力コードを達成するのは困難になります。この場合は、読み込み値を平均化しなければならないこともあります。

このノイズ・データは非常にノイズの少ないテスト治具でとったものです。システム構成によって誘導されるノイズ ( $V_{CC}$ ,  $V_{REF}$ ,  $V_{IN}$  のノイズまたはリップル) はすべて内部ノイズに追加されます。使用するリファレンス電圧が低くなればなるほど、ノイズのないシステム構成にすることが重要になります。

## アプリケーション情報

### 縮小V<sub>REF</sub>での変換速度

縮小リファレンス電圧では、LSBのステップ・サイズが縮小され、LTC1594L/LTC1598Lの内部コンパレータ・オーバードライブも縮小されます。そのため、小さい値のV<sub>REF</sub>を使用したときは、場合によっては最大CLK周波数を低くしなければなりません。

### ダイナミック特性

LTC1594L/LTC1598Lは卓越した高速サンプリング能力を備えています。ADCの定格スループットにおける周波数応答、歪み、およびノイズをテストするために、FFT(高速フーリエ変換)テスト・テクニックを使用しています。低歪み正弦波を加え、FFTアルゴリズムを用いてデジタル出力を分析することにより、基本成分外の周波数に対するADCのスペクトル成分を調べることができます。図10に標準的なLTC1594L/LTC1598Lのプロットを示します。

図10. LTC1594L/LTC1598Lの非平均化4096点FFTプロット

### SN比

SN + 歪み比S( N + D )は、ADC出力における基本入力周波数のRMS振幅と他のすべての周波数成分のRMS振幅との比率です。出力はDCからサンプリング周波数の1/2の周波数帯域に限定されます。図11に10.5 kHzサンプリング・レートでの標準スペクトル成分を示します。

### 有効ビット数

有効ビット数(ENOB)はADCの分解能の尺度であり、次式のとおりS( N + D )に直接関係します。

$$\text{ENOB} = [\text{S}(N + D) - 1.76]/6.02$$

ここで、S( N + D )はdBで表されます。5V電源の最大サンプリング速度10.5kHzにおいて、LTC1594L/LTC1598Lは入力周波数10kHzで10.7 ENOB以上を維持します。10kHz以上のサンプリング速度では、図11に示すとおり、第2高調波歪みが増加するため、ENOBは徐々に低下します。ノイズ・フロアは低く維持されます。

図11. 有効ビットおよびS( N + D )と入力周波数

### 全高調波歪み

全高調波歪み( THD )は、入力信号のすべての高調波のRMSの合計と基本波との比率です。帯域外高調波は、DCとサンプリング周波数の1/2の周波数帯域に限定されます。THDは次式で表されます。

$$\text{THD} = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + \dots + V_N^2}}{V_1}$$

ここで、V<sub>1</sub>は基本周波数のRMS振幅であり、V<sub>2</sub>からV<sub>N</sub>は第2高調波から第N次高調波の振幅です。ダイナミック精度表の標準THD仕様には第2高調波から第5高調波ま

## アプリケーション情報

で含まれています。入力信号が1kHzの場合、LTC1594L/LTC1598LはV<sub>CC</sub> = 2.7Vで標準78dBのTHDを有しています。

### 混変調歪み

ADC入力信号が2つ以上のスペクトル成分からなるときには、ADC伝達関数の非直線性によって、THDに加えて混変調(IMD)が発生する可能性があります。IMDは別の異なる周波数の正弦波入力が現れたときに、ある正弦波入力に起こる変化です。

ADC入力にf<sub>a</sub>とf<sub>b</sub>の2つの周波数の純粋な正弦波が供給されると、ADC伝達関数の非直線性によって、和および差の周波数mf<sub>a</sub>±nf<sub>b</sub>に歪み成分が形成されます。ただし、mおよびn=0、1、2、3、...です。たとえば、2次IMDの項は(f<sub>a</sub>+f<sub>b</sub>)、(f<sub>a</sub>-f<sub>b</sub>)、3次IMDの項は(2f<sub>a</sub>+f<sub>b</sub>)、(2f<sub>a</sub>-f<sub>b</sub>)、(f<sub>a</sub>+2f<sub>b</sub>)、(f<sub>a</sub>-2f<sub>b</sub>)です。2つの入力正弦波の振幅が等しい場合、2次IMD積の値(dB)は次式で表すことができます。

$$IMD(f_a \pm f_b) = 20 \log \left[ \frac{(f_a \pm f_b) \text{での振幅}}{f_a \text{での振幅}} \right]$$

### 最大高調波またはスプリアス・ノイズ

最大高調波つまり最大スプリアス・ノイズは、入力信号とDCを除く最大スペクトル成分です。この値はフルスケール入力信号のRMS値に対するdBで表されます。

### フルパワーおよび最大直線帯域幅

フルパワー帯域幅はフルスケール入力信号を供給したときに、再生される基本成分の振幅が3dBだけ低下する入力周波数です。

最大直線帯域幅は、ADCの有効ビット定格が11ビットに低下する入力周波数です。この周波数を超えると、サンプリングされた入力信号の歪みが増大します。LTC1594L/LTC1598Lは、入力帯域幅が最大になるように設計されており、ADCは入力信号をコンバータのナイキスト周波数より高い周波数でアンダサンプルすることができます。

---

## 標準的応用例

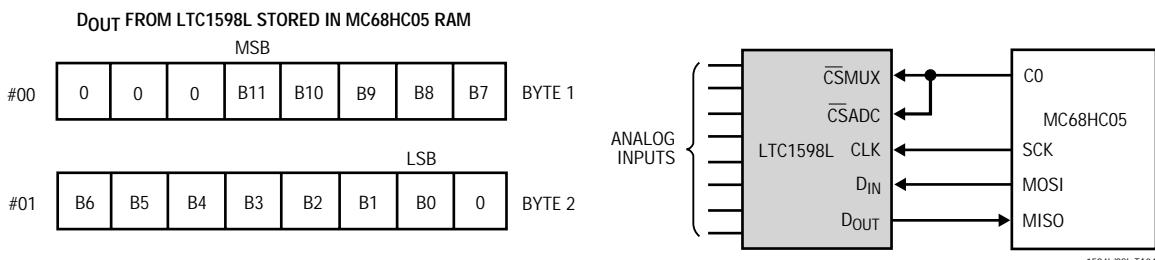

### マイクロプロセッサ・インターフェース

LTC1594L/LTC1598Lは、MICROWIRE、SPI、およびQSPIなど、ほとんどのポピュラーなマイクロプロセッサ(MPU)の同期シリアル・フォーマットに直接(外部ハードウェアなしで)インターフェースすることができます。専用のシリアル・ポートのないMPUを使用する場合、MPUの3つのパラレル・ポート・ラインをプログラミングして、LTC1594L/LTC1598Lへのシリアル・リンクを形成することができます。ここでは、シリアル・インターフェースの例を1つ紹介します。

### モトローラSP(MC68HC05)

専用シリアル・ポート付きMPUの例としてMC68HC05を選択しました。このMPUは、MSBファーストおよび8ビット単位でデータを転送します。データ・レジスタにD<sub>IN</sub>ワードが転送されると、SPIプロセスを開始します。3回の8ビット転送で、A/Dの結果がMPUに読み込まれます。2回目の8ビット転送でA/D変換結果のB11からB7までがプロセッサにクロック・インされます。3回目の8ビット転送では残りのビットB6からB0までがMPUにクロック・インされます。第2バイトと1F<sub>HEX</sub>の論理積をとることによって、最上位3ビットがクリアされ、第3バイトとFE<sub>HEX</sub>の論理積をとることによって、最下位3ビットがクリアされます。データを右に1ビットだけシフトすると、ワードは右詰になります。

## 標準的応用例

| MC68HC05 CODE     |                                                                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| LDA #\$52         | Configuration data for serial peripheral control register (Interrupts disabled, output enabled, master, Norm = 0, Ph = 0, Clk/16) |

| STA \$0A          | Load configuration data into location \$0A (SPCR)                                                                                 |

| LDA #\$FF         | Configuration data for I/O ports (all bits are set as outputs)                                                                    |

| STA \$04          | Load configuration data into Port A DDR (\$04)                                                                                    |

| STA \$05          | Load configuration data into Port B DDR (\$05)                                                                                    |

| STA \$06          | Load configuration data into Port C DDR (\$06)                                                                                    |

| LDA #\$08         | Put D <sub>IN</sub> word for LTC1598L into Accumulator (CH0 with respect to GND)                                                  |

| STA \$50          | Load D <sub>IN</sub> word into memory location \$50                                                                               |

| START BSET 0,\$02 | Bit 0 Port C (\$02) goes high (CS goes high)                                                                                      |

| LDA \$50          | Load D <sub>IN</sub> word at \$50 into Accumulator                                                                                |

| STA \$0C          | Load D <sub>IN</sub> word into SPI data register (\$0C) and start clocking data                                                   |

| LOOP1 TST \$0B    | Test status of SPIF bit in SPI status register (\$0B)                                                                             |

| BPL LOOP1         | Loop if not done with transfer to previous instruction                                                                            |

| BCLR 0,\$02       | Bit 0 Port C (\$02) goes low (CS goes low)                                                                                        |

| LDA \$0C          | Load contents of SPI data register into Accumulator                                                                               |

| STA \$0C          | Start next SPI cycle                                                                                                              |

| LOOP2 TST \$0B    | Test status of SPIF                                                                                                               |

| BPL LOOP2         | Loop if not done                                                                                                                  |

| LDA \$0C          | Load contents of SPI data register into Accumulator                                                                               |

| STA \$0C          | Start next SPI cycle                                                                                                              |

| AND #\$1F         | Clear 3 MSBs of first D <sub>OUT</sub> word                                                                                       |

| STA \$00          | Load Port A (\$00) with MSBs                                                                                                      |

| LOOP3 TST \$0B    | Test status of SPIF                                                                                                               |

| BPL LOOP3         | Loop if not done                                                                                                                  |

| LDA \$0C          | Load contents of SPI data register into Accumulator                                                                               |

| AND #\$FE         | Clear LSB of second D <sub>OUT</sub> word                                                                                         |

| STA \$01          | Load Port B (\$01) with LSBs                                                                                                      |

| JMP START         | Go back to start and repeat program                                                                                               |

## LTC1598LとMC68HC05の間のデータ交換

## モトローラMC68HC05へのハードウェアおよびソフトウェア・インターフェース

## 標準的応用例

多重チャネルA/Dで1つのアンチエイリア・フィルタを使用

この回路は、LTC1598Lの独立したアナログ・マルチブレクサで12ビット・データ収集システムの設計をどのように単純化できるかを示します。8チャネルすべてが、単一電源動作に設計された1つの1kHz、4次Sallen-Keyアンチエイリアシング・フィルタに多重化されます。LTC1598Lのデータ・コンバータはグランドから正電源までの入力を受け入れるため、ダイナミック・レンジを最大にするために、フィルタにはレール・トゥ・レール・オペアンプが選択されました。LT1368デュアル・レール・トゥ・レール・オペアンプは、0.1 $\mu$ Fの負荷コンデンサ(C1とC2)で動作するように設計されています。これらのコンデンサは、アンプに周波数補償を提供し、アンプの出力インピーダンスを低減して、高周波数での電源変動除去を改善します。フィルタが原因で

生じるオフセットとバイアス電流による誤差は1 LSB以下です。フィルタのノイズと歪みは、100Hz, 2V<sub>P-P</sub>オフセット・サイン入力に対して -72dB以下です。

MUX誤差とA/D誤差の合計誤差は、±3 LSB(最大)の積分非直線性誤差と±3/4LSB(最大)の微分非直線性誤差になります。標準のS(N+歪み)比は68dBで、全高調波歪み -78dB程度です。LTC1598Lは、MICROWIRE、SPI、およびQSPIと互換性のある4線シリアル・インターフェースを通してプログラムされます。最大シリアル・クロック速度は200kHzで、10.5kHzのサンプリング・レートに相当します。

回路全体は単一3V電源から約600 $\mu$ Aを消費します。

RAIL-TO-RAILは日本モトローラ(株)の登録商標です。

A/D変換の前にアナログ信号をフィルタするために、LTC1598Lのアドバンテージ、MUXOUT/ADCINのピンを利用する簡単なデータ収集システム

## 標準的应用例

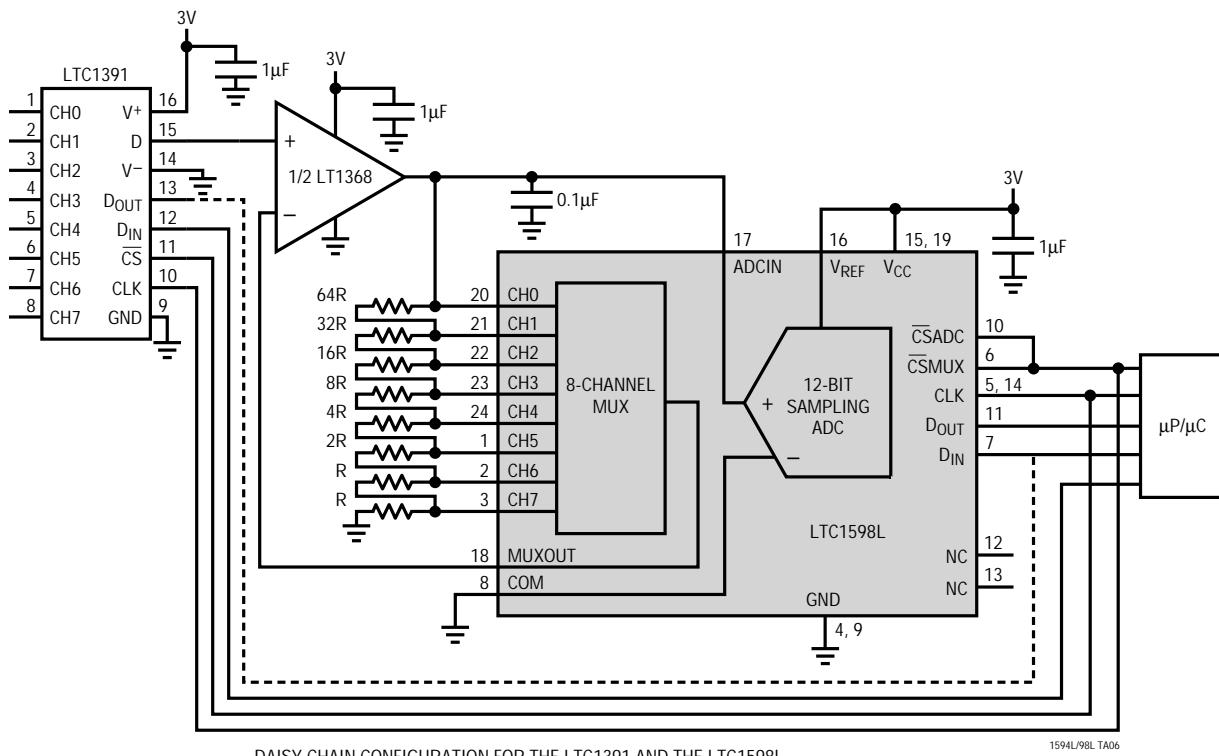

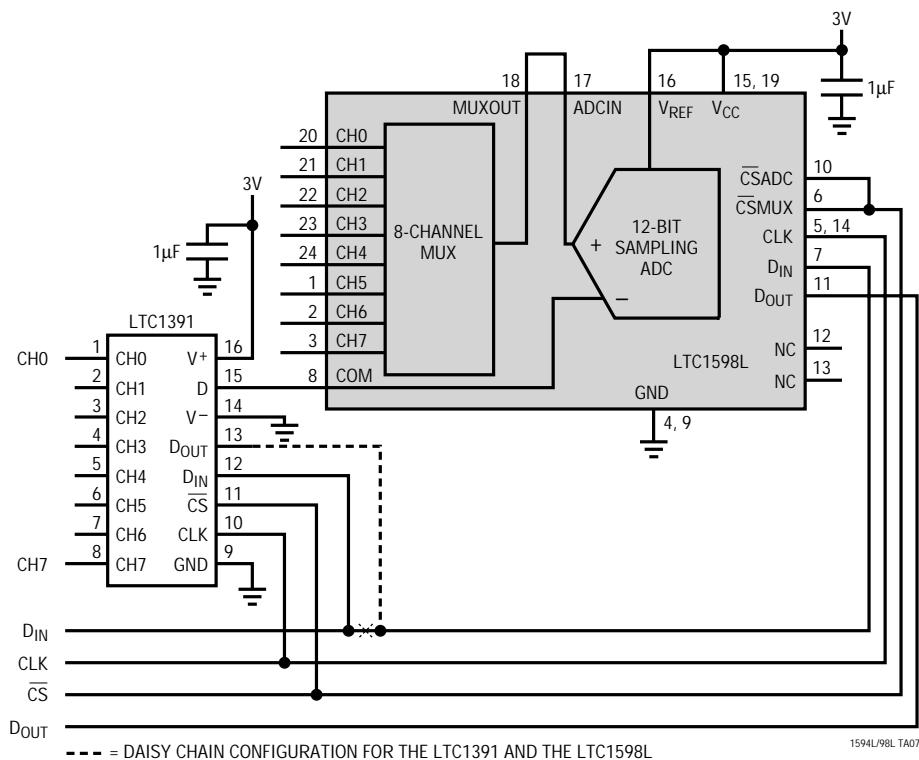

### MUXOUT/ADCINループをPGAとして使用

この図はLTC1598LのMUXOUT/ADCINピンとLT1368を使用して、8つの非反転利得を持つ單一チャネルPGAを構築する様子を示します。LTC1391と組み合わせれば、システムは8チャネルおよび各チャネルごとに8つの利得を持つように拡張できます。LTC1594Lを使用すれば、PGAは4つの利得に低減されます。LT1368の出力はADCINと抵抗ラダーをドライブします。選択したMUXチャネルより上の抵抗で、LT1368のための帰還を形成します。このアンプの利得は $R_{S1}/R_{S2} + 1$ です。 $R_{S1}$ は選択したMUXチャネルより上の抵抗を合計したもので、

$R_{S2}$ は選択したMUXチャネルより下の抵抗を合計したものです。CH0を選択した場合、 $R_{S1}$ が0であるので利得は1です。表1は各MUXチャネルの利得を示します。LT1368デュアル・レール・トゥ・レール・オペアンプは、 $0.1\mu F$ の負荷コンデンサで動作するように設計されています。これらのコンデンサは、アンプに周波数補償を提供し、アンプの出力インピーダンス低減して、高周波数での電源変動除去を改善します。LT1368の $I_B$ は低いので、選択したチャネルの $R_{ON}$ は上記の式で与えられたループ利得に影響を及ぼしません。

LTC1598LのMUXOUT/ADCINピンを使用したPGAの構築

LTC1391 MUXにより、8つの入力チャネルのデジタル化が可能

## LTC1594L/LTC1598L

## 標準的应用例

LTC1598LとLTC1391を8チャネル差動12ビットADCシステムとして使用

## 関連製品

| Part Number       | Description                           | Comments                                                 |

|-------------------|---------------------------------------|----------------------------------------------------------|

| LTC1096/LTC1098   | 8-Pin SO, Micropower 8-Bit ADCs       | Low Power, Small Size, Low Cost                          |

| LTC1096L/LTC1098L | 8-Pin SO, 2.65V Micropower 8-Bit ADCs | Low Power, Small Size, Low Cost                          |

| LTC1196/LTC1198   | 8-Pin SO, 1Msps 8-Bit ADCs            | Low Power, Small Size, Low Cost                          |

| LTC1282           | 3V High Speed Parallel 12-Bit ADC     | 140ksps, Complete with $V_{REF}$ , CLK, Sample-and-Hold  |

| LTC1285/LTC1288   | 8-Pin SO, 3V, Micropower ADCs         | 1- or 2-Channel, Auto Shutdown                           |

| LTC1286/LTC1298   | 8-Pin SO, 5V, Micropower ADCs         | 1- or 2-Channel, Auto Shutdown                           |

| LTC1289           | Multiplexed 3V, 1A, 12-Bit ADC        | 8-Channel 12-Bit Serial I/O                              |

| LTC1296           | Multiplexed 12-Bit ADC                | 8-Channel 12-Bit Serial I/O                              |

| LTC1415           | 5V High Speed Parallel 12-Bit ADC     | 1.25Msps, Complete with $V_{REF}$ , CLK, Sample-and-Hold |

| LTC1594           | 4-Channel, 5V Micropower 12-Bit ADC   | Low Power, Small Size, Low Cost                          |

| LTC1598           | 8-Channel, 5V Micropower 12-Bit ADC   | Low Power, Small Size, Low Cost                          |