## 特長

- DNLおよびINL(全温度範囲):  $\pm 0.5$ LSB最大

- 利得誤差:  $\pm 1$ LSB最大

- 低消費電流:  $10\mu A$ 最大

- 4象限乗算

- パワーオン・リセット

- 非同期クリア入力

- ディジーチェイン3線式シリアル・インターフェース

- 16ピン細型SOおよびPDIPパッケージ

## アプリケーション

- プロセス制御/産業オートメーション

- ソフトウェア制御による利得調整

- デジタル制御のフィルタ/電源

- 自動試験装置

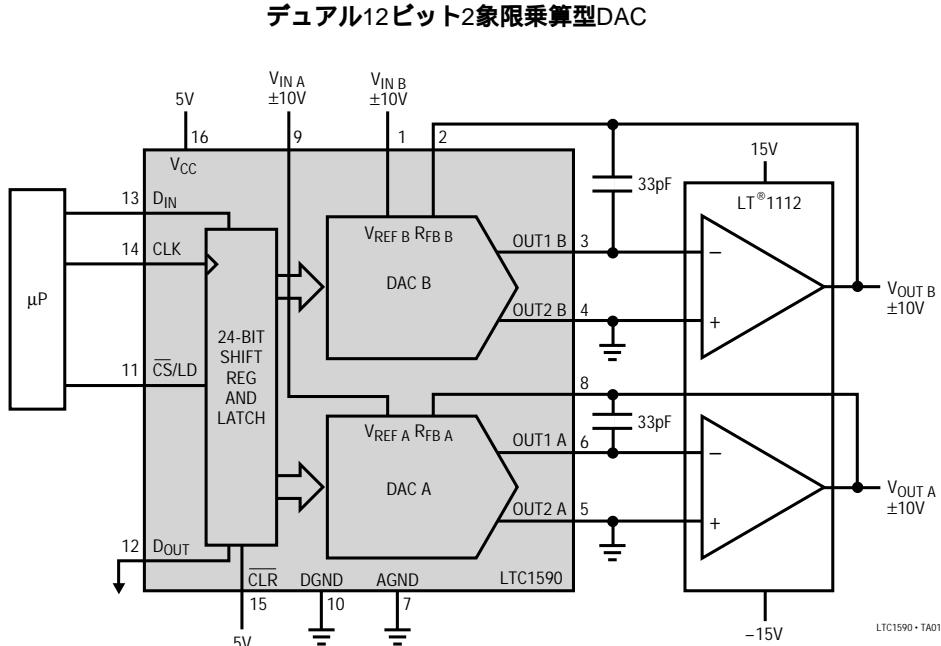

## 標準的応用例

## 概要

LTC<sup>®</sup>1590は、デュアル、シリアル入力の12ビット乗算型デジタル - アナログ・コンバータ(DAC)です。2つの電流出力乗算型CMOS DACとディジーチェイン出力付きの簡易SPI互換シリアル・インターフェースを備えています。非同期CLRピンが両方のDACをゼロ・スケールに設定します。

優れた精度、安定性、および多様性を、デュアル12ビット乗算型DACでは最も小型のパッケージで実現しています。

これらのデバイスは、16ピンPDIPおよび細型SOパッケージで供給され、コマーシャルおよびインダストリアル温度範囲で仕様が規定されています。

**△**、LTC、LTはリニアテクノロジー社の登録商標です。

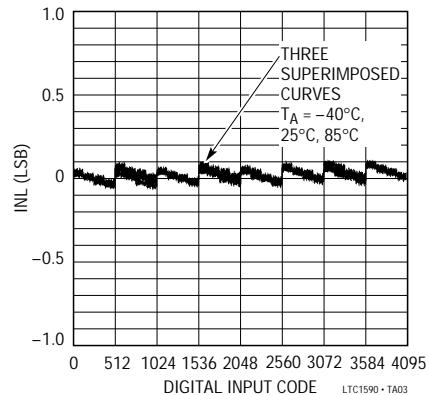

全温度範囲での

積分非直線性、DAC A

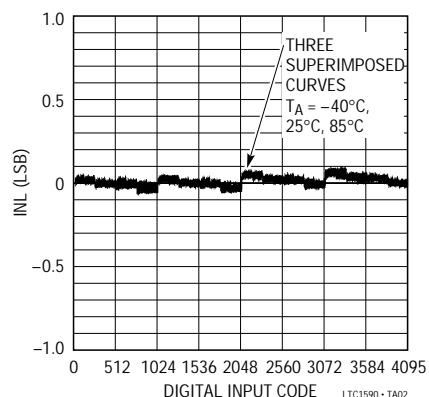

全温度範囲での

積分非直線性、DAC B

## 絶対最大定格

|                                              |                                 |

|----------------------------------------------|---------------------------------|

| AGNDに対するV <sub>CC</sub>                      | - 0.5V ~ 7V                     |

| DGNDに対するV <sub>CC</sub>                      | - 0.5V ~ 7V                     |

| DGNDに対するAGND                                 | V <sub>CC</sub> + 0.5V          |

| AGNDに対するDGND                                 | V <sub>CC</sub> + 0.5V          |

| AGNDに対するV <sub>REF</sub>                     | ± 25V                           |

| AGNDに対するR <sub>FB</sub>                      | ± 25V                           |

| DGNDに対するデジタル入力                               | - 0.5V ~ V <sub>CC</sub> + 0.5V |

| AGNDに対するV <sub>OUT1</sub> 、V <sub>OUT2</sub> | - 0.5V ~ V <sub>CC</sub> + 0.5V |

| 最大接合部温度                                      | 150                             |

| 動作温度範囲                                       |                                 |

| LTC1590C                                     | 0 ~ 70                          |

| LTC1590I                                     | - 40 ~ 85                       |

| 保存温度範囲                                       | - 65 ~ 150                      |

| リード温度(半田付け、10秒)                              | 300                             |

## パッケージ/発注情報

| TOP VIEW                                                 | ORDER PART NUMBER    |           |

|----------------------------------------------------------|----------------------|-----------|

|                                                          | 16 V <sub>CC</sub>   | LTC1590CN |

| 1 V <sub>REF</sub> B                                     | 15 CLR               | LTC1590CS |

| 2 R <sub>FB</sub> B                                      | 14 CLK               | LTC1590IN |

| 3 OUT1 B                                                 | 13 D <sub>IN</sub>   | LTC1590IS |

| 4 OUT2 B                                                 | 12 D <sub>OUT</sub>  |           |

| 5 OUT2 A                                                 | 11 CS/LD             |           |

| 6 OUT1 A                                                 | 10 DGND              |           |

| 7 AGND                                                   | 9 V <sub>REF</sub> A |           |

| 8 R <sub>FB</sub> A                                      |                      |           |

| N PACKAGE                                                | S PACKAGE            |           |

| 16-LEAD PDIP                                             | 16-LEAD PLASTIC SO   |           |

| T <sub>JMAX</sub> = 150°C, θ <sub>JA</sub> = 100°C/W (N) |                      |           |

| T <sub>JMAX</sub> = 150°C, θ <sub>JA</sub> = 150°C/W (S) |                      |           |

ミリタリ・グレードに関してはお問い合わせください。

## 電気的特性

注記がない限り、V<sub>CC</sub> = 4.5V ~ 5.5V、V<sub>REF</sub> = 10V、V<sub>OUT1</sub> = V<sub>OUT2</sub> = AGND = DGND = 0V、T<sub>A</sub> = T<sub>MIN</sub> ~ T<sub>MAX</sub>

| SYMBOL                         | PARAMETER                                                     | CONDITIONS                                                              | MIN | TYP | MAX            | UNITS      |        |

|--------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|-----|-----|----------------|------------|--------|

| <b>Accuracy</b>                |                                                               |                                                                         |     |     |                |            |        |

|                                | Resolution                                                    |                                                                         | ●   | 12  |                | Bits       |        |

| INL                            | Integral Nonlinearity                                         | (Note 1)                                                                | ●   |     | ±0.5           | LSB        |        |

| DNL                            | Differential Nonlinearity                                     | Guaranteed Monotonic, T <sub>MIN</sub> to T <sub>MAX</sub>              | ●   |     | ±0.5           | LSB        |        |

| GE                             | Gain Error                                                    | (Note 2), T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | ●   |     | ±1<br>±2       | LSB        |        |

|                                | Gain Temperature Coefficient                                  | (Note 3) ΔGain/ΔTemperature                                             | ●   | 1   | 5              | ppm/°C     |        |

| I <sub>LEAKAGE</sub>           | OUT1 A, OUT1 B Leakage Current                                | (Note 4), T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | ●   |     | ±5<br>±25      | nA<br>nA   |        |

|                                | Zero-Scale Error                                              | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>           | ●   |     | ±0.03<br>±0.15 | LSB<br>LSB |        |

| PSRR                           | Power Supply Rejection                                        | V <sub>CC</sub> = 5V ±10%                                               | ●   |     | ±0.0001        | ±0.002     | %/%    |

| <b>Reference Input</b>         |                                                               |                                                                         |     |     |                |            |        |

| R <sub>REF</sub>               | V <sub>REF</sub> Input Resistance                             |                                                                         | ●   | 8   | 11             | 15         | kΩ     |

|                                | V <sub>REF</sub> A, V <sub>REF</sub> B Input Resistance Match |                                                                         | ●   |     | 3              |            | %      |

| <b>AC Performance (Note 3)</b> |                                                               |                                                                         |     |     |                |            |        |

|                                | Digital-to-Analog Glitch Impulse                              | (Notes 5, 6)                                                            |     |     | 1              |            | nV-s   |

|                                | Multiplying Feedthrough Error                                 | (Note 11)                                                               |     |     | -89            | -80        | dB     |

|                                | Output Current Settling Time                                  | (Note 5) To 0.01% for Full-Scale Change                                 |     |     | 0.3            | 0.8        | μs     |

|                                | Channel-to-Channel Isolation                                  | (Note 7)                                                                |     |     |                | -90        | dB     |

|                                | Digital Crosstalk                                             | (Notes 5, 8)                                                            |     |     | 1              |            | nV-s   |

|                                | Output Noise Voltage Density                                  | (Note 9)                                                                |     |     | 13             |            | nV/√Hz |

| THD                            | Total Harmonic Distortion                                     | (Note 10)                                                               |     |     | -108           | -92        | dB     |

|                                | Multiplying Bandwidth                                         | (Note 12)                                                               |     |     | 1              |            | MHz    |

## 電気的特性

注記がない限り、 $V_{CC} = 4.5V \sim 5.5V$ 、 $V_{REF} = 10V$ 、 $V_{OUT1} = V_{OUT2} = AGND = DGND = 0V$ 、 $T_A = T_{MIN} \sim T_{MAX}$

| SYMBOL                        | PARAMETER                       | CONDITIONS                                                     |        | MIN      | TYP      | MAX     | UNITS   |

|-------------------------------|---------------------------------|----------------------------------------------------------------|--------|----------|----------|---------|---------|

| <b>Analog Outputs</b>         |                                 |                                                                |        |          |          |         |         |

| $C_{OUT}$                     | Output Capacitance (Note 3)     | DAC Register Loaded to All 1s<br>DAC Register Loaded to All 0s | ●<br>● | 60<br>30 | 90<br>60 |         | pF      |

| <b>Digital Input</b>          |                                 |                                                                |        |          |          |         |         |

| $V_{IH}$                      | Digital Input High Voltage      |                                                                | ●      | 2.4      |          |         | V       |

| $V_{IL}$                      | Digital Input Low Voltage       |                                                                | ●      |          | 0.8      |         | V       |

| $I_{IN}$                      | Digital Input Current           |                                                                | ●      |          | 0.001    | $\pm 1$ | $\mu A$ |

| $C_{IN}$                      | Digital Input Capacitance       | (Note 3) $V_{IN} = 0V$                                         | ●      |          | 8        |         | pF      |

| <b>Digital Output</b>         |                                 |                                                                |        |          |          |         |         |

| $V_{OH}$                      | Digital Output High Voltage     | $I_{OH} = 200\mu A$                                            | ●      | 4        |          |         | V       |

| $V_{OL}$                      | Digital Output Low Voltage      | $I_{OL} = 1.6mA$                                               | ●      |          | 0.4      |         | V       |

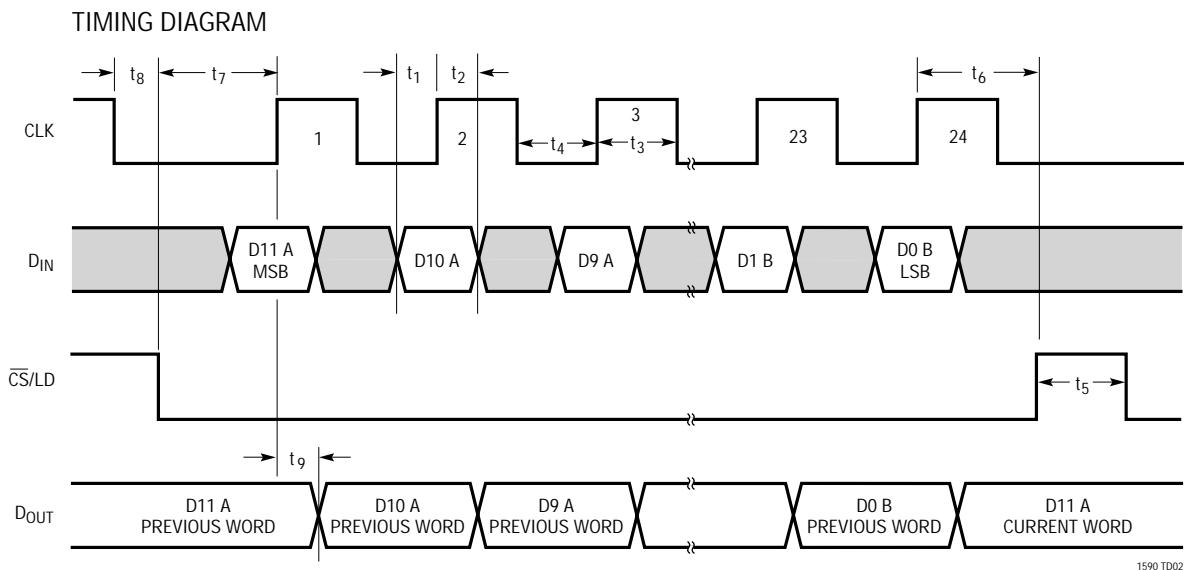

| <b>Timing Characteristics</b> |                                 |                                                                |        |          |          |         |         |

| $t_1$                         | $D_{IN}$ to CLK Setup Time      |                                                                | ●      | 50       |          |         | ns      |

| $t_2$                         | $D_{IN}$ to CLK Setup Hold Time |                                                                | ●      | 0        |          |         | ns      |

| $t_3$                         | CLK High Time                   |                                                                | ●      | 40       |          |         | ns      |

| $t_4$                         | CLK Low Time                    |                                                                | ●      | 40       |          |         | ns      |

| $t_5$                         | $\bar{CS}/LD$ High Time         |                                                                | ●      | 50       |          |         | ns      |

| $t_6$                         | LSB CLK to CS/LD                |                                                                | ●      | 40       |          |         | ns      |

| $t_7$                         | $\bar{CS}/LD$ Low to CLK High   |                                                                | ●      | 20       |          |         | ns      |

| $t_8$                         | CLK Low to $\bar{CS}/LD$ Low    |                                                                | ●      | 20       |          |         | ns      |

| $t_9$                         | CLK to $D_{OUT}$ Delay          |                                                                | ●      | 10       | 160      |         | ns      |

| <b>Power Supply</b>           |                                 |                                                                |        |          |          |         |         |

| $V_{CC}$                      | Operating Supply Range          |                                                                | ●      | 4.5      | 5        | 5.5     | V       |

| $I_{CC}$                      | Supply Current                  | Digital Inputs = 0V or $V_{CC}$                                | ●      |          | 10       |         | $\mu A$ |

は全動作温度範囲の規格値を意味する。

Note 1 :  $\pm 0.5LSB$  = フルスケールの  $\pm 0.012\%$

Note 2 : 内部帰還抵抗を使用する。

Note 3 : 設計で保証されているが、テストされていない。

Note 4 : DACレジスタにすべて0をロードした状態での $I_{OUT1}$ 。

Note 5 : OUT1負荷 = 100  $\Omega$  と13pFを並列に。

Note 6 :  $V_{REF} = 0V$ 。DACレジスタの内容はオール0からオール1、またはオール1からオール0に変化。

Note 7 :  $V_{REFA} = 0V$ および $V_{REFB} = 10kHz\ 20V_{P-P}$ でのDACA出力、または $V_{REFB} = 0V$ 、 $V_{REFA} = 10kHz\ 20V_{P-P}$ でのDACB出力。両方のDACレジスタにはオール1がロードされる。

Note 8 : 他のDACがフルスケール遷移を行うと、DAC AまたはDAC B上でグリッヂが発生する。

Note 9 :  $10Hz \sim 100kHz$ ,  $e_n = \sqrt{4KTRB}$  から計算。ただし: K = ポルツマン定数(  $J/K$  ), R = 抵抗(  $\Omega$  ), T = 抵抗温度(  $K$  ), B = 帯域幅( Hz )。

Note 10 :  $V_{REF} = 6VRMS$  ( 1kHz ), LT<sup>®</sup>1124オペアンプを使用して、DACレジスタにオール1をロード。

Note 11 :  $V_{REF} = \pm 10V$ , 10kHz正弦波、LT1358オペアンプを使用して、DACレジスタにオール0をロード。

Note 12 : LT1358オペアンプを使用した - 3dB帯域幅。

## 標準的性能特性

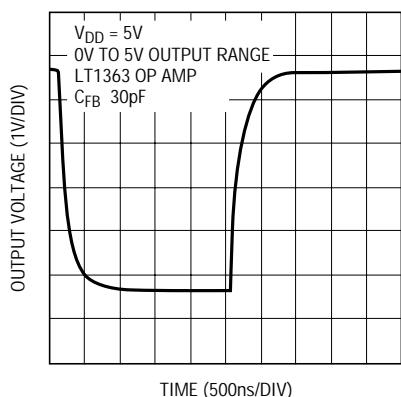

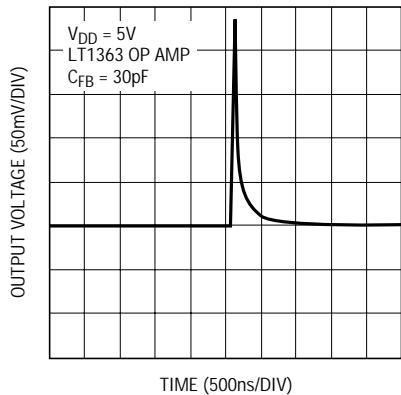

フルスケール・セトリング波形

1590 G12

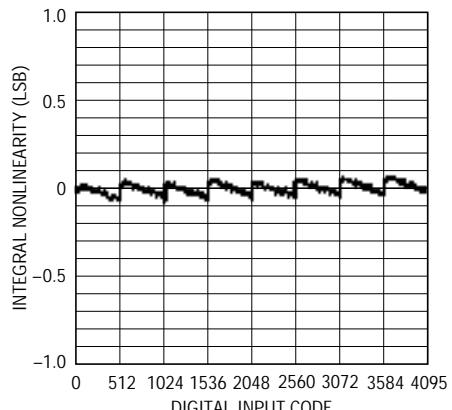

積分非直線性(INL)

1590 G02

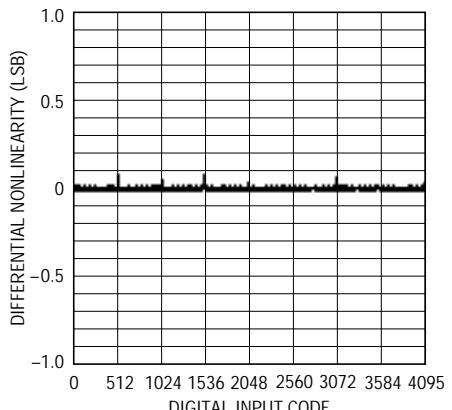

微分非直線性(DNL)

1590 G03

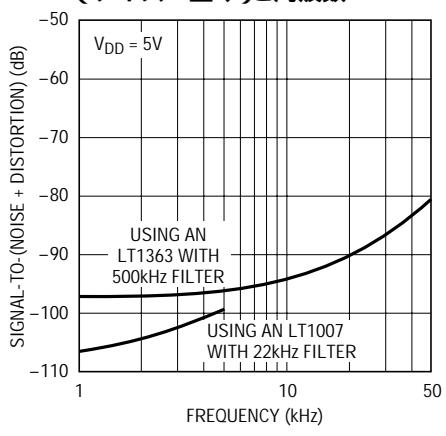

乗算モードでの信号対

(ノイズ+歪み)と周波数

1590 G10

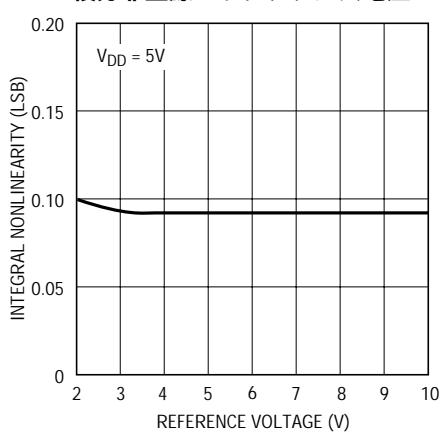

積分非直線とリファレンス電圧

1590 G05

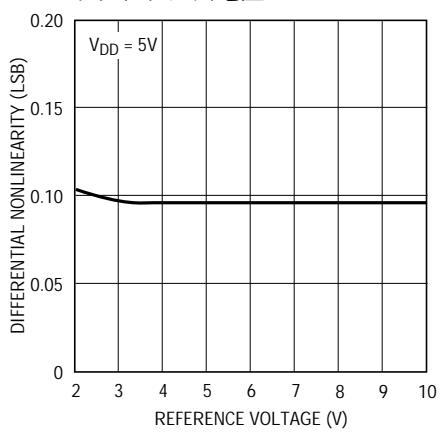

微分非直線性と

リファレンス電圧

1590 G06

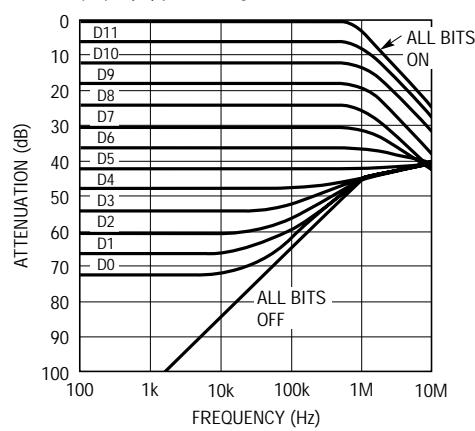

乗算モード周波数応答と

デジタル・コード

1590 G07

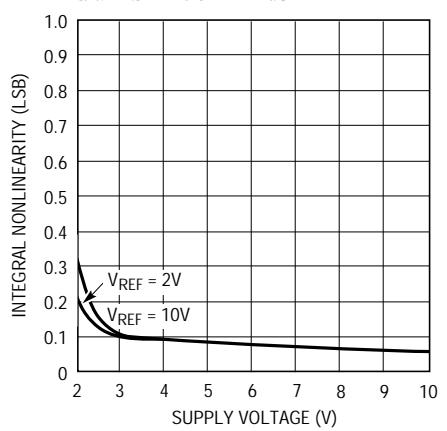

積分非直線性と電源電圧

1590 G08

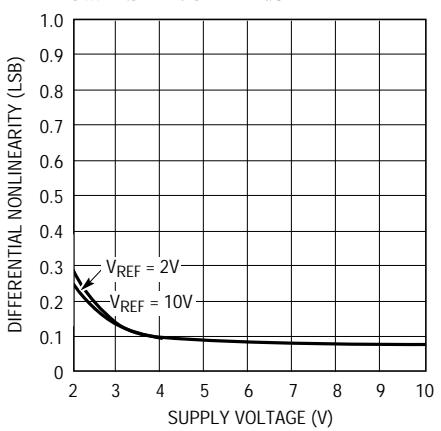

微分非直線性と電源電圧

1590 G09

## 標準的性能特性

中間スケールでの

グリッチ・インパルス

1590 G11

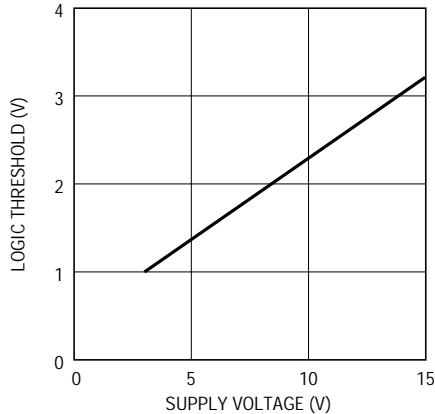

ロジック・スレッショルドと

電源電圧

1590 G04

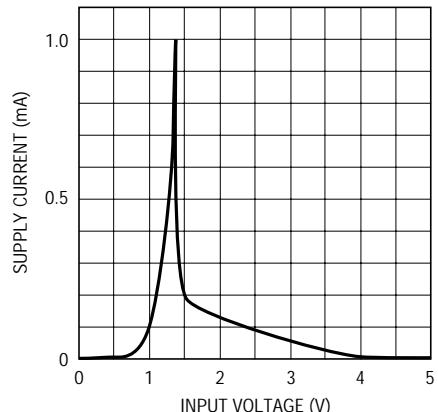

電源電流とロジック入力電圧

1590 G01

## ピン機能

$V_{REF\,B}$ 、 $V_{REF\,A}$ ( ピン1、9 ): DAC A/Bのリファレンス入力。標準  $\pm 10V$  で、  $\pm 25V$  まで受け入れます。

$R_{FB\,B}$ 、 $R_{FB\,A}$ ( ピン2、8 ): DAC A/Bの帰還抵抗。通常、電流 - 電圧コンバータ・オペアンプの出力に接続します。標準振幅は  $\pm 10V$  です。0Vから  $-V_{REF}$  まで振幅します。

OUT1 B、OUT1 A( ピン3、6 ): DAC A/B用の真の電流出力。通常、電流 - 電圧コンバータ・オペアンプの反転入力に接続します。

OUT2 B、OUT2 A( ピン4、5 ): DAC A/B用の相補電流出力。通常、グランドに接続します。

AGND( ピン7 ): アナログ・グランド・ピン。グランドに接続します。

DGND( ピン10 ): デジタル・グランド・ピン。グランドに接続します。

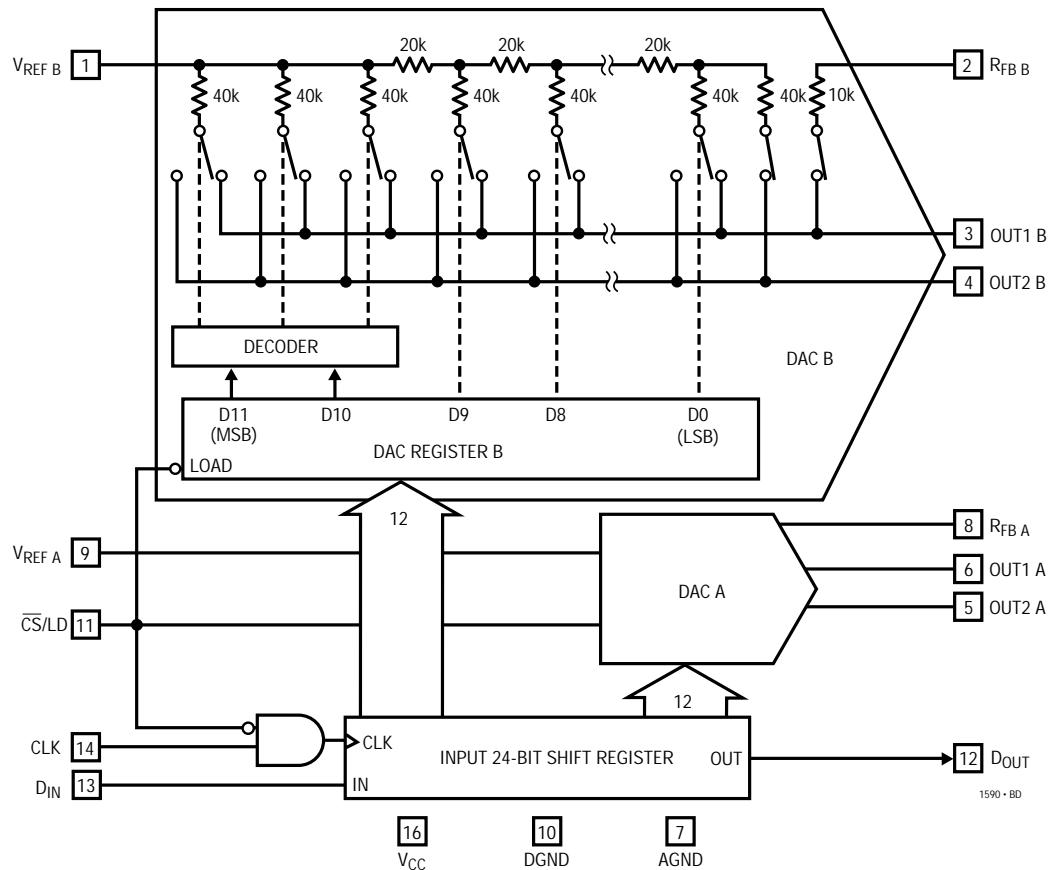

$\overline{CS/LD}$ ( ピン11 ): シリアル・インターフェース・イネーブルおよびロード・コントロール入力。 $\overline{CS/LD}$ が“L”的とき、CLK信号がイネーブルされデータをクロック・インする

ことができます。 $\overline{CS/LD}$ を“H”にすると、シフト・レジスタからDACレジスタにデータがロードされ、DAC出力が更新されます。

$D_{OUT}$ ( ピン12 ): シリアル・データ出力。データはCLKの立上りエッジで有効になります。

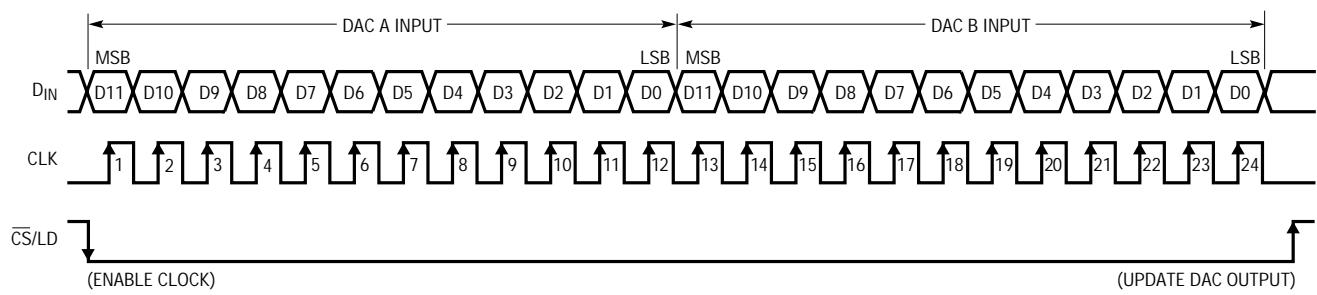

$D_{IN}$ ( ピン13 ): シリアル・データ入力。 $D_{IN}$ ピン上のデータは、シリアル・クロックの立上りエッジでシフト・レジスタにラッチされます。データは1つの24ビット・ワードとしてロードされます。最初の12ビットはMSBを先頭にしてDAC Aに、2番目の12ビットはMSBを先頭にしてDAC Bに送られます。

CLK( ピン14 ): シリアル・インターフェース・クロック入力。

$\overline{CLR}$ ( ピン15 ): DAC用クリア・ピン。“L”にすると、両方のDACがゼロ・スケールにクリアされます。このピンは通常動作では、 $V_{CC}$ に接続しなければなりません。

$V_{CD}$ ( ピン16 ): 正の電源入力。 $4.5 \leq V_{CC} \leq 5.5V$ 。グランドへバイパス・コンデンサを接続する必要があります。

## ブロック図

## タイミング図

### OPERATING SEQUENCE

## タイミング図

1590 TD02

## アプリケーション情報

### 概要

LTC1590はシリアル入力と電流出力を備えたデュアル12ビット乗算型DACです。高精度R/2R抵抗ラダー・テクノロジーを駆使して、卓越した直線性と安定性を提供します。このデバイスは単一5V電源で動作し、オペアンプを外付けして使用すれば、±10Vのリファレンス入力および電圧出力範囲を提供します。

### シリアルI/O

LTC1590は24ビットのシリアル・ワードを受け入れる3線式SPI/MICROWIRE™対応シリアル・ポートを備えています。データはMSBを先頭にしてロードされ、最初の12ビットはDAC A、そして2番目の12ビットはDAC Bを制御します。データはCLKの立上りエッジで、DIN入力にシフトインされます。CLK入力をイネーブルするためにデータを転送する前に、CS/LD入力を“L”にしなければなりません。データを転送した後、CS/LDを“H”にして、シフト・レジスタから両方のDACを更新するDACレジスタにデータをロードします。

24ビット・シフト・レジスタのバッファ出力は、DOUTピンに現れます。あるDACのDOUTピンを次のDACのDINピンに接続することにより、複数のDACをまとめて1本の3線式インターフェースにディジーチェインすることができます(タイミング図のセクションを参照)。

MICROWIREはナショナル・セミコンダクター社の商標です。

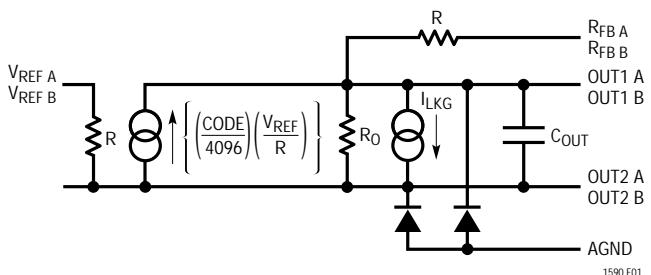

### 等価回路

図1はLTC1590 DACの等価アナログ回路を示します。Rはリファレンス入力R<sub>REF</sub>で、標準11kです。DAC出力は以下の値のテブナン等価電流源によって表されます：

$$( \text{コード}/4096 ) ( V_{\text{REF}}/R )$$

電流源I<sub>LKG</sub>はDAC出力スイッチの接合リーキをモデル化したものです。I<sub>LKG</sub>は85nA未満であり、温度が10°C低下するごとに、ほぼ1/2ずつ減少します。C<sub>OUT</sub>は出力容量で、これもDAC出力スイッチから来ており、ゼロスケールの30pFからフルスケールの60pFまで変化します。R<sub>O</sub>は等価出力抵抗で、デジタル入力コードに応じて変化します(オペアンプの選択セクションを参照)。

図1. 等価回路

## アプリケーション情報

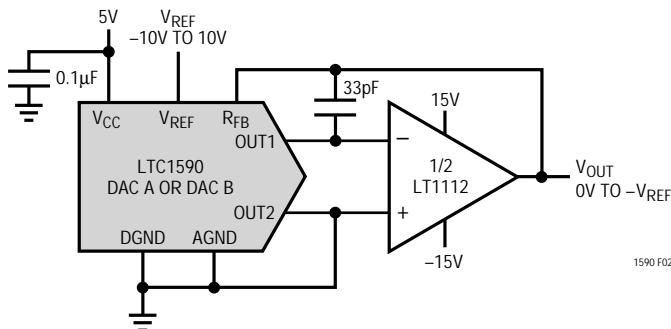

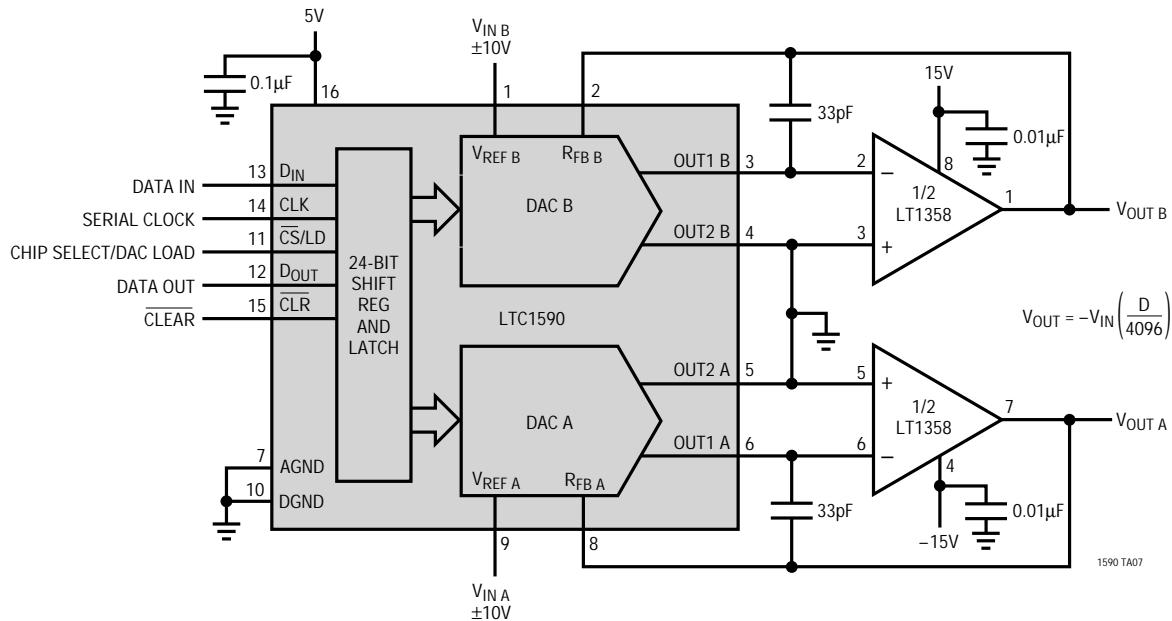

### ユニポーラ2象限乗算モード ( $V_{OUT} = 0V \sim -V_{REF}$ )

LTC1590は、図2に示すとおり1個のデュアル・オペアンプを外付けして、デュアルの2象限乗算DACにすることができます。ユニポーラDAC伝達特性を表1に示します。内部帰還抵抗とOUT1出力容量によって生じるポールを補償するために、33pFの帰還コンデンサが推奨されます。高速オペアンプの場合は安定動作のためにこの帰還コンデンサが必要で、高速過渡応答と最短セトリング・タイムを実現するには、より小さな8pF～15pFの容量が望ましい場合があります。より低い周波数の信号に対しては、広帯域ノイズ、グリッヂ・インパルス、および歪みを低減するために、より大きな帰還コンデンサを使用することができます。ほぼ( $C_{FB} \times R_{FB}$ )でDAC伝達特性にポールが現れます。たとえば、100pFの帰還コンデンサは、通常以下のところにポールを導入します：

$$145\text{kHz} = \frac{1}{2\pi(100\text{pF})(11\text{k}\Omega)}$$

図2. ユニポーラ動作(2象限乗算)

表1. ユニポーラ・バイナリ・コード表

| DIGITAL INPUT<br>BINARY NUMBER<br>IN DAC REGISTER | ANALOG OUTPUT<br>$V_{OUT}$ |                      |

|---------------------------------------------------|----------------------------|----------------------|

| MSB                                               | LSB                        |                      |

| 1111                                              | 1111                       | 1111                 |

| 1000                                              | 0000                       | 0000                 |

| 0000                                              | 0000                       | - $V_{REF}$ (1/4096) |

| 0000                                              | 0000                       | 0V                   |

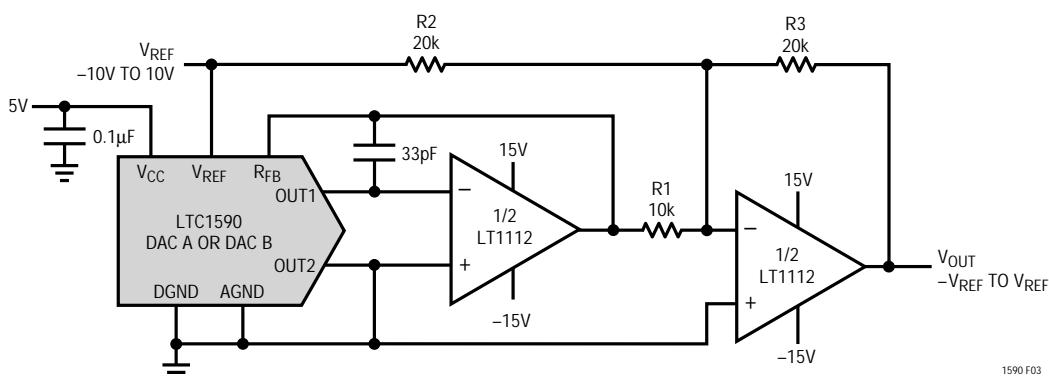

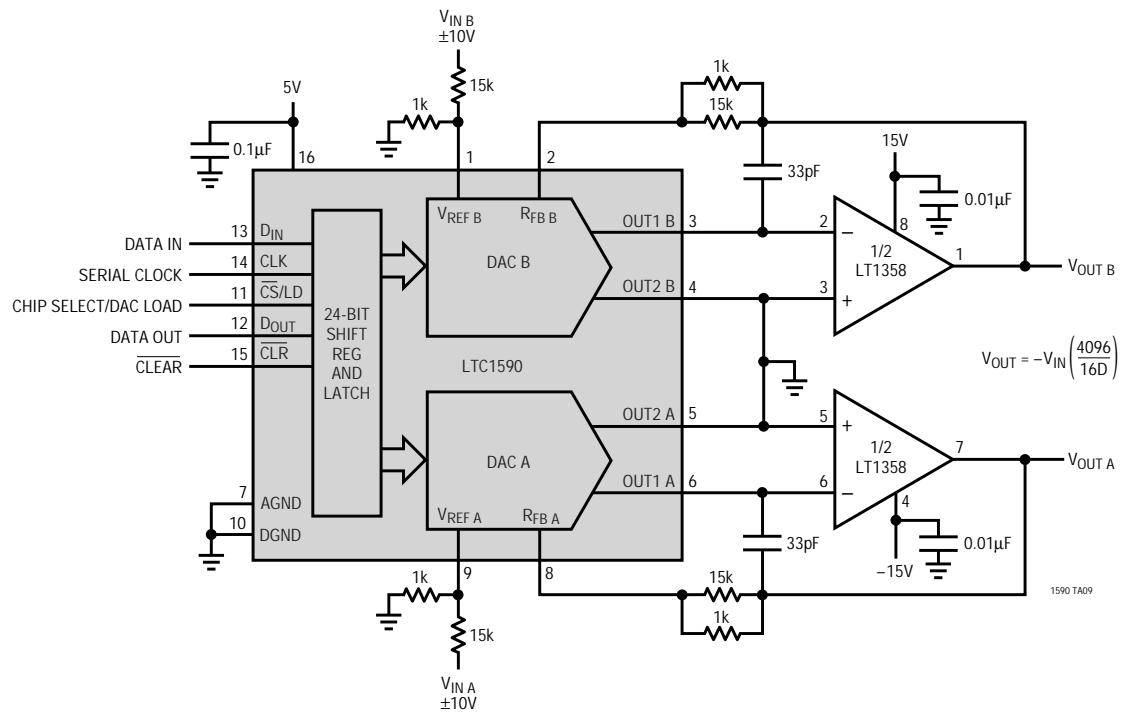

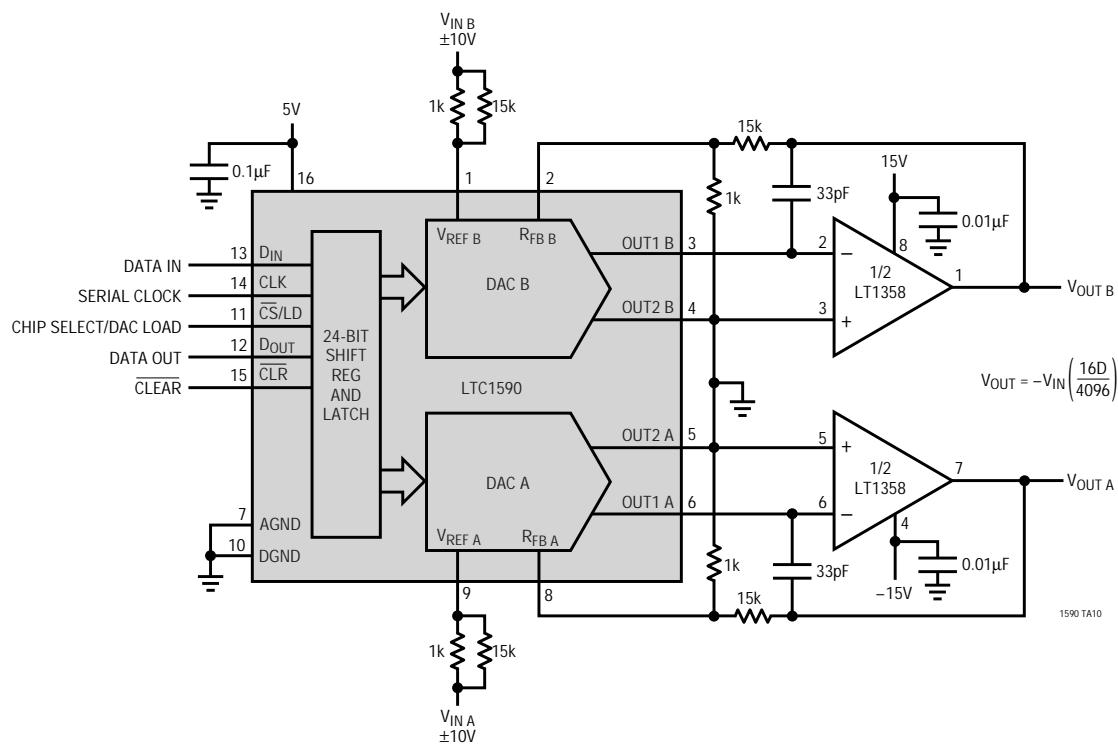

### バイポーラ4象限乗算モード

( $V_{OUT} = -V_{REF} \sim +V_{REF}$ )

図3の回路を使用して、デュアルの4象限乗算DACにすることができます。この回路はユニポーラ・アプリケーション回路を基にして、3本の抵抗とオペアンプが追加されています。これらの追加デバイスは、ユニポーラ出力からバイポーラ出力まで-2の利得と、(-1 × V<sub>REF</sub>)のオフセットを提供し、表2に示す伝達特性を生成します。マッチングのとれた20k抵抗パックを使用し、2本の抵抗を並列にして10k抵抗にすることを推奨します。

表2. バイポーラ・オフセット・バイナリ・コード表

| DIGITAL INPUT<br>BINARY NUMBER<br>IN DAC REGISTER | ANALOG OUTPUT<br>$V_{OUT}$ |                                       |

|---------------------------------------------------|----------------------------|---------------------------------------|

| MSB                                               | LSB                        |                                       |

| 1111                                              | 1111                       | + $V_{REF}$ (2047/2048)               |

| 1000                                              | 0000                       | + $V_{REF}$ (1/2048)                  |

| 1000                                              | 0000                       | 0V                                    |

| 0111                                              | 1111                       | - $V_{REF}$ (1/2048)                  |

| 0000                                              | 0000                       | - $V_{REF}$ (2048/2048) = - $V_{REF}$ |

図3. バイポーラ動作(4象限乗算)

## アプリケーション情報

### オペアンプの選択

LTC1590の優れた精度と安定性を維持するには、オペアンプの選択に配慮が必要です。幸いにも、オペアンプ・オフセットに対するINLおよびDNLの感度は、この種の競合デバイスに比べて大幅に低減されています。オペアンプの $V_{OS}$ によって、DAC出力オフセットが生じます。さらに、DACの等価出力抵抗 $R_O$ はコードの関数として変化するので、 $V_{OS}$ に比例したコードに依存するDAC出力誤差があります。固定リファレンス・アプリケーションの場合、これによって利得、INL、およびDNL誤差が生じます。乗算アプリケーションの場合、コードに依存するDC出力電圧誤差が見られます。ゼロスケールでは、DAC出力誤差はオペアンプ・オフセットと等しく、フルスケールでは出力誤差はオペアンプ・オフセットの2倍になります。たとえば、1mVのオペアンプ・オフセットにより、10Vのフルスケール範囲において0.41 LSBのゼロスケール誤差と0.82 LSBのフルスケール誤差が生じます。オフセットに生じるINL誤差は、ほぼオペアンプ $V_{OS} \times 0.4$ 、DNL誤差はオペアンプ $V_{OS} \times 0.07$ です。1mVのオペアンプ $V_{OS}$ と10Vのフルスケール範囲では、INLの性能低下は0.17 LSBで、DNLの性能低下は0.03 LSBです。

オペアンプのバイアス電流によって、 $(I_{BIAS})(R_{FB}) \approx (I_{BIAS})(11k\Omega)$ のオフセット誤差しか生じません。たとえば、

### 標準的応用例

デュアルのプログラム可能な減衰器

100nAのオペアンプ・バイアス電流によって、1.1mVのDACオフセット、すなわち10Vのフルスケール範囲に対して0.45LSBが生じます。オペアンプの非反転入力を、抵抗を通してグランドに接続しても、バイアス電流誤差はキャンセルされないので、これを行わないことが重要です！ 同様に、オペアンプのバイアス電流によって生じるオフセットはオペアンプのヌル・ピンを使って調節してはなりません。これは、DAC OUT1ピンとOUT2ピン間のオフセットを増大させ、INL、DNL、および利得誤差を生じるためです。オペアンプのオフセット誤差調整が必要な場合は、オペアンプの入力オフセット電圧(OUT1とOUT2の電圧差)をゼロにしなければなりません。

### 接地

他の高精度データ・コンバータと同様、クリーンなグランド接続が重要です。低インピーダンスのアナログ・グランド・ブレーンと星状接地を使用してください。OUT2は相補的なDAC出力電流を伝達し、できる限り低い抵抗で、星状グランドに接続しなければなりません。星状グランド点に接続しなければならない他のグランド点には、 $V_{REF}$ 入力グランド、オペアンプの非反転入力、および $V_{OUT}$ グランド・リファレンス点があります。

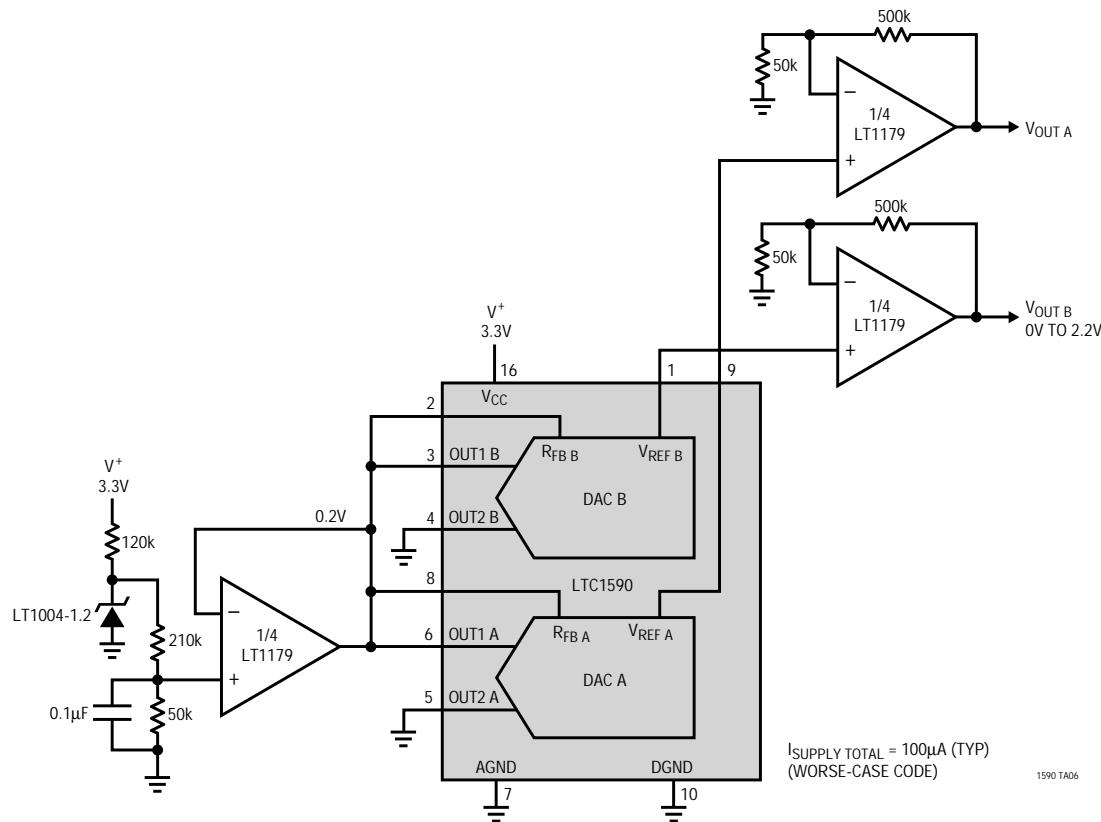

## 標準的応用例

超低消費電力、単一電源、デュアルV<sub>OUT</sub> DAC

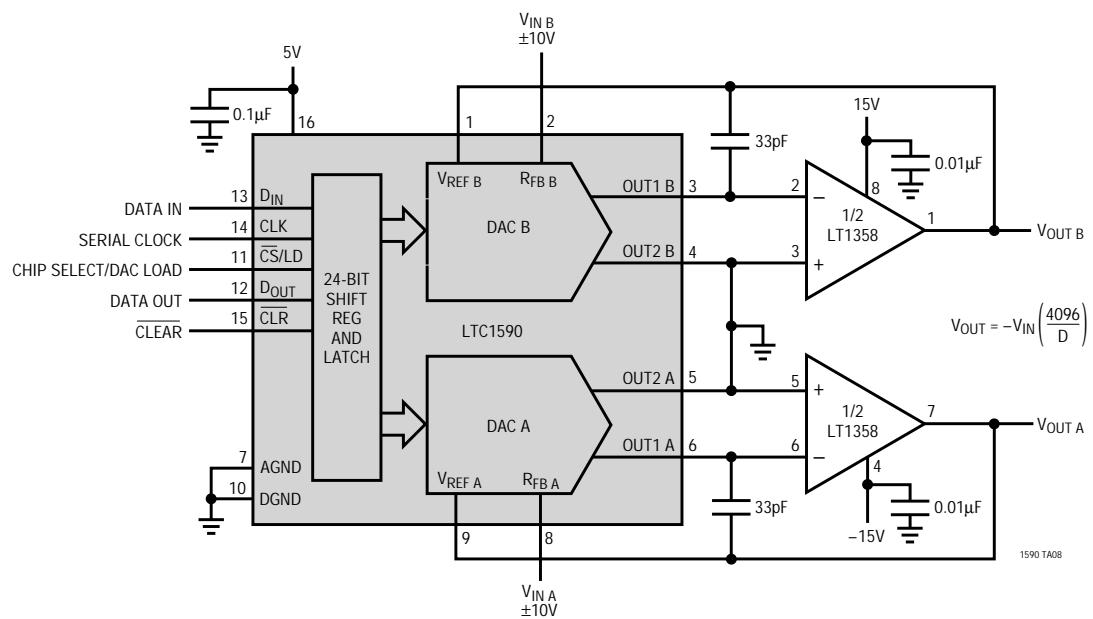

デュアルのプログラム可能な利得アンプ

## 標準的応用例

デュアルの入力減衰付きプログラム可能な利得アンプ

## 標準的応用例

### デュアルの利得付きプログラム可能減衰器

## 関連製品

| PART NUMBER     | DESCRIPTION                                   | COMMENTS                                   |

|-----------------|-----------------------------------------------|--------------------------------------------|

| LTC1595         | 16-Bit Multiplying $I_{OUT}$ DAC in SO-8      | True 16-Bit Upgrade for DAC8043            |

| LTC1596         | 16-Bit Multiplying $I_{OUT}$ DAC              | True 16-Bit Upgrade for DAC8143 and AD7543 |

| LTC7541A        | Parallel I/O Multiplying $I_{OUT}$ 12-Bit DAC | 12-Bit Wide Parallel Input                 |

| LTC7543/LTC8143 | Serial I/O Multiplying $I_{OUT}$ 12-Bit DACs  | Clear Pin and Serial Data Output (LTC8143) |

| LTC7545A        | Parallel I/O Multiplying $I_{OUT}$ 12-Bit DAC | 12-Bit Wide Latched Parallel Input         |

| LTC8043         | Serial I/O Multiplying $I_{OUT}$ 12-Bit DAC   | 8-Pin SO and PDIP                          |