# 超高速過渡応答 低ドロップアウト・レギュレータ 可変および固定出力電圧

## 特長

- UltraFast™過渡応答によりタンタル

および電解出力コンデンサが不要

- FET R<sub>Ds(ON)</sub>によってドロップアウト電圧が決定

- 全温度で1%のリファレンス/出力電圧許容差

- 標準ロード・レギュレーション: 1mV

- ハイ・サイド・センス電流制限

- ラッチオフ付き多機能シャットダウン・ピン

## アプリケーション

- Pentium®プロセッサ用電源

- PowerPC™用電源

- 5Vから3.XXVまたは3.3Vから2.XXVの

マイクロプロセッサ用電源

- GTL終端

- 低電圧ロジック電源

|                             |                        |

|-----------------------------|------------------------|

| LT1575CN8/LT1575CS8         | Adjustable             |

| LT1575CN8-1.5/LT1575CS8-1.5 | 1.5V Fixed             |

| LT1575CN8-2.8/LT1575CS8-2.8 | 2.8V Fixed             |

| LT1575CN8-3.3/LT1575CS8-3.3 | 3.3V Fixed             |

| LT1575CN8-3.5/LT1575CS8-3.5 | 3.5V Fixed             |

| LT1575CN8-5/LT1575CS8-5     | 5V Fixed               |

| LT1577CS-ADJ/ADJ            | Adjustable, Adjustable |

| LT1577CS-3.3/ADJ            | 3.3V Fixed, Adjustable |

| LT1577CS-3.3/2.8            | 3.3V Fixed, 2.8V Fixed |

LT1577で可能なその他の出力電圧の組合せについてはお問い合わせください。

## 概要

LT®1575/LT1577は、低コストの外部NチャネルMOSFETをソース・フォロワとしてドライブし、超高速過渡応答、低ドロップアウト電圧レギュレータを実現するシングル/デュアル・コントローラICです。

LT1575/LT1577は最もニーズが多い最新マイクロプロセッサ・アプリケーションにおいて、高価なタンタルまたはバルク電解出力コンデンサをなくすことによって、比類のない過渡負荷性能を達成しています。精密に調整された可変および固定出力電圧バージョンは、要求されるどのマイクロプロセッサ用電源電圧にも対応します。NチャネルMOSFETのR<sub>Ds(ON)</sub>を選択することによって、非常に低いドロップアウト電圧を達成できます。

独自の保護機能としては、フォールト保護タイマ回路を起動するハイ・サイド電流制限アンプがあります。多機能シャットダウン・ピンは、ラッチオフでの電流制限タイムアウト、過電圧保護、サーマル・シャットダウン、またはこれらの機能の組合せを提供します。LT1575は8ピンSOまたはPDIPで供給され、LT1577は16ピン細型SOパッケージで供給されます。

□、LTC、LTはリニアテクノロジー社の登録商標です。UltraFastはリニアテクノロジー社の商標です。PentiumはIntel Corporationの登録商標です。PowerPCはIBM Corporationの商標です。

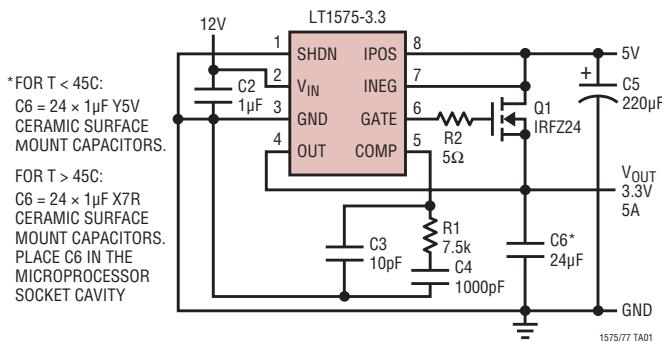

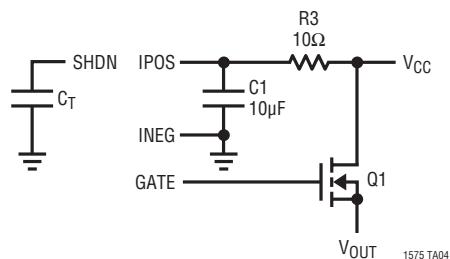

## 標準的応用例

超高速過渡応答、5Vから3.3Vの低ドロップアウト・レギュレータ

(電流制限を含む回路図は、「標準的応用例」を参照してください。)

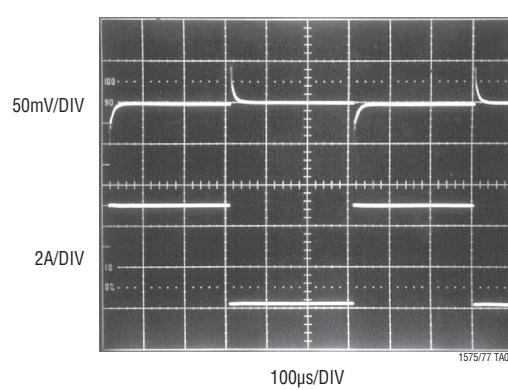

### 0.2Aから5Aの出力負荷ステップの 過渡応答

# LT1575/LT1577

## 絶対最大定格

(Note 1)

|                     |          |                 |             |

|---------------------|----------|-----------------|-------------|

| $V_{IN}$ 、IPOS、INEG | 22V      | 接合部温度 (Note 2)  | 0°C~100°C   |

| SHDN                | $V_{IN}$ | 保存温度範囲          | -65°C~150°C |

| 動作周囲温度範囲            | 0°C~70°C | リード温度(半田付け、10秒) | 300°C       |

## パッケージ/発注情報

| TOP VIEW                                                                      |                                 | TOP VIEW                                                                      |                                 | TOP VIEW                                                                 |               |

|-------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------|---------------|

| SHDN [1]                                                                      | IPOS [8]                        | SHDN [1]                                                                      | IPOS [8]                        | SHDN1 [1]                                                                | IPOS1 [16]    |

| $V_{IN}$ [2]                                                                  | INEG [7]                        | $V_{IN}$ [2]                                                                  | INEG [7]                        | $V_{IN1}$ [2]                                                            | INEG1 [15]    |

| GND [3]                                                                       | GATE [6]                        | GND [3]                                                                       | GATE [6]                        | GND1 [3]                                                                 | GATE1 [14]    |

| FB [4]                                                                        | COMP [5]                        | OUT [4]                                                                       | COMP [5]                        | SHDN2 [5]                                                                | COMP1 [13]    |

| N8 PACKAGE<br>8-LEAD PDIP                                                     | S8 PACKAGE<br>8-LEAD PLASTIC SO | N8 PACKAGE<br>8-LEAD PDIP                                                     | S8 PACKAGE<br>8-LEAD PLASTIC SO | V <sub>IN2</sub> [6]                                                     | IPOS2 [12]    |

| $T_{JMAX} = 100^\circ\text{C}, \theta_{JA} = 100^\circ\text{C}/\text{W}$ (N8) |                                 | $T_{JMAX} = 100^\circ\text{C}, \theta_{JA} = 100^\circ\text{C}/\text{W}$ (N8) |                                 | GND2 [7]                                                                 | INEG2 [11]    |

| $T_{JMAX} = 100^\circ\text{C}, \theta_{JA} = 130^\circ\text{C}/\text{W}$ (S8) |                                 | $T_{JMAX} = 100^\circ\text{C}, \theta_{JA} = 130^\circ\text{C}/\text{W}$ (S8) |                                 | FB2 [8]                                                                  | GATE2 [10]    |

| ORDER PART NUMBER                                                             |                                 |                                                                               | ORDER PART NUMBER               |                                                                          |               |

| LT1575CN8                                                                     | LT1575CS8-1.5                   | LT1575CS8-3.3                                                                 | LT1575CN8-1.5                   | LT1575CN8-3.5                                                            | LT1575CS8-3.3 |

| LT1575CS8                                                                     | LT1575CS8-2.8                   | LT1575CS8-3.5                                                                 | LT1575CS8-2.8                   | LT1575CN8-5                                                              | LT1575CS8-5   |

|                                                                               | LT1575CN8-3.3                   | LT1575CS8-5                                                                   |                                 |                                                                          |               |

| S8 PART MARKING                                                               |                                 |                                                                               | S8 PART MARKING                 |                                                                          |               |

| 1575                                                                          | 157515                          | 157535                                                                        | 157528                          | 15755                                                                    | 157533        |

|                                                                               |                                 |                                                                               |                                 |                                                                          |               |

| TOP VIEW                                                                      |                                 |                                                                               |                                 |                                                                          |               |

| SHDN1 [1]                                                                     | IPOS1 [16]                      | SHDN1 [1]                                                                     | IPOS1 [16]                      | SHDN1 [1]                                                                | IPOS1 [16]    |

| $V_{IN1}$ [2]                                                                 | INEG1 [15]                      | $V_{IN1}$ [2]                                                                 | INEG1 [15]                      | $V_{IN1}$ [2]                                                            | INEG1 [15]    |

| GND1 [3]                                                                      | GATE1 [14]                      | GND1 [3]                                                                      | GATE1 [14]                      | GND1 [3]                                                                 | GATE1 [14]    |

| OUT-3.3 [4]                                                                   | COMP1 [13]                      | OUT-3.3 [4]                                                                   | COMP1 [13]                      | OUT-3.3 [4]                                                              | COMP1 [13]    |

| SHDN2 [5]                                                                     | IPOS2 [12]                      | SHDN2 [5]                                                                     | IPOS2 [12]                      | SHDN2 [5]                                                                | IPOS2 [12]    |

| $V_{IN2}$ [6]                                                                 | INEG2 [11]                      | $V_{IN2}$ [6]                                                                 | INEG2 [11]                      | $V_{IN2}$ [6]                                                            | INEG2 [11]    |

| GND2 [7]                                                                      | GATE2 [10]                      | GND2 [7]                                                                      | GATE2 [10]                      | GND2 [7]                                                                 | GATE2 [10]    |

| FB [8]                                                                        | COMP2 [9]                       | FB [8]                                                                        | COMP2 [9]                       | FB [8]                                                                   | COMP2 [9]     |

| S PACKAGE<br>16-LEAD PLASTIC NARROW SO                                        |                                 | S PACKAGE<br>16-LEAD PLASTIC NARROW SO                                        |                                 | S PACKAGE<br>16-LEAD PLASTIC NARROW SO                                   |               |

| $T_{JMAX} = 100^\circ\text{C}, \theta_{JA} = 100^\circ\text{C}/\text{W}$      |                                 | $T_{JMAX} = 100^\circ\text{C}, \theta_{JA} = 100^\circ\text{C}/\text{W}$      |                                 | $T_{JMAX} = 100^\circ\text{C}, \theta_{JA} = 100^\circ\text{C}/\text{W}$ |               |

| ORDER PART NUMBER                                                             |                                 |                                                                               | ORDER PART NUMBER               |                                                                          |               |

| LT1577CS-3.3/ADJ                                                              |                                 |                                                                               | LT1577CS-3.3/2.8                |                                                                          |               |

インダストリアルおよびミリタリ・グレードに関してはお問い合わせください。

## 電気的特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $GATE = 6\text{V}$ 、 $IPOS = INEG = 5\text{V}$ 、 $SHDN = 0.75\text{V}$

| SYMBOL    | PARAMETER                                          | CONDITIONS                               | MIN              | TYP            | MAX          | UNITS    |     |

|-----------|----------------------------------------------------|------------------------------------------|------------------|----------------|--------------|----------|-----|

| $I_Q$     | Supply Current                                     |                                          | ● 5              | 12             | 19           | mA       |     |

| $V_{FB}$  | LT1575 Reference Voltage                           |                                          | ● -0.6<br>● -1.0 | 1.210<br>1.210 | 0.6<br>1.0   | %        |     |

| $V_{OUT}$ | LT1575-1.5 Output Voltage                          |                                          | ● -0.6<br>● -1.0 | 1.500<br>1.500 | 0.6<br>1.0   | %        |     |

|           | LT1575-2.8 Output Voltage                          |                                          | ● -0.6<br>● -1.0 | 2.800<br>2.800 | 0.6<br>1.0   | %        |     |

|           | LT1575-3.3 Output Voltage                          |                                          | ● -0.6<br>● -1.0 | 3.300<br>3.300 | 0.6<br>1.0   | %        |     |

|           | LT1575-3.5 Output Voltage                          |                                          | ● -0.6<br>● -1.0 | 3.500<br>3.500 | 0.6<br>1.0   | %        |     |

|           | LT1575-5 Output Voltage                            |                                          | ● -0.6<br>● -1.0 | 5.000<br>5.000 | 0.6<br>1.0   | %        |     |

|           | Line Regulation                                    | $10\text{V} \leq V_{IN} \leq 20\text{V}$ | ●                | 0.01           | 0.03         | %/V      |     |

| $I_{FB}$  | FB Input Bias Current                              | $FB = V_{FB}$                            | ●                | -0.6           | -4.0         | μA       |     |

| $I_{OUT}$ | OUT Divider Current                                | $OUT = V_{OUT}$                          | ●                | 0.5            | 1.0          | 1.5      | mA  |

| AVOL      | LT1575 Large-Signal Voltage Gain                   | $V_{GATE} = 3\text{V}$ to $10\text{V}$   | ●                | 69             | 84           | dB       |     |

|           | LT1575-1.5 Large-Signal Voltage Gain               | $V_{GATE} = 3\text{V}$ to $10\text{V}$   | ●                | 67             | 82           | dB       |     |

|           | LT1575-2.8 Large-Signal Voltage Gain               | $V_{GATE} = 3\text{V}$ to $10\text{V}$   | ●                | 60             | 76           | dB       |     |

|           | LT1575-3.3 Large-Signal Voltage Gain               | $V_{GATE} = 3\text{V}$ to $10\text{V}$   | ●                | 60             | 75           | dB       |     |

|           | LT1575-3.5 Large-Signal Voltage Gain               | $V_{GATE} = 3\text{V}$ to $10\text{V}$   | ●                | 60             | 74           | dB       |     |

|           | LT1575-5 Large-Signal Voltage Gain                 | $V_{GATE} = 3\text{V}$ to $10\text{V}$   | ●                | 56             | 71           | dB       |     |

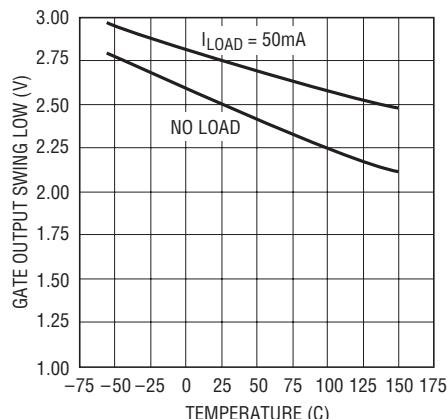

| $V_{OL}$  | GATE Output Swing Low (Note 3)                     | $I_{GATE} = 0\text{mA}$                  | ●                | 2.5            | 3.0          | V        |     |

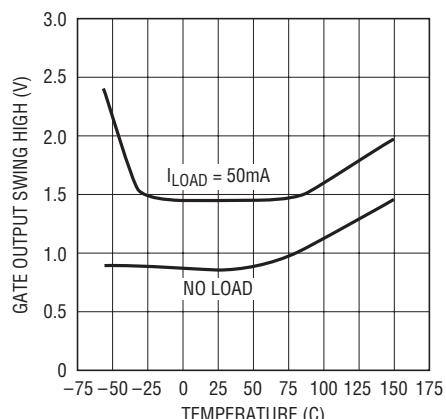

| $V_{OH}$  | GATE Output Swing High                             | $I_{GATE} = 0\text{mA}$                  | ●                | $V_{IN} - 1.6$ | $V_{IN} - 1$ | V        |     |

|           | IPOS + INEG Supply Current                         | $3\text{V} \leq IPOS \leq 20\text{V}$    | ●                | 0.3            | 0.625        | 1.0      | mA  |

|           | Current Limit Threshold Voltage                    |                                          | ●                | 42<br>37       | 50<br>50     | 58<br>63 | mV  |

|           | Current Limit Threshold Voltage<br>Line Regulation | $3\text{V} \leq IPOS \leq 20\text{V}$    | ●                |                | -0.20        | -0.50    | %/V |

|           | SHDN Sink Current                                  | Current Flows Into Pin                   | ●                | 2.5            | 5.0          | 8.0      | μA  |

|           | SHDN Source Current                                | Current Flows Out of Pin                 | ●                | -8             | -15          | -23      | μA  |

|           | SHDN Low Clamp Voltage                             |                                          | ●                |                | 0.1          | 0.25     | V   |

|           | SHDN High Clamp Voltage                            |                                          | ●                | 1.50           | 1.85         | 2.20     | V   |

|           | SHDN Threshold Voltage                             |                                          | ●                | 1.18           | 1.21         | 1.240    | V   |

|           | SHDN Threshold Hysteresis                          |                                          | ●                | 50             | 100          | 150      | mV  |

●は全動作温度範囲の規格値を意味します。

Note 1: 絶対最大定格は、それを超えるとデバイスの寿命に影響を及ぼす値です。

Note 2:  $T_J$ は、周囲温度 $T_A$ と消費電力 $P_D$ から次の公式に従って計算されます:LT1577は1パッケージにつき2つのレギュレータで構成されているので、LT1577の全消費電力を使って接合部温度を計算しなければなりません。LT1577の全 $P_D = P_D(\text{レギュレータ1}) + P_D(\text{レギュレータ2})$

$$\begin{aligned} \text{LT1575CN8: } T_J &= T_A + (P_D \cdot 100^\circ\text{CW}) \\ \text{LT1575CS8: } T_J &= T_A + (P_D \cdot 130^\circ\text{CW}) \\ \text{LT1577CS: } T_J &= T_A + (P_D \cdot 100^\circ\text{CW}) \end{aligned}$$

Note 3: 外部MOSFETの $V_{GS(th)}$ は $(3\text{V} - V_{OUT})$ より大きくなればなりません。

# LT1575/LT1577

## 標準的性能特性

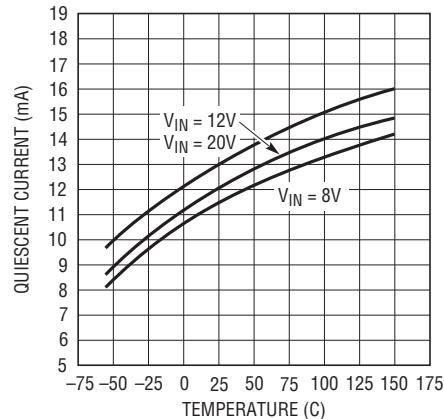

消費電流と温度

1575/77 G01

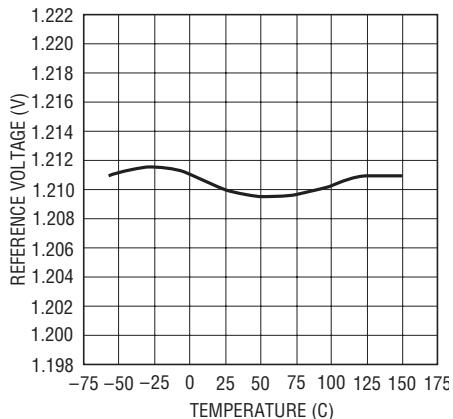

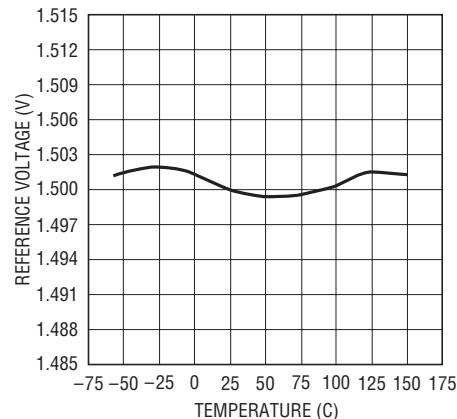

可変LT1575 V<sub>REF</sub>と温度

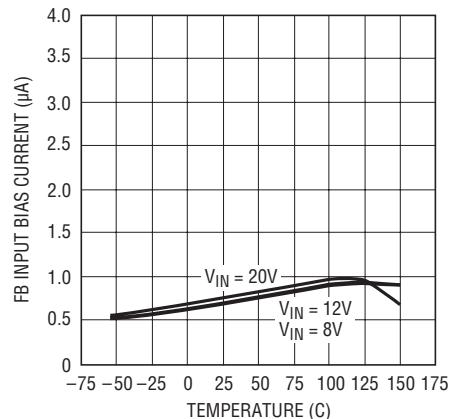

FB入力バイアス電流と温度

1575/77 G03

LT1575-1.5 V<sub>OUT</sub>と温度

1575/77 G04

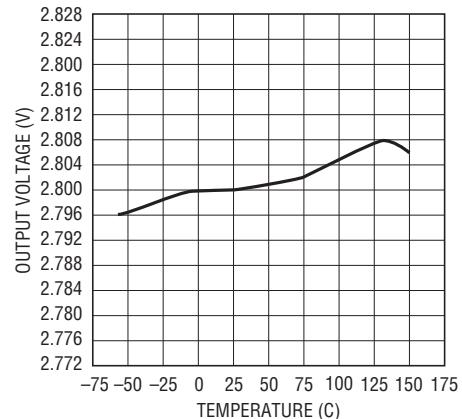

LT1575-2.8 V<sub>OUT</sub>と温度

1575/77 G05

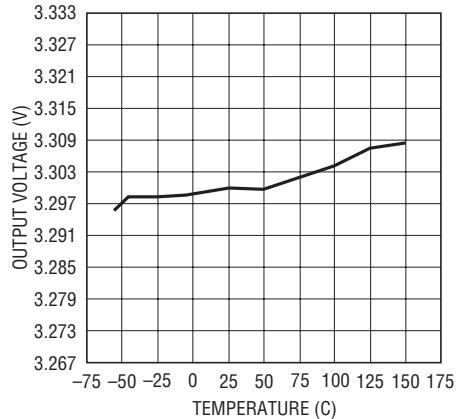

LT1575-3.3 V<sub>OUT</sub>と温度

1575/77 G06

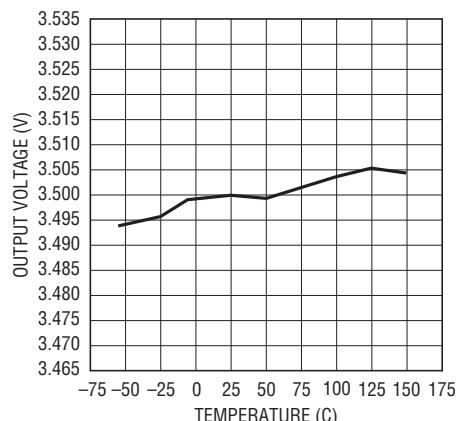

LT1575-3.5 V<sub>OUT</sub>と温度

1575/77 G07

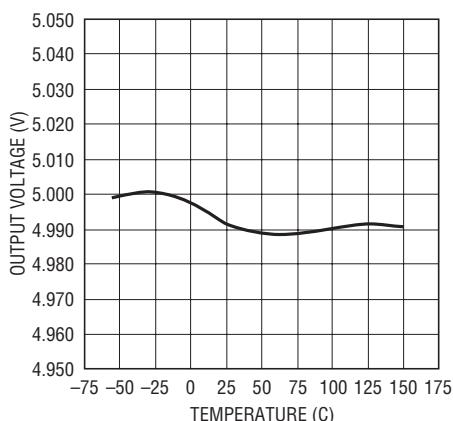

LT1575-5 V<sub>OUT</sub>と温度

1575/77 G08

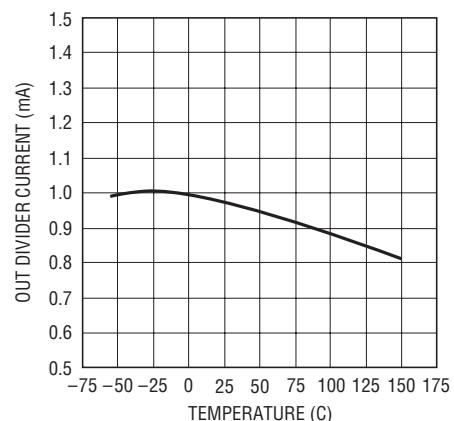

OUT分割器電流と温度

1575/77 G09

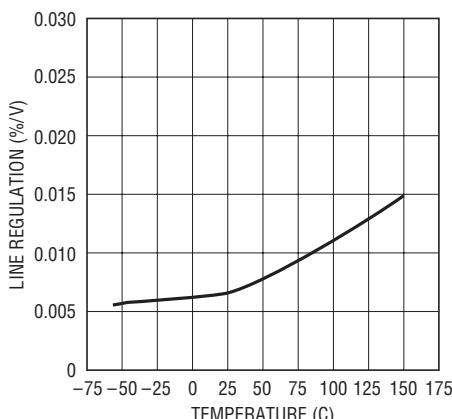

## 標準的性能特性

V<sub>REF</sub>/V<sub>OUT</sub>ライン・

レギュレーションと温度

1575/77 G10

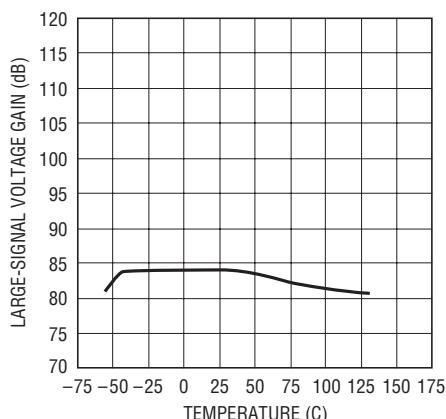

誤差アンプ大信号電圧利得と温度

1575/77 G11

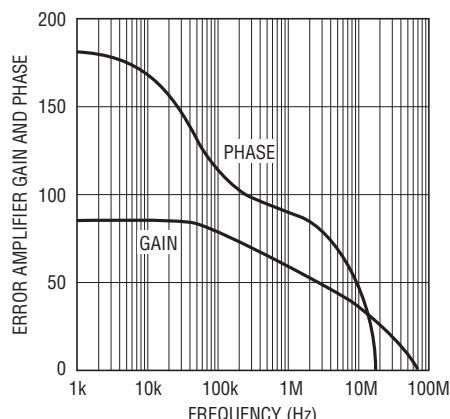

利得および位相と周波数

1575/77 G12

ゲート出力振幅“L”と温度

1575/77 G13

ゲート出力振幅“H”と温度

1575/77 G14

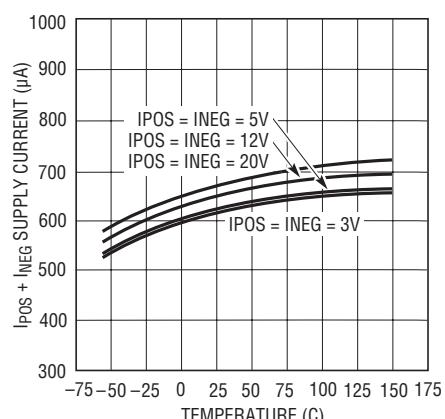

IPOS+INEG電源電流と温度

1575/77 G15

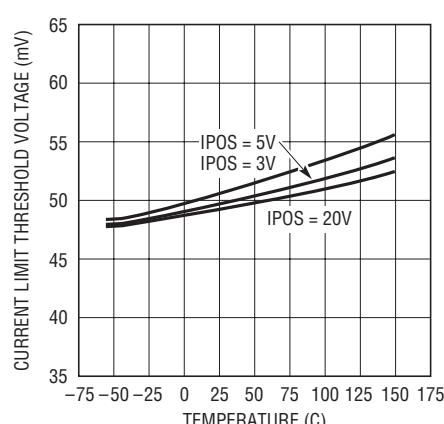

電流制限スレッショルド電圧と温度

1575/77 G16

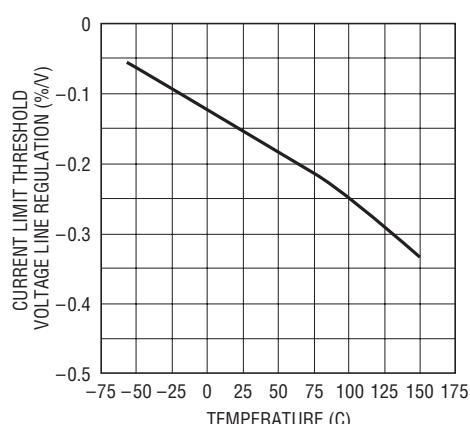

電流制限スレッショルド電圧ライン・

レギュレーションと温度

1575/77 G17

## 標準的性能特性

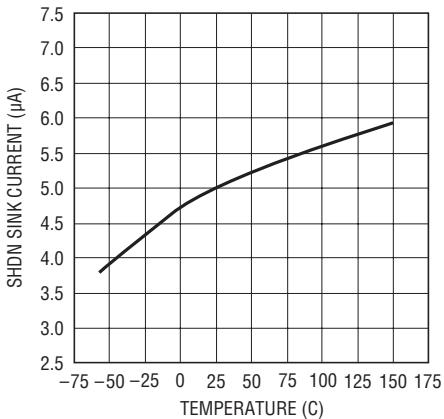

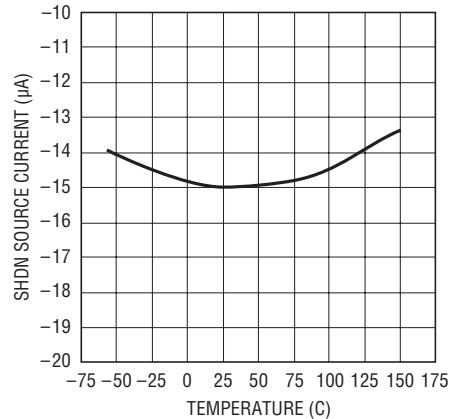

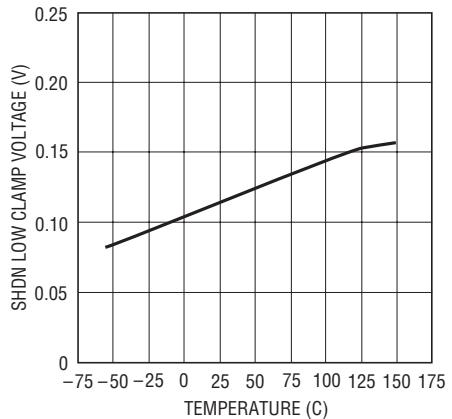

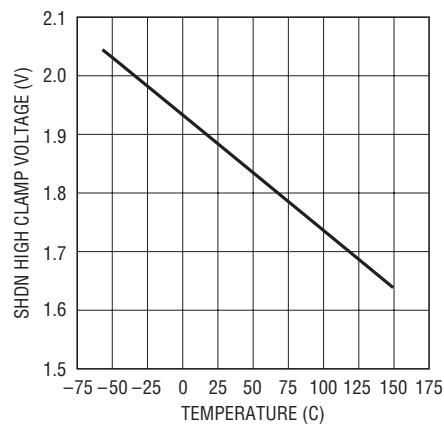

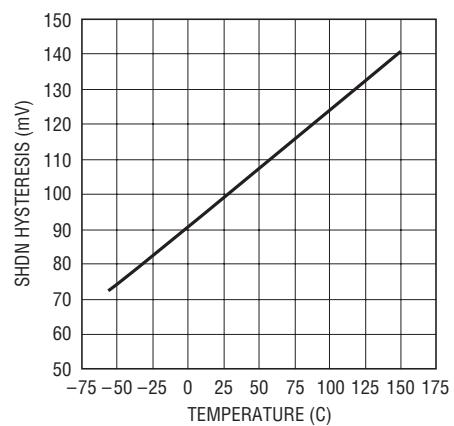

SHDNシンク電流と温度

SHDNソース電流と温度

SHDN低クランプ電圧と温度

SHDN高クランプ電圧と温度

SHDNヒステリシスと温度

## ピン機能

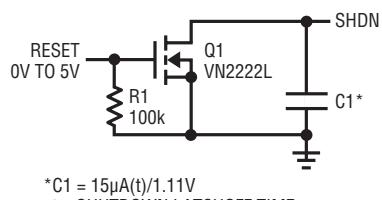

**SHDN(ピン1)**:これはゲート・ドライブ・ラッチオフ機能を提供する多機能シャットダウン・ピンです。電流制限が起動されたときにターンオンし、SHDNと直列にGNDに配置されたコンデンサを充電し、電流制限タイムアウト機能を実行する $15\mu A$ の電流源です。このピンは $V_{REF}$ (1.21V)を基準にするコンパレータへの入力でもあります。このピンを $V_{REF}$ 以上にプルアップすると、コンパレータは外部MOSFETへのゲート・ドライブをオフにラッチします。コンパレータは標準100mVのヒステリシスを有し、シャットダウン・ピンを“L”にプルダウンすると、ラッチオフ機能をリセットすることができます。このピンはさまざまな抵抗分割回路からドライブすることにより、過電圧保護またはサーマル・シャットダウン保護を提供します。

**$V_{IN}$ (ピン2)**:これは内部回路の大部分に電力を供給し、外部NチャネルMOSFETに十分なゲート・ドライブ電圧を供給するこのICのための入力電源です。標準電源電圧は12Vで消費電流は12.5mAです。最大動作 $V_{IN}$ 電圧は20V、最小動作 $V_{IN}$ 電圧は最大 $I_{OUT}+1.6V$ (ワーストケースの $V_{IN}$ からGATEまでの出力振幅)におけるMOSFETの( $V_{OUT}+V_{GS}$ )によって設定されます。

**GND(ピン3)**:アナログ・グランド。このピンは内部1.21Vリファレンスの負センス端子でもあります。最良の安定化および性能を実現するには、GNDに終端される外部帰還分割器ネットワークとGNDに終端される周波数補償部品を、このピンに直接接続してください。

**FB(ピン4)**:LT1575を可変電圧レギュレータとして使用する場合の誤差アンプの反転入力です。非反転入力は内部1.21Vリファレンスに接続されます。このピンの入力バイアス電流は標準 $0.6\mu A$ で、ピンから流れ出します。このピンは通常、出力電圧を設定するために抵抗分割器ネットワークに接続されます。最良の安定化性能を実現するには、外部抵抗分割器のトップを出力電圧に直接接続してください。

**OUT(ピン4)**:これはLT1575を固定電圧で使用する場合の誤差アンプの反転入力です。固定電圧部品は、出力電圧を設定するための高精度抵抗分割器ネットワークを内蔵しています。標準抵抗分割器電流は1mAでピンに流れ込みます。最良の安定化性能を実現するには、このピンを出力電圧に直接接続してください。

**COMP(ピン5)**:これは誤差アンプのハイ・インピーダンス利得ノードで、外部周波数補償に使用されます。誤差アンプの相互コンダクタンスは15ミリモー、開ループ電圧利得は標準84dBです。周波数補償は一般に、接地された直列RCネットワークで実行します。

**ゲート(ピン6)**:これは、最大5000pFまでの「実効」ゲート容量のNチャネルMOSFETをドライブする誤差アンプの出力です。標準開ループ出力インピーダンスは $2\Omega$ です。低入力容量のMOSFET(< 1500pF)を使用するときは、 $2\Omega \sim 10\Omega$ の小さなゲート抵抗によって、MOSFETゲートのリード・インダクタンスと入力容量に起因する、LC共振による高周波数リンギングが減衰されます。GATEピンは、出力負荷過渡電流に応答してNチャネルMOSFETのゲートをスルーライングするときに、数百nsの間に最大50mAを供給します。

**INEG(ピン7)**:これは電流制限アンプの負センス端子です。小さなセンス抵抗が外部MOSFETのドレインと直列に接続され、さらにIPOSピンとINEGのピン間に接続されています。50mVのスレッショルド電圧とセンス抵抗値によって、電流制限レベルを設定します。電流センス抵抗は低い値のシャントにするか、またはPCボード・トレースの一部を利用して作成することができます。電流制限アンプを使用しない場合は、INEGピンをIPOSに接続して電流制限を無効にしてください。別の方針はINEGピンを接地することです。この処置によって電流制限アンプがディスエーブルされ、GATEピンが $V_{IN}$ レールまで振幅する場合、追加内部回路がSHDNピンのタイマ回路を起動します。このオプションによって、ユーザに「センスレス」電流制限機能を提供します。

**IPOS(ピン8)**:これは電流制限アンプの正センス端子です。このピンを出力電圧が安定化されるメイン入力電圧に直接接続してください。標準入力電圧は5Vロジック電源です。このピンは外部MOSFETの入出力差動電圧をモニタする、固定電圧バージョンのコンパレータへの入力でもあります。この差動電圧が0.5V未満の場合、GATEが $V_{IN}$ レールであってもSHDNタイマは始動できません。これにより、上昇率が非常に低い場合でも入力電圧が上昇すると、レギュレータは通常どおり始動することができます。

# LT1575/LT1577

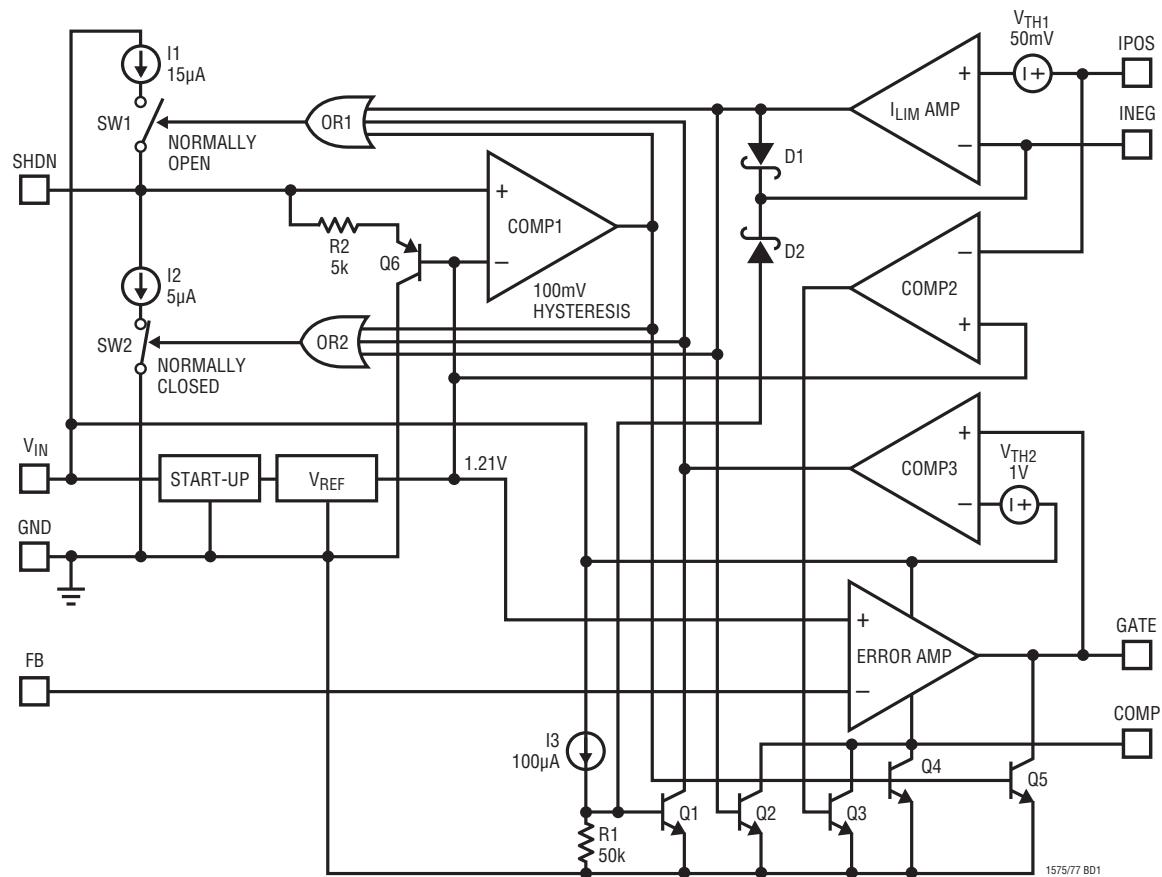

## ブロック図

LT1575可変電圧

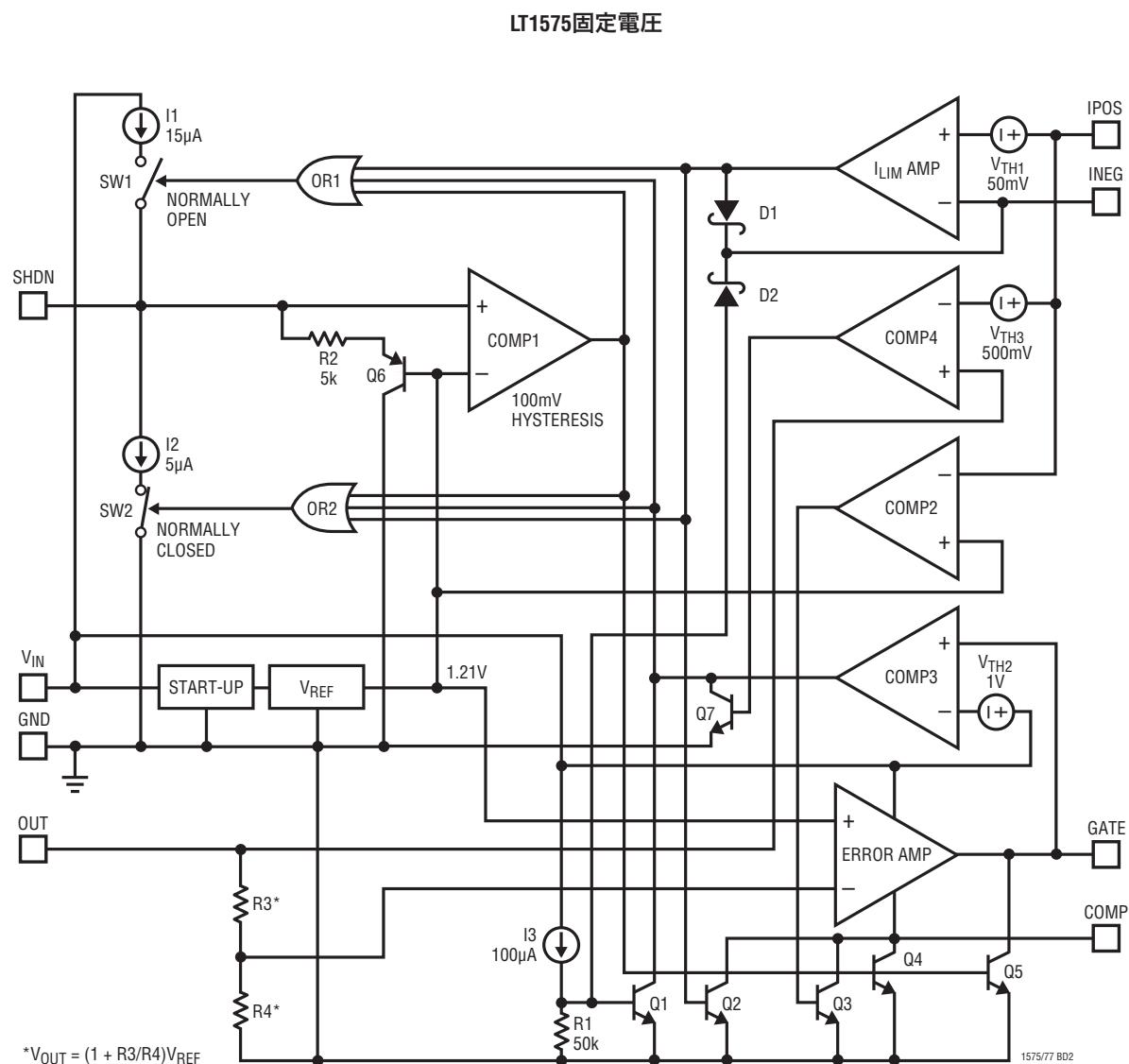

## ブロック図

## アプリケーション情報

### はじめに

現世代のマイクロプロセッサでは、プロセッサ・コアに電力を供給する電源に厳密な条件が課されています。これらのマイクロプロセッサは数十nsで、ほぼゼロから数Aまで負荷電流が増加します。最小±100mVの出力電圧許容差には、仕様の一部として過渡応答が含まれています。マイクロプロセッサには、コアおよびI/O回路が動作するのに单一出力電圧しか必要なものがあります。他のより高性能のプロセッサでは、プロセッサ・コアとI/O回路のために独立した電源電圧が必要です。これらの人間の要求条件を満たすには、非常に精密かつ高速なレギュレータ回路が必要になります。

従来の解決法では、モノリシック3端子リニア・レギュレータ、低コストの制御回路でドライブされるPNPトランジスタ、および単純なバック・コンバータ・スイッチング・レギュレータを使用していました。3端子レギュレータは高度に集積化されており、PNPドライブ・レギュレータは非常に低いドロップアウト性能を実現し、スイッチング・レギュレータは高い電気的効率を実現しています。

しかし、これらの解決法で明らかになる共通の特徴は、過渡応答に何マイクロ秒も要することです。このため、CPUの周囲に複数のコンデンサを使用して、数百μFの非常に低いESRバルク容量を必要とするレギュレータ出力デカップリング・コンデンサ回路が必要になります。ここで必要なバルク容量は、最初の数百ns間の過渡負荷応答を処理するセラミック・デカップリング・コンデンサ・ネットワークとともに、マイクロプロセッサ・クロック周波数のノイズ余裕度を提供します。すべてのコンデンサの総コストは、電源コスト全体のかなりの部分を占めます。

シングル/デュアル・コントローラICのLT1575/LT1577ファミリーは、外部NチャネルMOSFETをソース・フォロワとしてドライブし、極端に低いドロップアウト性能を実現可能なユニークで使いやすい超高速過渡応答レギュレータです。これらの回路は、最新かつ最もニーズの多いマイクロプロセッサ・アプリケーションで、高価なタンタルまたはバルク電解コンデンサをまったくなくすことによって、優れたレギュレータ・バンド幅と過渡負荷性能を達成します。例えば200MHz Pentiumプロセッサは、推奨される24個の1μFセラミック・コンデンサだけで動作します。ユーザは、追加バルク容量がまったく不要になるため、コストが大幅に削減され直接恩恵を享受できます。さらに挿

入コスト、購買/在庫管理コスト、およびボード・スペースを節約できることも容易に理解できます。

精密に調整された可変および固定出力電圧バージョンは、要求されるどのマイクロプロセッサ用電源電圧にも対応します。NチャネルMOSFET  $R_{DS(ON)}$ を適切に選択すれば、ユーザが設定可能なドロップアウト電圧性能を実現できます。必要な出力コンデンサは、高周波セラミック・デカップリング・コンデンサだけです。このレギュレータ設計は広いバンド幅を提供し、応答に何μsもかかるレギュレータと比べて数百nsの過渡負荷変化に対応します。セラミック・コンデンサ・ネットワークは一般に、個々のマイクロプロセッサの要求条件に応じて、10~24個の1μFコンデンサで構成されています。また、LT1575/LT1577ファミリーは電流制限を内蔵しており、システム・コストを増大させることなく、簡単な外部部品だけで、オン/オフ制御や過電圧保護またはサーマル・シャットダウンを提供しています。

したがって、これらの新しいICのユニークな設計によって、低ドロップアウト電圧、高機能の集積化、高精度性能、超高速過渡応答を達成しているだけでなく、高速負荷過渡アプリケーションで必要な出力容量についても大幅なコストダウンを実現します。入出力差電圧がより低いアプリケーションが主流になるに伴って、LT1575を使用したソリューションによって、スイッチング・レギュレータと同等な効率性能をかなりの低コストで達成できます。

新しいLT1575/LT1577低ドロップアウト・レギュレータ・コントローラICファミリーは、システム設計者が最新世代のマザーボードやマイクロプロセッサに求める一段高いレベルの性能を実現しています。これらの回路で得られる多様性と利点によって、今日の高性能マイクロプロセッサ用電源のニーズに容易に応えることができます。

### ブロック図の動作説明

ブロック図の主要要素は単純なフィードバック制御ループで構成され、ブロック図の補助要素は複数の保護機能で構成されています。LT1575のブロック図を調べると、起動回路が精密に調整されたバンドギャップ・リファレンスを含め、ICを制御しながら起動し、すべての内部電流と電圧のバイアスを確立します。

## アプリケーション情報

可変バージョンのリファレンス電圧精度および固定電圧バージョンの出力電圧精度は、室温で $\pm 0.6\%$ 、全動作温度範囲で $\pm 1\%$ として規定されています。これはLT1575/LT1577ファミリーが、出力電圧許容差が非常に厳しく規定されたレギュレータ・グループのひとつであることを示しています。正確な1.21Vリファレンスは、帰還制御ループ内のメイン誤差アンプの非反転入力に接続されます。

誤差アンプは、15ミリモードの相互コンダクタンスを持つ1つの高利得 $g_m$ 段で構成されます。反転端子は、可変電圧バージョンのFBピン、固定電圧バージョンのOUTピンとして引き出されています。 $g_m$ 段は、COMPピンで差動からシングルエンドへの変換を提供します。 $g_m$ 段の出力インピーダンスは約 $1M\Omega$ なので、84dBの標準DC誤差アンプの開ループ利得は、標準75MHzの非補償ユニティゲイン・クロスオーバ周波数で実現されます。帰還ループの総合DC利得は、誤差アンプが提供する利得よりもDC出力電圧を設定する抵抗分割器ネットワークの減衰係数分だけ減少することに注意してください。これらの減衰係数は、ユーザが簡単に計算できるように「電気的特性」表に記載されるLT1575固定電圧バージョンの「開ループ電圧利得」の仕様にすでに加味されています。誤差アンプのハイ・インピーダンス利得ノードに外部からアクセスできるため、接地した直列RCネットワークによって標準ループ補償が可能です。

高速、高電流の出力段はCOMPノードをバッファし、負荷過渡性能をほとんど変化させることなく、最大5000pFの「実効」MOSFETゲート容量をドライブします。出力段は負荷過渡電流に応答して、MOSFETゲートをスルーライングするときに最大50mAを供給します。GATEピンの標準出力インピーダンスは標準で $2\Omega$ です。これにより、誤差アンプの出力インピーダンスとMOSFET入力容量がループ・クロスオーバ周波数をはるかに超えるため、ポールが押し出されます。使用するMOSFETの容量が1500pF未満の場合、 $2\Omega \sim 10\Omega$ の小さい値の直列ゲート抵抗を追加する必要があります。このゲート抵抗は、MOSFETゲートのリード・インダクタンスと入力容量によって生じるLC共振の減衰を促進します。さらに、この抵抗とMOSFET入力容量によって形成されるポールを微調整することができます。

MOSFETパス・トランジスタはソース・フォロワとして接続されているので、個別PNPトランジスタをパス・デバイスとして採用する設計と比べて、パワー・パス利得の予測がはるかに容易です。これはPNP Betaの製造バラツキが大きいためです。MOSFETは非常に高速なデバイスで、安定した広いバンド幅をもつ制御ループを実現するのに役立ちます。フォロワ・トポロジーによる別の利点は、本質的にライン除去が良好であることです。入力電源の乱れが出力に伝達されません。レギュレータ回路の帰還ループは、可変電圧バージョンのFBピン、および固定電圧バージョンのOUTピンに誤差信号を供給して完結します。いずれの場合も、抵抗分割器ネットワークは出力電圧を検知して安定化されたDCバイアス・ポイントを設定します。一般に、LT1575レギュレータ帰還ループでは良好な位相および利得のマージンを維持しながら、約1MHz単位のループ・クロスオーバ周波数を許容しています。このユニティゲイン周波数は、マイクロプロセッサ用電源のために現在採用されているレギュレータ・ソリューションのバンド幅の20~30倍です。この大幅な性能の向上は、バルク出力容量をすべてなくすことができます。

機能性と強固さを高める他の独自の機能がいくつか設計に組み込まれています。これらの機能はブロック図の他の部分に記載されています。

ハイサイド・センス電流制限アンプは、レギュレータに対してアクティブな電流制限を提供します。電流制限アンプは、外部MOSFETのドレインに直列に接続された低い値の外部シャント抵抗を使用します。この抵抗は個別シャント抵抗にするか、または「無償の」PCボード・トレースのケルビンセンス部を利用して作成することができます。負荷電流はすべてMOSFETのドレインを流れ、したがってセンス抵抗を流れることになります。このトポロジーでハイサイド電流センスを使用する利点は、MOSFETの利得とメイン帰還ループの利得が影響されないことです。センス抵抗には $I_{OUT}(R_{SENSE})$ の電圧が生じます。電流制限アンプの50mVスレッショルド電圧は、センス抵抗の消費電力、ドロップアウト電圧の影響、およびノイズ余裕度の間で妥協を図った結果です。電流制限は、センス抵抗電圧が50mVスレッショルドになるとアクティブになります。

## アプリケーション情報

電流制限がアクティブになると、次の2つの事象が起こります：まず、電流制限アンプがブロック図のQ2をドライブし、メイン誤差アンプのCOMPノードの正振幅を、50mV/RSENSEの出力負荷電流を供給する電圧にクランプします。この動作は出力電流過負荷が存在する限り継続します。もう1つは、タイマ回路がSHDNピンでアクティブになります。このピンは通常、グランドから $\approx 100\text{mV}$ 高い電圧に制限する5 $\mu\text{A}$ のアクティブ・プルダウンによって“L”に保持されます。電流制限がアクティブになると、5 $\mu\text{A}$ のプルダウンがターン・オフし、15 $\mu\text{A}$ のプルアップ電流源がターン・オンします。接地したSHDNピンにコンデンサを直列に接続すると、時間をプログラム可能なランプ電圧を生成します。

SHDNピンはCOMP1の正入力でもあります。負入力は内部1.21Vリファレンスに接続されます。SHDNピンがVREFを超えて上昇すると、コンパレータはQ4とQ5をドライブします。この動作によってCOMPとGATEのピンが“L”に引き下げられ、外部MOSFETドライブをオフにラッチします。これによりMOSFET消費電力がゼロに低減されます。ラッチオフ状態になるまでの時間間隔は、標準で $C_{SHUT}(1.11\text{V})/15\mu\text{A}$ です。例えば、SHDNピンに1 $\mu\text{F}$ のコンデンサがあるとランプ時間は74msになります。つまりこの独特な回路ブロックは、予め定義された時間が経過した後でレギュレータ・ドライブをラッチオフする電流制限タイムアウト機能を実行します。選択されたタイムアウト期間は、スタートアップおよび安全動作領域を含むシステム要求条件によって決まります。SHDNピンは内部でQ6とR2によって標準1.85Vにクランプされます。SHDNピンに接続されるコンパレータは、ノイズ余裕度を与えるために100mVの標準ヒステリシスを持っています。このヒステリシスは、SHDNピンをサーマル・シャットダウンに使用するときに特に有用です。

負荷電流フォールトがクリアされた後通常動作に復帰するには、次の2つおりの方法によります。1つはシャットダウン・ピン・コンデンサに外部放電経路を用意しながら、標準12VのLT1575電源電圧を一度切って入れ直す方法です。もう1つは、SHDNピンをV<sub>REF</sub>以下に引き下げるアクティブ・リセット回路を設ける方法です。SHDNピンをV<sub>REF</sub>以下に引き下げると、15 $\mu\text{A}$ のプルアップ電流源がターン・オフされ、5 $\mu\text{A}$ のプルダウンが再起動されます。フォールト状態の間にSHDNピンをV<sub>REF</sub>以下に保持した場合、レギュレータは短絡時の電流制限により動作を継続します。この動作には、1V未満の電圧でSHDNピンから15 $\mu\text{A}$ をシンクする能力が必要です。5 $\mu\text{A}$ のプルダウン電流源と15 $\mu\text{A}$ のプルアップ電流源は、外部抵抗分割器ネットワークがSHDNピンをドライブして過電圧保護を提

供したり、ドライバ・ネットワークのサーミスタを使用してサーマル・シャットダウンを提供できるだけの低い値に設計されています。これらの機能をまとめてダイオードでORするのは簡単で、1本のピンで複数の機能を提供します。

電流制限アンプを使用しない場合には、2つの選択肢があります。最も簡素な方法は、INEGピンを直接IPOSピンに接続することです。この処置によって電流制限が無効になり、周辺回路のない最も単純な回路を提供します。極端に低いドロップアウト電圧を達成しなければならない電流制限アンプを使用しないアプリケーションでは、50mVスレッショルド電圧は許容されません。

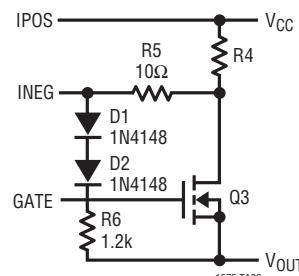

しかし可能なもう1つの方法では、ユーザは外部センスを行わずに短絡保護を提供できます。この手法はINEGピンを接地してアクティブにします。この処置によって、ショットキー・ダイオードD1が電流制限アンプの出力をクランプし、Q2がCOMPノードをプルダウンするのを防止するため、電流制限アンプがディスエーブルされます。さらに、ショットキー・ダイオードD2がプルダウン・トランジスタQ1をターン・オフします。Q1は通常オンの状態であり、内部コンパレータCOMP3の出力を“L”に保持します。これでこのコンパレータ回路がインエーブルされ、GATEピンをモニタして正レールでの飽和を検出します。飽和状態が検出されると、COMP3はシャットダウン・タイマを起動します。一度タイムアウト周期が発生すると出力はシャットダウンされ、ラッチオフされます。ラッチをリセットする動作は同じです。この手法では、タイムアウト期間中にFET電流が制限されないので注意してください。出力電流は、入力電源と入出力インピーダンスによってのみ制限されます。この動作モードでタイマを短い周期に設定すると、外部MOSFETはSOA(安全動作領域)の境界内で維持され、MOSFETの温度上昇が抑えられます。

LT1575に組み込まれている独自の回路設計によって、電源シーケンスに関する問題がすべて軽減されます。標準LT1575アプリケーションには2つの別々の電源電圧から入力があるため、電源シーケンスの問題は重要です。標準12V V<sub>IN</sub>電源電圧のランプアップが遅い場合、MOSFETゲート・ドライブが不十分になるため出力電圧が現れません。V<sub>IN</sub>電源電圧は存在するがIPOSピンに接続された標準5V電源電圧がまだ立ち上がりっていない場合、帰還ループはGATEピンを正V<sub>IN</sub>レールにドライブしようとします。この結果、5V電源が上昇し始めるとすぐに、非常に大きな電流スパイクが生じます。しかし、IPOS電源電圧をモニタする低電圧ロックアウト回路COMP2がQ3

## アプリケーション情報

をオンに保持し、IPOS電圧が内部1.21リファレンス電圧より高くなるまで、COMPピンを“L”に引き下げます。次に低電圧ロックアウト回路がCOMPピンを円滑に解放し、出力電圧が入力電源電圧からドロップアウトした形で立ち上がるようになります。LT1575帰還ループの速度から得られる別の利点は、適切に補償されたシステムでは、実質上ターンオン・オーバーシュートが存在しないということです。

LT1575固定電圧バージョンには別の回路機能が組み込まれています。レギュレータ回路は立ち上がると、出力コンデンサを充電しなければなりません。出力電圧は通常、出力電圧がドロップアウト電圧によって決まる入出力電圧差で上昇しながら入力電圧電源に追従します。帰還ループが安定化状態になるまで、回路動作によってGATEピンは正V<sub>IN</sub>レールになり、電流制限アンプがディスエーブルされている場合は、SHDNピンでタイマが起動されます。しかし、内部コンパレータCOMP4は入出力電圧差をモニタします。電圧差が500mVを超えるまで、このコンパレータはシャットダウン・タイマが始動するのを許しません。これにより、通常の起動が行われます。

LT1575固定電圧バージョンを使用するまでの最終的な利点がもう1つあります。今日の最高性能マイクロプロセッサでは、現在入手可能な可変電圧レギュレータに高精度抵抗を使用

して、初期設定点の許容差に適合させなければなりません。LT1575固定電圧バージョンは、高精度抵抗分割器をICに内蔵しながら、全温度範囲にわたって1%の出力電圧許容差を維持しています。したがって、LT1575固定電圧バージョンでは高精度抵抗がまったく不要で、これによりさらにシステム・コストを節約できます。

## アプリケーション・サポート

リニアテクノロジーは、システム設計者にマイクロプロセッサ用電源ソリューションを理解し、設計、評価してもらうために、多大な時間と人材および技術力を投資しています。プロセッサの速度と能力が向上するにつれて、マザーボード設計者が電源にかける労力も増加します。アプリケーション・ノート69「LT1575リニア・レギュレータ・コントローラの使用法」は、この新しいICファミリのための有用なガイドとして利用できるように記述されています。このアプリケーション・ノートでは、LT1575/LT1577ファミリのPCボード・レイアウト、MOSFETの選択基準、外部部品の選択（コンデンサ）、およびループ補償などを扱っています。リニアテクノロジー社では、顧客と一緒にマイクロプロセッサ用電源ソリューションに関する意見交換、設計、評価、および最適化を行う機会を歓迎しています。詳細についてはお問い合わせください。

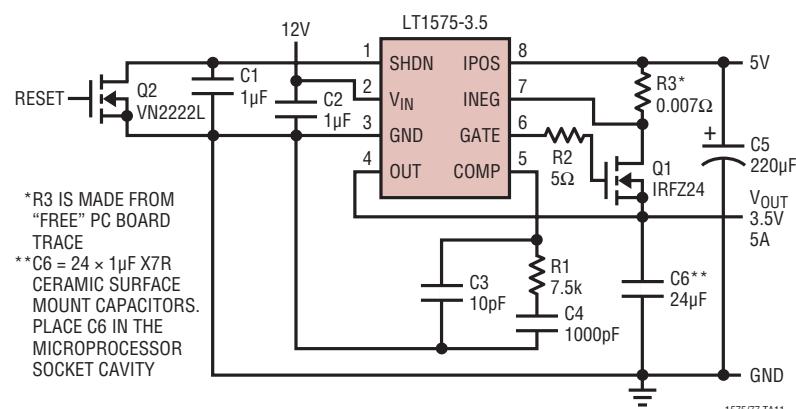

## 標準的応用例

電流制限とタイマ・ラッチオフ付きの5Vから3.5Vの

UltraFast過渡応答、低ドロップアウト・レギュレータ

# LT1575/LT1577

## 標準的応用例

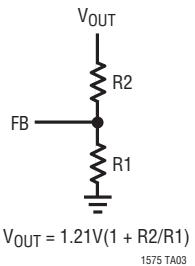

### 可変LT1575の出力電圧の設定

### 「センスレス」電流制限の使用法

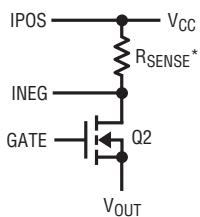

### 電流制限の設定

\* $I_{LIM} = 50mV/R_{SENSE}$

$R_{SENSE} =$ DISCRETE SHUNT RESISTOR OR

$R_{SENSE} =$ KELVIN-SENSED PC BOARD TRACE

ACTIVATING CURRENT LIMIT ALSO ACTIVATES

THE SHDN PIN TIMER

1575 TA05

### フォルドバック制限による電流制限の設定

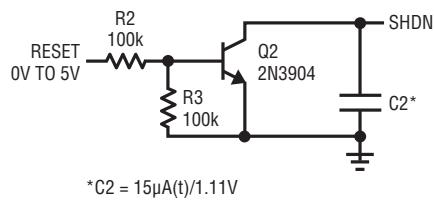

### リセットによるシャットダウン・タイムアウト

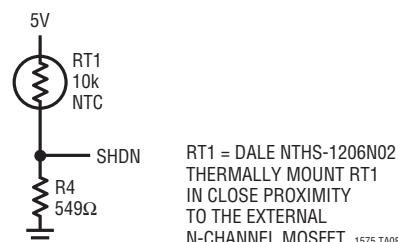

### 基本的なサーマル・シャットダウン

### リセットによるシャットダウン・タイムアウト

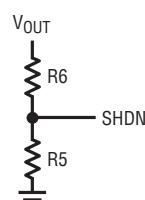

### 過電圧保護

$$V_{OUT(uth)} = 1.21(R_6/R_5) + 5\mu A(R_6)$$

$$V_{OUT(lth)} = 1.11(R_6/R_5) - 15\mu A(R_6)$$

1575f

## アプリケーション情報

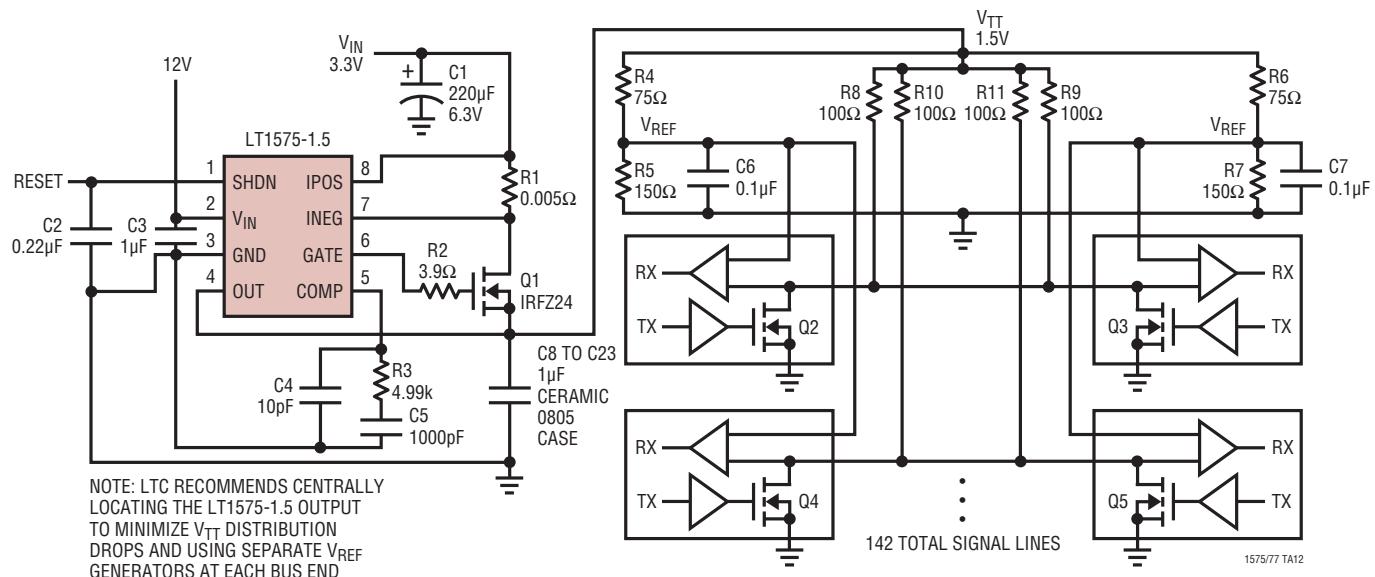

## Pentium® IIプロセッサGTL+電源

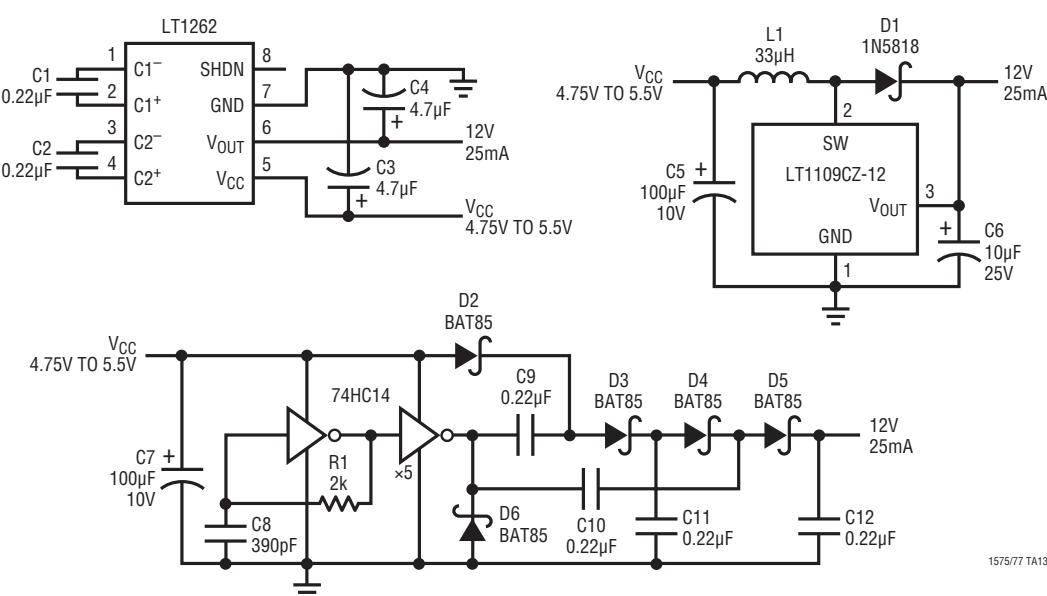

## 5V電源から12Vのゲート・ドライブを生成

PentiumはIntel Corporationの登録商標です。

1575f

# LT1575/LT1577

## 標準的応用例

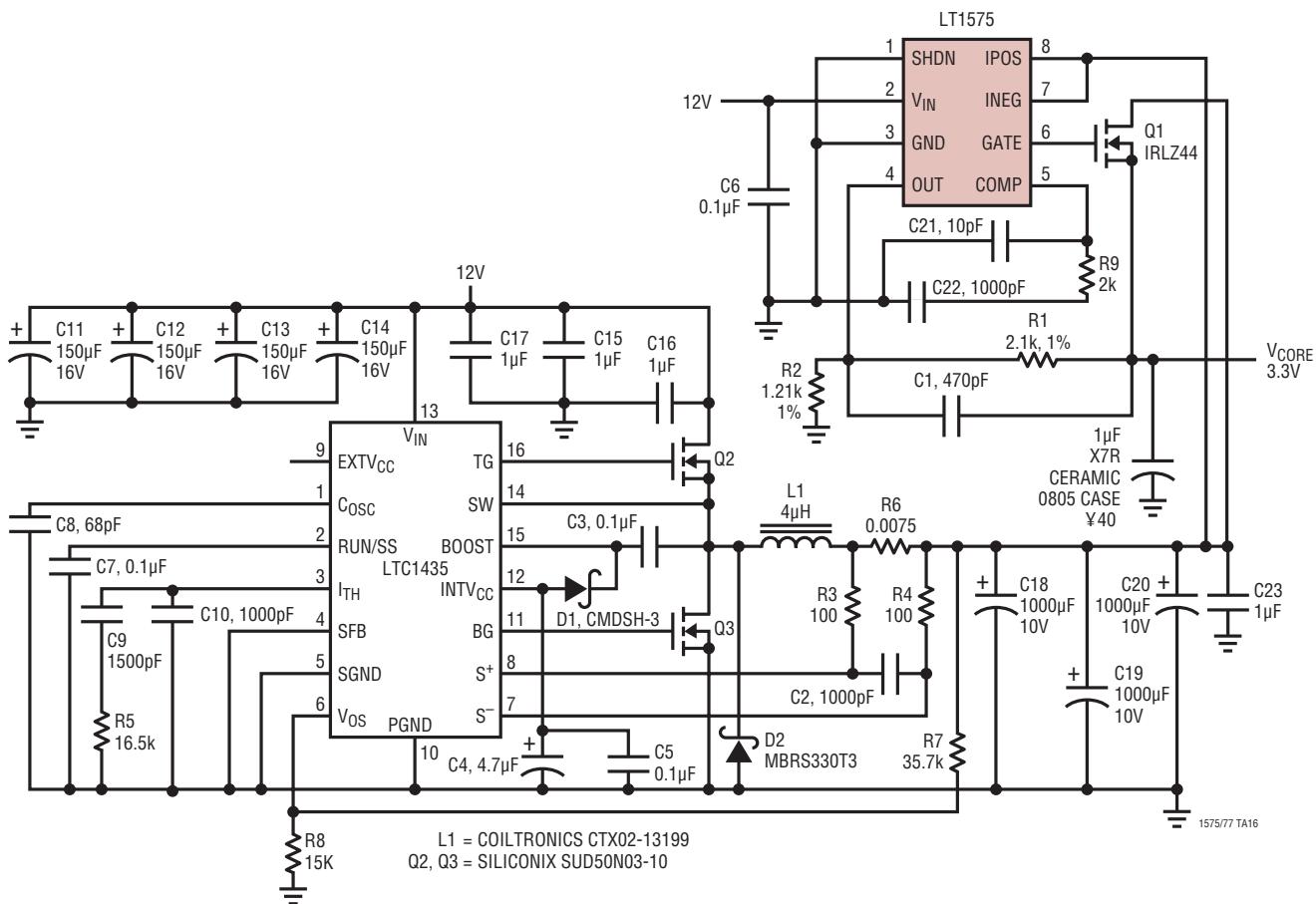

12Vから3.3V/9A(14Aピーク)のハイブリッド・レギュレータ

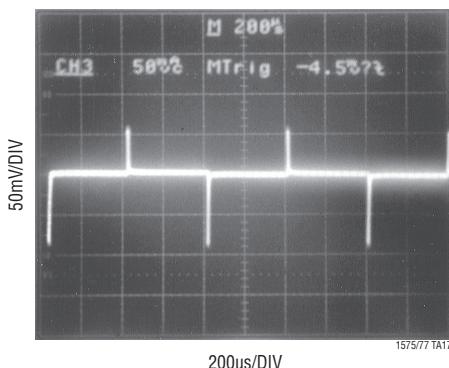

10Aの負荷ステップに対する過渡応答

## 標準的応用例

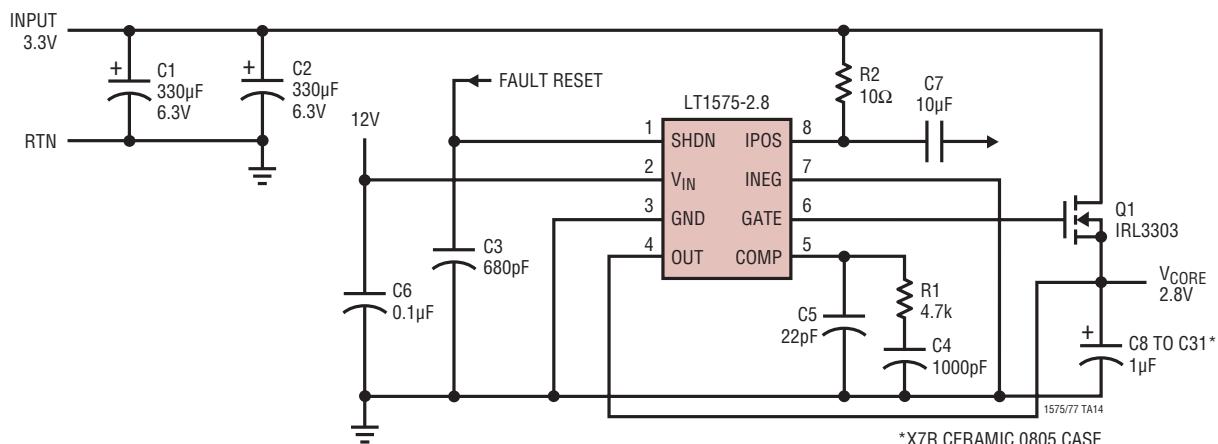

電流制限センスなし、タイマ・ラッチオフ付き3.3Vから2.8V±100mV/5.7A

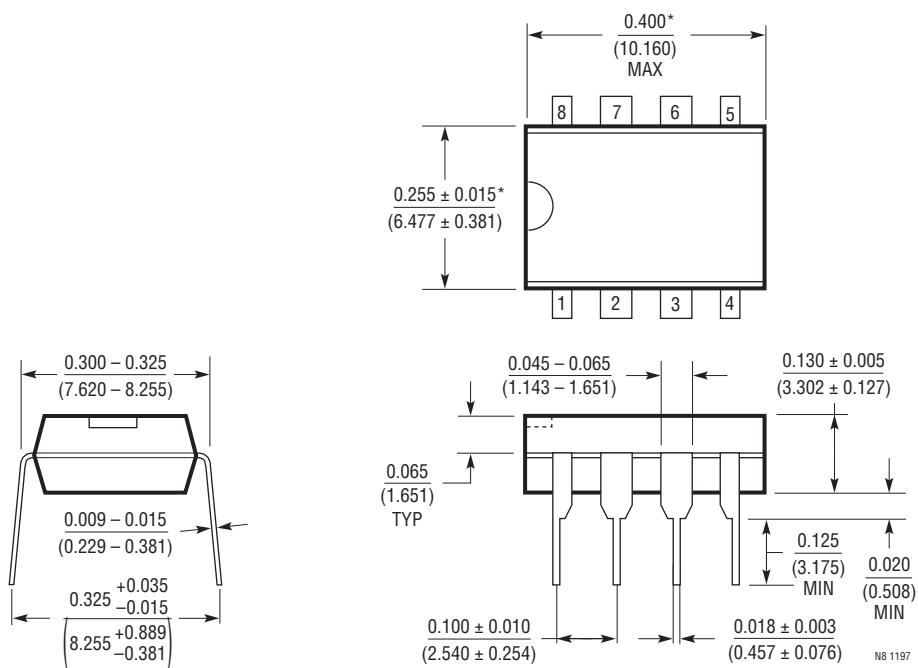

## パッケージ 注記がない限り、寸法はインチ(mm)

N8パッケージ

8ピンPDIP(細型0.300)

(LTC DWG # 05-08-1510)

\*これらの寸法にはモールドのバリまたは突出部を含まない

モールドのバリまたは突出部は0.010インチ(0.254mm)を超えないこと

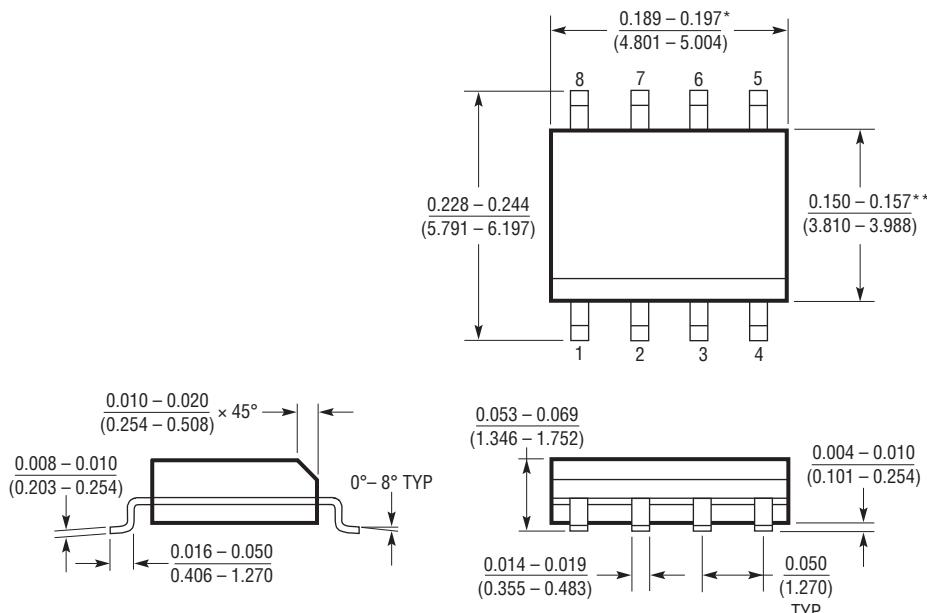

# LT1575/LT1577

パッケージ 注記がない限り、寸法はインチ(mm)

S8/パッケージ

8ピン・プラスチック・スマール・アウトライン(細型0.150)

(LTC DWG # 05-08-1610)

\*寸法にはモールドのバリは含まない

モールドのバリは各サイドで0.006インチ(0.152mm)を超えないこと

\*\*寸法にはリード間のバリを含まない

リード間のバリは各サイドで0.010インチ(0.254mm)を超えないこと

S08 0996

1575f

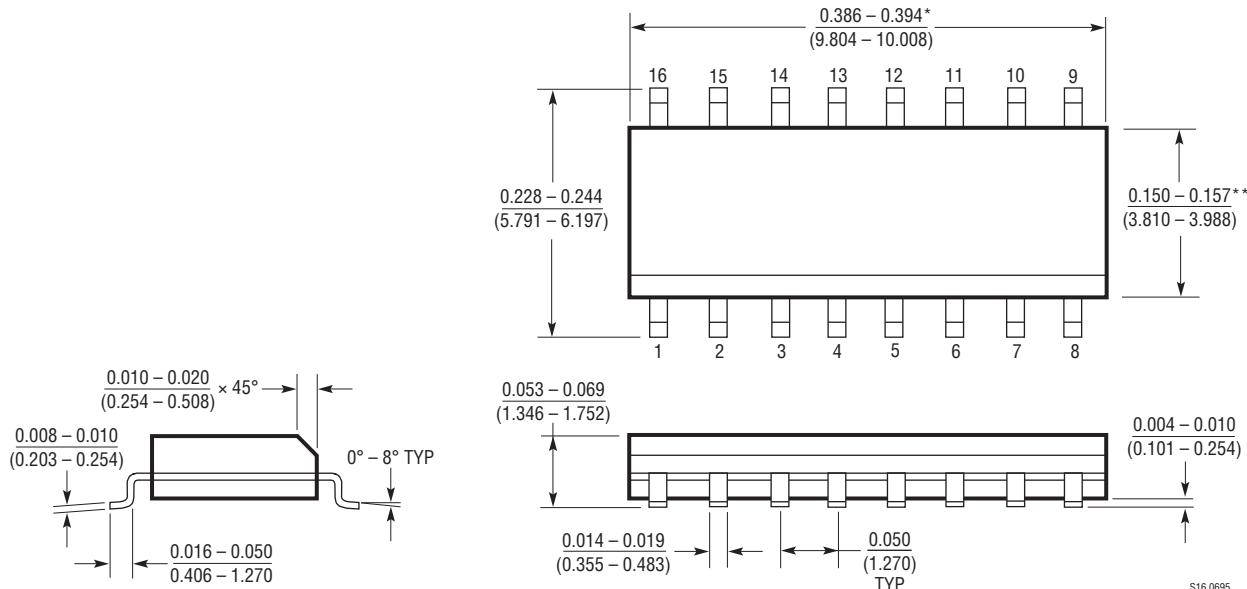

## パッケージ 注記がない限り、寸法はインチ(mm)

Sパッケージ

16ピン・プラスチック・スマール・アウトライン(細型0.150)

(LTC DWG # 05-08-1610)

\*寸法にはモールドのバリは含まない

モールドのバリは各サイドで0.006インチ(0.152mm)を超えないこと

\*\*寸法にはリード間のバリを含まない

リード間のバリは各サイドで0.010インチ(0.254mm)を超えないこと

# LT1575/LT1577

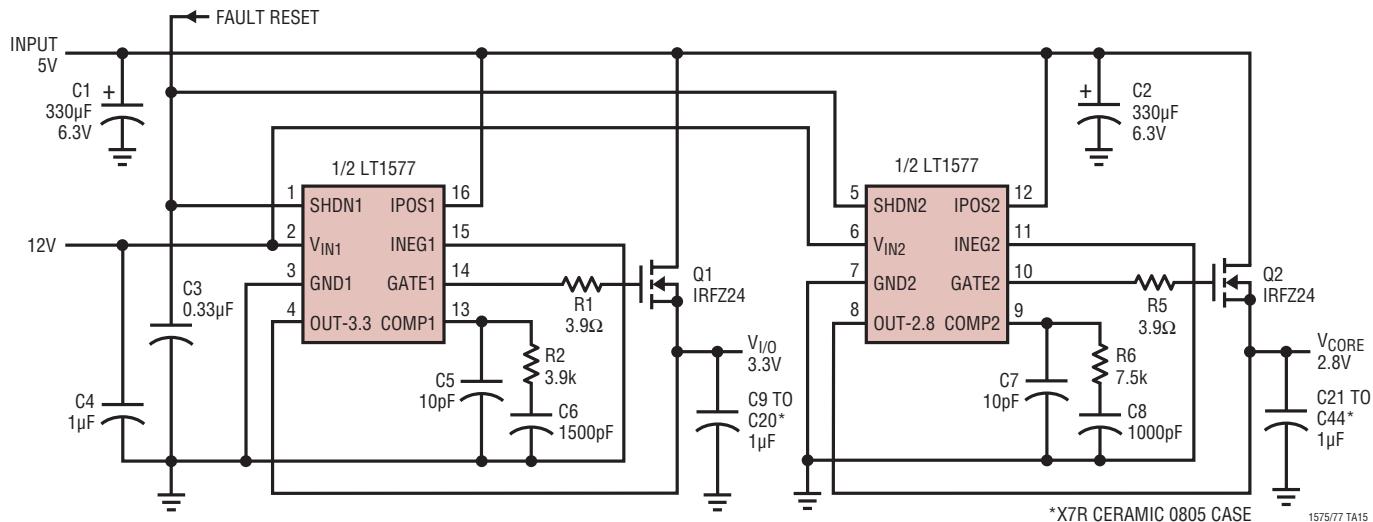

## 標準的応用例

LT1577スプリット・プレーン・システム

## 関連製品

| 製品番号       | 説明                             | 注釈                                        |

|------------|--------------------------------|-------------------------------------------|

| LTC1266    | 電流モード昇圧/降圧スイッチング・レギュレータ・コントローラ | 同期式、NまたはPチャネルFET、コンパレータ/バッテリ電圧低下検知器       |

| LTC1392    | マイクロパワー温度電源および差動電圧モニタ          | 温度からビット変換の制御                              |

| LTC1430    | 高電力降圧スイッチング・レギュレータ・コントローラ      | 電圧モード、5Vから3.xxV(10A以上)                    |

| LTC1435    | 高効率低ノイズ同期式降圧スイッチング・レギュレータ      | 広い入力電圧範囲の電流モード                            |

| LTC1553    | デジタル制御の同期整流スイッチング・レギュレータコントローラ | Pentium IIプロセッサ用コントローラ、5Vまたは12V主電源からの降圧   |

| LTC1553L   | デジタル制御の同期整流スイッチング・レギュレータコントローラ | Pentium IIプロセッサ用コントローラ、5V主電源からの降圧         |

| LT1573     | 低損失レギュレータ・ドライバ                 | 高電力、低損失アプリケーション用低成本PNPトランジスタをドライブ         |

| LT1580     | 7A、低損失レギュレータ                   | 7Aで0.54Vの損失、固定2.5V <sub>OUT</sub> および可変出力 |

| LT1585-1.5 | 固定1.5V 5Aおよび低損失高速応答レギュレータ      | GTL+レギュレータ                                |