# PCIアプリケーション用 高精度トリプル電源モニタ

### 特長

■ 5V、3.3V、可変入力を同時にモニタ ■ 保証スレッショルド精度: ±0.75%

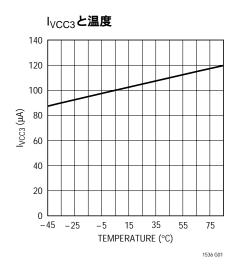

■ 低消費電流:100uA

■ 内部リセット遅延時間: 200ms

■ マニュアル・プッシュボタン・リセット入力

■ アクティブ L "およびアクティブ" H "リセット出力

■ アクティブ L "ソフト」リセット出力

■ 電源グリッチ余裕度

■ V<sub>CC3</sub> ≥ 1VまたはV<sub>CC5</sub> ≥ 1VでResetを保証

■ PCI t<sub>FAII</sub> タイミング仕様Rev 2.1に適合

■ 8ピンSOおよびMSOPパッケージ

## アプリケーション

- PCIベース・システム

- デスクトップ・コンピュータ

- ノートブック・コンピュータ

- インテリジェント計測器

- 携帯用バッテリ駆動機器

- ネットワーク・サーバー

### 概要

LTC®1536は、低消費電力、小型サイズ、高速、高精度の 電源監視が必要な、複数の電源電圧を使用するPCIローカ ル・バス・アプリケーション用に設計されています。

スペックより500mV以上低い3.3Vおよび5V電源の場 合、または5V電源が3.3V電源より低くなる状態に対応 し、LTC1536はPCI t<sub>FAIL</sub>タイミング仕様に適合する非常 に高速な応答時間を達成しています。厳密な0.75%ス レッショルド精度とグリッチ余裕度により、偽トリガな しで信頼性の高いリセット動作を保証します。

RST出力はV<sub>CC5</sub>またはV<sub>CC3</sub>が1Vに低下しても、正しい状 態になることが保証されています。標準消費電流が 100μAと低いため、LTC1536は電力消費に敏感なシステ ムに最適です。

マニュアル・プッシュボタン・リセット入力により、非 常に幅が狭い「ソフト」リセット・パルス(標準100µs)また はパワーオン・リセットと同等の200msリセット・パル スを生成します。SRST出力とRST出力はオープン・ドレ インであり、他のリセット・ソースとOR接続できます。

**▲ブ、LTC、LTはリニアテクノロジー社の登録商標です。**

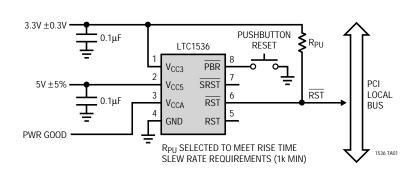

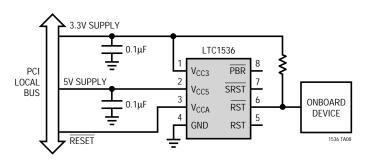

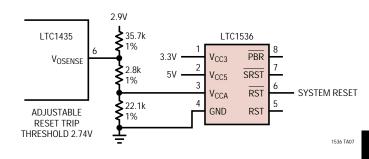

## 標準的応用例

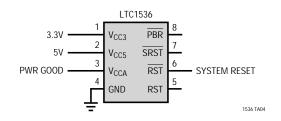

#### マザーボードPCI RSTの生成

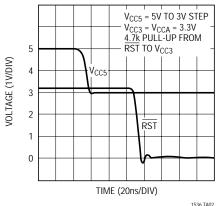

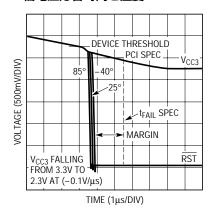

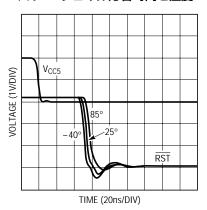

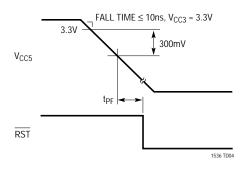

### 5Vが3.3Vから300mV低下した パワー・フェイル波形

1536 TA02

9

## 絶対最大定格

(Note 1, 2)

| 端子電圧                                  |                                  |

|---------------------------------------|----------------------------------|

| V <sub>CC3</sub> , V <sub>CC5</sub> , | V <sub>CCA</sub> 0.3V ~ 7V       |

| RST, SRST.                            | 0.3V ~ 7V                        |

| RST                                   | - 0.3V ~ V <sub>CC3</sub> + 0.3V |

| PBR                                   | 7V ~ 7V                          |

### 動作温度範囲

| LTC1536C 0      | ~ 70  |

|-----------------|-------|

| LTC1536I 40     | ~ 85  |

| 保存温度範囲 65       | ~ 150 |

| リード温度(半田付け、10秒) | 300   |

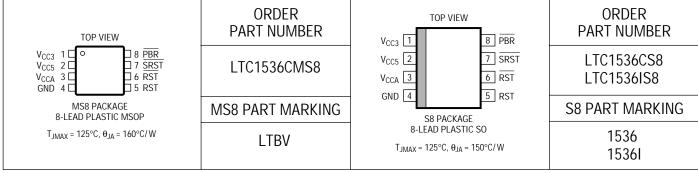

## パッケージ/発注情報

ミリタリ・グレードに関してはお問い合わせください。

## 電気的特性

注記がない限り、V<sub>CC3</sub>=3.3V、V<sub>CC5</sub>=5V、V<sub>CCA</sub>=V<sub>CC3</sub>、T<sub>A</sub>=25

| SYMBOL            | PARAMETER                                              | CONDITIONS                                                                                                     |   | MIN            | TYP            | MAX            | UNITS    |

|-------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|----------|

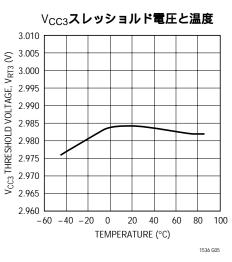

| V <sub>RT3</sub>  | Reset Threshold V <sub>CC3</sub>                       | $0^{\circ}C \le T_{A} \le 70^{\circ}C$<br>- $40^{\circ}C \le T_{A} \le 85^{\circ}C$                            | • | 2.962<br>2.925 | 2.985<br>2.985 | 3.000<br>3.008 | V        |

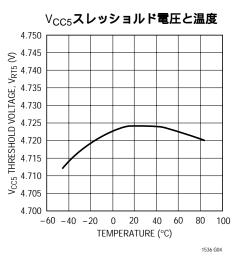

| V <sub>RT5</sub>  | Reset Threshold V <sub>CC5</sub>                       | $0^{\circ}C \le T_{A} \le 70^{\circ}C$<br>- $40^{\circ}C \le T_{A} \le 85^{\circ}C$                            | • | 4.687<br>4.625 | 4.725<br>4.725 | 4.700<br>4.762 | V        |

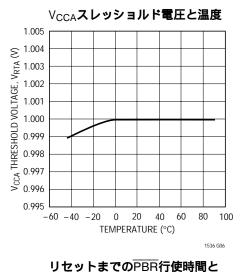

| V <sub>RTA</sub>  | Reset Threshold V <sub>CCA</sub>                       | $0^{\circ}C \le T_{A} \le 70^{\circ}C$<br>- $40^{\circ}C \le T_{A} \le 85^{\circ}C$                            | • | 0.992<br>0.980 | 1.000<br>1.000 | 1.007<br>1.007 | V        |

| $V_{CC}$          | V <sub>CC3</sub> or V <sub>CC5</sub> Operating Voltage | RST in Correct Logic State                                                                                     | • | 1              |                | 7              | V        |

| I <sub>VCC3</sub> | V <sub>CC3</sub> Supply Current                        | PBR = V <sub>CC3</sub>                                                                                         | • |                | 100            | 200            | μА       |

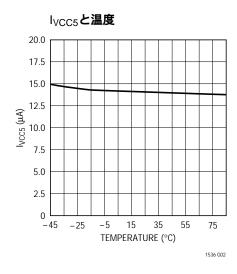

| I <sub>VCC5</sub> | V <sub>CC5</sub> Input Current                         | V <sub>CC5</sub> = 5V                                                                                          | • |                | 10             | 20             | μА       |

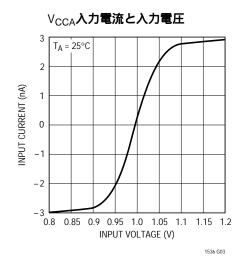

| I <sub>VCCA</sub> | V <sub>CCA</sub> Input Current                         | $V_{CCA} = 1V, 0^{\circ}C \le T_{A} \le 70^{\circ}C$<br>$V_{CCA} = 1V, -40^{\circ}C \le T_{A} \le 85^{\circ}C$ | • | -5<br>-15      | 0<br>0         | 5<br>15        | nA<br>nA |

| t <sub>RST</sub>  | Reset Pulse Width                                      | $\overline{\text{RST}}$ Low with 10kΩ Pull-Up to V <sub>CC3</sub> 0°C to 70°C $-40$ °C to 85°C                 | • | 140<br>140     | 200<br>200     | 280<br>300     | ms<br>ms |

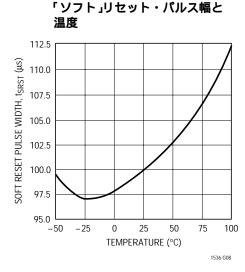

| t <sub>SRST</sub> | Soft Reset Pulse Width                                 | $\overline{\sf SRST}$ Low with 10k $\Omega$ Pull-Up to V <sub>CC3</sub>                                        | • | 50             | 100            | 200            | μs       |

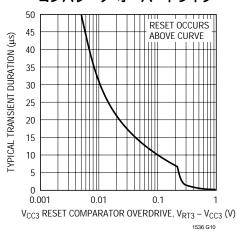

| t <sub>UV</sub>   | V <sub>CC</sub> Undervoltage Detect to RST             | $V_{\text{CC5}}$ , $V_{\text{CC3}}$ or $V_{\text{CCA}}$ Less Than Reset Threshold $V_{\text{RT}}$ by 1%        |   |                | 13             |                | μs       |

## 電気的特性

注記がない限り、 $V_{CC3}$  = 3.3V、 $V_{CC5}$  = 5V、 $V_{CCA}$  =  $V_{CC3}$ 、 $T_A$  = 25

| SYMBOL              | PARAMETER                                                              | CONDITIONS                                                                                                                                |                                                                                                |   | MIN                  | TYP                  | MAX               | UNITS       |

|---------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---|----------------------|----------------------|-------------------|-------------|

| I <sub>PBR</sub>    | PBR Pull-Up Current                                                    | $ \overline{\frac{PBR}{PBR}} = 0V, 0^{\circ}C \le T_{A} \le 70^{\circ}C $ $ \overline{PBR} = 0V, -40^{\circ}C \le T_{A} \le 85^{\circ}C $ |                                                                                                | • | 3 3                  | 7<br>7               | 10<br>15          | μA<br>μA    |

| V <sub>IL</sub>     | PBR, RST Input Low Voltage                                             | 12.1 3.7 .0 32.4 <u>4</u> 30 3                                                                                                            |                                                                                                | • |                      |                      | 0.8               |             |

| V <sub>IH</sub>     | PBR, RST Input High Voltage                                            |                                                                                                                                           |                                                                                                | • | 2                    |                      |                   | V           |

| t <sub>PW</sub>     | PBR Min Pulse Width                                                    |                                                                                                                                           |                                                                                                | • | 40                   |                      |                   | ns          |

| t <sub>DB</sub>     | PBR Debounce                                                           | Deassertion of PBR Input to SRST Output (PBR Pulse Width = 1µs)                                                                           |                                                                                                | • |                      | 20                   | 35                | ms          |

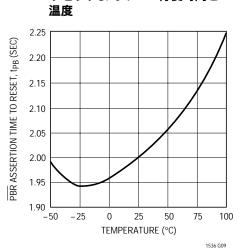

| t <sub>PB</sub>     | PBR Assertion Time for Transition from Soft to Hard Reset Mode         | PBR Held Less Than V <sub>IL</sub> , 0°C to 70°C<br>PBR Held Less Than V <sub>IL</sub> , -40°C to 85°C                                    |                                                                                                | • | 1.4<br>1.4           | 2.0<br>2.0           | 2.8<br>3.0        | S<br>S      |

| $\overline{V_{OL}}$ | RST Output Voltage Low                                                 | I <sub>SINK</sub> = 5mA                                                                                                                   | I <sub>SINK</sub> = 5mA                                                                        |   |                      | 0.15                 | 0.4               | V           |

|                     |                                                                        | $I_{SINK} = 100\mu A$<br>$0^{\circ}C \le T_{A} \le 70^{\circ}C$                                                                           | $V_{CC3} = 1V, V_{CC5} = 0V$ $V_{CC3} = 0V, V_{CC5} = 1V$ $V_{CC3} = 1V, V_{CC5} = 1V$         | • |                      | 0.05<br>0.05<br>0.05 | 0.4<br>0.4<br>0.4 | V<br>V<br>V |

|                     |                                                                        | $I_{SINK} = 100\mu A$<br>$-40^{\circ}C \le T_{A} \le 85^{\circ}C$                                                                         | $V_{CC3} = 1.1V, V_{CC5} = 0V$ $V_{CC3} = 0V, V_{CC5} = 1.1V$ $V_{CC3} = 1.1V, V_{CC5} = 1.1V$ | • |                      | 0.05<br>0.05<br>0.05 | 0.4<br>0.4<br>0.4 | V<br>V<br>V |

|                     | SRST Output Voltage Low                                                | I <sub>SINK</sub> = 2.5mA                                                                                                                 | I <sub>SINK</sub> = 2.5mA                                                                      |   |                      | 0.15                 | 0.4               | V           |

|                     | RST Output Voltage Low                                                 | I <sub>SINK</sub> = 2.5mA                                                                                                                 |                                                                                                | • |                      | 0.15                 | 0.4               | V           |

| V <sub>OH</sub>     | RST Output Voltage High (Note 3)                                       | I <sub>SOURCE</sub> = 1μA                                                                                                                 |                                                                                                | • | V <sub>CC3</sub> – 1 |                      |                   | V           |

|                     | SRST Output Voltage High (Note 3)                                      | I <sub>SOURCE</sub> = 1μA                                                                                                                 |                                                                                                | • | V <sub>CC3</sub> – 1 |                      |                   | V           |

|                     | RST Output Voltage High                                                | I <sub>SOURCE</sub> = 600μA                                                                                                               |                                                                                                | • | V <sub>CC3</sub> – 1 |                      |                   | V           |

| t <sub>PHL</sub>    | Propagation Delay RST to RST High Input to Low Output                  | C <sub>RST</sub> = 20pF                                                                                                                   |                                                                                                |   |                      | 25                   |                   | ns          |

| t <sub>PLH</sub>    | Propagation Delay RST to RST<br>Low Input to High Output               | C <sub>RST</sub> = 20pF                                                                                                                   |                                                                                                |   |                      | 45                   |                   | ns          |

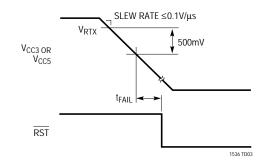

| t <sub>FAIL</sub>   | V <sub>CC5</sub> or V <sub>CC3</sub> 0.5V Undervoltage to RST (Note 4) | V <sub>CC5</sub> Drops Below 4.25V or V <sub>CC3</sub> Drops<br>Below 2.5V (Note 5)                                                       |                                                                                                | • |                      | 150                  | 450               | ns          |

| t <sub>PF</sub>     | V <sub>CC5</sub> < (V <sub>CC3</sub> – 300mV) RST (Note 4)             | V <sub>CC5</sub> Drops Below V <sub>CC3</sub> By 300mV (Note 6)                                                                           |                                                                                                | • |                      | 50                   | 90                | ns          |

● は全動作温度範囲の規格値を意味する。

Note 1: 絶対最大定格はそれを超えるとデバイスの寿命を損う可能性がある

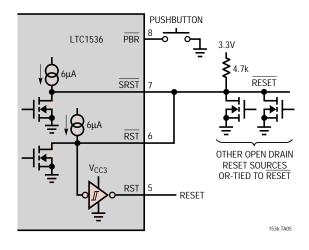

Note 2:電圧値はすべてGNDを基準にする。 Note 3:出力ピンSRSTおよびRSTは、6μAの微弱なV<sub>CC3</sub>への内部プルアップを 備えている。しかし、高速立上り時間が要求される場合は、外部プルアップ抵 抗を使用することができる。

Note  $4:t_{FAIL}$ は、PCIローカル・パス仕様Rev 2.1、Sect. 4.3.2に適合する。 Note 5:-0.1V/ $\mu$ sで立ち下がる $V_{CC3}$ または $V_{CC5}$ 。 測定時間は $V_{RTX}$  - 500mVからRSTが1.5Vになるまで。

Note 6:5Vから3Vまで10ns以下で立ち下がるV<sub>CC5</sub>。 測定時間はV<sub>CC5</sub> = (V<sub>CC3</sub> -300mV)からRSTが1.5Vになるまで。

### 標準的性能特性

リセット・パルス幅と温度 225 220 RESET PULSE WIDTH, t<sub>RST</sub> (ms) 215 210 205 200 195 190 -50 -25 25 50 75 100 TEMPERATURE (°C)

### 9

### 標準的性能特性

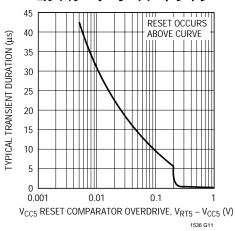

∨<sub>CC3</sub>標準過渡期間とリセット・ コンパレータ・オーパードライブ

∨<sub>CC5</sub>標準過渡期間とリセット・ コンパレータ・オーバードライブ

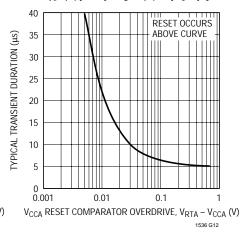

V<sub>CCA</sub>標準過渡期間とリセット・ コンパレータ・オーバードライブ

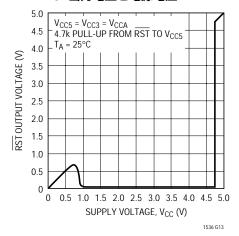

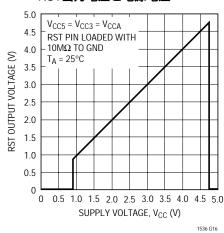

#### RST出力電圧と電源電圧

RST出力電圧と電源電圧

### 低電圧応答時間と温度

パワー・フェイル応答時間と温度

1536 G15

1536 G14

### ピン機能

V<sub>CC3</sub>(ピン1):3.3Vセンス入力兼ICの電源ピン。0.1μF以上のセラミック・コンデンサでグランドにバイパスしてください。

$V_{CCS}$ (ピン2):5Vセンス入力。 $V_{CCS}$ の電圧が $V_{CCS}$ の電圧より大きい場合、RST出力FETのゲート・ドライブとして使用されます。

$V_{CCA}$ (ピン3): 1Vセンス、高インピーダンス入力。スレッショルドが1Vのロジック入力として使用できます。未使用の場合は、 $V_{CC3}$ または $V_{CC5}$ に接続しておくことができます。

GND(ピン4):グランド。

RST(ピン5): リセット・ロジック出力。アクティブ"H" CMOSロジック出力で"H"は $V_{CC3}$ の電圧までドライブされるRSTのバッファされた相補出力です。RSTピンを外部からプルダウンすると、このピンが"H"にドライブされます。

RST(ピン6):リセット・ロジック出力。アクティブ L "のオープンドレイン・ロジック出力で、V<sub>CC3</sub>に微弱にプルアップされています。5Vロジックにインタフェースする

ときは、 $V_{CC3}$ より高い電圧に引き上げることが可能です。 1つ以上の電源がトリップ・スレッショルドより低く、かつすべての電源が有効になった後で200msの間そのまま保持されると行使されます。また、 $\overline{PBR}$ が2秒以上の間 L "に保持され、 $\overline{PBR}$ が解放されてからさらに200msの間 L "に保持された後も行使されます。

SRST(ピン7):ソフト・リセット。アクティブ'L"のオープンドレイン・ロジック出力で、VCC3に微弱にプルアップされています。5Vロジックにインタフェースするときは、VCC3より高い電圧に引き上げることが可能です。PBRが2秒以内の間'L"に保持されてから解放されると、100μsの間行使されます。

PBR(ピン8): プッシュボタン・リセット。アクティブ L"ロジック入力で $V_{CC3}$ に微弱にプルアップされています。 5Vロジックにインタフェースするときは、 $V_{CC3}$ より高い電圧に引き上げることが可能です。2秒以下行使されると、 $\overline{SRST}$ ピンに $100\mu s$ のソフト・リセット・パルスを出力します。 $\overline{PBR}$ が2秒以上行使されると、 $\overline{PBR}$ が解放された200ms後まで、 $\overline{RST}$ 出力は"L"に強制されます。

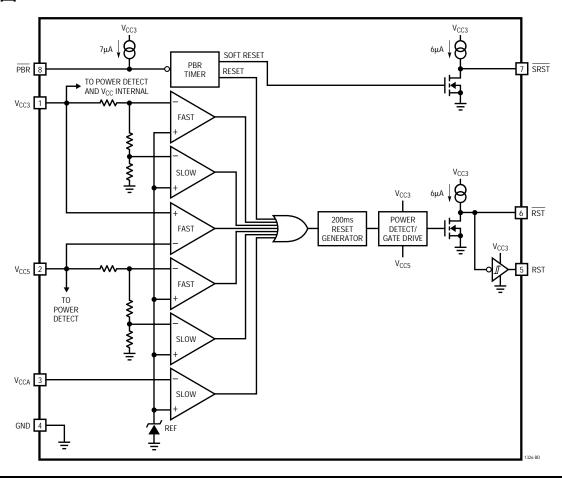

### ブロック図

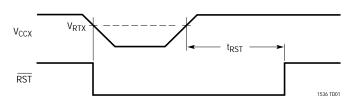

## タイミング図

VCCモニタ・タイミング

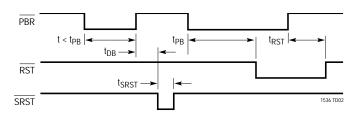

### プッシュボタン・リセット機能のタイミング

#### t<sub>FAII</sub> 高速低電圧検出

#### 電源フェイル検出

### アプリケーション情報

### 動作

LTC1536は低消費電力、高精度トリプル電源モニタ回路です。このリセット・ジェネレータは、次の2つの基本機能を備えています:1つは電源が範囲から外れたときにリセットを発生し、もう1つはリセット・ボタンが押されるとリセットまたは「ソフト」リセットを発生します。LTC1536には、リセット電源が大幅に低電圧になったとき、低電圧検出からRSTの行使まで非常に短い遅延を挿入する機能が付加されています。

#### 電源のモニタ

3つの $V_{CC}$ 入力はすべてリセット出力が解放される前に 200msの間、予め決定されたスレッショルドより高く保持されなければなりません。LTC1536は1つ以上の $V_{CC}$ 入力が電源投入、切断、および低下状態になるとリセットを行使します。

電源投入時には、 $V_{CC5}$ または $V_{CC3}$ ピンのいずれかでRSTピンのドライブ回路に電源を供給することができます。これによって、 $V_{CC5}$ または $V_{CC3}$ が1Vに達すると、RSTが確実に"L"になるようにしています。 $V_{CC}$ 入力のいずれ

か1つが予め決定されたスレッショルドより低い限り、 RSTはロジック" L "に保持されます。すべてのV<sub>CC</sub>入力が それぞれのスレッショルドより高くなると、内部タイマ が始動し、200ms後にRSTが解放されます。RSTはRSTの レベルの反転状態を出力します。

RSTは $V_{cc}$ 入力のいずれか1つが、予め決定されたスレッショルドより低くなると再行使され、すべての $V_{cc}$ 入力がそれぞれのスレッショルドより高くなってから200msの間行使状態を保持します。

電源切断時に、 $V_{CC}$ 入力のいずれかがスレッショルドより低くなると、 $\overline{RST}$ はロジック" L"に保持されます。  $V_{CC3}$ と $V_{CC5}$ が1Vより低くなるまで、0.4Vのロジック" L" が保証されます。

### プッシュボタン・リセット

LTC1536にはプッシュボタン・リセット入力ピンがあります。PBR入力はV<sub>CC3</sub>に接続されたプルアップ電流源を内蔵しています。PBRピンは使用しない場合はフロートさせておくことができます。

### アプリケーション情報

PBRが L "になっているのがtel 約2秒 以内のときは、ボタンを放した後でSRST出力ピンに狭い(標準100μs)ソフト・リセット・パルスが発生します。プッシュボタン回路はソフト・リセット・パルス出力を標準20ms遅延させる、内部デバウンス・カウンタを内蔵しています。このピンはRSTピンにOR接続することができ、「ソフト」リセットと呼ぶパルスを送出します。このためSRSTはDRAMリフレッシュ・サイクルを中断しないで、マイクロプロセッサをリセットします。DRAM情報が破壊されることはありません。また、SRSTをプロセッサでモニタして、ソフトウェア制御リセットを開始することもできます。

PBRピンがtPB(約2秒)より長く"L"に保持されると、標準リセットが生成されます。2秒の期間が経過すると、プッシュボタン・ロジックによってリセット信号が生成され、リセット・カウンタがクリアされます。PBRピンが解放されると、リセット・カウンタがリセット期間(通常200ms)のカウントを開始します。したがって、リセット出力はボタンが放された後、約200msの間行使されたままです。

### PCIアプリケーション用高速低電圧

LTC1536は、電源レール(5Vおよび3.3V)の1つまたは両方がスペックを外れそうになると、素早くリセットを行使する必要のあるPCIローカル・バス・アプリケーション用に設計されています。t<sub>FAIL</sub>およびt<sub>PF</sub>のスペックは、設計者がシステム条件に応じて必要な周辺ロジック回路を追加できるだけのマージンをもって規定されています。V<sub>CCA</sub>ピンは「パワーグッド」信号をモニタし、両方の電源が仕様範囲内に収まり、パワーグッド信号が"H"になるまで、リセットを印加しておくのに使用できます。

### グリッチ余裕度と高速低電圧検出

LTC1536は2組のコンパレータを使用して、グリッチ余裕度を維持したまま高速特性を達成しています。V<sub>CC5</sub>およびV<sub>CC3</sub>センス入力はそれぞれ、異なるスレッショルドが設定された2つのコンパレータを備えています。低速で非常に高精度のコンパレータは、電源をモニタして精密な低電圧検出を行います。他方、非常に高速でスレッショルドが高精度なスレッショルドより250mV低いコンパレータは、電源が急速に仕様から逸脱するとそれを検出します。高速コンパレータのスレッショルドはPCI仕様より250mV高く設定されているため、t<sub>FAII</sub>の標準値を負にすることもできます。

### 3Vまたは5V電源検出/ゲート・ドライブ

LTC1536ではほとんどの場合、内部で $V_{CC3}$ ピンから電源が供給されます。例外は、 $\overline{RST}$ ピン上の出力FETのゲート・ドライブです。このFETのゲートには、3.3Vピンまたは5Vピンのうち電位の高いピンを検出し、ゲートをドライブするのに使用する電源検出回路があります。これにより、いずれかのピンが1V以上になると、 $\overline{RST}$ ピンは確実に" L"になります。

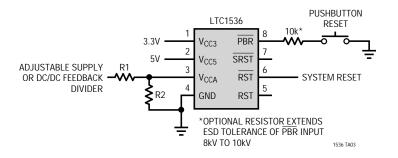

#### PBR入力ピンのESD耐久性の拡張

PBRピンは一般的なアプリケーションではフロントパネルに出されることがあるため、ESDの影響を受けやすいといえます。PBRピンと直列に抵抗を追加すれば、このピンのESD耐久性を向上することができます。10kの抵抗でPBRピンのESD耐久性を約10kVに向上させることができます。PBRピンの内部プルアップ電流が標準7μAならば、抵抗両端の電圧降下はわずか70mV(150mV最大)ということになります。

## 標準的応用例

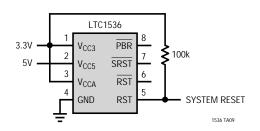

#### PCI**拡張ボード**RST**の生成**

### デュアル電源モニタ(3.3V、5V、「パワーグッド」 を監視するV<sub>CCA</sub>入力)

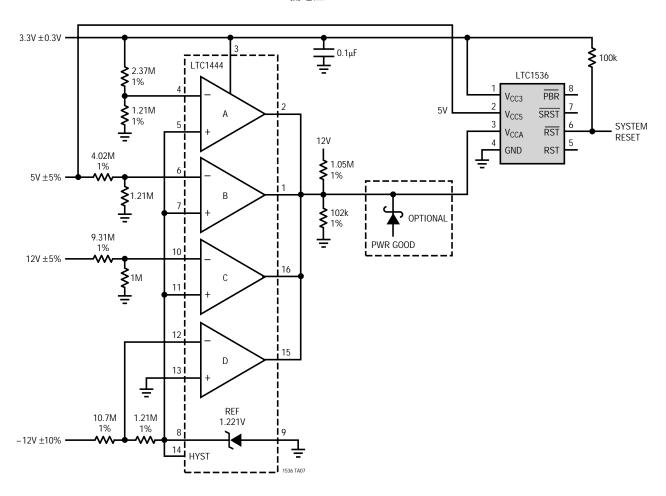

## 標準的応用例

### トリプル電源モニタ(3.3V、5V、可変)

### デュアル電源アプリケーションにおいて VCC3が0Vに低下してもRESETは有効

### SRSTをRSTに接続し、他のRSTへのソースを OR接続して、RESETとRESETを生成

### DC/DC**帰還分周器に接続した**V<sub>CCA</sub>を使用

0

## 標準的応用例

### クワッド電源モニタ:

12V: 低電圧、過電圧 5V: 低電圧、過電圧 3.3V: 低電圧、過電圧

- 12V: 低電圧

## 関連製品

| 製品番号        | 説明                                  | 注釈                               |

|-------------|-------------------------------------|----------------------------------|

| LTC690      | 5V電源モニタ、ウォッチドッグ・タイマおよびバッテリ・バックアップ   | スレッショルド:4.65V                    |

| LTC694-3.3  | 3.3V電源モニタ、ウォッチドッグ・タイマおよびバッテリ・バックアップ | スレッショルド:2.9V                     |

| LTC699      | 5V電源モニタおよびウォッチドッグ・タイマ               | スレッショルド:4.65V                    |

| LTC1232     | 5V電源モニタ、ウォッチドッグ・タイマおよびプッシュボタン・リセット  | スレッショルド:4.37V/4.62V              |

| LTC1326     | マイクロパワー高精度トリプル電源モニタ                 | スレッショルド(±0.75%):4.725V、3.118V、1V |

| LTC1326-2.5 | マイクロパワー高精度トリプル電源モニタ                 | スレッショルド(±0.75%):2.363V、3.118V、1V |