## 特長

- 単調性を保証

- バッファされた真のレール・トゥ・レール電圧出力

- 12ビット分解能

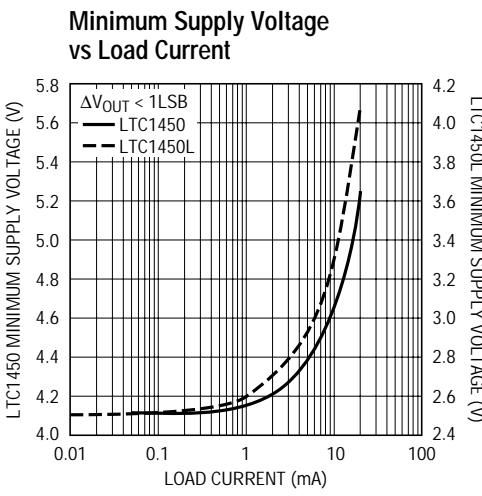

- 3V動作 (LTC1450L)  $I_{CC}$  : 250 $\mu$ A( 標準 )

- 5V動作 (LTC1450)  $I_{CC}$  : 400 $\mu$ A( 標準 )

- パラレル12ビットまたは8+4ビット・ダブルバッファ・デジタル入力

- 内部リファレンス

- 利得1または2に構成可能な出力バッファ

- 乗算DACとして構成可能

- 内部パワーオン・リセット

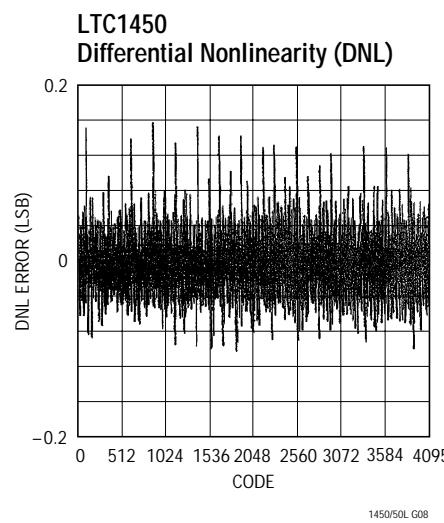

- 最大DNL誤差 : 0.5LSB

## アプリケーション

- デジタル校正

- 産業用プロセス・コントロール

- 自動試験装置

- 汎用ファンクション・ジェネレータ

- バッテリ動作データ変換製品

- フィードバック制御ループおよび利得制御

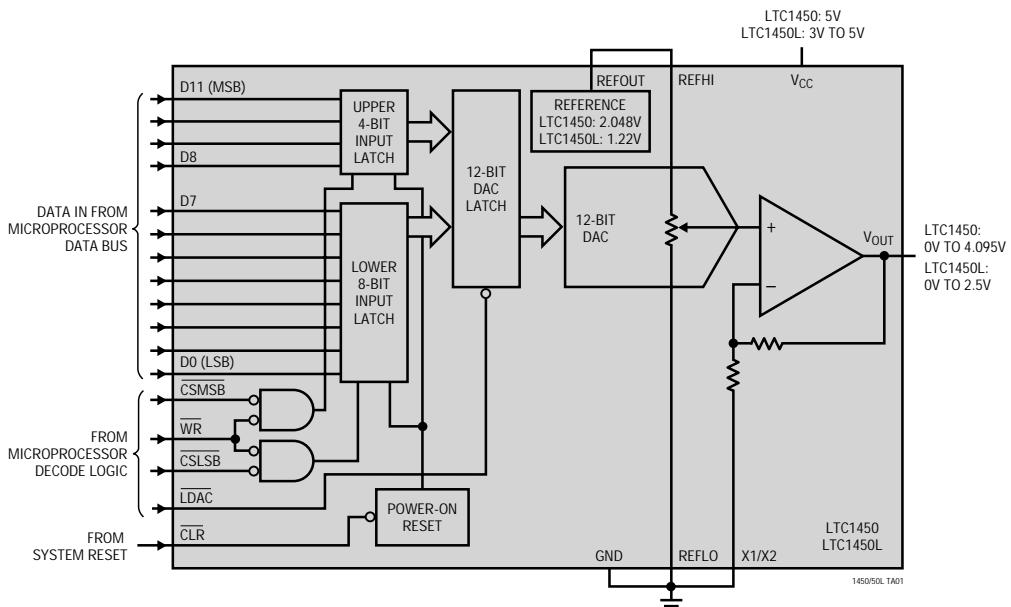

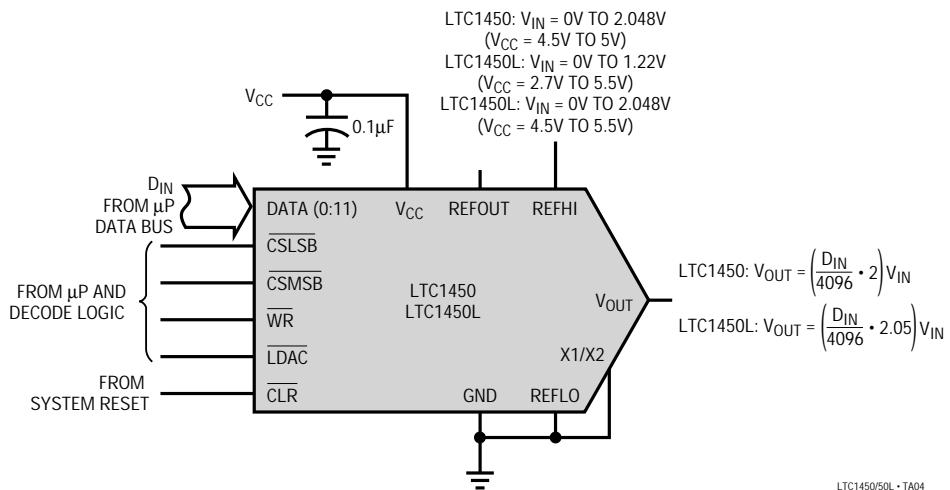

## TYPICAL APPLICATION

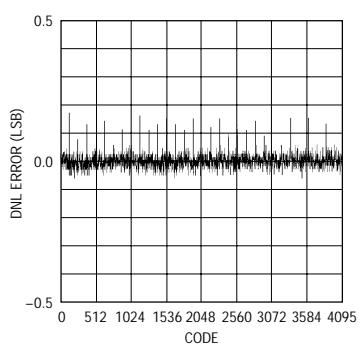

Differential Nonlinearity

vs Input Code

# LTC1450/LTC1450L

## ABSOLUTE MAXIMUM RATINGS

|                                            |                          |

|--------------------------------------------|--------------------------|

| $V_{CC}$ to GND .....                      | -0.5V to 7.5V            |

| Logic Inputs to GND .....                  | -0.5V to 7.5V            |

| $V_{OUT}$ .....                            | -0.5V to $V_{CC}$ + 0.5V |

| REFOUT, REFLO, REFHI, X1/X2 .....          | -0.5V to $V_{CC}$ + 0.5V |

| Maximum Junction Temperature .....         | 125°C                    |

| Operating Temperature Range                |                          |

| Commercial .....                           | 0°C to 70°C              |

| Industrial .....                           | -40°C to 85°C            |

| Storage Temperature Range .....            | -65°C to 150°C           |

| Lead Temperature (Soldering, 10 sec) ..... | 300°C                    |

## PACKAGE/ORDER INFORMATION

| TOP VIEW                                                                                                                                                   |    | ORDER PART NUMBER                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------|

| WR                                                                                                                                                         | 1  | LDAC                              |

| CSLSB                                                                                                                                                      | 2  | CLR                               |

| CSMSB                                                                                                                                                      | 3  | X1/X2                             |

| (LSB) D0                                                                                                                                                   | 4  | $V_{OUT}$                         |

| D1                                                                                                                                                         | 5  | $V_{CC}$                          |

| D2                                                                                                                                                         | 6  | REFOUT                            |

| D3                                                                                                                                                         | 7  | REFHI                             |

| D4                                                                                                                                                         | 8  | REFLO                             |

| D5                                                                                                                                                         | 9  | GND                               |

| D6                                                                                                                                                         | 10 | D11(MSB)                          |

| D7                                                                                                                                                         | 11 | D10                               |

| D8                                                                                                                                                         | 12 | D9                                |

| G PACKAGE<br>24-LEAD PLASTIC SSOP                                                                                                                          |    | N PACKAGE<br>24-LEAD PLASTIC PDIP |

| $T_{JMAX} = 125^\circ\text{C}, \theta_{JA} = 95^\circ\text{C}/\text{W}$ (G)<br>$T_{JMAX} = 125^\circ\text{C}, \theta_{JA} = 58^\circ\text{C}/\text{W}$ (N) |    |                                   |

Consult factory for Military grade parts.

## ELECTRICAL CHARACTERISTICS

$V_{CC} = 4.5\text{V}$  to  $5.5\text{V}$  (LTC1450),  $2.7\text{V}$  to  $5.5\text{V}$  (LTC1450L),  $V_{OUT}$  unloaded,

REFOUT = REFHI, REFLO = GND = X1/X2,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL                           | PARAMETER                                  | CONDITIONS                                                   | MIN | TYP   | MAX                    | UNITS                        |                       |

|----------------------------------|--------------------------------------------|--------------------------------------------------------------|-----|-------|------------------------|------------------------------|-----------------------|

| <b>DAC</b>                       |                                            |                                                              |     |       |                        |                              |                       |

|                                  | Resolution                                 |                                                              | ●   | 12    |                        | Bits                         |                       |

| DNL                              | Differential Nonlinearity                  | Guaranteed Monotonic (Note 1)                                | ●   |       | $\pm 0.5$              | LSB                          |                       |

| INL                              | Integral Nonlinearity                      | $T_A = 25^\circ\text{C}$<br>(Note 1)                         | ●   |       | $\pm 3.5$<br>$\pm 4.0$ | LSB                          |                       |

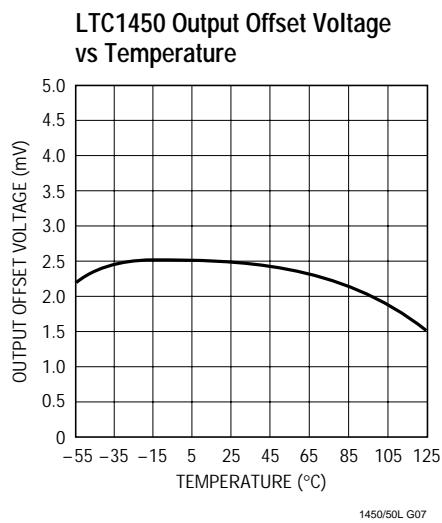

| $V_{OS}$                         | Offset Error                               | $T_A = 25^\circ\text{C}$                                     | ●   |       | $\pm 12$<br>$\pm 18$   | mV                           |                       |

| $V_{OS\ TC}$                     | Offset Error Temperature Coefficient       |                                                              |     |       | $\pm 15$               | $\mu\text{V}/^\circ\text{C}$ |                       |

| $V_{FS}$                         | Full-Scale Voltage                         | Using Internal Reference, LTC1450, $T_A = 25^\circ\text{C}$  | ●   | 4.065 | 4.095                  | 4.125                        |                       |

|                                  |                                            | Using Internal Reference, LTC1450                            | ●   | 4.045 | 4.095                  | 4.145                        |                       |

|                                  |                                            | External 2.048V Reference, LTC1450                           | ●   | 4.075 | 4.095                  | 4.115                        |                       |

|                                  |                                            | Using Internal Reference, LTC1450L, $T_A = 25^\circ\text{C}$ | ●   | 2.470 | 2.500                  | 2.530                        |                       |

|                                  |                                            | Using Internal Reference, LTC1450L                           | ●   | 2.460 | 2.500                  | 2.540                        |                       |

| $V_{FS\ TC}$                     | Full-Scale Voltage Temperature Coefficient | External 1.22V Reference, LTC1450L                           | ●   | 2.480 | 2.500                  | 2.520                        |                       |

|                                  |                                            | Using Internal Reference, LTC1450                            |     |       | $\pm 0.10$             | LSB/ $^\circ\text{C}$        |                       |

|                                  |                                            | Using External Reference, LTC1450/LTC1450L                   |     |       | $\pm 0.02$             | LSB/ $^\circ\text{C}$        |                       |

|                                  |                                            | Using Internal Reference, LTC1450L                           |     |       | $\pm 0.10$             | LSB/ $^\circ\text{C}$        |                       |

| <b>Reference Output (REFOUT)</b> |                                            |                                                              |     |       |                        |                              |                       |

|                                  | Reference Output Voltage                   | LTC1450L<br>LTC1450                                          | ●   | 1.195 | 1.220                  | 1.245                        | V                     |

|                                  |                                            |                                                              | ●   | 2.008 | 2.048                  | 2.088                        | V                     |

|                                  | Reference Output Temperature Coefficient   |                                                              |     |       | $\pm 0.08$             |                              | LSB/ $^\circ\text{C}$ |

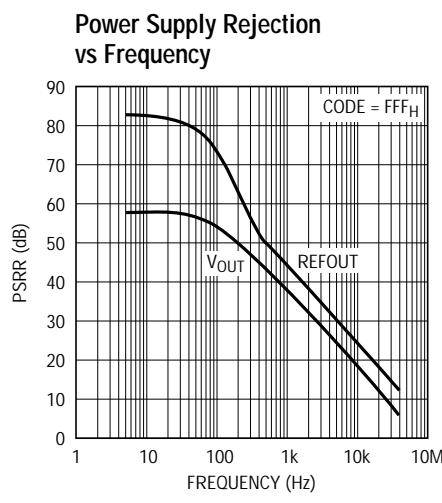

|                                  | Reference Line Regulation                  |                                                              | ●   |       | 0.7                    | $\pm 2$                      | LSB/V                 |

|                                  | Reference Load Regulation                  | $0 \leq I_{OUT} \leq 100\mu\text{A}$ , LTC1450L<br>LTC1450   | ●   |       | 0.6                    | $\pm 3.0$                    | LSB                   |

|                                  |                                            |                                                              | ●   |       | 0.2                    | $\pm 1.5$                    | LSB                   |

|                                  | Short-Circuit Current                      | REFOUT Shorted to GND                                        | ●   |       | 80                     | mA                           |                       |

**ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 4.5V to 5.5V (LTC1450), 2.7V to 5.5V (LTC1450L),  $V_{OUT}$  unloaded,

$REFOUT = REFHI$ ,  $REFLO = GND = X1/X2$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL                               | PARAMETER                    | CONDITIONS                                                                                      | MIN | TYP | MAX        | UNITS     |

|--------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|------------|-----------|

| <b>Reference Input (REFLO = GND)</b> |                              |                                                                                                 |     |     |            |           |

|                                      | REFHI Input Range            | $V_{REFHI} \leq V_{CC} - 1.5V$                                                                  | ●   |     | $V_{CC}/2$ | V         |

|                                      | REFHI Input Resistance       |                                                                                                 | ●   | 8   | 18         | $k\Omega$ |

|                                      | REFHI Input Capacitance      |                                                                                                 |     |     | 15         | pF        |

| <b>Power Supply</b>                  |                              |                                                                                                 |     |     |            |           |

| $V_{CC}$                             | Positive Supply Voltage      | For Specified Performance, LTC1450L<br>LTC1450                                                  | ●   | 2.7 | 5.5        | V         |

|                                      |                              |                                                                                                 | ●   | 4.5 | 5.5        | V         |

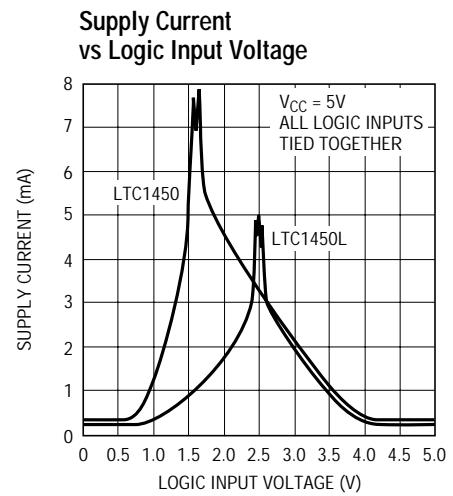

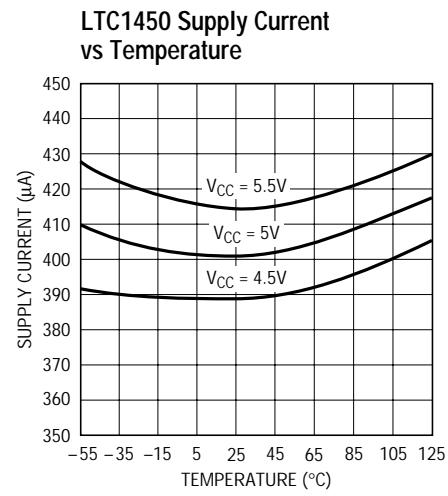

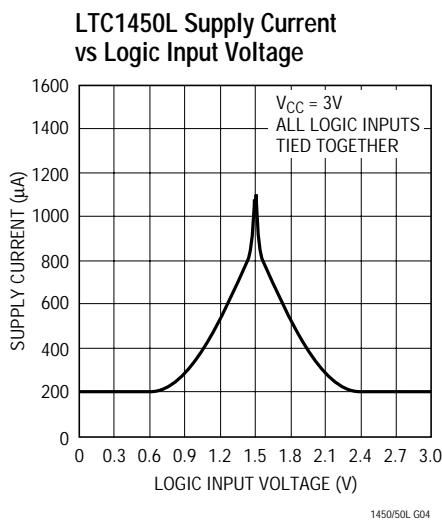

| $I_{CC}$                             | Supply Current               | 4.5V $\leq V_{CC} \leq$ 5.5V (Note 4) LTC1450<br>2.7V $\leq V_{CC} \leq$ 5.5V (Note 4) LTC1450L | ●   | 300 | 400        | 620       |

|                                      |                              |                                                                                                 | ●   | 150 | 250        | 500       |

| <b>Op Amp DC Performance</b>         |                              |                                                                                                 |     |     |            |           |

|                                      | Short-Circuit Current Low    | $V_{OUT}$ Shorted to GND                                                                        | ●   |     | 100        | mA        |

|                                      | Short-Circuit Current High   | $V_{OUT}$ Shorted to $V_{CC}$                                                                   | ●   |     | 120        | mA        |

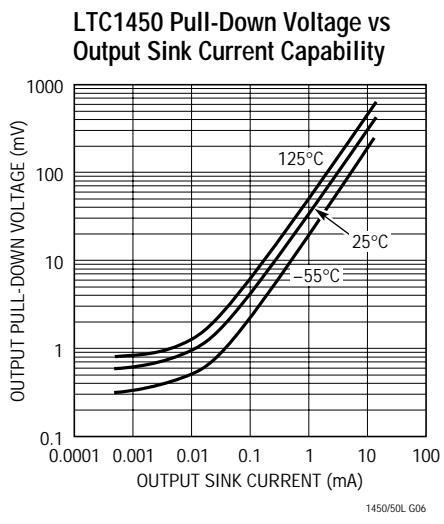

|                                      | Output Impedance to GND      | Input Code = 0                                                                                  | ●   | 40  | 120        | $\Omega$  |

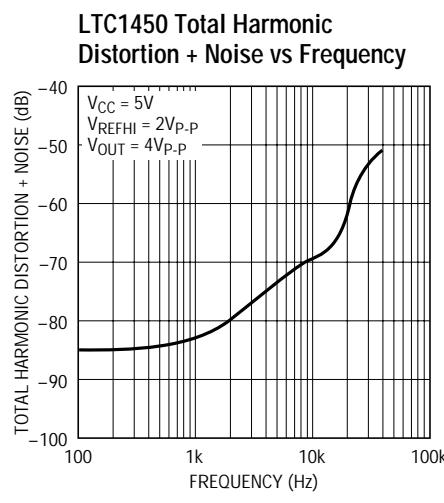

| <b>AC Performance</b>                |                              |                                                                                                 |     |     |            |           |

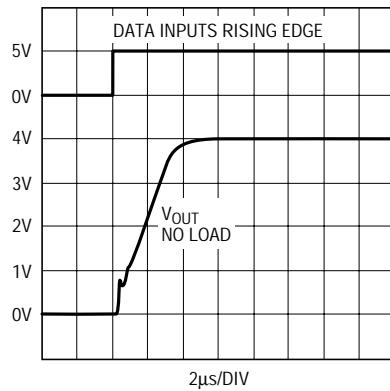

|                                      | Voltage Output Slew Rate     | (Note 2)                                                                                        | ●   | 0.5 | 1.0        | $V/\mu s$ |

|                                      | Voltage Output Settling Time | (Notes 2, 3) to $\pm 0.5$ LSB                                                                   |     |     | 14         | $\mu s$   |

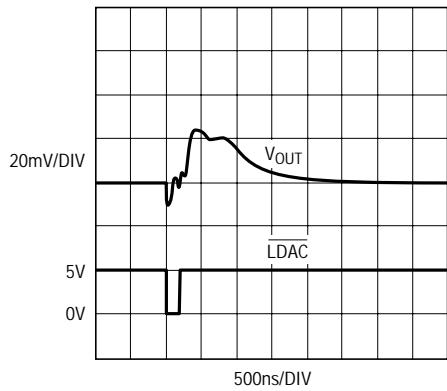

|                                      | Digital Feedthrough          | LDAC = 1                                                                                        |     |     | 5          | (nV)(s)   |

|                                      | AC Feedthrough               | REFHI = 1kHz, $2V_{P-P}$                                                                        |     |     | -95        | dB        |

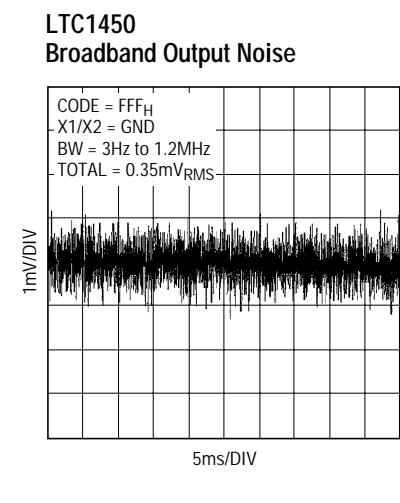

| SINAD                                | Signal-to-Noise + Distortion | REFHI = 1kHz, $2V_{P-P}$ (Code: All 1's)                                                        |     |     | 85         | dB        |

| <b>Digital Inputs</b>                |                              |                                                                                                 |     |     |            |           |

| $V_{IH}$                             | Digital Input High Voltage   | $V_{CC} = 3V$ , LTC1450L<br>$V_{CC} = 5V$ , LTC1450                                             | ●   | 2.2 |            | V         |

|                                      |                              |                                                                                                 | ●   | 2.4 |            | V         |

| $V_{IL}$                             | Digital Input Low Voltage    | $V_{CC} = 3V$ , LTC1450L<br>$V_{CC} = 5V$ , LTC1450                                             | ●   |     | 0.8        | V         |

|                                      |                              |                                                                                                 | ●   |     | 0.8        | V         |

| $V_{LTH}$                            | Logic Threshold Voltage      | LTC1450L                                                                                        |     |     | $V_{CC}/2$ | V         |

| $I_{LEAK}$                           | Digital Input Leakage        | $V_{CC} = 5V$ , $V_{IN} = GND$ to $V_{CC}$                                                      | ●   | -10 | 10         | $\mu A$   |

| $C_{IN}$                             | Digital Input Capacitance    | Guaranteed by Design. Not Subject to Test                                                       | ●   |     | 10         | pF        |

# LTC1450/LTC1450L

## ELECTRICAL CHARACTERISTICS

$V_{CC} = 4.5V$  to  $5.5V$  (LTC1450),  $V_{CC} = 2.7V$  to  $3.6V$  (LTC1450L),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL                                    | PARAMETER                                | CONDITIONS                                                                                              | MIN | TYP | MAX | UNITS |

|-------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| <b>Switching Characteristics (Note 5)</b> |                                          |                                                                                                         |     |     |     |       |

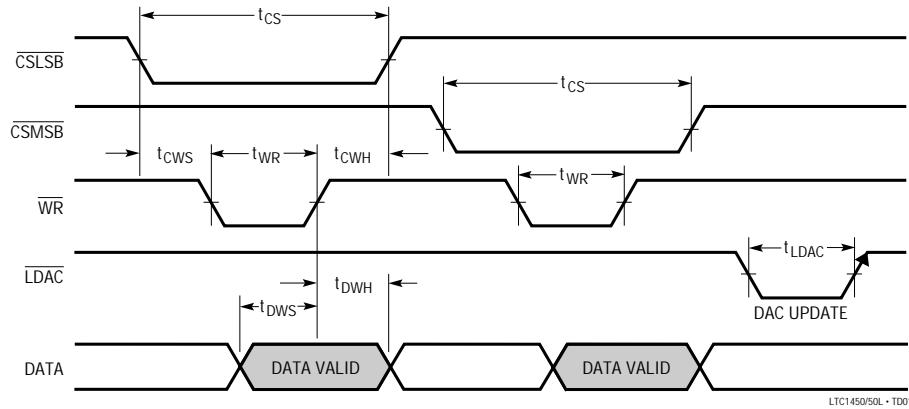

| $t_{CS}$                                  | $\overline{CS}$ (MSB or LSB) Pulse Width |                                                                                                         | ●   | 40  |     | ns    |

| $t_{WR}$                                  | $\overline{WR}$ Pulse Width              |                                                                                                         | ●   | 40  |     | ns    |

| $t_{CWS}$                                 | $\overline{CS}$ to $\overline{WR}$ Setup |                                                                                                         | ●   | 0   |     | ns    |

| $t_{CWH}$                                 | $\overline{CS}$ to $\overline{WR}$ Hold  |                                                                                                         | ●   | 0   |     | ns    |

| $t_{DWS}$                                 | Data Valid to $\overline{WR}$ Setup      | $V_{CC} = 4.5V$ to $5.5V$ (LTC1450)<br>$V_{CC} = 2.7V$ to $3.6V$ (LTC1450L)<br>$V_{CC} = 5V$ (LTC1450L) | ●   | 40  | 15  | ns    |

|                                           |                                          |                                                                                                         | ●   | 40  | 15  | ns    |

|                                           |                                          |                                                                                                         | ●   |     | 10  | ns    |

| $t_{DWH}$                                 | Data Valid to $\overline{WR}$ Hold       | $V_{CC} = 4.5V$ to $5.5V$ (LTC1450)<br>$V_{CC} = 2.7V$ to $3.6V$ (LTC1450L)<br>$V_{CC} = 5V$ (LTC1450L) | ●   | 0   | -10 | ns    |

|                                           |                                          |                                                                                                         | ●   | 0   | -10 | ns    |

|                                           |                                          |                                                                                                         |     |     | -5  | ns    |

| $t_{LDAC}$                                | $\overline{LDAC}$ Pulse Width            |                                                                                                         | ●   | 40  |     | ns    |

| $t_{CLR}$                                 | $\overline{CLR}$ Pulse Width             |                                                                                                         | ●   | 40  |     | ns    |

The ● denotes specifications which apply over the full operating temperature range.

**Note 1:** Nonlinearity is defined from the first code that is greater than or equal to the maximum offset specification to code 4095 (full-scale).

**Note 2:** Load is  $5k\Omega$  in parallel with  $100pF$ .

**Note 3:** DAC switched all 1's and the code corresponding to  $V_{OS(MAX)}$  for the part.

**Note 4:** Digital inputs at  $0V$  or  $V_{CC}$ .

**Note 5:** Digital inputs swing 10% to 90% of  $V_{CC}$ ,  $t_f = t_r = 5ns$  and timing measurements are from  $V_{CC}/2$ .

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

# LTC1450/LTC1450L

## TYPICAL PERFORMANCE CHARACTERISTICS

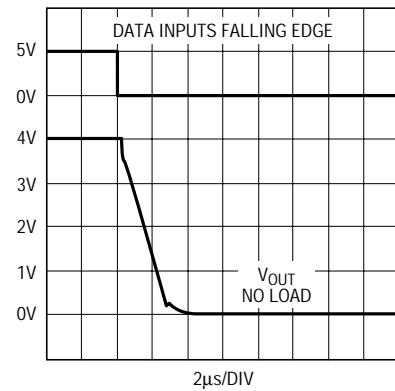

LTC1450 Midscale Transition

Data = 2048 to 2047

1450/50L G13

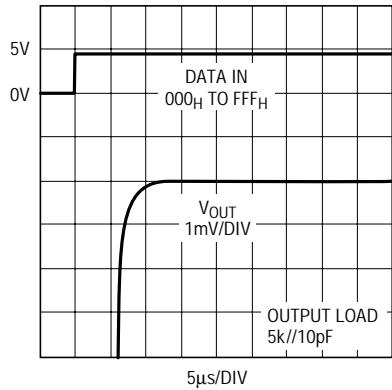

LTC1450

Large-Scale Settling (Rising)

1450/50L G14

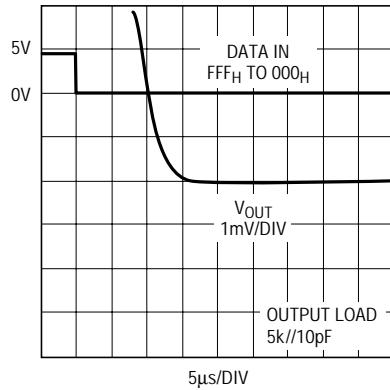

LTC1450

Large-Scale Settling (Falling)

1450/50L G15

Output Voltage Full-Scale Settling

1450/50L G16

Output Voltage Zero-Scale Settling

1450/50L G17

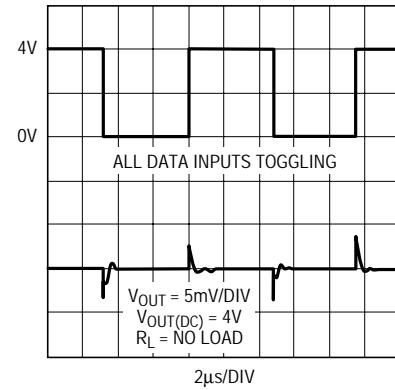

LTC1450 Digital Feedthrough

1450/50L G18

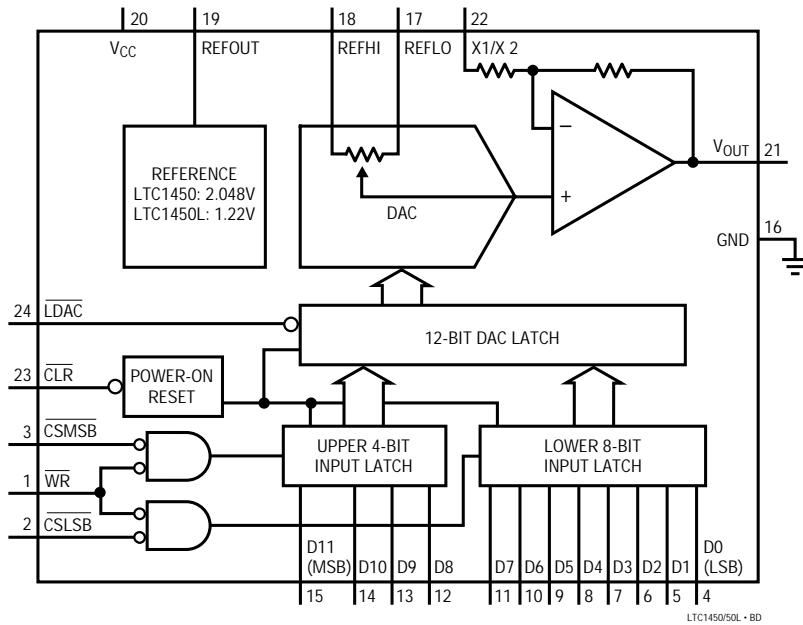

## ピン機能

WR( ピン1 ): ライト入力( アクティブ“ L ”)。 CSMSBまたは/およびCSLSBとともに使用され、データを入力ラッチにロードします。 WRとCSLSBまたは/およびCSMSBが“ L ”に保持されると、イネーブルされた入力ラッチは簡易的に制御でき、WRの立上りエッジで、データはすべての入力ラッチにラッチされます。

CSLSB( ピン2 ): チップ・セレクト最下位バイト( アクティブ“ L ”)。データを8つの LSB 入力ラッチにロードするのに使用されます。 WRとCSLSBを“ L ”に保持すると、8つの LSB 入力ラッチが簡易的に制御でき、立上りエッジでデータが8つの LSB 入力ラッチにラッチされます。CSMSBに接続すると、12ビット・バス上の2組の入力ラッチに同時にロードすることができます。

CSMSB( ピン3 ): チップ・セレクト最上位バイト( アクティブ“ L ”)。 WRとともに使用され、データを4つの MSB 入力ラッチにロードします。 WRおよびCSMSBが“ L ”に保持されると、4つの MSB 入力ラッチは簡易的に制御でき、立上りエッジでデータが4つの MSB 入力ラッチにラッチされます。CSMSBに接続すると、12ビット・バス上の2組の入力ラッチに同時にロードすることができます。

D0 ~ D7( ピン4 ~ 11 ): 最下位バイトの入力データ。 WR = 0 および CSLSB = 0 のときは、LSB 入力ラッチにロードされます。

D8、D9、D10、D11( ピン12、14、14、15 ): 最上位バイトの入力データ。 WR = 0 および CSMSB = 0 のときは、MSB 入力ラッチにロードされます。8ビット・バス上で多重化動作を行う場合は、D0 ~ D3に接続できます。

GND( ピン16 ): グランド

REFLO( ピン17 ): DACの内部抵抗ストリングの下部入力端子。通常、アナログ・グランドに接続します。コー

ド(000H)を入力すると、出力バッファの正入力がこの端子に接続されます。グランドより高いゼロ・スケールをオフセットするのに使用できます。

REFHI( ピン18 ): DACの内部抵抗ストリングの上部入力端子。通常、REFOUTに接続します。コード(FFFH)を入力すると、出力バッファの正入力がこの端子から1LSBに接続されます。

REFOUT( ピン19 ): 内部2.048V/1.22Vリファレンスの出力。通常、内部DAC抵抗ストリングをドライブするためにREFHIに接続されます。

V<sub>CC</sub>( ピン20 ): 正電源入力。4.5V ≤ V<sub>CC</sub> ≤ 5.5V(LTC1450)、2.7V ≤ V<sub>CC</sub> ≤ 5.5V(LTC1450L)です。グランドにバイパス・コンデンサを接続する必要があります。

V<sub>OUT</sub>( ピン21 ): バッファされたDAC出力。

X1/X2( ピン22 ): 利得設定抵抗ピン。G = 2 を実現するにはGNDに、G = 1 を実現するにはV<sub>OUT</sub>に接続します。容量性負荷ドライブ時に出力バッファの安定性を確保するために、常にグランドやV<sub>OUT</sub>などの低インピーダンス源に接続しなければなりません。

CLR( ピン23 ): クリア入力( 非同期アクティブ“ L ”)。このピンが“ L ”のときは、すべての内部ラッチが非同期で0にリセットされます。

LDACT( ピン24 ): ロードDAC( 非同期アクティブ“ L ”)。入力ラッチ内容を非同期でDACラッチに転送するのに使用されます。DACラッチにデータが転送されると出力電圧が変化します。データは立上りエッジでDACラッチにラッチされます。このピンを“ L ”に保持すると、DACラッチは簡易的に制御され、入力ラッチからのデータによって直ちにV<sub>OUT</sub>が変化します。

# LTC1450/LTC1450L

## DIGITAL INTERFACE TRUTH TABLE

| CLR | CSMSB | CSLSB | WR | LDAC | FUNCTION                                                |

|-----|-------|-------|----|------|---------------------------------------------------------|

| H   | H     | L     | L  | H    | Loads the eight LSBs into the input latch               |

| H   | H     | L     | ↑  | H    | Latches the eight LSBs into the input latch             |

| H   | H     | ↑     | L  | H    | Latches the eight LSBs into the input latch             |

| H   | L     | H     | L  | H    | Loads the four MSBs into the input latch                |

| H   | L     | H     | ↑  | H    | Latches the four MSBs into the input latch              |

| H   | ↑     | H     | L  | H    | Latches the four MSBs into the input latch              |

| H   | H     | H     | H  | L    | Loads the input latch data into the DAC latch           |

| H   | H     | H     | H  | ↑    | Latches the input latch data into the DAC latch         |

| H   | L     | L     | L  | L    | Loads input data into DAC latches (latches transparent) |

| H   | L     | L     | L  | ↑    | Latches input data into DAC latches                     |

| L   | X     | X     | X  | X    | All zeros loaded into input and DAC latches             |

## TIMING DIAGRAM

## BLOCK DIAGRAM

## 定義

分解能( $n$ )：分解能はデジタル入力ビット数( $n$ )と定義されます。フルスケール・レンジを分割するDAC出力ステート数( $2^n$ )を定義します。分解能は直線性を意味するものではありません。

フルスケール電圧( $V_{FS}$ )：これはすべてのビットが1にセットされたときのDACの出力です。

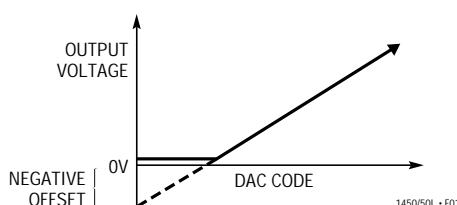

電圧オフセット誤差( $V_{OS}$ )：DACにオール・ゼロをロードしたときの出力の理論電圧です。出力アンプは真の負オフセットを持つことができますが、デバイスは単一電源で動作するため、出力はゼロ以下に低下することはできません。オフセットが負の場合、出力はほぼ0Vを保持し、図1に示すような伝達曲線となります。

デバイスのオフセットは、次のとおり最大オフセット仕様に対応するコードで測定されます。

$$V_{OS} = V_{OUT} - [(CODE/V_{FS})/2^n - 1]$$

最下位ビット LSB : 1 LSBは2つの連続するコード間の理想電圧差です。

$$LSB = (V_{FS} - V_{OS})/(2^n - 1) = (V_{FS} - V_{OS})/4095$$

公称LSB:

LTC1450

$$LSB = 4.095V/4095 = 1mV$$

LTC1450L

$$LSB = 2.5V/4095 = 0.610mV$$

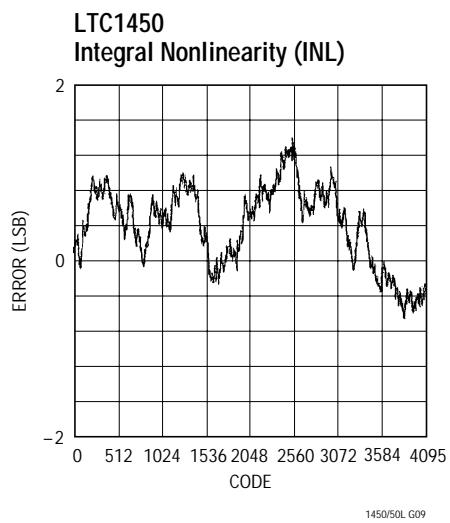

積分非直線性(INL)：エンドポイントINLは、DAC伝達曲線の両端を通る直線からの最大偏差です。デバイスは単一電源で動作し出力はゼロ以下にできないため、直線性はフルスケールと最大オフセット仕様に対応するコードの間で測定されます。ある入力コードに対するINL誤差は、次式で計算されます。

$$INL = [V_{OUT} - V_{OS} - (V_{FS} - V_{OS})(CODE/4095)]/LSB$$

$V_{OUT}$  = ある入力コードで測定されるDACの出力電圧

微分非直線性(DNL)：DNLは測定された変化と2つの隣接するコード間の理想1 LSB変化との差です。2つのコード間のDNL誤差は、次式で計算されます。

$$DNL = (\Delta V_{OUT} - LSB)/LSB$$

$\Delta V_{OUT}$  = 2つの隣接するコード間で測定した電圧差

デジタル・フィードスルー：アナログ出力が状態を変化したときに、デジタル入力からのAC結合によって、アナログ出力に発生するグリッチです。グリッチの面積は( $nV$ )(s)で規定されます。

Figure 1. Effect of Negative Offset

## 動作

### パラレル・インターフェース

DAC入力のデータは、チップ・セレクト(CSLSBおよびCSMSB )とWRが論理“L”のときにDAC入力ラッチにロードされます。入力ラッチにロードされるデータは、論理“L”的チップ・セレクトによって決まります(デジタル・インターフェース真理値表を参照)。WRとCSLSBの両方が“L”でCSMSBが“H”的場合、8つのLSB上のデータ(D0～D7)だけが入力ラッチにロードされます。同様に、WRとCSMSBの両方が“L”でCSLSBが“H”的場合は、4つのMSB上のデータ(D8～D11)だけが入力ラッチにロードされます。WR、CSLSB、CSMSBが“L”的場合、データは最下位データ・ビット群(D0～D7)と最上位ビット群(D8～D11)に同時にロードされます。

入力データはWRまたはチップ・セレクトの1つの立上りエッジで、入力ラッチにラッチされます。WRが“H”に変化すると、両方の入力ラッチにデータがラッチされます。CSMSBの立上りエッジで、データ・ビットD8～D11がラッチされます。CSLSBの立上りエッジで、データ・ビットD8～D11がラッチされます。

入力ラッチにロードされたデータは、DACラッチにロードできます。これによって、DACのアナログ電圧出力がアップデートされます。DACラッチはLDACに論理“L”があるとロードされます。DACラッチにロードされたデータは、LDACの立上りエッジでラッチされます。

WR、CSLSB、CSMSB、およびLDACがすべて“L”的とき、ラッチは簡易的に制御され、ピンD0～D11のデータがDACラッチに直接ロードされます。

### パワーオン・リセット

LTC1450/LTC1450Lはパワーオン・リセット回路を内蔵しており、電源投入時にすべての内部ラッチを0にリセットします(CLRピン機能と同等)。

### リファレンス

LTC1450は内部2.048Vリファレンスを内蔵し、利得2の構成で4.095Vのフルスケール・レンジを実現します。LTC1450Lは、利得2の構成で2.5Vのフルスケール・レンジと利得2.05を有する内部1.22Vリファレンスを内蔵しています。LTC1450およびLTC1450Lのオンボード・リファレンスは、内部でDACのリファレンス抵抗ストリングに接続されていませんが、柔軟性を高めるために隣

接ピンに供給されます。内部リファレンスは内部でDAC抵抗ストリングに接続されていないため、外部リファレンスを使用するか、または乗算構成で外部ソースによって抵抗ストリングをドライブすることができます。外部リファレンスまたは外部ソースは、8kの最小DACラダー抵抗をドライブできなければなりません。

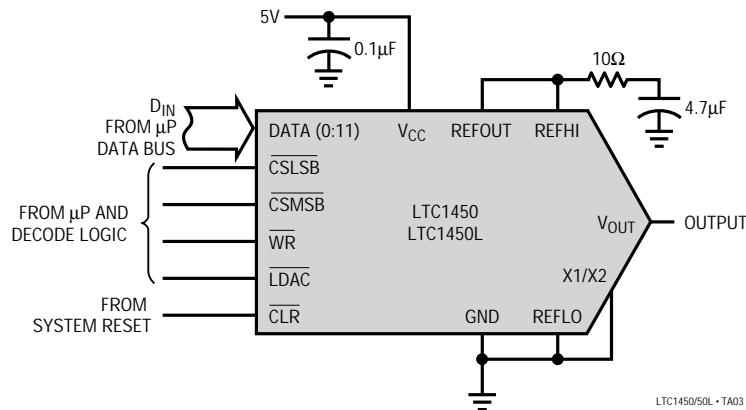

リファレンス出力のノイズは、バイパス・コンデンサをグランドに接続すると低減できます(ただし、グランドにバイパス・コンデンサを接続しないと適切に動作しないわけではありません)。リファレンスをバイパスするときは、出力のピーニングを低減するためにコンデンサと直列に小さな値の抵抗を使用することを推奨します。リファレンスで生成されたノイズを低減するには、4.7μFコンデンサと直列に10Ω抵抗を接続すれば効果的です。

### DACラダー抵抗ストリング

DACラダー抵抗ストリングの上端と下端(それぞれREFHIとREFLO)は、内部では接続されていません。通常、REFHIはREFOUTに接続され、REFLOはGNDに接続されます。これによって、LTC1450は4.095Vのフルスケール・レンジとなります。LTC1450Lのフルスケール・レンジは2.5Vです。

利得1構成のバッファを使用するときは、これらのピンのいずれかをV<sub>CC</sub>-1.5Vまでドライブできます。バッファが利得2構成の場合には、抵抗ストリングのピンをV<sub>CC</sub>/2にドライブできます(LTC1450Lの場合は2.05)。これら2本のピン間の抵抗は標準18k(最小で8k)です。

### 電圧出力

LTC1450/LTC1450Lの出力バッファは、2種類の利得設定に構成することができます。X1/X2ピンをGNDに接続すると、利得は2に設定されます(LTC1450Lの場合は2.05)。X1/X2ピンをV<sub>OUT</sub>に接続すると、利得は1に設定されます。

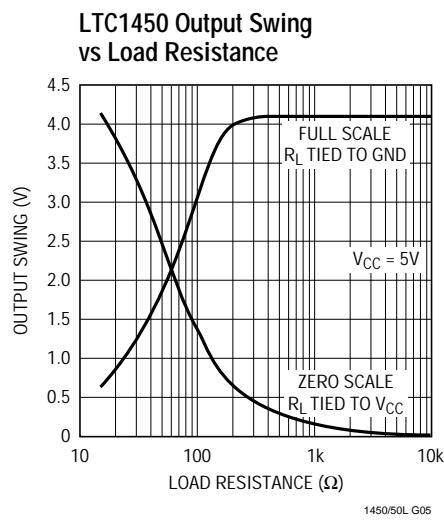

LTC1450ファミリのレール・トゥ・レール・バッファ出力は、全動作温度範囲において5mAをソースまたはシンクできると同時に、正電源電圧またはGNDの300mV以内にプルアップまたはプルダウンすることができます。無負荷時には出力はいずれかの電源レールの数mV以内に振幅し、負荷をレールにドライブする場合には等価出力抵抗は40Ωになります。

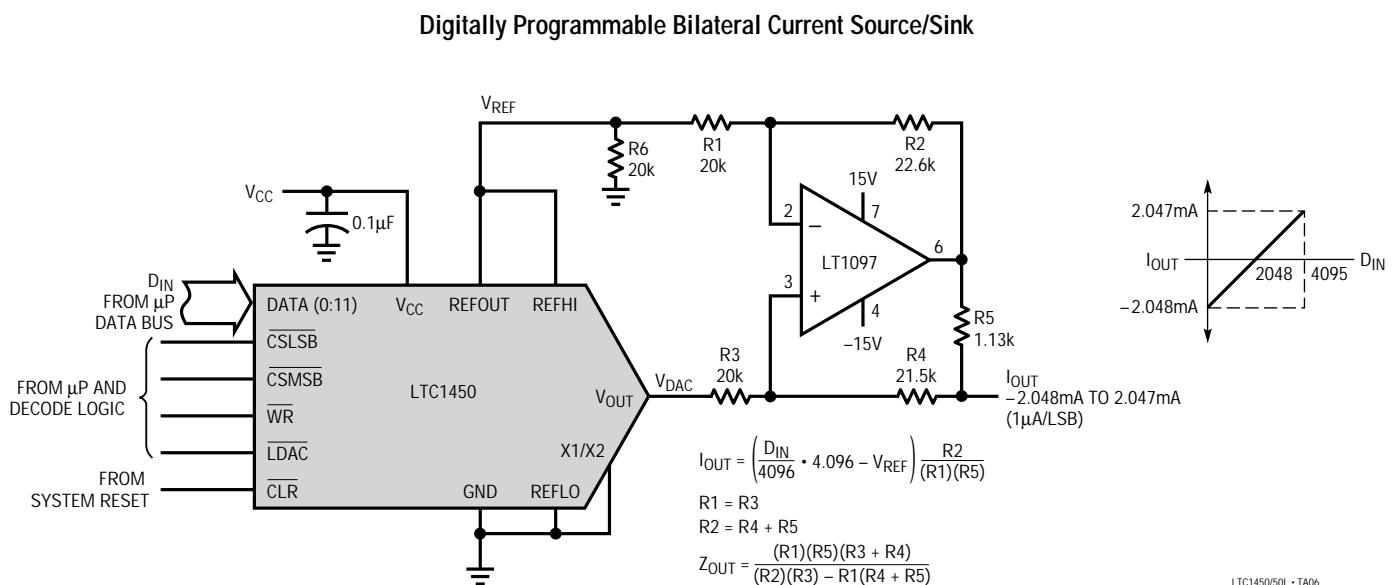

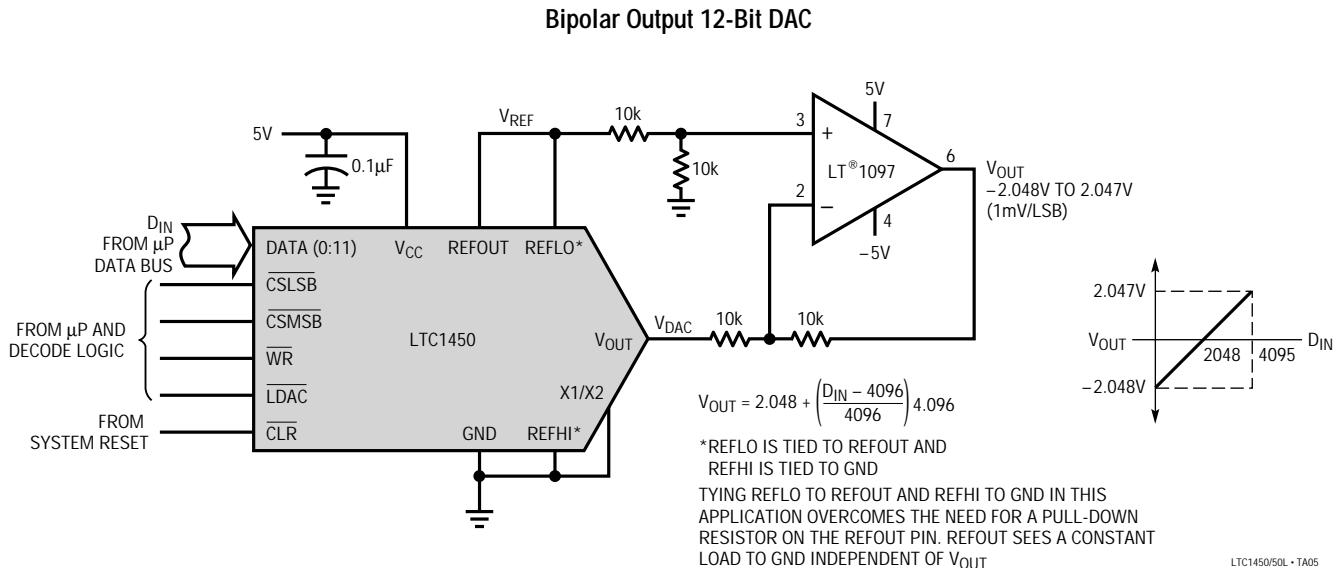

## TYPICAL APPLICATIONS

Filter V<sub>REF</sub> to Lower Output Noise (0.18mV<sub>RMS</sub> at V<sub>OUT</sub>)

Digitally Programmable Noninverting Amplifier

# LTC1450/LTC1450L

## TYPICAL APPLICATIONS

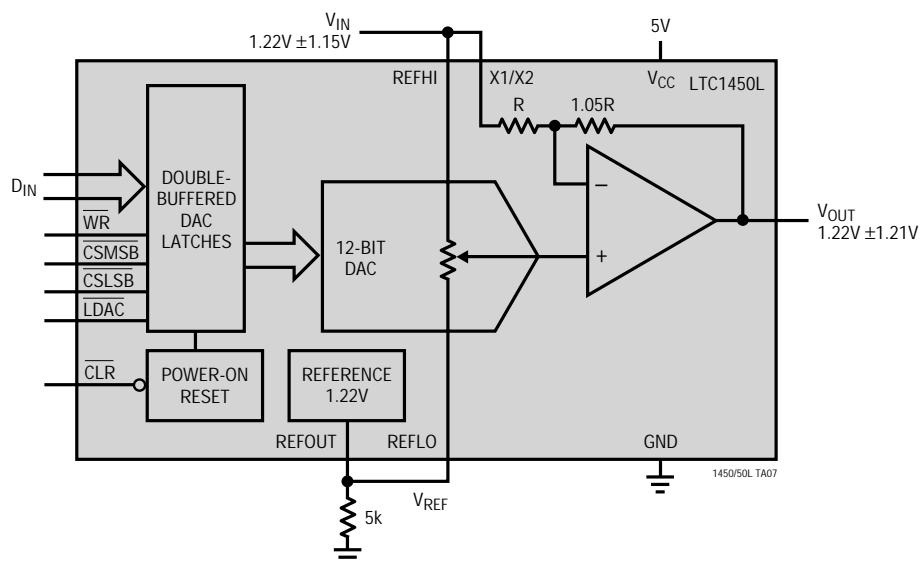

## Typical Application

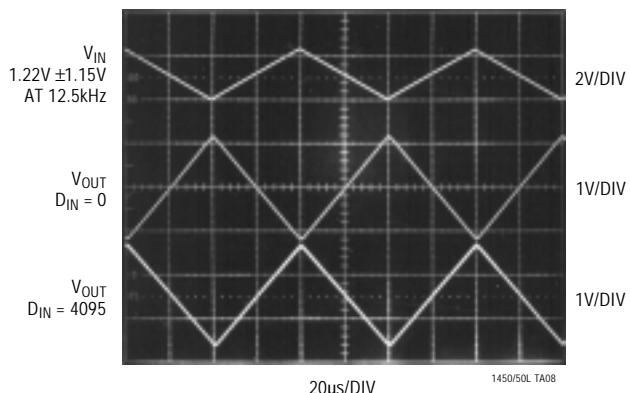

### 4象限乗算DACアプリケーション

このアプリケーションは、単一電源4象限乗算DACとして構成したLTC1450Lを示します。5V電源と1つの外部部品、すなわちREFOUTからグランドに接続した5k抵抗だけを使用します（LTC1450も同様な方法で使用できます）。乗算DACを使用すれば、ユーザは1.22Vリファレンス電圧によって供給されるオフセット信号グランドを中心電圧とするAC入力信号の振幅と極性をデジタル的に変化させることができます。以下の式に伝達関数を示します。

$$V_{\text{OUT}} = (V_{\text{IN}} - V_{\text{REF}}) \left[ \text{利得} \left( \frac{D_{\text{IN}}}{4096} - 1 \right) + 1 \right] + V_{\text{REF}}$$

LTC1450Lの場合は、利得 = 2.05、 $V_{\text{REF}} = 1.22\text{V}$ であり、次のようにになります。

$$V_{\text{OUT}} = (V_{\text{IN}} - 1.22\text{V}) \left[ 2.05 \left( \frac{D_{\text{IN}}}{4096} \right) - 1.05 \right] + 1.22\text{V}$$

表1に $V_{\text{OUT}}$ の式を、 $V_{\text{IN}}$ 、 $V_{\text{REF}}$ 、 $D_{\text{IN}}$ の関数として示します。スコープ写真に、12.5kHz、2.3V<sub>P-P</sub>の三角波入力信号と、対応する出力波形をゼロスケールおよびフルスケール・コードについて示します。

Table 1. Binary Code Table for 4-Quadrant, Multiplying DAC Application

| BINARY DIGITAL INPUT CODE IN DAC REGISTER |      | ANALOG OUTPUT ( $V_{\text{OUT}}$ )                             |

|-------------------------------------------|------|----------------------------------------------------------------|

| MSB                                       | LSB  |                                                                |

| 1111                                      | 1111 | $(4094/4096)(V_{\text{IN}} - V_{\text{REF}}) + V_{\text{REF}}$ |

| 1100                                      | 0001 | $0.5(V_{\text{IN}} - V_{\text{REF}}) + V_{\text{REF}}$         |

| 1000                                      | 0011 | $V_{\text{REF}}$                                               |

| 0100                                      | 0100 | $-0.5(V_{\text{IN}} - V_{\text{REF}}) + V_{\text{REF}}$        |

| 0000                                      | 0110 | $-1.0(V_{\text{IN}} - V_{\text{REF}}) + V_{\text{REF}}$        |

| 0000                                      | 0000 | $-1.05(V_{\text{IN}} - V_{\text{REF}}) + V_{\text{REF}}$       |

Clean 4-Quadrant Multiplying Is Shown in the Output Waveforms for Zero-Scale and Full-Scale DAC Settings

Internal Reference, REFLO/REFHI Pins, Gain Adjust and Wide Supply Voltage Range Allow 4-Quadrant Multiplying on a 5V Single Supply

# LTC1450/LTC1450L

---

## RELATED PARTS

| PART NUMBER             | DESCRIPTION                                                                | COMMENTS                                                                                                                |

|-------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| LTC1257                 | Complete Serial I/O $V_{OUT}$ 12-Bit DAC                                   | 5V to 15V Single Supply in 8-Pin SO and PDIP                                                                            |

| LTC1451/LTC1452/LTC1453 | Complete Serial I/O $V_{OUT}$ 12-Bit DACs                                  | 3V/5V Single Supply, Rail-to-Rail in 8-Pin SO and PDIP                                                                  |

| LTC1446/LTC1446L        | Dual 12-Bit $V_{OUT}$ DACs in SO-8 Package                                 | LTC1446: $V_{CC} = 4.5V$ TO 5.5V, $V_{OUT} = 0V$ TO 4.095V<br>LTC1446L: $V_{CC} = 2.7V$ to 5.5V, $V_{OUT} = 0V$ to 2.5V |

| LTC1454/LTC1454L        | Dual 12-Bit $V_{OUT}$ DACs in a 16-Pin SO Package with Added Functionality | LTC1454: $V_{CC} = 4.5V$ to 5.5V, $V_{OUT} = 0V$ TO 4.095V<br>LTC1454L: $V_{CC} = 2.7V$ to 5.5V, $V_{OUT} = 0V$ to 2.5V |

| LTC1458/LTC1458L        | Quad 12-Bit $V_{OUT}$ DACs in 28-Lead SW and SSOP Packages                 | LTC1458: $V_{CC} = 4.5V$ to 5.5V, $V_{OUT} = 0V$ to 4.095V<br>LTC1458L: $V_{CC} = 2.7V$ to 5.5V, $V_{OUT} = 0V$ to 2.5V |

| LTC7541A                | Parallel I/O Multiplying 12-Bit DAC                                        | 12-Bit Wide Input                                                                                                       |

| LTC7543/LTC8143         | Serial Multiplying 12-Bit DACs                                             | Daisy-Chainable, Flexible Analog and Digital Interface                                                                  |

| LTC7545A                | Parallel Latched Input Multiplying 12-Bit DAC                              | 12-Bit Wide Latched Input                                                                                               |

| LTC8043                 | Serial Multiplying 12-Bit DAC                                              | 8-Pin SO and PDIP                                                                                                       |