## 特長

- SO-8パッケージで供給

- 12ビット分解能

- バッファされた真のレール・トゥ・レール電圧出力

- 外部リファレンス入力を $V_{CC}$ に接続可能

- 0Vから $V_{REF}$ までの出力振幅

- 3Vおよび5V電源動作

- クロック入力のシムミット・トリガによりオプトカプラーへの直接インターフェースが可能

- パワーオン・リセットでDACを0Vにクリア

- 3線式シリアル・インターフェース

- **最大DNL誤差 : 0.5LSB**

- 低コスト

## アプリケーション

- デジタル較正

- 産業用プロセス・コントロール

- 自動試験装置

- セルラー電話

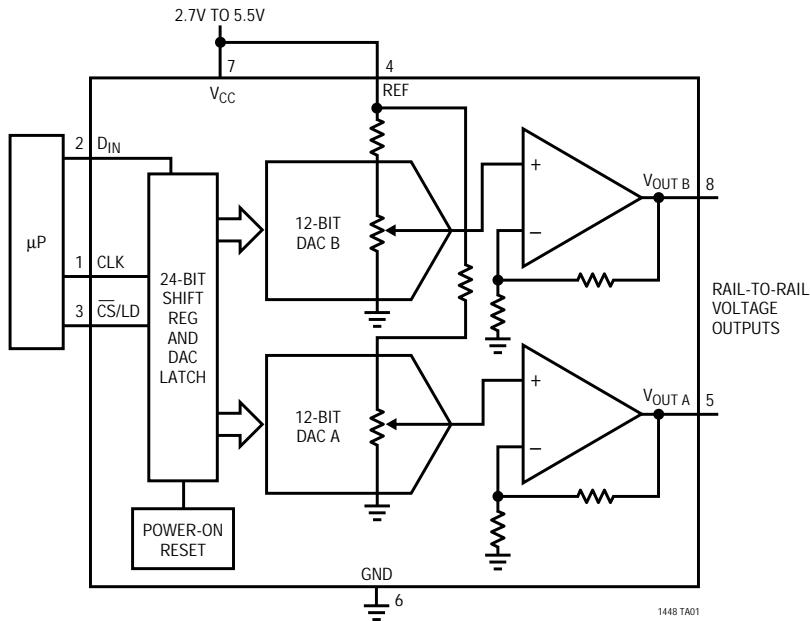

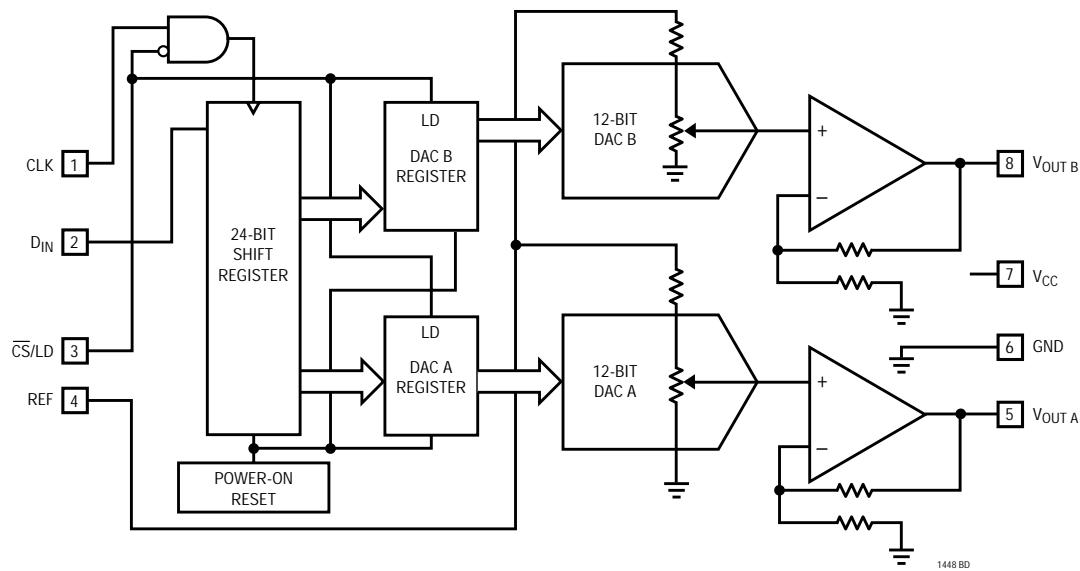

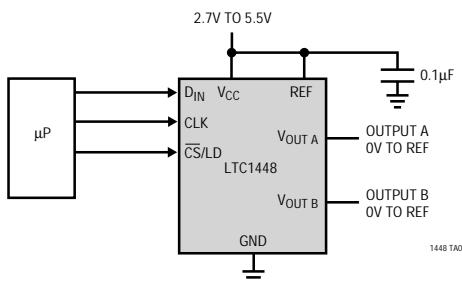

## 標準的応用例

機能ブロック図:12ビット・レール・トゥ・レール・デュアルDAC

## 概要

LTC<sup>®</sup>1448はデュアル・レール・トゥ・レール電圧出力、12ビット・デジタル-アナログ・コンバータ(DAC)です。レール・トゥ・レール出力バッファ・アンプと使いやすい3線式シリアル・インターフェースを内蔵しています。8ピンSOおよびPDIPパッケージで供給され、どのデュアル12ビットDACよりも実装面積が小さくなっています。

LTC1448には外部リファレンス入力ピン(REF)があり、出力は0V～REFまで振幅します。REF入力を $V_{CC}$ に接続すれば、2.7V～5.5Vの範囲のレール・トゥ・レール動作が可能です(リファレンス内蔵デバイスについては、LTC1446データシートを参照)。LTC1448の消費電力は5V電源で2.5mWです。

電源電流が低く小型SO-8パッケージで供給されるため、LTC1448はバッテリ駆動アプリケーションに最適です。

**LTC**、LTC、LTはリニアテクノロジー社の登録商標です。

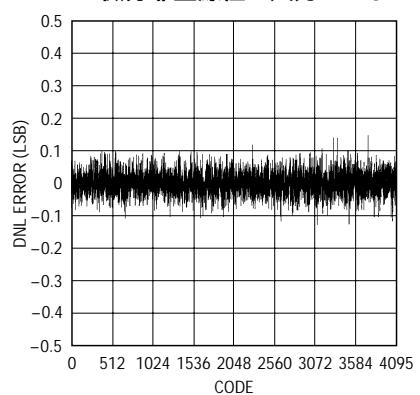

微分非直線性と入力コード

1448 TA02

## 絶対最大定格

|                                       |                          |

|---------------------------------------|--------------------------|

| $V_{CC}$ からGND                        | - 0.5V ~ 7.5V            |

| GNDに対するロジック入力                         | - 0.5V ~ 7.5V            |

| $V_{OUT\ A}$ 、 $V_{OUT\ B}$ 、REFからGND | - 0.5V ~ $V_{CC}$ + 0.5V |

| 最大接合部温度                               | 125                      |

| 動作温度範囲                                |                          |

| LTC1448C                              | 0 ~ 70                   |

| LTC1448I                              | - 40 ~ 85                |

| 保存温度範囲                                | - 65 ~ 150               |

| リード温度(半田付け、10秒)                       | 300                      |

## パッケージ/発注情報

| TOP VIEW                        | ORDER PART NUMBER        |

|---------------------------------|--------------------------|

|                                 | LTC1448CN8               |

| N8 PACKAGE<br>8-LEAD PDIP       | LTC1448IN8               |

| S8 PACKAGE<br>8-LEAD PLASTIC SO | LTC1448CS8<br>LTC1448IS8 |

| S8 PART MARKING                 |                          |

|                                 | 1448                     |

|                                 | 1448I                    |

ミリタリ・グレードに関してはお問い合わせください。

## 電気的特性

注記がない限り、 $V_{CC} = 2.7V \sim 5.5V$ 、 $V_{OUT\ A}$ および $V_{OUT\ B}$ 無負荷、 $REF \leq V_{CC}$ 、 $T_A = T_{MIN} \sim T_{MAX}$

| SYMBOL                | PARAMETER                                  | CONDITIONS                                                                                         | MIN | TYP       | MAX       | UNITS            |

|-----------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------|-----|-----------|-----------|------------------|

| DAC                   |                                            |                                                                                                    |     |           |           |                  |

|                       | Resolution                                 |                                                                                                    | ●   | 12        |           | Bits             |

|                       | Monotonicity                               |                                                                                                    | ●   | 12        |           | Bits             |

| DNL                   | Differential Nonlinearity                  | $V_{REF} \leq V_{CC} - 0.1V$ (Note 1)                                                              | ●   | $\pm 0.2$ | $\pm 0.5$ | LSB              |

| INL                   | Integral Nonlinearity                      | $V_{REF} \leq V_{CC} - 0.1V$ (Note 1), $T_A = 25^\circ C$<br>$V_{REF} \leq V_{CC} - 0.1V$ (Note 1) | ●   | $\pm 5.0$ | $\pm 5.5$ | LSB              |

| $V_{OS}$              | Offset Error                               | Measured at Code 20, $T_A = 25^\circ C$<br>Measured at Code 20                                     | ●   | $\pm 10$  | $\pm 15$  | mV<br>mV         |

| $V_{OS}TC$            | Offset Error Temperature Coefficient       |                                                                                                    |     | $\pm 15$  |           | $\mu V/^\circ C$ |

| $V_{FS}$              | Full-Scale Voltage                         | $V_{REF} = 4.096V$ , $T_A = 25^\circ C$<br>$V_{REF} = 4.096V$                                      | ●   | 4.070     | 4.095     | 4.120            |

| $V_{FS}TC$            | Full-Scale Voltage Temperature Coefficient |                                                                                                    |     | 4.060     | 4.095     | 4.130            |

| Power Supply          |                                            |                                                                                                    |     |           |           |                  |

| $V_{CC}$              | Positive Supply Voltage                    | For Specified Performance                                                                          | ●   | 2.7       | 5.5       | V                |

| $I_{CC}$              | Supply Current                             | (Note 4)                                                                                           | ●   | 450       | 700       | $\mu A$          |

| Op Amp DC Performance |                                            |                                                                                                    |     |           |           |                  |

|                       | Short-Circuit Current Low                  | $V_{OUT}$ Shorted to GND                                                                           | ●   | 55        | 120       | mA               |

|                       | Short-Circuit Current High                 | $V_{OUT}$ Shorted to $V_{CC}$                                                                      | ●   | 65        | 120       | mA               |

|                       | Output Impedance to GND                    | Input Code = 0                                                                                     | ●   | 30        | 120       | $\Omega$         |

|                       | Output Line Regulation                     | Input Code = 4095. $V_{CC} = 4.5V$ to $5.5V$ , $V_{REF} = 4.096V$                                  | ●   | 0.2       | 1.5       | LSB/V            |

## 電気的特性

注記がない限り、 $V_{CC} = 2.7V \sim 5.5V$ 、 $V_{OUT\ A}$ および $V_{OUT\ B}$ 無負荷、 $REF \leq V_{CC}$ 、 $T_A = T_{MIN} \sim T_{MAX}$

| SYMBOL                                                             | PARAMETER                         | CONDITIONS                     | MIN    | TYP        | MAX        | UNITS        |            |

|--------------------------------------------------------------------|-----------------------------------|--------------------------------|--------|------------|------------|--------------|------------|

| <b>AC Performance</b>                                              |                                   |                                |        |            |            |              |            |

|                                                                    | Voltage Output Slew Rate          |                                | ●      | 0.5        | 1.0        | V/ $\mu$ s   |            |

|                                                                    | Voltage Output Settling Time      | (Notes 2, 3) to $\pm 0.5$ LSB  |        |            | 14         | $\mu$ s      |            |

|                                                                    | Digital Feedthrough               |                                |        |            | 0.3        | nV $\cdot$ s |            |

| <b>Reference Input</b>                                             |                                   |                                |        |            |            |              |            |

| $R_{IN}$                                                           | REF Input Resistance              |                                | ●      | 7.5        | 12.5       | 18           | k $\Omega$ |

| REF                                                                | REF Input Range                   | (Notes 5, 6)                   | ●      | 0          | $V_{CC}$   | V            |            |

| <b>Digital I/O</b>                                                 |                                   |                                |        |            |            |              |            |

| $V_{IH}$                                                           | Digital Input High Voltage        | $V_{CC} = 5V$<br>$V_{CC} = 3V$ | ●<br>● | 2.4<br>2.0 |            | V            | V          |

| $V_{IL}$                                                           | Digital Input Low Voltage         | $V_{CC} = 5V$<br>$V_{CC} = 3V$ | ●<br>● |            | 0.8<br>0.6 | V            | V          |

| $I_{LEAK}$                                                         | Digital Input Leakage             | $V_{IN} = GND$ to $V_{CC}$     | ●      |            | $\pm 10$   | $\mu$ A      |            |

| $C_{IN}$                                                           | Digital Input Capacitance         | (Note 6)                       | ●      |            | 10         | pF           |            |

| <b>Switching (<math>V_{CC} = 4.5V</math> to <math>5.5V</math>)</b> |                                   |                                |        |            |            |              |            |

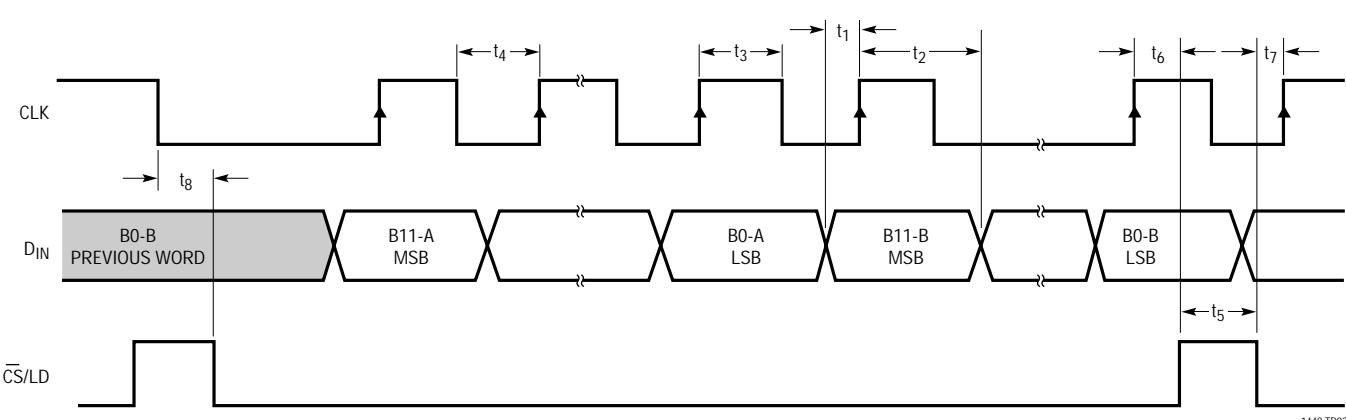

| $t_1$                                                              | $D_{IN}$ Valid to CLK Setup       |                                | ●      | 40         |            | ns           |            |

| $t_2$                                                              | $D_{IN}$ Valid to CLK Hold        |                                | ●      | 0          |            | ns           |            |

| $t_3$                                                              | CLK High Time                     | (Note 6)                       | ●      | 40         |            | ns           |            |

| $t_4$                                                              | CLK Low Time                      | (Note 6)                       | ●      | 40         |            | ns           |            |

| $t_5$                                                              | $\overline{CS}/LD$ Pulse Width    | (Note 6)                       | ●      | 50         |            | ns           |            |

| $t_6$                                                              | LSB CLK to $\overline{CS}/LD$     | (Note 6)                       | ●      | 40         |            | ns           |            |

| $t_7$                                                              | $\overline{CS}/LD$ Low to CLK     | (Note 6)                       | ●      | 20         |            | ns           |            |

| $t_8$                                                              | CLK Low to $\overline{CS}/LD$ Low | (Note 6)                       | ●      | 20         |            | ns           |            |

| <b>Switching (<math>V_{CC} = 2.7V</math> to <math>5.5V</math>)</b> |                                   |                                |        |            |            |              |            |

| $t_1$                                                              | $D_{IN}$ Valid to CLK Setup       |                                | ●      | 60         |            | ns           |            |

| $t_2$                                                              | $D_{IN}$ Valid to CLK Hold        |                                | ●      | 0          |            | ns           |            |

| $t_3$                                                              | CLK High Time                     | (Note 6)                       | ●      | 60         |            | ns           |            |

| $t_4$                                                              | CLK Low Time                      | (Note 6)                       | ●      | 60         |            | ns           |            |

| $t_5$                                                              | $\overline{CS}/LD$ Pulse Width    | (Note 6)                       | ●      | 80         |            | ns           |            |

| $t_6$                                                              | LSB CLK to $\overline{CS}/LD$     | (Note 6)                       | ●      | 60         |            | ns           |            |

| $t_7$                                                              | $\overline{CS}/LD$ Low to CLK     | (Note 6)                       | ●      | 30         |            | ns           |            |

| $t_8$                                                              | CLK Low to $\overline{CS}/LD$ Low | (Note 6)                       | ●      | 30         |            | ns           |            |

●は全動作温度範囲の規格値を意味する。

Note 1 : 非直線性はコード20からコード4095(フルスケール)までの範囲で定義される。アプリケーション情報を参照。

Note 2 : 負荷は5k $\Omega$ と100pFを並列に接続したものである。Note 3 : DACは、オール1とICの $V_{OS}$ に対応するコードの間で切り替わる。Note 4 : デジタル入力は0Vまたは $V_{CC}$ 。Note 5 : 出力無負荷時には $V_{OUT}$ は( $GND + |V_{OS}|$ )から( $V_{CC} - |V_{OS}|$ )まで振幅する。

Note 6 : 設計で保証されているが、テストされていない。

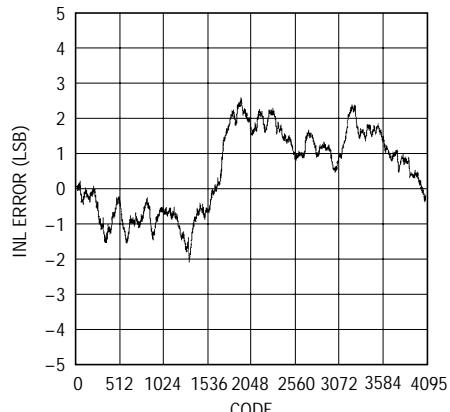

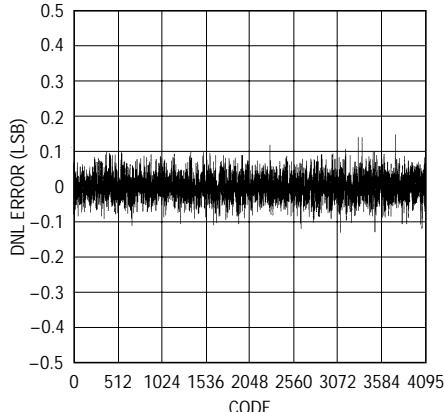

## 標準的性能特性

積分非直線性(INL)

微分非直線性(DNL)

全出力振幅に対する最小電源

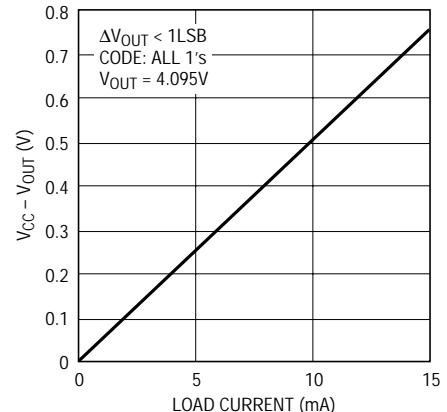

ヘッドルームと負荷電流

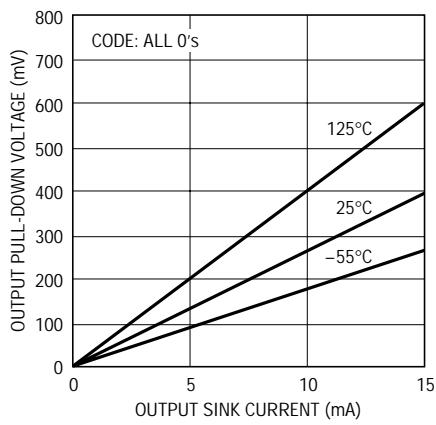

最小出力電圧と出力シンク電流

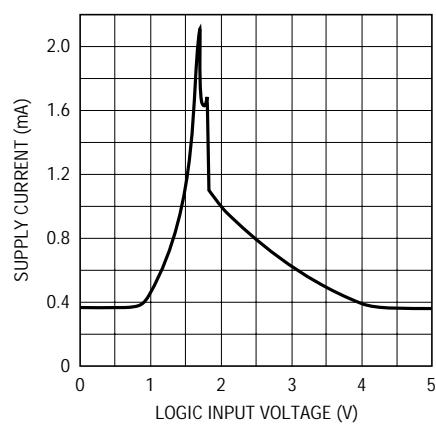

電源電流と

ロジック入力電圧

6

## ピン機能

CLK(ピン1): シリアル・インターフェース・クロック。この入力の内部シュミット・トリガにより、オプトカプラーと直接インターフェースできます。

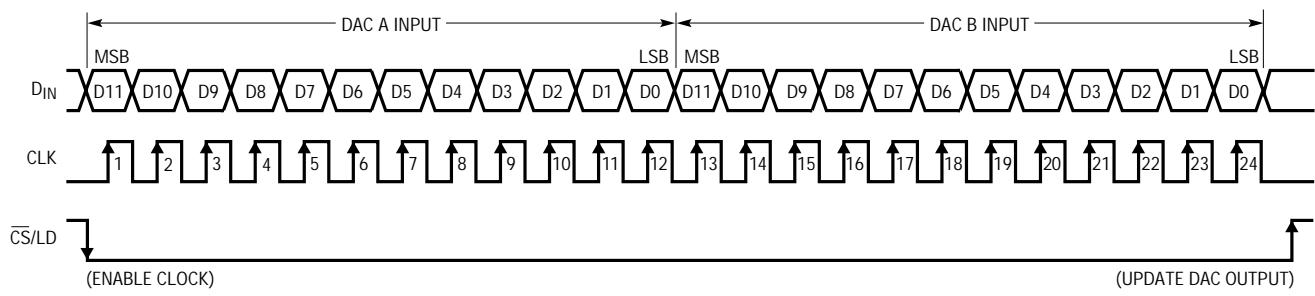

D<sub>IN</sub>(ピン2): シリアル・インターフェース・データ。D<sub>IN</sub>ピン上の入力データは、シリアル・クロックの立上りエッジでシフト・レジスタにラッチされます。

CS/LD(ピン3): シリアル・インターフェース・イネーブルおよびロード・コントロール。CS/LDが" L "のとき、CLK信号がイネーブルされデータをクロック・インすることができます。CS/LDが" H "になると、シフトレジス

タからDACレジスタにデータがロードされ、内部でDAC出力が更新されCLKがディスエーブルされます。

REF(ピン4): 両方のDAC用のリファレンス入力。このピンはV<sub>CC</sub>に接続できます。出力は0VからREFまで振幅します。標準入力抵抗は12.5kです。

V<sub>OUTA</sub>, V<sub>OUTB</sub>(ピン5, 8): バッファされたDAC出力

GND(ピン6): グラウンド。

V<sub>CC</sub>(ピン7): 正電源入力。2.7V ≤ V<sub>CC</sub> ≤ 5.5V。グラウンドへのバイパス・コンデンサが必要です。

## プロック図

## タイミング図

### OPERATING SEQUENCE

## 定義

微分非直線性( DNL )：任意の2つの隣接するコード間で測定した変化と理想的な1LSB変化の違いです。2つのコード間のDNL誤差は、次式で計算されます。

$$DNL = (\Delta V_{OUT} - LSB) / LSB$$

ここで、 $\Delta V_{OUT}$ は2つの隣接するコード間で測定した電圧の差です。

デジタル・フィードスルー：デジタル入力が状態を変えたときに、その入力からのAC結合によって生じるアナログ出力に現れるグリッチです。グリッチの面積は( $nV$ )(sec)で規定されます。

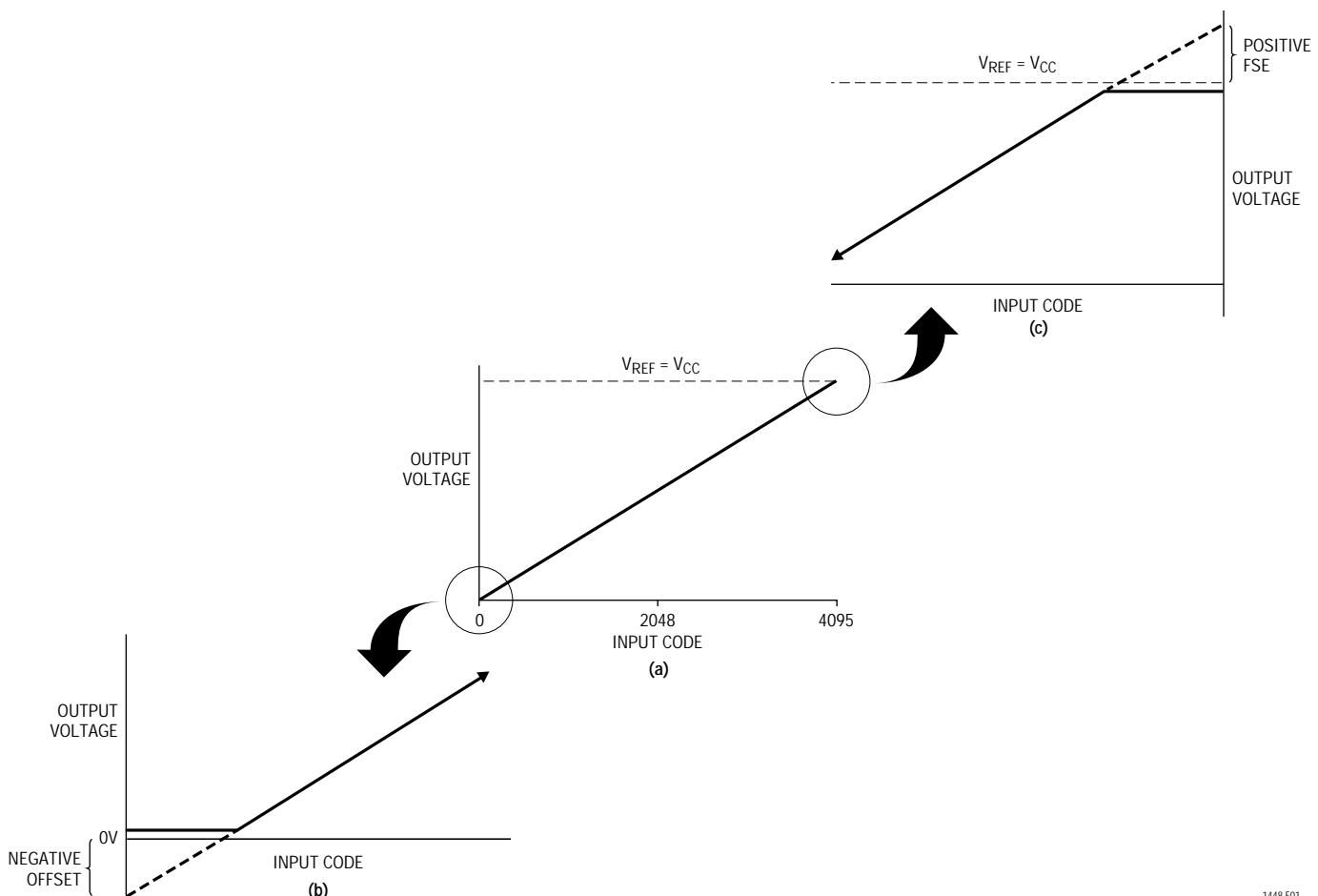

フルスケール誤差( FSE )：理想的な電圧からの実際のフルスケール電圧の偏差です。FSEにはオフセット誤差と利得誤差の影響が含まれます( アプリケーション情報を参照 )。

積分非直線性( INL )：DAC伝達曲線のエンド・ポイントを通過する直線からの偏差です( エンド・ポイントINL )。出力はゼロ以下になれないため、直線性はフルスケールと、出力がゼロを超えることを保証する最小

コード間で測定されます。ある入力コードに対するINL誤差は、次式で計算されます。

$$INL = [V_{OUT} - V_{OS} - (V_{FS} - V_{OS})(code/4095)]/LSB$$

ここで、 $V_{OUT}$ は与えられた入力コードで測定したDACの出力電圧です。

最下位ビット( LSB )：2つの連続したコードの理想的な電圧差です。

$$LSB = V_{REF}/4096$$

分解能( n )：フルスケール・レンジを分割するDAC出力の状態数( $2^n$ )を定義します。分解能は直線性を意味するものではありません。

電圧オフセット誤差(  $V_{OS}$  )：定義上、DACにすべてゼロがロードされたときの出力の電圧です。単一電源DACは真の負のオフセットを持つことができますが、出力はゼロ以下になりません( アプリケーション情報を参照 )。

このため、単一電源DACオフセットは、出力がゼロを超えることを保証する最小コードで測定されます。

## 動作

### シリアル・インターフェース

DIN入力のデータは、クロックの立上りエッジでシフト・レジスタにロードされます。データは1つの24ビット・ワードとしてロードされ、最初の12ビットはDAC Aに、そして2番目の12ビットはDAC Bに送られます。各12ビット・セグメントでは、MSBが最初にロードされます。シフト・レジスタからのデータは、 $\overline{CS}/LD$ が" H "になると、DACレジスタにロードされます。 $\overline{CS}/LD$ が" H "のとき、クロックは内部でディスエーブルされます。注：余分な内部クロック・パルスを避けるために、 $\overline{CS}/LD$ が" L "にプルダウンされる前に、CLKが" L "にならなければなりません。

### 電圧出力

LTC1448のレール・トゥ・レールのバッファ出力は、正電源電圧またはグランドの300mV以内に維持しながら全

動作温度範囲で5mAをソースまたはシンクできます。無負荷時には出力はいずれかの電源レールの数mV以内に振幅し、負荷をレールにドライブする場合には等価出力抵抗は30 $\Omega$ になります。出力は発振することなく1000pFをドライブ可能です。

出力は0VからREFピンの電圧まで振幅します。すなわち、REFから $V_{OUT}$ までの利得は1です。REFを $V_{CC}$ に接続した場合は、出力が( $V_{CC} - V_{OS}$ )まで振幅することに注意してください。アプリケーション情報を参照。

## アプリケーション情報

### レール・トゥ・レール出力の考慮事項

どんなレール・トゥ・レールDACでも、出力振幅は電源範囲内の電圧に制限されます。

DACオフセットが負の場合、最小コードの出力は、図1bに示すとおり0Vに制限されます。

同様に、REFピンを $V_{CC}$ に接続したとき、フルスケール

の近くでリミッティングが発生します。 $V_{REF} = V_{CC}$ でDACフルスケール誤差(FSE)が正の場合、最大コードの出力は図1cに示すとおり $V_{CC}$ に制限されます。 $V_{REF}$ が $V_{CC}$  - FSE未満の場合は、フルスケール・リミッティングは生じません。

オフセットと直線性は、出力リミッティングが発生しないDAC伝達関数領域で定義され、テストされます。

図1. レール・トゥ・レール動作のDAC伝達曲線での影響：(a) 全伝達関数、(b) ゼロ・スケール近くのコードに対する負オフセットの影響、(c)  $V_{REF} = V_{CC}$ のときのフルスケール近くの入力コードに対する正フルスケール誤差の影響

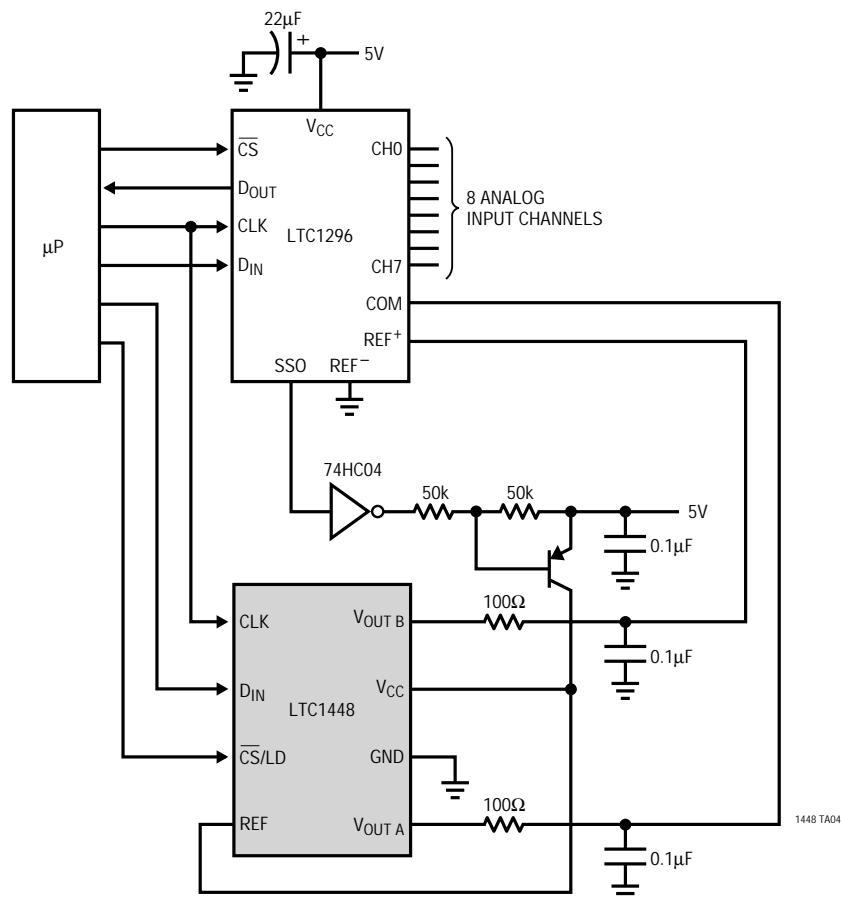

## 標準的应用例

この回路は、1個のLTC1448を使用してオートレンジングADCを構築する方法を示します。マイクロプロセッサは、LTC1448に適切なデジタルコードをロードすることによって、アナログ入力のリファレンス幅と共通ピンを設定します。 $V_{OUT_A}$ はLTC1296のアナログ入力の共通ピンをコントロールし、 $V_{OUT_B}$ はLTC1296のREF<sup>+</sup>ピン

をセットして、リファレンス幅をコントロールします。LTC1296にはシャットダウン・モードで“L”になるシャットダウン・ピンもあります。これはLTC1448に電源を供給するPNPトランジスタをターンオフします。LTC1448出力の抵抗とコンデンサは、ノイズに対するローパス・フィルタとして働きます。

## シャットダウン機能付きオートレンジ8チャネルADC

## 標準的応用例

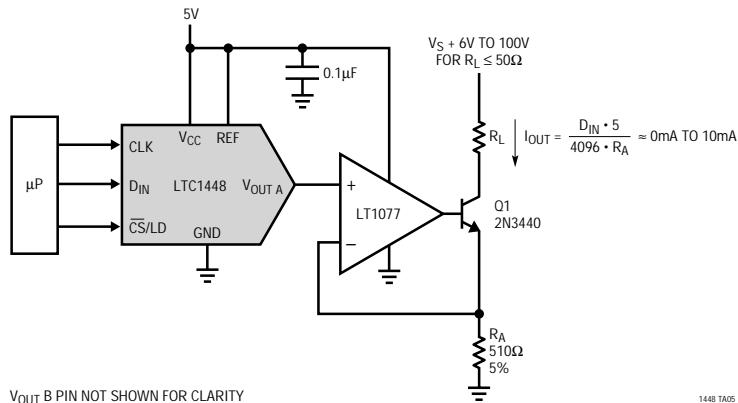

### デジタル的にプログラム可能な電流源

### 12ビット、3V～5V電源、デュアル電圧出力DAC

## 関連製品

| 製品番号             | 説明                                                                                                                       | 注釈                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| LTC1257          | シングル12ビットV <sub>OUT</sub> DAC、フルスケール:2.048V、V <sub>CC</sub> :4.75V～15.75V、12Vまでリファレンスでオーバードライブ可能、FS <sub>MAX</sub> = 12V | 5V～15V単一電源、SO-8パッケージの完全なV <sub>OUT</sub> DAC                                                                                        |

| LTC1446/LTC1446L | SO-8パッケージの内部リファレンス付きデュアル12ビットV <sub>OUT</sub> DAC                                                                        | LTC1446:V <sub>CC</sub> = 4.5V～5.5V、V <sub>OUT</sub> = 0V～4.095V<br>LTC1446L:V <sub>CC</sub> = 2.7V～5.5V、V <sub>OUT</sub> = 0V～2.5V |

| LTC1450/LTC1450L | パラレル・インターフェース付きシングル12ビットV <sub>OUT</sub> DAC                                                                             | LTC1450:V <sub>CC</sub> = 4.5V～5.5V、V <sub>OUT</sub> = 0V～4.095V<br>LTC1450L:V <sub>CC</sub> = 2.7V～5.5V、V <sub>OUT</sub> = 0V～2.5V |

| LTC1451          | シングル、レール・トゥ・レール12ビットDAC、フル・スケール:4.095V、V <sub>CC</sub> :4.5V～5.5V、ピンに出された内部2.048Vリファレンス                                  | SO-8パッケージの5V、低消費電力の完全なV <sub>OUT</sub> DAC                                                                                          |

| LTC1452          | シングル、レール・トゥ・レール12ビットV <sub>OUT</sub> 乗算DAC、V <sub>CC</sub> :2.7V～5.5V                                                    | SO-8パッケージのレール・トゥ・レール・バッファ・アンプ付き低消費電力、乗算型V <sub>OUT</sub> DAC                                                                        |

| LTC1453          | シングル、レール・トゥ・レール12ビットV <sub>OUT</sub> DAC、フルスケール:2.5V、V <sub>CC</sub> :2.7V～5.5V                                          | SO-8パッケージの3V、低消費電力、完全なV <sub>OUT</sub> DAC                                                                                          |

| LTC1454/LTC1454L | 追加機能付きSO-16パッケージのデュアル12ビットV <sub>OUT</sub> DAC                                                                           | LTC1454:V <sub>CC</sub> = 4.5V～5.5V、V <sub>OUT</sub> = 0V～4.095V<br>LTC1454L:V <sub>CC</sub> = 2.7V～5.5V、V <sub>OUT</sub> = 0V～2.5V |

| LTC1456          | クリア・ピン付き、シングル、レール・トゥ・レール出力12ビットDAC、フルスケール:4.095V、V <sub>CC</sub> :4.5V～5.5V                                              | SO-8パッケージのクリア・ピン付き低消費電力の完全なV <sub>OUT</sub> DAC                                                                                     |

| LTC1458/LTC1458L | 追加機能付きクワッド12ビットレール・トゥ・レール出力DAC                                                                                           | LTC1458:V <sub>CC</sub> = 4.5V～5.5V、V <sub>OUT</sub> = 0V～4.095V<br>LTC1458L:V <sub>CC</sub> = 2.7V～5.5V、V <sub>OUT</sub> = 0V～2.5V |

| LTC1659          | シングル・レール・トゥ・レール12ビットV <sub>OUT</sub> DAC、MSOP-8パッケージ、V <sub>CC</sub> = 2.7V～5.5V                                         | MSOP-8パッケージの低消費電力乗算型V <sub>OUT</sub> DAC。出力はGNDからREFまで振幅。REF入力をV <sub>CC</sub> に接続可能。                                               |