# 5V出力の絶縁型 フライバック スイッチング・レギュレータ

1998年7月

## 特長

- トランジスタの“3次巻線”やオプトアイソレータが不要

- 1:1のトランジスタ用に設計

- 固定5V出力電圧向けアプリケーション

- 不連続モードでレギュレーションを維持(軽負荷時)

- 負荷補償により卓越したロード・レギュレーションを提供

- 8ピンPDIPおよびSOパッケージで供給

- 動作周波数: 285kHz

## アプリケーション

- 絶縁型通信電源

- 産業オートメーション

- 計測システム

## 概要

LT<sup>®</sup>1424-5は特に絶縁型フライバック・トポロジーのために設計されたモノリシック高電力スイッチング・レギュレータです。“3次巻線”やオプトアイソレータは必要ありません。集積回路が一次側フライバック波形から絶縁出力電圧を直接検知します。高電流、高効率スイッチがすべての発振器、制御、および保護回路と併せてダイに搭載されています。

LT1424-5は3Vから20Vの入力電源電圧で動作し、消費電流はわずか7mAです。外付けパワー・デバイスなしで、5Vで最大400mAを供給できます。電流モード・スイッチング技術を利用しているため、優れたACおよびDCライン・レギュレーションを提供します。

LT1424-5は他のスイッチング・レギュレータICには見られない多くの特長を備えています。独自の制御回路によって不連続モードでもレギュレーションを維持できます。負荷補償回路によりロード・レギュレーションを改善しています。外部から操作できるシャットダウン・モードでは、全消費電流を待機動作で標準20μAまで低減できます。

LTC、LTはリニアテクノロジー社の登録商標です。

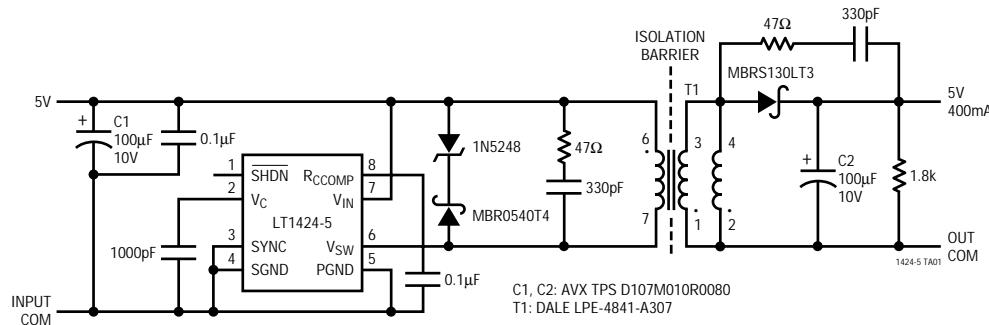

## 標準的応用例

### 5V出力の絶縁電源

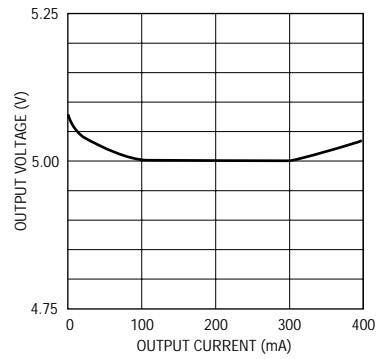

### ロード・レギュレーション

## 絶対最大定格

|                    |            |

|--------------------|------------|

| 電源電圧( $V_{IN}$ )   | 20V        |

| スイッチ電圧( $V_{SW}$ ) | 35V        |

| SHDN、SYNCピン電圧      | 7V         |

| 動作接合部温度範囲          |            |

| コマーシャル             | 0 ~ 100    |

| インダストリアル           | - 40 ~ 100 |

| 保存温度範囲             | - 65 ~ 150 |

| リード温度( 半田付け、10秒 )  | 300        |

## パッケージ/発注情報

| ORDER PART NUMBER |

|-------------------|

| LT1424CN8-5       |

| LT1424CS8-5       |

| LT1424IN8-5       |

| LT1424IS8-5       |

| S8 PART MARKING   |

| 14245             |

| 14245I            |

TOP VIEW

$T_{JMAX} = 145^{\circ}\text{C}$ ,  $\theta_{JA} = 130^{\circ}\text{C}/\text{W}$  (N)

$T_{JMAX} = 145^{\circ}\text{C}$ ,  $\theta_{JA} = 110^{\circ}\text{C}/\text{W}$  (S)

ミリタリ・グレードに関してはお問い合わせください。

電気的特性 注記がない限り、 $V_{IN} = 5\text{V}$ 、 $T_J = 25^{\circ}\text{C}$ 、 $V_{SW}$ はオープン、 $V_C = 1.4\text{V}$

| SYMBOL                    | PARAMETER                                  | CONDITIONS                                                                                                                                                               | MIN | TYP  | MAX  | UNITS         |                 |

|---------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|---------------|-----------------|

| <b>Power Supply</b>       |                                            |                                                                                                                                                                          |     |      |      |               |                 |

| $V_{IN(MIN)}$             | Minimum Operating Voltage                  |                                                                                                                                                                          | ●   | 2.8  | 3.1  | V             |                 |

| $I_{CC}$                  | Supply Current                             |                                                                                                                                                                          | ●   | 7.0  | 9.5  | mA            |                 |

|                           | Shutdown Mode Supply Current               |                                                                                                                                                                          | ●   | 15   | 40   | $\mu\text{A}$ |                 |

|                           | SHDN Pin Threshold                         |                                                                                                                                                                          | ●   | 0.4  | 0.9  | 1.3           | V               |

| <b>Feedback Amplifier</b> |                                            |                                                                                                                                                                          |     |      |      |               |                 |

| $V_{REF}$                 | Reference Voltage                          | Measured at $V_{SW}$ Pin (Note 3)                                                                                                                                        | ●   | 5.23 | 5.30 | 5.37          | V               |

|                           |                                            |                                                                                                                                                                          | ●   | 5.18 | 5.30 | 5.42          | V               |

| $g_m$                     | Feedback Amplifier Transconductance        | $\Delta I_C = \pm 10\mu\text{A}$ (Note 1)                                                                                                                                | ●   | 400  | 1000 | 1600          | $\mu\text{mho}$ |

| $I_{SOURCE}, I_{SINK}$    | Feedback Amplifier Source or Sink Current  |                                                                                                                                                                          | ●   | 30   | 50   | 80            | $\mu\text{A}$   |

| $V_{CL}$                  | Feedback Amplifier Clamp Voltage           |                                                                                                                                                                          |     |      | 1.9  |               | V               |

|                           | Reference Voltage/Current Line Regulation  | $5\text{V} \leq V_{IN} \leq 18\text{V}$                                                                                                                                  | ●   | 0.01 | 0.04 |               | %/V             |

|                           | Voltage Gain                               | (Note 2)                                                                                                                                                                 |     |      | 500  |               | V/V             |

| <b>Output Switch</b>      |                                            |                                                                                                                                                                          |     |      |      |               |                 |

| $BV$                      | Output Switch Breakdown Voltage            | $I_C = 5\text{mA}$                                                                                                                                                       | ●   | 35   | 50   |               | V               |

| $V(V_{SW})$               | Output Switch ON Voltage                   | $I_{SW} = 1\text{A}$                                                                                                                                                     | ●   |      | 0.55 | 0.85          | V               |

| $I_{LIM}$                 | Switch Current Limit                       | Duty Cycle = 50%, $0^{\circ}\text{C} \leq T_J \leq 100^{\circ}\text{C}$<br>Duty Cycle = 50%, $-40^{\circ}\text{C} \leq T_J \leq 100^{\circ}\text{C}$<br>Duty Cycle = 80% | ●   | 1.35 | 1.55 | 1.90          | A               |

|                           |                                            |                                                                                                                                                                          | ●   | 1.25 | 1.55 | 1.90          | A               |

|                           |                                            |                                                                                                                                                                          |     |      | 1.3  |               | A               |

| <b>Current Amplifier</b>  |                                            |                                                                                                                                                                          |     |      |      |               |                 |

|                           | Control Pin Threshold                      | Duty Cycle = Minimum                                                                                                                                                     | ●   | 0.95 | 1.2  | 1.3           | V               |

|                           |                                            |                                                                                                                                                                          | ●   | 0.85 | 1.2  | 1.4           | V               |

|                           | Control Voltage to Switch Transconductance |                                                                                                                                                                          |     |      | 2    |               | A/V             |

## 電気的特性

注記がない限り、 $V_{IN} = 5V$ 、 $T_J = 25^\circ C$ 、 $V_{SW}$ はオープン、 $V_C = 1.4V$

| SYMBOL                   | PARAMETER                      | CONDITIONS | MIN             | TYP        | MAX        | UNITS      |

|--------------------------|--------------------------------|------------|-----------------|------------|------------|------------|

| <b>Timing</b>            |                                |            |                 |            |            |            |

| f                        | Switching Frequency            |            | ●<br>260<br>240 | 285<br>285 | 300<br>320 | kHz<br>kHz |

| $t_{ON}$                 | Minimum Switch ON Time         |            |                 | 170        | 200        | 260        |

| $t_{ED}$                 | Flyback Enable Delay Time      |            |                 |            | 150        | ns         |

| $t_{EN}$                 | Minimum Flyback Enable Time    |            |                 |            | 180        | ns         |

|                          | Maximum Switch Duty Cycle      |            | ●               | 85         | 90         | 95         |

| <b>Load Compensation</b> |                                |            |                 |            |            |            |

|                          | $\Delta V_{REF}/\Delta I_{SW}$ |            |                 |            | 0.9        | $\Omega$   |

| <b>SYNC Function</b>     |                                |            |                 |            |            |            |

|                          | Minimum SYNC Amplitude         |            | ●               | 1.5        | 2.2        | V          |

|                          | Synchronization Range          |            | ●               | 320        | 450        | kHz        |

|                          | SYNC Pin Input Resistance      |            |                 |            | 40         | $k\Omega$  |

●は全動作温度範囲の規格値を意味する。

Note 1: 帰還アンプの相互コンダクタンスは $R_{REF}$ を基準にしている。

Note 2: 電圧ゲインは $R_{REF}$ を基準にしている。

Note 3:  $V_{REF}$ は $V_{SW}$ ピンで測定されるパラメータ。出力電圧とは異なる。出力電圧は出力ダイオード損失やトランジス・リーカ・インダクタンス等を収支したもの。目的のアプリケーション回路での公称出力電圧は5Vである。

## ピン機能

**SHDN( ピン1 )**: シャットダウン。このピンを使用してレギュレータをターンオフし、 $V_{IN}$ 入力電流を数十マイクロアンペアに低減します。使用しないときはSHDNピンをフロートさせておくことができます。

**$V_C$  ( ピン2 )**: 制御電圧。このピンは帰還アンプの出力で、電流コンパレータの入力でもあります。全ループの周波数補償はこのノードとグランドの間にコンデンサを配置して行います。

**SYNC( ピン3 )**: 内部発振器を外部周波数基準に同期させるピンです。このピンはロジックレベル・コンパチブルで、デューティ・サイクルが10%から90%の信号でドライブできます。使用しない場合、このピンはグランドに接続しておきます。

**SGND( ピン4 )**: 信号グランド。このピンはクリーンなグランドです。内部リファレンスおよび帰還アンプはこれを基準にします。 $V_C$ 補償コンデンサとグランド・バスとの接続は大きなグランド電流が影響しないようにしてください。

**PGND( ピン5 )**: パワー・グランド。このピンはパワースイッチ・デバイスのエミッタで、大きな電流が流れます。良質のグランド・プレーンに直接接続しなければなりません。

**$V_{SW}$  ( ピン6 )**: これは出力スイッチのコレクタ・ノードで、大きな電流が流れます。電磁放射や電圧スパイクを最小限に抑えるため、スイッチング部品に接続されるトレースを可能な限り短くしてください。

**$V_{IN}$  ( ピン7 )**: 電源電圧。入力電源ピンを10 $\mu$ F以上のコンデンサでバイパスします。 $V_{IN}$ が2.8Vより低下するとICは低電圧ロックアウトに入ります。低電圧ロックアウト時には、スイッチングは停止し $V_C$ ピンは“L”になります。

**$R_{CCOMP}$  ( ピン8 )**: 負荷補償機能のための外部フィルタ・コンデンサ用のピンです。標準0.1 $\mu$ Fセラミック・コンデンサで十分です。

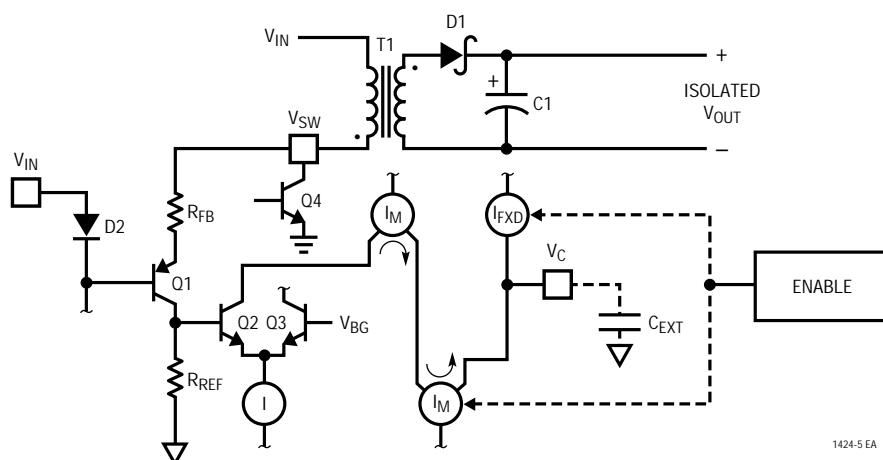

## プロック図

4

## フライバック誤差アンプ図

1424-5 EA

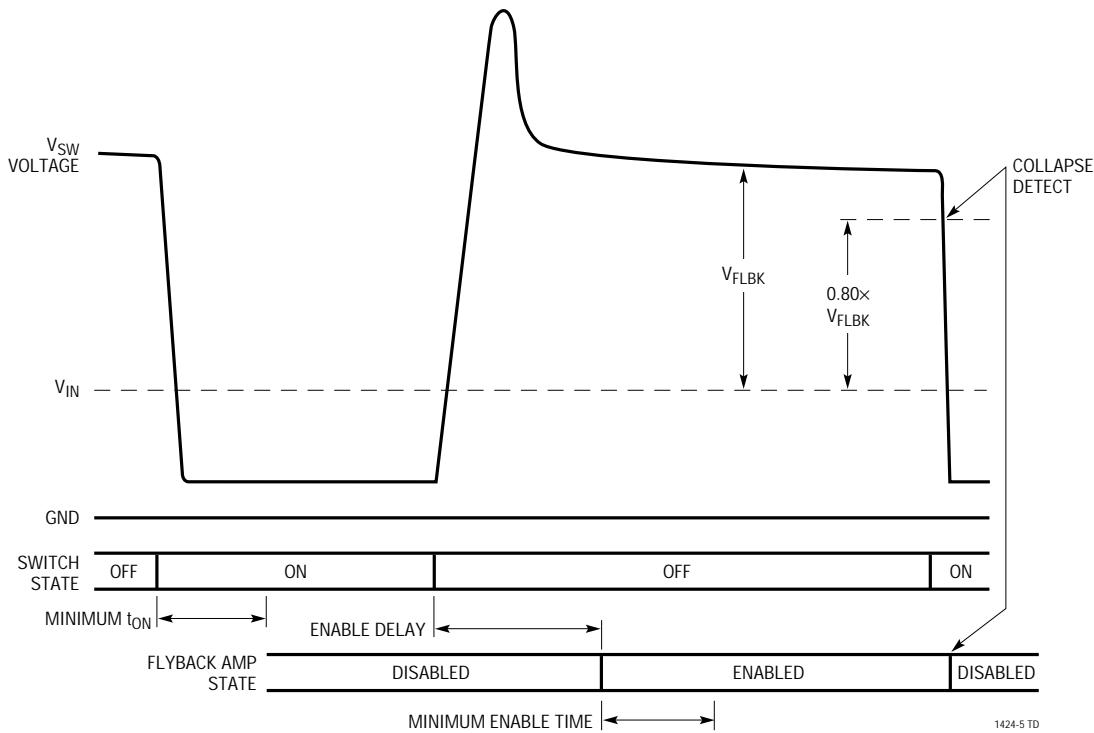

## タイミング図

## 動作

LT1424-5は特に絶縁型フライバック・トポロジーのため設計された電流モード・スイッチング・レギュレータICです。このような回路で通常遭遇する特別な問題として、レギュレーションを維持するためトランジスタの絶縁された二次側の出力電圧に関する情報が、一次側に伝達されなければならぬことがあります。これは、過去においてはオプトアイソレータまたは追加トランジスタによって行われてきました。オプトアイソレータ回路では出力電力と追加部品が必要であり、電源のコストと物理的容積が増加します。また、オプトアイソレータでは制限されたダイナミック応答(瞬間的な)非直線性、および個体間のバラツキ、および経年劣化による問題も発生します。追加トランジスタを用いた回路でも問題が起こります。追加トランジスタを使用するとトランジスタの物理的サイズとコストの追加が生じます。そのダイナミック応答はほとんどの場合は平凡なものです。一般に、負荷に応じてロード・レギュレーションを維持する方法はありません。

LT1424-5は一次側フライバック・パルス波形を照査することによって絶縁された出力電圧に関する情報を引き出します。この方法ではオプトアイソレータや追加トラン

ス巻線は不要です。このICは前述の方法より大きく改善されています。つまり、目的の出力電圧は抵抗比でプログラミングされ、レギュレーションが不連続モードでも十分に維持され、そしてオプションの負荷補償も利用できるのです。

ブロック図にシステムの全体を示します。多くのブロックは従来の設計に見られるブロックに類似しており、内部バイアス・レギュレータ、発振器、ロジック、電流アンプ、およびコンパレータ、ドライバ、そして出力スイッチを内蔵しています。主要部には特殊なフライバック誤差アンプと負荷補償メカニズムを内蔵しています。また、ロジック・システムはフライバック制御の特殊動作条件のため、従来の設計に見られない機能性を備えています。

ブロック図の $R_{REF}$ 、 $R_{FB}$ 、 $R_{OCOMP}$ の各抵抗は特定用途薄膜抵抗であり、LT1424-5に内蔵されています。 $R_{CCOMP}$ ピンに接続されたコンデンサは外部部品です。

LT1424-5は従来の電流モード・スイッチャと同様に類似した動作を行いますが、主な相違点は誤差アンプのタ

## 動作

イプが異なることで、フライバック・パルスから帰還情報を引き出します。スペースの制約からこの説明では電流モード・スイッチャ/コントローラや絶縁フライバック・コンパレータの基本については繰り返し述べません。これらの点に関する情報は、LTCのアプリケーション・ノート19に記載されています。

### 誤差アンプ - 擬似DC理論

フライバック誤差アンプの簡略図を参照してください。動作は以下のとおりです。出力スイッチQ4がターンオフすると、コレクタ電圧が $V_{IN}$ レールより上昇します。このフライバック・パルスの振幅、つまりこれと $V_{IN}$ との差は次式で与えられます。

$$V_{FLBK} = \frac{V_{OUT} + V_F + (I_{SEC})(ESR)}{N_{SP}}$$

$V_F$  = D1順方向電圧

$I_{SEC}$  = トランスの二次側電流

ESR = 二次側回路の全インピーダンス

$N_{SP}$  = トランスの二次側対一次側の実効巻数比

次に、フライバック電圧が $R_{FB}$ とQ1の動作によって電流に変換されます。この電流のほとんどが抵抗 $R_{REF}$ を流れ、グランド基準電圧を形成します。次に、これが差動トランジスタ・ペアQ2/Q3によって内部バンドギャップ・リファレンスと比較されます。Q2からのコレクタ電流がミラーされ、 $V_C$ ピンの定電流源 $I_{FXD}$ から減じられます。外部コンデンサは、正味電流を積分し、電流モードのトリップ・ポイントをセットして、制御電圧を供給します。

全体のループが比較的高利得であるため、 $R_{REF}$ 抵抗の電圧がバンドギャップ・リファレンス $V_{BG}$ とほぼ等しくなります。したがって、 $V_{FLBK}$ と $V_{BG}$ の関係は次のように表現されます。

$$\alpha \frac{V_{FLBK}}{R_{FB}} = \frac{V_{BG}}{R_{REF}} \text{ または、}$$

$$V_{FLBK} = V_{BG} \left( \frac{R_{FB}}{R_{REF}} \right) \left( \frac{1}{\alpha} \right)$$

= Q1  $I_C$ 対 $I_E$ の比

$V_{BG}$  = 内部バンドギャップ・リファレンス

前述の $V_{FLBK}$ の式と組み合わせると、以下のとおり内部リファレンス、プログラミング抵抗、トランスの巻数比、およびダイオード順方向電圧降下の項で表される $V_{OUT}$ の式が得られます。

$$V_{OUT} = V_{BG} \left( \frac{R_{FB}}{R_{REF}} \right) \left( \frac{N_{SP}}{\alpha} \right) - V_F - I_{SEC} (ESR)$$

さらに、非ゼロ二次出力インピーダンスの効果も含まれます。詳細については負荷補償を参照してください。 $V_{OUT}$ に対するこの式の応用の実際例はアプリケーション情報の章に記載されています。

これまで、フライバック誤差アンプ動作の擬似DC処理でした。しかし、フライバック信号はパルスであり、DCレベルではありません。フライバック・パルスが現れたときだけフライバック・アンプを動作させるには方策が必要です。これは“ENABLE”と記載されたブロックへ点線の接続を行うことによって実行されます。したがって、フライバック・アンプをイネーブルおよびディスエーブルするには、タイミング信号が必要です。

### 誤差アンプ - ダインミック理論

LT1424-5を適切に動作させるために必要なタイミング信号がいくつかあります。タイミング図を参照してください。

### 最小出力スイッチ・オン時間

LT1424-5はフライバック・パルス動作により出力電圧リギュレーションを行います。出力スイッチがまったくターンオンしなければフライバック・パルスは現れず、出力電圧の情報はまったく得られません。こうなるとループ応答が不規則となり、スタートアップ/ラッチアップ問題が起こります。これを解決するには、各発振器サイクルに対し絶対最少時間の間出力スイッチをターンオンさせます。これによって、リギュレーションを維持するための最小負荷条件が確立されます。詳細についてはアプリケーション情報の章を参照してください。

### イネーブル遅延

出力スイッチがシャットオフするとフライバック・パルスが現れます。しかし、トランスの一次側電圧波形が出力電圧に現れるまで一定の時間がかかります。これは部分的には $V_{SW}$ ノードの立上り時間によるものですが、さら

## 動作

に重要なのはトランスのリーク・インダクタンスによるものです。後者は出力電圧には直接関係のない一次側に電圧スパイクを発生します。(帰還アンプ回路を内部でセトリングさせるにも一定時間が必要です)。

これらの現象に対処するために、スイッチのターンオフ命令と帰還アンプが動作するまでに一定時間が導入されます。これは“イネーブル遅延”と呼ばれています。リーク・スパイクがイネーブル遅延期間の終わりまでに十分にセトリングしないケースでは、レギュレーション・エラーが生じことがあります。詳細についてはアプリケーション情報の章を参照してください。

### 崩壊検出

帰還アンプが一度イネーブルされると、それをディスエーブルするためのメカニズムが必要です。これは崩壊検出コンパレータによって実行され、フライバック電圧( $R_{REF}$ 基準)を通常は $V_{BG}$ の80%である固定リファレンスと比較します。フライバック波形がこのレベルより低下すると帰還アンプがディスエーブルされます。この作用は連続および不連続の両モード動作に適応します。

### 最少イネーブル時間

帰還アンプは一度イネーブルされると“最少イネーブル時間”と呼ばれる固定最小周期の間イネーブルされたままです。これによって、特に出力電圧が異常に低い、たとえば始動時にはロックアップが回避されます。最少イネーブル時間周期によって $V_C$ ノードが“ポンプアップ”可能となり、電流モードのトリップ・ポイントは崩壊検出システムが適切な動作を行えるレベルまで増加します。“最少イネーブル時間”は出力電圧レギュレーションが失われる低負荷レベルを決定します。詳細についてはアプリケーション情報の章を参照してください。

### 可変イネーブル期間の影響

フライバック・アンプがサイクル時間の一部でしかイネーブルされないことは明らかです。これは前述の一定“最少イネーブル時間”からオフスイッチ時間 - イネーブル遅延時間の最大値まで変化させることができます。したがって、フライバック・アンプ動作の特定パラメータは可変イネーブル周期によって影響されます。これらには実効相互コンダクタンスや $V_C$ ノードのスルーレートが含まれます。

### 負荷補償理論

LT1424-5はフライバック・パルスを使用して絶縁出力電圧に関する情報を得ます。潜在的な誤差要因は出力整流器のリアルライフ・非ゼロ・インピーダンス、トランスの二次側、出力コンデンサを流れるトランスの二次側電流によって発生します。これは前述の式( $I_{SEC}$ )( $ESR$ )によって表されます。しかし、一般にはこの式を実効出力インピーダンスに変換するほうが便利です。二次電流はデューティ・サイクルのオフ期間しか流れないので、実効出力インピーダンスは一括二次側インピーダンスとオフ・デューティ・サイクルの逆数を乗算した値に等しくなります。つまり、

$$R_{OUT} = ESR \left( \frac{1}{DC \text{ OFF}} \right)$$

$R_{OUT}$  = 電源出力の実効インピーダンス

$ESR$  = 一括二次側インピーダンス

$DC \text{ OFF}$  = オフ・デューティ・サイクル

$DC \text{ OFF} = 1 - DC$ であることから、これをオン・デューティ・サイクルで表現すると、次のようにになります。

$$R_{OUT} = ESR \left( \frac{1}{1 - DC} \right)$$

$DC$  = オン・デューティ・サイクル

それほど厳密でないアプリケーション、または出力負荷電流が比較的一定に保持される場合、この出力インピーダンス誤差は許容可能と判断され、外部 $R_{FB}$ 抵抗値が公称期待誤差を補償するために調整されます。条件の厳しいアプリケーションでは出力インピーダンス誤差を、負荷補償機能を使用して最小限に抑制することができます。

負荷補償機能を実行するために、平均出力スイッチ電流に比例した電圧を発生させます。この電圧が内部 $R_{OCOMP}$ 抵抗に印加され、その分の電流が $R_{FB}$ ノードから差し引かれます。出力負荷が増大すると出力電圧レギュレーションをおおよそ維持するため平均スイッチ電流が増加します。つまり、 $R_{FB}$ ノードから差し引かれた $R_{OCOMP}$ 抵抗の電流が増加します。それにより、帰還

## 動作

ループ動作が目的の出力電圧の増加に対応します。

電源効率Effが比較的一定していると仮定します。

$$\text{電力出力} = (\text{Eff})(\text{電力入力})$$

$$(V_{\text{OUT}})(I_{\text{OUT}}) = (\text{Eff})(V_{\text{IN}})(I_{\text{IN}})$$

平均一次側電流は、以下のとおり出力電流で表現することができます。

$$I_{\text{IN}} = \left( \frac{V_{\text{OUT}}}{(V_{\text{IN}})(\text{Eff})} \right) I_{\text{OUT}}$$

効率と電圧を1つの変数として組み合わせると、以下のようになります。

$$I_{\text{IN}} = K1(I_{\text{OUT}}) \text{ ここで}$$

$$K1 = \left( \frac{V_{\text{OUT}}}{(V_{\text{IN}})(\text{Eff})} \right)$$

ただし、スイッチ電流はセンス抵抗によって電圧に変換され、ゲインGを持つ電流センス・アンプによって増幅されます。次にこの電圧はR<sub>FB</sub>ノードから差し引かれる電流を形成するために内部R<sub>OCOMP</sub>抵抗に印加されます。したがって、目標のV<sub>OUT</sub>の有効変化は以下のとおりです。

$$\Delta V_{\text{OUT}} = K1(\Delta I_{\text{OUT}}) \left( \frac{(R_{\text{SENSE}})(G)}{R_{\text{OCOMP}}} \right) R_{\text{FB}} \text{ and,}$$

$$\frac{\Delta V_{\text{OUT}}}{\Delta I_{\text{OUT}}} = K1(R_{\text{SENSE}})(G) \left( \frac{R_{\text{FB}}}{R_{\text{OCOMP}}} \right)$$

公称出力インピーダンスのキャンセレーションはこの式とR<sub>OUT</sub>を等しくすると得られます。

簡単にするために、本データ・シートでは $\Delta V_{\text{REF}}/\Delta I_{\text{SW}}$ について述べます。これは、次式で与えられます。

$$\frac{\Delta V_{\text{REF}}}{\Delta I_{\text{SW}}} = (R_{\text{SENSE}})(G) \left( \frac{R_{\text{FB}}}{R_{\text{OCOMP}}} \right)$$

4

## アプリケーション情報

LT1424-Xは、特定用途の8ピン・デバイスであり、絶縁型フライバック・スイッチャ/コントローラを実現します。3つの内蔵薄膜抵抗を使用し、主に所要出力電圧、トランス巻数比および二次側回路のESR特性を含む特定用途にデバイスをプログラムします。新製品としては、LT1424のバージョンを2つ用意しております。ここで記述するLT1424-5は、標準的応用例に示すような1:1の汎用トランスを使用し、5V絶縁出力電源を実現します。また、別のデータシートで記述するLT1424-9は、PCMCIAタイプIIの高さ互換部品を使用し、-9Vの絶縁出力LAN電源を実現します。

他のアプリケーションにおいて大ボリューム要求を持つユーザに、一般的な実験およびブレッドボード製作はLT1425で行えることをお知らせします。LT1425は多目

的16ピン・デバイスであり、アプリケーション抵抗3つは外付け部品としてユーザが用意するという点を除けば、LT1424-Xと同じ機能を持ちます。これらの抵抗値の適切な選択に関するアプリケーション情報は、LT1425のデータ・シートに記載されています。技術的に実行可能なことが実証されましたら、LT1424-Xの別バージョンの実現性についてご相談ください。

### 出力電圧誤差源

一般に従来の非絶縁スイッチング電源ICには、実際2つの出力電圧誤差源しかありません。V<sub>OUT</sub>に接続される内部または外部抵抗分割器ネットワークと内部ICリファレンスです。ダイナミックおよび絶縁方式の両方で出力電圧を検知するLT1424-5には、議論すべき追加の潜在的

## アプリケーション情報

誤差源があります。これらの誤差のいくつかは出力電圧に比例し、その他は絶対的なミリボルトで固定されています。可能性のある誤差源のリストとその影響要因を記載します。

### 内部電圧リファレンス

内部バンドギャップ電圧リファレンスはもちろん完璧ではありません。25°Cと全温度における誤差はすでにリファレンス電圧に対する仕様に含まれています。

### ショットキ・ダイオードの電圧降下

LT1424-5は出力電圧を周期のフライバックの部分でトランスの一次側から検知します。したがって、この検知された電圧には整流器(通常はショットキ・ダイオード)の順方向電圧降下 $V_F$ が含まれます。ロット間および周囲温度でのバラツキは出力電圧シフト/ドリフトとして現れます。

### 二次側リーク・インダクタンス

トランスの二次側リーク・インダクタンスは、一次側対二次側の実効巻数比( $N_p/N_s$ )を理想値から減少させます。これはLT1424-5の設計において通常考慮されており、同じパーセンテージで出力電圧を増加させます。二次側リーク・インダクタンスが部品間で変化する大きさで、出力電圧は影響を受けます。

### 出力インピーダンス誤差

LT1424-5は負荷補償機能を備え、二次側回路ESRの影響を公称1次キャンセルします。個体間のバラツキがあり、キャンセレーションに若干の非直線性がある場合、残留 $V_{OUT}$ は負荷により多少変動します。

### 最小負荷の検討事項

LT1424-5は一般に間接的な出力電圧センス技術を利用した前世代スイッチャ/コントローラより優れた低負荷性能を実現します。特にフライバック・パルスの“崩壊”を検出する回路を内蔵しているため、不連続モードに入る動作をサポートしています。一般に、低い負荷での動作

を実現するために、予想される制約が2つあります。1つは最小スイッチ時間の制約であり、供給電力の最小レベルを設定します。もう1つは、最小フライバック・イネーブル時間の制約であり、フライバック・パルスから有効な出力電圧の情報を得る帰還システムの能力に関与します。LT1424-5が設計に盛り込まれているアプリケーションでは、最小フライバック・イネーブル時間はいっそう厳密になります。

LT1424-5はフライバック・パルスから出力電圧情報を得ます。内部最少イネーブル時間パルスがフライバック・パルスより幅が広ければ、レギュレーション・ロスが生じます。この状態のオンセットは、フライバック・パルス幅をフライバック・イネーブル遅延 $t_{ED}$ と最少イネーブル時間 $t_{EN}$ との和に等しく設定すると決定できます。負荷に供給される最小電力は以下のとおりです。

$$\begin{aligned} \text{最小電力} &= \left(\frac{1}{2}\right) \left(\frac{f}{L_{SEC}}\right) [V_{OUT} \cdot (t_{EN} + t_{ED})]^2 \\ &= (V_{OUT})(I_{OUT}) \end{aligned}$$

したがって、以下の最小出力制約が得られます。

$$I_{OUT(MIN)} = \left(\frac{1}{2}\right) \left(\frac{f(V_{OUT})}{L_{SEC}}\right) (t_{ED} + t_{EN})^2, \text{ここで}$$

$f$  = スイッチング周波数(通常285kHz)

$L_{SEC}$  = トランスの二次側インダクタンス

$V_{OUT}$  = 出力電圧

$t_{ED}$  = イネーブル遅延時間

$t_{ED}$  = 最小イネーブル時間

実際には、前述の式では控え目にも軽負荷のケースにはない完全な「方形」波形を仮定しています。そのうえ、これは制御誤差のオンセットだけを求めるために作られた式です。言い換えれば、次のようなことです。この式が提案する最小負荷電流はおそらく3mAですが、実験での観測結果によれば著しい出力電圧の上昇が認められる前に1mA ~ 2mAの動作に抑えることが提案されています。しかし、アプリケーションでは通常2.8mAの電源をプリードする1.8kの固定負荷抵抗を使用してこの状況に対処します。

## アプリケーション情報

### 最大負荷/短絡に関する検討事項

LT1424-5は電流モード・コントローラです。V<sub>C</sub>ノード電圧を電流コンパレータの入力として使用し、ピーク電流に達すると出力スイッチをサイクルごとにターンオフします。そのとき標準1.9VのV<sub>C</sub>ノードの内部クランプは、出力スイッチのピーク電流制限として動作します。この動作がスイッチ電流制限仕様になります。最大利用可能出力電力はスイッチ電流制限によって決定され、内部スロープ補償動作のため、いくらかデューティ・サイクルに依存します。

短絡状態は同じメカニズムで処理されます。出力スイッチがターンオンし、ピーク電流に瞬時に到達し、スイッチがターンオフします。出力スイッチが有効期間のごく一部でのみオンするため内部消費電力が制御されます。(LT1424-5は過温度シャットダウン回路を内蔵しており、適宜スイッチ動作を停止させます)。

### 熱に関する検討事項

ワーストケースの入力電圧および負荷電流条件によって、ダイの定格温度を超えないように注意してください。パッケージの熱抵抗は、SO-8で110 °W、N8で130 °Wと規定されています。

平均電源電流( ドライバ電流を含む )は、以下のとおりです：

$$I_{IN} = 7mA + DC \left( \frac{I_{SW}}{35} \right) \text{ ここで、}$$

I<sub>SW</sub> = スイッチ電流

DC = オンスイッチのデューティ・サイクル

スイッチの消費電力は次式で与えられます。

$$P_{SW} = (I_{SW})^2(R_{SW})(DC)$$

R<sub>SW</sub> = 出力スイッチのオン抵抗

ダイの全消費電力は電源電流 × 電源電圧とスイッチ電力の和です。

$$P_{D(TOTAL)} = (I_{IN} \cdot V_{IN}) + P_{SW}$$

### 周波数補償

ループ周波数補償は、コンデンサを誤差アンプの出力 (V<sub>C</sub>ピン)からグランドに接続して行います。従来の電流モード・スイッチャ・コントローラで必要な場合が多いもう1つの直列抵抗は通常必要なく、有害ですらある場合があります。従来この抵抗で得られた位相マージンの改善は、通常は非ゼロ二次側回路インピーダンスによって実現され、これによってループ応答に“ゼロ”が加わります。

従来の電流モード・スイッチャとは対照的に、LT1424-5でV<sub>C</sub>ピンのリップルが問題となることはありません。クランプされた帰還アンプのダイナミック特性は有効なトラック/ホールド・タイプの応答を形成するため、V<sub>C</sub>電圧はフライバック・パルス期間中に変化しますが、次のサイクルの次の“スイッチオン”の間「保持」されます。電流コンパレータ・センス動作( 電流モード・スイッチング )の間、V<sub>C</sub>電圧はこの動作によって自然に安定します。

### PCBレイアウトの考察

効率を最大限に高めるために、スイッチの立上り時間と立下り時間は実用上可能な限り短くします。放射および高周波数共振問題を回避するには、ICに接続する部品、特に電源バス( 一次側および二次側 )の適切なレイアウトが不可欠です。磁界( 磁気 )放射は、出力ダイオード、スイッチ・ピン、および出力バイパス・コンデンサのリードを可能な限り短くすれば低く抑えることができます。電界放射はスイッチ・ピンに接続されるすべてのトレースの長さと面積を小さくすれば低くすることができます。スイッチング回路の下に必ずグランド・プレーンを使用して、プレーン間の結合を防止する必要があります。

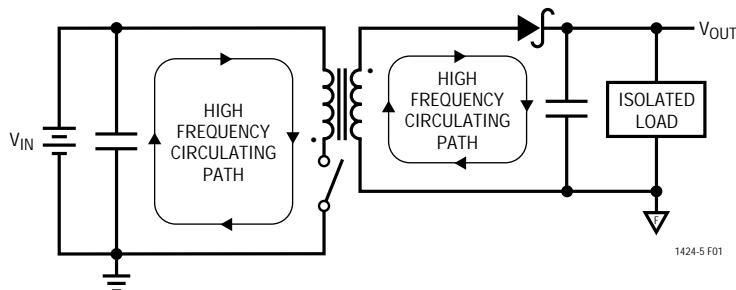

図1に高速スイッチング電流パスを図解します。クリーンなスイッチングと最小のEMIを保証するには、これらのバスのリード長を最短にする必要があります。入力コンデンサ、トランスの一次側、出力スイッチを含むバス、そしてトランスの二次側、出力ダイオード、および出力コンデンサがあるバスは立上り時間と立下り時間がナノセコンドのバスです。これらのバスは可能な限り短くしてください。

## アプリケーション情報

図1

## 標準的応用例

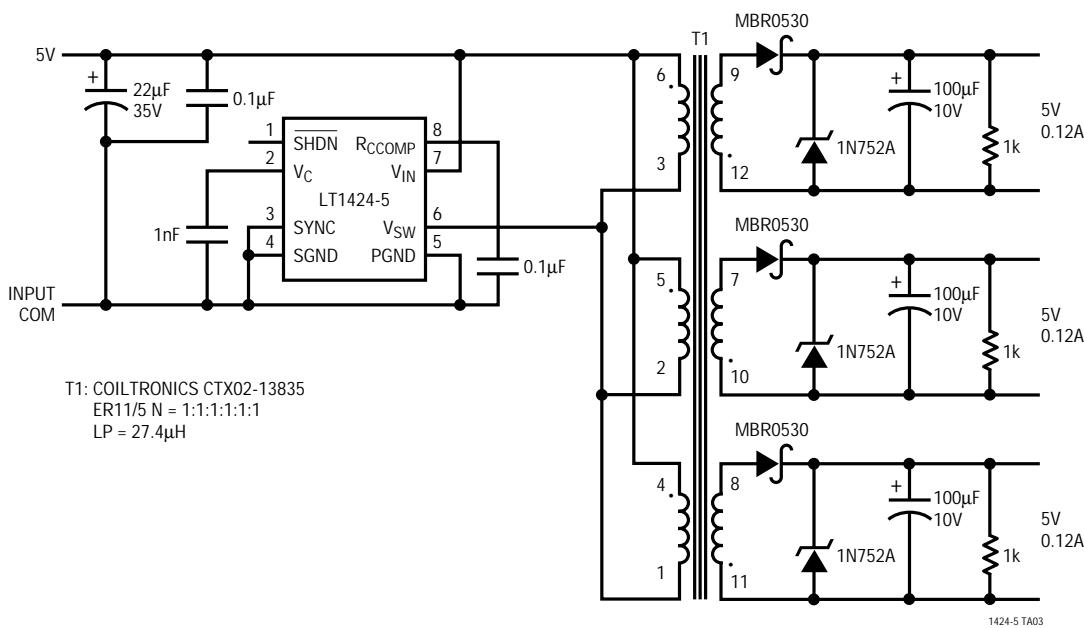

## トリプル5V絶縁電源

## 関連製品

| 製品番号         | 説明                           | 注釈                        |

|--------------|------------------------------|---------------------------|

| LT1105       | オフライン・スイッチング・レギュレータ          | 内蔵型絶縁レギュレーション、オプトアイソレータ不要 |

| LTC®1145/46  | 絶縁型デジタル・データ・トランシーバ           | 最高200kbpsのデータ転送速度、UL登録済   |

| LT1170/71/72 | 5A/3A/1.25A フライバック・レギュレータ    | 高電流用の絶縁型フライバック・モード        |

| LT1372/77    | 500kHz/1MHzの昇圧/フライバック・レギュレータ | 超小型磁気部品を使用                |

| LT1424-9     | 9V出力の絶縁型フライバック・スイッチング・レギュレータ | - 9VのPCMCIAタイプII LAN電源を実現 |

| LT1425       | 絶縁型フライバック・スイッチング・レギュレータ      | 外付けアプリケーション抵抗で多目的使用       |