## 特長

- 電源の入ったバックプレーンへの挿入、引抜きを安全に行う

- システムリセット、パワーゲット制御出力

- プログラム可能な回路ブレーカ

- ユーザがプログラム可能な供給電圧上昇レート

- 2つの外付けNチャネルFET用のハイサイドドライバ

- 3V～12Vまで可能な供給電圧の制御

- 接続入力がボードの挿入、引抜きを検出

- 低電圧ロックアウト

- パワーオンリセット入力

## アプリケーション

- ボードの活線挿入

- 電子回路ブレーカ

## 概要

LTC<sup>®</sup>1421/LTC1421-2.5は電源の入った状態でのバックプレーンからの挿入引抜きを安全に可能にするホットスワップ<sup>TM</sup>(活線挿抜)コントローラです。外付けNチャネル・パス・トランジスタを使用し、ボードへの供給電圧を徐々に増加させるプログラミングが可能です。2つのハイサイド・スイッチ・ドライバは3V～12Vの電圧を供給するためにNチャネルのゲートを制御することができます。

プログラム可能な電子回路ブレーカにより短絡から保護します。警報信号はブレーカがトリップしたことを表示し、電源異常が発生したことや、スイッチ・ドライバがターンオフしたことを知らせます。リセット出力はパワーサイクルや、異常が発生した時にシステムリセットを発生することができます。2つの接続入力はスタガ・コネクタ(ピンの接続が時差を持って行われる)とともに使用され、ボードが挿入されたか引き抜かれたかを指示します。パワーオンリセット入力はボードの電源を循環させたり、ブレーカをリセットしたりするために使用されます。

グランド・センス・コンパレータのトリップ・ポイントは、LTC1421の場合は0.1V、LTC1421-2.5の場合は2.5Vに設定されています。

LTC1421/LTC1421-2.5は24ピンSOおよびSSOPパッケージで供給されます。

△、LTC、LTはリニアテクノロジー社の登録商標です。

ホットスワップはリニアテクノロジー社の商標です。

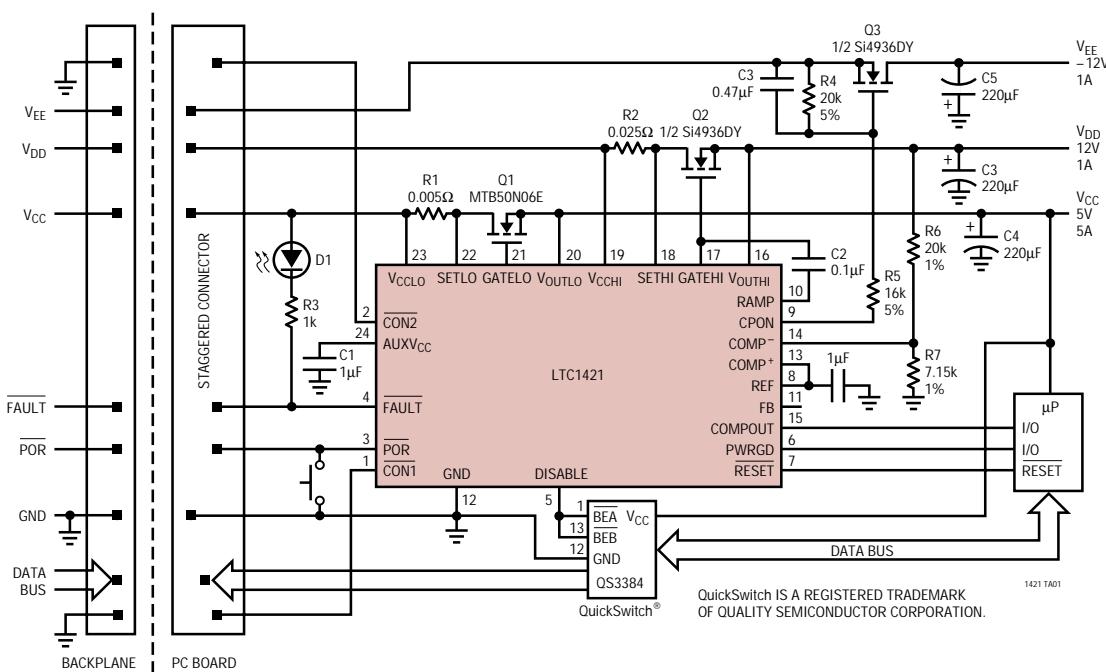

## 標準的応用例

## 絶対最大定格

(Note 1)

|                                               |       |                             |

|-----------------------------------------------|-------|-----------------------------|

| 供給電圧( $V_{CCLO}$ 、 $V_{CCHI}$ 、 $AUXV_{CC}$ ) | ..... | 13.2V                       |

| 入力電圧( アナログ・ピン )                               | ..... | - 0.3V ~ $V_{CCHI}$ + 0.3V  |

| 入力電圧( デジタル・ピン )                               | ..... | - 0.3V ~ 13.2V              |

| 出力電圧( デジタル・ピン )                               | ..... | - 0.3V ~ $V_{CCLO}$ + 0.3V  |

| 出力電圧( CPON )                                  | ..... | - 13.2V ~ $V_{CCLO}$ + 0.3V |

| 出力電圧( $V_{OUTLO}$ 、 $V_{OUTHI}$ )             | ..... | - 0.3V ~ 13.2V              |

| 出力電圧( GATELO、 GATEHI )                        | ..... | - 0.3V ~ 20V                |

| 動作温度範囲                                        | ..... | 0 ~ 70                      |

| 保存温度範囲                                        | ..... | - 65 ~ 150                  |

| リード温度( 半田付け、 10秒 )                            | ..... | 300                         |

## パッケージ/発注情報

| TOP VIEW                                                                     |    | ORDER PART NUMBER |

|------------------------------------------------------------------------------|----|-------------------|

| CON1                                                                         | 1  | $AUXV_{CC}$       |

| CON2                                                                         | 2  | $V_{CCLO}$        |

| POR                                                                          | 3  | SETLO             |

| FAULT                                                                        | 4  | GATELO            |

| DISABLE                                                                      | 5  | $V_{OUTLO}$       |

| PWRGD                                                                        | 6  | $V_{CCHI}$        |

| RESET                                                                        | 7  | SETHI             |

| REF                                                                          | 8  | GATEHI            |

| CPON                                                                         | 9  | $V_{OUTHI}$       |

| RAMP                                                                         | 10 | COMP <sup>+</sup> |

| FB                                                                           | 11 | COMP <sup>-</sup> |

| GND                                                                          | 12 | COMP <sup>+</sup> |

| G PACKAGE                                                                    |    |                   |

| 24-LEAD PLASTIC SSOP                                                         |    |                   |

| SW PACKAGE                                                                   |    |                   |

| 24-LEAD PLASTIC SO                                                           |    |                   |

| $T_{JMAX} = 125^{\circ}\text{C}$ , $\theta_{JA} = 100^{\circ}\text{C/W}$ (G) |    |                   |

| $T_{JMAX} = 125^{\circ}\text{C}$ , $\theta_{JA} = 85^{\circ}\text{C/W}$ (SW) |    |                   |

インダストリアルおよびミリタリ・グレードはお問い合わせください。

## 電気的特性 注記がない限り $V_{CCHI} = 12\text{V}$ 、 $V_{CCLO} = 5\text{V}$ 、 $T_A = 25$ ( Note 2 )

| SYMBOL                    | PARAMETER                                  | CONDITIONS                                                                                        | MIN         | TYP                  | MAX                  | UNITS                |

|---------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|-------------|----------------------|----------------------|----------------------|

| <b>DC Characteristics</b> |                                            |                                                                                                   |             |                      |                      |                      |

| $I_{CCLO}$                | $V_{CCLO}$ Supply Current                  | $\overline{CON1} = \overline{CON2} = \text{GND}$ , $\overline{POR} = V_{CCLO}$                    | ●           | 1.5                  | 3                    | mA                   |

| $I_{CCHI}$                | $V_{CCHI}$ Supply Current                  | $\overline{CON1} = \overline{CON2} = \text{GND}$ , $\overline{POR} = V_{CCLO}$                    | ●           | 0.6                  | 1                    | mA                   |

| $V_{LKO}$                 | Undervoltage Lockout                       | $V_{CCLO}$ and $V_{CCHI}$                                                                         |             | 2.28                 | 2.45                 | 2.60                 |

| $V_{LKH}$                 | Undervoltage Lockout Hysteresis            | $V_{CCLO}$ and $V_{CCHI}$                                                                         |             | 100                  |                      | mV                   |

| $V_{REF}$                 | Reference Output Voltage                   | No Load                                                                                           | ●           | 1.220                | 1.232                | 1.244                |

| $\Delta V_{LNR}$          | Reference Line Regulation                  | $3\text{V} \leq V_{CCLO} \leq 12\text{V}$ , No Load                                               | ●           | 4                    | 8                    | mV                   |

| $\Delta V_{LDR}$          | Reference Load Regulation                  | $I_0 = 0\text{mA}$ to $-5\text{mA}$ , Sourcing Only                                               | ●           | 1                    | 3                    | mV                   |

| $I_{RSC}$                 | Reference Short-Circuit Current            | $V_{REF} = 0\text{V}$                                                                             |             | 45                   |                      | mA                   |

| $V_{COF}$                 | Comparator Offset Voltage                  | $0\text{V} \leq V_{CM} \leq (V_{CCLO} - 1.3\text{V})$                                             | ●           |                      | ±10                  | mV                   |

| $V_{CPSR}$                | Comparator Power Supply Rejection          | $0\text{V} \leq V_{CM} \leq (V_{CCLO} - 1.3\text{V})$ , $3\text{V} \leq V_{CCLO} \leq 12\text{V}$ | ●           |                      | 1                    | mV/V                 |

| $V_{CHST}$                | Comparator Hysteresis                      | $0\text{V} \leq V_{CM} \leq (V_{CCLO} - 1.3\text{V})$                                             |             | 7                    |                      | mV                   |

| $V_{RST}$                 | Reset Voltage Threshold ( $V_{OUTLO}$ )    | $FB = V_{OUTLO}$<br>$FB = \text{Floating}$<br>$FB = \text{GND}$                                   | ●<br>●<br>● | 2.80<br>4.50<br>5.75 | 2.90<br>4.65<br>5.88 | 3.00<br>4.75<br>6.01 |

| $V_{RHST}$                | Reset Threshold Hysteresis ( $V_{OUTLO}$ ) | $FB = V_{OUTLO}$<br>$FB = \text{Floating}$<br>$FB = \text{GND}$                                   |             |                      | 7<br>12<br>15        | mV<br>mV<br>mV       |

| $R_{FB}$                  | FB Pin Input Resistance                    | $0\text{V} \leq V_{FB} \leq V_{CCLO}$                                                             |             | 95                   |                      | k $\Omega$           |

| $V_{CB}$                  | Circuit Breaker Trip Voltage               | $V_{CB} = (V_{CCLO} - V_{SETLO})$ or $V_{CB} = (V_{CCHI} - V_{SETHI})$                            | ●           | 40                   | 50                   | 60                   |

| $V_{TRIP}$                | Output Voltage for Re-Power-Up             | LTC1421 ( Note 3 )<br>LTC1421-2.5 ( Note 4 )                                                      |             |                      | 0.1<br>2.5           | V<br>V               |

電気的特性 注記がない限り  $V_{CCHI} = 12V$ 、 $V_{CCLO} = 5V$ 、 $T_A = 25$  (Note 2)

| SYMBOL              | PARAMETER                         | CONDITIONS                                                                                                     | MIN | TYP  | MAX  | UNITS   |

|---------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-----|------|------|---------|

| $I_{RAMP}$          | RAMP Pin Output Current           | Charge Pump On, $V_{RAMP} = 0.4V$                                                                              | ●   | 11   | 17   | $\mu A$ |

| $I_{CP}$            | Charge Pump Output Current        | Charge Pump On, $GATEHI = 0V$<br>$GATELO = 0V$                                                                 |     | -600 | -300 | $\mu A$ |

| $\Delta V_{GATEHI}$ | GATEHI N-Channel Gate Drive       | $V_{GATEHI} - V_{OUTHI}$                                                                                       |     | 6    | 16   | V       |

| $\Delta V_{GATELO}$ | GATELO N-Channel Gate Drive       | $V_{GATELO} - V_{OUTLO}$                                                                                       |     | 10   | 16   | V       |

| $V_{AUXVCC}$        | Auxiliary $V_{CC}$ Output Voltage | $V_{CCLO} = 5V$ , Unloaded                                                                                     |     | 4.5  |      | V       |

| $V_{IL}$            | Input Low Voltage                 | $\overline{CON1}, \overline{CON2}, \overline{POR}$                                                             | ●   |      | 0.8  | V       |

| $V_{IH}$            | Input High Voltage                | $\overline{CON1}, \overline{CON2}, \overline{POR}$                                                             | ●   | 2    |      | V       |

| $I_{IN}$            | Input Current                     | $\overline{CON1}, \overline{CON2}, \overline{POR} = GND$                                                       | ●   | -30  | -60  | $\mu A$ |

| $V_{OL}$            | Output Low Voltage                | $\overline{RESET}, \overline{COMPOUT}, \overline{PWRGD}, \overline{DISABLE}, \overline{FAULT},$<br>$I_0 = 3mA$ | ●   |      | 0.4  | V       |

|                     |                                   | $CPON, I_0 = 3mA$                                                                                              | ●   |      | 1.45 | V       |

| $V_{OH}$            | Output High Voltage               | $\overline{DISABLE}, I_0 = -3mA$                                                                               | ●   | 4    |      | V       |

|                     |                                   | $CPON, I_0 = -1mA$                                                                                             | ●   | 3.4  |      | V       |

| $I_{PU}$            | Logic Output Pull-Up Current      | $\overline{RESET}, \overline{PWRGD}, \overline{FAULT} = GND$                                                   |     |      | -15  | $\mu A$ |

## AC CHARACTERISTICS

|           |                                                                                    |                                                                                           |   |     |      |     |         |

|-----------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---|-----|------|-----|---------|

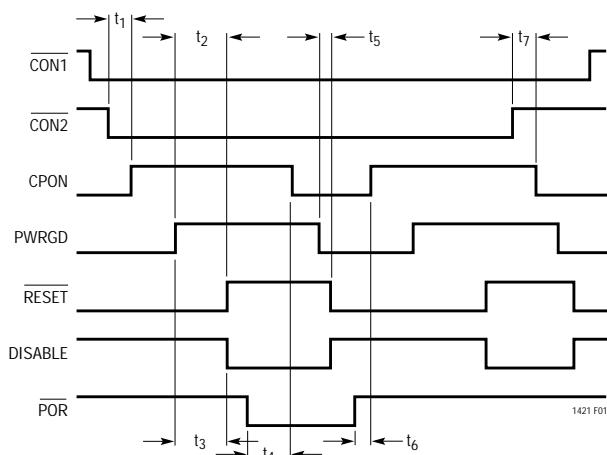

| $t_1$     | $\overline{CON1} \text{ or } \overline{CON2} \downarrow \text{ to } CPON \uparrow$ | Figure 1, $C_L = 15pF$                                                                    | ● | 15  | 20   | 30  | ms      |

| $t_2$     | $PWRGD \uparrow \text{ to } \overline{RESET} \uparrow$                             | Figure 1, $R_L = 10k$ to $V_{CCLO}$ , $C_L = 15pF$                                        | ● | 160 | 200  | 240 | ms      |

|           |                                                                                    |                                                                                           |   | 140 | 200  | 280 | ms      |

| $t_3$     | $PWRGD \uparrow \text{ to } \overline{DISABLE} \downarrow$                         | Figure 1, $C_L = 15pF$                                                                    | ● | 160 | 200  | 240 | ms      |

| $t_4$     | $\overline{POR} \downarrow \text{ to } CPON \downarrow$                            | Figure 1, $C_L = 15pF$                                                                    | ● | 140 | 200  | 280 | ms      |

|           |                                                                                    |                                                                                           |   | 15  | 20   | 30  | ms      |

| $t_5$     | $PWRGD \downarrow \text{ to } \overline{RESET} \downarrow$                         | Figure 1, $R_L = 10k$ to $V_{CCLO}$ , $C_L = 15pF$                                        |   |     | 32   |     | $\mu s$ |

| $t_6$     | $\overline{POR} \uparrow \text{ to } CPON \uparrow$                                | Figure 1, $C_L = 15pF$                                                                    |   |     | 50   |     | ns      |

| $t_7$     | $\overline{CON1} \text{ or } \overline{CON2} \uparrow \text{ to } CPON \downarrow$ | Figure 1, $C_L = 15pF$                                                                    |   |     | 50   |     | ns      |

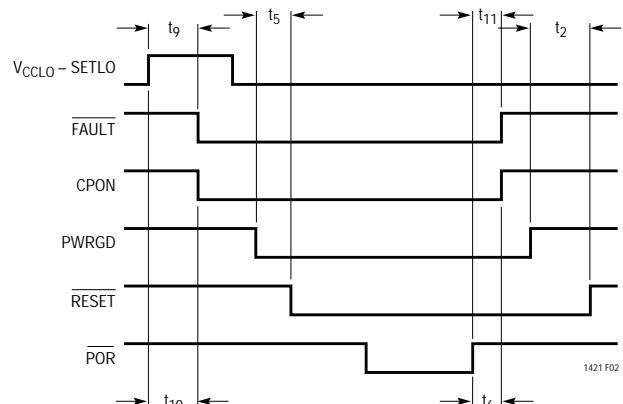

| $t_9$     | Short-Circuit Detect to $\overline{FAULT} \downarrow$                              | Figure 1, $R_L = 10k$ to $V_{CCLO}$ , $C_L = 15pF$<br>$V_{CCLO} - SETLO = 0mV$ to $100mV$ |   |     | 20   |     | $\mu s$ |

| $t_{10}$  | Short-Circuit Detect to $CPON \downarrow$                                          | Figure 2, $C_L = 15pF$<br>$V_{CCLO} - SETLO = 0mV$ to $100mV$                             |   |     | 20   |     | $\mu s$ |

| $t_{11}$  | $\overline{POR} \uparrow \text{ to } \overline{FAULT} \uparrow$                    | Figure 2, $R_L = 10k$ to $V_{CCLO}$ , $C_L = 15pF$                                        |   |     | 20   |     | ns      |

| $t_{CHL}$ | Comparator High to Low                                                             | $COMP^- = 1.232V$ , 10mV Overdrive<br>$R_L = 10k$ to $V_{CCLO}$ , $C_L = 15pF$            | ● |     | 0.25 | 0.5 | $\mu s$ |

| $t_{CLH}$ | Comparator Low to High                                                             | $COMP^- = 1.232V$ , 10mV Overdrive<br>$R_L = 10k$ to $V_{CCLO}$ , $C_L = 15pF$            | ● |     | 1    | 1.5 | $\mu s$ |

は全動作温度範囲の規格値を意味する。

Note 1: 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2: デバイスのピンに流入する電流はすべて正。デバイスのピンから流出する電流はすべて負。注記がない限りすべての電圧はグランドを基準にしている。

Note 3: パワーオン・リセットの後、 $V_{OUTLO}$ および $V_{OUTHI}$ はチャージポンプが再始動する前に、 $V_{TRIP}$ ポイント以下に低下しなければならない。Note 4: パワーオン・リセットの後、 $V_{OUTLO}$ はチャージポンプが再始動する前に、 $V_{TRIP}$ ポイント以下に低下しなければならない。

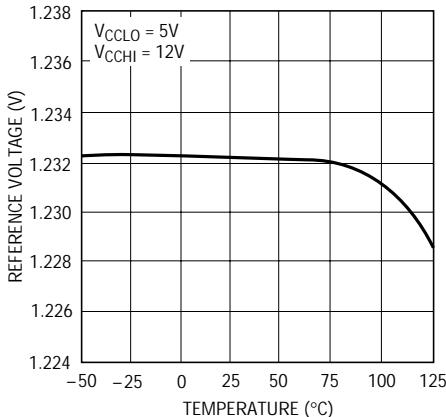

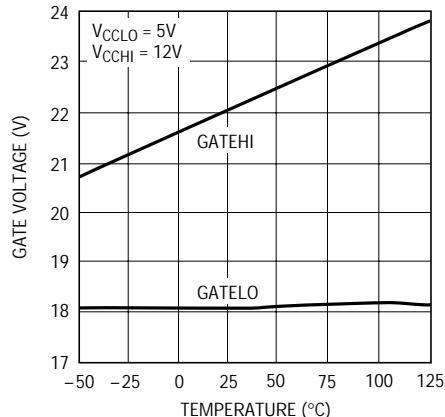

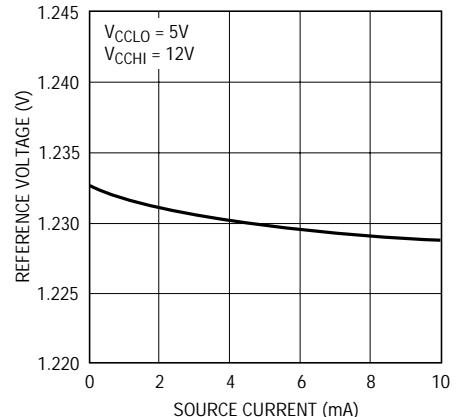

## 標準的性能特性

### リファレンス電圧と温度

1421 G01

### ゲート電圧と温度

1421 G02

### リファレンス電圧とソース電流

1421 G03

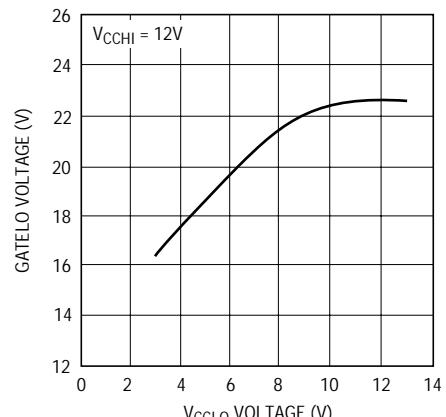

### GATELO電圧とV<sub>CCLO</sub>電圧

1421 G04

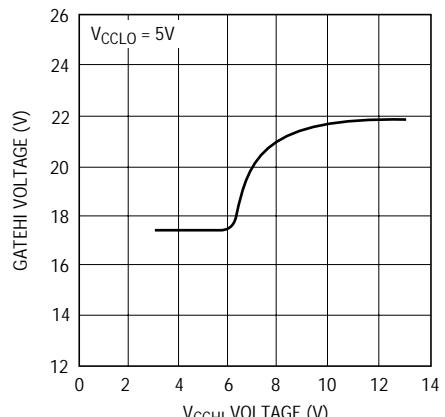

### GATEHI電圧とV<sub>CCHI</sub>電圧

1421 G05

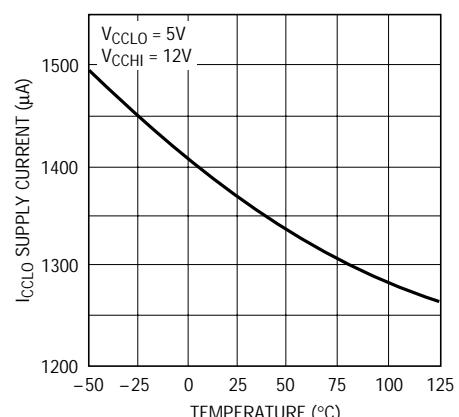

### I<sub>CCLO</sub>電源電流と温度

1421 G06

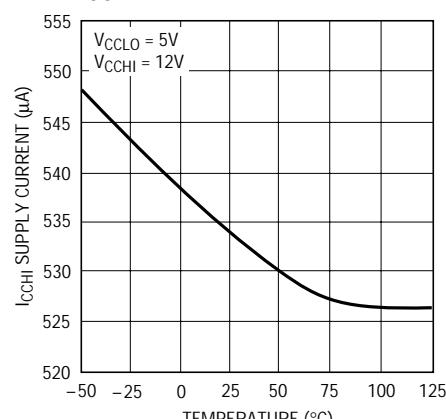

### I<sub>CCHI</sub>電源電流と温度

1421 G07

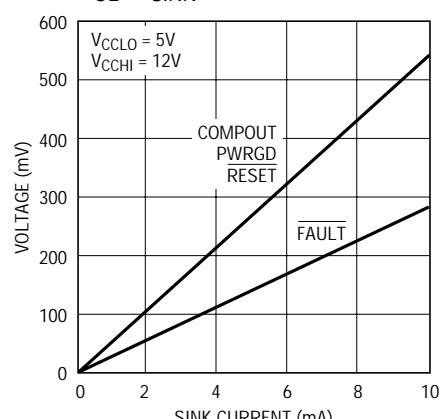

### V<sub>OL</sub>とI<sub>SINK</sub>

1421 G08

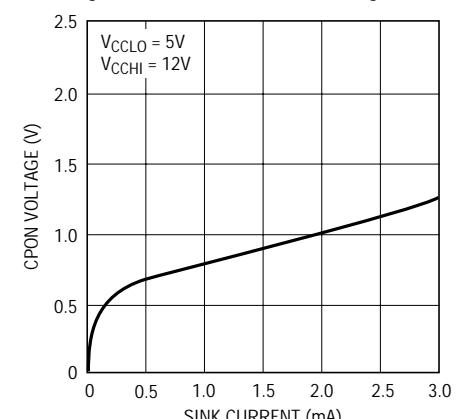

### CPON電圧とシンク電流 (チャージ・ポンプ・オフ)

1421 G09

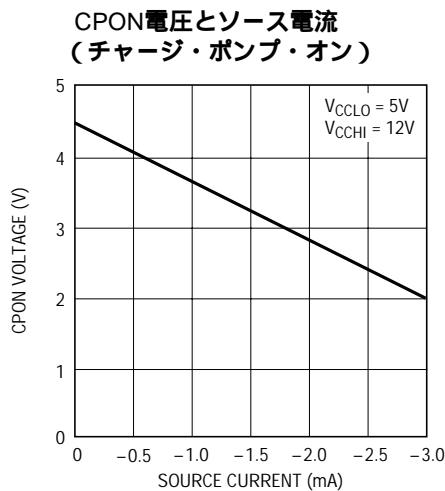

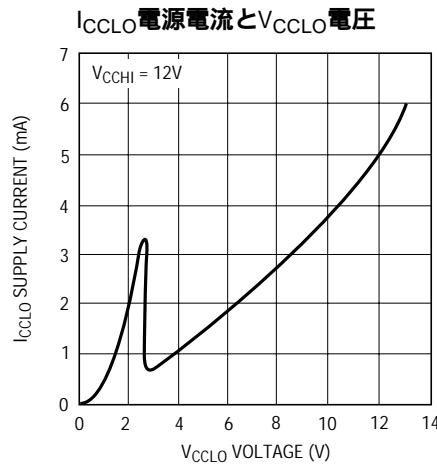

## 標準的性能特性

1421 G10

1421 G11

## ピン機能

CON1( ピン1): V<sub>CCL0</sub>へのプルアップ付TTLレベル入力。CON2とともにボードの接続状況を指示するために使用されます。このピンはホスト側でグランドに接続しなければなりません。スタガ・コネクタピンを使用する場合には、CON1とCON2は最短でなくてはならずまたコネクタの端と端に位置させなくてはなりません。ボードの挿入はCON1とCON2が両方とも“L”になってから20ms後と仮定しています。

CON2( ピン2): V<sub>CCL0</sub>へのプルアップ付TTLレベル入力。CON1とともにボードの接続状況を指示するために使用されます。

POR( ピン3): V<sub>CCL0</sub>へのプルアップ付TTLレベル入力。このピンが少なくとも20msの間“L”に設定されるとハードリセットが発生します。V<sub>OUTL0</sub>とV<sub>OUTH1</sub>は制御されたレートでオフします。電源立上げシーケンスはPORピンが“H”に設定されている限りスタートしません。V<sub>OUTL0</sub>とV<sub>OUTH1</sub>が完全に放電する前にPORが“H”に設定されると、それらのピンの電圧がV<sub>TRIP</sub>以下になるまでは電源立上げシーケンスは開始されません。電子回路ブレーカはPORが“L”に設定されるとリセットされます。

FAULT( ピン4): オープンドレイン出力でV<sub>CCL0</sub>に微弱にプルアップされています。このピンはV<sub>OUTL0</sub>またはV<sub>OUTH1</sub>で過電流異常が検出されたときに“L”に設定されます。

DISABLE( ピン5): CMOS出力。この信号はボードを挿入あるいは引抜き中にデータ・バスを使用不可にするために使用されます。

PWRGD( ピン6): オープンドレイン出力でV<sub>CCL0</sub>に微弱にプルアップされています。このピンはV<sub>OUTL0</sub>がリセット・スレッショルド電圧を下回るとすぐに“L”になります。このピンはV<sub>OUTL0</sub>がリセット・スレッショルド電圧を上回るとすぐに“H”になります。

リセット( ピン7): オープンドレイン出力でV<sub>CCL0</sub>にかかるにプルアップされています。このピンはリセット状態を検出すると“L”になります。次の条件のうち1つでも満足するとリセット信号が発生します：CON1またはCON2が“H”、PORが“L”、V<sub>CCL0</sub>またはV<sub>CCH1</sub>が低電圧ロックアウト・スレッショルド電圧よりも低い、PWRGDが“L”になるかあるいはV<sub>OUTL0</sub>かV<sub>OUTH1</sub>で低電圧ロックアウトが検出されたとき。RESETピンはPWRGDが“H”になってから200ms後に“H”になります。電源異常のときには、RESETピンはPWRGDピンが“L”になってから32μs後に“L”になります。

REF( ピン8): リファレンス電圧出力。V<sub>OUT</sub> = 1.232V ± 1%。リファレンスは5mAまでの電流を供給できます。1μFのバイパス・コンデンサが推奨されます。

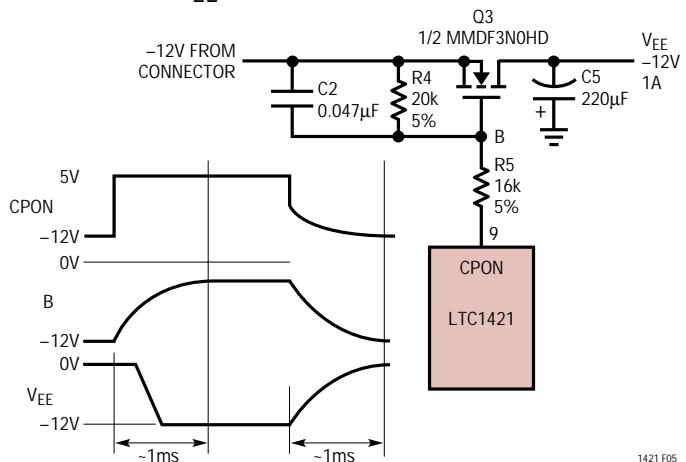

CPON( ピン9): CMOS出力で、グランド以下に下げるすることができます。GATEL0とGATEHI用の内部チャージポンプがターンオンしているときにCPONは“H”になります。チャージ・ポンプがターンオフしているときにCPONは“L”になります。このピンは -5V、-12V用の外部MOSFETの制御用に使用できます。

## ピン機能

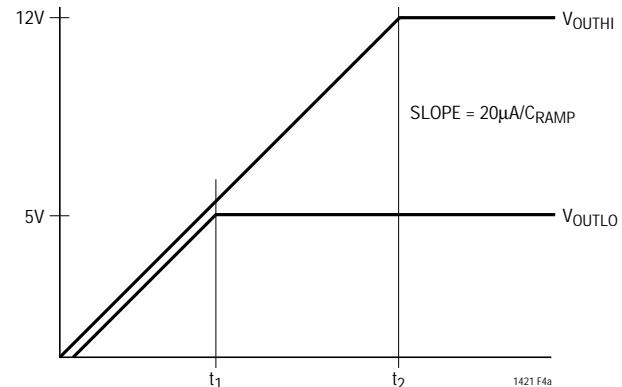

RAMP( ピン10 ): アナログ・パワーアップ・ランプ制御ピンです。RAMPとGATEHIに外部コンデンサを接続することにより、GATEHIとGATELOピンに正のランプ電圧を発生させることができます。ランプ波のスロープは  $20\mu\text{A}/\text{C}_{\text{RAMP}}$  になります。

FB( ピン11 ): アナログ帰還入力。FBピンはV<sub>CCLO</sub>におけるリセット・スレッショルド電圧を設定するために使用します。5V電源のときにはこのピンは無接続にします。3.3V電源の場合にはFBピンをV<sub>CCLO</sub>に接続します。

GND( ピン12 ): グランド。

COMP<sup>+</sup>( ピン13 ): コンパレータの非反転入力。

COMP<sup>-</sup>( ピン14 ): コンパレータの反転入力。

COMPOUT( ピン15 ): コンパレータのオープン・ドレン出力

V<sub>OUTH</sub>( ピン16 ): 高供給電圧出力。このピンは2つの供給電圧出力より高くなければなりません。

GATEHI( ピン17 ): 高供給電圧出力用Nチャネル・ハイサイド・ゲート・ドライバ。内部のチャージポンプは少なくとも6Vのゲートドライブ電圧を発生します。GATEHIピンの電圧上昇のスロープはGATEHIピンとRAMPピンに接続された外部コンデンサによって設定されます。回路ブレーカがトリップすると、GATEHIピンはただちにグランド電位になります。

SETHI( ピン18 ): 高供給電圧出力用回路ブレーカの設定ピンです。電流供給パスのV<sub>CCHI</sub>とSETHI間に接続された電流センス抵抗によって、その電圧降下が20 $\mu\text{s}$ 以上の間50mV以上になると回路ブレーカはトリップします。このブレーカを無効にするにはV<sub>CCHI</sub>とSETHIを短絡します。

V<sub>CCHI</sub>( ピン19 ): 正の電源入力。このピンは他の電源入力ピンより高くなければなりません。低電圧ロックアウト回路はV<sub>CCHI</sub>の電圧が2.45V以上になるまではこのチップを使用不能にします。

V<sub>OUTLO</sub>( ピン20 ): 低供給電圧出力。このピンは他の供給電圧出力より低くなければなりません。

GATELO( ピン21 ): 低供給電圧出力用Nチャネル・パストランジスタ・ハイサイド・ゲート・ドライバ。内部チャージ・ポンプは少なくとも10Vのゲート・ドライブ電圧を発生します。GATELOピンの電圧上昇スロープは、GATEHIピンとRAMPピンに接続された外部コンデンサによって設定されます。回路ブレーカがトリップすると、GATELOピンは直ちにグランド電位になります。

SETLO( ピン22 ): 低電圧出力用回路ブレーカの設定ピンです。電流供給パスのV<sub>CCLO</sub>とSETLO間に接続された電流センス抵抗によって、その電圧降下が20 $\mu\text{s}$ 以上の間50mV以上になると回路ブレーカはトリップします。このブレーカを無効にするには、V<sub>CCLO</sub>とSETLOを短絡します。

V<sub>CCLO</sub>( ピン23 ): 正の電源入力。このピンはV<sub>CCHI</sub>ピンの電圧以下でなければなりません。低電圧ロックアウト回路はV<sub>CCLO</sub>の電圧が2.45V以上になるまではこのチップを使用不能にします。

AUXV<sub>CD</sub>( ピン24 ): GATELOとGATEHIの放電回路用の供給入力です。このピンからグランドに1 $\mu\text{F}$ のコンデンサが必要です。このピンは内部ショットキ・ダイオードと直列抵抗を通して、V<sub>CCLO</sub>から電力が供給されます。

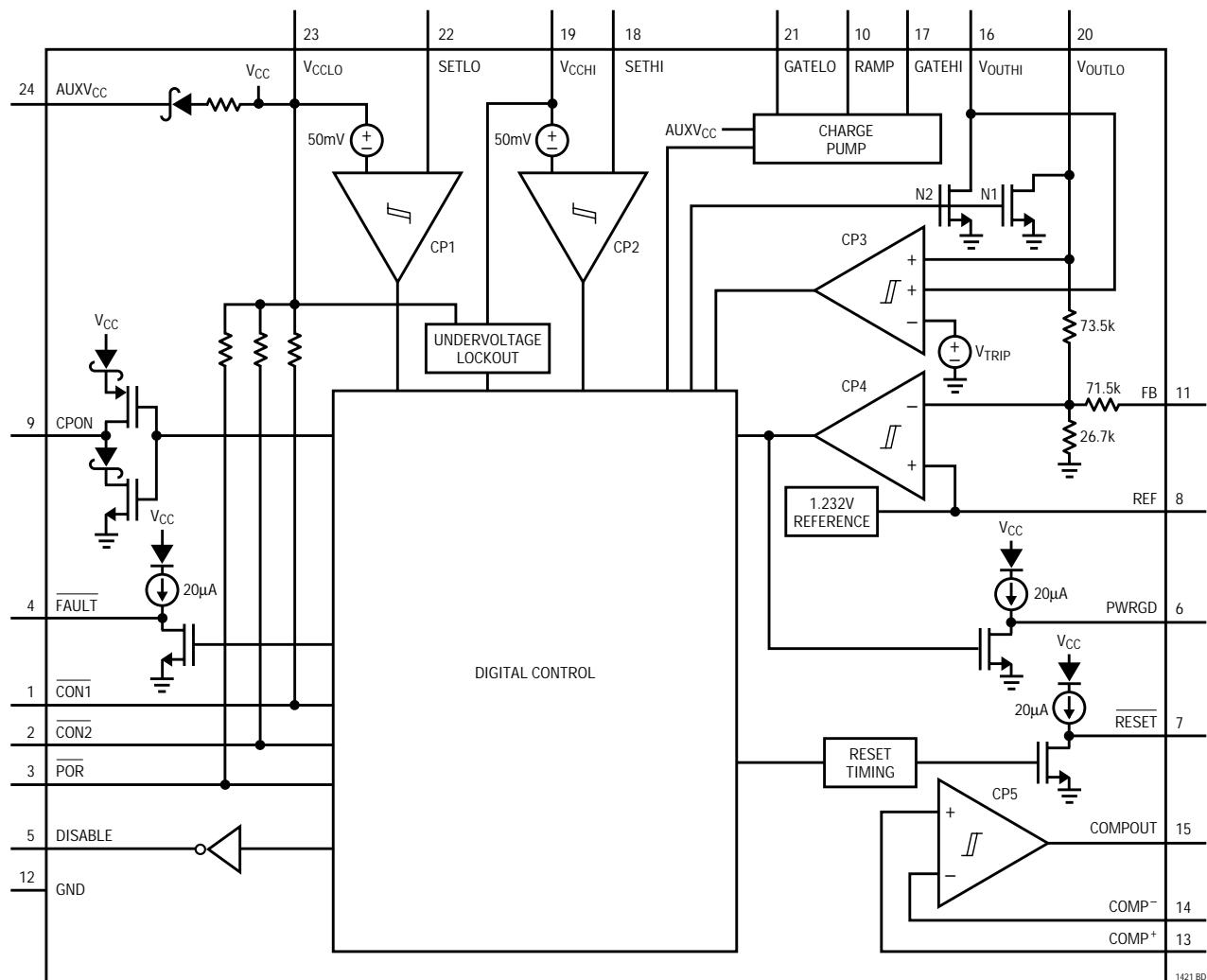

## ブロック図

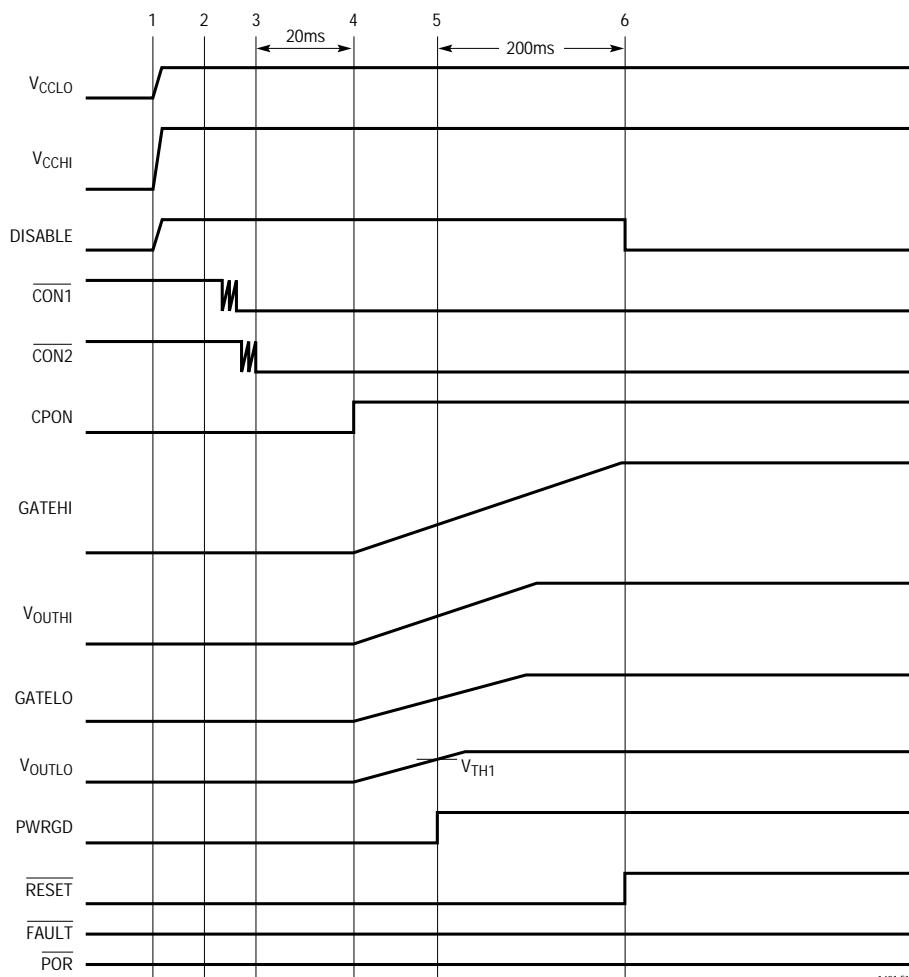

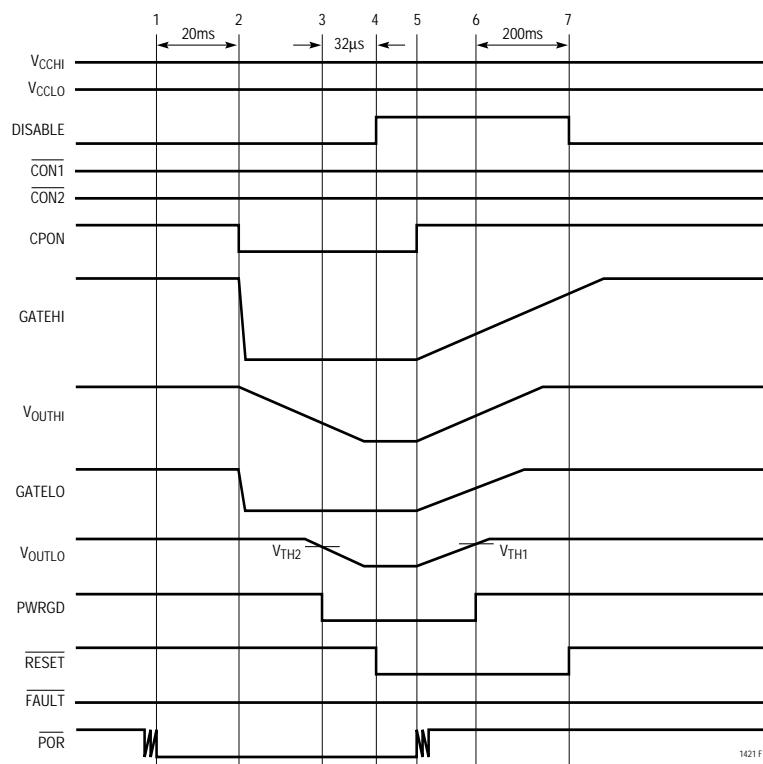

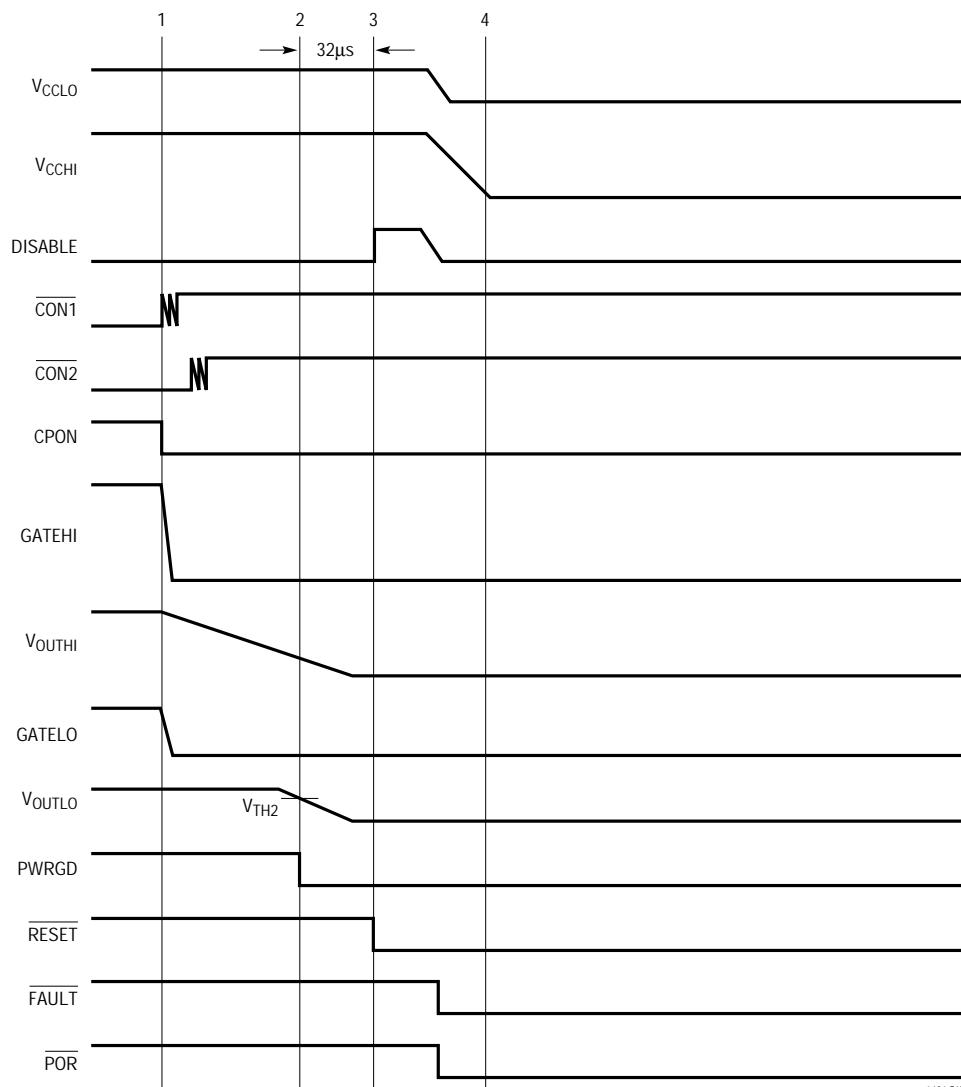

## スイッチング時間波形

図1. 標準動作スイッチング波形

図2. フォールト検出回路の切替え

## アプリケーション情報

### 活線挿入

回路ボードが電源の入っているバックプレーンに挿入されるとき、ボード上のバイパス・コンデンサの充電が完了するまで大きな過渡電流が流れる可能性があります。その過渡電流によってコネクタのピンに回復不可能な損傷が生じたり、電源にグリッチが生じこれにより他のボードがリセットしたりする原因となります。同時に、ボードのデータ・ピンがマークしたりブレークしたりすると、システム・データ・バスが中断することがあります。

LTC1421はボードの供給電圧のオン/オフを制御された方法で行い、電源の入ったバックプレーンへの挿抜を安全に行えるようにします。このICはボードの挿抜の最中にデータ・バスに対してディスエーブル信号を出力したり、ボードに対してすべて必要な電源の管理機能を提供します。

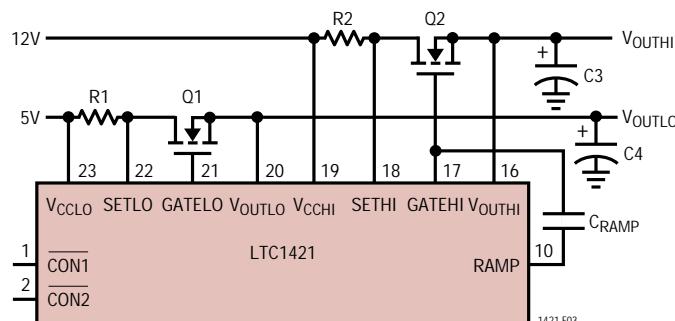

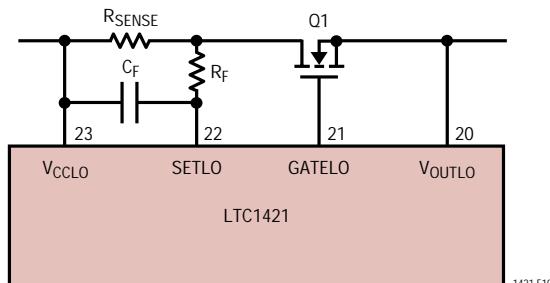

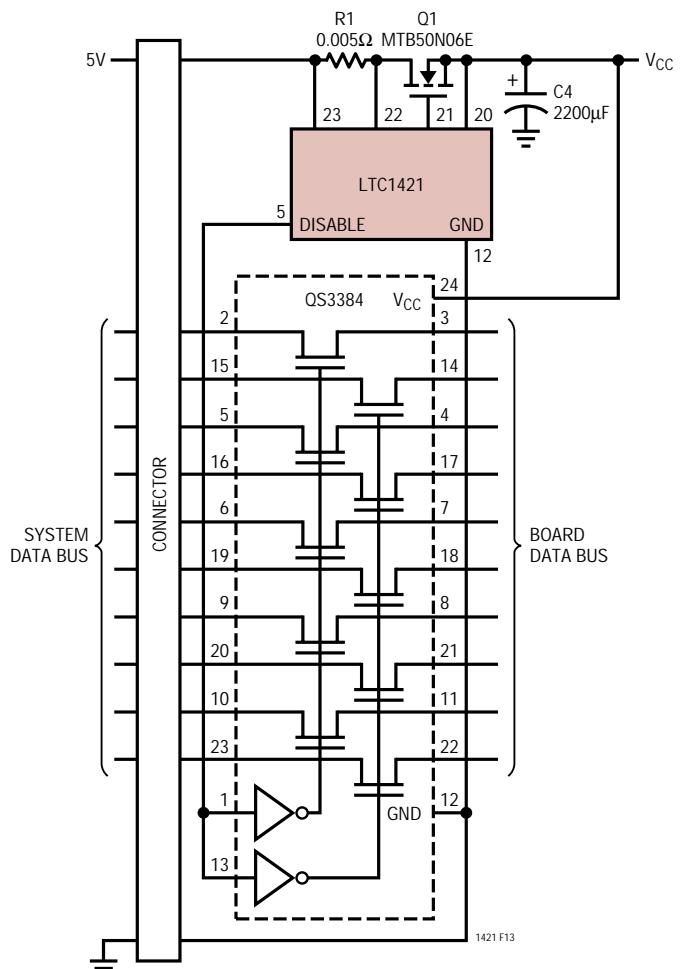

### 電源電圧の上昇方法

ボードの電源供給は電源経路に挿入された外部Nチャネルバス・トランジスタによって制御されます(図3)。R1とR2によって電流フォールトを検出します。バス・トランジスタのゲート電圧を制御されたレートで徐々に上昇させることによって、ボードが挿入されたときに生じるバックプレーンからの過渡サージ電流( $I = C \cdot dV/dt$ )を安全な値に制限することができます。

図3. 電源制御回路

最初にこのICに電源を供給すると両Nチャネルのゲート電位、GATELOとGATEHIは“L”になります。接続検出ピンCON1とCON2が両方とも“L”になって最低20ms経過してから、20μAのリファレンス電流がRAMPからGNDへ接続されます。GATEHIの電圧は20μA/CRAMPのスロープで上昇します(図4)。CRAMPはRAMPピンとGATEHIピン間に接続された外部コンデンサです。GATELOピンの電圧

図4. 電源のターンオン

はGATEHIの電圧からショットキ・ダイオード1個分の電圧降下分を引いた電圧にクランプされます。

各電源の電圧上昇時間は $t = (V_{CC} \times C_{RAMP}) / 20\mu A$ です。パワーダウン時には、ゲートは2つの内部NチャネルFETによってアクティブにプルダウンされます。

図5に示すとおり、負電圧供給もCPONピンによって制御可能です。

ボードがバックプレーンに接続されると、R4によってQ3のゲートが-12VにプルダウンされるためQ3はターンオフします。CPONも同様に-12Vになります。チャージ・ポンプがターンオンすると、CPONは $V_{CCLO}$ になります。Q3のゲートはR4、R5とC2で決る時定数で上昇します。チャージ・ポンプがターンオフすると、CPONはハイインピーダンス状態になり、Q3のゲートはR4とC2の時定数で $V_{EE}$ に放電されQ3はターンオフします。

図5. 負電源制御

## アプリケーション情報

### PRWGDとRESET

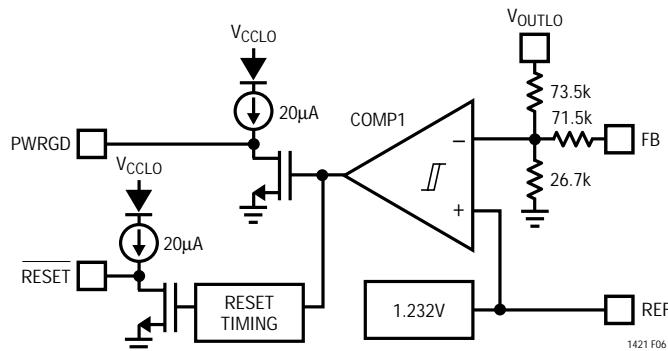

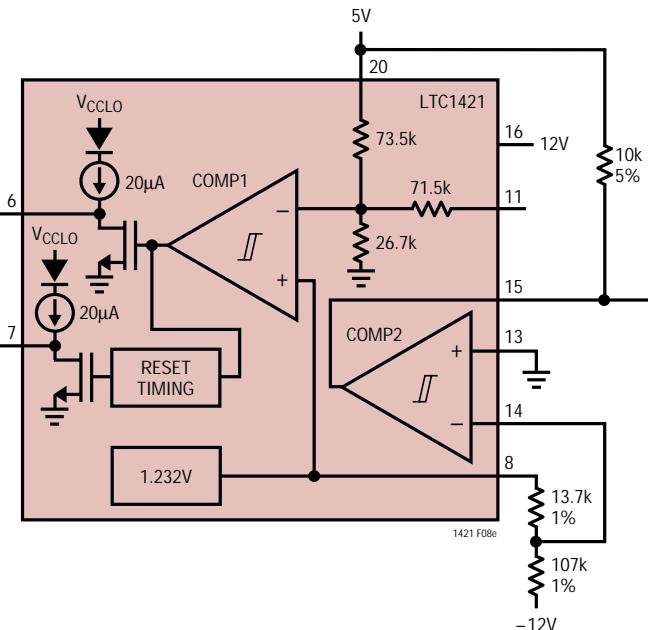

LTC1421は1.232Vのバンドギャップ・リファレンス、内部分割抵抗、およびV<sub>OUTLO</sub>をモニタするための高精度電圧コンパレータを使用しています(図6参照)。

V<sub>OUTLO</sub>用のリセット・スレッショルド電圧は表1にまとめたようにFBピンの接続によって決定されます。

図6. 電源モニタ・ブロック図

表1

| 帰還ピン               | V <sub>OUTLO</sub> リセット電圧 |

|--------------------|---------------------------|

| Floating           | 4.65V                     |

| V <sub>OUTLO</sub> | 2.90V                     |

| GND                | 5.88V                     |

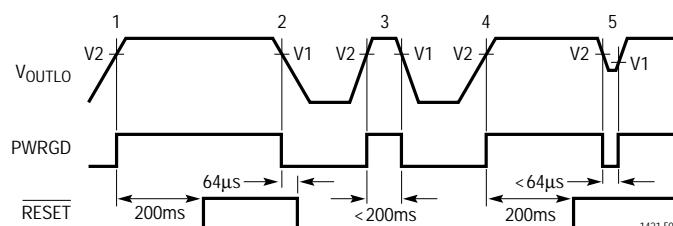

V<sub>OUTLO</sub>電圧がリセット・スレッショルド電圧を超えると、コンパレータ出力が“L”になり、PWRGDピンは直ちに小さな内部電流源または外部抵抗によってV<sub>CCLO</sub>にプルアップされます(図7のタイム・ポイント1と4を参照)。200msの遅延後にRESETは“H”になります。PWRGDの小さい電流源とRESETピンには直列にダイオードが入っているので、それらのピンは外部プルアップ抵抗によって、V<sub>CCLO</sub>に電流を逆流させることなくV<sub>CCLO</sub>より高い電圧に引くことができます。

図7. 電源モニタ波形

V<sub>OUTLO</sub>がリセット・スレッショルド電圧になるとコンパレータの出力が“H”になり、PWRGDはただちに“L”になります(タイム・ポイント2参照)。32µsの遅延後、RESETは“L”になります。このRESETの遅延により、PWRGDが起こるとしているリセットの初期段階の警報として使用できるようにしています。PWRGD信号がマイクロプロセッサの割込み入力に接続されていると、リセットが生じる前にパワーダウン・ルーチンを実行させることができます。

V<sub>OUTLO</sub>が200ms以内の時間リセット・スレッショルドを超えるとPWRGD出力はトリップしますが、RESET出力には影響ありません(タイム・ポイント3参照)。もし、V<sub>OUTLO</sub>がリセット・スレッショルド32µs以内の時間下回ると、PWRGDはトリップしますが、RESET出力は影響されません(タイム・ポイント5参照)。

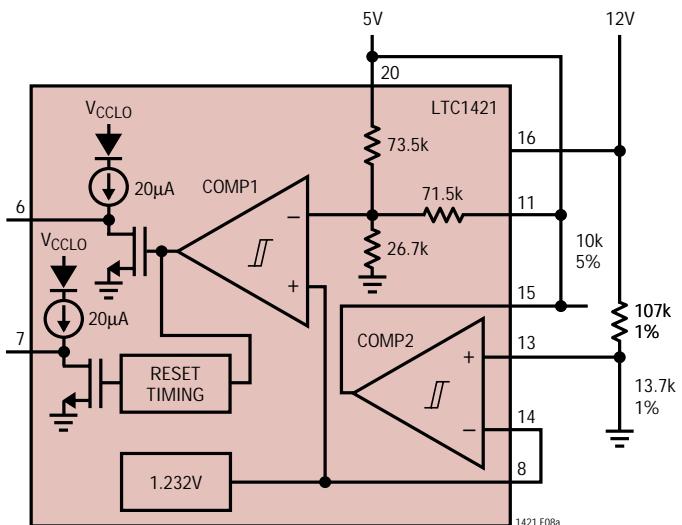

### 電圧コンパレータ

用途を限定しないコンパレータ(COMP2)はV<sub>OUTLO</sub>以外の出力電圧のモニタに使用することができます。図8aにどのように12V電源(V<sub>OUTHI</sub>)をモニタするか、5V電源(V<sub>OUTLO</sub>)が4.65V以下になったときにどのようにリセットを出力するかを示します。12V電源が10.8Vを下回ると、COMP2OUTは“L”になります。FBピンはフローティングされたままでです。

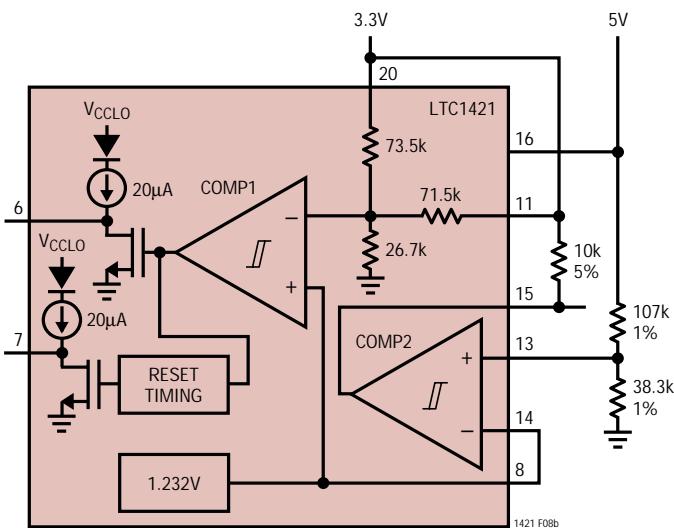

図8bにどのように5V電源(V<sub>OUTHI</sub>)をモニタするか、3.3V電源(V<sub>OUTLO</sub>)が2.9V以下になったときにどのようにリセットを出力するかを示します。5V電源が4.65V下回ると、COMP2OUTは“L”になります。FBピンはV<sub>OUTLO</sub>に接続します。

図8a. 12Vのモニタ、4.65Vでの5Vのリセット

## アプリケーション情報

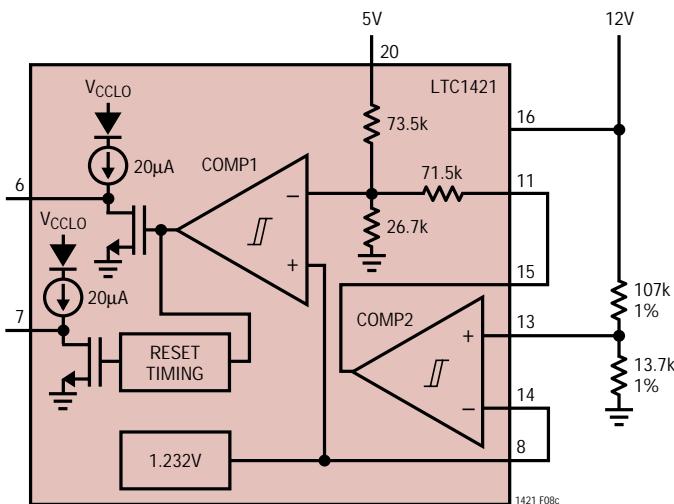

図8cには12V電源( $V_{OUTHI}$ )が10.8Vを下回ったときにリセット信号を発生させるための使い方を示します。5V電源( $V_{OUTLO}$ )も同様に4.65Vを下回ったときにリセットを発生します。12V電源が10.8Vを下回ると、COMPOUT1はFBピンを“L”にして、コンパレータ1の内部スレッショルド電圧を5.88Vに設定します。 $V_{OUTLO}$ が5.88Vより低いので、PWRGDはただちに“L”になり200ms後にリセット信号が出力されます。

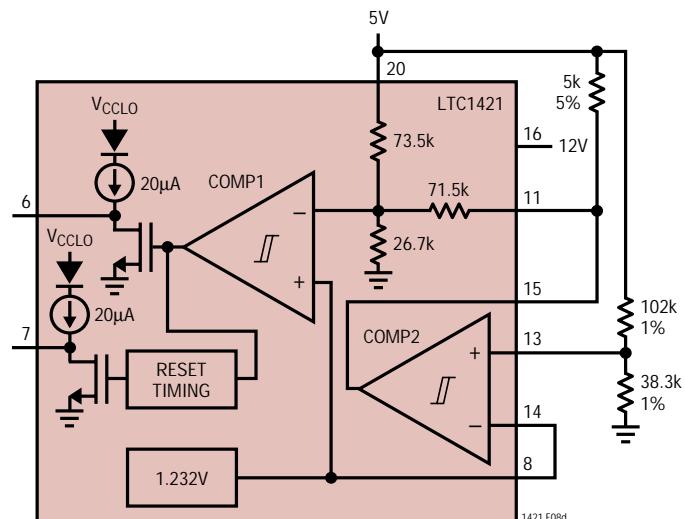

図8dに5V電源 $V_{OUTLO}$ の内部リセット電圧を無視するコンパレータの使い方を示します。

図8b. 5Vをモニタ、2.9Vで3.3Vをリセット

図8c. 10.8Vで12Vをリセット、4.65Vで5Vをリセット

FBピンと $V_{OUTLO}$ ピンに接続された5kの抵抗により、内部スレッショルド電圧が約2.9Vに設定されます。COMP2に外部分割抵抗を接続すると新たなスレッショルド電圧を設定できます。 $V_{OUTLO}$ がこの新たなスレッショルドを下回ると、COMP2はFBピンをグランドにプルダウンし、COMP1の内部スレッショルド電圧を5.88Vに変更し、リセットを発生します。

最後に、コンパレータは図8eに示すように、負電圧のモニタ用にも使用できます。外部の分割抵抗をREFと負電源の間

図8d. 4.5Vで5Vをリセット

図8e. -10.8Vで-12Vをモニタし、-4.65Vで5Vをリセット

## アプリケーション情報

に接続し、コンパレータのトリップ点はGNDになります。

### ソフト・リセットの発生

図9に示すようにピン11(FB)を使用して、供給電圧を循環させないためのソフト・リセットを発生させることができます。5V用にはFBピンは未接続とします。これにより内部のトリップ電圧は4.65Vに設定されます。しかし、FBピンが64μs以上プッシュボタンまたはオープンコレクタ・ロジック・ゲートによってグランドにされると、内部のトリップ点は5.88Vになります。RESETピンは“L”になります。FBピンがリリースされてもRESETピンは200msの間“L”を保ちます。またV<sub>OUTLO</sub>ピンの電圧が32μs以上の時間4.65V以下になると、RESET信号も“L”になります。3.3V電源を使用するときには内部のトリップ点を2.90Vに設定するために、FBピンとV<sub>CCLO</sub>ピンの間に1kの抵抗を接続しなければなりません。

図9. ソフト・リセットの生成

### 低電圧ロックアウト

電源投入時に低電圧ロックアウト回路によって、V<sub>CCLO</sub>とV<sub>CCHI</sub>の両方が2.45Vを超えるまでは、GATELOとGATEHIチャージ・ポンプがオンしないように制御します。

### 電子回路ブレーカ

LTC1421の特徴として、短絡や過電流保護のために装備した電子回路ブレーカがあります。センス抵抗を両方の電源供給ピンとセット・ピンの間に挿入することにより、20μs以上の間センス抵抗の両端の電圧が50mV以上になるときはいつでもブレーカはトリップします。回路ブレーカがト

リップすると、両方のNチャネルMOSFETはすぐにターンオフし、FAULTとPWRGDは“L”になります。そしてRESETピンは32μs後に“L”になります。FAULTはLEDまたはホストに戻るロジック信号に接続して、ボードのフォールト表示を行うことができます。このICはパワー・オン・リセットが発生するか、V<sub>CCHI</sub>およびV<sub>CCLO</sub>の電源が循環するまでトリップ状態を保持します。回路ブレーカ機能を使用しない場合には、V<sub>CCLO</sub>をSETLOに、V<sub>CCHI</sub>をSETHIにそれぞれ接続します。

供給電源のノイズを除去するために応答時間が20μs以上必要な場合は、図10に示すとおり、センス抵抗に外部抵抗とコンデンサを追加することができます。

図10. 短絡保護回路

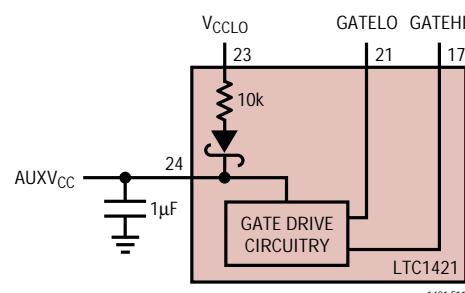

### 補助V<sub>CC</sub>

ボードで短絡が発生すると、過電流が流れ、バックブレーンの電源を壊す可能性があります。もし、入力電圧が十分低くなり、LTC1421のゲート・ドライブ回路がNチャネルパスFETをシャットオフできなくなると、システムは永久短絡状態に陥るかもしれません。

このような状態を避けるため、LTC1421の内部のゲート放電回路の電源はAUXV<sub>CC</sub>からとります。AUXV<sub>CC</sub>はV<sub>CCLO</sub>からショットキ・ダイオードと抵抗を通して接続されています(図11)。

図11. AUXV<sub>CC</sub>回路

## アプリケーション情報

$V_{CCLO}$ が低下すると、AUX $V_{CC}$ に接続された $1\mu F$ のコンデンサには、外部のNチャネルFETを完全にターンオフするのに十分な時間ゲート放電回路を動作させるだけのエネルギーが蓄積されています。

## パワーNチャネルFETの選択

外部バス・トランジスタの $R_{DS(ON)}$ は、全電流時の電圧降下が200mV以下になるように十分低くなければなりません。もし $R_{DS(ON)}$ が高すぎると、トランジスタの電圧降下によって出力電圧がリセット回路をトリップさせる可能性があります。表2にLTC1421に使用できる推奨トランジスタを示します。

表2. NチャンネルFETの選択ガイド

| 電流<br>レベル (A) | 製品番号       | 製造業者  | 説明                                          |

|---------------|------------|-------|---------------------------------------------|

| 0 ~ 1         | MMDF2N02E  | モトローラ | デュアルNチャネルSO-8<br>$R_{DS(ON)}=0.1$           |

| 1 ~ 2         | MMDF3N02HD | モトローラ | デュアルNチャネルSO-8<br>$R_{DS(ON)}=0.09$          |

| 2 ~ 5         | MTB30N06   | モトローラ | シングル30A<br>NチャネルDD Pak<br>$R_{DS(ON)}=0.05$ |

| 5 ~ 10        | MTB50N06E  | モトローラ | シングル<br>NチャネルDD Pak<br>$R_{DS(ON)}=0.025$   |

| 10 ~ 20       | MTB75N05HD | モトローラ | シングル<br>NチャネルDD Pak<br>$R_{DS(ON)}=0.0095$  |

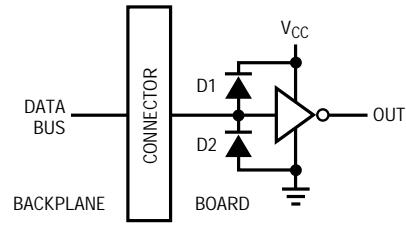

## データ・バス

ホストへのボードの挿入/引抜き時に、データのピンの接続がマーク/ブレークしたとき、システムのデータ・バスに障害が発生しないように注意してください。1つの問題として、データ・バスのピンが最初に接触したときに、完全に放電しているボードのロジック・ゲートの入出力コンデンサに突入電流が流れることです。この突入電流は一時的にデータ・バスに障害を発生させありますが、長期間のダメージにはなりません。この問題を最小限にするには可能な限り入出力コンデンサを小さくすることです。

二番目より重大な問題としては、ほとんどのロジック・ファミリの入出力に着いている $V_{CC}$ へのダイオードです。

図12. データ・バスを装荷している標準ロジック・ゲート

図13. データ・バスのバッファリング

最初ボードに電源が入っていない状態では、ロジック・ゲートの $V_{CC}$ 入力はグランド電位になっています。そしてデータ・バスのピンの接続がマークすると、バス・ラインは入力ダイオードD1によってグランド電位の $V_{CC}$ にクランプされます。大電流がそのダイオードを通して流れ、ロジック・ゲートがラッチアップし、電源が供給されると最終的には

## アプリケーション情報

破壊に至ります。通常これを避けるためには、クランプ・ダイオードの着いていない物、たとえばQSI74FCTTファミリや10ビットQS3384 QuickSwitchなどのデータ・バス・スイッチ(どちらもQuality Semiconductor社製)を使用します。QuickSwitchのバス・スイッチはデータ・バスに直列にNチャネルFETが入っています。ボードが挿入されるとこのスイッチはオフし、電源が安定すると使用可能になります。このスイッチの入出力には $V_{CC}$ への寄生ダイオードは存在せず、しかも容量は非常に小さくなっています。

LTC1421は図13に示すように、QuickSwitchと直結して動作するように設計されています。

DISABLE信号をQS3384のイネーブル入力に接続します。各スイッチはデータ・バス信号に直列に接続されま

す。ボードが挿入されるとDISABLE信号が“H”になりスイッチをオフします。供給電圧が立ち上がりRESETが“H”になると、DISABLEが“L”になりスイッチが有効になります。

### ボード挿入タイミング

ボードが挿入されると、GNDピンがまず接触し、 $V_{CCHI}$ と $V_{CCLO}$ が続きます(図14タイム・ポイント1)。DISABLEはただちに“H”になり、データ・バス・スイッチはオフになります。同時にCON1とCON2が接触し、ホスト・サイドでグランドに接続されます(タイム・ポイント3)。ほとんどのボードは正しく取り付けるために前後でロックされる必要があるので、コネクタの片側だけが接触した時には時間的余裕があります。CON1とCON2はコネクタの両サイドに配置する必要があります。

図14. ボード挿入タイミング

## アプリケーション情報

CON1とCON2の両方が20ms以上接地されると、LTC1421はボードが完全に接続されたものと判断します。そして電源投入が可能になります。V<sub>CCLO</sub>とV<sub>CCHI</sub>が低電圧ロックアウト・スレッショルド電圧2.45Vを超えると、20μA電流リファレンスがRAMPピンからGNDピンに接続されます。チャージ・ポンプがターンオンし、CPONが“H”になります(タイム・ポイント4)。V<sub>OUTHI</sub>とV<sub>OUTLO</sub>が徐々に上昇し始めます。V<sub>OUTLO</sub>がリセット・スレッショルド電圧を超えると、PWRGDはすぐに“H”になります(タイム・ポイント5)。200msの遅延後、RESETは“H”にプルアップされDISABLEは“L”になり、データ・バスは有効になります(タイム・ポイント6)。

### グランド・センス・コンパレータ

PORを20ms以上“L”にすると、GATELOとGATEHIがグランド電位になり、V<sub>OUTLO</sub>とV<sub>OUTHI</sub>は放電します。V<sub>OUTHI</sub>とV<sub>OUTLO</sub>が電圧を降下させている間にPORを“H”に戻すと、放電が続きます。そしてV<sub>TRIP</sub>ポイント以下に低下すると、自動的に電源立上げシーケンスが始まります。

LTC1421のトリップ・ポイント電位は0.1V、LTC1421-2.5のトリップ・ポイント電位は2.5Vに設定されます。

電源立上げ前にV<sub>OUTLO</sub>またはV<sub>OUTHI</sub>を100mV以上にしなければならないアプリケーションでは、LTC1421-2.5を使用しなければなりません。これは、ロジック・チップのボディ・ダイオードを流れるリークによってV<sub>OUTLO</sub>が“H”に保持されるか、ロジック・ラインがブリチャージされる場合に発生します。

ロジック・チップを適切な初期状態にするために、出力をいったんグランド電位付近まで降下させてから再度上昇させる必要があるアプリケーションでは、LTC1421を使用しなければなりません。

### パワーオン・リセット・タイミング

POR入力はボードの電源供給を循環させるためと、回路ブレーカをリセットするために使用されます。PORピンは片側を接地したプッシュボタン・スイッチ、トグル・スイッチ、またはホストからのロジック信号に接続できます。PORが20ms以上“L”になるとパワーオン・リセッ

図15. パワーオン・リセット・タイミング

## アプリケーション情報

ト・シーケンスが始まります(図15のタイム・ポイント2)。PORに加えられた20ms以下のパルスは無視されます。CPONは“L”になります。GATEHIとGATELOはグランドにプルダウンされます。V<sub>OUTLO</sub>がリセット・スレッショルド電圧より低くなると、PWRGDは直ちに“L”になります(タイム・ポイント3)。32μs後(タイム・ポイント4)に続いてRESETとDISABLEが真になります。両方ともグランドに放電し、PORが“H”になるまでそのレベルを維持します。

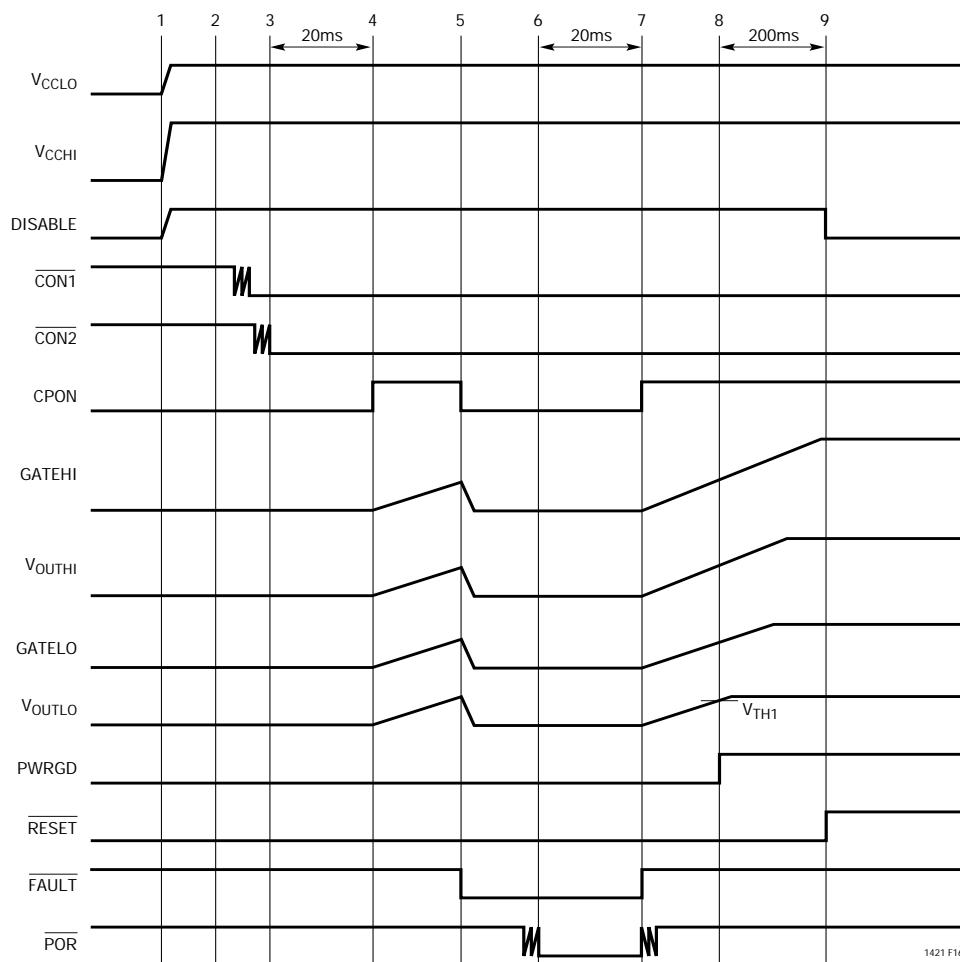

### 回路ブレーカ・タイミング

ボード挿入時にいずれかの電源に短絡が発生した場合の波形を図16に示します。タイム・ポイント1~4はボード

挿入時と同じですが、タイム・ポイント5では電源に短絡が検出された場合を示します。チャージ・ポンプはすぐにターンオフし、V<sub>OUTHI</sub>とV<sub>OUTLO</sub>はグランドにプルダウンされます。CPONとFAULTピンは“L”になります。タイム・ポイント6では、PORを“L”にしてブレーカをリセットしています。PORが20msの間“L”になった(タイム・ポイント7)後、CPONとFAULTは“H”になります。20μAの電流リファレンスがRAMPに接続され、チャージ・ポンプが有効になります。V<sub>OUTHI</sub>とV<sub>OUTLO</sub>は設定されたレートで徐々に上昇します。V<sub>OUTLO</sub>がリセット・スレッショルドを超えるとPWRGDは“H”になります(タイム・ポイント8)。200msの遅延後、RESETは“H”になりDISABLEは“L”になります。

図16. 回路ブレーカ・タイミング

## アプリケーション情報

### ボードの引抜きタイミング

ボードがホストから引き抜かれると、逆のシーケンスが発生します(図17)。CON1とCON2は最も短いピンなので、最初に接触が離れ、内部で“H”にされます(タイム・ポイント1)。チャージ・ポンプはターンオフし、CPONは“L”になります。V<sub>OUTLO</sub>とV<sub>OUTHI</sub>はアクティブ・プルダウンされます。OUTLOがリセット・スレッショルドを下回ると(タイム・ポイント2)、PWRGDは“L”になります。不揮発性メモリに電源異常の情報を格

納するための時間を確保するために、RESETの立下りエッジ(タイム・ポイント3)はPWRGDの立下りエッジから32μs遅れています。

最後に、電源入力ピンV<sub>CCHI</sub>とV<sub>CCLO</sub>が離れます(タイム・ポイント4)。もしスタガピン・コネクタを使用していない場合には、抜き去る前にトグル・スイッチでPORピンをグランドに接続してから電源を切断してください。

図17. ボードの引抜きタイミング

## アプリケーション情報

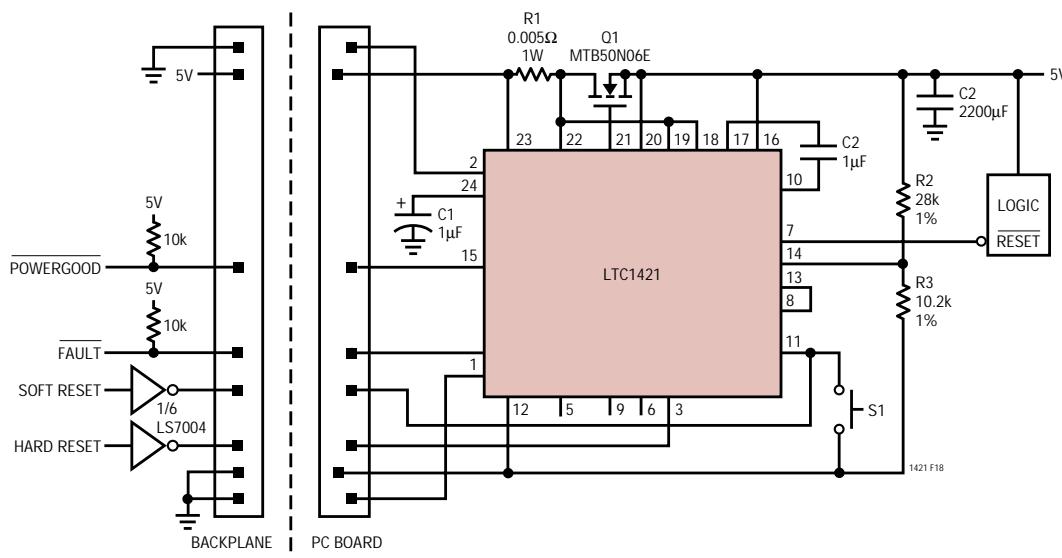

### 5Vのみのアプリケーション

LTC1421は図18に示すように単一5Vのアプリケーションにも使用できます。バックプレーンのオープン・コレクタ・インバータでFB(ピン11)をドライブしたり、プッシュ・ボタンでグランドに落としたりすることでソフト・リセットを発生させることができます。POR(ピン3)をドライブするオープンコレクタ・インバータで、バックプレーンからハード・パワー・リセットを発生させることができます。ハード・リセットはボードをパワーオンさせたり、電子回路ブレーカ

をリセットします。コンパレータは供給電圧をモニタするために使用され、電源電圧が4.65V以上になっている間POWERGOOD信号を“L”にプルダウンします。ソフト・リセットはPOWERGOOD信号に影響しないことに注意してください。FAULT信号は回路ブレーカがトリップしたかどうかを判断するのにもモニタされます。

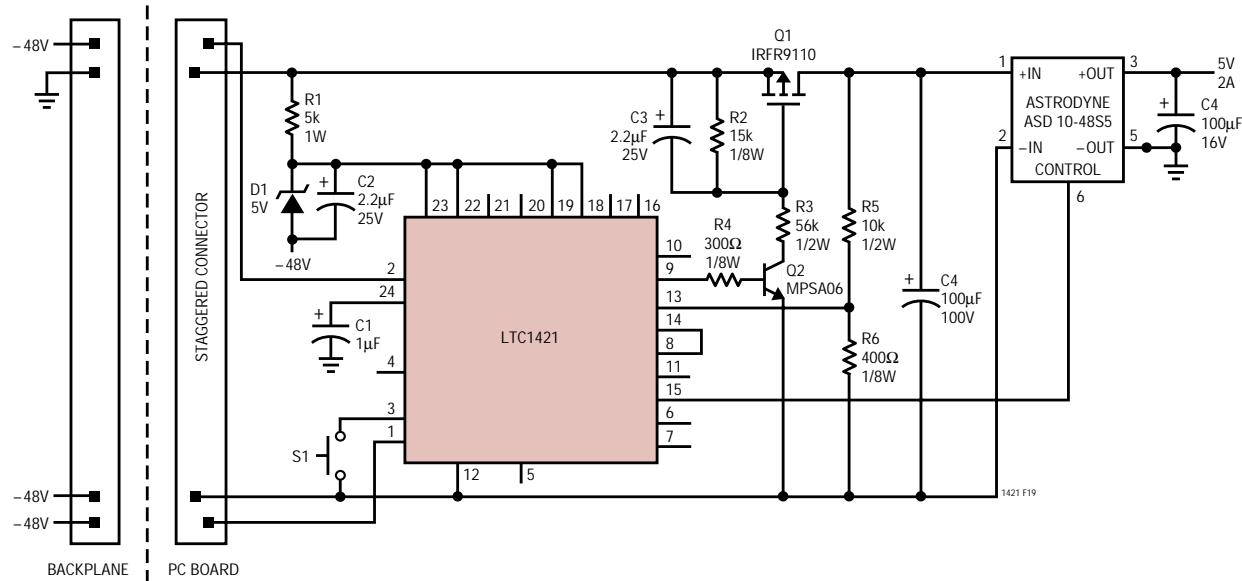

### - 48Vおよび24Vアプリケーション

LTC1421は、図19に示すとおり -48Vアプリケーションでも使用できます。LTC1421はパワー・モジュールで +5Vを供給

図18. ソフト・リセット付き単一5Vアプリケーション

図19. -48Vから5Vのホット・スワップ可能な電源

## アプリケーション情報

しながら活線挿入時の保護を提供します。LTC1421のグランド・ピンは -48Vに接続され、ツェナー・ダイオードD1と抵抗R1によりチップに正の電源を供給します。バイパス・コンデンサC4はPチャネルQ1によって突入電流から保護されます。ボードがバックプレーンに挿入されるとき、トランジスタQ1は抵抗R2によってターンオフされます。接続検出ピンCON1とCON2が20ms以上の間 -48Vに接続されると、CPONは“H”になってQ2をターンオンし、Q1のゲートはR2、R3、C3で決まる時定数で“L”になります。同時に電源モジュールへの電源も立ち上がります。電源モジュールの入力両端の電圧がR5とR6によって設定されるコンパレータ・トリップ・レベルに達すると(この場合は -32V)、コンパレータ出力が“H”になり、5V電源をターンオンします。

LT<sup>®</sup>1170HVスイッチャを用いた安価なソリューションを図20に示します。この場合も、Pチャネル・トランジスタQ1がバイパス・コンデンサを突入電流から保護し、抵抗R5とR6でトリップ電圧を設定します。LT1170HVはVCピンを通してターンオンします。抵抗R11とR14、トランジスタQ4によってRESET信号のモニタを可能にしています。RESET信号はオプト・アイソレータによって5Vにレベル・シフトされます。

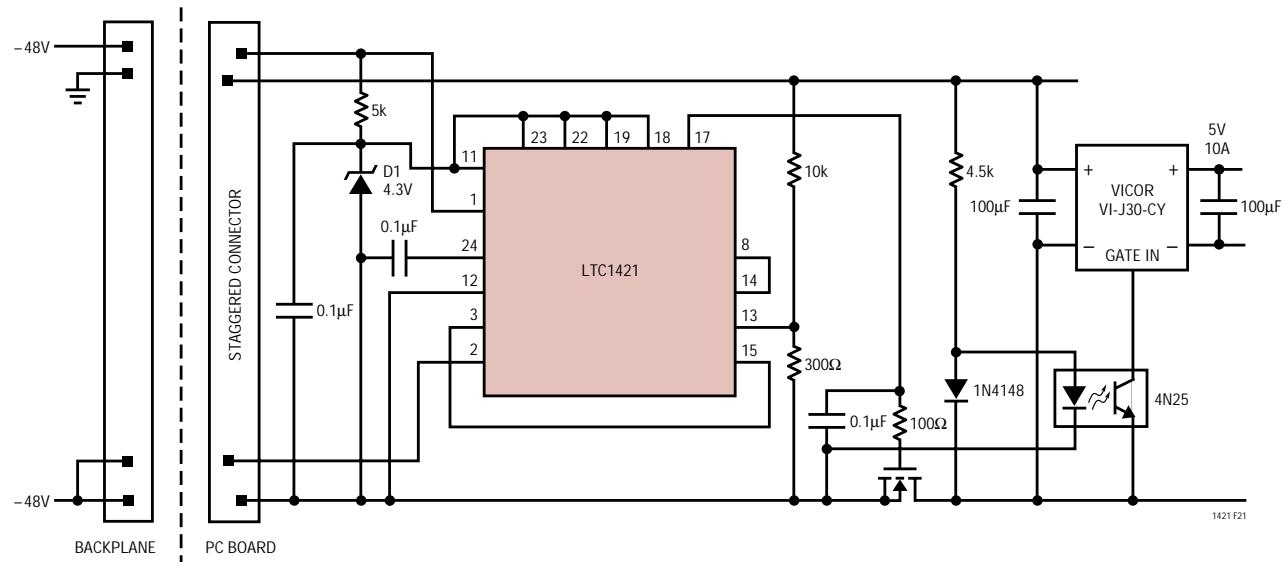

図21では -48Vアプリケーションのために、Pチャネル・パワーFETがNチャネルFETに置き換えられています。この場合も、ツェナー・ダイオードD1と抵抗R1はチップに正電源を供給します。コンデンサC1は、ボードをバックプレーンに活線挿入するときに、Q1をオフにしたままにします。抵抗分割器R1とR2は、内部コンパレータとともに、低電圧ロックアウト機能を実行します。Q1は入力電源電圧が -42V以下のときにのみターンオンします。電源モジュールは、モジュールの入力電圧が47Vに達すると、オプト・アイソレータ4N25によってターンオンします。

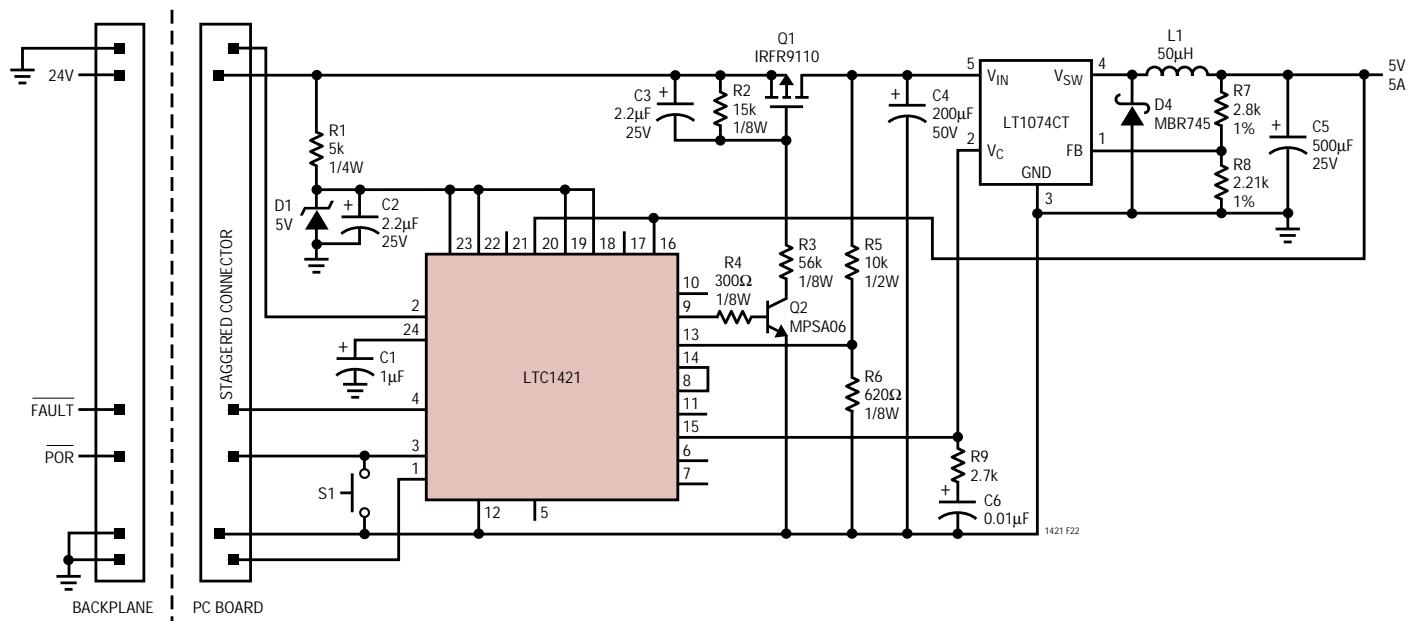

図22にLTC1421を24V電源およびLT1074CT降圧スイッチャで使用する方法を示します。抵抗R5とR6でターンオン・スレッショルドを22Vに設定します。すべての管理信号をレベル・シフトなしで使用できます。

図23に、LTC1421を5V電源およびLTC1430CS8同期降圧スイッチャ・レギュレータとともに使用して、マイクロプロセッサのための最大10A、3.3V出力を生成する方法を示します。抵抗R4、R8、R9は、4.8Vのターンオン電圧と、4.25Vのターンオフ電圧に設定されます。ユーザはプッシュボタン・スイッチS1で出力をリセットします。スイッチS2はマイクロプロセッサをソフト・リセットするためにのみ使用します。

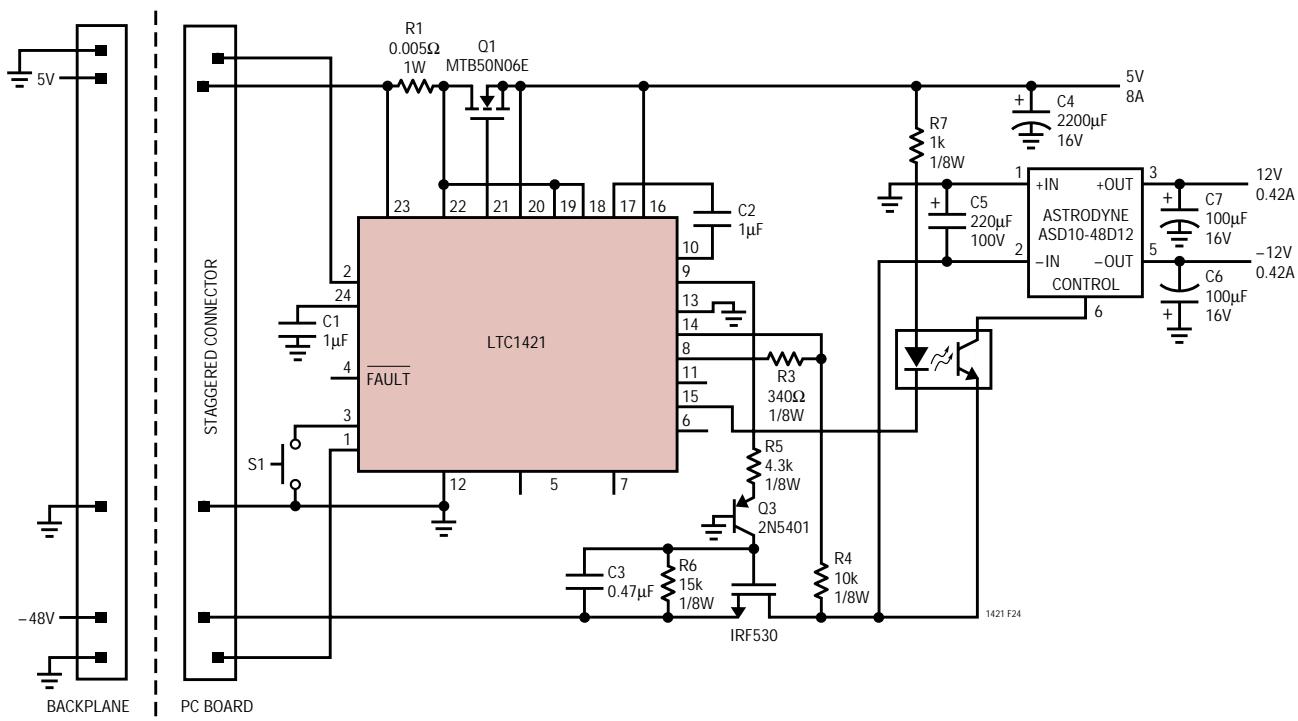

図24にはLTC1421を使用して、5Vおよび -48Vから ±12Vを発生させる方法を示します。抵抗R3とR4は電源モジュールの入力電圧をモニタするのに使用されます。電源モジュールは入力電圧が -36Vに達するまで、ターンオンしないようオプトアイソレータを経由してコントロールされています。ツェナー・ダイオードD2はLTC1421のCPONピンが過電圧によって損傷するのを防止します。

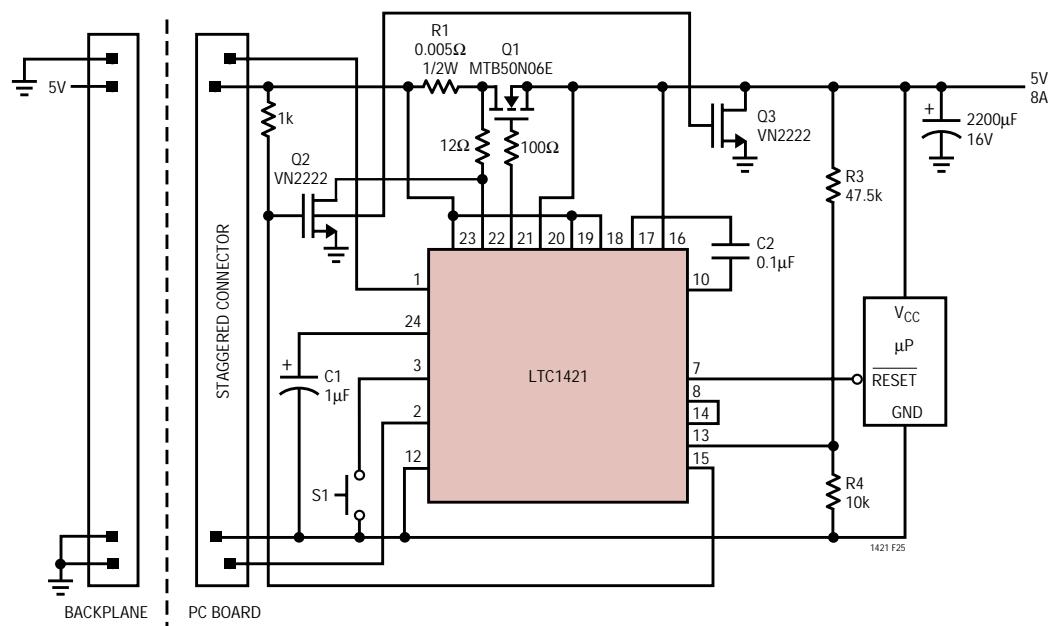

図25にLTC1421を過電圧保護に使用する方法を示します。抵抗R3とR4はトリップ点を7Vに設定します。入力電源電圧が7Vを超えると、Q2がターンオンしQ1がターンオフして、Q3は出力電圧を放電するのを助けます。

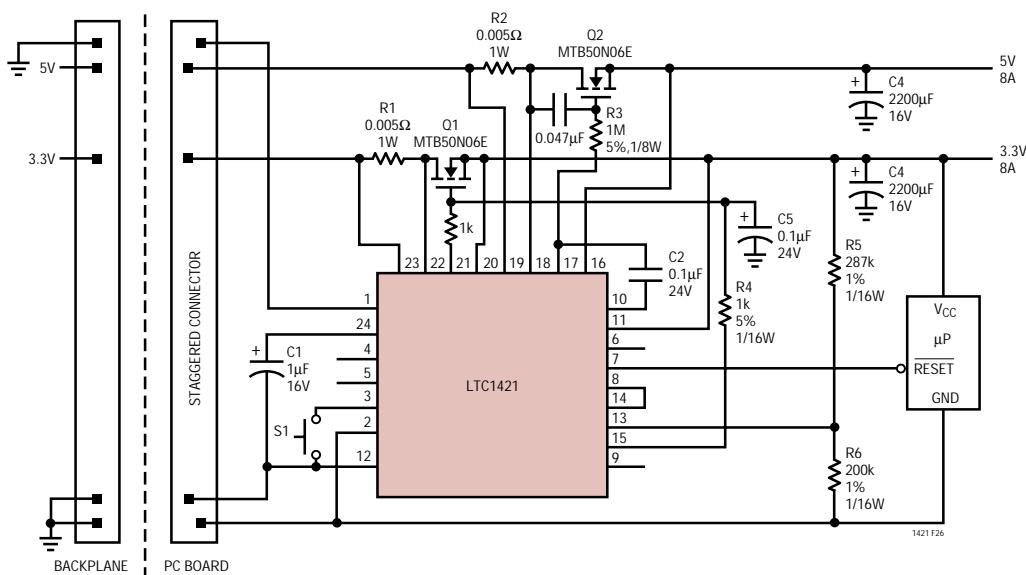

図26はLTC1421を使用して出力の投入および切断シーケンスを制御する方法を示します。5V出力が最初に立ち上がり、続いて3V出力が立ち上がります。切断シーケンスでは、3V出力が最初に立ち下がり、5V電源がそれに続きます。

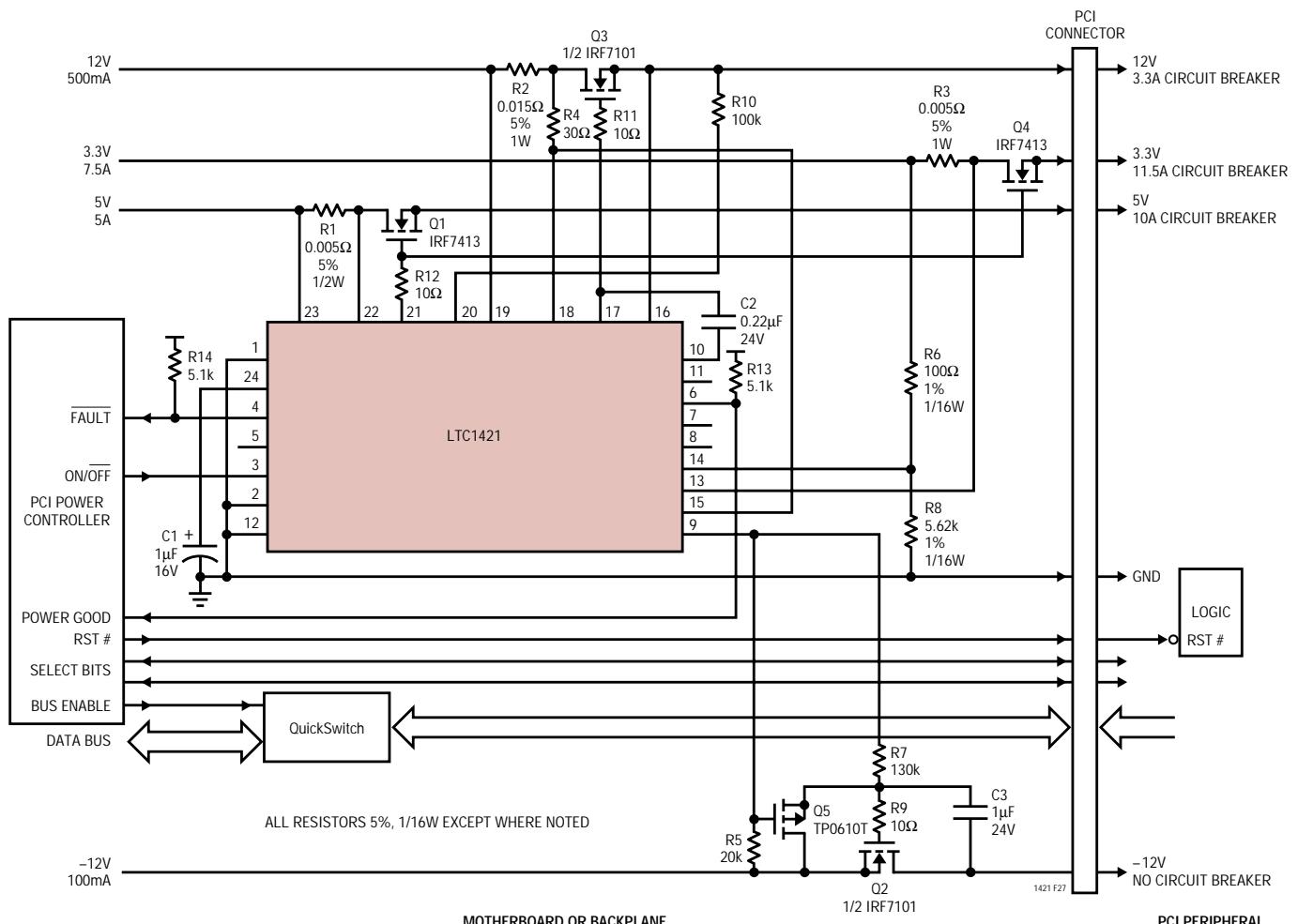

図27はLTC1421を使用してPCIアプリケーション用の3.3V、5V、12V、-12V電源を切り替える方法を示します。3.3V、5V、および12Vの上昇レートはランプ・コンデンサC2によって決定され、-12V電源はR7とC3によって制御されます。内部コンパレータはQ4の過電流保護を行うために使用され、トリップ点は抵抗R6とR8によって設定されます。-12V電源には過電流保護はありません。R10は電源正常信号のトリップ点を10Vに設定するのに使用されます。12V出力が10Vを超えると、PCIコントローラは電源正常信号を受け取り、200ms後にRESETが続けます。

## アプリケーション情報

図20. LT1170HVCTを使用したホット・スワップ可能な - 48Vから5Vへの電源

## アプリケーション情報

図21. ホット・スワップ可能な -48Vから5Vへの電源

図22. LT1074CTを使用したホット・スワップ可能な24Vから5Vへの電源

## アプリケーション情報

図23. LTC1430CS8を使用したホット・スワップ可能な5Vから3.3Vへの電源

## アプリケーション情報

図24. ホット・スワップ可能な5Vおよび-48Vから±12Vへの電源

図25. ホット・スワップ可能な過電圧保護付き5V電源

## アプリケーション情報

図26. 電源投入および切断シーケンス・コントローラ

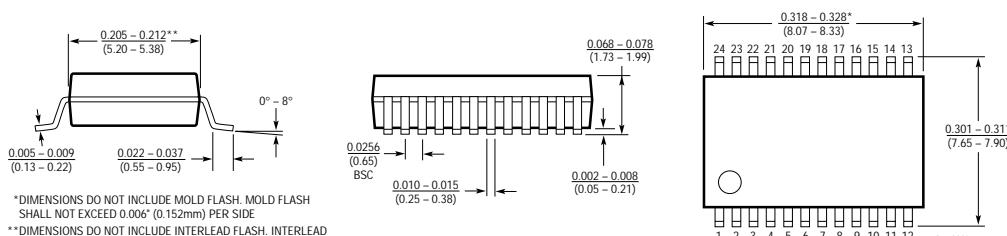

## パッケージ 注記がない限り寸法はインチ(ミリメートル)

**Gパッケージ**

**24ピン・プラスチックSSOP(0.209)**

(LTC DWG # 05-08-1640)

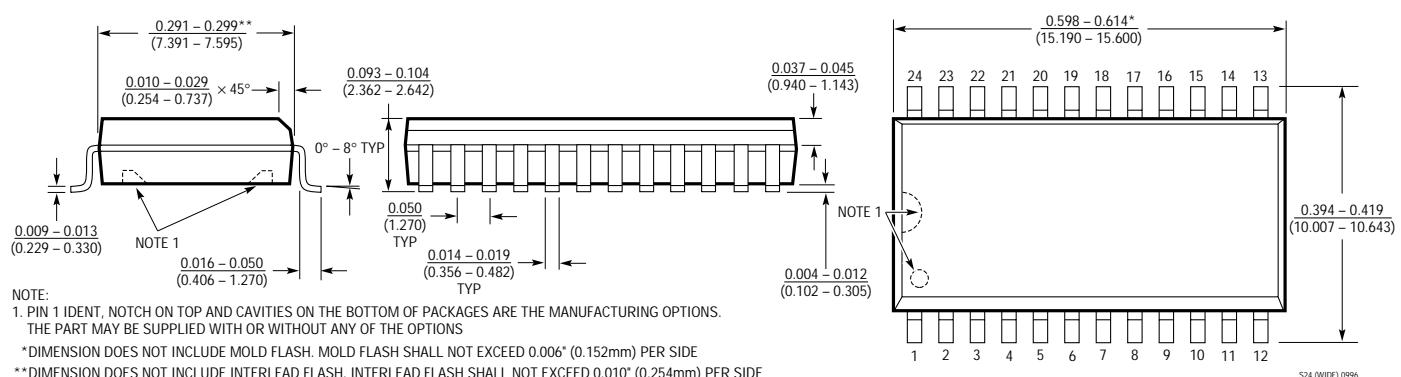

**SWパッケージ**

**24ピン・プラスチック・スモール・アウトライン(広型0.300)**

(LTC DWG # 05-08-1620)

## 標準的応用例

図27. PCI電源コントローラ

## 関連製品

| 製品番号            | 説明                          | 注釈                   |

|-----------------|-----------------------------|----------------------|

| LTC1155         | デュアル・ハイサイド・ドライバ             | 短絡保護とマイクロパワー・スタンバイ動作 |

| LTC1477/LTC1478 | シングルおよびデュアル保護機能付きハイサイド・スイッチ | 突入電流制限、2A短絡保護機能内蔵    |