## 特長

- サンプル・レート: 800ksps

- 消費電力: 150mW

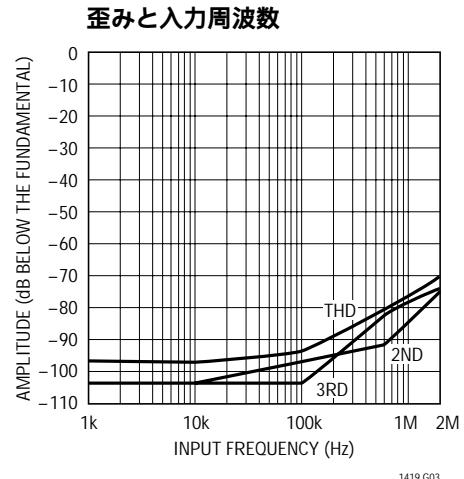

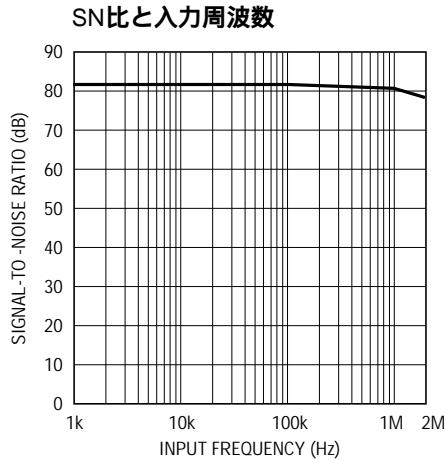

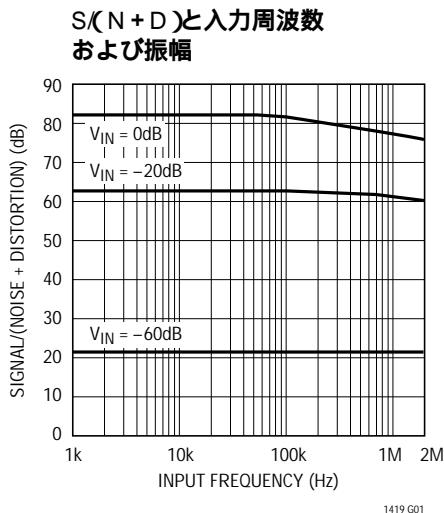

- 81.5dBのS/(N+D)および93dBのTHD

- ミッシング・コードなし

- パイプライン遅延なし

- ナップとスリープのシャットダウン・モード

- 2.5V内部リファレンス(15ppm/°C)または外部リファレンスで動作

- 真の差動入力により同相ノイズを除去

- 20MHzのフルパワー帯域幅サンプリング

- バイポーラ入力範囲: ±2.5V

- 28ピンSSOPおよびSOパッケージ

## アプリケーション

- テレコム

- デジタル信号処理

- 多チャネル・データ収集システム

- 高速データ収集

- スペクトラム分析

- イメージング・システム

## 概要

LTC<sup>®</sup>1419は1μs、800kspsサンプリング14ビットA/Dコンバータです。±5V電源で動作し、消費電力はわずか150mWです。このデバイスは使いやすく、広いダイナミック・レンジをもつサンプル&ホールド、高精度リファレンスを備えています。2つのデジタル的に選択可能なパワー・シャットダウン・モードがあり、低消費電力システムに柔軟性を提供します。

LTC1419のフルスケール入力範囲は $\pm 2.5\text{V}$ です。100kHzの入力周波数での81.5dBのS( N + D )および93dBのTHD、そして400kHzのナイキスト入力周波数での80dBのS( N + D )および86dBのTHDなど、卓越したAC性能を実現しています。

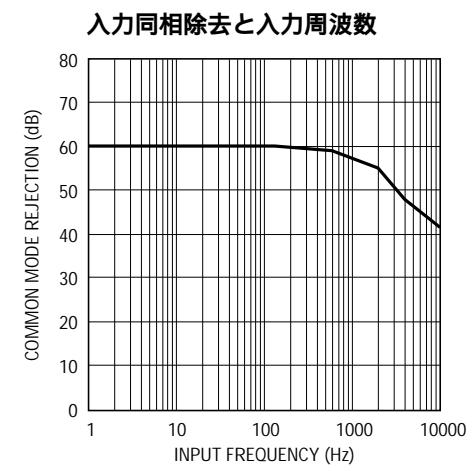

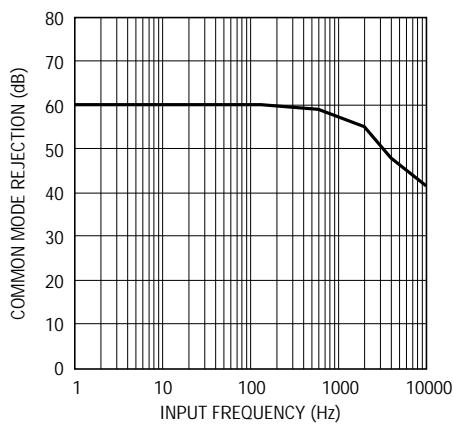

独自の差動入力サンプル・ホールドにより、20MHz帯域幅までシングルエンドまたは差動入力信号を得ることができます。また、60dBの同相除去を実現しているため、ユーザはソースから差動的に信号を測定することにより、グランド・ループと同相ノイズを除去できます。

このADCはμPコンパチブルの14ビット・パラレル出力ポートを備えています。変換結果にはパイプライン遅延はありません。変換スタート入力とデータ・レディ信号(BUSY)が独立しているため、FIFO、DSP、マイクロプロセッサに容易に接続できます。

© LTC LTCはリニアテクノロジー社の登録商標です。

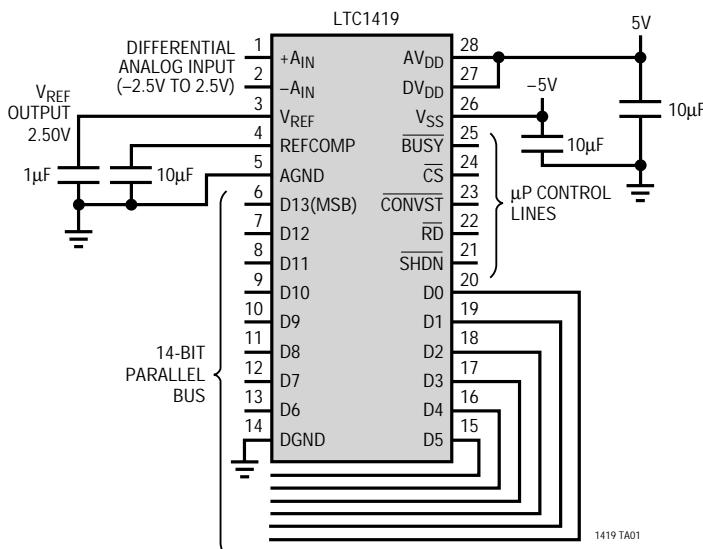

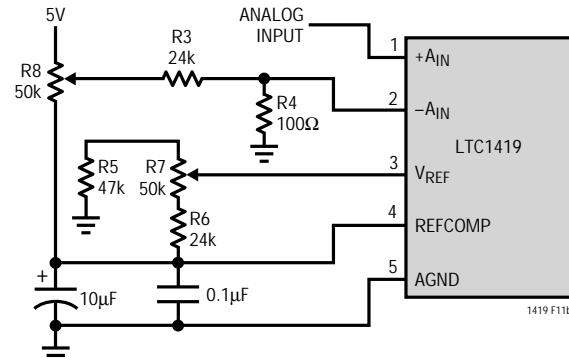

## 標準的应用例

800kHz、14ビット・サンプリングA/Dコンバータ

## 有効ビット数および信号対(ノイズ+歪み) と入力周波数

## 絶対最大定格

$AV_{DD} = V_{DD} = DV_{DD}$  (Note 1, 2)電源電圧 ( $V_{DD}$ ) ..... 6V負電源電圧 ( $V_{SS}$ ) ..... - 6V全電源電圧 ( $V_{SS}$ に対する  $V_{DD}$ ) ..... 12V

アナログ入力電圧 (Note 3)

..... ( $V_{SS} - 0.3V$ )~( $V_{DD} + 0.3V$ )デジタル入力電圧 (Note 4) ..... ( $V_{SS} - 0.3V$ )~10Vデジタル出力電圧 ..... ( $V_{SS} - 0.3V$ )~( $V_{DD} + 0.3V$ )

消費電力 ..... 500mW

動作温度範囲

LTC1419C ..... 0 ~ 70

LTC1419I ..... - 40 ~ 85

保存温度範囲 ..... - 65 ~ 150

リード温度(半田付け、10秒) ..... 300

## パッケージ/発注情報

| TOP VIEW                                                                      |    | ORDER<br>PART NUMBER    |

|-------------------------------------------------------------------------------|----|-------------------------|

| +A <sub>IN</sub>                                                              | 1  | 28 AV <sub>DD</sub>     |

| -A <sub>IN</sub>                                                              | 2  | 27 DV <sub>DD</sub>     |

| V <sub>REF</sub>                                                              | 3  | 26 V <sub>SS</sub>      |

| REFCOMP                                                                       | 4  | 25 BUSY                 |

| AGND                                                                          | 5  | 24 CS                   |

| D13(MSB)                                                                      | 6  | 23 CONVST               |

| D12                                                                           | 7  | 22 RD                   |

| D11                                                                           | 8  | 21 SHDN                 |

| D10                                                                           | 9  | 20 D0                   |

| D9                                                                            | 10 | 19 D1                   |

| D8                                                                            | 11 | 18 D2                   |

| D7                                                                            | 12 | 17 D3                   |

| D6                                                                            | 13 | 16 D4                   |

| DGND                                                                          | 14 | 15 D5                   |

| G PACKAGE                                                                     |    | SW PACKAGE              |

| 28-LEAD PLASTIC SSOP                                                          |    | 28-LEAD PLASTIC SO WIDE |

| $T_{JMAX} = 110^{\circ}\text{C}$ , $\theta_{JA} = 95^{\circ}\text{C/W}$ (G)   |    |                         |

| $T_{JMAX} = 110^{\circ}\text{C}$ , $\theta_{JA} = 130^{\circ}\text{C/W}$ (SW) |    |                         |

ミリタリ・グレードに関してはお問い合わせください。

## コンバータ特性 内部リファレンス (Note 5, 6)

| PARAMETER                     | CONDITIONS                                      | LTC1419 |           |           | LTC1419A |           |            | UNITS                   |

|-------------------------------|-------------------------------------------------|---------|-----------|-----------|----------|-----------|------------|-------------------------|

|                               |                                                 | MIN     | TYP       | MAX       | MIN      | TYP       | MAX        |                         |

| Resolution (No Missing Codes) |                                                 | ●       | 13        |           | 14       |           |            | Bits                    |

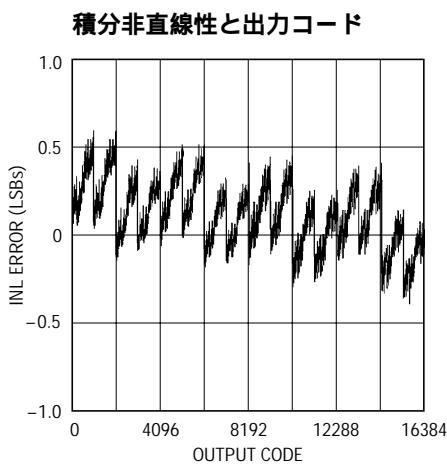

| Integral Linearity Error      | (Note 7)                                        | ●       | $\pm 0.8$ | $\pm 2$   |          | $\pm 0.6$ | $\pm 1.25$ | LSB                     |

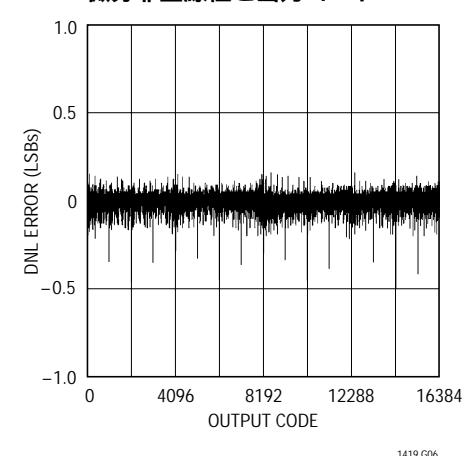

| Differential Linearity Error  |                                                 | ●       | $\pm 0.7$ | $\pm 1.5$ |          | $\pm 0.5$ | $\pm 1$    | LSB                     |

| Offset Error                  | (Note 8)                                        | ●       | $\pm 5$   | $\pm 20$  |          | $\pm 5$   | $\pm 20$   | LSB                     |

| Full-Scale Error              | Internal Reference<br>External Reference = 2.5V |         | $\pm 10$  | $\pm 60$  |          | $\pm 10$  | $\pm 60$   | LSB                     |

| Full-Scale Tempco             | $ I_{OUT(REF)}  = 0$                            |         |           | $\pm 15$  |          |           | $\pm 15$   | ppm/ $^{\circ}\text{C}$ |

## アナログ入力 (Note 5)

| SYMBOL       | PARAMETER                                  | CONDITIONS                                                       | MIN | TYP       | MAX     | UNITS                    |

|--------------|--------------------------------------------|------------------------------------------------------------------|-----|-----------|---------|--------------------------|

| $V_{IN}$     | Analog Input Range (Note 9)                | $4.75V \leq V_{DD} \leq 5.25V$ , $-5.25 \leq V_{SS} \leq -4.75V$ | ●   | $\pm 2.5$ |         | V                        |

| $I_{IN}$     | Analog Input Leakage Current               | CS = High                                                        | ●   |           | $\pm 1$ | $\mu\text{A}$            |

| $C_{IN}$     | Analog Input Capacitance                   | Between Conversions<br>During Conversions                        |     |           | 15<br>5 | pF<br>pF                 |

| $t_{ACQ}$    | Sample-and-Hold Acquisition Time           |                                                                  | ●   | 90        | 300     | ns                       |

| $t_{AP}$     | Sample-and-Hold Aperture Delay Time        |                                                                  |     |           | -1.5    | ns                       |

| $t_{jitter}$ | Sample-and-Hold Aperture Delay Time Jitter |                                                                  |     |           | 2       | $\text{ps}_{\text{RMS}}$ |

| CMRR         | Analog Input Common Mode Rejection Ratio   | $-2.5V < (-A_{IN} = A_{IN}) < 2.5V$                              |     |           | 60      | dB                       |

## ダイナミック精度 (Note 5)

| SYMBOL    | PARAMETER                            | CONDITIONS                                                                       |   | MIN  | TYP  | MAX | UNITS |

|-----------|--------------------------------------|----------------------------------------------------------------------------------|---|------|------|-----|-------|

| S/(N + D) | Signal-to-(Noise + Distortion) Ratio | 100kHz Input Signal<br>390kHz Input Signal                                       | ● | 78   | 81.5 |     | dB    |

|           |                                      |                                                                                  |   | 80.0 |      |     | dB    |

| THD       | Total Harmonic Distortion            | 100kHz Input Signal, First 5 Harmonics<br>390kHz Input Signal, First 5 Harmonics | ● |      | -93  | -86 | dB    |

|           |                                      |                                                                                  |   |      | -86  |     | dB    |

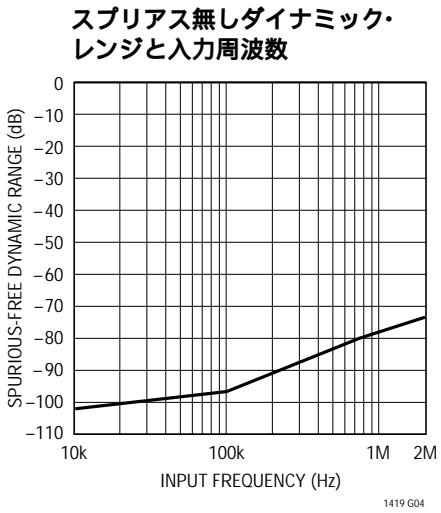

| SFDR      | Spurious Free Dynamic Range          | 100kHz Input Signal                                                              | ● |      | -95  | -86 | dB    |

| IMD       | Intermodulation Distortion           | $f_{IN1} = 29.37\text{kHz}$ , $f_{IN2} = 32.446\text{kHz}$                       |   |      | -86  |     | dB    |

|           | Full-Power Bandwidth                 |                                                                                  |   |      | 20   |     | MHz   |

|           | Full-Linear Bandwidth                | $S/(N + D) \geq 77\text{dB}$                                                     |   |      | 1    |     | MHz   |

## 内部リファレンス特性 (Note 5)

| PARAMETER                   | CONDITIONS                                                                            |  | MIN   | TYP   | MAX   | UNITS  |

|-----------------------------|---------------------------------------------------------------------------------------|--|-------|-------|-------|--------|

| $V_{REF}$ Output Voltage    | $I_{OUT} = 0$                                                                         |  | 2.480 | 2.500 | 2.520 | V      |

| $V_{REF}$ Output Tempco     | $I_{OUT} = 0$                                                                         |  |       | ±15   |       | ppm/°C |

| $V_{REF}$ Line Regulation   | $4.75\text{V} \leq V_{DD} \leq 5.25\text{V}$ , $-5.25 \leq V_{SS} \leq -4.75\text{V}$ |  |       | 0.05  |       | LSB/V  |

| $V_{REF}$ Output Resistance | $-0.1\text{mA} \leq  I_{OUT}  \leq 0.1\text{mA}$                                      |  |       | 2     |       | kΩ     |

| REFCOMP Output Voltage      | $I_{OUT} = 0$                                                                         |  |       | 4.06  |       | V      |

## デジタル入力とデジタル出力特性 (Note 5)

| SYMBOL       | PARAMETER                         | CONDITIONS                                                               |   | MIN | TYP  | MAX  | UNITS |

|--------------|-----------------------------------|--------------------------------------------------------------------------|---|-----|------|------|-------|

| $V_{IH}$     | High Level Input Voltage          | $V_{DD} = 5.25\text{V}$                                                  | ● | 2.4 |      |      | V     |

| $V_{IL}$     | Low Level Input Voltage           | $V_{DD} = 4.75\text{V}$                                                  | ● |     |      | 0.8  | V     |

| $I_{IN}$     | Digital Input Current             | $V_{IN} = 0\text{V}$ to $V_{DD}$                                         | ● |     |      | ±10  | μA    |

| $C_{IN}$     | Digital Input Capacitance         |                                                                          |   |     | 5    |      | pF    |

| $V_{OH}$     | High Level Output Voltage         | $V_{DD} = 4.75\text{V}$<br>$I_O = -10\text{μA}$<br>$I_O = -200\text{μA}$ | ● |     | 4.5  |      | V     |

| $V_{OL}$     | Low Level Output Voltage          | $V_{DD} = 4.75\text{V}$<br>$I_O = 160\text{μA}$<br>$I_O = 1.6\text{mA}$  | ● | 4.0 | 0.05 | 0.10 | V     |

| $I_{OZ}$     | Hi-Z Output Leakage D13 to D0     | $V_{OUT} = 0\text{V}$ to $V_{DD}$ , $\overline{CS}$ High                 | ● |     |      | ±10  | μA    |

| $C_{OZ}$     | Hi-Z Output Capacitance D13 to D0 | $\overline{CS}$ High (Note 9)                                            | ● |     |      | 15   | pF    |

| $I_{SOURCE}$ | Output Source Current             | $V_{OUT} = 0\text{V}$                                                    |   |     | -10  |      | mA    |

| $I_{SINK}$   | Output Sink Current               | $V_{OUT} = V_{DD}$                                                       |   |     | 10   |      | mA    |

## 電源要求条件 (Note 5)

| SYMBOL   | PARAMETER                                         | CONDITIONS                                                                                                      |   | MIN   | TYP              | MAX   | UNITS          |

|----------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---|-------|------------------|-------|----------------|

| $V_{DD}$ | Positive Supply Voltage                           | (Notes 10, 11)                                                                                                  |   | 4.75  |                  | 5.25  | V              |

| $V_{SS}$ | Negative Supply Voltage                           | (Note 10)                                                                                                       |   | -4.75 |                  | -5.25 | V              |

| $I_{DD}$ | Positive Supply Current<br>Nap Mode<br>Sleep Mode | $\overline{SHDN} = 0\text{V}$ , $\overline{CS} = 0\text{V}$<br>$\overline{SHDN} = 0\text{V}$ , $CS = 5\text{V}$ | ● |       | 11<br>1.5<br>250 | 20    | mA<br>mA<br>μA |

| $I_{SS}$ | Negative Supply Current<br>Nap Mode<br>Sleep Mode | $\overline{SHDN} = 0\text{V}$ , $\overline{CS} = 0\text{V}$<br>$\overline{SHDN} = 0\text{V}$ , $CS = 5\text{V}$ | ● |       | 19<br>100<br>1   | 30    | mA<br>μA<br>μA |

## 電源要求条件 (Note 5)

| SYMBOL           | PARAMETER                                   | CONDITIONS                                                                                                           |   | MIN               | TYP       | MAX               | UNITS          |

|------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---|-------------------|-----------|-------------------|----------------|

| P <sub>DIS</sub> | Power Dissipation<br>Nap Mode<br>Sleep Mode | $\overline{\text{SHDN}} = 0V, \overline{\text{CS}} = 0V$<br>$\overline{\text{SHDN}} = 0V, \overline{\text{CS}} = 5V$ | ● | 150<br>7.5<br>1.2 | 240<br>12 | 150<br>7.5<br>1.2 | mW<br>mW<br>mW |

## タイミング特性 (Note 5)

| SYMBOL                   | PARAMETER                                                                                      | CONDITIONS                                         |   | MIN      | TYP  | MAX | UNITS |

|--------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------|---|----------|------|-----|-------|

| f <sub>SAMPLE(MAX)</sub> | Maximum Sampling Frequency                                                                     |                                                    | ● | 800      |      |     | kHz   |

| t <sub>CONV</sub>        | Conversion Time                                                                                |                                                    | ● | 950      | 1150 |     | ns    |

| t <sub>ACQ</sub>         | Acquisition Time                                                                               |                                                    | ● | 90       | 300  |     | ns    |

| t <sub>ACQ + CONV</sub>  | Acquisition + Conversion Time                                                                  |                                                    | ● | 1040     | 1250 |     | ns    |

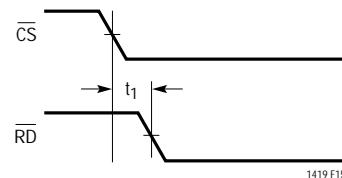

| t <sub>1</sub>           | $\overline{\text{CS}} \rightarrow \overline{\text{RD}}$ Setup Time                             | (Notes 9, 10)                                      | ● | 0        |      |     | ns    |

| t <sub>2</sub>           | $\overline{\text{CS}} \downarrow \rightarrow \overline{\text{CONVST}} \downarrow$ Setup Time   | (Notes 9, 10)                                      | ● | 40       |      |     | ns    |

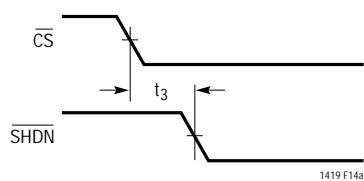

| t <sub>3</sub>           | $\overline{\text{CS}} \downarrow \rightarrow \overline{\text{SHDN}} \downarrow$ Setup Time     | (Notes 9, 10)                                      |   | 40       |      |     | ns    |

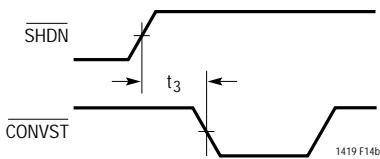

| t <sub>4</sub>           | $\overline{\text{SHDN}} \uparrow \rightarrow \overline{\text{CONVST}} \downarrow$ Wake-Up Time | (Note 10)                                          |   | 400      |      |     | ns    |

| t <sub>5</sub>           | $\overline{\text{CONVST}}$ Low Time                                                            | (Notes 10, 11)                                     | ● | 40       |      |     | ns    |

| t <sub>6</sub>           | $\overline{\text{CONVST}}$ to $\overline{\text{BUSY}}$ Delay                                   | $C_L = 25\text{pF}$                                |   | 20       |      |     | ns    |

|                          |                                                                                                |                                                    | ● |          | 50   |     | ns    |

| t <sub>7</sub>           | Data Ready Before $\overline{\text{BUSY}} \uparrow$                                            |                                                    | ● | 20       | 50   |     | ns    |

|                          |                                                                                                |                                                    | ● | 15       |      |     | ns    |

| t <sub>8</sub>           | Delay Between Conversions                                                                      | (Note 10)                                          | ● | 40       |      |     | ns    |

| t <sub>9</sub>           | Wait Time $\overline{\text{RD}} \downarrow$ After $\overline{\text{BUSY}} \uparrow$            |                                                    | ● | -5       |      |     | ns    |

| t <sub>10</sub>          | Data Access Time After $\overline{\text{RD}} \downarrow$                                       | $C_L = 25\text{pF}$                                |   | 15       | 25   |     | ns    |

|                          |                                                                                                |                                                    | ● |          | 35   |     | ns    |

| t <sub>11</sub>          | Bus Relinquish Time                                                                            | $C_L = 100\text{pF}$                               |   | 20       | 35   |     | ns    |

|                          |                                                                                                |                                                    | ● |          | 50   |     | ns    |

| t <sub>11</sub>          | Bus Relinquish Time                                                                            | $0^\circ\text{C} \leq T_A \leq 70^\circ\text{C}$   |   | 10       | 20   |     | ns    |

|                          |                                                                                                | $-40^\circ\text{C} \leq T_A \leq 85^\circ\text{C}$ | ● |          | 25   |     | ns    |

|                          |                                                                                                |                                                    | ● |          | 30   |     | ns    |

| t <sub>12</sub>          | $\overline{\text{RD}}$ Low Time                                                                |                                                    | ● | $t_{10}$ |      |     | ns    |

| t <sub>13</sub>          | $\overline{\text{CONVST}}$ High Time                                                           |                                                    | ● | 40       |      |     | ns    |

は全動作温度範囲の規格値を意味する。その他すべてのリミット値と標準値は $T_A = 25^\circ\text{C}$ 。

Note 1 : 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2 : すべての電圧値は、注記がない限り、DGNDとAGNDが連結されたグランドを基準とする。

Note 3 : これらのピン電圧を $V_{SS}$ より低くすると、 $V_{DD}$ より高くすると、内部ダイオードによってクランプされる。この製品は $V_{SS}$ より低い、または $V_{DD}$ より高い電圧を加えてもラッチアップを起こさずに100mA以上の入力電流を処理することができる。

Note 4 : これらのピン電圧を $V_{SS}$ より低くすると、内部ダイオードでクランプされる。この製品は $V_{SS}$ より低い電圧を加えても、ラッチアップを起こさずに100mA以上の入力電流を処理することができる。これらのピンは $V_{DD}$ にクランプされない。

Note 5 : 注記がない限り、 $V_{DD} = 5V$ 、 $f_{\text{SAMPLE}} = 800\text{kHz}$ 、 $t_r = t_f = 5\text{ns}$

Note 6 : 直線性、オフセット、およびフルスケール仕様は、 $-A_{IN}$ を接地した状態のシングルエンド +  $A_{IN}$ 入力に適用される。

Note 7 : 積分非直線性は伝達曲線の実際のエンドポイントを通過する直線からのコードの偏差として定義される。偏差は量子化幅の中心から測定される。

Note 8 : バイポーラ・オフセットは、出力コードが0000 0000 0000 00と1111 1111 1111の間で変化するときに、-0.5LSBから測定したオフセット電圧。

Note 9 : 設計で保証されているが、テストされていない。

Note 10 : 推奨動作条件。

Note 11 :  $\overline{\text{CONVST}}$ の立ち下りエッジで変換を開始する。変換中にビット決定点で $\overline{\text{CONVST}}$ が "H" に戻ると、わずかな誤差が生じる可能性がある。最良の性能を得るために、変換開始からまたは $\overline{\text{BUSY}}$ が立ち上がってから650ns以内に $\overline{\text{CONVST}}$ が "H" に戻るようにする。

## 標準的性能特性

## ピン機能

+A<sub>IN</sub>( ピン1 ): ±2.5Vの正アナログ入力。

-A<sub>IN</sub>( ピン2 ): ±2.5Vの負アナログ入力。

V<sub>REF</sub>( ピン3 ): 2.5Vリファレンス出力。1μFでAGNDにバイパスします。

REFCOMP( ピン4 ): 4.06Vリファレンス出力。10μFタンタル・コンデンサと0.1μFまたは10μFセラミック・コンデンサを並列に接続してAGNDにバイパスします。

AGND( ピン5 ): アナログ・グランド。

D13からD0( ピン6から13 ): スリーステート・データ出力。

DGND( ピン14 ): 内部ロジック用デジタル・グランド。AGNDに接続してください。

D5からD0( ピン15から20 ): スリーステート・データ出力。

SHDN( ピン21 ): シャットダウン入力。“L”でシャットダウンを選択します。シャットダウン・モードはCSピンによって選択されます。CS=0はナップ・モード、CS=1はスリープ・モードです。

RD( ピン22 ): READ入力。CSが“L”的ときに出力ドライバをイネーブルします。

CONVST( ピン23 ): 変換開始信号。このアクティブ“L”信号の立下りエッジで変換を開始します。

CS( ピン24 ): チップ・セレクト。この入力は、ADCがCONVSTおよびRD入力を認識するには“L”でなければなりません。また、SHDNが“L”になるとシャットダウン・モードに設定します。CSとSHDNが“L”的とき、高速ウェイクアップのナップ・モードを選択します。CSが“H”でSHDNが“L”的とき、スリープ・モードを選択します。

BUSY( ピン25 ): BUSY出力はコンバータのステータスを示します。変換を実行中のときには“L”になります。BUSYの立上りエッジでデータが有効になります。

V<sub>SS</sub>( ピン26 ): -5V負電源。10μFタンタル・コンデンサと0.1μFまたは10μFセラミック・コンデンサを並列に接続してAGNDにバイパスします。

DV<sub>DD</sub>( ピン27 ): 5V正電源。ピン28に短絡します。

AV<sub>DD</sub>( ピン28 ): 5V正電源。10μFタンタル・コンデンサと0.1μFまたは10μFセラミック・コンデンサを並列に接続してAGNDにバイパスします。

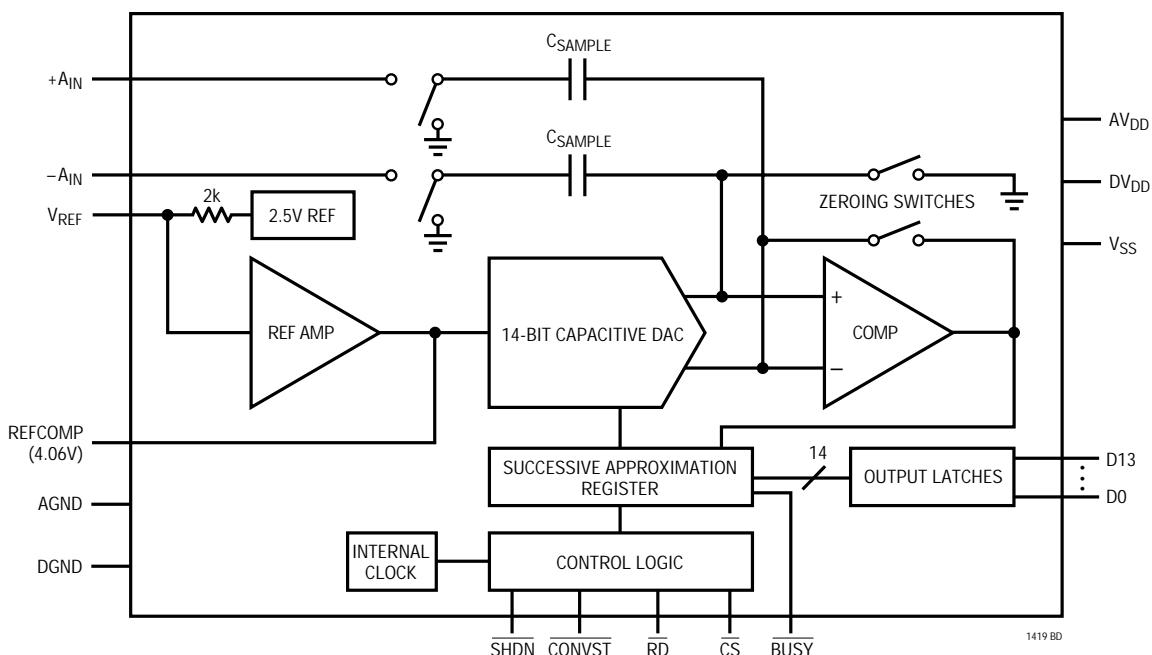

## 機能ブロック図

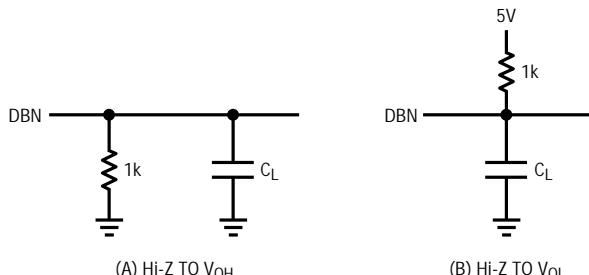

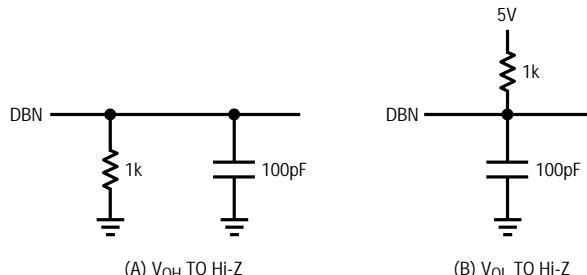

## テスト回路

## アクセス・タイミングの負荷回路

1419 TC01

## 出力フロート遅延の負荷回路

1419 TC02

## アプリケーション情報

## 変換の詳細説明

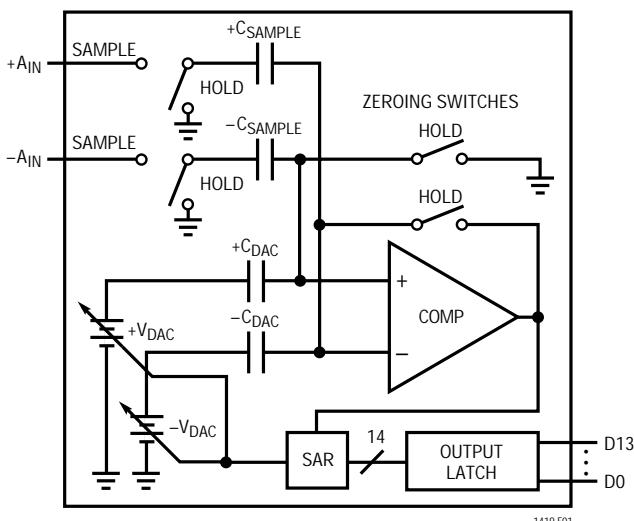

LTC1419は、逐次比較アルゴリズムと内部サンプル&ホールド回路を使用して、アナログ信号を14ビットのパラレル出力に変換します。このADCは高精度リファレンスと内部クロックを備えています。コントロール・ロジックにより、簡単にマイクロプロセッサやDSPにインターフェースすることができます(データ・フォーマットについては、デジタル・インターフェースのセクションを参照してください)。

変換開始は、CSおよびCONVST入力でコントロールされます。変換が始まると、逐次比較レジスタ(SAR)がリセットされます。一度変換サイクルが始まると、再スタートすることはできません。

図1. 簡略ブロック図

変換中は、内部の差動14ビット容量性DAC出力が、SARによって最上位ビット(MSB)から最下位ビット(LSB)にシーケンスされます。図1を参照すると、+A<sub>IN</sub>および-A<sub>IN</sub>入力はアクイジション・フェーズ中にサンプル&ホールド・コンデンサ(C<sub>SAMPLE</sub>)に接続され、コンパレータ・オフセットはゼロ調整スイッチによってゼロになります。このアクイジション・フェーズでは、200nsの最小遅延時間により、サンプル&ホールド・コンデンサがアナログ信号を収集するのに十分な時間を与えます。変換フェーズ中は、コンパレータのゼロ調整スイッチがオープンして、コンパレータを比較モードにします。入力スイッチはC<sub>SAMPLE</sub>コンデンサをグランドにスイッチして、アナログ入力電荷をコンパレータの加算点に送ります。この入力電荷は、微分容量性DACから供給されるバイナリ・ウェイト電荷と逐次比較されます。ビットの決定は高速コンパレータで行われます。変換が終わると、差動DAC出力は+ A<sub>IN</sub>および-A<sub>IN</sub>入力電荷とバランスします。+ A<sub>IN</sub>と-A<sub>IN</sub>の差を表すSAR成分(14ビット・データ・ワード)が14ビット出力ラッチにロードされます。

## ダイナミック特性

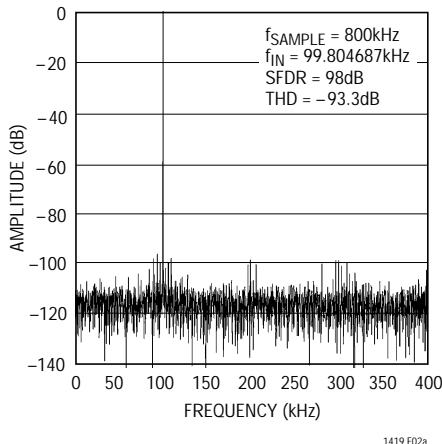

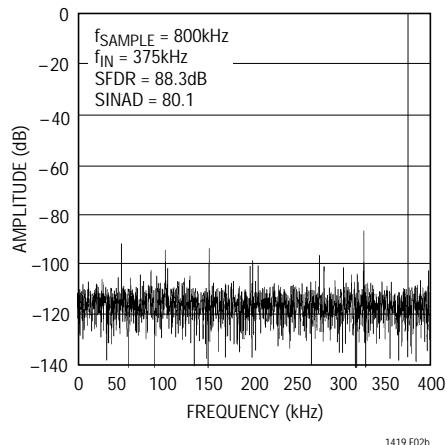

LTC1419は、非常に高速なサンプリング能力を備えています。FFT(高速フーリエ変換)テスト手法を使用して、定格スループットでのADCの周波数応答、歪み、およびノイズ特性をテストしています。低歪み正弦波を加え、FFTアルゴリズムを用いてデジタル出力を分析することにより、基本成分外の周波数に対するADCのスペ

## アプリケーション情報

クトル成分を調べることができます。図2に標準的なLTC1419のFFTプロットを示します。

図2a. LTC1419の非平均化4096ポイントFFT、

入力周波数 = 100kHz

図2b. LTC1419の非平均化4096ポイントFFT、

入力周波数 = 375kHz

### SN比

SN + 歪み比[  $S(N + D)$  ]は、A/D出力における基本入力周波数のRMS振幅と他のすべての周波数成分のRMS振幅との比率です。出力はDCからサンプリング周波数の1/2の周波数帯域に限定されます。図2に800kHzのサンプリング・レートと100kHz入力での標準スペクトル成分を示します。ダイナミック特性は入力周波数が400kHz以上のナイキスト限界まで良好です。

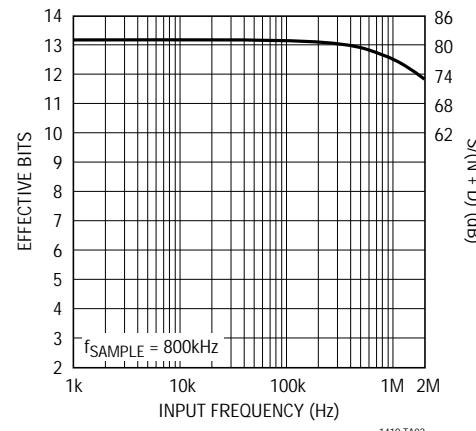

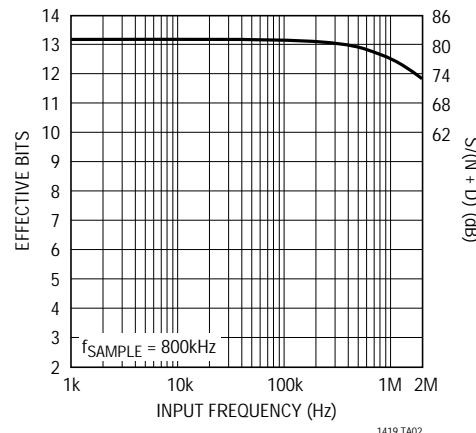

### 有効ビット数

有効ビット数( ENOB )はADCの分解能の尺度であり、次式のとおり  $S(N + D)$  に直接関係します。

$$N = [S(N + D) - 1.76]/6.02$$

ここで、Nは分解能の有効ビット数であり、  $S(N + D)$  はdBで表されます。800kHzの最大サンプリング・レートで、LTC1419は400kHzのナイキスト入力周波数まで、非常に良好なENOBを維持します( 図3を参照 )。

6

図3. 有効ビットおよび  $S(N + D)$  と入力周波数

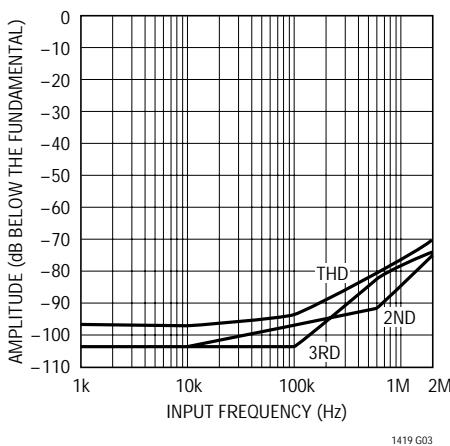

### 全高調波歪み

全高調波歪み( THD )は、入力信号のすべての高調波のRMSの合計と基本波との比率です。帯域外高調波は、DCとサンプリング周波数の1/2の周波数帯域に限定されます。THDは次式で表されます。

$$THD = 20 \log \frac{\sqrt{V2^2 + V3^2 + V4^2 + \dots + Vn^2}}{V1}$$

ここで、V1は基本周波数のRMS振幅であり、V2からVnは第2高調波から第N高調波の振幅です。THDと入力周波数の関係を図4に示します。LTC1419は、ナイキストおよびそれを超える周波数まで良好な歪み特性を有しています。

## アプリケーション情報

図4. 歪みと入力周波数

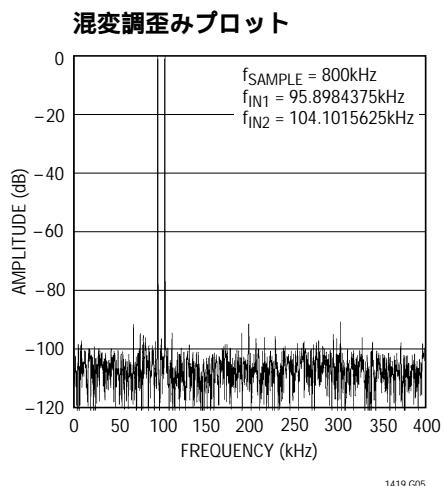

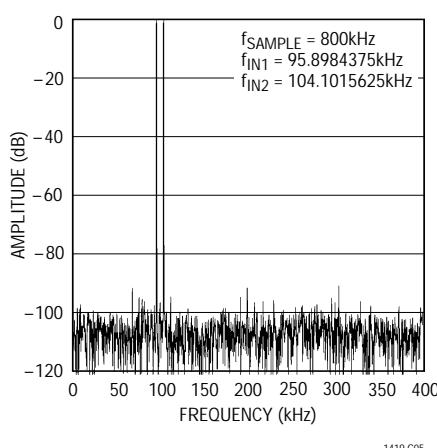

## 混変調歪み

ADC入力信号が2つ以上のスペクトル成分からなるときには、ADC伝達関数の非直線性によって、THDに加えて混変調( IMD )が発生する可能性があります。IMDは別なる異なる周波数の正弦波入力が現れたときに、ある正弦波入力に起こる変化です。

ADC入力に  $f_a$  と  $f_b$  の2つの周波数の純粋な正弦波が供給されると、ADC伝達関数の非直線性によって、和および差の周波数  $mf_a \pm nf_b$  に歪み成分が形成されます。ただし、 $m$  および  $n = 0, 1, 2, 3, \dots$  です。たとえば、2次 IMDの項は  $(f_a + f_b)$  と  $(f_a - f_b)$  です。2つの入力正弦波の

図5. 混変調歪みプロット

振幅が等しい場合、2次IMD積の値( dB )は次式で表すことができます。

$$\text{IMD}(f_a \pm f_b) = 20 \log \frac{(f_a \pm f_b) \text{での振幅}}{f_a \text{での振幅}}$$

## 最大高調波またはスプリアス・ノイズ

最大高調波つまり最大スプリアス・ノイズは、入力信号とDCを除く最大スペクトル成分です。この値はフルスケール入力信号のRMS値に対するdBで表されます。

## フルパワーおよび最大直線帯域幅

フルパワー帯域幅はフルスケール入力信号を供給したときに、再生される基本成分の振幅が3dBだけ低下する入力周波数です。

最大直線帯域幅は、 $S(N + D)$  が 77dB( 有効ビット 12.5 ビット )に低下する入力周波数です。LTC1419は入力帯域幅が最大になるように設計されており、ADCは入力信号をコンバータのナイキスト周波数より高い周波数でアンダーサンプルすることができます。ノイズ・フロアは高周波数でも非常に低く、ナイキスト周波数よりはるかに高い周波数では、 $S(N + D)$  では歪みが大きな部分を占めます。

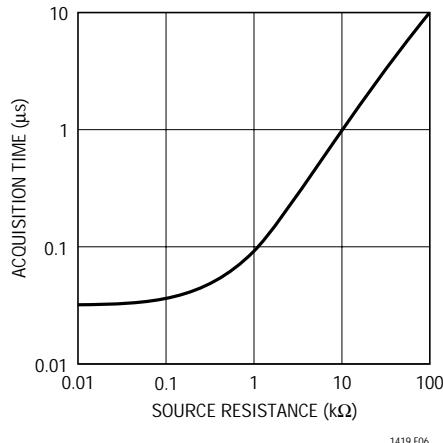

## アナログ入力のドライブ

LTC1419の差動アナログ入力は簡単にドライブできます。入力は差動、あるいはシングルエンド入力として( すなわち、 $-A_{IN}$  入力を接地 )ドライブ可能です。 $+A_{IN}$  入力と  $-A_{IN}$  入力は同時にサンプリングされます。両方の入力に同相となる不要な信号は、サンプル&ホールド回路の同相除去比によって低減されます。入力電流は、変換終了時にサンプル&ホールド・コンデンサを充電する間に1つだけ小さな電流スパイクを生じます。変換中、アナログ入力にはわずかなリーキ電流しか流れません。ドライブ回路のソース・インピーダンスが低い場合は、LTC1419入力を直接ドライブすることができます。ソース・インピーダンスが増加すると、アクイジション・タイムも増加します( 図6参照 )。ソース・インピーダンスが高いときに、アクイジション・タイムを最小にするには、バッファ・アンプを使用します。必要な条件は、アナログ入力をドライブするアンプが、小さな電流スパイクが発生した後、次の変換が

## アプリケーション情報

開始する前に安定しなければならないことだけです(最大スループット・レートを得るには、セトリング時間が200nsであること)。

図6.  $t_{ACQ}$  とソース抵抗

### 入力アンプの選択

いくつかの要求条件を考慮に入れれば、入力アンプは簡単に選択できます。まず、サンプリング・コンデンサを充電する際にアンプで発生する電圧スパイクの振幅を制限するために、閉ループ帯域幅周波数で低い出力インピーダンス(100 以下)をもつアンプを選択します。たとえば、+1の利得と50MHzのユニティゲイン帯域幅をもつアンプを使用した場合、50MHzでの出力インピーダンスは、100 以下でなければなりません。もう1つの要求条件は、最大スループット・レートを得るために十分な小信号セトリング時間を保証するには、閉ループ帯域幅が20MHz以上でなければならないことです。低速オペアンプを使用する場合、変換と変換の間の時間を長くすれば、セトリングのための時間を長くとることができます。

LTC1419をドライブするための最適なオペアンプの選択は、アプリケーションに依存します。一般に、アプリケーションは次の2つに分類されます。ダイナミック仕様が最も重要なACアプリケーションと、DC精度とセトリング・タイムが最も重要なタイム・ドメイン・アプリケーションです。以下のリストはLTC1419をドライブするのに適したオペアンプをまとめたものです。より詳細な情報は、リニアテクノロジーのデータブック、LinearView™ CD-ROM、およびウェブ・サイトwww.linear-tech.comで入手できます。

LinearViewはリニアテクノロジー社の商標です。

LT®1220: 30MHzユニティゲイン帯域幅電圧帰還アンプ。±5V ~ ±15V電源。優れたDC仕様。

LT1223: 100MHzビデオ電流帰還アンプ。±5V ~ ±15V電源、6mAの電源電流。400kHz以上の周波数で低歪み。低ノイズ。ACアプリケーションに最適。

LT1227: 140MHzビデオ電流帰還アンプ。±5V ~ ±15V電源、消費電流10mA。400kHz以上の周波数で歪みが最小。低ノイズ。ACアプリケーションに最適。

LT1229/LT1230: デュアル/クワッド100MHz帰還アンプ。±2V ~ ±15V電源、各アンプの消費電流6mA。低ノイズ。良好なACスペック。

LT1360: 50MHz電圧帰還アンプ。±5V ~ ±15V電源、消費電流3.8mA。良好なACおよびDCスペック。

LT1363: 70MHz、1000V/μsオペアンプ、消費電流6.3mA。良好なACおよびDCスペック。

LT1364/LT1365: デュアルおよびクワッド70MHz、1000V/μsオペアンプ。アンプ当たりの消費電流6.3mA。

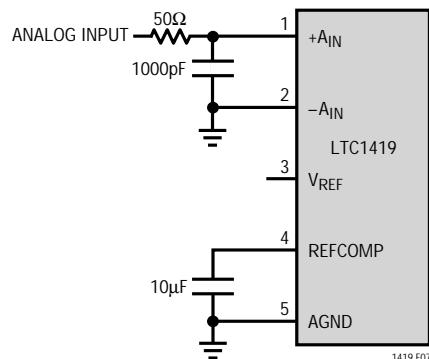

### 入力フィルタリング

入力アンプおよび他の回路のノイズと歪みがLTC1419のノイズと歪みに加えられるため、これらについても考慮しなければなりません。サンプル&ホールド回路の小信号帯域幅は20MHzです。アナログ入力に現れるノイズまたは歪み成分は、この全帯域幅に加えられます。ノイズの多い入力回路は、ノイズを低減するためにアナログ入力に送られる前にフィルタしなければなりません。多くのアプリケーションで、単純な1ポールRCフィルタで十分です。たとえば、図7は+  $A_{IN}$ からグランドに1000pFコンデンサと100  $\Omega$  のソース抵抗を接続すると、入力帯域幅が1.6MHzに制限されることを示します。また、

図7. RC入力フィルタ

## アプリケーション情報

1000pFコンデンサは入力サンプル&ホールドのための電荷貯蔵庫として働き、ADC入力をグリッチの影響を受けやすいサンプリング回路から切り離します。コンデンサと抵抗は歪みを増大させる可能性があるため、これらの部品には高品質なものを使用しなければなりません。NPOとシルバ・マイカ型誘電体コンデンサは優れた直線性を備えています。また、カーボン表面実装抵抗は、自己加熱や半田付け中に生じる損傷から歪みを生じることがあります。金属皮膜表面実装抵抗はこれらの問題の影響を受けにくいものです。

### 入力範囲

LTC1419の $\pm 2.5\text{V}$ 入力範囲は、ノイズと歪みが低くなるように最適化されています。大部分の高性能オペアンプもこの範囲で最適に動作するため、アナログ入力への直接結合が可能で、特殊な変換回路は必要ありません。

アプリケーションによっては、他の入力範囲が必要です。LTC1419の差動入力とリファレンス回路は、多くの場合、回路をほとんどあるいはまったく追加しなくても、他の入力範囲に対応できます。以下の項ではリファレンスおよび入力回路と、それらが入力レンジに与える影響について述べます。

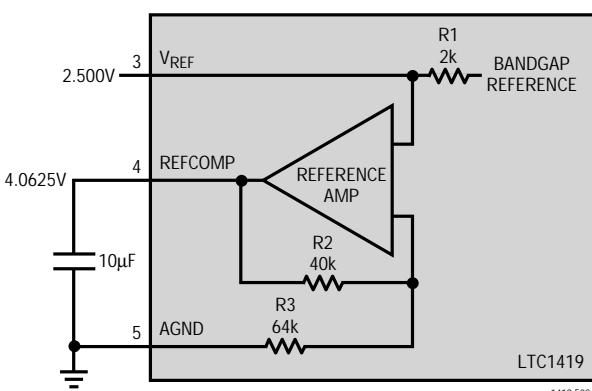

### 内部リファレンス

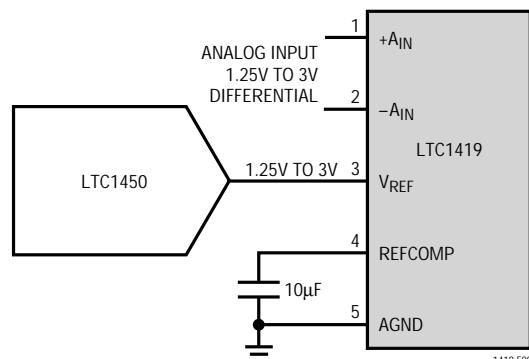

LTC1419は、温度補償および曲線補正されたバンドギャップ・リファレンスを内蔵しており、このリファレンスは製造時に $2.500\text{V}$ に調整されています。このリファレンスは内部でリファレンス・アンプに接続され、 $V_{\text{REF}}$ (ピン3)から外部に引き出されています。図8aを参照してください。 $2\text{k}\Omega$ の抵抗が出力と直列に接続されているため、外部リファ

図8a. LTC1419リファレンス回路

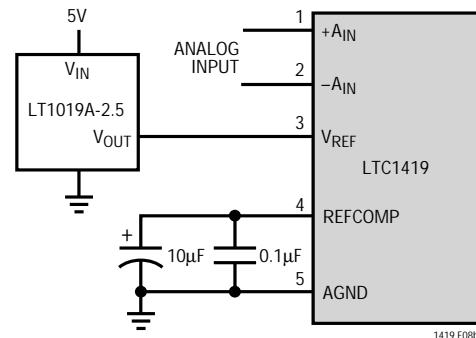

図8b. LT1019-2.5を外部リファレンスとして使用

レンスまたは他の回路で簡単にオーバードライブできます。図8bを参照してください。リファレンス・アンプは、 $V_{\text{REF}}$ ピンの電圧を1.625倍に昇圧して、必要な内部リファレンス電圧を生成します。これによって、 $V_{\text{REF}}$ ピンと高速容量性DAC間にバッファリングを提供します。リファレンス・バッファ補償ピン(REFCOMP、ピン4)は、コンデンサでグランドにバイパスしなければなりません。リファレンス・アンプは $1\mu\text{F}$ 以上のコンデンサで安定動作します。最高のノイズ性能を得るために、 $10\mu\text{F}$ のセラミック・コンデンサか $10\mu\text{F}$ のタンタル・コンデンサと並列に $0.1\mu\text{F}$ のセラミック・コンデンサを接続することを推奨しています。

$V_{\text{REF}}$ ピンは、図9に示すとおり、DACまたは他の方法でドライブすることができます。これはピーク入力信号振幅が変動する可能性があるアプリケーションに役立ちます。ADCの入力スパンを調整してピーク入力信号に一致させ、SN比を最大限に高めることができます。内部LTC1419リファレンス・アンプのフィルタリングにより、この回路の帯域幅とセトリング・タイムが制限されます。リファレンス調整の後、5msのセトリング・タイムを設ける必要があります。

図9. DACによる $V_{\text{REF}}$ のドライブ

## アプリケーション情報

### 差動入力

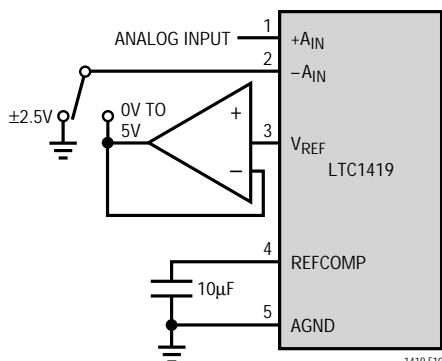

LTC1419はユニークな差動サンプル&ホールド回路を備え、レール・トゥ・レール入力が可能です。ADCは同相電圧に関係なく、常に  $+A_{IN} - (-A_{IN})$  の差を変換します(図11aを参照)。同相除去は、非常に高い周波数まで有効です。図10aを参照してください。唯一の要求条件は、両方の入力が  $A_{VDD}$  または  $A_{VSS}$  電源電圧を超えてはならないことです。積分非直線性誤差( INL )と微分直線性誤差( DNL )は、同相電圧とは無関係ですが、バイポーラ・ゼロ誤差( BZE )は変動します。BZEの変化は、標準で同相電圧の0.1%未満です。また、ダイナミック性能も同相電圧によって影響を受けます。入力がいずれかの電源レールに近付くと、THDは同相0Vでの86dBから同相2.5Vまたは-2.5Vでの76dBに低下します。

図10a. CMRRと入力周波数

図10b. 0V ~ 5Vまたは±2.5Vの入力範囲を選択可能

差動入力は、異なる入力範囲を受け入れることができます柔軟性が高くなっています。図10bは信号経路以外に1個のバッファを追加するだけで、0V ~ 5Vのアナログ入力信号を変換する回路を示します。

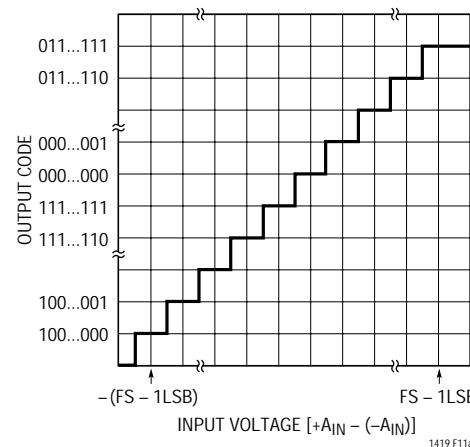

### フルスケールおよびオフセットの調整

図11aにLTC1419の理想的な入出力特性を示します。コード遷移は、連続する整数のLSB値の間の中間( すなわち、- FS + 0.5LSB、- FS + 1.5LSB、- FS + 2.5LSB、...FS - 1.5LSB、FS - 0.5LSB )に現れます。出力コードは、 $1LSB = FS - (-FS) / 16384 = 5V / 16384 = 305.2\mu V$  の2の補数バイナリです。

絶対精度が重要なアプリケーションの場合、オフセットとフルスケール誤差をゼロに調整できます。フルスケール誤差を調整する前に、オフセット誤差を調整しなければなりません。図11bにフルスケール誤差の調整に必要な追加部品を示します。ゼロ・オフセットは、 $-A_{IN}$ 入力に印加されるオ

図11a. LTC1419伝達特性

図11b. オフセットおよびフルスケール調整回路

## アプリケーション情報

フセッタを調整して達成されます。オフセッタ誤差をゼロにするには、 $-152\mu\text{V}$  ( すなわち  $-0.5\text{LSB}$  )を  $+A_{\text{IN}}$ に印加し、出力コードが0000 0000 0000 00と1111 1111 1111 11の間で変化するまで、 $-A_{\text{IN}}$ 入力のオフセッタ調整します。フルスケール調整を行うには、 $2.499544\text{V}$  ( FS/2 - 1.5LSB )の入力電圧を  $+A_{\text{IN}}$ に印加し、出力コードが0111 1111 1111 10と0111 1111 1111 11の間で変化するまでR2を調整します。

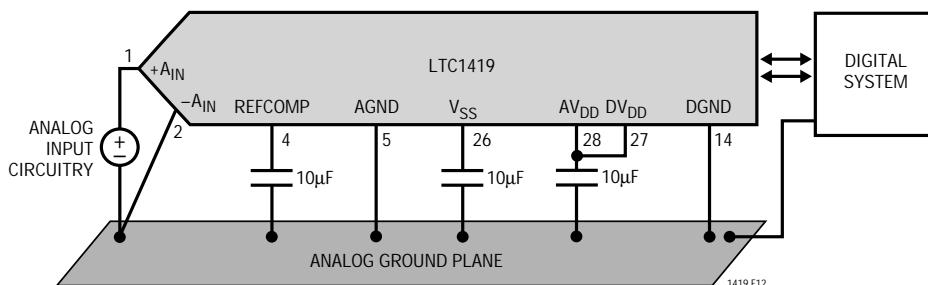

### ボード・レイアウトと接地

高分解能または高速A/Dコンバータには、ワイヤラップ・ボードは使用しないでください。LTC1419から最も適な性能を引き出すには、グランド・プレーン付きのPCボードが必要です。レイアウトでは、デジタルおよびアナログ信号ラインができるだけ離れてていなければなりません。特にADCの下やアナログ信号トラックに沿ってデジタル・トラックを走らせないよう注意してください。アナログ入力はAGNDで遮蔽しなければなりません。

ロジックのシステム・グランドから離したアナログ・グランド・プレーンを、ADCの下またはADCの近くに設けなければなりません。ピン5 ( AGND )、ピン14、およびピン19 ( ADCのDGND )他のすべてのアナログ・グランドは、この1つのアナログ・グランド・ポイントに接続してください。また、REFCOMPバイパス・コンデンサとDV<sub>DD</sub>バイパス・コンデンサもこのアナログ・グランド・プレーンに接続します。他のデジタル・グランドをこのアナログ・グランド・プレーンに接続してはなりません。このADCを低ノイズで動作させるのに、低インピーダンスのアナログおよびデジタル電源のコモン・リターンが不可欠です。また、これらのトラックのフォイル幅はできる限り広くなければなりません。ADCのデータ出力と制御信号が常時アクティブであるマイクロプロセッサ・バスに接続されるアプリケーションでは、変換結果に誤差が生じことがあります。これらの誤差は、マイクロプロセッサから逐次比

較コンパレータへのフィードスルーによるものです。この問題は、変換中にマイクロプロセッサをウェイト・ステートにするか、またはスリーステート・バッファを使ってADCのデータ・バスを分離すれば解決できます。ピンとバイパス・コンデンサを接続するトレースは、できる限り短く、また幅を広くとってください。

LTC1419はノイズの結合を最小限に抑えるために差動入力を備えています。 $+A_{\text{IN}}$ と $-A_{\text{IN}}$ リードの同相ノイズは入力CMRRによって除去されます。 $-A_{\text{IN}}$ 入力を $+A_{\text{IN}}$ 入力のグランド・センスとして使用することができます。LTC1419は $+A_{\text{IN}}$ と $-A_{\text{IN}}$ 間の電圧差を保持し変換します。 $+A_{\text{IN}}$  ( ピン1 )と $-A_{\text{IN}}$  ( ピン2 )へのリードは、できる限り短くしなければなりません。これが可能でないアプリケーションでは、 $+A_{\text{IN}}$ および $-A_{\text{IN}}$ トレースを平行して走らせて、結合を等しくしなければなりません。

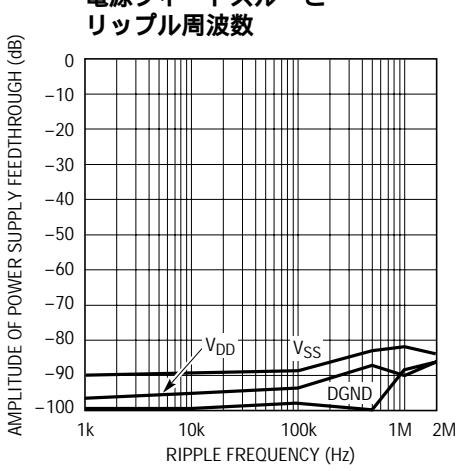

### 電源のバイパス

V<sub>DD</sub>ピンとREFCOMPピンには、本データシートの最初のページにある標準的応用例に示すように、高品質で低直列抵抗のセラミックの $10\mu\text{F}$ バイパス・コンデンサを使用してください。村田製作所製GRM235Y5V106Z016などの表面実装セラミック・コンデンサは、小さなボード・スペースで優れたバイパスを提供します。あるいは、 $10\mu\text{F}$ タンタル・コンデンサと $0.1\mu\text{F}$ セラミック・コンデンサを並列に接続して使用することもできます。これらのコンデンサはできる限りピンの近くに配置します。ピンとバイパス・コンデンサを接続するトレースは、できる限り短く、また幅を広くとってください。

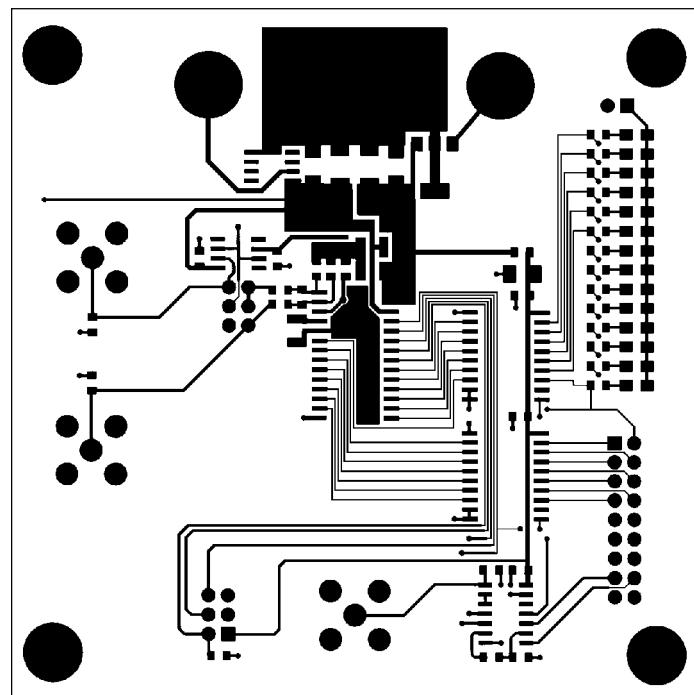

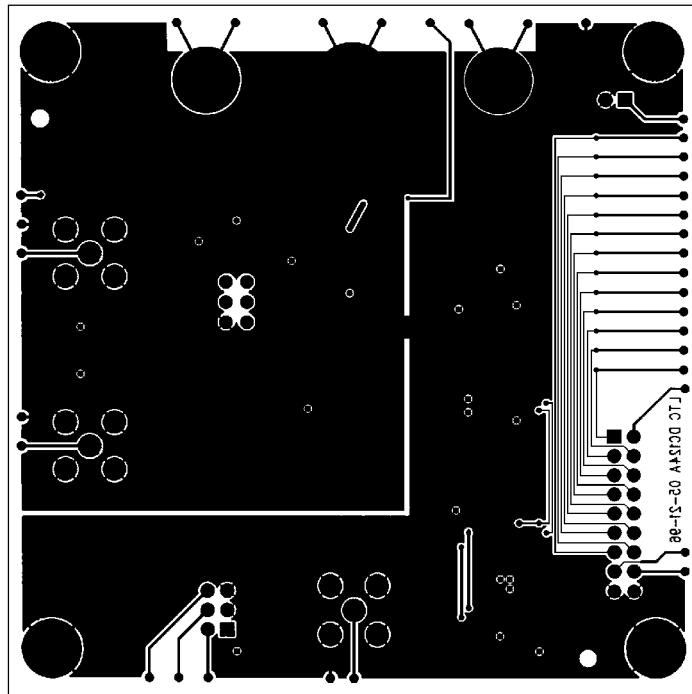

### レイアウト例

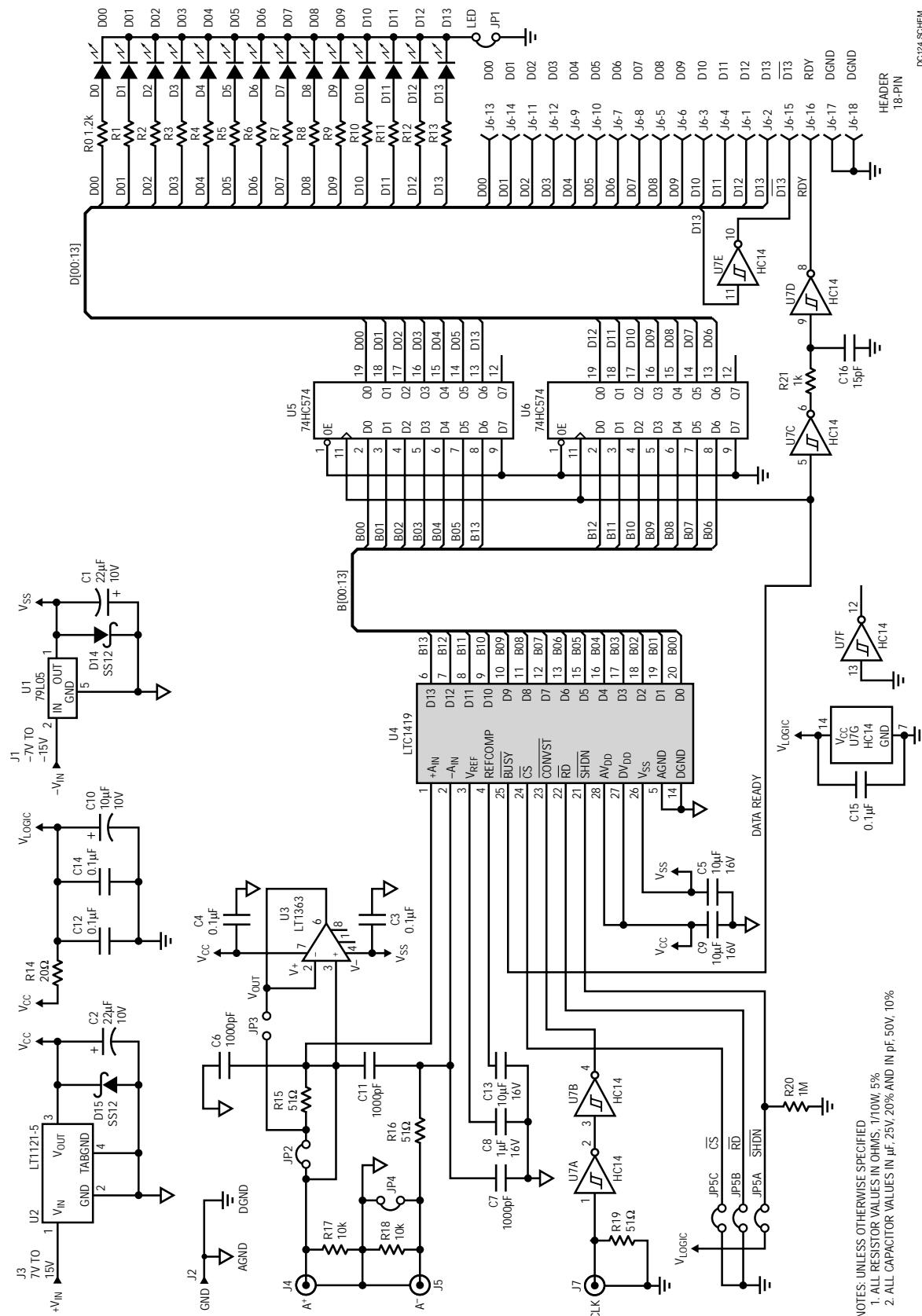

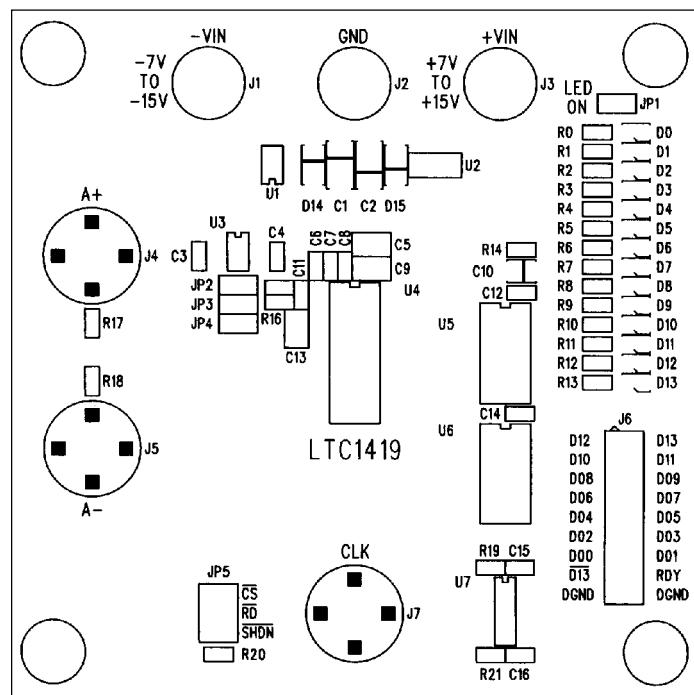

図13a、13b、13c、13dは、推奨評価ボードの回路図とレイアウトを示します。レイアウトは、2層PCボードでのデカップリング・コンデンサとグランド・プレーンの正しい使い方を示しています。

図12. 電源グランドの実際

## アプリケーション情報

図13a. 推奨評価回路

アプリケーション情報

図13b. 推奨評価回路ボード部品面のシルクスクリーン

図13c. 推奨評価回路ボード部品面のレイアウト

## アプリケーション情報

図13d. 推奨評価回路ボード半田面のレイアウト

### デジタル・インターフェース

このA/Dコンバータは、メモリ・マップド・デバイスとしてマイクロプロセッサにインターフェースするように設計されています。CSおよびRDコントロール入力は、すべての周辺メモリ・インターフェースに共通です。別々のCONVSTを使用して、変換を開始します。

### 内部クロック

このA/Dコンバータには内部クロックがあり、他のADCのように外部クロックとCSおよびRD信号間で同期をとる必要はありません。内部クロックは標準変換時間0.95μs、および全動作温度範囲における最大変換時間1.15μsを達成するよう製造時に調整されています。外部調整は不要です。保証最大アクイジション・タイムは300nsです。加えて、1.25μsのスループット時間と800kspsの最小サンプリング・レートが保証されます。

### 電源シャットダウン

LTC1419にはナップとスリープの2つのパワー・シャットダウン・モードがあり、非アクティブ期間中の電力を節減します。ナップ・モードでは消費電力が95%低減され、デジタル・ロジックとリファレンスだけが動作状態になり

ます。ナップからアクティブになるまでのウェイクアップ時間は200nsです。スリープ・モードでは、リファレンスがシャットダウンされ、リーク電流は約250μAのままであります。スリープ・モードからのウェイクアップ時間は、リファレンス回路が立ち上がった後に、完全14ビット精度では0.005%にセトリングしなければならないため、より低速になります。スリープ・モードのウェイクアップ時間は、REFCOMP(ピン4)に接続されたコンデンサの値によって決まります。ウェイクアップ時間は推奨される10μFコンデンサでは10msです。シャットダウンはピン21(SHDN)で制御され、SHDNが“L”的ときにADCはシャットダウン状態になっています。シャットダウン・モードはピン20(CS)で選択され、“L”的ときナップを選択します。

図14a. CSからSHDNのタイミング

## アプリケーション情報

図14b.  $\overline{\text{SHDN}}$ から $\overline{\text{CONVST}}$ のウェイクアップ・タイミング

## タイミングとコントロール

変換スタートおよびデータ読み込み動作は、 $\overline{\text{CONVST}}$ 、 $\overline{\text{CS}}$ 、および $\overline{\text{RD}}$ の3つのデジタル入力でコントロールされます。 $\overline{\text{CONVST}}$ ピンにロジック“0”を印加すると、ADCが選択された後(すなわち、 $\overline{\text{CS}}$ が“L”)変換を開始します。一度変換を開始すると、変換が完了するまで再スタートすることはできません。コンバータのステータスは $\overline{\text{BUSY}}$ 出力で表示され、変換実行中この出力は“L”になっています。

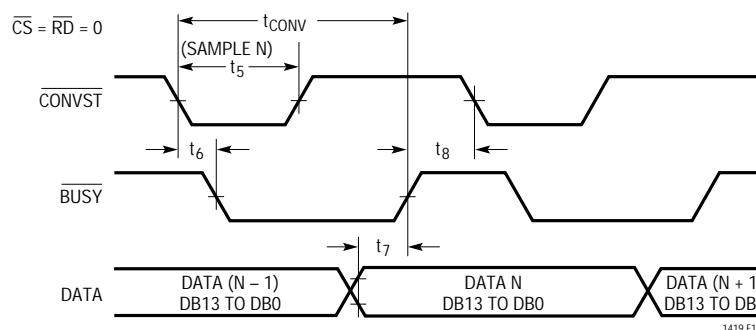

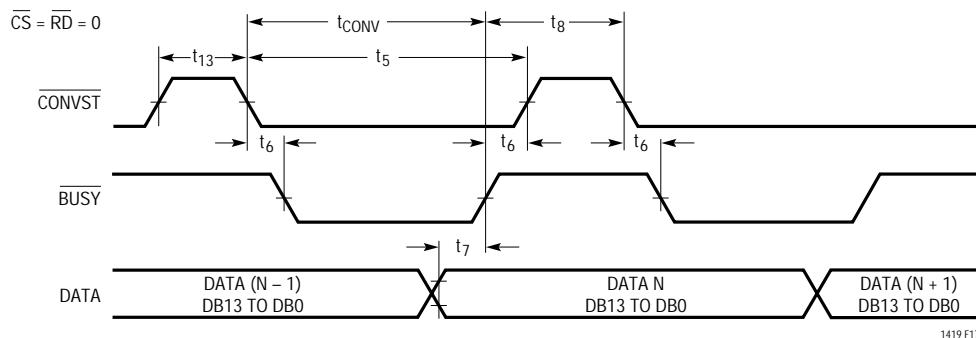

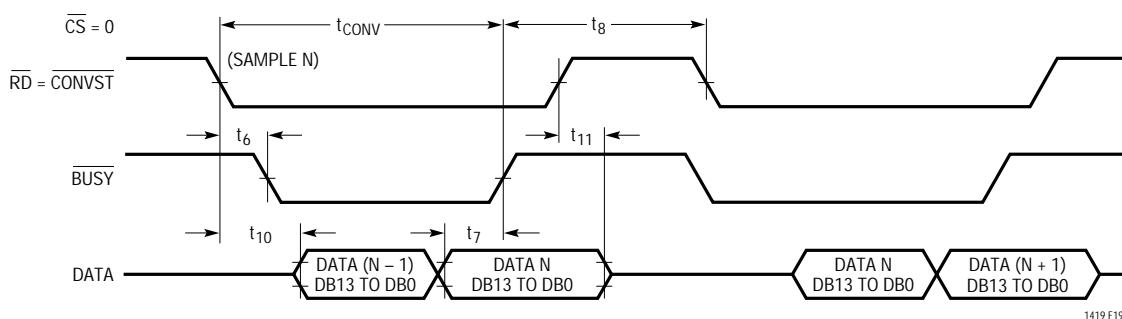

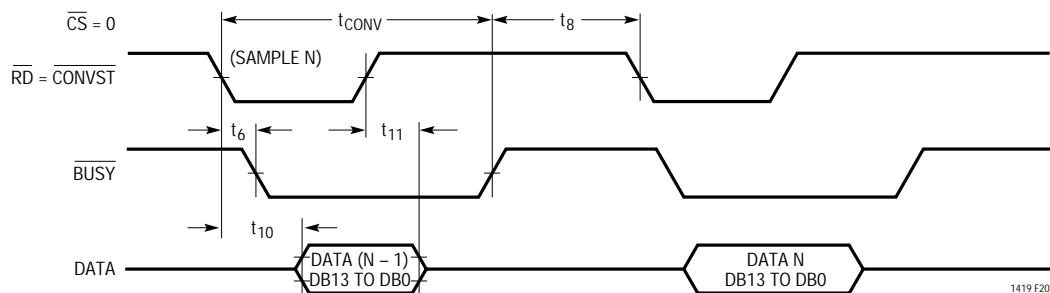

図16～図20に、いくつかの異なる動作モードを示します。モード1aと1b(図16と図17)では、 $\overline{\text{CS}}$ と $\overline{\text{RD}}$ は両方とも“L”に接続されます。 $\overline{\text{CONVST}}$ の立下りエッジで変換を開始します。データ出力は常にイネーブルされ、データは $\overline{\text{BUSY}}$ の立上りエッジでラッチすることができます。モード1aは、幅の狭いロジック“L”的 $\overline{\text{CONVST}}$ パルスによる動作を示します。モード1bは、幅の狭いロジック“H”的 $\overline{\text{CONVST}}$ パルスによる動作を示します。

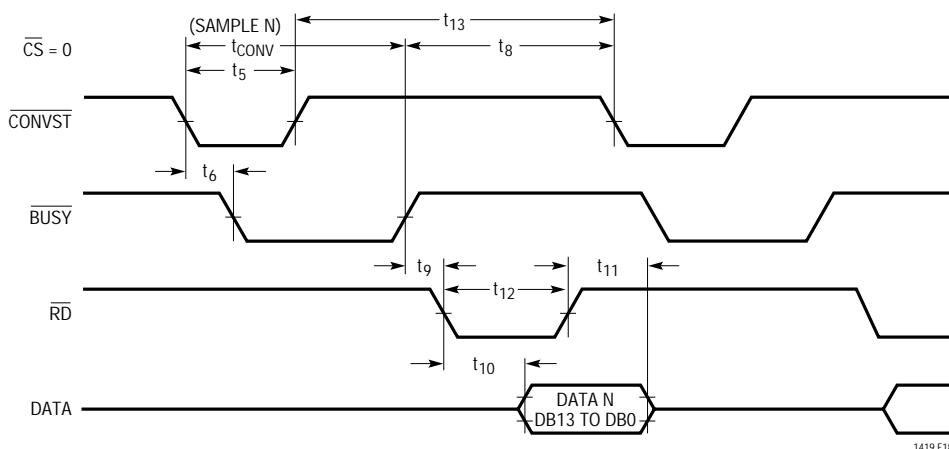

モード2(図18)では、 $\overline{\text{CS}}$ は“L”に接続されます。 $\overline{\text{CONVST}}$ 信号の立下りエッジで再び変換を開始します。データ出力は、MPUが $\overline{\text{RD}}$ 信号で読み出すまでスリーステートになっています。モード2は、共有MPUデータ・バスでの動作に使用できます。

図16. モード1a。 $\overline{\text{CONVST}}$ による変換の開始。データ出力は常時イネーブル

( $\overline{\text{CONVST}} = \text{[ } \text{ ] }$ )

低速メモリ・モードおよびROMモード(図19と図20)では、 $\overline{\text{CS}}$ は“L”に接続され、 $\overline{\text{CONVST}}$ と $\overline{\text{RD}}$ は連結されます。MPUは変換を開始して、 $\overline{\text{RD}}$ 信号で出力を読み出します。変換はMPUまたはDSP(外部サンプル・クロックではなく)によって開始されます。

低速メモリ・モードでは、プロセッサは $\overline{\text{RD}} = \overline{\text{CONVST}}$ にロジック“L”を印加します。 $\overline{\text{BUSY}}$ が“L”になり、プロセッサを強制的にウェイト・ステートにします。前の変換結果がデータ出力に現れます。変換が完了すると、新しい変換結果がデータ出力に現れます。 $\overline{\text{BUSY}}$ が“H”になって、プロセッサを解放すると、プロセッサは $\overline{\text{RD}} = \overline{\text{CONVST}}$ を“H”に戻して、新しい変換データを読み出します。

ROMモードでは、プロセッサは $\overline{\text{RD}} = \overline{\text{CONVST}}$ を“L”にして変換を開始し、前の変換結果を読み出します。変換が完了すると、プロセッサは新しい結果を読み出して、別の変換を開始することができます。

図15.  $\overline{\text{CS}}$ から $\overline{\text{CONVST}}$ のセットアップ・タイミング

## アプリケーション情報

図17. モード1b。CONVSTによる変換の開始。データ出力は常時イネーブル

(CONVST=□□□□)

6

図18. モード2。CONVSTによる変換の開始。RDでデータの読み出し。

図19. 低速メモリ・モード・タイミング

## アプリケーション情報

図20. ROMモード・タイミング

## 関連製品

| PART NUMBER | DESCRIPTION                                 | COMMENTS                                                               |

|-------------|---------------------------------------------|------------------------------------------------------------------------|

| LTC1278/79  | Single Supply, 500ksps/600ksps ADCs         | Low Power, 5V or $\pm 5V$ Supply                                       |

| LTC1400     | High Speed, Serial 12-Bit ADC               | 400ksps, Complete with Internal Reference, SO-8 Package                |

| LTC1409     | Low Power, 12-Bit, 800ksps Sampling ADC     | Best Dynamic Performance, $f_{SAMPLE} \leq 800$ ksps, 80mW Dissipation |

| LTC1410     | 12-Bit, 1.25Msps Sampling ADC with Shutdown | Best Dynamic Performance, THD = 84dB and SINAD = 71dB at Nyquist       |

| LTC1415     | Single 5V, 12-Bit 1.25Msps ADC              | Single Supply, 55mW Dissipation                                        |

| LTC1605     | Single 5V, 16-Bit 100ksps ADC               | Low Power, $\pm 10V$ Inputs                                            |