## 特長

- 変換レート: 2.8Msps

- 低消費電力: 14mW

- 3Vの単一電源動作

- 2.5Vの内部バンドギャップ・リファレンスをオーバードライブ可能

- 3線シリアル・インターフェイス

- スリープ( $10\mu\text{W}$ )シャットダウン・モード

- ナップ(3mW)シャットダウン・モード

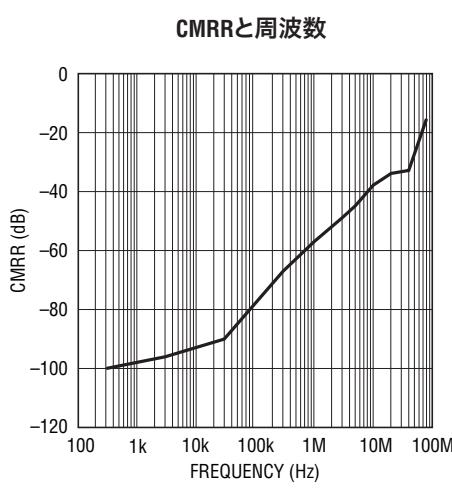

- 同相除去比: 80dB

- バイポーラ入力範囲:  $\pm 1.25\text{V}$

- 小型10ピンMSEパッケージ

## アプリケーション

- 通信

- データ収集システム

- 無停電電源

- マルチフェーズ・モータ制御

- マルチプレクス・データ収集

## 概要

LTC<sup>®</sup>1403-1/LTC1403A-1は、差動入力を備えた12ビット/14ビット、2.8MspsシリアルA/Dコンバータです。これらのデバイスは3Vの単一電源で動作し、消費電流はわずか4.7mAで、小型10ピンMSEパッケージで供給されます。スリープ・シャットダウン時には、消費電力が $10\mu\text{W}$ まで低減されます。高速動作と低消費電力を小型パッケージで実現するLTC1403-1/LTC1403A-1は、高速の携帯アプリケーションに適しています。

同相除去比が80dBなので、ソースから差動で信号を測定することによってグランド・ループと同相ノイズを除去できます。

これらのデバイスは $-1.25\text{V} \sim 1.25\text{V}$ のバイポーラ入力を差動変換します。 $A_{IN^+}$ と $A_{IN^-}$ の絶対電圧振幅は、グランドから電源電圧までです。

シリアル・インターフェイスによってCONV入力信号の立ち上がり後16サイクルの間、変換結果を送出するので、標準シリアル・インターフェイスと互換性があります。無変換時にデータストリームの後に収集時間として2クロック・サイクルを追加可能な場合、50.4MHzクロックで2.8Mspsのフル・サンプル・レートを達成できます。

、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標で、SoftSpanはリニアテクノロジー社の商標です。他のすべての商標はそれぞれの所有者に所有権があります。

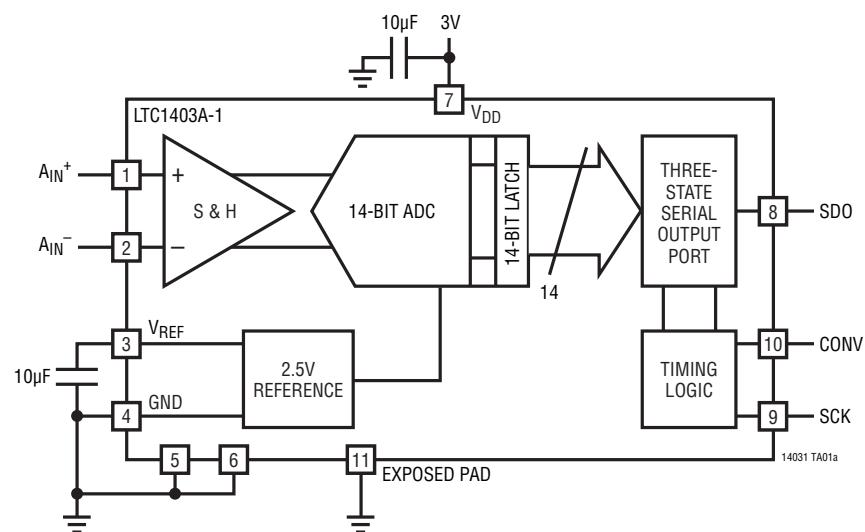

## ブロック図

14031 TA01b

# LTC1403-1/LTC1403A-1

## 絶対最大定格

(Note 1,2)

|                        |                             |

|------------------------|-----------------------------|

| 電源電圧 ( $V_{DD}$ )      | 4V                          |

| アナログ入力電圧 (Note 3)      | -0.3V ~ ( $V_{DD} + 0.3V$ ) |

| デジタル入力電圧               | -0.3V ~ ( $V_{DD} + 0.3V$ ) |

| デジタル出力電圧               | -0.3V ~ ( $V_{DD} + 0.3V$ ) |

| 消費電力                   | 100mW                       |

| 動作温度範囲                 |                             |

| LTC1403C-1/LTC1403AC-1 | 0°C ~ 70°C                  |

| LTC1403I-1/LTC1403AI-1 | -40°C ~ 85°C                |

| 保存温度範囲                 | -65°C ~ 150°C               |

| リード温度(半田付け、10秒)        | 300°C                       |

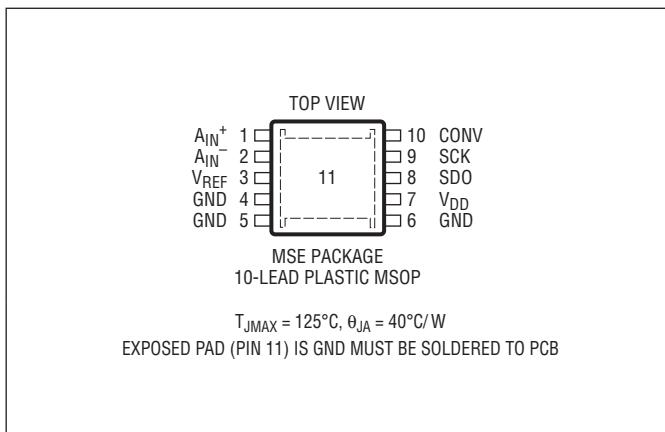

## ピン配置

## 発注情報

| 鉛フリー仕様             | テープアンドリール            | 製品マーキング | パッケージ                | 温度範囲          |

|--------------------|----------------------|---------|----------------------|---------------|

| LTC1403CMSE-1#PBF  | LTC1403CMSE-1#TRPBF  | LTBGP   | 10-Lead Plastic MSOP | 0°C to 70°C   |

| LTC1403IMSE-1#PBF  | LTC1403IMSE-1#TRPBF  | LTBGQ   | 10-Lead Plastic MSOP | -40°C to 85°C |

| LTC1403ACMSE-1#PBF | LTC1403ACMSE-1#TRPBF | LTBGR   | 10-Lead Plastic MSOP | 0°C to 70°C   |

| LTC1403AIMSE-1#PBF | LTC1403AIMSE-1#TRPBF | LTBGS   | 10-Lead Plastic MSOP | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

## コンバータの特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$ での値。内部リファレンス使用時。 $V_{DD} = 3\text{V}$

| PARAMETER                     | CONDITIONS                                        | LTC1403-1 |     |           | LTC1403A-1 |     |           | UNITS            |

|-------------------------------|---------------------------------------------------|-----------|-----|-----------|------------|-----|-----------|------------------|

|                               |                                                   | MIN       | TYP | MAX       | MIN        | TYP | MAX       |                  |

| Resolution (No Missing Codes) |                                                   | ●         | 12  |           | 14         |     |           | Bits             |

| Integral Linearity Error      | (Notes 4, 5, 18)                                  | ●         | -2  | ±0.25     | 2          | -4  | ±0.5      | 4                |

| Offset Error                  | (Notes 4, 18)                                     | ●         | -10 | ±1        | 10         | -20 | ±2        | 20               |

| Gain Error                    | (Note 4, 18)                                      | ●         | -30 | ±5        | 30         | -60 | ±10       | 60               |

| Gain Tempco                   | Internal Reference (Note 4)<br>External Reference |           |     | ±15<br>±1 |            |     | ±15<br>±1 | ppm/°C<br>ppm/°C |

## アナログ入力

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$ での値。 $V_{DD} = 3\text{V}$

| SYMBOL   | PARAMETER                                               | CONDITIONS             | MIN | TYP | MAX           | UNITS |

|----------|---------------------------------------------------------|------------------------|-----|-----|---------------|-------|

| $V_{IN}$ | Analog Differential Input Range (Notes 3, 8, 9)         | 2.7V ≤ $V_{DD}$ ≤ 3.3V | ●   |     | -1.25 to 1.25 | V     |

| $V_{CM}$ | Analog Common Mode + Differential Input Range (Note 10) |                        |     |     | 0 to $V_{DD}$ | V     |

| $I_{IN}$ | Analog Input Leakage Current                            |                        | ●   |     | 1             | μA    |

| $C_{IN}$ | Analog Input Capacitance                                |                        |     |     | 13            | pF    |

14031fc

## アナログ入力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $V_{DD} = 3\text{V}$

| SYMBOL       | PARAMETER                                  | CONDITIONS                                                                                                             | MIN | TYP | MAX        | UNITS    |

|--------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----|------------|----------|

| $t_{ACQ}$    | Sample-and-Hold Acquisition Time           | (Note 6)                                                                                                               |     | ●   | 39         | ns       |

| $t_{AP}$     | Sample-and-Hold Aperture Delay Time        |                                                                                                                        |     | 1   |            | ns       |

| $t_{JITTER}$ | Sample-and-Hold Aperture Delay Time Jitter |                                                                                                                        |     | 0.3 |            | ps       |

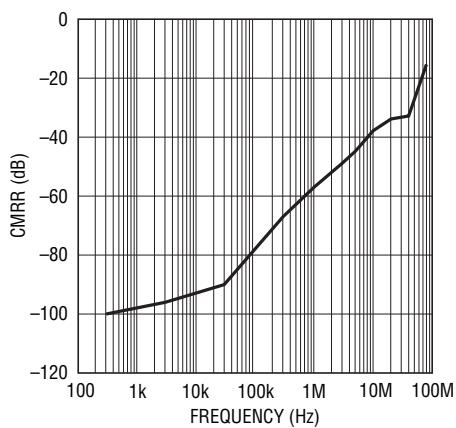

| CMRR         | Analog Input Common Mode Rejection Ratio   | $f_{IN} = 1\text{MHz}, V_{IN} = 0\text{V to } 3\text{V}$<br>$f_{IN} = 100\text{MHz}, V_{IN} = 0\text{V to } 3\text{V}$ |     |     | -60<br>-15 | dB<br>dB |

## ダイナミック精度

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $V_{DD} = 3\text{V}$ ,  $A_{IN^-} = 1.5\text{V DC}$ に固定してシングルエンドの $A_{IN^+}$ 信号でドライブ。 $V_{CM} = 1.5\text{V}$ に設定して差動信号で $A_{IN^+}$ および $A_{IN^-}$ をドライブ

| Symbol | PARAMETER                             | CONDITIONS                                                                                                                                                                                                                                                         | LTC1403-1 |                    |                      | LTC1403A-1 |              |      | UNITS              |

|--------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|----------------------|------------|--------------|------|--------------------|

|        |                                       |                                                                                                                                                                                                                                                                    | MIN       | TYP                | MAX                  | MIN        | TYP          | MAX  |                    |

| SINAD  | Signal-to-Noise Plus Distortion Ratio | 100kHz Input Signal (Note 19)<br>1.4MHz Input Signal (Note 19)<br>100kHz Input Signal, External $V_{REF} = 3.3\text{V}$ ,<br>$V_{DD} \geq 3.3\text{V}$ (Note 19)<br>750kHz Input Signal, External $V_{REF} = 3.3\text{V}$ ,<br>$V_{DD} \geq 3.3\text{V}$ (Note 19) | ●<br>68   | 70.5<br>70.5<br>72 | 73.5<br>73.5<br>76.3 | 70         | 73.5<br>76.3 | 76.3 | dB<br>dB<br>dB     |

| THD    | Total Harmonic Distortion             | 100kHz First 5 Harmonics (Note 19)<br>1.4MHz First 5 Harmonics (Note 19)                                                                                                                                                                                           | ●         | -87<br>-83         | -76                  | -90<br>-86 | -86<br>-78   | -78  | dB<br>dB           |

| SFDR   | Spurious Free Dynamic Range           | 100kHz Input Signal (Note 19)<br>1.4MHz Input Signal (Note 19)                                                                                                                                                                                                     |           | -87<br>-83         |                      | -90<br>-86 |              | -86  | dB<br>dB           |

| IMD    | Intermodulation Distortion            | 0.625V <sub>P-P</sub> 1.4MHz Summed with 0.625V <sub>P-P</sub><br>1.56MHz into $A_{IN^+}$ and Inverted into $A_{IN^-}$                                                                                                                                             |           | -82                |                      | -82        |              | -82  | dB                 |

|        | Code-to-Code Transition Noise         | $V_{REF} = 2.5\text{V}$ (Note 18)                                                                                                                                                                                                                                  |           | 0.25               |                      | 1          |              | 1    | LSB <sub>RMS</sub> |

|        | Full Power Bandwidth                  | $V_{IN} = 2.5\text{V}_P\text{-}_P$ , SDO = 11585LSB <sub>P-P</sub> (Note 15)                                                                                                                                                                                       |           | 50                 |                      | 50         |              | 50   | MHz                |

|        | Full Linear Bandwidth                 | $S/(N + D) \geq 68\text{dB}$                                                                                                                                                                                                                                       |           | 5                  |                      | 5          |              | 5    | MHz                |

## 内部リファレンスの特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $V_{DD} = 3\text{V}$

| PARAMETER                   | CONDITIONS                                                    | MIN | TYP | MAX | UNITS  |

|-----------------------------|---------------------------------------------------------------|-----|-----|-----|--------|

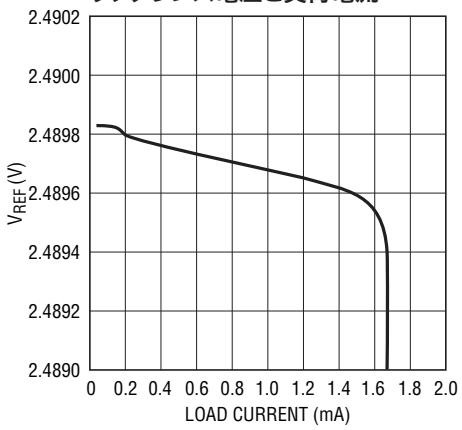

| $V_{REF}$ Output Voltage    | $I_{OUT} = 0$                                                 |     | 2.5 |     | V      |

| $V_{REF}$ Output Tempco     |                                                               |     | 15  |     | ppm/°C |

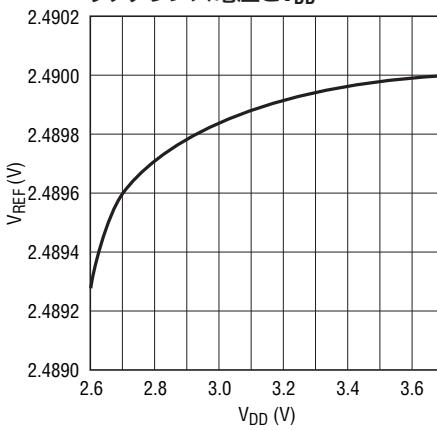

| $V_{REF}$ Line Regulation   | $V_{DD} = 2.7\text{V to } 3.6\text{V}, V_{REF} = 2.5\text{V}$ |     | 600 |     | μV/V   |

| $V_{REF}$ Output Resistance | Load Current = 0.5mA                                          |     | 0.2 |     | Ω      |

| $V_{REF}$ Settling Time     |                                                               |     | 2   |     | ms     |

# LTC1403-1/LTC1403A-1

## デジタル入力およびデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $V_{DD} = 3\text{V}$

| SYMBOL       | PARAMETER                           | CONDITIONS                                                                                               | MIN | TYP          | MAX      | UNITS         |

|--------------|-------------------------------------|----------------------------------------------------------------------------------------------------------|-----|--------------|----------|---------------|

| $V_{IH}$     | High Level Input Voltage            | $V_{DD} = 3.3\text{V}$                                                                                   | ●   | 2.4          |          | V             |

| $V_{IL}$     | Low Level Input Voltage             | $V_{DD} = 2.7\text{V}$                                                                                   | ●   |              | 0.6      | V             |

| $I_{IN}$     | Digital Input Current               | $V_{IN} = 0\text{V}$ to $V_{DD}$                                                                         | ●   |              | $\pm 10$ | $\mu\text{A}$ |

| $C_{IN}$     | Digital Input Capacitance           | (Note 20)                                                                                                |     | 5            |          | pF            |

| $V_{OH}$     | High Level Output Voltage           | $V_{DD} = 3\text{V}$ , $I_{OUT} = -200\mu\text{A}$                                                       | ●   | 2.5          | 2.9      | V             |

| $V_{OL}$     | Low Level Output Voltage            | $V_{DD} = 2.7\text{V}$ , $I_{OUT} = 160\mu\text{A}$<br>$V_{DD} = 2.7\text{V}$ , $I_{OUT} = 1.6\text{mA}$ | ●   | 0.05<br>0.10 | 0.4      | V<br>V        |

| $I_{OZ}$     | Hi-Z Output Leakage $I_{OUT}$       | $V_{OUT} = 0\text{V}$ to $V_{DD}$                                                                        | ●   |              | $\pm 10$ | $\mu\text{A}$ |

| $C_{OZ}$     | Hi-Z Output Capacitance $D_{OUT}$   |                                                                                                          |     | 1            |          | pF            |

| $I_{SOURCE}$ | Output Short-Circuit Source Current | $V_{OUT} = 0\text{V}$ , $V_{DD} = 3\text{V}$                                                             |     | 20           |          | mA            |

| $I_{SINK}$   | Output Short-Circuit Sink Current   | $V_{OUT} = V_{DD} = 3\text{V}$                                                                           |     | 15           |          | mA            |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 17)

| SYMBOL   | PARAMETER               | CONDITIONS                                                                   | MIN    | TYP                  | MAX                  | UNITS                                      |

|----------|-------------------------|------------------------------------------------------------------------------|--------|----------------------|----------------------|--------------------------------------------|

| $V_{DD}$ | Supply Voltage          |                                                                              | 2.7    | 3.6                  |                      | V                                          |

| $I_{DD}$ | Positive Supply Voltage | Active Mode<br>Nap Mode<br>Sleep Mode (LTC1403-1)<br>Sleep Mode (LTC1403A-1) | ●<br>● | 4.7<br>1.1<br>2<br>2 | 7<br>1.5<br>15<br>10 | mA<br>mA<br>$\mu\text{A}$<br>$\mu\text{A}$ |

| $P_D$    | Power Dissipation       | Active Mode with SCK in Fixed State (Hi or Lo)                               |        | 12                   |                      | mW                                         |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $V_{DD} = 3\text{V}$

| SYMBOL            | PARAMETER                                                                                  | CONDITIONS       | MIN | TYP  | MAX   | UNITS       |

|-------------------|--------------------------------------------------------------------------------------------|------------------|-----|------|-------|-------------|

| $f_{SAMPLE(MAX)}$ | Maximum Sampling Frequency per Channel (Conversion Rate)                                   |                  | ●   | 2.8  |       | MHz         |

| $t_{THROUGHPUT}$  | Minimum Sampling Period (Conversion + Acquisition Period)                                  |                  | ●   | 357  |       | ns          |

| $t_{SCK}$         | Clock Period                                                                               | (Note 16)        | ●   | 19.8 | 10000 | ns          |

| $t_{CONV}$        | Conversion Time                                                                            | (Note 6)         |     | 16   | 18    | SCLK cycles |

| $t_1$             | Minimum Positive or Negative SCLK Pulse Width                                              | (Note 6)         |     | 2    |       | ns          |

| $t_2$             | CONV to SCK Setup Time                                                                     | (Notes 6, 10)    |     | 3    |       | ns          |

| $t_3$             | Nearest SCK Edge Before CONV                                                               | (Note 6)         |     | 0    |       | ns          |

| $t_4$             | Minimum Positive or Negative CONV Pulse Width                                              | (Note 6)         |     | 4    |       | ns          |

| $t_5$             | SCK to Sample Mode                                                                         | (Note 6)         |     | 4    |       | ns          |

| $t_6$             | CONV to Hold Mode                                                                          | (Notes 6, 11)    |     | 1.2  |       | ns          |

| $t_7$             | 16th $\text{SCK}^\uparrow$ to $\text{CONV}^\uparrow$ Interval (Affects Acquisition Period) | (Notes 6, 7, 13) |     | 45   |       | ns          |

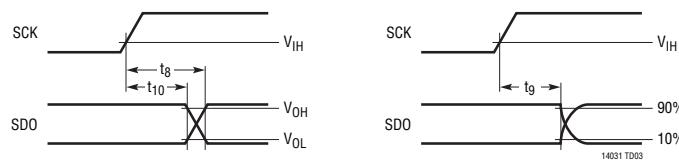

| $t_8$             | Minimum Delay from SCK to Valid Data                                                       | (Notes 6, 12)    |     | 8    |       | ns          |

| $t_9$             | SCK to Hi-Z at SDO                                                                         | (Notes 6, 12)    |     | 6    |       | ns          |

| $t_{10}$          | Previous SDO Bit Remains Valid After SCK                                                   | (Notes 6, 12)    |     | 2    |       | ns          |

| $t_{12}$          | $V_{REF}$ Settling Time After Sleep-to-Wake Transition                                     | (Notes 6, 14)    |     | 2    |       | ms          |

## 電気的特性

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**電圧値はすべてGNDを基準とする。

**Note 3:**これらのピンがGNDより低い値か $V_{DD}$ を超える値をとると、内部ダイオードによってクランプされる。本製品はラッチアップを生じることなしにGNDより低いかまたは $V_{DD}$ より高い電圧で100mAを超える電流を処理することができる。

**Note 4:**オフセットおよびフルスケール仕様は、シングルエンドの $A_{IN}^+$ 入力として $A_{IN}^-$ を接地した状態で内部2.5Vリファレンスを使用して測定される。

**Note 5:**積分直線性は外部2.55Vリファレンスでテストされ、伝達曲線の実際のエンドポイントを通過する直線からのコードの偏差として定義される。偏差は量子化幅の中心から測定される。

**Note 6:**設計上保証されているが、テストは行われない。

**Note 7:**推奨動作条件。

**Note 8:**アナログ入力範囲は $A_{IN}^+$ と $A_{IN}^-$ の電圧差として定義される。性能は、 $A_{IN}^- = 1.5\text{ V DC}$ に固定し $A_{IN}^+$ をドライブした状態で規定されている。

**Note 9:** $A_{IN}^+$ と $A_{IN}^-$ の絶対電圧はこの範囲内になければならない。

**Note 10:**3ns未満が許容される場合、出力データは1クロック・サイクル後に現れる。クロックが定格速度のときには、CONVがSCKの半クロック前に立ち上がるのが最良である。

**Note 11:**アバーチャ遅延とは異なる。サンプル・ホールドの2.2nsの遅延が、CONVからホールドモードまでの遅延から減算されるので、アバーチャ遅延のほうが短い(1ns)。

**Note 12:**出力されるデータはSCKの立ち上がりエッジでストレージ・ラッチに捕捉されることが保証されている。

**Note 13:**入力信号を捕捉する期間は16番目の立ち上がりクロックによって開始され、変換の立ち上がりエッジで終了する。

**Note 14:**SCKが1サイクル以上および容量性負荷が $10\mu\text{F}$ の場合、内部リファレンスはスリープ・モードからウェイクアップ後2msで安定する。

**Note 15:**フル・パワー帯域幅は、2.5Vp-p入力正弦波で出力コードの振幅が3dBに低下する周波数。

**Note 16:**最大クロック周期により変換時のアナログ性能が保証される。出力データは任意に長いクロックを使わないで読み出すことができる。

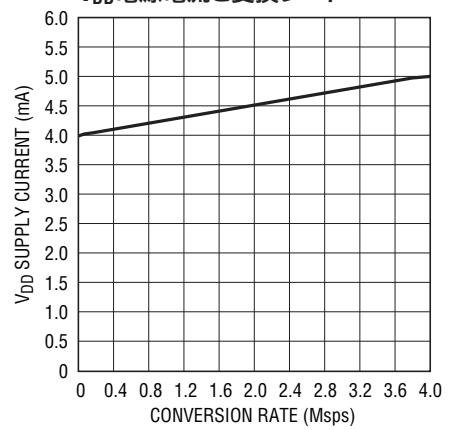

**Note 17:** $V_{DD} = 3\text{V}$ 、 $f_{SAMPLE} = 2.8\text{Msps}$ 。

**Note 18:**LTC1403A-1は14ビットの分解能( $1\text{LSB} = 152\mu\text{V}$ )で測定され、規定されており、LTC1403-1は12ビットの分解能( $1\text{LSB} = 610\mu\text{V}$ )で測定され、規定されている。

**Note 19:**反転入力が $1.5\text{ V DC}$ に固定された状態で、フルスケールの正弦波が非反転入力に供給される。

**Note 20:**各入力のサンプリング・コンデンサが入力容量のうちの $4.1\text{pF}$ を占める。

# LTC1403-1/LTC1403A-1

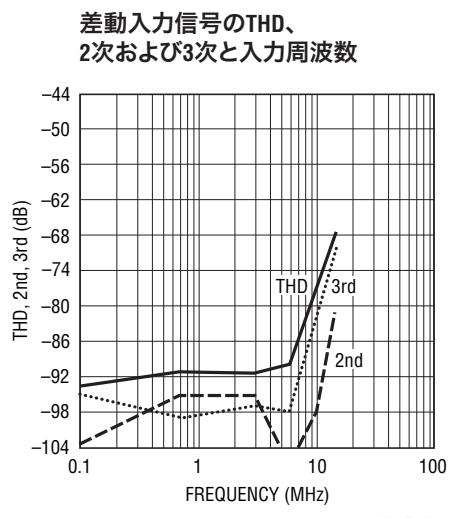

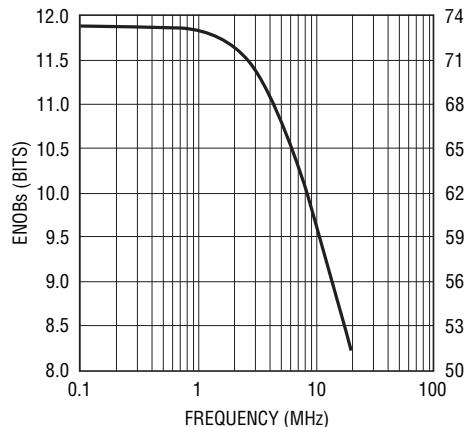

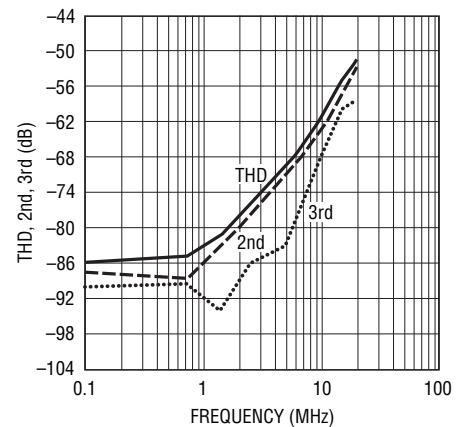

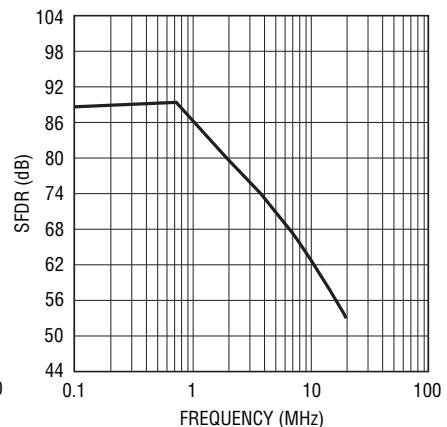

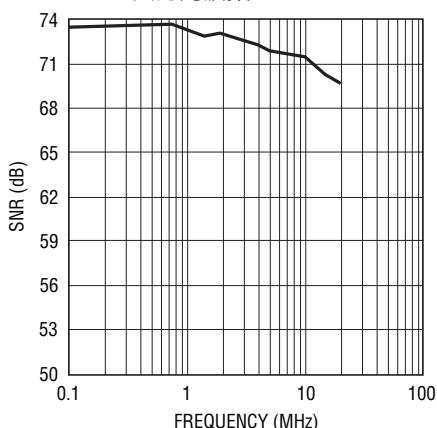

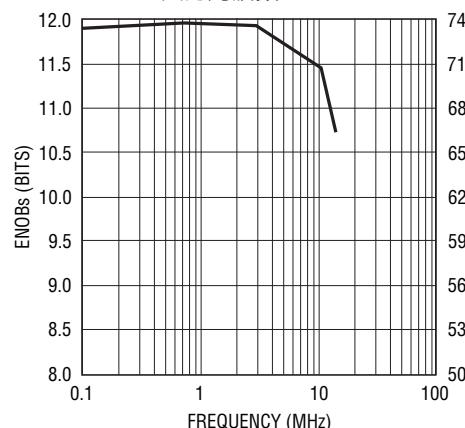

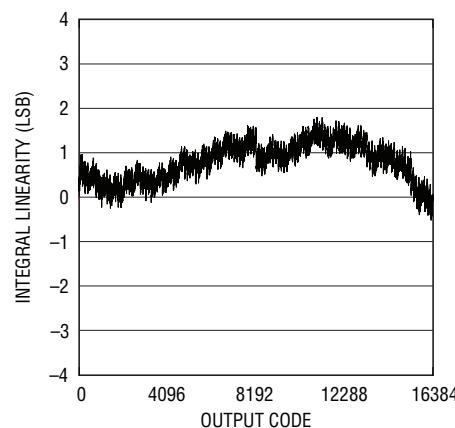

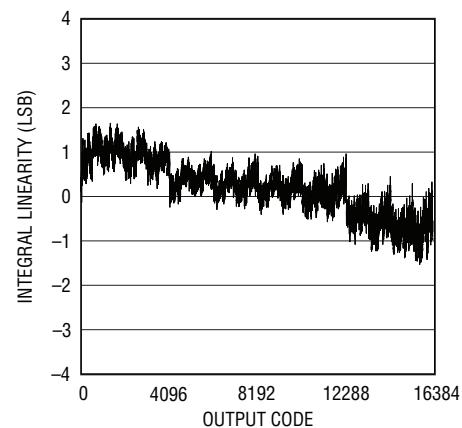

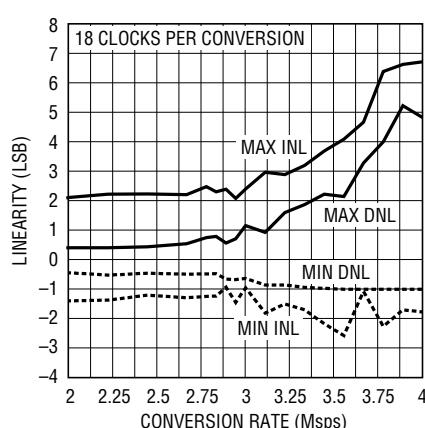

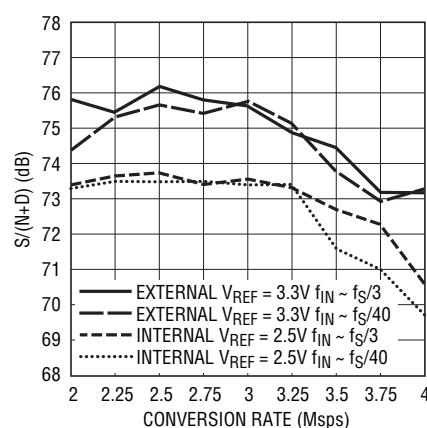

**標準的性能特性**  $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 3\text{V}$ 、 $A_{IN^-} = 1.5\text{V DC}$ に固定してシングルエンドの $A_{IN^+}$ 信号でドライブ、 $V_{CM} = 1.5\text{V DC}$ に設定して差動信号で両方の入力をドライブ (LTC1403A-1)

ENOBおよびSINADと入力周波数

14031 G01

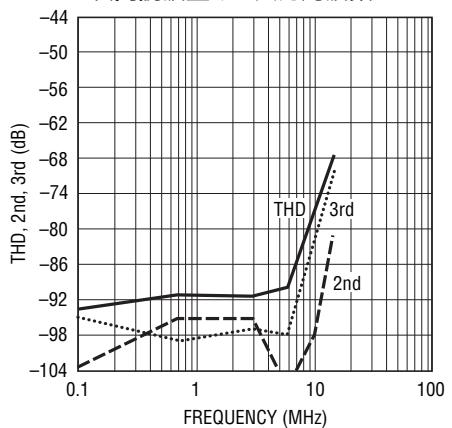

THD、2次および3次と入力周波数

14031 G02

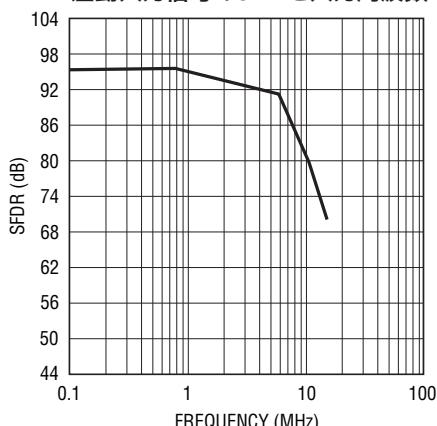

SFDRと入力周波数

14031 G03

SNRと入力周波数

14031 G04

差動入力信号のENOBおよびSINADと入力周波数

14031 G18

差動入力信号のTHD、2次および3次高調波歪みと入力周波数

14031 G19

差動入力信号のSFDRと入力周波数

14031 G20

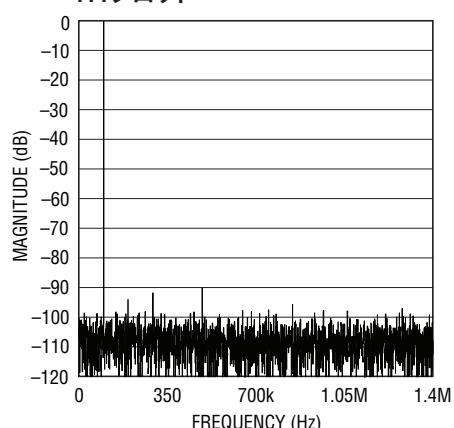

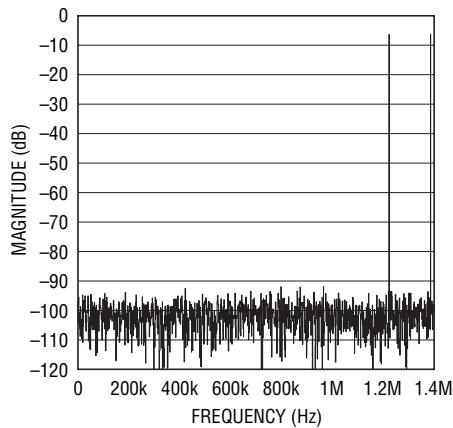

98kHz正弦波の4096ポイントのFFTプロット

14031 G05

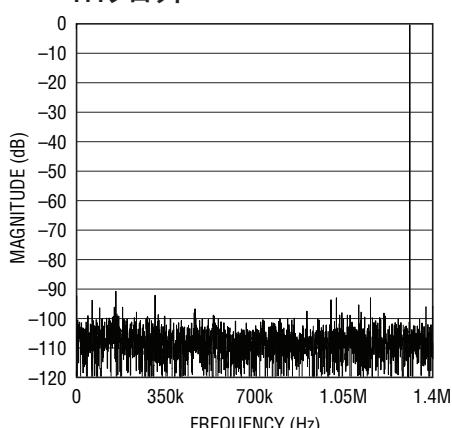

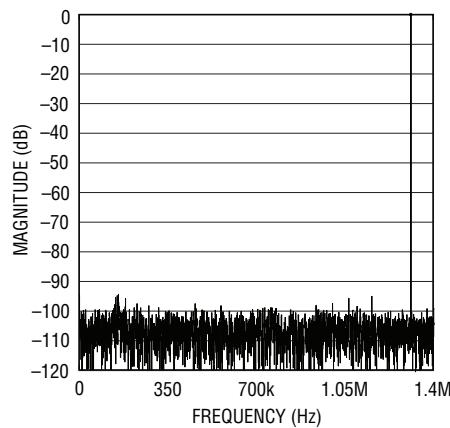

1.3MHz正弦波の4096ポイントのFFTプロット

14031 G06

14031fc

**標準的性能特性**  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 3\text{V}$ ,  $A_{IN^-} = 1.5\text{V DC}$ に固定してシングルエンドの $A_{IN^+}$ 信号でドライブ、 $V_{CM} = 1.5\text{V DC}$ に設定して差動信号で両方の入力をドライブ(LTC1403A-1)

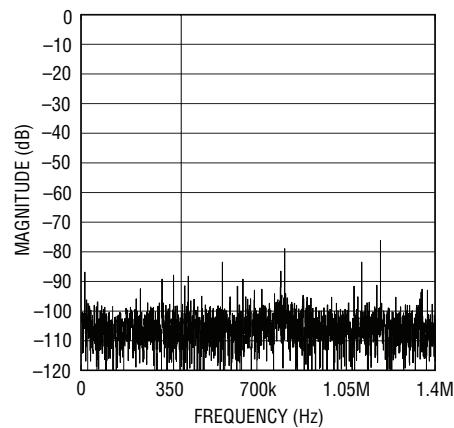

差動入力信号の1.4MHz入力と

加算された1.56MHz入力のIMDの

4096ポイントのFFTプロット

差動入力信号の1.3MHz正弦波の

4096ポイントのFFTプロット

差動入力信号の10.7MHz正弦波の

4096ポイントのFFTプロット

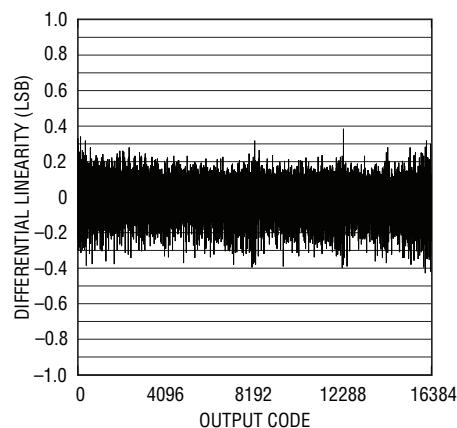

微分直線性と出力コード

積分直線性と出力コード

差動入力信号の積分直線性と

出力コード

微分および積分直線性と

変換レート

SINADと変換レート

# LTC1403-1/LTC1403A-1

標準的性能特性  $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 3\text{V}_o$  (LTC1403-1およびLTC1403A-1)

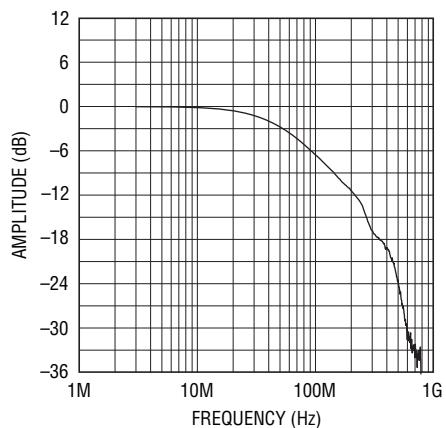

2.5V<sub>P-P</sub> パワー帯域幅

CMRRと周波数

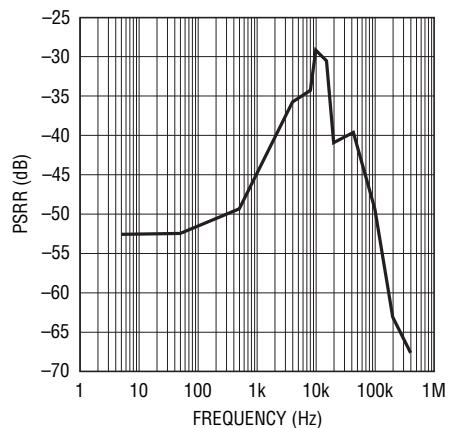

PSRRと周波数

リファレンス電圧と負荷電流

リファレンス電圧と $V_{DD}$

$V_{DD}$ 電源電流と変換レート

## ピン機能

**A<sub>IN</sub><sup>+</sup>(ピン1)**: 非反転アナログ入力。A<sub>IN</sub><sup>+</sup>はA<sub>IN</sub><sup>-</sup>に対して完全に差動で動作し、A<sub>IN</sub><sup>-</sup>を基準にした差動振幅は-1.25V～1.25V、同相振幅は0V～V<sub>DD</sub>です。

**A<sub>IN</sub><sup>-</sup>(ピン2)**: 反転アナログ入力。A<sub>IN</sub><sup>-</sup>はA<sub>IN</sub><sup>+</sup>に対して完全に差動で動作し、A<sub>IN</sub><sup>+</sup>を基準にした差動振幅は1.25V～-1.25V、同相振幅は0V～V<sub>DD</sub>です。

**V<sub>REF</sub>(ピン3)**: 2.5V内部リファレンス。10μFセラミック・コンデンサ(または0.1μFセラミックと10μFタンタル・コンデンサの並列接続)でGNDおよび切れ目のないアナログ・グランド・プレーンにバイパスします。2.55V～V<sub>DD</sub>間の外部リファレンスでオーバードライブすることができます。

**GND(ピン4、5、6、露出パッド・ピン11)**: グランド。これらのグランド・ピンと露出パッドはデバイス下部の切れ目のないグランド・プレーンに直接接続する必要があります。アナログ信号電流とデジタル出力信号電流がこれらのピンを流れることに留意してください。

**V<sub>DD</sub>(ピン7)**: 3V正電源。この単一電源ピンでチップ全体に3Vを供給します。10μFセラミック・コンデンサ(または0.1μFセラミックと10μFタンタル・コンデンサの並列接続)でGNDおよび切れ目のないアナログ・グランド・プレーンにバイパスします。

ミックと10μFタンタル・コンデンサの並列接続)でGNDおよび切れ目のないアナログ・グランド・プレーンにバイパスします。内部アナログ電流とデジタル出力信号電流がこのピンを流れることに留意してください。0.1μFバイパス・コンデンサはピン6とピン7にできるだけ近づけて配置するように注意してください。

**SDO(ピン8)**: スリーステート・シリアル・データ出力。各出力データ・ワードは、前回の変換の開始時のA<sub>IN</sub><sup>+</sup>とA<sub>IN</sub><sup>-</sup>のアナログ入力間の差を表しています。出力形式は2の補数です。

**SCK(ピン9)**: 外部クロック入力。変換プロセスを進めて、立ち上がりエッジで出力データを順番に出力します。TTLレベル( $\leq 3V$ )および3V CMOSレベルに応答します。1つ以上のパルスによってスリープからウェイクアップします。

**CONV(ピン10)**: 変換開始。立ち上がりエッジでアナログ入力信号をホールドして、変換を開始します。TTLレベル( $\leq 3V$ )および3V CMOSレベルに応答します。SCKが“H”か“L”に固定された状態で2つのパルスがあると、ナップ・モードを開始します。SCKが“H”か“L”に固定された状態で4つ以上のパルスがあると、スリープ・モードを開始します。

## ブロック図

# LTC1403-1/LTC1403A-1

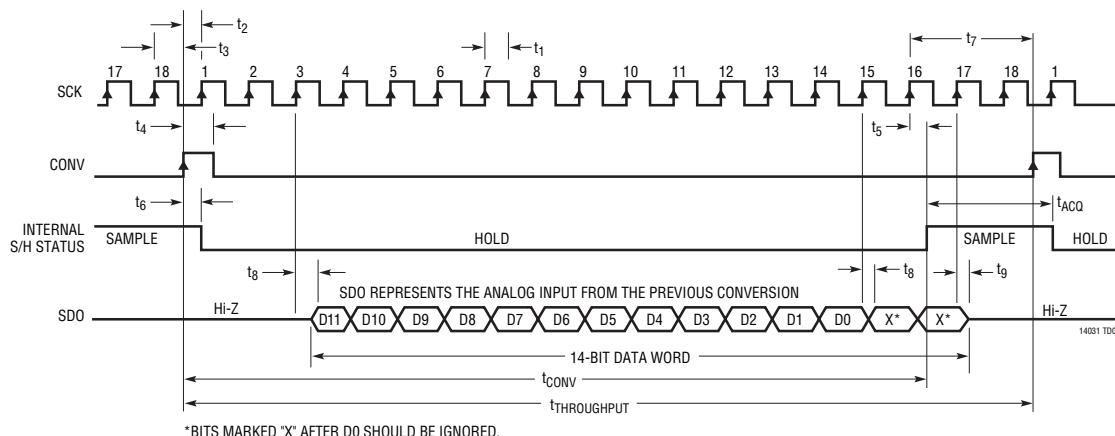

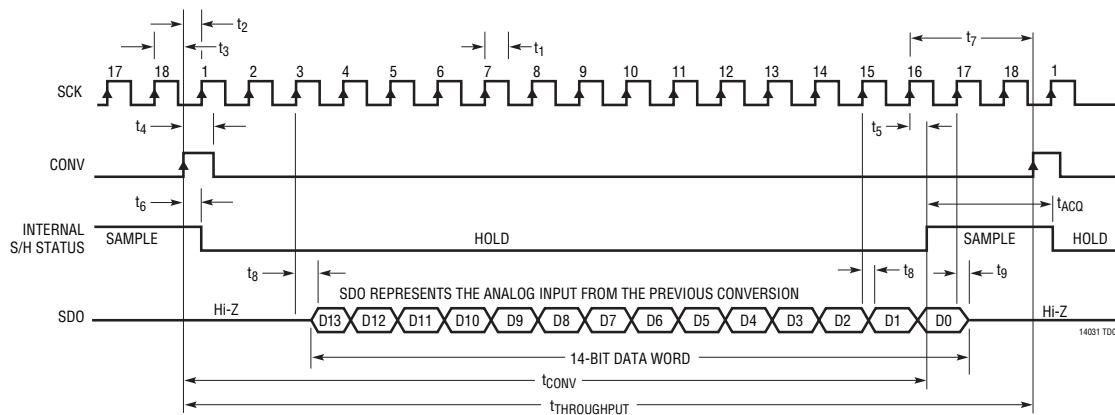

## タイミング図

LTC1403-1タイミング図

\*BITS MARKED 'X' AFTER D0 SHOULD BE IGNORED.

LTC1403A-1タイミング図

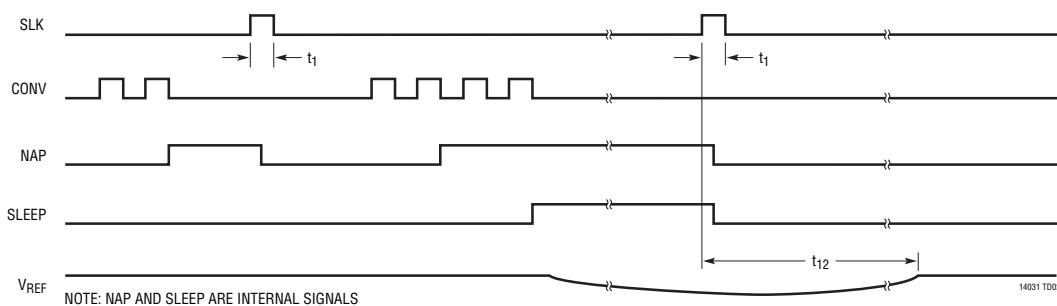

ナップ・モードとスリープ・モードの波形

SCKとSDO間の遅延

14031fc

## アプリケーション情報

### アナログ入力のドライブ

LTC1403-1/LTC1403A-1の差動アナログ入力は簡単にドライブできます。入力は差動あるいはシングルエンド入力として(すなわち $A_{IN}^-$ 入力を $V_{CM}$ に設定)ドライブ可能です。両方の差動アナログ入力 $A_{IN}^+$ と $A_{IN}^-$ は同時にサンプリングされます。各入力ペアの両方の入力に共通などんな不要信号でも、サンプル・ホールド回路の同相除去によって低減されます。変換の終わりにサンプル・ホールド・コンデンサを充電する間、入力には小さな電流スパイクが1回だけ生じます。変換中、アナログ入力にはわずかなリーク電流しか流れません。ドライブ回路のソース・インピーダンスが低い場合は、LTC1403-1/LTC1403A-1の入力を直接ドライブすることができます。ソース・インピーダンスが増加すると、収集時間も増加します。ソース・インピーダンスが高いときに収集時間を最短にするには、バッファ・アンプを使用する必要があります。主な要件は、アナログ入力をドライブするアンプが、小さな電流スパイクが発生した後、次の変換が開始する前に安定しなければならないことです(最大スループット・レートを得るには、セトリング時間は39nsであること)。入力アンプの選択時には、アンプによってノイズや高調波歪みが増えることにも留意してください。

### 入力アンプの選択

いくつかの要件を考慮に入れれば、入力アンプは簡単に選択できます。まず、サンプリング・コンデンサを充電する際にアンプで発生する電圧スパイクの大きさを制限するために、閉ループ帯域幅周波数で出力インピーダンスが低い( $<100\Omega$ )アンプを選択します。たとえば、1の利得でアンプが使用されており、そのユニティゲイン帯域幅が50MHzであれば、50MHzでの出力インピーダンスは $100\Omega$ 未満でなければなりません。2番目の要件は、最大スループット・レートを得るための十分な小信号セトリング時間を確保するには、閉ループ帯域幅が40MHzより大きくなければならないことです。低速オペアンプを使用する場合、変換と変換の間の時間を長くすれば、セトリングのための時間を長くとることができます。LTC1403-1/LTC1403A-1をドライブするための最適なオペアンプの選択は、アプリケーションに依存します。一般に、アプリケーションは2つのカテゴリーに分類されます。ダイナミック仕様が最も重要なACアプリケーションと、DC精度とセトリング時間が最も重要なタイム・ドメイン・アプリケーションです。以下のリストは、LTC1403-1/LTC1403A-1をドライブするのに適したオペアンプをまとめたものです。(より詳細な情報は、リニアテクノロジーのデータブックおよびWebサイト:[www.linear-tech.co.jp](http://www.linear-tech.co.jp)で提供されます。)

**LTC®1566-1:** 低ノイズ2.3MHz連続時間ローパス・フィルタ。

**LT1630:** デュアル30MHzレール・トゥ・レール電圧FBアンプ。2.7V～±15V電源。非常に高いAVOL、500μVのオフセットと4V振幅で0.5LSBへのセトリング時間が520ns。THDとノイズは40kHzまで-93dB、320kHzまで1LSB未満( $A_V = 1$ 、 $1k\Omega$ に対して $2V_{P-P}$ 、 $V_S = 5V$ )、レール・トゥ・レール性能が必要なACアプリケーション(1/3ナイキスト周波数まで)に最適。クワッド・バージョンのLT1631あり。

**LT1632:** デュアル45MHzレール・トゥ・レール電圧FBアンプ。2.7V～±15V電源。非常に高いAVOL、1.5mVのオフセットと4V振幅で0.5LSBへのセトリング時間が400ns。単一5V電源アプリケーションに最適。THDとノイズは40kHzまで-93dB、800kHzまで1LSB未満( $A_V = 1$ 、 $1k\Omega$ に対して $2V_{P-P}$ 、 $V_S = 5V$ )、レール・トゥ・レール性能が必要なACアプリケーションに最適。クワッド・バージョンのLT1633あり。

**LT1813:** デュアル100MHzの750V/μs3mA電圧帰還アンプ。5V～±5V電源。歪みは±5V電源で100kHzまで-86dB、1MHzまで-77dB( $500\Omega$ 、 $2V_{P-P}$ )。±5V電源を使用した高速ACアプリケーションに最適なデバイス。

**LT1801:** 80MHzGBWP、-75dBc/500kHz、2mA/アンプ、 $8.5nV/\sqrt{Hz}$ 。

**LT1806/LT1807:** 325MHzGBWP、-80dBc低歪み(5MHz)、ユニティゲイン安定、レール・トゥ・レール入出力、10mA/アンプ、 $3.5nV/\sqrt{Hz}$ 。

**LT1810:** 180MHzGBWP、-90dBc低歪み(5MHz)、ユニティゲイン安定、レール・トゥ・レール入出力、15mA/アンプ、 $16nV/\sqrt{Hz}$ 。

**LT1818/LT1819:** 400MHz、2500V/μs、9mA、シングル/デュアル電圧モード・オペアンプ。

**LT6200:** 165MHzGBWP、-85dBc低歪み(1MHz)、ユニティゲイン安定、レール・トゥ・レール入出力、15mA/アンプ、 $0.95nV/\sqrt{Hz}$ 。

**LT6203:** 100MHzGBWP、-80dBc低歪み(1MHz)、ユニティゲイン安定、レール・トゥ・レール入出力、3mA/アンプ、 $1.9nV/\sqrt{Hz}$ 。

**LT6600-10:** アンプ/フィルタ、差動入出力、10MHzカットオフ。

# LTC1403-1/LTC1403A-1

## アプリケーション情報

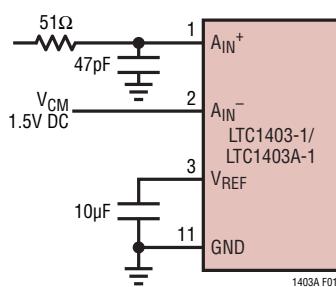

### 入力フィルタ処理とソース・インピーダンス

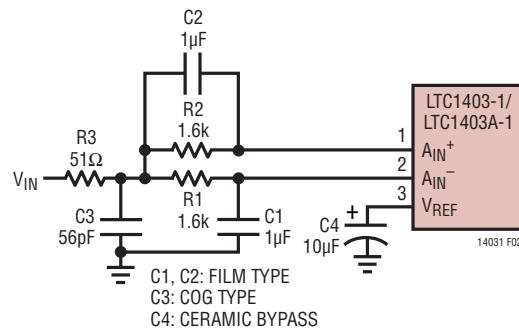

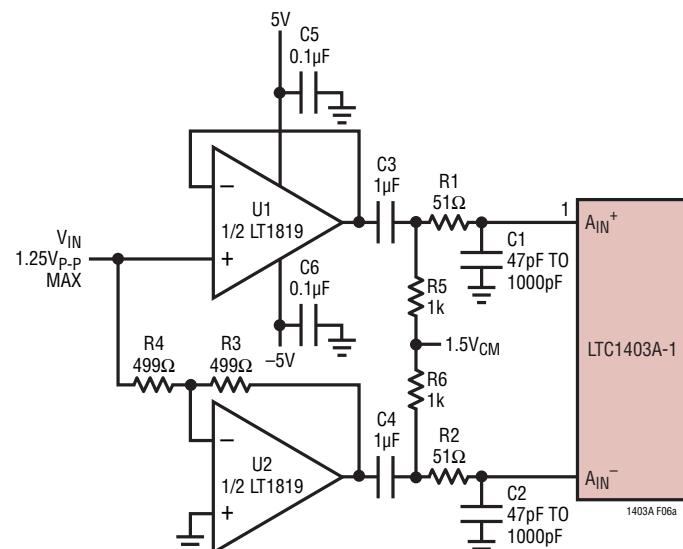

入力アンプおよび他の回路のノイズと歪みはLTC1403-1/LTC1403A-1のノイズと歪みに加わるので、これらについて考慮する必要があります。サンプル・ホールド回路の小信号帯域幅は50MHzです。アナログ入力に現れるいづれのノイズまたは歪み積もこの帯域幅全体で合算されます。ノイズの多い入力回路は、アナログ入力の前にフィルタ処理してノイズを最小限に抑える必要があります。多くのアプリケーションでは、簡単な1ポールRCフィルタで十分です。たとえば、図1は $A_{IN}^+$ からグランドに接続した47pFのコンデンサと51Ωのソース抵抗を示しており、入力帯域幅が47MHzに制限されます。47pFのコンデンサは、入力のサンプル・ホールド用の蓄電器としても機能し、サンプリング・グリッチの影響を受けやすい回路からADCの入力を絶縁します。これらの部品は歪みを増加させる可能性があるため、高品質のコンデンサと抵抗を使用してください。NPOとシルバ・マイカ型誘電体コンデンサは、優れた直線性を備えています。また、表面実装カーボン抵抗は、自己発熱や半田付け時に生じる損傷によって歪みを生じるおそれがあります。表面実装金属皮膜抵抗は、両方の問題の影響を非常に受けにくいものです。振幅の大きい不要な信号の周波数が望みの信号周波数に近いときには、多極フィルタが必要です。外付けの大きなソース抵抗を13pFの入力コンデンサと組み合わせると、50MHz定格の帯域幅が減少し、収集時間が39nsよりも長くなります。

図1. RC入力フィルタ

### 入力範囲

LTC1403-1/LTC1403A-1のアナログ入力は単一電源で完全に差動でドライブすることができます。各入力は個別に3V<sub>P-P</sub>まで振幅することができます。変換範囲では、各入力は各チャネルの反転入力を基準にして常にプラスまたはマイナス1.25Vまでの範囲内にあります。単一電源アプリケーションでは、

±1.25Vの範囲はAC結合した信号にも最適です。ミッドサプライ(電源中央値)の1.5Vの外部リファレンスを使用せずに单一電源システムで信号をAC結合する方法を図2に示します。DC同相レベルは、システムの単一電源電圧で既に制限されている前段によって与えられます。入力の同相範囲は、グランドから電源電圧 $V_{DD}$ に及びます。 $A_{IN}^+$ 入力と $A_{IN}^-$ 入力の差が1.25Vを超えると、出力コードは0およびオール1に固定され、この差が−1.25Vを下回ると、出力コードは1およびオール0に固定されます。

図2. カットオフ周波数が低い(1kHz)AC信号のAC結合

### 内部リファレンス

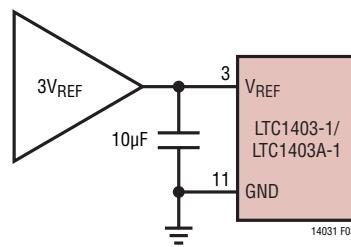

LTC1403-1/LTC1403A-1は温度補償されたバンドギャップ・リファレンスを内蔵しており、±1.25Vの入力範囲を得るために製造時に約2.5Vに調整されています。リファレンス・アンプの出力 $V_{REF}$ (ピン3)はコンデンサでグランドにバイパスする必要があります。リファレンス・アンプは1μF以上のコンデンサで安定します。最高のノイズ性能を得るには、10μFセラミック・コンデンサか10μFタンタル・コンデンサを0.1μFセラミック・コンデンサと並列接続することを推奨します。図3に示すように、 $V_{REF}$ ピンは外部リファレンスでオーバードライブすることができます。外部リファレンスの電圧は内部リファレンスのクラスAのフルアップ出力の2.5Vより高くする必要があります。外部リファレンスの推奨範囲は、2.55V～ $V_{DD}$ です。2.55Vの外部リファレンスには0.75mAのDC静止負荷電流が流れ、変換時には3mAが流れます。

図3

14031fc

## アプリケーション情報

### 入力範囲とリファレンス電圧

差動入力範囲のユニポーラ電圧範囲は、ピン3のリファレンス・バッファ出力V<sub>REF</sub>の電圧とグランド(露出パッド・グランド)の電圧との差に等しくなります。内部リファレンス使用時は、ADCの差動入力範囲は±1.25Vになります。内部のADCは、これら2つのノードを基準にしています。この関係は外部リファレンスにも当てはまります。

### 差動入力

LTC1403-1/LTC1403A-1は独自の差動サンプル・ホールド回路を備えており、グランドからV<sub>DD</sub>までの電圧入力が可能です。ADCは入力の同相電圧に関係なく、常にA<sub>IN</sub><sup>+</sup>-A<sub>IN</sub><sup>-</sup>のバイポーラの差を変換します。同相除去は、非常に高い周波数まで有効です(図4を参照)。唯一の要件は、両方の入力がグランドを下回らないかV<sub>DD</sub>を超えないことです。積分非直線性誤差(INL)と微分非直線性誤差(DNL)は、同相電圧とはほとんど無関係ですが、オフセット誤差は変化します。オフセット誤差の変化は、通常、同相電圧の0.1%未満です。

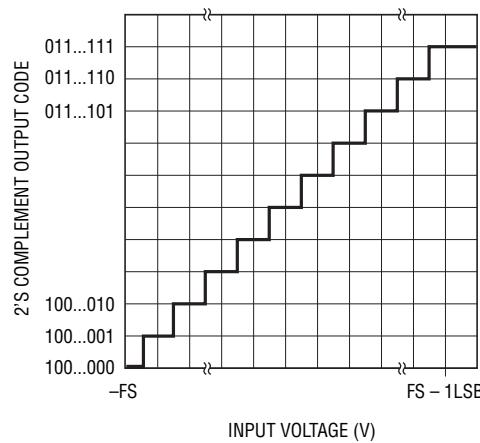

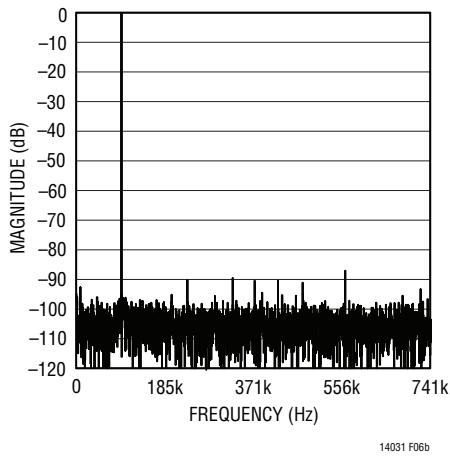

LTC1403-1/LTC1403A-1の理想的な入出力特性を図5に示します。コードの遷移は連続する整数のLSB値の中間点(つまり、0.5LSB、1.5LSB、2.5LSB、FS-1.5LSB)で発生します。出力コードは2の補数で、LTC1403A-1の場合1LSB = 2.5V/16384 = 153μV、LTC1403-1の場合1LSB = 2.5V/4096 = 610μVです。LTC1403A-1には1LSB RMSのランダム・ホワイト・ノイズがあります。図6aに、FFTのプロット(図6b)に示すような最適なTHD性能とSHDR性能を得るためにシングルエンドの入力信号を差動入力信号に変換するLTC1819を示します。

LTC1403-1/LTC1403A-1の

伝達特性

図5

図4

図6a. LTC1403A-1を差動でドライブするLT1819

# LTC1403-1/LTC1403A-1

## アプリケーション情報

図6b LTC1403-1の6MHz正弦波の4096ポイントのFFTプロット

(LT1819が入力を差動でドライブ)

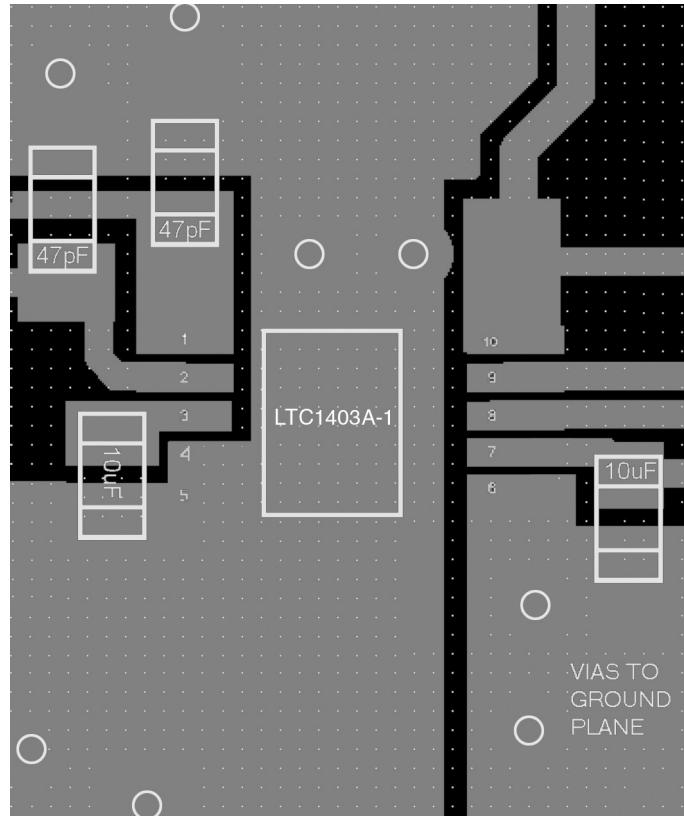

### ボード・レイアウトとバイパス

ワイヤ・ラップ・ボードは、高分解能A/Dコンバータや高速A/Dコンバータには推奨しません。LTC1403-1/LTC1403A-1から最良の性能を得るには、グランド・プレーン付きのPCボードが必要です。PCボードのレイアウトでは、デジタル信号ラインとアナログ信号ラインをできるだけ離すようにします。特に、どのデジタル・トラックもアナログ信号トラックに沿って配置しないように注意します。入力間に最適な位相の整合が必要な場合は、2つの入力線の長さを一致させます。

VDDピンとV<sub>REF</sub>ピンには、このデータシートの最初のページのブロック図に示したように、高品質のタンタルおよびセラミックのバイパス・コンデンサを使用します。最適な性能を得るために、VDDピンとV<sub>REF</sub>ピンには10μFの表面実装AVXコンデンサと0.1μFのセラミック・コンデンサを使うことを推奨します。あるいは、村田製作所製GRM219R60J106Mのような10μFのセラミック・チップ・コンデンサを使用することができます。コンデンサはピンにできるだけ近づけて配置する必要があります。ピンとバイパス・コンデンサを接続するトレースは短くし、幅をできるだけ広くします。

推奨するシステム・グランドの接続を図7に示します。アナログ回路のグランドはすべてLTC1403-1/LTC1403A-1のGND(ピン4、5、6および露出パッド)で終端します。ノイズのない動作を実現するため、LTC1403-1/LTC1403A-1(ピン4、5、6および露出パッド)から電源へのグランド・リターンは低インピーダンスにします。デジタル回路のグランドは、共通のデジタル電源に接続します。ADCのデータ出力と制御信号が常時アクティブなマイクロプロセッサ・バスに接続されているアプリケーション

図7. 推奨レイアウト

では、変換結果に誤差が生じことがあります。これらの誤差は、マイクロプロセッサから逐次比較コンパレータへのフィードスルーによるものです。この問題は、変換時にマイクロプロセッサを強制的に待機状態にするか、スリーステート・バッファを使用してADCのデータ・バスを絶縁することによって解決することができます。

### パワーダウン・モード

電源を投入すると、LTC1403-1/LTC1403A-1はアクティブ状態に初期化され、変換を行う準備が整います。ナップ・モードおよびスリープ・モードの波形は、LTC1403-1/LTC1403A-1のパワーダウン・モードを示します。SCK入力およびCONV入力は、パワーダウン・モードを制御します(「タイミング図」を参照)。CONVに2つの立ち上がりエッジが与えられ、その間にSCKの立ち上がりエッジが与えられない場合、LTC1403-1/LTC1403A-1はナップ・モードになり、消費電力が14mWから6mWに減少します。ナップ・モードでは、内部リファレンスに電力が供給されたままです。SCKに1つ以上の立ち上がりエッジが与えられると、LTC1403-1/LTC1403A-1は動作のために直

## アプリケーション情報

ちにウェイクアップし、CONVによって1クロック・サイクル以内に正確な変換を開始することができます。CONVに4つの立ち上がりエッジが与えられ、その間にSCKの立ち上がりエッジが与えられない場合、LTC1403-1/LTC1403A-1はスリープ・モードになり、消費電力は16mWから10μWに減少します。SCKに1つ以上の立ち上がりエッジが与えられると、LTC1403-1/LTC1403A-1はウェイクアップして動作を開始します。内部リファレンス( $V_{REF}$ )は、10μFの負荷ではスルーしてセトリングするのに2msを要します。スリープ・モードを2msごとよりも高い頻度で使用すると、内部リファレンスのセトリング精度が低下することに注意してください。変換速度が遅い場合は、ナップ・モードとスリープ・モードを使用して消費電力を大幅に低減できることに注意してください。

## デジタル・インターフェイス

LTC1403-1/LTC1403A-1は、3線SPI(シリアル・プロトコル・インターフェイス)インターフェイスを備えています。SCK入力とCONV入力およびSDO出力によりこのインターフェイスが実装されています。ロジック振幅が $V_{DD}$ を超えないければ、SCK入力とCONV入力は3Vロジックからの振幅を受け入れ、TTL互換です。3つのシリアル・ポート信号について以下に詳細に説明します。

### 変換開始入力(CONV)

CONVの立ち上がりエッジで変換が開始されますが、それ以降のCONVの立ち上がりエッジは、その後SCKに16の立ち上がりエッジが発生するまでLTC1403-1/LTC1403A-1によって無視されます。CONVの立ち上がりエッジの間には、クロック入力SCKの立ち上がりエッジが少なくとも16個必要です。ただし最大変換速度を得るには、変換と変換の間にさらに2つのクロック周期を与えて内部のADCのサンプル・ホールド回路の39nsの収集時間を与える必要があります。1変換当たり16クロック周期かかる場合、39nsの収集時間を与えるために最大変換速度が2.8Mspsに制限されます。いずれの場合も出力データストリームが最初の16クロック周期内に出力され、プロセッサのシリアル・ポートとの互換性が保たれます。CONVのデューティ・サイクルは、プロセッサのシリアル・ポート用のフレーム同期信号として使用するために任意に選択できます。CONVを生成する簡単な方法としては、LTC1403-1/LTC1403A-1をドライブするSCK1個分の幅のパルスを生成し、この信号を適当な数のインバータでバッファして、プロセッサのシリアル・ポートのフレーム同期入力をドライブするのに適切な遅延を確保します。変換開始時にCONVによってトリガされるサンプルからホールドへの遷移時にデジタル・ノ

イズによる干渉を回避するために、LTC1403-1/LTC1403A-1のCONV入力を最初にドライブするのが良い方法です。また、CONVの立ち上がりエッジでサンプル・ホールドがホールド・モードになる直前にADCのフロント・エンドにグリッチが生じるのを防ぐために、CONV信号の“L”部分の幅を15nsより広くすることも良い方法です。

### CONV入力のジッタの最小化

100kHzを超える振幅の大きい正弦波がサンプリングされる高速アプリケーションでは、CONV信号のジッタをできる限り小さくする(10ps以下)必要があります。一般的な水晶クロック・モジュールの方形波出力は、通常この要件を容易に満たします。難しいのは、システムの他のデジタル回路からのジッタの影響を受けずに、この水晶クロックからCONV信号を生成することです。クロック分周器も水晶クロックからCONV入力への信号経路にあるどのゲートも、システムの他のデバイスと同じ集積回路を共有しないようにします。インターフェイス回路の例に示すように、SCK入力とCONV入力は、シリアル・ポート・インターフェイスのドライブに使用されるデジタル・バッファで最初にドライブする必要があります。DSPのマスター・クロックがDSPの水晶発振器から直接生成されていても、ジッタによって既に損なわれているおそれがあることにも注意してください。プロセッサの高速クロックのもう1つの問題は、安価な低速水晶発振器(10MHz)を使用して高速だがジッタの多いフェーズロック・ループ・システムのクロック(40MHz)が生成される場合が多いことです。これらのPLLで生成される高速クロックのジッタは数ナノ秒に達することがあります。DSPポートで生成されたフレーム同期信号を使用することにした場合、この信号にはDSPのマスター・クロックと同じジッタが含まれることに注意してください。

### シリアル・クロック入力(SCK)

SCKの立ち上がりエッジで変換プロセスが進み、SDOデータストリームの各ビットも更新されます。CONVが立ち上がった後、SCKの3番目の立ち上がりエッジで12/14データ・ビットがMSBを先頭にクロックアウトされ始めます。簡単な方法としては、LTC1403-1/LTC1403A-1をドライブするSCKを最初に生成し、この信号を適当な数のインバータでバッファしてからプロセッサのシリアル・ポートのシリアル・クロック入力をドライブします。クロックの立ち下がりエッジでシリアル・データ出力(SDO)のデータをプロセッサ・シリアル・ポートにラッチします。14ビットのシリアル・データは、フレーム同期ごとに16以上のクロックを使って16ビット・ワードとして右揃えで受け取られます。内部の高速コンパレータによる内部ビット比較の判定時

## アプリケーション情報

にデジタル・ノイズによる干渉を回避するために、LTC1403-1/LTC1403A-1のSCK入力を最初にドライブするのが良い方法です。CONV入力とは異なり、入力信号が既にサンプリングされて一定に保たれているので、SCK入力はジッタの影響を受けません。

### シリアル・データ出力(SDO)

電源を投入すると、SDO出力は自動的にハイインピーダンス状態にリセットされます。新たな変換が開始するまでSDO出力はハイインピーダンス状態のままであります。CONVの立ち上がりエッジの後、SDOは、SCKの3番目の立ち上がりエッジから始まる出力データストリームに12/14ビットを2の補数の形式で送出します。データ・ビットを送出していないときは、SDOは常にハイインピーダンス・モードです。SCKから有効なSDOまでの遅延の規定値に注意してください。SDOはSCKの次の立ち上がりエッジまで有効であることが常に保証されています。16ビットの出力データストリームは、ほとんどのプロセッサの16ビットまたは32ビットのシリアル・ポートと互換性があります。

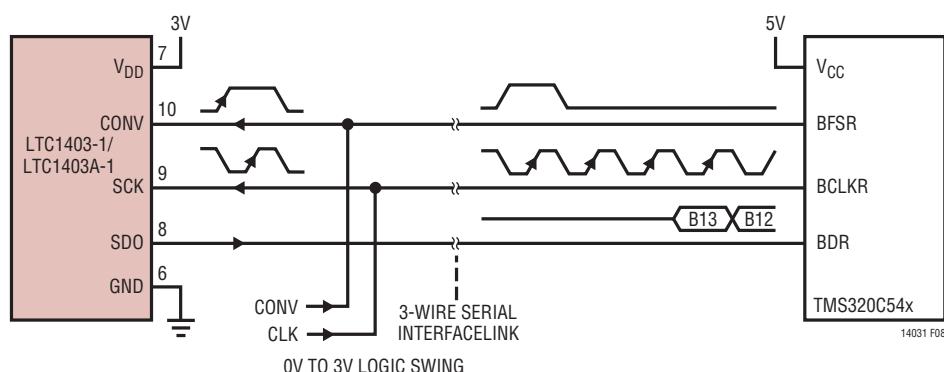

### TMS320C54xへのハードウェア・インターフェイス

LTC1403-1/LTC1403A-1は、高速デジタル・シグナル・プロセッサ(DSP)のバッファ付き高速シリアル・ポート向けに設計されたインターフェイスを備えたシリアル出力ADCです。図8にTMS320C54xを使用したこのインターフェイスの例を示します。

TMS320C54xのバッファ付きシリアル・ポートは、2kBのメモリ・セグメントに直接アクセスします。ADCのシリアル・データは、LTC1403-1/LTC1403A-1の最大2.8Mspsの変換レートで、交互に切り替わる2つの1kBセグメントにリアルタイムで収集できます。DSPアセンブリ・コードにより、外部の立ち上がりパルスを受け入れるためにBFSRピンにフレーム同期モードを設定し、立ち上がりエッジ・クロックを受け入れるためにBCLKRピンにシリアル・クロックを設定します。LTC1403-1/LTC1403A-1の近くにバッファを追加すれば、DSPまでの長いトラックをドライブしてLTC1403-1/LTC1403A-1への信号の劣化を防止することができます。この構成は標準的なシステム・ボードを横断するには充分ですが、非常に長い伝送ラインの特性インピーダンスを整合させるには、バッファ出力にソース抵抗が、またDSPには終端抵抗が必要な場合があります。SDO伝送ラインを終端する必要がある場合は、まずその伝送ラインを1個または2個の74ACTxxゲートを使ってバッファします。DSPポートのTTLスレッシュホールド入力は、SDOピンの3V振幅に正しく応答します。

図8. TMS320C54xへのDSPシリアル・インターフェイス

## アプリケーション情報

```

; 10-23-03 ****

; Files: 014SI.ASM -> 1403 bipolar Sine wave collection with Serial Port interface

;          bvectors.asm      buffered mode.

;          s2k14ini.asm      2k buffer size.

; first element at 1024, last element at 1023, two middles at 2047 and 0000

; bipolar mode

; Works 16 or 64 clock frames.

; negative edge BCLKR

; negative BFSR pulse

; -0 data shifted

; 1' cable from counter to CONV at DUT

; 2' cable from counter to CLK at DUT

; ****

.width 160

.length 110

.title "sineb0 BSP in auto buffer mode"

.mmregs

.setsect ".text", 0x500,0 ;Set address of executable

.setsect "vectors", 0x180,0 ;Set address of incoming 1403 data

.setsect "buffer", 0x800,0 ;Set address of BSP buffer for clearing

.setsect "result", 0x1800,0 ;Set address of result for clearing

.text ;.text marks start of code

start:

;this label seems necessary

;Make sure /PWRDWN is low at J1-9

;to turn off AC01 adc

tim=#0fh

prd=#0fh

tcr = #10h ; stop timer

tspc = #0h ; stop TDM serial port to AC01

pmst = #01a0h ; set up iptr. Processor Mode STatus register

sp = #0700h ; init stack pointer.

dp = #0 ; data page

ar2 = #1800h ; pointer to computed receive buffer.

ar3 = #0800h ; pointer to Buffered Serial Port receive buffer

ar4 = #0h ; reset record counter

call sineinit ; Double clutch the initialization to insure a proper

sinepeek:

call sineinit ; reset. The external frame sync must occur 2.5 clocks

; or more after the port comes out of reset.

wait goto wait

; -----Buffered Receive Interrupt Routine -----

breceive:

ifr = #10h ; clear interrupt flags

TC = bitf(@BSPCE,#4000h) ; check which half (bspce(bit14)) of buffer

if (NTC) goto bufull ; if this still the first half get next half

bspce = #(2023h + 08000h); turn on halt for second half (bspce(bit15))

return_enable

; -----mask and shift input data-----

bufull:

b = *ar3+ << -0 ; load acc b with BSP buffer and shift right -0

b = #03FFFh & b ; mask out the TRISTATE bits with #03FFFh

b = b ^ #2000h ; invert the MSB for bipolar operation B

*ar2+ = data(#0bh) ; store B to out buffer and advance AR2 pointer

TC = (@ar2 == #02000h) ; output buffer is 2k starting at 1800h

if (TC) goto start ; restart if out buffer is at 1fffh

goto bufull

```

## アプリケーション情報

```

;           dummy bsend return

bsend    return_enable          ;this is also a dummy return to define bsend

;                                ;in vector table file BVECTORS.ASM

;           end ISR

;

;copy "c:\dskplus\1403\s2k14ini.asm"      ;initialize buffered serial port

;space 16*32                         ;clear a chunk at the end to mark the end

=====

;

;  VECTORS

;

;=====

.sect "vectors"                  ;The vectors start here

.copy "c:\dskplus\1403\bvectors.asm" ;get BSP vectors

;

.sect "buffer"                   ;Set address of BSP buffer for clearing

.space 16*0x800

.sect "result"                   ;Set address of result for clearing

.space 16*0x800

;

.end

;

*****

; File: BVECTORS.ASM -> Vector Table for the 'C54x DSKplus          10.Jul.96

;                                BSP vectors and Debugger vectors

;                                TDM vectors just return

*****

; The vectors in this table can be configured for processing external and

; internal software interrupts. The DSKplus debugger uses four interrupt

; vectors. These are RESET, TRAP2, INT2, and HPIINT.

; * DO NOT MODIFY THESE FOUR VECTORS IF YOU PLAN TO USE THE DEBUGGER *

;

; All other vector locations are free to use. When programming always be sure

; the HPIINT bit is unmasked (IMR=200h) to allow the communications kernel and

; host PC interact. INT2 should normally be masked (IMR(bit 2) = 0) so that the

; DSP will not interrupt itself during a HINT. HINT is tied to INT2 externally.

;

;

;

.title "Vector Table"

.mmregs

;

reset   goto #80h      ;00; RESET  * DO NOT MODIFY IF USING DEBUGGER *

nop

nop

;

nmi     return_enable ;04; non-maskable external interrupt

nop

nop

nop

;

trap2   goto #88h      ;08; trap2  * DO NOT MODIFY IF USING DEBUGGER *

nop

nop

;

int0    .space 52*16   ;0C-3F: vectors for software interrupts 18-30

return_enable ;40; external interrupt int0

nop

nop

nop

;

int1    return_enable ;44; external interrupt int1

nop

nop

;

```

14031fc

## アプリケーション情報

```

nop

int2    return_enable    ;48; external interrupt int2

nop

nop

nop

tint    return_enable    ;4C; internal timer interrupt

nop

nop

nop

brint   goto breceive   ;50; BSP receive interrupt

nop

nop

nop

bxint   goto bsend      ;54; BSP transmit interrupt

nop

nop

nop

trint   return_enable    ;58; TDM receive interrupt

nop

nop

nop

txint   return_enable    ;5C; TDM transmit interrupt

nop

nop

int3    return_enable    ;60; external interrupt int3

nop

nop

nop

hpiint  dgoto #0e4h      ;64; HPIint * DO NOT MODIFY IF USING DEBUGGER *

nop

nop

.space  24*16      ;68-7F; reserved area

*****

* (C) COPYRIGHT TEXAS INSTRUMENTS, INC. 1996

*****

*

* File: s2k14ini.ASM  BSP initialization code for the 'C54x DSKplus

* for use with 1403 in buffered mode

* BSPC and SPC are the same in the 'C542

* BSPCE and SPCE seem the same in the 'C542

*****

.title "Buffered Serial Port Initialization Routine"

ON     .set 1

OFF    .set !ON

YES    .set 1

NO     .set !YES

BIT_8  .set 2

BIT_10 .set 1

BIT_12 .set 3

BIT_16 .set 0

GO     .set 0x80

*****

* This is an example of how to initialize the Buffered Serial Port (BSP).

* The BSP is initialized to require an external CLK and FSX for

* operation. The data format is 16-bits, burst mode, with autobuffering

* enabled.

*

```

# LTC1403-1/LTC1403A-1

## アプリケーション情報

## 改訂履歴

| REV | 日付   | 修正内容                       | 頁番号 |

|-----|------|----------------------------|-----|

| A   | 1/10 | 「ピン配置」を改訂                  | 2   |

| B   | 6/10 | 「発注情報」セクションの製品マーキングを入れ替え修正 | 2   |

| C   | 6/12 | 出力コードを自然バイナリから2の補数に修正      | 13  |

14031fc

# LTC1403-1/LTC1403A-1

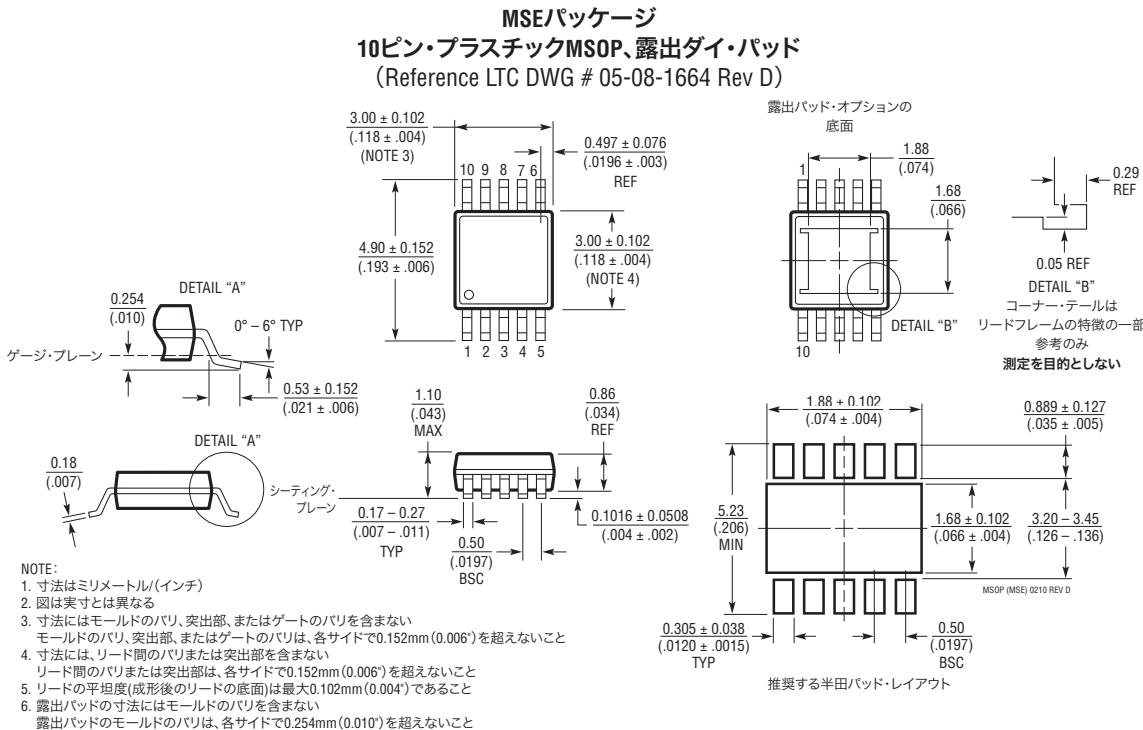

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/design-tools/packaging/>をご覧ください。

## 関連製品

| 製品番号                    | 説明                                       | 注釈                                |

|-------------------------|------------------------------------------|-----------------------------------|

| <b>ADC</b>              |                                          |                                   |

| LTC1608                 | 16ビット、500kspsパラレルADC                     | ±5V電源、入力範囲: ±2.5V、SINAD: 90dB     |

| LTC1604                 | 16ビット、333kspsパラレルADC                     | ±5V電源、入力範囲: ±2.5V、SINAD: 90dB     |

| LTC1609                 | 16ビット、200kspsシリアルADC                     | 5V、設定可能なバイポーラ/ユニポーラ入力             |

| LTC1411                 | 14ビット、2.5MspsパラレルADC                     | 5V、選択可能な入力範囲、SINAD: 80dB          |

| LTC1414                 | 14ビット、2.2MspsパラレルADC                     | ±5V電源、入力範囲: ±2.5V、SINAD: 78dB     |

| LTC1403/LTC1403A        | 12/14ビット、2.8MspsシリアルADC                  | 3V、14mW、ユニポーラ入力、MSOPパッケージ         |

| LTC1407/LTC1407A        | 12/14ビット、3Msps同時サンプリングADC                | 3V、2チャネル差動、ユニポーラ入力、14mW、MSOPパッケージ |

| LTC1407-1/LTC1407A-1    | 12/14ビット、3Msps同時サンプリングADC                | 3V、2チャネル差動、バイポーラ入力、14mW、MSOPパッケージ |

| LTC1420                 | 12ビット、10MspsパラレルADC                      | 5V、選択可能な入力範囲、SINAD: 71dB          |

| LTC1405                 | 12ビット、5MspsパラレルADC                       | 5V、選択可能な入力範囲、115mW                |

| LTC1412                 | 12ビット、3MspsパラレルADC                       | ±5V電源、入力範囲: ±2.5V、SINAD: 72dB     |

| LTC1402                 | 12ビット、2.2MspsシリアルADC                     | 5Vまたは±5V電源、入力範囲: 4.096Vまたは±2.048V |

| LTC1864/LTC1865         | 16ビット、250kspsシリアルADC                     | 5V電源、1チャネル/2チャネル、4.3mW、MSOPパッケージ  |

| <b>DAC</b>              |                                          |                                   |

| LTC1666/LTC1667/LTC1668 | 12/14/16ビット、50Msps DAC                   | SFDR: 87dB、セトリング時間: 20ns          |

| LTC1592                 | 16ビット、シリアルSoftSpan™ I <sub>OUT</sub> DAC | INL/DNL: ±1LSB、ソフトウェアで選択可能な出力範囲   |

| <b>リファレンス</b>           |                                          |                                   |

| LTC1790-2.5             | マイクロパワー・シリーズ・リファレンス、SOT-23パッケージ          | 初期精度: 0.05%、ドリフト: 10ppm           |

| LTC1461-2.5             | 高精度電圧リファレンス                              | 初期精度: 0.04%、ドリフト: 3ppm            |

| LTC1460-2.5             | マイクロパワー・シリーズ電圧リファレンス                     | 初期精度: 0.075%、ドリフト: 10ppm          |

14031fc