## 特長

- ソフトウェア選択可能な次のトランシーバをサポート:

RS232、RS449、EIA-530、EIA-530-A、V.35、V.36、X.21

- NE1およびNET2に適合

- LT1344を使用したソフトウェア選択可能なケーブル終端

- 4ドライバ/4レシーバ構成により完全な2チップDTEまたはDCEポートを形成

- 単一5V電源で動作

- 内部エコー・クロックおよびループバック・ロジック

## アプリケーション

- データ・ネットワーク

- CSUおよびDSU

- データ・ルータ

HTC、HTCはリニアテクノロジー社の登録商標です。

概要

LTC®1343は単一5V電源で動作する4ドライバ/4レシーバのマルチ・プロトコル・トランシーバです。2個のLTC1343により、RS232、RS449、EIA-530、EIA-530-A、V.35、V.36、またはX.21プロトコルをサポートする完全にソフトウェア選択可能なDTEまたはDCEインターフェース・ポートのコアを形成します。ケーブル終端は、LTC1344ソフトウェア・セレクタブル・ケーブル終端チップ、または既存のディスクリート設計を使用して実現できます。

LTC1343は内部チャージ・ポンプを使用した単一5V電源で動作し、5個の省スペース・タイプの表面実装コンデンサしか必要ありません。モード・ピンは内部でラッチされ、マルチプル・インターフェース・ポートでセレクト・ラインを共用することができます。

ソフトウェア選択可能なエコー・クロックやループバック・モードによって、シリアル・コントローラとライン・トランシーバ間に、無用な外付けロジックは不要です。LTC1343は、EMIシールドが簡素化されるフロースルー・アーキテクチャを採用し、44ピンSSOP表面実装パッケージで供給されます。

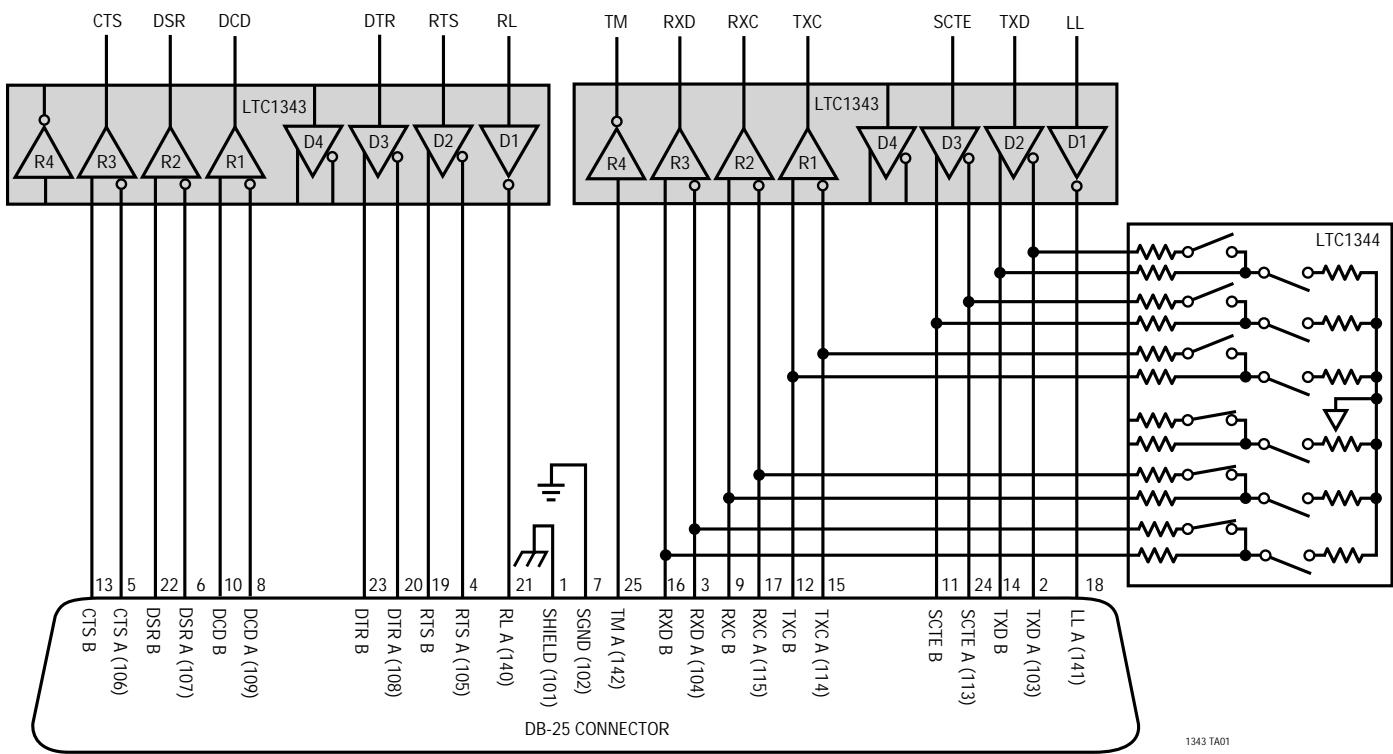

## 標準的應用例

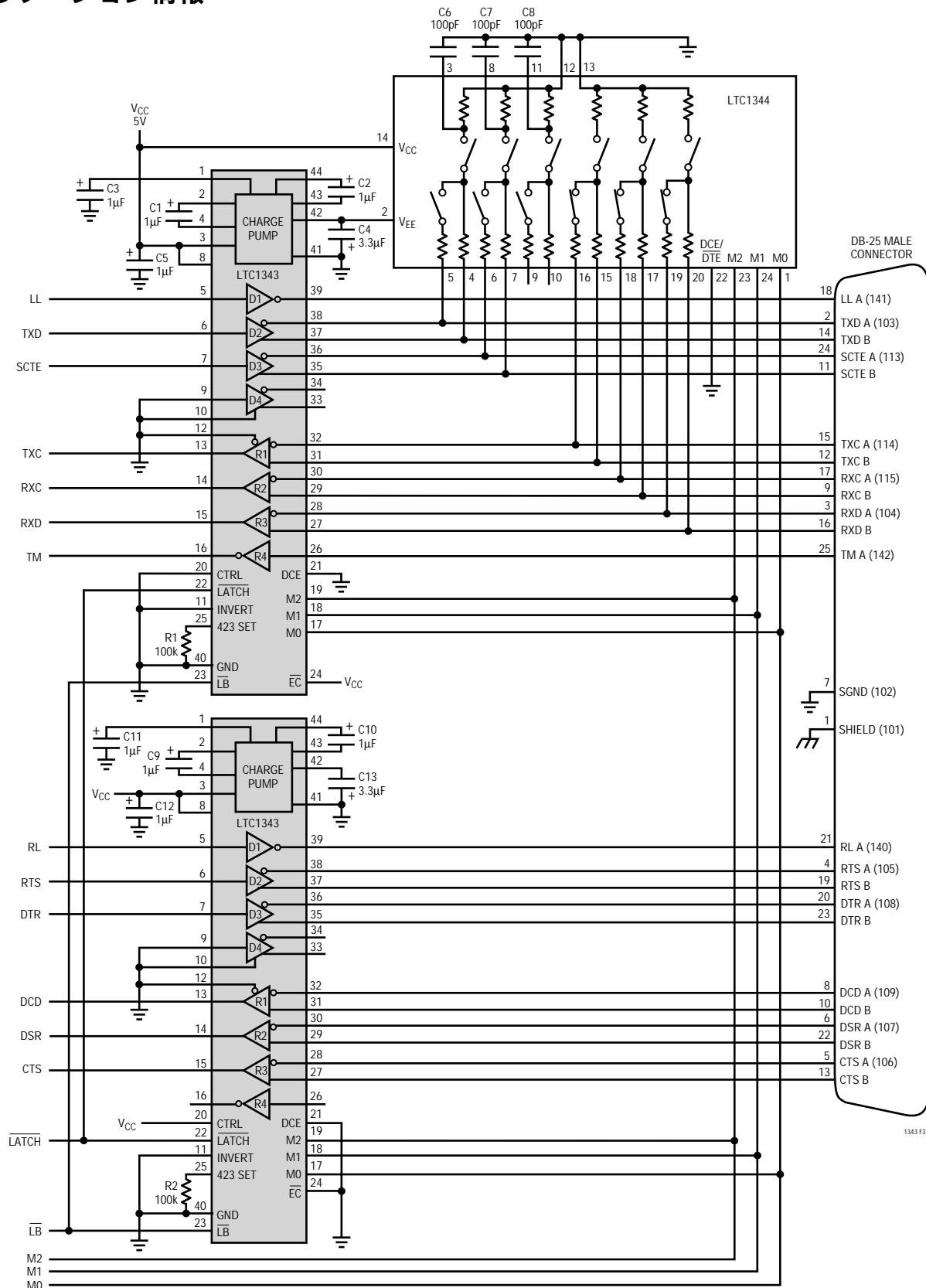

## DB-25コネクタ付きDTEマルチプロトコル・シリアル・インターフェース

**絶対最大定格**

(Note 1)

|                 |                                   |

|-----------------|-----------------------------------|

| 電源電圧            | ..... 6.5V                        |

| 入力電圧            |                                   |

| トランスマッタ         | - 0.3V ~ (V <sub>CC</sub> + 0.3V) |

| レシーバ            | - 25V ~ 25V                       |

| ロジック・ピン         | - 0.3V ~ (V <sub>CC</sub> + 0.3V) |

| 出力電圧            |                                   |

| トランスマッタ         | - 25V ~ 25V                       |

| レシーバ            | - 0.3V ~ (V <sub>CC</sub> + 0.3V) |

| ロジック・ピン         | - 0.3V ~ (V <sub>CC</sub> + 0.3V) |

| V <sub>EE</sub> | - 10V ~ 0.3V                      |

| V <sub>DD</sub> | - 0.3V ~ 10V                      |

| 短絡時間            |                                   |

| トランスマッタ出力       | 無限                                |

| レシーバ出力          | 無限                                |

| V <sub>EE</sub> | 30秒                               |

| 動作温度範囲          | 0 ~ 70                            |

| 保存温度範囲          | - 65 ~ 150                        |

| リード温度(半田付け、10秒) | 300                               |

**パッケージ/発注情報**

| TOP VIEW                                                                                                                                                                        | ORDER PART NUMBER |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| <br>GW PACKAGE<br>44-LEAD PLASTIC SSOP<br>T <sub>JMAX</sub> = 150°C, θ <sub>JA</sub> = 65°C/W | LTC1343CGW        |

インダストリアルおよびミリタリ・グレードに関してはお問い合わせください。

**電気的特性** V<sub>CC</sub> = 5V (Notes 2, 3)

| SYMBOL          | PARAMETER                                                                                | CONDITIONS                                                                                                                                                                                                                              | MIN                                            | TYP                                                    | MAX                                                                          | UNITS |

|-----------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------|-------|

| <b>Supplies</b> |                                                                                          |                                                                                                                                                                                                                                         |                                                |                                                        |                                                                              |       |

| I <sub>CC</sub> | V <sub>CC</sub> Supply Current (DCE Mode,<br>All Digital Pins = GND or V <sub>CC</sub> ) | V.10 Mode, No Load<br>V.10 Mode, Full Load<br>RS530, RS530-A, X.21 Modes, No Load<br>RS530, RS530-A, X.21 Modes, Full Load<br>V.35 Mode, No Load<br>V.35 Mode, Full Load<br>V.28 Mode, No Load<br>V.28 Mode, Full Load<br>No-Cable Mode | ●<br><br>●<br><br>●<br><br>●<br><br>●<br><br>● | 12<br>80<br>80<br>160<br>20<br>115<br>20<br>30<br>0.05 | 120<br>190<br>140<br>60<br>1<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA | mA    |

| P <sub>D</sub>  | Internal Power Dissipation (DCE Mode,<br>All Digital Pins = GND or V <sub>CC</sub> )     | V.10 Mode, Full Load<br>RS530, RS530-A, X.21 Modes, Full Load<br>V.35 Mode, Full Load<br>V.28 Mode, Full Load                                                                                                                           |                                                | 400<br>680<br>500<br>150                               |                                                                              | mW    |

| V <sup>+</sup>  | Positive Charge Pump Output Voltage                                                      | Any Mode, No Load<br>V.28 Mode, with Load                                                                                                                                                                                               | ●<br>●                                         | 8.5<br>8.0                                             | 9.1<br>7.0                                                                   | V     |

| V <sup>-</sup>  | Negative Charge Pump Output Voltage                                                      | V.28 Mode, Full Load<br>V.35 Mode, Full Load<br>V.10, RS530, RS530-A, X.21 Modes, Full Load<br>RS530, RS530-A, X.21 Modes, Full Load                                                                                                    | ●<br>●<br>●<br>●                               | -7.8<br>-5.8<br>-5.0<br>-5.0                           | -8.4<br>-6.7<br>-6.1<br>-6.1                                                 | V     |

| t <sub>r</sub>  | Supply Rise Time                                                                         | No-Cable Mode or Power-Up to Turn On                                                                                                                                                                                                    |                                                | 2                                                      |                                                                              | ms    |

電気的特性  $V_{CC} = 5V$  (Notes 2、3)

| SYMBOL                          | PARAMETER                                          | CONDITIONS                                                                   | MIN    | TYP        | MAX            | UNITS      |           |

|---------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|--------|------------|----------------|------------|-----------|

| <b>Logic Inputs and Outputs</b> |                                                    |                                                                              |        |            |                |            |           |

| $V_{IH}$                        | Logic Input High Voltage                           |                                                                              | ●      | 2          |                | V          |           |

| $V_{IL}$                        | Logic Input Low Voltage                            |                                                                              | ●      |            | 0.8            | V          |           |

| $I_{IN}$                        | Logic Input Current                                |                                                                              | ●      |            | $\pm 10$       | $\mu A$    |           |

| $V_{OH}$                        | Output High Voltage                                | $I_O = -4mA$                                                                 | ●      | 3          | 4.5            | V          |           |

| $V_{OL}$                        | Output Low Voltage                                 | $I_O = 4mA$                                                                  | ●      |            | 0.3            | 0.8        | V         |

| $I_{OSR}$                       | Output Short-Circuit Current                       | $0V \leq V_O \leq V_{CC}$                                                    | ●      | -60        | 60             | mA         |           |

| $I_{OZR}$                       | Three-State Output Current                         | $M0 = M1 = M2 = V_{CC}, 0V \leq V_O \leq V_{CC}$                             |        |            | $\pm 1$        | $\mu A$    |           |

| <b>V.11 Driver</b>              |                                                    |                                                                              |        |            |                |            |           |

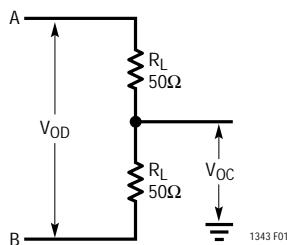

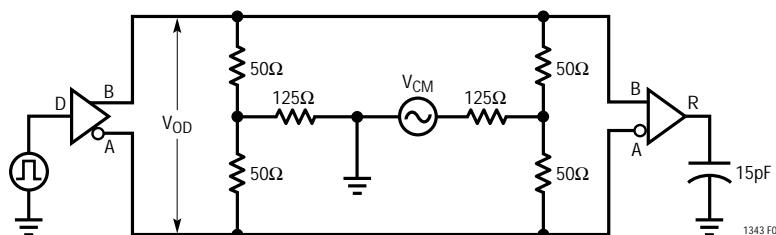

| $V_{OD}$                        | Differential Output Voltage                        | Open Circuit<br>$R_L = 50\Omega$ (Figure 1)                                  | ●<br>● |            | 6.0<br>$\pm 2$ | V          |           |

| $\Delta V_{OD}$                 | Change in Magnitude of Differential Output Voltage | $R_L = 50\Omega$ (Figure 1)                                                  | ●      |            | 0.2            | V          |           |

| $V_{OC}$                        | Common Mode Output Voltage                         | $R_L = 50\Omega$ (Figure 1)                                                  | ●      |            | 3.0            | V          |           |

| $\Delta V_{OC}$                 | Change in Magnitude of Common Mode Output Voltage  | $R_L = 50\Omega$ (Figure 1)                                                  | ●      |            | 0.2            | V          |           |

| $I_{SS}$                        | Short-Circuit Current                              | $V_O = GND$                                                                  | ●      |            | $\pm 150$      | mA         |           |

| $I_{OZ}$                        | Output Leakage Current                             | $-0.25V \leq V_O \leq 0.25V$ , Power Off or No-Cable Mode or Driver Disabled | ●      |            | $\pm 0.01$     | $\pm 100$  | $\mu A$   |

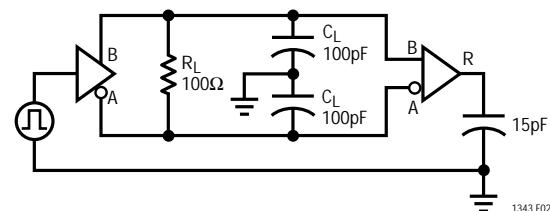

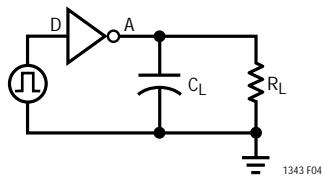

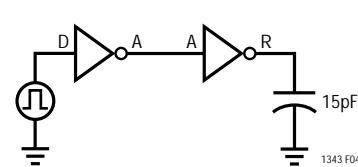

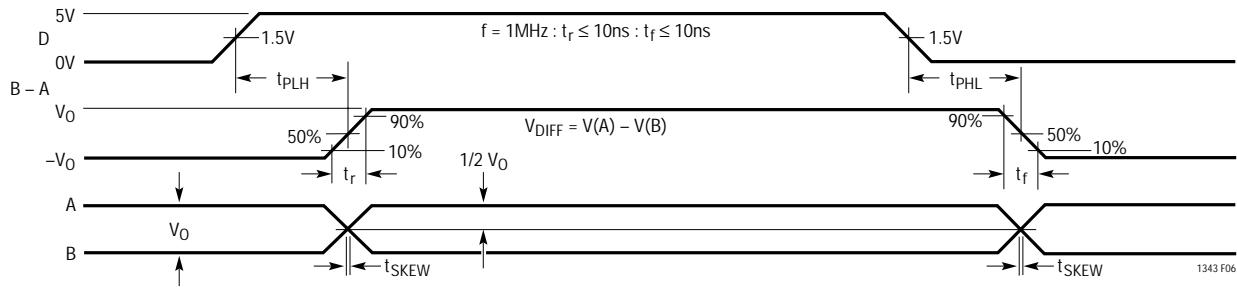

| $t_r, t_f$                      | Rise or Fall Time                                  | (Figures 2, 6)                                                               | ●      | 4          | 13             | 25         | ns        |

| $t_{PLH}$                       | Input to Output                                    | (Figures 2, 6)                                                               | ●      | 35         | 55             | 80         | ns        |

| $t_{PHL}$                       | Input to Output                                    | (Figures 2, 6)                                                               | ●      | 35         | 55             | 80         | ns        |

| $\Delta t$                      | Input to Output Difference, $ t_{PLH} - t_{PHL} $  | (Figures 2, 6)                                                               | ●      | 0          | 3              | 12         | ns        |

| $t_{SKEW}$                      | Output to Output Skew                              | (Figures 2, 6)                                                               |        |            | 3              |            | ns        |

| <b>V.11 Receiver</b>            |                                                    |                                                                              |        |            |                |            |           |

| $V_{TH}$                        | Input Threshold Voltage                            | $-7V \leq V_{CM} \leq 7V$                                                    | ●      | -0.2       | 0.2            | V          |           |

| $\Delta V_{TH}$                 | Input Hysteresis                                   | $-7V \leq V_{CM} \leq 7V$                                                    | ●      |            | 15             | 40         | mV        |

| $I_{IN}$                        | Input Current (A, B)                               | $-10V \leq V_A, B \leq 10V$                                                  | ●      |            |                | $\pm 0.50$ | mA        |

| $R_{IN}$                        | Input Impedance                                    | $-10V \leq V_A, B \leq 10V$                                                  | ●      | 20         | 32             |            | $k\Omega$ |

| $t_r, t_f$                      | Rise or Fall Time                                  | (Figures 2, 7)                                                               |        |            | 15             |            | ns        |

| $t_{PLH}$                       | Input to Output                                    | (Figures 2, 7), CTRL = GND<br>CTRL = $V_{CC}$                                | ●      | 50         | 80             | 115        | ns        |

|                                 |                                                    |                                                                              |        |            |                | 400        | ns        |

| $t_{PHL}$                       | Input to Output                                    | (Figures 2, 7), CTRL = GND<br>CTRL = $V_{CC}$                                | ●      | 50         | 80             | 115        | ns        |

|                                 |                                                    |                                                                              |        |            |                | 400        | ns        |

| $\Delta t$                      | Input to Output Difference, $ t_{PLH} - t_{PHL} $  | (Figures 2, 7)                                                               | ●      | 0          | 5              | 12         | ns        |

| <b>V.35 Driver</b>              |                                                    |                                                                              |        |            |                |            |           |

| $V_{OD}$                        | Differential Output Voltage                        | Open Circuit<br>With Load, $-4.0V \leq V_{CM} = 4.0V$ (Figure 3)             | ●      | $\pm 0.44$ | $\pm 0.55$     | $\pm 0.66$ | V         |

| $I_{OH}$                        | Transmitter Output High Current                    | $V_A, B = 0V$                                                                | ●      | -12.6      | -11            | -9.4       | mA        |

| $I_{OL}$                        | Transmitter Output Low Current                     | $V_A, B = 0V$                                                                | ●      | 9.4        | 11             | 12.6       | mA        |

| $I_{OZ}$                        | Transmitter Output Leakage Current                 | $-0.25V \leq V_A, B \leq 0.25V$                                              | ●      |            | $\pm 0.01$     | $\pm 100$  | $\mu A$   |

## 電気的特性 $V_{CC} = 5V$ (Notes 2, 3)

| SYMBOL     | PARAMETER                                         | CONDITIONS     | MIN | TYP | MAX | UNITS |

|------------|---------------------------------------------------|----------------|-----|-----|-----|-------|

| $t_r, t_f$ | Rise or Fall Time                                 | (Figures 3, 6) |     |     | 5   | ns    |

| $t_{PLH}$  | Input to Output                                   | (Figures 3, 6) | ●   | 25  | 45  | 75    |

| $t_{PHL}$  | Input to Output                                   | (Figures 3, 6) | ●   | 25  | 45  | 75    |

| $\Delta t$ | Input to Output Difference, $ t_{PLH} - t_{PHL} $ | (Figures 3, 6) | ●   | 0   | 5   | 12    |

| $t_{SKew}$ | Output to Output Skew                             | (Figures 3, 6) |     |     | 4   | ns    |

### V.35 Receiver

|                 |                                                   |                                             |   |      |            |    |

|-----------------|---------------------------------------------------|---------------------------------------------|---|------|------------|----|

| $V_{TH}$        | Differential Receiver Input Threshold Voltage     | $-2V \leq (V_A + V_B)/2 \leq 2V$ (Figure 3) | ● | -0.2 | 0.2        | V  |

| $\Delta V_{TH}$ | Receiver Input Hysteresis                         | $-2V \leq (V_A + V_B)/2 \leq 2V$ (Figure 3) | ● | 11   | 40         | mV |

| $I_{IN}$        | Receiver Input Current (A, B)                     | $-10V \leq V_A, B \leq 10V$                 | ● |      | $\pm 0.50$ | mA |

| $R_{IN}$        | Receiver Input Impedance                          | $-10V \leq V_A, B \leq 10V$                 | ● | 20   | 32         | kΩ |

| $t_r, t_f$      | Rise or Fall Time                                 | (Figures 3, 7)                              |   |      | 15         | ns |

| $t_{PLH}$       | Input to Output                                   | (Figures 3, 7)                              | ● | 80   | 115        | ns |

| $t_{PHL}$       | Input to Output                                   | (Figures 3, 7)                              | ● | 100  | 115        | ns |

| $\Delta t$      | Input to Output Difference, $ t_{PLH} - t_{PHL} $ | (Figures 3, 7)                              | ● | 4    | 12         | ns |

### V.10 Driver

|            |                        |                                                                                 |   |           |           |    |

|------------|------------------------|---------------------------------------------------------------------------------|---|-----------|-----------|----|

| $V_0$      | Output Voltage         | Open Circuit, $R_L = 3.9k$<br>$R_L = 450\Omega$ (Figure 4)                      |   | $\pm 4.0$ | $\pm 6.0$ | V  |

|            |                        |                                                                                 |   | $\pm 3.6$ |           | V  |

| $I_{SS}$   | Short-Circuit Current  | $V_0 = GND$                                                                     | ● |           | $\pm 150$ | mA |

| $I_{OZ}$   | Output Leakage Current | $-0.25V \leq V_0 \leq 0.25V$ , Power Off or<br>No-Cable Mode or Driver Disabled | ● | $\pm 0.1$ | $\pm 100$ | μA |

| $t_r, t_f$ | Rise or Fall Time      | (Figures 4, 8), $R_L = 450\Omega$ , $C_L = 100pF$<br>$R_{423SET} = 100k$        |   |           | 4         | μs |

| $t_{PLH}$  | Input to Output        | (Figures 4, 8), $R_L = 450\Omega$ , $C_L = 100pF$<br>$R_{423SET} = 100k$        |   |           | 8         | μs |

| $t_{PHL}$  | Input to Output        | (Figures 4, 8), $R_L = 450\Omega$ , $C_L = 100pF$<br>$R_{423SET} = 100k$        |   |           | 8         | μs |

5

### V.10 Receiver

|                 |                                  |                          |   |      |            |    |

|-----------------|----------------------------------|--------------------------|---|------|------------|----|

| $V_{TH}$        | Receiver Input Threshold Voltage |                          | ● | -0.2 | 0.2        | V  |

| $\Delta V_{TH}$ | Receiver Input Hysteresis        |                          | ● | 11   | 50         | mV |

| $I_{IN}$        | Receiver Input Current           | $-10V \leq V_A \leq 10V$ | ● |      | $\pm 0.50$ | mA |

| $R_{IN}$        | Receiver Input Impedance         | $-10V \leq V_A \leq 10V$ | ● | 20   | 30         | kΩ |

| $t_r, t_f$      | Rise or Fall Time                | (Figures 5, 9)           |   |      | 15         | ns |

| $t_{PLH}$       | Input to Output                  | (Figures 5, 9)           |   |      | 350        | ns |

| $t_{PHL}$       | Input to Output                  | (Figures 5, 9)           |   |      | 350        | ns |

## 電気的特性 $V_{CC} = 5V$ (Note 2、3)

| SYMBOL               | PARAMETER                    | CONDITIONS                                                                   | MIN | TYP        | MAX       | UNITS      |

|----------------------|------------------------------|------------------------------------------------------------------------------|-----|------------|-----------|------------|

| <b>V.28 Driver</b>   |                              |                                                                              |     |            |           |            |

| $V_0$                | Output Voltage               | Open Circuit<br>$R_L = 3k$ (Figure 4)                                        | ●   | $\pm 5$    | 7.6       | V          |

| $I_{SS}$             | Short-Circuit Current        | $V_0 = GND$                                                                  | ●   |            | $\pm 150$ | mA         |

| $I_{OZ}$             | Output Leakage Current       | $-0.25V \leq V_0 \leq 0.25V$ , Power Off or No-Cable Mode or Driver Disabled | ●   | $\pm 0.01$ | $\pm 100$ | $\mu A$    |

| SR                   | Slew Rate                    | (Figures 4, 8), $R_L = 3k$ , $C_L = 2500pF$                                  | ●   | 4.0        | 30.0      | V/ $\mu s$ |

| $t_{PLH}$            | Input to Output              | (Figures 4, 8), $R_L = 3k$ , $C_L = 2500pF$                                  | ●   |            | 1.6       | 2.5        |

| $t_{PHL}$            | Input to Output              | (Figures 4, 8), $R_L = 3k$ , $C_L = 2500pF$                                  | ●   |            | 1.6       | 2.5        |

| <b>V.28 Receiver</b> |                              |                                                                              |     |            |           |            |

| $V_{THL}$            | Input Low Threshold Voltage  |                                                                              | ●   | 1.4        | 0.8       | V          |

| $V_{TLH}$            | Input High Threshold Voltage |                                                                              | ●   | 2.0        | 1.4       | V          |

| $\Delta V_{TH}$      | Receiver Input Hysteresis    |                                                                              | ●   | 0.1        | 0.4       | 1.0        |

| $R_{IN}$             | Receiver Input Impedance     | $-15V \leq V_A \leq 15V$                                                     | ●   | 3          | 5         | 7          |

| $t_r, t_f$           | Rise or Fall Time            | (Figures 5, 9)                                                               |     |            | 15        | ns         |

| $t_{PLH}$            | Input to Output              | (Figures 5, 9), CTRL = 0V<br>CTRL = $V_{CC}$                                 | ●   |            | 110       | ns         |

| $t_{PHL}$            | Input to Output              | (Figures 5, 9), CTRL = 0V<br>CTRL = $V_{CC}$                                 | ●   |            | 330       | 800        |

|                      |                              |                                                                              | ●   |            | 170       | ns         |

|                      |                              |                                                                              | ●   |            | 480       | 800        |

|                      |                              |                                                                              |     |            |           | ns         |

は全動作温度範囲の規格値を意味する。

Note 1 : 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2 : デバイスのピンに流入する電流はすべて正。デバイスのピンから流出する電流はすべて負。注記がない限り、すべての電圧はデバイスのグランドを基準にしている。

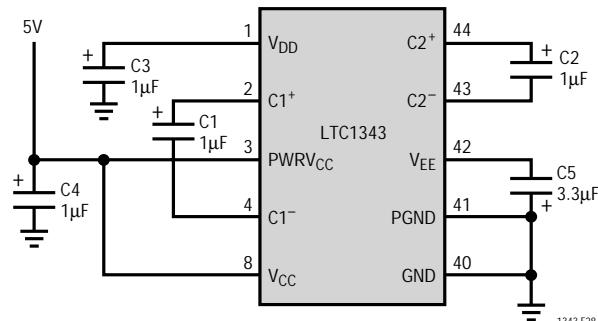

Note 3 : すべての標準値は、 $V_{CC} = 5V$ 、 $C1 = C2 = C_{VCC} = C_{VDD} = 1\mu F$ 、 $C_{VEE} = 3.3\mu F$  タンタル・コンデンサおよび  $T_A = 25^\circ C$ 。

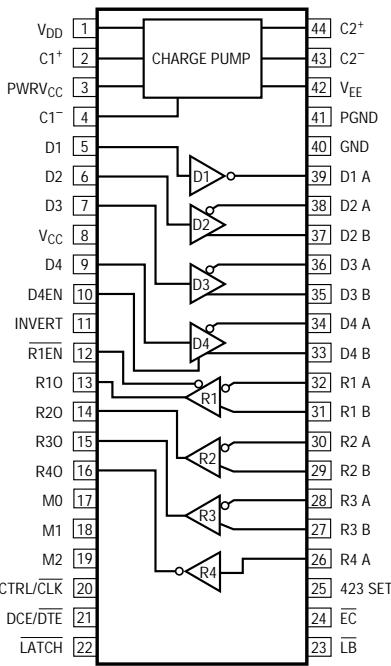

## ピン機能

$V_{DD}$ ( ピン1 ) : RS232用に生成された正電源電圧。このピンからグランドへ $1\mu F$ のコンデンサを接続します。

$C1^+$ ( ピン2 ) : コンデンサC1の正端子。 $C1^+$ と $C1^-$ 間に $1\mu F$ のコンデンサを接続します。

$PWRV_{CC}$ ( ピン3 ) : チャージ・ポンプ用正電源。 $4.75V \leq PWRV_{CC} \leq 5.25V$ 。 $V_{CC}$ ( ピン8 )に接続し、 $1\mu F$ コンデンサでグランドにバイパスします。

$C1^-$ ( Pin 4 ) : コンデンサC1の負端子。

$D1$ ( ピン5 ) : TTLレベル・ドライバ1入力。

$D2$ ( ピン6 ) : TTLレベル・ドライバ2入力

$D3$ ( ピン7 ) : TTLレベル・ドライバ3入力。チップがエコー・クロック・モード( $EC = 0V$ )の場合、CMOSレベル出力になります。

$V_{CD}$ ( ピン8 ) : トランシーバ用正電源。 $4.75V \leq V_{CC} \leq 5.25V$ 。 $PWRV_{CD}$ ( ピン3 )に接続します。

$D4$ ( ピン9 ) : TTLレベル・ドライバ4入力。

$D4EN$ ( ピン10 ) : ドライバ4用TTLレベル・イネーブル入力。“H”的とき、ドライバ4出力がイネーブルされます。“L”的とき、ドライバ4出力がハイ・インピーダンス状態になります。 $D4EN$ はLATCHピンに影響されません。

$INVERT$ ( ピン11 ) : TTLレベル信号反転入力。“H”的とき、ドライバ4およびレシーバ1信号バスに1個のインバータが追加されます。データ・ストリームは極性を変化させます。すなわち、1は0になり、0は1になります。ピンが“L”的とき、データは極性を変えずに流れます。 $INVERT$ はLATCHピンに影響されません。

## ピン機能

**R1EN( ピン12 )**: レシーバ1に対するロジック・レベル・イネーブル入力。“ L ”のとき、レシーバ1出力がイネーブルされます。“ H ”のとき、レシーバ1出力がハイ・インピーダンス状態になります。

**R1O( ピン13 )**: CMOSレベル・レシーバ1出力

**R2O( ピン14 )**: CMOSレベル・レシーバ2出力

**R3O( ピン15 )**: CMOSレベル・レシーバ3出力

**R4O( ピン16 )**: CMOSレベル・レシーバ4出力

**M0( ピン17 )**: TTLレベル・モード・セレクト入力0。M0のデータはLATCHが“ H ”のときにラッチされます。

**M1( ピン18 )**: TTLレベル・モード・セレクト入力1。M1のデータはLATCHが“ H ”のときにラッチされます。

**M2( ピン19 )**: TTLレベル・モード・セレクト入力2。M2のデータはLATCHが“ H ”のときにラッチされます。

**CTRL/CLK( ピン20 )**: TTLレベル・モード・セレクト入力。このピンが“ L ”のとき、チップはクロックおよびデータ信号用に構成されます。ピンが“ H ”のとき、チップは制御信号用に構成されます。LATCHが“ H ”のとき、CTRL/CLK上のデータがラッチされます。

**DCE/DTE( ピン21 )**: TTLレベル・モード・セレクト入力。“ H ”のときDCEモードが選択されます。“ L ”のときDTEモードが選択されます。DCE/DTEのデータはLATCHが“ H ”のときにラッチされます。

**LATCH( ピン22 )**: TTLレベル・ロジック信号ラッチ入力。“ L ”のとき、M0、M1、M2、CTRL/CLK、DCE/DTE、LB、およびECピンの入力バッファは簡易制御されます。LATCHが“ H ”にプルアップされると、ロジック・ピンのデータは各入力バッファにラッチされます。データ・ラッチによって、ロジック・ラインが複数のI/Oポートで共用されます。

**LB( ピン23 )**: TTLレベル・ループバック・セレクト入力。“ L ”のとき、チップはループバック構成になり、LBが“ H ”のときに通常動作に構成されます。LBのデータはLATCHが“ H ”のときにラッチされます。

**EQ( ピン24 )**: TTLレベル・エコー・クロック・セレクト入力。“ L ”のとき、LTC1343はエコー・クロック構成になり、EQが“ H ”のときに通常動作に構成されます。EQのデータはLATCHが“ H ”のときにラッチされます。

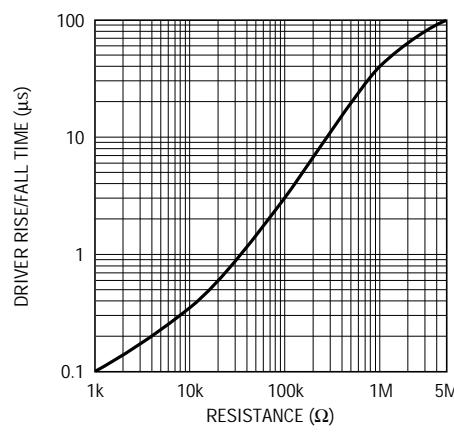

**423 SET( ピン25 )**: RS423ドライバ出力の立上りおよび立下り時間設定抵抗に対するアナログ入力ピン。このピンからグランドに抵抗を接続します。

**R4 A( ピン26 )**: レシーバ4反転入力。

**R3 B( ピン27 )**: レシーバ3非反転入力。

**R3 A( ピン28 )**: レシーバ3反転入力。

**R2 B( ピン29 )**: レシーバ2非反転入力。

**R2 A( ピン30 )**: レシーバ2反転入力。

**R1 B( ピン31 )**: レシーバ1非反転入力。

**R1 A( ピン32 )**: レシーバ1反転入力。

**D4 B( ピン33 )**: ドライバ4非反転出力。

**D4 A( ピン34 )**: ドライバ4反転出力。

**D3 B( ピン35 )**: ドライバ3非反転出力。

**D3 A( ピン36 )**: ドライバ3反転出力。

**D2 B( ピン37 )**: ドライバ2非反転出力。

**D2 A( ピン38 )**: ドライバ2反転出力。

**D1 A( ピン39 )**: ドライバ1反転出力。

**GND( ピン40 )**: 信号グランド。PGND( ピン41 )に接続します。

**PGND( ピン41 )**: チャージ・ポンプ電源グランド。SGND( ピン40 )に接続します。

**V<sub>EE</sub>( ピン42 )**: 生成される負電源電圧。3.3μFコンデンサをグランドに接続します。

**C2<sup>-</sup>( ピン43 )**: コンデンサC2の負端子。C2<sup>+</sup>とC2<sup>-</sup>の間に1μFのコンデンサを接続します。

**C2<sup>+</sup>( ピン44 )**: コンデンサC2の正端子。C2<sup>+</sup>とC2<sup>-</sup>の間に1μFのコンデンサを接続します。

# LTC1343

## テスト回路

図1. RS422 ドライバ・テスト回路

図2. RS422 ドライバ/レシーバACテスト回路

図3. V.35 ドライバ/レシーバ・テスト回路

図4. V.10/V.28 ドライバ・テスト回路

図5. V.10/V.28 レシーバ・テスト回路

## モード選択

| LTC1343 MODE NAME        | M2 | M1 | M0 | CTRL/CLK | D1   | D2   | D3   | D4   | R1   | R2   | R3   | R4   |

|--------------------------|----|----|----|----------|------|------|------|------|------|------|------|------|

| V.10, RS423              | 0  | 0  | 0  | X        | V.10 |

| EIA-530-A Clock and Data | 0  | 0  | 1  | 0        | V.10 | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 | V.10 |

| EIA-530-A Control        | 0  | 0  | 1  | 1        | V.10 | V.11 | V.10 | V.11 | V.11 | V.10 | V.11 | V.10 |

| Reserved                 | 0  | 1  | 0  | X        | V.10 | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 | V.10 |

| X.21                     | 0  | 1  | 1  | X        | V.10 | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 | V.10 |

| V.35 Clock and Data      | 1  | 0  | 0  | 0        | V.28 | V.35 | V.35 | V.35 | V.35 | V.35 | V.35 | V.28 |

| V.35 Control             | 1  | 0  | 0  | 1        | V.28 |

| EIA-530, RS449, V.36     | 1  | 0  | 1  | X        | V.10 | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 | V.10 |

| V.28, RS232              | 1  | 1  | 0  | X        | V.28 |

| No Cable                 | 1  | 1  | 1  | X        | Z    | Z    | Z    | Z    | Z    | Z    | Z    | Z    |

## スイッチング時間波形

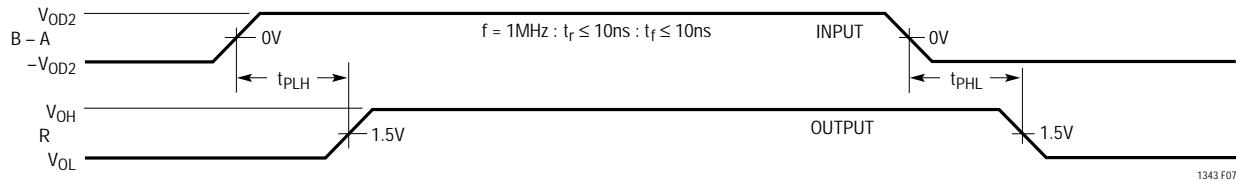

図6. V.11、V.35 ドライバ伝搬遅延

図7. V.11、V.35 レシーバ伝搬遅延

5

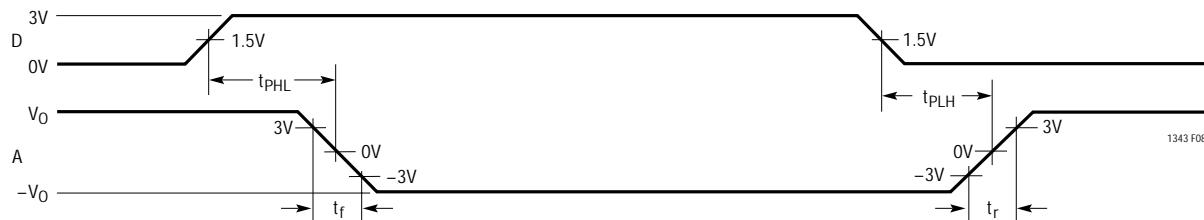

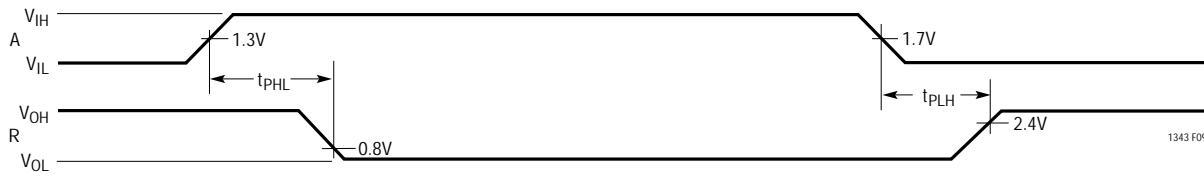

図8. V.10、V.28 ドライバ伝搬遅延

図9. V.10、V.28 レシーバ伝搬遅延

## アプリケーション情報

### 概要

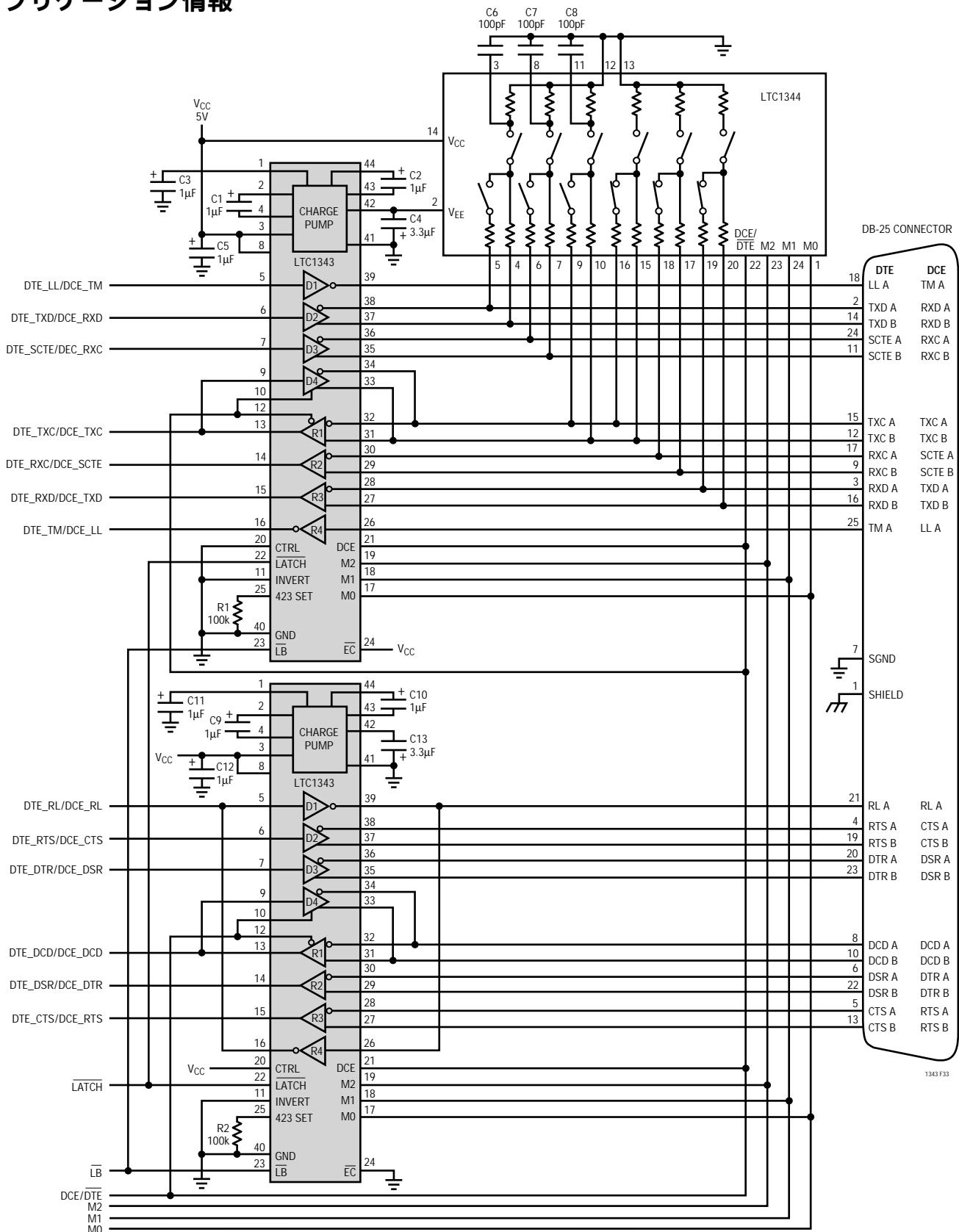

LTC1343は単一5V電源で動作する4ドライバ/4レシーバのマルチ・プロトコル・トランシーバです。2個のLTC1343により、RS232、RS449、EIA-530、EIA-530-A、V.35、V.36、またはX.21プロトコルをサポートする完全にソフトウェア選択可能なDTEまたはDCEインターフェース・ポートのコアを形成します。ケーブル終端は、LTC1344ソフトウェ

ア・セレクタブル・ケーブル終端チップ、または既存のディスクリート設計を使用して実現できます。

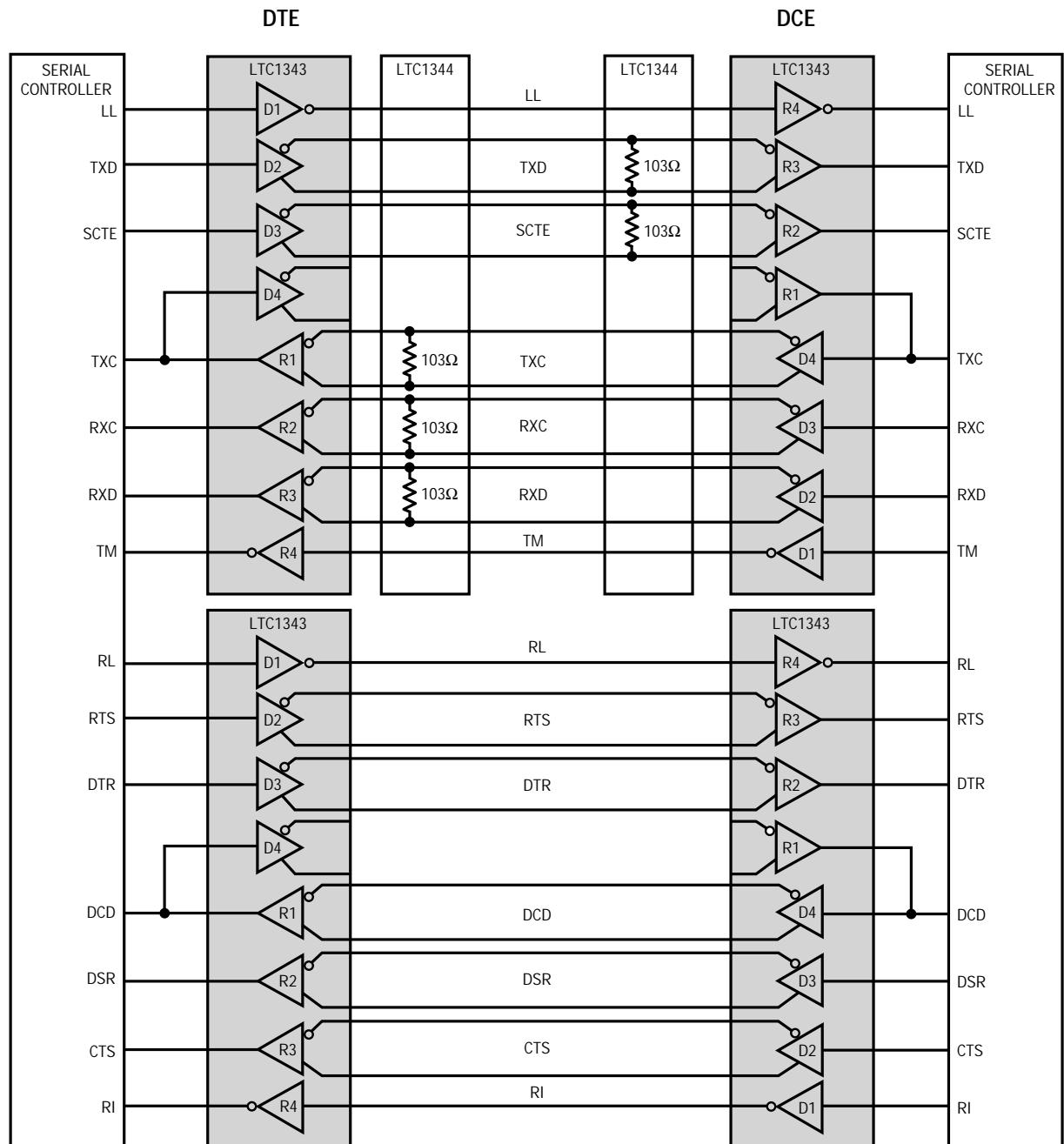

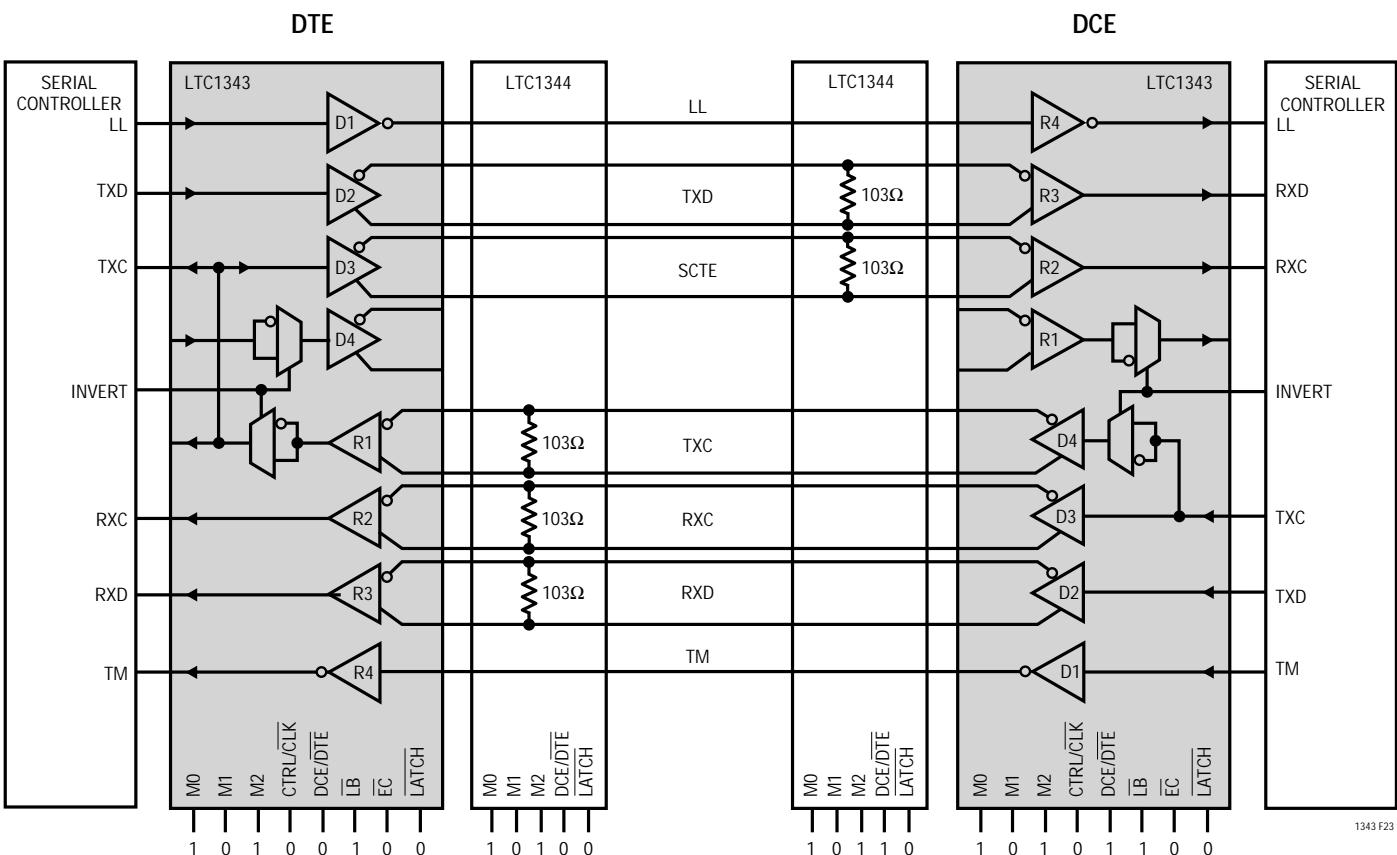

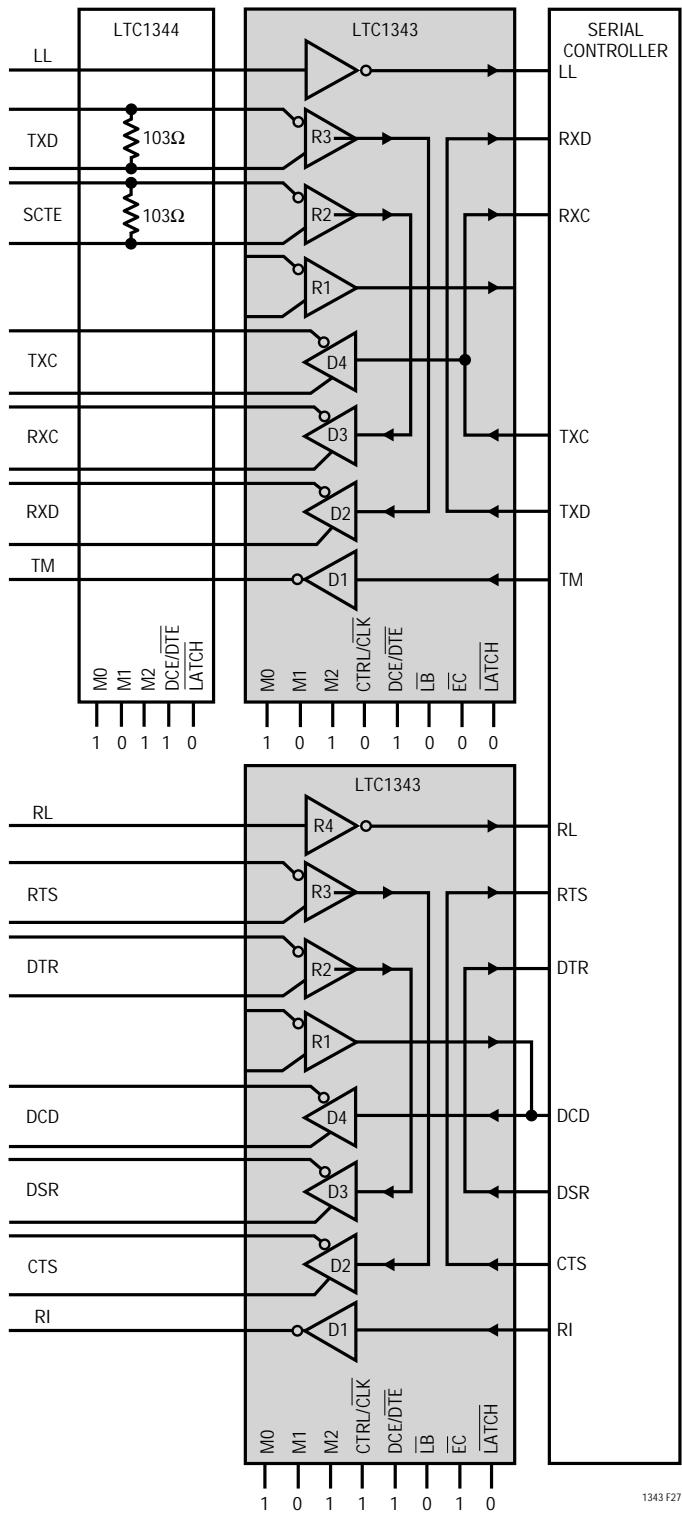

EIA-530モードで動作する完全なDCE対DTEインターフェースを図10に示します。各ポートの第一のLTC1343を使用して、LL(ローカル・ループバック)およびTM(テスト・モード)をサポートするとともに、クロックおよびデータ信号を生成します。2番目のLTC1343を使用して、RL(リモート・ルー

図10. EIA-530モードの完全なマルチプロトコル・インターフェース

## アプリケーション情報

パック)やRX(リング表示)そして制御信号を生成します。LTC1344ケーブル終端チップは、V.35ケーブル終端をサポートしなければならないため、クロックとデータ信号用にのみ使用します。制御信号には外付け抵抗は不要です。

### モード選択

インターフェース・プロトコルはモード・セレクト・ピンM0、M1、M2、およびCTRL/CLKを使用して選択されます(モード選択テーブルを参照)。CTRL/CLKピンはLTC1343を使用して制御信号を生成する場合は、“H”にプルアップし、クロックおよびデータ信号を生成する場合は“L”にプルダウンしなければなりません。

たとえば、ポートがV.35インターフェースとして構成される場合、モード選択ピンはM2 = 1、M1 = 0、M0 = 0でなければなりません。制御信号の場合、CTRL/CLK = 1であり、ドライバとレシーバはRS232C( V.28 )電気的モードで動作します。クロックおよびデータ信号の場合、CTRL/CLK = 0であり、ドライバとレシーバはRS232C( V.28 )電気的モードで動作するシングル・エンディッド・ドライバおよびレシーバを除いて、V.35電気的モードで動作します。DCE/DTEピンは“H”的ときは、DCEモード

ド、まだ“L”的ときにはDTEに対してポートを構成します。

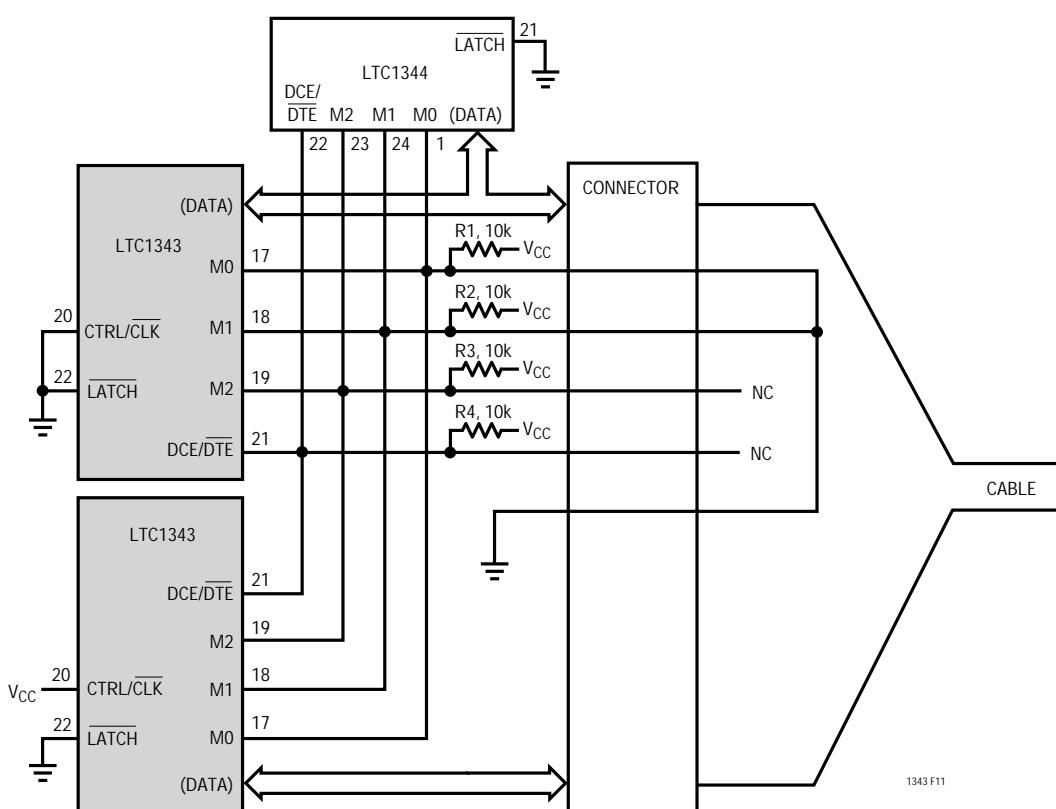

インターフェース・プロトコルは適切なインターフェース・ケーブルをコネクタに差し込むだけで選択できます。モード・ピンは図11に示すようにコネクタに配線され、コネクタからは接続されないか(1)あるいはケーブルのグランドに配線されます(0)。

プルアップ抵抗R1~R4はピンが接続されないときはバイナリの1を保証し、2個のLTC1343とLTC1344はケーブルが取り外されるとノーケーブル・モードに入ります。ノーケーブル・モードでは、LTC1343の電源電流は200 $\mu$ A以下に低下し、すべてのLTC1343ドライバ出力とLTC1344抵抗終端はハイインピーダンス状態になります。データ・ラッチ・ピンLATCHは、すべてのチップでグランドに短絡されることに注意してください。

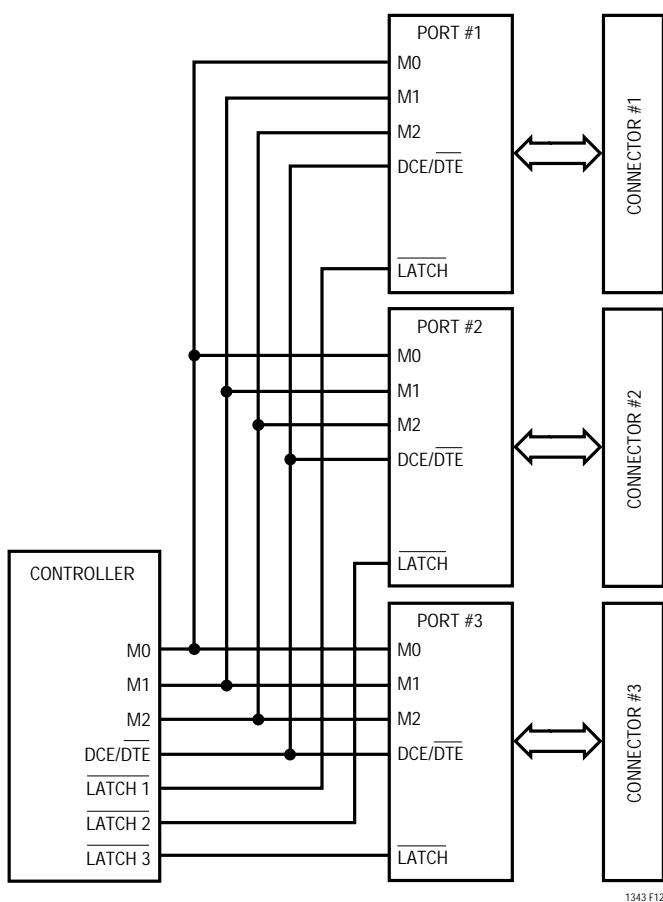

インターフェース・プロトコルは図12に示すとおり、シリアル・コントローラまたはホスト・マイクロプロセッサでも選択できます。

モード・セレクト・ピンM0、M1、M2、およびDCE/DTEは複数のインターフェース・ポート間で共用することができ、各

図11：ケーブルでのシングル・ポートDCE/V.35モード選択

## アプリケーション情報

図12：コントローラによるモード選択

ポートはライト・イネーブルとして機能する独自のデータ・ラッチ信号を持っています。LATCHピンが“L”のとき、M0、M1、M2、CTRL/CLK、DCE/DTE、LB、およびECピンのバッファは簡易制御されます。LATCHピンを“H”にすると、バッファはデータをラッチするため、入力ピンが変化してもチップには影響ありません。

モード選択は、ジャンパを使用してモード・ピンをグランドまたは $V_{CC}$ に接続しても行うことができます。

## ケーブル終端

従来の方法は、高価なリレー付きスイッチング抵抗を用いたり、インターフェース規格が変更されるたびにユーザに終端モジュールを変更させることなどでした。ケーブル・ヘッドに終端を備えたカスタム・ケーブルを使用するか、ボード上に別々の終端が実装され、カスタム・ケーブルが信号を適切な終端に配線します。信号電圧がFETドライバの電源電圧を超えるか、あるいは電源がオフにな

った場合でも、FETがオフ状態を保持しなければならないため、FETによる終端の切替えは困難です。

LTC1343に伴ってLTC1344を使用すれば、ケーブル終端の切替え問題を解決できます。ソフトウェア・コントロールによって、LTC1344はV.10( RS423 )、V.11( RS422 )、V.28( RS232 )、およびV.35電気的プロトコルに対応する終端を提供します。

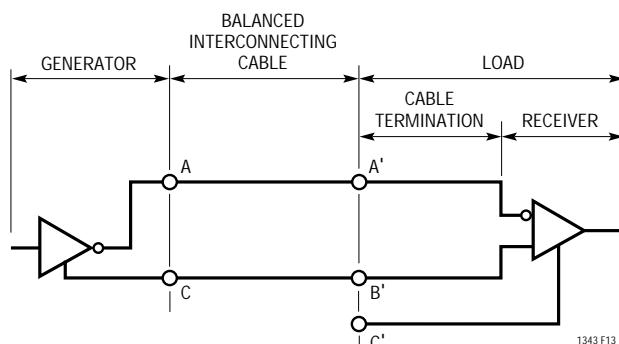

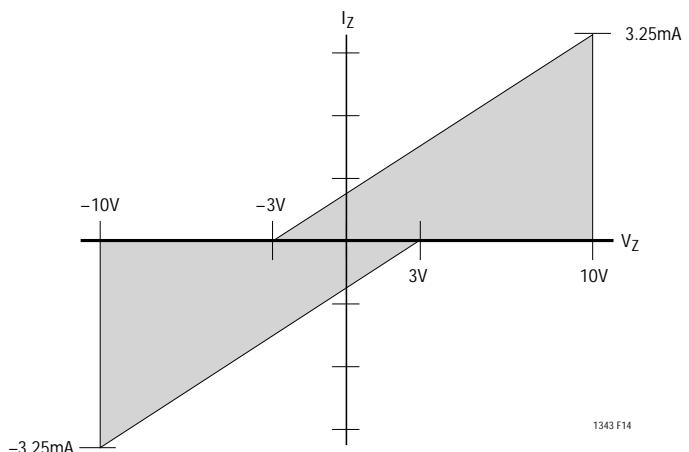

## V.10( RS423 )インターフェース

標準V.10不平衡型インターフェースを図13に示します。グランドCを備えたV.10シングル・エンデッド・ジェネレータ出力Aは、差動レシーバに接続され、入力A'はAに、また入力B'は信号リターン・グランドCに接続されます。レシーバのグランドC'は信号リターンから分離しています。通常V.10インターフェースにはケーブル終端は必要ありませんが、レシーバ入力は図14のインピーダンス曲線に従わなければなりません。

図13. 標準V.10インターフェース

図14. V.10 レシーバ入力インピーダンス

## アプリケーション情報

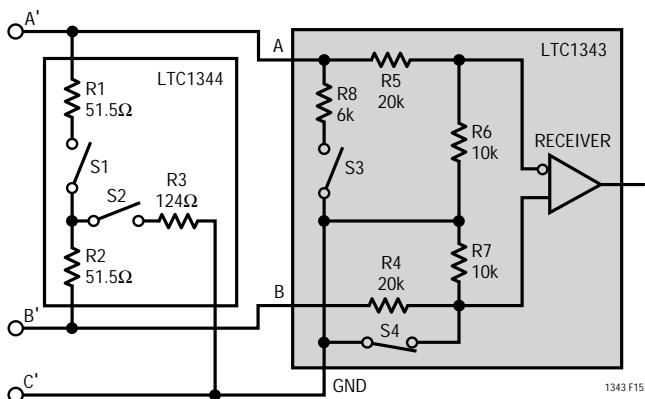

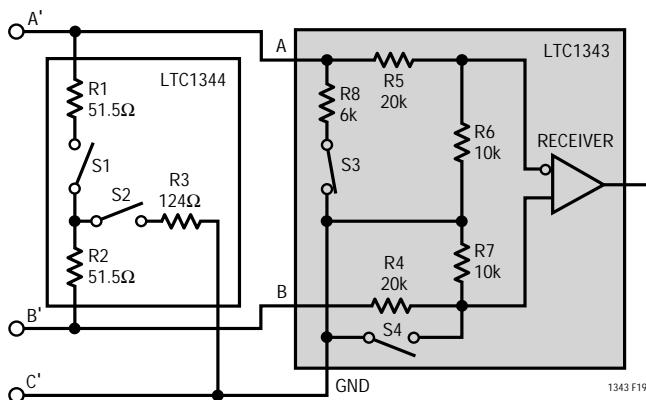

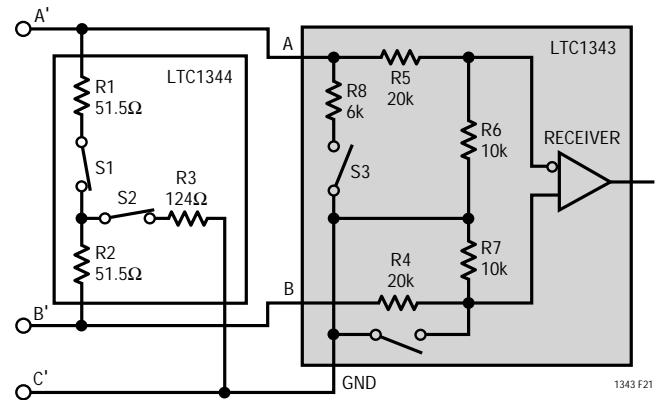

LTC1343とLTC1344を使用したV.10レシーバ構成を図15に示します。V.10モードでは、LTC1344内のスイッチS1とS2、およびLTC1343内のスイッチS3がターンオフします。LTC1343内のスイッチS4は非反転レシーバ入力をグランドに短絡するため、コネクタのB入力はフロートさせておくことができます。したがって、ケーブル終端はLTC1343のV.10レシーバのグランドに対して、30kの入力インピーダンスになります。

### V.11( RS422 )インターフェース

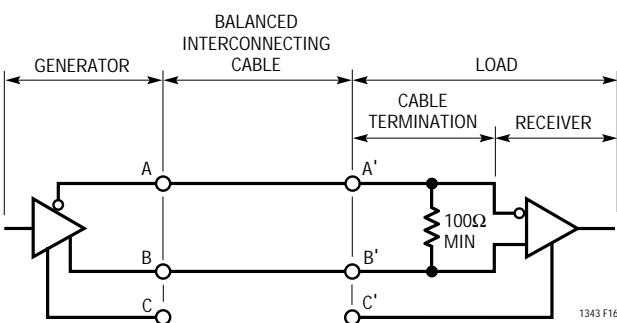

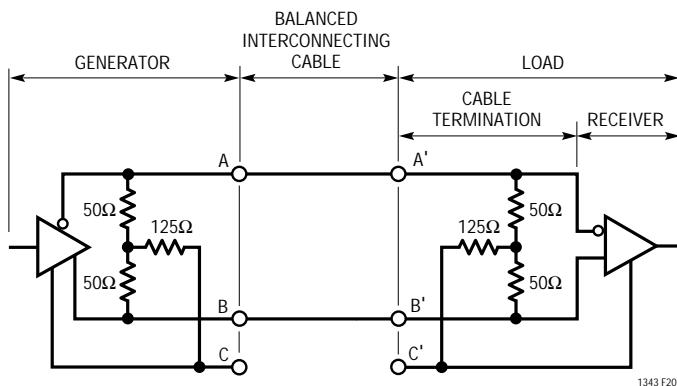

標準V.11平衡型インターフェースを図16に示します。出力AおよびBそしてグランドCを備えたV.11差動ジェネレータは、グランドC'を備えた差動レシーバに接続され、入力A'はAに、またB'はBに接続されます。V.11インターフェースはレシーバ・エンドで最小100Ωの抵抗で差動終端されます。終端抵抗はV.11仕様ではオプションですが、高速クロックおよびデータ・ラインに対しては、反射によってデータが破壊されるのを防止するために終端が必要です。レシーバ入力も図14に示すインピーダンス曲線に従わなければなりません。

図15. V.10レシーバ構成

5

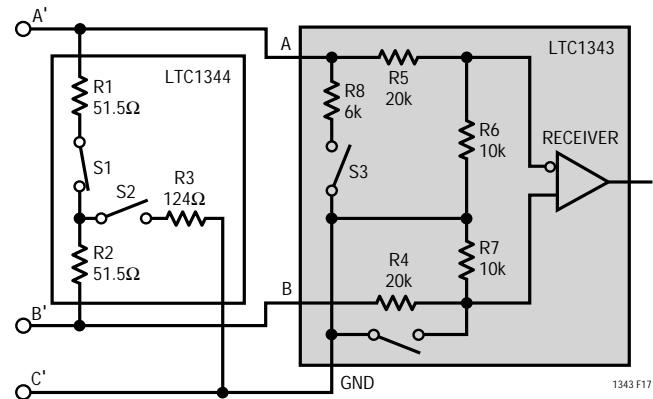

V.11モードでは図17に示すとおり、103Ω差動終端インピーダンスをケーブルに接続するLTC1344内のS1を除く、すべてのスイッチがオフになります。

### V.28( RS232 )インターフェース

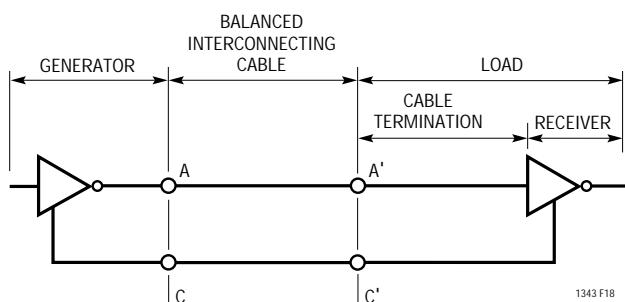

標準V.28不平衡型インターフェースを図18に示します。グランドCを備えたV.28シングル・エンデッド・ジェネレータ出力Aは、シングル・エンデッド・レシーバに接続され、入力A'はAに、またグランドC'は信号リターン・グランドを通してCに接続されます。

V.28モードでは図19に示すとおり、LTC1343内のS3を除くすべてのスイッチがオフになり、6kΩ( R5 )インピーダンスを20kΩ( R5 )+10kΩ( R6 )と並列にしてグランドに接続し、5kの合成インピーダンスを実現しています。非反転入力はLTC1343レシーバ内で切断され、1.4Vレシーバ・トリップ・ポイントに対するTTLレベルのリファレンス電圧に接続されます。

図17. V.11レシーバ構成

図16. 標準V.11インターフェース

図18. 標準V.28インターフェース

## アプリケーション情報

図19. V.28レシーバ構成

図21. V.35レシーバ構成

### V.35インターフェース

標準V.35平衡型インターフェースを図20に示します。出力AおよびB、そしてグランドCを備えたV.35差動ジェネレータが、グランドC'を備えた差動レシーバに接続され、入力A'はAに、また入力B'はBに接続されます。V.35インターフェースにはレシーバ・エンドとジェネレータ・エンドに、Tまたはデルタ・ネットワーク終端が必要です。コネクタで測定される差動インピーダンスは、 $100 \pm 10$  でなければならず、短絡した端子(A'およびB')とグランドC'間のインピーダンスは $150 \pm 15$  でなければなりません。

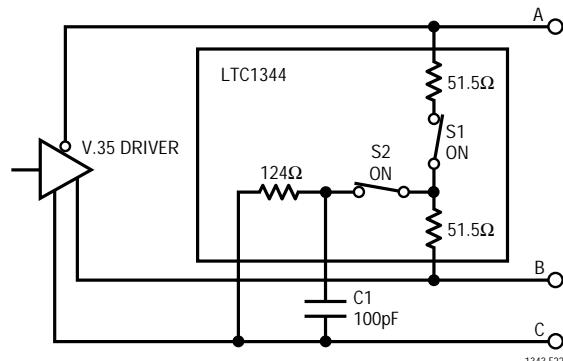

V.35モードでは図21に示すとおり、LTC1344内のスイッチS1とS2がオンになります。Tネットワーク・インピーダンス接続となります。LTC1343内の2つのスイッチはオフです。レシーバの30k入力インピーダンスがTネットワーク終端と並列に配置されますが、総合入力インピーダンスに大きく影響することはありません。

図20. 標準V.35インターフェース

ジェネレータ差動インピーダンスは50から150、また短絡した端子(AおよびB)とグランドC間のインピーダンスは、 $150 \pm 15$  でなければなりません。ジェネレータを終端するには、スイッチS1とS2を両方ともオンにし、センタ抵抗のトップサイドをピンに引き出します。これによって図22に示すとおり、外付けコンデンサでバイパスして、同相ノイズを低減することができます。

ドライバの立上り時間と立下り時間の不整合、またはドライバ伝搬遅延のスキューによって、センタ終端抵抗からグランドに電流が流れ、AおよびB端子に高周波の同相スパイクが発生します。同相スパイクがEMI問題を引き起こすおそれがありますが、多くの同相エネルギーをケーブルではなく、グランドに分流させるコンデンサC1によって軽減されます。

図22. LTC1344を使用するV.35 ドライバ

## アプリケーション情報

### エコー・クロック・モード

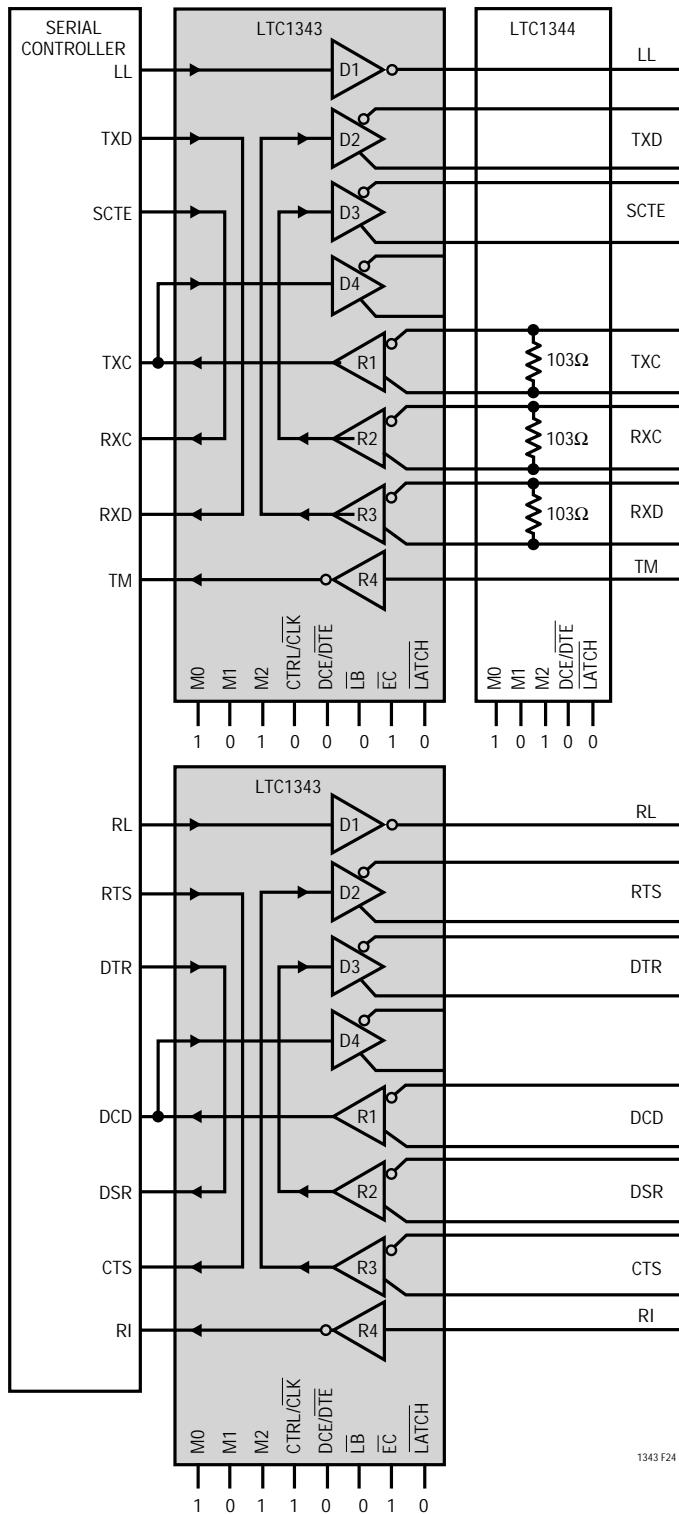

LTC1343は、わずか2本のクロック・ピンを持つシリアル・コントローラを使用してエコー・クロックを生成するロジックを内蔵しています。図23にEIA-530モード構成のDTEおよびDCEエコー・クロックのチップを示します。制御信号は示してありません。エコー・クロック構成はECピンを“L”にすると選択されます。DTEサイドでは送信クロックTXCレシーバ出力がエコー・クロック、SCTE、ドライバ入力に接続されます。シリアル・コントローラのTXCピンは入力として構成されます。DCEサイドでは、シリアル・コントローラからの送信クロックを使用してTXCとRXCを生成します。TDEとDCEの両サイドのTXC信号パスにフェーズ・インバータが配置され、長いケーブルでの位相問題を解決します。インバータ・ピンが“H”的とき、データの位相が反転します。

### ループバック

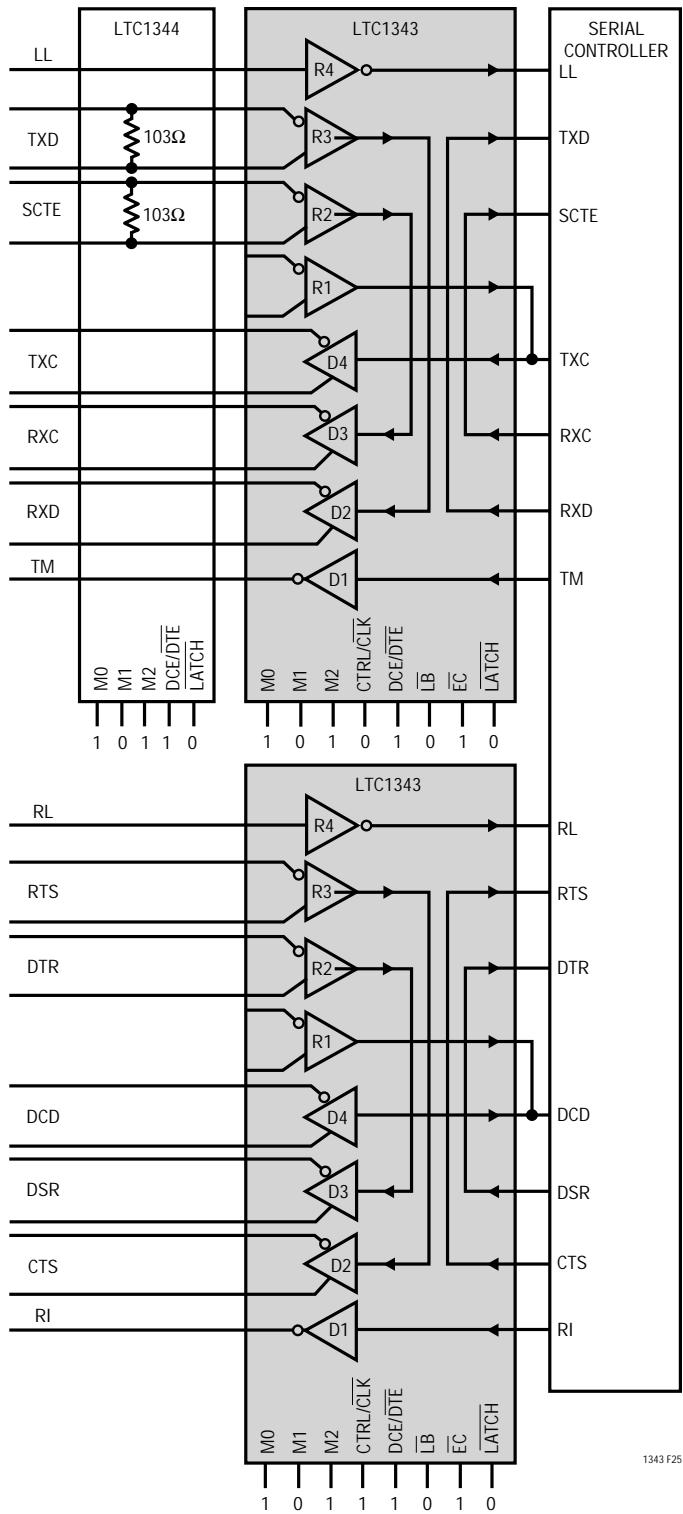

LTC1343はインターフェースをテストの目的でループバック構成にするロジックを内蔵しています。DTEおよびDCEの両方のループバック構成がサポートされています。図24にECピンを“H”にしたループバック構成の完全なDTEインターフェースを示します。ループバック構成は、LBピンを“L”にすると選択されます。ライン・サイドおよびロジック・サイド信号の両方がループバックされます。DCEループバック構成を図25に示します。

ECを“L”にしてエコー・クロック・モードが選択された場合、D3が出力になり、図26に示すとおりDTEモードのレシーバ2の出力R3に接続されます。エコー・クロックDCEループバックでは、図27に示すようにドライバ4はドライバ3の入力D3に接続されます。

図23. EIA-530エコー・クロック構成

## アプリケーション情報

図24. 通常のDTEループバック

図25. 通常のDCEループバック

## アプリケーション情報

1343 F26

図26. エコー・クロック、DTEループバック

1343 F27

図27. エコー・クロック、DCEループバック

## アプリケーション情報

### ノード・ケーブル・モード

ノード・ケーブル・モード( $M_0 = M_1 = M_2 = 1$ )はケーブルがコネクタから切り離されたときのためのものです。チャージ・ポンプ、バイアス回路、ドライバ、およびレシーバがターンオフされ、ドライバ出力がハイ・インピーダンス状態となり、電源電流が $200\mu A$ 以下に低下します。これは信号を切り離すことなく、I/Oラインを他のドライバやレシーバと共に使用することができます。

### チャージ・ポンプ

LTC1343は図28に示すとおり、内蔵の容量性チャージ・ポンプを使用して $V_{DD}$ と $V_{EE}$ を生成します。電圧ダブラーは $V_{DD}$ に約8Vを生成し、電圧インバータは $V_{EE}$ に約-7.5Vを生成します。C1、C2、C3、およびC4に4個の $1\mu F$ 表面実装型タンタル・コンデンサが必要です。 $V_{EE}$ コンデンサC5は最低 $3.3\mu F$ でなければなりません。すべてのコンデンサは16Vです。

### レシーバ・フェイルセーフおよびグリッチ・フィルタ

すべてのLTC1343レシーバはすべてのモードでフェイルセーフ動作を実行します。レシーバ入力がフロートしているか、あるいは終端抵抗によって一括して短絡される場合、レシーバ出力は常にロジック“H”に強制されます。

$\overline{CTRL/CLK}$ を“H”にしてチップを制御信号に対して構成すると、グリッチ・フィルタがすべての入力に接続されます。フィルタはレシーバ入力で300ns以下のグリッチを除去します。

### V.10ドライバの立上りおよび立下り時間

V.10ドライバの立上りおよび立下り時間は、423 SET(ピン25)とグランドの間に $1/8W$ 、5%抵抗を配置してプログラムされます。ドライバの立上りおよび立下り時間と抵抗値のグラフを図29に示します。

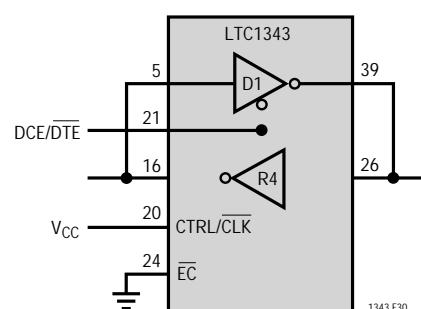

**シングル・エンデッド・ドライバおよびレシーバのイネーブル**

LTC1343が制御信号の生成に使用され( $\overline{CTRL/CLK} = “H”$ )

$\overline{EC}$ ピンが“L”になると、 $DCE/DTE$ ピンがドライバ1およびレシーバ4のイネーブル・ピンになるため、図30に示すとおり、それらの入力および出力は一括して接続できます。

図28. チャージ・ポンプ

図29. V.10 ドライバの立上りおよび立下り時間と抵抗値

図30. シングル・エンデッド・ドライバおよびレシーバのイネーブル

## アプリケーション情報

DCEピンはCTRL/CLKが“H”的とき、DCE/DTEピンをイネーブル・ピンにできること以外は、構成に影響を与えることはありません。DCE/DTEが“L”的とき、ドライバ1出力がイネーブルされます。レシーバ4出力は3ステートになります、入力はグランドに対して30k 負荷となります。

DCE/DTEが“H”的とき、ドライバ1出力は3ステートとなり、レシーバ4出力がイネーブルされます。レシーバ4入力は入力インピーダンスがグランドに対して5k となるRS232動作に構成した場合を除く、すべてのモードで、グランドに対して30k 負荷となります。

### DTE対DCE動作

DCE/DTEピンはLTC1343のピンをドライバまたはレシーバとして再構成するためのものではありません。DCE/DTEピンはループバック・トポロジーを選択するだけで、制御信号を得るためのシングル・エンディッド・ドライバおよびレシーバのイネーブルとして機能します。

しかし、LTC1343は次の3つの方式の1つでDTEまたはDCE動作に構成することができます。つまり、適切なジェンダのコネクタ付き専用DTEまたはDCEポート、専用DTEケーブルまたは専用DCEケーブルを使用してLTC1343への信号を再ルーチングすることによってDTEまたはDCE動作に構成可能な1個のコネクタ付きポート、あるいは4個のLTC1343を使用した1個のコネクタと1本のケーブル付きポートです。

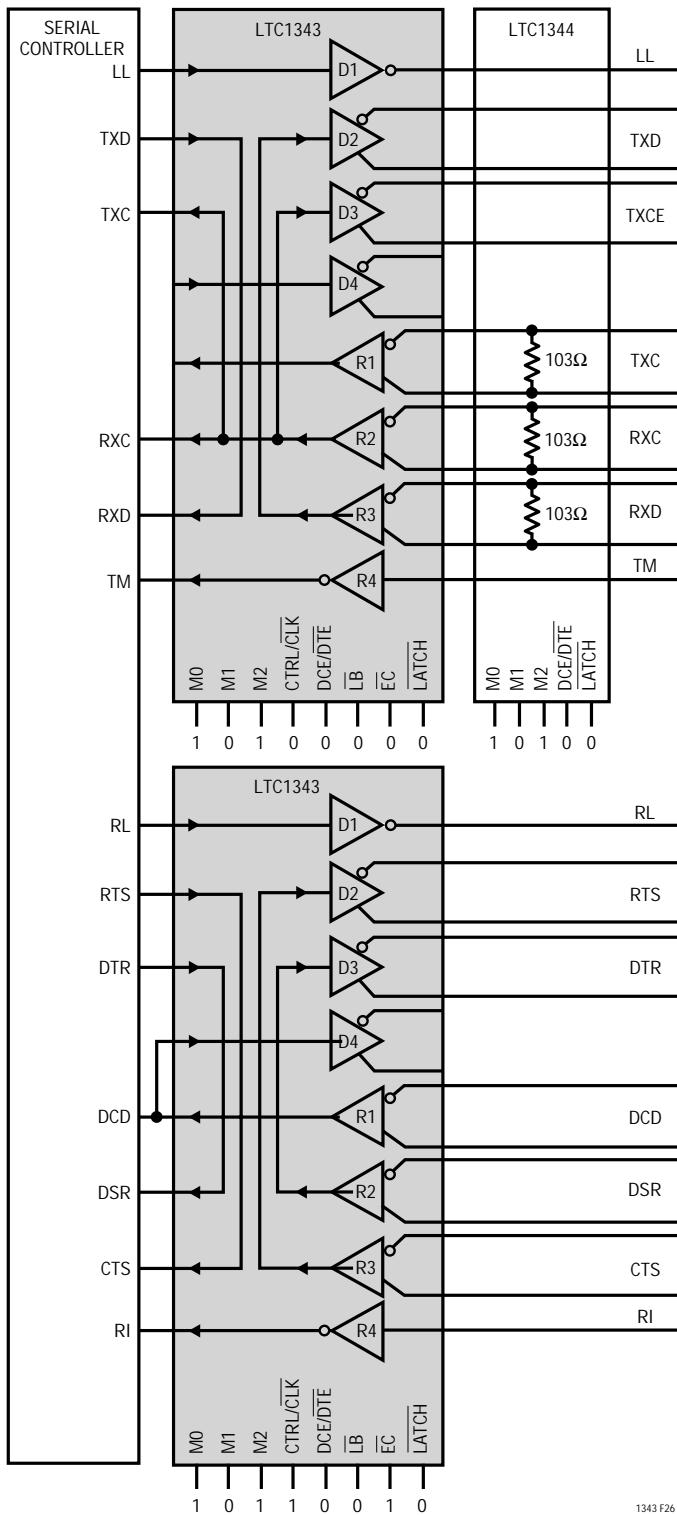

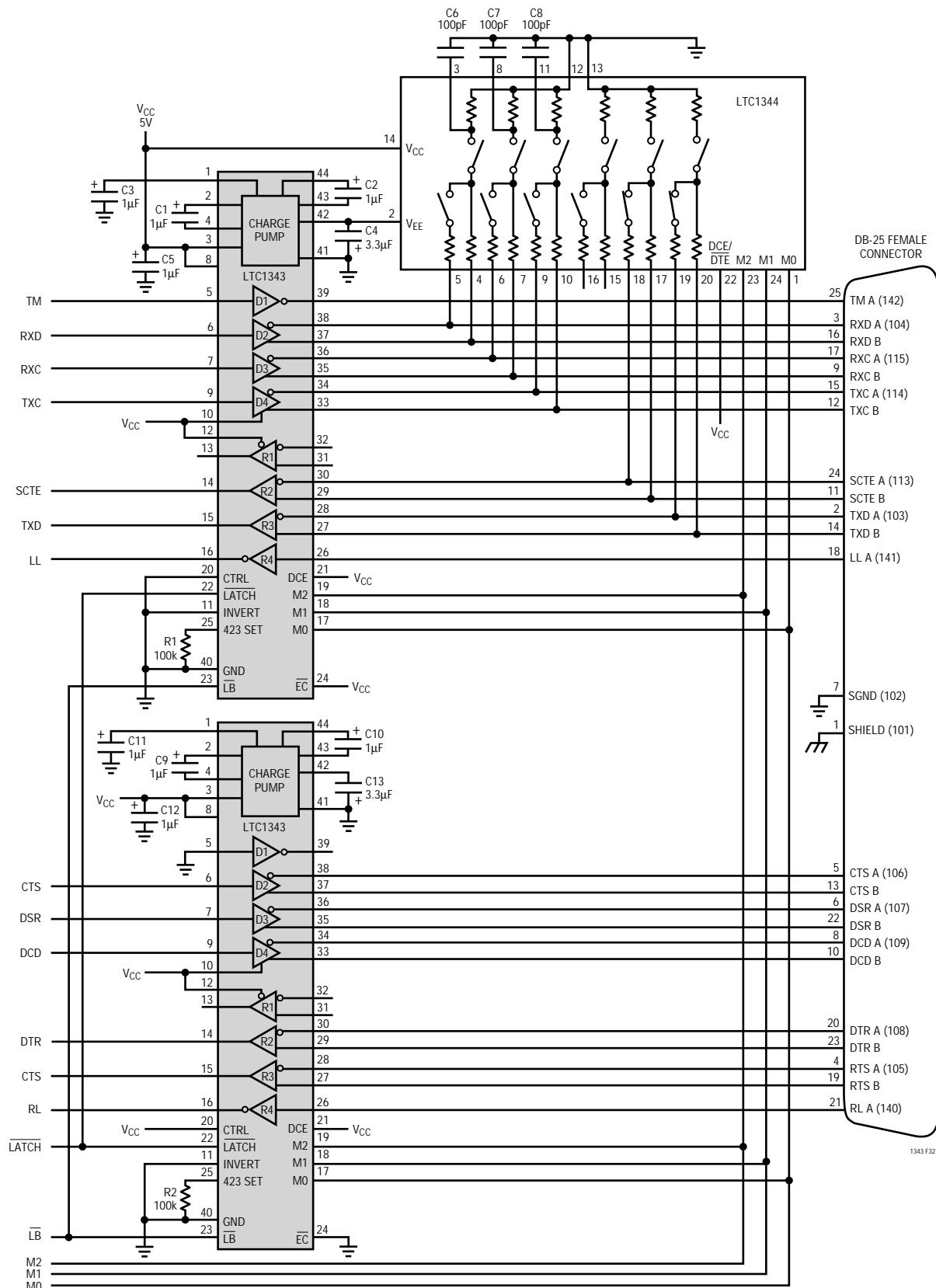

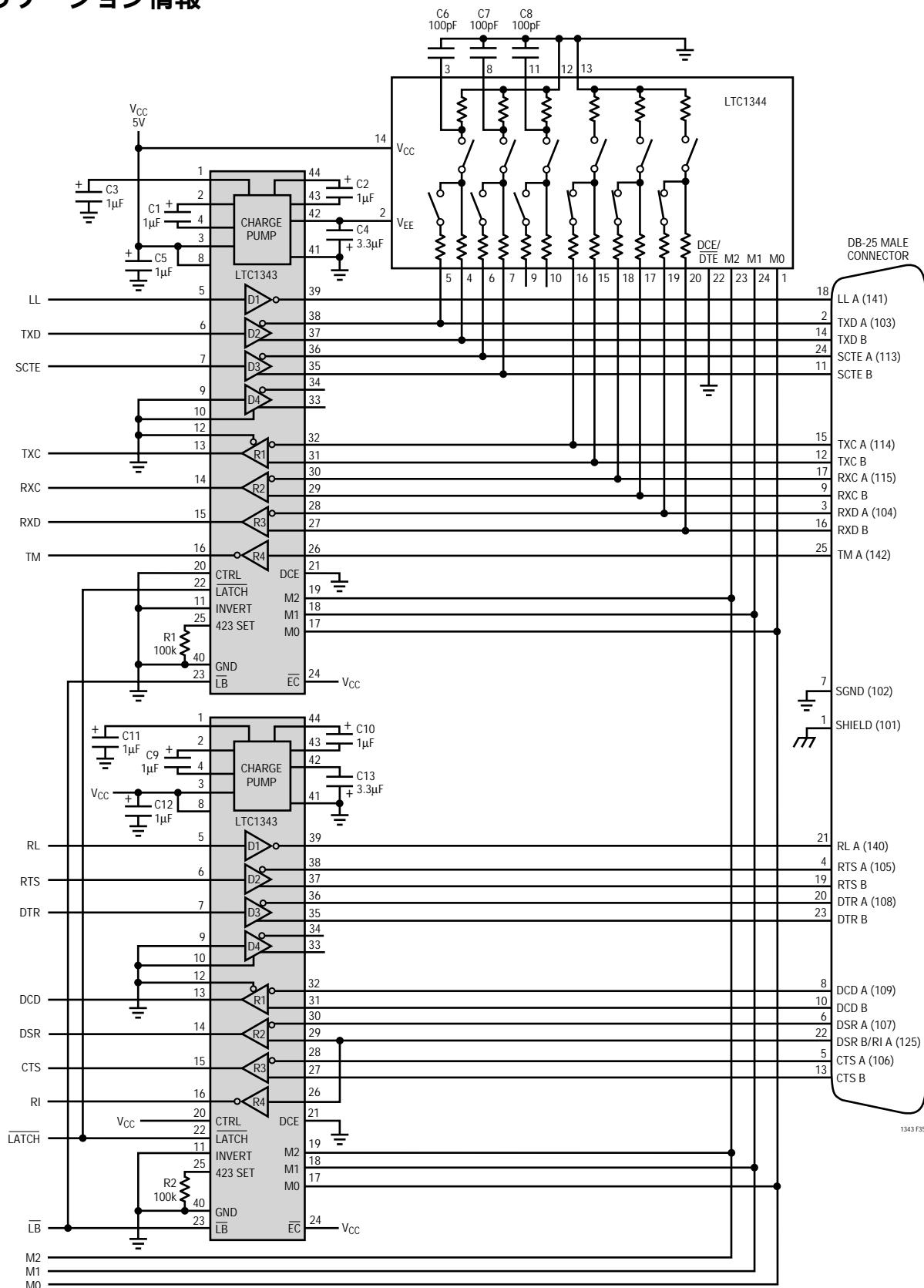

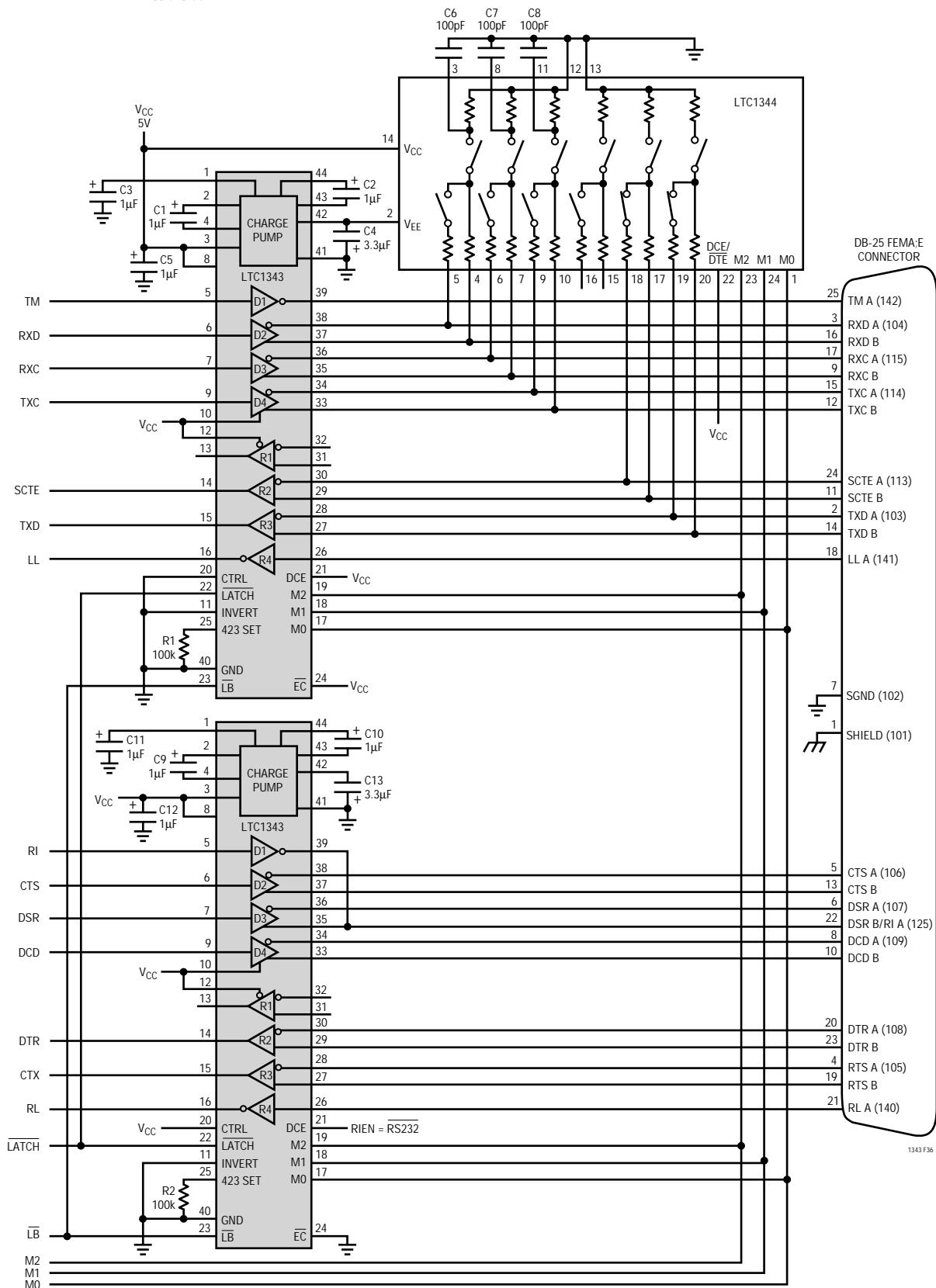

DB-25雄コネクタを使用した専用DTEポートを図31に示します。インタフェース・モードはコントローラから、またはジャンパからモード・セレクト・ピンのV<sub>CC</sub>、またはGNDに供給されるロジック出力によって選択されます。DB-25雌コネクタを使用した専用DCEポートを図32に示します。

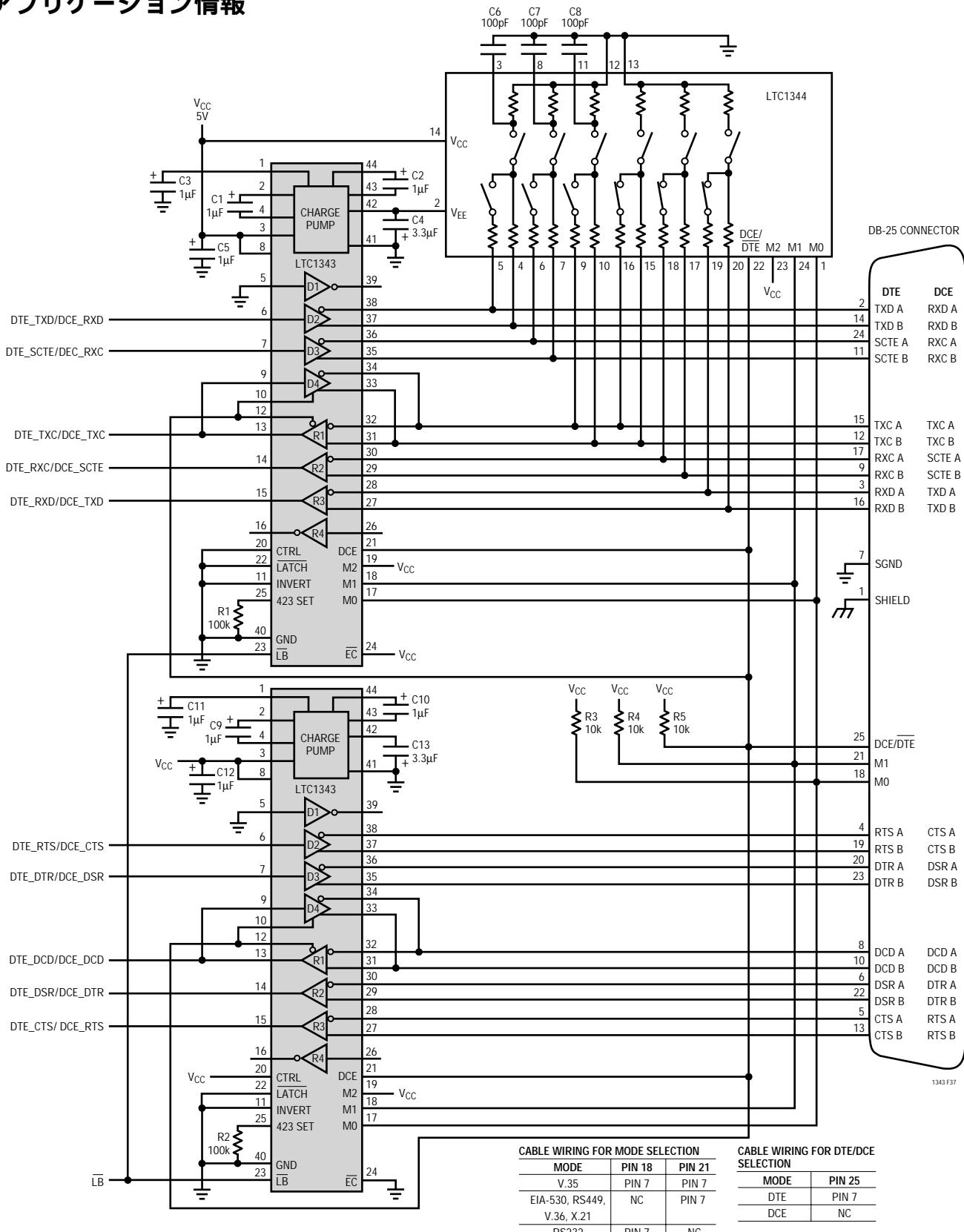

1個のDB-25コネクタを備えたDTEまたはDCE動作に構成可能なポートを図33に示します。DTEまたはDCE動作で適切な信号ルーティングを行うには、構成ごとに別々のケーブルが必要です。たとえば、DTEモードではTXD信号がLTC1343のドライバ2を経由して、コネクタ・ピン2および14に伝達されます。DCEモードでは、ドライバ2がRXD信号をピン2と14に伝達します。

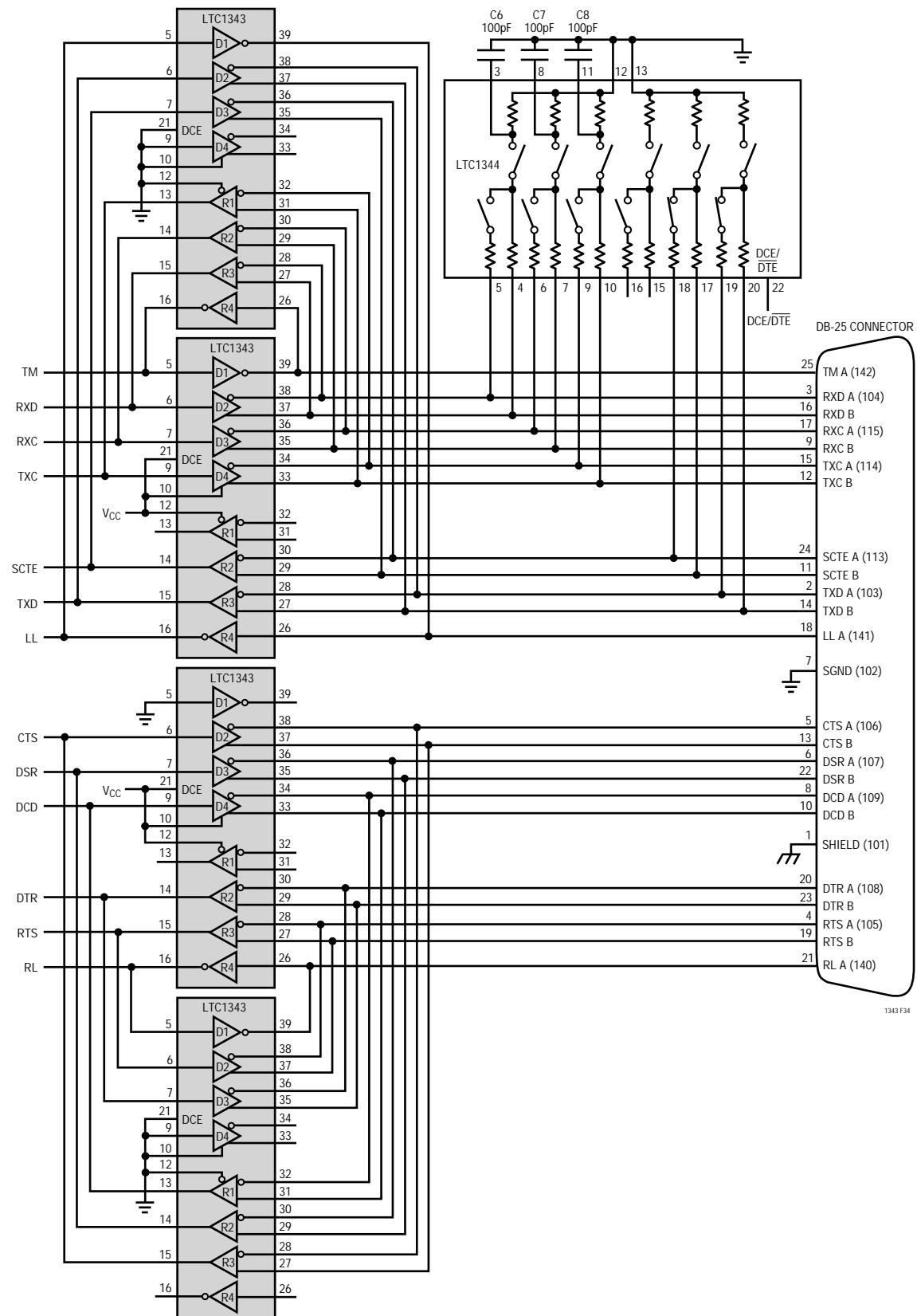

個別のDCE/DTEケーブルを必要としないコンビネーションDTE/DCEポートを図34に示します。DTEモードでは、トップおよびボトムのLTC1343がイネーブルされ、中間の2個は

ノー・ケーブル・モードで配置されます。これによって、すべてのドライバおよびレシーバがハイ・インピーダンス状態になります。DCEモードでは中間の2個のLTC1343がイネーブルされ、トップおよびボトムのLTC1343はディスエーブルされます。この方式では、コネクタ・ピンを送信または受信信号用に構成することができます。1個のLTC1343しか必要ないことに注意してください。

### リング表示とDB-25コネクタを備えたマルチプロトコル・インタフェース

RS232モードのRI信号を実装する場合、コントロール・チップのドライバ4およびレシーバ1をコネクタ・ピン22に接続して、RS232モードのRI信号やその他のモードのDSR B信号を生成することができます。図35にDTE構成を、図36にDCE構成を示します。DCEモードではDCE/DTEピンは、インターフェースがRS232モードのときにのみ“L”になるコントローラからロジック信号でドライブしなければなりません。レシーバ4の入力インピーダンスは、RS232モードを除くすべてのモードで30k 以上になるため、いつでもイネーブルできますが、ラインの負荷が切り離されることはありません。ドライバ1がディスエーブルされるとハイ・インピーダンス状態を保持するため、ラインが装荷されることはありません。

### ケーブル・セレクタブル・マルチプロトコル・インタフェース

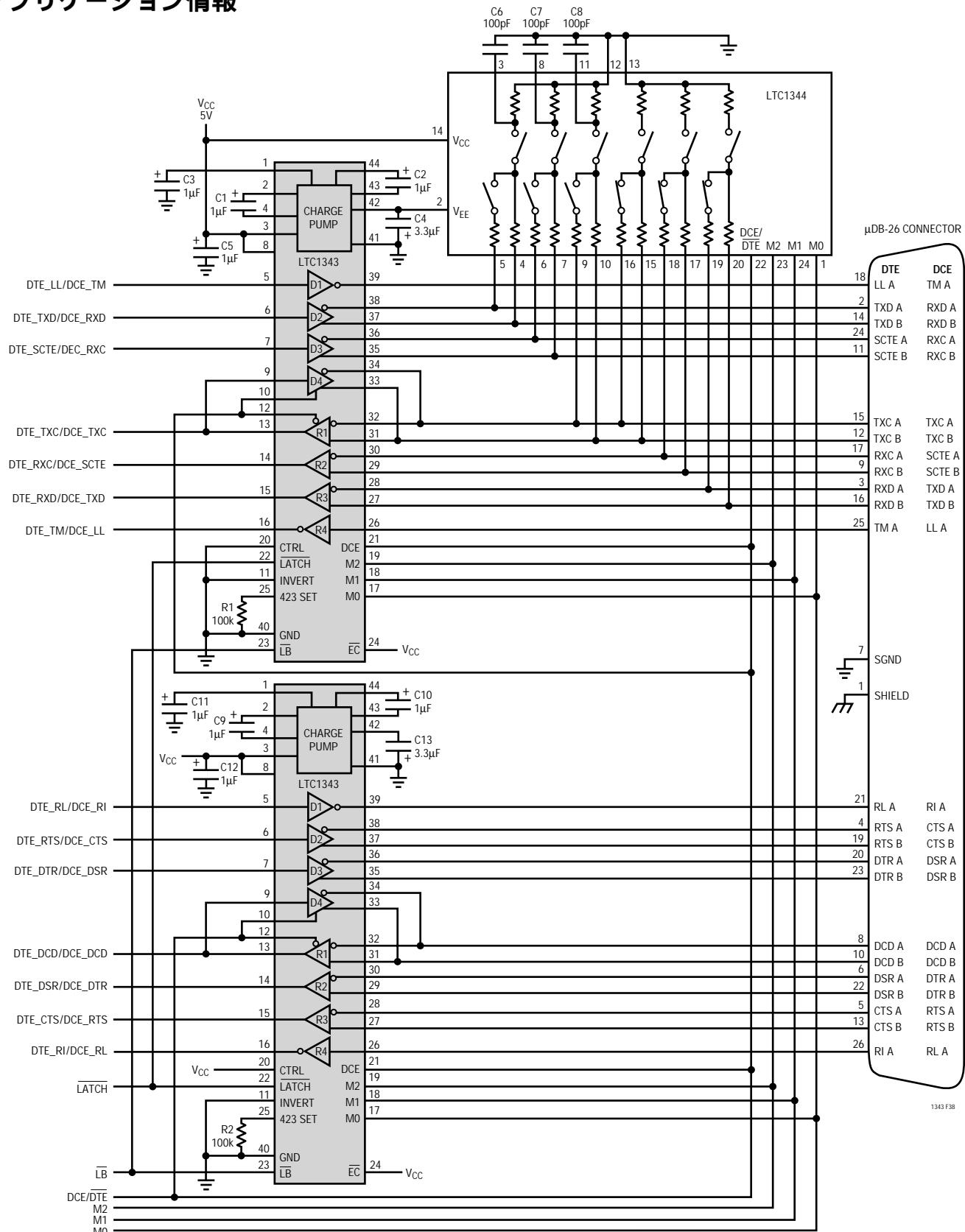

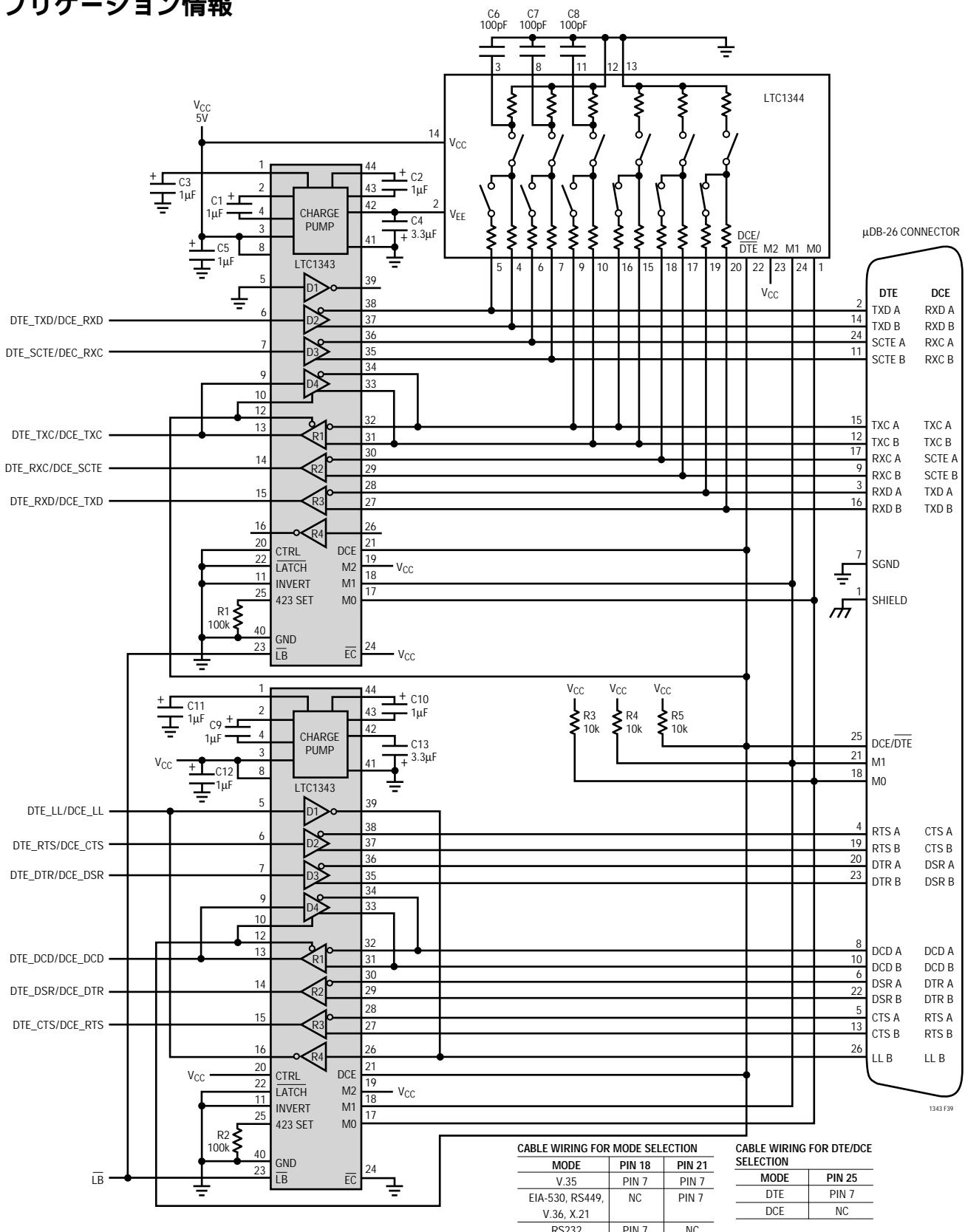

ケーブル・セレクタブル・マルチプロトコルDTE/DCEインターフェースを図37に示します。制御信号LL、RL、およびTMは実行されません。セレクト・ラインM0、M1、およびDCE/DTEはコネクタに引き出されます。モードはM0(コネクタ・ピン18) M1(コネクタ・ピン21) およびDCE/DTE(コネクタ・ピン25)をグランドに配線するか、またはこれらをフロートさせることによりケーブルを通して選択されます。M0、M1、またはDCE/DTEがフロートしている場合、ブルアップ抵抗R3、R4、およびR5が信号をV<sub>CC</sub>にブルアップします。セレクト・ビットM1はV<sub>CC</sub>にハードワイヤされます。ケーブルが引き抜かれると、インタフェースはノー・ケーブル・モードになります。

μDB-26コネクタ付きマルチプロトコル・インタフェース標準μDB-26コネクタを備えたコントローラ・セレクタブル・マルチプロトコルDTE/DCEインターフェースを図38に示します。RL、LL、およびTM信号が実行され、RIIはコネクタのピン26にマップされます。ケーブル・セレクタブル・バージョンを図39に示します。TMおよびRL信号はありませんが、LLは残っています。

## アプリケーション情報

図31：DB-25コネクタ付きコントローラ・セレクタブル・マルチプロトコルDTEポート

## アプリケーション情報

図32：DB-25コネクタ付きコントローラ・セレクタブル・マルチプロトコルDCEポート

## アプリケーション情報

図33. DB-25コネクタ付きコントローラ・セレクタブル・マルチプロトコルDTE/DCEポート

## アプリケーション情報

図34. DB-25コネクタ付きコントローラ・セレクタブル・マルチプロトコルDTE/DCEポート

## アプリケーション情報

図35. RIおよびDB-25コネクタ付きコントローラ・セレクタブル・マルチプロトコルDTEポート

## アプリケーション情報

図36. RIおよびDB-25コネクタ付きコントローラ・セレクタブル・マルチプロトコルDCEポート

## アプリケーション情報

図37. DB-25コネクタ付きケーブル・セレクタブル・マルチプロトコルDTE/DCEポート

## アプリケーション情報

図38. DB-26コネクタ付きコントローラ・セレクタブル・マルチプロトコルDTE/DCEポート

## アプリケーション情報

図39. DB-26コネクタ付きケーブル・セレクタブル・マルチプロトコルDTEポート

**関連製品**

| PART NUMBER | DESCRIPTION                                     | COMMENTS                                                       |

|-------------|-------------------------------------------------|----------------------------------------------------------------|

| LTC1321     | Dual RS232/RS485 Transceiver                    | 2 RS232 Driver/Receiver Pairs or 2 RS485 Driver/Receiver Pairs |

| LTC1334     | Single 5V RS232/RS485 Multiprotocol Transceiver | 2 RS232 Driver/Receiver or 4 RS232 Driver/Receiver Pairs       |

| LTC1344     | Software-Selectable Cable Terminator            | Perfect for Terminating the LTC1343                            |

| LTC1345     | Single Supply V.35 Transceiver                  | 3 Driver/3 Receiver for Data and Clock Signals                 |

| LTC1346A    | Dual Supply V.35 Transceiver                    | 3 Driver/3 Receiver for Data and Clock Signals                 |