## 特長

- AB級バイアス電流を設定

- 調整不要

- $I_Q$ の熱暴走なし

- デバイス不整合を補正

- 単純なヒート・シンク

- プログラム可能な電流制限

- 並列接続により高電流を供給能

- 小型SO-8またはPDIPパッケージ

## アプリケーション

- パワーMOSFETのバイアス

- 高電圧アンプ

- シェーカ・テーブル・アンプ

- オーディオ・パワー・アンプ

## 概要

LT<sup>®</sup>1166は高電力アンプにおいてAB級出力電流を制御するバイアス生成システムです。外付けトランジスタを接続すると、ユニティ・ゲイン電圧フォロワになります。LT1166は、無信号時電流調整や厳密なトランジスタの整合がまったく必要ないため、パワーMOSFETデバイスのドライブに最適です。LT1166を使用した複数の出力段を並列に接続すれば、高出力電流を得ることができます。

バイアス・システムが小さな外付けセンス抵抗を使用して、各パワー・トランジスタの電流を検知するため、静止点の熱暴走は発生しません。高速レギュレータ・ループは、各パワー・デバイスに供給されるドライブ量を制御します。LT1166は1組のトランジスタまたは電流源からバイアスでき、また出力トランジスタに供給されるドライブ電圧で動作するため、どのような電源電圧でも動作可能です。

△、LTC、LTはリニアテクノロジー社の登録商標です。

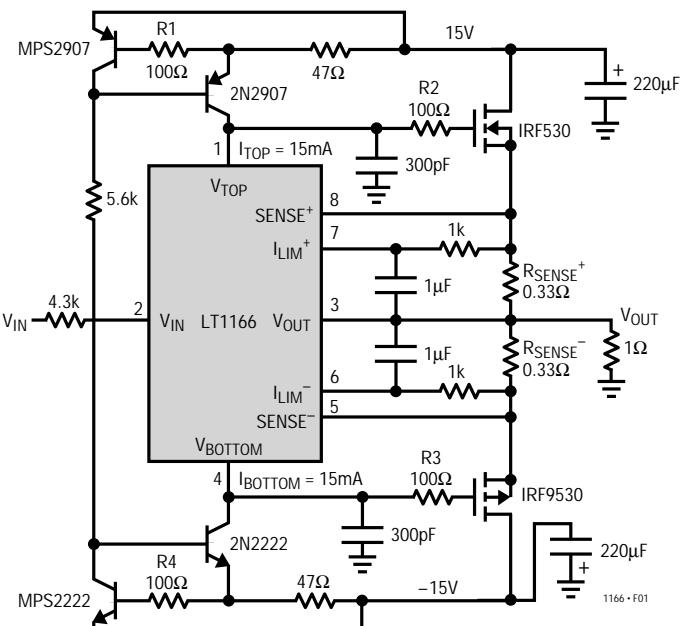

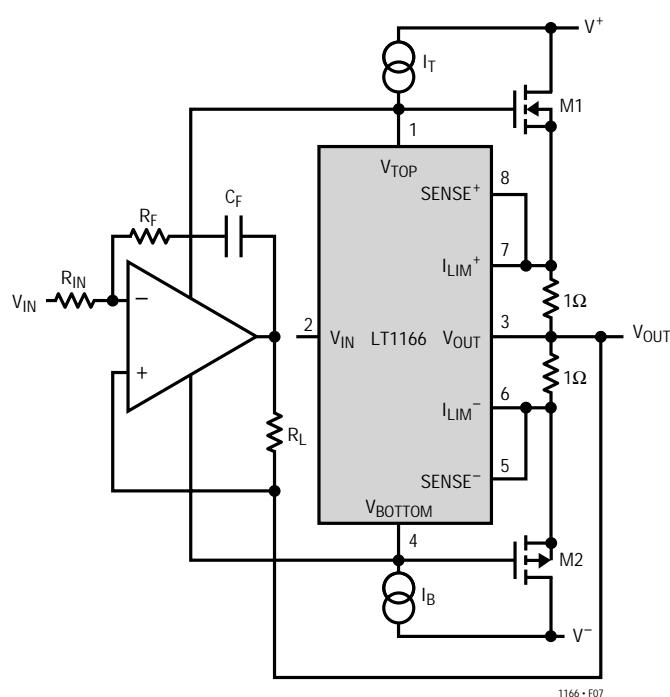

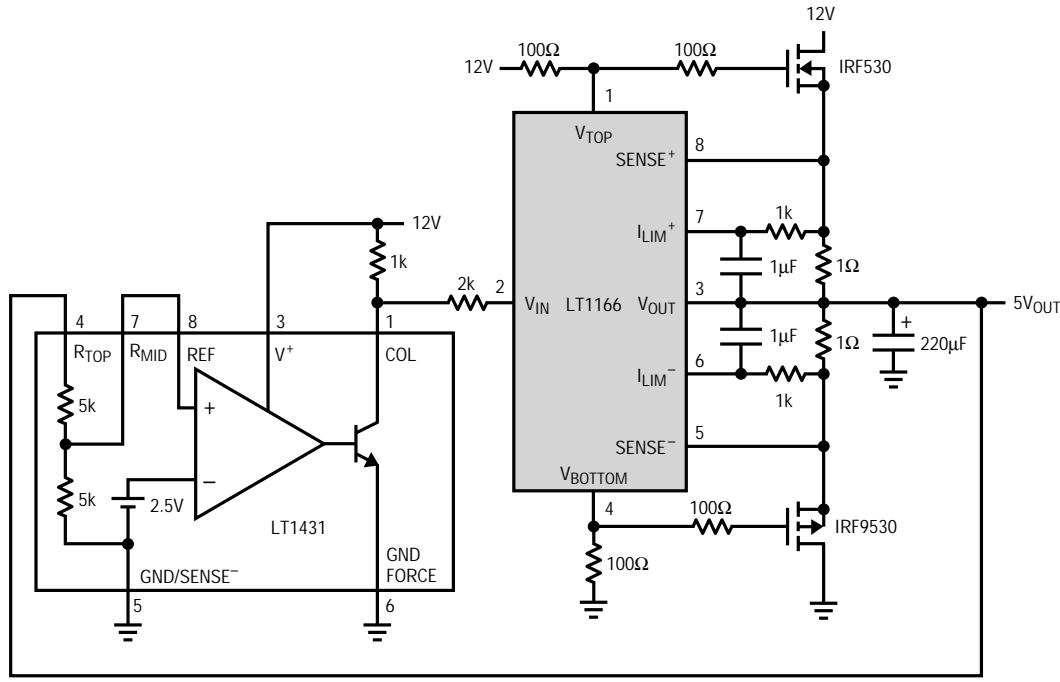

## TYPICAL APPLICATION

Figure 1. Unity Gain Buffer with Current Limit

## ABSOLUTE MAXIMUM RATINGS

|                                              |                |

|----------------------------------------------|----------------|

| Supply Current (Pin 1 or Pin 4) .....        | 75mA           |

| Differential Voltage (Pin 2 to Pin 3) .....  | $\pm 6V$       |

| Output Short-Circuit Duration (Note 1) ..... | Continuous     |

| Specified Temperature Range (Note 2) .....   | 0°C to 70°C    |

| Operating Temperature Range .....            | -40°C to 85°C  |

| Storage Temperature Range .....              | -65°C to 150°C |

| Junction Temperature (Note 3) .....          | 150°C          |

| Lead Temperature (Soldering, 10 sec) .....   | 300°C          |

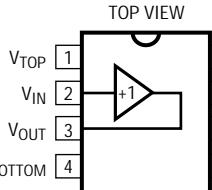

## PACKAGE/ORDER INFORMATION

| TOP VIEW                                                                                                        | ORDER PART NUMBER      |

|-----------------------------------------------------------------------------------------------------------------|------------------------|

| <br>N8 PACKAGE<br>8-LEAD PDIP | LT1166CN8<br>LT1166CS8 |

| S8 PACKAGE<br>8-LEAD PLASTIC SO                                                                                 | S8 PART MARKING        |

|                                                                                                                 | 1166                   |

$T_{JMAX} = 150^\circ\text{C}$ ,  $\theta_{JA} = 100^\circ\text{C}/\text{W}$  (N8)

$T_{JMAX} = 150^\circ\text{C}$ ,  $\theta_{JA} = 150^\circ\text{C}/\text{W}$  (S8)

Consult factory for Industrial and Military grade parts.

## ELECTRICAL CHARACTERISTICS

Pin 1 = 2V, Pin 4 = -2V, Operating current 15mA and  $R_{IN} = 20k$ , unless otherwise specified.

| PARAMETER             | CONDITIONS                              | MIN | TYP     | MAX      | UNITS         |

|-----------------------|-----------------------------------------|-----|---------|----------|---------------|

| Output Offset Voltage | Operating Current 15mA to 50mA          | ●   | 50      | 250      | mV            |

| Input Bias Current    | Operating Current 15mA to 50mA (Note 4) | ●   | 2       | 10       | $\mu\text{A}$ |

| Input Resistance      | Operating Current 15mA to 50mA (Note 5) | ●   | 2       | 15       | $M\Omega$     |

| $V_{AB}$ (Top)        | Measure Pin 8 to Pin 3, No Load         |     | 14      | 20       | 26            |

| $V_{AB}$ (Bottom)     | Measure Pin 5 to Pin 3, No Load         |     | -14     | -20      | -26           |

| Voltage Compliance    | Operating Current = 50mA (Notes 6, 9)   | ●   | $\pm 2$ | $\pm 10$ | V             |

| Current Compliance    | Operating Voltage = $\pm 2V$            | ●   | $\pm 4$ | $\pm 50$ | mA            |

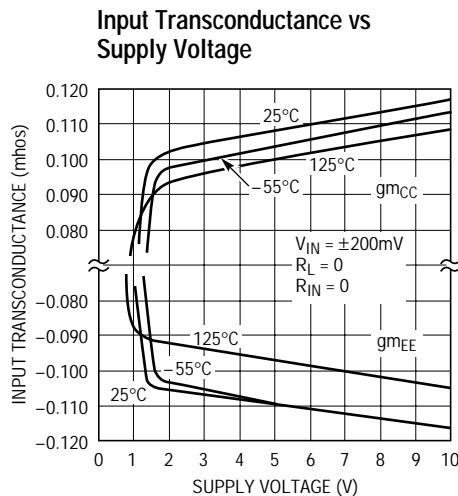

| Transconductance      | (Note 7)                                |     |         |          |               |

| $gm_{CC2}$            | Pin 1 = 2V, Pin 4 = -2V                 | ●   | 0.08    | 0.100    | mho           |

| $gm_{EE2}$            | Pin 1 = 2V, Pin 4 = -2V                 | ●   | 0.08    | 0.100    | mho           |

| $gm_{CC10}$           | Pin 1 = 10V, Pin 4 = -10V               | ●   | 0.09    | 0.125    | mho           |

| $gm_{EE10}$           | Pin 1 = 10V, Pin 4 = -10V               | ●   | 0.09    | 0.125    | mho           |

| PSRR <sub>CC</sub>    | (Note 8)                                |     | 19      |          | dB            |

| PSRR <sub>EE</sub>    | (Note 8)                                |     | 19      |          | dB            |

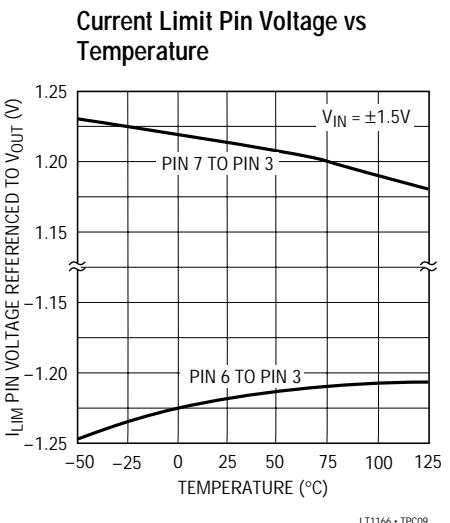

| Current Limit Voltage | Operating Current 15mA to 50mA          |     |         |          |               |

|                       | Pin 7 Voltage to Pin 3                  | ●   | 1.0     | 1.3      | V             |

|                       | Pin 6 Voltage to Pin 3                  | ●   | -1.0    | -1.3     | V             |

|                       |                                         |     |         | -1.5     | V             |

The ● denotes specifications which apply over the full operating temperature range.

**Note 1:** External power devices may require heat sinking.

**Note 2:** Commercial grade parts are designed to operate over the temperature range of -40°C to 85°C but are neither tested nor guaranteed beyond 0°C to 70°C. Industrial grade parts specified and tested over -40°C and 85°C are available on special request, consult factory.

**Note 3:**  $T_J$  calculated from the ambient temperature  $T_A$  and the power dissipation  $P_D$  according to the following formulas:

$$\text{LT1166CN8: } T_J = T_A + (P_D \cdot 100^\circ\text{C}/\text{W})$$

$$\text{LT1166CS8: } T_J = T_A + (P_D \cdot 150^\circ\text{C}/\text{W})$$

**Note 4:**  $I_{TOP} = I_{BOTTOM}$

**Note 5:** The input resistance is typically  $15M\Omega$  when the loop is closed. When the loop is open (current limit) the input resistance drops to  $200\Omega$  referred to Pin 3.

**Note 6:** Maximum  $T_J$  can be exceeded with 50mA operating current and simultaneous 10V and -10V (20V total).

**Note 7:** Apply  $\pm 200\text{mV}$  to Pin 2 and measure current change in Pin 1 and 4. Pin 3 is grounded.

$$\begin{aligned} \text{Note 8: PSRR}_{CC} &= \frac{gm_{CC2} - gm_{CC10}}{gm_{CC2}} \\ \text{PSRR}_{EE} &= \frac{gm_{EE2} - gm_{EE10}}{gm_{EE2}} \end{aligned}$$

**Note 9:** For Linear Operation, Pin 1 must not be less than 2V or more than 10V from Pin 3. Similarly, Pin 4 must not be less than 2V or more than 10V from Pin 3.

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

### ピン機能

$V_{TOP}$ ( ピン1 ): ピン1は出力トランジスタのトップ・ドライブ電圧を設定します。動作電源電流はピン1に供給され、その一部が内部回路をバイアスします。ピン1の電流は4mA以上でなければなりません。ピン1の電圧は  $V_{OUT}$ を基準にして内部で12Vにクランプされているため、このピン電流は最大75mAに制限する必要があります。

$V_{IN}$ ( ピン2 ): ピン2は  $V_{OUT}$ ( ピン3 )をドライブするユニティ・ゲイン・バッファの入力です。フォールト条件(短絡)では、入力インピーダンスが200Ωに低下するため、入力電流を5mAに制限するか、 $V_{IN}$ と  $V_{OUT}$ 間の電圧を±6V以下に制限しなければなりません。

$V_{OUT}$ ( ピン3 ): LT1166のピン3は、出力電圧を入力電圧に保持する電圧制御ループの出力です。

$V_{BOTTOM}$ ( ピン4 ): ピン4は出力トランジスタのボトム・サイド・ドライブ電圧を設定します。動作電源電流はこのピンから流出します。ピン4の電流は4mA以上でなければなりません。ピン4の電圧は、内部で  $V_{OUT}$ を基準にして -12Vにクランプされているため、このピン電流は最大75mAに制限する必要があります。

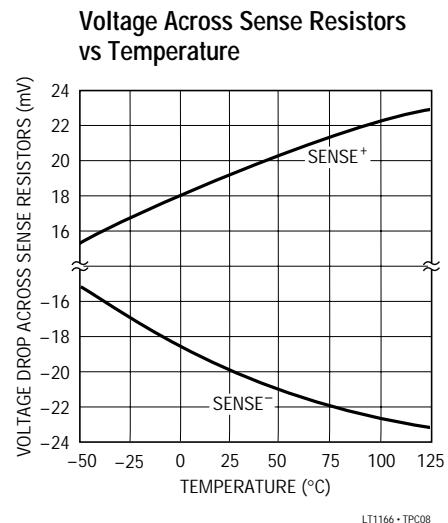

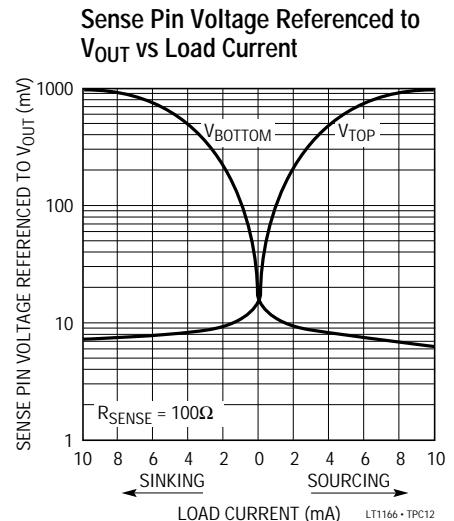

$SENSE^-$ ( ピン5 ):  $SENSE^-$  ピン電圧は電流制御ループによって設定され、ボトムサイド・パワー・デバイスの出力静止電流を制御します。フォールト条件では、ピン5とピン3間の最大電圧差を±6Vに制限してください。

$I_{LIM^-}$ ( ピン6 ): 負側電流制限ピンです。負のフォールト条件では  $V_{BOTTOM}$ と  $V_{OUT}$ 間の電圧を制限します。ピン6の最大逆電圧は  $V_{OUT}$ を基準にして6Vです。

$I_{LIM^+}$ ( ピン7 ): 正側電流制限ピンです。正のフォールト条件では  $V_{TOP}$ と  $V_{OUT}$ 間の電圧を制限します。ピン7の最大逆電圧は  $V_{OUT}$ を基準にして -6Vです。

$SENSE^+$ ( ピン8 ):  $SENSE^+$  ピン電圧は電流制御ループによって設定され、トップサイド・パワー・デバイスの出力静止電流を制御します。フォールト条件では、ピン8とピン3間の最大電圧差を±6Vに制限してください。

## アプリケーション情報

## 過電圧保護

$V_{TOP}$ ( ピン1)および $V_{BOTTOM}$ ( ピン4)電源ピンにはクランプ・ダイオードがあり、電圧が $\pm 12V$ を超えるとタン・オンします。クランプ・ダイオードはESD保護ダイオードとして機能し、高い $V_{GS}$ 電圧を生成する大型パワーMOSデバイスと組み合わせて使用して、LT1166を保護します。ピン1またはピン4に流入する電流は最大 $\pm 75mA$ に制限しなければなりません。

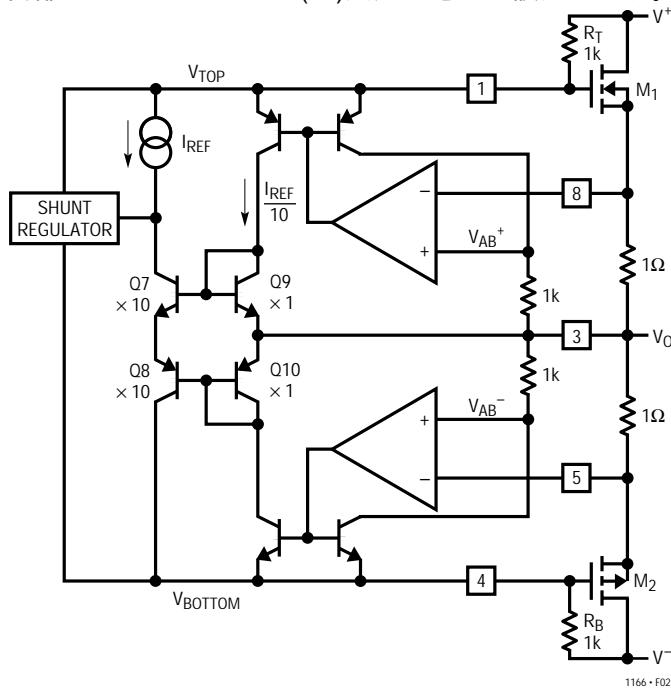

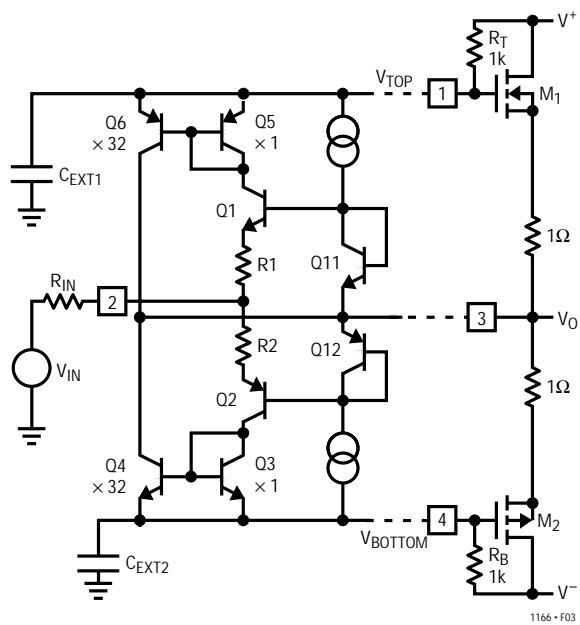

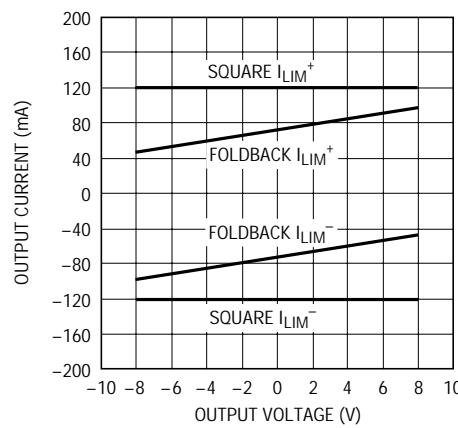

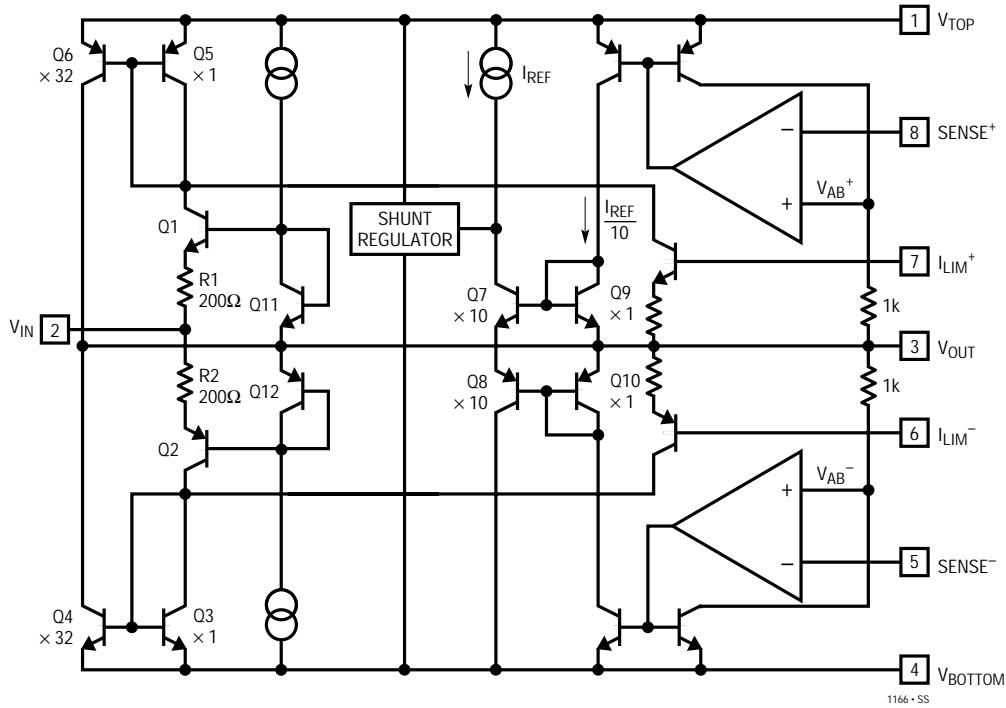

## 乗算器の動作

図2にLT1166内部の電流乗算器回路と、出力トランジスタとの関連性を示します。LT1166の電源電圧 $V_T$ ( トップ)と $V_B$ ( ボトム)は、パワー・デバイスの所要“オン”電圧によって設定されます。また、基準電流 $I_{REF}$ で、 $V_{BE7}$ と $V_{BE8}$ が一定電圧に設定されます。この電圧はQ9とQ10のエミッタ・ベース間の電圧で、Q7とQ8のエミッタ部分の1/10になります。この電流乗算器に対応する式は、以下のとおりです。

$$V_{BE7} + V_{BE8} = V_{BE9} + V_{BE10}$$

あるいは、電流に関しては、以下のとあります。

$$(I_{C9})(I_{C10}) = (I_{REF})^2/100 = \text{一定}$$

IC9とIC10の積は一定です。これらの電流はミラーされ、内部オペアンプ・ペアの(+)入力の電圧を設定します。

Figure 2. Constant Product Generator

オペアンプの帰還によって(-)入力の電圧が等しくなり、これらの電圧はパワー・デバイスと直列に接続されるセンス抵抗に現れます。パワー・デバイスの2つの電流の積は一定で、一方が増加すると他方が減少します。Q9とQ10は対数特性に優れているため、10倍単位の電流変動においてもこの関係が維持されます。

Q7とQ8の全電流は実際には、 $I_{REF}$ とシャント・レギュレータの小さな誤差電流の和になります。高い出力電流条件では、レギュレータからの誤差電流は減少します。レギュレータによって流れる電流も減少し、パワー・デバイスをドライブするのに必要なだけ $V_T$ または $V_B$ を上昇させることができます。

## 入力段のドライブ

図3に $V_T$ と $V_B$ をドライブするLT1166の入力相互コンダクタンス段を示します。正電圧 $V_{IN}$ を $R_{IN}$ に印加すると、R2とQ2のエミッタに小さな入力電流が流れます。これによって、 $V_O$ はアンプの利得誤差内で $V_O$ に追従します。ついで、入力電流はQ3/Q4でミラーされ、Q4のコレクタへの電流はパワー・デバイスM1が供給します。Q4のエミッタの信号電流は外付け抵抗 $R_B$ によって吸収され、これによって、 $V_B$ は $V_{IN}$ の場合と同程度上昇します。

Figure 3. Input Stage Driving Gates

## アプリケーション情報

$V_T$ に対しても同様に、 $R_{IN}$ に正の電圧が印加されると、 $R1$ および $Q1$ を流れる電流は $R_{IN}$ を通して供給されるようになります。この効果によって、ミラー $Q5/Q6$ の電流が減少します。減少した電流は $RT$ の電圧を低下させ、 $V_T$ が上昇して $V_O$ が $V_{IN}$ に追従します。

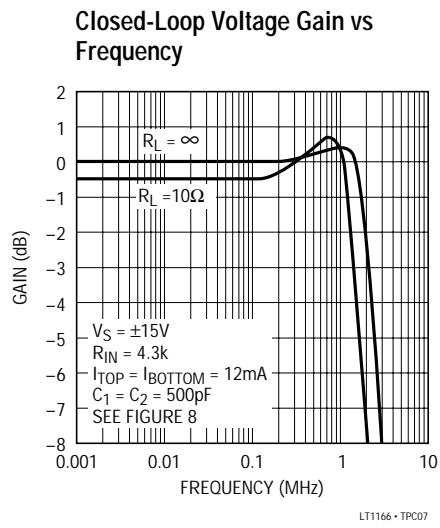

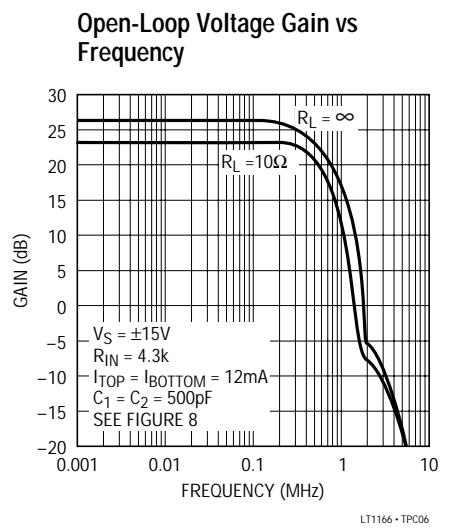

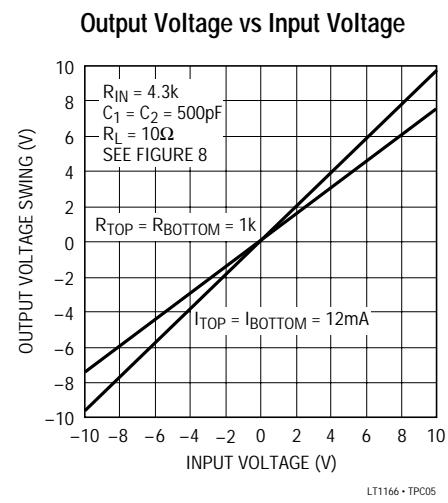

開ループ電圧利得 $V_O/(V_{IN} - V_{PIN2})$ は $R_T$ と $R_B$ を電流源に置き換えれば増大させることができます。この目的は電圧利得 $V_{OUT}/V_{IN}$ を約0.8から1に増加させることです(標準性能特性曲線を参照)。抵抗の代わりに電流源を使用するとループ利得が大幅に増加して、出力段の非直線性を補償するため、きわめて歪が低くなります。

### 周波数補償および安定性

入力相互コンダクタンスは入力抵抗 $R_{IN}$ と32:1電流ミラー $Q3/Q4$ および $Q5/Q6$ によって設定されます。抵抗 $R1$ および $R2$ は $R_{IN}$ の値と比較して小さくなります。 $R_{IN}$ の電流は $Q4$ または $Q6$ の電流の32倍になり、外部補償コンデンサ $C_{EXT1}$ と $C_{EXT2}$ をドライブします。これら2つの入力信号経路が並列になって、下記の相互コンダクタンスを与えます。

$$g_m = 16/R_{IN}$$

利得バンド幅は以下のとおりです。

$$GBW = \frac{16}{2\pi(R_{IN})(C_{EXT})}$$

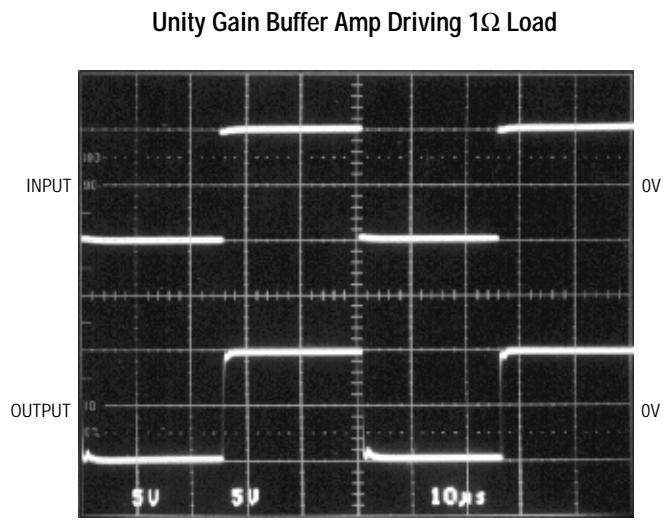

出力デバイスの速度に応じて、標準値は $R_{IN} = 4.3k$ 、 $C_{EXT1} = C_{EXT2} = 500pF$ であり、1.2MHzの-3dBバンド幅が得られます(標準性能特性曲線を参照)。

不安定動作を回避するには、図1に示すとおり優れた電源バイパスを実現することが重要です。大容量電源バイパス・コンデンサ(220μF)を使用し、電源リードを短くすれば、これらの高電流レベルでの不安定性を解消できます。出力デバイスのゲートと直列に100Ω抵抗( $R2$ および $R3$ )を接続すれば、図1の100Ω抵抗 $R1$ および $R4$ と同様に、100MHz領域での発振が停止します。

### 容量性負荷のドライブ

理想的には、アンプは容量性負荷でも発振せず、低速になるだけの十分な位相マージンを持っているはずです。実際には、大きな電力をドライブするアンプは、発振を防止するために重い容量性負荷から絶縁する必要があります。この絶縁は通常、アンプ出力と直列にインダクタを接続して行います。多くのアプリケーションでは、10Ω抵抗と並列に1μHインダクタを接続するだけで十分です。

### 出力ABバイアス電流の設定

出力AB静止電流の設定には調整は不要です。内部オペアンプは各センス(ピン5およびピン8)と出力間を強制的に $V_{AB} = \pm 20mV$ にします。静止レベルでは出力電流は次式のとおり設定されます。

$$I_{AB} = 20mV/R_{SENSE}$$

LT1166にはヒート・シンクは必要なく、またサーマル・トラッキングのためにヒート・シンクに実装する必要もありません。 $V_{AB}$ の温度係数は約0.3%/°Cで、これはパワー・トランジスタの温度ではなく、LT1166の接合部温度で設定されます。

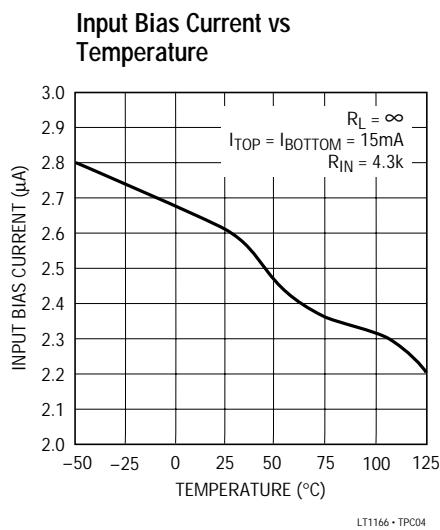

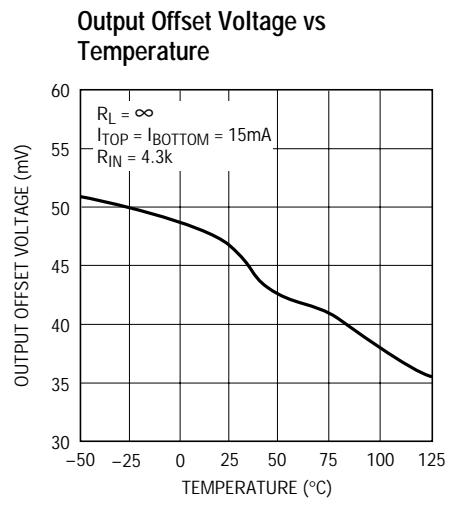

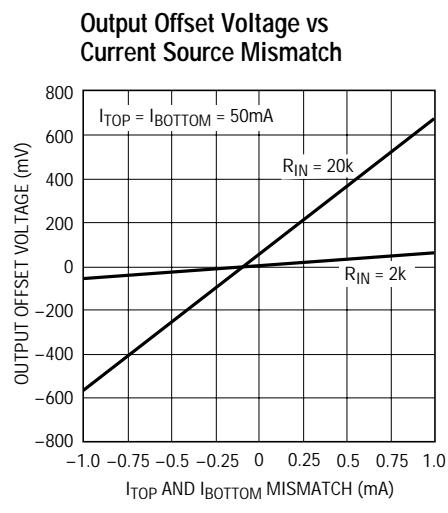

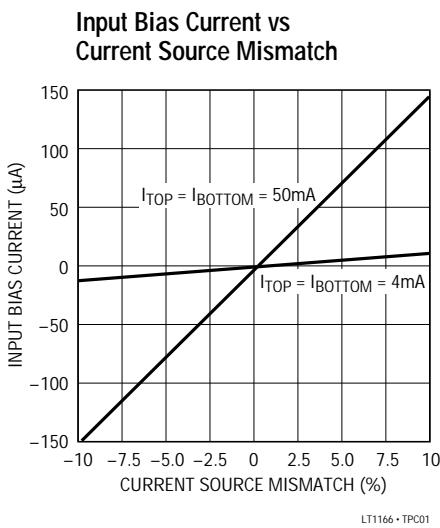

### 出力オフセット電圧および入力バイアス電流

出力オフセット電圧は、 $R_{IN}$ の値と外部電流源 $I_{TOP}$ および $I_{BOTTOM}$ 間の不整合によって生じます(標準性能特性曲線を参照)。 $I_{TOP}$ および $I_{BOTTOM}$ の整合誤差は32:1入力電流ミラーによって減少しますが、入力抵抗 $R_{IN}$ によって増倍されます。

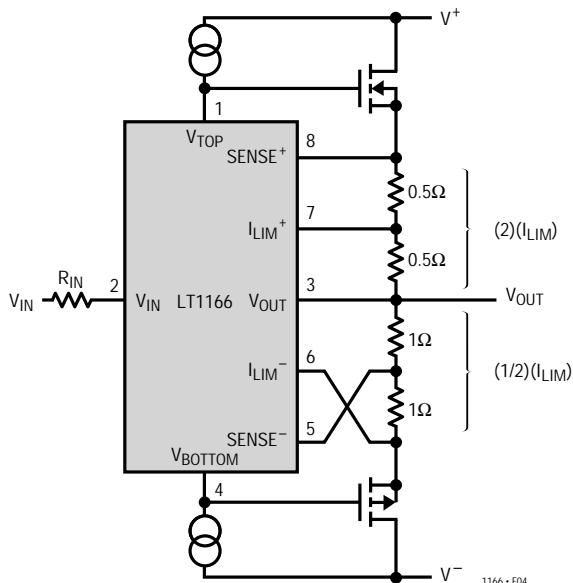

### 電流制限

電流制限をアクティブにする電圧は±1.3Vです。出力トランジスタを保護する最も単純な方法は、電流制限ピン6と7をセンス・ピン5と8に接続することです。1Ωセンス抵抗を使用して、1.3Aの電流制限を設定できます。電流制限回路がハード制限で発振しないようにするには、図1に示すとおりセンス・ピンと $I_{LIM}$ の間に $RQ(1k\Omega)$ および $1\mu F$ を接続する必要があります。

センス抵抗はタップ・アップまたはタップ・ダウンして、パワー・トランジスタのABバイアス電流を変化させないで、電流制限を増大または減少させることができます。

## アプリケーション情報

ます。図4に制限電流を2倍または1/2にするセンス抵抗のタッピング方法を示します。

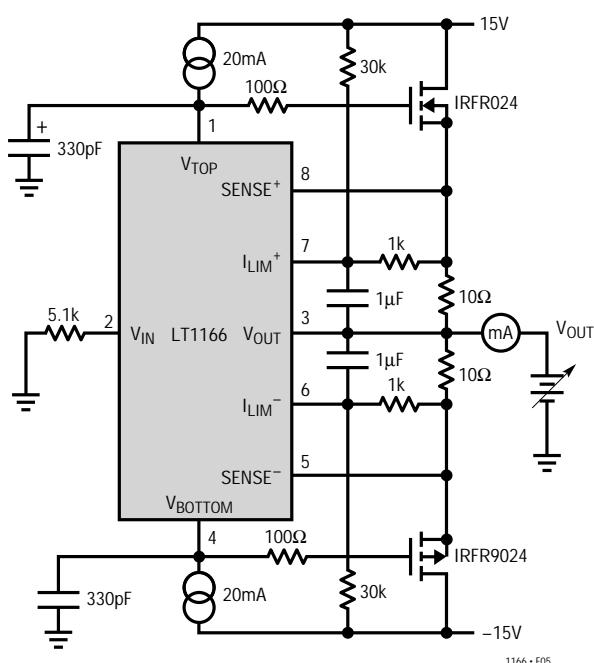

図5に示すとおり、電源から $I_{LIM}$ ピンに2本の抵抗(標準30k)を接続すれば、通常または“矩形”電流制限にフォルドバック電流制限を追加することができます。矩形電流

制限では、最大出力電流はパワー・デバイス両端の電圧とは無関係です。フォルドバック制限では、単に出力電流が出力電圧に関係付けられます。この方式では出力デバイスに消費電力の制限が課されます。パワー・デバイスの電圧が大きくなるほど、得られる出力電流が減少します。これを図6に(図5の回路の)出力電圧対出力電流として示します。

Figure 4. Tapping Current Limit Resistors

Figure 5. Unity Gain Buffer Amp with Foldback Current Limit

Figure 6. Output Current vs Output Voltage

## シャント・レギュレータのドライブ

入力相互コンダクタンス段をドライブせずに、シャント・レギュレータを直接電流ドライブすることができます。この方法には速度が向上する利点があり、 $g_m$ 段を補償する必要がなくなります。ピン2をフロートさせると、LT1166を帰還ループの内側に置き、バイアス電流源を通してドライブすることができます。入力相互コンダクタンス段はバイアスされたままで、回路動作に影響を与えることはありません。図7の $R_L$ を使用すれば、入力信号でオペアンプの電源電流を変調することができます。このオペアンプは、電源リードを電流源出力とするV/Iコンバータとして機能します。負荷抵抗とオペアンプの正入力は、LT1166の出力に接続され、 $A_V = 1V/V$ とするために帰還されます。コンデンサ $C_F$ は $I_{TOP}$ と $I_{BOTTOM}$ 間の不整合による出力 $V_{OS}$ をなくし、DCにポールを形成し、 $1/R_F C_F$ にゼロを形成します。MOSFETの位相がループの安定性を低下させる前に、オペアンプの利得が $-1V/V$ となるようにゼロ周波数を選択します。

## アプリケーション情報

### アプリケーション回路

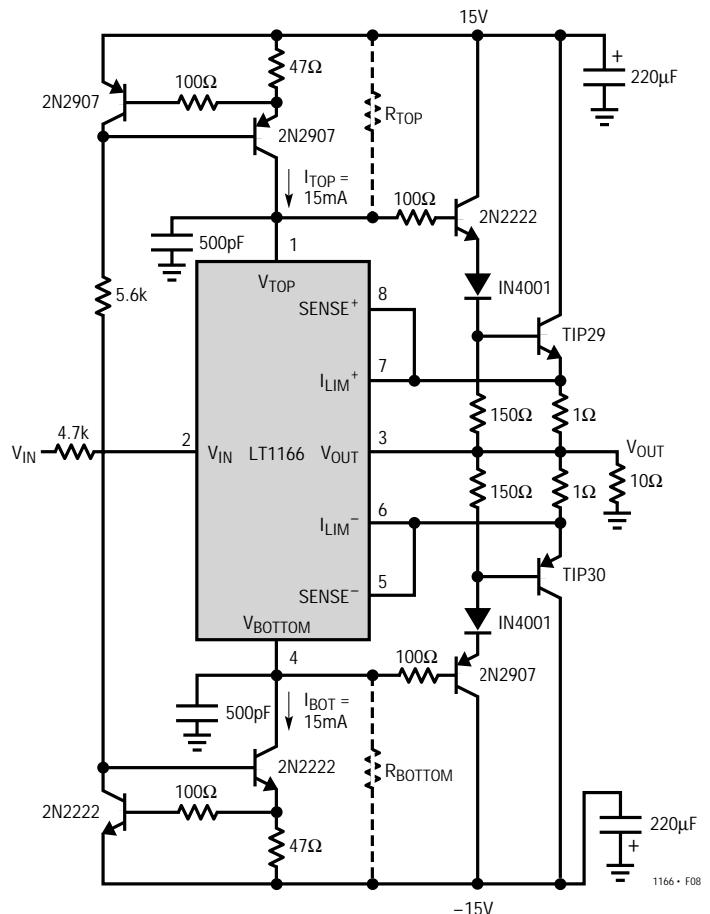

#### バイポーラ・バッファ

LT1166は、図1のユニティ・ゲイン・バッファと同様、図8のようにバイポーラ・トランジスタをバイアスするのに使用できます。LT1166の最小動作電圧は $\pm 2V$ であるため、出力段から適切な電圧でバイアスする必要があります。これを行う最も単純な方法は、ダーリントン・

ドライバと直列ダイオードを使用することです。LT1166にはサーマル・トラッキング回路がないため調整が不要で、パワー・デバイスとともにヒートシンクに実装する必要もありません。 $R_{TOP}$ と $R_{BOTTOM}$ を使用して、 $I_{TOP}$ と $I_{BOTTOM}$ を置き換えることができます。標準性能特性曲線を参照してください。

Figure 7. Current Source Drive

Figure 8. Bipolar Buffer Amp

## アプリケーション情報

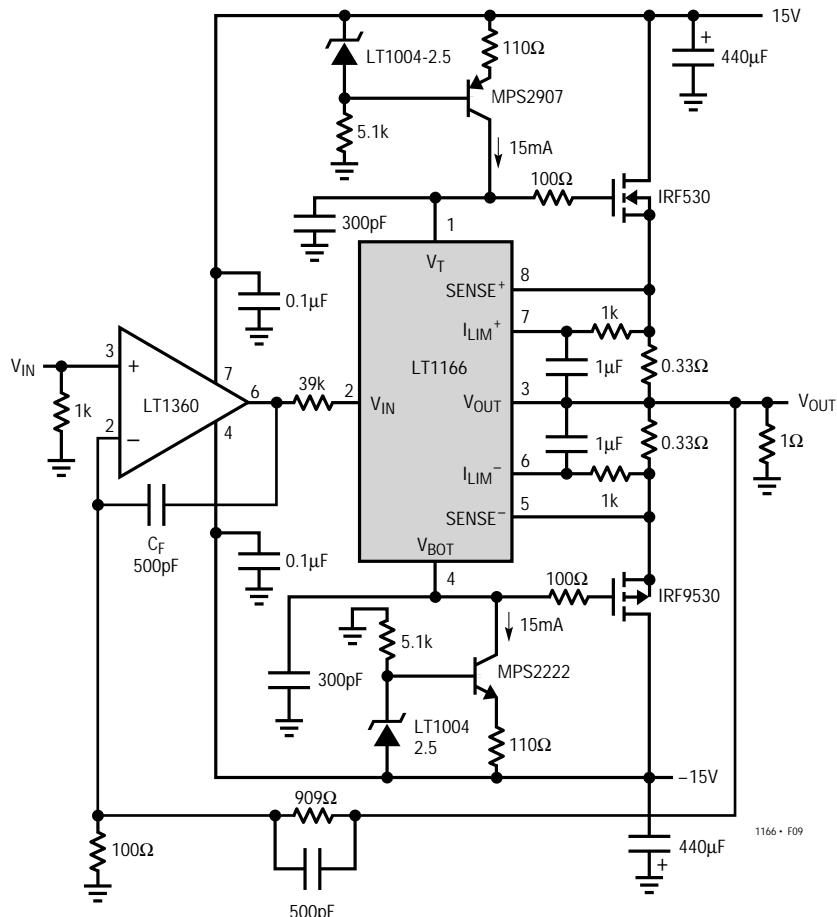

### 電圧利得の追加

図9の回路は、図1の回路に電圧利得を追加します。低周波数ではLT1166はLT1360の帰還ループ内にあるため、

利得誤差と $V_{OS}$ が減少し、閉ループ利得は10V/Vです。

Figure 9. Power Op Amp  $A_V = 10$

**Figure 10. Power Amp Driving 1Ω Load**

**Figure 11. Power Amp at 6A Current Limit**

## アプリケーション情報

### 1A可変電圧リファレンス

図12の回路はLT1166をLT1431との帰還ループ内に使用して、電圧リファレンスにある“傾向”を持たせます。この5Vリファレンスは $\pm 1\text{A}$ をドライブでき、出力で0.4%の許容差を維持します。他の出力電圧が必要な場合は、LT1143の内部5k抵抗の代わりに外部抵抗を使用することができます。

### 高電圧アプリケーション回路

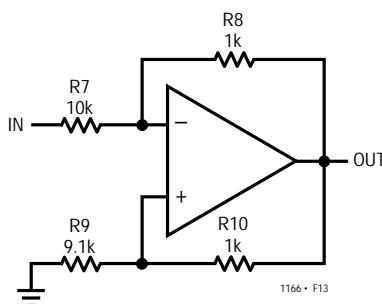

オペアンプを高電圧アプリケーションで使用するには、アンプの同相電圧をその出力に限定する手法を使用する

必要があります。以下のアプリケーションでは、サスペンデッド電源動作で動作するアンプを利用します(図13)。サスペンデッド電源の説明は、『Linear Technology Magazine Volume IV Number 2』を参照してください。サスペンデッド電源動作に使用する利得設定抵抗には、許容差が小さなものを使用してください。そうしないと、適切な利得が得られません。例：1%抵抗では利得が75%も変動することがあります、0.1%抵抗では誤差は5%以下に収まります。図13に記載した値を使用する場合、利得計算式は以下のとおりです。

$$A_V = \frac{R_8(R_9 + R_{10})}{(R_8 \cdot R_9) - (R_7 \cdot R_{10})} = -11.22$$

Figure 12.  $\pm 1\text{A}$ , 5V Voltage Reference

1166 • F12

Figure 13. Op Amp in Suspended-Supply Operation

## アプリケーション情報

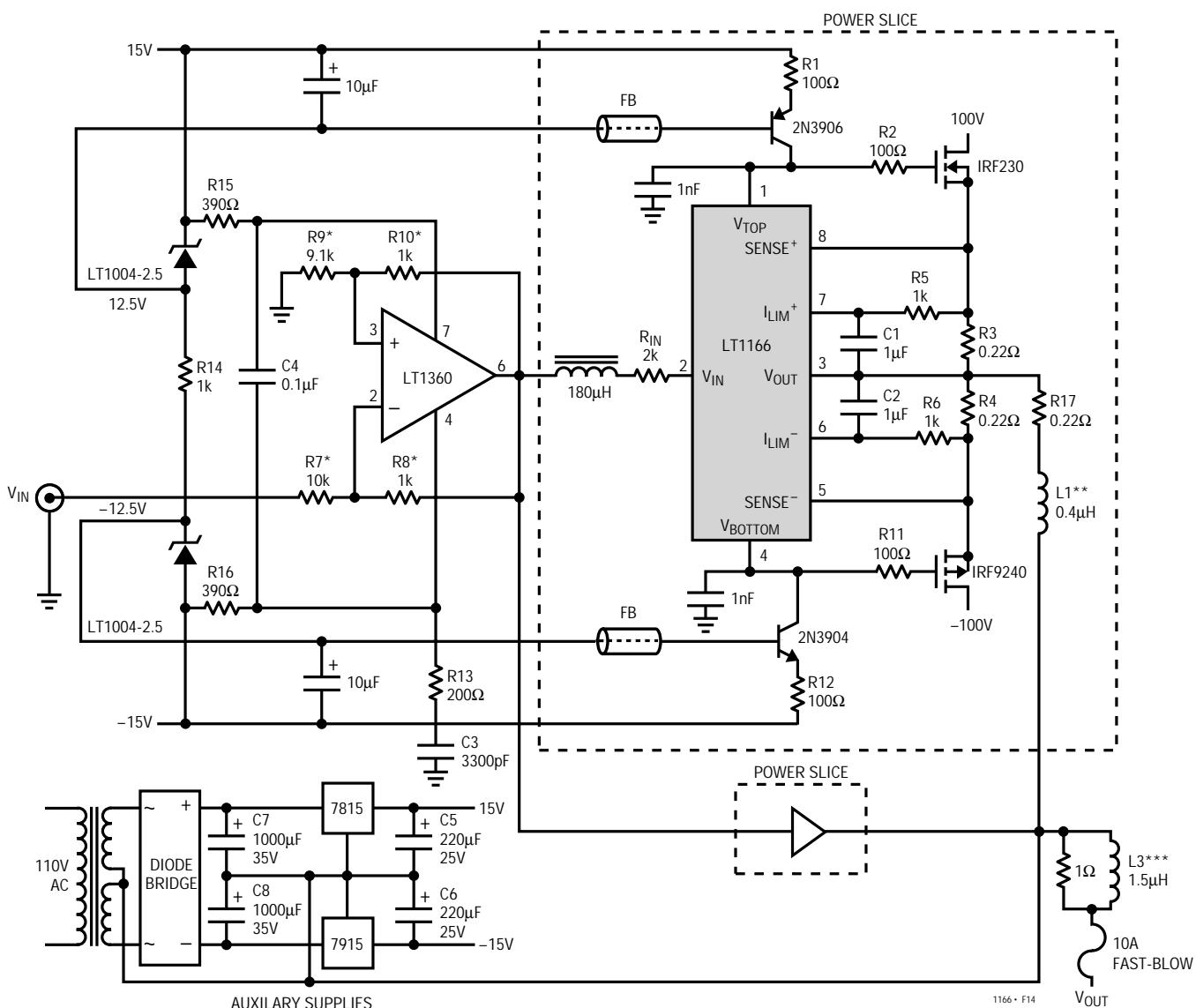

## 並列動作

並列動作は複数のパワー・ドライバを接続して、より大きな出力電力を得る有効な手段です。必要なのは小さなパラスト抵抗1個だけで、ドライバと絶縁インダクタ間で確実に電流を分流させ、高周波数でドライバを分離します。図14では、1個のパワー・スライスが $\pm 6A$ ( $100V_{PK}$ )または $300W$  RMSを16に供給することができます。もう1つのスライスを追加すれば、8に供給することができます。もう1つのスライスを追加すれば、8に供給するパワー出力を $600W$  RMSに増幅します。2つ以上のドライバを追加すれば、理論的には4に供給するパワー出

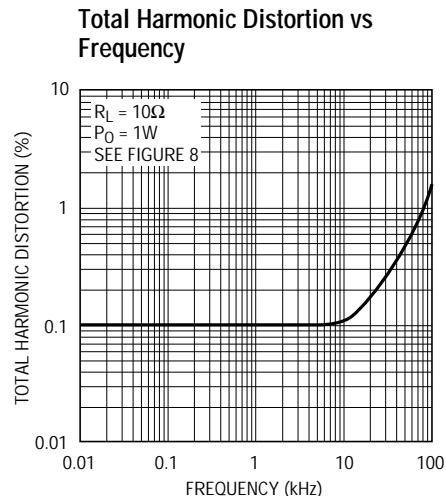

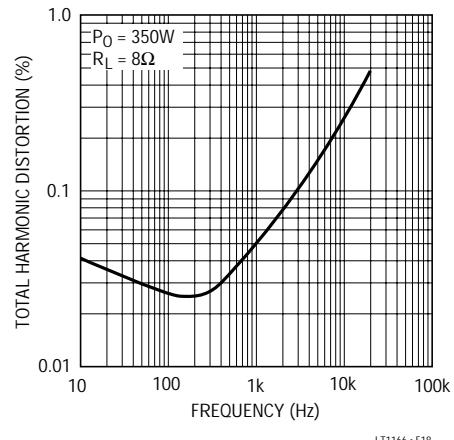

力は $1200W$  RMSに増加します。センス抵抗のIR損失、 $10A$ でのFET  $R_{ON}$ 抵抗、および電源のふらつきのため、図14の回路は実際には8に $350W$  RMSを供給します。図15から図18に性能写真とTHD対周波数プロットを示します。周波数補償は $2k$ の入力抵抗、 $180\mu H$ のインダクタ、および $1nF$ の補償コンデンサによって行われます。補助電源の共通ノードはアンプ出力に接続され、フローティング $\pm 15V$ 電源を構成します。

\* 0.1% RESISTORS

\*\* 4 TURNS T37-52 (MICROMETALS)

\*\*\* 6 TURNS T80-52 (MICROMETALS)

Figure 14. 350W Shaker Table Amplifier

## アプリケーション情報

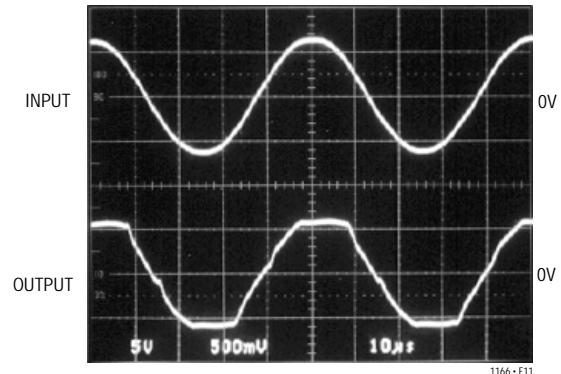

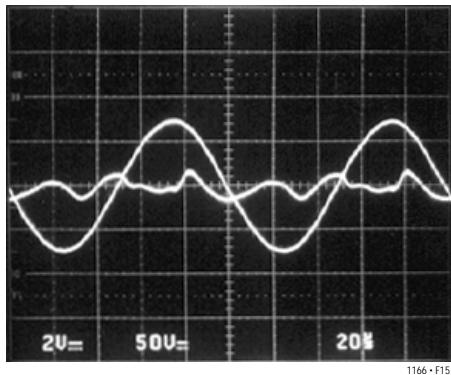

Figure 15. 0.3% THD at 10kHz,  $P_0 = 350W$ ,  $R_L = 8\Omega$

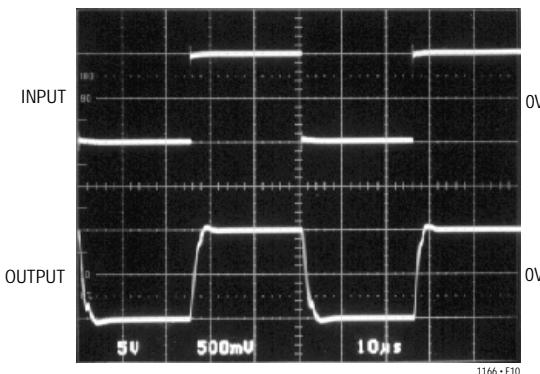

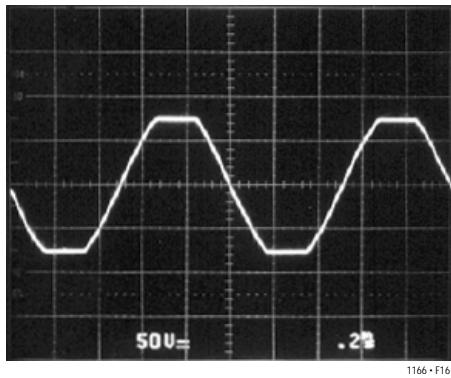

Figure 17. 2kHz Square-Wave,  $C_L = 1\mu F$

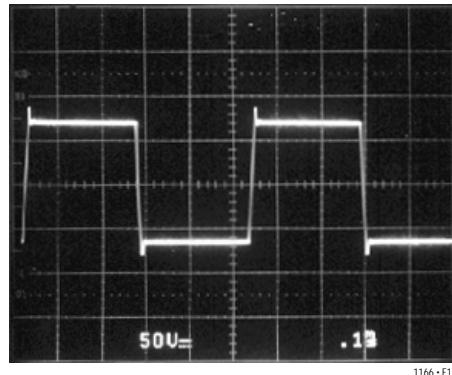

Figure 16. Clipping at 1kHz,  $R_L = 8\Omega$

Figure 18. THD vs Frequency

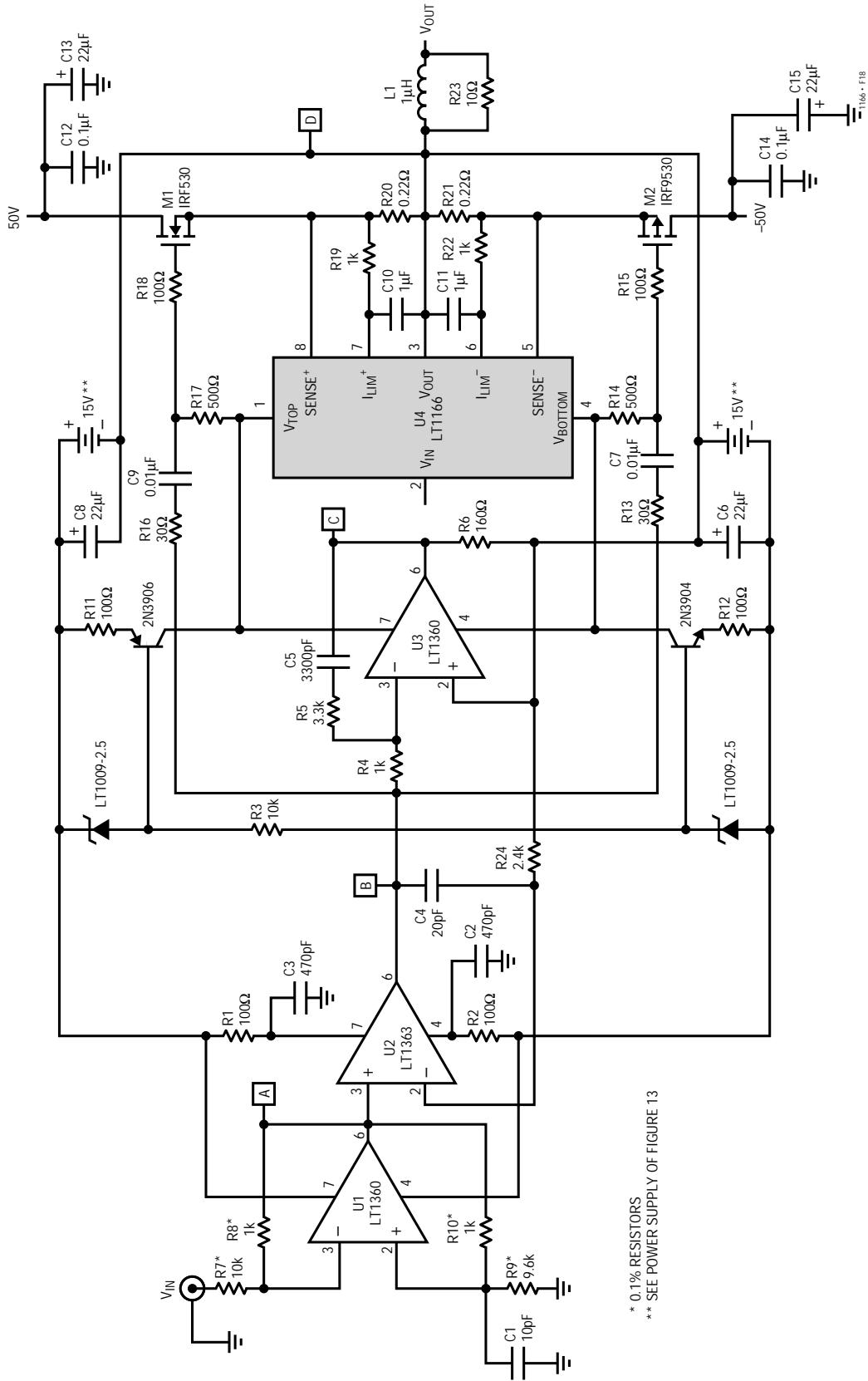

## 100Wオーディオ・パワー・アンプ

低歪みオーディオ・アンプの詳細を図19に示します。CMRR特性が優れている理由からLT1360( U1という名前が付けられている )が選択され、サスペンデッド電源モードにて - 26.5V/Vの閉ループ利得で動作します。U1の±15V電源は、D点の出力で効果的にブーストストラップされ、図14に示すとおり構成されます。 $V_{IN}$ に3V<sub>P-P</sub>信号が入力されると、A点では出力に80V<sub>PP</sub>の信号が現れます。抵抗7~10は、U1の利得を - 26.5V/Vに設定し、C1はU1のCMRRで生成される追加極を補償します。回路の残りの部分( A点からD点 )は、超低歪みのユニティ・ゲイン・バッファになります。

ユニティ・ゲイン・バッファの主要部品はU4( LT1166 )です。このコントローラには2つの重要な機能があります。すなわち、R20とR21の電圧積を一定に維持しながら、M1とM2のゲート間のDC電圧を変化させること。そして、電流制限を行って、短絡時にM1とM2を保護す

ることです。U3の役割は、M1とM2のゲートをドライブすることです。このアンプの実際の出力は、一見したところ考えられる点Cではなく電源ピンです。R6を流れる電流を使用して電源電流を変調し、 $V_{TOP}$ および $V_{BOTTOM}$ をドライブします。U3の出力インピーダンス( 電源ピンを通した )は非常に高いため、20kHzでの歪みを非常に低く抑えるのに必要な速度と精度でM1およびM2の容量性入力をドライブすることはできません。U2の目的は、低出力インピーダンスを通して、M1およびM2のゲート容量をドライブし、M1およびM2の相互コンダクタンスの非直線性を低減することです。R24とC4は、U2がU3とU4を管理しなくなるが、利得が1になると自身を管理するような周波数よりも高い周波数を設定します。R1/R2とC2/C3はCMRRフィードスルーに対する補償部品です。アンプの性能を示す曲線を図20から図22に示します。

## APPLICATIONS INFORMATION

Figure 19. 100W Audio Amplifier

## APPLICATIONS INFORMATION

$R_L = 8\Omega$

$f = 8\text{kHz}$

Figure 20. Square Wave Response Into  $8\Omega$

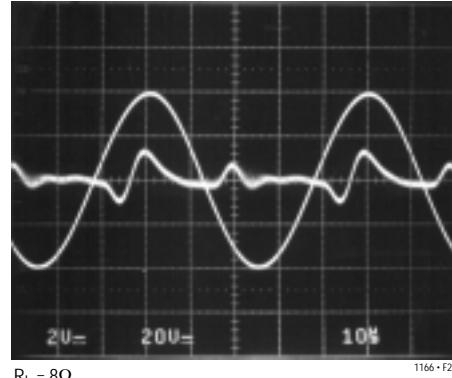

$R_L = 8\Omega$

$f = 20\text{kHz}$

Figure 21. 100W 20kHz Sine Wave and Its Distortion

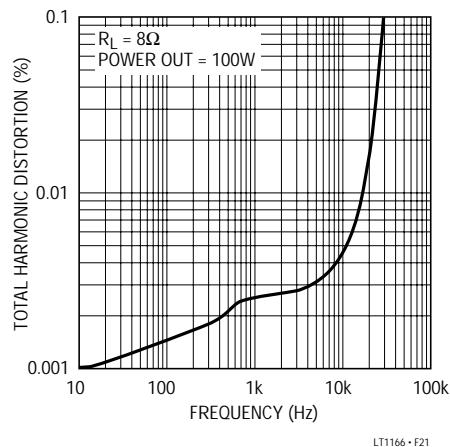

Figure 22. THD vs Frequency

## SIMPLIFIED SCHEMATIC

## RELATED PARTS

| PART NUMBER | DESCRIPTION                             | COMMENTS                                                                          |

|-------------|-----------------------------------------|-----------------------------------------------------------------------------------|

| LT1010      | Fast $\pm 150\text{mA}$ Power Buffer    | Ideal for Boosting Op Amp Output Current                                          |

| LT1105      | Off-Line Switching Regulator            | Generate High Power Supplies                                                      |

| LT1206      | 250mA/60MHz Current Feedback Amplifier  | C-Load <sup>TM</sup> Op Amp with Shutdown and $900\text{V}/\mu\text{s}$ Slew Rate |

| LT1210      | 1A/40MHz Current Feedback Amplifier     | C-Load Op Amp with Shutdown and $700\text{V}/\mu\text{s}$ Slew Rate               |

| LT1270A     | 10A High Efficiency Switching Regulator | Use as Battery Boost Converter                                                    |

| LT1360      | 50MHz, $800\text{V}/\mu\text{s}$ Op Amp | $\pm 15\text{V}$ , Ideal for Driving Capacitive Loads                             |

| LT1363      | 70MHz, $800\text{V}/\mu\text{s}$ Op Amp | $\pm 15\text{V}$ , Very High Speed, C-Load                                        |

C-Load is a registered trademark of Linear Technology