## 狭帯域および広帯域 RF トランシーバ

### 特長

- ▶ 1×1 高集積トランシーバ

- ▶ 周波数範囲 : 30MHz～6000MHz

- ▶ トランスマッタおよびレシーバの帯域幅 : 12kHz～40MHz

- ▶ 全機能内蔵型のフラクショナル N 方式 RF シンセサイザを 2 個装備

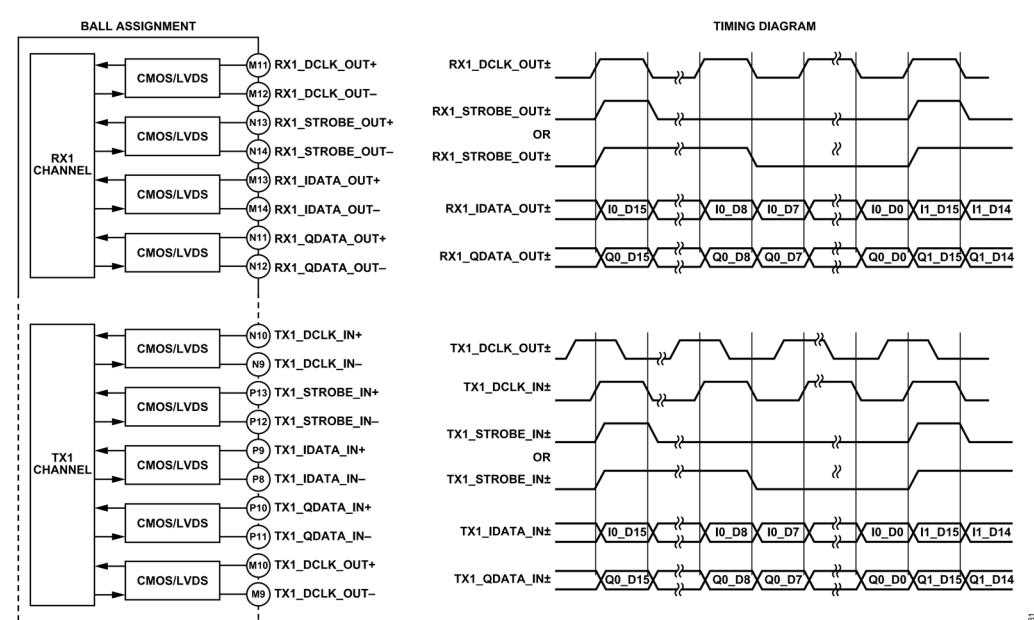

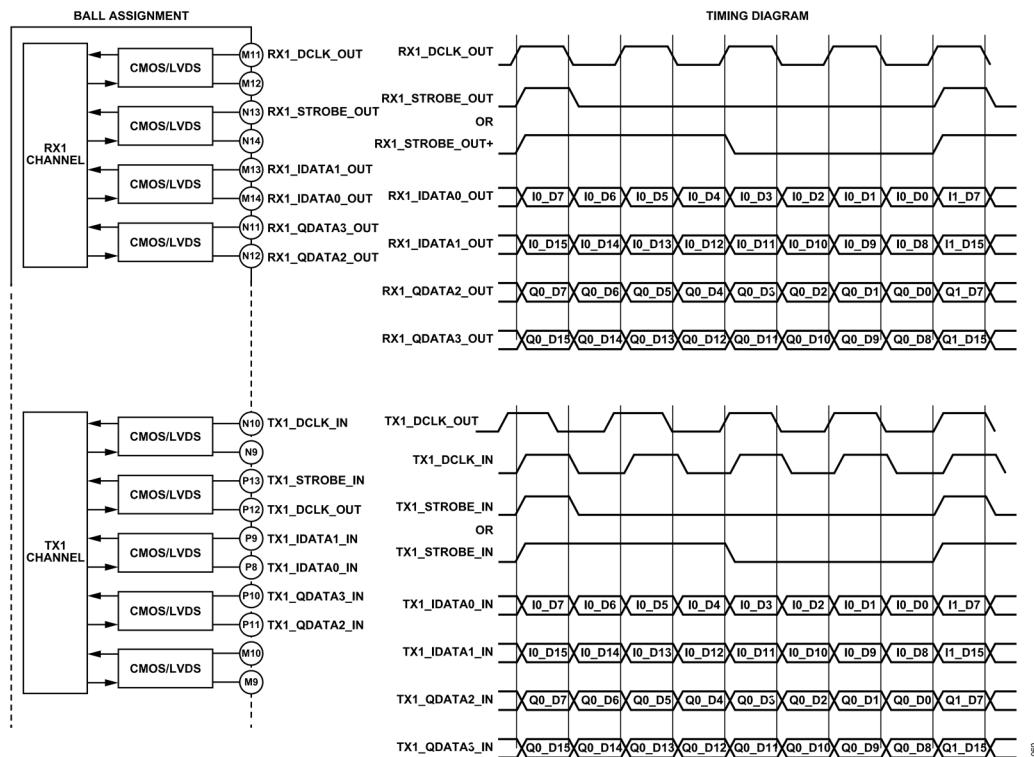

- ▶ LVDS および CMOS 同期シリアル・データ・インターフェースのオプション

- ▶ 低消費電力のモニタ・モードおよびスリープ・モード

- ▶ マルチチップ同期機能

- ▶ 高速周波数ホッピング

- ▶ プロファイルを動的に切り替えることにより動的なデータ・レートとサンプリング・レートを実現

- ▶ 狹帯域波形および広帯域波形に対応する完全統合型 DPD

- ▶ 4 線式 SPI を介して全機能をプログラム可能

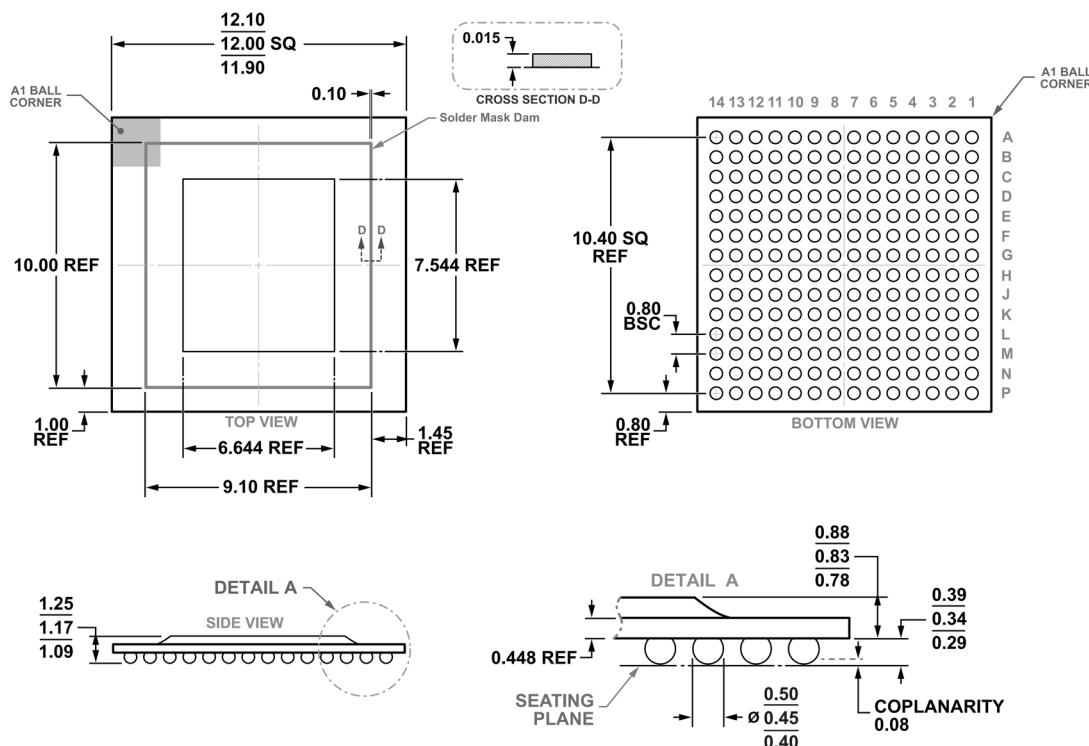

- ▶ 12mm × 12mm、196 ポール CSP\_BGA

### アプリケーション

- ▶ 基幹系通信

- ▶ 超短波 (VHF)、極超短波 (UHF)、6GHz までのセルラ式携帯電話

- ▶ 時分割複信 (TDD)

### 概要

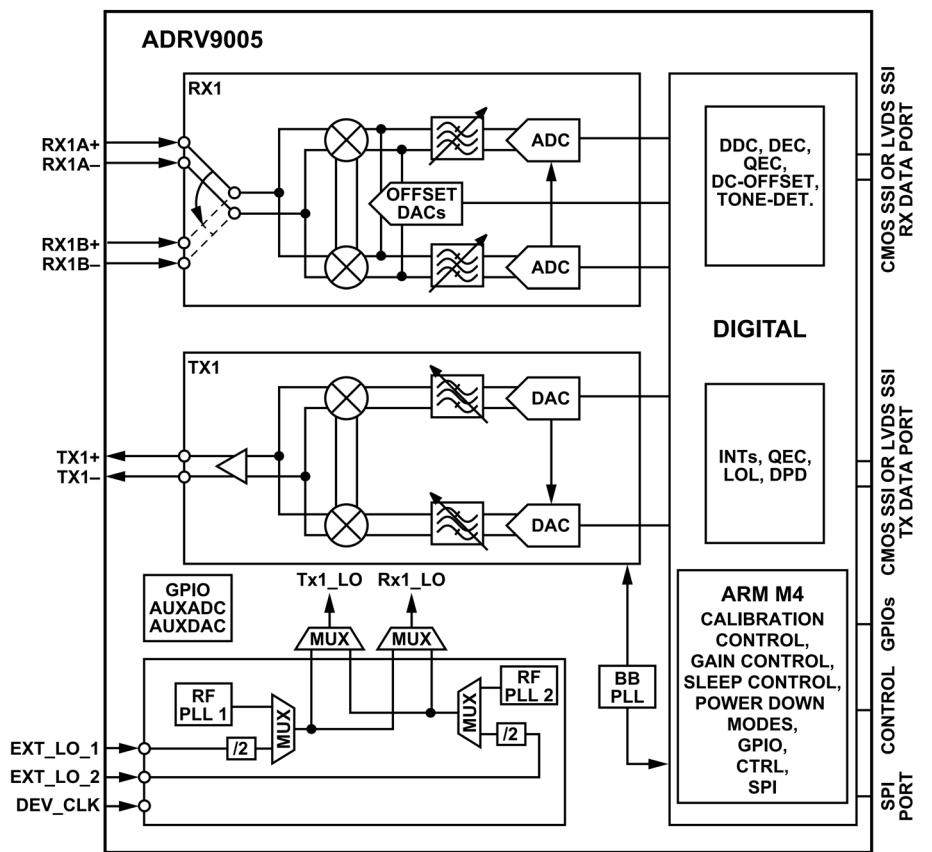

ADRV9005 は、シンセサイザ機能およびデジタル信号処理機能を統合した高集積 RF トランシーバです。

ADRV9005 は、性能と消費電力の関係をシステムに応じて最適化するよう設計された、高性能で直線性が高い、高ダイナミック・レンジのトランシーバです。このデバイスは設定変更が可能で、要求の厳しい、低消費電力でバッテリ駆動の携帯機器に最適です。ADRV9005 は、30MHz～6000MHz で動作し、UHF、VHF、産業、科学、医療用 (ISM) バンド、狭帯域 (kHz) のセルラ周波数帯、最大 40MHz の広帯域動作に対応します。

トランシーバは、最高水準のノイズ指数と直線性を持つ直接変換信号経路で構成されています。レシーバとトランスマッタを一体化した各サブシステムは、DC オフセット補正回路、直交誤差補正回路 (QEC)、プログラマブル・デジタル・フィルタを内蔵しているため、デジタル・ベースバンドではこれらの機能が不要です。また、補助 A/D コンバータ (ADC)、補助 D/A コンバータ (DAC)、汎用入出力 (GPIO) などのいくつかの補助機能を内蔵しているため、モニタリングや制御などの機能を更に追加できます。

完全統合型フェーズ・ロック・ループ (PLL) により、トランスマッタ、レシーバ、クロックの各セクションに対して高性能で低消費電力のフラクショナル N 周波数合成が可能です。注意深い設計とレイアウト技術により、民生用高性能無線アプリケーションに必要な絶縁が実現されます。

電圧制御発振器 (VCO) とループ・フィルタのすべての構成要素が内蔵されており、外付け部品数が最小限に抑えられています。局部発振器 (LO) には、高速ロック・モードを含む柔軟な設定オプションがあります。

トランシーバには、低消費電力のスリープ・モードとモニタ・モードがあり、通信を監視しながらも電力を節約し、ポータブル機器のバッテリ寿命を延ばすことができます。

完全統合型の低消費電力デジタル・プリディストーション (DPD) は、狭帯域信号と広帯域信号の両方に對し最適化されており、これにより、高効率パワー・アンプの直線化が可能になります。

ADRV9005 のコアは、1.0V、1.3V、1.8V のレギュレータから直接給電でき、標準的な 4 線式シリアル・ペリフェラル・インターフェース (SPI) を介して制御されます。その他の電源を使用すれば、適切なデジタル・インターフェース・レベルを提供すると共に、レシーバ、トランスマッタ、補助コンバータの性能を最適化できます。

高データ・レート・インターフェースおよび低データ・レート・インターフェースへの対応は、設定変更可能な CMOS または低電圧差動シグナリング (LVDS) のシリアル同期インターフェース (SSI) を使用して行います。

ADRV9005 は、12mm × 12mm、196 ポールのチップ・スケール・パッケージ・ポール・グリッド・アレイ (CSP\_BGA) を採用しています。

## 目次

|                         |    |

|-------------------------|----|

| 特長                      | 1  |

| アプリケーション                | 1  |

| 概要                      | 1  |

| 機能ブロック図                 | 3  |

| 仕様                      | 4  |

| トランスマッタ仕様               | 4  |

| レシーバ仕様                  | 6  |

| 内部 LO、外部 LO、デバイス・クロック   | 12 |

| デジタル・インターフェースおよび補助コンバータ | 13 |

| 電源仕様                    | 15 |

| 消費電流の推定値（代表値）           | 16 |

| タイミング仕様                 | 18 |

| 絶対最大定格                  | 20 |

| リフロー・プロファイル             | 20 |

| 熱抵抗                     | 20 |

| 静電放電（ESD）定格             | 20 |

| ESD に関する注意              | 20 |

| ピン配置およびピン機能の説明          | 21 |

|                   |    |

|-------------------|----|

| 代表的な性能特性          | 25 |

| 広帯域               | 25 |

| 狭帯域               | 63 |

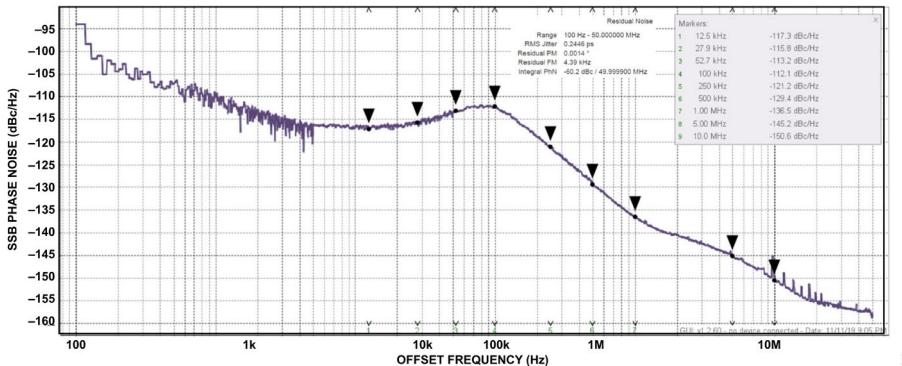

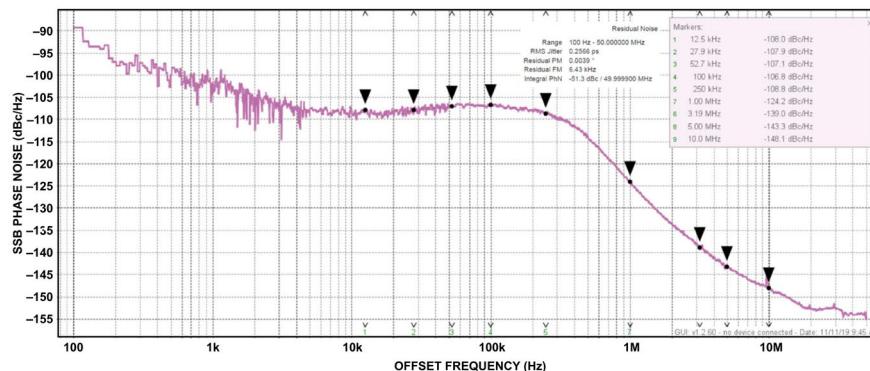

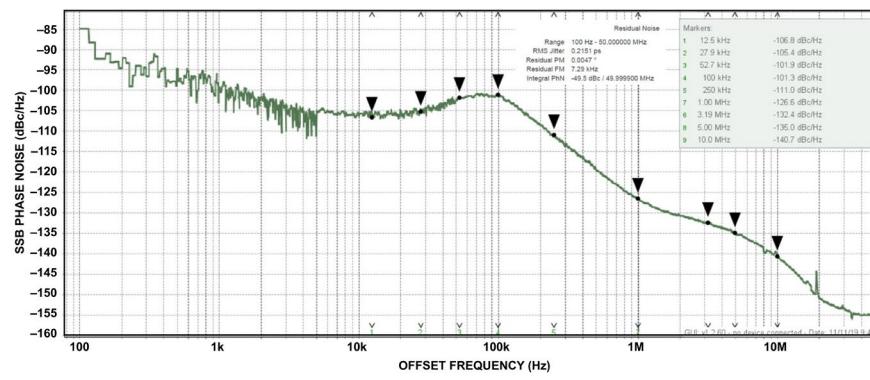

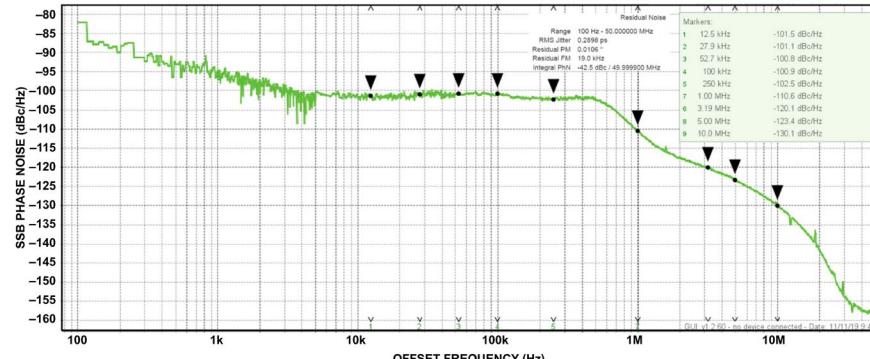

| 位相ノイズ             | 88 |

| 動作原理              | 90 |

| トランスマッタ           | 90 |

| レシーバ              | 91 |

| DPD               | 92 |

| クロック入力            | 92 |

| シンセサイザ            | 92 |

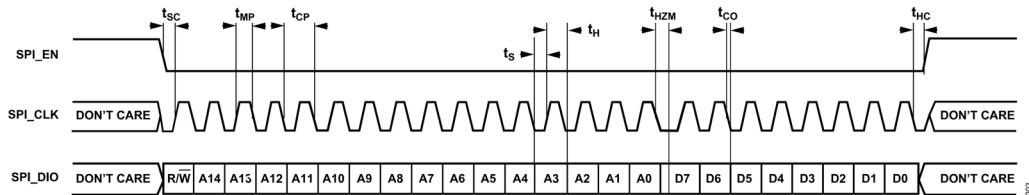

| SPI               | 93 |

| GPIO ピン           | 93 |

| 補助コンバータ           | 93 |

| JTAG バウンダリ・スキャン   | 95 |

| アプリケーション情報        | 96 |

| 電源シーケンス           | 96 |

| デジタル・データ・インターフェース | 96 |

| 外形寸法              | 99 |

| オーダー・ガイド          | 99 |

## 改訂履歴

5/2024—Revision 0: Initial Version

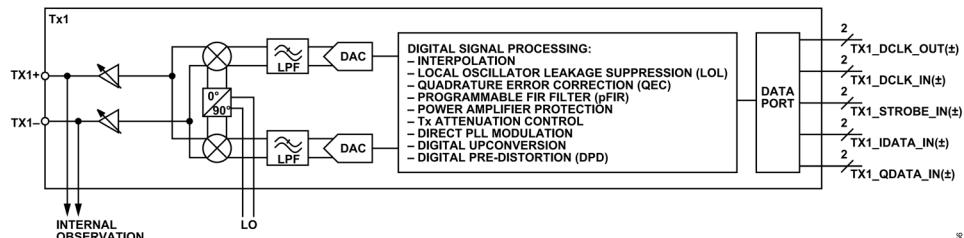

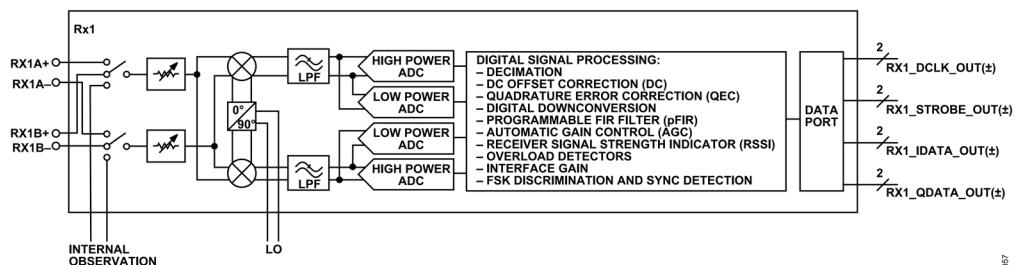

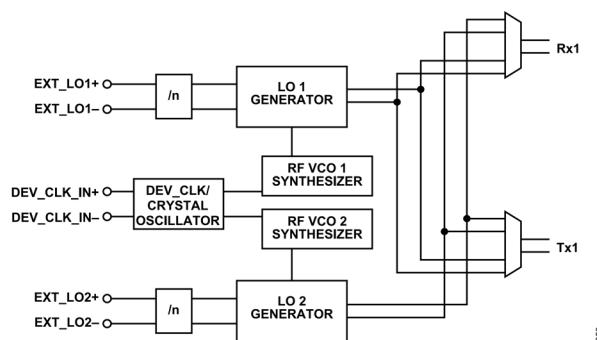

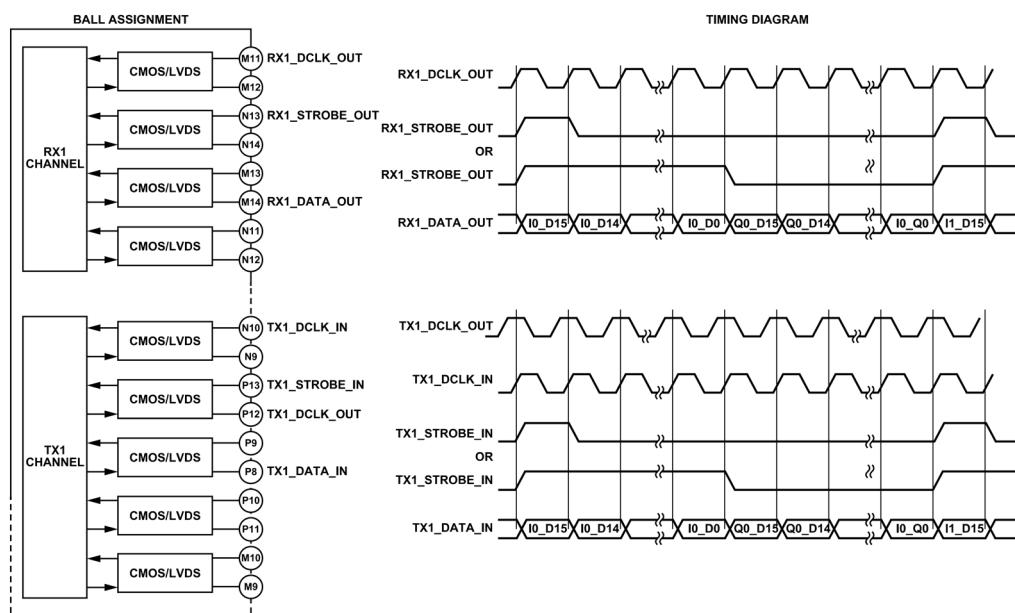

## 機能ブロック図

図 1.

## 仕様

電気的特性は、動作周囲温度範囲、VDDA\_1P0 = 1.0V、VDDA\_1P3 = 1.3V、VDDA\_1P8 = 1.8V、VDD\_1P0 = 1.0V、VDD\_1P8 = 1.8V でのものです。

## トランスマッタ仕様

表 1. トランスマッタ (Tx1)

| Parameter                                                                | Symbol | Min   | Typ  | Max                   | Unit | Test Conditions/Comments                                                                                                                                                                           |

|--------------------------------------------------------------------------|--------|-------|------|-----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CENTER FREQUENCY                                                         |        | 30    | 6000 | MHz                   |      |                                                                                                                                                                                                    |

| TRANSMITTER SYNTHESIS BANDWIDTH                                          |        | 0.012 | 40   | MHz                   |      | Zero-intermediate frequency (IF) mode, see the <a href="#">DPD</a> section for more information                                                                                                    |

| BANDWIDTH FLATNESS                                                       |        | 0.1   |      | dB                    |      | 10 MHz bandwidth span, including digital compensation                                                                                                                                              |

| DEVIATION FROM LINEAR PHASE                                              |        | 1     |      | Degrees               |      | 40 MHz bandwidth                                                                                                                                                                                   |

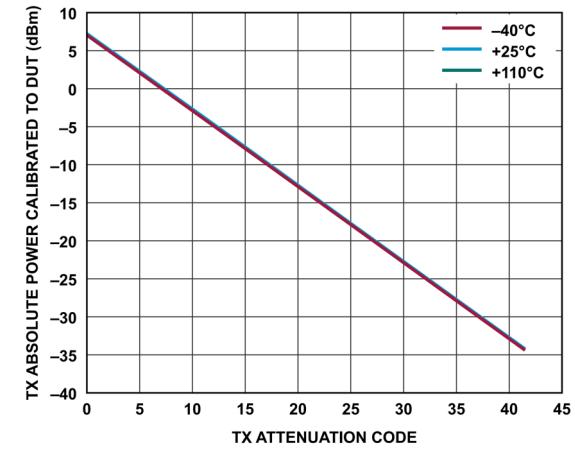

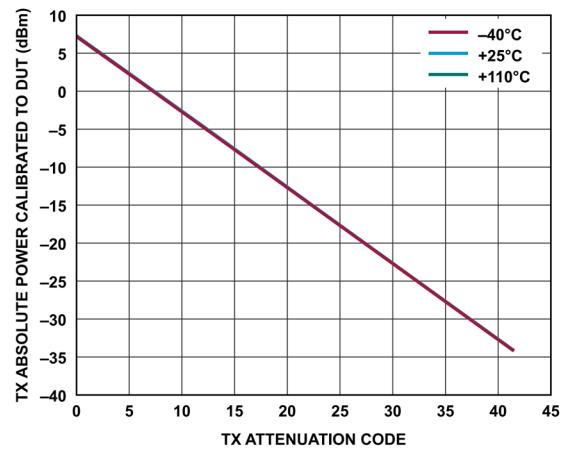

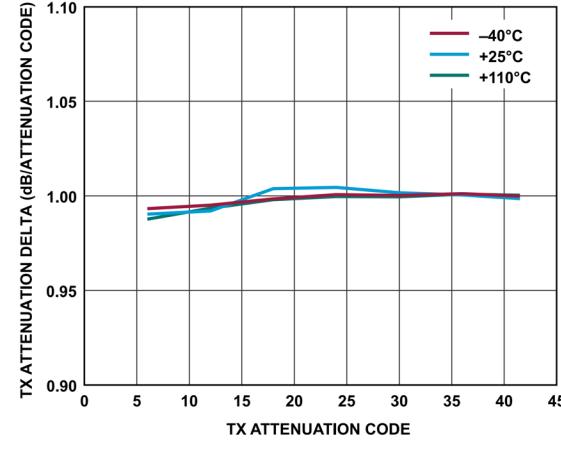

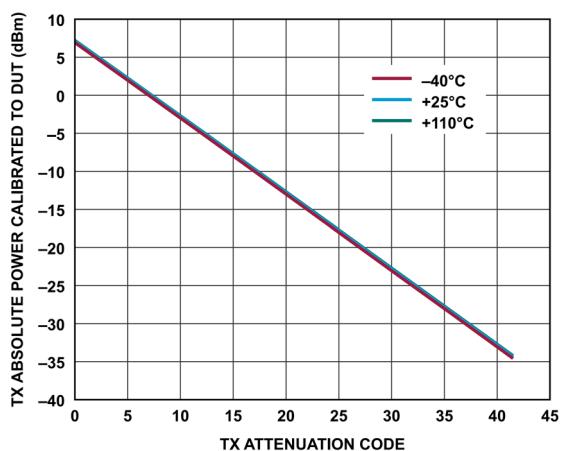

| POWER CONTROL RANGE                                                      |        |       |      |                       |      |                                                                                                                                                                                                    |

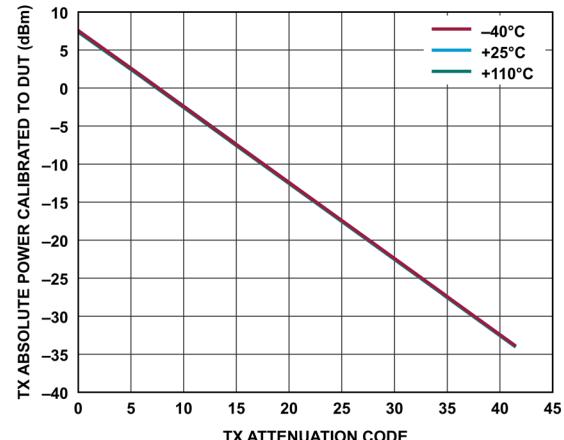

| In-Phase (I) and Quadrature (Q) Mode                                     |        |       | 42   | dB                    |      |                                                                                                                                                                                                    |

| Direct Modulation Mode                                                   |        |       | 12   | dB                    |      |                                                                                                                                                                                                    |

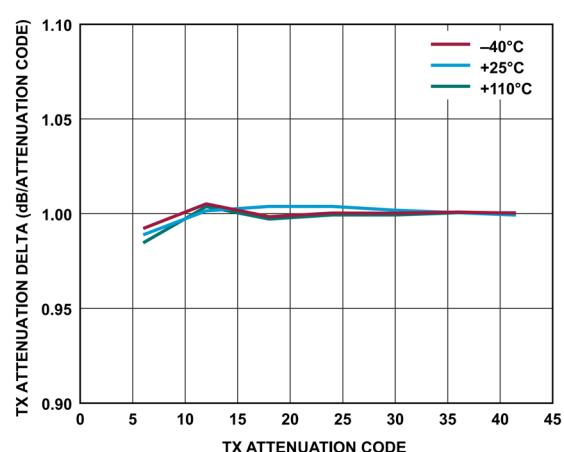

| POWER CONTROL RESOLUTION                                                 |        |       |      |                       |      |                                                                                                                                                                                                    |

| I and Q Mode                                                             |        |       | 0.05 | dB                    |      |                                                                                                                                                                                                    |

| Direct Modulation Mode                                                   |        |       | 0.5  | dB                    |      |                                                                                                                                                                                                    |

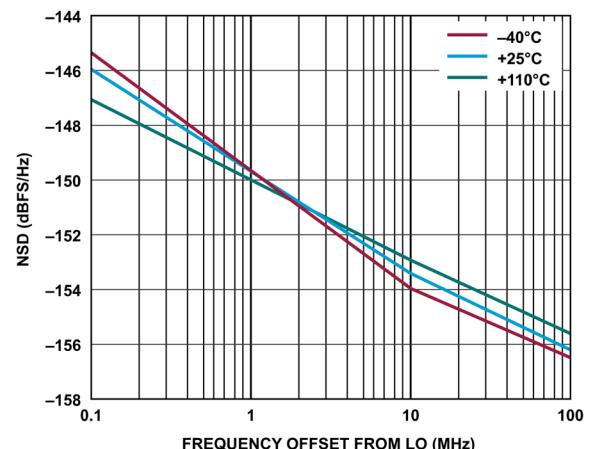

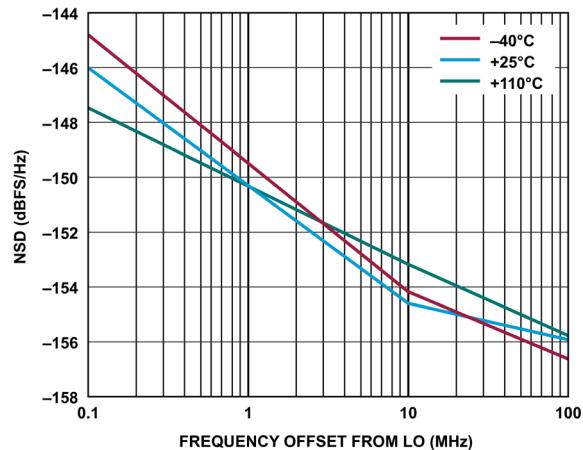

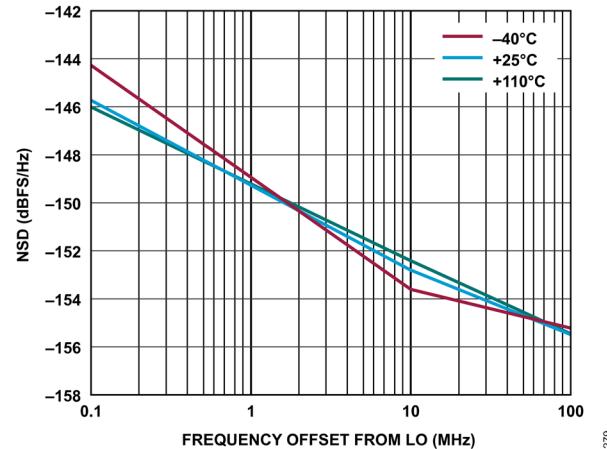

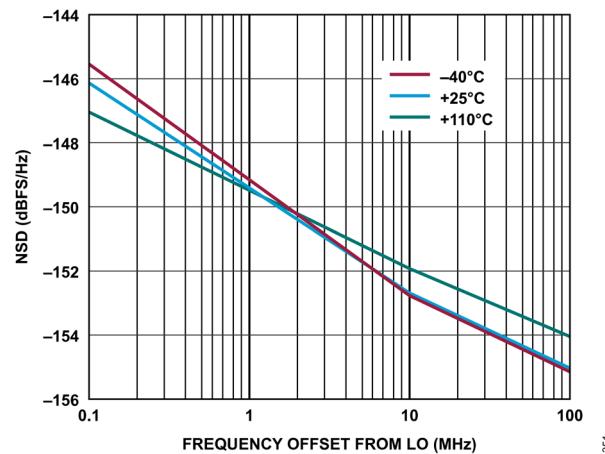

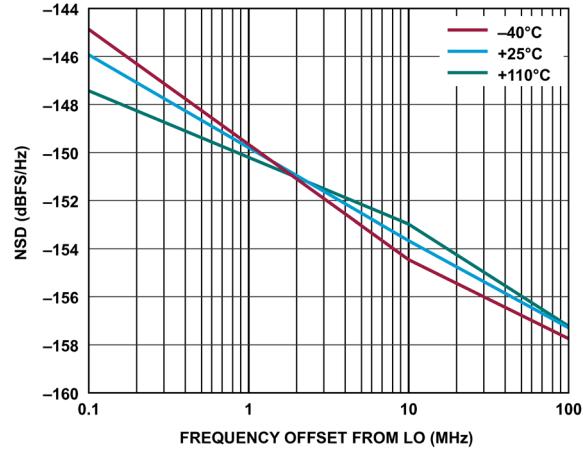

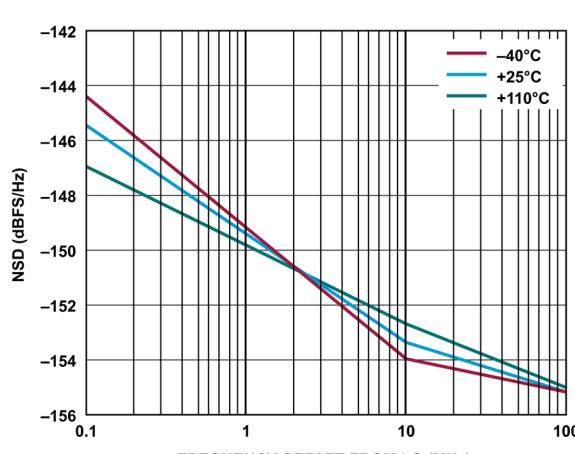

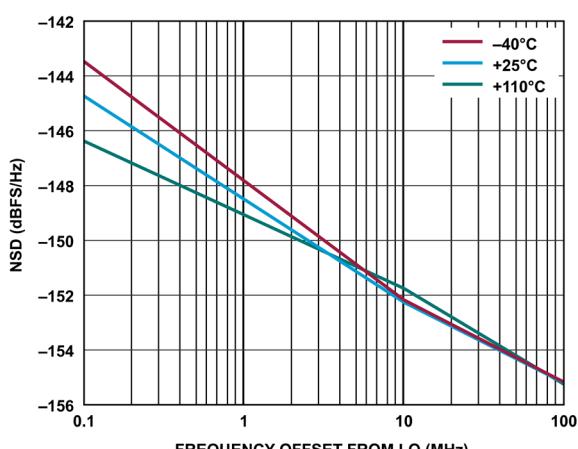

| IN BAND NOISE FLOOR                                                      |        | -154  |      | dBFS <sup>1</sup> /Hz |      | 0 dB attenuation, in band noise falls 1 dB for each dB of attenuation for attenuation settings between 0 dB and 20 dB                                                                              |

| OUT OF BAND NOISE FLOOR                                                  |        | -156  |      | dBFS <sup>1</sup> /Hz |      | 0 dB attenuation with 3 × bandwidth/2 offset                                                                                                                                                       |

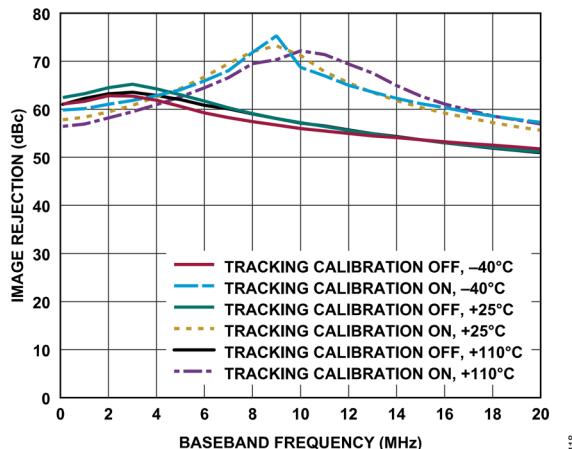

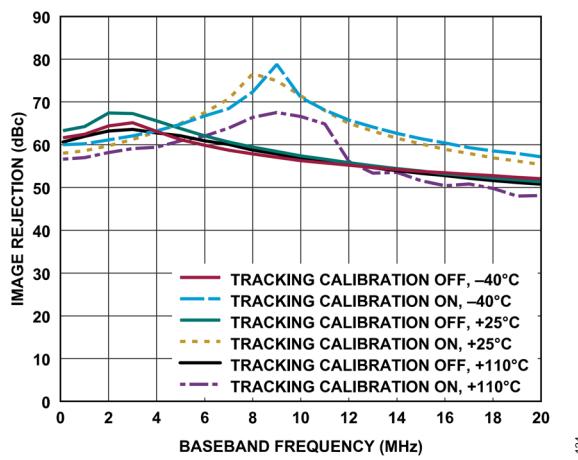

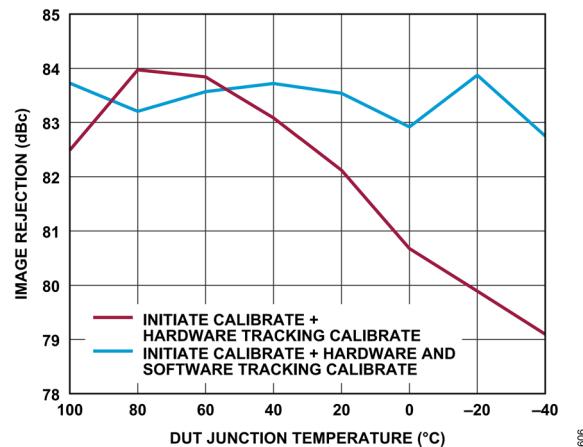

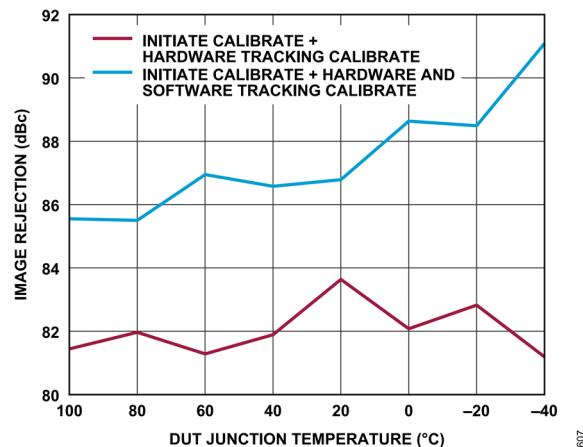

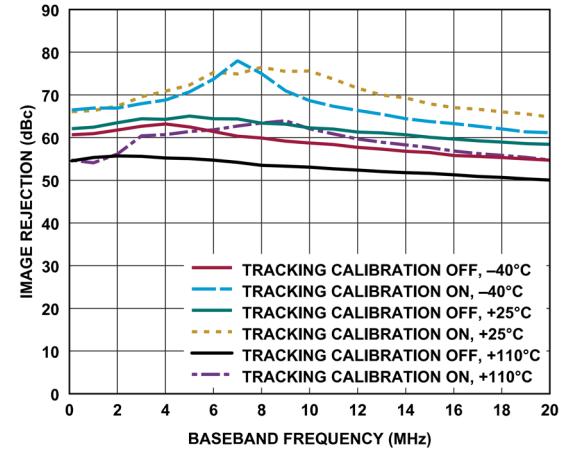

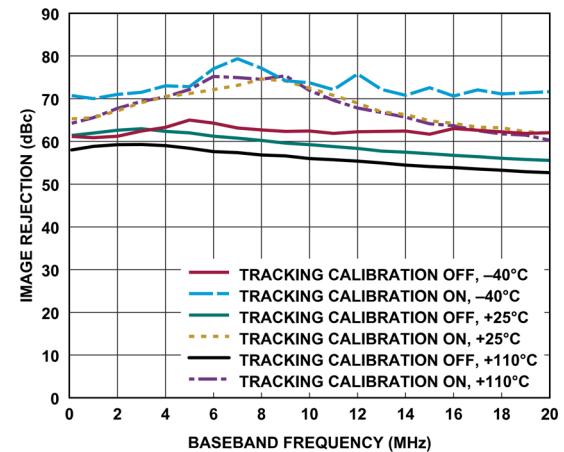

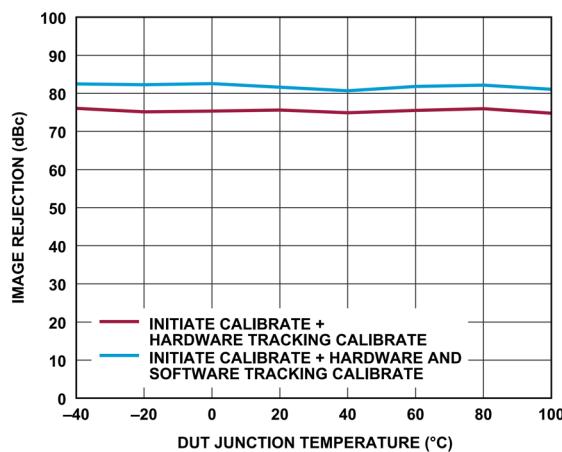

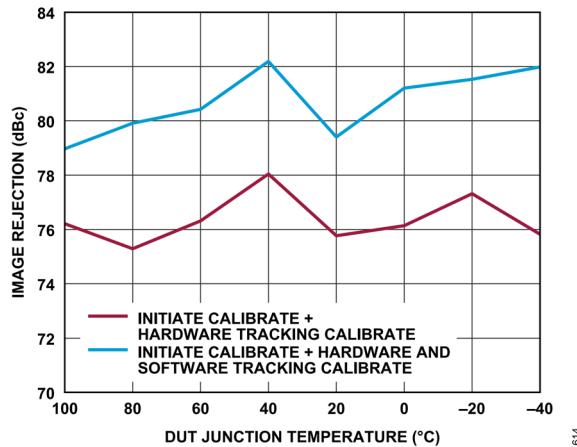

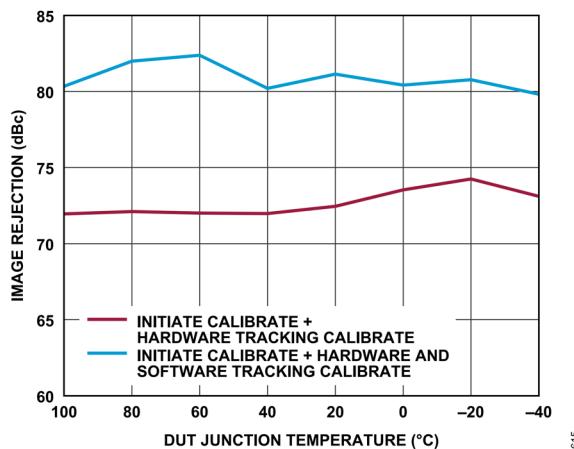

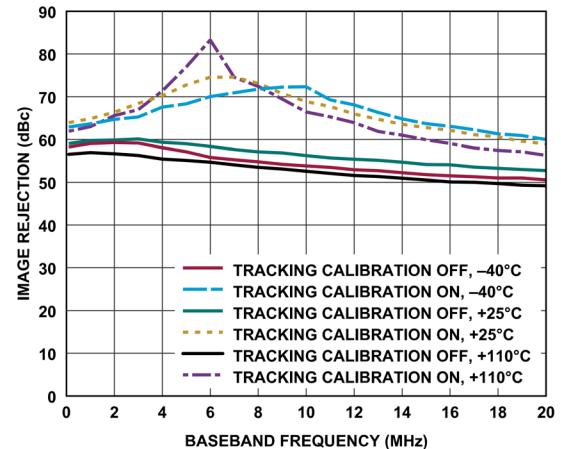

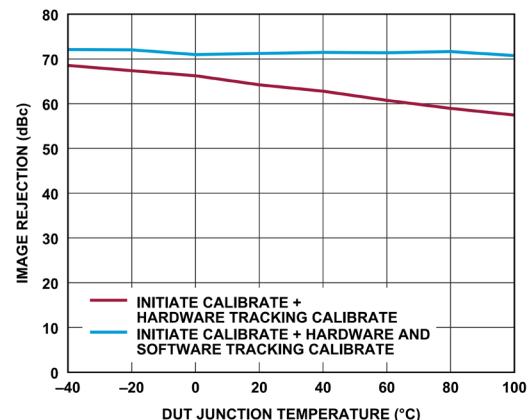

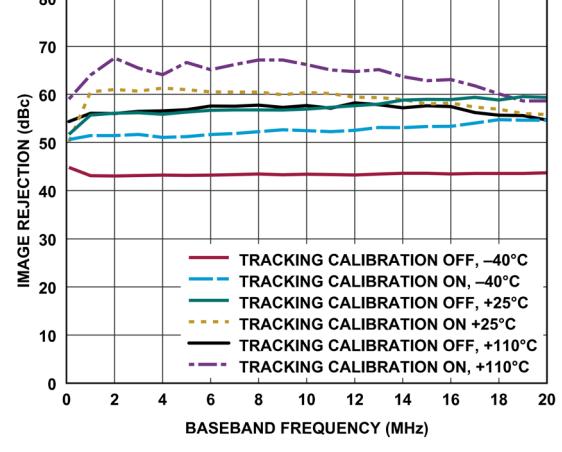

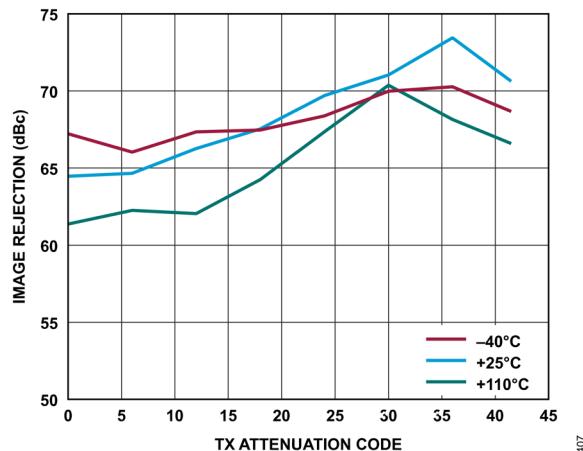

| IMAGE REJECTION WITH INITIALIZATION CALIBRATION ONLY                     |        |       |      |                       |      |                                                                                                                                                                                                    |

| Wideband                                                                 |        |       |      |                       |      | Up to 20 dB transmitter attenuation, 40 MHz bandwidth, 0 dB observation receiver attenuation, 18 MHz continuous wave <sup>2</sup> signal input, QEC <sup>3</sup> tracking calibration is disabled  |

| 50 MHz                                                                   |        | 55    |      | dBc                   |      |                                                                                                                                                                                                    |

| 470 MHz                                                                  |        | 63    |      | dBc                   |      |                                                                                                                                                                                                    |

| 900 MHz                                                                  |        | 59    |      | dBc                   |      |                                                                                                                                                                                                    |

| 2400 MHz                                                                 |        | 60    |      | dBc                   |      |                                                                                                                                                                                                    |

| 3500 MHz                                                                 |        | 57    |      | dBc                   |      |                                                                                                                                                                                                    |

| 5800 MHz                                                                 |        | 55    |      | dBc                   |      |                                                                                                                                                                                                    |

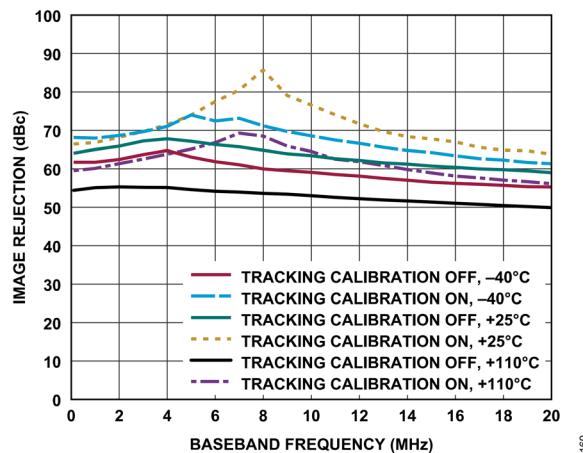

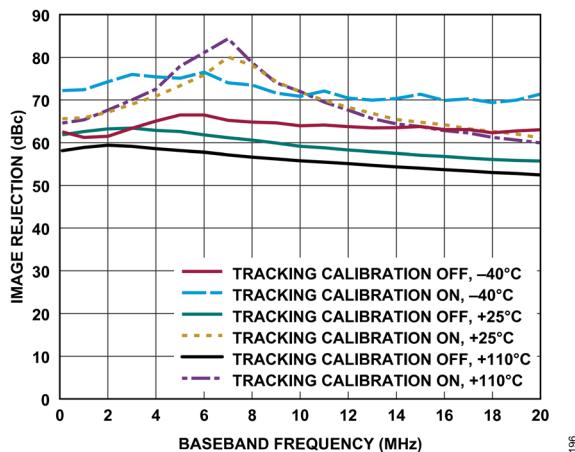

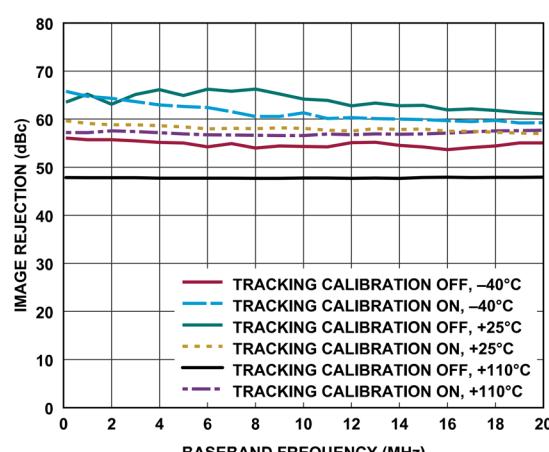

| Narrow-Band                                                              |        |       |      |                       |      | Up to 20 dB transmitter attenuation, 25 kHz bandwidth, 0 dB observation receiver attenuation, 2.1 kHz continuous wave <sup>2</sup> signal input, QEC <sup>3</sup> tracking calibration is disabled |

| 30 MHz                                                                   |        | 61    |      | dBc                   |      |                                                                                                                                                                                                    |

| 470 MHz                                                                  |        | 68    |      | dBc                   |      |                                                                                                                                                                                                    |

| 900 MHz                                                                  |        | 65    |      | dBc                   |      |                                                                                                                                                                                                    |

| 2400 MHz                                                                 |        | 60    |      | dBc                   |      |                                                                                                                                                                                                    |

| 3500 MHz                                                                 |        | 50    |      | dBc                   |      |                                                                                                                                                                                                    |

| 5800 MHz                                                                 |        | 50    |      | dBc                   |      |                                                                                                                                                                                                    |

| IMAGE REJECTION WITH INITIALIZATION CALIBRATION AND TRACKING CALIBRATION |        |       |      |                       |      |                                                                                                                                                                                                    |

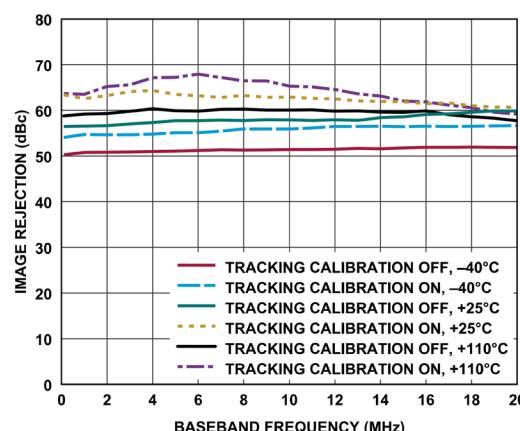

| Wideband                                                                 |        |       |      |                       |      | 0 dB transmitter attenuation, 40 MHz bandwidth, -0.2 dBFS, 18 MHz continuous wave <sup>2</sup> signal input, 50 Ω load, 0 dB observation receiver attenuation, QEC <sup>3</sup> is active          |

| 50 MHz                                                                   |        | 57    |      | dBc                   |      |                                                                                                                                                                                                    |

| 470 MHz                                                                  |        | 66    |      | dBc                   |      |                                                                                                                                                                                                    |

| 900 MHz                                                                  |        | 63    |      | dBc                   |      |                                                                                                                                                                                                    |

| 2400 MHz                                                                 |        | 60    |      | dBc                   |      |                                                                                                                                                                                                    |

| 3500 MHz                                                                 |        | 61    |      | dBc                   |      |                                                                                                                                                                                                    |

| 5800 MHz                                                                 |        | 57    |      | dBc                   |      |                                                                                                                                                                                                    |

## 仕様

表 1. トランスマッタ (Tx1) (続き)

| Parameter                                                 | Symbol                    | Min | Typ | Max | Unit | Test Conditions/Comments                                                                                                                                                      |

|-----------------------------------------------------------|---------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTINUOUS WAVE FULL-SCALE<br>OUTPUT POWER                |                           |     |     |     |      | -0.2 dBFS, 18 MHz continuous wave <sup>2</sup> signal input, 50 Ω load, 0 dB transmitter attenuation                                                                          |

| 30 MHz                                                    |                           |     | 7.3 |     | dBm  |                                                                                                                                                                               |

| 470 MHz                                                   |                           |     | 7.3 |     | dBm  |                                                                                                                                                                               |

| 900 MHz                                                   |                           |     | 7.6 |     | dBm  |                                                                                                                                                                               |

| 2400 MHz                                                  |                           |     | 7.4 |     | dBm  |                                                                                                                                                                               |

| 3500 MHz                                                  |                           |     | 7.8 |     | dBm  |                                                                                                                                                                               |

| 5800 MHz                                                  |                           |     | 7.2 |     | dBm  |                                                                                                                                                                               |

| OUTPUT IMPEDANCE                                          | $Z_{\text{OUT}}$          | 50  |     |     | Ω    | Differential, see the <a href="#">ADRV9001 System Development User Guide</a> for more information                                                                             |

| MAXIMUM OUTPUT LOAD VOLTAGE<br>STANDING WAVE RATIO (VSWR) |                           |     | 3   |     |      | Use the maximum value to ensure adequate calibration                                                                                                                          |

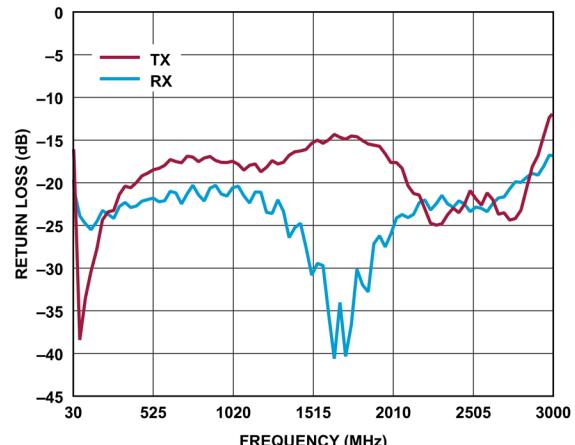

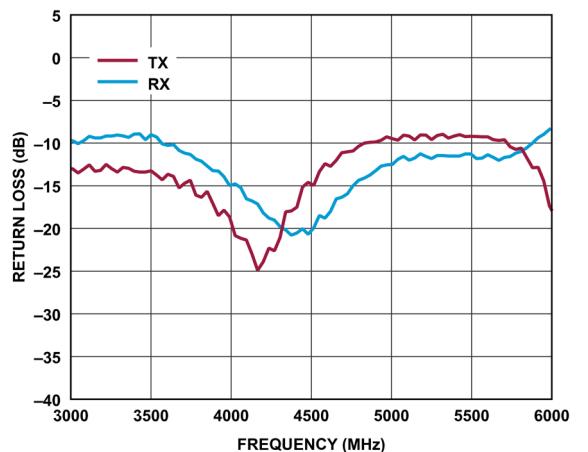

| OUTPUT RETURN LOSS                                        |                           |     |     |     |      | Single-ended return loss measured with balun in place on board                                                                                                                |

| 30 MHz                                                    |                           |     | 17  |     | dB   |                                                                                                                                                                               |

| 470 MHz                                                   |                           |     | 18  |     | dB   |                                                                                                                                                                               |

| 900 MHz                                                   |                           |     | 17  |     | dB   |                                                                                                                                                                               |

| 2400 MHz                                                  |                           |     | 23  |     | dB   |                                                                                                                                                                               |

| 3500 MHz                                                  |                           |     | 13  |     | dB   |                                                                                                                                                                               |

| 5800 MHz                                                  |                           |     | 10  |     | dB   |                                                                                                                                                                               |

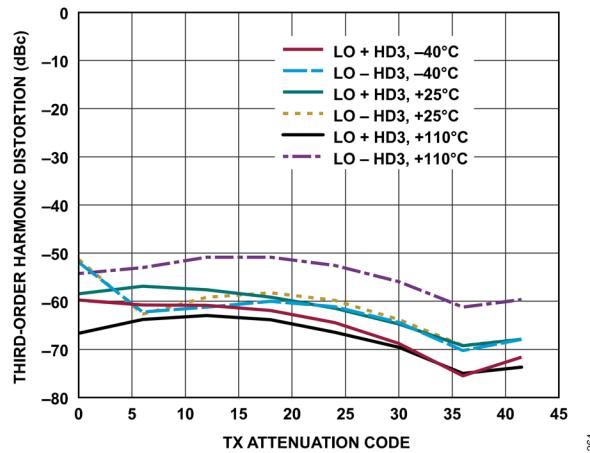

| OUTPUT THIRD-ORDER INTERCEPT<br>POINT                     |                           |     |     |     |      | 0 dB transmitter attenuation, 40 MHz bandwidth, 17 MHz and 18 MHz continuous wave <sup>2</sup> signal input, digital backoff = 11 dBFS/tone, calibrated at the device output  |

| Wideband                                                  | $\text{OIP3}_{\text{WB}}$ |     |     |     |      |                                                                                                                                                                               |

| 50 MHz                                                    |                           |     | 31  |     | dBm  |                                                                                                                                                                               |

| 470 MHz                                                   |                           |     | 31  |     | dBm  |                                                                                                                                                                               |

| 900 MHz                                                   |                           |     | 30  |     | dBm  |                                                                                                                                                                               |

| 2400 MHz                                                  |                           |     | 28  |     | dBm  |                                                                                                                                                                               |

| 3500 MHz                                                  |                           |     | 29  |     | dBm  |                                                                                                                                                                               |

| 5800 MHz                                                  |                           |     | 27  |     | dBm  |                                                                                                                                                                               |

| Narrow-Band                                               | $\text{OIP3}_{\text{NB}}$ |     |     |     |      | 0 dB transmitter attenuation, 25 kHz bandwidth, 2.1 kHz and 3.1 kHz continuous wave <sup>2</sup> signal input, digital backoff = 5 dBFS/tone, calibrated at the device output |

| 30 MHz                                                    |                           |     | 30  |     | dBm  |                                                                                                                                                                               |

| 470 MHz                                                   |                           |     | 31  |     | dBm  |                                                                                                                                                                               |

| 900 MHz                                                   |                           |     | 30  |     | dBm  |                                                                                                                                                                               |

| 2400 MHz                                                  |                           |     | 28  |     | dBm  |                                                                                                                                                                               |

| 3500 MHz                                                  |                           |     | 27  |     | dBm  |                                                                                                                                                                               |

| 5800 MHz                                                  |                           |     | 25  |     | dBm  |                                                                                                                                                                               |

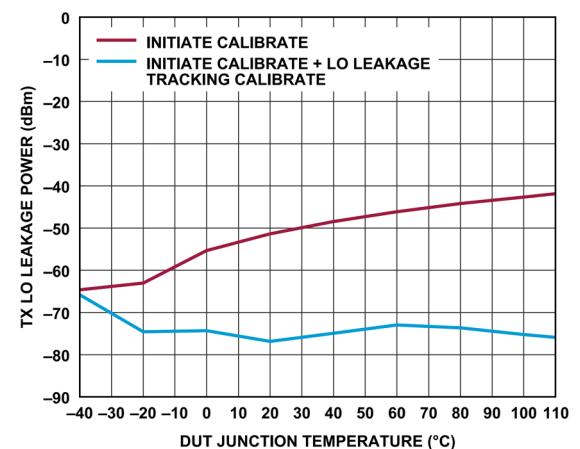

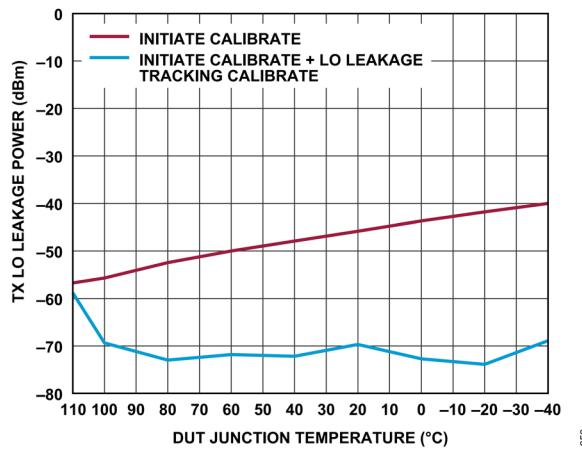

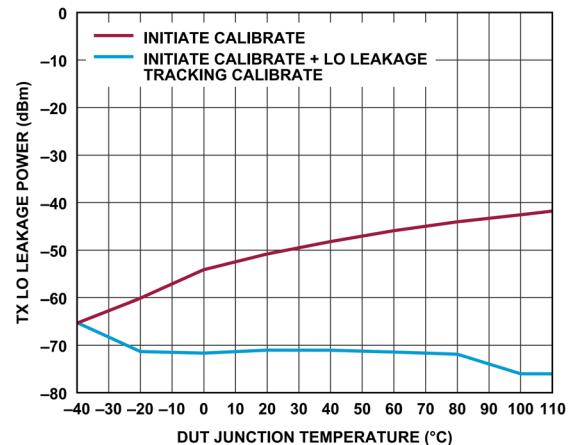

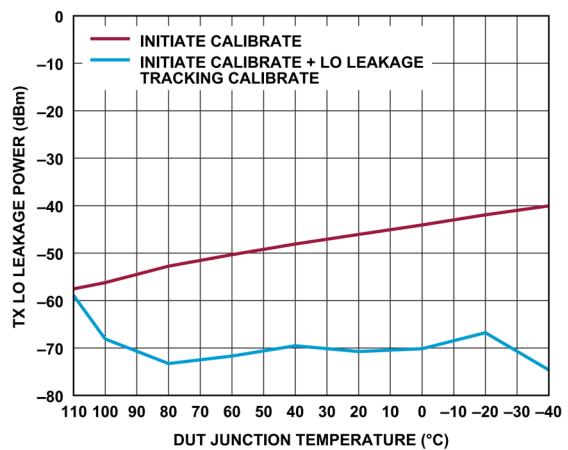

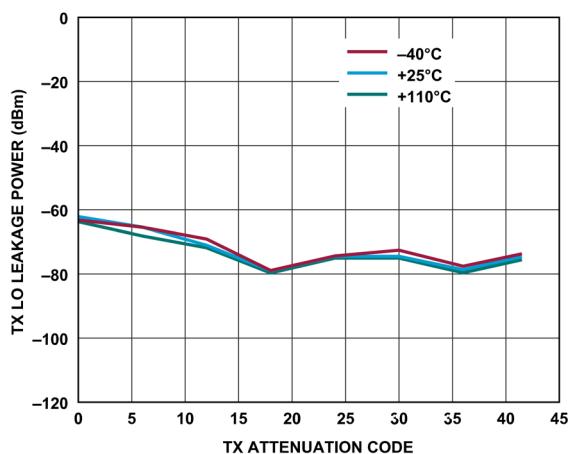

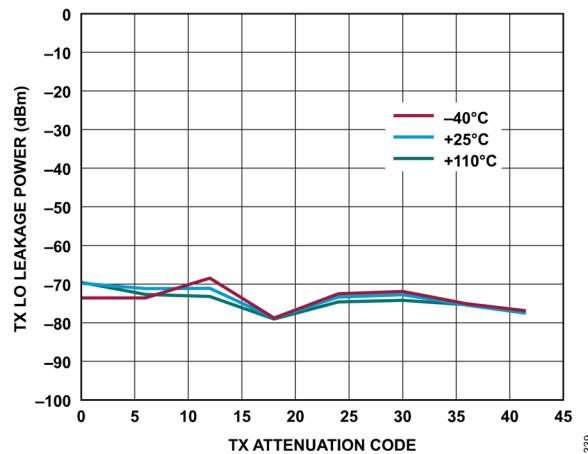

| CARRIER LEAKAGE WITH<br>INITIALIZATION CALIBRATION ONLY   |                           |     |     |     |      | LO leakage tracking calibration disabled, 0 dB transmitter attenuation, scales dB for dB with attenuation, input tone backoff = 6 dBFS                                        |

| Wideband                                                  |                           |     |     |     |      |                                                                                                                                                                               |

| 50 MHz                                                    |                           |     | -68 |     | dBm  |                                                                                                                                                                               |

| 470 MHz                                                   |                           |     | -65 |     | dBm  |                                                                                                                                                                               |

| 900 MHz                                                   |                           |     | -67 |     | dBm  |                                                                                                                                                                               |

| 2400 MHz                                                  |                           |     | -68 |     | dBm  |                                                                                                                                                                               |

| 3500 MHz                                                  |                           |     | -62 |     | dBm  |                                                                                                                                                                               |

| 5800 MHz                                                  |                           |     | -56 |     | dBm  |                                                                                                                                                                               |

| Narrow-Band                                               |                           |     |     |     |      |                                                                                                                                                                               |

| 30 MHz                                                    |                           |     | -70 |     | dBm  |                                                                                                                                                                               |

| 470 MHz                                                   |                           |     | -72 |     | dBm  |                                                                                                                                                                               |

## 仕様

表 1. トランシミッタ (Tx1) (続き)

| Parameter | Symbol | Min | Typ | Max | Unit | Test Conditions/Comments |

|-----------|--------|-----|-----|-----|------|--------------------------|

| 900 MHz   |        |     | -74 |     | dBm  |                          |

| 2400 MHz  |        |     | -71 |     | dBm  |                          |

| 3500 MHz  |        |     | -71 |     | dBm  |                          |

| 5800 MHz  |        |     | -58 |     | dBm  |                          |

<sup>1</sup> dBFS は、所定の RF 減衰設定での連続波出力信号に対する、実際の出力信号と可能な最大出力レベルの比です。

<sup>2</sup> 連続波は、單一周波数の信号です。

<sup>3</sup> 直交誤差補正 (QEC) は、対象とする信号の直交イメージを最小限に抑えるための方式です。

## レシーバ仕様

表 2. レシーバ (Rx1A および Rx1B)

| Parameter                                           | Symbol | Min   | Typ   | Max | Unit     | Test Conditions/Comments                                                                                                                                                                                          |

|-----------------------------------------------------|--------|-------|-------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CENTER FREQUENCY                                    |        | 30    | 6000  |     | MHz      |                                                                                                                                                                                                                   |

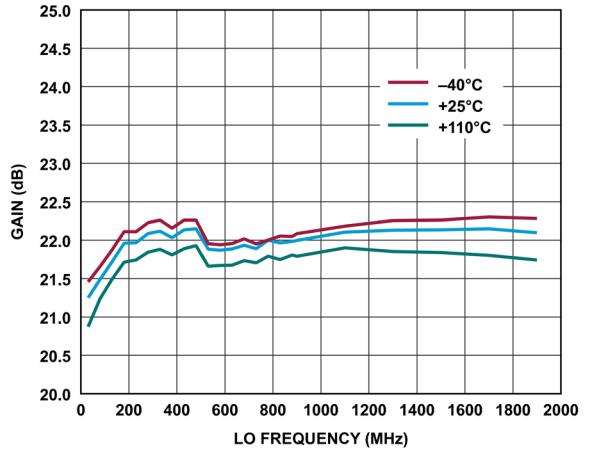

| MAXIMUM GAIN                                        |        |       |       |     |          |                                                                                                                                                                                                                   |

| Wideband                                            |        |       |       |     |          | High performance receiver ADCs, 0 dB attenuation, 5.6 MHz baseband frequency                                                                                                                                      |

| 50 MHz                                              |        |       | 21    |     | dB       |                                                                                                                                                                                                                   |

| 470 MHz                                             |        |       | 22    |     | dB       |                                                                                                                                                                                                                   |

| 900 MHz                                             |        |       | 22    |     | dB       |                                                                                                                                                                                                                   |

| 2400 MHz                                            |        |       | 22    |     | dB       |                                                                                                                                                                                                                   |

| 3500 MHz                                            |        |       | 21    |     | dB       |                                                                                                                                                                                                                   |

| 5800 MHz                                            |        |       | 21    |     | dB       |                                                                                                                                                                                                                   |

| Narrow-Band                                         |        |       |       |     |          | High performance receiver ADCs, 0 dB attenuation, 2.1 kHz baseband frequency                                                                                                                                      |

| 30 MHz                                              |        |       | 21    |     | dB       |                                                                                                                                                                                                                   |

| 470 MHz                                             |        |       | 22    |     | dB       |                                                                                                                                                                                                                   |

| 900 MHz                                             |        |       | 22    |     | dB       |                                                                                                                                                                                                                   |

| 2400 MHz                                            |        |       | 22    |     | dB       |                                                                                                                                                                                                                   |

| 3500 MHz                                            |        |       | 21    |     | dB       |                                                                                                                                                                                                                   |

| 5800 MHz                                            |        |       | 21    |     | dB       |                                                                                                                                                                                                                   |

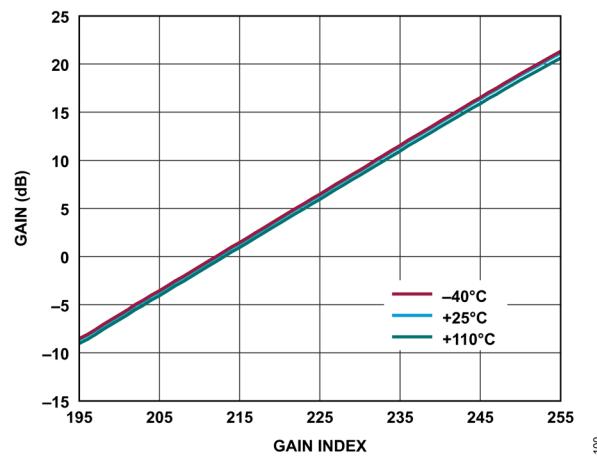

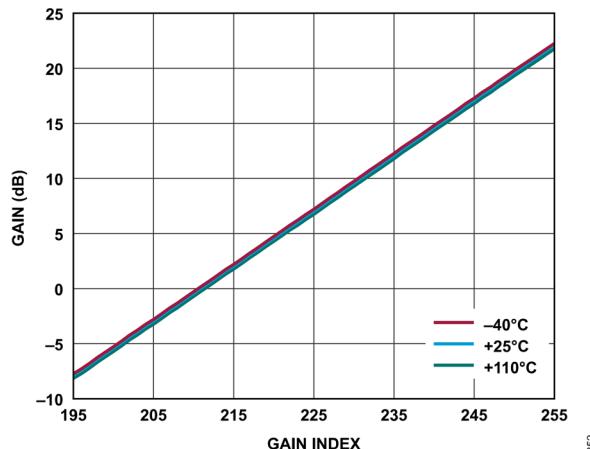

| ATTENUATION RANGE FROM MAXIMUM GAIN                 |        |       | 34    |     | dB       |                                                                                                                                                                                                                   |

| Attenuation Accuracy                                |        |       |       |     |          |                                                                                                                                                                                                                   |

| Gain Step                                           |        |       | 0.5   |     | dB       | Attenuator steps from 0 dB to 30 dB                                                                                                                                                                               |

|                                                     |        |       | 1.0   |     | dB       | Attenuator steps from 30 dB to 34 dB                                                                                                                                                                              |

| Gain Step Error                                     |        |       | 0.1   |     | dB       | Attenuation step from 0 dB to 30 dB, LO from 30 MHz to 3 GHz                                                                                                                                                      |

|                                                     |        |       | 0.2   |     | dB       | Attenuation step from 0 dB to 30 dB, LO from 3 GHz to 6 GHz                                                                                                                                                       |

|                                                     |        |       | 0.1   |     | dB       | Attenuation step from 30 dB to 34 dB                                                                                                                                                                              |

| FREQUENCY RESPONSE                                  |        |       |       |     |          |                                                                                                                                                                                                                   |

| Peak-to-Peak Gain Deviation                         |        |       | 1     |     | dB       | 40 MHz bandwidth including digital compensation                                                                                                                                                                   |

|                                                     |        |       | 0.2   |     | dB       | Any 10 MHz span including digital compensation                                                                                                                                                                    |

| RECEIVER BANDWIDTH                                  |        | 0.012 | 40    |     | MHz      | Zero-IF mode, the analog low-pass filter (LPF) bandwidth is 5 MHz minimum, the programmable finite impulse response (FIR) filter bandwidth is configurable over the entire range                                  |

| RECEIVER ALIAS BAND REJECTION                       |        | 80    |       |     | dB       | This performance is achieved because of the digital filters                                                                                                                                                       |

| CONTINUOUS WAVE FULL-SCALE INPUT POWER <sup>1</sup> | FSIP   |       | -11.4 |     | dBm      | This continuous wave signal level corresponds to the input power at maximum gain that produces 0 dBFS at the ADC output, this level increases dB for dB with attenuation, backoff by at least -2 dBFS is required |

| INPUT IMPEDANCE                                     |        | 100   |       |     | $\Omega$ | Differential, see the <a href="#">ADRV9001 System Development User Guide</a> for more information                                                                                                                 |

## 仕様

表 2. レシーバ (Rx1A および Rx1B) (続き)

| Parameter                                             | Symbol             | Min | Typ  | Max | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                     |

|-------------------------------------------------------|--------------------|-----|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT PORT RETURN LOSS                                |                    |     |      |     |      | Single-ended return loss measured with balun in place on board                                                                                                                                                                                                               |

| 30 MHz                                                |                    |     | 20   |     | dB   |                                                                                                                                                                                                                                                                              |

| 470 MHz                                               |                    |     | 21   |     | dB   |                                                                                                                                                                                                                                                                              |

| 900 MHz                                               |                    |     | 20   |     | dB   |                                                                                                                                                                                                                                                                              |

| 2400 MHz                                              |                    |     | 22   |     | dB   |                                                                                                                                                                                                                                                                              |

| 3500 MHz                                              |                    |     | 9    |     | dB   |                                                                                                                                                                                                                                                                              |

| 5800 MHz                                              |                    |     | 10   |     | dB   |                                                                                                                                                                                                                                                                              |

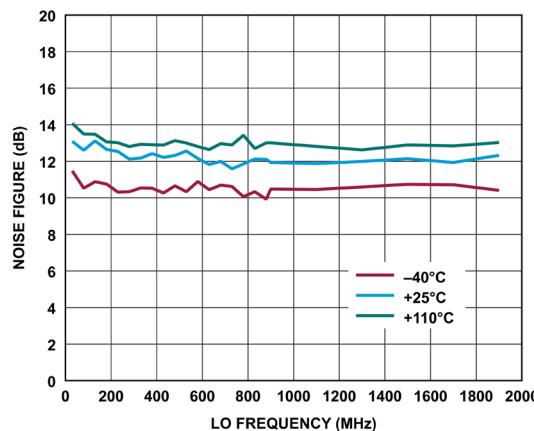

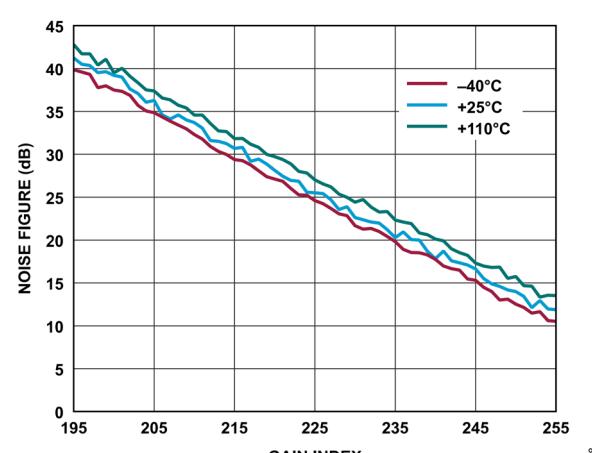

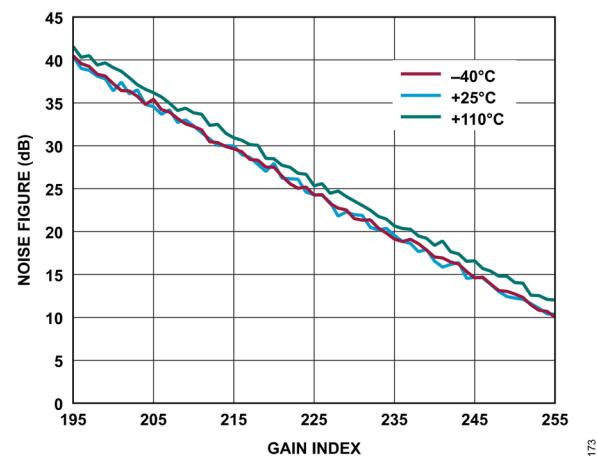

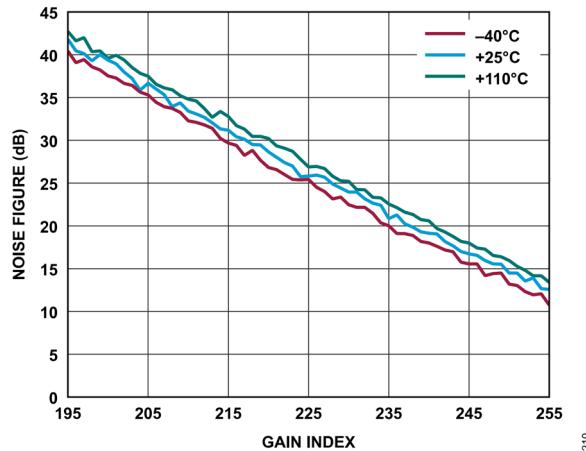

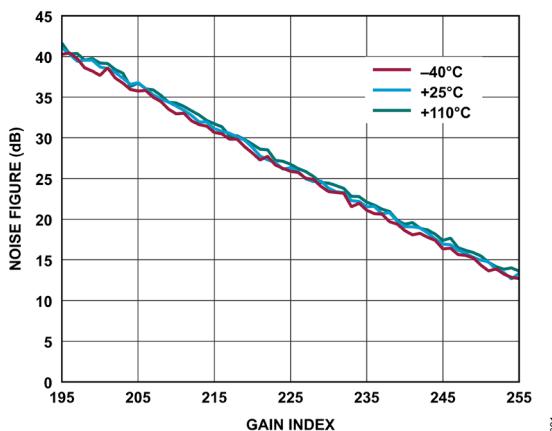

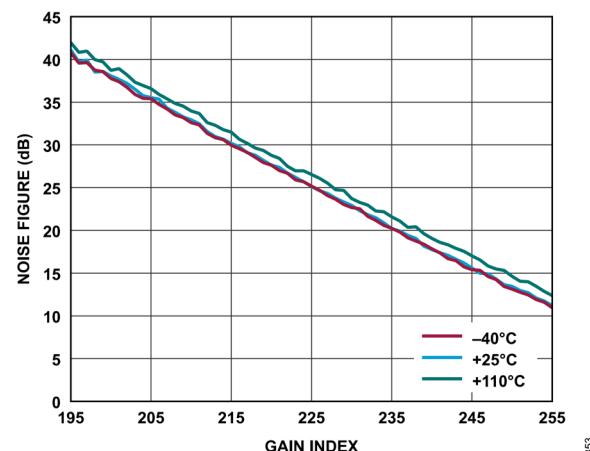

| NOISE FIGURE                                          |                    |     |      |     |      |                                                                                                                                                                                                                                                                              |

| High Performance Receiver ADCs                        |                    |     |      |     |      |                                                                                                                                                                                                                                                                              |

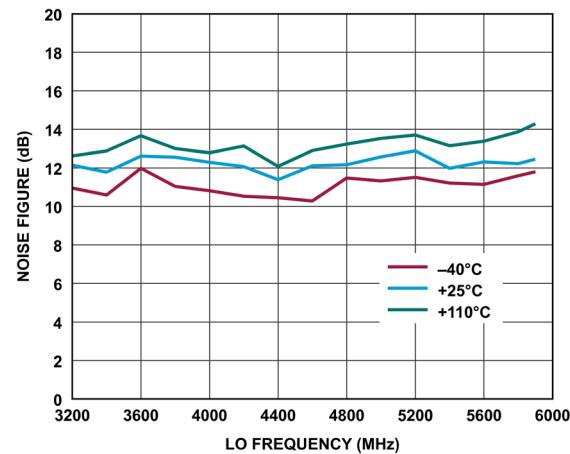

| Wideband                                              | NF <sub>WB</sub>   |     |      |     |      | 0 dB attenuation at the device under test (DUT) receive port, integrated bandwidth from 8 MHz to 9 MHz                                                                                                                                                                       |

| 50 MHz                                                |                    |     | 11.6 |     | dB   |                                                                                                                                                                                                                                                                              |

| 470 MHz                                               |                    |     | 10.6 |     | dB   |                                                                                                                                                                                                                                                                              |

| 900 MHz                                               |                    |     | 10.5 |     | dB   |                                                                                                                                                                                                                                                                              |

| 2400 MHz                                              |                    |     | 11.4 |     | dB   |                                                                                                                                                                                                                                                                              |

| 3500 MHz                                              |                    |     | 12.5 |     | dB   |                                                                                                                                                                                                                                                                              |

| 5800 MHz                                              |                    |     | 12.6 |     | dB   |                                                                                                                                                                                                                                                                              |

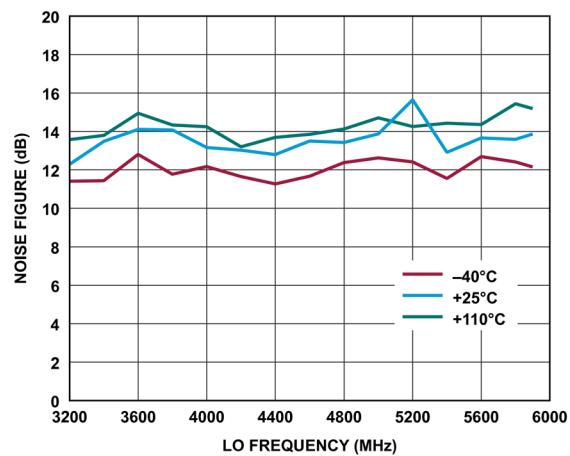

| Narrow-Band                                           | NF <sub>NB</sub>   |     |      |     |      | 0 dB attenuation at the DUT receive port, integrated bandwidth from 4 kHz to 8 kHz, 18 dB interface gain, IF = 490 kHz                                                                                                                                                       |

| 30 MHz                                                |                    |     | 13.8 |     | dB   |                                                                                                                                                                                                                                                                              |

| 470 MHz                                               |                    |     | 11.8 |     | dB   |                                                                                                                                                                                                                                                                              |

| 900 MHz                                               |                    |     | 11.8 |     | dB   |                                                                                                                                                                                                                                                                              |

| 2400 MHz                                              |                    |     | 12.3 |     | dB   |                                                                                                                                                                                                                                                                              |

| 3500 MHz                                              |                    |     | 14.2 |     | dB   |                                                                                                                                                                                                                                                                              |

| 5800 MHz                                              |                    |     | 15.1 |     | dB   |                                                                                                                                                                                                                                                                              |

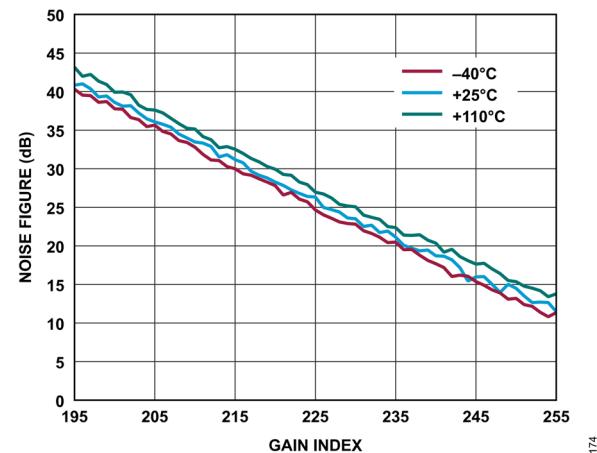

| Low Power Receiver ADCs                               |                    |     |      |     |      |                                                                                                                                                                                                                                                                              |

| Wideband                                              | NF <sub>WB</sub>   |     |      |     |      | 0 dB attenuation at the DUT receive port, integrated bandwidth from 8 MHz to 9 MHz                                                                                                                                                                                           |

| 50 MHz                                                |                    |     | 13.1 |     | dB   |                                                                                                                                                                                                                                                                              |

| 470 MHz                                               |                    |     | 11.9 |     | dB   |                                                                                                                                                                                                                                                                              |

| 900 MHz                                               |                    |     | 12.0 |     | dB   |                                                                                                                                                                                                                                                                              |

| 2400 MHz                                              |                    |     | 12.6 |     | dB   |                                                                                                                                                                                                                                                                              |

| 3500 MHz                                              |                    |     | 13.6 |     | dB   |                                                                                                                                                                                                                                                                              |

| 5800 MHz                                              |                    |     | 13.9 |     | dB   |                                                                                                                                                                                                                                                                              |

| Narrow-Band                                           | NF <sub>NB</sub>   |     |      |     |      | 0 dB attenuation at the DUT receive port, integrated bandwidth from 4 kHz to 8 kHz, 18 dB interface gain, IF = 490 kHz                                                                                                                                                       |

| 30 MHz                                                |                    |     | 16.7 |     | dB   |                                                                                                                                                                                                                                                                              |

| 470 MHz                                               |                    |     | 14.8 |     | dB   |                                                                                                                                                                                                                                                                              |

| 900 MHz                                               |                    |     | 15.1 |     | dB   |                                                                                                                                                                                                                                                                              |

| 2400 MHz                                              |                    |     | 15.6 |     | dB   |                                                                                                                                                                                                                                                                              |

| 3500 MHz                                              |                    |     | 17.0 |     | dB   |                                                                                                                                                                                                                                                                              |

| 5800 MHz                                              |                    |     | 17.5 |     | dB   |                                                                                                                                                                                                                                                                              |

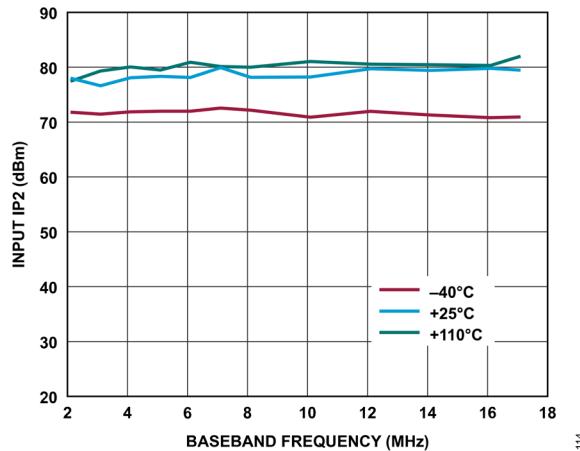

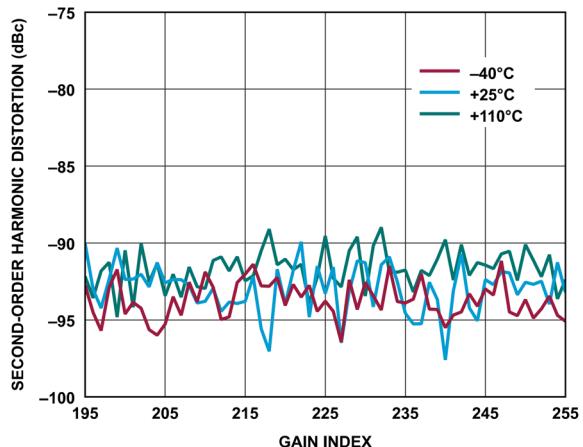

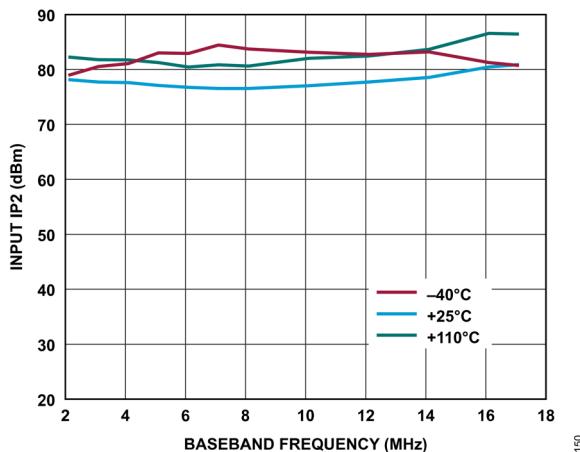

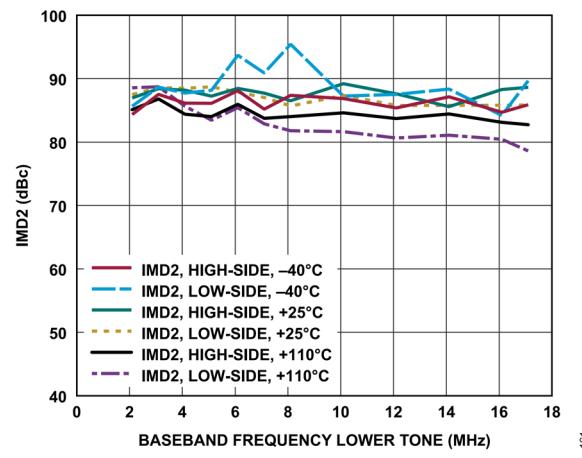

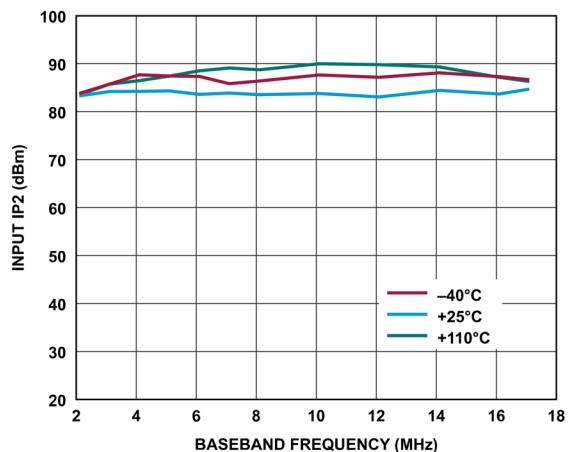

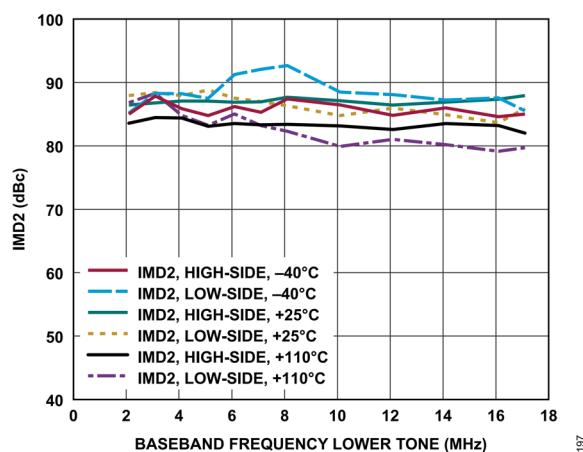

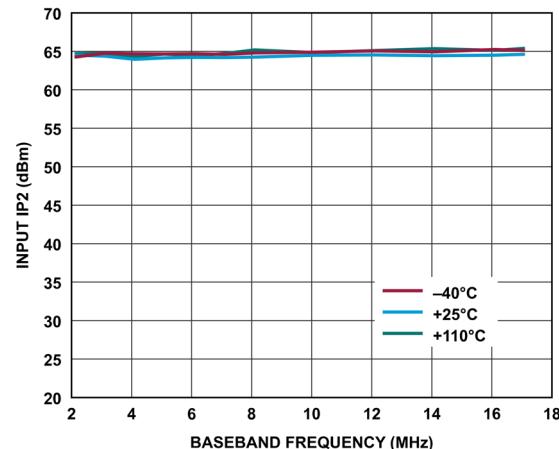

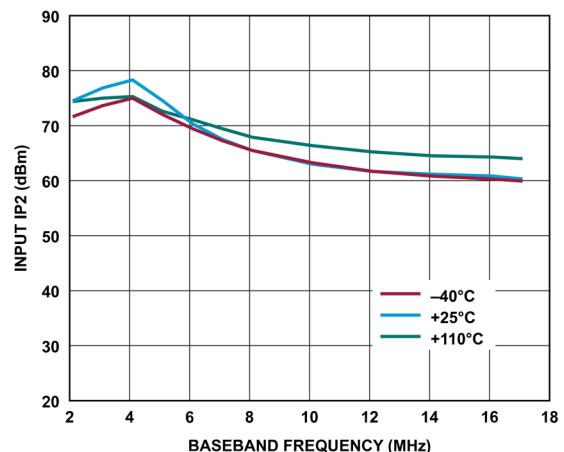

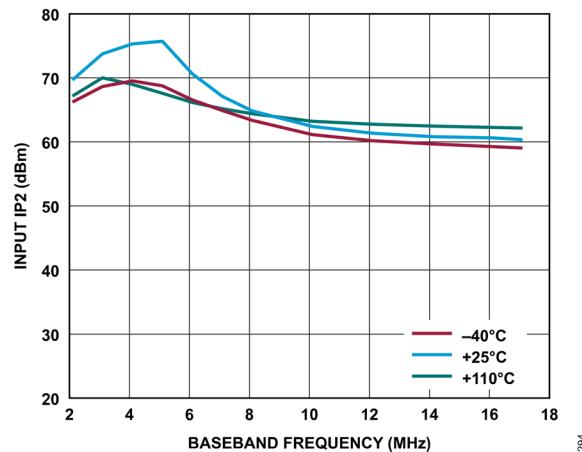

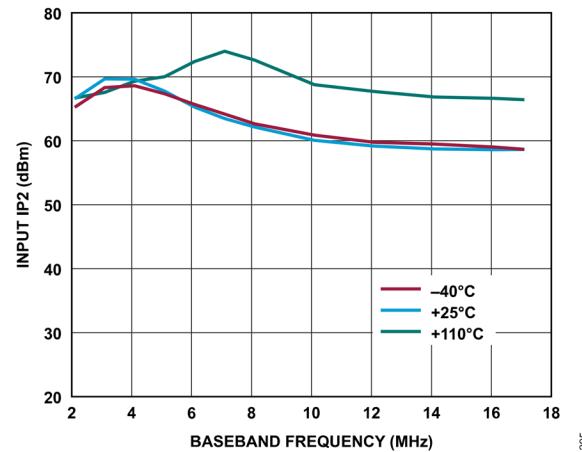

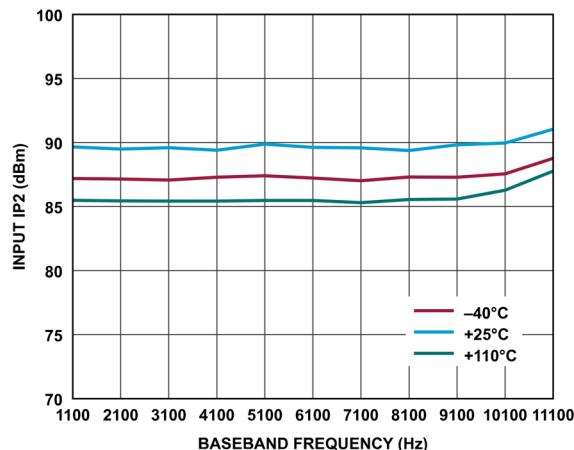

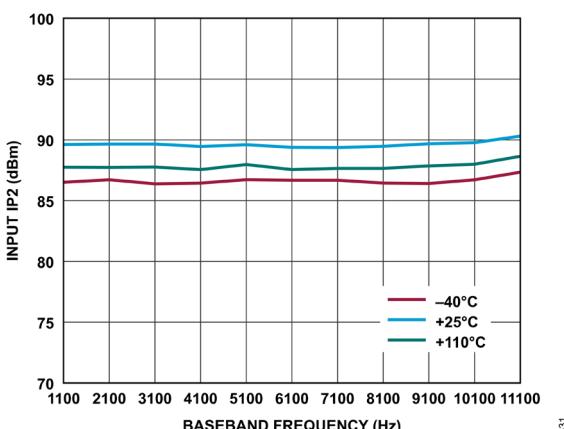

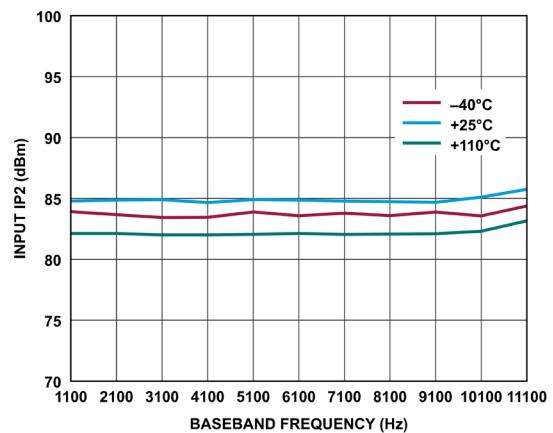

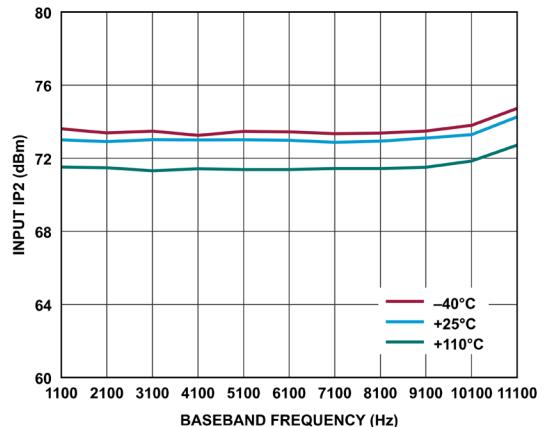

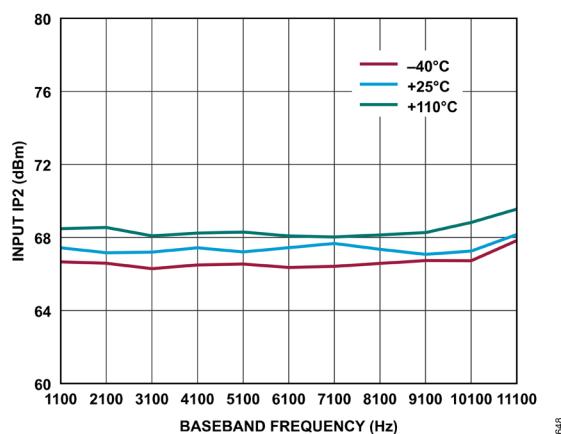

| SECOND-ORDER INPUT<br>INTERMODULATION INTERCEPT POINT |                    |     |      |     |      |                                                                                                                                                                                                                                                                              |

| High Performance Receiver ADCs                        |                    |     |      |     |      |                                                                                                                                                                                                                                                                              |

| Wideband                                              | IIP2 <sub>WB</sub> |     |      |     |      | 0 dB receiver attenuation, 1 dB cutoff frequency ( $f_{1dB}$ ) of the transimpedance amplifier (TIA) = 20 MHz, two continuous wave tones at 17 MHz and 18 MHz, for LO = 50 MHz, tone output power is -11.6 dBFS/tone, for all other LOs, tone output power is -8.1 dBFS/tone |

| 50 MHz                                                |                    |     | 79   |     | dBm  |                                                                                                                                                                                                                                                                              |

## 仕様

表 2. レシーバ (Rx1A および Rx1B) (続き)

| Parameter                                                                   | Symbol             | Min | Typ | Max | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------|--------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 470 MHz                                                                     | IIP2 <sub>NB</sub> |     | 81  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 900 MHz                                                                     |                    |     | 85  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 2400 MHz                                                                    |                    |     | 73  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 3500 MHz                                                                    |                    |     | 60  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 5800 MHz                                                                    |                    |     | 60  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

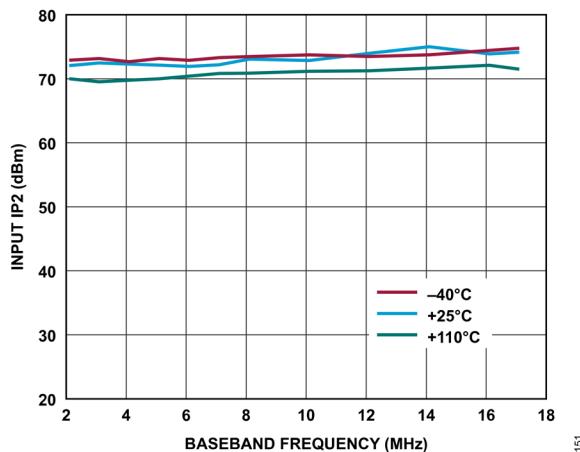

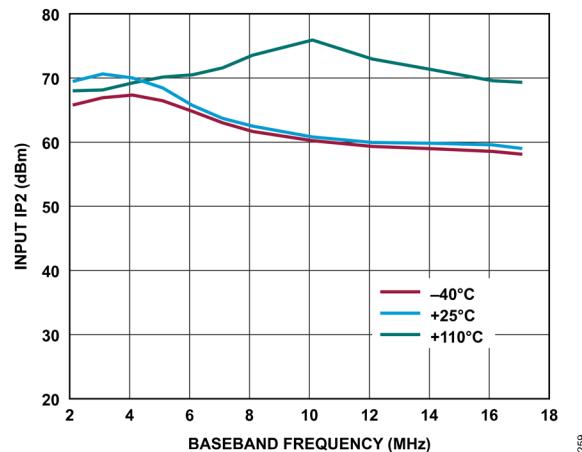

| Narrow-Band                                                                 |                    |     |     |     |      | 0 dB receiver attenuation, 3 dB cutoff frequency ( $f_{3dB}$ ) of the first-order TIA = 4 MHz, two continuous wave tones at 1.0061 MHz and 2.0061 MHz, for LO = 30 MHz, 470 MHz, 900 MHz and 2400 MHz, tone output power is -11.6 dBFS/tone, for LO = 3500 MHz and 5800 MHz, tone output power is -6.6 dBFS/tone |

| 30 MHz                                                                      |                    |     | 90  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 470 MHz                                                                     |                    |     | 89  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 900 MHz                                                                     |                    |     | 85  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 2400 MHz                                                                    |                    |     | 68  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 3500 MHz                                                                    |                    |     | 73  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 5800 MHz                                                                    |                    |     | 67  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

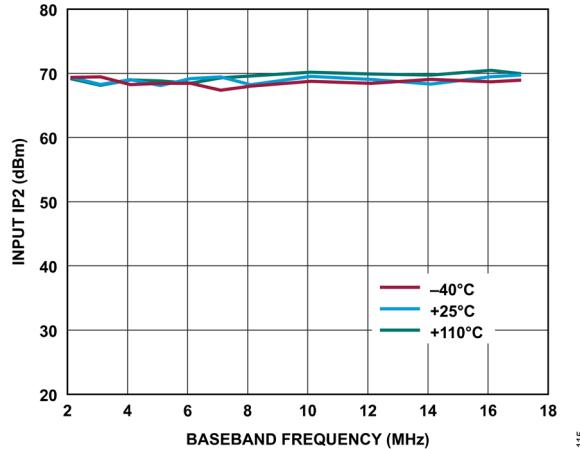

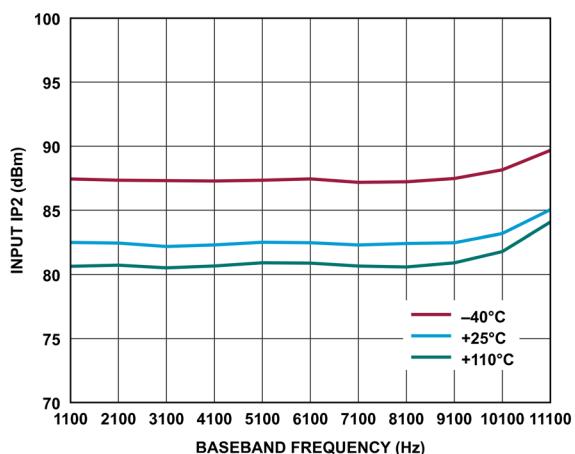

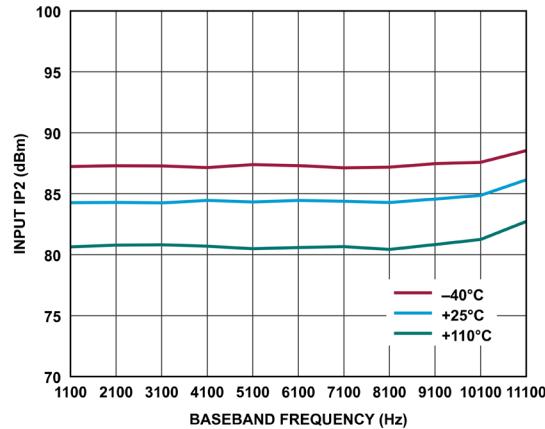

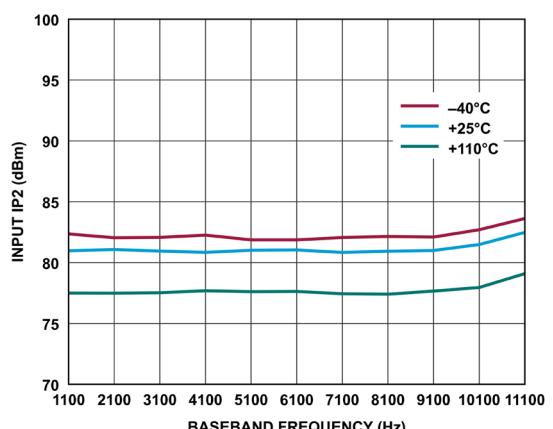

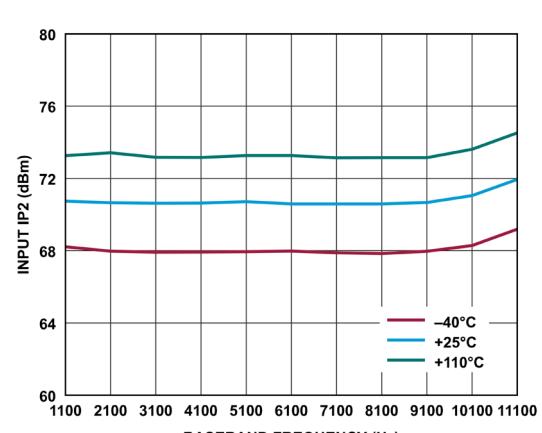

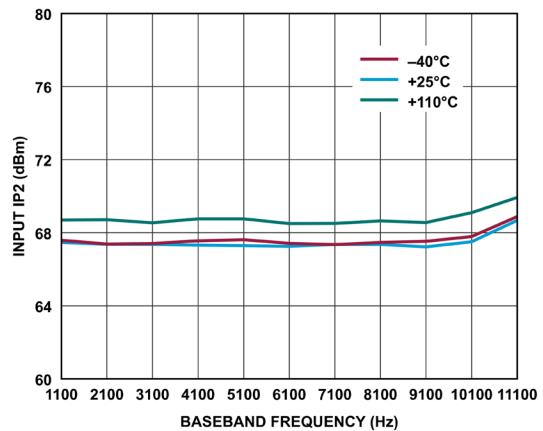

| Low Power Receiver ADCs                                                     |                    |     |     |     |      |                                                                                                                                                                                                                                                                                                                  |

| Wideband                                                                    | IIP2 <sub>WB</sub> |     |     |     |      | 0 dB receiver attenuation, $f_{1dB}$ of the TIA = 20 MHz, two continuous wave tones at 17 MHz and 18 MHz, for LO = 50 MHz, tone output power is -11.6 dBFS/tone, for all other LOs, tone output power is -8.1 dBFS/tone                                                                                          |

| 50 MHz                                                                      |                    |     | 70  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 470 MHz                                                                     |                    |     | 74  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 900 MHz                                                                     |                    |     | 72  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 2400 MHz                                                                    |                    |     | 65  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 3500 MHz                                                                    |                    |     | 59  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 5800 MHz                                                                    |                    |     | 60  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| Narrow-Band                                                                 | IIP2 <sub>NB</sub> |     |     |     |      | 0 dB receiver attenuation, $f_{3dB}$ of the first-order TIA = 4 MHz, two continuous wave tones at 1.0061 MHz and 2.0061 MHz, for LO = 30 MHz, 470 MHz, 900 MHz and 2400 MHz, tone output power is -11.6 dBFS/tone, for LO = 3500 MHz and 5800 MHz, tone output power is -6.6 dBFS/tone                           |

| 30 MHz                                                                      |                    |     | 82  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 470 MHz                                                                     |                    |     | 84  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 900 MHz                                                                     |                    |     | 81  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 2400 MHz                                                                    |                    |     | 70  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 3500 MHz                                                                    |                    |     | 71  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 5800 MHz                                                                    |                    |     | 67  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

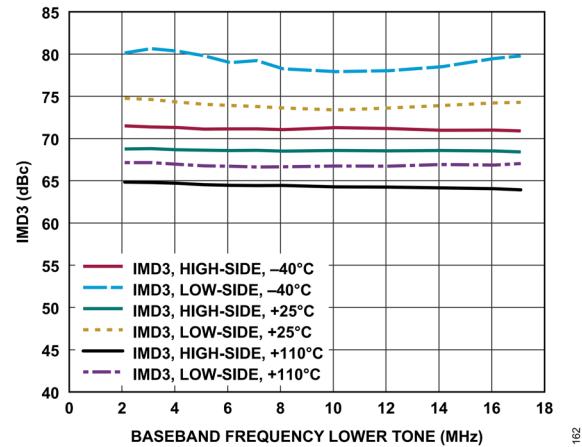

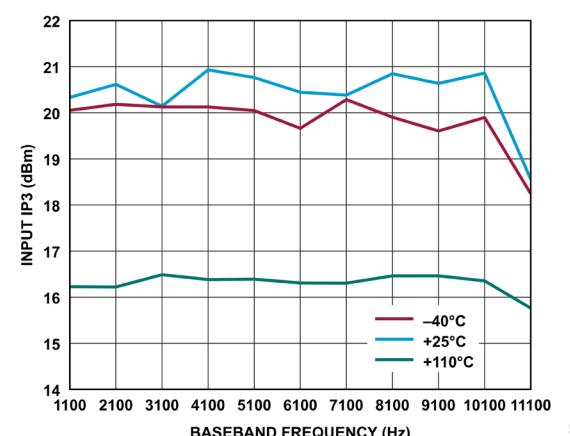

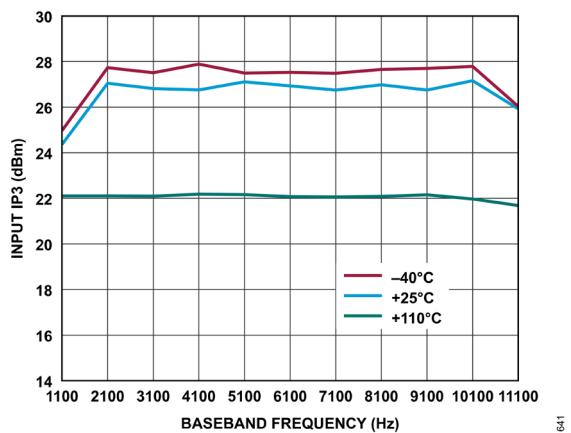

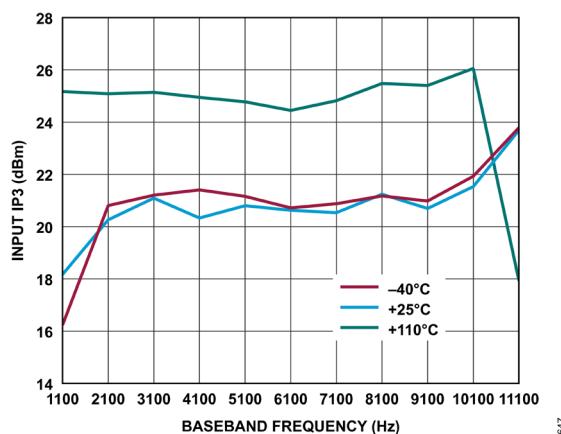

| THIRD-ORDER INPUT<br>INTERMODULATION INTERCEPT POINT,<br>DIFFERENCE PRODUCT |                    |     |     |     |      |                                                                                                                                                                                                                                                                                                                  |

| High Performance Receiver ADCs                                              |                    |     |     |     |      |                                                                                                                                                                                                                                                                                                                  |

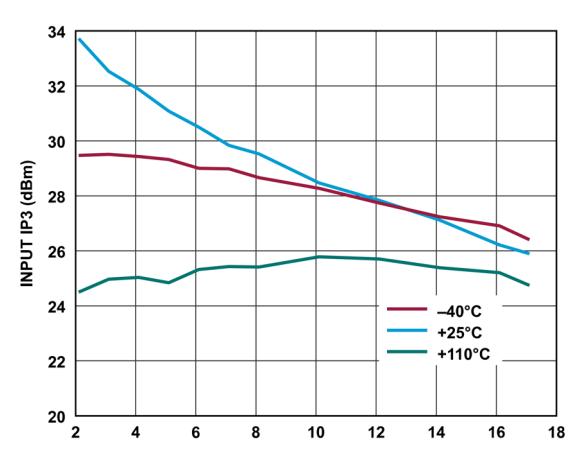

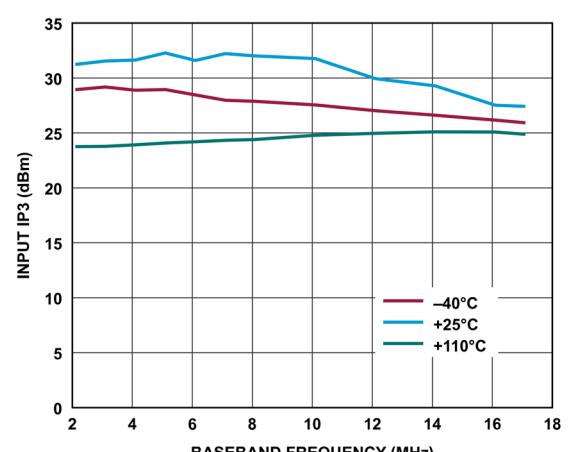

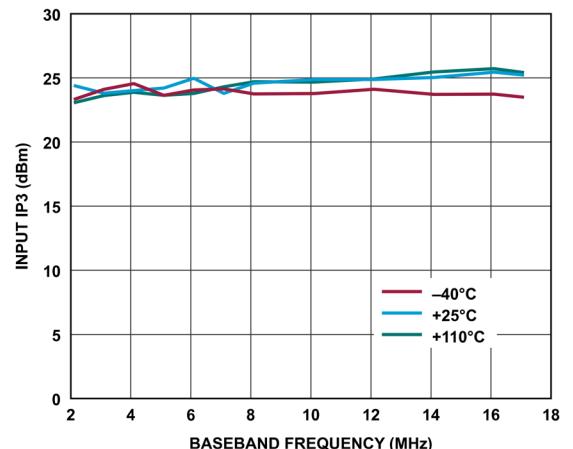

| Wideband                                                                    | IIP3 <sub>WB</sub> |     |     |     |      | 0 dB receiver attenuation, $f_{1dB}$ of the TIA = 20 MHz, two continuous wave tones at 17 MHz and 18 MHz, for LO = 50 MHz, tone output power is -11.6 dBFS/tone, for all other LOs, tone output power is -8.1 dBFS/tone                                                                                          |

| 50 MHz                                                                      |                    |     | 22  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 470 MHz                                                                     |                    |     | 26  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 900 MHz                                                                     |                    |     | 27  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 2400 MHz                                                                    |                    |     | 28  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 3500 MHz                                                                    |                    |     | 26  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

| 5800 MHz                                                                    |                    |     | 25  |     | dBm  |                                                                                                                                                                                                                                                                                                                  |

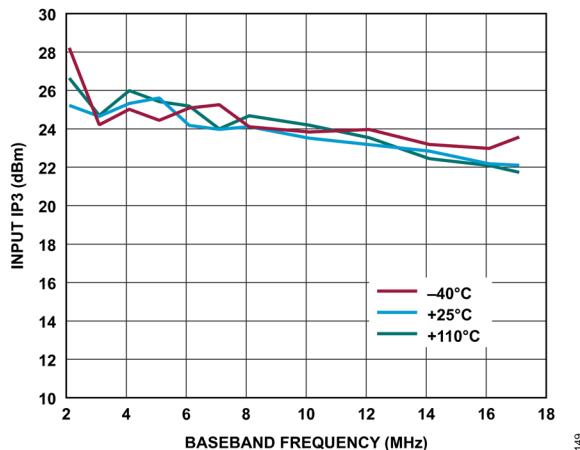

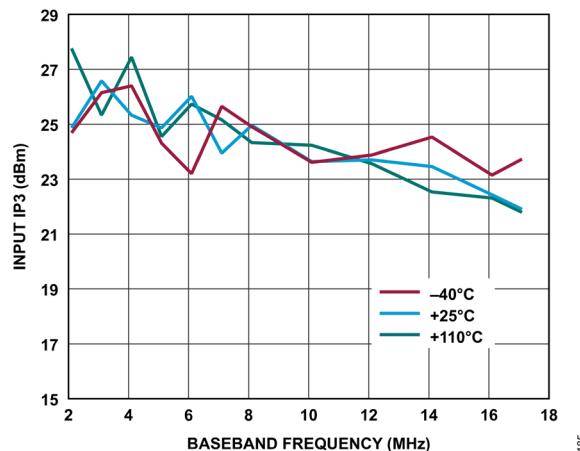

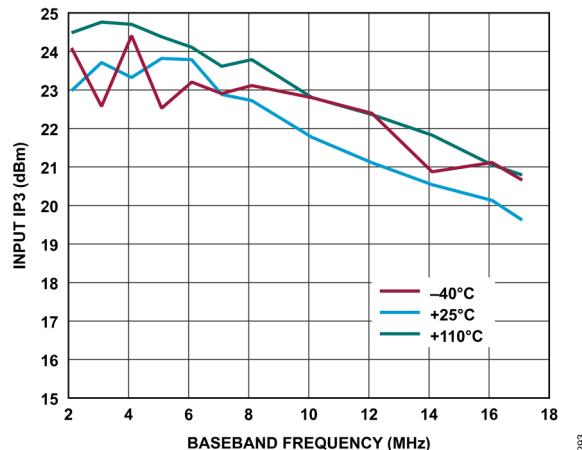

| Narrow-Band                                                                 | IIP3 <sub>NB</sub> |     |     |     |      | 0 dB receiver attenuation, for LO = 30 MHz, second-order TIA is used and $f_{1dB}$ of the TIA = 7 MHz, for all others, first-order TIA is used and $f_{1dB}$ of the                                                                                                                                              |

|                                                                             |                    |     |     |     |      |                                                                                                                                                                                                                                                                                                                  |

## 仕様

表 2. レシーバ (Rx1A および Rx1B) (続き)

| Parameter                       | Symbol             | Min | Typ  | Max | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|--------------------|-----|------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30 MHz                          |                    |     | 31   |     | dBm  | TIA = 4 MHz, two continuous wave tones at 1.0061 MHz and 2.0061 MHz, for LO = 30 MHz and 900 MHz, tone output power is -15.1 dBFS/tone, for LO = 470 MHz and 2400 MHz, tone output power is -13.6 dBFS/tone, for LO = 3500 MHz, tone output power is -12.6 dBFS/tone, for LO = 5800 MHz, tone output power is -14 dBFS/tone                                                                                                                                                                                   |

| 470 MHz                         |                    |     | 33   |     | dBm  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 900 MHz                         |                    |     | 29   |     | dBm  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2400 MHz                        |                    |     | 26   |     | dBm  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3500 MHz                        |                    |     | 27   |     | dBm  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5800 MHz                        |                    |     | 23   |     | dBm  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

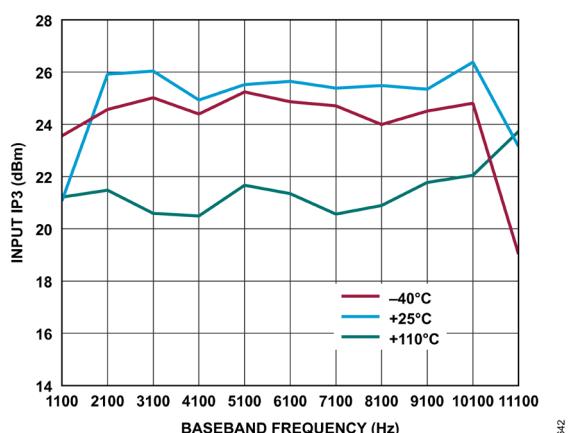

| Low Power Receiver ADCs         |                    |     |      |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |