## 0.25dB LSB、7ビット、9kHz~20GHzのシリコン・デジタル・アッテネータ

### 特長

- 周波数範囲 : 9kHz~20GHz

- 減衰範囲 : 31.75dB (0.25dB のステップ・サイズ)

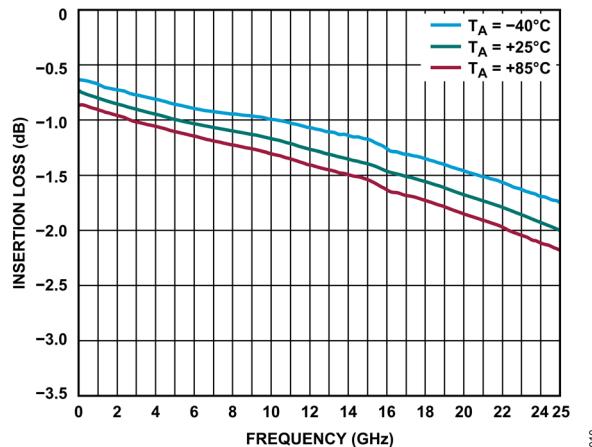

- 低インサーション・ロス

- ~6GHz : 1dB (代表値)

- ~12GHz : 1.3dB (代表値)

- ~20GHz : 1.7dB (代表値)

- 減衰精度 : -(減衰状態の 4%)または+0.1 (代表値、20GHzまで)

- ステップ誤差 : ~20GHz : 0.20dB (代表値)

- 高直線性

- 入力 P0.1dB

- 減衰状態が 16dB 未満の場合 : ATTIN で 33dBm (代表値)

- 減衰状態が 16dB 以上の場合 : ATTIN で 31dBm (代表値)

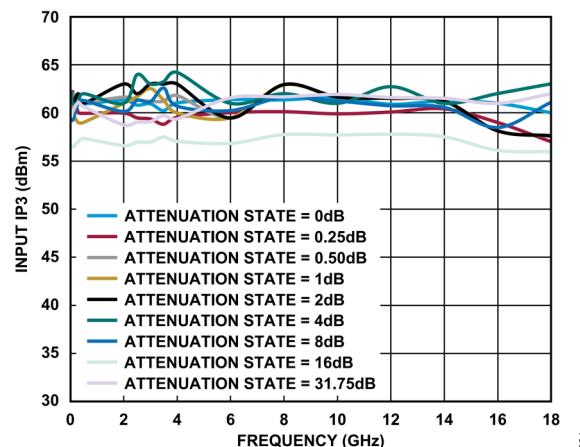

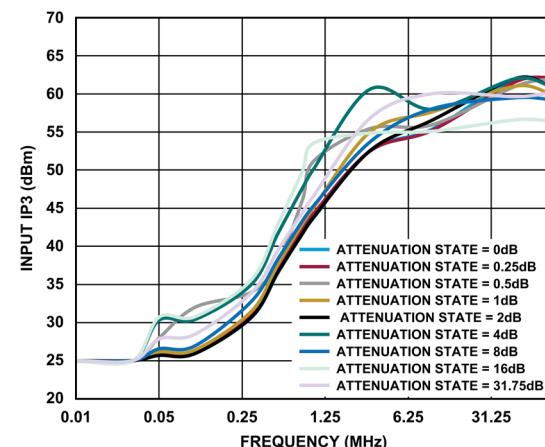

- 入力 IP3 : ATTIN で 55dBm (代表値)

- 大 RF 電力処理

- ATTIN での平均値 27dBm

- ATTIN でのピーク値 30dBm

- ATTIN でのホット・スイッチング時 27dBm

- RF 振幅のセトリング・タイム (50%でトリガ制御されてから最終 RF 出力の 0.05dB に達するまでの時間) : 1μs (代表値)

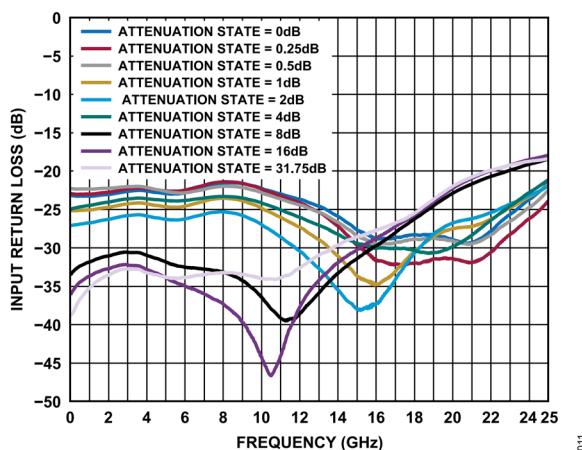

- 全減衰状態で一貫したリターン・ロス

- ディレーティングした電力処理で単電源動作可能

- 低周波スプリアスなし、内部電圧の発生なし

- シリアルおよびパラレルのモード制御、CMOS/LVTTL 互換

- 24 端子、4.0mm × 4.0mm、ランド・グリッド・アレイ (LGA) パッケージ

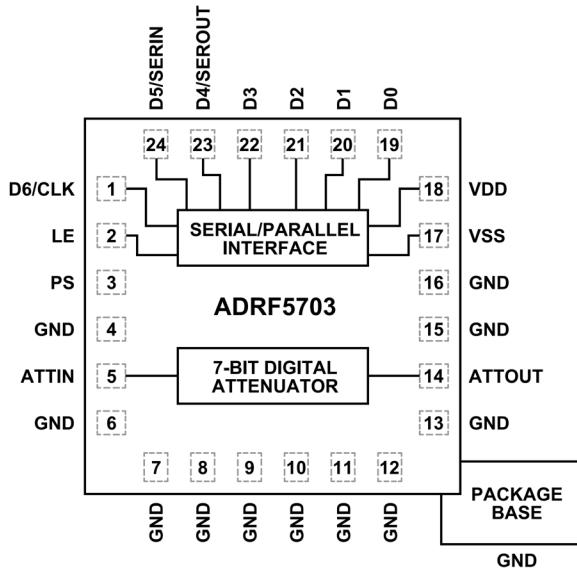

### 機能ブロック図

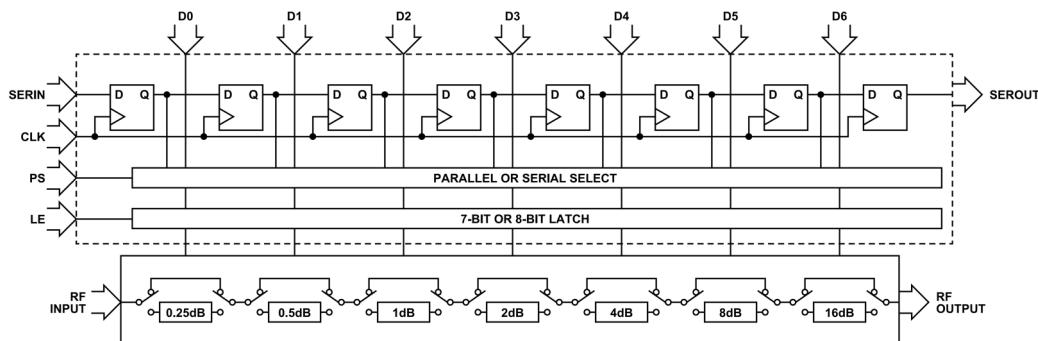

図 1. 機能ブロック図

### 概要

ADRF5703 は、シリコン・オン・インシユレータ (SOI) プロセスで製造された、31.75dB の減衰範囲と 0.25dB のステップ・サイズを備えた 7 ビット・デジタル・アッテネータです。

このデバイスは 9kHz~20GHz で動作し、1.7dB 未満のインサーション・ロスと優れた減衰精度を実現します。ADRF5703 の RF 入力電力処理能力は、ATTIN ピンのすべての状態に対し、平均値で 27dBm、ピーク値で 30dBm です。

ADRF5703 は、+3.3V と-3.3V の両電源電圧で動作します。また、負電源電圧 (Vss) をグラウンドに接続し、単電源電圧 (Vdd) を印加して動作させることもできます。この動作条件では、スイッチング特性、直線性、電力処理性能はディレーティングされますが、小信号性能は維持されます。表 2 を参照してください。

このデバイスは、シリアルまたはパラレルのモード制御と、相補型金属酸化膜半導体 (CMOS) / 低電圧トランジスタ-トランジスタ・ロジック (LVTTL) 互換制御を備えています。

ADRF5703 は、24 端子、4.0mm × 4.0mm のランド・グリッド・アレイ (LGA) パッケージで提供され、動作可能温度は-40°C~+105°C です。

### アプリケーション

- 工業用スキャナ

- 試験および計測器

- セルラ・インフラストラクチャ : 5G 用ミリ波

- 防衛用無線、レーダー、電子対抗手段 (ECM)

- マイクロ波無線機、超小型地球局 (VSAT)

## 目次

|                |    |

|----------------|----|

| 特長             | 1  |

| アプリケーション       | 1  |

| 機能ブロック図        | 1  |

| 概要             | 1  |

| 仕様             | 3  |

| 電気仕様           | 3  |

| 単電源動作          | 5  |

| タイミング仕様        | 5  |

| 絶対最大定格         | 6  |

| 熱抵抗            | 6  |

| パワー・ディレーティング曲線 | 6  |

| 静電放電 (ESD) 定格  | 7  |

| ESD に関する注意     | 7  |

| ピン配置およびピン機能の説明 | 8  |

| インターフェース回路図    | 9  |

| 代表的な性能特性       | 10 |

|                          |    |

|--------------------------|----|

| インサーション・ロス、リターン・ロス、状態誤差、 |    |

| ステップ誤差、リアクティブ・フェーズ       | 10 |

| 入力電力圧縮と3次インターセプト         | 14 |

| 動作原理                     | 15 |

| 電源                       | 15 |

| 単電源動作                    | 15 |

| RF入出力                    | 15 |

| シリアル・モードまたはパラレル・モードの選択   | 16 |

| シリアル・モード・インターフェース        | 16 |

| パラレル・モード・インターフェース        | 17 |

| アプリケーション情報               | 18 |

| PCB 設計のための推奨事項           | 18 |

| 外形寸法                     | 19 |

| オーダー・ガイド                 | 19 |

## 改訂履歴

9/2025—Revision 0: Initial Version

## 仕様

## 電気仕様

特に指定のない限り、 $V_{DD} = 3.3V$ 、 $V_{SS} = -3.3V$ 、制御電圧 ( $V_{CTRL}$ ) = 0V または 3.3V、 $T_{CASE} = 25^\circ C$ 、 $50\Omega$  システム。 $V_{CTRL}$  は、デジタル制御入力ピンの電圧です。

表 1. 電気仕様

| Parameter                    | Symbol                                    | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                       | Min   | Typ                                                | Max   | Unit    |

|------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------|-------|---------|

| FREQUENCY RANGE              | f                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.009 |                                                    | 20000 | MHz     |

| INSERTION LOSS               |                                           | 9kHz to 6GHz<br>6GHz to 12GHz<br>12 GHz to 20GHz                                                                                                                                                                                                                                                                                                                                                                               |       | 1<br>1.3<br>1.7                                    |       | dB      |

| RETURN LOSS                  |                                           | ATTIN and ATTOUT, all attenuation states<br>9kHz to 6GHz<br>6GHz to 12GHz<br>12 GHz to 20GHz                                                                                                                                                                                                                                                                                                                                   |       | 22<br>21<br>21                                     |       | dB      |

| ATTENUATION                  |                                           | Between minimum and maximum attenuation states<br>Between any successive attenuation states<br>Referenced to insertion loss<br>9kHz to 20GHz                                                                                                                                                                                                                                                                                   |       | 31.75<br>0.25                                      |       | dB      |

| Step Error                   |                                           | -(4% of the attenuation state) or +(0.1)                                                                                                                                                                                                                                                                                                                                                                                       |       |                                                    |       | dB      |

| Step Error                   |                                           | Between any successive state<br>9kHz to 6GHz<br>6GHz to 12GHz<br>12 GHz to 20GHz                                                                                                                                                                                                                                                                                                                                               |       | 0.04<br>0.05<br>0.20                               |       | dB      |

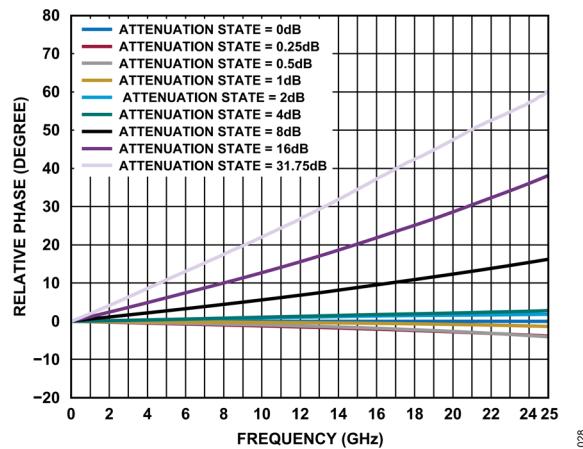

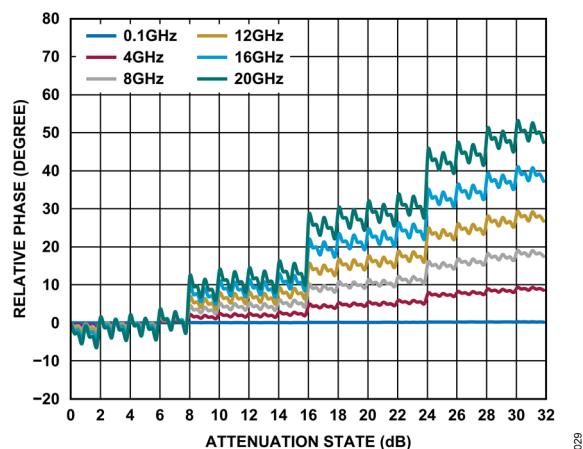

| RELATIVE PHASE               |                                           | Maximum attenuation state referenced to insertion loss<br>6GHz<br>12GHz<br>20GHz                                                                                                                                                                                                                                                                                                                                               |       | 13<br>27<br>48                                     |       | Degrees |

| SWITCHING CHARACTERISTICS    | $t_{RISE}, t_{FALL}$<br>$t_{ON}, t_{OFF}$ | All attenuation states at input power ( $P_{IN}$ ) = 10dBm, $f = 1GHz$<br>10% to 90% of RF output<br>50% triggered control to 90% of RF output<br>50% triggered control to 0.1dB of final RF output<br>50% triggered control to 0.05dB of final RF output<br>Worst-case transition<br>Worst-case transition<br>$f = 20GHz$<br>50% triggered control to 5° of final RF output<br>50% triggered control to 1° of final RF output |       | 0.4<br>0.6<br>0.9<br>1<br>3.7<br>2.4<br>0.5<br>0.6 |       | μs      |

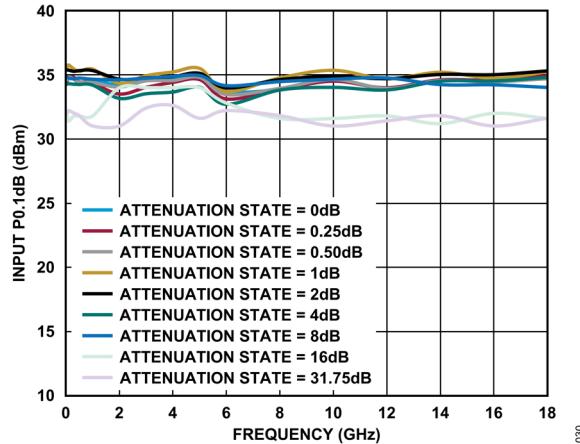

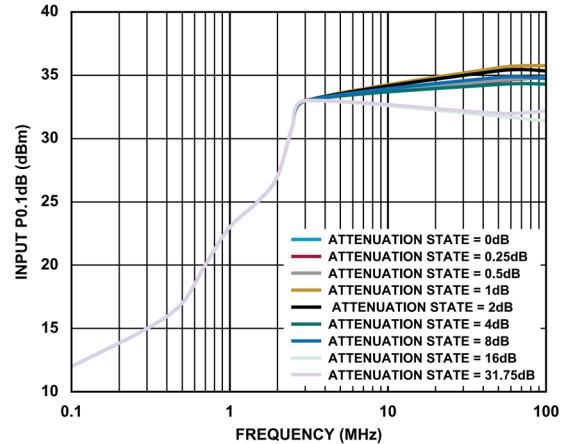

| INPUT LINEARITY <sup>1</sup> | $P_{0.1dB}$                               | 3MHz to 18GHz<br>Attenuation state < 16dB<br>Attenuation state $\geq$ 16dB<br>Attenuation state < 16dB<br>Attenuation state $\geq$ 16dB                                                                                                                                                                                                                                                                                        |       | 33<br>31<br>30<br>27                               |       | dBm     |

## 仕様

表 1. 電気仕様 (続き)

| Parameter                        | Symbol     | Test Conditions/Comments                                                                                  | Min   | Typ | Max      | Unit          |

|----------------------------------|------------|-----------------------------------------------------------------------------------------------------------|-------|-----|----------|---------------|

| Third-Order Intercept            | IP3        | Two-tone $P_{IN} = 22\text{dBm}$ per tone, $\Delta f = 1\text{MHz}$ , all attenuation states              |       |     |          | dBm           |

| Input at ATTIN                   |            |                                                                                                           |       | 55  |          | dBm           |

| Input at ATTOUT                  |            |                                                                                                           |       | 55  |          | dBm           |

| Second-Order Intercept           | IP2        | Two-tone $P_{IN} = 22\text{dBm}$ per tone, $\Delta f = 1\text{MHz}$ , all attenuation states              |       | 110 |          | dBm           |

| VIDEO FEEDTHROUGH <sup>2</sup>   |            |                                                                                                           |       | 2   |          | mV p-p        |

| DIGITAL CONTROL INPUTS           |            | LE, PS, and D0 to D6                                                                                      |       |     |          |               |

| Voltage                          |            |                                                                                                           |       |     |          |               |

| Low                              | $V_{INL}$  |                                                                                                           | 0     |     | 0.8      | V             |

| High                             | $V_{INH}$  |                                                                                                           | 1.2   |     | 3.3      | V             |

| Current                          |            |                                                                                                           |       |     |          |               |

| Low                              | $I_{INL}$  |                                                                                                           |       | <1  |          | $\mu\text{A}$ |

| High                             | $I_{INH}$  |                                                                                                           |       |     | 30       | $\mu\text{A}$ |

| D0, D1, D2, and D3               |            |                                                                                                           |       |     | <1       | $\mu\text{A}$ |

| LE, PS, D4, D5, and D6           |            |                                                                                                           |       |     |          | $\mu\text{A}$ |

| SUPPLY CURRENT                   |            |                                                                                                           |       |     |          |               |

| Positive Supply Current          | $I_{DD}$   | $V_{DD} = 3.3\text{V}$                                                                                    |       | 0.7 |          | mA            |

| Negative Supply Current          | $I_{SS}$   | $V_{SS} = -3.3\text{V}$                                                                                   |       | 0.6 |          | mA            |

| RECOMMENDED OPERATING CONDITIONS |            |                                                                                                           |       |     |          |               |

| Supply Voltage                   |            |                                                                                                           |       |     |          |               |

| Positive                         | $V_{DD}$   |                                                                                                           | 3.15  |     | 3.45     | V             |

| Negative                         | $V_{SS}$   |                                                                                                           | -3.45 |     | -3.15    | V             |

| Digital Control Voltage          | $V_{CTRL}$ |                                                                                                           | 0     |     | $V_{DD}$ | V             |

| RF Power Handling <sup>3</sup>   |            | $f = 3\text{MHz}$ to $18\text{GHz}$ , $T_{CASE} = 85^\circ\text{C}$ , <sup>4</sup> all attenuation states |       |     |          |               |

| Input at ATTIN                   |            |                                                                                                           |       |     |          |               |

| Average                          |            |                                                                                                           |       | 27  |          | dBm           |

| Peak <sup>5</sup>                |            |                                                                                                           |       | 30  |          | dBm           |

| Hot Switching                    |            |                                                                                                           |       | 27  |          | dBm           |

| Input at ATTOUT                  |            |                                                                                                           |       |     |          |               |

| Average                          |            |                                                                                                           |       | 24  |          | dBm           |

| Peak                             |            |                                                                                                           |       | 27  |          | dBm           |

| Hot Switching                    |            |                                                                                                           |       | 24  |          | dBm           |

| $T_{CASE}$                       |            |                                                                                                           | -40   |     | +105     | °C            |

<sup>1</sup> 入力直線性と周波数の関係については、図 30 および図 31 を参照してください。

<sup>2</sup> ビデオ・フィードスルーは、制御電圧のスイッチングの間 RF 信号がない状態で、 $50\Omega$  のテスト・セットアップの RF ポートで測定されるピーク・トランジエントです。

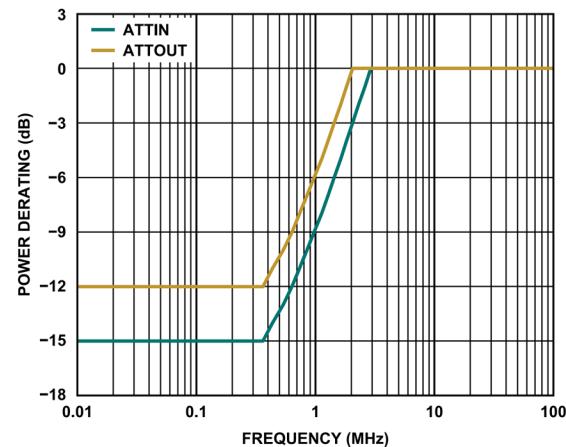

<sup>3</sup> 拡張周波数範囲での RF 電力処理能力の低下については、図 2 を参照してください。

<sup>4</sup>  $T_{CASE} = 105^\circ\text{C}$  での動作の場合、RF 電力処理能力は、 $T_{CASE} = 85^\circ\text{C}$  での仕様から 3dB 低下します。

<sup>5</sup> ピーク：100ns 以下のパルス継続時間および 5% のデューティサイクル。

## 仕様

## 単電源動作

特に指定のない限り、 $V_{DD} = 3.3V$ 、 $V_{SS} = 0V$ 、 $V_{CTRL} = 0V$  または  $3.3V$ 、 $T_{CASE} = 25^\circ C$ 、 $50\Omega$  システム。 $V_{CTRL}$  は、デジタル制御入力ピンの電圧です。

小信号およびバイアスの仕様は、単電源動作に対し維持されます。

表 2. 単電源動作の仕様

| Parameter                        | Symbol               | Test Conditions/Comments                                            | Min   | Typ  | Max   | Unit |

|----------------------------------|----------------------|---------------------------------------------------------------------|-------|------|-------|------|

| FREQUENCY RANGE                  | $f$                  |                                                                     | 0.009 |      | 20000 | MHz  |

| SWITCHING CHARACTERISTICS        |                      |                                                                     |       |      |       |      |

| Rise Time and Fall Time          | $t_{RISE}, t_{FALL}$ | 10% to 90% of $RF_{OUT}$                                            |       | 1.7  |       | μs   |

| On Time and Off Time             | $t_{ON}, t_{OFF}$    | 50% $V_{CTRL}$ to 90% of $RF_{OUT}$                                 |       | 1.7  |       | μs   |

| 0.1dB Settling Time              |                      | 50% $V_{CTRL}$ to 0.1dB of final $RF_{OUT}$                         |       | 2    |       | μs   |

| 0.05dB Settling Time             |                      | 50% $V_{CTRL}$ to 0.05dB of final $RF_{OUT}$                        |       | 2.1  |       | μs   |

| INPUT LINEARITY                  |                      | 3MHz to 18GHz                                                       |       |      |       |      |

| 0.1dB Power Compression          | $P_{0.1dB}$          |                                                                     |       | 20   |       | dBm  |

| Third-Order Intercept            | $IP_3$               | Two-tone $P_{IN} = 22\text{dBm}$ per tone, $\Delta f = 1\text{MHz}$ |       | 43   |       | dBm  |

| SUPPLY CURRENT                   |                      |                                                                     |       |      |       |      |

| Positive Supply Current          | $I_{DD}$             |                                                                     |       | 0.55 |       | mA   |

| RECOMMENDED OPERATING CONDITIONS |                      |                                                                     |       |      |       |      |

| RF Power Handling                |                      | $f = 3\text{MHz to 18GHz}, T_{CASE} = 85^\circ C$                   |       |      |       |      |

| Input at ATTIN                   |                      |                                                                     |       |      |       |      |

| Average                          |                      |                                                                     |       | 20   |       | dBm  |

| Peak                             |                      |                                                                     |       | 20   |       | dBm  |

| How Switching                    |                      |                                                                     |       | 20   |       | dBm  |

| Input at ATTOUT                  |                      |                                                                     |       |      |       |      |

| Average                          |                      |                                                                     |       | 20   |       | dBm  |

| Peak                             |                      |                                                                     |       | 20   |       | dBm  |

| Hot Switching                    |                      |                                                                     |       | 20   |       | dBm  |

| Case Temperature                 | $T_{CASE}$           |                                                                     | -40   |      | +105  | °C   |

## タイミング仕様

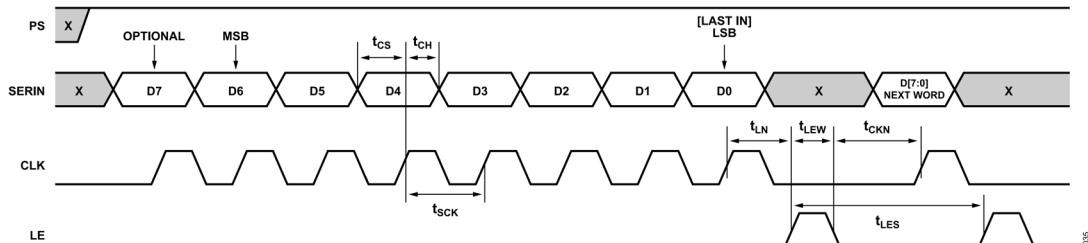

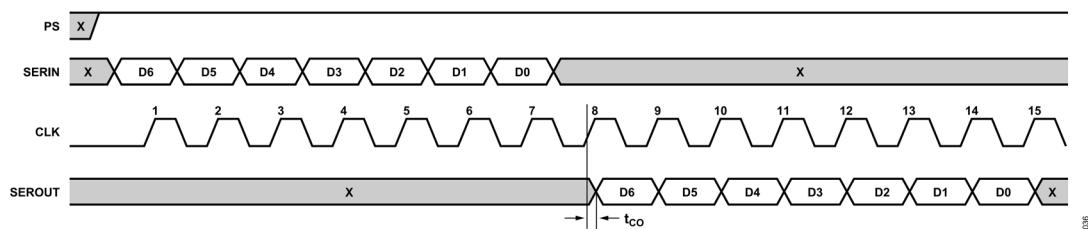

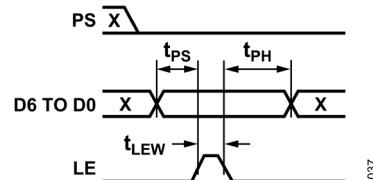

タイミング図については図 35、図 36、図 37 を参照してください。

表 3. タイミング仕様

| Parameter | Description                                                                                                                 | Min | Typ | Max | Unit |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $t_{SCK}$ | Serial period, see the <a href="#">Serial Mode Interface</a> section                                                        | 20  |     |     | ns   |

| $t_{CS}$  | Control setup time, see the <a href="#">Serial Mode Interface</a> section                                                   | 3   |     |     | ns   |

| $t_{CH}$  | Control hold time, see the <a href="#">Serial Mode Interface</a> section                                                    | 3   |     |     | ns   |

| $t_{LN}$  | LE setup time, see the <a href="#">Serial Mode Interface</a> section                                                        | 3   |     |     | ns   |

| $t_{LEW}$ | LE pulse width, see the <a href="#">Serial Mode Interface</a> section and the <a href="#">Latched Parallel Mode</a> section | 5   |     |     | ns   |

| $t_{LES}$ | LE pulse spacing, see the <a href="#">Serial Mode Interface</a> section                                                     | 150 |     |     | ns   |

| $t_{CKN}$ | Serial clock hold time from LE, see the <a href="#">Serial Mode Interface</a> section                                       | 3   |     |     | ns   |

| $t_{PH}$  | Hold time, see the <a href="#">Latched Parallel Mode</a> section                                                            | 3   |     |     | ns   |

| $t_{PS}$  | Setup time, the <a href="#">Latched Parallel Mode</a> section                                                               | 5   |     |     | ns   |

| $t_{CO}$  | Clock to output (SEROUT) time, see the <a href="#">Serial Mode Interface</a> section                                        |     | 20  |     | ns   |

## 絶対最大定格

表 4. 絶対最大定格

| Parameter                                                                  | Rating                  |

|----------------------------------------------------------------------------|-------------------------|

| Positive Supply Voltage                                                    | -0.3V to +3.6V          |

| Negative Supply Voltage                                                    | -3.6V to +0.3V          |

| Digital Control Inputs                                                     |                         |

| Voltage                                                                    | -0.3V to $V_{DD}$ +0.3V |

| Current                                                                    | 3mA                     |

| RF Power <sup>1</sup> (f = 3MHz to 20GHz, $T_{CASE}$ = 85°C <sup>2</sup> ) |                         |

| Dual Supply ( $V_{DD}$ = 3.3V, $V_{SS}$ = -3.3V)                           |                         |

| Input at ATTIN                                                             |                         |

| Average                                                                    | 27.5dBm                 |

| Peak                                                                       | 30.5dBm                 |

| Hot Switching                                                              | 27.5dBm                 |

| Input at ATTOUT                                                            |                         |

| Average                                                                    | 24.5dBm                 |

| Peak                                                                       | 27.5dBm                 |

| Hot Switching                                                              | 24.5dBm                 |

| Single Supply ( $V_{DD}$ = 3.3V, $V_{SS}$ = 0V)                            |                         |

| Input at ATTIN                                                             |                         |

| Average                                                                    | 20.5dBm                 |

| Peak                                                                       | 20.5dBm                 |

| Hot Switching                                                              | 20.5dBm                 |

| Input at ATTOUT                                                            |                         |

| Average                                                                    | 20.5dBm                 |

| Peak                                                                       | 20.5dBm                 |

| Hot Switching                                                              | 20.5dBm                 |

| Unbiased ( $V_{DD}$ and $V_{SS}$ = 0V, Input at ATTIN and ATTOUT)          | 27dBm                   |

| Temperature                                                                |                         |

| Junction ( $T_J$ )                                                         | 135°C                   |

| Storage                                                                    | -65°C to 150°C          |

| Reflow                                                                     | 260°C                   |

<sup>1</sup> 拡張周波数範囲での RF 電力処理能力の低下については、図 2 を参照してください。

<sup>2</sup>  $T_{CASE}$  = 105°C での動作の場合、RF 電力処理能力は、 $T_{CASE}$  = 85°C での仕様から 3dB 低下します。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意を払う必要があります。

$\theta_{JC}$  は、ジャンクションとケース底部 (チャンネルとキャリア底部) の間の熱抵抗です。

表 5. 热抵抗

| Package Type | $\theta_{JC}$ | Unit |

|--------------|---------------|------|

| CC-24-20     | 100           | °C/W |

## パワー・ディレーティング曲線

図 2. パワー・ディレーティングと周波数の関係、 $T_{CASE}$  = 85°C

## 絶対最大定格

### 静電放電 (ESD) 定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の帯電デバイス・モデル (CDM)。

### ADRF5703 の ESD 定格

表 6. ADRF5703、24 端子 LGA

| ESD Model                | Withstand Threshold (V) | Class |

|--------------------------|-------------------------|-------|

| HBM                      |                         |       |

| ATTIN Pin and ATTOUT Pin | 1500                    | 1C    |

| Supply and Control Pins  | 3000                    | 2     |

| CDM                      | 500                     | C2A   |

### ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することができます。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

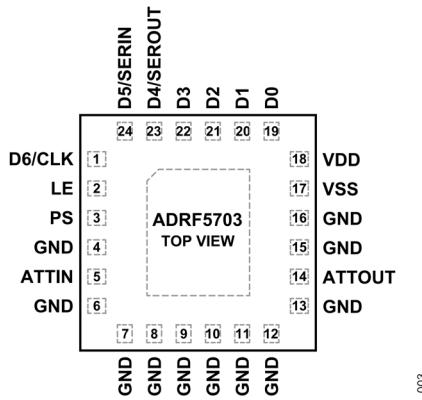

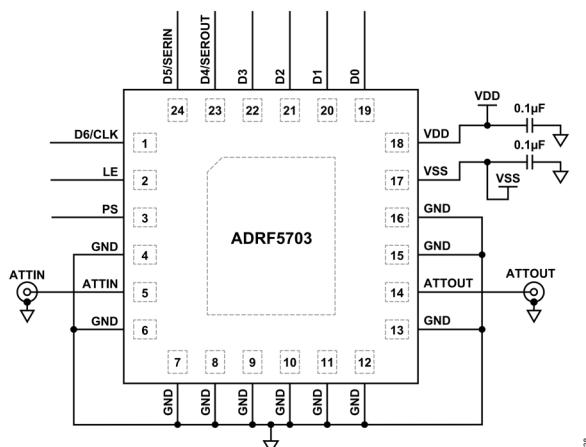

## ピン配置およびピン機能の説明

図 3. ピン配置

表 7. ピン機能の説明

| ピン番号               | 記号        | 説明                                                                                                                                         |

|--------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | D6/CLK    | 16dB アッテネータ・ビット用パラレル制御入力。シリアル・クロック入力 (CLK)。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 7</a> を参照してください。  |

| 2                  | LE        | ラッチ・イネーブル入力。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 7</a> を参照してください。                                 |

| 3                  | PS        | パラレルまたはシリアル制御インターフェースの選択入力。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 7</a> を参照してください。                  |

| 4, 6 to 13, 15, 16 | GND       | グラウンド。GND ピンは、PCB の RF グラウンドおよび DC グラウンドに接続する必要があります。                                                                                      |

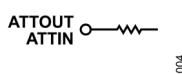

| 5                  | ATTIN     | アッテネータ入力。RF ラインの電位が 0V DC に等しい場合は、DC 阻止コンデンサは不要です。インターフェース回路図については、 <a href="#">図 4</a> を参照してください。                                         |

| 14                 | ATTOUT    | アッテネータ出力。RF ラインの電位が 0V DC に等しい場合は、DC 阻止コンデンサは不要です。インターフェース回路図については、 <a href="#">図 4</a> を参照してください。                                         |

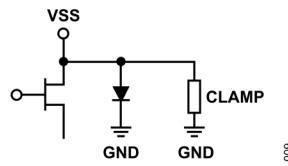

| 17                 | VSS       | 負電源入力。インターフェース回路図については、 <a href="#">図 9</a> を参照してください。                                                                                     |

| 18                 | VDD       | 正電源入力。インターフェース回路図については、 <a href="#">図 8</a> を参照してください。                                                                                     |

| 19                 | D0        | 0.25dB アッテネータ・ビット用パラレル制御入力。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 5</a> を参照してください。                  |

| 20                 | D1        | 0.5dB アッテネータ・ビット用パラレル制御入力。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 5</a> を参照してください。                   |

| 21                 | D2        | 1.0dB アッテネータ・ビット用パラレル制御入力。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 5</a> を参照してください。                   |

| 22                 | D3        | 2dB アッテネータ・ビット用パラレル制御入力。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 5</a> を参照してください。                     |

| 23                 | D4/SEROUT | 4dB アッテネータ・ビット用パラレル制御入力。シリアル・データ出力 (SEROUT)。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 6</a> を参照してください。 |

| 24                 | D5/SERIN  | 8dB アッテネータ・ビット用パラレル制御入力。シリアル・データ入力 (SERIN)。詳細については、 <a href="#">動作原理</a> のセクションを参照してください。インターフェース回路図については、 <a href="#">図 7</a> を参照してください。  |

## ピン配置およびピン機能の説明

## インターフェース回路図

図 4. ATTIN および ATTOUT のインターフェース回路図

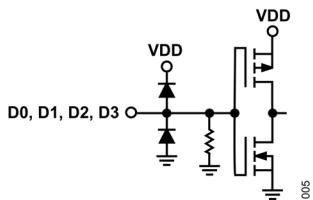

図 5. デジタル入力のインターフェース回路図

(D0、D1、D2、D3)

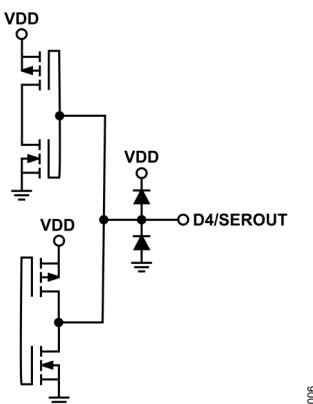

図 6. デジタル入力のインターフェース回路図 (D4/SEROUT)

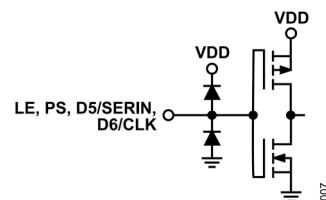

図 7. デジタル入力のインターフェース回路図

(LE、PS、D5/SERIN、D6/CLK)

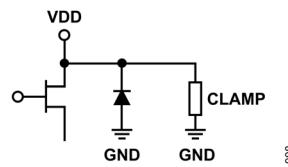

図 8. VDD 入力のインターフェース回路図

図 9. VSS 入力のインターフェース回路図

## 代表的な性能特性

## インサーション・ロス、リターン・ロス、状態誤差、ステップ誤差、リアクティブ・フェーズ

特に指定のない限り、 $V_{DD} = +3.3V$ 、 $V_{SS} = -3.3V$ 、 $V_{CTRL} = 0V$  または  $3.3V$ 、 $T_{CASE} = 25^{\circ}C$ 、 $50\Omega$  システム。

図 10. 様々な温度でのインサーション・ロスと周波数の関係

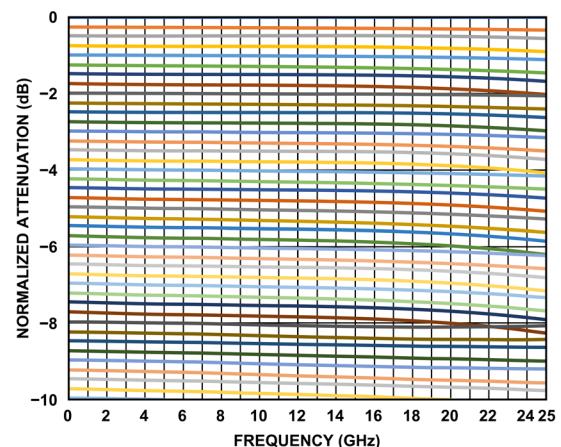

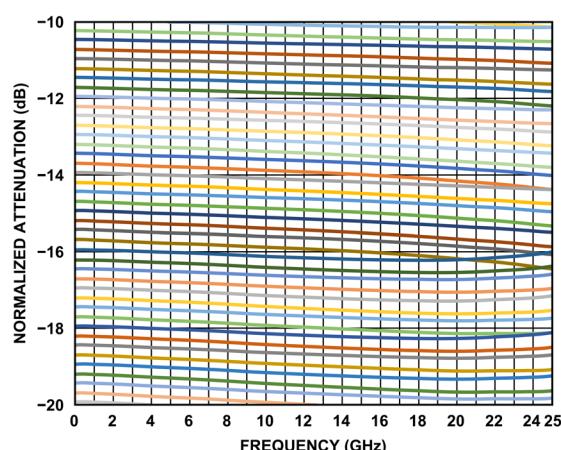

図 13. 減衰状態での規格化減衰量と周波数の関係、-10dB まで

図 11. 主要な減衰状態での入力リターン・ロスと周波数の関係

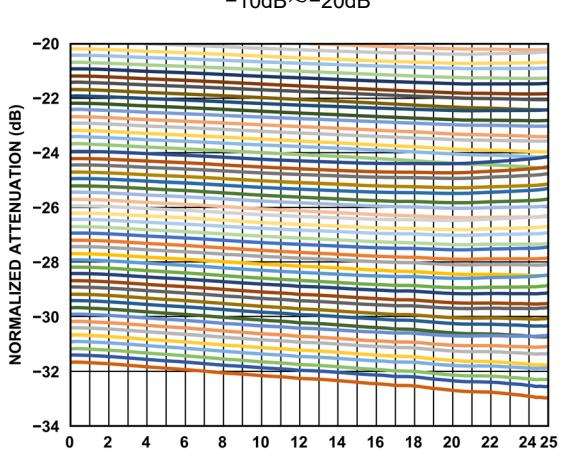

図 14. 減衰状態での規格化減衰量と周波数の関係、-10dB～-20dB

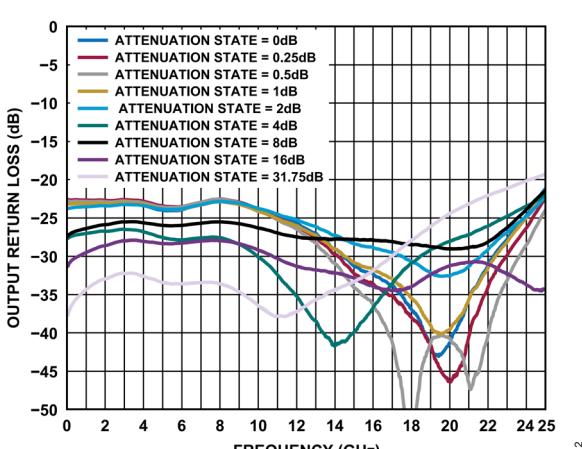

図 12. 主要な減衰状態での出力リターン・ロスと周波数の関係

図 15. 減衰状態での規格化減衰量と周波数の関係、-20dB～-32dB

## 代表的な性能特性

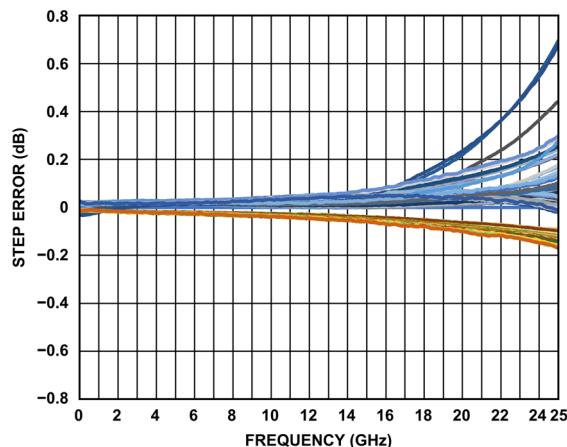

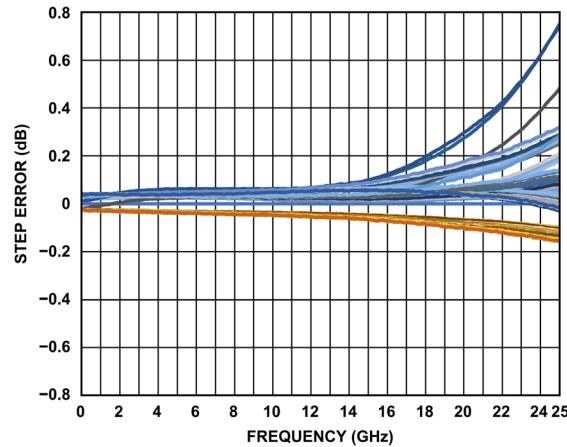

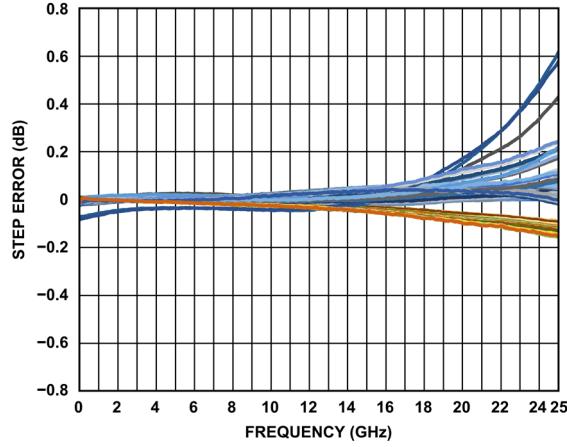

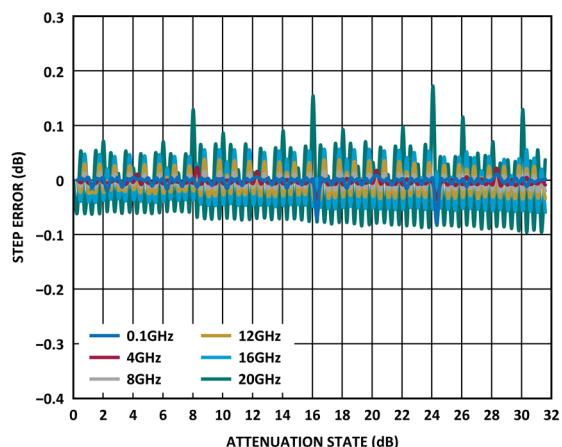

図 16. 25°C における 128 の減衰状態でのステップ誤差と周波数の関係

図 17. 85°C における 128 の減衰状態でのステップ誤差と周波数の関係

図 18. -40°C における 128 の減衰状態でのステップ誤差と周波数の関係

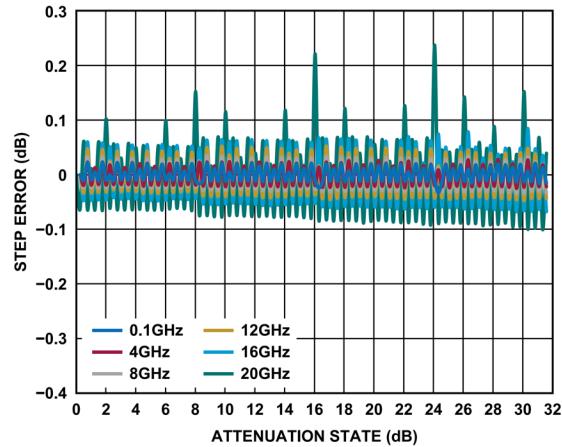

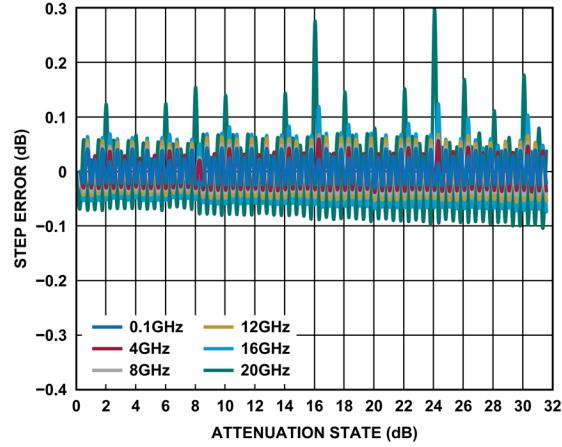

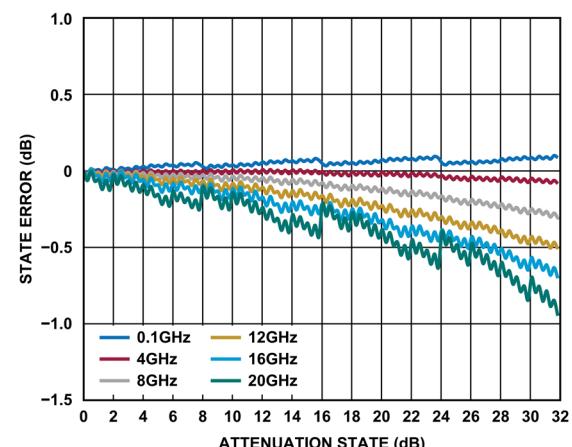

図 19. 25°C における様々な周波数でのステップ誤差と減衰状態の関係

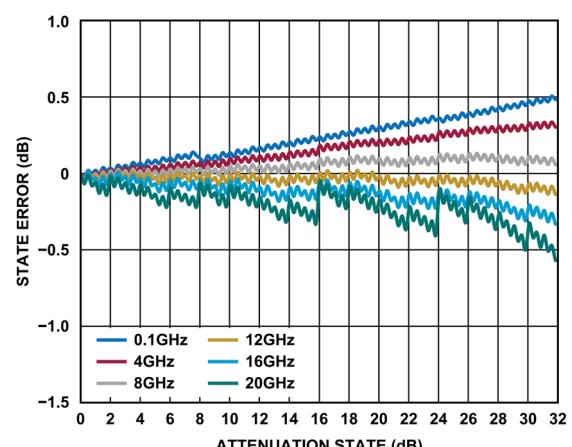

図 20. 85°C における様々な周波数でのステップ誤差と減衰状態の関係

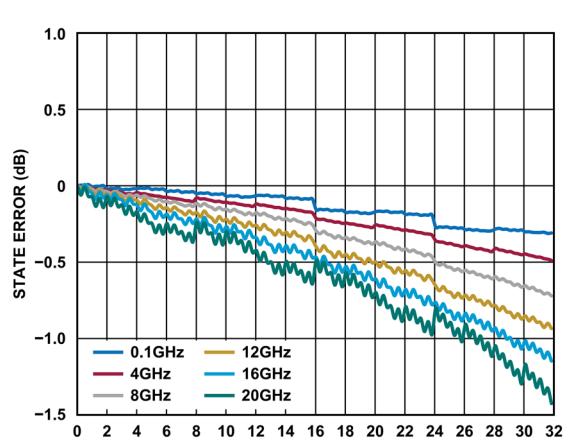

図 21. -40°C における様々な周波数でのステップ誤差と減衰状態の関係

## 代表的な性能特性

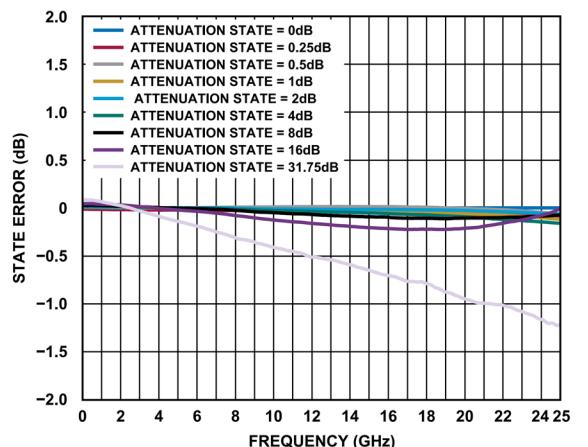

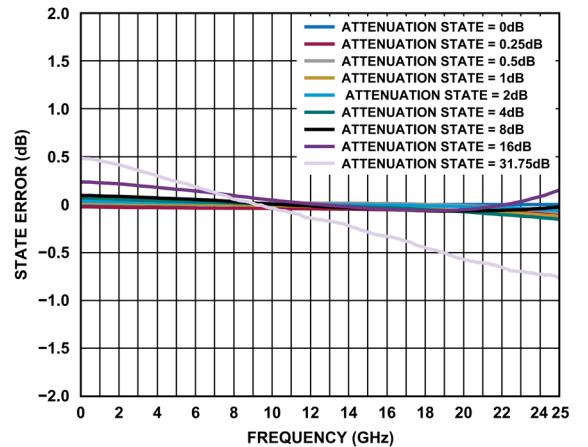

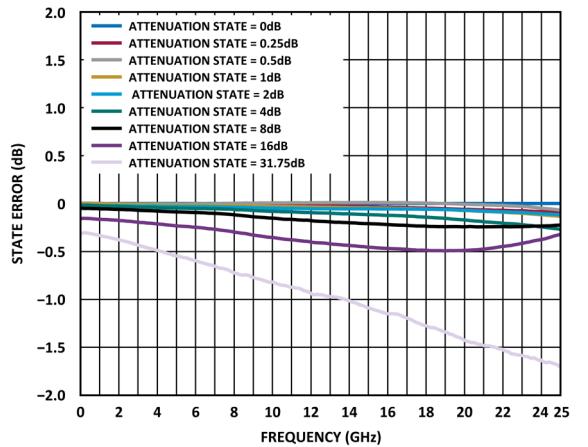

図 22. 25°C における主要な減衰状態での状態誤差と周波数の関係

図 23. 85°C における主要な減衰状態での状態誤差と周波数の関係

図 24. -40°C における主要な減衰状態での状態誤差と周波数の関係

図 25. 25°C における様々な周波数での状態誤差と減衰状態の関係

図 26. 85°C における様々な周波数での状態誤差と減衰状態の関係

図 27. -40°C における様々な周波数での状態誤差と減衰状態の関係

## 代表的な性能特性

028

図 28. 主要な減衰状態でのリアクティブ・フェーズと周波数の関係

029

図 29. 様々な周波数でのリアクティブ・フェーズと減衰状態の関係

## 代表的な性能特性

## 入力電力圧縮と3次インターセプト

特に指定のない限り、 $V_{DD} = +3.3V$ 、 $V_{SS} = -3.3V$ 、 $V_{CTRL} = 0V$  または  $3.3V$ 、 $T_{CASE} = 25^{\circ}C$ 、 $50\Omega$  システム。

図 30. 主要な減衰状態での入力 P0.1dB と周波数の関係

図 32. 主要な減衰状態での入力 P0.1dB と周波数の関係、

低周波数の詳細

図 31. 主要な減衰状態での入力 IP3 と周波数の関係

図 33. 主要な減衰状態での入力 IP3 と周波数の関係、

低周波数の詳細

## 動作原理

ADRF5703 は、0.25dB ステップで 31.75dB の減衰範囲を備えた 7 ビット固定のアッテネータ・アレイを内蔵しています。内蔵のドライバがアッテネータ・アレイのシリアルまたはパラレルのモード制御を行います。

ADRF5703 には、D0 (LSB) ~D6 (MSB)、LE、PS の 9 つのデジタル制御入力があります。必要な減衰状態をシリアル・モードまたはパラレル・モードで選択するには、表 8 および表 9 を参照してください。タイミング図については、図 35、図 36、図 37 を参照してください。

## 電源

ADRF5703 には、VDD ピンに印加する正電源電圧と、VSS ピンに印加する負電源電圧が必要です。高周波ノイズをフィルタリングするため、電源ラインにバイパス・コンデンサを接続することを推奨します。

パワーアップ・シーケンスは次のとおりです。

1. GND をグラウンドに接続します。

2. VDD と VSS に電源を入れます。ランプアップ中に VDD で電流トランジエントが発生しないように、VDD の電源投入後に VSS を電源投入します。

3. デジタル制御入力に電源を投入します。デジタル制御入力の順序は重要ではありません。しかし、VDD に電源を入れる前に誤ってデジタル制御入力に電源を入れると、順方向バイアスがかかり、内部の ESD 構造を損傷するおそれがあります。この損傷を防ぐには、1kΩ の抵抗を直列接続して、そのような場合にデジタル制御入力ピンに流入する電流を制限します。

表 8. 真理値表

| Digital Control Input <sup>1</sup> |      |      |      |      |      |      |               | Attenuation State (dB) |

|------------------------------------|------|------|------|------|------|------|---------------|------------------------|

| D6                                 | D5   | D4   | D3   | D2   | D1   | D0   |               |                        |

| Low                                | Low  | Low  | Low  | Low  | Low  | Low  | 0 (reference) |                        |

| Low                                | Low  | Low  | Low  | Low  | Low  | High | 0.25          |                        |

| Low                                | Low  | Low  | Low  | Low  | High | Low  | 0.5           |                        |

| Low                                | Low  | Low  | Low  | High | Low  | Low  | 1.0           |                        |

| Low                                | Low  | Low  | High | Low  | Low  | Low  | 2.0           |                        |

| Low                                | Low  | High | Low  | Low  | Low  | Low  | 4.0           |                        |

| Low                                | High | Low  | Low  | Low  | Low  | Low  | 8.0           |                        |

| High                               | Low  | Low  | Low  | Low  | Low  | Low  | 16.0          |                        |

| High                               | High | High | High | High | High | High | 31.75         |                        |

<sup>1</sup> この表に示す減衰状態をどのように組み合わせても、選択したビットの和に等しい減衰量が得られます。

図 34. 簡素化した回路図

4. RF 入力信号を ATTIN と ATTOUT に印加します。

パワーダウン・シーケンスは、パワーアップ・シーケンスと逆の順序です。

## パワーアップ状態

ADRF5703 は、VDD の印加時にアッテネータを最大減衰状態 (31.75dB) に設定するパワー・リセット回路を内蔵しています。

## 単電源動作

ADRF5703 は、単一の正電源電圧を VDD ピンに印加し、VSS ピンをグラウンドに接続した状態でも動作できます。単電源動作においては、スイッチング特性、直線性、電力処理能力が低下します。詳細については表 2 を参照してください。

## RF 入出力

両方の RF ポート (ATTIN および ATTOUT) は 0V に DC カップリングさせます。RF ラインの電位が 0V に等しい場合、RF ポートでの DC 阻止は不要です。

電力処理は、ATTIN ポートによって定義されます。表 1 の RF 入力電力の各仕様を参照してください。

## 動作原理

## シリアル・モードまたはパラレル・モードの選択

ADRF5703 は、PS ピンをハイに設定することでシリアル・モード制御、ローに設定することでパラレル・モード制御が可能です（表 9 参照）。

表 9. モード選択

| PS   | Control Mode |

|------|--------------|

| Low  | Parallel     |

| High | Serial       |

## シリアル・モード・インターフェース

ADRF5703 は、シリアル・データ入力（SERIN）、クロック（CLK）、シリアル・データ出力（SEROUT）、ラッチ・イネーブル（LE）の 4 線式 SPI に対応します。シリアル制御インターフェースは、PS ピンをハイに設定することでアクティベート化できます。

ADRF5703 の減衰状態は、7 ビットまたは 8 ビットの SERIN データを用いて制御できます。8 ビット・ワードを使用してアッテネータの状態を制御する場合、最初の 2 ビットはドント・ケア・ビットとなります。これらのビットはローのままでもハイのままでも、あるいは完全に省略されてもかまいません。アッテネータの状態はビット[D6:D0]のみで設定されます。

シリアル・モードでは、SERIN データは CLK の立上がりエッジでクロックされ、シフト・レジスタに MSB ファーストで入力されます。その後、新しい減衰状態をデバイスにラッチするため、LE をハイにトグルする必要があります。LE がハイのままでは CLK がマスクされてアッテネータの値を変更できないので、新しい SERIN データをクロックしてシフト・レジスタに入力するには、LE をローにする必要があります。詳細については、図 35、図 36、タイミング仕様のセクション、RF 入出力のセクションを参照してください。

図 35. シリアル制御のタイミング図

図 36. シリアル出力のタイミング図

## 動作原理

### パラレル・モード・インターフェース

ADRF5703 には、D0 (LSB) ~D6 (MSB) の 7 つのデジタル制御入力があり、パラレル・モードで目的の減衰状態を選択できます (表 8 参照)。

パラレル動作には、直接パラレルとラッチド・パラレルの 2 つのモードがあります。

#### 直接パラレル・モード

パラレル・モードを有効にするには、LE ピンをハイのままにします。減衰状態を変更するには、制御電圧入力 (D0~D6) を直接使用します。直接パラレル・モードは、アッテネータを手動で制御する場合に使用します。

### ラッチド・パラレル・モード

ラッチド・パラレル・モードを有効にするには、制御電圧入力 (D0~D6) を変更して減衰状態を設定する際に、LE ピンをローのままにしておく必要があります。目的の状態を設定したら、LE をハイにトグルして、7 ビット・データをアッテネータ・アレイのバイパス・スイッチに転送し、次に LE をローにトグルして、次の目的の減衰変更までデバイスに変更をラッチします (詳細については図 37 および表 3 を参照)。

図 37. ラッチド・パラレル・モードのタイミング図

## アプリケーション情報

ADRF5703 には、2 つの電源ピン (VDD および VSS) と 9 つの制御ピン (PS、LE、D0~D6) があります。図 38 に、電源ピンおよび制御ピンの外付け部品、およびその接続方法を示します。電源ピン (VDD および VSS) は、0.1 $\mu$ F の多層セラミック・コンデンサを用いてデカップリングします。デカップリング・コンデンサは、ADRF5703 のできるだけ近くに配置します。このデバイスのピン配置により、デカップリング・コンデンサを ADRF5703 の近くに配置することができます。RF ラインを 0V 以外の電圧でバイアスする場合に RF ピン (ATTIN および ATTOUT) に接続する DC 阻止コンデンサを除き、バイアスおよび動作用には他の外付け部品は不要です。詳細については、[ピン配置およびピン機能の説明](#)のセクションを参照してください。

図 38. 簡略アプリケーション回路

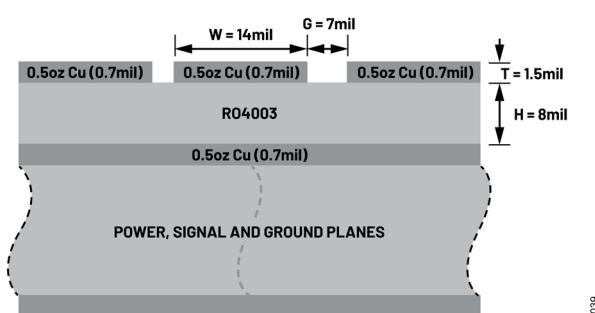

## PCB 設計のための推奨事項

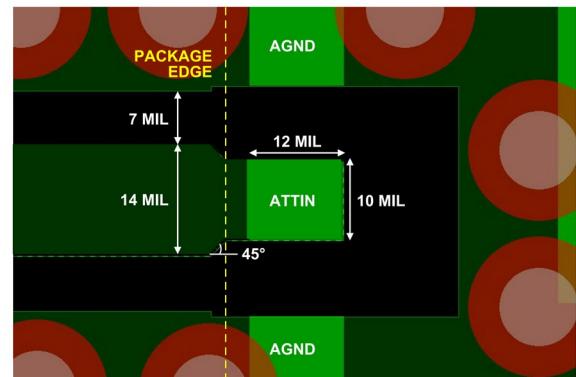

RF ポートは内部で  $50\Omega$  に整合されており、ピン配置は、PCB 上にある特性インピーダンスが  $50\Omega$  のコブレーナ導波路 (CPWG) に接合できるよう設計されています。図 39 に、厚さ 8mil の Rogers RO4003 誘電体材料を用いた RF 基板の CPWG RF パターン設計の参考例を示します。1.5mil の銅仕上げ厚さに対し、幅 14mil、クリアランス 7mil の RF パターンを使用することを推奨します。

図 39. PCB 層構成例

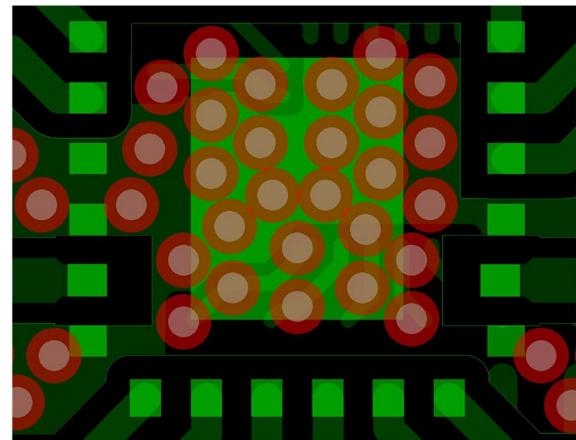

図 40 に、ADRF5703 からの RF 配線パターン、電源、制御信号のルーティングを示します。グランド・プレーンは、RF および熱性能を最適化するため、できる限り多数の充填スルーピアで接続されています。デバイスの主な熱経路は裏面です。

図 40. PCB 配線

ADRF5703 の ATTIN ピンおよび ATTOUT ピンからリファレンス層構成の  $50\Omega$  CPWG までの間の推奨レイアウトを図 41 に示します。PCB パッドは、デバイス・パッドと 1 対 1 に対応します。グラウンド・パッドは、ハンダ・マスク定義で描かれ、信号パッドはパッド定義で描かれています。PCB パッドからの RF パターンは、デバイス端まで延長され、その後  $45^\circ$  の角度で RF パターンに向けてテーパ状になっています。ペースト・マスクも、アーチャーが減少することなくパッドと一致するよう設計されており、パドル用の複数の開口部に分割されています。

図 41. ATTIN および ATTOUT ピンの推奨される遷移

異なる誘電体厚さや CPWG 設計の代替 PCB 層構成に関する推奨事項は、[アナログ・デバイセズのテクニカル・サポート・リクエスト](#)にお問い合わせください。

## 外形寸法

| Package Drawing Option | Package Type | Package Description                 |

|------------------------|--------------|-------------------------------------|

| CC-24-20               | LGA          | 24-Terminal Land Grid Array Package |

最新のパッケージ外形情報およびランド・パターン（実装面積）については、[パッケージ索引](#)を参照してください。

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description               | Package Quantity | Package Option |

|--------------------|-------------------|-----------------------------------|------------------|----------------|

| ADRF5703BCCZN      | -40°C to +105°C   | 24-Terminal Land Grid Array [LGA] | Tape, 500        | CC-24-20       |

| ADRF5703BCCZN-R7   | -40°C to +105°C   | 24-Terminal Land Grid Array [LGA] | Reel, 500        | CC-24-20       |

<sup>1</sup> Z = RoHS 準拠製品。