# 無反射、100MHz～44GHz シリコン SP4T スイッチ

## データシート

ADRF5042

### 特長

超広帯域周波数範囲：100MHz～44GHz

無反射 50Ω 設計

低挿入損失

1.8dB (最大 18GHz)

2.8dB (最大 40GHz)

3.2dB (最大 44GHz)

高アイソレーション

50dB (最大 18GHz)

39dB (最大 40GHz)

35dB (最大 44GHz)

高入力直線性

P0.1dB : 26dBm (代表値)

IP3 : 47dBm (代表値)

大電力処理

スルー・パス : 24dBm

終端パス : 24dBm

オール・オフ状態コントロール

ロジック・セレクト制御

低周波数スプリアスなし

セトリング・タイム (最終 RF 出力の 0.1dB まで) : 30ns

24 端子、3mm × 3mm ランド・グリッド・アレイ (LGA)

パッケージ

ADRF5043 低周波数カットオフ・バージョンとピン互換

### アプリケーション

工業用スキャナ

試験用計測器

セルラ・インフラストラクチャ - ミリ波 (mmWave) 5G

防衛用無線、レーダー、電子対抗手段 (ECM)

マイクロ波無線および超小型地球局 (VSAT)

### 概要

ADRF5042 はシリコン・オン・インシレータ (SOI) プロセスで製造された無反射の SP4T スイッチです。

このデバイスは、100 MHz～44GHz で動作し、挿入損失は 3.2dB 未満、絶縁は 35dB を上回ります。24dBm の RF 入力電力処理機能を備えており、スルー・パスと終端パスに対応しています。

ADRF5042 は+3.3V と-3.3V の両電源電圧を必要とし、CMOS/低電圧トランジスタ・トランジスタ・ロジック (LVTTL) 互換の制御を備えています。

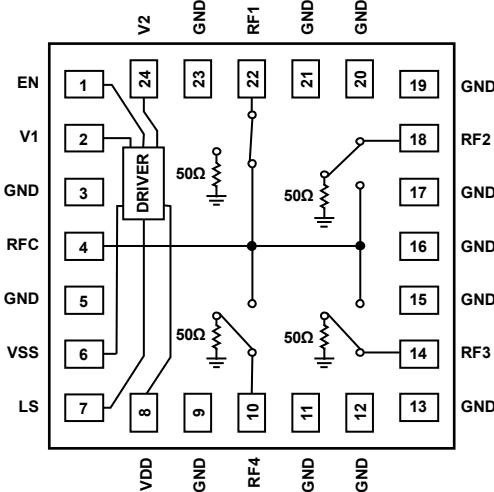

### 機能ブロック図

23793-001

図 1.

ADRF5042 は、イネーブル制御とロジック・セレクト制御を備え、イネーブル制御はオール・オフ状態、ロジック・セレクト制御はポート・ミラーリングをつかさどります。

ADRF5042 は、9kHz～44GHz で動作する ADRF5043 (低周波カットオフ・バージョン) とのピン互換性を備えています。

ADRF5042 は、24 端子、3mm × 3mm の RoHS 準拠ランド・グリッド・アレイ (LGA) パッケージで提供され、-40°C～+105°C で動作可能です。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

Rev. 0

©2020 Analog Devices, Inc. All rights reserved.

アナログ・デバイセズ株式会社

本社／〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワー 10F

電話 03 (5402) 8200

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F

電話 06 (6350) 6868

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F

電話 052 (569) 6300

## 目次

|                |   |                      |    |

|----------------|---|----------------------|----|

| 特長             | 1 | ピン配置およびピン機能の説明       | 6  |

| アプリケーション       | 1 | インターフェース回路図          | 6  |

| 機能ブロック図        | 1 | 代表的な性能特性             | 7  |

| 概要             | 1 | 挿入損失、リターン損失、アイソレーション | 7  |

| 改訂履歴           | 2 | 入力電力圧縮と3次インターセプト     | 9  |

| 仕様             | 3 | 動作原理                 | 10 |

| 絶対最大定格         | 5 | アプリケーション情報           | 11 |

| 熱抵抗            | 5 | 評価用ボード               | 11 |

| 静電放電（ESD）定格    | 5 | 外形寸法                 | 12 |

| パワー・ディレーティング曲線 | 5 | オーダー・ガイド             | 12 |

| ESDに関する注意      | 5 |                      |    |

## 改訂履歴

7/2020—Revision 0: Initial Version

## 仕様

特に指定のない限り、 $50\Omega$ システムに対し、正電源電圧 ( $V_{DD}$ ) = 3.3V、負電源電圧 ( $V_{SS}$ ) = -3.3V、V1ピン電圧 ( $V_1$ ) = 0Vまたは3.3V、V2ピン電圧 ( $V_2$ ) = 0Vまたは3.3V、LS = 0Vまたは3.3V、EN = 0Vまたは3.3V、 $T_{CASE} = 25^\circ\text{C}$ 。RFxはRF1～RF4を意味します。 $V_{CTL}$ はデジタル制御入力電圧です。

表 1.

| パラメータ                          | 記号                   | テスト条件／コメント                                                                                       | Min | Typ                             | Max    | 単位            |

|--------------------------------|----------------------|--------------------------------------------------------------------------------------------------|-----|---------------------------------|--------|---------------|

| FREQUENCY RANGE                | f                    |                                                                                                  | 100 |                                 | 44,000 | MHz           |

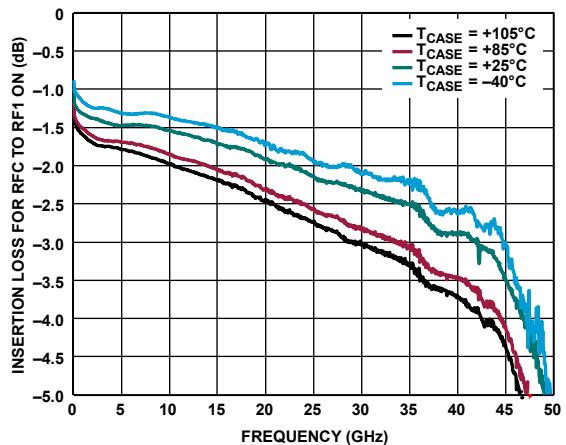

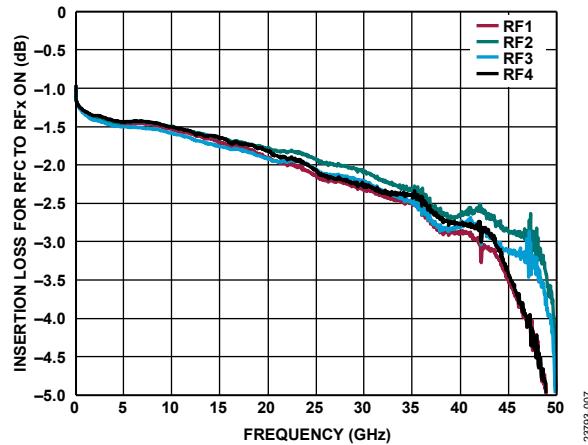

| INSERTION LOSS                 |                      |                                                                                                  |     |                                 |        |               |

| Between RFC and RFx (On)       |                      | 100 MHz～18 GHz<br>18 GHz～26 GHz<br>26 GHz～35 GHz<br>35 GHz～40 GHz<br>40 GHz～44 GHz               |     | 1.8<br>2.2<br>2.5<br>2.8<br>3.2 |        | dB            |

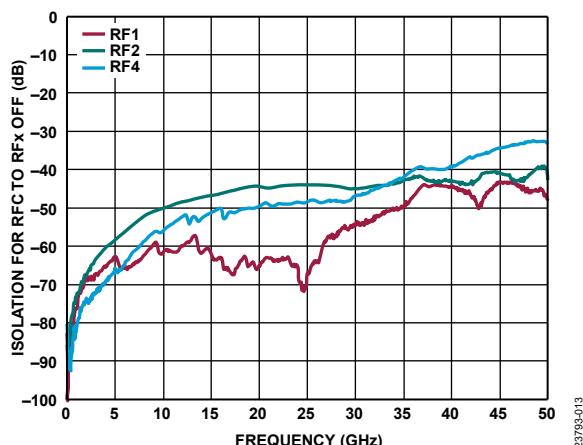

| ISOLATION                      |                      |                                                                                                  |     |                                 |        |               |

| Between RFC and RFx (Off)      |                      | 100 MHz～18 GHz<br>18 GHz～26 GHz<br>26 GHz～35 GHz<br>35 GHz～40 GHz<br>40 GHz～44 GHz               |     | 50<br>46<br>41<br>39<br>35      |        | dB            |

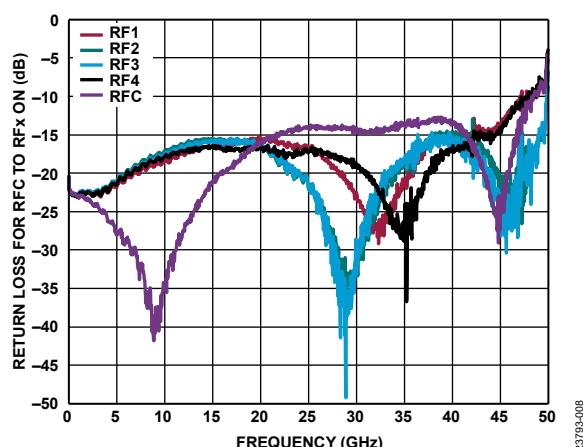

| RETURN LOSS                    |                      |                                                                                                  |     |                                 |        |               |

| RFC and RFx (On)               |                      | 100 MHz～18 GHz<br>18 GHz～26 GHz<br>26 GHz～35 GHz<br>35 GHz～40 GHz<br>40 GHz～44 GHz               |     | 16<br>14<br>13<br>13<br>14      |        | dB            |

| RFx (Off)                      |                      | 100 MHz～18 GHz<br>18 GHz～26 GHz<br>26 GHz～35 GHz<br>35 GHz～40 GHz<br>40 GHz～44 GHz               |     | 24<br>22<br>15<br>12<br>10      |        | dB            |

| SWITCHING                      |                      |                                                                                                  |     |                                 |        |               |

| Rise and Fall Time             | $t_{RISE}, t_{FALL}$ | RF出力の 10%～90%                                                                                    |     | 3                               |        | ns            |

| On and Off Time                | $t_{ON}, t_{OFF}$    | 50% $V_{CTL}$ ～RF出力の 90%                                                                         |     | 14                              |        | ns            |

| Settling Time                  |                      |                                                                                                  |     |                                 |        |               |

| 0.1 dB                         |                      | 50% $V_{CTL}$ ～最終RF出力の 0.1dB                                                                     |     | 30                              |        | ns            |

| 0.05 dB                        |                      | 50% $V_{CTL}$ ～最終RF出力の 0.05dB                                                                    |     | 36                              |        | ns            |

| INPUT LINEARITY <sup>1</sup>   |                      |                                                                                                  |     |                                 |        |               |

| 0.1 dB Power Compression       | P0.1dB               | $f = 500 \text{ MHz} \sim 40 \text{ GHz}$                                                        |     | 26                              |        | dBm           |

| 1 dB Power Compression         | P1dB                 | $f = 500 \text{ MHz} \sim 40 \text{ GHz}$                                                        |     | 27                              |        | dBm           |

| Third-Order Intercept          | IP3                  | ツー・トーン入力電力 = トーンあたり 15dB、<br>$f = 500 \text{ MHz} \sim 40 \text{ GHz}, \Delta f = 1 \text{ MHz}$ |     | 47                              |        | dBm           |

| Second-Order Intercept         | IP2                  | ツー・トーン入力電力 = トーンあたり 15dB、<br>$f = 10 \text{ GHz}, \Delta f = 1 \text{ MHz}$                      |     | 120                             |        | dBm           |

| VIDEO FEEDTHROUGH <sup>2</sup> |                      |                                                                                                  |     | 60                              |        | mV p-p        |

| SUPPLY CURRENT                 |                      |                                                                                                  |     |                                 |        |               |

| Positive Supply Current        | $I_{DD}$             | $V_{DD}$ ピン、 $V_{SS}$ ピン                                                                         |     | 370                             |        | $\mu\text{A}$ |

| Negative Supply Current        | $I_{SS}$             |                                                                                                  |     | -100                            |        | $\mu\text{A}$ |

| DIGITAL CONTROL INPUTS         |                      |                                                                                                  |     |                                 |        |               |

| Voltage                        |                      |                                                                                                  |     |                                 |        |               |

| Low                            | $V_{INL}$            | V1ピン、V2ピン、ENピン、LSピン                                                                              | 0   | 0.8                             |        | V             |

| High                           | $V_{INH}$            |                                                                                                  | 1.2 | 3.3                             |        | V             |

# データシート

ADRF5042

| パラメータ                            | 記号                | テスト条件／コメント                                              | Min   | Typ             | Max  | 単位  |

|----------------------------------|-------------------|---------------------------------------------------------|-------|-----------------|------|-----|

| Current                          |                   |                                                         |       |                 |      |     |

| Low                              | I <sub>INL</sub>  |                                                         |       | 3               |      | μA  |

| High                             | I <sub>INH</sub>  |                                                         |       | 6               |      | μA  |

| RECOMMENDED OPERATING CONDITIONS |                   |                                                         |       |                 |      |     |

| Supply Voltage                   |                   |                                                         |       |                 |      |     |

| Positive                         | V <sub>DD</sub>   |                                                         | 3.15  | 3.45            |      | V   |

| Negative                         | V <sub>SS</sub>   |                                                         | -3.45 | -3.15           |      | V   |

| Digital Control Inputs Voltage   | V <sub>CTL</sub>  |                                                         | 0     | V <sub>DD</sub> |      | V   |

| RFx Input Power <sup>3</sup>     | P <sub>IN</sub>   | f = 500 MHz～44GHz、T <sub>CASE</sub> = 85°C <sup>4</sup> |       |                 |      |     |

| Through Path                     |                   | 平均                                                      |       | 24              |      | dBm |

|                                  |                   | ピーク                                                     |       | 24              |      | dBm |

| Terminated Path                  |                   | 平均                                                      |       | 24              |      | dBm |

|                                  |                   | ピーク                                                     |       | 24              |      | dBm |

| Hot Switching                    |                   | 平均                                                      |       | 24              |      | dBm |

|                                  |                   | ピーク                                                     |       | 24              |      | dBm |

| Case Temperature                 | T <sub>CASE</sub> |                                                         | -40   |                 | +105 | °C  |

<sup>1</sup> 入力直線性と周波数の関係については、図18～図21を参照してください。

<sup>2</sup> ビデオ・フィードスルーは、制御電圧のスイッチングの間RF信号がない状態で、50Ωのテスト・セットアップのRFポートで測定されるスプリアスDCトランジエンントです。

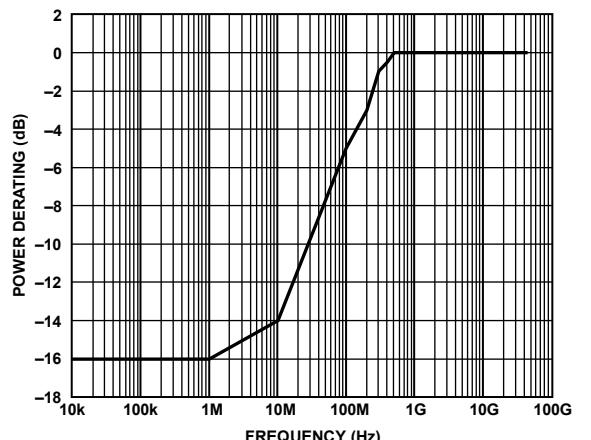

<sup>3</sup> パワー・ディレーティングと周波数の関係については、図2を参照してください。

<sup>4</sup> 105°Cでの動作の場合、電力処理はT<sub>CASE</sub> = 85°Cでの仕様より3dB低下します。

## 絶対最大定格

推奨動作条件については、[表1](#)を参照してください。

表2.

| Parameter                                                                    | Rating                                                       |

|------------------------------------------------------------------------------|--------------------------------------------------------------|

| Supply Voltage                                                               |                                                              |

| Positive                                                                     | -0.3 V to +3.6 V                                             |

| Negative                                                                     | -3.6 V to +0.3 V                                             |

| Digital Control Inputs <sup>1</sup>                                          | -0.3 V to $V_{DD}$ + 0.3 V or 3.3 mA, whichever occurs first |

| RFx Input Power ( $f^2 = 500$ MHz to 44 GHz, $T_{CASE} = 85^\circ\text{C}$ ) |                                                              |

| Through Path                                                                 |                                                              |

| Average                                                                      | 26 dBm                                                       |

| Peak                                                                         | 26 dBm                                                       |

| Terminated Path                                                              |                                                              |

| Average                                                                      | 25 dBm                                                       |

| Peak                                                                         | 25 dBm                                                       |

| Hot Switching                                                                |                                                              |

| Average                                                                      | 25 dBm                                                       |

| Peak                                                                         | 25 dBm                                                       |

| Temperature                                                                  |                                                              |

| Junction, $T_J$                                                              | 135°C                                                        |

| Storage Range                                                                | -65°C to +150°C                                              |

| Reflow                                                                       | 260°C                                                        |

<sup>1</sup>デジタル制御ピンの過電圧は、内蔵ダイオードによりクランプされます。電流は所定の最大定格に制限する必要があります。

<sup>2</sup>パワー・ディレーティングと周波数の関係については、[図2](#)を参照してください。

<sup>3</sup>105°Cでの動作の場合、電力処理は  $T_{CASE} = 85^\circ\text{C}$ での仕様より 3dB 低下します。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCB の熱設計には、細心の注意を払う必要があります。

$\theta_{JC}$  は、ジャンクションからケース底部（チャンネルからパッケージ底部）への熱抵抗です。

表3. 热抵抗

| Package Type    | $\theta_{JC}$ <sup>1</sup> | Unit |

|-----------------|----------------------------|------|

| CC-24-12        |                            |      |

| Through Path    | 468                        | °C/W |

| Terminated Path | 200                        | °C/W |

<sup>1</sup>  $\theta_{JC}$  は、以下の条件でのシミュレーションによって求めました。すなわち、熱伝達はチャンネルからグラウンド・パッドを通って PCB までの熱伝導のみに起因し、グラウンド・パッドは 85°C の動作温度で一定に保たれるものとします。

## 静電放電（ESD）定格

以下の ESD 情報は、ESD による影響を受けやすいデバイスの取り扱いについて、ESD に対して保護された環境においてのみ適用できます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル（HBM）。

## ADRF5042 の ESD 定格

表4. ADRF5042、24 端子 LGA

| ESD Model                       | Withstand Threshold (V) |

|---------------------------------|-------------------------|

| HBM                             |                         |

| RFx Pins                        | 375                     |

| Supply and Digital Control Pins | 2000                    |

## パワー・ディレーティング曲線

図2. パワー・ディレーティングと周波数の関係、低周波数の詳細、 $T_{CASE} = 85^\circ\text{C}$

## ESDに関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することができます。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

## データシート

**ADRF5042**

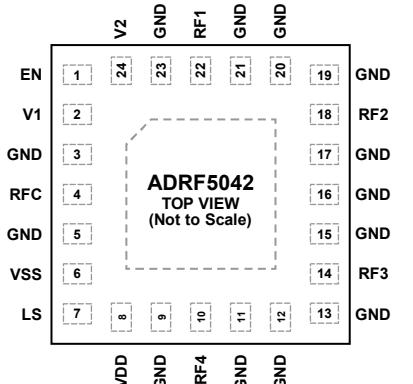

## ピン配置およびピン機能の説明

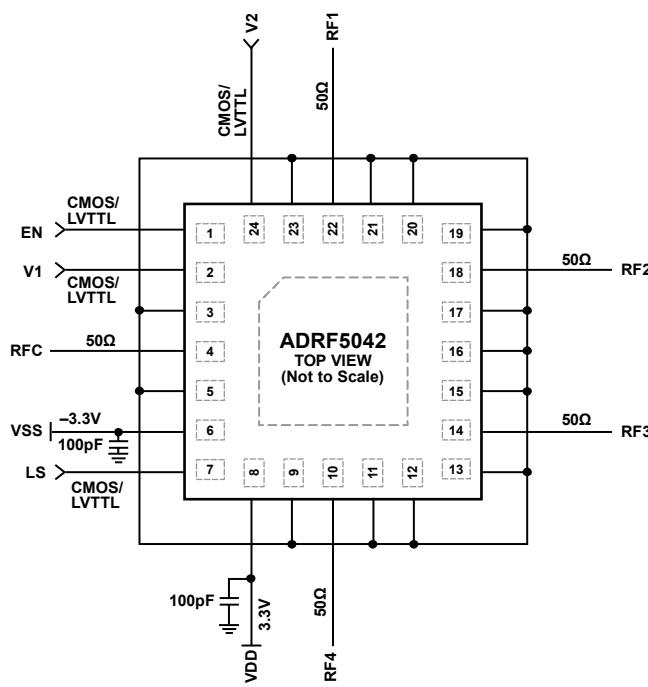

図 3. ピン配置（上面図）

表 5. ピン機能の説明

| ピン番号                                         | 記号   | 説明                                                                                                                                 |

|----------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| 1                                            | EN   | イネーブル入力。真理値表については表 6 を参照してください。インターフェース回路図については、図 5 を参照してください。                                                                     |

| 2                                            | VI   | 制御入力 1。真理値表については表 6 を参照してください。インターフェース回路図については、図 5 を参照してください。                                                                      |

| 3, 5, 9, 11 to 13, 15 to 17,<br>19 to 21, 23 | GND  | グラウンド。GND ピンは、PCB の RF/DC グラウンドに接続する必要があります。                                                                                       |

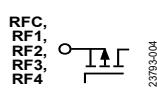

| 4                                            | RFC  | RF 共通ポート。RFC は 0V に DC カップリングされ、 $50\Omega$ に AC 整合されています。RF ラインの電位が 0Vdc に等しい場合は、DC 阻止コンデンサは不要です。インターフェース回路図については、図 4 を参照してください。  |

| 6                                            | VSS  | 負電源電圧。                                                                                                                             |

| 7                                            | LS   | ロジック・セレクト入力。真理値表については表 6 を参照してください。インターフェース回路図については、図 5 を参照してください。                                                                 |

| 8                                            | VDD  | 正電源電圧。                                                                                                                             |

| 10                                           | RF4  | RF 投ポート 4。RF4 は 0V に DC カップリングされ、 $50\Omega$ に AC 整合されています。RF ラインの電位が 0Vdc に等しい場合は、DC 阻止コンデンサは不要です。インターフェース回路図については、図 4 を参照してください。 |

| 14                                           | RF3  | RF 投ポート 3。RF3 は 0V に DC カップリングされ、 $50\Omega$ に AC 整合されています。RF ラインの電位が 0Vdc に等しい場合は、DC 阻止コンデンサは不要です。インターフェース回路図については、図 4 を参照してください。 |

| 18                                           | RF2  | RF 投ポート 2。RF2 は 0V に DC カップリングされ、 $50\Omega$ に AC 整合されています。RF ラインの電位が 0Vdc に等しい場合は、DC 阻止コンデンサは不要です。インターフェース回路図については、図 4 を参照してください。 |

| 22                                           | RF1  | RF 投ポート 1。RF1 は 0V に DC カップリングされ、 $50\Omega$ に AC 整合されています。RF ラインの電位が 0Vdc に等しい場合は、DC 阻止コンデンサは不要です。                                |

| 24                                           | V2   | 制御入力 2。真理値表については表 6 を参照してください。インターフェース回路図については、図 5 を参照してください。                                                                      |

|                                              | EPAD | 露出パッド。露出パッドは RF/DC グラウンドに接続する必要があります。                                                                                              |

## インターフェース回路図

図 4. RFC および RF1～RF4 ピンのインターフェースの回路図

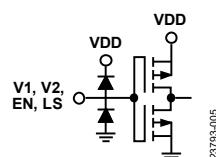

図 5. V1、V2、EN、LS ピンのインターフェース回路図

## 代表的な性能特性

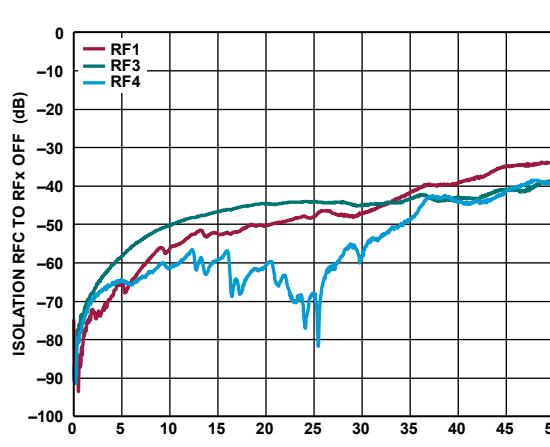

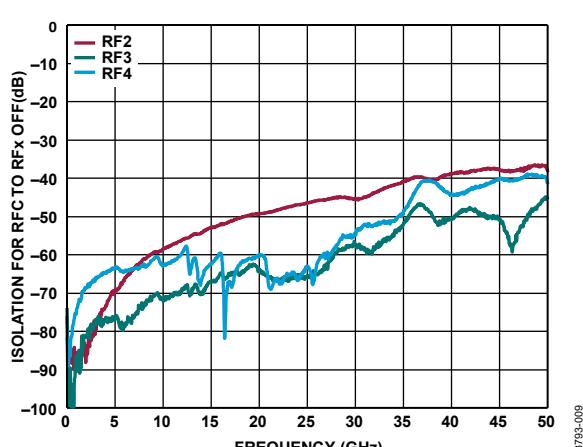

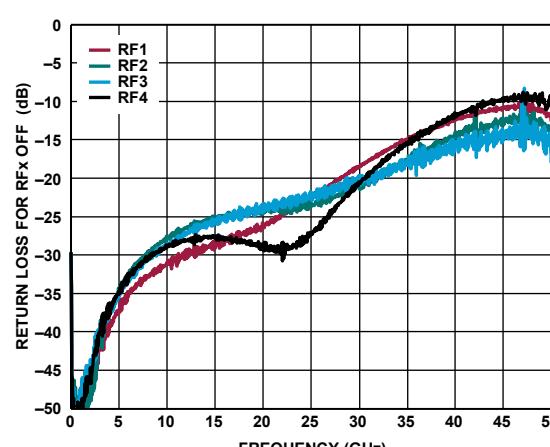

### 挿入損失、リターン損失、アイソレーション

特に指定のない限り、 $50\Omega$  システムに対し、 $V_{DD} = 3.3V$ 、 $V_{SS} = -3.3V$ 、 $V_{CTL} = 0V$  または  $3.3V$ 、 $T_{CASE} = 25^{\circ}\text{C}$ 。評価用ボード上で測定。

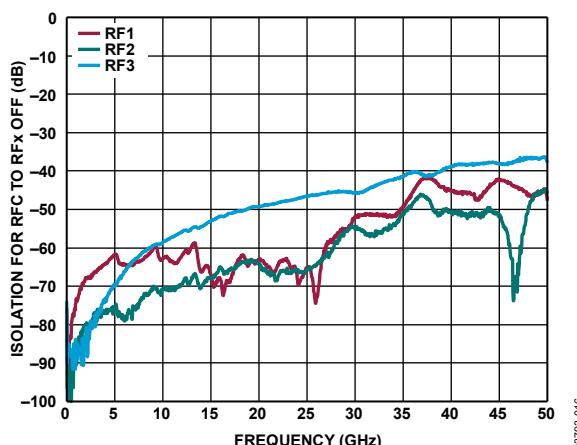

図 12. RFC と RF<sub>x</sub> オフとのアイソレーションの周波数特性、

RFC から RF3 へのパスがオン

図 15. RFC と RF<sub>x</sub> オフとのアイソレーションの周波数特性、

RFC から RF4 へのパスがオン

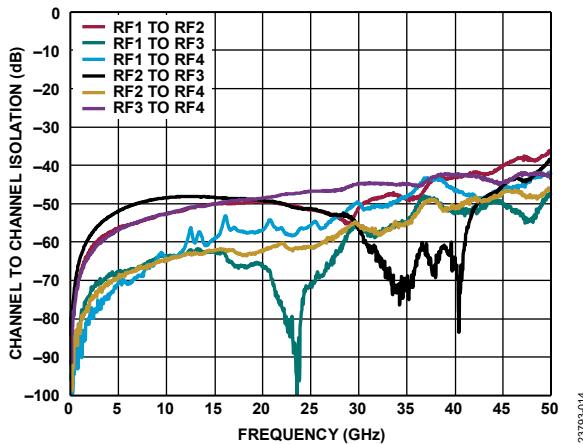

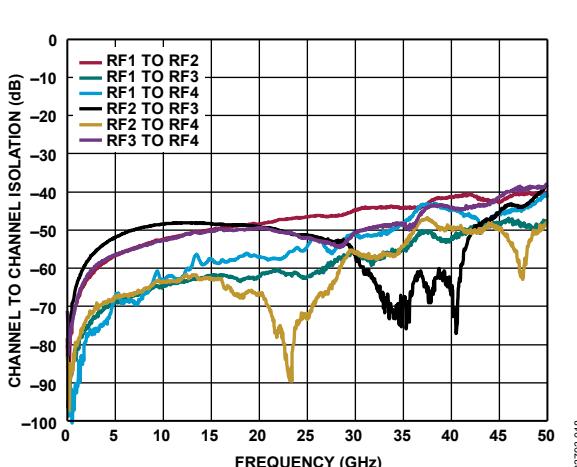

図 13. チャンネル間のアイソレーションの周波数特性、

RFC から RF1 へのパスがオン

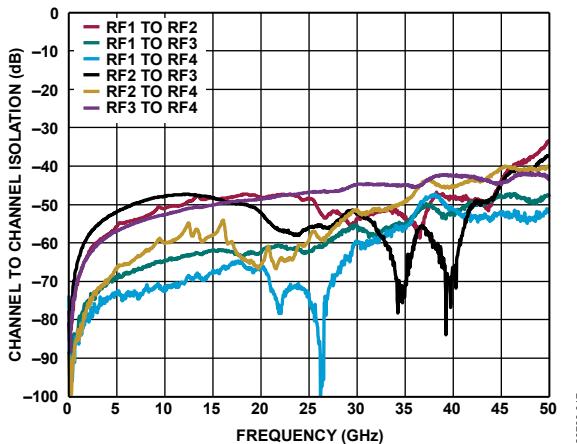

図 16. チャンネル間のアイソレーションの周波数特性、

RFC から RF2 へのパスがオン

図 14. チャンネル間のアイソレーションの周波数特性、

RFC から RF3 へのパスがオン

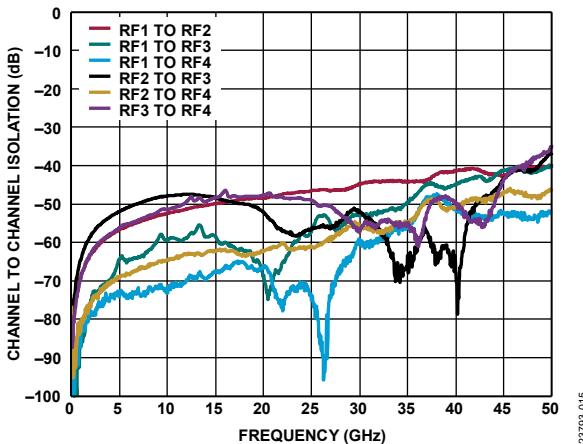

図 17. チャンネル間のアイソレーションの周波数特性、

RFC から RF4 へのパスがオン

## 入力電力圧縮と3次インターセプト

特に指定のない限り、 $50\Omega$ システムに対し、 $V_{DD} = 3.3V$ 、 $V_{SS} = -3.3V$ 、 $V_{CTL} = 0V$  または  $3.3V$ 、 $T_{CASE} = 25^{\circ}C$ 。評価用ボード上で測定。

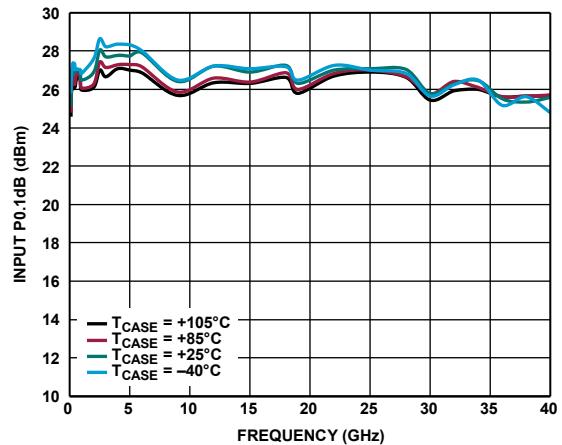

図 18. 様々な温度での入力 P0.1dB の周波数特性

23793-019

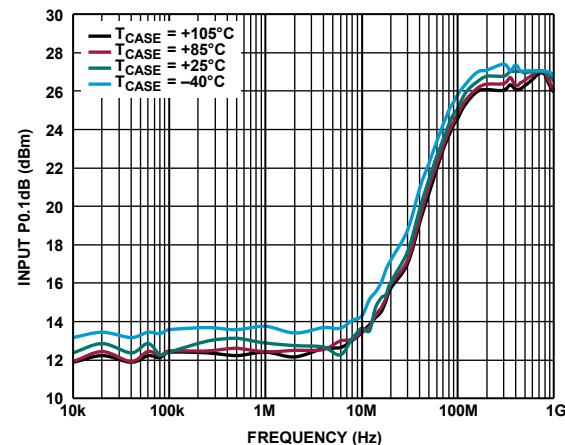

図 20. 様々な温度での入力 P0.1dB の周波数特性

(低周波数の詳細)

23793-021

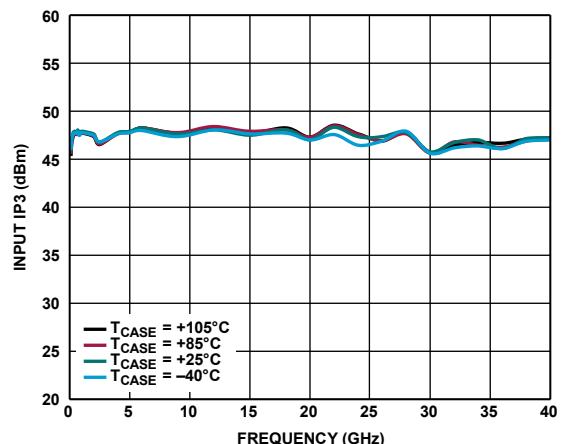

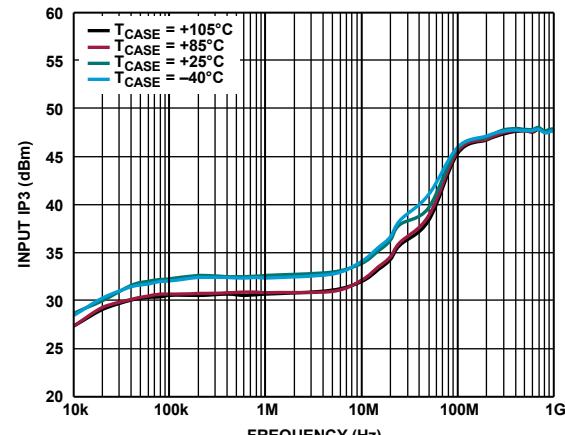

図 19. 様々な温度での入力 IP3 の周波数特性

23793-020

図 21. 様々な温度での入力 IP3 の周波数特性 (低周波数の詳細)

23793-022

## 動作原理

ADRF5042 は、VDD ピンに供給する正電源電圧と、VSS ピンに供給する負電源電圧を必要とします。RF カップリングを最小限に抑えるために、電源ラインにはバイパス・コンデンサを推奨します。

すべての RF ポート (RFC, RF1~RF4) は 0V に DC カップリングしており、RF ラインの電位が 0V に等しい場合、RF ポートでの DC 阻止は不要です。RF ポートは内部で  $50\Omega$  に整合しています。そのため、外付けのマッチング回路は不要です。

ADRF5042 にはロジック機能を内部で実行するためのドライバが内蔵されているため、CMOS/LVTTL 互換の制御インターフェースを簡素化できるメリットがあります。このドライバは、RFx パスの状態を制御する 4 つのデジタル制御入力ピン (EN、LS、V1、V2) を備えています (表 6 参照)。

ロジック・セレクト入力 (LS) を使用すると、制御入力ロジック・シーケンスを定義して RF パスの選択ができます。V1 ピンおよび V2 ピンに加えられたロジック・レベルに応じて、どの RFx ポートが挿入損失状態になり、その他の 3 本のパスがアイソレーション状態になるかが決まります。

EN ピンがロジック・ハイの場合、LS、V1、V2 のロジック状態に関係なく、4 本の RFx パスすべてがアイソレーション状態になります。RFx ポートは、内蔵の  $50\Omega$  抵抗で終端されており、RFC は反射性になります。

挿入損失パスは、選択した RF 投ポートと RF 共通ポートの間で RF 信号を導通します。スイッチの設計は、均等な電力処理機能を備えた双方向なものとなっています。RF 入力信号は RFC ポートに印加することも、RF 投ポートに印加することもできます。アイソレーション・パスは、挿入損失パスと内蔵  $50\Omega$  抵抗に終端されている未選択の RF 投ポートとの間では、高損失となります。

理想的なパワーアップ・シーケンスは以下のとおりです。

1. GND を接地します。

2. VDD と VSS に電源を入れます。ランプ上昇する間に VDD で電流トランジエントが発生しないように、VDD の電源投入後に VSS を電源投入してください。

3. デジタル制御入力 (EN、LS、V1、V2) に制御電圧を印加します。VDD への電源投入の前にデジタル制御入力に制御電圧を印加すると、意図せぬ順方向バイアスの原因となり、内蔵 ESD 保護構造に損傷を与えるおそれがあります。そのような場合は、 $1k\Omega$  の抵抗を直列に接続して、制御ピンに流入する電流を制限してください。VDD への電源投入後、制御ピンを有効なロジック状態に駆動できない（すなわち、コントローラ出力が高インピーダンス状態になっている）場合は、プルアップ抵抗またはプルダウン抵抗を使用することを推奨します。

4. RF 入力信号を印加します。

理想的なパワーダウン・シーケンスはこの電源投入シーケンスの逆順序です。

表 6. 制御電圧の真理値表

| Digital Control Inputs |             |             |             | RFx Paths           |                     |                     |                     |

|------------------------|-------------|-------------|-------------|---------------------|---------------------|---------------------|---------------------|

| EN                     | LS          | V1          | V2          | RFC to RF1          | RFC to RF2          | RFC to RF3          | RFC to RF4          |

| Low                    | Low         | Low         | Low         | Insertion loss (on) | Isolation (off)     | Isolation (off)     | Isolation (off)     |

| Low                    | Low         | High        | Low         | Isolation (off)     | Insertion loss (on) | Isolation (off)     | Isolation (off)     |

| Low                    | Low         | Low         | High        | Isolation (off)     | Isolation (off)     | Insertion loss (on) | Isolation (off)     |

| Low                    | Low         | High        | High        | Isolation (off)     | Isolation (off)     | Isolation (off)     | Insertion loss (on) |

| Low                    | High        | Low         | Low         | Isolation (off)     | Isolation (off)     | Isolation (off)     | Insertion loss (on) |

| Low                    | High        | High        | Low         | Isolation (off)     | Isolation (off)     | Isolation (off)     | Isolation (off)     |

| Low                    | High        | Low         | High        | Isolation (off)     | Insertion loss (on) | Isolation (off)     | Isolation (off)     |

| Low                    | High        | High        | High        | Insertion loss (on) | Isolation (off)     | Isolation (off)     | Isolation (off)     |

| High                   | Low or high | Low or high | Low or high | Isolation (off)     | Isolation (off)     | Isolation (off)     | Isolation (off)     |

## アプリケーション情報

### 評価用ボード

このデータシートに示すすべての測定値は、ADRF5042-EVALZ 評価用ボードで測定しています。ADRF5042-EVALZ 評価用ボードの簡略化したアプリケーション回路を図 24 に示します。評価用ボードの使用に関する詳細については、ADRF5042-EVALZ ユーザ・ガイドを参照してください。

ADRF5042-EVALZ ボードの設計は、レイアウトに関する推奨事項の役割を果たします。ADRF5042-EVALZ 評価用ボードのガーバー・ファイルは、[www.analog.com/jp/EVAL-ADRF5042](http://www.analog.com/jp/EVAL-ADRF5042) で入手できます。

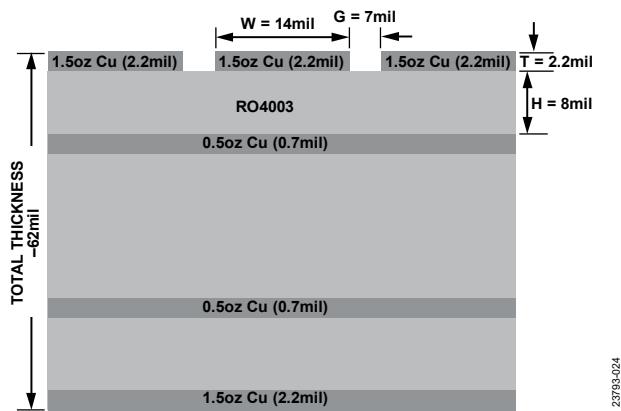

ADRF5042-EVALZ は、4 層の評価用ボードです。外側の銅 (Cu) 層は、内部の 0.5oz (0.7mil) とは異なり 1.5oz (2.2mil) の厚さにメッキされ、誘電体材料で分離されています。評価用ボードの層構成の断面図を図 22 に示します。

図 22. 評価用ボード・スタッカップ（断面図）

すべての RF パターンが上面の銅層に配線されています。一方、内部の層と底面の層はグランド・プレーンで、RF 伝送ラインに安定したグラウンドを提供します。上部の誘電体材料は 8mil の Rogers RO4003 で、最適な高周波性能を実現します。中間部および下部の誘電体材料によって、機械的な強度がもたらされます。ボード全体の厚さが 62 mil であるので、2.4mm の RF ランチャをボード端に接続できます。

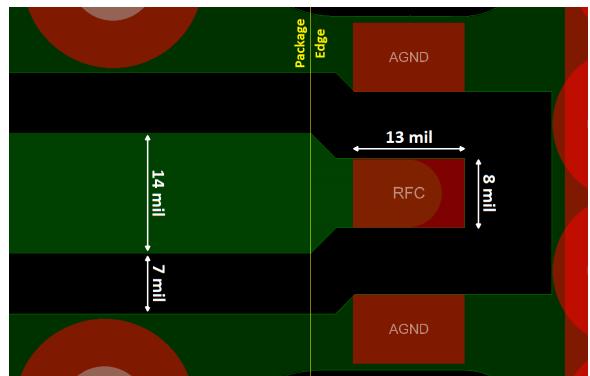

RF 伝送ラインはコプレーナ導波路 (CPWG) モデルを使用して設計されており、パターン幅を 14 mil、グラウンド・クリアランスを 7 mil とし、特性インピーダンスが  $50\Omega$  になるようにしています。図 23 に示すように、この RF 伝送ラインは、RFC または RFx ピンに向けてテーパー形状となっています。RF グラウンドディングと熱グラウンドディングを最適化するため、伝送ラインの周囲とパッケージの露出パッド下には、可能な限り多くのメッキ・スルー・ビアが配置されています。

図 23. RF 伝送ライン

23733-025

図 24. アプリケーション回路

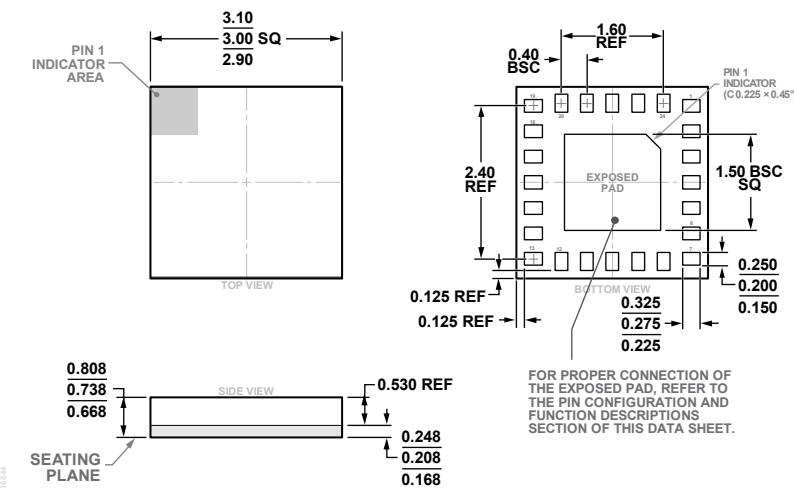

## 外形寸法

図 25.24 端子ランド・グリッド・アレイ [LGA]

3mm × 3mm ボディ、0.738 mm パッケージ高

(CC-24-12)

寸法 : mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description               | Package Option | Marking Code |

|--------------------|-------------------|-----------------------------------|----------------|--------------|

| ADRF5042BCCZN      | -40°C to +105°C   | 24-Terminal Land Grid Array [LGA] | CC-24-12       | 042          |

| ADRF5042BCCZN-R7   | -40°C to +105°C   | 24-Terminal Land Grid Array [LGA] | CC-24-12       | 042          |

| ADRF5042-EVALZ     |                   | Evaluation Board                  |                |              |

<sup>1</sup> Z = RoHS 準拠製品