**ADPL63164**

#### 概要

ADPL63164 低消費電力マイクロプロセッサ ( $\mu$ P) 監視回路は、1.575V~5V のシングル/デュアル・システム電源電圧をモニタでき、また、リセット機能とウォッチドッグ機能が最大限に調整可能です。 $V_{cc}$ 電源電圧または RESET IN がリセット閾値を下回るか、手動リセットがローに引き下げられると、デバイスはリセット信号をアサートします。 $V_{cc}$ と RESET IN がリセット関値を上回った後、リセット・タイムアウト時間が経過するまでリセット出力はアサート状態を維持します。このリセット機能は、電源のトランジェントに対する耐性を備えています。

ADPL63164 は、 $1.575V\sim5V$  の範囲を約 100mV 刻みでメーカー 調整した精度 $\pm2\%$ のリセット閾値電圧や、外部抵抗を使用して 調整可能なリセット閾値電圧を備えています。

リセット/ウォッチドッグ遅延は外部キャパシタで調整可能です。ADPL63164 には、ウォッチドッグ・タイムアウト期間を128 倍に延長するウォッチドッグ選択入力が備わっています。

ADPL63164 は、オープン・ドレインのアクティブローRESET出力で使用できます。ADPL63164 は、8 ピン SOT23 パッケージを採用しており、 $-40^{\circ}$ C~ $+125^{\circ}$ C の温度範囲で完全に仕様規定されています。

#### アプリケーション

- 医療機器

- オートモーティブ

- インテリジェント計測器

- ポータブル機器

- バッテリ駆動コンピュータ/コントローラ

- 組み込みコントローラ

- 重要なマイクロプロセッサのモニタリング

- セット・トップ・ボックス

- コンピュータ

#### 特長と利点

- 設定可変のリセットおよびウォッチドッグ・オプションにより、 幅広いアプリケーションが可能

- 1.575V~5V の範囲を約 100mV 刻みで工場設定された リセット閾値オプション

- ・ 調整可能なリセット閾値オプション

- シングル/デュアル電圧モニタリング

- キャパシタ調整可能なリセット・タイムアウト

- キャパシタ調整可能なウォッチドッグ・タイムアウト

- ・ オープン・ドレインRESET出力

- 4µA の電源電流がシステムの消費電力を削減

- 統合された電源保護機能が堅牢性を向上

- 電源過渡耐性

- ・ V<sub>CC</sub> ≥ 1.2V で有効なRESETを確保

- 8 ピン SOT23 パッケージで基盤スペースを節約

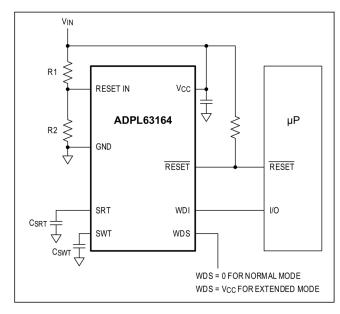

### 標準動作回路

#### 絶対最大定格

| $V_{CC}\sim$ GND0.3V $\sim$ +6.0V                                                |

|----------------------------------------------------------------------------------|

| SRT, SWT, RESET IN, WDS, WDI $\sim$ GND $-0.3$ V $\sim$ V <sub>CC</sub> $+0.3$ V |

| RESET (オープン・ドレイン) ~GND0.3V~+6.0V                                                 |

| 入力電流(全てのピン)±20mA                                                                 |

| 出力電流(RESET)±20mA                                                                 |

| 連続消費電力 (T <sub>A</sub> = +70℃) 8 | ピン SOT23 (+70℃ を超えると |

|----------------------------------|----------------------|

| 5.1mW/℃ でディレーティング)               | 408.2mW              |

| 動作温度範囲                           | 40°C∼+125°C          |

| 保管温度範囲                           | 65°C~+150°C          |

| ジャンクション温度                        | +150°C               |

| リード温度(ハンダ付け処理、1                  | 10s)+300°C           |

| ハンダ付け処理温度(リフロー)                  | )+260°C              |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する 規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### パッケージ情報

| Package Code                                           | K8+5, K8+5A    |  |

|--------------------------------------------------------|----------------|--|

| Outline Number                                         | <u>21-0078</u> |  |

| Land Pattern Number                                    | <u>90-0176</u> |  |

| Thermal Resistance, Single-Layer Board                 |                |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | N/A            |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 800            |  |

| Thermal Resistance, Four-Layer Board                   |                |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 196            |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 70             |  |

最新のパッケージ外形図とランド・パターン(フットプリント)に関しては、https://www.analog.com/jp/design-center/packaging-quality-symbols-footprints/package-index.html で確認してください。パッケージ・コードの「+」、「#」、「-」は RoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、https://www.analog.com/jp/technical-articles/thermal-characterization-of-ic-packages.html を参照してください。

### 電気的特性

(特に指定のない限り、V<sub>CC</sub> = +1.7V~+5.5V、T<sub>A</sub> = T<sub>MIN</sub>~T<sub>MAX</sub>。 代表値は V<sub>CC</sub> = +5V、T<sub>A</sub> = +25℃ での値) (Note 1)

| PARAMETER                                                        | SYMBOL                | CONDITIONS                                                                          | MIN                      | TYP   | MAX                      | UNITS |

|------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------|--------------------------|-------|--------------------------|-------|

| Supply Voltage Reset output is guaranteed to be in a known state |                       | 1.2                                                                                 |                          | 5.5   | V                        |       |

| Cappi, remage                                                    | 33                    | T <sub>A</sub> = -40°C to 125°C                                                     | 1.7                      |       | 5.5                      |       |

|                                                                  |                       | V <sub>CC</sub> <= 5.5V                                                             |                          | 7     | 15                       |       |

| Supply Current                                                   | Icc                   | V <sub>CC</sub> <= 3.3V                                                             |                          | 4.5   | 10                       | μA    |

|                                                                  |                       | V <sub>CC</sub> <= 2.0V                                                             |                          | 4     | 9                        |       |

| V <sub>CC</sub> Reset Threshold                                  | V <sub>TH</sub>       | See <u>Table 1</u> $T_A = -40$ °C to $+125$ °C                                      | V <sub>TH</sub> - 2.5%   |       | V <sub>TH</sub> + 2.5%   | V     |

| Hysteresis                                                       | $V_{HYST}$            |                                                                                     |                          | 8.0   |                          | %     |

| V <sub>CC</sub> to RESET Delay                                   |                       | $V_{CC}$ falling from $V_{TH}$ + 100mV to $V_{TH}$ - 100mV at 1mV/ $\mu$ s          |                          | 20    |                          | μs    |

| Deast Timesut Deried                                             | too                   | C <sub>SRT</sub> = 1500pF                                                           | 5.692                    | 7.59  | 9.487                    |       |

| Reset Timeout Period                                             | t <sub>RP</sub>       | C <sub>SRT</sub> = 100pF                                                            |                          | 0.506 |                          | ms    |

| SRT Ramp Current                                                 | I <sub>RAMP</sub>     | $V_{SRT} = 0$ to 1.23V; $V_{CC} = 1.6$ V to 5V                                      | 180                      | 250   | 320                      | nA    |

| SRT Ramp Threshold                                               | $V_{RAMP}$            | V <sub>CC</sub> = 1.6V to 5V (V <sub>RAMP</sub> rising)                             | 1.17                     | 1.235 | 1.3                      | V     |

| Normal Watchdog                                                  | turn                  | C <sub>SWT</sub> = 1500pF                                                           | 5.692                    | 7.59  | 9.487                    |       |

| Timeout Period                                                   | $t_{WD}$              | C <sub>SWT</sub> = 100pF                                                            |                          | 0.506 |                          | ms    |

| Extended Watchdog Timeout Period                                 |                       | C <sub>SWT</sub> = 1500pF                                                           | 728.6                    | 971.5 | 1214.4                   |       |

|                                                                  |                       | C <sub>SWT</sub> = 100pF                                                            |                          | 64.77 |                          | ms    |

| SWT Ramp Current                                                 | I <sub>RAMP</sub>     | V <sub>SWT</sub> = 0 to 1.23V; V <sub>CC</sub> = 1.6V to 5V                         | 180                      | 250   | 320                      | nA    |

| SWT Ramp Threshold                                               | V <sub>RAMP</sub>     | V <sub>CC</sub> = 1.6V to 5V (VRAMP rising)                                         | 1.17                     | 1.235 | 1.3                      | V     |

| RESET Output-Voltage                                             |                       | V <sub>CC</sub> ≥ 1.0V, I <sub>SINK</sub> = 50μA                                    |                          |       | 0.3                      |       |

| Low                                                              | $V_{OL}$              | V <sub>CC</sub> ≥ 2.7V, I <sub>SINK</sub> = 1.2mA                                   |                          |       | 0.3                      | V     |

| (Asserted)                                                       |                       | V <sub>CC</sub> ≥ 4.5V, I <sub>SINK</sub> = 3.2mA                                   |                          |       | 0.4                      |       |

| RESET Output Leakage<br>Current                                  | I <sub>LKG</sub>      | V <sub>CC</sub> > V <sub>TH</sub> , reset not asserted<br>V <sub>RESET</sub> = 5.5V |                          |       | 1.5                      | μΑ    |

| DIGITAL INPUTS (WDI, V                                           | VDS)                  |                                                                                     |                          |       |                          |       |

|                                                                  | V <sub>IL</sub>       | V <sub>CC</sub> ≥ 4.0V                                                              |                          |       | 0.8                      |       |

|                                                                  | V <sub>IH</sub>       | V <sub>CC</sub> ≥ 4.0V                                                              | 2.4                      |       |                          |       |

| Input Logic Levels                                               | V <sub>IL</sub>       | V <sub>CC</sub> < 4.0V                                                              |                          |       | 0.2 x<br>V <sub>CC</sub> | V     |

|                                                                  | $V_{IH}$              |                                                                                     | 0.8 x<br>V <sub>CC</sub> |       |                          |       |

| WDI Minimum Pulse<br>Width                                       |                       |                                                                                     | 300                      |       |                          | ns    |

| RESET IN                                                         |                       | 1                                                                                   |                          |       |                          |       |

| RESET IN Threshold                                               | V <sub>RESET IN</sub> | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                      | 1.21                     | 1.235 | 1.26                     | V     |

| RESET IN Leakage<br>Current                                      | I <sub>RESET</sub> IN |                                                                                     | -55                      | ±1    | 55                       | nA    |

| RESET IN to RESET Delay                                          |                       | RESET IN falling at 1mV/µs                                                          |                          | 20    |                          | μs    |

Note 1: 製品テストは  $T_A = +25$ °C で行っています。温度範囲全体に対する制限値は設計により裏付けられています。

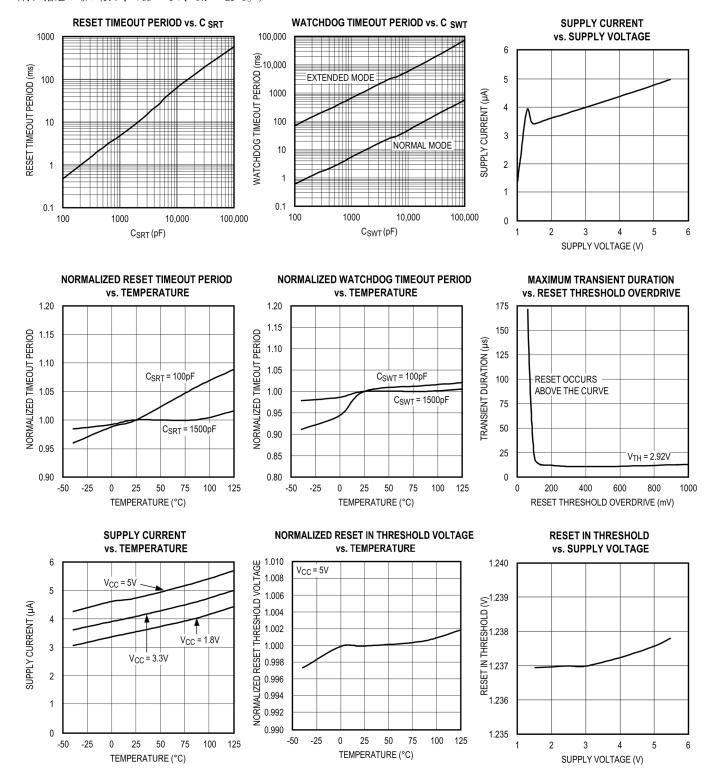

#### 標準動作特性

(特に指定のない限り、Vcc=+5V、T<sub>A</sub>=+25℃。)

(特に指定のない限り、V<sub>CC</sub>=+5V、T<sub>A</sub>=+25℃。)

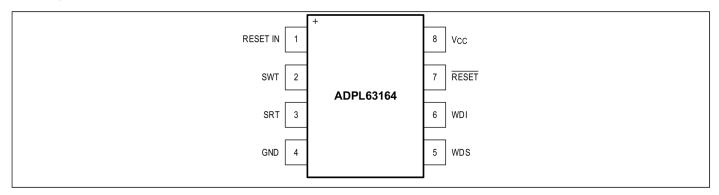

#### ピン配置

#### 端子説明

| ピン | 名称              | 説明                                                                                                                                                                                                                                                                        |

|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | RESET IN        | リセット入力。調整可能なリセット・コンパレータへの高インピーダンス入力です。外部モニタされる電圧の閾値を<br>設定するには、外部抵抗分圧器の中点に RESET IN を接続します。                                                                                                                                                                               |

| 2  | SWT             | ウォッチドッグ・タイムアウト入力。基本ウォッチドッグ・タイムアウト期間の長さ(tWD)を設定するには、<br>SWT とグラウンドの間にキャパシタを接続します。この期間の長さは tWD = 4.94 × 106 × CSWT(tWD の単位は<br>秒、CSWT の単位はファラッド)の式に従って定まります。基本ウォッチドッグ・タイムアウト期間は WDS 入力を<br>用いて延長できます。SWT をグラウンドに接続するとウォッチドッグ・タイマ機能は無効化されます。                                 |

| 3  | SRT             | リセット・タイムアウト入力。リセット・タイムアウト期間の長さを選択するには、SRT とグラウンドの間にキャパシタを接続します。この期間の長さは次式で定まります: $tRP = 4.94 \times 106 \times CSRT$ ( $tRP$ の単位は秒、CSRT の単位はファラッド)。                                                                                                                       |

| 4  | GND             | グラウンド。                                                                                                                                                                                                                                                                    |

| 5  | WDS             | ウォッチドッグ選択入力。WDS はウォッチドッグ・モードを選択します。通常モードとウォッチドッグ・タイムアウト期間の長さを選択するには、WDS をグラウンドに接続します。WDS を Vcc に接続すると延長モードが選択され、基本タイムアウト期間の長さの 128 倍に延長されます。WDS の状態が変化するとウォッチドッグ・タイマはクリアされます。                                                                                             |

| 6  | WDI             | ウォッチドッグ入力。選択したウォッチドッグ・タイムアウト期間内にWDIに立下がり遷移を発生させる必要があります。さもないとリセット・パルスが発生します。WDIに遷移が発生した場合はウォッチドッグ・タイマがクリアされます。あるいはRESETがアサートされた場合は常にクリアされます。SWTをグラウンドに接続するとウォッチドッグ・タイマ機能は無効化されます。WDIをフローティング状態のままにすることはできません。ウォッチドッグ機能を使用しないときに正しい動作を確保するには、WDIとグラウンドの間に100kの抵抗を接続します。    |

| 7  | RESET           | オープン・ドレインのリセット出力。 $V_{CC}$ または RESET IN が選択したリセット閾値電圧(それぞれ、 $V_{TH}$ または $V_{RESETIN}$ )未満に低下した場合は常に、 $\overline{RESET}$ がアサートされます。 $\overline{RESET}$ は、全てのリセット条件がデアサートされた後、リセット・タイムアウト期間の間ローを維持し、その後ハイに移行します。ウォッチドッグ・フォルトが発生すると必ず、ウォッチドッグ・タイマはリセット・パルス( $tRP$ )をトリガします。 |

| 8  | V <sub>CC</sub> | 電源電圧。 $V_{CC}$ は電源入力および、固定閾値 $V_{CC}$ モニタ用の入力です。                                                                                                                                                                                                                          |

#### 詳細

ADPL63164は、 $V_{CC}$ 電源電圧またはRESET INがそのリセット閾値未満に低下した場合、常にリセット信号をアサートします。このリセット出力は、 $V_{CC}$  または RESET IN がそれぞれのリセット閾値を超えた後リセット・タイムアウト期間の間、アサートされたままになります。ウォッチドッグ・フォルトが発生すると必ず、ウォッチドッグ・タイマはリセット・パルスをトリガします。

リセット/ウォッチドッグ遅延は外部キャパシタで調整可能です。ADPL63164には、ウォッチドッグ・タイムアウト期間を 128 倍に延長するウォッチドッグ選択入力が備わっています。

#### リセット出力

リセット出力は通常、マイクロプロセッサのリセット入力に接続されます。マイクロプロセッサのリセット入力は、既知の状態でマイクロプロセッサを起動または再起動します。ADPL63164のマイクロプロセッサ監視回路は、パワーアップ時、パワーダウン時、ブラウンアウト時のコード実行エラーを防止するためのリセット・ロジックを備えています(標準動作回路を参照)。

モニタ対象電圧である RESET IN や  $V_{CC}$  がリセット閾値電圧未満に低下すると常に、RESET はハイからローに変化します。 $V_{RESET\ IN}$ や  $V_{CC}$  がそれぞれのリセット閾値電圧を超えると、RESET はリセット・タイムアウト期間の間ローを維持し、その後ハイに移行します。

RESETは、Vccが 1V より高い場合に正しいロジック状態になるよう設計されています。

#### RESET IN 閾値

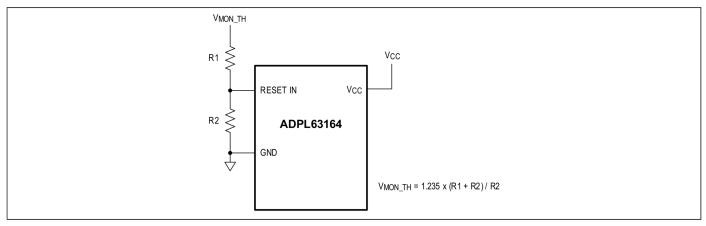

ADPL63164 は、外部抵抗分圧器で設定される調整可能なリセット閾値( $V_{RESET\,IN}$ )を用いて RESET IN の電圧をモニタします(図 1参照)。外部でモニタされる電圧( $V_{MON\,TH}$ )を計算するには、次式を用います。

$$V_{MON\ TH} = V_{RESET\ IN} \times (R1 + R2)/R2$$

図 1. モニタする閾値電圧(V<sub>MON\_TH</sub>)の計算

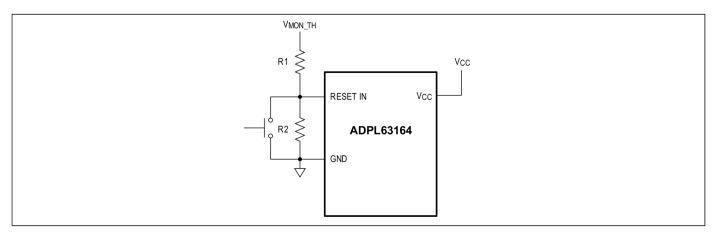

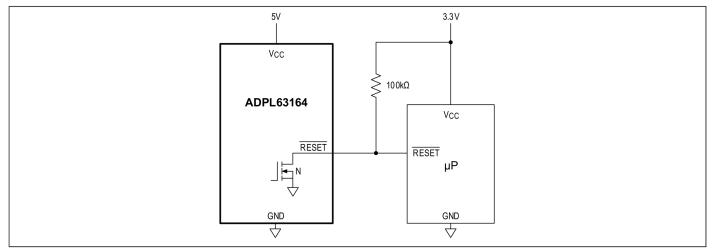

図 2. ADPL63164 への外部手動リセット機能の追加

ここで、 $V_{MON\_TH}$ は目的のリセット関値電圧、 $V_{TH}$ はリセット入力関値(1.235V)です。抵抗 R1 および R2 は非常に高抵抗にすることができ、リーク電流が少ないために消費電流を最小限に抑えられます。R2 を適当な高い値(例えば  $500k\Omega$ )に設定し、目的のリセット関値電圧に基づいて R1 を計算するには次式を用います。

$$R1 = R2 \times \left(\frac{V_{MON\_TH}}{V_{RESETIN}} - 1\right)(\Omega)$$

#### デュアル電圧モニタリング

ADPL63164 は、メーカー調整済みの閾値電圧と調整可能なリセット閾値入力の両方を備えているため、 $V_{CC}$ および  $V_{MON\_TH}$  の 2 つの電圧のモニタリングが可能です(図 1 参照)。 RESETは、いずれかの電圧がその閾値電圧未満に低下した場合にアサートされます。

#### 手動リセット

ノーマリ・オープンのモーメンタリ・スイッチを R2 に並列に接続することで、手動リセット・オプションを ADPL63164 に簡単に実装できます(図 2 参照)。スイッチが閉じると RESET IN の電圧がゼロに移行し、リセットが開始されます。リセットは、RESET IN の電圧がゼロになっている間、およびスイッチが開いた後リセット・タイムアウト期間が経過する間、アサートされたままになります。

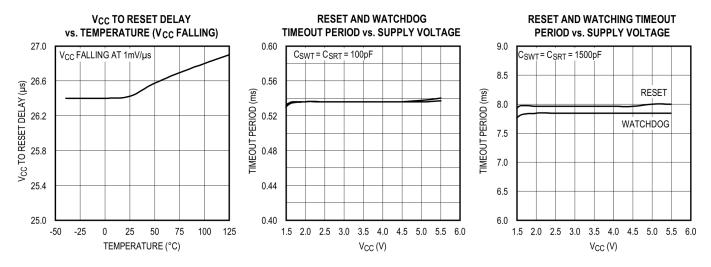

#### ウォッチドッグ・タイマ

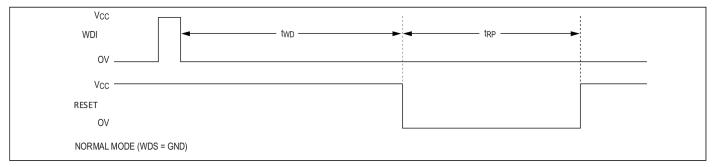

ウォッチドッグの回路は、マイクロプロセッサの動作をモニタします。マイクロプロセッサがウォッチドッグ入力(WDI)を twp (ユーザ選択)以内にトグルしない場合、リセット・タイムアウト期間の間、RESETがアサートされます。内部ウォッチドッグ・タイマはRESETをアサートするイベントによりクリアされます。つまり、WDIの立下がり遷移(300nsの短パルスを検出可能)またはWDSの遷移によりクリアされます。リセットがアサートされている間、ウォッチドッグ・タイマはクリアされたままになり、リセットが解除されると直ちにタイマはカウントを開始します。

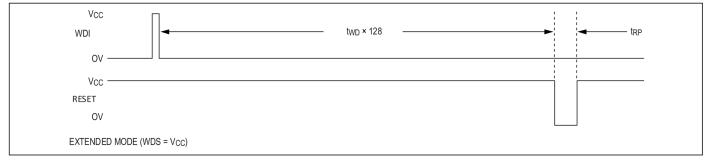

ADPL63164 は、通常モードと延長モードの 2 つのウォッチドッグ動作が可能です。通常モード(図 3 参照)では、ウォッチドッグ・タイムアウト期間は、SWT とグラウンドの間に接続されたキャパシタの値で決まります。延長モード(図 3 参照)では、ウォッチドッグ・タイムアウト期間が 128 倍になります。例えば、延長モードの場合、 $0.1\mu F$  のキャパシタでウォッチドッグ・タイムアウト期間は 65s になります(標準動作特性のウォッチドッグ・タイムアウト期間と  $C_{SWT}$  の関係を示すグラフ(Watchdog Timeout Period vs.  $C_{SWT}$ )の延長モードを参照)。ウォッチドッグ・タイマ機能を無効化するには、SWT をグラウンドに接続します。

ウォッチドッグのタイミング図、WDS = GND

図 3. ウォッチドッグのタイミング図、WDS = Vcc

#### アプリケーション情報

#### リセット/ウォッチドッグ・タイムアウト・キャパシタの選択

様々なマイクロプロセッサ・アプリケーションに対応できるよう、リセット・タイムアウト期間は調整可能です。リセット・タイムアウト期間(t<sub>RP</sub>)を調整するには、SRT とグラウンドの間にキャパシタ(C<sub>SRT</sub>)を接続します。リセット・タイムアウト・キャパシタは次式で計算します。

$C_{SRT} = t_{RP}/(4.94 \times 10^6)$

ここで、tRPの単位は秒、CSRTの単位はファラッドです。

様々なマイクロプロセッサ・アプリケーションに対応できるよう、ウォッチドッグ・タイムアウト期間は調整可能です。この機能を用いると、ウォッチドッグ・タイムアウトをソフトウェアの実行に合わせて最適化できます。プログラマは、ウォッチドッグ・タイマを機能させる頻度を決定できます。ウォッチドッグ・タイムアウト期間(twp)を調整するには、SWT と GND の間に特定の値のキャパシタ(Cswr)を接続します。ウォッチドッグ・タイムアウト・キャパシタは次式で計算します。

$$C_{SWT} = t_{WD}/(4.94 \times 106)$$

ここで、twDの単位は秒、CswTの単位はファラッドです。

CSRTおよび CSWT は、低リーク (< 10nA) タイプのキャパシタであることが必要です。セラミック・キャパシタを推奨します。

#### 過渡耐性

パワーアップ、パワーダウン、ブラウンアウトの状態時にマイクロプロセッサにリセットを指示する他、この監視回路は、短時間の電源トランジェント (グリッチ) に対し比較的耐性があります。標準動作特性の最大トランジェント時間とリセット閾値オーバードライブの関係を示すグラフ (Maximum Transient Duration vs. Reset Threshold Overdrive) に、この関係が示されています。

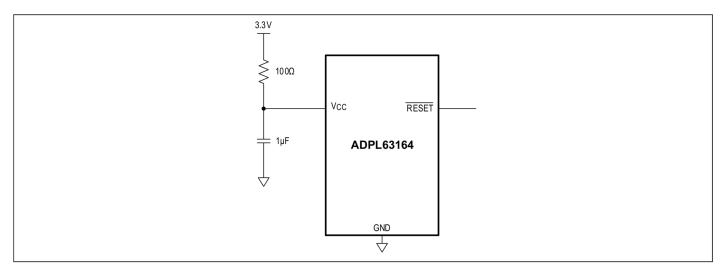

グラフの曲線より下の領域は、これらのデバイスが通常はリセット・パルスを発生しない領域です。このグラフは、実際のリセット閾値  $(V_{TH})$  を超える電圧で始まり、示された大きさ(リセット閾値オーバードライブ)だけ下回った電圧で終了する立下がりパルスを、 $V_{CC}$  に印加して生成されたものです。トランジェントの大きさが増加するにつれ(リセット閾値を下回るにつれ)、許容可能な最大パルス幅が減少します。通常、リセット閾値より 100mV 低く、持続時間が  $50\mu$ S 以下の  $V_{CC}$  トランジェントは、リセット・パルス発行の原因にはなりません。 $V_{CC}$  への電源のトランジェント・レートが高いアプリケーションの場合( $dV/dt > 5V/50\mu$ S)は、 $V_{CC}$  に RC フィルタが必要です。図 6 を参照してください。

図 4. 他の電圧レベルとのインターフェース

図 6. 高入力電圧トランジェント・アプリケーション用のアプリケーション回路

### ロジック互換性を確保するための他電圧とのインターフェース

オープン・ドレイン $\overline{\text{RESET}}$ 出力を用いることで、その他のロジック・レベルのマイクロプロセッサとインターフェースできます。 $\boxtimes$  4 に示すように、オープン・ドレイン出力は、 $OV\sim 6V$  の電圧に接続できます。

一般に、 $\overline{\text{RESET}}$ に接続されたプルアップ抵抗は、IC の  $V_{CC}$  ピンでモニタされる電源電圧に接続します。しかし、一部のシステムでは、このオープン・ドレイン出力を用いて、モニタする電源からレベルシフトし、別の電源から給電される回路をリセットできます。なお、監視回路の  $V_{CC}$  が IV に向かって減少するのに伴い、IC の $\overline{\text{RESET}}$  での電流シンク能力も同様に低下する点に注意してください。また、何らかのプルアップ抵抗を用いると、 $V_{CC}$  がゼロに向かって徐々に減少するのに伴って、 $\overline{\text{RESET}}$ はハイに引き上げられます。このようなことが生じる電圧は、プルアップ抵抗値とそれが接続されている電圧に依存します。

表 1. リセット閾値電圧のサフィックス( $T_A = -40^{\circ}$ C~ $+125^{\circ}$ C)

| SUFFIX | MIN   | TYP   | MAX   |

|--------|-------|-------|-------|

| 50     | 4.875 | 5.000 | 5.125 |

| 49     | 4.778 | 4.900 | 5.023 |

| 48     | 4.680 | 4.800 | 4.920 |

| 47     | 4.583 | 4.700 | 4.818 |

| 46     | 4.509 | 4.625 | 4.741 |

| 45     | 4.388 | 4.500 | 4.613 |

| 44     | 4.266 | 4.375 | 4.484 |

| 43     | 4.193 | 4.300 | 4.408 |

| 42     | 4.095 | 4.200 | 4.305 |

| 41     | 3.998 | 4.100 | 4.203 |

| 40     | 3.900 | 4.000 | 4.100 |

| 39     | 3.803 | 3.900 | 3.998 |

| 38     | 3.705 | 3.800 | 3.895 |

| 37     | 3.608 | 3.700 | 3.793 |

| 36     | 3.510 | 3.600 | 3.690 |

| 35     | 3.413 | 3.500 | 3.588 |

| 34     | 3.315 | 3.400 | 3.485 |

| 33     | 3.218 | 3.300 | 3.383 |

| 32     | 3.120 | 3.200 | 3.280 |

| 31     | 2.998 | 3.075 | 3.152 |

| 30     | 2.925 | 3.000 | 3.075 |

| 29     | 2.852 | 2.925 | 2.998 |

| 28     | 2.730 | 2.800 | 2.870 |

| 27     | 2.633 | 2.700 | 2.768 |

| 26     | 2.559 | 2.625 | 2.691 |

| 25     | 2.438 | 2.500 | 2.563 |

| 24     | 2.340 | 2.400 | 2.460 |

| 23     | 2.255 | 2.313 | 2.371 |

| 22     | 2.133 | 2.188 | 2.243 |

| 21     | 2.048 | 2.100 | 2.153 |

| 20     | 1.950 | 2.000 | 2.050 |

| 19     | 1.853 | 1.900 | 1.948 |

| 18     | 1.755 | 1.800 | 1.845 |

| 17     | 1.623 | 1.665 | 1.707 |

| 16     | 1.536 | 1.575 | 1.614 |

#### 型番

| PART NUMBER      | TEMP RANGE      | PIN-PACKAGE |

|------------------|-----------------|-------------|

| ADPL63164AKA+    | -40°C to +125°C | 8 SOT23     |

| ADPL63164AKA+T   | -40°C to +125°C | 8 SOT23     |

| ADPL63164AKA31+  | -40°C to +125°C | 8 SOT23     |

| ADPL63164AKA31+T | -40°C to +125°C | 8 SOT23     |

Note: 「\_\_」は、リセット関値電圧値を発注する際に必要な 2 桁のサフィックスです。リセット関値電圧は、約 100mV のインクリメントで指定できます。表 1 には、サフィックスとメーカー調整リセット電圧が示されています。全てのデバイスはテープのリール巻きでのみ供給されます。標準パージョン(型番を参照)の場合、最小 2500 個単位の発注条件があります。サンプル在庫は通常、標準パージョンでのみ確保されています。標準以外のバージョンでは最小 10,000 個単位の発注が必要です。在庫については弊社にお問い合わせください。

+は鉛 (Pb) フリー/RoHS 準拠のパッケージであることを示します。T =テープ&リール。

#### チップ情報

プロセス:BiCMOS

### ADPL63164

# リセット/ウォッチドッグのタイムアウト遅延を キャパシタで調整可能なマイクロプロセッサ・ リセット回路

#### 改訂履歴

| 版数 | 改訂日  | 説明   | 改訂ページ |

|----|------|------|-------|

| 0  | 1/24 | 初版発行 | -     |

# 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、2024 年 9 月 30 日現在、アナログ・デバイセズ株式会社で確認した誤りを 記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日: 2024年9月30日

製品名:ADPL63164

対象となるデータシートのリビジョン(Rev): Rev.0

訂正箇所:9頁、過渡特性の項、最初の文

#### 【誤】

「・・この監視回路は、短時間の電源トランジェント(グリッチ)に対し**比較的耐性があ**ります。」

#### 【正】

「・・この監視回路は、短時間の電源トランジェント (グリッチ) に対し**比較的耐性があります。 (図 6 参照)**」