ADPL62933

## 手動リセット機能とウォッチドッグ・タイマを備えた ナノパワーμP 監視回路

### 概要

ADPL62933 は、電圧モニタリング、ウォッチドッグ・タイマ、手動リセット入力機能を 5 ピン SOT23 パッケージ内で組み合わせた、超低消費電流（代表値 200nA）のマイクロプロセッサ（μP）監視回路です。このデバイスは、モニタ対象の電圧が工場調整済みのリセット閾値電圧未満に低下した場合、手動リセットがアサートされた場合、あるいはウォッチドッグ・タイマの時間が経過した場合に、必ずリセット信号をアサートします。V<sub>CC</sub> がリセット閾値以上に増加し手動リセットのアサートが解除された後も、最小タイムアウト時間の間は、リセット出力がアサートされたままになります。工場調整済みのリセット閾値電圧は、+1.575V～+4.625V の範囲を約 100mV 刻みで提供されます（表 1 を参照）。各デバイスには、10ms～1200ms の範囲の 6 通りの最小リセット・タイムアウト・オプションがあります。

ADPL62933 は、WDI 入力で動作をモニタするウォッチドッグ・タイマを備えており、コード実行エラーを防止しています。これにも、3.3 秒または 209 秒（いずれも代表値）のウォッチドッグ・タイマアウト・オプションがあります。オープン・ドレイン、アクティブ・ローのリセット出力が使用できます。

### アプリケーション

- ポータブル／バッテリ駆動機器

- PDA／携帯電話

- MP3 プレーヤ／ポケベル

- 血糖値モニタ／患者モニタ

### 特長

- 超低供給電流 : 170nA (代表値)

- リセット閾値 : +1.575V～+4.625V、約 100mV 刻み

- 10ms～1200ms の範囲で 6 通りの最小リセット・タイムアウト時間のオプション

- 手動リセット・オプション

- ウォッチドッグ・タイマ・オプション

- V<sub>CC</sub> の短いトランジメントに対する耐性

- 有効なリセットを+1.1V の V<sub>CC</sub> に対し確保

- オープン・ドレイン RESET 出力

- 外付け部品不要

- 小型 5 ピン SOT23 パッケージ

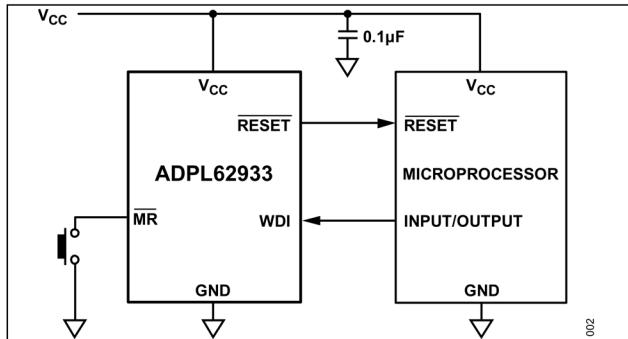

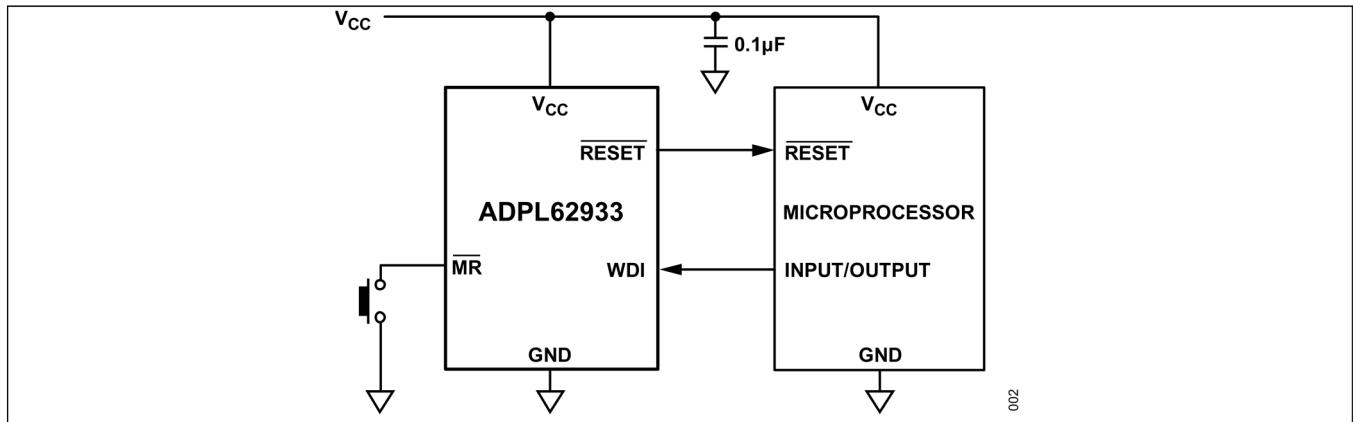

### 標準動作回路

型番は、データシートの末尾に記載しています。

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

©2024 Analog Devices, Inc. All rights reserved. 商標および登録商標は各社の所有に属します。

本 社／〒105-7323 東京都港区東新橋 1-9-1 東京汐留ビルディング 23F

大 阪営業所／〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F

19-101821; Rev 1; 01/24

目次

|                                    |    |

|------------------------------------|----|

| 概要 .....                           | 1  |

| アプリケーション .....                     | 1  |

| 特長 .....                           | 1  |

| 標準動作回路 .....                       | 1  |

| 絶対最大定格 .....                       | 3  |

| パッケージ情報 .....                      | 4  |

| 電気的特性 .....                        | 5  |

| 標準動作特性 .....                       | 7  |

| ピン配置 .....                         | 9  |

| 端子説明 .....                         | 9  |

| 機能図 .....                          | 10 |

| 詳細説明 .....                         | 12 |

| RESET出力 .....                      | 12 |

| 手動リセット入力 .....                     | 12 |

| ウォッチドッグ入力 .....                    | 12 |

| アプリケーション情報 .....                   | 13 |

| 過渡耐性 .....                         | 13 |

| ロジック互換性を確保するための他電圧とのインターフェース ..... | 13 |

| ウォッチドッグのソフトウェアに関する考慮事項 .....       | 13 |

| 標準アプリケーション回路 .....                 | 16 |

| 型番 .....                           | 17 |

### 絶対最大定格

|                                                                                      |                                |

|--------------------------------------------------------------------------------------|--------------------------------|

| V <sub>CC</sub> 、オープン・ドレインRESET～GND.....                                             | -0.3V～+6.0                     |

| MR、WDI.....                                                                          | -0.3V～(V <sub>CC</sub> + 0.3V) |

| 入力電流、出力電流（すべてのピン）.....                                                               | ±20mA                          |

| 連続消費電力 (T <sub>A</sub> = +70°C) 5 ピン SOT23 (+70°C を超えると<br>7.1mW/°C でディレーティング) ..... | 571mW                          |

|                         |              |

|-------------------------|--------------|

| 動作温度範囲.....             | -40°C～+85°C  |

| ジャンクション温度.....          | +150°C       |

| 保管温度範囲.....             | -65°C～+150°C |

| リード温度（ハンダ付け処理、10秒）..... | +300°C       |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作のセクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

パッケージ情報

|                     |                         |

|---------------------|-------------------------|

| Package Code        | U5+2                    |

| Outline Number      | <a href="#">21-0057</a> |

| Land Pattern Number | <a href="#">90-0174</a> |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、<http://www.analog.com/packages> で確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面はRoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、<http://www.analog.com/thermal-tutorial> を参照してください。

## 電気的特性

(特に指定のない限り、 $V_{CC} = 1.7V \sim 5.5V$ 、 $T_A = -40^{\circ}C \sim +85^{\circ}C$ 。代表値は  $V_{CC} = 2.5V$ 、 $T_A = +25^{\circ}C$  での値です。 (Note 1) )

| PARAMETER                        | SYMBOL     | CONDITIONS                                                                         | MIN             | TYP      | MAX            | UNITS      |

|----------------------------------|------------|------------------------------------------------------------------------------------|-----------------|----------|----------------|------------|

| Supply Voltage                   | $V_{CC}$   | Reset output is guaranteed to be in a known state                                  | 1.1             | 5.5      |                | V          |

|                                  |            | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                      | 1.7             | 5.5      |                |            |

| Supply Current                   | $I_{CC}$   | $V_{CC} > V_{TH}$ , no load, reset output deasserted (Note 2)                      | $V_{CC} = 5.0V$ | 220      | 410            | nA         |

|                                  |            |                                                                                    | $V_{CC} = 3V$   | 200      | 390            |            |

|                                  |            | $V_{CC} < V_{TH}$ , no load, reset output asserted                                 |                 | 7        | 15             | μA         |

| $V_{CC}$ Reset Threshold         | $V_{TH}$   | $V_{CC}$ falling (see Table 1)                                                     | $V_{TH} - 3\%$  | $V_{TH}$ | $V_{TH} + 3\%$ | V          |

| Reset Threshold Hysteresis       | $V_{HYST}$ | Reset asserted to reset deasserted                                                 |                 | 0.5      |                | % $V_{TH}$ |

| Reset Timeout Period             | $t_{RP}$   | $V_{CC} = V_{TH} + 150mV$ (Figure 13 and Figure 14)                                | D1              | 10       | 15             | 25         |

|                                  |            |                                                                                    | D2              | 40       | 60             | 80         |

|                                  |            |                                                                                    | D3              | 150      | 225            | 300        |

|                                  |            |                                                                                    | D4              | 1200     | 1800           | 2400       |

|                                  |            |                                                                                    | D5              | 300      | 450            | 600        |

|                                  |            |                                                                                    | D6              | 600      | 900            | 1200       |

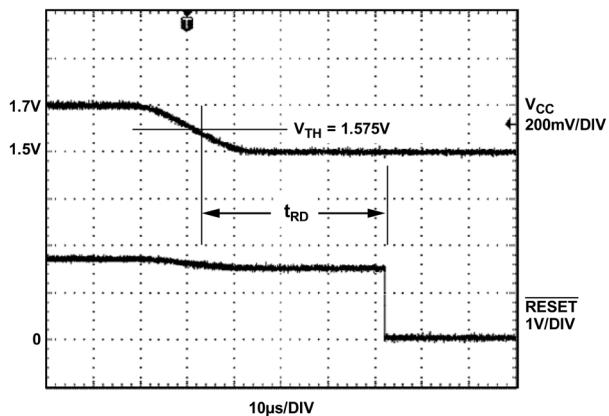

| $V_{CC}$ to Reset Delay          | $t_{RD}$   | $V_{CC}$ falling from ( $V_{TH} + 100mV$ ) to ( $V_{TH} - 100mV$ ) at $10mV/\mu s$ |                 | 40       |                | μs         |

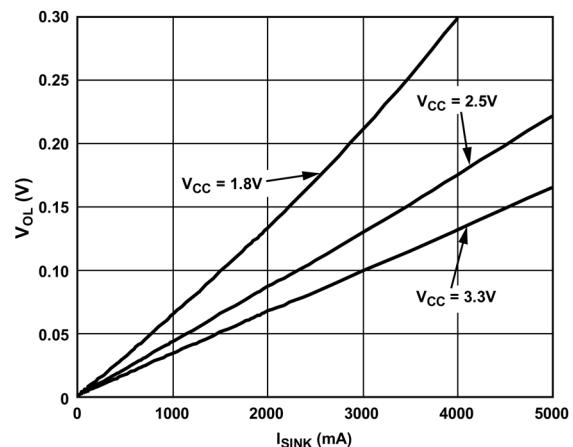

| RESET Output Voltage             | $V_{OL}$   | $V_{CC} \geq 1.1V$ , $I_{SINK} = 50\mu A$ , RESET asserted, $T_A \geq 0^{\circ}C$  |                 |          | 0.3            | V          |

|                                  |            | $V_{CC} \geq 1.2V$ , $I_{SINK} = 100\mu A$ , RESET asserted                        |                 |          | 0.3            |            |

|                                  |            | $V_{CC} \geq 2.12V$ , $I_{SINK} = 1.2mA$ , RESET asserted                          |                 |          | 0.3            |            |

| Open-Drain RESET Leakage Current | $I_{LKG}$  | RESET deasserted                                                                   |                 | 30       |                | nA         |

| <b>MANUAL RESET INPUT</b>        |            |                                                                                    |                 |          |                |            |

| MR Input Voltage                 | $V_{IH}$   |                                                                                    | 0.8 x $V_{CC}$  |          |                | V          |

|                                  | $V_{IL}$   |                                                                                    | 0.2 x $V_{CC}$  |          |                |            |

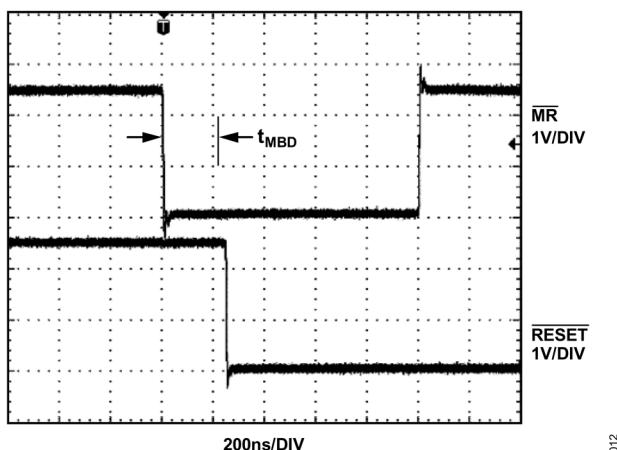

| MR Minimum Pulse Width           | $t_{MPW}$  |                                                                                    | 1               |          |                | μs         |

| MR Glitch Rejection              |            |                                                                                    | 200             |          |                | ns         |

| MR to Reset Delay                | $t_{MRD}$  |                                                                                    | 250             |          |                | ns         |

| MR Pullup Resistance             |            |                                                                                    | 5               | 10       | 20             | kW         |

| <b>WATCHDOG TIMER</b>            |            |                                                                                    |                 |          |                |            |

| WDI Input Voltage                | $V_{IH}$   |                                                                                    | 0.8 x $V_{CC}$  |          |                | V          |

|                                  | $V_{IL}$   |                                                                                    | 0.2 x $V_{CC}$  |          |                |            |

| WDI Input Current                |            | WDI = GND or $V_{CC}$                                                              |                 | 20       |                | nA         |

| WDI Pulse Width                  | $t_{WDI}$  | (Note 3)                                                                           | 150             |          |                | ns         |

# 手動リセット機能とウォッチドッグ・タイマを備えた ナノパワーμP 監視回路

ADPL62933

(特に指定のない限り、 $V_{CC} = 1.7V \sim 5.5V$ 、 $T_A = -40^{\circ}C \sim +85^{\circ}C$ 。代表値は  $V_{CC} = 2.5V$ 、 $T_A = +25^{\circ}C$  での値です。 (Note 1) )

| PARAMETER               | SYMBOL   | CONDITIONS | MIN | TYP | MAX  | UNITS |

|-------------------------|----------|------------|-----|-----|------|-------|

| Watchdog Timeout Period | $t_{WD}$ | S          | 1.5 | 3.3 | 7.75 | s     |

|                         |          | L          | 95  | 209 | 487  |       |

Note 1 : デバイスは、 $T_A = +25^{\circ}C$  でテストされています。 $T_A = -40^{\circ}C \sim +85^{\circ}C$  での仕様は設計により確保されています。

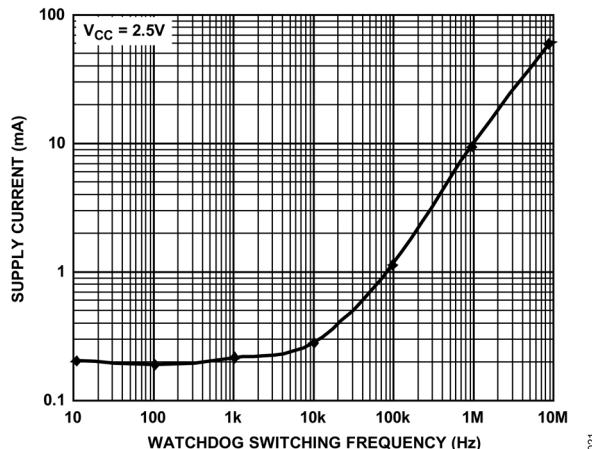

Note 2 : ウォッチドッグ時間は 1 秒で、 $t_{RISE}$  および  $t_{FALL}$  は 50ns 未満です。

Note 3 : 設計により確保されています。

### 標準動作特性

(特に指定のない限り、 $V_{CC} = +2.5V$ 、 $T_A = +25^{\circ}\text{C}$ 。)

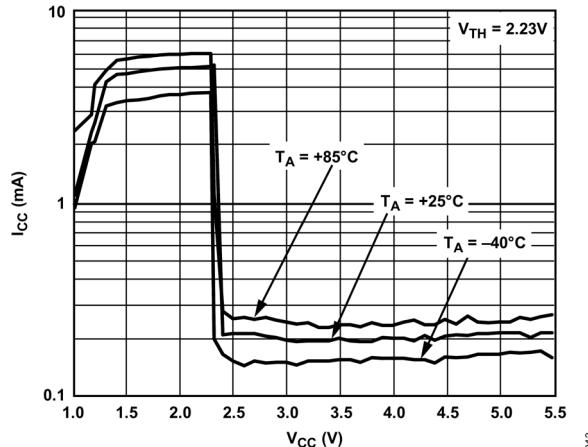

図 1. 電源電流と電源電圧の関係

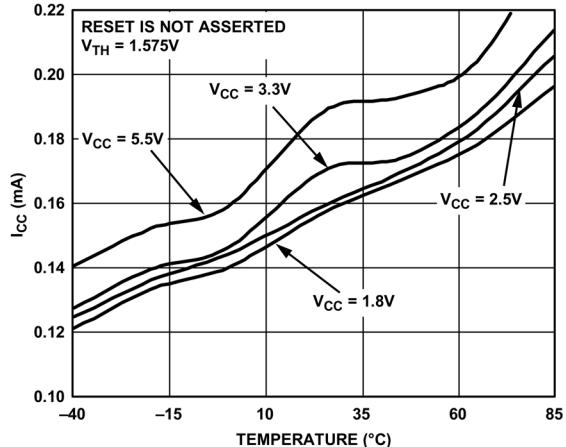

図 2. 電源電流と温度の関係

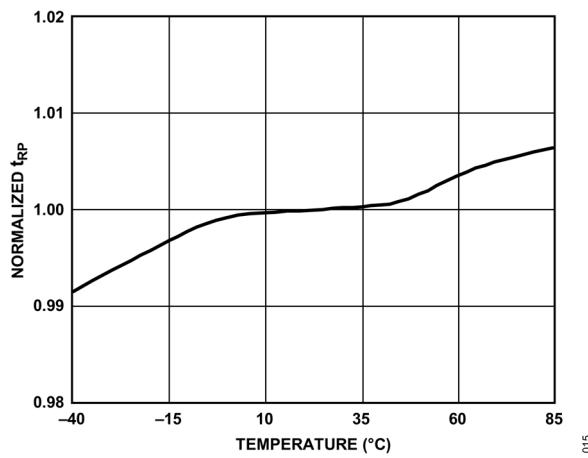

図 3. 正規化リセット・タイムアウト時間と温度の関係

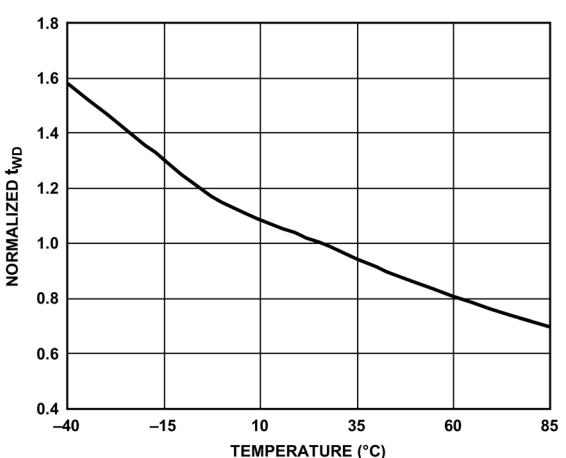

図 4. 正規化ウォッチドッグ・タイムアウト時間と温度の関係

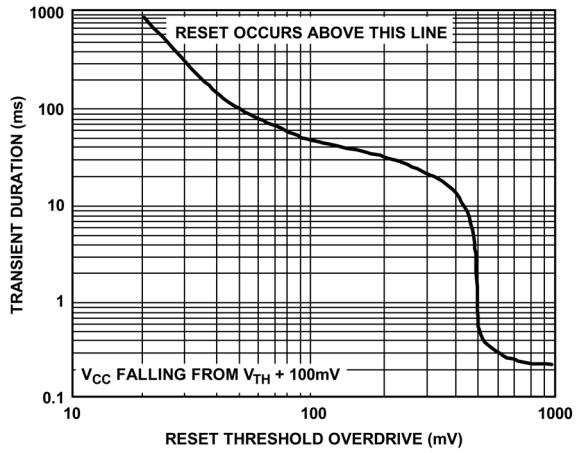

図 5.  $V_{CC}$  の最長トランジエント時間と

リセット閾値オーバードライブの関係

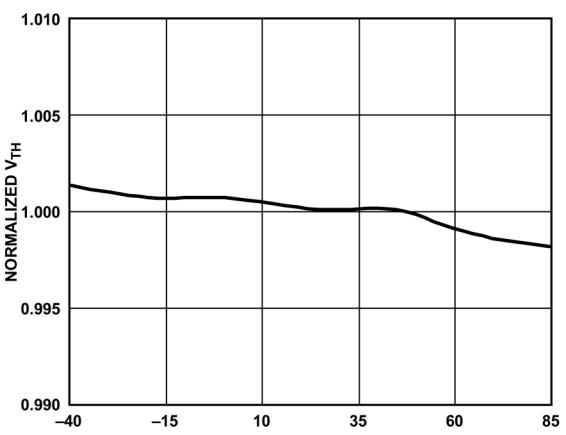

図 6. 正規化リセット閾値電圧と温度の関係

# 手動リセット機能とウォッチドッグ・タイマを備えた ナノパワーμP 監視回路

ADPL62933

(特に指定のない限り、 $V_{CC} = +2.5V$ 、 $T_A = +25^{\circ}C$ 。)

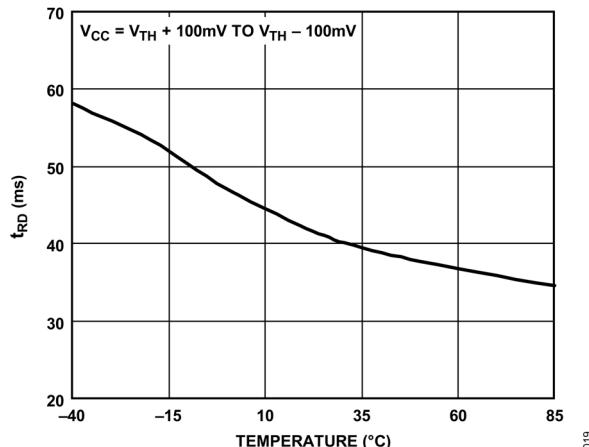

図 7.  $V_{CC}$  からリセットまでの遅延と温度の関係

図 8. 出力ロード電圧とシンク電流の関係

図 9. 電源電流とウォッチドッグ・スイッチング周波数の関係

図 10.  $V_{CC}$  からリセットまでの遅延

図 11. 手動リセットの遅延

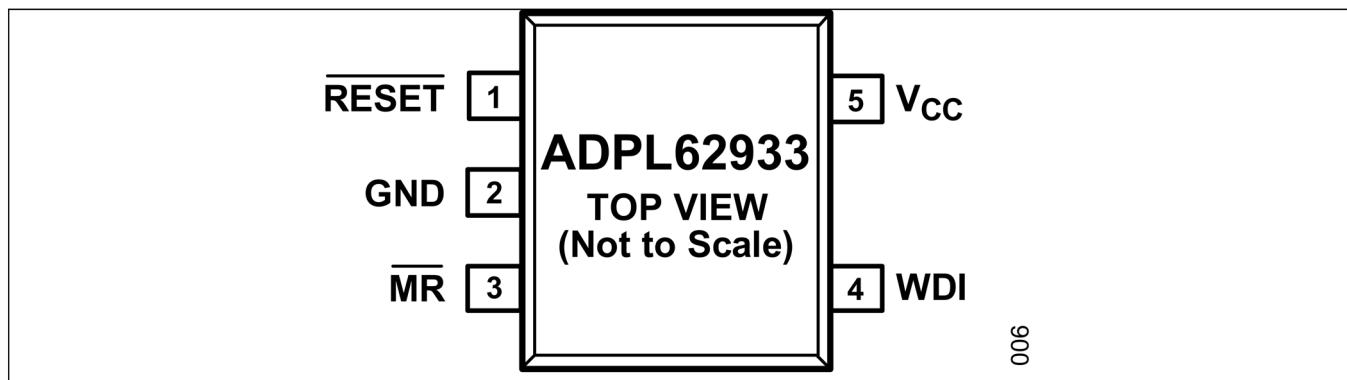

ピン配置

端子説明

| 端子        | 名称              | 機能                                                                                                                                                                                                                                                                        |

|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADPL62933 |                 |                                                                                                                                                                                                                                                                           |

| 1         | RESET           | アクティブ・ロー、オープン・ドレインのリセット出力。V <sub>CC</sub> が選択されたリセット閾値未満に低下する、MRがローにプルダウンされる、あるいはウォッチドッグ・タイマ時間が経過すると、RESETはハイからローに遷移します。V <sub>CC</sub> がデバイスのリセット閾値を超えた後、MRがデアサートされた後、あるいはウォッチドッグ・タイマ時間が経過した後、RESETはリセット・タイムアウト時間が経過するまでロー状態を維持します。オープン・ドレインのRESET出力には、外付けのプルアップ抵抗が必要です。 |

| 2         | GND             | グラウンド。                                                                                                                                                                                                                                                                    |

| 3         | MR              | アクティブ・ローの手動リセット入力。リセットを起動するにはMRをローに駆動します。MRがローに保持されている間、およびMRがハイに遷移後リセット・タイムアウト時間が経過するまでの間、リセット出力はアサートされたままになります。使用しない場合、MRは無接続のままにするか、V <sub>CC</sub> に接続します。MRは 10kW を通じて内部で V <sub>CC</sub> にプルアップされています。                                                              |

| 4         | WDI             | ウォッチドッグ入力。ウォッチドッグ・タイムアウト時間より長い時間 WDI がハイまたはローのままである場合、内蔵ウォッチドッグ・タイマが期限切れとなり、リセット・タイムアウト時間が経過するまでリセットがトリガされます。内蔵ウォッチドッグ・タイマは、リセットがアサートされた場合、手動リセットがアサートされた場合、あるいは、WDI に立上がりエッジまたは立下がりエッジが生じた場合は、常にクリアされます。                                                                 |

| 5         | V <sub>CC</sub> | 電源電圧。V <sub>CC</sub> リセット・モニタ用の入力。ノイズの多いシステムでは、0.1μF のコンデンサで V <sub>CC</sub> を GND にバイパスしてください。                                                                                                                                                                           |

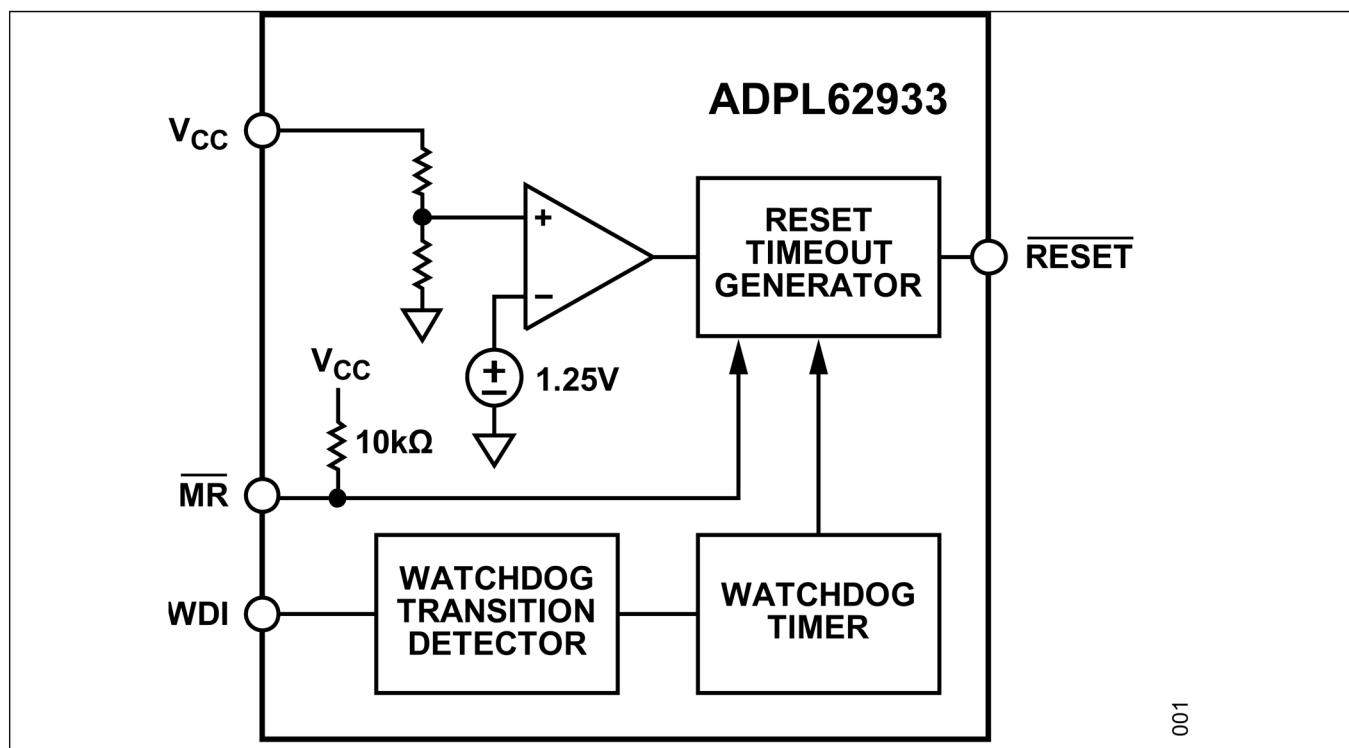

機能図

図 12. 機能図

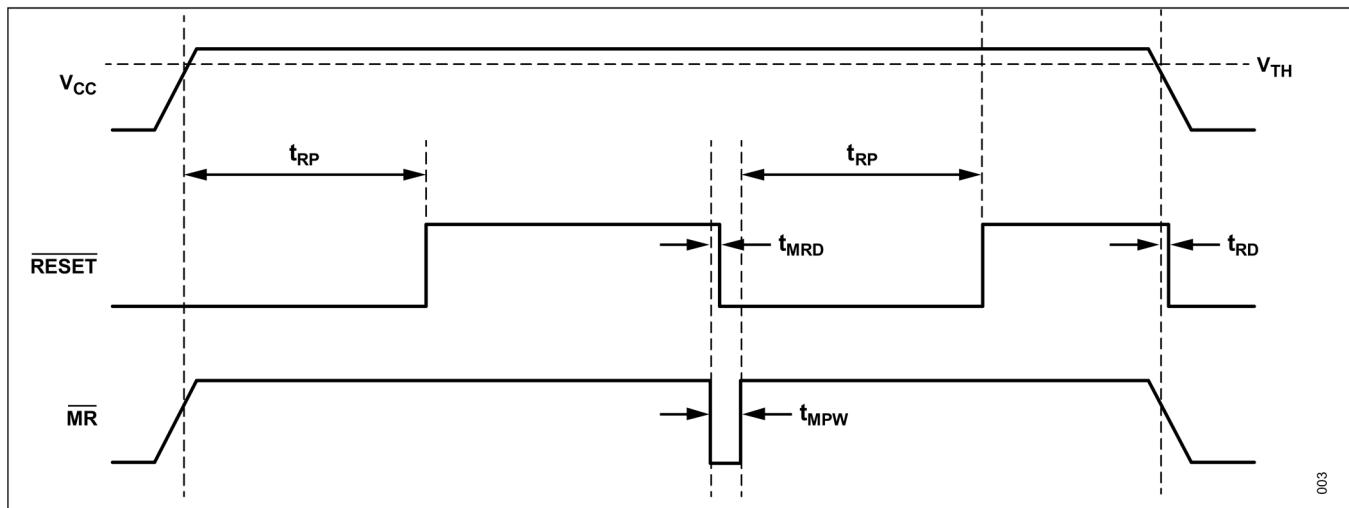

図 13.  $\overline{\text{RESET}}$ のタイミング関係

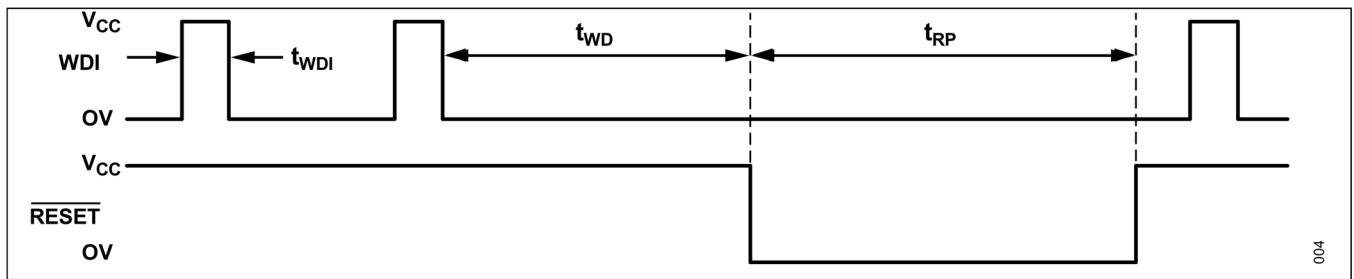

図 14. ウォッチドッグ入力の詳細なタイミング関係

004

## 詳細説明

### RESET出力

μP のリセット入力は、既知の状態で μP を起動します。ADPL62933 の μP 監視回路は、パワーアップ、パワーダウン、ブラウンアウト状態時に、コードの実行エラー発生を防ぐためリセットをアサートします。ADPL62933 のリセット出力は、V<sub>CC</sub> が 1.1V まで低下しても有効であるようになっています。

V<sub>CC</sub> がリセット閾値未満に低下した場合は常に、リセット出力が **RESET** にローをアサートします。V<sub>CC</sub> がリセット閾値を超えると、内部タイマーが特定のリセット・タイムアウト時間が経過するまでリセット出力をアサートし続けます。そして、この時間が経過した後、リセット出力がデアサートされます（図 13 参照）。

### 手動リセット入力

多くの μP ベースの製品には手動リセット機能が必要となります。これにより、オペレータやテスト担当者によって、あるいは外部ロジック回路によってリセットを起動できます。ADPL62933 は **MR** 入力を備えています。**MR** がロジック・ローになるとリセットがアサートされます。**MR** がローの間、あるいは、**MR** がハイに復帰後タイムアウト時間 ( $t_{RP}$ ) が経過するまでの間、リセットはアサートされたままになります。デバイスの **MR** と V<sub>CC</sub> の間には 10kΩ のプルアップ抵抗が内蔵されています。使用しない場合、**MR** は無接続のままにするか、V<sub>CC</sub> に接続します。**MR** は、CMOS ロジック・レベル、あるいは、オープン・ドレイン／コレクタ出力で駆動できます。手動リセット機能を動作させるには、ノーマリ・オープンのモーメンタリ・スイッチを **MR** と GND の間に接続します。外付けのバウンス防止回路は不要です。**MR** を長いケーブルで駆動する場合、または、デバイスをノイズの多い環境で用いる場合は、**MR** と GND の間に 0.1μF のコンデンサを接続して、ノイズ耐性を強化します。

### ウォッチドッグ入力

ADPL62933 のウォッチドッグ・タイマ回路は、μP の動作をモニタします。μP がウォッチドッグ・タイムアウト時間 ( $t_{WDI}$ ) 内にウォッチドッグ入力 (WDI) を（ローからハイまたはハイからローに）トグルしない場合、リセット・タイムアウト時間 ( $t_{RP}$ ) が経過するまでリセットがアサートされます。内蔵タイマーがクリアされるのは、リセットがアサートされた場合、手動リセットがアサートされた場合、あるいは、WDI に立上がりエッジまたは立下がりエッジが生じた場合です。ウォッチドッグ入力は、150ns の短パルスも検出します。リセットがアサートされている間、ウォッチドッグ・タイマはカウントを行いません。ウォッチドッグ・タイマは、リセットがデアサートされると直ちにカウントを再開します（図 14 参照）。

## アプリケーション情報

### 過渡耐性

ADPL62933 は、パワーアップ、パワーダウン、ブラウンアウトの状態時に μP にリセットを指示する他、短時間の電源トランジエントまたはグリッヂに対し比較的耐性があります。標準動作特性のセクションの V<sub>CC</sub> の最長トランジエント時間とリセット閾値オーバードライブの関係を示すグラフに、この関係が示されています。

グラフの曲線より下の領域は、これらのデバイスが通常はリセット・パルスを発生しない領域です。このグラフは、実際のリセット閾値 (V<sub>TH</sub>) を 100mV 超える電圧で始まり、この閾値 (リセット閾値オーバードライブ) を下回った電圧で終了する立下がりパルスを、V<sub>CC</sub> に印加して生成されたものです。トランジエントの大きさが増加するにつれ、許容可能な最大パルス幅は減少します。通常、100mV の V<sub>CC</sub> トランジエントが 40μs 以下の場合、リセットは生じません。

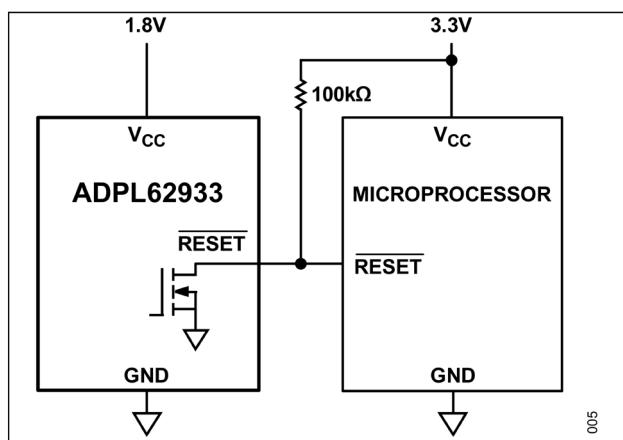

### ロジック互換性を確保するための他の電圧とのインターフェース

オープン・ドレイン RESET 出力を用いることで、その他のロジック・レベルの μP とインターフェースできます。図 15 に示すように、オープン・ドレイン出力は、0V~5.5V の電圧に接続できます。一般に、RESET に接続されたプルアップ抵抗は、IC の V<sub>CC</sub> 入力でモニタする電源電圧に接続します。ただし、一部のシステムでは、オープン・ドレイン出力を用いて、モニタする電源からレベルシフトし、別の電源電圧から給電される回路をリセットできます。なお、監視回路の V<sub>CC</sub> が減少するのに伴い、IC の RESET での電流シンク能力も低下する点に注意してください。

図 15. 他の電圧レベルとのインターフェース

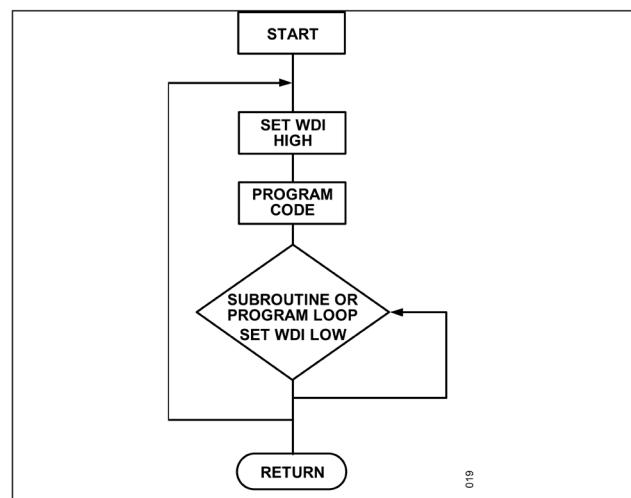

図 16. ウォッチドッグの流れ図

### ウォッチドッグのソフトウェアに関する考慮事項

ウォッチドッグ・タイマがソフトウェアの実行をより緊密にモニタするのをサポートするための方法の 1 つは、ウォッチドッグ入力をハイ・ロー・ハイあるいはロー・ハイ・ローとパルス的に動作させるのではなく、プログラムの様々な場所でウォッチドッグ入力のセット/リセットを行うことです。この手法により、ウォッチドッグ・タイマがループ内でリセットされ続けウォッチドッグがタイムアウトできなくなるという、スタック・ループが回避できます。

図 16 に、ウォッチドッグ入力を駆動する I/O がプログラムの最初にハイにセットされ、サブルーチンまたはループが始まるたびにローにセットされ、プログラムが最初に戻ると再びハイにセットされる、という流れ図の例を示します。万一プログラムがいずれかのサブルーチンでハンギングした場合、プログラムは直ちに修正されます。I/O が継続的にローにセットされてウォッチドッグ・タイマがタイムアウトでき、リセットまたは割込みを指示できるためです。

# 手動リセット機能とウォッチドッグ・タイマを備えた ナノパワーμP 監視回路

ADPL62933

表 1. 閾値サフィックス・ガイド

| SUFFIX | V <sub>CC</sub> THRESHOLD FALLING |       |       | UNITS |

|--------|-----------------------------------|-------|-------|-------|

|        | MIN                               | TYP   | MAX   |       |

| 46     | 4.486                             | 4.625 | 4.764 | V     |

| 45     | 4.365                             | 4.500 | 4.635 |       |

| 44     | 4.244                             | 4.375 | 4.506 |       |

| 43     | 4.171                             | 4.300 | 4.408 |       |

| 42     | 4.074                             | 4.200 | 4.429 |       |

| 41     | 3.977                             | 4.100 | 4.326 |       |

| 40     | 3.880                             | 4.000 | 4.120 |       |

| 39     | 3.783                             | 3.900 | 4.017 |       |

| 38     | 3.686                             | 3.800 | 3.914 |       |

| 37     | 3.589                             | 3.700 | 3.811 |       |

| 36     | 3.492                             | 3.600 | 3.708 |       |

| 35     | 3.395                             | 3.500 | 3.605 |       |

| 34     | 3.298                             | 3.400 | 3.502 |       |

| 33     | 3.201                             | 3.300 | 3.399 |       |

| 32     | 3.104                             | 3.200 | 3.296 |       |

| 31     | 2.983                             | 3.075 | 3.167 |       |

| 30     | 2.910                             | 3.000 | 3.090 |       |

| 29     | 2.837                             | 2.925 | 3.013 |       |

| 28     | 2.716                             | 2.800 | 2.884 |       |

| 27     | 2.619                             | 2.700 | 2.781 |       |

| 26     | 2.546                             | 2.625 | 2.704 |       |

| 25     | 2.425                             | 2.500 | 2.575 |       |

| 24     | 2.328                             | 2.400 | 2.472 |       |

| 23     | 2.244                             | 2.313 | 2.382 |       |

| 225    | 2.168                             | 2.235 | 2.302 |       |

| 22     | 2.122                             | 2.188 | 2.254 |       |

| 21     | 2.037                             | 2.100 | 2.163 |       |

| 20     | 1.940                             | 2.000 | 2.060 |       |

| 19     | 1.843                             | 1.900 | 1.957 |       |

| 18     | 1.746                             | 1.800 | 1.854 |       |

| 17     | 1.615                             | 1.665 | 1.715 |       |

| 16     | 1.528                             | 1.575 | 1.622 |       |

表 2. ウォッチドッグ・タイムアウト

| SUFFIX | WATCHDOG TIMEOUT PERIOD |     |      | UNITS |

|--------|-------------------------|-----|------|-------|

|        | MIN                     | TYP | MAX  |       |

| S      | 1.5                     | 3.3 | 7.75 | s     |

| L      | 95                      | 209 | 487  |       |

表 3. リセット・タイムアウト時間

| TIMEOUT OPTION | RESET TIMEOUT PERIODS |      |      |  | UNITS |

|----------------|-----------------------|------|------|--|-------|

|                | MIN                   | TYP  | MAX  |  |       |

| D1             | 10                    | 15   | 25   |  | ms    |

| D2             | 40                    | 60   | 80   |  |       |

| D3             | 150                   | 225  | 300  |  |       |

| D4             | 1200                  | 1800 | 2400 |  |       |

| D5             | 300                   | 450  | 600  |  |       |

| D6             | 600                   | 900  | 1200 |  |       |

標準アプリケーション回路

型番

| PART†              | TEMP RANGE     | PIN-PACKAGE |

|--------------------|----------------|-------------|

| ADPL62933UK29D3S+  | -40°C to +85°C | 5 SOT23-5   |

| ADPL62933UK29D3S+T | -40°C to +85°C | 5 SOT23-5   |

| ADPL62933UK__D__+  | -40°C to +85°C | 5 SOT23-5   |

| ADPL62933UK__D__+T | -40°C to +85°C | 5 SOT23-5   |

†UK の後にリセット閾値サフィックスを挿入してください（[表1. 閾値サフィックス・ガイド](#)を参照）。D の後には、目的のリセット・タイムアウト時間に対応する数字を挿入します（[表3. リセット・タイムアウト時間](#)を参照）。リセット・タイムアウト時間のサフィックスに続く空欄には、目的のウォッチドッグ・タイムアウト時間に対応する文字（S またはL、[表2](#)を参照）を挿入します。

注：サンプル在庫は通常、標準バージョンでのみ確保されています（[型番](#)のセクションを参照）。標準バージョンでは2500個単位の発注条件があります。標準以外のバージョンでは10,000個単位の発注条件があります。標準以外のバージョンの在庫については弊社にお問い合わせください。

改訂履歴

| 版数 | 改訂日   | 説明           | 改訂ページ |

|----|-------|--------------|-------|

| 0  | 01/24 | 市場投入のためのリリース | -     |

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2025年12月2日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2025年12月2日

製品名：ADPL62933

対象となるデータシートのリビジョン(Rev)：Rev.1

訂正箇所：5頁、電気的スペック表、下から5行目、MR Pull-Up Resistance の単位

### 【誤】

“kW”

### 【正】

“kΩ”

アナログ・デバイセズ株式会社

本 社／〒105-7323 東京都港区東新橋1-9-1

東京汐留ビルディング 23F

大 阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36

新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1

名古屋ルーセントタワー 40F

## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2025年12月2日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2025年12月2日

製品名：ADPL62933

対象となるデータシートのリビジョン(Rev)：Rev.1

訂正箇所：9頁、端子説明の表、3番ピンの機能説明欄、最後の分

### 【誤】

「MRは10kWを通じて内部でVCCにプルアップされています。」

### 【正】

「MRは10kΩを通じて内部でVCCにプルアップされています。」

アナログ・デバイセズ株式会社

本 社／〒105-7323 東京都港区東新橋1-9-1

東京汐留ビルディング 23F

大 阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36

新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1

名古屋ルーセントタワー 40F