## 20V、500mA の低ノイズ CMOS LDO

### 特長

- ▶ 入力電圧範囲 : 4V~20V

- ▶ 最大出力電流 : 500mA

- ▶ 低ノイズ : 固定出力モデルで  $32\mu\text{VRms}$

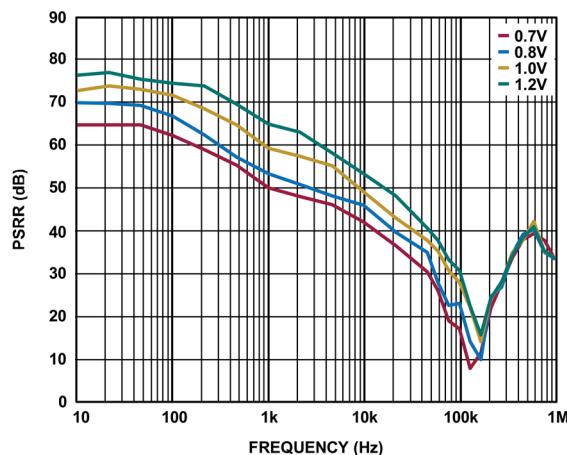

- ▶ 58dB の PSRR 性能 (10kHz,  $V_{\text{OUT}} = 3.3\text{V}$ )

- ▶ 逆電流保護

- ▶ 低ドロップアウト電圧 : 400mV (500mA 時)

- ▶ 初期精度 :  $\pm 0.8\%$

- ▶ 電源ライン、負荷、温度に対する精度 :

- ▶  $-2\% \sim +1\%$ ,  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$

- ▶ 低静止電流 :  $I_{\text{GND}} = 900\mu\text{A}$  ( $V_{\text{IN}} = 10\text{V}$ , 500mA 負荷時)

- ▶ 低シャットダウン電流 :  $V_{\text{IN}} = 12\text{V}$  で  $40\mu\text{A}$  未満、小型の  $1\mu\text{F}$  セラミック出力コンデンサで安定

- ▶ 6通りの固定出力電圧オプション : 1.5V、1.8V、2.5V、3V、3.3V、5V

- ▶ 調整可能な出力範囲 :  $1.22\text{V} \sim V_{\text{IN}} - V_{\text{DO}}$

- ▶ フォールドバック電流制限と熱過負荷保護

- ▶ ユーザ・プログラマブルな高精度 UVLO/イネーブル

- ▶ パワー・グッド・インジケータ

- ▶ 8ピン LFCSP パッケージまたは 8ピン SOIC パッケージ

### アプリケーション

- ▶ ノイズに敏感なアプリケーションのレギュレーション : ADC および DAC 回路、高精度アンプ、高周波発振器、クロック、PLL

- ▶ 通信およびインフラストラクチャ

- ▶ 医療機器、健康機器

- ▶ 工業用機器、計測機器

### 概要

ADPL42005 は、4V~20V で動作し、最大 500mA の電流を出力する低ドロップアウトの CMOS (相補型金属酸化膜半導体) リニア・レギュレータです。入力電圧の高いこの LDO は、19V~1.22V のレールで動作する高性能アナログ回路やミックスド・シグナル回路のレギュレーションに最適です。独自の最新アーキテクチャを採用して高い電源電圧変動除去比と低ノイズを実現すると共に、小型の  $1\mu\text{F}$  セラミック出力コンデンサを使って優れた入力過渡応答と負荷過渡応答が得られます。

ADPL42005 では、6通りの固定出力電圧オプションと 1つの調整可能モデルが提供されています。調整可能モデルでは、外付けの帰還分圧器によって  $1.22\text{V} \sim V_{\text{IN}} - V_{\text{DO}}$  の範囲の出力電圧が得られます。

ADPL42005 の出力ノイズ電圧は、出力電圧に関係なく  $32\mu\text{VRms}$  です。デジタルのパワー・グッド出力によって、パワー・システム・モニターで出力電圧の正常性を確認できます。ユーザ・プログラマブルな高精度低電圧ロックアウト機能により、複数の電源のシーケンス処理が可能です。

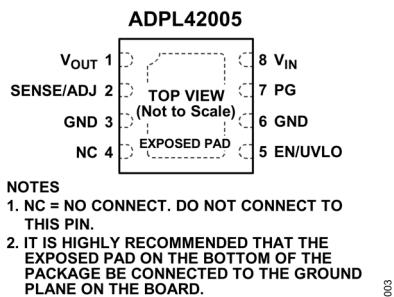

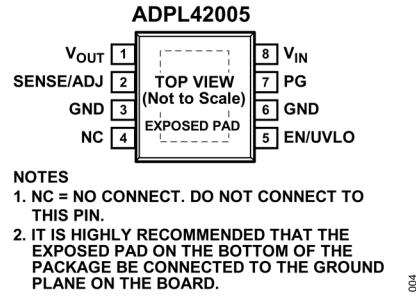

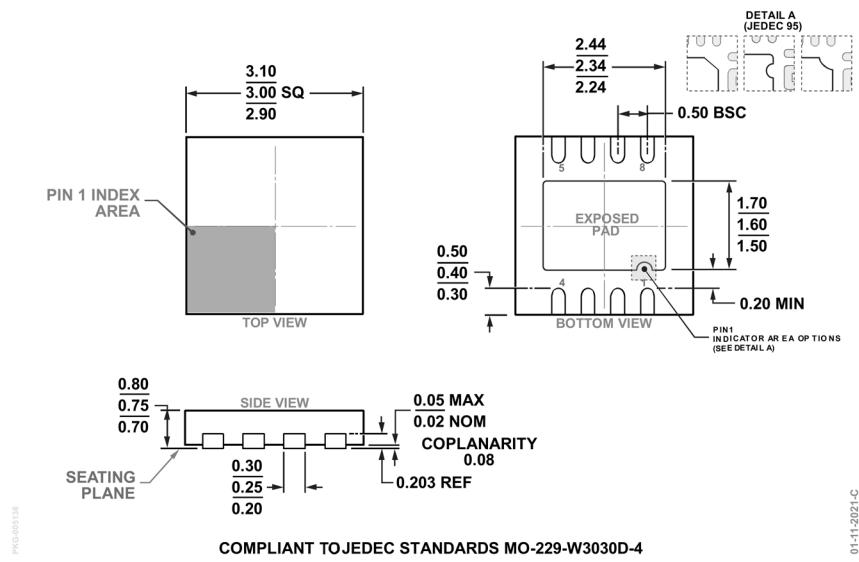

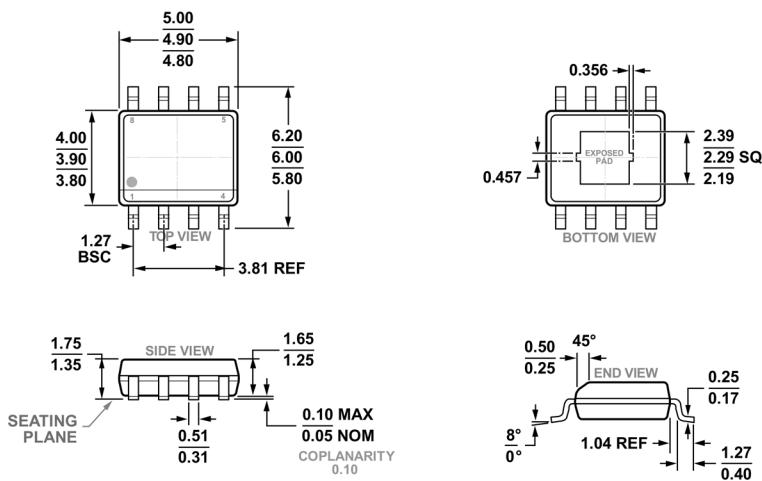

ADPL42005 は、8ピンの  $3\text{mm} \times 3\text{mm}$  LFCSP パッケージと 8ピン SOIC パッケージ (図 51 と図 52) で提供されます。LFCSP パッケージでは、非常に小型のソリューションが実現します。また、フットプリントが小さく、低プロファイルのパッケージで、500mA までの出力電流を必要とするアプリケーションに対して優れた熱性能を発揮します。

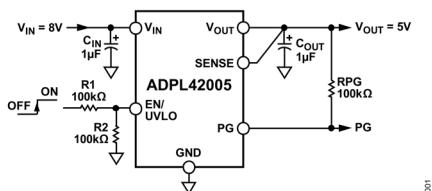

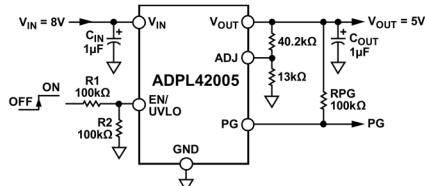

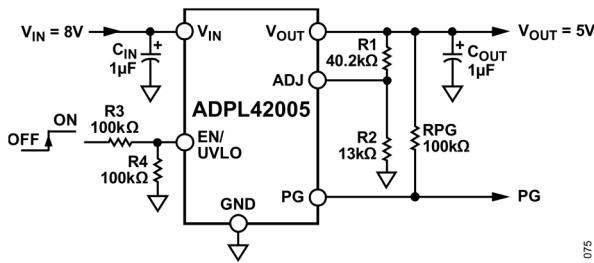

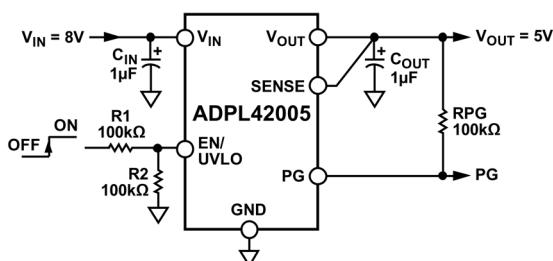

### 簡略アプリケーション回路図

図 1. 固定出力電圧 5V の ADPL42005

図 2. 調整可能出力電圧 5V の ADPL42005

## 目次

|                            |    |

|----------------------------|----|

| 特長                         | 1  |

| アプリケーション                   | 1  |

| 概要                         | 1  |

| 簡略アプリケーション回路図              | 1  |

| 仕様                         | 3  |

| 絶対最大定格                     | 6  |

| 熱データ                       | 6  |

| 熱抵抗                        | 7  |

| ESD に関する注意                 | 7  |

| ピン配置およびピン機能の説明             | 8  |

| 端子説明                       | 8  |

| 代表的な性能特性                   | 9  |

| 動作原理                       | 15 |

| アプリケーション情報                 | 17 |

| 設計ツール                      | 17 |

| コンデンサの選択                   | 17 |

| 入力バイパス・コンデンサ               | 17 |

| プログラマブルな低電圧ロックアウト (UVLO)   | 17 |

| パワー・グッド機能                  | 19 |

| 調整可能モードの ADPL42005 でのノイズ低減 | 20 |

| 電流制限と熱過負荷保護                | 20 |

| プリント回路基板レイアウトに関する考慮事項      | 22 |

| 外形寸法                       | 23 |

| オーダー・ガイド                   | 24 |

| 出力電圧オプション                  | 24 |

| 評価用ボード                     | 24 |

| 改訂履歴                       | 25 |

## 仕様

表 1. 電気的特性

(特に指定のない限り、 $V_{IN} = (V_{OUT} + 1V)$ または4Vのいずれか大きい方、EN =  $V_{IN}$ 、 $I_{OUT} = 10mA$ 、 $C_{IN} = C_{OUT} = 1\mu F$ 、代表値は $T_A = 25^\circ C$ での値、最大値／最小値は $T_J = -40^\circ C \sim +125^\circ C$ での値。)

| PARAMETER                            | SYMBOL                          | CONDITIONS                                                                                                            | MIN    | TYP  | MAX    | UNITS      |

|--------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------|------|--------|------------|

| INPUT VOLTAGE RANGE                  | $V_{IN}$                        |                                                                                                                       | 4      |      | 20     | V          |

| OPERATING SUPPLY CURRENT             | $I_{GND}$                       | $I_{OUT} = 100\mu A, V_{IN} = 10V$                                                                                    |        | 440  | 900    | $\mu A$    |

|                                      |                                 | $I_{OUT} = 10mA, V_{IN} = 10V$                                                                                        |        | 450  | 1050   | $\mu A$    |

|                                      |                                 | $I_{OUT} = 300mA, V_{IN} = 10V$                                                                                       |        | 750  | 1400   | $\mu A$    |

|                                      |                                 | $I_{OUT} = 500mA, V_{IN} = 10V$                                                                                       |        | 900  | 1600   | $\mu A$    |

| SHUTDOWN CURRENT                     | $I_{GND-SD}$                    | EN = GND, $V_{IN} = 12V$                                                                                              |        | 40   | 75     | $\mu A$    |

| INPUT REVERSE CURRENT                | $I_{REV-INPUT}$                 | EN = GND, $V_{IN} = 0V, V_{OUT} = 20V$                                                                                |        | 0.3  | 5      | $\mu A$    |

| <b>OUTPUT VOLTAGE</b>                |                                 |                                                                                                                       |        |      |        |            |

| FIXED OUTPUT VOLTAGE ACCURACY        | $V_{OUT}$                       | $I_{OUT} = 10mA$                                                                                                      | -0.8   |      | +0.8   | %          |

|                                      |                                 | $1mA < I_{OUT} < 500mA, V_{IN} = (V_{OUT} + 1V) \text{ to } 20V$                                                      | -2     |      | +1     | %          |

| ADJUSTABLE OUTPUT VOLTAGE ACCURACY   | $V_{ADJ}$                       | $I_{OUT} = 10mA$                                                                                                      | 1.21   | 1.22 | 1.23   | V          |

|                                      |                                 | $1mA < I_{OUT} < 500mA, V_{IN} = (V_{OUT} + 1V) \text{ to } 20V$                                                      | 1.196  |      | 1.232  | V          |

| LINE REGULATION                      | $\Delta V_{OUT}/\Delta V_{IN}$  | $V_{IN} = (V_{OUT} + 1V) \text{ to } 20V$                                                                             | -0.015 |      | +0.015 | %/V        |

| LOAD REGULATION <sup>1</sup>         | $\Delta V_{OUT}/\Delta I_{OUT}$ | $I_{OUT} = 1mA \text{ to } 500mA$                                                                                     |        | 0.2  | 0.75   | %/A        |

| ADJ INPUT BIAS CURRENT               | $ADJ_{I-BIAS}$                  | $1mA < I_{OUT} < 500mA, V_{IN} = (V_{OUT} + 1V) \text{ to } 20V, ADJ \text{ connected to } V_{OUT}$                   |        | 10   |        | nA         |

| SENSE INPUT BIAS CURRENT             | $SENSE_{I-BIAS}$                | $1mA < I_{OUT} < 500mA, V_{IN} = (V_{OUT} + 1V) \text{ to } 20V, SENSE \text{ connected to } V_{OUT}, V_{OUT} = 1.5V$ |        | 1    |        | $\mu A$    |

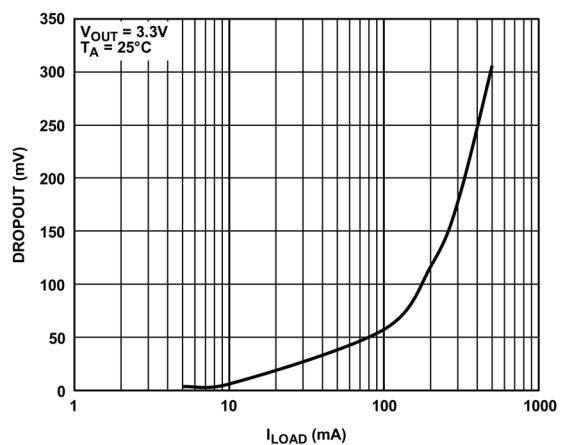

| DROPOUT VOLTAGE <sup>2</sup>         | $V_{DROPOUT}$                   | $I_{OUT} = 10mA$                                                                                                      |        | 20   | 40     | mV         |

|                                      |                                 | $I_{OUT} = 150mA$                                                                                                     |        | 100  | 175    | mV         |

|                                      |                                 | $I_{OUT} = 300mA$                                                                                                     |        | 200  | 325    | mV         |

|                                      |                                 | $I_{OUT} = 500mA$                                                                                                     |        | 400  | 600    | mV         |

| CURRENT-LIMIT THRESHOLD <sup>3</sup> | $I_{LIMIT}$                     |                                                                                                                       | 625    | 775  | 1000   | mA         |

| <b>PG OUTPUT LOGIC LEVEL</b>         |                                 |                                                                                                                       |        |      |        |            |

| PG OUTPUT LOGIC HIGH                 | $PG_{HIGH}$                     | $I_{OH} < 1\mu A$                                                                                                     | 1.0    |      |        | V          |

| PG OUTPUT LOGIC LOW                  | $PG_{LOW}$                      | $I_{OL} < 2mA$                                                                                                        |        |      | 0.4    | V          |

| <b>PG OUTPUT THRESHOLD</b>           |                                 |                                                                                                                       |        |      |        |            |

| PG OUTPUT VOLTAGE FALLING            | $PG_{FALL}$                     |                                                                                                                       |        | -9.2 |        | %          |

| PG OUTPUT VOLTAGE RISING             | $PG_{RISE}$                     |                                                                                                                       |        | -6.5 |        | %          |

| <b>THERMAL SHUTDOWN</b>              |                                 |                                                                                                                       |        |      |        |            |

| THERMAL SHUTDOWN THRESHOLD           | $TS_{SD}$                       | $T_J \text{ rising}$                                                                                                  |        | 150  |        | $^\circ C$ |

| THERMAL SHUTDOWN HYSTERESIS          | $TS_{SD-HYS}$                   |                                                                                                                       |        | 15   |        | $^\circ C$ |

| <b>PROGRAMMABLE EN/UVLO</b>          |                                 |                                                                                                                       |        |      |        |            |

| UVLO THRESHOLD RISING                | $UVLO_{RISE}$                   | $3.3V \leq V_{IN} \leq 20V$                                                                                           | 1.18   | 1.22 | 1.28   | V          |

(特に指定のない限り、 $V_{IN} = (V_{OUT} + 1V)$ または4Vのいずれか大きい方、 $EN = V_{IN}$ 、 $I_{OUT} = 10mA$ 、 $C_{IN} = C_{OUT} = 1\mu F$ 、代表値は $T_A = 25^\circ C$ での値、最大値／最小値は $T_J = -40^\circ C \sim +125^\circ C$ での値。)

| PARAMETER                    | SYMBOL         | CONDITIONS                                                           | MIN  | TYP  | MAX | UNITS  |

|------------------------------|----------------|----------------------------------------------------------------------|------|------|-----|--------|

| UVLO THRESHOLD FALLING       | $UVLO_{FALL}$  | $3.3V \leq V_{IN} \leq 20V$ , 10kΩ in series with the enable pin     |      | 1.13 |     | V      |

| UVLO Hysteresis Current      | $UVLO_{HYS}$   | $V_{EN} > 1.25V$                                                     | 7.5  | 9.8  | 12  | μA     |

| ENABLE PULL-DOWN CURRENT     | $I_{EN-IN}$    | $EN = V_{IN}$                                                        |      | 500  |     | nA     |

| START THRESHOLD              | $V_{START}$    |                                                                      |      |      | 3.2 | V      |

| SHUTDOWN THRESHOLD           | $V_{SHUTDOWN}$ |                                                                      | 2.45 |      |     | V      |

| Hysteresis                   |                |                                                                      |      | 250  |     | mV     |

| OUTPUT NOISE                 | $OUT_{NOISE}$  | 10Hz to 100kHz, $V_{IN} = 6.3V$ , $V_{OUT} = 3.3V$                   |      | 32   |     | μV rms |

|                              |                | 10Hz to 100kHz, $V_{IN} = 5.5V$ , $V_{OUT} = 1.5V$ , adjustable mode |      | 18   |     | μV rms |

|                              |                | 10Hz to 100kHz, $V_{IN} = 12V$ , $V_{OUT} = 5V$ , adjustable mode    |      | 30   |     | μV rms |

|                              |                | 10Hz to 100kHz, $V_{IN} = 20V$ , $V_{OUT} = 15V$ , adjustable mode   |      | 65   |     | μV rms |

| POWER SUPPLY REJECTION RATIO | PSRR           | 100kHz, $V_{IN} = 4.3V$ , $V_{OUT} = 3.3V$                           |      | 50   |     | dB     |

|                              |                | 10kHz, $V_{IN} = 4.3V$ , $V_{OUT} = 3.3V$                            |      | 58   |     | dB     |

|                              |                | 100kHz, $V_{IN} = 3.3V$ , $V_{OUT} = 1.8V$ , adjustable mode         |      | 50   |     | dB     |

|                              |                | 10kHz, $V_{IN} = 3.3V$ , $V_{OUT} = 1.8V$ , adjustable mode          |      | 60   |     | dB     |

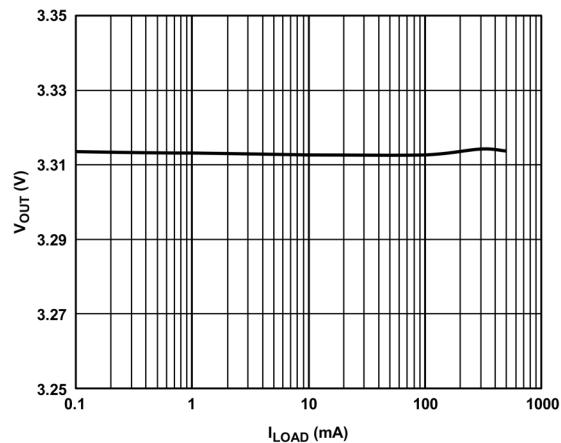

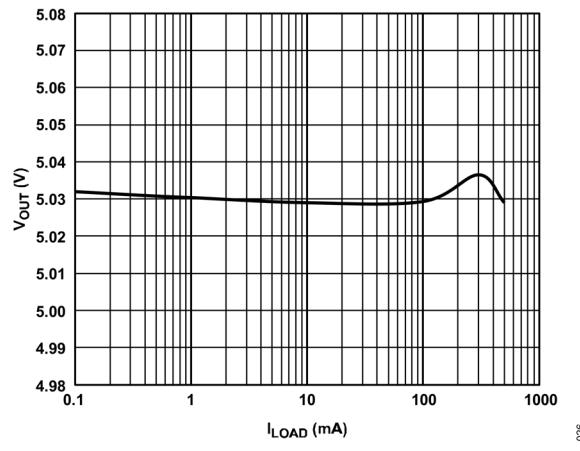

<sup>1</sup> 1mAと500mAの負荷を使用したエンドポイント計算に基づきます。1mA未満の負荷に対する代表的な負荷レギュレーション性能については、図6を参照してください。

<sup>2</sup> ドロップアウト電圧は、入力電圧を公称出力電圧に設定したときの入力電圧と出力電圧間の電圧差として定義されます。これは、3.0Vを超える出力電圧に対してのみ適用されます。

<sup>3</sup> 電流制限の閾値は、出力電圧が規定代表値の90%に低下する電流値として定義されます。例えば、5.0V出力電圧の電流制限値は、出力電圧が5.0Vの90% (4.5V) に低下する電流値として定義されます。

表2. 入力コンデンサと出力コンデンサの推奨仕様

| PARAMETER                                         | SYMBOL           | CONDITIONS                       | MIN   | TYP | MAX | UNITS |

|---------------------------------------------------|------------------|----------------------------------|-------|-----|-----|-------|

| Minimum Input and Output Capacitance <sup>1</sup> | C <sub>MIN</sub> | T <sub>A</sub> = -40°C to +125°C | 0.7   |     |     | μF    |

| Capacitor ESR                                     | R <sub>ESR</sub> | T <sub>A</sub> = -40°C to +125°C | 0.001 |     | 0.2 | Ω     |

<sup>1</sup> 最小入力容量と最小出力容量は、動作条件の全範囲で 0.7μF より大きいことが必要です。最小容量規定値を確実に満たすため、デバイス選択時にアプリケーションの動作条件の全範囲を考慮する必要があります。X7R タイプと X5R タイプのコンデンサの使用を推奨します。Y5V コンデンサと ZSU コンデンサは、LDO での使用は推奨できません。

## 絶対最大定格

表 3. 絶対最大定格

| PARAMETER                            | RATING                    |

|--------------------------------------|---------------------------|

| V <sub>IN</sub> to GND               | -0.3V to +22V             |

| V <sub>OUT</sub> to GND              | -0.3V to +20V             |

| EN/UVLO to GND                       | -0.3V to V <sub>IN</sub>  |

| PG to GND                            | -0.3V to V <sub>IN</sub>  |

| SENSE/ADJ to GND                     | -0.3V to V <sub>OUT</sub> |

| Storage Temperature Range            | -65°C to +150°C           |

| Operating Junction Temperature Range | -40°C to +125°C           |

| Soldering Conditions                 | JEDEC J-STD-020           |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱データ

絶対最大定格は、組合せではなく個別に適用されます。ジャンクション温度制限値を超えると、ADPL42005 が損傷を受けることがあります。周囲温度を監視しても、T<sub>J</sub> が仕様規定の温度内とは限らない場合があります。消費電力が大きく、熱抵抗が高いアプリケーションでは、最大周囲温度を下げる必要があります。

中程度の消費電力で、PCB の熱抵抗が低いアプリケーションでは、ジャンクション温度が規定値内にある限り、最大周囲温度はこの最大値を超えてかまいません。デバイスのジャンクション温度 (T<sub>J</sub>) は、周囲温度 (T<sub>A</sub>) 、デバイスの消費電力 (P<sub>D</sub>) 、パッケージのジャンクション-周囲間の熱抵抗 ( $\theta_{JA}$ ) に依存します。

最大ジャンクション温度 (T<sub>J</sub>) は、周囲温度 (T<sub>A</sub>) と消費電力 (P<sub>D</sub>) から次式を使って計算します。

$$T_J = T_A + (P_D \times \theta_{JA}) \quad (1)$$

パッケージのジャンクション-周囲間の熱抵抗 ( $\theta_{JA}$ ) は、4 層ボードを使ったモデリングと計算に基づいています。ジャンクション-周囲間の熱抵抗は、アプリケーションとボード・レイアウトに強く依存します。最大消費電力が大きいアプリケーションでは、ボードの熱設計に細心の注意が必要です。 $\theta_{JA}$  の値は、PCB 材料、レイアウト、環境条件に応じて変化します。 $\theta_{JA}$  の規定値は、4 層の 4 インチ × 3 インチ回路基板に基づいています。ボード構造については JESD51-7 と JESD51-9 を参照してください。詳細については、アプリケーション・ノート AN-617 を参照してください。

$\Psi_{JB}$  はジャンクション-ボード間の熱特性評価パラメータで、単位は °C/W です。パッケージの  $\Psi_{JB}$  は、4 層ボードを使ったモデリングと計算に基づいています。JESD51-12 「Guidelines for Reporting and Using Electronic Package Thermal Information」 には、熱特性評価パラメータは熱抵抗と同じではないと記載されています。 $\Psi_{JB}$  は、熱抵抗 ( $\theta_{JB}$ ) の場合のように 1 つの経路ではなく、複数の熱経路を通過する電力成分を表します。

したがって、 $\Psi_{JB}$ の熱経路には、パッケージ上面からの対流やパッケージからの放射が含まれており、実際のアプリケーションでは  $\Psi_{JB}$  がより有用になります。最大ジャンクション温度 ( $T_J$ ) は、ボード温度 ( $T_B$ ) と消費電力 ( $P_D$ ) から次式を使って計算します。

$$T_J = T_B + (P_D \times \Psi_{JB}) \quad (2)$$

$\Psi_{JB}$  の詳細については、JESD51-8 と JESD51-12 を参照してください。

### 熱抵抗

$\theta_{JA}$  と  $\Psi_{JB}$  は最も厳しい条件での規定であり、表面実装パッケージの場合はデバイスを回路基板にハンダ付けした状態で規定します。 $\theta_{JC}$  は、上面にヒート・シンクの付いた表面実装パッケージのパラメータです。 $\theta_{JC}$  は参考値としてのみの提示です。

表 4. 热抵抗

| Package Type | $\theta_{JA}$ | $\theta_{JC}$ | $\Psi_{JB}$ | Unit |

|--------------|---------------|---------------|-------------|------|

| 8-Lead LFCSP | 40.1          | 27.1          | 17.2        | °C/W |

| 8-Lead SOIC  | 48.5          | 58.4          | 31.3        | °C/W |

### ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能の説明

図 3. LFCSP パッケージ

図 4. ナロー・ボディ SOIC パッケージ

## 端子説明

表 5. 端子説明

| ピン<br>CFG 1 | 名称               | 説明                                                                                                                                                                                                               |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | V <sub>OUT</sub> | 安定化された出力電圧。V <sub>OUT</sub> は、1μF 以上のコンデンサで GND にバイパスしてください。                                                                                                                                                     |

| 2           | SENSE/ADJ        | センス (SENSE)。負荷での実際の出力電圧を測定し、エラー・アンプに供給します。SENSE はできるだけ負荷の近くに接続し、レギュレータの出力と負荷との間の IR 電圧降下の影響を最小限に抑えます。この機能は固定電圧でのみ有効です。調整入力 (ADJ)。外付け抵抗分圧器を使用して、出力電圧を設定します。この機能は調整可能電圧のみで有効です。                                    |

| 3           | GND              | グラウンド。                                                                                                                                                                                                           |

| 4           | NC               | このピンには接続しないでください。                                                                                                                                                                                                |

| 5           | EN/UVLO          | イネーブル入力 (EN)。EN をハイにするとレギュレータがオンになり、ローにするとレギュレータがオフになります。自動スタートアップの場合は、EN を V <sub>IN</sub> に接続してください。プログラマブルな低電圧ロックアウト (UVLO)。プログラマブルな UVLO 機能を使用する場合、上側と下側の閾値はプログラミング抵抗によって決まります。                              |

| 6           | GND              | グラウンド。                                                                                                                                                                                                           |

| 7           | PG               | パワー・グッド。このオープン・ドレイン出力には、V <sub>IN</sub> または V <sub>OUT</sub> との間に外付けのブルアップ抵抗が必要です。デバイスがシャットダウン、電流制限、サーマル・シャットダウンになった場合や、出力が公称出力電圧の 90% を下回った場合には、PG が直ちにローになります。パワー・グッド機能を使用しない場合、このピンはオープンにしてもグラウンドに接続しても構いません。 |

| 8           | V <sub>IN</sub>  | レギュレータの入力電源。V <sub>IN</sub> は、1μF 以上のコンデンサで GND にバイパスしてください。                                                                                                                                                     |

|             | EPAD             | 露出パッド。露出パッドはパッケージ底面にあります。EPAD は熱性能を強化し、パッケージ内部で GND に電気的に接続されています。EPAD は基板のグランド・プレーンに接続することを強く推奨します。                                                                                                             |

## 代表的な性能特性

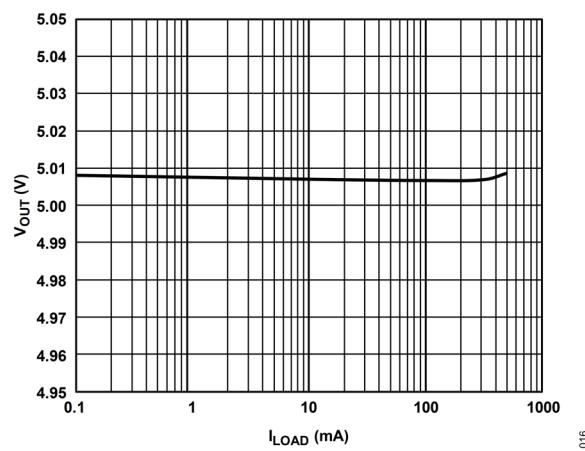

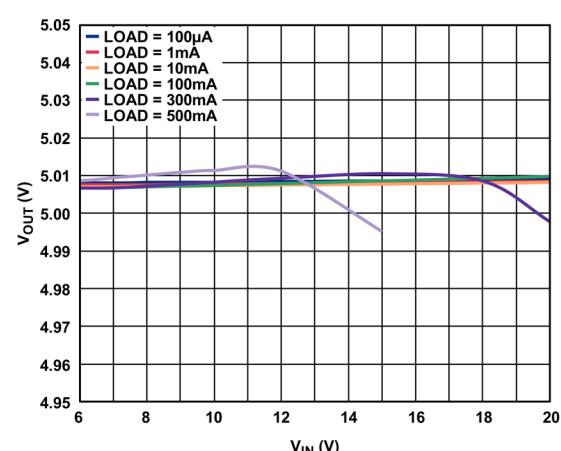

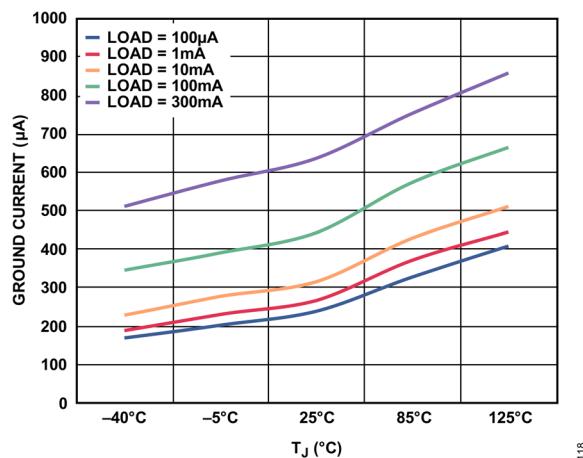

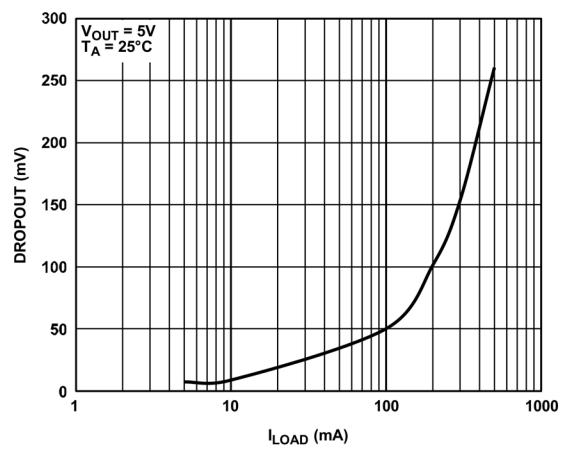

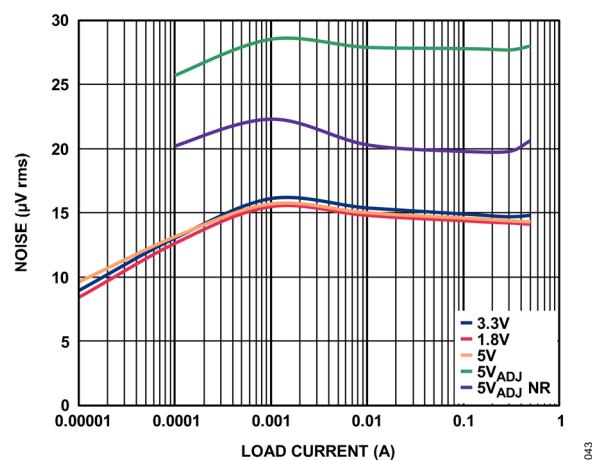

特に指定のない限り、 $V_{IN} = 7.5V$ 、 $V_{OUT} = 5V$ 、 $I_{OUT} = 10mA$ 、 $C_{IN} = C_{OUT} = 1\mu F$ 、 $T_A = 25^{\circ}C$ 。

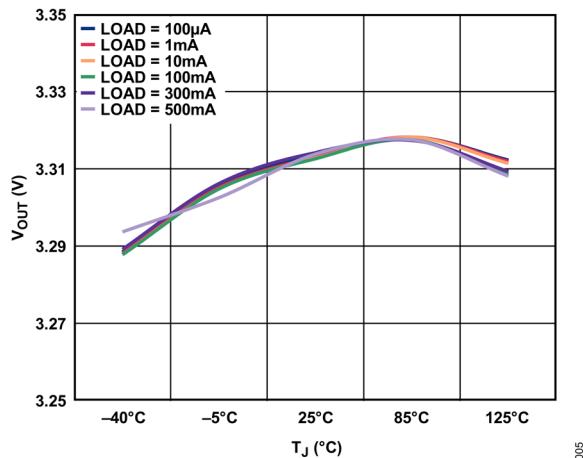

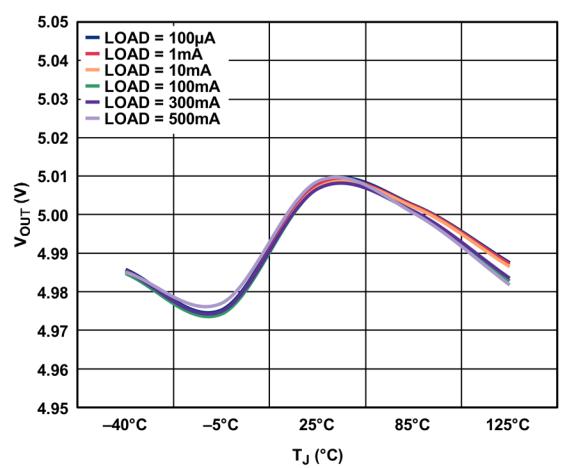

図 5. 出力電圧 ( $V_{OUT}$ ) とジャンクション温度 ( $T_J$ ) の関係、

$V_{OUT} = 3.3V$

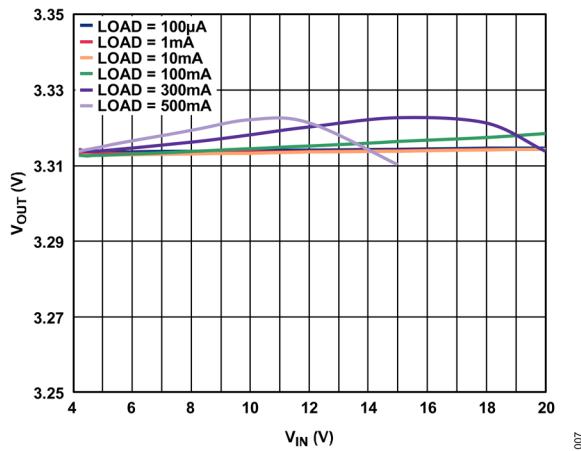

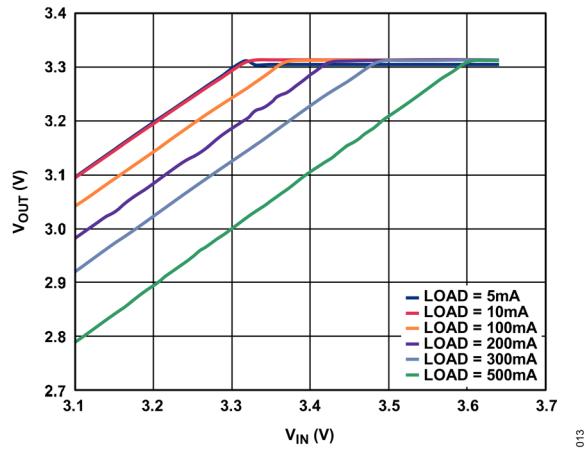

図 7. 出力電圧 ( $V_{OUT}$ ) と入力電圧 ( $V_{IN}$ ) の関係、

$V_{OUT} = 3.3V$

図 6. 出力電圧 ( $V_{OUT}$ ) と負荷電流 ( $I_{LOAD}$ ) の関係、

$V_{OUT} = 3.3V$

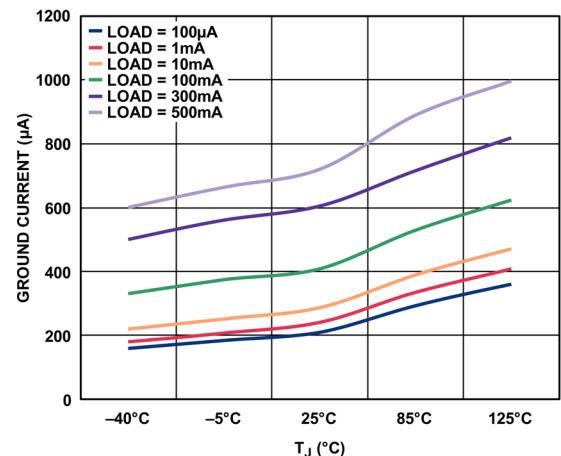

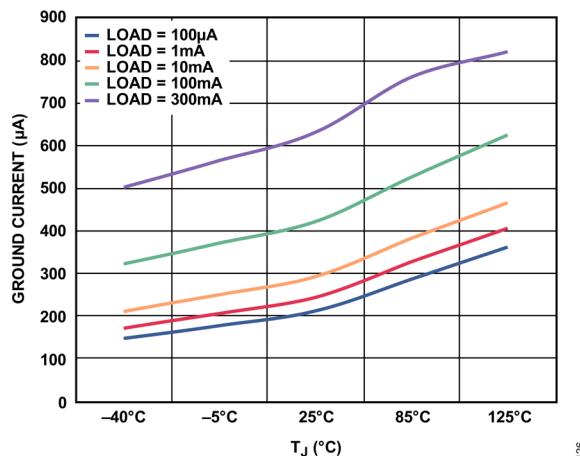

図 8. グラウンド電流 ( $I_{GND}$ ) とジャンクション温度 ( $T_J$ ) の

関係、 $V_{OUT} = 3.3V$

011

012

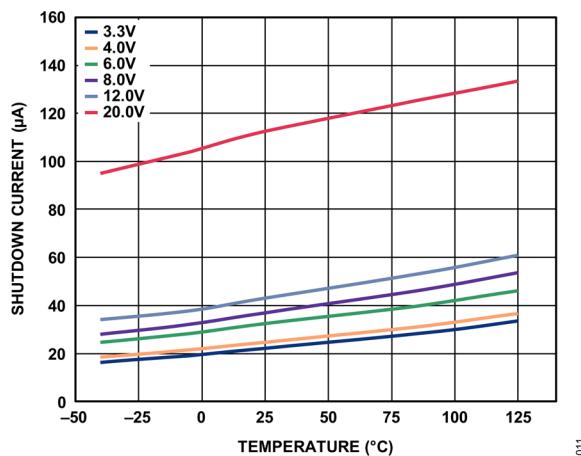

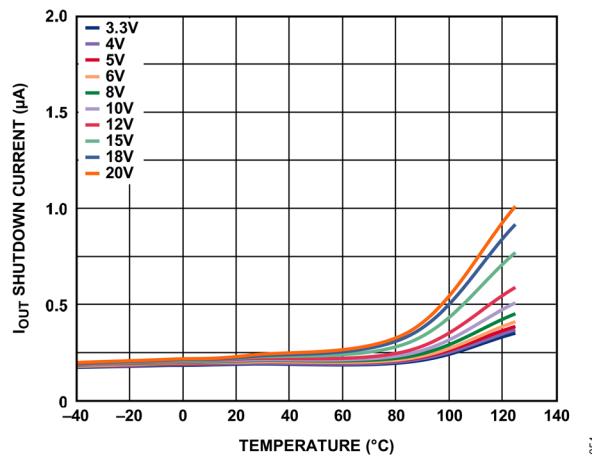

図 9. 様々な入力電圧でのシャットダウン電流 ( $I_{GND-SD}$ ) と 温度 ( $T_J$ ) の関係、 $V_{OUT} = 3.3V$

013

012

図 11. ドロップアウト時の出力電圧 ( $V_{OUT}$ ) と入力電圧 ( $V_{IN}$ ) の関係、 $V_{OUT} = 3.3V$

016

017

図 13. 出力電圧 ( $V_{OUT}$ ) と負荷電流 ( $I_{LOAD}$ ) の関係、 $V_{OUT} = 5V$

図 15. グラウンド電流 ( $I_{GND}$ ) とジャンクション温度 ( $T_J$ ) の関係、 $V_{OUT} = 5V$

図 16. ドロップアウト電圧 ( $V_{DROPOUT}$ ) と負荷電流 ( $I_{LOAD}$ ) の関係、 $V_{OUT} = 5V$

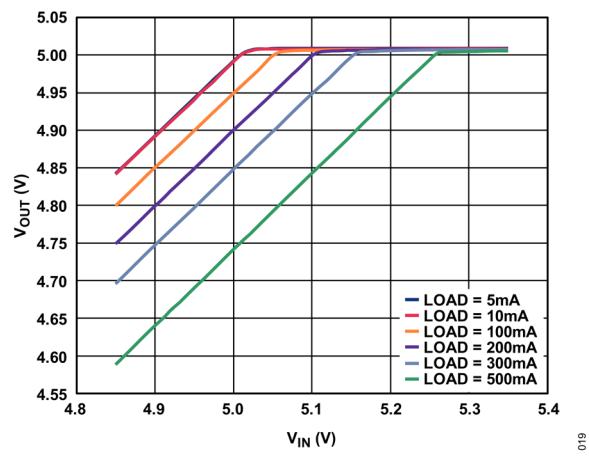

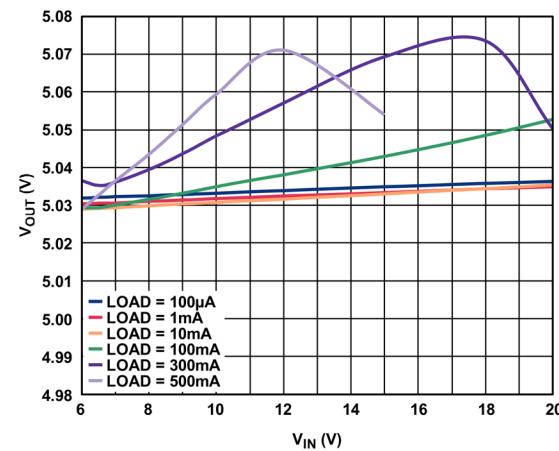

図 17. ドロップアウト時の出力電圧 ( $V_{OUT}$ ) と入力電圧 ( $V_{IN}$ ) の関係、 $V_{OUT} = 5V$

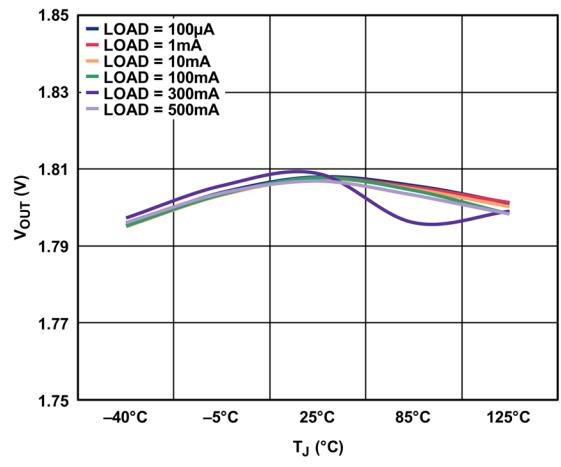

図 18. 出力電圧 ( $V_{OUT}$ ) とジャンクション温度 ( $T_J$ ) の関係、 $V_{OUT} = 1.8V$

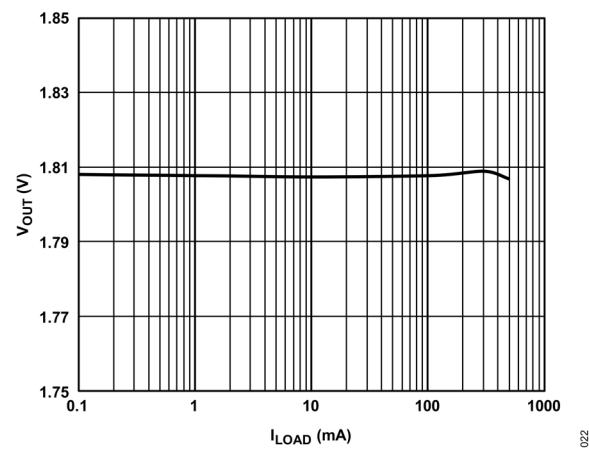

図 19. 出力電圧 ( $V_{OUT}$ ) と負荷電流 ( $I_{LOAD}$ ) の関係、 $V_{OUT} = 1.8V$

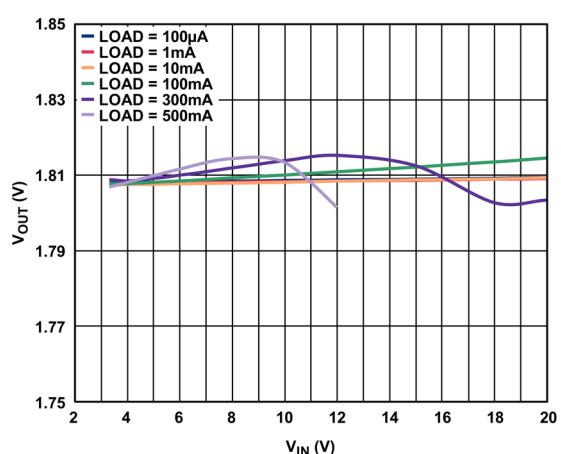

図 20. 出力電圧 ( $V_{OUT}$ ) と入力電圧 ( $V_{IN}$ ) の関係、 $V_{OUT} = 1.8V$

図 21. グラウンド電流 ( $I_{GND}$ ) とジャンクション温度 ( $T_J$ ) の関係、 $V_{OUT} = 1.8V$

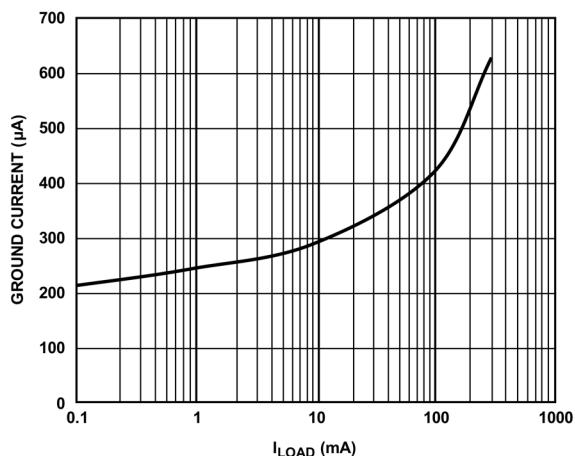

図 22. グラウンド電流 ( $I_{GND}$ ) と負荷電流 ( $I_{LOAD}$ ) の関係、 $V_{OUT} = 1.8V$

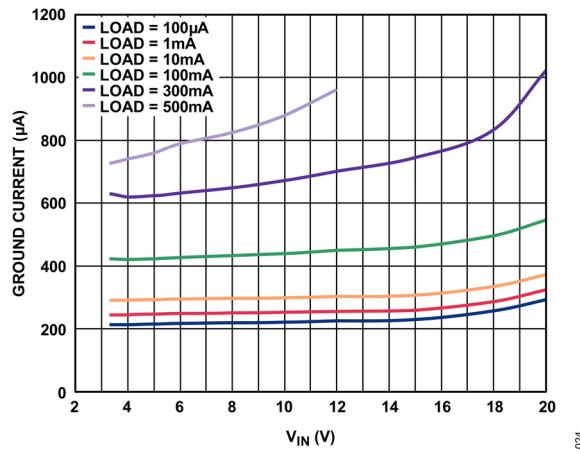

図 23. グラウンド電流 ( $I_{GND}$ ) と入力電圧 ( $V_{IN}$ ) の関係、 $V_{OUT} = 1.8V$

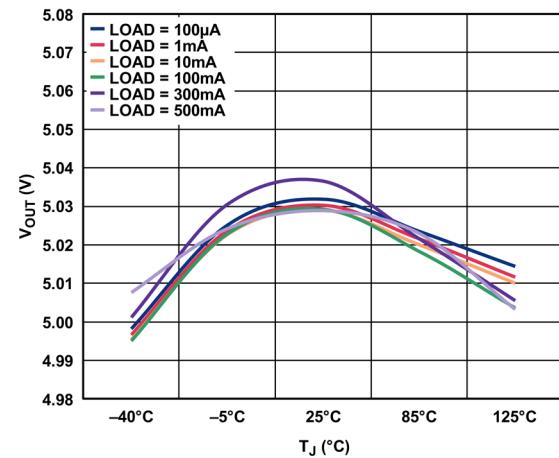

図 24. 出力電圧 ( $V_{OUT}$ ) とジャンクション温度 ( $T_J$ ) の関係、 $V_{OUT} = \text{調整可能 } 5V$

図 25. 出力電圧 ( $V_{OUT}$ ) と負荷電流 ( $I_{LOAD}$ ) の関係、 $V_{OUT} = \text{調整可能 } 5V$

図 26. 出力電圧 ( $V_{OUT}$ ) と入力電圧 ( $V_{IN}$ ) の関係、 $V_{OUT} = \text{調整可能 } 5V$

054

200

043

045

046

047

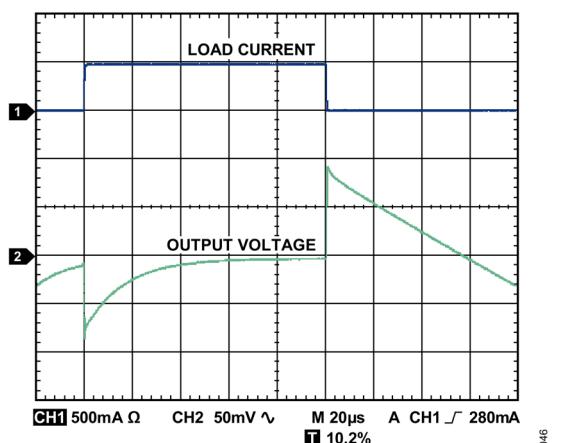

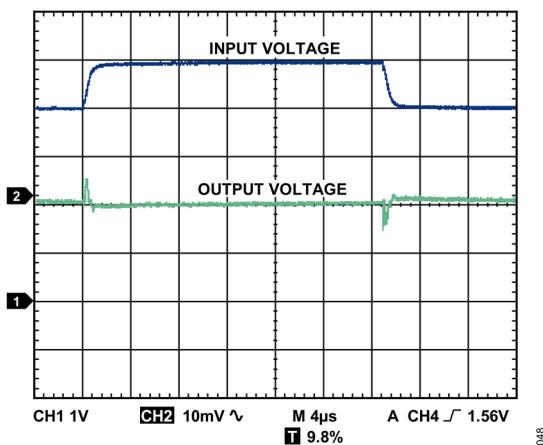

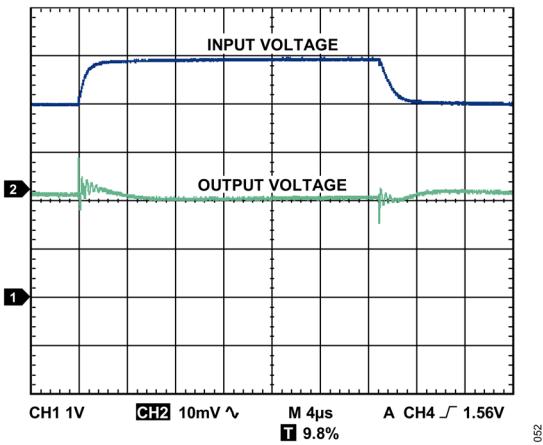

図 33. ライン過渡応答、 $C_{IN} = C_{OUT} = 1\mu F$ 、

$I_{LOAD} = 500mA$ 、 $V_{OUT} = 1.8V$

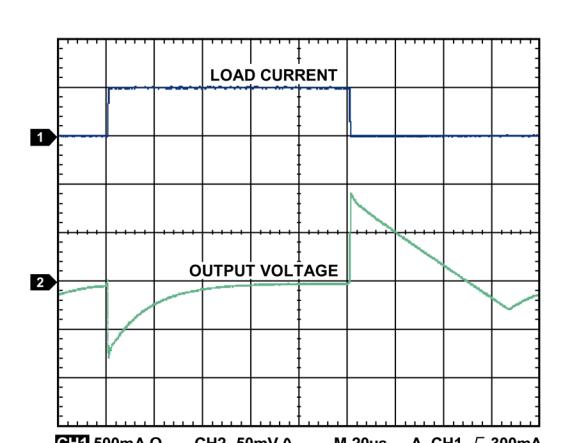

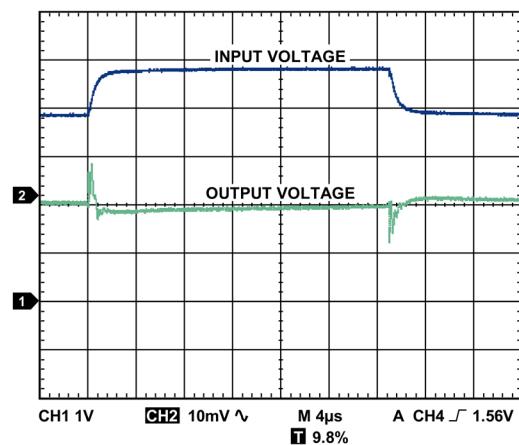

図 34. ライン過渡応答、 $C_{IN} = C_{OUT} = 1\mu F$ 、

$I_{LOAD} = 500mA$ 、 $V_{OUT} = 3.3V$

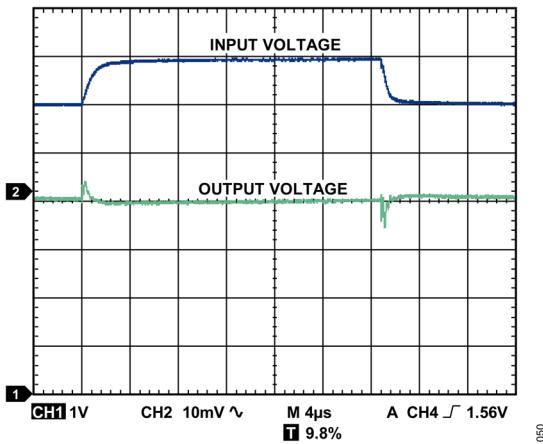

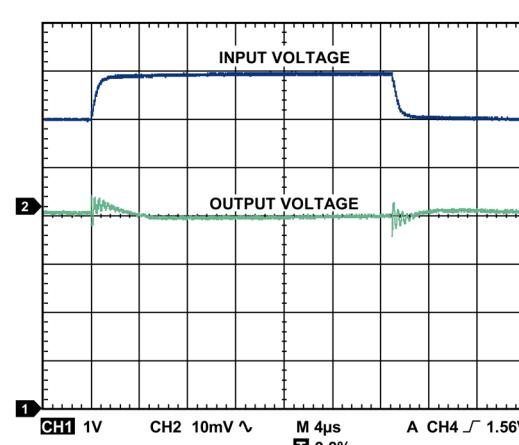

図 35. ライン過渡応答、 $C_{IN} = C_{OUT} = 1\mu F$ 、

$I_{LOAD} = 500mA$ 、 $V_{OUT} = 5V$

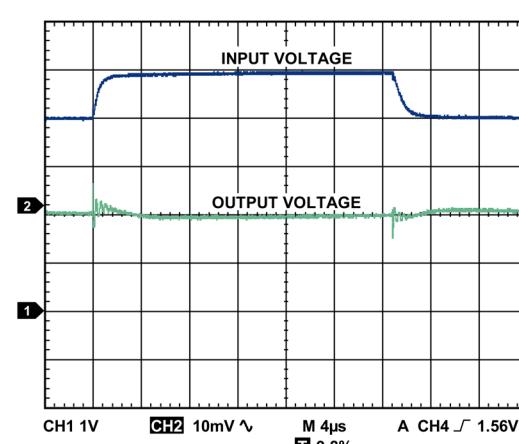

図 36. ライン過渡応答、 $C_{IN} = C_{OUT} = 1\mu F$ 、

$I_{LOAD} = 1mA$ 、 $V_{OUT} = 1.8V$

図 37. ライン過渡応答、 $C_{IN} = C_{OUT} = 1\mu F$ 、

$I_{LOAD} = 1mA$ 、 $V_{OUT} = 3.3V$

図 38. ライン過渡応答、 $C_{IN} = C_{OUT} = 1\mu F$ 、

$I_{LOAD} = 1mA$ 、 $V_{OUT} = 5V$

## 動作原理

ADPL42005 は、4V～20V で動作し、最大 500mA の電流を出力する低静止電流、低ドロップアウトのリニア・レギュレータです。全負荷時に流れる静止電流が 1mA（代表値）と低いため、バッテリ駆動のポータブル機器に最適です。シャットダウン時の消費電流は室温で 40μA（代表値）です。

ADPL42005 は、小型の 1μF セラミック・コンデンサを使用するように最適化されており、優れたトランジメント性能を備えています。

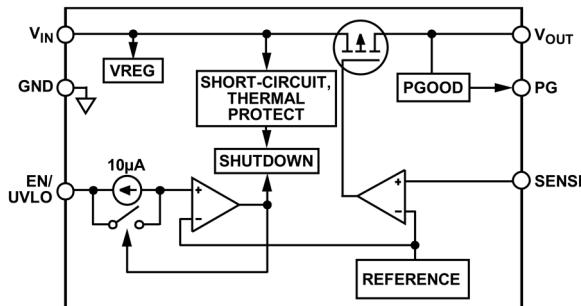

図 39. 固定出力電圧の内部ブロック図

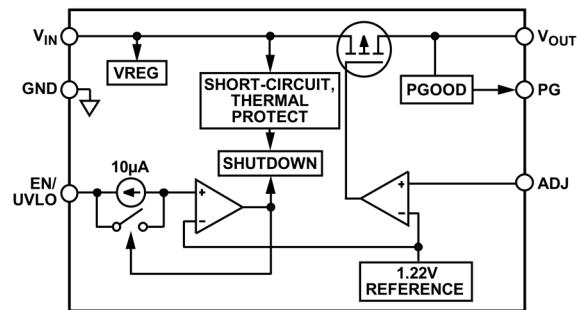

図 40. 調整可能な出力電圧の内部ブロック図

ADPL42005 の内部は、リファレンス、エラー・アンプ、PMOS パス・トランジスタで構成されています。出力電流は、エラー・アンプによって制御される PMOS パス・デバイスを経由して供給されます。エラー・アンプはリファレンス電圧と出力からの帰還電圧を比較して、その差を増幅します。帰還電圧がリファレンス電圧より低いと、PMOS デバイスのゲート電圧が低くなるので、通過する電流が増え、出力電圧が上昇します。帰還電圧がリファレンス電圧より高いと、PMOS デバイスのゲート電圧が高くなるので、通過する電流が減り、出力電圧が低下します。

ADPL42005 では、1.5V～5.0V の範囲の 6 通りの固定出力電圧オプションと、外付けの分圧器により 1.22V～19V の範囲で出力電圧を設定できる調整可能モデルが 1 つ提供されています。出力電圧は、次の式 3 に従って設定されます。

$$V_{OUT} = 1.22V \left( 1 + \frac{R_1}{R_2} \right) \quad (3)$$

図 41. 出力電圧を調整する場合の代表的なアプリケーション図

ADJ ピンの入力電流によって生じる出力電圧誤差を小さくするため、R2 の値は  $200\text{k}\Omega$  未満にします。例えば、R1 と R2 が共に  $200\text{k}\Omega$  の場合、出力電圧は  $2.44\text{V}$  になります。 $25^\circ\text{C}$  での ADJ ピンの入力電流を  $10\text{nA}$ （代表値）とすると、ADJ ピン入力電流によって生じる出力電圧誤差は  $2\text{mV}$ 、すなわち  $0.08\%$  になります。

ADPL42005 では、EN/UVLO ピンを使用して、通常動作状態で  $V_{OUT}$  ピンをイネーブル／ディスエーブルします。EN/UVLO がハイのとき  $V_{OUT}$  はオンになります。EN がローのとき  $V_{OUT}$  はオフになります。自動スタートアップの場合は、EN/UVLO を  $V_{IN}$  に接続します。

ADPL42005 は逆電流保護回路を備えており、出力電圧が入力電圧より高いときに電流が通過素子を逆方向に流れるのを防止します。コンバレータが入力電圧と出力電圧の差を検出します。入力電圧と出力電圧の差が  $55\text{mV}$  を超えると、PFET のボディが  $V_{OUT}$  に切り替わり、オフあるいはオープンになります。言い方を変えると、ゲートが  $V_{OUT}$  に接続されます。

## アプリケーション情報

### 設計ツール

ADPL42005 は設計ツールである LTpowerCAD® と LTspice® でサポートされており、電源設計とシミュレーションのすべてを行うことができます。設計ツールの詳細については、[ADPL42005 の製品ページ](#)を参照してください。

### コンデンサの選択

#### 出力コンデンサ

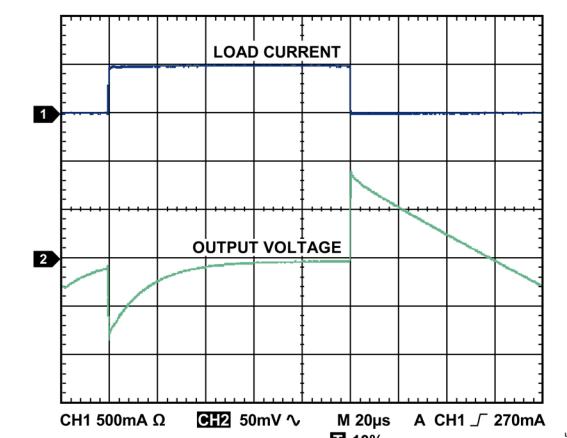

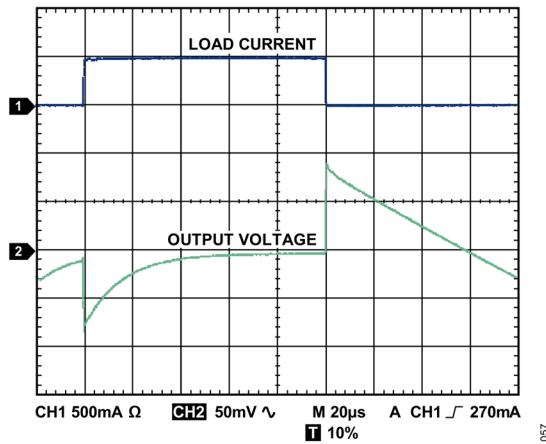

ADPL42005 は、省スペースの小型セラミック・コンデンサで動作するよう設計されていますが、等価直列抵抗 (ESR) 値に注意すれば、一般的に使用される多くのコンデンサでも動作します。出力コンデンサの ESR は、LDO 制御ループの安定性に影響します。ADPL42005 を安定に動作させるには、ESR が  $1\Omega$  以下で最小  $1\mu\text{F}$  のコンデンサの使用を推奨します。負荷電流の変化に対する過渡応答も、出力コンデンサの影響を受けます。大きな値の出力容量を使用すると、負荷電流の大きな変化に対する ADPL42005 の過渡応答を改善することができます。出力容量が  $1\mu\text{F}$  の場合の過渡応答を図 42 に示します。

図 42. 出力の過渡応答 ( $V_{\text{OUT}} = 1.8\text{V}$ ,  $C_{\text{OUT}} = 1\mu\text{F}$ )

### 入力バイパス・コンデンサ

$V_{\text{IN}}$  と GND の間に  $1\mu\text{F}$  のコンデンサを接続すると、特に入力の配線パターンが長い場合やソース・インピーダンスが高い場合に、プリント回路基板 (PCB) レイアウトに対する回路の感度を下げることができます。出力コンデンサで  $1\mu\text{F}$  を超える容量が必要な場合は、これに対応して入力コンデンサの値も増やします。

### プログラマブルな低電圧ロックアウト (UVLO)

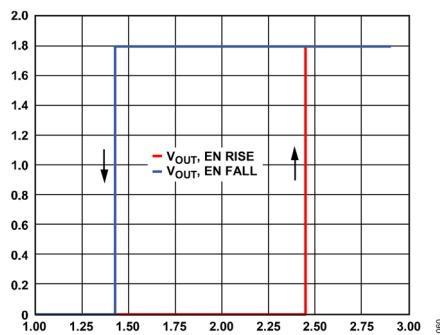

ADPL42005 では、EN/UVLO ピンを使用して、通常動作状態で  $V_{\text{OUT}}$  ピンをイネーブル／ディスエーブルします。図 43 に示すように、EN の電圧が上昇して上側の閾値を上回ると、 $V_{\text{OUT}}$  がオンになります。EN/UVLO の電圧が下降して下側の閾値を下回ると、 $V_{\text{OUT}}$  がオフになります。EN/UVLO 閾値のヒステリシスは、EN/UVLO ピンと直列のテブナン等価抵抗によって決まります。

図 43. EN ピン動作に対する代表的な  $V_{OUT}$  応答

上側と下側の閾値はユーザ・プログラマブルで、2 個の抵抗を使用して設定できます。EN/UVLO ピンの電圧が 1.22V を下回ると、LDO はディスエーブルされます。EN/UVLO ピンの電圧が 1.22V より高く遷移すると、LDO がイネーブルされ、 $10\mu A$  のヒステリシス電流がこのピンから流れで電圧を上昇させ、これにより閾値のヒステリシスが発生します。一般的には、2 つの外付け抵抗で LDO の最小動作電圧をプログラムします。抵抗値  $R_1$  と  $R_2$  は次式によって求めます。

$$R_1 = V_{HYS}/10\mu A$$

$$R_2 = 1.22V \times R_1/(V_{IN} - 1.22V)$$

ここで、

$V_{IN}$  は目的のオン電圧。

$V_{HYS}$  は目的の EN/UVLO ヒステリシス・レベル。

EN/UVLO ピンと直列に抵抗を接続することによってもヒステリシスを実現できます。図 44 に示す例では、イネーブル閾値は 2.44V で、ヒステリシスは 1V です。

図 44. EN ピンの代表的な分圧器

EN/UVLO ピンの代表的なヒステリシスを図 43 に示します。このヒステリシスにより、EN ピンが閾値を通過するときのノイズにより発生するおそれのあるオン／オフ発振が防止されます。

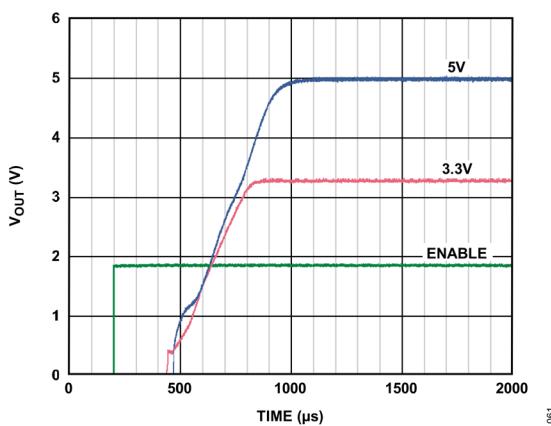

ADPL42005 は内部ソフトスタート機能を使って、出力をイネーブルしたときの突入電流を制限します。3.3V オプションでのスタートアップ時間は、EN のアクティブ閾値を通過してから、出力が最終値の 90% に達するまでの約  $580\mu s$  です。図 45 に示すように、スタートアップ時間は出力電圧の設定値には依存しません。

図 45. 代表的なスタートアップ動作

## パワー・グッド機能

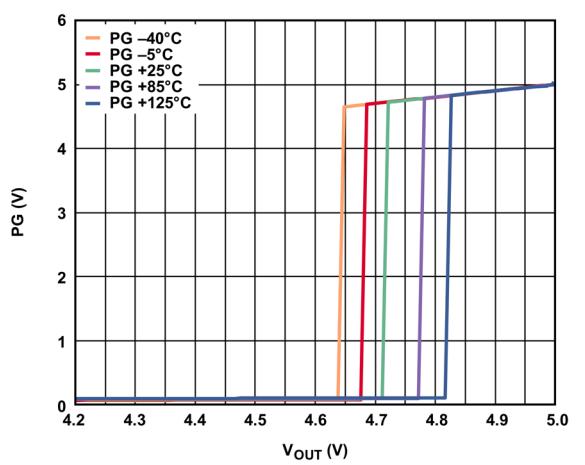

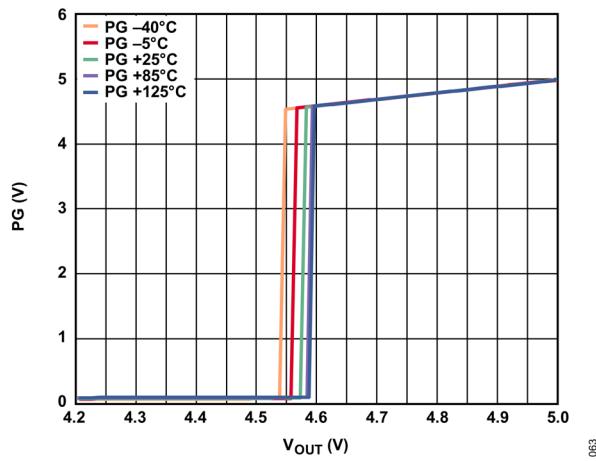

ADPL42005 は、出力の状態を示すパワー・グッド・ピン (PG) を備えています。このオープン・ドレイン出力には、V<sub>IN</sub> または V<sub>OUT</sub> との間に外付けのプルアップ抵抗が必要です。デバイスがシャットダウン・モード、電流制限モード、サーマル・シャットダウンのいずれかになるか、出力が公称出力電圧の 90%を下回ると、パワー・グッド・ピン (PG) は直ちにローになります。ソフトスタート時のパワー・グッド信号の立上がり閾値は、公称出力電圧の 93.5%です。

ADPL42005 の入力電圧が内部 PG トランジスタをオンするのに十分になれば、このオープン・ドレイン出力はローに保たれます。PG トランジスタは、V<sub>OUT</sub> または V<sub>IN</sub> に接続したプルアップ抵抗で終端します。

パワー・グッドの精度は、出力電圧の上昇時は公称レギュレータ出力電圧の 93.5%で、出力電圧の下降時は 90%がトリップ・ポイントです。レギュレータ入力電圧のブラウンアウト (降下) またはグリッッチにより V<sub>OUT</sub> が 90%を下回ると、パワー・グッド信号がオフになります。

通常のパワーダウンでは、V<sub>OUT</sub> が 90%を下回ったときにパワー・グッド信号がローになります。

図 46 と図 47 は、様々な温度での代表的な立上がりと立下がりのパワー・グッド閾値を示しています。

図 46. 代表的なパワー・グッド閾値と温度の関係、V<sub>OUT</sub> 立上がり

図 47. 代表的なパワー・グッド閾値と温度の関係、 $V_{OUT}$  立下がり

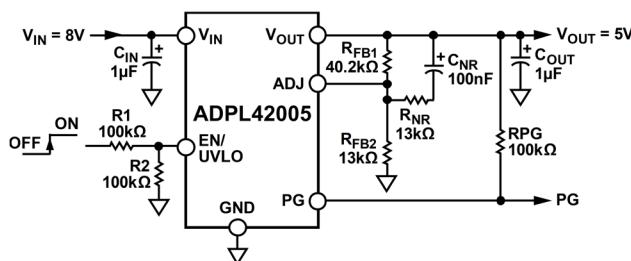

### 調整可能モードの ADPL42005 でのノイズ低減

固定出力の ADPL42005 では、LDO のエラー・アンプをユニティ・ゲインに保ち、リファレンス電圧と出力電圧と同じ値に設定することにより、非常に低い出力ノイズを実現しています。このアーキテクチャは、出力電圧を調整できる LDO では機能しません。出力電圧を調整可能な ADPL42005 は、従来型のアーキテクチャを使用しており、リファレンス電圧が固定でエラー・アンプのゲインは出力電圧の関数です。この従来型の LDO アーキテクチャのデメリットは、出力電圧に比例した出力電圧ノイズが生じることです。

調整可能な LDO の回路をわずかに修正することで、固定出力の ADPL42005 におけるノイズに近いレベルまで出力電圧ノイズを低減させることができます。図 48 に示す回路では、出力電圧設定用の抵抗分圧器に 2 つの部品が追加されています。 $C_{NR}$  と  $R_{NR}$  を  $R_{FB1}$  と並列に追加で接続することで、エラー・アンプの AC ゲインを低減します。 $R_{NR}$  は  $R_{FB2}$  と同じ値を選択します。これにより、エラー・アンプの AC ゲインが約 6dB に制限されます。実際のゲインは、 $R_{NR}$  と  $R_{FB1}$  の並列接続を  $R_{FB2}$  で除算した値です。これにより、エラー・アンプは常にユニティ・ゲインより大きなゲインで動作します。

$C_{NR}$  は、50Hz～100Hz の周波数範囲のリアクタンスが  $R_{FB1} - R_{NR}$  になるものを選定します。これによって、エラー・アンプの AC ゲインが DC ゲインより 3dB 低くなる周波数が定まります。

図 48. 調整可能な LDO のノイズ低減用修正

### 電流制限と熱過負荷保護

ADPL42005 は、過電流保護回路と熱過負荷保護回路により過大な消費電力による損傷から保護されています。ADPL42005 は、出力負荷が 775mA（代表値）に達すると、電流を制限するように設計されています。出力負荷が 775mA を超えると、出力電圧を下げて一定の電流制限値に維持します。

また、ジャンクション温度を最大 150°C（代表値）に制限する熱過負荷保護機能を備えています。過酷な状態（高周囲温度や高消費電力）でジャンクション温度が 150°C を超えると、出力がオフになり、出力電流がゼロまで減少します。ジャンクション温度が 135°C を下回ると、出力が再びオンになり、出力電流は動作値に戻ります。

$V_{OUT}$ とグラウンドの間でハード短絡が発生する場合を考えます。まず、ADPL42005の電流制限により、775mAだけ短絡箇所に流れます。ジャンクションの自己発熱が非常に大きくなつて 150°C を超えると、サーマル・シャットダウン機能が作動して、出力がオフになり、出力電流はゼロまで減少します。ジャンクション温度が下がり 135°C を下回ると、出力がオンになって短絡箇所に 775mA の電流が流れ、ジャンクション温度が再び 150°C を超えます。135°C と 150°C の間で発生するこの熱発振により、775mA と 0mA の間で電流発振が発生します。出力が短絡状態にある限り、この発振は継続します。

電流機能と熱過負荷保護機能は、偶発的な過負荷状態に対してデバイスを保護することを目的としています。信頼性の高い動作を実現するには、ジャンクション温度が 125°C を超えないようにデバイスの消費電力を外部で制限します。

## プリント回路基板レイアウトに関する考慮事項

ADPL42005 のピンに接続する銅の量を増やすことによりパッケージからの放熱を改善することができます。ただし、最終的には効果の限界点に達して、それ以上銅の面積を増やしても放熱を大きく改善できなくなります。

入力コンデンサは  $V_{IN}$  ピンと GND ピンのできるだけ近くに配置します。出力コンデンサは  $V_{OUT}$  ピンと GND ピンのできるだけ近くに配置します。0805 または 0603 サイズのコンデンサと抵抗を使うと、面積が制限されているボード上で最小のフットプリント・ソリューションを実現できます。

図 49. LFCSP の PCB レイアウト例

図 50. SOIC の PCB レイアウト例

## 外形寸法

図 51. 8 ピン、リード・フレーム・チップ・スケール・パッケージ [LFCSP]

3mm × 3mm ボディ、0.75mm パッケージ高 (CP-8-11)

寸法 : mm

PRG-200910

図 52. 8 ピン標準スモール・アウトライン・パッケージ、露出パッド付き [SOIC\_N\_EP]

ナロー・ボディ (RD-8-1)

寸法 : mm

## オーダー・ガイド

表 6. オーダー・ガイド

| MODEL <sup>1</sup>   | TEMPERATURE RANGE | PACKAGE DESCRIPTION            | PACKING QUANTITY | PACKAGE OPTION | MARKING CODE |

|----------------------|-------------------|--------------------------------|------------------|----------------|--------------|

| ADPL42005ACPZ-1.5-R7 | -40°C to +125°C   | 8-Lead LFCSP (3mm x 3mm w/ EP) | Reel, 1500       | CP-8-11        | LXX          |

| ADPL42005ACPZ-1.8-R7 | -40°C to +125°C   | 8-Lead LFCSP (3mm x 3mm w/ EP) | Reel, 1500       | CP-8-11        | LXY          |

| ADPL42005ACPZ-2.5-R7 | -40°C to +125°C   | 8-Lead LFCSP (3mm x 3mm w/ EP) | Reel, 1500       | CP-8-11        | LXZ          |

| ADPL42005ACPZ-3.0-R7 | -40°C to +125°C   | 8-Lead LFCSP (3mm x 3mm w/ EP) | Reel, 1500       | CP-8-11        | LY0          |

| ADPL42005ACPZ-3.3-R7 | -40°C to +125°C   | 8-Lead LFCSP (3mm x 3mm w/ EP) | Reel, 1500       | CP-8-11        | LY1          |

| ADPL42005ACPZ-5.0-R7 | -40°C to +125°C   | 8-Lead LFCSP (3mm x 3mm w/ EP) | Reel, 1500       | CP-8-11        | LY2          |

| ADPL42005ACPZ-R7     | -40°C to +125°C   | 8-Lead LFCSP (3mm x 3mm w/ EP) | Reel, 1500       | CP-8-11        | LY3          |

| ADPL42005ARDZ-1.5-R7 | -40°C to +125°C   | 8-Lead SOIC w/ EP              | Reel, 1000       | RD-8-1         | 200515       |

| ADPL42005ARDZ-1.8-R7 | -40°C to +125°C   | 8-Lead SOIC w/ EP              | Reel, 1000       | RD-8-1         | 200518       |

| ADPL42005ARDZ-2.5-R7 | -40°C to +125°C   | 8-Lead SOIC w/ EP              | Reel, 1000       | RD-8-1         | 200525       |

| ADPL42005ARDZ-3.0-R7 | -40°C to +125°C   | 8-Lead SOIC w/ EP              | Reel, 1000       | RD-8-1         | 200530       |

| ADPL42005ARDZ-3.3-R7 | -40°C to +125°C   | 8-Lead SOIC w/ EP              | Reel, 1000       | RD-8-1         | 200533       |

| ADPL42005ARDZ-5.0-R7 | -40°C to +125°C   | 8-Lead SOIC w/ EP              | Reel, 1000       | RD-8-1         | 420055       |

| ADPL42005ARDZ-R7     | -40°C to +125°C   | 8-Lead SOIC w/ EP              | Reel, 1000       | RD-8-1         | 42005        |

<sup>1</sup> Z = RoHS 準拠製品。

## 出力電圧オプション

| MODEL <sup>1</sup>   | OUTPUT VOLTAGE (V) <sup>2</sup> |

|----------------------|---------------------------------|

| ADPL42005ACPZ-1.5-R7 | 1.5                             |

| ADPL42005ACPZ-1.8-R7 | 1.8                             |

| ADPL42005ACPZ-2.5-R7 | 2.5                             |

| ADPL42005ACPZ-3.0-R7 | 3.0                             |

| ADPL42005ACPZ-3.3-R7 | 3.3                             |

| ADPL42005ACPZ-5.0-R7 | 5                               |

| ADPL42005ACPZ-R7     | Adjustable                      |

| ADPL42005ARDZ-1.5-R7 | 1.5                             |

| ADPL42005ARDZ-1.8-R7 | 1.8                             |

| ADPL42005ARDZ-2.5-R7 | 2.5                             |

| ADPL42005ARDZ-3.0-R7 | 3.0                             |

| ADPL42005ARDZ-3.3-R7 | 3.3                             |

| ADPL42005ARDZ-5.0-R7 | 5                               |

| ADPL42005ARDZ-R7     | Adjustable                      |

<sup>1</sup> Z = RoHS 準拠製品。<sup>2</sup> その他の電圧オプションについては、最寄りのアナログ・デバイセズ販売代理店にお問い合わせください。

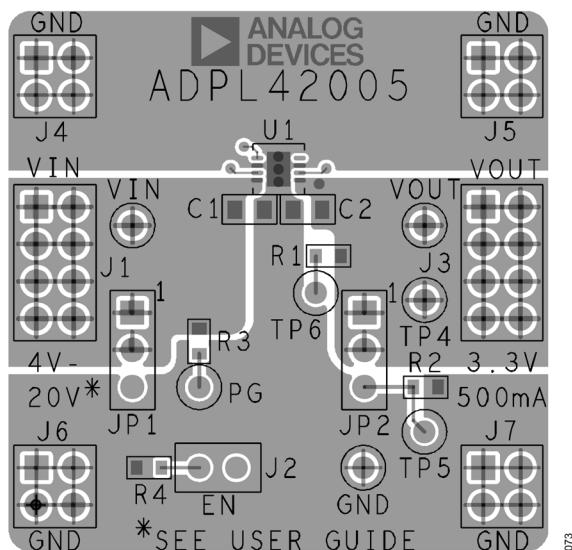

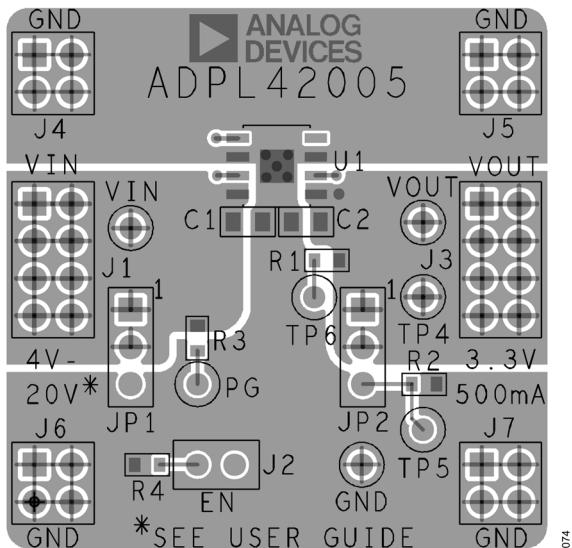

## 評価用ボード

| MODEL <sup>1</sup>   | PACKAGE DESCRIPTION    |

|----------------------|------------------------|

| EVAL-ADPL42005CP-AZ  | LFCSP Evaluation Board |

| EVAL-ADPL42005RD-AZ  | SOIC Evaluation Board  |

| ADPL42005CPZ-REDYKIT | LFCSP REDYKIT          |

| ADPL42005RDZ-REDYKIT | SOIC REDYKIT           |

<sup>1</sup> Z = RoHS 準拠製品。

## 改訂履歴

| 版数 | 改訂日  | 説明   | 改訂ページ |

|----|------|------|-------|

| 0  | 2/25 | 初版発行 | -     |

ここに含まれるすべての情報は、現状のまま提供されるものであり、アナログ・デバイセズはそれに関するいかなる種類の保証または表明も行いません。アナログ・デバイセズは、その情報の利用に関して、また利用によって生じる第三者の特許またはその他の権利の侵害に関して、一切の責任を負いません。仕様は予告なく変更されることがあります。明示か黙示かを問わず、アナログ・デバイセズ製品またはサービスが使用される組み合わせ、機械、またはプロセスに関するアナログ・デバイセズの特許権、著作権、マスクワーク権、またはその他のアナログ・デバイセズの知的財産権に基づくライセンスは付与されません。商標および登録商標は、各社の所有に属します。