## 20 $\mu$ A 自己消費電流、2相動作可能な 20V、8A/10A 全機能内蔵降圧コンバータ

ADPL12008/ADPL12010

### 概要

ADPL12008/ADPL12010 IC は、高集積型同期整流式降圧コンバータであり、ハイサイド・スイッチとローサイド・スイッチを内蔵しています。これらの IC は、3V~20V の入力電圧範囲で、最大 8A/10A を供給するように設計されています。PGOOD 信号により適切な電圧の発生をモニタ可能です。これらの IC は、非常に高いデューティ・サイクルで稼働することによりドロップアウト・モードで動作が可能であるため、ファクトリ・オートメーション・アプリケーションに理想的です。

ADPL12008/ADPL12010 IC には、プログラマブルな出力電圧オプションがあります。1.5MHz と 400kHz が選択可能で、高いスイッチング周波数のために外付け部品を小さくでき、出力リップルを低減できます。SYNC 入力がプログラマブルであるため、3 つのモード（強制パルス幅変調（PWM）モード、超低自己消費電流のスキップ・モード、外部クロックへの同期モード）が可能であり、性能を最適化できます。

ADPL12008/ADPL12010 IC は 2 相動作も可能で、最大 20A に対応した設計ができます。2 個の IC をコントローラおよびターゲットとして接続し、動的な電流分担と 180° 位相差で動作させることができます。

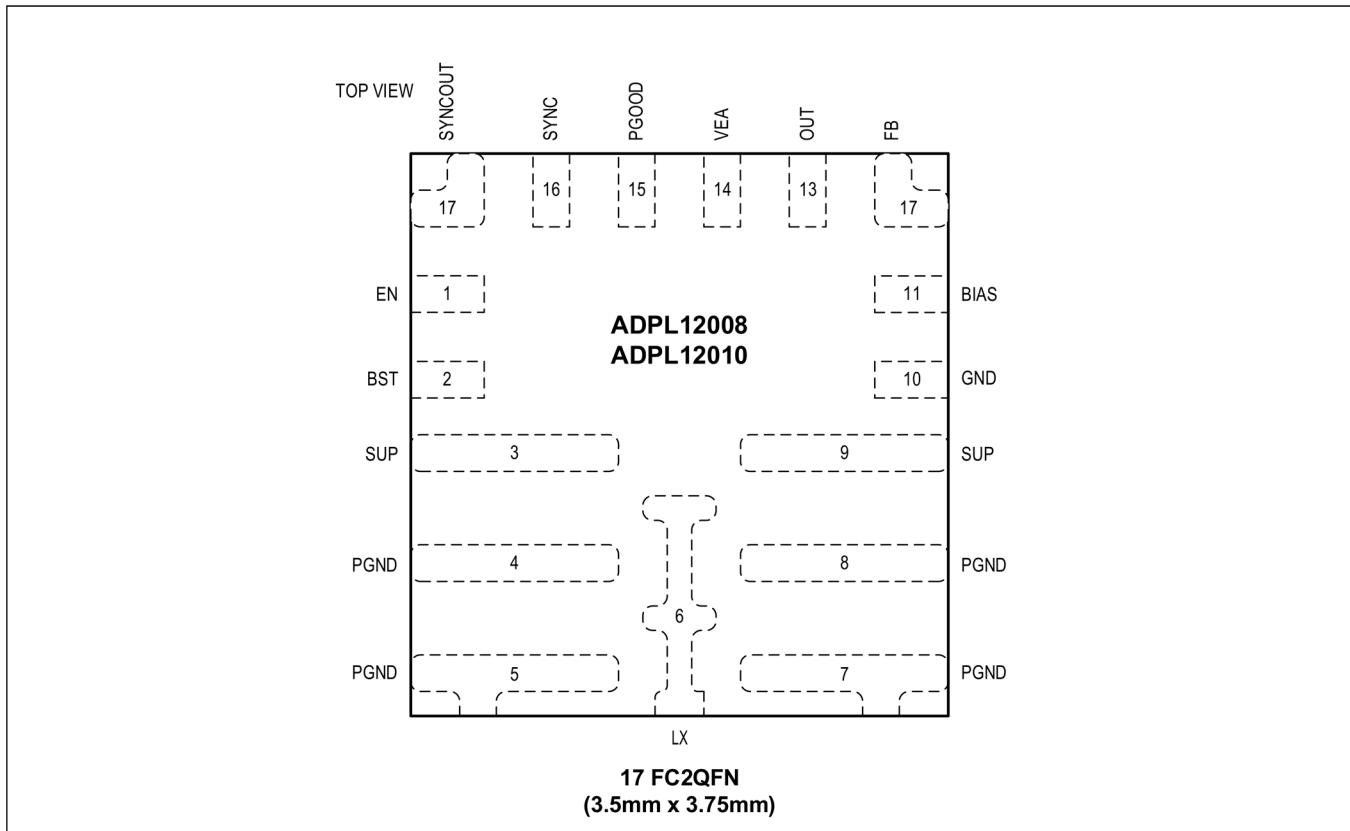

ADPL12008/ADPL12010 IC は小型（3.5mm × 3.75mm）の 17 ピン・フリップチップ・クワッド・フラット・ノーリード（FC2QFN）パッケージで提供されます。これらは、ADPL12005/ADPL12006（5A～6A）製品ファミリとピン互換です。

### アプリケーション

- ファクトリ・オートメーション

- ポイントオブロード

- 分散型 DC 電源システム

- 通信インフラストラクチャ

- 試験および計測

### 利点および特長

- 小型ソリューションの高出力 DC/DC コンバータ

- 動作可能な  $V_{IN}$  範囲 : 3V~20V

- FET を内蔵した同期整流式 DC/DC コンバータ

- 最大出力電流 : 8A/10A

- 400kHz と 1.5MHz の固定周波数オプション

- 固定のソフトスタート時間

- 2.5ms (400kHz の場合)

- 3.5ms (1.5MHz の場合)

- 最小オン時間 : 36ns

- プログラマブルな出力電圧

- 0.8V~10V (400kHz の場合)

- 0.8V~6V (1.5MHz の場合)

- SUP ピンと PGND ピンの対称かつ平衡な配置による電磁干渉（EMI）性能の向上

- 熱強化型の 3.5mm × 3.75mm、17 ピン FC2QFN パッケージ

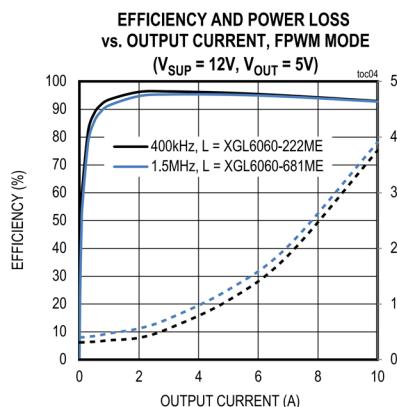

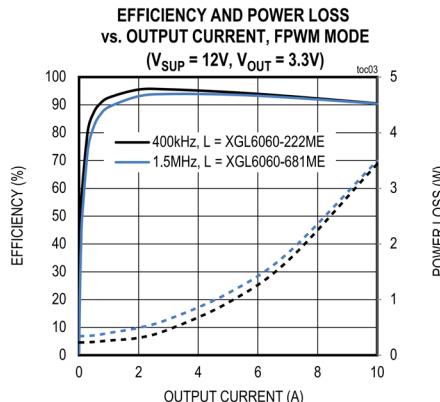

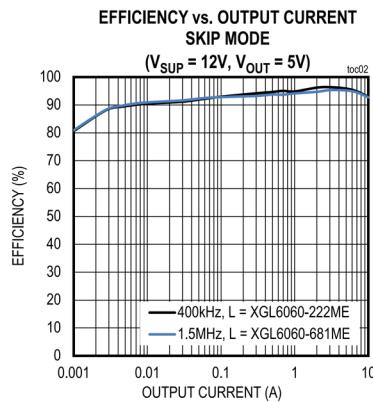

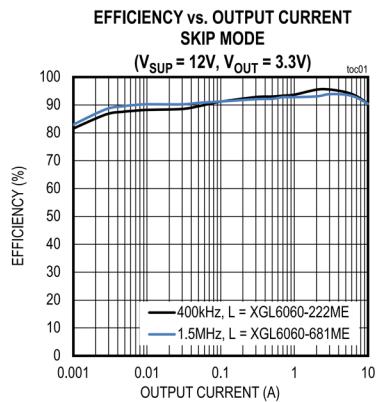

- 負荷レンジ全域で高効率を実現

- スキップ・モードでの自己消費電流 : 20 $\mu$ A

- 12 $V_{IN}$ /3.3 $V_{OUT}$ /400kHz での最大効率 : 95.6%

- 12 $V_{IN}$ /3.3 $V_{OUT}$ /1.5MHz での最大効率 : 93.9%

- 2 相動作により最大 20A 負荷に対応

- 周波数同期の入力／出力

- コントローラとターゲット間で 180° 位相差動作

- 動的電流分担

- 強制 PWM 動作とスキップ・モード動作

- 低ドロップアウト動作

- パワー・グッド・インジケータ

- 過熱および短絡に対する保護

- 動作ジャンクション温度範囲 : -40°C~+150°C

- スケーラブルな電力ソリューション

- ADPL12005/ADPL12006 とフットプリント互換

オーダー情報はデータシート末尾に記載されています。

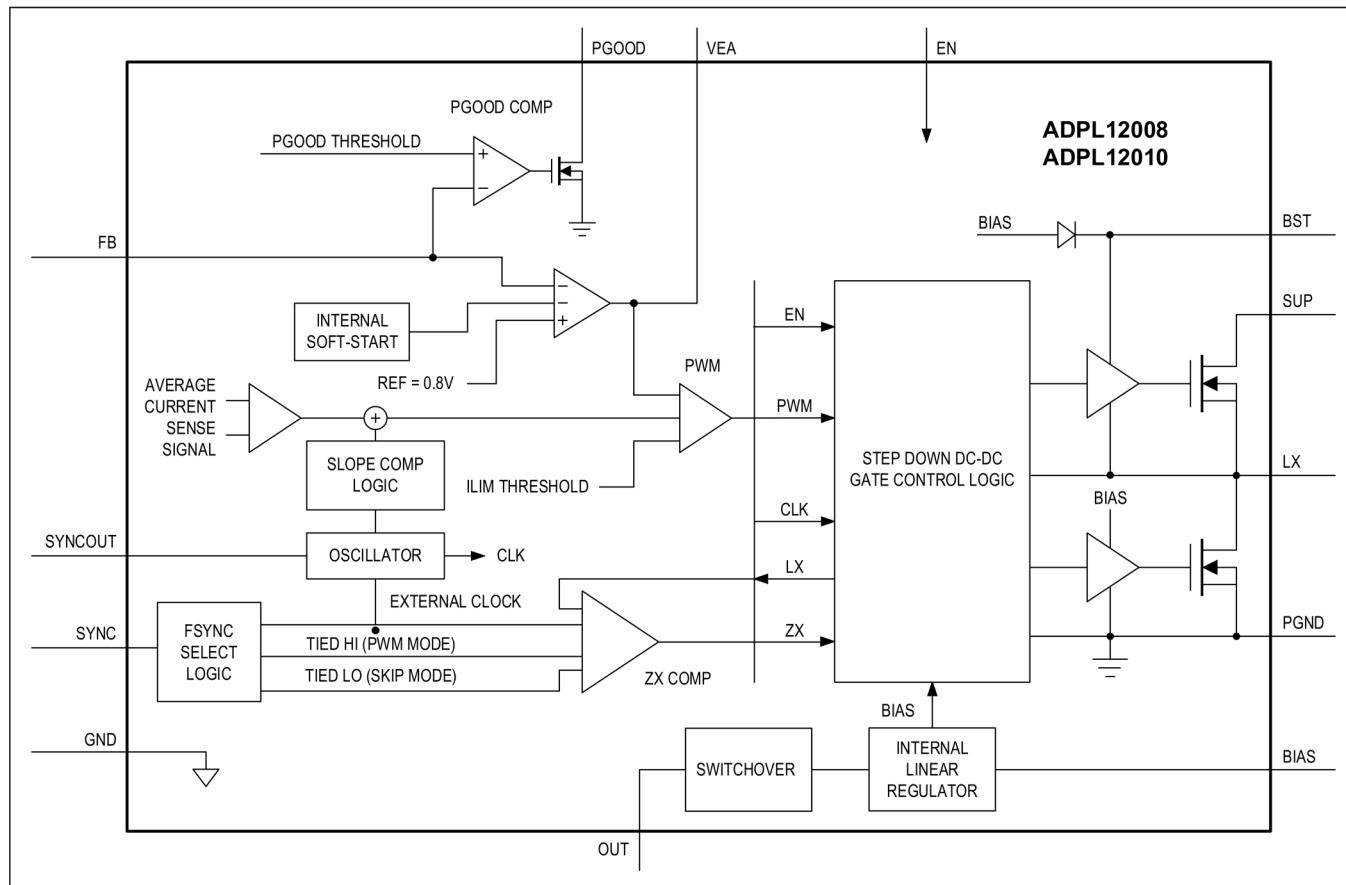

## 簡略化したブロック図

## 目次

|                        |    |

|------------------------|----|

| 概要                     | 1  |

| アプリケーション               | 1  |

| 利点および特長                | 1  |

| 絶対最大定格                 | 4  |

| パッケージ情報                | 4  |

| 電気的特性                  | 5  |

| 標準動作特性                 | 7  |

| ピン配置                   | 9  |

| 端子説明                   | 10 |

| 詳細説明                   | 11 |

| リニア・レギュレータ出力 (BIAS)    | 11 |

| 同期入力 (SYNC)            | 11 |

| イネーブル入力 (EN)           | 11 |

| ソフトスタート                | 11 |

| 短絡保護                   | 11 |

| パワー・グッド・インジケータ (PGOOD) | 11 |

| サーマル・シャットダウン保護         | 12 |

| デュアルフェーズ動作             | 12 |

| 2相構成での低 $I_Q$ 動作       | 13 |

| アプリケーション情報             | 14 |

| 出力電圧の設定                | 14 |

| 入力コンデンサ                | 14 |

| インダクタの選択               | 15 |

| 出力コンデンサ                | 15 |

| PCB レイアウトのガイドライン       | 16 |

| 標準アプリケーション回路           | 18 |

| オーダー情報                 | 19 |

**絶対最大定格**

|                         |                   |

|-------------------------|-------------------|

| SUP、EN～PGND             | -0.3V～+22V        |

| BST～LX                  | -0.3V～+2.2V       |

| BST～BIAS                | -0.3V～+22V        |

| BST～PGND                | -0.3V～+24V        |

| LX～PGND                 | -0.3V～SUP + 0.3V  |

| SYNC、SYNCOOUT、PGOOD～GND | -0.3V to 6V       |

| FB、VEA～GND              | -0.3V～BIAS + 0.3V |

| OUT～GND                 | -0.3V～16V         |

| PGND～GND                | -0.3V～0.3V        |

|                                                                                |                                 |

|--------------------------------------------------------------------------------|---------------------------------|

| BIAS～GND                                                                       | -0.3V～+2.2V                     |

| LX 連続実効電流                                                                      | 10A                             |

| SUP 連続実効電流                                                                     | 5A                              |

| ESD 保護（人体モデル）                                                                  | $\pm 2kV$                       |

| 連続消費電力 ( $T_A = +70^\circ C$ 、 $+70^\circ C$ を超えると 37mW/ $^\circ C$ でディレーティング) | 2963mW                          |

| 動作ジャンクション温度範囲                                                                  | -40 $^\circ C$ ～+150 $^\circ C$ |

| 保管温度範囲                                                                         | -65 $^\circ C$ ～+150 $^\circ C$ |

| リード温度（ハンダ処理 10 秒）                                                              | +300 $^\circ C$                 |

上記の**絶対最大定格**を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

**パッケージ情報**

|                                                       |                           |

|-------------------------------------------------------|---------------------------|

| Package Code                                          | F173A3F+1F                |

| Outline Number                                        | <a href="#">21-100699</a> |

| Land Pattern Number                                   | <a href="#">90-100239</a> |

| <b>Thermal Resistance, Single-Layer Board:</b>        |                           |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 38.6 $^\circ C/W$         |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 7.7 $^\circ C/W$          |

| <b>Thermal Resistance, Four-Layer Board:</b>          |                           |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 27 $^\circ C/W$           |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 8.5 $^\circ C/W$          |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、<https://www.analog.com/jp/design-center/packaging-quality-symbols-footprints/package-index.html> で確認してください。パッケージ・コードの「+」、「#」、「-」は RoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、<https://www.analog.com/jp/technical-articles/thermal-characterization-of-ic-packages.html> を参照してください。

**電気的特性**

(特に指定のない限り、 $V_{SUP} = V_{EN} = 14V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 。代表値は、特に指定のない限り、 $T_A = +25^{\circ}C$ での通常条件下の値 (Note 1、Note 2 参照)。)

| PARAMETER                                        | SYMBOL                | CONDITIONS                                                                | MIN               | TYP   | MAX   | UNITS |

|--------------------------------------------------|-----------------------|---------------------------------------------------------------------------|-------------------|-------|-------|-------|

| Supply Voltage Range                             | $V_{SUP}$             |                                                                           | 3                 | 20    |       | V     |

| Supply Current                                   | $I_{SUP\_SHDN}$       | $V_{EN} = 0, T_A = +25^{\circ}C$                                          |                   | 4     | 6     | µA    |

|                                                  | $I_{SUP}$             | $V_{EN} = \text{high}, V_{OUT} = 3.3V, \text{no load, switching}$         |                   | 20    |       |       |

| SUP Undervoltage Lockout                         |                       | Rising                                                                    | 2.9               | 3.0   | 3.2   | V     |

|                                                  |                       | Falling                                                                   | 2.6               | 2.7   | 2.9   |       |

| BIAS Voltage                                     |                       | $+2.5V \leq V_{SUP} \leq +20V$                                            |                   | 1.8   |       | V     |

| BIAS Undervoltage Lockout                        | $V_{BIAS\_UVLO}$      | Rising                                                                    | 1.58              | 1.63  | 1.68  | V     |

|                                                  | $V_{BIAS\_UVLO\_HYS}$ | Hysteresis                                                                |                   | 50    |       | mV    |

| <b>BUCK CONVERTER</b>                            |                       |                                                                           |                   |       |       |       |

| Adjustable Output-Voltage Range                  |                       | $f_{SW} = 1.5MHz$                                                         | 0.8               | 6     |       | V     |

|                                                  |                       | $f_{SW} = 400kHz$                                                         | 0.8               | 10    |       |       |

| FB Voltage Accuracy                              | $V_{FB\_PWM}$         | PWM mode, no load                                                         | 0.788             | 0.800 | 0.812 | V     |

| FB Leakage Current                               | $I_{FB}$              | $V_{FB} = 0.8V, T_A = +25^{\circ}C$                                       |                   | 100   |       | nA    |

| High-Side Switch On Resistance                   | $R_{DSON\_HS}$        | $V_{BIAS} = 1.8V, I_{LX} = 5A$                                            |                   | 26    | 53    | mΩ    |

| Low-Side Switch On Resistance                    | $R_{DSON\_LS}$        | $V_{BIAS} = 1.8V, I_{LX} = 5A$                                            |                   | 13    | 26    | mΩ    |

| High-Side Switch Current-Limit Threshold         | $I_{LIM}$             | ADPL12008                                                                 | 10                | 12    | 14    | A     |

|                                                  |                       | ADPL12010                                                                 | 11.9              | 14    | 16    |       |

| Low-Side Switch Negative Current-Limit Threshold | $I_{NEG}$             |                                                                           |                   | -4    |       | A     |

| LX Leakage Current                               | $I_{LX\_LKG}$         | $V_{SUP} = 20V, V_{LX} = 0V \text{ or } V_{LX} = 20V, T_A = +25^{\circ}C$ | -5                | 5     |       | µA    |

| Soft-Start Ramp Time                             | $t_{SS}$              | $f_{SW} = 1.5MHz$                                                         |                   | 3.5   |       | ms    |

|                                                  |                       | $f_{SW} = 400kHz$                                                         |                   | 2.5   |       |       |

| Minimum On-Time                                  | $T_{ON}$              | (See Note 3)                                                              |                   | 36    | 65    | ns    |

| Maximum Duty Cycle                               |                       | Dropout mode                                                              | 96                |       |       | %     |

| <b>SWITCHING FREQUENCY</b>                       |                       |                                                                           |                   |       |       |       |

| PWM Switching Frequency                          | $f_{SW}$              | $f_{SW} = 1.5MHz$                                                         | 1.375             | 1.500 | 1.625 | MHz   |

|                                                  |                       | $f_{SW} = 400kHz$                                                         | 360               | 400   | 440   | kHz   |

| SYNC External Clock Frequency                    | $f_{SYNC}$            | $f_{SW} = 1.5MHz$                                                         |                   | 1.215 | 1.845 | MHz   |

|                                                  |                       | $f_{SW} = 400kHz$                                                         | 360               | 600   |       | kHz   |

| <b>PGOOD OUTPUT</b>                              |                       |                                                                           |                   |       |       |       |

| PGOOD Threshold                                  | $V_{PGOOD\_R}$        | Percentage of $V_{OUT}$ , rising                                          | 92                | 94    | 96    | %     |

|                                                  | $V_{GOOD\_F}$         | Percentage of $V_{OUT}$ , falling                                         | 91                | 93    | 95    |       |

| PGOOD Debounce                                   | $T_{DEB}$             | PWM mode, falling                                                         | $f_{SW} = 1.5MHz$ | 70    |       | µs    |

|                                                  |                       |                                                                           | $f_{SW} = 400kHz$ | 50    |       |       |

|                                                  |                       | PWM mode, rising                                                          | $f_{SW} = 1.5MHz$ | 140   |       | µs    |

(特に指定のない限り、 $V_{SUP} = V_{EN} = 14V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 。代表値は、特に指定のない限り、 $T_A = +25^{\circ}C$ での通常条件下の値 (Note 1、Note 2 参照)。)

| PARAMETER                    | SYMBOL           | CONDITIONS                                   | MIN | TYP | MAX | UNITS       |

|------------------------------|------------------|----------------------------------------------|-----|-----|-----|-------------|

|                              |                  | $f_{SW} = 400kHz$                            | 100 |     |     |             |

| PGOOD High-Leakage Current   | $I_{PGOOD\_LKG}$ | $T_A = +25^{\circ}C$                         |     | 1   |     | $\mu A$     |

| PGOOD Low-Voltage Level      | $V_{PGOOD\_LOW}$ | Sinking 1mA                                  |     | 0.4 |     | V           |

| <b>LOGIC LEVELS</b>          |                  |                                              |     |     |     |             |

| EN High-Voltage Level        | $V_{EN\_HIGH}$   |                                              | 1.2 |     |     | V           |

| EN Low-Voltage Level         | $V_{EN\_LOW}$    |                                              |     | 0.5 |     | V           |

| EN Input Current             | $I_{EN}$         | $V_{EN} = V_{SUP} = 20V, T_A = +25^{\circ}C$ |     | 1   |     | $\mu A$     |

| SYNC High-Voltage Level      | $V_{SYNC\_HIGH}$ |                                              | 1.4 |     |     | V           |

| SYNC Low-Voltage Level       | $V_{SYNC\_LOW}$  |                                              |     | 0.4 |     | V           |

| SYNC Input Current           | $I_{IN,SYNC}$    | $T_A = +25^{\circ}C$                         |     | 1   |     | $\mu A$     |

| SYNCOUT Output-Voltage Level | $V_{SYNCOUT}$    | No load                                      | 2.6 | 3.3 | 3.9 | V           |

| <b>THERMAL PROTECTION</b>    |                  |                                              |     |     |     |             |

| Thermal Shutdown             | $T_{SHDN}$       |                                              | 175 |     |     | $^{\circ}C$ |

| Thermal Shutdown Hysteresis  | $T_{SHDN\_HYS}$  |                                              | 20  |     |     | $^{\circ}C$ |

Note 1 : 全ユニットを $+25^{\circ}C$ で 100% 製品テストしています。温度限界は全て設計と特性評価により裏付けられています。

Note 2 : このデバイスは、 $T_J = +125^{\circ}C$ で 95,000 時間、 $T_J = +150^{\circ}C$ で 5,000 時間、連続動作するように設計されています。

Note 3 : これらの仕様については製品テストを行っていませんが、設計により裏付けられています。

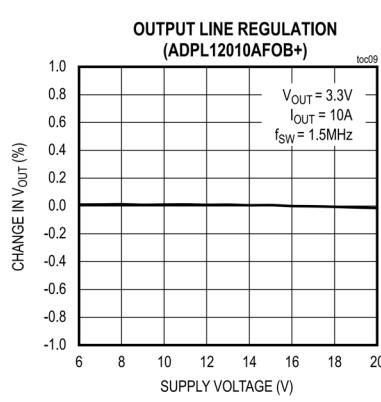

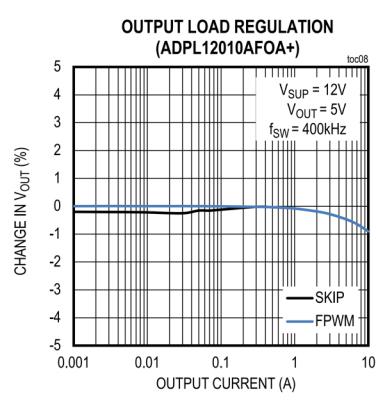

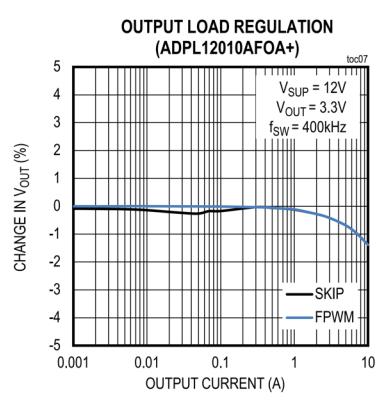

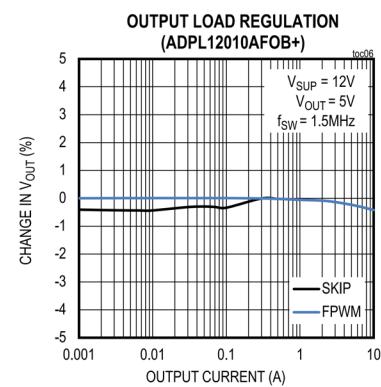

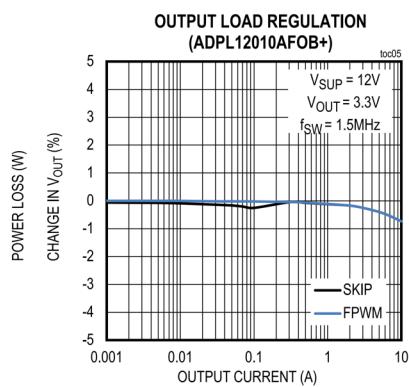

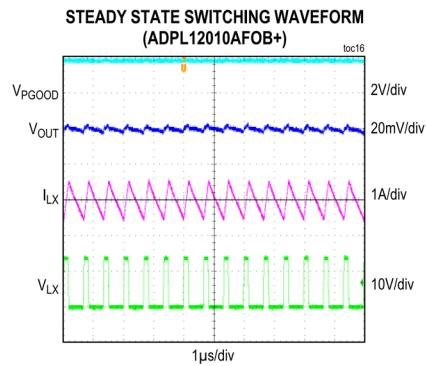

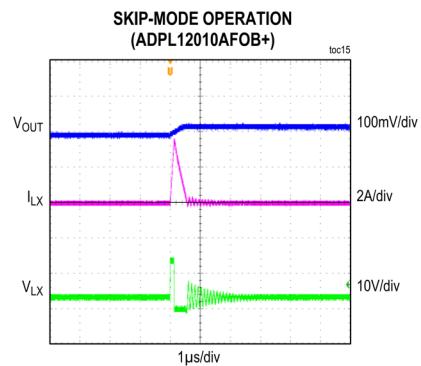

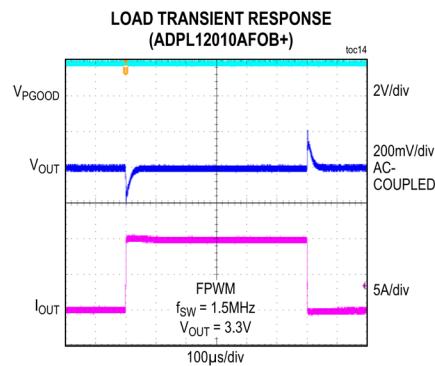

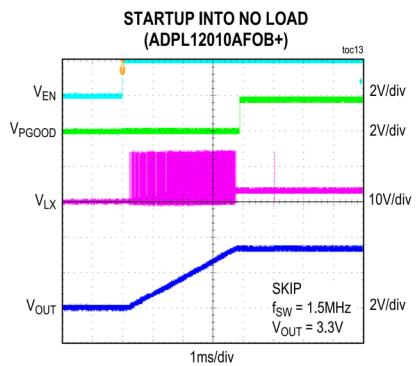

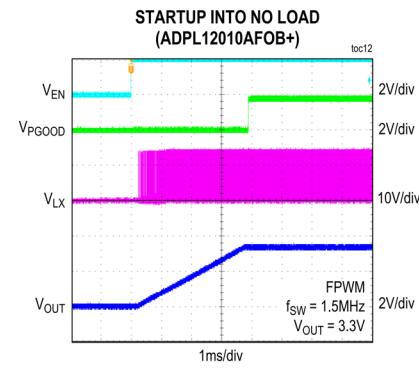

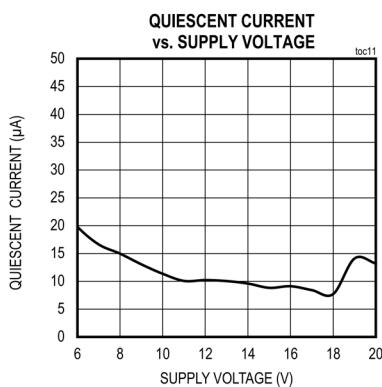

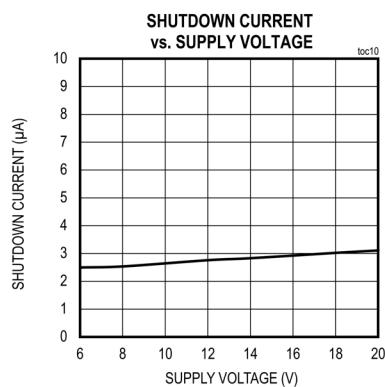

## 標準動作特性

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ )

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ )

## ピン配置

## 端子説明

| ピン   | 名称      | 機能                                                                                                                                                                                                                  |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | EN      | 高電圧対応イネーブル入力。EN をハイにすると降圧コンバータが有効化されます。                                                                                                                                                                             |

| 2    | BST     | ハイサイド・ゲート・ドライバ電源。BST と LX の間に 0.1µF のセラミック・コンデンサを接続します。                                                                                                                                                             |

| 3    | SUP     | IC の入力側電源および内蔵ハイサイド・スイッチ入力電源。0.1µF と 4.7µF のセラミック・コンデンサを使用して、SUP から PGND にできるだけ近くでバイパスします。両方の SUP ピンは内部で接続されています。                                                                                                   |

| 4, 5 | PGND    | 電源グラウンド。全ての PGND ピンを相互に接続します。                                                                                                                                                                                       |

| 6    | LX      | 降圧インダクタの接続。インダクタを LX と降圧出力の間に接続します。IC が無効化されている間、LX は高インピーダンスになります。                                                                                                                                                 |

| 7, 8 | PGND    | 電源グラウンド。全ての PGND ピンを相互に接続します。                                                                                                                                                                                       |

| 9    | SUP     | IC の入力側電源および内蔵ハイサイド・スイッチ入力電源。0.1µF と 4.7µF のセラミック・コンデンサを使用して、SUP から PGND にできるだけ近くでバイパスします。両方の SUP ピンは内部で接続されています。                                                                                                   |

| 10   | GND     | アナログ・グラウンド。GND と PGND はスター接続で PCB のグランド・プレーンに接続します。                                                                                                                                                                 |

| 11   | BIAS    | 1.8V 内部リニア・レギュレータ出力。最小 2.2µF のセラミック・コンデンサを使用して、BIAS をグラウンドに接続します。                                                                                                                                                   |

| 12   | FB      | 帰還入力。OUT と GND の間に配置した抵抗分圧器に FB を接続して、0.8V~10V の範囲で出力電圧を調整します。                                                                                                                                                      |

| 13   | OUT     | 出力電圧検出入力。降圧コンバータは OUT を使用して出力電圧を検出します。                                                                                                                                                                              |

| 14   | VEA     | 内部電圧ループのエラー・アンプ出力。2 相動作の場合には、コントローラとターゲットの VEA を相互に接続します。単相動作の場合には VEA はオープンにします。                                                                                                                                   |

| 15   | PGOOD   | オープンドレインのパワー・グッド出力。降圧出力電圧がレギュレーション電圧の 93%（代表値）より下がると、PGOOD はローになります。降圧出力電圧がレギュレーション電圧の 94%（代表値）より高くなると、PGOOD は高インピーダンスになります。ソフトスタート中は、PGOOD がローにアサートされます。PGOOD を BIAS または 5.5V より低い正電圧にプルアップ抵抗で接続すると、降圧出力の状況を提示します。 |

| 16   | SYNC    | 外部クロック同期入力。SYNC をローに接続すると、スキップ・モード動作が有効になります。SYNC をハイに接続すると、強制 PWM 動作に設定されます。有効な外部クロック信号を SYNC に接続すると、外部クロック同期が有効となります。                                                                                             |

| 17   | SYNCOUT | 180°位相差クロック出力。2 相動作時の場合には、SYNCOUT を BIAS に接続してそのデバイスをターゲットに設定し、コントローラの SYNCOUT をターゲットの SYNC に接続します。単相動作の場合には SYNC はオープンにします。                                                                                        |

## 詳細説明

ADPL12008/ADPL12010 IC は、高集積型同期整流式降圧コンバータであり、ハイサイド・スイッチとローサイド・スイッチを内蔵しています。この IC は3V~20Vの電圧の入力を受けて8A/10Aの電流を供給するよう設計されており、無負荷状態の自己消費電流はわずか20 $\mu$ Aです。PGOOD 信号により適切な電圧の発生をモニタ可能です。これらの IC は、非常に高いデューティ・サイクルで稼働することによりドロップアウト・モードで動作が可能であるため、ファクトリ・オートメーション・アプリケーションに理想的です。

ADPL12008/ADPL12010 IC では、外付け抵抗分圧器によって出力電圧を調整できます。周波数は内部で 1.5MHz オプションと 400kHz オプションに固定されているので、使用する外付け部品を少なくし、また、出力リップルを抑制できます。SYNC に信号を与えることにより、IC をスキップ・モード、FPWM（強制パルス幅変調モード）、または外部クロックへの同期動作に設定できます。オン時間が最短 36ns である平均電流モード制御により、サイクル・スキップなしで入出力電圧に大きな降圧比が得られます。

ADPL12008/ADPL12010 IC は 2 相モードに設定することも可能で、その場合は最大 20A の負荷を供給できます。平均電流モード制御により、ノイズ耐性とトランジエント時の正確な動的電流分担が実現されます。

FC2QFN パッケージを使用しているため、パッケージの寄生インピーダンスが低く熱特性が良好です。SUP と PGND のピン配置は対称になっているため、IC 周辺の電流ループが平衡し、EMI 性能が更に改善されます。

## リニア・レギュレータ出力 (BIAS)

これらのデバイスには、内部回路ブロックに給電する 1.8V のリニア・レギュレータ ( $V_{BIAS}$ ) が内蔵されています。BIAS と GND の間に 2.2 $\mu$ F のセラミック・コンデンサを接続します。起動時はバイアス・レギュレータは入力側から電力を引き出し、起動が完了すると出力側に切り替わります ( $V_{OUT} > 2.5V$  の場合)。

## 同期入力 (SYNC)

ADPL12008/ADPL12010 IC は内部発振器を備えており、400kHz と 1.5MHz が選択可能です。SYNC をハイにすると、400kHz もしくは 1.5MHz のスイッチング周波数で FPWM 動作します。SYNC をローにすると、スキップ・モードが有効となり、軽負荷時の効率が改善されます。この IC は、SYNC に有効な外部クロックを与えることにより、外部クロックへの同期動作が可能です。

## イネーブル入力 (EN)

イネーブル入力 (EN) により IC はシャットダウン・モードから有効化されます。EN をハイにすると IC が有効化されます。EN をローにすると IC は無効化され、シャットダウン・モードに移行します。シャットダウン中は自己消費電流は 4 $\mu$ A（代表値）まで低減されます。

## ソフトスタート

EN をハイにすると IC が有効化されます。ソフトスタート回路はソフトスタート時間中（代表値 400kHz 時 2.5ms、1.5MHz 時 3.5ms）にリファレンス電圧を徐々に上昇させることにより、起動時の入力突入電流を低減します。

## 短絡保護

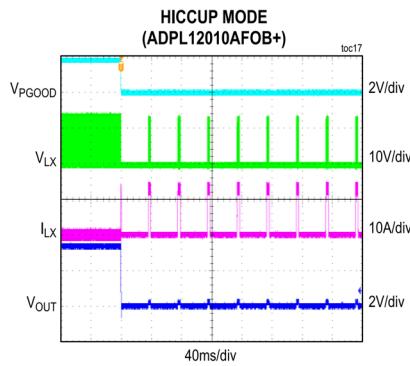

これらの IC にはサイクルごとの電流制限とヒップ・モードがあり、短絡や過負荷の条件から保護します。過負荷の条件では、インダクタの電流が電流制限値 ILIM に達するまでハイサイド FET がオン状態を保ちます。電流制限値に達するとハイサイド FET がオフ、ローサイド FET がオンになり、これによりインダクタ電流が低下します。インダクタ電流が減少して谷電流の制限値に達すると、コンバータは再びハイサイド FET をオンにします。このサイクルが過負荷の条件が除去されるまで繰り返します。

短絡の検出は、出力電圧がプリセットされたスレッショルド電圧より低くなり、インダクタ電流が電流制限値に達したことによります。スレッショルド電圧は出力レギュレーション電圧の 25%です。ヒップ・モード動作中は、IC は降圧コンバータの動作を 35ms（ソフトスタート時間の 10 倍、fsw = 1.5MHz 時）停止した後に再起動し、過電流や短絡の条件が排除されたかをチェックします。短絡状態が継続している間はヒップ動作を繰り返します。

## パワー・グッド・インジケータ (PGOOD)

この IC にはオープンドレインのパワー・グッド (PGOOD) 出力があり、出力電圧の状態を示します。コンバータ出力電圧が公称レギュレーション電圧の 94%（代表値）より高くなると、PGOOD はローから高インピーダンスになります。出力電圧が公称レギュレーション電圧の 93%（代表値）より下がると、PGOOD はローになります。PGOOD はプルアップ抵抗を介してコンバータの出力もしくは BIAS 電圧に接続します。ソフトスタート中は、PGOOD がローにアサートされます。

## サーマル・シャットダウン保護

サーマル・シャットダウン保護は IC の合計消費電力を制限します。ジャンクション温度が+175°C を超過すると、内蔵センサーが IC をシャットダウンし、温度が下がるのを待ちます。ジャンクション温度が 20°C 低下すると、温度センサーにより再び IC の動作が開始します。

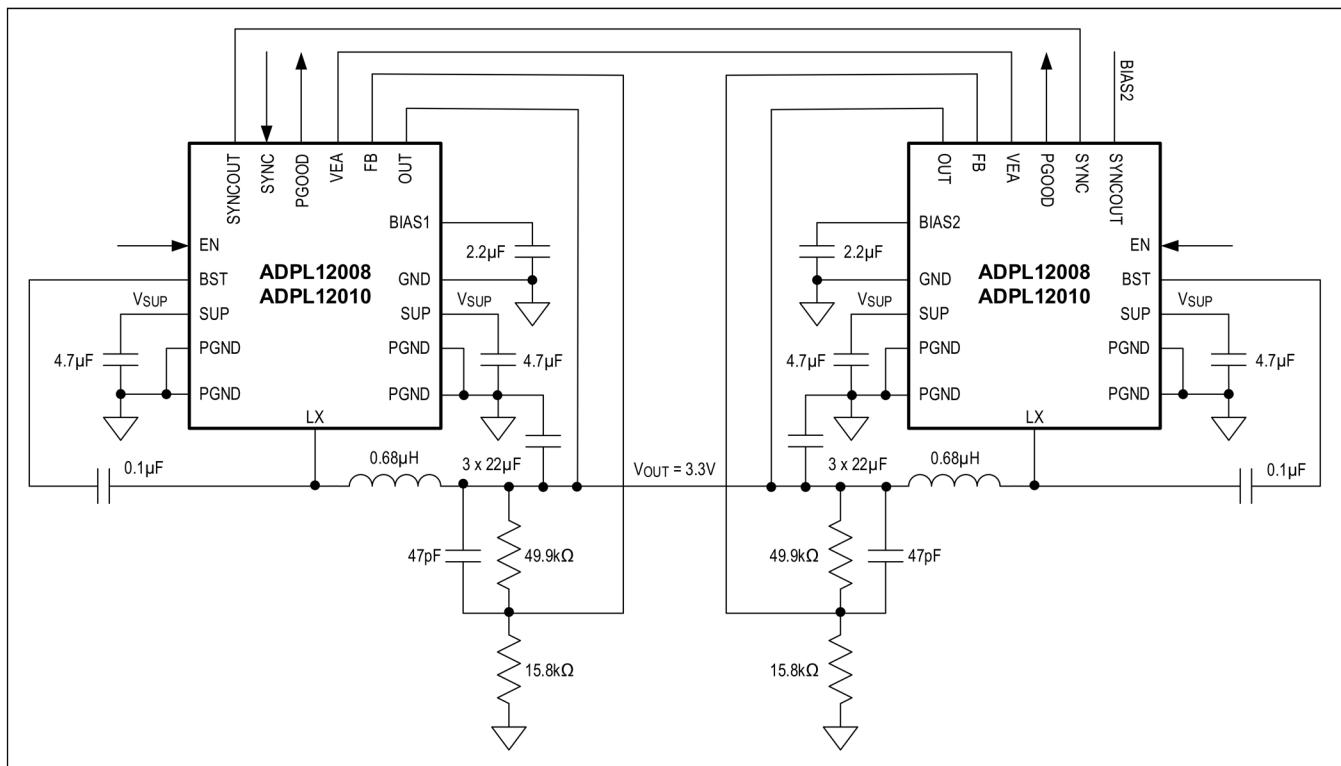

## デュアルフェーズ動作

ADPL12008/ADPL12010 IC を 2 個使用して 2 相動作構成にすると、出力電流を最大 20A に増加できます。2 相モードで動作させるには、一方の IC の SYNCOUT を BIAS に接続してターゲットとして設定し、他方の IC をコントローラとします。コントローラの SYNCOUT をターゲットの SYNC に接続すると、両 IC が 180° の位相差でスイッチングできます。このため、2 相動作を行う場合は、コントローラから SYNCOUT 信号を供給し、FPWM 操作させることができます。

コントローラとターゲットの VEA ノードを互いに接続し、2 つの相の間でバランスの取れた電流分担が行われるようにします。これにより、コントローラとターゲットの電圧制御ループも共有化されます。FB ノードは相互に接続するのではなく、相ごとに別々の抵抗分圧器を使用します。

出力電圧の値を設定するため、図 1 に示すように、降圧出力、FB、GND の間に抵抗分圧器を接続します。コントローラとターゲットには同一の設定でそれぞれ別の抵抗分圧器を用います。

図 1. 外部抵抗分圧器を使用した 2 相構成の代表的なアプリケーション回路

## 2相構成での低 $I_Q$ 動作

ADPL12008/ADPL12010 IC は 2 相動作が可能であり、各 IC をコントローラまたはターゲットとして設定することが可能です。コントローラの SYNCOUT ピンは、SYNC がハイに接続されていれば (FPWM モード) 、180° 位相差のクロックを出力します。低  $I_Q$  モードに設定するためには、コントローラの SYNC ピンをローにプルダウンします (スキップ・モード)。このモードでは、コントローラの SYNCOUT ピンにはクロックは出力されず、コントローラ IC はスキップ・モードに入ります。ターゲット IC の内部回路はこの期間中オン状態を保ち、コントローラからの SYNCOUT 信号を待つ状態となります。ターゲット IC はオン状態なので、両 IC がパルス・スキップ動作をしていても自己消費電流はわずかに高くなります。

更に軽負荷時の効率を高め  $I_Q$  を低減するためには、ターゲットの EN をローにプルダウンします。これによりターゲット側は内部回路も含め無効化され、更に  $I_Q$  が低減します。[表 1](#) に低  $I_Q$  動作の真理値表をまとめます。

表 1. 低  $I_Q$  動作の設定

| CONTROLLER             | TARGET    | MODE                            |

|------------------------|-----------|---------------------------------|

| EN = High, SYNC = BIAS | EN = High | FPWM (high $I_Q$ )              |

| EN = High, SYNC = Low  | EN = High | Skip-mode (low $I_Q$ )          |

| EN = High, SYNC = Low  | EN = Low  | Standby-mode (ultra-low $I_Q$ ) |

| EN = Low               | EN = High | Not allowed                     |

## アプリケーション情報

### 出力電圧の設定

外部で出力電圧を設定する場合、スイッチング周波数が 400kHz の場合は 0.8V~10V、スイッチング周波数が 1.5MHz の場合は 0.8V~6V の出力電圧が設定可能で、そのためには降圧コンバータ出力から FB を経て GND に至る抵抗分圧器を接続します。標準アプリケーション回路において、FB と GND の間に接続する  $R_{FB2}$  には 20kΩ より小さい値を選択します。降圧出力と FB の間に接続する  $R_{FB1}$  の値は次の式によって計算します。

$$R_{FB1} = R_{FB2} \times \left( \frac{V_{OUT}}{V_{FB}} - 1 \right)$$

ここで、 $V_{FB} = 0.8V$  で、 $R_{FB2}$  は 20kΩ より小さい値です。

表 2 に各出力レンジに対する部品選択の推奨値を示します ( $C_{FF}$  は  $R_{FB1} = 50k\Omega$  を前提とした推奨値です)。

表 2. 部品選択の推奨値

| SWITCHING FREQUENCY (kHz) | $V_{OUT}$ (V) | INDUCTOR (µH) | OUTPUT CAPACITOR (µF) | $C_{FF}$ (pF) |

|---------------------------|---------------|---------------|-----------------------|---------------|

| 400                       | 0.8V~1.8V     | 0.68µH        | 500µF                 | N/A           |

| 400                       | 1.8V~3.3V     | 1µH           | 220µF                 | N/A           |

| 400                       | 3.3V~5V       | 2.2µH         | 120µF                 | 82pF          |

| 400                       | 5V~7V         | 2.2µH         | 88µF                  | 56pF          |

| 400                       | 7V~10V        | 3.3µH         | 66µF                  | 47pF          |

| 1500                      | 0.8V~1.8V     | 0.38µH        | 88µF                  | N/A           |

| 1500                      | 1.8V~3.3V     | 0.47µH        | 88µF                  | N/A           |

| 1500                      | 3.3V~5V       | 0.68µH        | 66µF                  | 47pF          |

| 1500                      | 5V~6V         | 0.68µH        | 44µF                  | 15pF          |

### 入力コンデンサ

入力コンデンサは電源から流れるピーク電流を減少させ、降圧コンバータのスイッチング・サイクルに起因する SUP ノードのノイズと電圧リップルを改善します。適正な降圧動作を行うためには、IC の両側に 0.1µF と 4.7µF の 2 つのセラミック入力コンデンサを並列に配置します。

0402 もしくは 0603 サイズの 0.1µF のセラミック・コンデンサを IC の両側の SUP と PGND のすぐ近くに配置することで、入力ノイズを低減し、EMI 性能を向上できます。入力電圧リップルを低減するために、両入力サイドの 0.1µF のコンデンサの先に 4.7µF のセラミック・コンデンサを配置することが必要です。入力電源や配線パターンに高いインピーダンスが存在する場合には、更に追加の降圧コンデンサが必要となることがあります。

入力コンデンサの実効電流の条件 ( $I_{RMS}$ ) は、次の式で定義されます。

$$I_{RMS} = I_{LOAD(MAX)} \times \left( \frac{\sqrt{V_{OUT} \times (V_{SUP} - V_{OUT})}}{V_{SUP}} \right)$$

$I_{RMS}$  は入力電圧が出力電圧の 2 倍であるときに最大値を取ります。

$$V_{SUP} = 2 \times V_{OUT}$$

したがって、

$$I_{RMS} = \frac{I_{LOAD(MAX)}}{2}$$

理想的な長期的信頼性を得るために、この RMS 入力電流における自己発熱による温度上昇が+10°C 未満になる入力コンデンサを選択してください。入力電圧リップルには $\Delta V_Q$ （コンデンサの放電に起因）と $\Delta V_{ESR}$ （コンデンサの ESR に起因）が含まれています。ESR とコンデンサ放電の寄与分が等しく共に 50%であると仮定します。指定された入力電圧リップルに対して必要な入力コンデンサおよび等価直列抵抗 (ESR) は、次の式を使用して計算されます。

$$\text{ESR}_{\text{IN}} = \frac{\Delta V_{\text{ESR}}}{I_{\text{LOAD(MAX)}} + \Delta I_L / 2}$$

$$C_{\text{IN}} = \frac{I_{\text{LOAD(MAX)}} \times D (1 - D)}{\Delta V_Q \times f_{\text{SW}}}$$

ここで、

$$\Delta I_L = \frac{(V_{\text{SUP}} - V_{\text{OUT}}) \times V_{\text{OUT}}}{V_{\text{SUP}} \times f_{\text{SW}} \times L}$$

$$D = \frac{V_{\text{OUT}}}{V_{\text{SUP}}}$$

であり、 $I_{\text{LOAD(MAX)}}$ は最大出力電流、 $\Delta I_L$  はピーク to ピークのインダクタ電流、 $f_{\text{sw}}$  はスイッチング周波数、 $D$  はデューティ・サイクルです。

## インダクタの選択

インダクタの選択は、部品のサイズ、効率、制御ループのバンド幅、ループ安定度の兼ね合いとなります。インダクタンスが不足しているとインダクタの電流リップル、導通損失、出力電圧リップルが増加し、最も厳しい場合にはループの安定性が損なわれます。大きな値のインダクタを用いるとインダクタ電流リップルが減少しますが、部品サイズが大きくなり応答が遅くなります。インダクタの推奨値の詳細については表 2 を参照してください。

## 出力コンデンサ

出力コンデンサはスイッチング・レギュレータにおける重要な構成部品です。出力電圧リップル、負荷過渡応答、ループ安定度に対する要件を満たすように選択します。

出力電圧リップルには $\Delta V_Q$ （コンデンサの放電に起因）と $\Delta V_{ESR}$ （出力コンデンサの ESR に起因）が含まれています。低 ESR のセラミック・コンデンサを使用してください。ESR に起因する成分とコンデンサの放電による成分の出力電圧リップルへの寄与が等量であると仮定します。次式を用いて、指定の出力電圧リップルを満たす出力容量と ESR を求めます。

$$ESR = \frac{\Delta V_{\text{ESR}}}{\Delta I_{\text{P-P}}}$$

$$C_{\text{OUT}} = \frac{\Delta I_{\text{P-P}}}{8 \times \Delta V_Q \times f_{\text{SW}}}$$

$$\Delta I_{\text{P-P}} = \frac{(V_{\text{SUP}} - V_{\text{OUT}}) \times V_{\text{OUT}}}{V_{\text{SUP}} \times f_{\text{SW}} \times L}$$

$$V_{\text{OUTRIPPLE}} = \Delta V_{\text{ESR}} + \Delta V_Q$$

ここで、 $\Delta I_{\text{P-P}}$ はピーク to ピークのインダクタ電流、 $f_{\text{sw}}$ はスイッチング周波数です。

負荷ステップに対しては、コンバータの制御ループが対応してデューティ・サイクルを高めるまでの間は、出力コンデンサが負荷電流を供給しますが、これによって出力電圧のアンダーシュートが発生します。出力電圧変動の最大値を、電力を供給する回路の許容限度以下に抑えるためには、次の式を用いて出力容量を計算します。

$$C_{\text{OUT}} = \frac{\Delta I_{\text{LOAD}}}{\Delta V \times 2\pi \times f_c}$$

ここで $\Delta I$ は負荷ステップ、 $\Delta V$ は出力電圧のアンダーシュートの許容値、 $f_c$ はループのクロスオーバー周波数であり、 $f_{\text{sw}}/10$  と 100kHz のいずれかの小さい方とします。計算された  $C_{\text{out}}$  に、容量の許容誤差、温度の影響、電圧のディレーティングを考慮して実際の容量を決定します。表 2 に、周波数と出力電圧に基づく出力容量の推奨値を示します。

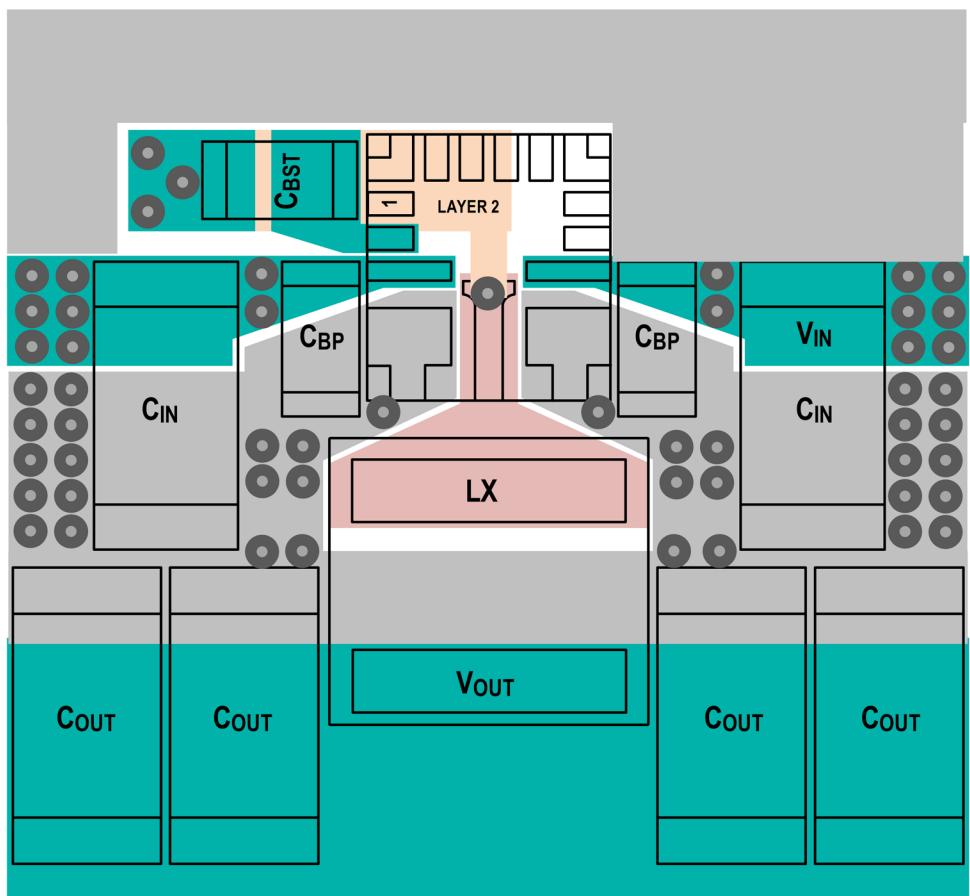

## PCB レイアウトのガイドライン

1. 低スイッチング損失、低EMI、およびノイズのない安定した動作を実現するには、プリント回路基板（PCB）の注意深いレイアウトが不可欠です。詳細については、例えば図2を参照してください。

2. 入力バイパス・コンデンサのC<sub>BP</sub>とC<sub>IN</sub>は、IC両側それぞれのSUPとPGNDの間にできるだけ近づけて配置します。C<sub>BP</sub>はSUPノードとPGNDノードと同一層でこれらの近傍に配置して、EMI除去効果を最大化し、SUPの入力ノイズを最小化します。C<sub>IN</sub>およびC<sub>BP</sub>を対称に配置することにより、反対方向のSUPループが発生し、磁場をキャンセルする効果によりEMIが軽減されます。

3. 降圧出力コンデンサのグラウンド端子と入力コンデンサのグラウンド端子の間の接続は最短にします。降圧回路の大電流経路と電力用パターンは、幅を広く、短くします。LXノードからインダクタを経由して出力コンデンサに至るパターンは最短にします。これにより降圧電流ループの領域が小さくなり、LXパターンの抵抗と浮遊容量が最小となり、効率が最適化されます。

4. ブートストラップ・コンデンサC<sub>BST</sub>はICの近くに配置します。BSTとLXの間は短く広い配線パターンとし、この配線の引き回しでの寄生インピーダンスを最小化します。BSTとLXの間の寄生インピーダンスが高いと、スイッチング速度に影響し、スイッチング損失とdV/dtノイズが更に増加します。BSTとLXの間の配線の引き回しについては、図2を参照してください。

5. BIASコンデンサはBIASノードにできるだけ近く配置します。このコンデンサがICから離れて配置されていると、BIASにノイズが結合することによりリファレンス回路やバイアス回路への外乱となることがあります。

6. 敏感なアナログ信号(FB/VEA)はノイズを伴うスイッチング・ノード(LXおよびBST)や高電流のループから離して配置します。

7. グラウンドは全てのICとの間で流入または流出する全負荷電流のリターン・パスです。また、全てのアナログ回路に対して共通のリファレンス電圧もあります。グラウンドへの配線の引き回しが不適切であると、電流ループの抵抗およびインダクタンスが増加し、それによって電圧リファレンスが相違し、電圧のリンギングやスパイクが悪化します。電力ループ部品用のレイヤの下にしっかりとグランド・プレーンを置き、他の敏感なパターンに対してスイッチング・ノイズを遮蔽します。アナログ・グラウンドのGNDと電源グラウンドのPGNDは、スター・グラウンド接続になるよう1点で相互に接続します。

8. PCB レイアウトは消費電力と熱特性に対しても重要な役割を果たします。PGNDノードはICとその外部との間の主要な電力接続領域です。熱伝達を効率的にするために、PGND領域の周辺にできるだけ大きくグラウンドの銅領域を設けます。PGNDノード周辺にはできるだけ多くのビアを配置して内層のグランド・プレーンやその他の層への熱伝達を改善し、それによってICのパッケージから周囲環境への熱抵抗を改善します。

図 2. PCB レイアウトの例

## 標準アプリケーション回路

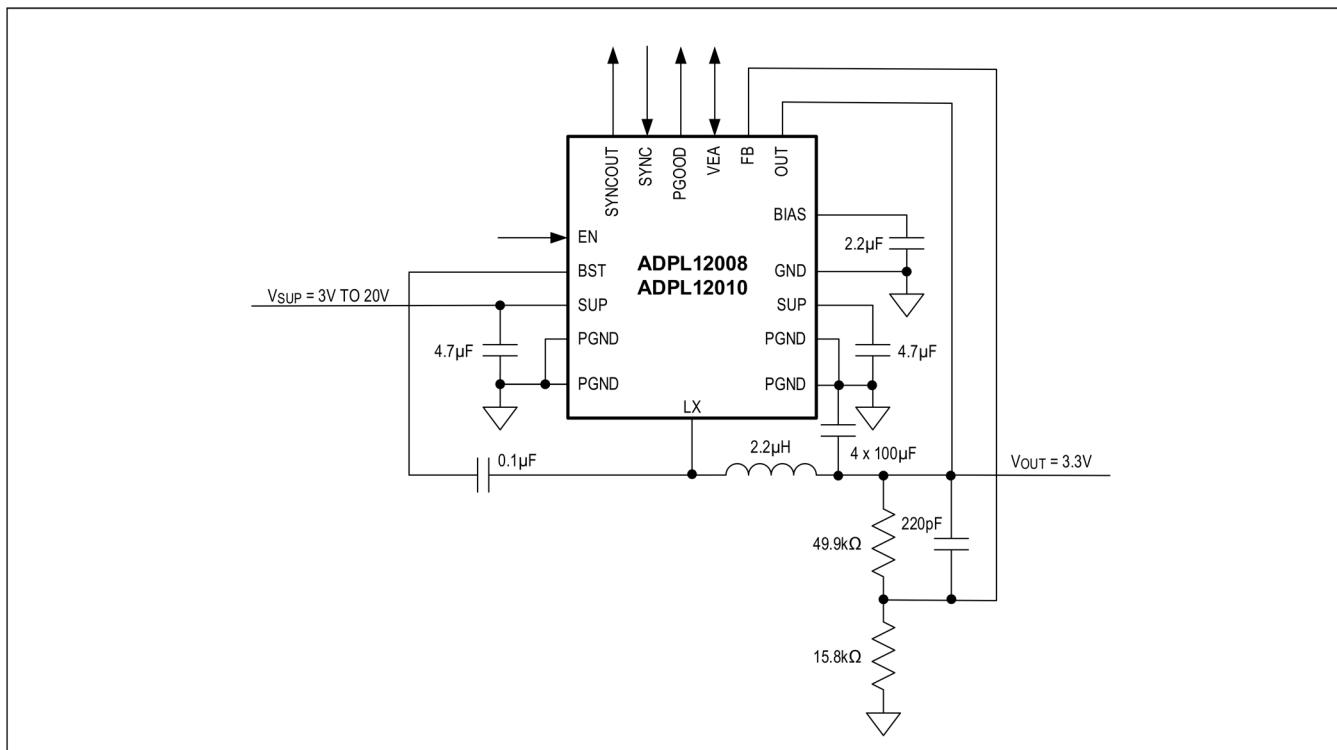

## 単相動作 (400kHz 時)

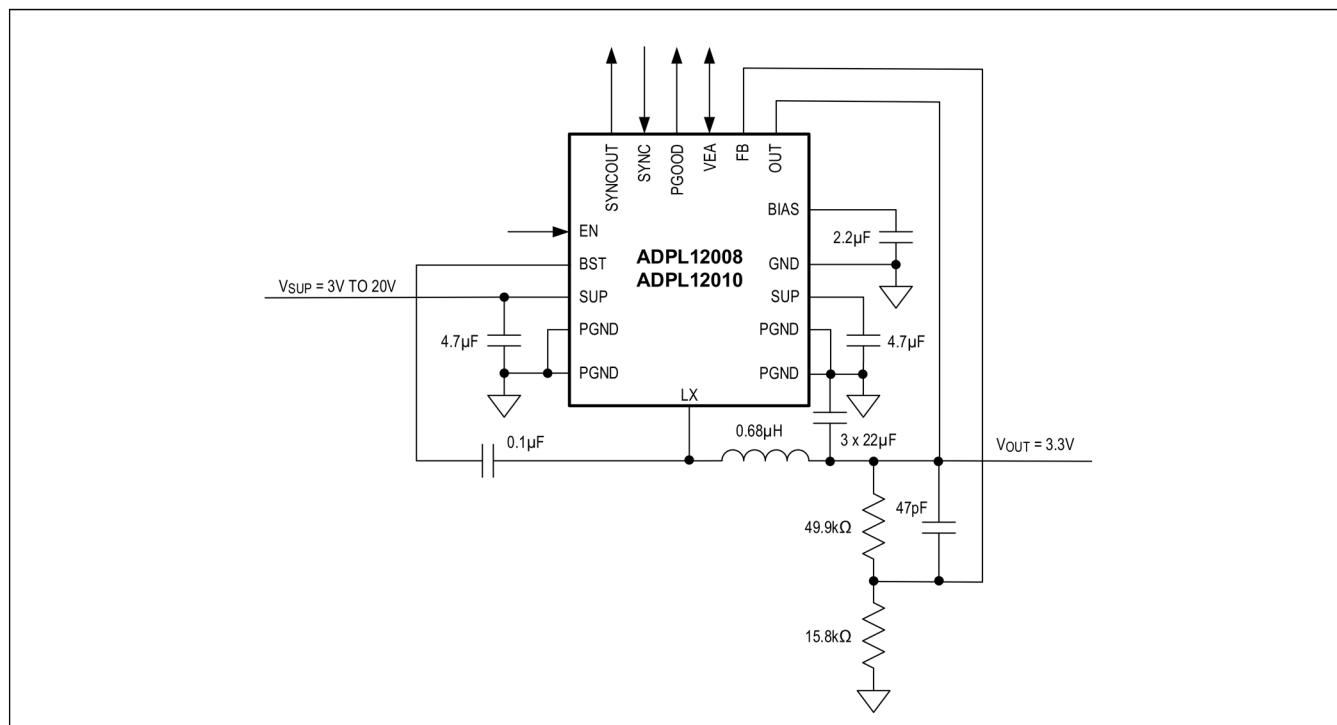

## 単相動作 (1.5MHz 時)

## 2相動作 (1.5MHz 時)

オーダー情報

| PART NUMBER     | V <sub>OUT</sub> (V)   | MAXIMUM OPERATING CURRENT (A) | FREQUENCY |

|-----------------|------------------------|-------------------------------|-----------|

| ADPL12008AFOA+T | Adjustable 0.8V to 10V | 8A                            | 400kHz    |

| ADPL12008AFOB+T | Adjustable 0.8V to 6V  | 8A                            | 1.5MHz    |

| ADPL12010AFOA+T | Adjustable 0.8V to 10V | 10A                           | 400kHz    |

| ADPL12010AFOB+T | Adjustable 0.8V to 6V  | 10A                           | 1.5MHz    |

+は鉛 (Pb) フリー／RoHS 準拠のパッケージであることを示します。

T = テープ & リール。

## 改訂履歴

| 版数 | 改訂日  | 説明   | 改訂ページ |

|----|------|------|-------|

| 0  | 5/25 | 初版発行 | -     |