### ADPL12002/ADPL12003

#### 概要

ADPL12002/ADPL12003 IC は、ハイサイド・スイッチおよびローサイド・スイッチを内蔵した小型の同期整流式降圧コンバータです。3V~20Vの広い入力電圧範囲で、最大2.5A/3.5Aを供給できるよう設計されています。PGOOD信号を観察することで電圧品質をモニタできます。これらの IC は、99%のデューティ・サイクルで稼働することによりドロップアウト・モードで動作が可能であり、ファクトリ・オートメーション・アプリケーションに理想的です。

ADPL12002/ADPL12003 IC では、出力電圧を外部設定できます。 400kHz/1.5MHz の固定内部周波数も選択できるようになってい るため、外付け部品の小型化と出力リップルの低減が可能です。

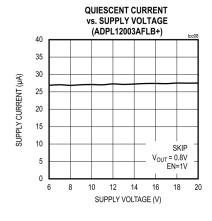

SYNC がローの場合、ADPL12002/ADPL12003 は軽負荷時に自動でスキップ・モードになり、無負荷時は27 $\mu$ A の超低自己消費電流になります。ピン選択可能な強制パルス幅変調(PWM)モードも使用でき、電磁干渉(EMI)性能向上に役立ちます。これらのデバイスは、変調周波数による EMI 放射エミッションを最小限に抑えるよう設計された、スペクトラム拡散周波数変調オプションを備えています。

ADPL12002/ADPL12003 IC は小型  $(3mm \times 3mm)$  の 17 ピン・フリップチップ・クワッド・フラット・ノーリード (FC2QFN) パッケージで提供され、使用する外付け部品はごくわずかです。

### アプリケーション

- ファクトリ・オートメーション

- ポイントオブロード

- 分散型 DC 電源システム

- 通信インフラストラクチャ

- 試験および計測

#### 利点および特長

- 小型サイズでありながら多機能

- 動作入力電圧範囲:3V~20V

- 最大 2.5A/3.5A の電界効果トランジスタ(FET)を内蔵 した同期整流式 DC/DC コンバータ

- スキップ・モードでの自己消費電流:27µA

- スイッチング周波数:400kHz/1.5MHz

- スペクトラム拡散オプション

- 内部ソフトスタート

- 2.5ms (400kHz の場合)

- 3.5ms (1.5MHz の場合)

- 0.8V~12V でプログラマブルな出力電圧範囲

- 低ドロップアウトで 99%デューティ・サイクル動作

- 安全性が不可欠なアプリケーションに対応する高精度

- 完全にプログラマブルな UVLO スレッショルドを実現する高精度イネーブル・スレッショルド

- ・ ウィンドウ化された正確な PGOOD

- 強制 PWM 動作とスキップ・モード動作

- 過熱、過電圧、短絡に対する保護機能

- 3mm×3mm、15ピンFC2QFN

- 動作ジャンクション温度範囲: -40°C~+150°C

オーダー情報はデータシート末尾に記載されています。

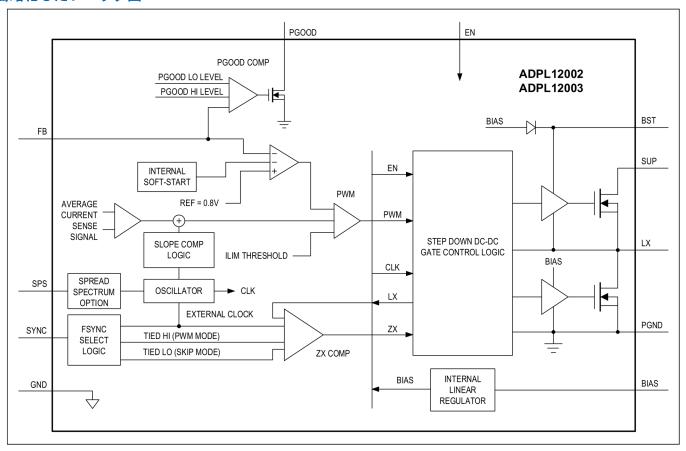

### 簡略化したブロック図

# 20V、2.5A/3.5A の全機能内蔵同期整流式降圧コンバータ

### 目次

| <b>慨</b> 安          | 1  |

|---------------------|----|

| アプリケーション            | 1  |

| 利点および特長             | 1  |

| 簡略化したブロック図          | 2  |

| 絶対最大定格              | 4  |

| パッケージ情報             | 4  |

| 電気的特性               | 5  |

| 標準動作特性              | 7  |

| ピン配置                | 9  |

| 端子説明                | 9  |

| 詳細説明                | 10 |

| リニア・レギュレータ出力 (BIAS) | 10 |

| システム・イネーブル (EN)     | 10 |

| 同期入力(SYNC)          | 10 |

| ソフトスタート             | 10 |

| スペクトラム拡散            | 10 |

| パワー・グッド出力(PGOOD)    | 10 |

| 過電流保護と短絡保護          | 10 |

| サーマル・シャットダウン        | 11 |

| 過電圧保護               | 11 |

| アプリケーション情報          | 12 |

| 出力電圧の設定             | 12 |

| 入力コンデンサ             | 12 |

| 出力コンデンサ             | 13 |

| インダクタの選択            | 15 |

| PCB レイアウトのガイドライン    | 16 |

| 標準アプリケーション回路        | 18 |

| オーダー情報              | 19 |

## 20V、2.5A/3.5A の全機能内蔵同期整流式降圧コンバータ

### 絶対最大定格

| SUP    |             |

|--------|-------------|

| EN     | 0.3V~+22V   |

| BST~LX |             |

| BST    | −0.3V~+24V  |

| LX     |             |

| SYNC   | 0.3V∼+6V    |

| FB     | −0.3V~+16V  |

| PGOOD  |             |

| BIAS   | −0.3V~+2.2V |

| SPS    | −0.3V~+2.2V |

|        |             |

| PGND~AGND                  | $-0.3V\sim+0.3V$ |

|----------------------------|------------------|

| LX 連続実効電流                  | 3.5A             |

| ESD保護                      |                  |

| 人体モデル                      | ±2kV             |

| チャージ・デバイス・モデル              | ±750V            |

| 連続消費電力(多層基板)(TA=+70℃、      |                  |

| +70℃を超えると 25mW/℃でディレーティング) | 2000mW           |

| 動作ジャンクション温度範囲              | -40°C∼+150°C     |

| 保管温度範囲                     | -65°C∼+150°C     |

| ハンダ付け処理温度(ハンダ付け処理:10秒)     | +300°C           |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する 規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### パッケージ情報

| Package Code                                           | F153B3F+1F       |  |  |  |

|--------------------------------------------------------|------------------|--|--|--|

| Outline Number                                         | <u>21-100701</u> |  |  |  |

| Land Pattern Number                                    | <u>90-100241</u> |  |  |  |

| Thermal Resistance, Single-Layer Board:                |                  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 40°C/W           |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 15°C/W           |  |  |  |

| Thermal Resistance, Four-Layer Board:                  |                  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 51°C/W           |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 21°C/W           |  |  |  |

最新のパッケージ外形図とランド・パターン(フットプリント)に関しては、https://www.analog.com/jp/design-center/packaging-quality-symbols-footprints/package-index.html で確認してください。パッケージ・コードの「+」、「#」、「-」は RoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています

パッケージの熱抵抗は、評価キットの 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、https://www.analog.com/jp/technical-articles/thermal-characterization-of-ic-packages.html を参照してください。

### 電気的特性

(特に指定のない限り、 $V_{SUP}=V_{EN}=14V$ 、 $T_J=-40^{\circ}C\sim+150^{\circ}C$ 。特に指定のない限り、代表値は  $T_A=+25^{\circ}C$  の通常条件下の値。Note 1 および Note 2 を参照。)

| PARAMETER                               | SYMBOL                         | CONDITIONS                                                                                     | MIN   | TYP   | MAX   | UNITS      |  |

|-----------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------|-------|-------|-------|------------|--|

| Supply Voltage Range                    | V <sub>SUP</sub>               |                                                                                                | 3     |       | 20    | V          |  |

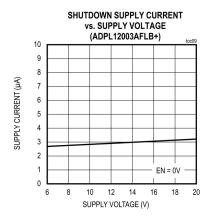

|                                         | I <sub>SUP_SHDN</sub>          | V <sub>EN</sub> = 0, T <sub>A</sub> = +25°C                                                    |       | 2.75  | 5.00  |            |  |

| Supply Current                          | I <sub>SUP</sub>               | V <sub>EN</sub> = high, V <sub>OUT</sub> = 0.8V, no load,<br>switching, T <sub>A</sub> = +25°C |       | 27    |       | μΑ         |  |

| SUP Undervoltage                        | V <sub>SUP_UVLO_R</sub><br>ISE | SUP voltage rising                                                                             | 2.900 | 3.025 | 3.150 | V          |  |

| Lockout                                 | V <sub>SUP_UVLO_F</sub>        | SUP voltage falling                                                                            | 2.600 | 2.725 | 2.850 | V          |  |

| BIAS Voltage                            | V <sub>BIAS</sub>              |                                                                                                |       | 1.8   |       | V          |  |

| BIAS Undervoltage<br>Lockout            | V <sub>BIAS_UVLO</sub>         | BIAS voltage rising                                                                            | 1.58  | 1.63  | 1.68  | V          |  |

| BIAS Undervoltage<br>Lockout Hysteresis | V <sub>BIAS_UVLO_</sub>        | BIAS UVLO hysteresis (See Note 3)                                                              |       | 65    |       | mV         |  |

| BUCK CONVERTER                          |                                | _                                                                                              |       |       |       | _          |  |

| Output Voltage<br>Adjustable Range      | V <sub>OUT</sub>               |                                                                                                | 0.8   |       | 12    | V          |  |

| Feedback Voltage<br>Accuracy            | V <sub>FB_PWM</sub>            | V <sub>FB</sub> = 0.8V, PWM mode, no load,<br>T <sub>A</sub> = -40°C to +125°C                 | 0.788 | 0.800 | 0.812 | V          |  |

| Feedback Leakage<br>Current             | I <sub>FB</sub>                | V <sub>FB</sub> = 0.8V, T <sub>A</sub> = +25°C                                                 |       |       | 100   | nA         |  |

| High-Side DMOS On-Resistance  RDSON_HS  |                                | V <sub>BIAS</sub> = 1.8V, I <sub>LX</sub> = 0.5A                                               |       | 96    | 175   | mΩ         |  |

| Low-Side DMOS On-Resistance  RDSON_LS   |                                | $V_{BIAS} = 1.8V, I_{LX} = 0.5A$ 46                                                            |       | 90    | mΩ    |            |  |

| High-Side DMOS                          | I <sub>LIM</sub>               | ADPL12002                                                                                      | 3.3   | 4.0   | 4.7   | A          |  |

| Current-Limit Threshold                 |                                | ADPL12003                                                                                      | 4.375 | 5.300 | 6.200 |            |  |

| LX Leakage I <sub>LX_LKG</sub>          |                                | $V_{SUP} = 20V$ , $V_{LX} = 0V$ , or $V_{LX} = 20V$ , $T_A = +25$ °C                           |       |       | 1     | μA         |  |

| Soft Start Romp Time too                |                                | f <sub>SW</sub> = 400kHz                                                                       |       | 2.5   | ms    |            |  |

| Soft-Start Ramp Time                    | t <sub>SS</sub>                | f <sub>SW</sub> = 1.5MHz                                                                       |       | 3.5   | 3.5   |            |  |

| Minimum On-Time                         | ton                            |                                                                                                |       | 37    | 65    | ns         |  |

| Maximum Duty Cycle                      | D <sub>MAX</sub>               | Dropout mode                                                                                   | 98    | 99    |       | %          |  |

| SWITCHING FREQUENC                      | CY                             |                                                                                                |       |       |       |            |  |

| PWM Switching                           |                                | f <sub>SW</sub> = 400kHz                                                                       | 360   | 400   | 440   | kHz        |  |

| Frequency                               | f <sub>SW</sub>                | f <sub>SW</sub> = 1.5MHz                                                                       | 1.375 | 1.500 | 1.625 | MHz        |  |

| SYNC External Clock                     | _                              | f <sub>SW</sub> = 400kHz                                                                       | 360   |       | 600   | kHz        |  |

| Frequency                               | fsync                          | f <sub>SW</sub> = 1.5MHz                                                                       | 1.215 |       | 1.845 | MHz        |  |

| Spread Spectrum                         | SPS                            | Percentage of f <sub>SW</sub>                                                                  |       | ±6    |       | %          |  |

| PGOOD OUTPUT                            | 1                              | ı                                                                                              | 1     |       |       | 1          |  |

|                                         | V <sub>PGOOD_UV_</sub>         | V <sub>OUT</sub> rising                                                                        | 91.75 | 94.00 | 96.25 | 0/         |  |

| PGOOD UV Threshold                      | V <sub>PGOOD_UV_</sub>         | V <sub>OUT</sub> falling                                                                       | 90.75 | 93.00 | 95.25 | <b>-</b> % |  |

# 20V、2.5A/3.5A の全機能内蔵同期整流式降圧コンバータ

(特に指定のない限り、 $V_{SUP} = V_{EN} = 14V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 。特に指定のない限り、代表値は  $T_A = +25^{\circ}C$  の通常条件下の値。Note 1 および Note 2 を参照。)

| PARAMETER                      | SYMBOL                                         | CONDITIONS                              |                                                       | MIN    | TYP    | MAX    | UNITS |

|--------------------------------|------------------------------------------------|-----------------------------------------|-------------------------------------------------------|--------|--------|--------|-------|

| PGOOD OV Threshold             | V <sub>PGOOD_OV_</sub> V <sub>OUT</sub> rising |                                         | 102.75                                                | 105.00 | 107.25 | - %    |       |

| PGOOD OV Threshold             | V <sub>PGOOD_OV_</sub>                         | V <sub>OUT</sub> falling                | V <sub>OUT</sub> falling                              |        | 104.00 | 106.25 | 70    |

| PGOOD Debounce                 | t <sub>DEB_rising</sub>                        | PWM mode                                | UV rising, OV falling, f <sub>SW</sub> = 1.5MHz       |        | 180    |        | lie.  |

| Time                           | t <sub>DEB_falling</sub>                       | PWM mode                                | UV falling, OV<br>rising, f <sub>SW</sub> =<br>1.5MHz |        | 70     |        | - μs  |

| PGOOD Leakage<br>Current       | I <sub>PGOOD_LKG</sub>                         |                                         |                                                       |        |        | 2      | μA    |

| PGOOD Low Voltage<br>Level     | V <sub>PGOOD_LOW</sub>                         | Sinking 1mA                             | Sinking 1mA                                           |        |        | 0.4    | V     |

| LOGIC LEVELS                   |                                                |                                         |                                                       | ·      |        |        |       |

| EN High Voltage Level          | V <sub>EN_HIGH</sub>                           |                                         |                                                       | 0.825  | 0.900  | 0.975  | V     |

| EN Low Voltage Level           | V <sub>EN_LOW</sub>                            |                                         |                                                       | 0.625  | 0.700  | 0.775  | V     |

| EN Hysteresis                  |                                                | (See Note 3)                            |                                                       |        | 200    |        | mV    |

| EN Input Current               | I <sub>EN</sub>                                | V <sub>EN</sub> = V <sub>SUP</sub> = 20 | $V, T_A = +25^{\circ}C$                               |        |        | 1      | μA    |

| SYNC High-Voltage<br>Level     | V <sub>SYNC_HIGH</sub>                         |                                         |                                                       | 1.4    |        |        | V     |

| SYNC Low-Voltage<br>Level      | V <sub>SYNC_LOW</sub>                          |                                         |                                                       |        |        | 0.4    | V     |

| SPS High-Voltage Level         | V <sub>SPS_HIGH</sub>                          |                                         |                                                       | 1.4    |        |        |       |

| SPS Low-Voltage Level          | V <sub>SPS_LOW</sub>                           |                                         |                                                       |        |        | 0.4    |       |

| THERMAL PROTECTION             |                                                |                                         |                                                       |        |        |        |       |

| Thermal Shutdown               | T <sub>SHDN</sub>                              |                                         |                                                       |        | 175    |        | °C    |

| Thermal Shutdown<br>Hysteresis | T <sub>SHDN_HYS</sub>                          |                                         |                                                       |        | 15     |        | °C    |

Note 1: すべてのユニットは T<sub>A</sub> = +25℃ で 100%製品テストしています。動作温度範囲および関連する電源電圧に関する限界値は、設計および特性評価で確保しています。

Note 2: このデバイスは、 $T_J$  = +125°C で 95000 時間、 $T_J$  = +150°C で 5000 時間、連続動作するように設計されています。

Note 3:製品テストは行っていませんが、設計により裏付けられています。

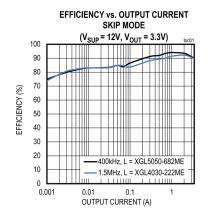

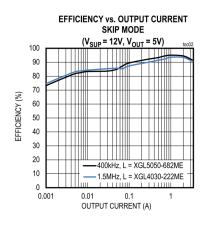

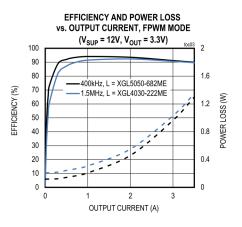

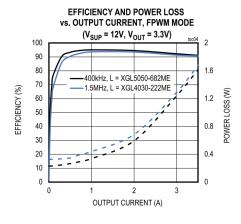

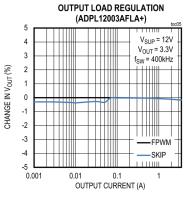

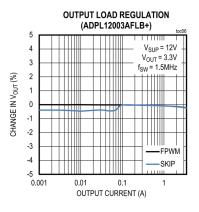

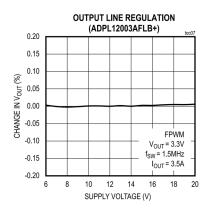

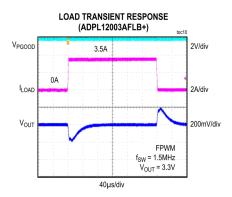

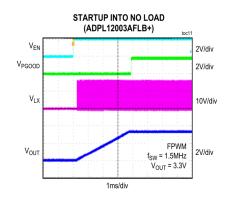

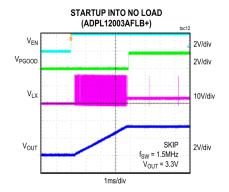

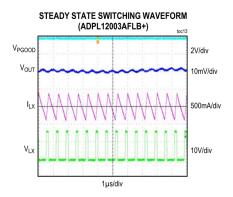

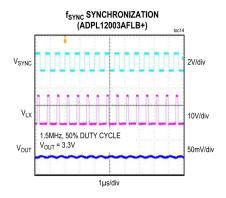

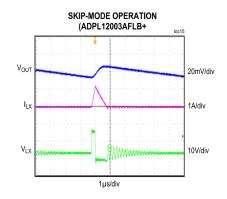

### 標準動作特性

(特に指定のない限り、T<sub>A</sub>=+25℃)

(特に指定のない限り、T<sub>A</sub>=+25℃)

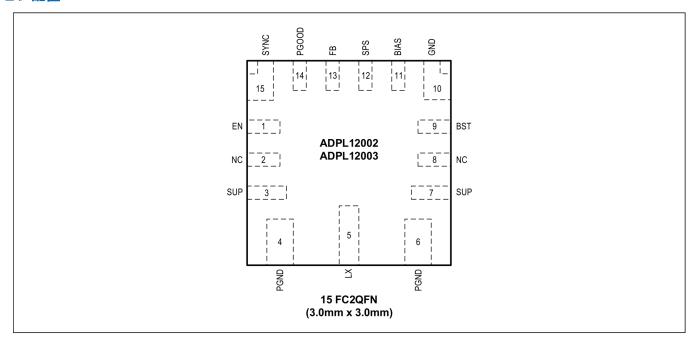

### ピン配置

### 端子説明

| 端子                                         | 名称    | 機能                                                                                                                                                                                 |

|--------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                          | EN    | 高耐圧、アクティブハイのデジタル・イネーブル入力。ENをハイにすると降圧コンバータが有効化されます。                                                                                                                                 |

| 2, 8                                       | NC    | 無接続。                                                                                                                                                                               |

| 3, 7                                       | SUP   | 内部ハイサイドの電源入力。SUP から内部スイッチおよび LDO に電力が供給されます。SUP は、 $0.1\mu F$ および $2.2\mu F$ のセラミック・コンデンサで PGND にバイパスします。 $0.1\mu F$ のコンデンサを SUP ピンと PGND ピンのできるだけ近くに配置し、 $2.2\mu F$ のコンデンサを追加します。 |

| 4, 6                                       | PGND  | 電源グラウンド。                                                                                                                                                                           |

| 5                                          | LX    | インダクタの接続。LXをインダクタの切り替え側に接続します。                                                                                                                                                     |

| 9 BST ハイサイド FET ゲート電圧用の昇圧フラ<br>ンデンサを接続します。 |       | ハイサイド FET ゲート電圧用の昇圧フライング・コンデンサ接続。BST と LX の間に 0.1μF のセラミック・コンデンサを接続します。                                                                                                            |

| 10                                         | GND   | 低ノイズ・アナログ・グラウンド。                                                                                                                                                                   |

| 11                                         | BIAS  | 1.8V の内蔵 BIAS 電源。BIAS と PGND の間に 2.2μF 以上のセラミック・コンデンサを接続します。                                                                                                                       |

| 12                                         | SPS   | スペクトラム拡散イネーブル。ロジック・ハイに接続すると、内部発振器のスペクトル拡散が有効化され、ロジック・ローに接続するとスペクトラム拡散が無効化されます。                                                                                                     |

| 13                                         | FB    | 帰還入力。出力電圧帰還入力として機能します。外部抵抗分圧器を、昇圧出力からFBおよびGNDに接続して、<br>出力電圧を設定します。                                                                                                                 |

| 14                                         | PGOOD | オープン・ドレインのパワー・グッド出力。PGOOD はプルアップ抵抗を介して BIAS もしくは外部の正電源に接続します。                                                                                                                      |

| 15                                         | SYNC  | 外部クロック同期入力。所定の周波数範囲の外部クロックを接続し、外部クロック同期を有効にします。SYNC をローに接続するとスキップ・モードが有効になります。SYNC をハイに接続すると FPWM モードが有効になります。                                                                     |

#### 詳細説明

ADPL12002/ADPL12003 IC は、ハイサイド・スイッチおよびローサイド・スイッチを内蔵した小型の同期整流式降圧コンバータです。 $3V\sim20V$ の入力電圧で、最大 2.5A/3.5A を供給するよう設計されています。出力電圧は、 $0.8V\sim12V$  の範囲で調整可能です。PGOOD 信号を観察することにより、出力電圧の品質を監視できます。これらの IC は、99%のデューティ・サイクルで稼働することによりドロップアウト・モードで動作が可能であるため、ファクトリ・オートメーション・アプリケーションに理想的です。

周波数は 400kHz/1.5MHz に内部固定されているため、外付け部品の小型化と出力リップルの低減が可能です。これらのコンバータは、SYNCがローにプルダウンされている場合、軽負荷時に自動でスキップ・モードになり、無負荷時には 27μA (代表値) の超低自己消費電流となります。ADPL12002/ADPL12003 IC は、EMI 放射エミッションを最小限に抑えるために、スペクトラム拡散周波数変調機能を備えています。平均電流モード・アーキテクチャにより、電流ループのノイズ除去能力が向上し、非常に短い最小オン時間を実現できます。

#### リニア・レギュレータ出力(BIAS)

このデバイスには 1.8V のリニア電圧レギュレータ( $V_{BIAS}$ )が内蔵されており、内部回路ブロックに電力を供給します。BIAS と GND の間に  $2.2\mu F$  のセラミック・コンデンサを接続します。

#### システム・イネーブル(EN)

イネーブル制御入力 (EN) により、デバイスは、低消費電力シャットダウン状態から起動します。EN をハイにすると内蔵のリニア BIAS LDO がオンになります。V<sub>BIAS</sub> が 1.63V (代表値) の内部ロックアウト・スレッショルドを超えると、コンバータが有効になり、出力電圧は設定されたソフトスタート時間で徐々に上昇します。

EN がロジック・ローの場合、デバイスはシャットダウンします。シャットダウン時、BIAS のレギュレータとゲート・ドライバはオフになり、自己消費電流は  $2.75\mu A$  (代表値) に減少します。

#### 同期入力 (SYNC)

SYNC は、動作モードの選択と周波数制御のために用いられる、ロジックレベルの入力です。SYNC を BIAS に接続すると強制固定周波数動作(FPWM)を有効化でき、GND に接続すると自動スキップ・モード動作を有効化して軽負荷時の効率を向上できます。SYNC を外部クロックに接続して、強制周波数動作を有効化することもできます。デバイスは 2 サイクル以内に外部クロックに同期し、印加信号の立上がりエッジに同期します。詳細については、電気的特性の表に仕様規定されている外部クロック周波数制限を参照してください。2 クロック・サイクルより長く外部クロック信号が検出されなければ、IC は内部クロック動作に切り替わります。

#### ソフトスタート

デバイスには、周波数に応じた固定ソフトスタート時間が組み込まれています。ソフトスタート時間は、出力電圧をレギュレーション・ポイントに向けて強制的に上げることによって、起動時の突入電流を制限します。ソフトスタートの上昇率は、400kHz の場合 2.5ms (代表値)、1.5MHz の場合 3.5ms (代表値)に設定されています。

#### スペクトラム拡散

このデバイスは、スペクトラム拡散オプションを備えています。SPS ピンがハイにプルアップされている場合、スペクトラム拡散機能が 有効になり、内部動作周波数は、内部生成された動作周波数に対し±6%の範囲で変動します。変調信号は 1.5MHz 時に 300μs (400kHz 時 には 1.25ms) の周期の三角波です。デバイスが外部クロックに同期している場合、スペクトラム拡散は無効化されます。

### パワー・グッド出力(PGOOD)

ADPL12002/ADPL12003 IC にはオープン・ドレインのパワー・グッド出力(PGOOD)があり、出力電圧の品質を監視します。PGOOD は アクティブハイの出力信号で、 $V_{OUT}$  が公称値の 93%(代表値)を下回るか 105%(代表値)を上回るとローにプルダウンされます。 $20k\Omega$ (代表値)のプルアップ抵抗を、外部電源またはオンチップの BIAS 出力に接続します。

#### 過電流保護と短絡保護

このデバイスは、出力での短絡および過負荷状態からデバイスを保護する電流制限機能を備えています。短絡または過負荷状態となった場合、インダクタ電流が仕様規定された LX 電流制限スレッショルドに達するまで、ハイサイド・スイッチはオンのままになります。インダクタ電流がスレッショルドに達すると、コンバータはハイサイド・スイッチをオフに、ローサイド・スイッチをオンにして、インダクタ電流が徐々に下がるようにします。インダクタ電流がローサイドの谷電流制限スレッショルドを下回ると、コンバータはハイサイド・スイッチを再びオンにします。このサイクルは、短絡または過負荷の状態が解消されるまで繰り返されます。

### 20V、2.5A/3.5A の全機能内蔵同期整流式降圧コンバータ

短絡は、出力電圧が電流制限時にレギュレーション電圧の 50%を下回ると検出されます。この状態になると、ヒカップ・モードがアクティブになり、出力は 35ms( $10 \times 3.5$ ms、1.5MHz 時)または 25ms( $10 \times 2.5$ ms、400kHz 時)の間オフになり、その後再起動を試みます。短絡状態が存在する間、これが無限に繰り返されます。ソフトスタートの間、ヒカップ・モードは無効になります。

#### サーマル・シャットダウン

サーマル・シャットダウンは、デバイスを過度な動作温度から保護するものです。ジャンクション温度が+175℃ を超えると、内蔵センサーが降圧コンバータをシャットダウンして、IC の温度を下げられるようにします。ジャンクション温度が 15℃ 下がると、センサーによって IC が再びオンになります。

### 過電圧保護

IC には、出力に対する過電圧保護機能があります。スキップ・モードで過電圧状態になった場合、インダクタ電流が負の固定値に達するまで、ハイサイド・スイッチがオフ、ローサイド・スイッチがオンになります。この値に達すると、ローサイド・スイッチはオフになり、次のサイクルで再びオンになります。出力が OV 立下がりスレッショルド未満になるまでこれが続きます。このようにして、出力が素早く放電され、安定状態に戻ります。

#### アプリケーション情報

#### 出力電圧の設定

ADPL12002/ADPL12003 IC では出力電圧の調整が可能です。出力電圧は外付けの抵抗分圧器を使用して  $0.8V\sim12V$  の範囲で調整できます。降圧出力から FB を介して GND に抵抗分圧器を接続し、降圧出力から FB にフィードフォワード・コンデンサを接続します(詳細は標準アプリケーション回路のセクションを参照)。 $R_{FB2}$ には  $50k\Omega$  以下のものを選択します。 $R_{FB1}$  は次式により計算します。

式1:

$$R_{FB1}$$

=  $R_{FB2}$   $\left[ \left( \frac{V_{OUT}}{V_{FB}} \right) - 1 \right]$ ;  $\succeq$   $\succeq$   $\sim$   $v_{FB}$  =0.8 $v_{\circ}$

表 1. 調整可能出力用の推奨部品

| PART NUMBER    | FREQUENCY | V <sub>OUT</sub> (V) | INDUCTOR (µH) | EFFECTIVE C <sub>OUT</sub> (μF) | C <sub>FF</sub> (pF) |

|----------------|-----------|----------------------|---------------|---------------------------------|----------------------|

|                |           | 0.8V-1.5V            | 3.3µH         | 130µF                           | -                    |

|                | 4001415   | 1.5V-3V              | 4.7µH         | 63µF                            | 33pF                 |

|                | 400kHz    | 3V–6V                | 6.8µH         | 40μF                            | 33pF                 |

| A D.D.I. 40000 |           | 6V-12V               | 8.2µH         | 30µF                            | 22pF                 |

| ADPL12002      |           | 0.8V-1.5V            | 0.68µH        | 120µF                           | _                    |

|                | 1.5MHz    | 1.5V-3V              | 1.5µH         | 55μF                            | 47pF                 |

|                |           | 3V-6V                | 2.2µH         | 42µF                            | 47pF                 |

|                |           | 6V-12V               | 4.7µH         | 25µF                            | 82pF                 |

|                |           | 0.8V-1.5V            | 3.3µH         | 130µF                           | _                    |

|                | 400111-   | 1.5V-3V              | 3.3µH         | 70µF                            | 33pF                 |

|                | 400kHz    | 3V-6V                | 6.8µH         | 50μF                            | 33pF                 |

| A D.D.I. 40000 |           | 6V-12V               | 8.2µH         | 40µF                            | 22pF                 |

| ADPL12003      | 1.5MHz    | 0.8V-1.5V            | 0.68µH        | 120µF                           | _                    |

|                |           | 1.5V-3V              | 1.0µH         | 74µF                            | 47pF                 |

|                |           | 3V-6V                | 2.2µH         | 42µF                            | 47pF                 |

|                |           | 6V-12V               | 3.3µH         | 25µF                            | 82pF                 |

表 1 に、各出力電圧範囲に対する部品選択の推奨を示します。フィードフォワード・コンデンサ( $C_{FF}$ )については、 $R_{FBI}=50k\Omega$  に基づく推奨値です。

### 入力コンデンサ

入力フィルタ・コンデンサは、電源から引き出されるピーク電流を抑制し、回路のスイッチングによって入力に生じるノイズおよび電圧 リップルを低減します。ADPL12002/ADPL12003 IC は、EMI 性能を向上するために対称なピン配置を採用しています。入力コンデンサは 2 つの SUP ピンの間で対称形になるよう分割することを推奨します。 $2.2\mu F$  (以上) のコンデンサを各 SUP ピンに接続すると入力電圧リップルを低減できます。 ノイズ耐性を更に高めるために、高周波数の 0603 またはそれより小型で  $0.1\mu F$  (推奨値) のコンデンサを各 SUP ピンに追加しても構いません。

通常は、フロントエンド回路のQを下げたり、入力電圧リップルを最小限に抑えるのに必要な残りの容量を提供したりするために、電解コンデンサなどの等価直列抵抗(ESR)が高いバルク・コンデンサが必要となります。

入力コンデンサの実効電流の条件 (IRMS) は、次の式で定義されます。

### 20V、2.5A/3.5A の全機能内蔵同期整流式降圧コンバータ

式2:

$$I_{RMS} = I_{LOAD(MAX)} \times \left( \frac{\sqrt{V_{OUT} \times (V_{SUP} - V_{OUT})}}{V_{SUP}} \right)$$

IRMS は入力電圧が出力電圧の2倍であるときに最大値を取ります。

$$V_{SUP} = 2 \times V_{OUT}$$

したがって、

$$I_{RMS} = \frac{I_{LOAD(MAX)}}{2}$$

理想的な長期的信頼性を得るためには、この RMS 入力電流における自己発熱による温度上昇が $+10^{\circ}$ C 未満になる入力コンデンサを選択してください。入力電圧リップルには  $\Delta V_Q$  (コンデンサの放電に起因) と  $\Delta V_{ESR}$  (コンデンサの ESR に起因) が含まれています。入力には、高いリップル電流を許容する低 ESR のセラミック・コンデンサを使用します。 ESR とコンデンサ放電の寄与分が等しく共に 50%であると仮定します。指定された入力電圧リップルに対して必要な入力コンデンサと ESR は、次の式を使用して計算されます。

式3:

$$ESR_{IN} = \frac{\Delta V_{ESR}}{I_{OUT} + \Delta I_{L/2}}$$

ここで、

$$\Delta I_L = \frac{(V_{SUP} - V_{OUT}) \times V_{OUT}}{V_{SUP} \times f_{SW} \times L}$$

また、

$$C_{IN} = \frac{I_{OUT} \times D(1 - D)}{\Delta V_Q \times f_{SW}}$$

$$D = \frac{V_{OUT}}{V_{SUP}}$$

ここで、

Iout = 最大出力電流

D=デューティ・サイクル

### 出力コンデンサ

出力コンデンサは、出力電圧リップル、負荷過渡応答、ループ安定性の条件を満たすように選択します。負荷ステップ時に、出力電流はほぼ瞬時に変わるのに対して、インダクタは遅い反応を示します。この遷移時間の間、負荷変動条件には出力コンデンサが対応するため、出力電圧にアンダーシュート/オーバーシュートが生じます。出力コンデンサは、制御ループの安定性にも影響します。出力コンデンサの推奨値の詳細については、表1を参照してください。

出力リップルは、 $\Delta V_Q$ (コンデンサの放電によるもの)と  $\Delta V_{ESR}$ (出力コンデンサの ESR によるもの)で構成されています。出力には、 ESR が低いセラミック・コンデンサまたはアルミ電解コンデンサを使用します。アルミ電解コンデンサの場合、出力リップル全体が  $\Delta V_{ESR}$  によるものです。式 4 を使用して、ESR の必要条件を計算し、それに応じてコンデンサを選択します。セラミック・コンデンサを 使用する場合、ESR とコンデンサの放電による出力リップル電圧への寄与分は等しいと仮定します。次式は、仕様規定された出力電圧 リップルに適した出力容量と ESR の必要条件を示しています。

### 20V、2.5A/3.5A の全機能内蔵同期整流式降圧コンバータ

式4:

$$ESR = \frac{\Delta V_{ESR}}{\Delta I_{L}}$$

$$C_{OUT} = \frac{\Delta I_L}{8 \times \Delta V_Q \times f_{SW}}$$

ここで、

$$V_{OUT}$$

RIPPLE =  $\Delta V_{ESR} + \Delta V_{Q}$

$\Delta I_L$ はピーク to ピークのインダクタ電流、 $f_{SW}$ はコンバータのスイッチング周波数です。

出力コンデンサは、コンバータがより大きいデューティ・サイクルに応答するまでステップ負荷電流を供給します。出力コンデンサの ESR における抵抗性ドロップとコンデンサ放電によって、ステップ負荷では電圧ドループが生じます。トランジェント負荷とリップル/ノイズ性能を改善するためには、ESR が低いタンタル・コンデンサとセラミック・コンデンサを組み合わせて使用します。出力電圧の最大偏差は、給電されている電子機器の許容限度未満に保ちます。セラミック・コンデンサを使用する場合、出力容量の放電と ESR ドロップの寄与分がそれぞれ 80%と 20%であると仮定します。次式を使用して、必要な ESR と容量の値を計算します。

式5:

$$C_{OUT} = \frac{\Delta I}{\Delta V \times 2\pi \times f_C}$$

ここで、 $\Delta I$  は負荷の変化、 $\Delta V$  は許容電圧ドループ、 $f_c$  はループのクロスオーバー周波数であり、この周波数は  $f_{SW}/10$  または 100kHz のいずれか小さい方とします。 $C_{OUT}$  に関わる計算はいずれも、容量公差、温度、電圧のディレーティングを考慮する必要があります。表 1 に、スイッチング周波数および出力電圧に基づいて推奨される出力コンデンサの値を示します。

### インダクタの選択

インダクタの設計は、サイズ、効率、制御ループの帯域幅、コンバータの安定性などの兼ね合いで決まります。インダクタンス値が不十分な場合、インダクタ電流リップルが増加し、それによって伝導損失や出力電圧リップルが大きくなります。ADPL12002/ADPL12003 では勾配補償が内部で固定されているため、これも電流モード制御の不安定性の原因となります。インダクタの値が大きいとリップルは減少しますが、ソリューションのサイズおよびコストが増加し、応答が遅くなります。表 2 に、各スイッチング周波数および出力電圧に対する最適なインダクタ値を示します。

表 2. 推奨インダクタ値

| DART NUMBER | EDECHENOV | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | INDUCTOR (µH) |     |     |

|-------------|-----------|---------------------------------------|---------------|-----|-----|

| PART NUMBER | FREQUENCY | V <sub>OUT</sub> (V)                  | MIN           | ТҮР | MAX |

|             |           | 3.3V                                  | 4.7           | 6.8 | 8.2 |

|             | 400kHz    | 5V                                    | 6.8           | 8.2 | 10  |

|             |           | 12V                                   | 10            | 12  | 15  |

| ADPL12002   |           | 3.3V                                  | 1.5           | 2.2 | 2.8 |

|             | 1.5MHz    | 5V                                    | 1.8           | 2.2 | 3.3 |

|             |           | 12V                                   | 3.3           | 4.7 | 5.6 |

|             |           | 3.3V                                  | 4.7           | 6.8 | 8.2 |

|             | 400kHz    | 5V                                    | 4.7           | 6.8 | 8.2 |

| ADDI 12002  |           | 12V                                   | 8.2           | 10  | 12  |

| ADPL12003   |           | 3.3V                                  | 1.0           | 2.2 | 2.8 |

|             | 1.5MHz    | 5V                                    | 1.5           | 2.2 | 3.3 |

|             |           | 12V                                   | 3.3           | 4.7 | 5.6 |

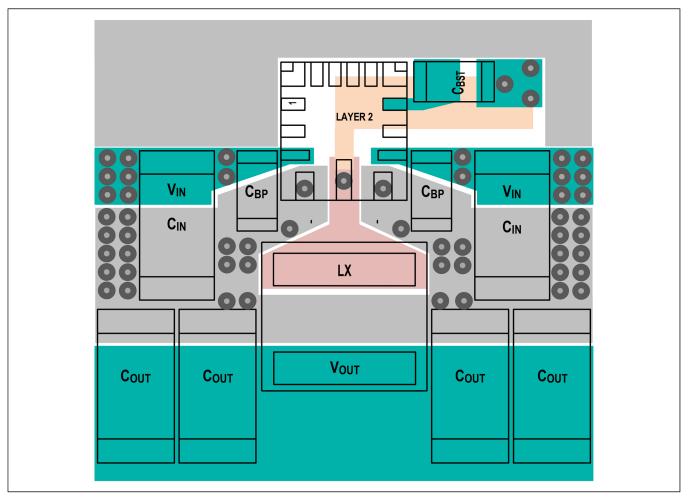

#### PCB レイアウトのガイドライン

低スイッチング電力損失とノイズのない安定した動作を実現するには、プリント回路基板 (PCB) の注意深いレイアウトが不可欠です。 ノイズ耐性と消費電力の改善には可能な限り多層基板を使用します。ADPL12002/ADPL12003 IC のパッケージは、独自の対称的な設計を 採用しており、互いに反対向きに生じる磁界を打ち消しあいます。適切な PCB レイアウトを行うため、図 1 に示すレイアウト例の図と以 下のガイドラインを参照してください。

- 1. 熱伝導を効率的にするため、ICのフットプリント下にはできるだけ多くの銅プレーンを設けます。

- 2. 各 SUP ピンに  $2.2\mu F$  (以上) の入力コンデンサをデバイスに近付けて、対称な構成で配置します。ノイズ耐性を更に高めるため、高周波数セラミック入力バイパス・コンデンサ ( $C_{BP}$ ) を各 SUP ピンに追加する場合は、まず高周波数コンデンサをできるだけピン近くに配置し、次いで  $2.2\mu F$  のコンデンサを接続します。セラミック・コンデンサは、IC の両側の SUP ピンと PGND ピンにできるだけ近付けて配置します。コンデンサと IC ピンの間には、(ビアなどの不連続点がない)低インピーダンスの接続を使用します。CBP はIC に最も近付けて配置し、非常に良好な高周波特性を持つことが必要です(小パッケージ・サイズと大容量)。これにより、EMI 除去性能が最大になり、性能低下につながるデバイスの内部ノイズを最小限に抑えられます。

- 3. PGND ピンと GND ピンは IC の下で直接接続します。これにより、GND と PGND 間の接続経路を最短にできます。

- 4. バイアス電流ループを抑えるために、BIAS コンデンサは IC の BIAS ピンにできるだけ近付けて配置します。これにより、BIAS のノイズを低減でき、滑らかな動作が実現できます。

- 5. ブートストラップ・コンデンサ C<sub>BST</sub> を IC に近付けて配置し、短くて幅広の配線パターンを使用してループの面積と寄生インダクタンスを最小限にします。リターン配線パターン (C<sub>BST</sub> から LX の間)には最も近い層を使用して、インダクタンスを更に最小限にします。寄生インダクタンスが高いと、スイッチング速度に影響を与え (スイッチング損失が増加)、高い dv/dt ノイズが発生する可能性があります。

- 6. インダクタは ICの LX ピンのできるだけ近くに配置し、LX ノードの面積を最小限に抑えます。

- 7. ノイズ耐性を最大限にするために、出力コンデンサは、インダクタの両側に対称に配置します。出力コンデンサ (Cour) をインダクタの近くに配置して、Cour のグラウンド側が Cin のグラウンド接続の近くになり、電流ループの面積が最小限になるようにします。コンデンサのグラウンドにはビアを追加してインダクタンスを最小限にします。ノイズ耐性を更に高めるため、インダクタの両側に高周波数コンデンサを配置し、次いで出力コンデンサを接続し、放射ノイズを更に低減します。

- 8. インダクタ、出力コンデンサ、ブートストラップ・コンデンサ、BIAS コンデンサは、電流ループで囲まれる面積が最小となるように 配置します。電源パターンと負荷の接続配線は短くします。この方法は、高い効率を得るために必須のものです。銅層の厚い PCB を 用いると、全負荷効率と低消費電力性能を向上させることができます。

- 9. PCB の内層をグランド・プレーンに用いることで、グランド・プレーンが放射ノイズに対するシールドとして作用するため、EMI を 改善できます。ボード全面、特にグラウンド接続付近には複数のビアを分散して配置します。

- 10. IC に隣接している層には連続的な銅の GND プレーンを使用して、回路全体をシールドします。また、GND は最上面の回路全体の周囲に広げる必要があります。すべての放熱部品は冷却のために銅と十分に接続するようにしてください。インピーダンスを低くし、放熱を最大限にするために、複数のビアを使用して GND プレーン/領域を相互に接続します。IC および入力/出力/バイパス・コンデンサの GND 端子にはビアを設けます。PGND と GND の接続を別々のプレーンまたは領域で分離したり絶縁したりしないでください。

- 11. ICの近くに帰還抵抗分圧器を配置し、帰還接続はインダクタと LX ノードおよび他のノイズの多い信号からは遠ざけて配線します。

図 1. PCB レイアウトの例

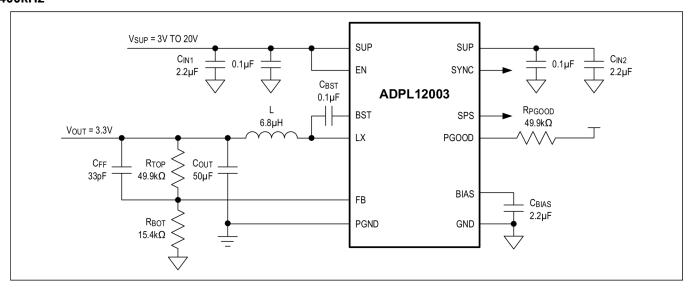

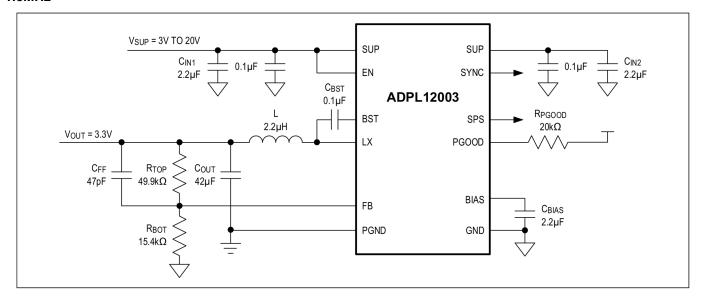

### 標準アプリケーション回路

#### 400kHz

### 1.5MHz

# 20V、2.5A/3.5A の全機能内蔵同期整流式降圧コンバータ

### オーダー情報

| PART NUMBER    | V <sub>OUT</sub> (V)   | MAXIMUM LOAD<br>CURRENT (A) | SWITCHING<br>FREQUENCY | SPREAD SPECTRUM (%) |

|----------------|------------------------|-----------------------------|------------------------|---------------------|

| ADPL12002AFLA+ | Adjustable 0.8V to 12V | 2.5A                        | 400kHz                 | ±6%                 |

| ADPL12002AFLB+ | Adjustable 0.8V to 12V | 2.5A                        | 1.5MHz                 | ±6%                 |

| ADPL12003AFLA+ | Adjustable 0.8V to 12V | 3.5A                        | 400kHz                 | ±6%                 |

| ADPL12003AFLB+ | Adjustable 0.8V to 12V | 3.5A                        | 1.5MHz                 | ±6%                 |

# 20V、2.5A/3.5A の全機能内蔵同期整流式降圧コンバータ

### 改訂履歴

| 版数 | 改訂日  | 説明   | 改訂ページ |

|----|------|------|-------|

| 0  | 5/25 | 初版発行 | -     |