## マルチモード・センサー・フロント・エンド

### 特長

- ▶ マルチモード・アナログ・フロント・エンド

- ▶ 光学チャンネル

- ▶ 様々なセンサー計測に対応した複数の動作モードを備える4つの入力チャンネル

- ▶ 同時サンプリングによる4チャンネル処理

- ▶ 同期されたセンサー計測が可能な12のプログラマブル・タイム・スロット

- ▶ シングルエンドのセンサー計測に対応する柔軟性に優れた入力マルチブレクス

- ▶ 2個のLEDを同時に駆動できる8つのLEDドライバ

- ▶ 内部発振器を使用した0.004Hz～9kHzの柔軟なサンプリング・レート

- ▶ AC周辺光の除去：78dB（最大100Hz）

- ▶ LEDのピーク駆動電流の合計：400mA

- ▶ 9ビットの制御（最大300μA）に対応した、TIA入力での個別の周辺光キャンセルDAC

- ▶ 7ビットの制御（最大190μA）に対応した、TIA入力での個別のLED DCキャンセルDAC

- ▶ ECGチャンネル

- ▶ 診断帯域幅でのRTIノイズ： $<1\mu\text{V RMS}$

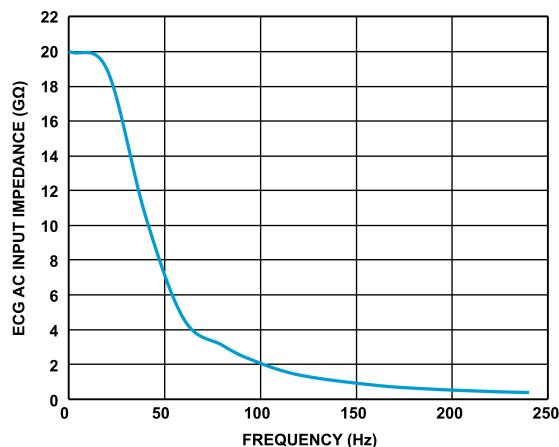

- ▶ 高入力インピーダンス：20GΩ

- ▶ 最大±1.2VのDC差動入力範囲に対応

- ▶ CMRR：115dB

- ▶ 様々なアプリケーションをサポートする柔軟性に優れた4電極構成

- ▶ ACリードオフ検出とDCリードオフ検出の両方をサポート

- ▶ 常時オン、低消費電力、リードオン検出をサポート

- ▶ BIAチャンネル

- ▶ 低消費電力、高精度励起パス

- ▶ 最大250kHzまで設定可能な励起周波数

- ▶ 12ビットDACによるサイン波励起

- ▶ 大きな不平衡接触インピーダンス（ $\leq 20\text{k}\Omega$ ）による高精度

- ▶ 低ノイズ設計の設定可能な受信フィルタ

- ▶ 複素インピーダンス測定エンジン

- ▶ 電流制限用の抵抗を内蔵

- ▶ EDAチャンネル

- ▶ 電圧励起と電流励起の両方をサポート

- ▶ 測定範囲：1nSの分解能で10kΩ～100MΩ

- ▶ DFTとデシメーションによる高精度の測定結果

- ▶ SPI通信に対応

- ▶ 704バイトのFIFO

### アプリケーション

- ▶ 健康/フィットネス・モニタ用ウェアラブル機器：心拍数、心拍数変化、パルス・オキシメータによる酸素飽和度、生体インピーダンス解析、体内水分量解析、カフなし非侵襲的血圧

- ▶ 臨床患者のモニタ：ベッドサイド用小型機器、自宅患者用携帯型機器、遠隔地用小型機器

- ▶ 工業用モニタリング：粒子、エアロゾル、およびガスの検出

- ▶ 導電率の検出

### 概要

ADPD7000は、様々な生体信号を測定するための高集積アナログ・フロント・エンド（AFE）です。

光学チャンネルは光トランシーバーとして設計され、最大8個の発光ダイオード（LED）を励起し、リターン信号を最大4つの個別の電流入力で測定します。シグナル・チェーンは、一般に周辺光によって生じる非同期の変調干渉に起因する信号のオフセットや破損を除去することができ、光学フィルタや外部制御のDCキャンセル回路は不要です。

心電図（ECG）信号の取得については、様々な干渉源がある状態で、低ノイズの診断レベル測定に対応できるよう設計されています。ECGシグナル・チェーンには、同相ノイズ除去用に駆動されるリファレンス機能、エレクトロードの接続が外れたことを特定するリードオフ検出機能など、ECG測定を支援する補完機能が数多く備わっています。

生体インピーダンス解析（BIA）のシグナル・チェーンは、構成設定可能な励起パスと測定パスを使用した、生体インピーダンスの測定用に設計されています。励起パスに12ビットのD/Aコンバータ（DAC）を使用してサイン波を生成し、構成設定可能なフィルタを使用した高精度測定によって刺激に対する体の反応を測定します。

皮膚電気活動（EDA）のシグナル・チェーンは、皮膚電気活動用に設計されています。BIAとECGの周辺回路をマルチブレクスすることにより、ADPD7000は1nSの分解能で高精度のAC測定とDC測定をサポートします。

データ出力と機能設定には、ADPD7000のシリアル・ポート・インターフェース（SPI）を使用します。制御回路には、柔軟なLED信号伝送および同期検出機能、デジタル・フィルタ、デジタル波形ジェネレータ、構成設定可能なフィルタが備わっています。

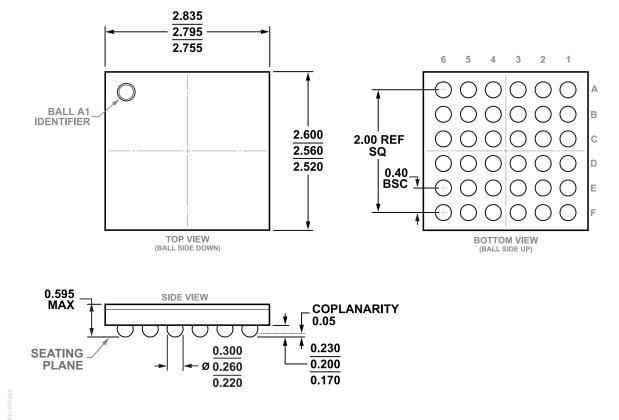

ADPD7000は、2.795mm×2.560mm、0.40mmピッチの36ボールWLCSPパッケージを採用しています。

## 目次

|                |    |

|----------------|----|

| 特長             | 1  |

| アプリケーション       | 1  |

| 概要             | 1  |

| 機能プロック図        | 3  |

| 仕様             | 4  |

| 温度と電力の仕様       | 4  |

| 性能仕様           | 4  |

| デジタル仕様         | 7  |

| タイミング仕様        | 8  |

| 絶対最大定格         | 9  |

| 熱抵抗            | 9  |

| 静電放電（ESD）定格    | 9  |

| ESD に関する注意     | 9  |

| ピン配置およびピン機能の説明 | 10 |

| 代表的な性能特性       | 12 |

| 動作原理           | 16 |

| はじめに           | 16 |

| タイミング・スロット動作   | 16 |

| リードオン検出        | 17 |

| 光シグナル・チェーン     | 17 |

| ECG シグナル・チェーン  | 19 |

|                |     |

|----------------|-----|

| BIA シグナル・チェーン  | 20  |

| EDA 信号パス       | 21  |

| FIFO           | 21  |

| クロッキング         | 23  |

| タイム・スタンプ動作     | 23  |

| 実行モード          | 24  |

| ホスト・インターフェース   | 25  |

| アプリケーション情報     | 27  |

| リードオンのアプリケーション | 27  |

| 光路             | 27  |

| ECG パス         | 30  |

| BIA パス         | 33  |

| EDA パス         | 33  |

| マルチモード         | 35  |

| 設計ガイド          | 36  |

| レジスタの一覧        | 38  |

| レジスタの詳細        | 89  |

| 外形寸法           | 127 |

| オーダー・ガイド       | 127 |

| 評価用ボード         | 127 |

## 改訂履歴

4/2023—Revision 0: Initial Version

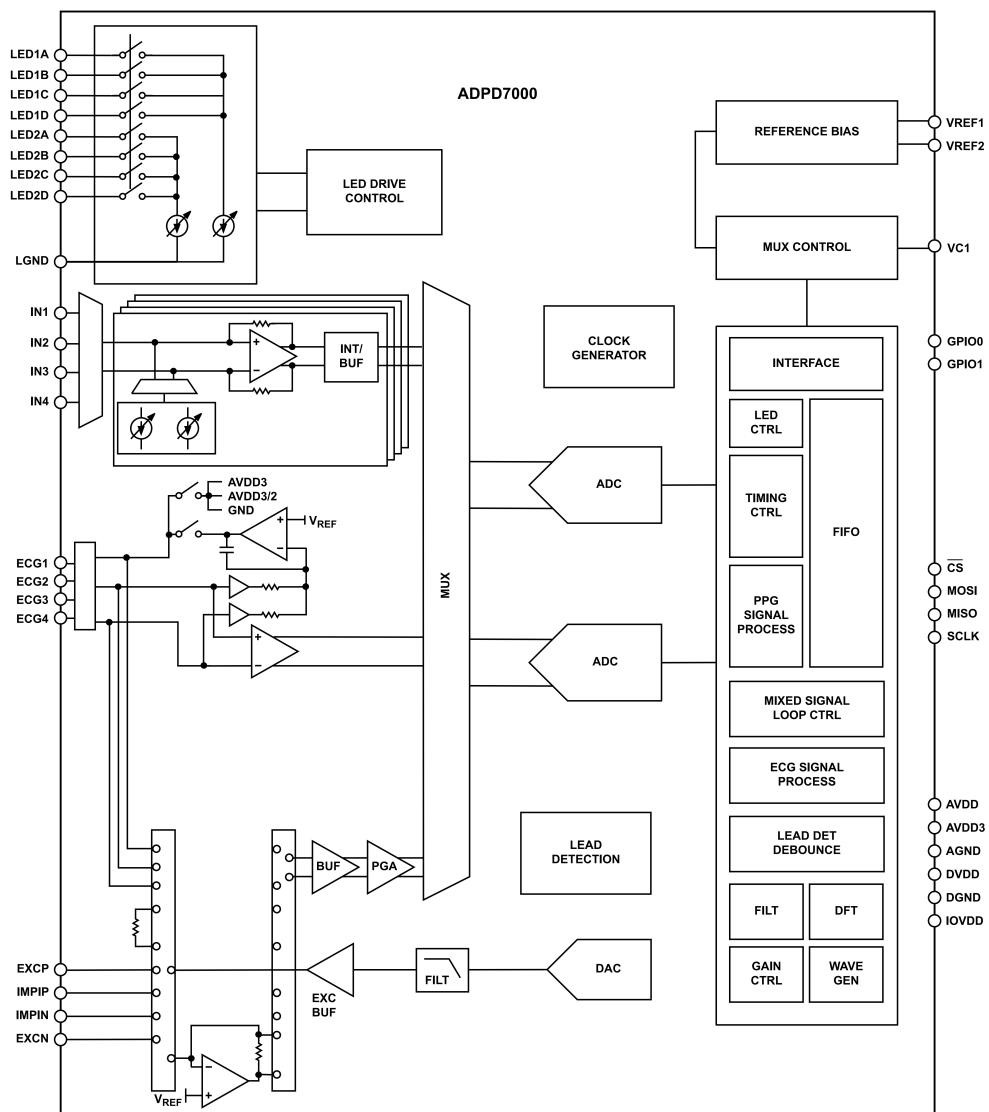

## 機能ブロック図

図 1. 機能ブロック図

## 仕様

## 温度と電力の仕様

表 1. 温度と電力の仕様

| Parameter             | Min | Typ | Max  | Unit |

|-----------------------|-----|-----|------|------|

| TEMPERATURE RANGE     |     |     |      |      |

| Operating Range       | -40 |     | +85  | °C   |

| Storage Range         | -65 |     | +150 | °C   |

| POWER SUPPLY VOLTAGES |     |     |      |      |

| AVDD                  | 1.7 | 1.8 | 1.9  | V    |

| AVDD3                 | 2.7 | 3.3 | 3.6  | V    |

| DVDD                  | 1.7 | 1.8 | 1.9  | V    |

| IOVDD                 | 1.7 | 1.8 | 3.6  | V    |

## 性能仕様

特に指定のない限り、AVDD = DVDD = IOVDD = 1.8V、AVDD3 = 3.3V、T<sub>A</sub> = 25°C。

表 2. 性能仕様

| Parameter                                    | Test Condition/Comments                          | Min  | Typ   | Max | Unit   |

|----------------------------------------------|--------------------------------------------------|------|-------|-----|--------|

| DATA ACQUISITION                             |                                                  |      |       | 32  | Bits   |

| Datapath Width                               |                                                  |      |       | 704 | Bytes  |

| FIRST IN, FIRST OUT (FIFO) SIZE              |                                                  |      |       |     |        |

| INTERNAL 960 kHz OSCILLATOR ACCURACY         | Full temperature range (-40°C to +85°C)          |      | ±1    |     | %      |

| PHOTOPLETHYSMOGRAPHY (PPG) CHANNEL           |                                                  |      |       |     |        |

| Transimpedance Amplifier (TIA) Gain          |                                                  | 12.5 |       | 400 | kΩ     |

| DIGITAL INTEGRATION MODE                     |                                                  |      |       |     |        |

| Analog-to-Digital Converter (ADC) Resolution | TIA feedback resistor (R <sub>F</sub> )          |      |       |     |        |

|                                              | 12.5 kΩ                                          |      | 5.84  |     | nA/LSB |

|                                              | 25 kΩ                                            |      | 2.92  |     | nA/LSB |

|                                              | 50 kΩ                                            |      | 1.46  |     | nA/LSB |

|                                              | 100 kΩ                                           |      | 0.73  |     | nA/LSB |

|                                              | 200 kΩ                                           |      | 0.365 |     | nA/LSB |

|                                              | 400 kΩ                                           |      | 0.183 |     | nA/LSB |

| ADC Saturation Level                         | TIA feedback resistor                            |      |       |     |        |

|                                              | 12.5 kΩ                                          |      | 48    |     | µA     |

|                                              | 25 kΩ                                            |      | 24    |     | µA     |

|                                              | 50 kΩ                                            |      | 12    |     | µA     |

|                                              | 100 kΩ                                           |      | 6     |     | µA     |

|                                              | 200 kΩ                                           |      | 3     |     | µA     |

|                                              | 400 kΩ                                           |      | 1.5   |     | µA     |

| DC Ambient Light Rejection (ALR)             |                                                  |      |       |     |        |

| ALR Range                                    |                                                  | 0    |       | 300 | µA     |

| ALR Resolution                               |                                                  |      | 0.6   |     | µA     |

| LED DC Cancellation                          |                                                  |      |       |     |        |

| Range                                        |                                                  | 0    |       | 190 | µA     |

| Resolution                                   |                                                  |      | 1.48  |     | µA     |

| Dark Noise                                   | Pulse = 1, ADC sample = 20<br>TIA gain = 12.5 kΩ |      | 1590  |     | pA RMS |

## 仕様

表 2. 性能仕様 (続き)

| Parameter                                                                    | Test Condition/Comments                                                                                                                                                                                                                                                                       | Min                                                                    | Typ         | Max | Unit                                                                                   |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------|-----|----------------------------------------------------------------------------------------|

| Signal-to-Noise Ratio (SNR)                                                  | TIA gain = 25 kΩ<br>TIA gain = 50 kΩ<br>TIA gain = 100 kΩ<br>TIA gain = 200 kΩ<br>TIA gain = 400 kΩ<br><br>White card reflection, pulse = 1, ADC sample = 20<br><br>TIA gain = 12.5 kΩ<br>TIA gain = 25 kΩ<br>TIA gain = 50 kΩ<br>TIA gain = 100 kΩ<br>TIA gain = 200 kΩ<br>TIA gain = 400 kΩ | 867<br>425<br>235<br>140<br>92<br><br>90<br>90<br>88<br>87<br>85<br>82 |             |     | pA RMS<br>pA RMS<br>pA RMS<br>pA RMS<br>pA RMS<br><br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| AC ALR                                                                       | Up to 100 Hz                                                                                                                                                                                                                                                                                  | 84                                                                     |             |     | dB                                                                                     |

| DC Power Supply Rejection Ratio (PSRR)                                       | At 75% full-scale (FS) input, optimal settings, all gains <sup>1</sup>                                                                                                                                                                                                                        | 60                                                                     |             |     | dB                                                                                     |

| LED DRIVER                                                                   |                                                                                                                                                                                                                                                                                               |                                                                        |             |     |                                                                                        |

| Peak Current per Driver                                                      | LED pulse enabled                                                                                                                                                                                                                                                                             | 200                                                                    |             |     | mA                                                                                     |

| Peak Current, Total                                                          | Using multiple LED drivers simultaneously                                                                                                                                                                                                                                                     | 400                                                                    |             |     | mA                                                                                     |

| Current Step                                                                 | High SNR mode                                                                                                                                                                                                                                                                                 | 1.57                                                                   |             |     | mA                                                                                     |

|                                                                              | Low compliance mode                                                                                                                                                                                                                                                                           | 0.78                                                                   |             |     | mA                                                                                     |

| Compliance Voltage                                                           | High SNR mode                                                                                                                                                                                                                                                                                 | 400                                                                    |             |     | mV                                                                                     |

|                                                                              | Low compliance mode                                                                                                                                                                                                                                                                           | 200                                                                    |             |     | mV                                                                                     |

| Power                                                                        | AFE current only, 70% FS output data rate (ODR) = 25 Hz                                                                                                                                                                                                                                       |                                                                        |             |     |                                                                                        |

| Standby                                                                      | DVDD + AVDD                                                                                                                                                                                                                                                                                   | 0.3                                                                    |             |     | µA                                                                                     |

| Typical Heart Rate Monitor (HRM) Application                                 | DVDD + AVDD                                                                                                                                                                                                                                                                                   | 18.7                                                                   |             |     | µA                                                                                     |

| SAMPLING RATE                                                                |                                                                                                                                                                                                                                                                                               | 0.004                                                                  | 9000        |     | Hz                                                                                     |

| ECG CHANNEL                                                                  |                                                                                                                                                                                                                                                                                               |                                                                        |             |     |                                                                                        |

| Input Bias Current                                                           | Resolution is 286 nV, unless otherwise noted<br><br>ECG input pins, room temperature, lead off detection is off, measured at dc                                                                                                                                                               | 22                                                                     |             |     | pA                                                                                     |

| Input Impedance                                                              | ECG input pins, measured at dc                                                                                                                                                                                                                                                                | 20                                                                     |             |     | GΩ                                                                                     |

| Differential Input Range                                                     |                                                                                                                                                                                                                                                                                               | -1.2                                                                   | +1.2        |     | V                                                                                      |

| Electrode Single-Ended Input Voltage Range                                   |                                                                                                                                                                                                                                                                                               | 0.2                                                                    | AVDD3 - 0.2 |     | V                                                                                      |

| Input Common-Mode Range                                                      |                                                                                                                                                                                                                                                                                               | 0.4                                                                    | AVDD3 - 0.4 |     | V                                                                                      |

| -3 dB Monitor Bandwidth                                                      | Data rate = 250 SPS                                                                                                                                                                                                                                                                           | 40                                                                     |             |     | Hz                                                                                     |

| -3 dB Diagnostic Bandwidth                                                   | Data rate = 500 SPS                                                                                                                                                                                                                                                                           | 150                                                                    |             |     | Hz                                                                                     |

| Gain Flatness                                                                | DC to 5.3 Hz (data rate = 250 SPS)<br>DC to 19 Hz (data rate = 500 SPS)                                                                                                                                                                                                                       | ±1                                                                     | ±1.5        |     | %                                                                                      |

| Gain Error                                                                   |                                                                                                                                                                                                                                                                                               | -2                                                                     | +2          |     | %                                                                                      |

| Resolution                                                                   |                                                                                                                                                                                                                                                                                               | 286                                                                    | 572         |     | nV/LSB                                                                                 |

| Input Referred Noise                                                         |                                                                                                                                                                                                                                                                                               |                                                                        |             |     | nV/LSB                                                                                 |

| 10 Sec Measurement Using Internal Shorted Mode, Measured at Room Temperature | Data rate = 250 SPS, monitoring filter bandwidth (40 Hz)<br>Data rate = 500 SPS, diagnostic filter bandwidth (150 Hz)                                                                                                                                                                         | 0.38                                                                   | 0.86        |     | µV RMS                                                                                 |

| 10 Sec System Level Measurement with Proper Electrode Model and              | Data rate = 250 SPS, monitoring filter bandwidth (40 Hz)<br>Data rate = 500 SPS, diagnostic filter bandwidth (150 Hz)                                                                                                                                                                         | 0.5                                                                    | 0.937       |     | µV RMS                                                                                 |

## 仕様

表 2. 性能仕様 (続き)

| Parameter                                                         | Test Condition/Comments                                                                                                                                                                                                                                                                      | Min         | Typ         | Max   | Unit    |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------|---------|

| All Functions Enabled (DC Lead Off (DCLO) and AC Lead Off (ACLO)) |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Channel Common-Mode Rejection Ratio (CMRR)                        | Balanced mode, measured at 60 Hz                                                                                                                                                                                                                                                             |             | 115         |       | dB      |

| Output Date Rate                                                  | Aligned with filter design                                                                                                                                                                                                                                                                   | 250         |             | 4000  | Hz      |

| ECG Channel Enable Time                                           | Data rate of 500 SPS                                                                                                                                                                                                                                                                         |             | 15          |       | ms      |

| Overload Recovery Time                                            |                                                                                                                                                                                                                                                                                              |             | 10          |       | ms      |

| ECG Channel Power                                                 | ODR = 500 Hz, ACLO and DCLO functions enabled, resolution = 286 nV/LSB                                                                                                                                                                                                                       |             | 1.7         |       | mW      |

| DCLO DETECTION                                                    |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Drive Circuit                                                     |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Lead Off Current Range                                            | Lead fail current is programmable over the specified range, programmed current magnitude setting applies across all electrode pins, current polarity is programmable on individual electrode basis                                                                                           | 0           | 1.1         |       | µA      |

| Measure Circuit                                                   |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Right Leg Driver (RLD) <sup>2</sup> Lead Off Thresholds           |                                                                                                                                                                                                                                                                                              | AVDD3 - 0.8 | AVDD3 - 0.2 |       | V       |

| High                                                              |                                                                                                                                                                                                                                                                                              | AVDD3 - 0.8 | AVDD3 - 0.2 |       | V       |

| Low                                                               |                                                                                                                                                                                                                                                                                              | 0.2         | 0.8         |       | V       |

| ACLO THRESHOLD                                                    |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Drive Circuit                                                     |                                                                                                                                                                                                                                                                                              |             | 4           |       | kHz     |

| Excitation Frequency                                              |                                                                                                                                                                                                                                                                                              | 0           | 70          |       | nA      |

| Current                                                           |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Measure Circuit                                                   |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Threshold                                                         |                                                                                                                                                                                                                                                                                              | 0.04        | 2.33        |       | nF      |

| RLD                                                               |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Output Voltage                                                    |                                                                                                                                                                                                                                                                                              | GND         | AVDD3/2     | AVDD3 | V       |

| Stable Load Capacitance                                           |                                                                                                                                                                                                                                                                                              |             |             | 2.2   | nF      |

| BIA CHANNEL SYSTEM PERFORMANCE                                    | For impedance ( $Z$ ) = 1 kΩ (0.1% tolerant resistor), excitation frequency ( $f_{EXCITATION}$ ) = 50 kHz, sine amplitude = 0.6 V p-p, TIA resistor ( $R_{TIA}$ ) = 2 kΩ, TIA capacitor ( $C_{TIA}$ ) = 7 pF, isolation capacitor = 470 nF, current-limiting resistor ( $R_{LIMIT}$ ) = 1 kΩ |             |             |       |         |

| Total System Accuracy                                             |                                                                                                                                                                                                                                                                                              |             | 0.26        |       | %       |

| Magnitude                                                         |                                                                                                                                                                                                                                                                                              |             | 1           |       | Degrees |

| Phase                                                             |                                                                                                                                                                                                                                                                                              |             | 0.26        |       | %       |

| Body Impedance Magnitude Error                                    | Contact resistor $\leq$ 1 kΩ                                                                                                                                                                                                                                                                 |             | 5           |       | %       |

|                                                                   | Contact resistor $\leq$ 20 kΩ                                                                                                                                                                                                                                                                |             | 0.1         |       | %       |

| Body Impedance Magnitude Repeatability                            | Room temperature, test 10 times, contact resistor $<$ 1 kΩ                                                                                                                                                                                                                                   |             | 1           |       | Degrees |

| Body Phase Angle Error                                            |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| TRANSMIT STAGE                                                    |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Output Frequency Range                                            |                                                                                                                                                                                                                                                                                              | 50          | 250         |       | kHz     |

| Output Frequency Resolution                                       |                                                                                                                                                                                                                                                                                              | 0.48        |             |       | Hz      |

| Output Voltage Range                                              |                                                                                                                                                                                                                                                                                              |             | 800         |       | mV      |

| Output Voltage Resolution                                         |                                                                                                                                                                                                                                                                                              |             | 0.39        |       | mV      |

| RECEIVE STAGE                                                     |                                                                                                                                                                                                                                                                                              |             |             |       |         |

| Input Leakage Current                                             |                                                                                                                                                                                                                                                                                              | 10          |             |       | pF      |

| Input Capacitance                                                 | Toward ground for current sensing                                                                                                                                                                                                                                                            | 10          |             |       | pF      |

|                                                                   | Toward ground for voltage sensing                                                                                                                                                                                                                                                            |             |             |       |         |

## 仕様

表 2. 性能仕様 (続き)

| Parameter                                 | Test Condition/Comments                                                                                                                                                                                                                               | Min                    | Typ  | Max  | Unit               |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|--------------------|

| ADC Saturation Level                      | Voltage<br>Current ( $R_{TIA} = 2\text{ k}\Omega$ )                                                                                                                                                                                                   | $\pm 0.8$<br>$\pm 400$ |      |      | V<br>$\mu\text{A}$ |

| CALIBRATION RESISTOR<br>Internal          |                                                                                                                                                                                                                                                       |                        | 2    |      | $\text{k}\Omega$   |

| Power Consumption                         | ODR = 30 Hz, DFT = 1024, $R_{TIA} = 2\text{ k}\Omega$ , $V_{EXCITATION\ p-p} = 600\text{ mV}$ ,<br>contact resistor ( $R_{CONTACT}$ ) = body resistor ( $R_{BODY}$ ) = 1 $\text{k}\Omega$ , $f_{EXCITATION} = 50\text{ kHz}$ , 12 $\times$ time slots |                        | 11.2 |      | $\text{mW}$        |

| EDA CHANNEL                               |                                                                                                                                                                                                                                                       |                        |      |      |                    |

| TIA Gain                                  | TIA feedback resistor                                                                                                                                                                                                                                 | 1                      | 1.5  | 1000 | $\text{k}\Omega$   |

| Programmable Gain Amplifier (PGA)<br>Gain |                                                                                                                                                                                                                                                       | 2<br>3<br>6            |      |      |                    |

| Discrete Fourier Transform (DFT) Points   |                                                                                                                                                                                                                                                       | 4                      | 8192 |      |                    |

| DC Current Range                          | For DC current mode                                                                                                                                                                                                                                   | 0.002                  | 1.1  |      | $\mu\text{A}$      |

| DC Excitation Voltage                     | For DC voltage mode                                                                                                                                                                                                                                   | 0.5                    | 1.3  |      | V                  |

| AC Voltage Excitation                     | For AC voltage mode                                                                                                                                                                                                                                   |                        | 800  |      | $\text{mV}$        |

| AC Voltage Frequency                      | For AC voltage mode                                                                                                                                                                                                                                   |                        | 100  |      | Hz                 |

| Impedance Measurement                     |                                                                                                                                                                                                                                                       |                        |      |      |                    |

| Range                                     |                                                                                                                                                                                                                                                       | 0.01                   | 100  |      | $\text{M}\Omega$   |

| Resolution                                |                                                                                                                                                                                                                                                       | 1                      |      |      | $\text{nS}$        |

| Error                                     |                                                                                                                                                                                                                                                       |                        | 5    |      | %                  |

| Power Consumption                         | ODR = 1 Hz, sampling frequency ( $f_S$ ) = 2.5 $\text{k}\Omega$ , DFT = 512, DCLO current ( $I_{DCLO}$ ) = 6 nA, $R_{TIA} = 1\text{ M}\Omega$ , body impedance ( $Z_{BODY}$ ) = 1 $\text{M}\Omega$                                                    | 0.78                   |      |      | $\text{mW}$        |

<sup>1</sup> DC PSRR =  $20 \times \log((\text{信号}(LSB)/\text{NUM\_INT\_x}/\text{NUM\_REPEAT\_x} \times 0.146\text{mV}/\text{LSB})/V_{IN}(\text{mV}))$

<sup>2</sup> ECG 信号 (RLD、ECGIP、およびECGIN) は、ECG\_MATRIX レジスタを設定することにより、ECG1～ECG4 ピンのどれか1つに接続することができます。

## デジタル仕様

特に指定のない限り、IOVDD = 1.7V～3.6V。

表 3. デジタル仕様

| Parameter                                              | Test Condition/Comments        | Min                | Typ | Max                 | Unit          |

|--------------------------------------------------------|--------------------------------|--------------------|-----|---------------------|---------------|

| LOGIC INPUTS                                           |                                |                    |     |                     |               |

| Input Voltage Level<br>GPIOx, MISO, MOSI, SCLK, and CS |                                |                    |     |                     |               |

| High                                                   |                                | 0.7 $\times$ IOVDD |     | IOVDD + 0.3         | V             |

| Low                                                    |                                | -0.3               |     | +0.3 $\times$ IOVDD | V             |

| Input Current Level                                    | All logic inputs               |                    |     |                     |               |

| High                                                   |                                |                    | 10  |                     | $\mu\text{A}$ |

| Low                                                    |                                | -10                |     |                     | $\mu\text{A}$ |

| Input Capacitance                                      |                                | 2                  |     |                     | pF            |

| LOGIC OUTPUTS                                          |                                |                    |     |                     |               |

| Output Voltage Level<br>GPIOx and MISO                 |                                |                    |     |                     |               |

| High                                                   | 2 mA high level output current | IOVDD - 0.5        |     |                     | V             |

| Low                                                    | 2 mA low level output current  |                    | 0.5 |                     | V             |

## 仕様

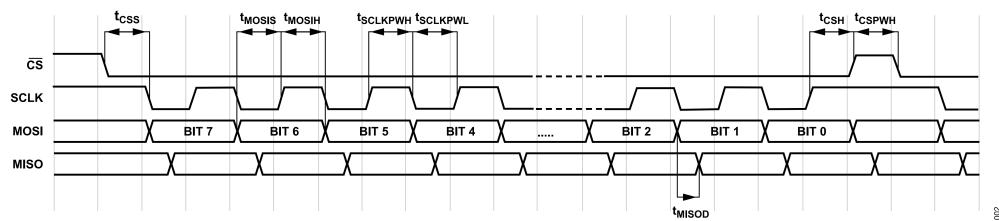

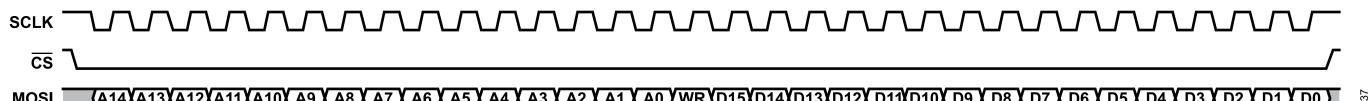

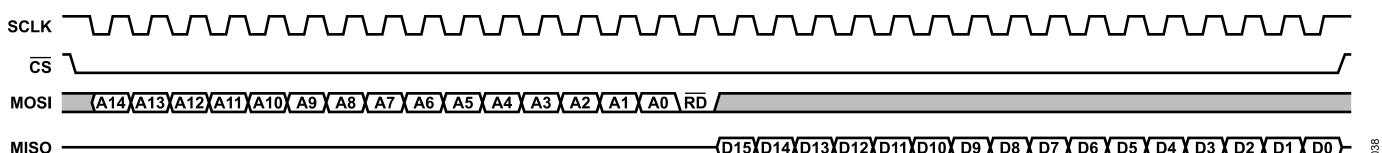

## タイミング仕様

表 4. タイミング仕様

| Parameter                 | Symbol        | Test Condition/Comments                                                                                                                                            | Min | Typ  | Max | Unit |

|---------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| SPI PORT                  |               |                                                                                                                                                                    |     |      |     |      |

| SCLK                      | $f_{SCLK}$    |                                                                                                                                                                    |     |      | 10  | MHz  |

| Frequency                 |               |                                                                                                                                                                    |     |      |     |      |

| Minimum Pulse Width       |               |                                                                                                                                                                    |     |      |     |      |

| High                      | $t_{SCLKPWH}$ |                                                                                                                                                                    | 15  |      |     | ns   |

| Low                       | $t_{SCLKPWL}$ |                                                                                                                                                                    | 15  |      |     | ns   |

| $\overline{CS}$           |               |                                                                                                                                                                    |     |      |     |      |

| Setup Time                | $t_{CSS}$     | $\overline{CS}$ setup to SCLK rising edge                                                                                                                          | 11  |      |     | ns   |

| Hold Time                 | $t_{CSH}$     | $\overline{CS}$ hold from SCLK rising edge                                                                                                                         | 5   |      |     | ns   |

| Pulse Width High          | $t_{CSPWH}$   | $\overline{CS}$ pulse width high                                                                                                                                   | 15  |      |     | ns   |

| MOSI                      |               |                                                                                                                                                                    |     |      |     |      |

| Setup Time                | $t_{MOSIS}$   | MOSI setup to SCLK rising edge                                                                                                                                     | 5   |      |     | ns   |

| Hold Time                 | $t_{MOSIH}$   | MOSI hold from SCLK rising edge                                                                                                                                    | 5   |      |     | ns   |

| SWITCHING CHARACTERISTICS |               |                                                                                                                                                                    |     |      |     |      |

| MISO Output Delay         | $t_{MISOD}$   | MISO valid output delay from SCLK falling edge<br>Register 0x057 = 0x0050 (default)<br>Register 0x057 = 0x005F (maximum slew rate, maximum drive strength for SPI) |     | 21.5 | ns  |      |

|                           |               |                                                                                                                                                                    |     | 14   | ns  |      |

## タイミング図

図 2. SPI タイミング図

## 絶対最大定格

表 5. 絶対最大定格

| Parameter                           | Rating           |

|-------------------------------------|------------------|

| AVDD to AGND                        | -0.3 V to +2.2 V |

| AVDD3 to AGND                       | -0.3 V to +3.9 V |

| DVDD to DGND                        | -0.3 V to +2.2 V |

| IOVDD to LGND                       | -0.3 V to +3.9 V |

| GPIOx, MOSI, MISO, SCLK, CS to DGND | -0.3 V to +3.9 V |

| LEDxx to LGND                       | -0.3 V to +3.9 V |

| Junction Temperature                | 150°C            |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意が必要です。

$\theta_{JA}$  は、1 立方フィートの密閉容器内で測定された、自然体流での周囲とジャンクションの間の熱抵抗です。 $\theta_{JC}$  は、ジャンクションとケースの間の熱抵抗です。

表 6. 热抵抗

| Package Type          | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|-----------------------|---------------|---------------|------|

| CB-36-11 <sup>1</sup> | 42.15         | 0.98          | °C/W |

<sup>1</sup> 热抵抗値は、JESD51-12 規格によって規定されています。

## 静電放電（ESD）定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル（HBM）。

ANSI/ESDA/JEDEC JS-002 準拠の帯電デバイス・モデル（CDM）。

ANSI/ESD STM5.2 によるマシン・モデル（MM）。MM 電圧値は特性評価にのみ使われます。

## ADPD7000 の ESD 定格

表 7. ADPD7000、36 ポール WLCSP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 2500                    | 2     |

| CDM       | 1250                    | C3    |

## ESD に関する注意

|                                                                                    |                                                                                                                                                                                               |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。 |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

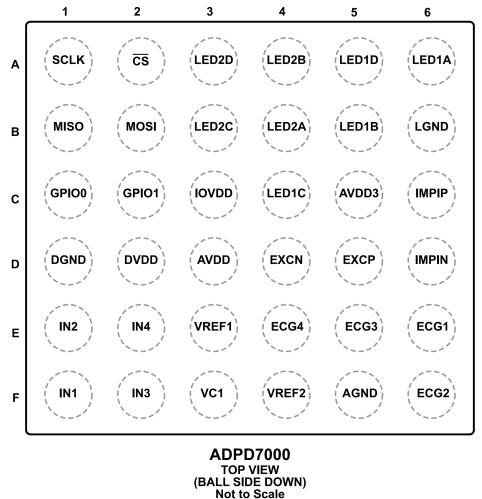

## ピン配置およびピン機能の説明

図 3. ピン配置、上面図

表 8. ピン機能の説明

| ピン番号 | 記号    | タイプ     | 説明                                            |

|------|-------|---------|-----------------------------------------------|

| D3   | AVDD  | Power   | 1.8V アナログ電源。                                  |

| C5   | AVDD3 | Power   | 3.3V アナログ電源。                                  |

| F5   | AGND  | Power   | アナログ・グラウンド。                                   |

| D2   | DVDD  | Power   | 1.8V デジタル電源。                                  |

| D1   | DGND  | Power   | デジタル・グラウンド。                                   |

| C3   | IOVDD | Power   | 入出力電源。                                        |

| B6   | LGND  | Power   | LED グラウンド。                                    |

| E3   | VREF1 | Analog  | ADC1 リファレンス。                                  |

| F4   | VREF2 | Analog  | ADC2 リファレンス。                                  |

| F3   | VC1   | Analog  | フォト・ダイオードのコモン・カソード・バイアス、または他のセンサー励起用の出力電圧源 1。 |

| F1   | IN1   | Analog  | 電流入力 1。                                       |

| E1   | IN2   | Analog  | 電流入力 2。                                       |

| F2   | IN3   | Analog  | 電流入力 3。                                       |

| E2   | IN4   | Analog  | 電流入力 4。                                       |

| A6   | LED1A | Analog  | LED ドライバ 1A。                                  |

| B5   | LED1B | Analog  | LED ドライバ 1B。                                  |

| C4   | LED1C | Analog  | LED ドライバ 1C。                                  |

| A5   | LED1D | Analog  | LED ドライバ 1D。                                  |

| B4   | LED2A | Analog  | LED ドライバ 2A。                                  |

| A4   | LED2B | Analog  | LED ドライバ 2B。                                  |

| B3   | LED2C | Analog  | LED ドライバ 2C。                                  |

| A3   | LED2D | Analog  | LED ドライバ 2D。                                  |

| E6   | ECG1  | Analog  | ECG エレクトロード・パッド 1。                            |

| F6   | ECG2  | Analog  | ECG エレクトロード・パッド 2。                            |

| E5   | ECG3  | Analog  | ECG エレクトロード・パッド 3。                            |

| E4   | ECG4  | Analog  | ECG エレクトロード・パッド 4。                            |

| C6   | IMPIP | Analog  | BIA 正入力。                                      |

| D6   | IMPIN | Analog  | BIA 負入力。                                      |

| D5   | EXCP  | Analog  | BIA 励起正出力。                                    |

| D4   | EXCN  | Analog  | BIA 励起負出力。                                    |

| A2   | CS    | Digital | SPI チップ・セレクト入力。                               |

表 8. ピン機能の説明（続き）

| ピン番号 | 記号    | タイプ     | 説明                   |

|------|-------|---------|----------------------|

| A1   | SCLK  | Digital | SPI クロック入力。          |

| B1   | MISO  | Digital | SPI コントローラ入力および目標出力。 |

| B2   | MOSI  | Digital | SPI コントローラ出力および目標入力。 |

| C1   | GPIO0 | Digital | 汎用入出力 0。             |

| C2   | GPIO1 | Digital | 汎用入出力 1。             |

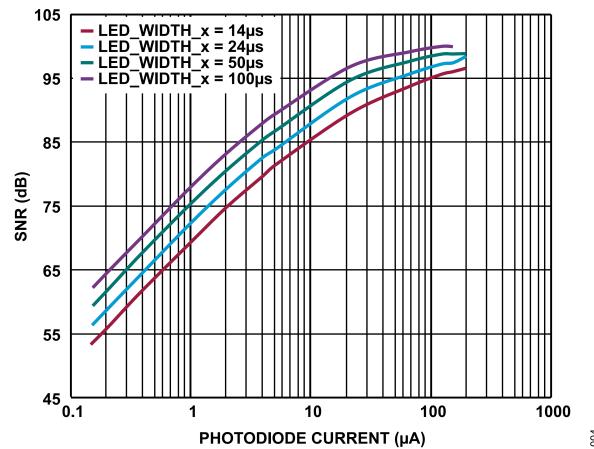

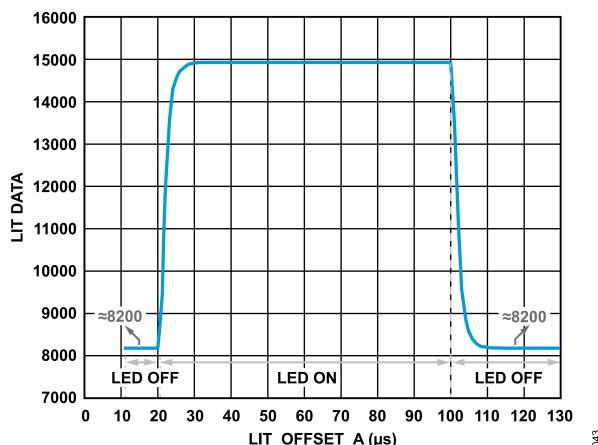

## 代表的な性能特性

特に指定のない限り、DVDD = AVDD = 1.8V、AVDD3 = 3.3V、LGND = DGND = AGND = 0V、 $T_A = 25^\circ\text{C}$ 。

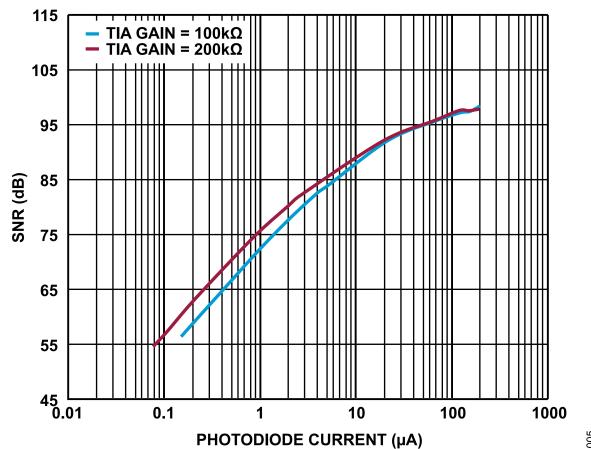

図 4. S/N 比とフォト・ダイオード電流の関係、

シーケンスの繰り返し回数 = 1、TIA ゲイン = 100k $\Omega$

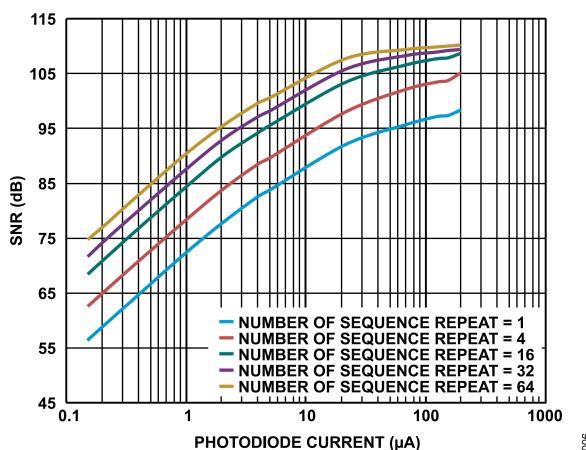

図 5. S/N 比とフォト・ダイオード電流の関係、LED 幅 = 24μs、

シーケンスの繰り返し回数 = 1

図 6. S/N 比とフォト・ダイオード電流の関係、LED 幅 = 24μs、

TIA ゲイン = 100k $\Omega$

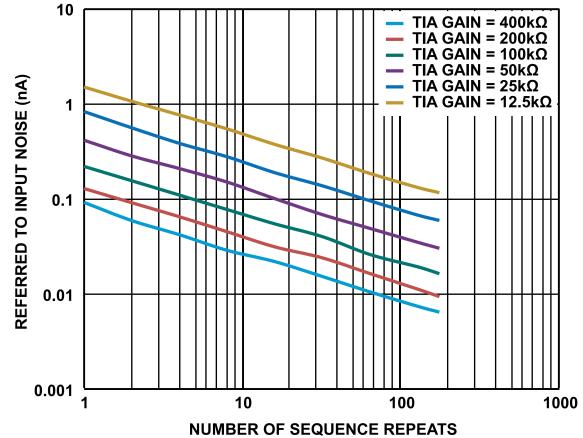

図 7. 入力換算ノイズとシーケンスの繰り返し回数の関係

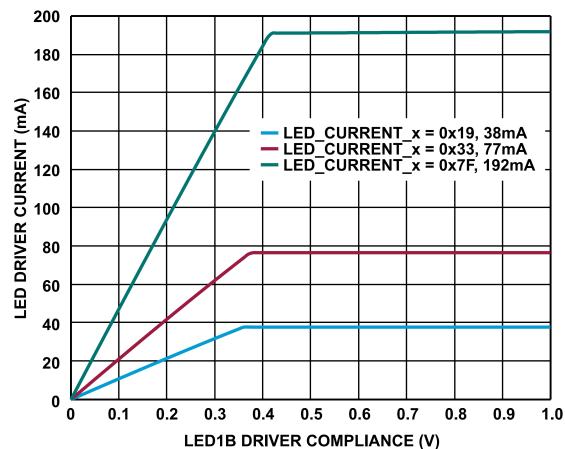

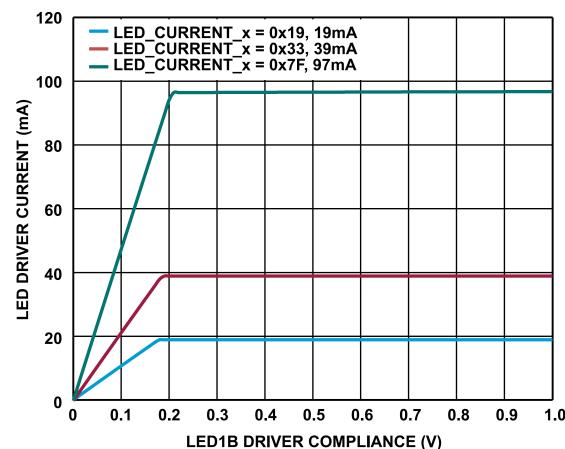

図 8. LED ドライバ電流と LED1B ドライバ・コンプライアンス

の関係、高 S/N 比モード

図 9. LED ドライバ電流と LED1B ドライバ・コンプライアンス

の関係、低コンプライアンス・モード

## 代表的な性能特性

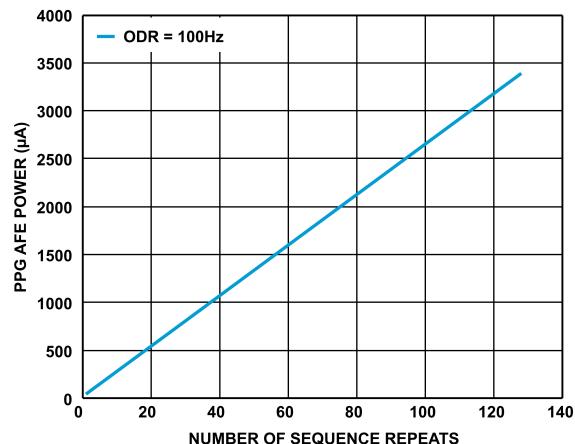

図 10. PPG AFE 電力とシーケンスの繰り返し回数の関係

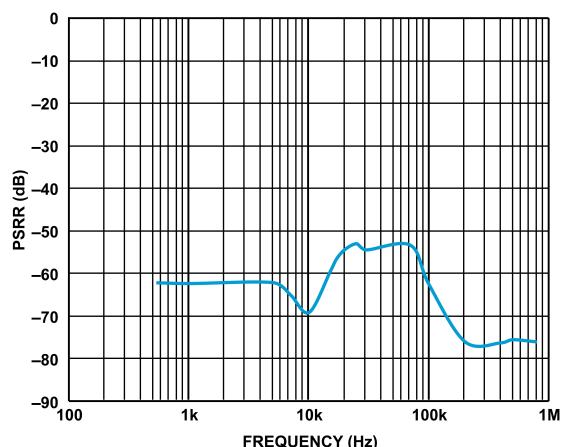

図 13. PSRR の周波数特性、フォト・ダイオード電流 = 8μA

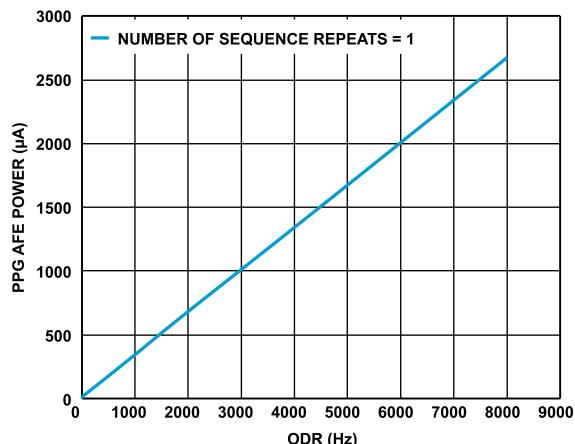

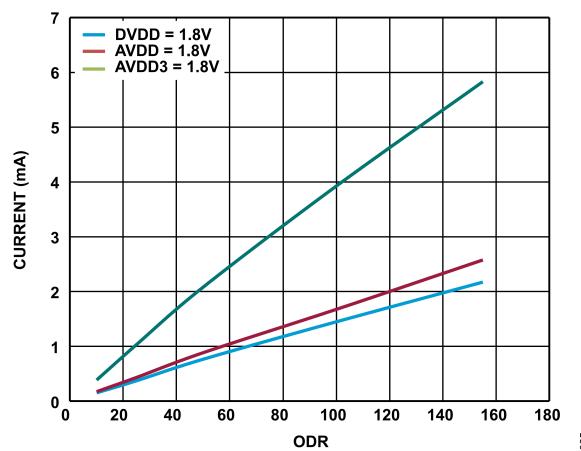

図 11. PPG AFE 電力とODRの関係

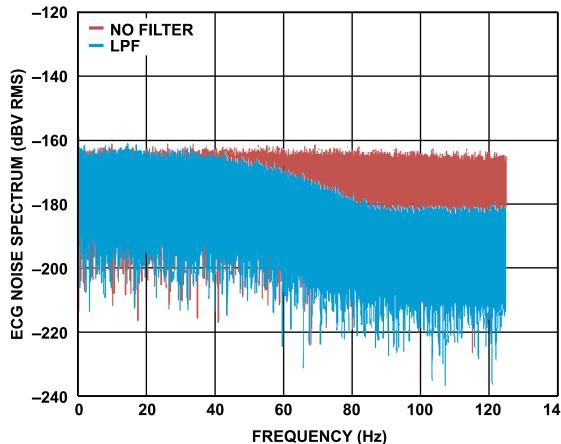

図 14. ECG ノイズ・スペクトルの周波数特性、入力をコモンモード電圧 ( $V_{CM}$ ) に短絡、分解能 = 286nV/ LSB、サンプル・レート = 250Hz (LPF はローパス・フィルタ)

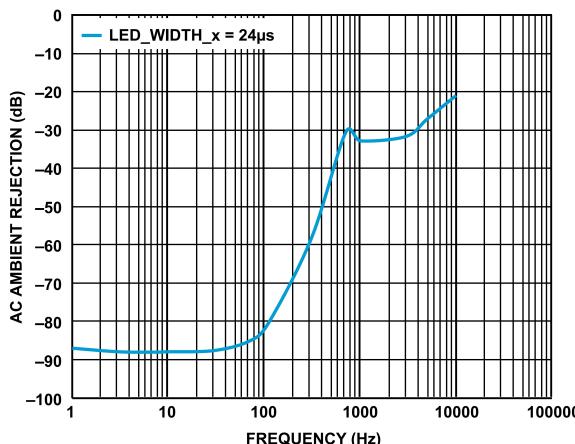

図 12. AC 周辺光除去の周波数特性

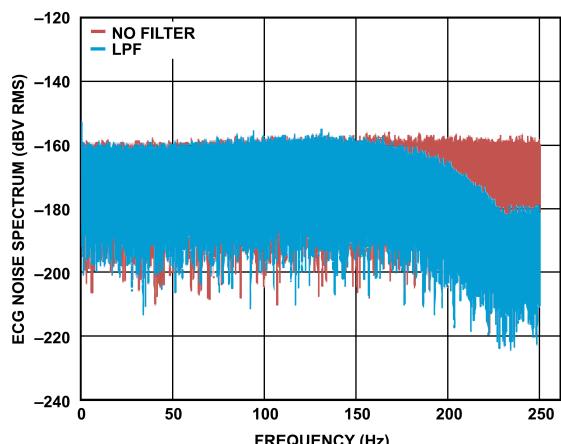

図 15. ECG ノイズ・スペクトルの周波数特性、入力を  $V_{CM}$  に短絡、分解能 = 286nV/ LSB、サンプル・レート = 500Hz

## 代表的な性能特性

017

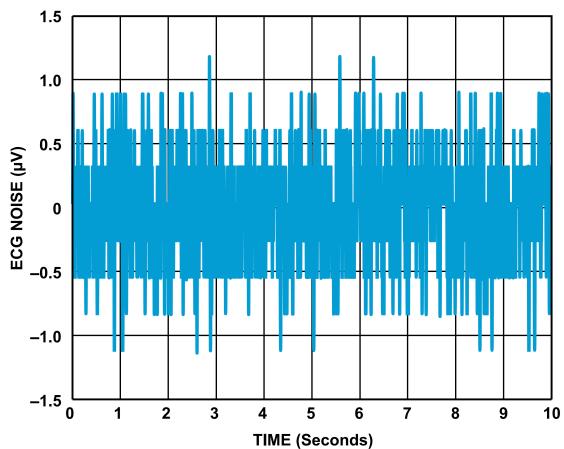

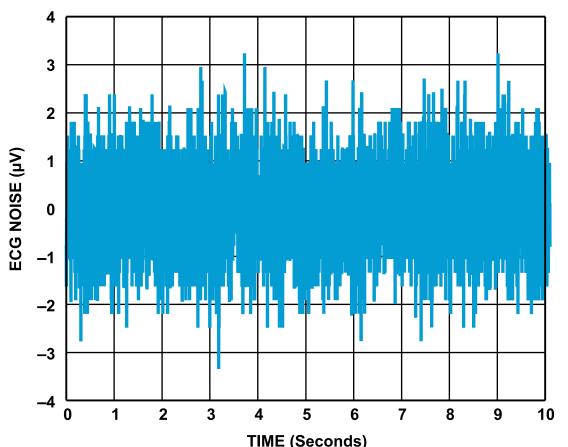

図 16. ECG ノイズと時間の関係、入力を  $V_{CM}$  に短絡、分解能 = 286nV/LSB、サンプル・レート = 250Hz

018

図 17. ECG ノイズと時間の関係、入力を  $V_{CM}$  に短絡、分解能 = 286nV/LSB、サンプル・レート = 500Hz

019

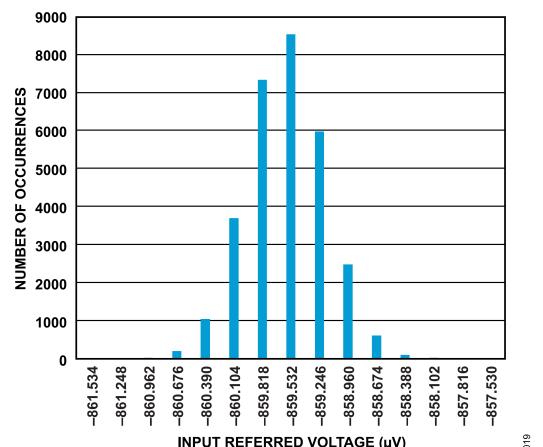

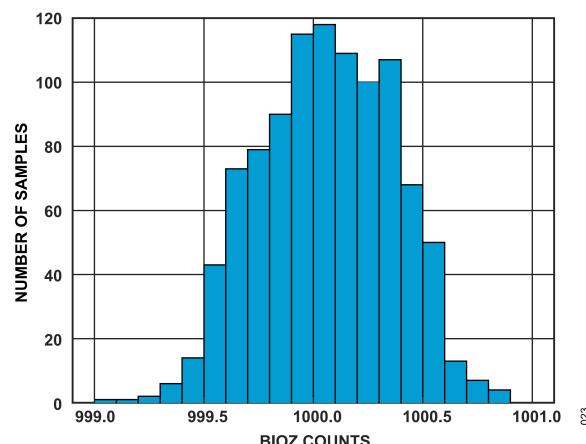

図 18. ECG ノイズのヒストグラム、入力を  $V_{CM}$  に短絡、分解能 = 286nV/LSB、サンプル・レート = 250Hz

020

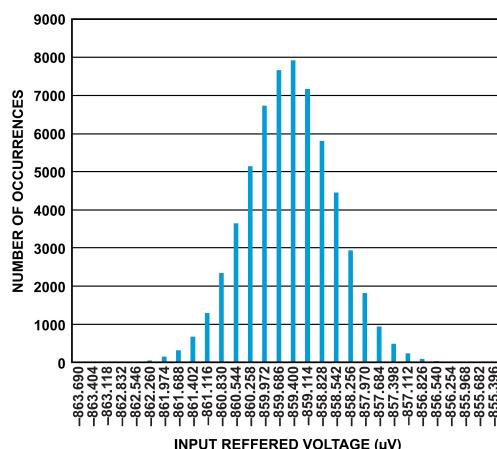

図 19. ECG ノイズのヒストグラム、入力を  $V_{CM}$  に短絡、分解能 = 286nV/LSB、サンプル・レート = 500Hz

021

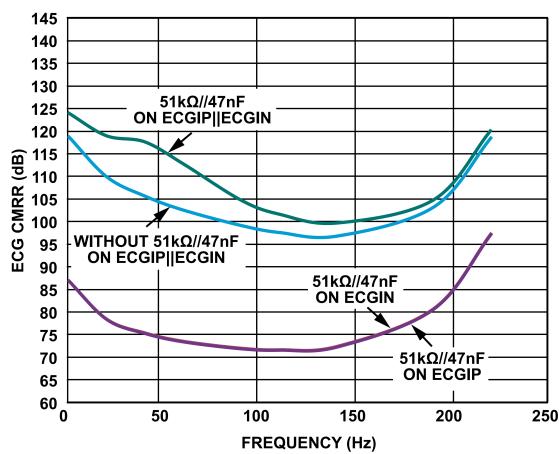

図 20. ECG CMRR の周波数特性、分解能 = 286nV/LSB、サンプル・レート = 500Hz

022

図 21. ECG AC 入力インピーダンスの周波数特性、分解能 = 286nV/LSB、サンプル・レート = 500Hz

## 代表的な性能特性

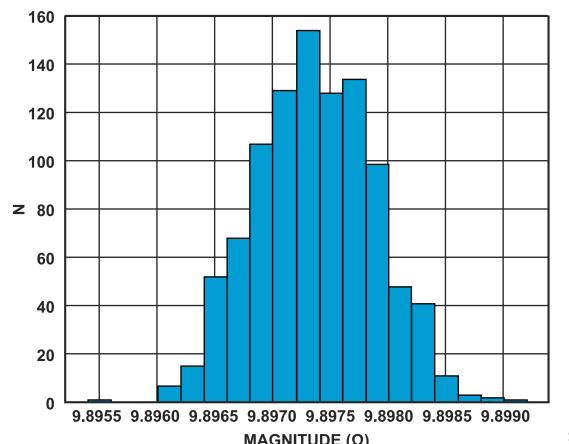

図 22. 生体インピーダンス (BIOZ) ノイズのヒストグラム

( $f_{EXCITATION} = 50\text{kHz}$ 、TIA GAIN =  $2\text{k}\Omega$ 、DFT = 1024、

$Z_{CONTACT} = 1\text{k}\Omega$ 、 $Z_{BODY} = 1\text{k}\Omega$ )

図 25. EDA ノイズのヒストグラム、 $f_s = 2.5\text{k}\Omega$ 、DFT = 1024、

PGA = 1.5、ODR = 100Hz

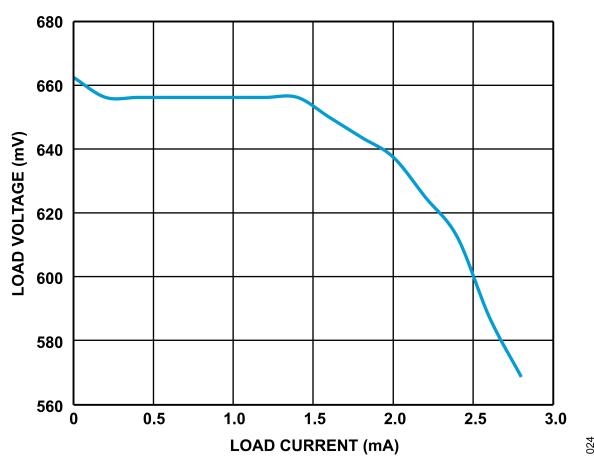

図 23. BIOZ 駆動能力

図 24. 消費電力と ODR の関係

(12 タイム・スロット、DFT = 1024)

## 動作原理

### はじめに

ADPD7000 は、マルチモードのバイタル信号モニタリング AFE で、光学測定パス（PPG）、ECG 測定パス、BIA 測定パス、EDA 測定パスの 4 つの高性能シグナル・チェーンで構成されています。

PPG 測定パスは、最大 8 個の LED と 4 個のフォト・ダイオードの入力をサポートするトランシーバーとして機能します。LED の電流は、2 個の 7 ビット LED ドライバによって設定できます。レシーバー・パスは、同時サンプリング可能で個別設定可能な 2 つの高性能読出しチャンネルを提供します。2 個の高性能電流 DAC (IDAC) がチャンネルごとに備わっており、優れた周辺光除去と大きなダイナミック・レンジを様々なアプリケーションで提供します。

ECG 測定パスは、高入力インピーダンス、低ノイズ、高ダイナミック・レンジのソリューションを提供し、ウェアラブル・デバイスにおいて高品質な ECG 信号のアクイジションを可能にします。DCLO 検出と ACLO 検出の両方が内蔵されているため、適切な検出能力が確保されています。

BIA パスにおける刺激信号は、様々な周波数、振幅、位相を持つサイン波を供給することができるため、ADPD7000 は様々な状況において測定の最適化が可能です。低ノイズ TIA、PGA、フィルタ、ADC がレシーバー・チャンネルに内蔵されているため、高性能なインピーダンス測定が可能です。ダイレクト・デジタル・シンセサイザ (DDS) エンジンと DFT エンジンもこのパスに内蔵されています。

EDA 測定パスは、AC 電圧測定、DC 電圧測定、DC 電流測定など、様々なモードを備えており、EDA アプリケーションにおいて低ノイズと高い測定精度を実現します。

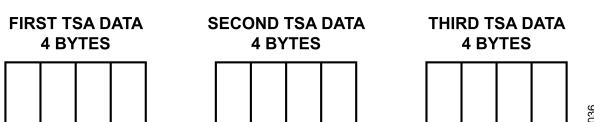

内蔵ステート・マシンが、これら 3 つの測定パスを柔軟に制御します。アクイジション・データは 704 バイトの FIFO に格納されます。

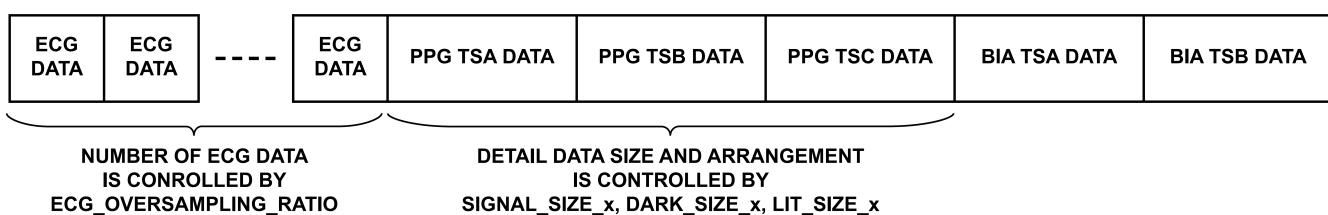

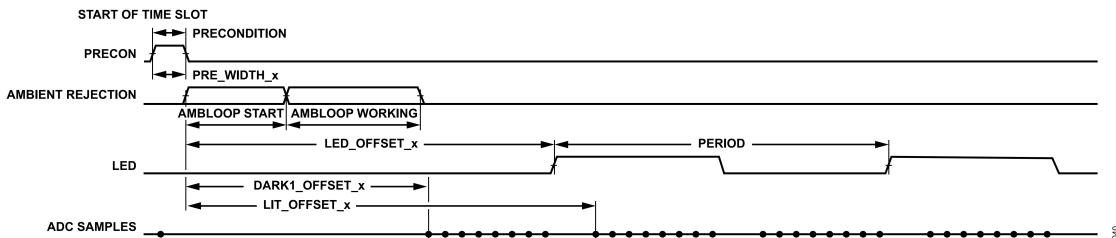

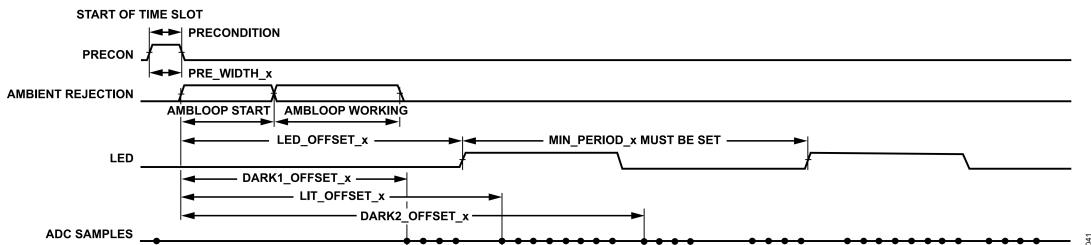

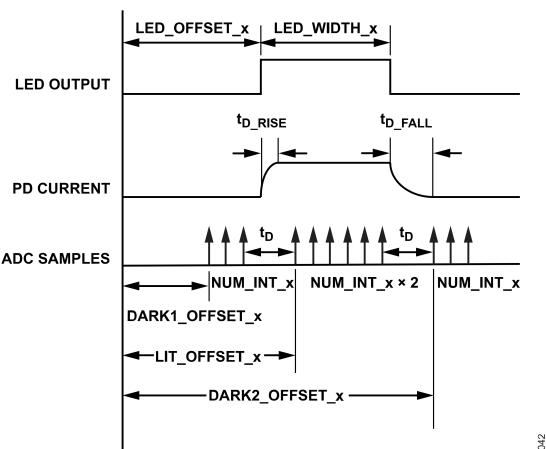

### タイム・スロット動作

内蔵の構成設定可能なコントローラが ADPD7000 の動作を処理します。このコントローラは、3 つの測定パスとスリーブ期間を組み合わせたサンプリング領域を生成するのに必要なタイミングを発生します。複数のシグナル・チェーンを使用しやすくするため、複数のタイム・スロットによって異なるトランスマッタやレシーバーへのアクセスを処理します。

システムは、イネーブルされた各タイム・スロットの繰り返し周期を決定する ODR によって特性が決まります。イネーブルされたタイム・スロットは、TIMESLOT\_PERIOD\_x ビットで設定されるタイム・スロット・レートで繰り返されます。

ADPD7000 には、図 26 に示すように 31 個のタイム・スロットがあります。

イネーブルされた PPG および BIA の各タイム・スロットは、タイム・スロット・レートで繰り返され、その後に超低消費電力のスリープ期間が続きます。

ECG\_TS は ECG のタイム・スロットです。ECG シグナル・チェーンの動作は、タイム・スロット形式では行われません。ECG タイム・スロットがオンになった後、ECG シグナル・チェーンはシステムが停止するまで動作します。ただし、ECG シグナル・チェーンの出力データは、このタイム・スロット・レートで FIFO に同期します。

ECG タイム・スロットの後、12 の PPG タイム・スロット (PPG\_TSA～PPG\_TSL) が続きます。各 PPG タイム・スロットでは、1 つ以上の LED パルスおよび変調パルスの生成と、その励起によるフォト・ダイオードや他のデバイスの電流のアクイジションが可能です。各タイム・スロットの動作パラメータは、細かい設定が可能です。

最後の 18 個のタイム・スロットは BIA タイム・スロット (BIA/EDA\_TSA～BIA/EDA\_TSR) で、EDA タイム・スロットと共有されます。各 BIA タイム・スロットでは励起電圧、周波数、レシーバーの設定が可能で、生体インピーダンスの正確な測定が容易にできるようになります。

サンプリング・レート（タイム・スロット・レート）は、次の式 1 に示すとおりです。

$$\text{Sampling Rate} = \text{Timer Clock Frequency (Hz)} / \text{TIMESLOT\_PERIODx} \quad (1)$$

表 9. 低周波数クロック (LFCLK) 源とタイマー・クロック源<sup>1</sup>

| LFCLK                                      | Timer Clock                                | ALT_CLOCKS | TM_CLK_GPIO_SEL |

|--------------------------------------------|--------------------------------------------|------------|-----------------|

| 960 kHz Internal                           | 960 kHz internal                           | 0          | N/A             |

| 960 kHz External                           | 960 kHz external                           | 1          | N/A             |

| 960 kHz Internal                           | 960 kHz internal                           | 2          | N/A             |

| 1 MHz External<br>(Divided from 32<br>MHz) | 1 MHz external<br>(divided from 32<br>MHz) | 3          | N/A             |

| 960 kHz Internal                           | 960 kHz external                           | 4          | 1               |

| 960 kHz Internal                           | 32 kHz external                            | 4          | 0               |

<sup>1</sup> N/A は該当なしを意味します。

|             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |             |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0           | 1           | 2           | 3           | 4           | 5           | 6           | 7           | 8           | 9           | 10          | 11          | 12          | 13          | 14          | 15          |

| ECG_TS      | PPG_TSA     | PPG_TSB     | PPG_TSC     | PPG_TSD     | PPG_TSE     | PPG_TSF     | PPG_TSG     | PPG_TSH     | PPG_TSI     | PPG_TSJ     | PPG_TSK     | PPG_TSL     | BIA/EDA_TSA | BIA/EDA_TSB | BIA/EDA_TSC |

| 16          | 17          | 18          | 19          | 20          | 21          | 22          | 23          | 24          | 25          | 26          | 27          | 28          | 29          | 30          | • • •       |

| BIA/EDA_TSD | BIA/EDA_TSE | BIA/EDA_TSF | BIA/EDA_TSG | BIA/EDA_TSJ | BIA/EDA_TSI | BIA/EDA_TSJ | BIA/EDA_TSK | BIA/EDA_TSL | BIA/EDA_TSN | BIA/EDA_TSO | BIA/EDA_TSQ | BIA/EDA_TSR |             |             |             |

図 26. タイム・スロットの割当て

## 動作原理

### リードオン検出

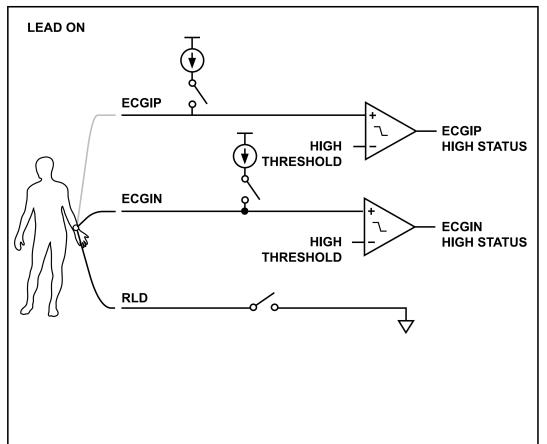

動作モードがスタンバイ・モードまたはPPGのみのモードに設定されている場合、LEAD\_ON\_MODEビット（レジスタ00F、ビット11）を1に設定することにより、ADPD7000に搭載されたリードオン検出機能によって超低消費電力モードで動作させることができます。この動作モードが、いずれかのECGまたはBIOZタイム・スロットがイネーブルされた状態で設定された場合には、リードオン検出回路の一部がECGやBIOZタイム・スロット動作によって制御されるため、リードオン検出モードは無視されます。

図27. リードオン検出

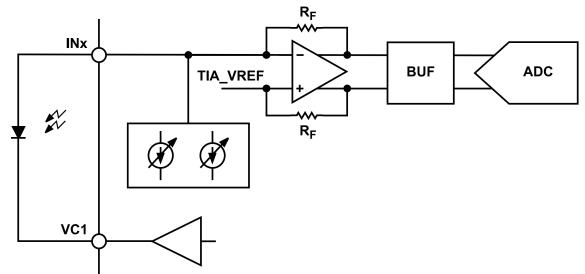

### 光シグナル・チェーン

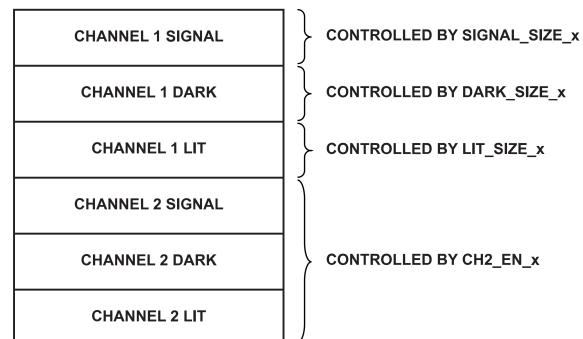

光信号パスは、最大8個のLEDを励起し、リターン信号を最大4つの別々の電流入力で測定します。光タイム・スロットは12個あるため、サンプリング周期ごとに最大12の光学測定ができます。

アナログ入力は、シングルエンドまたは差動ペアで駆動できます。4個のアナログ入力は、単一チャンネルまたは独立した2つのチャンネルにマルチプレクスされ、同時に2個のセンサーのサンプリングが可能です。

光シグナル・チェーンは、TIA、レジスタ設定によってはバッファとしても設定可能な積分器、およびADCで構成されています。デジタル・ロックは、複数の動作モード、プログラマブルなタイミング調整、およびロック平均化が可能です。

また、最大200mAで駆動できる2個の独立したLEDドライバを搭載しています。2個のLEDドライバは任意のタイム・スロットで使用でき、7ビットのレジスタ設定値により1.57mAから200mAまでの単調増加のプログラムが可能です。イネーブルされたLEDドライバは、いずれのタイム・スロットでも、組み合わせることで合計400mAまでのLED電流を供給できます。

光学測定を行う場合、周辺光の除去は、外部の制御ループ、DC電流の減算、あるいはデジタル・アルゴリズムなどを必要とせず、自動的に行われます。

LEDドライバは電流シンクなので、LED電源電圧やLEDの種類による影響を受けません。光学測定は、比較的小さなLED電力で高いS/N比を達成すると同時に、周辺光が測定信号に及ぼす影響を大幅に軽減します。

### アナログ信号パス

光シグナル・チェーンのアナログ信号パスは4個の電流入力からなり、これらはシングルエンドまたは差動ペアとして構成され、4つの独立したチャンネルの1つに供給されます。この4つのチャンネルは同時にサンプリング可能で、4個のセンサーの瞬時サンプリングが求められるアプリケーションに使用できます。

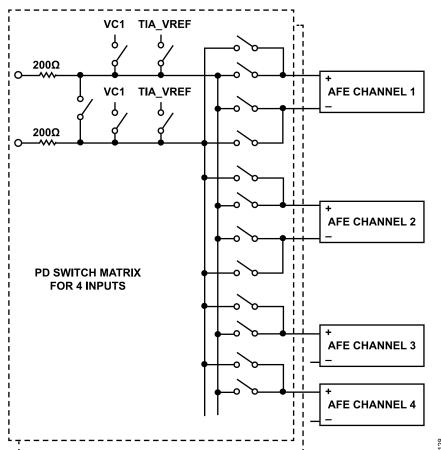

### アナログ入力マルチプレクサ

光シグナル・チェーンは4個のアナログ入力ピンをサポートしています。各入力はシングルエンド入力として、または差動ペアの一部として使用できます。図28に入力スイッチ・マトリックスの1つを示します。これにより、4つの光学チャンネルとのプログラマブルな接続が可能になります。各入力ペア（IN1とIN2、IN3とIN4）は、このマルチプレクサを複製した回路になっています。接続はタイム・スロットごとにプログラム可能です。

PAIR12ビットとPAIR34ビットを使用して、それぞれの入力ペアを2つのシングルエンド入力として使用するか、差動ペアとして使用するかを選択します。この選択は、すべてのアクティブなタイム・スロットに対して有効です。INP12\_xビットおよびINP34\_xビットによって、該当するタイム・スロットにおいて入力ペアをイネーブルするかどうかを設定できます。イネーブルされた場合は、どの入力をどの光学チャンネルに接続するかも設定します。チャンネル1とチャンネル2はシングルエンド入力または差動入力をサポートしますが、チャンネル3とチャンネル4はシングルエンド入力のみをサポートすることに注意してください。

スリープ条件は、イネーブルされていないすべての入力に使用します。スリープ条件は、INP\_SLEEP\_12ビットとINP\_SLEEP\_34ビットによって決定し、これらのビットで、スリープ時および入力がアクティブになっていないときの入力ペアの状態を設定します。入力は、前処理の間、および入力がイネーブルされたタイム・スロットのパルス領域でのみアクティブと見なされます。

入力に接続されたセンサーの前処理は、サンプリングの前に入力の動作ポイントを設定するために使用します。前処理にはいくつかの異なるオプションがあり、PRECON\_xビットによって決定します。PRECON\_xビットは各タイム・スロットに対して用意されており、タイム・スロット期間におけるイネーブルされた入力、または入力ペアの前処理を設定します。前処理の選択肢として、フロート状態、VC1、TIAの内部電圧リファレンス信号（TIA\_VREF）、TIA入力、入力ペア短絡があります。前処理は各タイム・スロットの開始時に実施され、その時間はPRE\_WIDTH\_xビットを使用してプログラムできます。デフォルトの前処理時間は4μsです。

図28のブロック図に、スリープ状態および前処理の間に入力と接続可能なバイアス・レベルを示します。これらの接続は、入力が選択されているタイム・スロットのサンプリング・フェーズの期間中は使用できません。

## 動作原理

図 28. スイッチ・マトリックスのブロック図

## 周辺光キャンセル

ADPD7000 には、次のように周辺光をキャンセルするモードが 3 つあります。

- ▶ 粗調整のみ

- ▶ 粗調整と微調整ループ

- ▶ 外部マイクロコントローラ・ユニット (MCU) 制御

粗調整のみのモードおよび粗調整と微調整ループのモードでは、ソフトウェアの助けを借りることなく ADPD7000 が自動で制御します。外部 MCU 制御モードでは、外部アルゴリズムを用いて周辺光除去が可能です。

モードを選択するには AMBIENT\_CANCELLATION\_x ビットを使用します。

各 PPG タイム・スロットの開始時には粗調整モードで動作します。このモードでは、周辺光のレベルを測定し、周辺光 DAC コードを設定します。これらの動作を完了し周辺光 DAC のベースラインを決定するために、回路としては 48 $\mu$ s を要します。その後、PPG チャンネルは通常動作を開始できます。例えば、デジタル積分モードの場合、PPG レシーバー・チャンネルは、暗サンプルの取得を開始できます。粗調整のみのモードが有効化されている場合、この周辺光ベースラインがそのタイム・スロットで使用されます。

粗調整と微調整ループのモードが有効化されている場合、粗調整回路は粗調整モードと同じように動作します。ただし、周辺光 DAC コードは暗サンプルの測定ごとに更新されます。

AMBIENT\_CANCELLATION\_x ビットでこれら 2 つのモードを選択することにより、システム・レベルで柔軟な設計が可能になります。

粗調整ループ・モードでは、周辺光電流の正確な値を求める測定を行います。その後、周辺光 DAC が、シグナル・チェーンの開始時に周辺光電流を差し引くため、PPG 信号測定に大きな誤差が生じることはありません。

アナログ積分モードとデジタル積分モードのどちらも、粗調整ループによる周辺光除去が可能です。

微調整ループは、暗サンプルの測定ごとに周辺光情報を更新します。この機能はデジタル積分モードでのみ利用できます。

MCU モードでは、ユーザーが周辺光電流を差し引くことができます。DAC\_AMBIENT\_CH1\_x ビットおよび DAC\_AMBIENT\_CH2\_x ビットは、ユーザーが周辺光電流値を入力できるよう設計されており、これにより、AFE はその値をシグナル・チェーンから差し引きます。DAC\_AMBIENT\_CH1\_x および DAC\_AMBIENT\_CH2\_x は 9 ビットのフィールドで、それぞれの LSB は 0 $\mu$ A～300 $\mu$ A の範囲で 0.6 $\mu$ A ステップに相当します。

## LED DC キャンセル機能

周辺光 DAC の他に、各シグナル・チェーンの入力にはもう 1 つの IDAC があります。この IDAC は、LED の反射光の不要な DC 成分を除去してレシーバー・チャンネルのダイナミック・レンジを拡大するために用いられます。

2 つの IDAC は、MCU によってのみ制御されます。DAC\_LED\_DC\_CH1\_x ビットおよび DAC\_LED\_DC\_CH2\_x ビットを使用して、LED の DC 成分をキャンセルする 7 ビット IDAC をフルスケールで制御します。

この LED DC キャンセル機能は、デジタル積分モードでのみ利用できます。

上位レベルの光学設計およびシステム設計に基づき、特定の量の DC 電流が AFE から差し引かれます。DAC\_LED\_DC\_CH1\_x および DAC\_LED\_DC\_CH2\_x は 7 ビットのフィールドで、それぞれの LSB は 0 $\mu$ A～190 $\mu$ A の範囲で 1.5 $\mu$ A ステップに相当します。

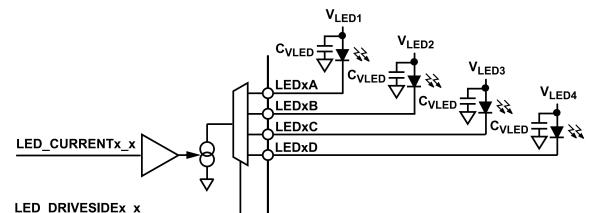

## LED ドライバ

光路には 2 つの LED ドライバがあり、それぞれが 4 つの LED ドライバ出力を備えているため、合計で 8 つの LED 出力ドライバが使用可能です。ドライバ・ペアごとに 1 つを使用することで、最大 2 個の LED を同時に駆動できます。LED 出力ドライバは電流シンクです。図 29 に、1 つの LED ドライバ出力ペアの例を示します。

図 29. LED ドライバ出力ペア (CVLED はバイパス・コンデンサ)

LED ドライバ出力ピン (LED1A、LED2A、LED1B、LED2B、LED1C、LED2C、LED1D、LED2D) の最大許容電圧は 3.6V です。この定格を超える電圧を印加すると、デバイス動作の信頼性に影響を与え、状況によってはデバイスが正常に動作しなくなる場合があります。LED ドライバ出力ピンの電圧と LED への電源電圧を混同しないでください。V<sub>LEDx</sub> は外部 LED のアノードに印加する電圧です。これに対し、LED 出力ドライバ・ピンは外部 LED のカソードに接続します。コンプライアンス電圧は、グラウンドを基準として測定した LED ドライバ・ピンのヘッドルームの総電圧で、設定した LED 電流レベルを維持するために必要となります。このコンプライアンス電圧は、必要とする電流の関数になっています。

## 動作原理

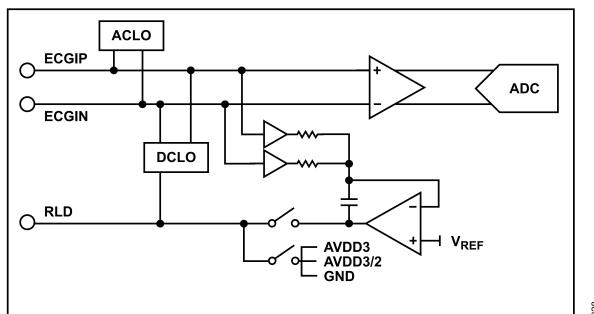

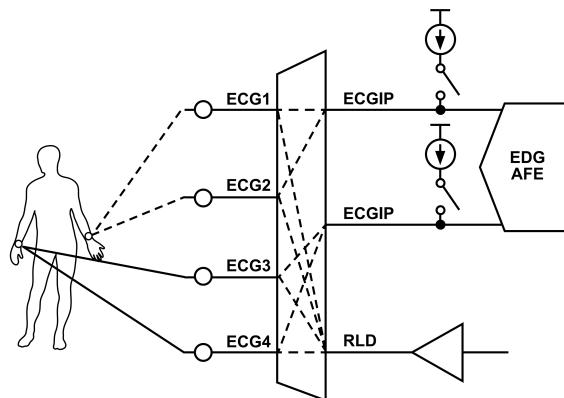

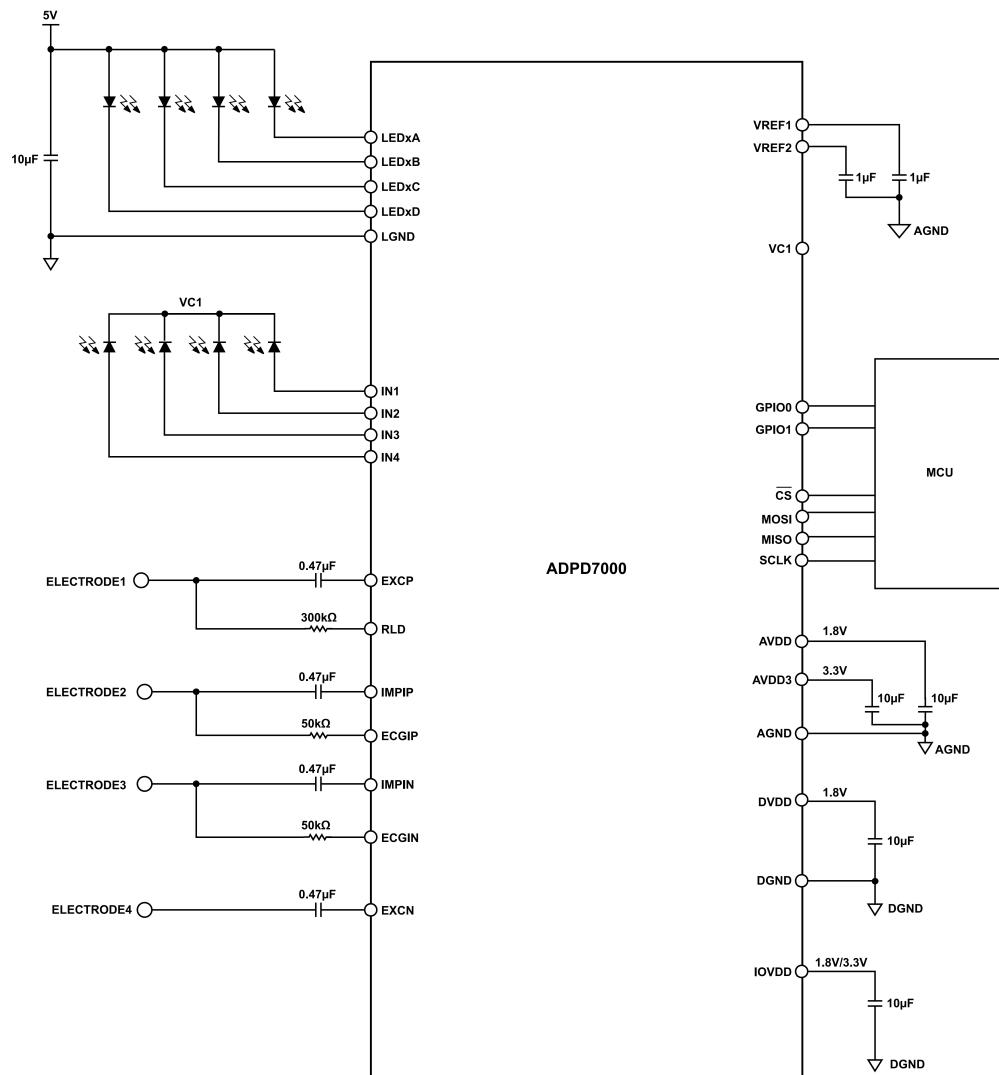

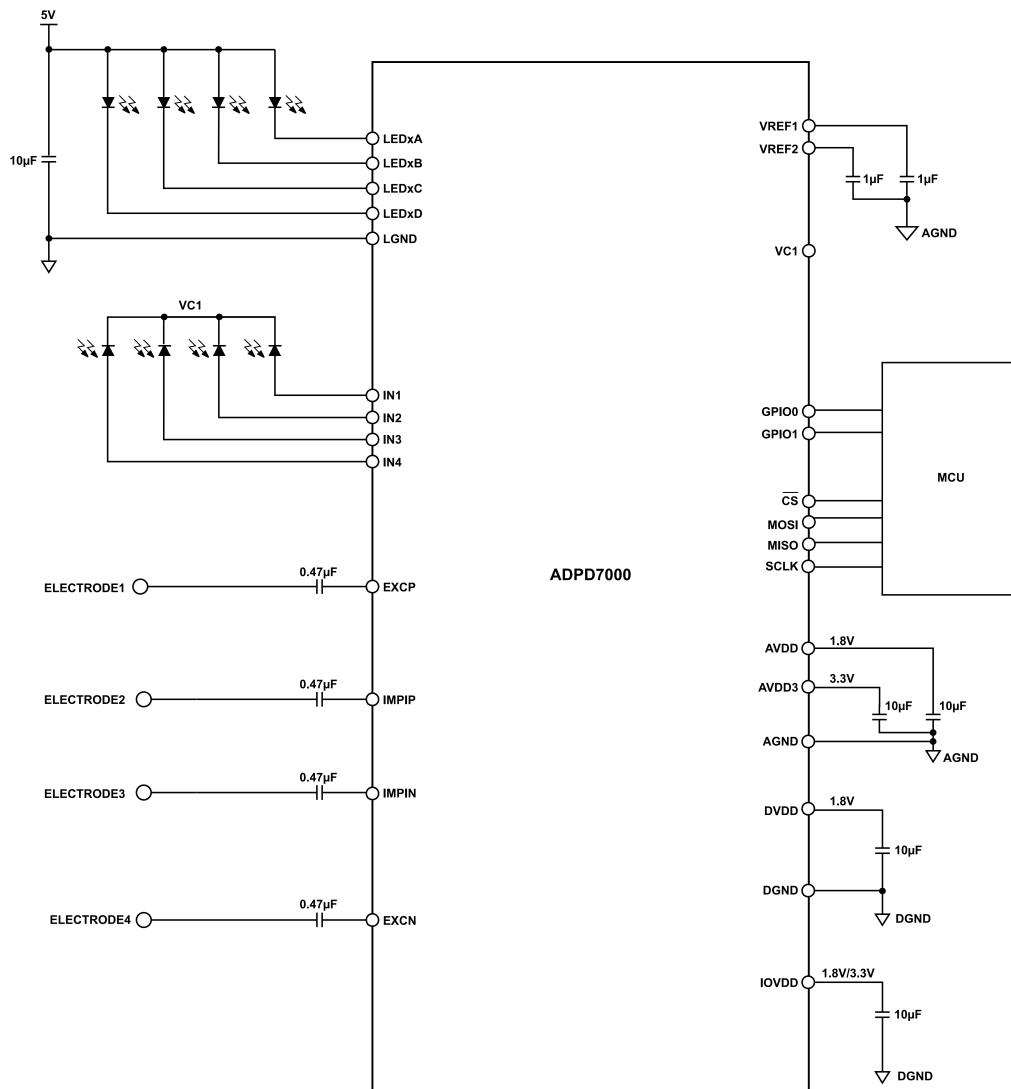

### ECG シグナル・チェーン

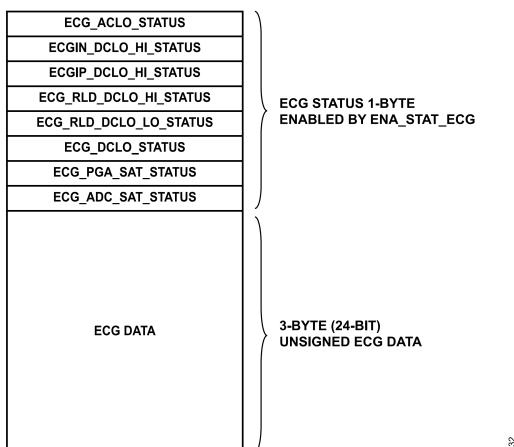

ECG チャンネルは、2 つのエレクトロード間の差動電圧を測定し、リード測定を行います。このチャンネルの出力は、測定した ECG 電圧を表す 24 ビットのデジタル・ワードです。最大入力差動信号は±1.2V で、LSB の大きさは 286nV です。出力データレートは、250SPS、500SPS、1kSPS、2kSPS、または 4kSPS です。このフィルタの選択はデジタル処理には影響しますが、アナログ処理には影響しません。更に、4kHz の AC リードオフ信号は、アナログ ECG パスによって変換され、デジタル領域で取り込まれます。

ECG チャンネルには、帰還構成を備えた専用の ADC パスがあり、ECG エレクトロードから生じる DC オフセットを除去します。ECG チャンネルは、高品質の ECG 信号処理を可能にすると同時に、複雑なシステム設計に起因する大きな DC オフセットを抑制するよう設計されています。

DC および AC リードオフ検出機能と DC リードオン検出機能の両方を備えているため、複雑で様々なリード接触条件に対応し信頼できるリード情報を提供できます。

RLD 信号は、人体電位をよりよくバイアスし干渉を回避できるよう設計されています。

ECGIP および ECGIN は ECG チャンネルの信号入力で、これらの入力は入力リードに接続する必要があります。RLD 信号はリファレンス・リードに接続する必要があります。

ECG 信号 (RLD、ECGIP、ECGIN) は、ECG\_MATRIX レジスタを設定することにより、ECG1～ECG4 ピンのどれか 1 つに接続することができます。

### ECG メイン・シグナル・チェーン

図 30 に ECG のメイン・シグナル・チェーンの回路図を示します。

図 30. ECG メイン・シグナル・チェーン図

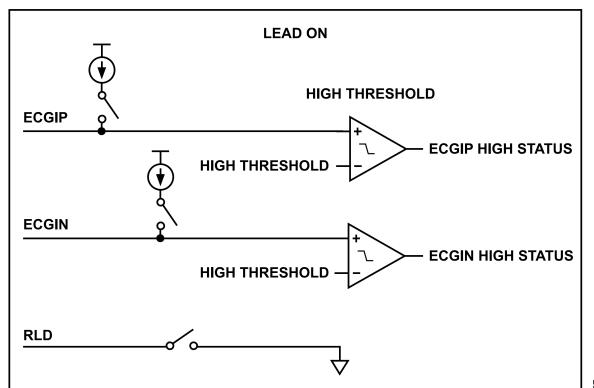

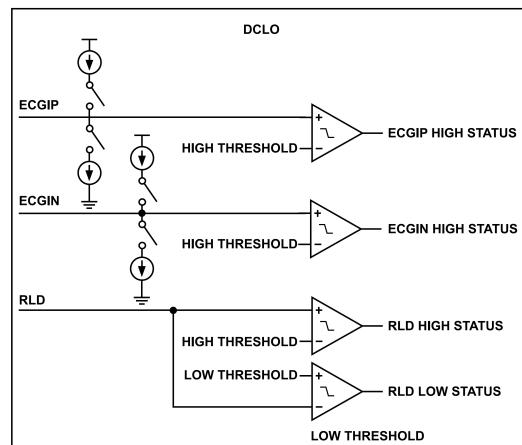

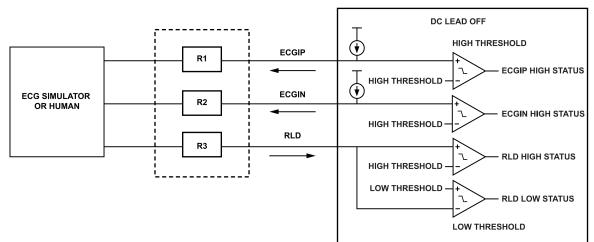

### DC リードオフ (DCLO) 検出

DCLO 回路は、設定可能な微小 DC 电流を各入力エレクトロードに印加し、その結果生じるエレクトロードの電圧をモニタします。図 31 に DCLO 検出回路の図を示します。

図 31. DCLO 検出回路図

ECGIP 信号と ECGIN 信号がどちらも正しく接続されている場合、ECG 入力の 1 つから患者を通じてもう 1 つの ECG 入力に電流が流れることで、微小な電圧シフトが生じます。このフェール電流の大きさは全 ECG エレクトロードに共通で、0nA～1.1μA の範囲で設定できます。

フェール電流の極性はエレクトロードごとに独立で、ECG\_DCLO\_POLARITY\_IN ビットと ECG\_DCLO\_POLARITY\_IP ビット（レジスタ 0x101 を参照）を使用して設定できます。エレクトロードの接続が悪化した場合あるいは外れた場合、このエレクトロードの信号電圧は、設定したフェール電流の極性に応じてハイまたはローになります。

検出回路は、それぞれのエレクトロード入力 (ECGIP および ECGIN) に基づいています。検出回路は、ECG 入力に対して個別に設定可能な閾値に基づくコンパレータを使用します。

入力リードのそれぞれ (ECGIP および ECGIN) には、上限閾値を持つコンパレータが 1 つだけあります。RLD 信号には、上限閾値を持つコンパレータと下限閾値を持つコンパレータの 2 つがあります。

これらの閾値の制限は、予想される信号範囲をすべての閾値電圧がカバーするよう選択されます。ウィンドウ・コンパレータは、エレクトロードの入力電圧とこれに対応する閾値電圧を比較します。特定のエレクトロードの電圧変化が、フェール電流として設定されたいずれかの閾値電圧を超えた場合、エレクトロード接触部の DC 抵抗はリードオフをフラグ通知できます。

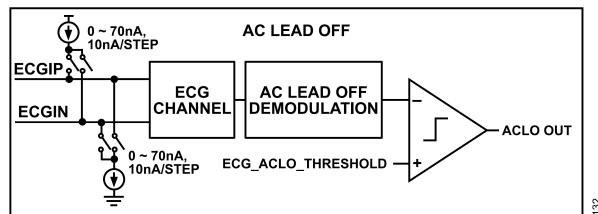

### AC リードオフ (ACLO) 検出

ECG パスは ACLO 検出回路を備えており、DCLO 検出回路と共に使用してリードオフを検出することができます、異なる種類のリード処理が可能です。図 32 に ACLO 検出回路の図を示します。

## 動作原理

図 32. ACLO 検出回路図

ACLO 法は、AC 电流を各 ECG エレクトロードに印加し、その結果生じる ECG チャンネルの電圧の大きさを測定することにより、エレクトロードが患者に接続されているかどうかを検出します。ACLO 機能を使用するには、ECG チャンネルをイネーブルする必要があります。

ACLO 电流の大きさは、ECG\_ACLO\_MAG ビットで設定できます。AC 电流を ECG 入力バスに印加することで、測定する ECG チャンネル入力間に電圧が生じます。測定された電圧は同期して復調され、コンパレータを通じて送られます。ユーザは、ECG\_ACLO\_THRESHOLD ビットを用いて閾値を設定できます。ACLO 検出機能は、ECG 入力ピン (ECGIP と ECGIN) にのみ使用でき、RLD 信号には対応していません。駆動電流は右脚 (RL) に印加されるため、エレクトロードが正しく接続されていれば信号は微小です。エレクトロードが適切に接続されていない、あるいは完全に乾燥している場合は、容量性分圧器で検出されるほどの大きな信号となります。

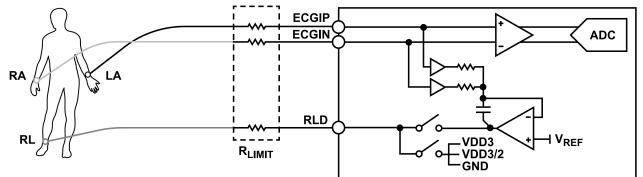

## 右脚 ドライバ (RLD)

駆動リファレンスを用いると、ノイズの同相モード除去や外部ソースからの干渉 (電源ラインの干渉 (50Hz または 60Hz) や患者に接続された他の機器からの干渉など) が改善されるため、全体的な性能が向上します。また、駆動段は、ECG エレクトロードに印加されたリード・フェール電流を吸収する働きもあります。

リファレンス・エレクトロード駆動回路は、患者の VCM を検出し、その反転波形を体に印加することで、患者を通じて負帰還ループを形成します。RLD アンプは  $V_{CM} = AVDD3/2$  を用います。これはエレクトロード電圧を ADC 入力範囲の中央におく値です。各エレクトロード入力はバッファされ、スイッチを介して RLD アンプに供給されます。

RLD 信号の容量は、RLD アンプに影響します。最高の性能を得るには、このノードの容量を  $2.2nF$  未満にします。通常動作では、RLD アンプの出力は RLD 信号とこれに関連する保護回路を介して RL エレクトロードに印加します。

RLD アンプはオフにすることができ、RLD 信号を、ECG\_RLD\_OUT\_SEL ビットで電圧を選択して駆動することができます。

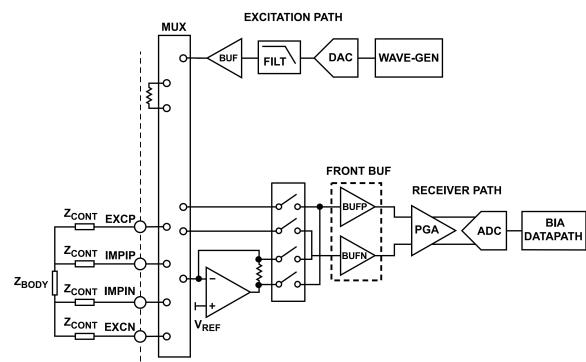

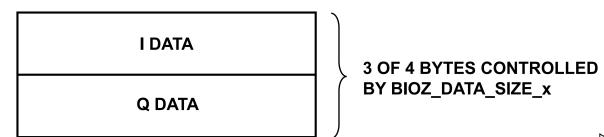

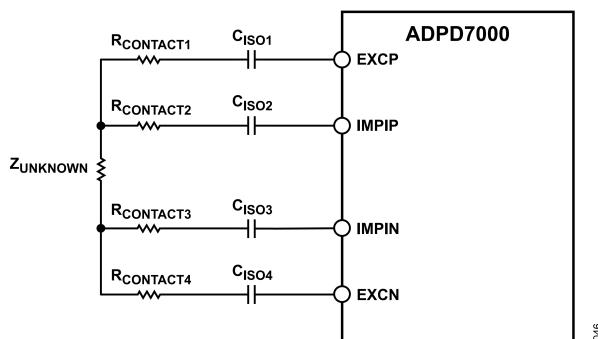

## BIA シグナル・チェーン

BIA シグナル・チェーンは、生体インピーダンス測定用に設計されたものです。このシグナル・チェーンは、高周波数の高精度励起ループと測定チャンネルからなり、様々な生体インピーダンス構成に対し幅広い測定機能が利用できます。

励起ループは高速 DAC とも呼ばれる 12 ビット DAC からなります。この DAC は、最大 250kHz の高周波励起信号を生成できます。

測定チャンネルは、入力バッファ付き ADC、内蔵アンチエイリアス・フィルタ、PGA を備えています。

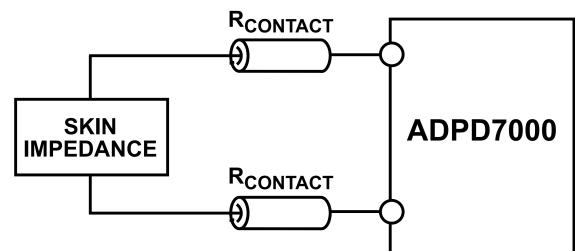

超低リークのプログラマブル・スイッチ・マトリックスによって、センサーと内部のアナログ励起ブロックおよび測定ブロックを接続します。このマトリックスは、外部の生体インピーダンスとキャリブレーション抵抗を接続するインターフェースとなっています。図 33 に、BIA シグナル・チェーンのブロック図を示します。

図 33. BIA チャンネルのブロック図

( $Z_{CONT}$  は接触インピーダンス)

励起ループの入力マルチプレクサ (mux) は、BIOZ\_TSW\_x、BIOZ\_DSW\_x、および BIOZ\_RINT\_SW\_x ビットで制御されます。測定バスの入力マルチプレクサは、BIOZ\_NCHAN\_x および BIOZ\_PCHAN\_x で制御されます。表 10 に入力マルチプレクサの接続とそのビット設定を示します。BIA チャンネルの柔軟な設計により、様々な構成で測定が可能となります。

表 10. BIA チャンネルの TIA 接続

| Bit Name                  | Setting | Connection                                                                                                              |

|---------------------------|---------|-------------------------------------------------------------------------------------------------------------------------|

| BIOZ_TSW_x                | 0001    | IMPIP                                                                                                                   |

|                           | 0010    | IMPIN                                                                                                                   |

|                           | 0100    | EXCP                                                                                                                    |

|                           | 1000    | EXCN                                                                                                                    |

| BIOZ_RINT_SW_x, Bits[1:0] | 1       | The internal resistor ( $R_{INT}$ ) that connects to the external buffer (EXCBUF) and the high power TIA (HPTIA) blocks |

|                           | 0       | $R_{INT}$ no connection                                                                                                 |

| BIOZ_DSW_x                | 0001    | IMPIP                                                                                                                   |

|                           | 0010    | IMPIN                                                                                                                   |

|                           | 0100    | EXCP                                                                                                                    |

|                           | 1000    | EXCN                                                                                                                    |

| BIOZ_NCHAN_x              | 000     | HPTIA_n <sup>1</sup>                                                                                                    |

|                           | 001     | IMPIN                                                                                                                   |

## 動作原理

表 10. BIA チャンネルの TIA 接続（続き）

| Bit Name         | Setting | Connection                 |

|------------------|---------|----------------------------|

| BIOZ_PCHAN_x     | 010     | EXCP                       |

|                  | 011     | $R_{INT\_SN}$ <sup>2</sup> |

|                  | 100     | IMPIP                      |

|                  | 101     | EXCN                       |

|                  | 110     | ECG RLD (EDA only)         |

|                  | 111     | ECGIP (EDA only)           |

| BIOZ_SINEFCW_x_x | 000     | HPTIA_p <sup>1</sup>       |

|                  | 001     | IMPIP                      |

|                  | 010     | EXCN                       |

|                  | 011     | $R_{INT\_SP}$ <sup>2</sup> |

|                  | 100     | IMPIN                      |

|                  | 101     | EXCP                       |

|                  | 110     | ECGIN (EDA only)           |

|                  | 111     | ECGIP (EDA only)           |

<sup>1</sup> HPTIA\_n と HPTIA\_p は TIA 抵抗の 2 つの端子を表します。

<sup>2</sup>  $R_{INT\_SN}$  と  $R_{INT\_SP}$  は内部抵抗の 2 つの端子を表します。