## 9kHz~26.5GHz の集積化ベクトル・ネットワーク・アナライザ・ フロント・エンド

## 特長

- ▶ 広帯域集積化双方向ブリッジ

- ▶ 指向性（未補正データ）：1GHz で 35.6dB、18GHz で 16.7dB

- ▶ 低挿入損失：1GHz で 1.1dB、18GHz で 2.0dB

- ▶ 反射損失：>12dB（代表値）

- ▶ SPI により設定可能な LO インターフェース

- ▶ 2 分周。1 週倍、2 週倍または 4 週倍

- ▶ オフセット LO インターフェースにより  $f_{RF} = f_{LO}$  での駆動が可能

- ▶ シングルエンドまたは差動駆動

- ▶ SYNC 機能 — 複数デバイス間の同期

- ▶ 高ダイナミック・レンジ広帯域 IF 信号パス

- ▶ SPI を介してプログラム可能な IF 帯域幅：1MHz～100MHz

- ▶ SPI を介してプログラム可能な IF ゲイン（ステップ・サイズ：6dB）

- ▶ 外部調整可能な出力コモンモード・レベル

- ▶ SPI を介して読み出し可能な 5 ビット温度センサー

- ▶ 低消費電力シャットダウン・モード

- ▶ 3mm × 4mm、26 ピン LGA パッケージ

## アプリケーション

- ▶ 広帯域マルチポート・ベクトル・ネットワーク・アナライザ

- ▶ Sパラメータの大きさおよび位相の測定

- ▶ インラインRF電力測定

- ▶ ATE（自動試験装置）

- ▶ 反射率計

- ▶ 材料解析

## 概要

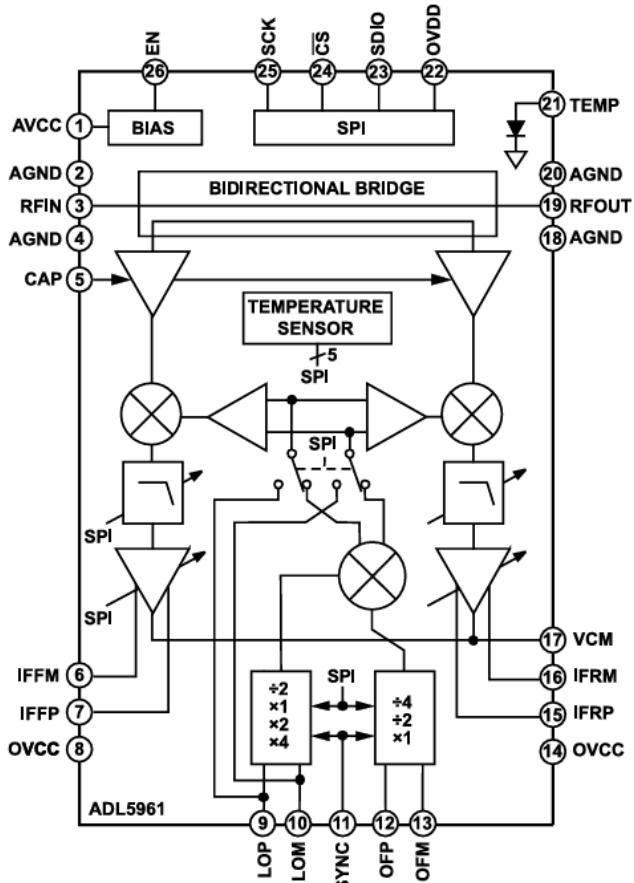

**ADL5961** は、抵抗性双方向ブリッジ、ダウンコンバージョン・ミキサー、プログラマブルな IF アンプおよびフィルタ、柔軟性の高い局部発振器 (LO) インターフェースからなる、広帯域でフォーム・ファクタの小さいベクトル・ネットワーク・アナライザ (VNA) フロント・エンドです。ブリッジは 17GHz まで、14dB を超える指向性を備えています。RFIN から RFOUT までの 1 次伝送ラインは  $50\Omega$  に広帯域整合されており、損失は DC に近い 9kHz ではわずか 1.1dB で、26.5GHz では 1.8dB です。

ADL5961 は、様々な LO インターフェース構成をサポートしており、VNA ソリューションのクロック設計、およびこのデバイスから A/D コンバータ (ADC) へのインターフェース接続を簡素化できます。LO インターフェースの分周器と倍増器により、LO ソースの動作周波数範囲を超える測定スイープが可能になるので、6GHz のシンセサイザを用いて ADL5961 を全周波数範囲 (26.5GHz) にわたって動作させることができます。IF 周波数オフセット・ミキサーは、OFP ピンと OFM ピンによって形成されたオフセット・インターフェースを介して駆動されますが、掃引される RF および LO インターフェースが同じ周波数ソースを共有できるようにすることで、設計を更に簡素化できます。

## 機能ブロック図

図 1. 機能ブロック図

IF 出力信号の周波数は、OFP/OFM インターフェースを駆動する低周波数ソースによって決まります。4 分周をイネーブルして、このインターフェースを ADC サンプル周波数で駆動すると、IF 出力信号が自動的に第 1 ナイキスト・ゾーンにセンタリングされます。

帯域幅をプログラム可能な IF フィルタと、ゲインを個別にプログラム可能な IF アンプにより、順方向チャンネル (IFFP、IFFM) と逆方向チャンネル (IFRP、IFRM) の IF 出力信号のダイナミック・レンジを同時に最適化できます。IF アンプは、出力コモンモード・レベルが調整可能で、十分な駆動能力と広い出力電圧振幅を備えているので、幅広い ADC に直接インターフェース接続することができます。

ADL5961 のすべての設定と機能は、3 線式シリアル・ペリフェラル・インターフェース (SPI) を介してプログラム可能です。

ADL5961 は、3mm × 4mm、26 ピン LGA（ランド・グリッド・アレイ）パッケージで提供されます。

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいはその利用によって生じる第三者の特許やその他の権利の侵害に関しては一切の責任を負いません。仕様は予告なく変更される場合があります。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                       |    |                      |    |

|-----------------------|----|----------------------|----|

| 特長                    | 1  | IF 信号パス              | 19 |

| アプリケーション              | 1  | マルチポート VNA           | 20 |

| 機能ブロック図               | 1  | キャリブレーションと誤差補正       | 21 |

| 概要                    | 1  | アプリケーション情報           | 25 |

| 仕様                    | 3  | インターフェースの説明          | 25 |

| シリアル・インターフェースのタイミング仕様 | 5  | LO インターフェースの構成       | 27 |

| 絶対最大定格                | 7  | IF 信号パスの構成           | 28 |

| 熱抵抗                   | 7  | シリアル・ペリフェラル・インターフェース | 30 |

| 静電放電 (ESD) 定格         | 7  | プロトコル                | 30 |

| ESD に関する注意            | 7  | レジスタ・アドレス            | 30 |

| ピン配置およびピン機能の説明        | 8  | 読み出し・書き込み方式          | 30 |

| 代表的な性能特性              | 9  | レジスタの詳細              | 30 |

| 動作原理                  | 18 | 代表的なアプリケーション・テスト回路   | 33 |

| 基本的な 1 ポート VNA        | 18 | 外形寸法                 | 34 |

| 周波数プラン作成 — LO 構成      | 18 | オーダー・ガイド             | 34 |

| オフセット周波数インターフェース      | 19 | 評価用ボード               | 34 |

## 改訂履歴

10/2024—Revision 0: Initial Version

## 仕様

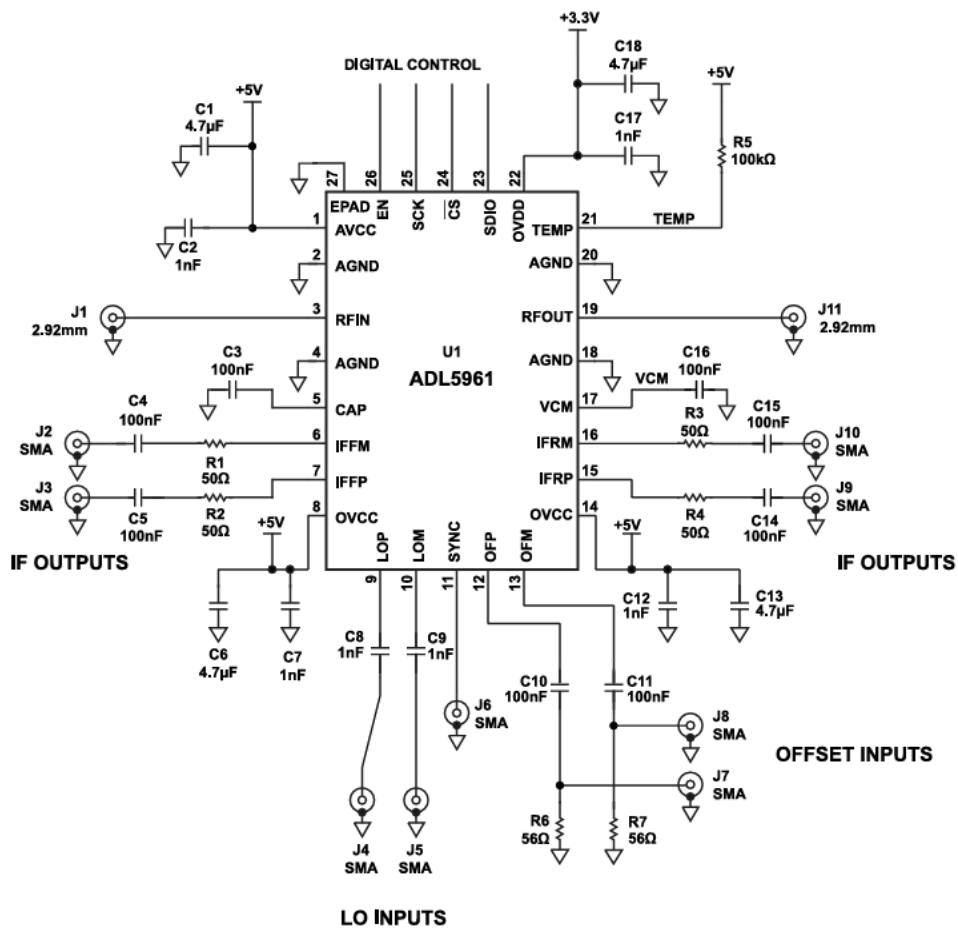

特に指定のない限り、AVCC = OVCC = 5.0V、EN = OVDD = 3.3V、VCM = 2.5V、TA = 25°C、ソース・インピーダンス (Z<sub>o</sub>) および負荷インピーダンス (Z<sub>L</sub>) = 50Ω、RFIN での連続波入力、RF 電力 (P<sub>RF</sub>) = 0dBm、LO 駆動シングルエンド、LO 電力 (P<sub>LO</sub>) = 0dBm、RF 周波数 (f<sub>RF</sub>) = 1GHz、LO 周波数 (f<sub>LO</sub>) = f<sub>RF</sub> + 500kHz、FGAIN (レジスタ 0x23、ビット[6:0]) = RGAIN (レジスタ 0x24、ビット[6:0]) = 24 (10 進数)、BYPASS (レジスタ 0x20、ビット 4) = 1、デフォルトの SPI レジスタ値。図 72 にテスト回路を示します。

表 1. 仕様

| パラメータ                                            | テスト条件/コメント                                                                                                                                                                                                                              | 最小値                                                | 代表値 | 最大値         | 単位  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|-------------|-----|

| BIDIRECTIONAL                                    | RFIN から RFOUT まで                                                                                                                                                                                                                        |                                                    |     |             |     |

| RF Frequency Range                               |                                                                                                                                                                                                                                         | 0.000009 to 26.5                                   |     |             | GHz |

| Insertion Loss                                   | f <sub>RF</sub> = 100kHz<br>f <sub>RF</sub> = 1GHz<br>f <sub>RF</sub> = 10GHz<br>f <sub>RF</sub> = 15GHz<br>f <sub>RF</sub> = 18GHz<br>f <sub>RF</sub> = 26.6GHz                                                                        | 0.9<br>1.1<br>1.8<br>1.9<br>2.0<br>4.8             |     |             | dB  |

| Return Loss (S11)                                | f <sub>RF</sub> < 20GHz                                                                                                                                                                                                                 | >12                                                |     |             | dB  |

| Directivity <sup>1</sup>                         | f <sub>RF</sub> = 100kHz、LOMODE = 0、BYPASS = 0<br>f <sub>RF</sub> = 1GHz<br>f <sub>RF</sub> = 10GHz<br>f <sub>RF</sub> = 15GHz<br>f <sub>RF</sub> = 18GHz<br>f <sub>RF</sub> = 26.5GHz                                                  | 40.5<br>35.6<br>20.4<br>25.1<br>16.7<br>9.1        |     |             | dB  |

| Third-Order Intercept (IP3)                      | f <sub>RF</sub> = 1GHz                                                                                                                                                                                                                  | 71                                                 |     |             | dBm |

| VNA CHANNELS                                     | RFIN から IFFP/IFFM まで、RFOUT から IFRP/IFRM まで                                                                                                                                                                                              |                                                    |     |             |     |

| RF Frequency Range                               |                                                                                                                                                                                                                                         | 0.000009 to 26.5                                   |     |             | GHz |

| RF to IF Leakage                                 | f <sub>RF</sub> = 50MHz、差動 IF 出力                                                                                                                                                                                                        | -13.5                                              |     |             | dBV |

| Maximum Voltage Conversion Gain <sup>2</sup>     | FGAIN、RGAIN = 0x42 (66dB)、f <sub>LO</sub> = f <sub>RF</sub> + 10MHz<br>f <sub>RF</sub> = 100kHz<br>f <sub>RF</sub> = 1GHz<br>f <sub>RF</sub> = 10GHz<br>f <sub>RF</sub> = 15GHz<br>f <sub>RF</sub> = 18GHz<br>f <sub>RF</sub> = 26.5GHz | 51.1<br>51.1<br>48.9<br>46.4<br>45<br>33.1         |     |             | dB  |

| Minimum Voltage Conversion Gain                  | FGAIN、RGAIN = 0x00 (0dB)、f <sub>LO</sub> = f <sub>RF</sub> + 10MHz<br>f <sub>RF</sub> = 100kHz<br>f <sub>RF</sub> = 1GHz<br>f <sub>RF</sub> = 10GHz<br>f <sub>RF</sub> = 15GHz<br>f <sub>RF</sub> = 18GHz<br>f <sub>RF</sub> = 26.5GHz  | -11.2<br>-11.2<br>-13.4<br>-15.9<br>-17.3<br>-26.4 | -13 | -11.2<br>-9 | dB  |

| Conversion Gain Step Size                        | 表 12 を参照                                                                                                                                                                                                                                | 4.4                                                |     | 6.3         | dB  |

| Input 1dB Compression Point (IP1dB)              | f <sub>RF</sub> = 1GHz、FGAIN = RGAIN = 0                                                                                                                                                                                                | 29                                                 |     |             | dBm |

| Output 1dB Compression Point (OP1dB)             | FGAIN、RGAIN ≥ 12、100Ω 差動負荷                                                                                                                                                                                                              | 18.4                                               |     |             | dBm |

| Input Third-Order Intercept (IIP3) <sup>3</sup>  | f <sub>RF</sub> = 1GHz、FGAIN、RGAIN = 0                                                                                                                                                                                                  | 32                                                 |     |             | dBm |

| Output Third-Order Intercept (OIP3)              | FGAIN = RGAIN = 30 (10 進数)                                                                                                                                                                                                              | 32.3                                               |     |             | dBm |

| Input Second-Order Intercept (IIP2) <sup>3</sup> | f <sub>RF</sub> = 1GHz、FGAIN = RGAIN = 0                                                                                                                                                                                                | 55                                                 |     |             | dBm |

## 仕様

表 1. 仕様 (続き)

| パラメータ                                  | テスト条件/コメント                                                                                                                                                                                                                                                                                                                                                          | 最小値          | 代表値         | 最大値          | 単位                             |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|--------------|--------------------------------|

| Noise Figure                           | FGAIN = RGAIN = 60 (10 進数)<br>$f_{RF} = 1\text{GHz}$<br>$f_{RF} = 10\text{GHz}$<br>$f_{RF} = 15\text{GHz}$<br>$f_{RF} = 18\text{GHz}$<br>$f_{RF} = 26.5\text{GHz}$                                                                                                                                                                                                  | 48.2         | 48.1        | 47.7         | dB                             |

| LO INTERFACE                           | LOP、LOM                                                                                                                                                                                                                                                                                                                                                             |              |             |              |                                |

| Input Frequency Range                  | BYPASS = 1<br>BYPASS = 0、LOMODE = 0 (2 分周)<br>BYPASS = 0、LOMODE = 1 (1 ×)<br>BYPASS = 0、LOMODE = 2 (2 ×)<br>BYPASS = 0、LOMODE = 3 (4 ×)<br>特性インピーダンス ( $Z_0$ ) = $100\Omega$ 差動                                                                                                                                                                                     | 0.01 to 26.6 | 0.01 to 2.4 | 0.01 to 26.6 | GHz                            |

| Return Loss                            |                                                                                                                                                                                                                                                                                                                                                                     | >10          |             |              | dB                             |

| Input Power                            |                                                                                                                                                                                                                                                                                                                                                                     | -6           | 0           | +6           | dBm                            |

| LO to RF Leakage                       | BYPASS = 1、 $f_{LO}$<br>BYPASS = 0、LOMODE = 0 (2 分周)、 $f_{LO}/2$<br>BYPASS = 0、LOMODE = 0 (2 分周)、 $f_{LO}$<br>BYPASS = 0、LOMODE = 1 (1 ×)、 $f_{LO}$<br>BYPASS = 0、LOMODE = 2 (2 ×)、 $f_{LO}$<br>BYPASS = 0、LOMODE = 2 (2 ×)、 $2f_{LO}$<br>BYPASS = 0、LOMODE = 3 (4 ×)、 $f_{LO}$<br>BYPASS = 0、LOMODE = 3 (4 ×)、 $2f_{LO}$<br>BYPASS = 0、LOMODE = 3 (4 ×)、 $4f_{LO}$ |              | -77.3       | -83.4        | dBm                            |

| LO to IF Leakage                       | $f_{RF} = 50\text{MHz}$ 、差動,                                                                                                                                                                                                                                                                                                                                        |              | 13.6        |              | dBm                            |

| OFFSET FREQUENCY (OF) INTERFACE        | OPF、OFM                                                                                                                                                                                                                                                                                                                                                             |              |             |              |                                |

| Input Frequency Range                  |                                                                                                                                                                                                                                                                                                                                                                     | 0.1 to 400   |             |              | MHz                            |

| OF Induced Spurious Tone at $f_{IF}^4$ | OFMODE = 2 (4 分周)、 $3f_{IF} = 1.5\text{MHz}$<br>$5f_{IF} = 2.5\text{MHz}$<br>$7f_{IF} = 3.5\text{MHz}$                                                                                                                                                                                                                                                              |              | -3.2        | -6.2         | dBc                            |

| Input Impedance                        | 差動                                                                                                                                                                                                                                                                                                                                                                  |              | 10  0.5     |              | $\text{k}\Omega  \text{pF}$    |

| Voltage Swing                          | 差動                                                                                                                                                                                                                                                                                                                                                                  | 0.125        | 0.5         | 2.0          | V p-p                          |

| IF OUTPUT INTERFACE                    | IFFP/IFFM および IFRP/IFRM                                                                                                                                                                                                                                                                                                                                             |              |             |              |                                |

| Output Frequency Range                 |                                                                                                                                                                                                                                                                                                                                                                     | 0.1 to 100   |             |              | MHz                            |

| Maximum Peak-to-Peak Voltage           | 差動                                                                                                                                                                                                                                                                                                                                                                  |              | 8           |              | V p-p                          |

| Short-Circuit Output Current           | シングルエンド、ソース、出力電圧 = 0V                                                                                                                                                                                                                                                                                                                                               | 200          |             |              | mA                             |

| Output Noise Spectral Density          | $f = f_{IF} = 500\text{kHz}$ 、FGAIN = RGAIN = 60 (10 進数)、差動                                                                                                                                                                                                                                                                                                         |              | 207         |              | $\mu\text{V}/\sqrt{\text{Hz}}$ |

| VCM INTERFACE                          | VCM                                                                                                                                                                                                                                                                                                                                                                 |              |             |              |                                |

| Input Voltage Range                    |                                                                                                                                                                                                                                                                                                                                                                     | 1.0          | 4.0         |              | V                              |

| Output VCM Error                       | IF 出力コモンモード電圧 ( $V_{CM}$ )                                                                                                                                                                                                                                                                                                                                          | -100         | 0           | +100         | mV                             |

| Input Impedance                        |                                                                                                                                                                                                                                                                                                                                                                     |              | 10k    4p   |              | $\Omega    \text{F}$           |

| ENABLE INTERFACE                       | EN                                                                                                                                                                                                                                                                                                                                                                  |              |             |              |                                |

| Logic Low Input Voltage                |                                                                                                                                                                                                                                                                                                                                                                     |              | 0.8         |              | V                              |

| Logic High Input Voltage               |                                                                                                                                                                                                                                                                                                                                                                     | 2.0          |             | 20           | V                              |

| Current into Pin                       |                                                                                                                                                                                                                                                                                                                                                                     |              |             |              | $\mu\text{A}$                  |

## 仕様

表 1. 仕様 (続き)

| パラメータ                        | テスト条件/コメント                                         | 最小値        | 代表値        | 最大値        | 単位      |

|------------------------------|----------------------------------------------------|------------|------------|------------|---------|

| SPI AND SYNC INTERFACE       |                                                    |            |            |            |         |

| Logic Low Input Voltage      | $\overline{CS}$ 、SCK、SDIO、SYNC                     |            | 0.3 × OVDD | 0.3 × OVDD | V       |

| Logic High Input Voltage     |                                                    | 0.7 × OVDD |            | 0.7 × OVDD | V       |

| Input Voltage Hysteresis     |                                                    | 209        |            | 209        | mV      |

| Current into Pin             | $\overline{CS}$ 、SCK、SYNC                          |            | 20         | 20         | $\mu$ A |

| Logic Low Output Voltage     | SDIO、10mA をシンク                                     |            | 0.3 × OVDD | 0.3 × OVDD | V       |

| Logic High Output Voltage    | SDIO、10mA をソース                                     | 0.7 × OVDD |            | 0.7 × OVDD | V       |

| POWER SUPPLY INTERFACES      | AVCC、OVCC、OVDD                                     |            |            |            |         |

| Supply Voltage (AVCC, OVCC)  |                                                    | 4.75       | 5.0        | 5.25       | V       |

| Supply Current (AVCC + OVCC) | EN = AVCC、レジスタ 0x20 = 0x0B (BYPASS = 0、LOMODE = 3) | 200        | 225        | 250        | mA      |

|                              | EN = AVCC、レジスタ 0x20 = 0x1D (OFMODE = 3)            | 110        | 120        | 130        | mA      |

|                              | EN = 0V (シャットダウン)                                  |            | 32         | 2000       | $\mu$ A |

| SPI Supply Voltage (OVDD)    |                                                    | 1.8        | 3.3        | 3.6        | V       |

| SPI Supply Current (OVDD)    |                                                    | 2          | 24         | 500        | $\mu$ A |

1 RFOUT のショート、オープンおよび負荷端末に対する逆方向と順方向の IF 出力ポートの比率の測定から得られる誤差補正係数 (e00)。プリント回路基板 (PCB) 上のスルー・ラインについて測定した伝送行列を 2 分割し、一方を終端の理想モデルに組み込むことによって、PCB 伝送ラインの組込みが解除されます。詳細については、[キャリブレーションと誤差補正のセクション](#)を参照してください。

2 高インピーダンス IF 負荷を用いた、RF 入力から差動 IF 出力までの電圧ゲイン。FGAIN および RGAIN ビット・フィールドは 7 ビット幅ですが、増幅されたノイズが IF 出力ドライバを飽和させ始めるため、0x42 を超える値の実用性は限られます。

3 第 2 の RF トーン電力 = 0dBm、周波数 =  $f_{RF} + 100\text{kHz}$ 。

4  $f_{IF} = 500\text{kHz}$  での必要な出力に対する大きさ。

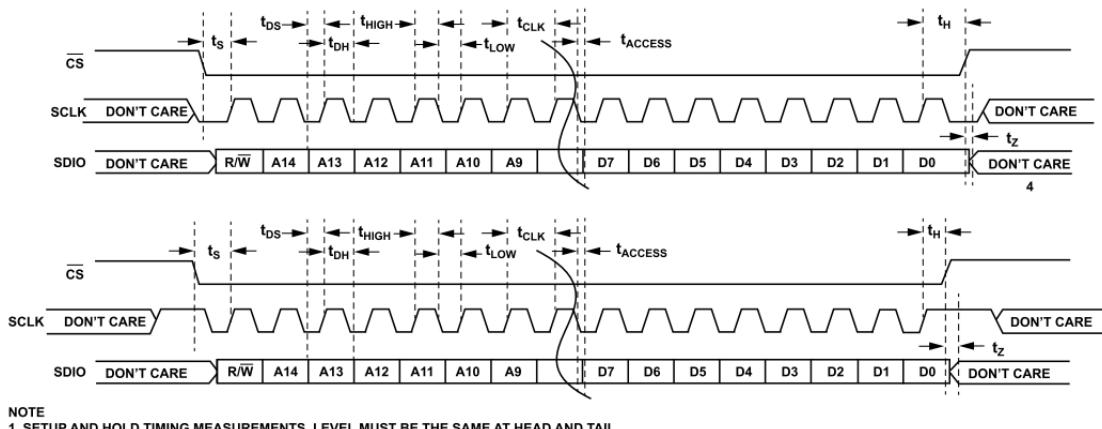

## シリアル・インターフェースのタイミング仕様

図 2. SPI タイミング図

表 2. SPI のタイミング仕様

| Parameter  | Description                                            | Min | Typ | Max | Unit |

|------------|--------------------------------------------------------|-----|-----|-----|------|

| $t_{DS}$   | Setup time between data and rising edge of SCLK        | 15  |     |     | ns   |

| $t_{DH}$   | Hold time between data and rising edge of SCLK         | 15  |     |     | ns   |

| $t_{CLK}$  | Clock period                                           | 150 |     |     | ns   |

| $t_s$      | Setup time between $\overline{CS}$ and SCLK            | 40  |     |     | ns   |

| $t_H$      | Hold time between $\overline{CS}$ and SCLK             | 40  |     |     | ns   |

| $t_{HIGH}$ | Minimum period that SCLK must be in a logic high state | 75  |     |     | ns   |

| $t_{LOW}$  | Minimum period that SCLK must be in a logic low state  | 75  |     |     | ns   |

## 仕様

表 2. SPI のタイミング仕様（続き）

| Parameter    | Description                                                                                | Min | Typ | Max | Unit |

|--------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $t_Z$        | Maximum time delay between CS deactivation and SDIO bus return to high impedance           |     |     | 150 | ns   |

| $t_{ACCESS}$ | Maximum time delay between falling edge of SCLK and output data valid for a read operation |     |     | 30  | ns   |

## 絶対最大定格

表 3. 絶対最大定格

| Parameter                           | Rating                 |

|-------------------------------------|------------------------|

| Supply Voltage (AVCC and OVCC)      | 5.5 V                  |

| RFIN, RFOUT Input AC Power          |                        |

| Average <sup>1</sup>                | 30 dBm                 |

| Peak <sup>1</sup>                   | 35 dBm                 |

| DC Voltage                          |                        |

| OVDD                                | -0.3 V to +3.8 V       |

| SCK, CS, and SDIO                   | -0.3 V to OVDD + 0.3 V |

| IFFP, IFFM, IFRP, IFRM <sup>2</sup> | -0.3 V to OVCC + 0.3 V |

| Any Other Pin <sup>3</sup>          | -0.3 V to AVCC + 0.3 V |

| DC Current RFIN to or from RFOUT    | 100 mA                 |

| Temperature                         |                        |

| Maximum T <sub>J</sub>              | 150°C                  |

| T <sub>A</sub> Operating Range      | -40°C to +105°C        |

| Storage Range                       | -65°C to +150°C        |

1 製品テストの対象外です。設計と、製品テスト済みパラメータとの相関によって確保されています。ピーク電力デューティ・サイクルは最大 10% です。

2 これらのピンの電圧は、5.5V、OVCC + 0.3V を超えないこと、または-0.3V を下回らないことが必要です。

3 これらのピンの電圧は、5.5V、AVCC + 0.3V を超えないこと、または-0.3V を下回らないことが必要です。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。これはストレス定格のみを定めたものであり、本仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを示唆するものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、PCB の設計と動作環境に直接関連しています。PCB の熱設計には、細心の注意を払う必要があります。

表 4. 热抵抗

| Package           |                              |                              |                               |                               |                              |                              |      |

|-------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|------------------------------|------------------------------|------|

| Type <sup>1</sup> | θ <sub>JA</sub> <sup>2</sup> | θ <sub>JB</sub> <sup>3</sup> | θ <sub>JCT</sub> <sup>4</sup> | θ <sub>JCB</sub> <sup>5</sup> | Ψ <sub>JT</sub> <sup>6</sup> | Ψ <sub>JB</sub> <sup>7</sup> | Unit |

| CC-26-2           | 39.32                        | 13.10                        | 30.09                         | 7.63                          | 1.30                         | 12.95                        | °C/W |

1 テスト条件 1 : 热抵抗のシミュレーション値は、2S2P JEDEC PCB の使用に基づいています。オーダー・ガイドを参照してください。

2 θ<sub>JA</sub>は、1 立方フィートの密封容器内で測定された、ジャンクションと周囲（またはダイと周囲）の間の熱抵抗です。

3 θ<sub>JB</sub>は、ジャンクションとボードの間の熱抵抗です。

4 θ<sub>JCT</sub>は、ジャンクションとケース上面（またはダイとパッケージ）の間の熱抵抗です。

5 θ<sub>JCB</sub>はジャンクションとケース底面の間の熱抵抗です。

6 Ψ<sub>JT</sub>はジャンクションと上面の間の熱特性値です。

7 Ψ<sub>JB</sub>はジャンクションとボードの間の熱特性値です。

## 静電放電 (ESD) 定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帶電デバイス・モデル (FICDM)。

## ADL5961 の ESD 定格

表 5. ADL5961、26 ピン LGA

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 2000                    | 2     |

| FICDM     | 500                     | 1B    |

## ESD に関する注意

### ESD (静電放電) の影響を受けやすいデバイスです。

帯電したデバイスや回路基板は、検出されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

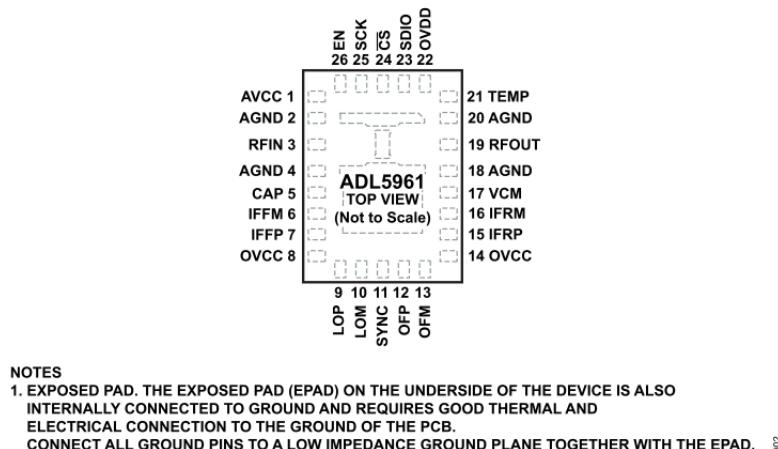

## ピン配置およびピン機能の説明

図 3. ピン配置

表 6. ピン機能の説明

| ピン番号         | 記号                     | 説明                                                                                                                                                                                     |

|--------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | AVCC                   | アナログ正電源ピン。1nF のコンデンサと 4.7μF のコンデンサを AVCC ピンのできるだけ近くに配置してバイパスします。パワーアップ時には、OVDD 電圧を印加する前に AVCC 電圧を印加します。パワーダウン時には、AVCC 電圧を除去する前に OVDD 電圧を除去します。                                         |

| 2, 4, 18, 20 | AGND                   | アナログ・グラウンド・ピン。すべてのグラウンド・ピンは内部接続されています。ピン 2 とピン 4 は、RFIN 伝送ライン（ピン 3）の RF リターン・グラウンドとして使用します。ピン 18 とピン 20 は、RFOUT 伝送ライン（ピン 19）の RF リターン・グラウンドとして使用します。                                   |

| 3, 19        | RFIN, RFOUT            | 1 次伝送ラインの RF 入出力。RFIN と RFOUT の負荷特性インピーダンスは 50Ω です。ソースと負荷への接続には DC 阻止コンデンサが必要です。オープンおよびショート終端を用いるときは、最大消費電力定格を超えないようにしてください。                                                           |

| 5            | CAP                    | バイパス・コンデンサ。100kHz 動作には 100nF のコンデンサを推奨します。                                                                                                                                             |

| 6, 7, 15, 16 | IFFM, IFFP, IFRP, IFRM | 差動 IF 出力。ピン 6 とピン 7 は、（RFIN から RFOUT への）順方向電力転送に結合されます。ピン 15 とピン 16 は、（RFOUT から RFIN への）逆方向電力転送に結合されます。                                                                                |

| 8, 14        | OVCC                   | IF アンプの正電源ピン。AVCC に接続する前に、各ピンに 1nF コンデンサと 4.7μF コンデンサを使用して OVCC をバイパスします。これらのコンデンサは OVCC のできるだけ近くに配置します。パワーアップ時には、OVDD 電圧を印加する前に OVCC 電圧を印加します。パワーダウン時には、OVCC 電圧を除去する前に OVDD 電圧を除去します。 |

| 9, 10        | LOP, LOM               | ダウンドコンバージョン・ミキサーの LO 入力。LOP と LOM は 100Ω 差動で内部終端されます。差動またはシングルエンドの信号ソースで LOP および LOM ピンを駆動できます。レジスタ 0x20 で LO インターフェースを設定します。LO インターフェースには DC 阻止コンデンサを推奨します。                           |

| 11           | SYNC                   | 同期入力。この CMOS 入力ピンは、ハイに駆動されたときに LO および IF 入力インターフェースの分周器を停止し、ローに駆動されたときに同期を開始します。フローティング状態の場合、内部の 415kΩ プルダウン抵抗によって SYNC 機能が無効になります。                                                    |

| 12, 13       | OFP, OFM               | IF オフセット基準周波数入力。OFP ピンと OFM ピンは、レジスタ 0x20 の OFMODE ビット（ビット[3:2]）が 0x0、0x1 または 0x2 に等しいときに、IF 出力の中心周波数を設定します。OFMODE ビットを 0x3 に設定すると、この入力は無効になります。                                       |

| 17           | VCM                    | IF 出力コモンモード電圧制御。VCM ピンは、IFFM、IFFP、IFRP、IFRM の出力コモンモード電圧を設定します。オープンの場合、OVCC/2 にフローティングします。                                                                                              |

| 21           | TEMP                   | 温度センス・ダイオード。TEMP ピンは、オンチップ接合ダイオードのアノードに接続されています。このピンに既知の電流を流しながら、ピンの電圧を測定することによって、ダイ温度を測定できます。                                                                                         |

| 22           | OVDD                   | SPI 正電源ピン。OVDD ピンを SPI コントローラの電源に接続すると、SPI バス接続で電圧レベル変換器が不要になります。パワーアップ時には、OVDD 電圧を印加する前に、AVCC 電圧と OVCC 電圧を印加します。パワーダウン時には、AVCC 電圧と OVCC 電圧を除去する前に、OVDD 電圧を除去します。                      |

| 23           | SDIO                   | SPI データの入出力。SDIO ピンがフローティング状態の場合、内部の 415kΩ プルダウン抵抗によりロジック・ローにプルダウンされます。                                                                                                                |

| 24           | CS                     | SPI チップ・セレクト（アクティブ・ロー）。CS ピンがフローティング状態の場合、内部の 415kΩ プルアップ抵抗により OVDD に接続されます。                                                                                                           |

| 25           | SCK                    | SPI クロック入力。SCK がフローティング状態の場合、内部の 415kΩ プルダウン抵抗よりロジック・ローにプルダウンされます。                                                                                                                     |

| 26           | EN                     | チップ・イネーブル。EN ピンがロジック・ハイの場合、ADL5961 はイネーブルされます。EN ピンがロジック・ローの場合、ADL5961 はシャットダウンされます。EN がフローティング状態の場合、内部の 415kΩ プルダウン抵抗により、ADL5961 はディスエーブルされます。                                        |

|              | EPAD                   | 露出パッド。デバイス下面の露出パッド（EPAD）は、グラウンドにも内部接続されており、PCB のグラウンドへの良好な熱的・電気的接続が必要です。すべてのグラウンド・ピンは、EPAD と共に低インピーダンスのグランド・プレーンに接続してください。                                                             |

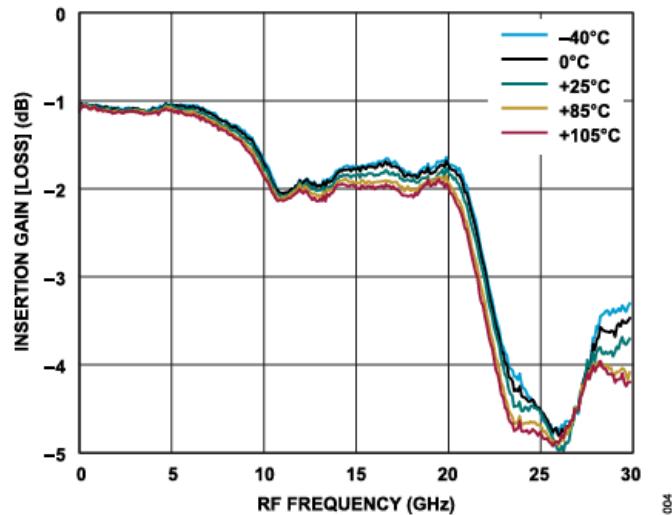

## 代表的な性能特性

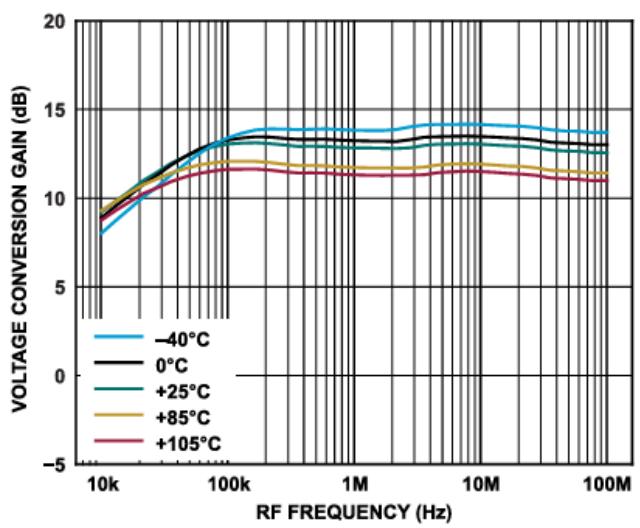

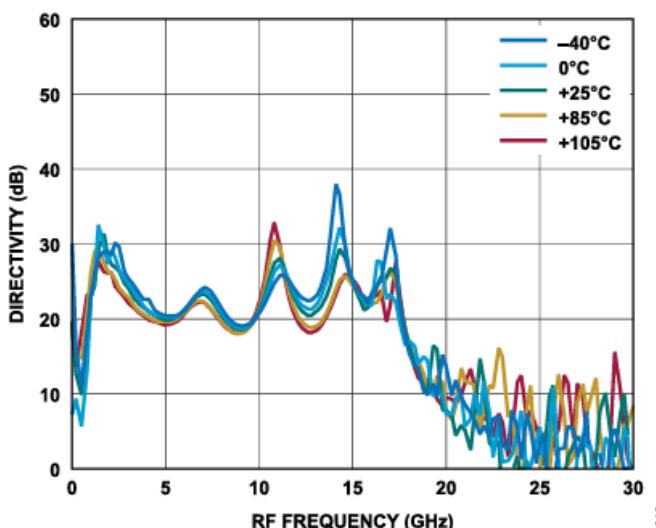

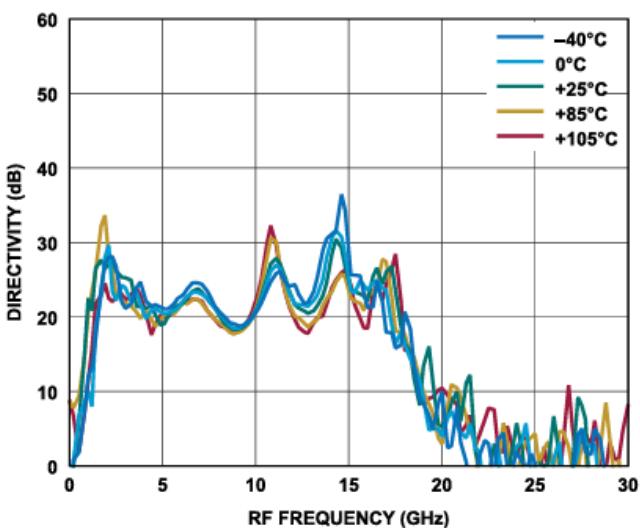

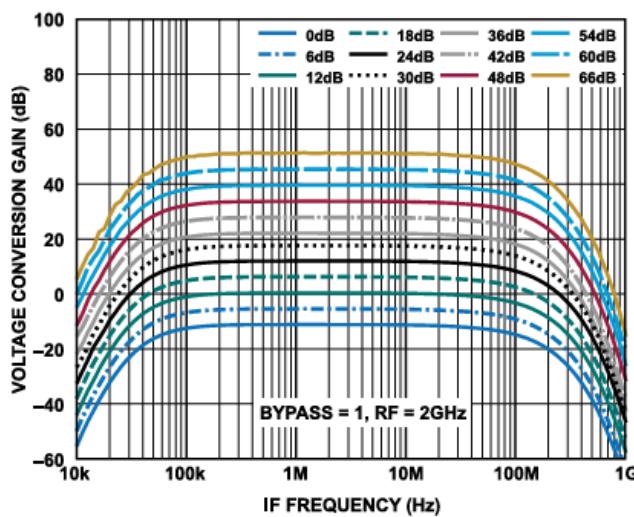

特に指定のない限り、AVCC = OVCC = 5.0V、EN = OVDD = 3.3V、VCM = 2.5V、TA = 25°C、50Ω のソースおよび負荷インピーダンス、RFIN での連続波入力、Z<sub>0</sub> = 50Ω、P<sub>RF</sub> = 0dBm、LO 駆動シングルエンド、P<sub>LO</sub> = 0dBm、f<sub>RF</sub> = 1GHz、f<sub>LO</sub> = f<sub>RF</sub> + 500kHz。BYPASS = 1、FGAIN = RGAIN = 24、CIF1 = CIF2 = 15。図 72 にテスト回路を示します。指向性と電圧変換ゲインのすべての測定において、RFOUT に 0.1μF のコンデンサを使用。

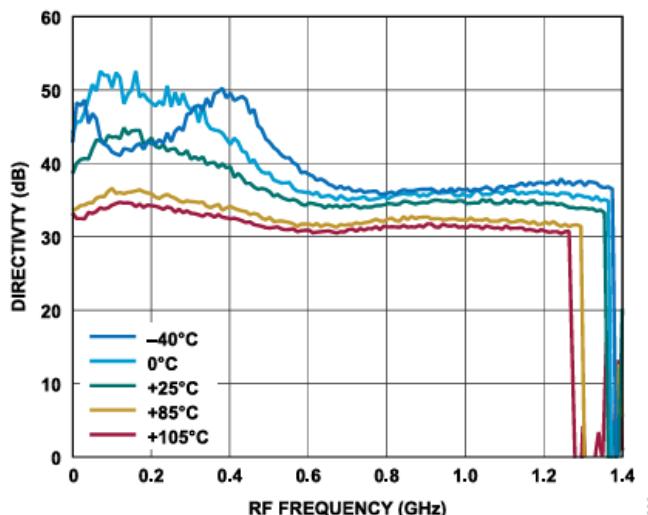

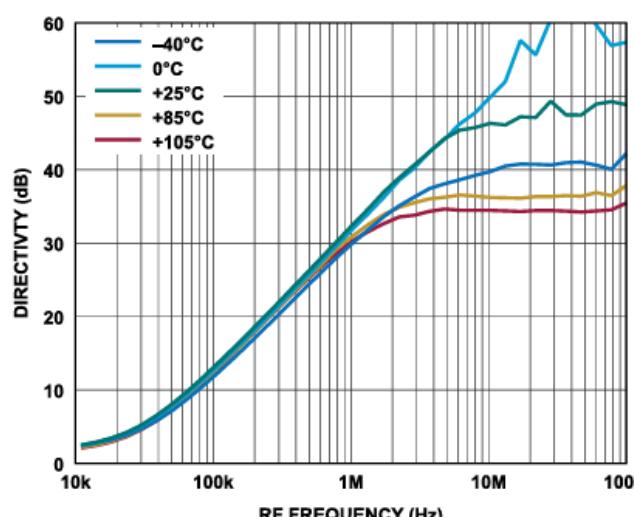

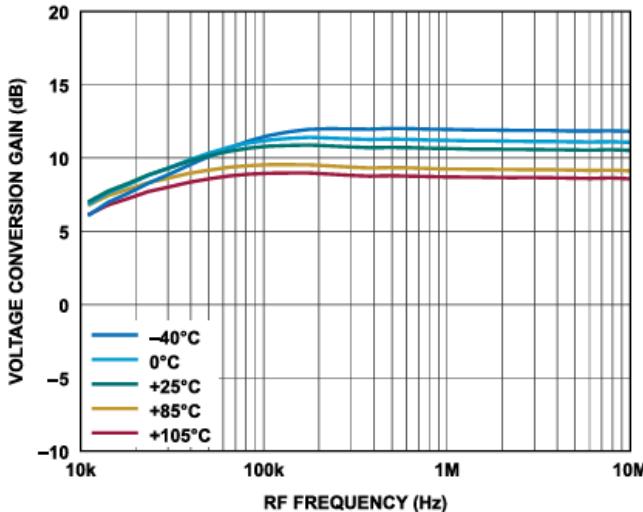

図 4. 様々な温度での、RFIN から RFOUT への挿入ゲイン (損失) と RF 周波数の関係

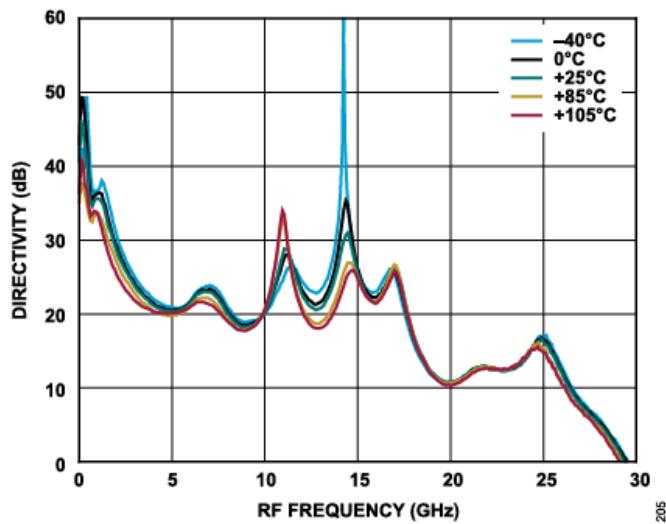

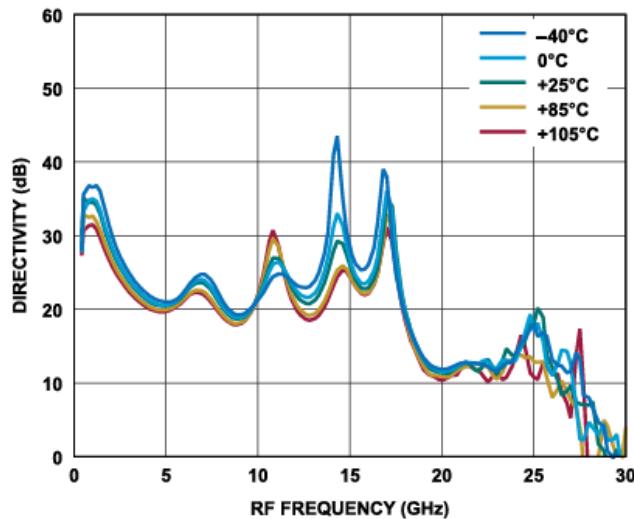

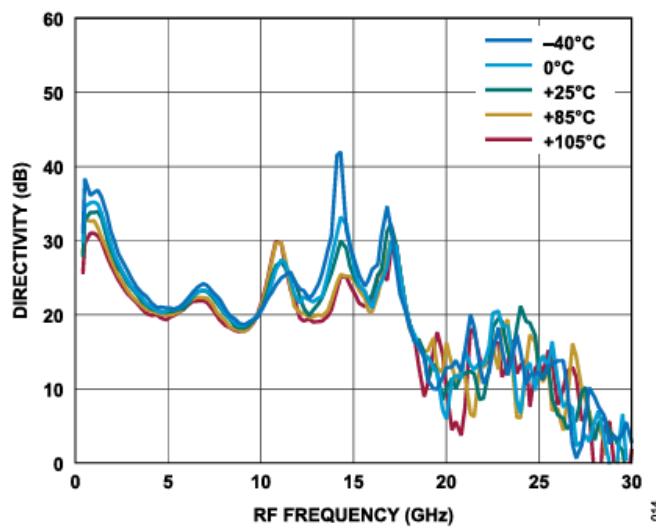

図 6. 様々な温度での指向性と RF 周波数の関係 (LOMODE = 0、OFMODE = 3)

図 5. 様々な温度での指向性と RF 周波数の関係 (BYPASS = 1)

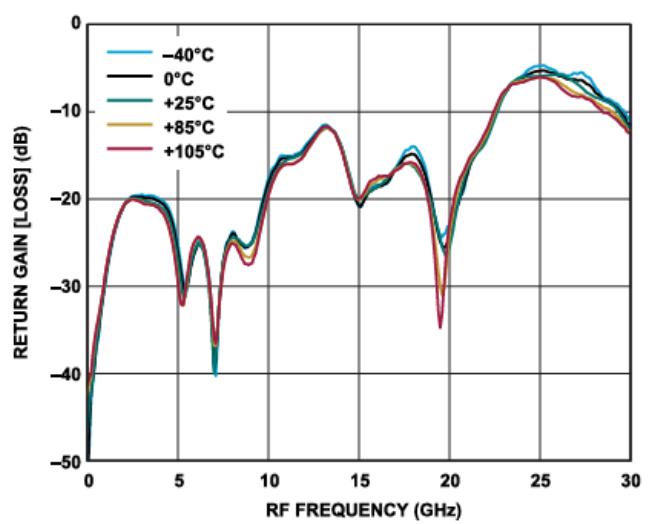

図 7. 様々な温度での、RFIN および RFOUT の反射ゲイン (損失) と RF 周波数の関係

## 代表的な性能特性

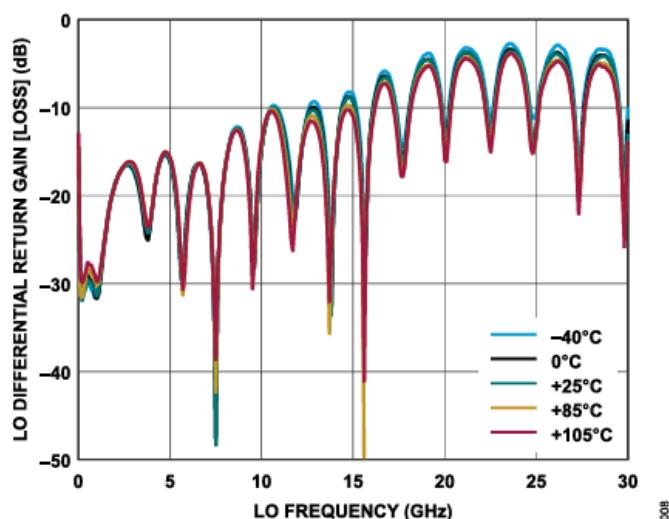

図 8. 様々な温度での LO 差動反射ゲイン（損失）と LO 周波数の関係 ( $Z_0 = 100\Omega$ )

図 11. 様々な温度での指向性と RF 周波数の関係 (LOMODE = 1、OFMODE = 3)

図 9. 様々な温度での指向性と RF 周波数の関係 (LOMODE = 0、OFMODE = 2)

図 12. 様々な温度での指向性と RF 周波数の関係 (LOMODE = 2、OFMODE = 3)

図 10. 様々な温度での指向性と RF 周波数の関係 (LOMODE = 0、OFMODE = 3)

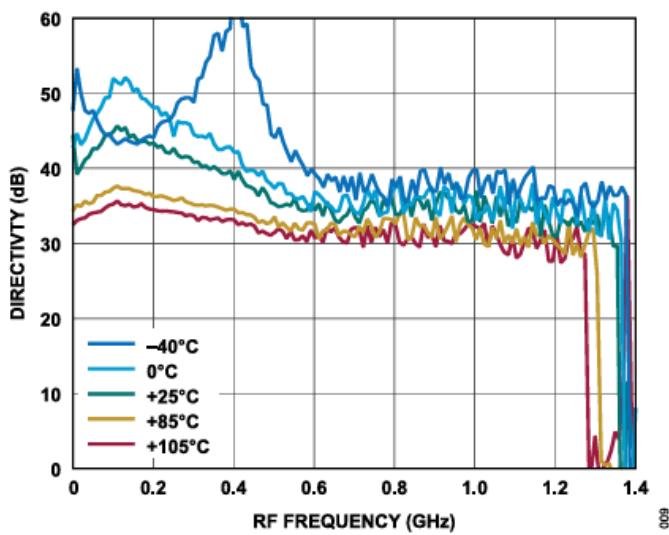

図 13. 様々な温度での指向性と低 RF 周波数の関係 (LOMODE = 0、OFMODE = 2)

## 代表的な性能特性

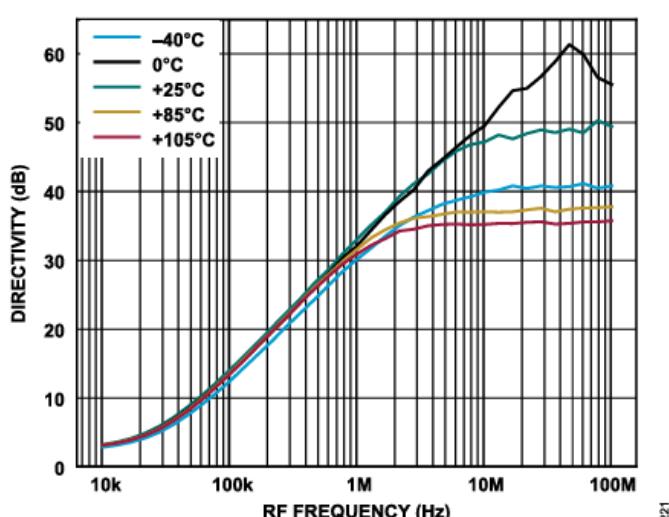

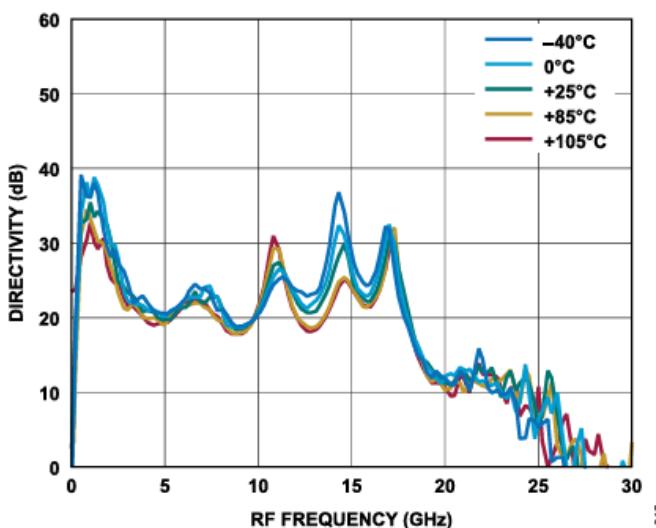

図 14. 様々な温度での指向性と RF 周波数の関係

(LOMODE = 1、OFMODE = 2)

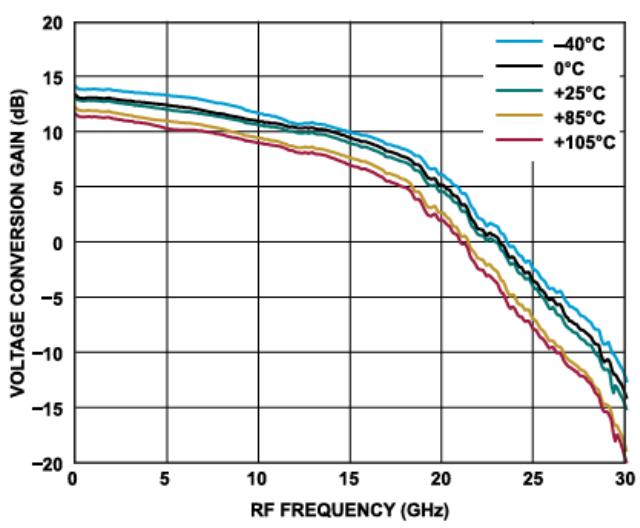

図 17. 様々な温度での、電圧変換ゲインと RF 周波数の関係

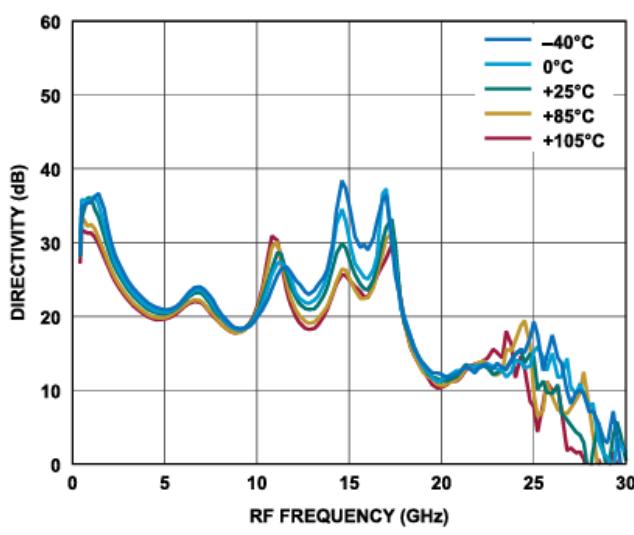

図 15. 様々な温度での指向性と RF 周波数の関係

(LOMODE = 2、OFMODE = 2)

図 18. 様々な温度での電圧変換ゲインと RF 周波数の関係

(LOMODE = 0、OFMODE = 3)

図 16. 様々な温度での指向性と RF 周波数の関係

(LOMODE = 3、OFMODE = 3)

図 19. 様々な温度での指向性と RF 周波数の関係

(LOMODE = 3、OFMODE = 2)

## 代表的な性能特性

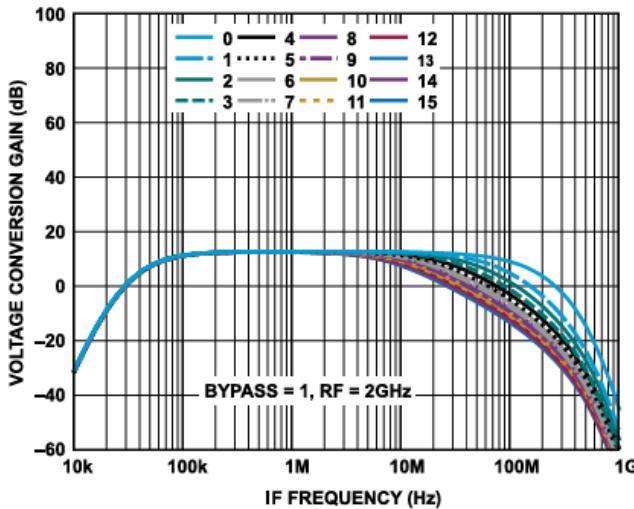

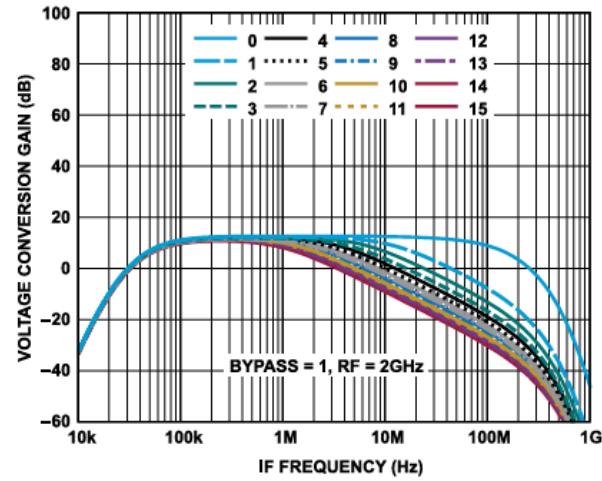

図 20. 様々なゲイン設定値 (FGAIN、RGAIN) での電圧変換ゲインと IF 周波数の関係

図 21. 様々な温度での電圧変換ゲインと RF 周波数の関係 (LOMODE = 0、OFMODE = 2)

図 22. 電圧変換ゲインと IF 周波数および CIF1 設定値の関係 (CIF2 = 0、BYPASS = 1、RF = 2GHz)

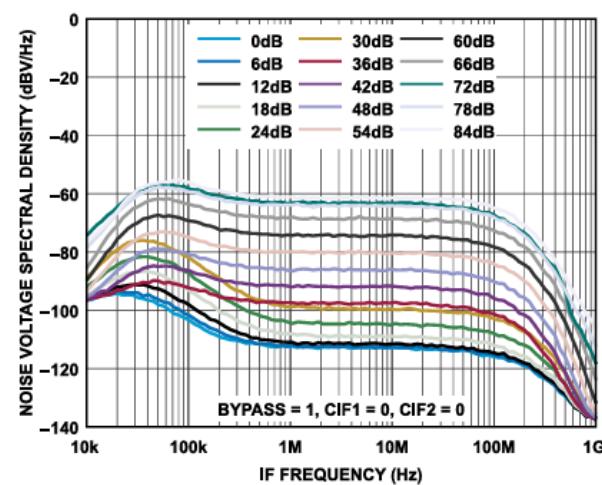

図 23. 様々なゲイン設定値 (FGAIN、RGAIN) での差動 IF 出力のノイズ電圧スペクトラル密度と IF 周波数の関係 (BYPASS = 1、CIF1 = CIF2 = 0)

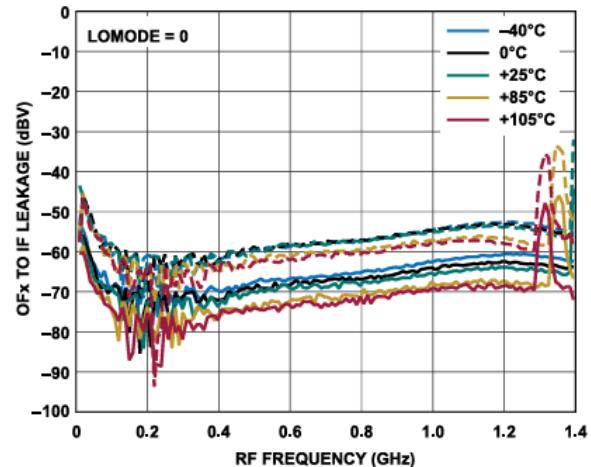

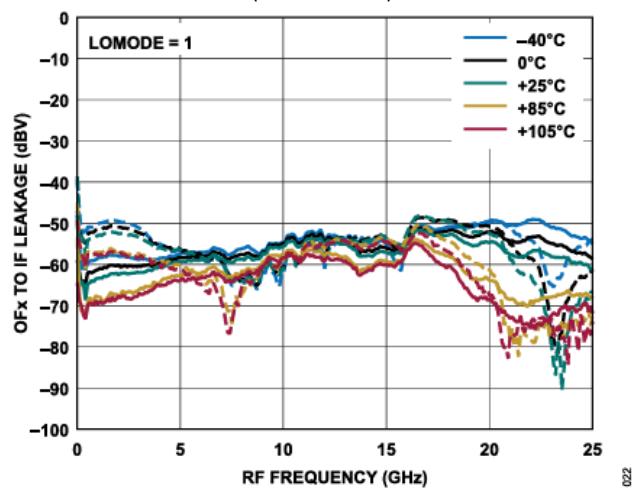

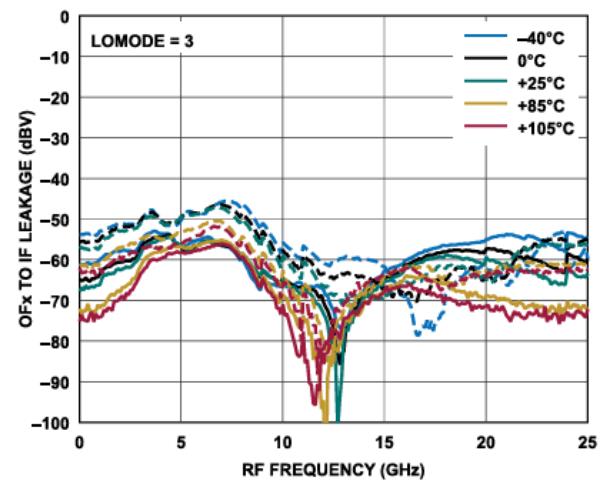

図 24. 様々な温度での、OFx から IF への漏れと RF 周波数の関係 (LOMODE = 0、OFMODE = 2、実線：順方向チャンネル、破線：逆方向チャンネル)

図 25. 様々なCIF2 設定値での電圧変換ゲインと IF 周波数の関係 (CIF1 = 0、BYPASS = 1、RF = 2GHz)

## 代表的な性能特性

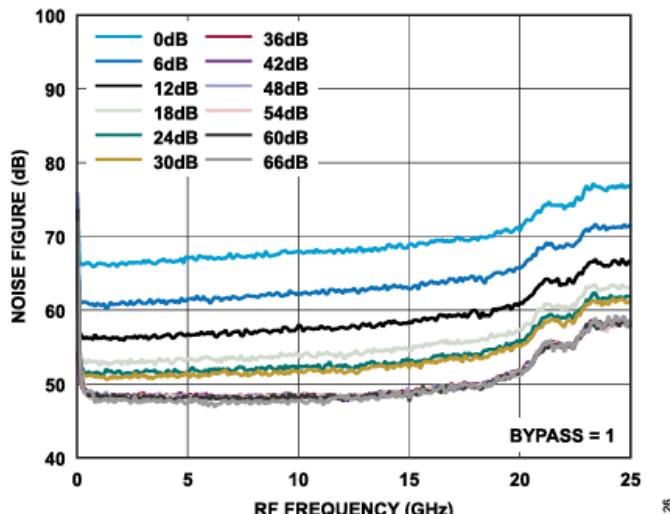

図 26. 様々な IF ゲイン設定値でのノイズ指数と RF 周波数の関係 (BYPASS = 1)

図 27. 様々な温度での、OFx から IF への漏れと RF 周波数の関係 (LOMODE = 1、OFMODE = 2、実線：順方向チャンネル、破線：逆方向チャンネル)

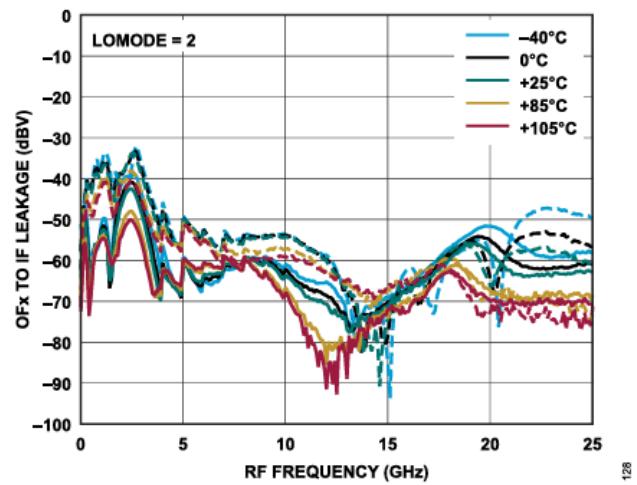

図 28. 様々な温度での、OFx から IF への漏れと RF 周波数の関係 (LOMODE = 2、OFMODE = 2、実線：順方向チャンネル、破線：逆方向チャンネル)

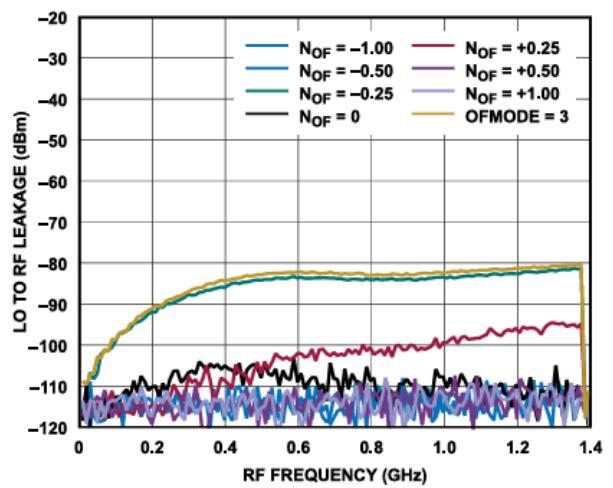

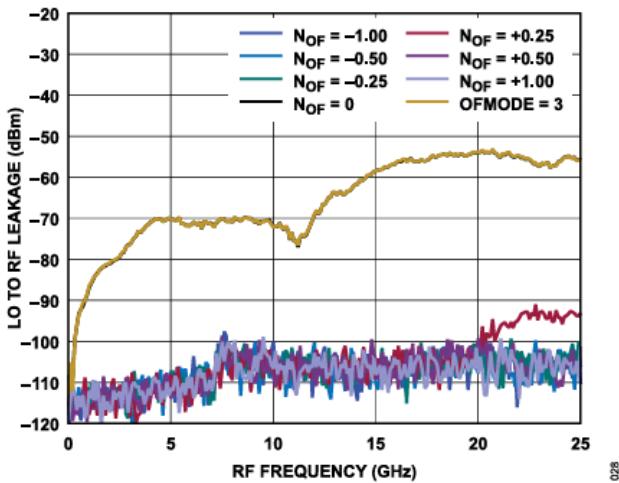

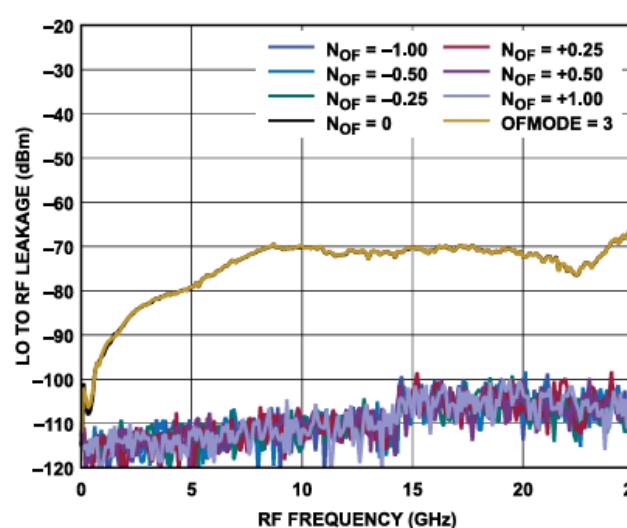

図 29. LO から RF への漏れと RF 周波数の関係 (LOMODE = 0、測定周波数 : OFMODE = 2 では  $f_{RF} + N_{OF} \times f_{OF}$ 、OFMODE = 3 では、 $f_{RF} + f_{IF}$ )

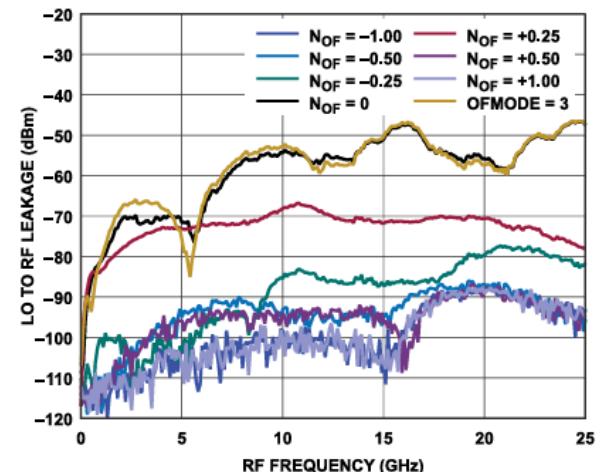

図 30. LO から RF への漏れと RF 周波数の関係 (LOMODE = 1、測定周波数 : OFMODE = 2 では  $f_{RF} + N_{OF} \times f_{OF}$ 、OFMODE = 3 では、 $f_{RF} + f_{IF}$ )

図 31. 様々な温度での、OFx から IF への漏れと RF 周波数の関係 (LOMODE = 3、OFMODE = 2、実線：順方向チャンネル、破線：逆方向チャンネル)

## 代表的な性能特性

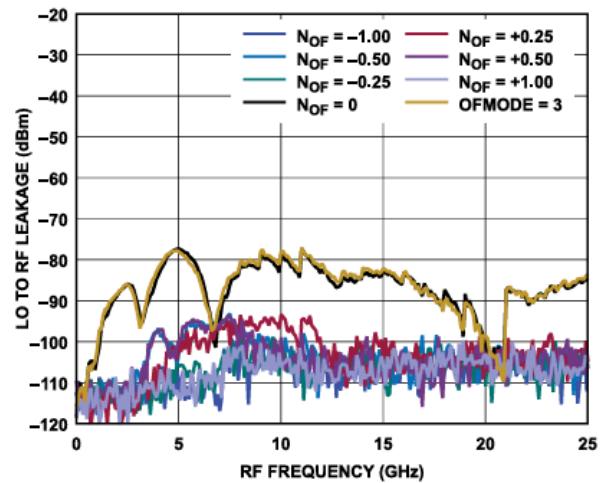

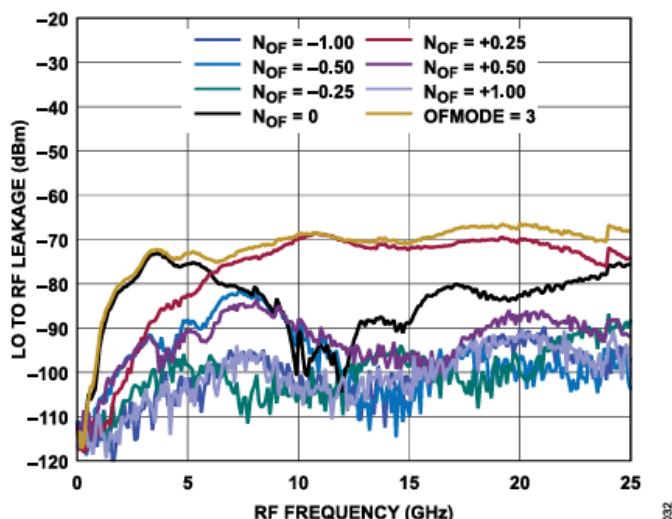

図 32. LO から RF への漏れと RF 周波数の関係 (LOMODE = 0、

測定周波数 : OFMODE = 2 では  $f_{RF} + N_{OF} \times f_{OF}$ 、

OFMODE = 3 では  $f_{RF} + f_{IF}$ )

図 33. LO から RF への漏れと RF 周波数の関係 (LOMODE = 2、

測定周波数 : OFMODE = 2 では  $f_{RF}/2 + N_{OF} \times f_{OF}$ 、

OFMODE = 3 では  $f_{RF}/2 + f_{IF}$ )

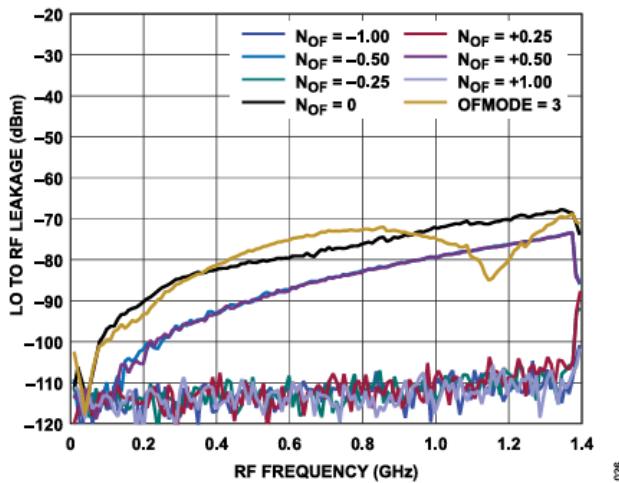

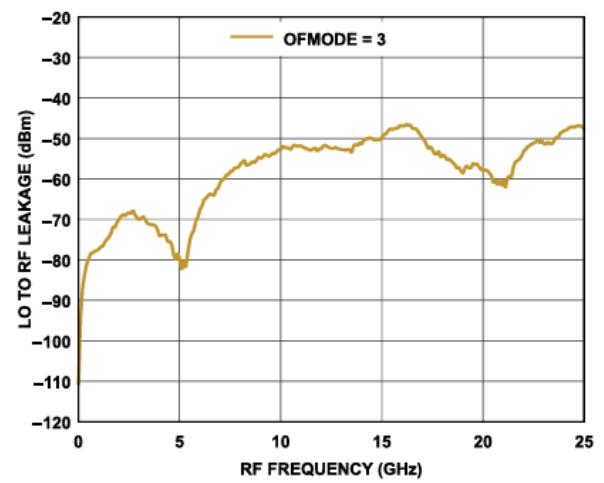

図 35. LO から RF への漏れと RF 周波数の関係 (LOMODE = 3、

測定周波数 : OFMODE = 2 では  $f_{RF}/2 + N_{OF} \times f_{OF}$ 、

OFMODE = 3 では  $f_{RF}/2 + f_{IF}$ )

図 36. LO から RF への漏れと RF 周波数の関係

(BYPASS = 1、測定周波数 =  $f_{RF} + f_{IF}$ )

図 34. LO から RF への漏れと RF 周波数の関係 (LOMODE = 2、

測定周波数 : OFMODE = 2 では  $f_{RF} + N_{OF} \times f_{OF}$ 、

OFMODE = 3 では  $f_{RF} + f_{IF}$ )

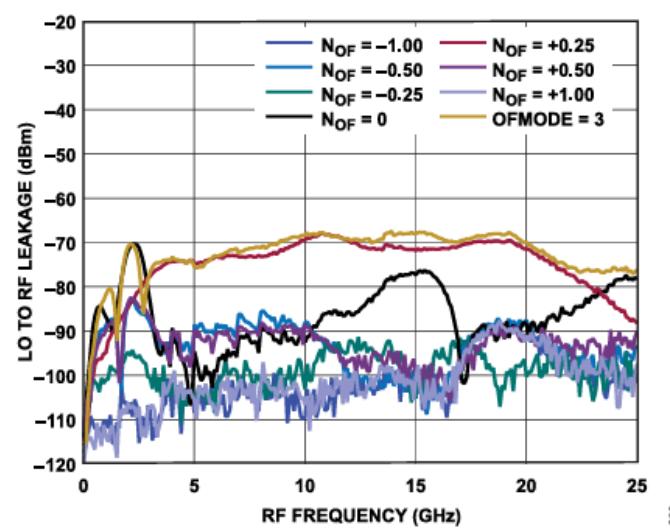

図 37. LO から RF への漏れと RF 周波数の関係 (LOMODE = 3、

測定周波数 : OFMODE = 2 では  $f_{RF}/4 + N_{OF} \times f_{OF}$ 、

OFMODE = 3 では  $f_{RF}/4 + f_{IF}$ )

## 代表的な性能特性

図 38. LO から RF への漏れと RF 周波数の関係 (LOMODE = 3、

測定周波数 : OFMODE = 2 では  $f_{RF} + N_{OF} \times f_{OF}$ 、

OFMODE = 3 では  $f_{RF} + f_{IF}$ )

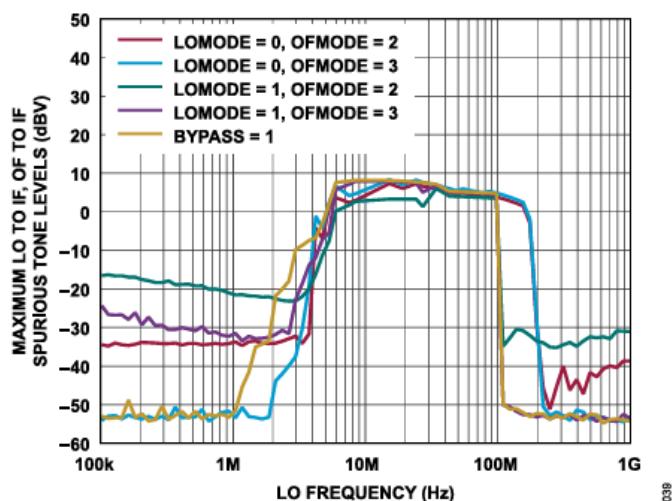

図 39. LO から IF および OF から IF への最大スプリアス・トン・レベルと LO 周波数の関係 (CIF1 = CIF2 = 0)

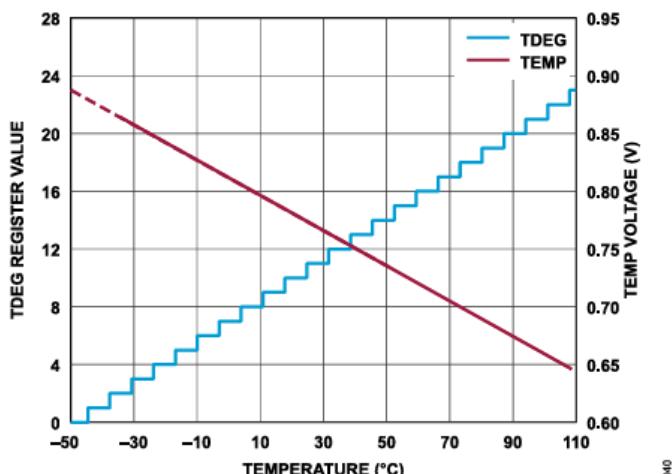

図 40. TDEG レジスタ値および TEMP 電圧と温度の関係

(TEMP 電流、 $I_{TEMP} = 42\mu A$ )

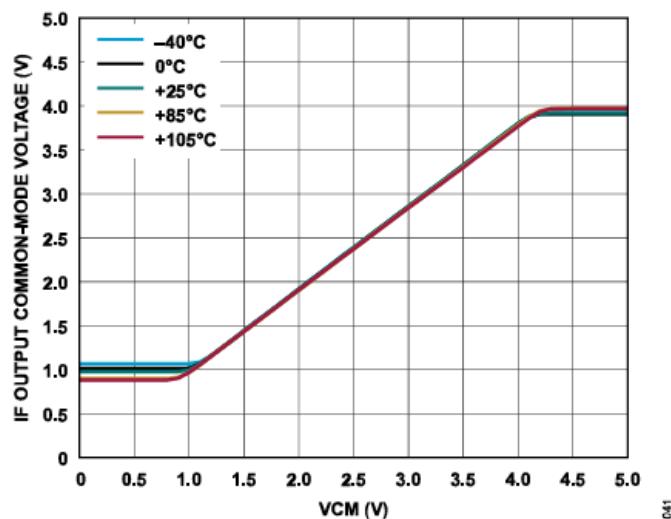

図 41. 様々な温度での IF 出力コモンモード電圧と VCM の関係

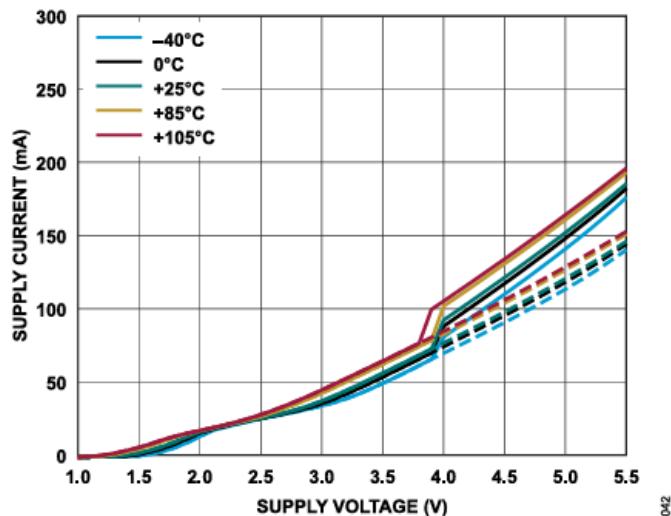

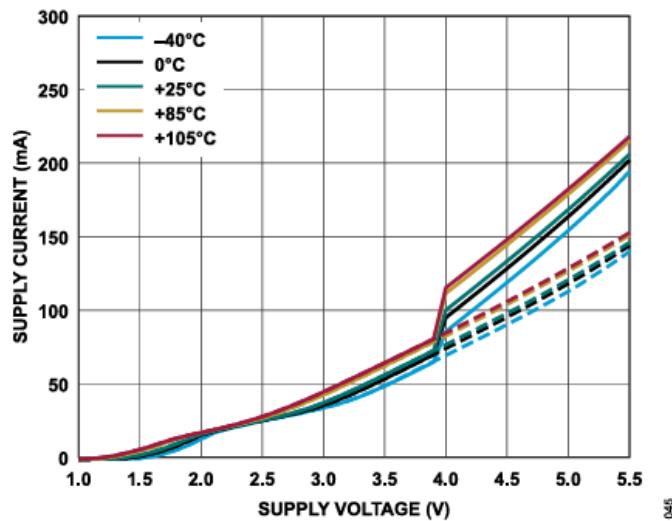

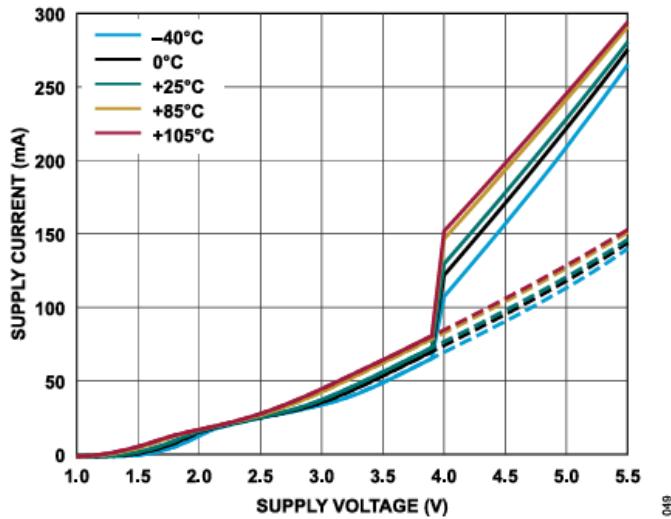

図 42. 様々な温度での電源電流と電源電圧の関係

(LOMODE = 0、実線 : OFMODE = 2、破線 : OFMODE = 3)

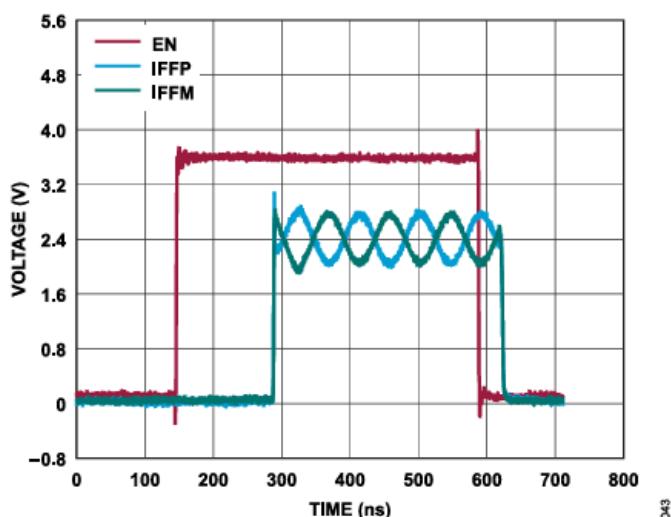

図 43. 連続波によるターン・オン/オフ時間 (RF = 1GHz、

10dBm、IF = 10MHz、IFFP および IFFM に 50Ω 負荷)

## 代表的な性能特性

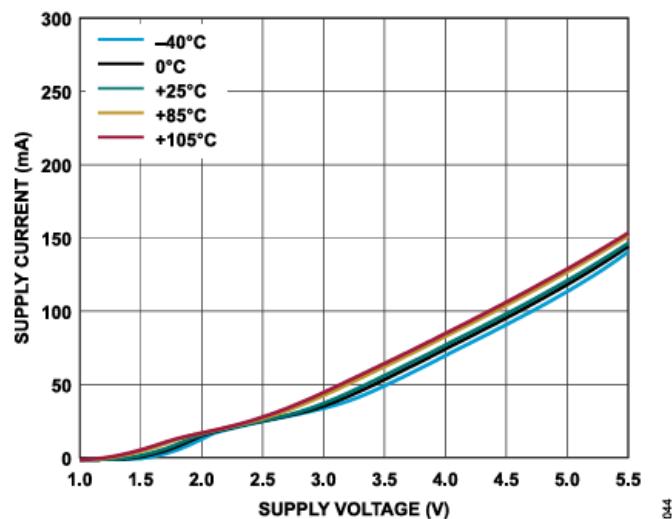

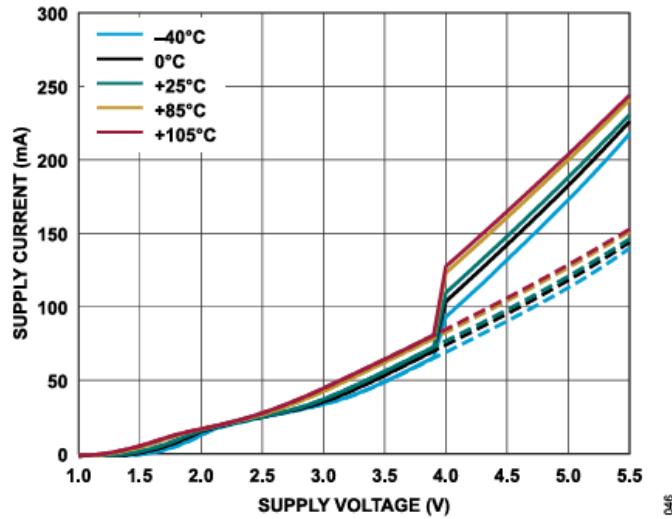

図 44. 様々な温度での電源電流と電源電圧の関係

(BYPASS = 1)

図 45. 様々な温度での電源電流と電源電圧の関係 (LOMODE = 1、実線 : OFMODE = 2、破線 : OFMODE = 3)

図 46. 様々な温度での電源電流と電源電圧の関係 (LOMODE = 2、実線 : OFMODE = 2、破線 : OFMODE = 3)

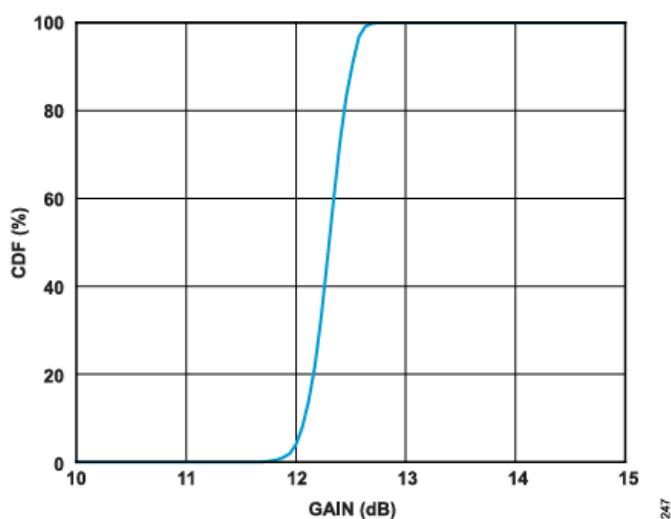

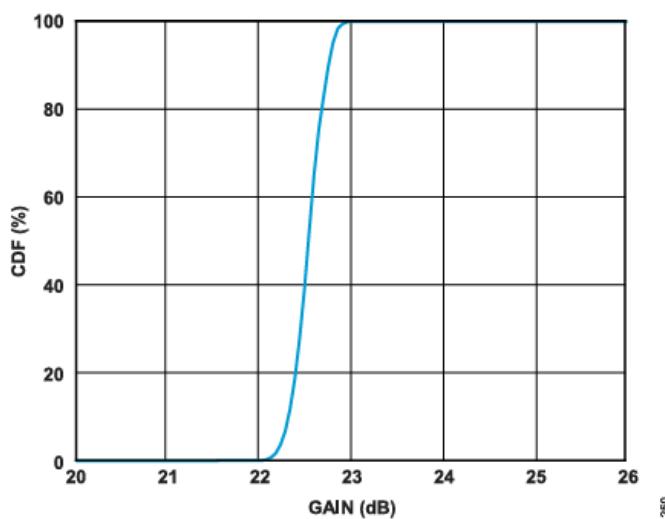

図 47. 変換ゲイン分布、RF = 100MHz、FGAIN = 24、サンプル・サイズ : デバイス 3500 個 (CDF=累積分布関数)

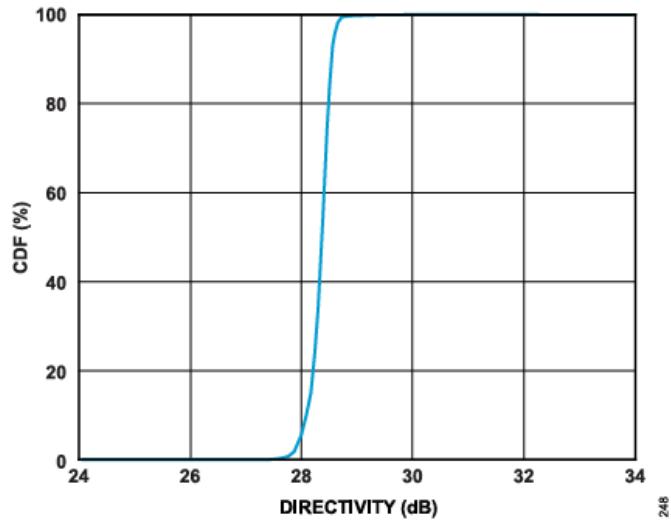

図 48. 指向性分布 (RF = 100MHz、サンプル・サイズ : デバイス 100 個)

図 49. 様々な温度での電源電流と電源電圧の関係 (LOMODE = 3、実線 : OFMODE = 2、破線 : OFMODE = 3)

## 代表的な性能特性

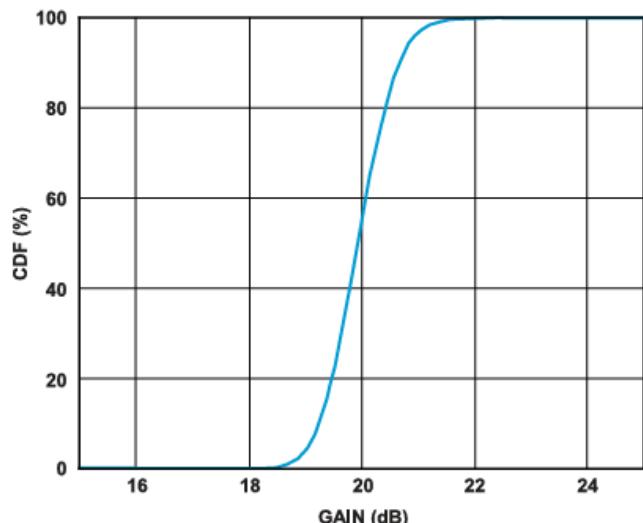

図 50. 変換ゲイン分布 (RF = 100MHz、FGAIN = 36、サンプル・サイズ : デバイス 3500 個)

図 51. 指向性分布 (RF = 10GHz、サンプル・サイズ : デバイス 100 個)

## 動作原理

ADL5961 は、広帯域マルチポート・ネットワーク・アナライザ・ソリューションを小さなフットプリントで実現できるように設計されています。

ADL5961 は集積化広帯域双方向抵抗性ブリッジを中心に構築され、広帯域デュアル・ダウンコンバージョン・ミキサーに結合されています。ミキサーの差動 IF 出力は、帯域幅を SPI でプログラム可能なローパス・フィルタと、ゲインを個別に SPI でプログラム可能な IF アンプを通過します。

ミキサーへの LO インターフェースは、SPI でプログラム可能な複数の構成をサポートし、VNA アプリケーションにおける周波数プランを簡略化するように設計されています。LO インターフェースには、LO 信号ソース自体がサポートするものより広い動作周波数範囲を可能にする周波数倍器と分周器が備わっています。OFP ピンと OFM ピンが形成するオフセット・インターフェースは LO インターフェースへの第 2 の入力であり、簡略化された周波数プランをもつゼロ・オフセット動作モードを可能にします。このモードでは、単一の掃引高周波信号ソースのみが必要で、ADL5961 の RF インターフェースと LO インターフェースの両方を駆動します。OF インターフェースに供給された信号は、ダウンコンバージョン・ミキサーを駆動する前に LOP および LOM インターフェースに供給された LO 信号とミックスされるため、IF 出力信号の周波数を制御します。

複数の ADL5961 デバイスを位相同期させて同時に動作させることができます。そのため、ネットワーク・アナライザ・ポートごとに 1 つの ADL5961 デバイスを用いて、フットプリントの小さいマルチポート・ネットワーク・アナライザを構築することができます。

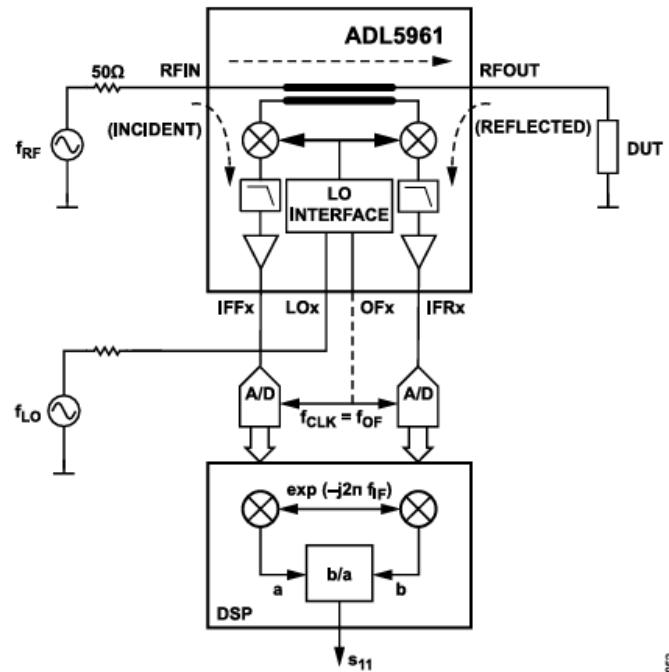

## 基本的な 1 ポート VNA

1 ポート VNA（すなわち、反射率計）を用いることで、負荷と周波数の関係が未知の場合に反射係数の大きさと位相を測定できます。

図 52 に、ADL5961 をベースとした 1 ポート VNA の基本構成を示します。ADL5961 の RFIN インターフェースは RF 信号ソース（通常は連続波）に接続し、一方、RFOUT インターフェースは未知の負荷であるテスト対象デバイス（DUT）に接続します。ADL5961 は完全に対称性であるため、RF ソースを RFOUT に接続し、負荷を RFIN に接続することもできます。RF ソースが ADL5961 の指向性ブリッジに入射 RF 信号を注入すると、この信号はソースから負荷へ伝送されます。負荷では、この入射電力波の一部は反射されて RF ソースに戻り、他の部分は負荷に吸収されます。測定される反射係数（大きさと位相の両方）は、負荷における入射電力に対する反射電力の比に等しくなります。双方向ブリッジを適切に動作させるには、RF 信号ソースが  $50\Omega$  の特性インピーダンスを持つことが重要です。LO インターフェースは、 $50\Omega$  のシングルエンド・ソースまたは  $100\Omega$  の差動ソースのいずれかによって駆動できます。

ADL5961 の指向性ブリッジは、入射信号の一部を順方向 IF チャンネルの入力に供給し、同様に、反射信号の一部を逆方向 IF チャンネルの入力に供給します。これら両方の IF 信号はダウンコンバージョン後、フィルタ処理および増幅を経て、差動 IF チャンネルの出力インターフェースである（IFFP および IFFM 端子を有する）IFFx と（IFRP および IFRM 端子を有する）IFRx にそれぞれ出力されます。

A/D 変換の後、入射波と反射波を表す IF 出力信号に対して、デジタル直交（複素）ダウンコンバージョン、フィルタ処理、デシメーションが行われます。最後に、反射波と入射波の比の計算により、（複素）反射係数が得られます。

図 52. 1 ポート VNA（反射率計）として使用される ADL5961

## 周波数プラン作成 - LO 構成

ADL5961 の LO インターフェースは、様々な構成をサポートしており、中には、精度をわずかに低下させる代わりに、VNA 構成を大幅に簡素化する構成もあります。

バイパス・モードは、レジスタ 0x20 のビット 4 をセットすることによって選択され、ADL5961 の最も基本的で最も高性能な動作モードです。このモードでは、LO インターフェース（LOP ピンと LOM ピン）に供給される LO 信号が、周波数倍器、分周器、オフセット・ミキサーをバイパスして、ダウンコンバージョン・ミキサーを直接駆動します。一定の IF 出力周波数を維持するには、LO 信号は必ず、周波数掃引全体で RF 信号に対して一定の周波数オフセットを維持する必要があります。

$$f_{LO} = f_{RF} \pm f_{IF} \quad (1)$$

十記号はハイサイド注入、一記号はローサイド注入に対応します。ハイサイド注入では、多くの場合、ダイナミック・レンジがわずかに広がりますが、これは、ミキシング成分のより多くが目的の IF 信号よりも高い周波数で計算され、ローパス・フィルタ処理によって抑制できるためです。ADL5961 は最大 100MHz の IF 周波数をサポートします。高ダイナミック・レンジの A/D 変換では、数 MHz の IF 周波数が望ましいことが多いのですが、2MHz ~3MHz の IF 周波数では信号ソースに問題が生じるため、26.5GHz までの信号周波数の RF と LO の間に、数 MHz の正確で小さな周波数オフセットが必要になります。

## 動作原理

ADL5961 の LO インターフェースに内蔵された分周器と倍器により、LO ソース自体（通常は周波数シンセサイザ）によってサポートされる周波数範囲を超える測定掃引が可能になります。レジスタ 0x20 のビット 4 がクリアされている（バイパス・モードが無効）場合は、次式に示すように、LO MODE ビット（レジスタ 0x20 のビット[1:0]）を用いて LO 通倍係数  $M_{LO}$  を設定できます。

$$M_{LO} = 2^{\text{LOMODE} - 1} \quad (2)$$

つまり、2 分周、あるいは 1 通倍、2 通倍または 4 通倍です。所望の出力信号が、所望の IF 出力周波数  $f_{IF}$  でダウンコンバージョンされるようにするには、LO インターフェースに供給される周波数は必ず、以下の条件を満たす必要があります。

$$f_{LO} = (f_{RF} \pm f_{IF}) / M_{LO} \quad (3)$$

表 1 からわかるとおり、2 分周モードは、2.4GHz までの LO 入力周波数に対してのみ使用でき、一方、2 通倍モードと 4 通倍モードは、それぞれ 2GHz~8GHz と 4GHz~8GHz でのみ動作します。LO インターフェースは、倍器出力の高調波と低調波を抑制する高周波フィルタも備えています。これらのフィルタの中心周波数は、レジスタ 0x21 とレジスタ 0x22 で設定できます。

## オフセット周波数インターフェース

差動オフセット周波数インターフェースを使用すれば、VNA 構成を更に簡略化できます。この構成では、一つの掃引ソースで RF インターフェースと LO インターフェース同じ周波数（ゼロ周波数オフセット）で駆動できます。一方、IF 出力周波数は、オフセット周波数インターフェースに印加される信号によって設定されます。オフセット・ミキサーをイネーブルにするには、レジスタ 0x20 のビット 4 をクリアし、ビット[3:2]の OFMODE ビットを設定します。オフセット周波数インターフェースがイネーブルされている場合は、比を 1、2、4 にプログラム可能な分周器を使用できます。表 7 に通倍係数  $M_{OF}$  を示します。

表 7. オフセット入力の設定

| Register 0x20, Bits[3:2], OFMODE | Divide by    | $M_{OF}$       |

|----------------------------------|--------------|----------------|

| 00                               | 1            | 1              |

| 01                               | 2            | 0.5            |

| 10 (Default)                     | 4            | 0.25           |

| 11                               | Dividers off | Not applicable |

オフセット・ミキサーを含む IF 出力信号の周波数は、次のように表されます。

$$f_{IF} = f_{RF} - M_{LO} \times f_{LO} + M_{OF} \times f_{OF} \quad (4)$$

したがって、真のゼロ・オフセット掃引のためには、LO 周波数は以下の条件を満たす必要があります。

$$f_{LO} = f_{RF} / M_{LO} \quad (5)$$

式 4 の最初の 2 つの項が相殺され、IF 出力周波数は以下のようになります。

$$f_{IF} = M_{OF} \times f_{OF} \quad (6)$$

$M_{OF} = 1/4$  (OFMODE = 2) の設定は特に有用で、OFMODE の設定値として推奨します。オフセット周波数インターフェースが ADC のサンプル・クロック周波数  $f_s$  によって駆動されると、IF 出力信号が ADC の第 1 ナイキスト・ゾーンに正確にセンタリングされ、IF 波形の 1 サイクル当たり  $4 \times$  の領域サンプル・ポイントでサンプリングされます。このモードでは、オフセット入力をデジタルで 4 分周するため、IF 波形の離散時間特性が明確になります。

## IF 信号パス

ミキサーの IF 出力信号は、ローパス・フィルタを通過して、不要なミキシング成分とノイズを除去します。これらのフィルタの帯域幅は、レジスタ 0x25 を介して SPI でプログラム可能です。同じ帯域幅設定値が、ADL5961 の両方の IF チャンネルに適用されます。

ローパス・フィルタに続く IF アンプでは、SPI を介してゲインを個別にプログラム可能で、6dB ステップで調整できます。このプログラム可能なゲインにより、ADC 入力ダイナミック・レンジへの、両方のチャンネルの最適なインターフェース接続が可能になります。

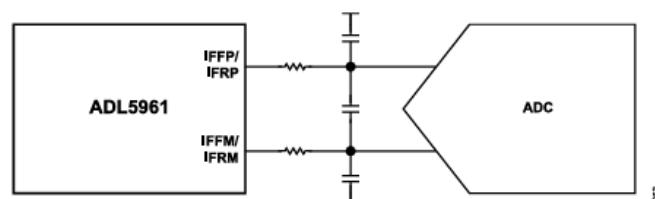

ADL5961 の IF 出力インターフェースは、広範囲の ADC の直接駆動に適しています。広帯域ノイズのエイリアシングを避けるため、図 53 に示すように、簡単なアンチエイリアシング・フィルタを挿入することを推奨します。

図 53. ADL5961 の ADC へのインターフェース接続

差動 IF 出力ノードは、いずれも低ソース・インピーダンスです。このため、フィルタや高容量の負荷またはケーブルの駆動などに必要な場合は、テスト回路に示すように、直列抵抗を使用することを推奨します（図 72 を参照）。

## 動作原理

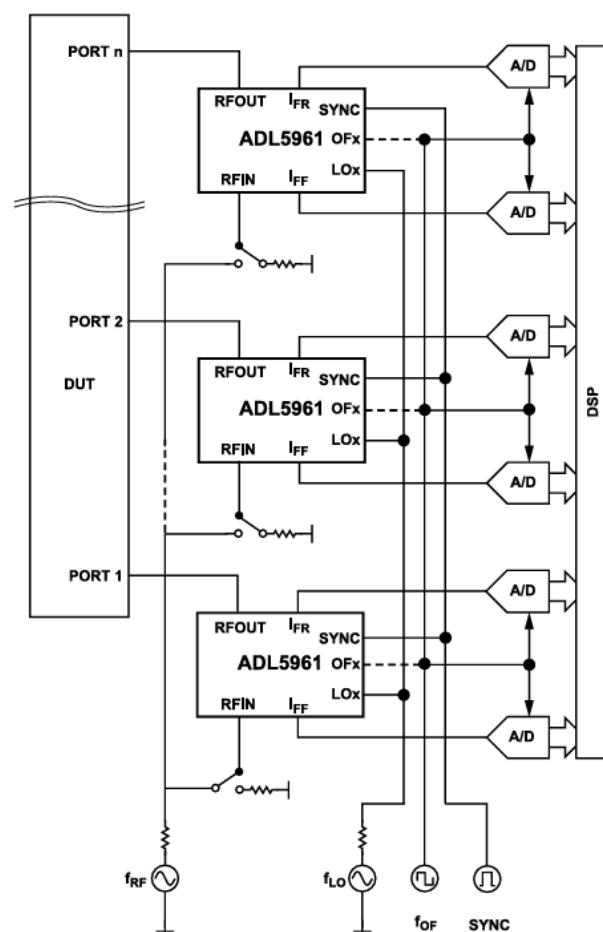

## マルチポート VNA

ADL5961 を使用して、図 54 に示すように、複数のポートからなる VNA を作成することもできます。各ポートは 1 つの ADL5961 デバイスに接続され、RF スイッチは一度に 1 つの ADL5961 に RF 信号をルーティングします。位相（および大きさ）の精度を最適化するには、RF ソースからすべてのポートへの接続の長さが等しくなるようにします。更に、ADL5961 デバイスの RFIN ポートは、RF ソースが接続されているときだけでなく、接続されていないときにも、常に  $50\Omega$  で終端します。これを実現するには、RF ソースを極に接続した SPxT 無反射型スイッチを使用します。多くのポートを有する VNA の場合、無反射型（終端接続）RF スイッチのカスケードを使用できますが、挿入損失が大きくなり、周波数傾斜が増大する可能性があります。図 54 に示す RF ソースへの接続は簡略図であり、システムの最適なレイアウトのための推奨事項には従っていない点に注意してください。

ADL5961 デバイス間の位相同期は、LO 信号とオフセット周波数信号を介して実現されます。最適な精度を得るために、LO ソースから各 ADL5961 デバイスへの伝搬遅延を一致させます。残留遅延差は、VNA システムのキャリブレーション手順によって対処可能です。オフセット・インターフェースへの信号ラインははるかに低い周波数で動作するため、これらの信号ラインのルーティングはそれほど重要ではありません。

すべての ADL5961 デバイスの LO およびオフセット分周器を同じ既知の初期状態にして、デバイス間に位相のあいまいさが存在しないようにするために、SYNC インターフェースが使用されます。電源投入後にこの入力にパルスを 1 つ印加するだけで、すべてのデバイスを同期させることができます。この同期は、LO 信号が印加される前に行います。この場合、SYNC パルスのタイミングは重要ではありません。

最適な精度を得るために、すべての ADL5961 の IF チャンネルを同時にサンプリングすることを推奨します。ポート数が多い場合は、マルチチャンネル同時サンプリング ADC を使用すると、ソリューションのフットプリントを大幅に縮小できます。このようなマルチチャンネル・デバイスの中には、デジタル・ダウンコンバージョン (DDC) とデシメーション・フィルタを内蔵し、これによってデジタル信号プロセッサ (DSP) で必要な処理量を削減するものもあります。

プログラマブル RF フィルタを RF パスに挿入して RF ソースのあらゆる高調波成分をフィルタ処理し、プログラマブル減衰器を挿入してフィルタ、スイッチ、伝送ラインによって生じる周波数に対する傾斜を補償することによって、システム性能を更に向上させることができます。

図 54. ADL5961 をベースにしたマルチポート VNA ( $I_{IFR}$  は逆方向 IF、 $I_{FF}$  は順方向 IF)

## 動作原理

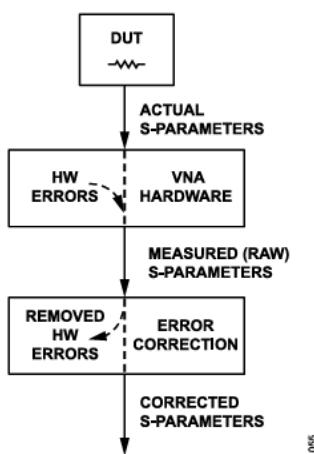

## キャリブレーションと誤差補正

S パラメータ測定の精度は、VNA のハードウェアによって生じる様々な誤差の影響を受けやすくなっています。再現性があり予測可能な系統誤差は、キャリブレーションと誤差補正の手法を用いて測定結果から除去できます。（ある程度まで）除去できる系統誤差の種類には、以下のものがあります。

- ▶ インピーダンスのミスマッチ

- ▶ チャンネル間のゲインと挿入損失の差

- ▶ チャンネル間のクロストーク

様々な誤差補正とキャリブレーションの手法が、長年開発されてきましたが（例えば、D. K. Rytting, "Network Analyzer Accuracy Overview," 58th ARFTG Conference Digest, 2001, pp. 1-13, doi: 10.1109/ARFTG.2001.327486）、特定の誤差を除去する有効性、複雑さ、使用するキャリブレーション標準は、手法により異なります。ただし、適用される一般原則はすべて同じです。系統誤差は、正確に既知の S パラメータ（キャリブレーション標準）を用いて、1 セットの DUT に対する VNA 応答を測定することによって求められます。測定された S パラメータを既知の S パラメータと比較すると、誤差係数の計算が可能になります。これらの誤差係数は、しばしば誤差アダプタと呼ばれるものに統合され、その後、後処理ステップで使用して、未知の DUT の S パラメータの測定値から誤差補正された S パラメータを計算できます。図 55 に概念図を示します。

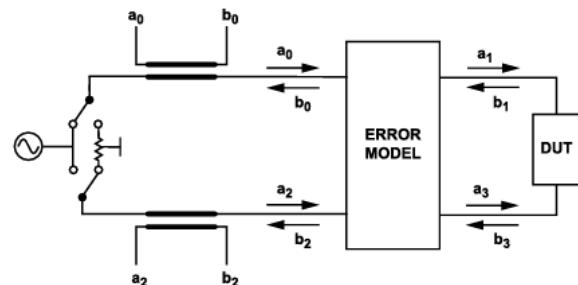

図 55. VNA における誤差補正の概念

異なる誤差補正手法には、異なるキャリブレーション標準セットを使用することが必要です。最もよく知られているものには、「ショート、オーブン、ロード、スルー」（SOLT）、「スルー、リフレクト、ライン」（TRL）、「スルー、リフレクト、マッチ」（TRM）があります。1 セット内の標準を選択する際は、スミス・チャート上の広い領域にまたがるように、S パラメータが大きく異なるものになります。一般に、キャリブレーション標準自体、特に、ショート標準やオーブン標準のような極端な S パラメータ値を持つものは、全てにおいて理想的というわけではなく、通常は、メーカーから提供される周波数に対する S パラメータのモデルが含まれています。一般に、キャリブレーション標準は、以下の 2 つのカテゴリーに細分化できます。

- ▶ 各 VNA ポートで測定された 1 ポート・キャリブレーション標準

- ▶ VNA ポートの組み合わせごとに測定された 2 ポート・キャリブレーション標準

ADL5961 デバイスをベースに構築された VNA のキャリブレーション手順は、その他の VNA システムのキャリブレーション手順と同様です。最大限の精度を得るためにには、使用する周波数に留意することが重要です。更に、キャリブレーション時に使用される ADL5961 のゲイン、帯域幅、周波数倍増器/分周器の SPI 設定値は、実際の DUT 測定時に使用される設定値と正確に一致する必要があります。ゲインなどの設定値はデバイス間およびチャンネル間の開き（ミスマッチ）の影響を受けるため、実際の測定時に設定値が異なることが予想される場合は、複数の異なる構成に対して VNA をキャリブレーションします。

S パラメータは電力比計算の結果であり、原理的には絶対電力レベルの影響を受けませんが、多くの場合、測定時に RF ソースの電力対周波数を正確に制御することが重要です。DUT が、半導体デバイスのように、印加された RF 電力レベル全体で非線形性を示す場合は、電力レベルが変化すると DUT の挙動が変化し、測定精度に影響を及ぼすことがあります。ADL5961 の順方向 IF チャンネルは、特に、ロード標準を用いたシステムのキャリブレーション時のようにポートが  $50\Omega$  で終端されている場合に、RF 信号バスにおける電力レベルをモニタするために使用することができます。ADL5961 自体の変換ゲインも同様に周波数に対するロール・オフを示すため、正確な電力測定を実施するには、これを考慮に入れる必要があります。

## 動作原理

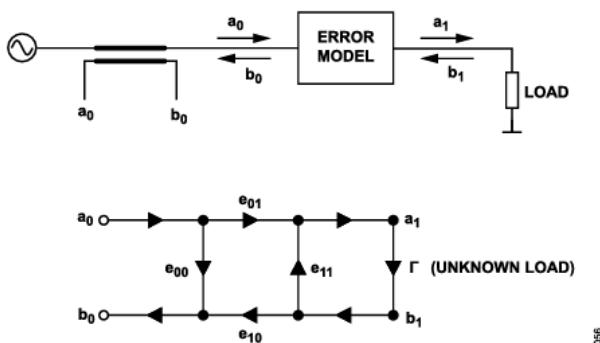

## 1 ポート・キャリブレーション

1 ポート S パラメータ測定のキャリブレーション手順は、図 56 のフロー図を用いて説明できます (D. K. Ryttig, "Network Analyzer Accuracy Overview," 58th ARFTG Conference Digest, 2001, pp. 1-13, doi: 10.1109/ARFTG.2001.327486 も参照)。指向性結合器と誤差モデルは合わせて、実用的な VNA の動作を記述します。入射波  $a_0$  と反射波  $b_0$  は、VNA が測定した順方向および逆方向の電力を表しています。ADL5961 を使用する場合、これらのベクトルは、IF 出力の IFFx と IFRx から得られます。負荷に入射する実際の電力は  $a_1$  で表され、負荷によって反射される実際の電力は  $b_1$  で表されます。誤差のない VNA で、 $a_1$  と  $b_1$  が測定されます。

図 56. 1 ポート S パラメータ測定の誤差モデル

このフロー図では、測定された反射係数  $\Gamma_M = b_0/a_0$  が実際の反射係数  $\Gamma = b_1/a_1$  と異なる原因となる様々な誤差要因について、より詳細に説明しています。係数  $e_{11}$  は、VNA ポートのインピーダンスの (50Ωとの) ミスマッチを表します。 $b_1$  の一部は負荷に反射されます。 $e_{01}$  および  $e_{10}$  係数はトラッキング誤差を表します。ADL5961 に関しては、トラッキング誤差は、ブリッジの挿入損失、RFIN から IFFx への変換ゲイン、RFOUT から IFRx への変換ゲイン、ならびにチャンネル間の変換ゲインのミスマッチで構成されています。最後に、 $e_{00}$  は、実際の VNA の有限の指向性を表し、これは、順方向および逆方向に進行する電力波を分離する能力の尺度です。負荷が正確に 50Ω の場合、 $b_1 = 0$  であり、理想的な VNA の測定では  $b_0 = 0$  となります。しかし、実際の VNA では、指向性は有限であり、いくらかの信号が順方向パスから逆方向パスに漏れます。

図 56 を用いると、測定された反射係数は、次のように誤差係数と負荷の反射係数で表すことができます。

$$\Gamma_M = e_{00} + \frac{e_{01}e_{10}}{1 - e_{11}}\Gamma \quad (7)$$

式 7 は並べ替えて、以下のように誤差係数を線形表現に変更できます。

$$\begin{aligned} e_{00} - \Delta_e\Gamma + e_{11}\Gamma_M &= \Gamma_M \\ \Delta_e &= e_{00}e_{11} - e_{01}e_{10} \end{aligned} \quad (8)$$

3 つの異なる既知の負荷を測定するキャリブレーション手順、すなわち、測定された反射係数と実際の反射係数の 3 つの組み合わせを集めることで、キャリブレーション手順を用いて、次のように誤差係数を計算できます。

$$\begin{pmatrix} 1 - \Gamma_1 \Gamma_{M1} \\ 1 - \Gamma_2 \Gamma_{M2} \\ 1 - \Gamma_3 \Gamma_{M3} \\ T \end{pmatrix} \begin{pmatrix} e_{00} \\ \Delta_e \\ e_{11} \\ \vec{e} \end{pmatrix} = \begin{pmatrix} \Gamma_{M1} \\ \Gamma_{M2} \\ \Gamma_{M3} \\ \vec{\Gamma}_M \end{pmatrix} \Rightarrow \vec{e} = T^{-1}\vec{\Gamma}_M \quad (9)$$

システムがキャリブレーションされた後、補正された反射係数は、式 7 を並べ替えて、測定された係数から計算できます。

$$\Gamma = \frac{\Gamma_M - e_{00}}{e_{11}\Gamma_M - \Delta_e} \quad (10)$$

原理的には、十分に異なる標準の任意の組み合わせを用いて、システムのキャリブレーションが可能ですが、ショート、オープン、50Ω 負荷の組み合わせが、最も一般的な選択肢です。式 9 で説明した手順は、対象とするすべての周波数点で繰り返す必要があります。

## 2 ポート・キャリブレーション

2 ポート S パラメータ測定のキャリブレーション手順は、図 57 を用いて説明できます。VNA は、ポート 0、ポート 2、誤差モデルによってモデル化されます。システムのハードウェア誤差の結果、ポート 0 で測定された S パラメータは、ポート 1 での実際の DUT の S パラメータとは異なり、ポート 2 で測定された S パラメータは、ポート 3 での DUT の S パラメータとは異なります。誤差の寄与が電力に対して線形に変化する限り、ポート 0 とポート 2 における入射波と反射波は、以下に示すブロック行列を用いて、ポート 1 とポート 3 における入射波と反射波に関連付けることができます。

$$\begin{pmatrix} b_0 \\ a_0 \\ b_2 \\ a_2 \end{pmatrix} = \begin{pmatrix} T_{01} & T_{03} \\ T_{21} & T_{23} \end{pmatrix} \begin{pmatrix} b_1 \\ a_1 \\ b_3 \\ a_3 \end{pmatrix} \quad (11)$$

図 57. 2 ポート S パラメータ測定の誤差モデル

式 11 の各行列要素  $T$  は、1 つの VNA ポートと 1 つの DUT ポートの間の相互作用を記述する  $2 \times 2$  行列であり、この行列から、

## 動作原理

合計 16 の未知の誤差係数が得られます。誤差係数（行列要素）のサブセットまたはすべてを求めるために、さまざまなキャリブレーション方法が文献で報告されています。

誤差モデルを単純化する 1 つの方法は、VNA チャンネル間のクロストークが無視できるほど小さい、すなわち、ポート 2 での測定誤差に対するポート 1 の寄与、およびポート 0 での測定誤差に対するポート 3 の寄与が小さいと、仮定することです。ADL5961 をベースとした VNA では、各 VNA ポートが別個のデバイスで実現されるので、この仮定は妥当です。VNA チャンネル間の相互作用は、綿密な PCB レイアウトによって最小限に抑えることができます。この状況では、式 11 の対角線上のブロック行列のみが非ゼロ要素を持つため、次のようにになります。

$$\begin{pmatrix} b_2 \\ a_2 \end{pmatrix} = T_{23}T_{31}T_{01}^{-1} \begin{pmatrix} b_0 \\ a_0 \end{pmatrix} = T_M \begin{pmatrix} b_0 \\ a_0 \end{pmatrix} \quad (12)$$

ここで、

$T_{31}$  は DUT 自体の伝送行列（測定すべき量）を表します。

$T_M$  は VNA によって測定された伝送行列です。

誤差補正された伝送行列は、次のように表すことができます。

$$T_{\text{CORRECTED}} = T_{23}^{-1} T_M T_{01} \quad (13)$$

伝送行列  $T_{01}$  および  $T_{23}$  を求めるためには、様々なキャリブレーション手法が利用できます。最も簡単で効果的な方法の 1 つは、SOLT キャリブレーションです。この方法では、1 ポート・キャリブレーションを各ポートに適用してから、スルー接続（ポート 1 とポート 3 の間のショート）を測定します。

## マルチポート・キャリブレーション

3 つ以上のポートで構成される VNA のキャリブレーションは、2 ポート・キャリブレーションのセクションで説明した 2 ポート・キャリブレーションと同様の手順で実行できます。決定される誤差係数の数は、 $4n^2$  ( $n$  はポートの数) として二次的に増加します。ただし、VNA ポート間の相互作用を無視する場合は、考慮する必要があるのは誤差モデルのブロック対角線上の係数のみなので、残りの係数の数は  $4n$  となります。

マルチポート・キャリブレーションで生じる実用上の問題は、キャリブレーション標準が通常、1 ポート（負荷）または 2 ポートであるのに対して、キャリブレーション手順では、原理的に、測定された  $n \times n$  S 行列と、実際の標準 S パラメータのための  $n \times n$  S 行列が必要になります。この問題は、一連の 2 ポート測定から  $n$  ポート S 行列を構築することによって対処できます。式 14 は 4 ポート・システムの概念を表します。

$$S = \begin{pmatrix} m_{12} & m_{12} & m_{13} & m_{14} \\ m_{12} & m_{12} & m_{23} & m_{24} \\ m_{13} & m_{23} & m_{13} & m_{34} \\ m_{14} & m_{24} & m_{34} & m_{14} \end{pmatrix} \quad (14)$$

ここで、 $m_{xy}$  は、どの 2 ポート測定から対応する S パラメータを求めるかを示します。

例えば、 $m_{12}$  で示されるポート 1 およびポート 2 を使用する 2 ポート測定を用いて、 $s_{11}$ 、 $s_{12}$ 、 $s_{21}$ 、 $s_{22}$  を求めることができます。S 行列全体を埋めるには、2 つのポートの様々な組み合わせで測定する必要があります。一部のパラメータは、( $s_{11}$  のように) 複数回求められ、1 回の測定を除くすべての測定で無視できます。一般に、 $n^2$  個の S パラメータのフルセットは、 $n(n - 1)/2$  回の 2 ポート測定セッションで求めることができます。

例えば、SOLT キャリブレーション方式を  $n$  ポート VNA に適用する場合、各ポートで 3 つの負荷を測定してから、2 つのポートのすべての組み合わせ間でスルー標準測定を行う必要があります。これに必要な測定実行の合計回数は次のとおりです。

$$3n + n(n - 1)/2 = n(n + 5)/2 \quad (15)$$

## IF スプリアス・トーンの除去

IF 出力信号スペクトルには、一般に、目的の出力信号の他に様々なスプリアス・トーンやミキシング成分が存在します。これらの不要なトーンの一部は、目的の IF 信号と同じ周波数で現れるため、測定精度が低下します。このセクションで説明する手法を用いると、こうした不要なトーンの影響を低減し、測定精度を向上させることができます。

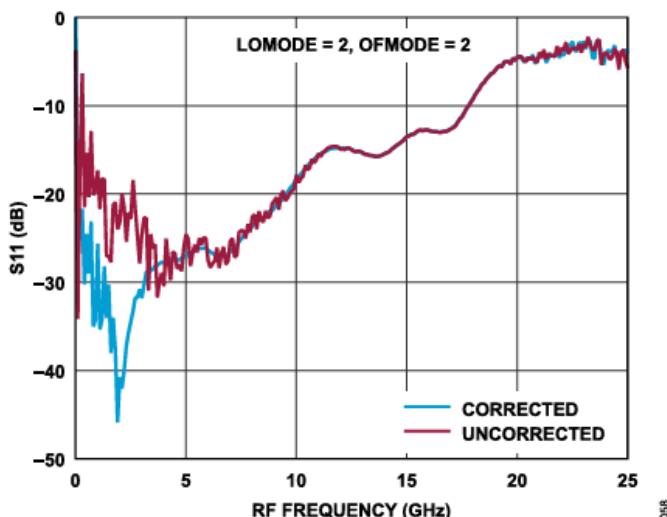

OF インターフェースを用いる LO インターフェース構成は、IF スプリアス・トーンの影響を最も受けやすくなっています。高調波、低調波、LO と OF の間のミキシング成分、部分的に抑制されたイメージ周波数は、IF 出力スペクトルにおけるスプリアス・トーンに寄与します。スプリアス・トーンの影響が最も顕著に現れるのは、RFOUT ポートの DUT がよくマッチングし、逆方向 IF 出力チャンネルの目的の信号が小さい場合です。図 58 は、IF 周波数におけるスプリアス・トーンの影響を示すもので、IF スプリアス・トーンについて、補正された反射損失測定結果と補正していない生の測定結果を比較しています。図 58 から明らかなように、スプリアス・トーンによって周波数に対するリップルが測定結果に現れ、特に 5GHz より低い周波数で測定感度を低下させます。

## 動作原理

図 58. IF スプリアス・トーンの補正がある場合とない場合の

50Ω 負荷の反射損失測定

次の簡単な手順により、スプリアス・トーンによるリップルを大幅に低減できます。

1. RF が存在する状態で IF 出力信号を測定する。

2. IF 出力周波数における複素高速フーリエ変換 (FFT) 周波数成分を計算する。

3. RF 信号をオフにするか、非常に低いレベルに設定して、IF 出力信号を測定する。

4. この場合の IF 周波数における周波数成分を計算する。

5. ステップ 2 の結果からステップ 4 の結果を差し引く。

6. 誤差補正とさらなる処理を、ステップ 5 の結果に適用する。

上述のステップの順序は変更可能で、RF 信号なしの周波数掃引は、将来の測定値の補正のためにメモリに保存できます。

## アプリケーション情報

## インターフェースの説明

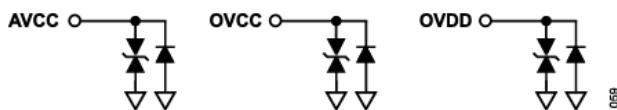

## 電源インターフェース

AVCC、OVCC および OVDD ピンには独立した電源クランプがあり、クランプを作動させないために、必ず  $100\mu\text{s}$  より低速でランプさせる必要があります。残留する高周波リップルを抑制するために、 $1\text{nF}$  コンデンサと  $4.7\mu\text{F}$  コンデンサを用いて電源インターフェースをデカップリングすることを推奨します。OVDD は SPI コントローラの電源に接続することができ、それにより SPI パス・ライン上にロジック・レベル変換器を配置する必要がなくなります。

図 59. 電源インターフェースの回路の簡略図

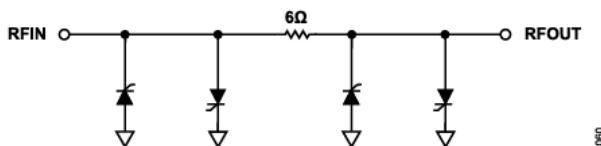

## RFIN と RFOUT のインターフェース

RFIN と RFOUT はどちらも、 $50\Omega$  の特性インピーダンスを持つシングルエンド RF 入力です。両方のインターフェースが内部で結合されているため、RFIN（または RFOUT）での入力インピーダンスは、もう一方のインターフェースである RFOUT（または RFIN）が  $50\Omega$  で終端されている場合に限り、 $50\Omega$  となります。

両方のピンは、双方向ブリッジの  $6\Omega$  の直列抵抗を介して内部で DC 結合されています。入力 RF ミキサのデバイアスを防ぐため、これらのピンには DC 阻止コンデンサを使用する必要があります。このブリッジは、整合条件で最大  $30\text{dBm}$  の平均信号レベルと、最大  $35\text{dBm}$  のピーク・レベルをサポートするように設計されています。整合終端の場合よりも大きな電圧振幅が生じることがあるオープン・サーキットなどの極端な不整合条件下では、インターフェースの信号電圧を  $-5\text{V} \sim +10\text{V}$  の範囲内に維持する必要があります。

図 60. RFIN と RFOUT のインターフェースの簡略図

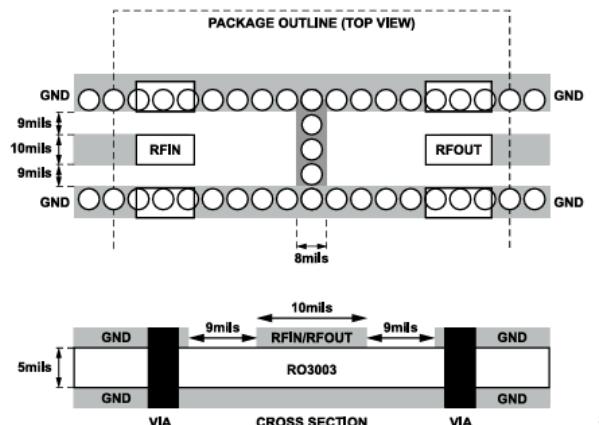

最良のブリッジ指向性を得るためにには、RFIN と RFOUT の両方を、綿密に整合させた  $50\Omega$  の広帯域伝送ラインに接続する必要があります。図 61 に示す接地コプレーナ導波路 (GCPW) は、この目的に適っています。RFIN インターフェースの RF リターン・パスとしてピン 2 とピン 4 (AGND) を使用し、RFOUT インターフェースのリターン・パスとしてピン 18 とピン 20 を使用します。また、ブリッジ外で生じる相互作用も、測定される指向性に影響を与えるため、その影響を最小限に抑えるために、RFIN と RFOUT 間にグラウンド・シールドが必要です。上部グラウンド層と下部グラウンド層は、RFIN と RFOUT 間のシールド内と、GCPW のグラウンド・リターン導体の端の周囲に、できるだけ多くのビアを用いて接続する必要があります。

図 61. RFIN と RFOUT をインターフェース接続するための GCPW 設計例

## IIEP、IFFM、IFRP および IFRM インターフェース

差動 IF 出力アンプは、 $100\Omega$  の差動負荷を 8V p-p まで駆動できます。グラウンドまたは AVCC に出力短絡が発生した場合、内部クランプにより、各シングルエンド出力 (IFFM、IFFP、IFRP、IFFR) の電流が約 200mA 未満に制限されます。

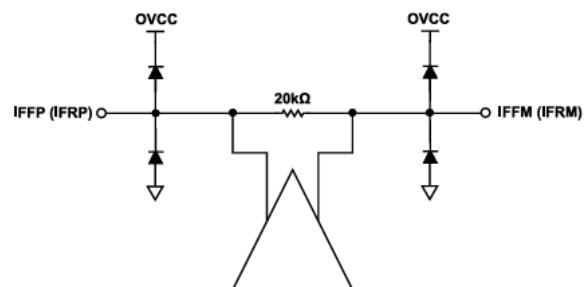

図 62. IF 出力インターフェースの簡略図

## VCM インターフェース

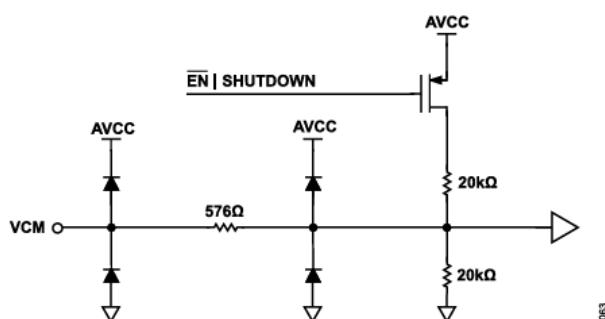

VCM インターフェースは、IFFx および IFRx 出力インターフェースでコモンモード電圧レベルを制御し、様々な ADC への DC 結合インターフェース接続を簡略化します。選択した ADC が VCM を提供する場合は、VCM ピンをコモンモード出力またはリファレンス出力ピンに接続して、コモンモード・レベルを整合させ、利用可能なダイナミック・レンジを最大にすることができます。

VCM ピンがフローティング状態の場合は、内部の分圧器によってコモンモード電圧レベルが OVCC/2 に設定されます。外部駆動の場合、低インピーダンス電圧源を用いて、VCM の電圧を設定する必要があります。コモンモード出力電圧に対する VCM 電圧のトラッキング範囲は、1V～4V の範囲で線形です。この範囲外の電圧レベルでは、出力コモンモード・レベルは、それぞれ 1V または 4V に固定されます。

## アプリケーション情報

図 63. コモンモード制御インターフェースの簡略図

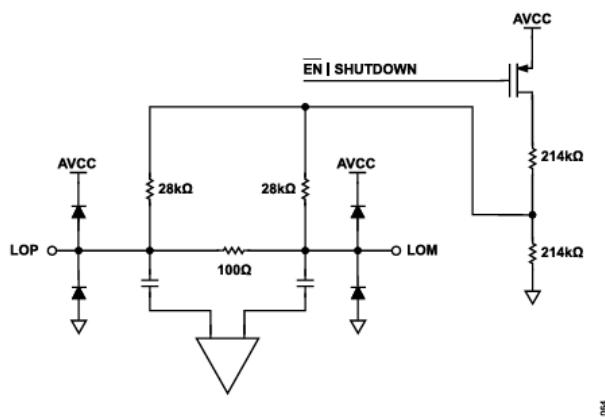

## LOP と LOM のインターフェース

LO インターフェースは、差動駆動またはシングルエンド駆動であります。PCB レイアウトを（例えば、グラウンド、信号、接地コアプレーナ導波路 (CPW) を用いて）適切に設計した差動駆動の LO インターフェースは、LO 信号の放射エミッションやシステム内の他のネットへの不要な結合を低減するのに役立ちます。LOP およびLOM 入力は、AVCC/2 に内部バイアスされています。シングルエンド駆動の場合、内部の 100Ω 終端は、2:1 外部バランを用いてインピーダンス整合できます。

図 64. LO インターフェースの簡略図

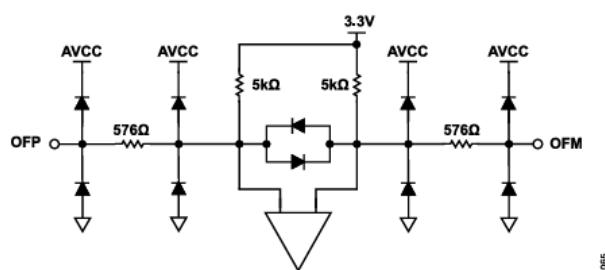

## OFP と OFM のインターフェース

オフセット周波数インターフェース (OFP と OFM) は、3.3V のコモンモード・レベルで内部バイアスされており、外部信号ソースに AC 結合する必要があります。これらの入力は差動またはシングルエンドで駆動でき、シングルエンド駆動のときは片方の端子を高容量コンデンサを使って AC 接地します。入力周波数が 400kHz の場合は、10nF 以上の値を推奨します。

図 65. オフセット周波数インターフェースの簡略図

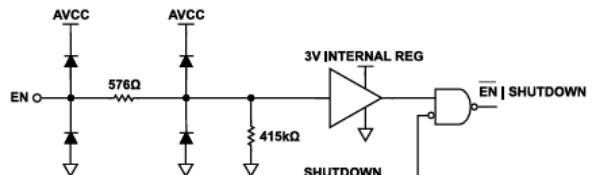

## EN インターフェース

DEVICE\_CONFIG の SHUTDOWN ビット（レジスタ 0x02 のビット 1）がセットされているか、EN ピンがアサート解除されている場合、このチップはシャットダウン状態にあります。内部の 415kΩ プルダウン抵抗により、EN ピンがフローティング状態の場合にデバイスが確実にオフになる（シャットダウンされる）ようにできます。

図 66. イネーブル・インターフェースの簡略図

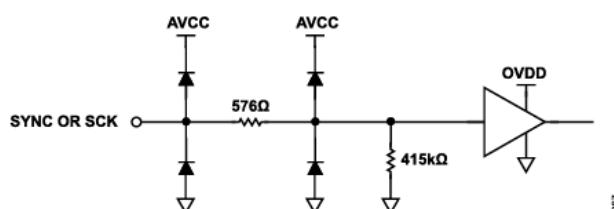

## SYNC および SCK インターフェース

SYNC インターフェースと SCK インターフェースはいずれも、高インピーダンス CMOS ロジック入力インターフェースです。表 1 に記載のとおり、ロジック・ハイ・レベルとロジック・ロー・レベルは、シリアル・ポート電源インターフェース OVDD に対して定義されています。どちらの入力も、フローティング状態のときは内部でローにプルダウンされます。

図 67. SYNC および SPI クロック・インターフェース

SYNC インターフェースは、システム内のすべての ADL5961 デバイスの同期に使用されます。このインターフェースの立下がりエッジは、LO および OF インターフェースの分周器を事前に定義された既知の状態にリセットします。すべての ADL5961 デバイスは、LO または OF インターフェースの次のエッジが来る前に、SYNC の負のエッジを受信します。SYNC パルスは、電源投入直後、LO と OF のクロックが印加される前に印加することもできます。

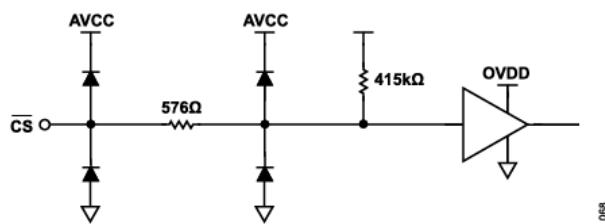

## CS インターフェース

CS インターフェースは、ADL5961 のシリアル・インターフェースを介して通信の開始と終了を制御します。SPI は、表 1 に定義されているように、CS の電圧がロジック・ローのときにアクティブで、ロジック・ハイのときにディスエーブルされます。このピンがフローティング状態のときは、この入力は内部でハイにプルアップされ、SPI をディスエーブルします。

## アプリケーション情報

図 68. SPI チップ・セレクト・インターフェース

## SDIO インターフェース

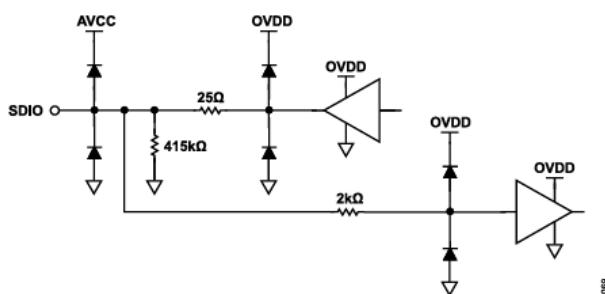

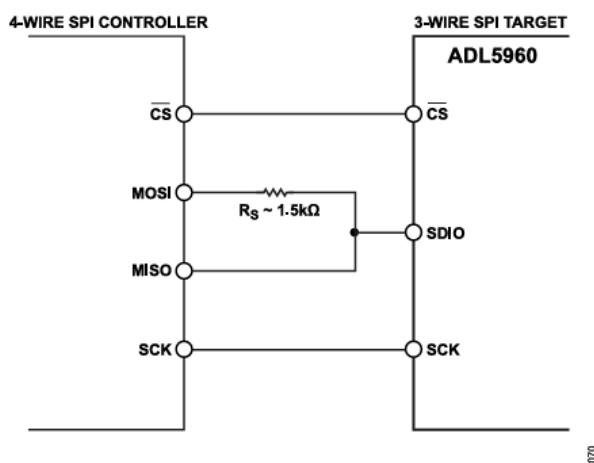

ADL5961 は、1 つのラインでデータの送受信を行う 3 線式の SPI を実装しています。データの受信時、すなわち、ADL5961 への書き込み動作時は、送信元のデバイスがデータ・ラインを必要に応じてローにプルダウンまたはハイにプルアップできるように、SDIO ピンに接続された出力ドライバが高インピーダンスになります。データ入力ラインとデータ出力ラインが分離した 4 線式インターフェースを用いて、このインターフェースを SPI コントローラに接続するには、図 70 に示すような直列の電流制限抵抗を使用して、コントローラ出力とターゲット出力を分離することを推奨します。この抵抗は、両方の出力が同時にアクティブになった場合の保護になります。

図 69. SDIO インターフェースの簡略図

図 70. SPI の 4 線式から 3 線式へのインターフェース接続

## TEMP インターフェース

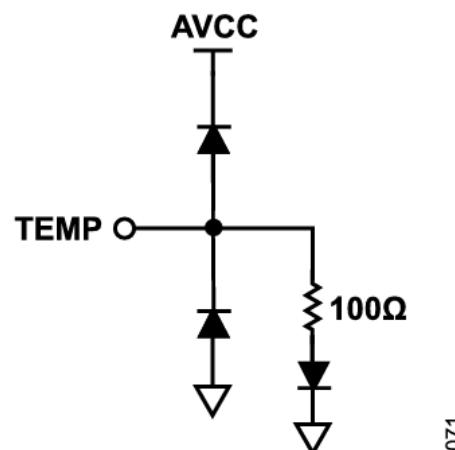

内蔵のデジタル温度センサーだけでなく、TEMP ピンによってもダイ温度をモニタすることができます。その場合、TEMP ピンに既知の基準電流を流し、グラウンドに対する電圧を測定します。

注入電流が  $42\mu\text{A}$  の場合は、 $25^\circ\text{C}$  で公称電圧が  $0.775\text{V}$  になり、温度勾配は約  $-1.54\text{mV/}^\circ\text{C}$  になります。

図 71. 温度ダイオード・インターフェース

## LO インターフェースの構成

LO インターフェースは、SPI のレジスタ  $0x20$  を介して選択可能なバイパス・モード、3 種類の通倍モード、1 種類の分周モードをサポートしています。これらの各動作モードについては、[バイパス・モード \(BYPASS = 1\)](#) から [4 通倍モード \(LOMODE = 3\)](#) までのセクションで説明しています。

## バイパス・モード (BYPASS = 1)

LO 信号は、周波数通倍器と分周器をバイパスして、内部ダウンコンバージョン・ミキサーに直接送られます。LO の通倍器と分周器、オフセット周波数インターフェースはディスエーブルされます。ADL5961 は、このモードで最も広い帯域幅と最も高いダイナミック・レンジを実現します。

## 2 分周モード (LOMODE = 0)

LO 入力信号の周波数は、2 分周された後にオフセット・ミキサーを通過し、ダウンコンバージョン・ミキサーに供給されます。RF 信号の周波数範囲でサポートされている場合、この LO 動作モードは、VNA 測定の周波数範囲を LO ソース自体がサポートする最低周波数より下に拡張する手段を提供します。この動作モードは、オフセット周波数インターフェースがイネーブルまたはディスエーブルのいずれの場合でも使用できます。

## 1 通倍モード (LOMODE = 1)

LO 信号は、LO の通倍器と分周器をバイパスしますが、オフセット・ミキサーを通じてダウンコンバージョン・ミキサーに送られます。オフセット周波数インターフェースをイネーブルした状態での使用を意図しています。オフセット周波数インターフェースをディスエーブルした状態でも使用できますが、ディスエーブルする代わりにバイパス・モード (BYPASS = 1) を選択すると、性能が向上します。

## アプリケーション情報

## 2 週倍モード (LOMODE = 2)

LO 信号は、周波数ダブル、プログラマブル・バンドパス・フィルタ、オフセット・ミキサーを通じてダウンコンバージョン・ミキサーに送られます。バンドパス・フィルタは、CT2 ビット (レジスタ 0x21 のビット[4:0]) の設定に応じてダブル出力信号の低調波を抑制します。[表 8](#) に、様々な  $2 \times f_{LO}$  周波数範囲の推奨設定値を示します。すべての CT2 設定値が有効です。[表 8](#) に示されていない CT2 設定値、例えば CT2 = 2, CT2 = 5, ... CT2 = 30 の場合は、 $2 \times f_{LO}$  の最小値と最大値は [表 8](#) に示されている項目に基づいて線形補間できます。

2 週倍モードは、単独でも、あるいは、オフセット周波数インターフェースと組み合わせても使用できます。

表 8. LOMODE = 2 の場合の推奨 CT2 バンドパス・フィルタ設定値

| CT2 | Minimum $2 \times f_{LO}$ (GHz) | Maximum $2 \times f_{LO}$ (GHz) |

|-----|---------------------------------|---------------------------------|

| 0   | 15                              | 20                              |

| 1   | 14                              | 15                              |

| 3   | 11                              | 14                              |

| 4   | 10                              | 12                              |

| 6   | 9                               | 10                              |

| 8   | 8                               | 9                               |

| 12  | 7                               | 8                               |

| 15  | 6                               | 7                               |

| 22  | 5                               | 6                               |

| 31  | 4                               | 5                               |

## 4 週倍モード (LOMODE = 3)

LO 信号は、最初に周波数ダブルを通過してから、CT2 ビット (レジスタ 0x21 のビット[4:0]) で調整されたバンドパス・フィルタを通過し、次に 2 つ目の周波数ダブルを通過してから、CT4 ビット (レジスタ 0x22 のビット[3:0]) で調整された 2 つ目のバンドパス・フィルタを通過します。その後、この信号は、オフセット・ミキサーを通じてダウンコンバージョン・ミキサーに送られます。[表 9](#) に、様々な  $4 \times f_{LO}$  周波数範囲の推奨設定値を示します。ただし、このリストはすべてを網羅したものではありません。他にも有効な組み合わせが存在するため、周波数範囲は推奨設定値と部分的または完全に重複します。このモードは、単独でも、あるいは、オフセット周波数インターフェースと組み合わせても使用できます。

表 9. LOMODE = 3 の場合の推奨 CT2/CT4 バンドパス・フィルタ設定値

| CT2 | CT4 | Minimum $4 \times f_{LO}$ (GHz) | Maximum $4 \times f_{LO}$ (GHz) |

|-----|-----|---------------------------------|---------------------------------|

| <5  | <12 | >20                             | >21                             |

| 5   | 12  | 20                              | 21                              |

| 6   | 13  | 19                              | 20                              |

| 7   | 14  | 17                              | 19                              |

| 12  | 15  | 14                              | 17                              |

## IF 信号パスの構成

ダウンコンバージョン・ミキサーに続く IF 信号パスは、出力信号のダイナミック・レンジを最適化し、幅広い ADC への最適なインターフェース接続を実現するように構成できます。

2 つのカスケード接続されたローパス・フィルタ (LPF) では、帯域外ノイズやスプリアス・トーンを抑制するために IF 帯域幅をプログラムすることができます。1 つ目のフィルタでは、[表 10](#) と [図 22](#) に示すように、CIF1 ビット (レジスタ 0x25 のビット[3:0]) を介して、粗い帯域幅調整を行えます。

表 10. CIF2 = 0 の場合の IF -3dB 帯域幅と CIF1 の関係

| CIF1 | f <sub>-3dB</sub> (MHz) |

|------|-------------------------|

| 0    | 126                     |

| 1    | 64.0                    |

| 2    | 41.0                    |

| 3    | 30.1                    |

| 4    | 24.1                    |

| 5    | 19.7                    |

| 6    | 16.7                    |

| 7    | 14.5                    |

| 8    | 13.0                    |

| 9    | 11.6                    |

| 10   | 10.5                    |

| 11   | 9.5                     |

| 12   | 8.8                     |

| 13   | 8.1                     |

| 14   | 7.6                     |

| 15   | 7.0                     |

2 つ目のフィルタでは、[表 11](#) と [図 25](#) に示すように、CIF2 ビット (レジスタ 0x25 のビット[7:4]) を介して、きめ細かい低帯域幅設定値をプログラムすることができます。両方の出力チャンネルは、同じ IF 帯域幅にプログラムされます。

表 11. CIF1 = 0 の場合の IF -3dB 帯域幅と CIF2 の関係

| CIF2 | f <sub>-3dB</sub> (MHz) |

|------|-------------------------|

| 0    | 126                     |

| 1    | 11.1                    |

| 2    | 5.9                     |

| 3    | 3.8                     |

| 4    | 3.1                     |

| 5    | 2.3                     |

| 6    | 2                       |

| 7    | 1.6                     |

| 8    | 1.5                     |

| 9    | 1.3                     |

| 10   | 1.2                     |

| 11   | 1.0                     |

| 12   | 0.99                    |

| 13   | 0.86                    |

## アプリケーション情報

表 11. CIF1 = 0 の場合の IF -3dB 帯域幅と CIF2 の関係（続き）

| CIF2 | f <sub>-3dB</sub> (MHz) |

|------|-------------------------|

| 14   | 0.80                    |

| 15   | 0.70                    |

これらのフィルタの後には、ゲインを個別にプログラム可能な差動出力アンプがあります。ゲインが調整可能なため、実際に使用されている RF 駆動レベルに合わせることができます。また様々なポート終端において、順方向チャンネルと逆方向チャンネルの両方のダイナミック・レンジを最適化することもできます。例えば、ブリッジが  $50\Omega$  に近いインピーダンスで終端されている場合、逆方向（反射）チャンネルのブリッジ出力信号レベルは、順方向（入射）チャンネルよりもはるかに低くなります。この差を補償するために、逆方向チャンネルのアンプを、順方向チャンネルよりも高いゲイン設定値にプログラムすることができます。そのため、両方のチャンネルは、IF 出力に接続された ADC の全入力ダイナミック・レンジを使用します。最適な測定精度を実現するために、キャリブレーション手順は、順方向チャンネルと逆方向チャンネルで使用されるすべてのゲイン設定の組み合わせを対象とする必要があります。

表 12 に示すように、順方向チャンネルと逆方向チャンネルのゲインは、それぞれ FGAIN ビット（レジスタ 0x23 のビット[6:0]）と RGAIN ビット（レジスタ 0x24 のビット[6:0]）を介して、6dB ステップでプログラムできます。次のゲイン設定値を選択するには、ビット値も 6 ずつ増やす必要があります（図 20 を参照）。48dB を超えるゲイン・レベルもサポートされていますが、増幅されたノイズが IF チャンネルを飽和させ始めるため、これらのレベルは通常、実用的な意味はほとんどありません。

表 12. IF アンプ・ゲインと FGAIN および RGAIN 設定値の関係

| FGAIN, RGAIN | IF Gain (dB) |

|--------------|--------------|

| 0 to 5       | 0            |

| 6 to 11      | 6            |

| 12 to 17     | 12           |

| 18 to 23     | 18           |

| 24 to 29     | 24           |

| 30 to 35     | 30           |

| 36 to 41     | 36           |

| 42 to 47     | 42           |

| 48 to 53     | 48           |

| ...          | ...          |

調整可能な出力コモンモード・レベル、最大 8V p-p の出力電圧振幅、最大 200mA の電流駆動能力により、数百 MHz までのサンプル・レートをもつ各種 ADC（Σ-Δ ADC、逐次近似レジスタ（SAR）ADC、またはパイプライン・ベース ADC）とインターフェース接続するのに十分な柔軟性が提供されます。

## シリアル・ペリフェラル・インターフェース

### プロトコル

ADL5961 は、その内部機能のいくつかを制御・監視するための周辺機器として、SPI バスに接続できます。タイミング条件の詳細については、[シリアル・インターフェースのタイミング仕様](#)のセクションを参照してください。共有データ入出力ラインを持つ 3 線インターフェースは、16 ビット・アドレスを用いて、8 ビット幅のレジスタにアクセスします。各 SPI 命令は、レジスタ・アドレスと、それに続く 1 つ以上のデータ・バイトからなり、MSB が最初に転送されます。ADL5961 は、単一バイト読出し・書込み操作と、ストリーミング読出し・書込み方式をサポートしています。

### レジスタ・アドレス

16 ビット・レジスタ・アドレスの 15 の LSB は、 $2^{15} = 32,768$  個の一意のレジスタ・アドレスを持つアドレス空間を定義します。ADL5961 が使用するのは、これらのアドレスの一部のみです。MSB は、デバイス・レジスタへの書込み操作 (MSB = 0) と、レジスタ・アドレスからのリードバック (MSB = 1) を区別するためのものです。

### 読出し・書込み方式

ADL5961 は、単一レジスタの読出し・書込み方式と、ストリーミング読出し・書込み方式の両方をサポートしています。後者的方式では、1 回の操作で複数のレジスタとの間でデータをやり取りします。

各命令は、 $\overline{CS}$  ラインのハイからローへの遷移で始まります。 $\overline{CS}$  がローのままである限り、データは、MSB アドレス・ビットを先頭

に、クロックの各立上がりエッジでラッチされます。命令は、 $\overline{CS}$  のローからハイへの遷移で終わります。読み出し命令が実行されると、SDIO 共有入出力ラインは、最後のアドレス・ビットをラッチした SCLK の立上がりエッジの次の立下がりエッジの直後の 1/2 クロック・サイクルの間に、高インピーダンス入力 (SDI) から低インピーダンス出力 (SDO) に変化します。 $\overline{CS}$  がアサート解除されると、SDIO は高インピーダンス入力 (SDI) 状態に戻ります。

ストリーミング読出し・書込み方式は、オートデクリメント・モードでのみ動作し、前のデータ・バイトより 1 つ下のアドレスを持つレジスタに対して次のデータ・バイトの読み出し・書込みを行います。

### レジスタの詳細

レジスタ 0x00～レジスタ 0x03 は、SPI を設定し、デバイス識別子を含みます。レジスタ 0x20～レジスタ 0x26 は、ADL5961 のアナログ回路機能を制御します。詳細については、[表 13](#) を参照してください。

### インターフェース設定レジスタ

レジスタ 0x00 はシリアル・インターフェース設定レジスタであり、4 ビットの回文として実装され、各ニブルはもう片方のニブルのミラーです。このミラーにより、データのシフト方向にかかわらず、デバイス同期が失われた場合に ADL5961 をプログラムすることができます。このため、このアドレスへの書込み時には、このレジスタを設定する際のあいまいさを取り除くために、回文が常に必要です。

表 13. ADL5961 の SPI レジスタの詳細

| アドレス | レジスタ名        | ビット   | ビット名       | 説明                                                                                                                                                                   | リセット | アクセス |

|------|--------------|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| 0x00 | SPI_CONFIG_A | 7     | SOFTRESET_ | ソフト・リセット。ビット 0 のコピー。                                                                                                                                                 | 0x0  | R/W  |

|      |              | 6     | LSB_FIRST_ | LSB ファースト。ビット 1 のコピー。                                                                                                                                                | 0x0  | R/W  |

|      |              | 5     | ASCENSION_ | アドレス・アセンション。ビット 2 のコピー。                                                                                                                                              | 0x0  | R/W  |

|      |              | [4:3] | RESERVED   | 予約済み。                                                                                                                                                                | 0x0  | R    |

|      |              | 2     | ASCENSION  | アドレス・アセンション。セットすると、アドレス・アセンション・モードが有効になります。クリアすると、アドレスは下降します。<br>0 : アドレス・オートデクリメント。<br>1 : アドレス・オートインクリメント。                                                         | 0x0  | R/W  |

|      |              | 1     | LSB_FIRST  | LSB ファースト。セットすると、入出力データは LSB ファーストで処理されます。このビットをクリアすると、データは MSB ファーストで処理されます。<br>1 : LSB ファースト。<br>0 : MSB ファースト。                                                    | 0x0  | R/W  |

|      |              | 0     | SOFTRESET  | ソフト・リセット。このビットをセットすると、ハード・リセットと同等のリセットが開始されます。ただし、0x00 (このレジスタ) のビットと SPI ステート・マシンは影響を受けません。このビットは、ソフト・リセットが完了すると自動的にクリアされます。<br>1 : リセットをアサート。<br>0 : リセットをアサートしない。 | 0x0  | R/W  |

表 13. ADL5961 の SPI レジスタの詳細 (続き)

| アドレス | レジスタ名         | ビット   | ビット名                 | 説明                                                                                                                                                                                                                                                                                                                     | リセット | アクセス |

|------|---------------|-------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| 0x01 | SPI_CONFIG_B  | 7     | SINGLE_INSTRUCTION   | 単一命令。このビットがセットされると、ストリーミングは無効になり、 $\overline{CS}$ ラインの状態にかかわらず、読み出しまでは書き込み操作が1回だけ実行されます。このビットをクリアすると、ストリーミングが有効になります。このビットがセットされ、 $\overline{CS}$ がアサートされたままの場合、ステート・マシンは、 $\overline{CS}$ がアサート解除されたかのようにデータ・バイトの後でリセットし、次の命令を待ちます。これにより、 $\overline{CS}$ ラインが SPI コントローラによりアサート解除されていない場合でも、各データ・バイトの前に新しい命令が配置されます。 | 0x0  | R/W  |

|      |               | 6     | CSB_STALL            | $\overline{CS}$ 停止。SINGLE_INSTRUCTION が有効、かつ CSB_STALL が有効になると、 $\overline{CS}$ 信号がハイにプルアップされても SPI ステート・マシンはリセットされません。CSB_STALL が無効になると、 $\overline{CS}$ 信号がハイのときは SPI ステート・マシンが常にリセットされます。                                                                                                                           | 0x0  | R/W  |

|      |               | 5     | CONTROLLER_TARGET_RB | コントローラまたはターゲット・デバイスのリードバック。このビットをセットすると、SPI コントローラのフリップ・フロップ出力のリードバックが可能になります。このビットをクリアすると、内部 SPI レジスタ出力にアクセスできます。                                                                                                                                                                                                     | 0x0  | R/W  |

|      |               | [4:0] | RESERVED             | 予約済み。                                                                                                                                                                                                                                                                                                                  | 0x0  | R    |

| 0x02 | DEVICE_CONFIG | [7:2] | RESERVED             | 予約済み。                                                                                                                                                                                                                                                                                                                  | 0x0  | R/W  |

|      |               | 1     | SHUTDOWN             | デバイス・シャットダウン。シャットダウンがアサートされると、デバイスは電源オフになります。 <a href="#">EN インターフェース</a> のセクションを参照してください。<br>0 : 通常動作。<br>1 : シャットダウン。                                                                                                                                                                                                | 0x0  | R/W  |

|      |               | 0     | RESERVED             | 予約済み。                                                                                                                                                                                                                                                                                                                  | 0x0  | R    |

| 0x03 | CHIPTYPE      | [7:0] | CHIPTYPE             | チップ・タイプ、読み出し専用。                                                                                                                                                                                                                                                                                                        | 0x1  | R    |

| 0x20 | LO_CONFIG     | [7:5] | RESERVED             | 予約済み。                                                                                                                                                                                                                                                                                                                  | 0x0  | R    |

|      |               | 4     | BYPASS               | LO パスをバイパス。アサートされると、LO チェーンはすべての倍器と分周器がオフになるように設定されます。このビットの設定は、IFMODE ビットと LOMODE ビットの設定より優先されます。LO 入力は、LO アンプによってのみ RF ミキサーに接続されます。                                                                                                                                                                                  | 0x1  | R/W  |

|      |               | [3:2] | OFMODE               | OFMODE。オフセット基準周波数インターフェースの分周器を設定します。<br>00 : 1 適倍。分周器はイネーブルされません。<br>01 : 2 分周モード。<br>10 : 4 分周モード。<br>11 : 分周器をオフ。オフセット基準信号を切断します。                                                                                                                                                                                    | 0x2  | R/W  |

|      |               | [1:0] | LOMODE               | LOMODE。LO チェーンの倍器と分周器を設定します。<br>00 : 2 分周。<br>01 : 1 適倍 (1×)。<br>10 : 2 適倍 (2×)。<br>11 : 4 適倍 (4×)。                                                                                                                                                                                                                    | 0x1  | R/W  |

| 0x21 | CT2           | [7:5] | RESERVED             | 予約済み。                                                                                                                                                                                                                                                                                                                  | 0x0  | R    |

|      |               | [4:0] | CT2                  | CT2 フィルタ設定値。LO インターフェースの周波数 2 倍器用にフィルタの中心周波数を設定します。                                                                                                                                                                                                                                                                    | 0x0  | R/W  |

| 0x22 | CT4           | [7:4] | RESERVED             | 予約済み。                                                                                                                                                                                                                                                                                                                  | 0x0  | R    |

|      |               | [3:0] | CT4                  | CT4 フィルタ設定値。LO インターフェースの周波数 4 倍器用にフィルタの中心周波数を設定します。                                                                                                                                                                                                                                                                    | 0x0  | R/W  |

表 13. ADL5961 の SPI レジスタの詳細 (続き)

| アドレス | レジスタ名     | ビット   | ビット名     | 説明                                                                                                      | リセット | アクセス |

|------|-----------|-------|----------|---------------------------------------------------------------------------------------------------------|------|------|

| 0x23 | FGAIN     | 7     | RESERVED | 予約済み。                                                                                                   | 0x0  | R    |

|      |           | [6:0] | FGAIN    | 順方向ゲイン。IFFP および IFFM 出力への順方向パスにおける IF アンプのゲインを 6dB ステップで設定します。10 進レジスタ値はゲインを dB 単位で表します。                | 0x0  | R/W  |

| 0x24 | RGAIN     | 7     | RESERVED | 予約済み。                                                                                                   | 0x0  | R    |

|      |           | [6:0] | RGAIN    | 逆方向ゲイン。IFRP および IFRM 出力への逆方向パスにおける IF アンプのゲインを 6dB ステップで設定します。10 進レジスタ値はゲインを dB 単位で表します。表 12 を参照してください。 | 0x0  | R/W  |

| 0x25 | CIF2_CIF1 | [7:4] | CIF2     | 狭帯域 IF フィルタ設定。狭帯域 IF フィルタのコーナー周波数を設定します。図 25 を参照してください。                                                 | 0x0  | R/W  |

|      |           | [3:0] | CIF1     | 広帯域 IF フィルタ設定。広帯域 IF フィルタのコーナー周波数を設定します。図 22 を参照してください。                                                 | 0x0  | R/W  |

| 0x26 | TDEG      | [7:5] | RESERVED | 予約済み。                                                                                                   | 0x0  | R    |

|      |           | [4:0] | TDEG     | 温度センサー用レジスタ。温度センサーの 5 ビットの読み出し値です。図 40 も参照してください。約 7.4°C /ステップ。-44.6°C で TDEG = 0 から TDEG = 1 へ遷移します。   | 0x0  | R    |

## 代表的なアプリケーション・テスト回路

図 72. テスト回路

評価用ボードのコンポーネントの詳細については、EVAL-ADL5961 ユーザ・ガイドを参照してください。

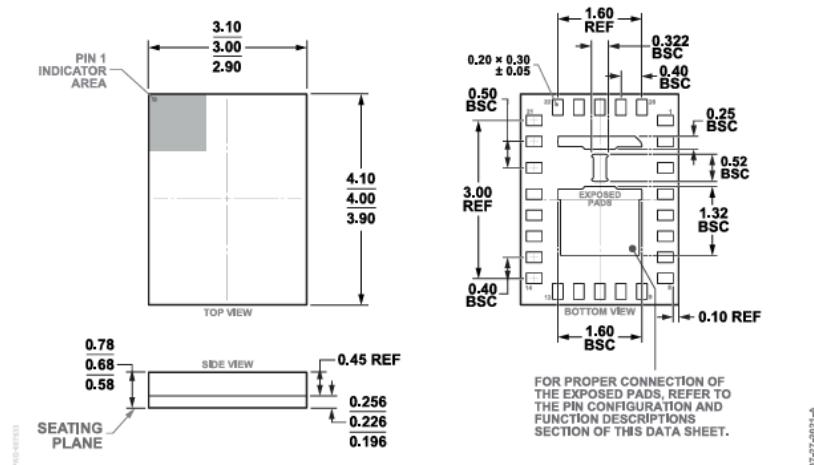

## 外形寸法

図 73. 26-ピン・ランド・グリッド・アレイ [LGA]

(CC-26-2)

寸法 : mm

更新 : 2023 年 7 月 5 日

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description           | Packing Quantity | Package Option |

|--------------------|-------------------|-------------------------------|------------------|----------------|

| ADL5961ACZ         | -40°C to +105°C   | 26-Lead Land Grid Array [LGA] |                  | CC-26-2        |

| ADL5961ACZ-R2      | -40°C to +105°C   | 26-Lead Land Grid Array [LGA] | Reel, 250        | CC-26-2        |

| ADL5961ACZ-R7      | -40°C to +105°C   | 26-Lead Land Grid Array [LGA] | Reel, 1500       | CC-26-2        |

1 Z = RoHS 適合製品。

## 評価用ボード

| Model <sup>1, 2, 3</sup> | Description             |