# 高精度 MEMS IMU モジュール

## データシート

## ADIS16467

### 特長

3軸、デジタル・ジャイロ・センサー

ダイナミック・レンジが、 $\pm 125^{\circ}/\text{sec}$ 、 $\pm 500^{\circ}/\text{sec}$ 、

$\pm 2000^{\circ}/\text{sec}$  の 3 モデル

動作中のバイアス安定度:  $2^{\circ}/\text{hr}$  (ADIS16467-1)

角度ランダム・ウォーク:  $0.15^{\circ}/\sqrt{\text{hr}}$

(ADIS16467-1 および ADIS16467-2)

軸間ミスマライメント誤差:  $\pm 0.05^{\circ}$

3軸、デジタル加速度センサー:  $\pm 40 \text{ g}$

動作中のバイアス安定度:  $13 \mu\text{g}$

3軸、角度変化および速度変化の出力

工場出荷時キャリブレーション済みの感度、バイアス、

軸アライメント

キャリブレーション温度範囲:  $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$

SPI 対応のデータ通信

プログラマブルな動作と制御

自動と手動のバイアス補正制御

同期データ・アクイジョン用データ・レディ・

インジケータ

外部同期モード: 直接、パルス、スケーリング、出力

慣性センサーのオン・デマンド・セルフ・テスト

フラッシュ・メモリのオン・デマンド・セルフ・テスト

単電源動作 (VDD) :  $3.0 \text{ V} \sim 3.6 \text{ V}$

2000 g の機械的衝撃耐性

動作温度範囲:  $-40^{\circ}\text{C} \sim +105^{\circ}\text{C}$

### 概要

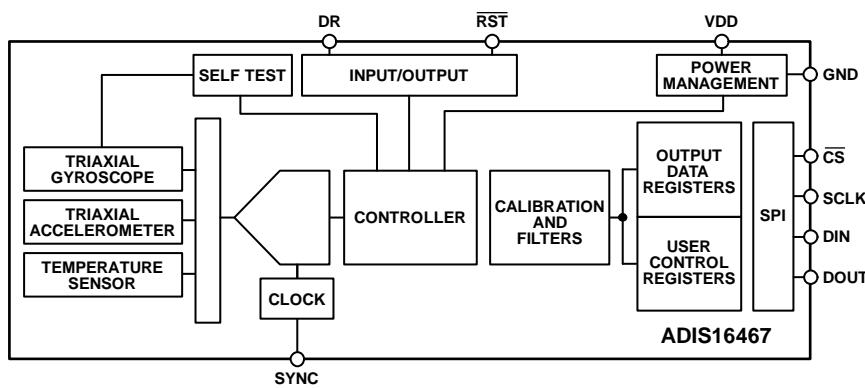

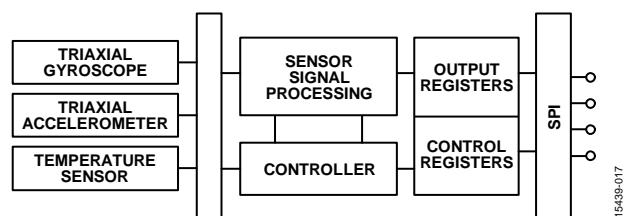

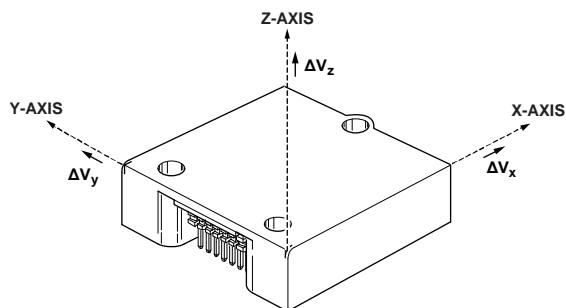

ADIS16467 は高精度の微小電気機械システム (MEMS) 慣性計測ユニット (IMU) で、3 軸のジャイロ・センサーと 3 軸の加速度センサーを内蔵しています。ADIS16467 内の各慣性センサーがシグナル・コンディショニングと組み合わさることで、動的性能が最適化されています。各センサーの感度、バイアス、アライメント、直線加速度 (ジャイロ・センサー・バイアス)、振動ポイント (加速度センサーの位置) の特性は、工場出荷時のキャリブレーションで評価されています。そのため、各センサーには動的な補償のための式が備わっており、幅広い条件に対して高精度のセンサー計測が可能となっています。

ADIS16467 は、高精度の多軸慣性センシングを工業用システムに組み込むためのシンプルで費用対効果に優れたソリューションを提供します。これは、特にディスクリート部品を使用した設計と比較して、複雑さや費用面でメリットがあります。すなわち、必要なモーション・テストとキャリブレーションがすべて工場での製造工程に組み込まれているため、システムを統合する時間を大幅に短縮できます。また、厳密な直交アライメントにより、ナビゲーション・システムの慣性フレーム・アライメントが簡単になります。シリアル・ペリフェラル・インターフェース (SPI) やレジスタ構造により、データ収集や設定制御とのインターフェースも容易です。

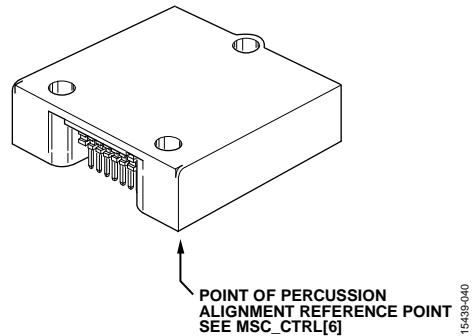

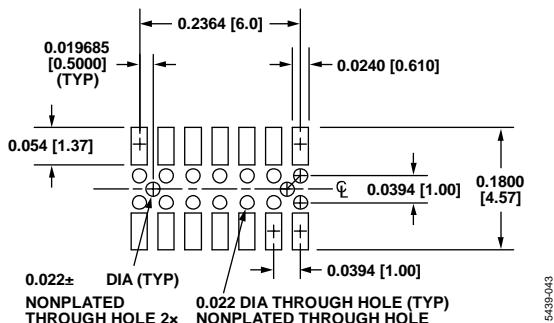

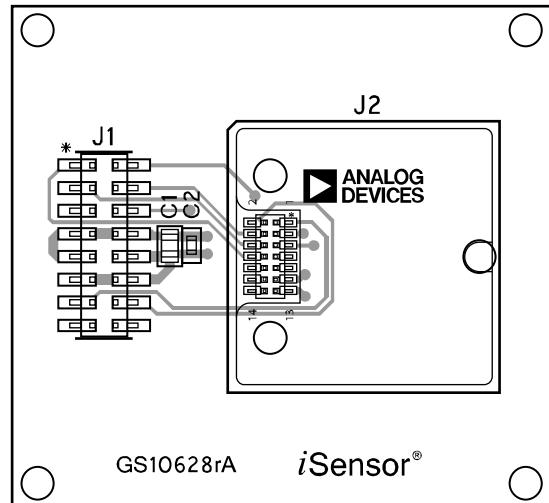

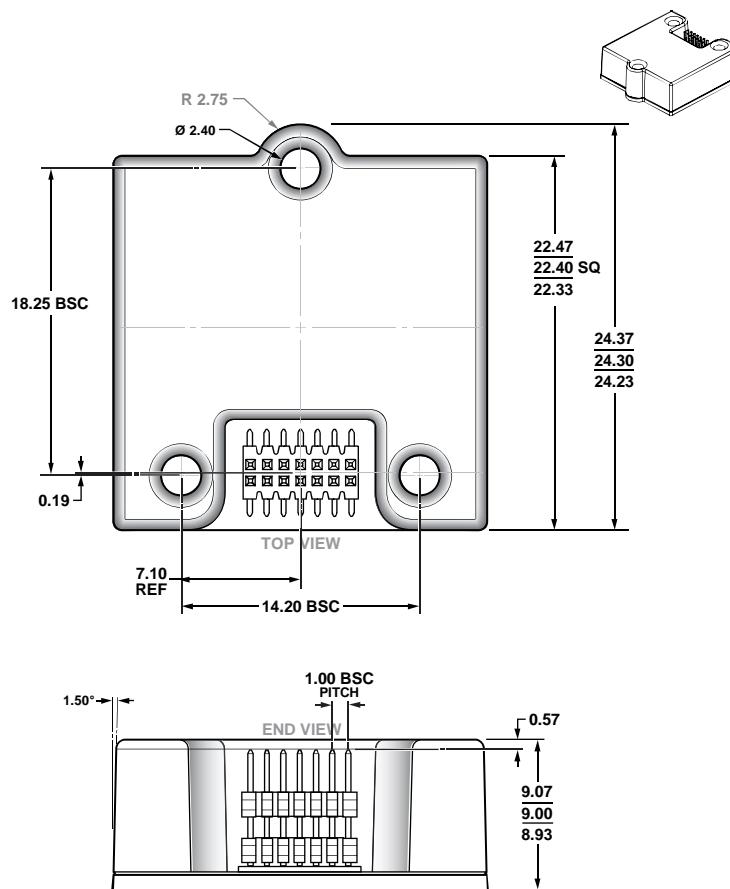

ADIS16467 は、約  $22.4 \text{ mm} \times 24.3 \text{ mm} \times 9 \text{ mm}$  のアルミニウム・モジュール・パッケージに収納され、14 ピン・コネクタ・インターフェースを備えています。

### アプリケーション

ナビゲーション、安定化、計測器

無人運転車、自動運転車

スマート農業、建設機械

ファクトリー／産業オートメーション、ロボティクス

仮想／拡張現実

動くモノのインターネット

### 機能ブロック図

15439-001

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                            |    |                   |    |

|----------------------------|----|-------------------|----|

| 特長                         | 1  | センサー・データの読み出し     | 13 |

| アプリケーション                   | 1  | デバイスの設定           | 14 |

| 概要                         | 1  | ユーザ・レジスタのメモリ・マップ  | 15 |

| 機能ブロック図                    | 1  | ユーザ・レジスタ定義        | 17 |

| 改訂履歴                       | 2  | ジャイロ・センサーのデータ     | 17 |

| 仕様                         | 3  | 角度変化              | 20 |

| タイミング仕様                    | 5  | 速度変化              | 21 |

| 絶対最大定格                     | 7  | キャリブレーション         | 23 |

| 熱抵抗                        | 7  | アプリケーション情報        | 30 |

| ESD に関する注意                 | 7  | アセンブリとハンドリングのポイント | 30 |

| ピン配置およびピン機能説明              | 8  | 電源に関する考慮事項        | 30 |

| 代表的な性能特性                   | 9  | ブレークアウト・ボード       | 30 |

| 動作原理                       | 10 | PC ベースの評価ツール      | 31 |

| はじめに                       | 10 | パッケージとオーダー情報      | 32 |

| 慣性センサーのシグナル・チェーン           | 10 | 外形寸法              | 32 |

| レジスタ構造                     | 11 | オーダー・ガイド          | 32 |

| シリアル・ペリフェラル・インターフェース (SPI) | 12 |                   |    |

| データ・レディ (DR)               | 12 |                   |    |

## 改訂履歴

12/2017—Revision 0: Initial Version

## 仕様

特に指定のない限り、ケース温度 ( $T_C$ ) = 25 °C、VDD = 3.3 V、角速度 = 0°/sec、ダイナミック・レンジ = ±2000°/sec ± 1 g。

表 1.

| Parameter                         | Test Conditions/Comments                                                                                                      | Min                   | Typ                                | Max | Unit                                            |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------|-----|-------------------------------------------------|

| <b>GYROSCOPES</b>                 |                                                                                                                               |                       |                                    |     |                                                 |

| Dynamic Range <sup>1</sup>        | ADIS16467-1<br>ADIS16467-2<br>ADIS16467-3                                                                                     | ±125<br>±500<br>±2000 |                                    |     | °/sec<br>°/sec<br>°/sec                         |

| Sensitivity                       | ADIS16467-1, 32-bit<br>ADIS16467-2, 32-bit<br>ADIS16467-3, 32-bit                                                             |                       | 10,485,760<br>2,621,440<br>655,360 |     | LSB/°/sec<br>LSB/°/sec<br>LSB/°/sec             |

| Error over Temperature            | -40°C ≤ $T_C$ ≤ +85°C, 1 σ                                                                                                    |                       | ±0.1                               |     | %                                               |

| Misalignment Error                | Axis to axis, 1 σ                                                                                                             |                       | ±0.05                              |     | Degrees                                         |

| Nonlinearity <sup>2</sup>         | ADIS16467-1, full scale (FS) = 125°/sec<br>ADIS16467-2, FS = 500°/sec<br>ADIS16467-3, FS = 2000°/sec                          |                       | 0.2<br>0.2<br>0.25                 |     | % FS<br>% FS<br>% FS                            |

| Bias                              |                                                                                                                               |                       |                                    |     |                                                 |

| In-Run Bias Stability             | ADIS16467-1, 1 σ<br>ADIS16467-2, 1 σ<br>ADIS16467-3, 1 σ                                                                      |                       | 2<br>2.5<br>6                      |     | %/hr<br>%/hr<br>%/hr                            |

| Angular Random Walk               | ADIS16467-1, 1 σ<br>ADIS16467-2, 1 σ<br>ADIS16467-3, 1 σ                                                                      |                       | 0.15<br>0.15<br>0.3                |     | °/√hr<br>°/√hr<br>°/√hr                         |

| Error over Temperature            | -40°C ≤ $T_C$ ≤ +85°C, 1 σ                                                                                                    |                       | ±0.2                               |     | °/sec                                           |

| Linear Acceleration Effect        | Any direction, 1 σ                                                                                                            |                       | 0.009                              |     | °/sec/g                                         |

| Vibration Rectification Effect    | Random vibration, 2 g rms, bandwidth = 50 Hz to 2 kHz                                                                         |                       | 0.0005                             |     | °/sec/g <sup>2</sup>                            |

| Output Noise                      | ADIS16467-1, 1 σ, no filtering<br>ADIS16467-2, 1 σ, no filtering<br>ADIS16467-3, 1 σ, no filtering                            |                       | 0.07<br>0.08<br>0.17               |     | °/sec rms<br>°/sec rms<br>°/sec rms             |

| Rate Noise Density                | ADIS16467-1, bandwidth = 10 Hz to 40 Hz<br>ADIS16467-2, bandwidth = 10 Hz to 40 Hz<br>ADIS16467-3, bandwidth = 10 Hz to 40 Hz |                       | 0.003<br>0.003<br>0.007            |     | °/sec/√Hz rms<br>°/sec/√Hz rms<br>°/sec/√Hz rms |

| 3 dB Bandwidth                    |                                                                                                                               |                       | 550                                |     | Hz                                              |

| Sensor Resonant Frequency         |                                                                                                                               |                       | 66                                 |     | kHz                                             |

| <b>ACCELEROMETERS<sup>3</sup></b> |                                                                                                                               |                       |                                    |     |                                                 |

| Dynamic Range                     | Each axis                                                                                                                     |                       |                                    |     |                                                 |

| Sensitivity                       | 32-bit data format                                                                                                            | ±40                   | 52,428,800                         |     | g<br>LSB/g                                      |

| Error over temperature            | -40°C ≤ $T_C$ ≤ +85°C, 1 σ                                                                                                    |                       | ±0.1                               |     | %                                               |

| Misalignment Error                | Axis to axis                                                                                                                  |                       | ±0.05                              |     | Degrees                                         |

| Nonlinearity                      | Best fit straight line, ±10 g<br>Best fit straight line, ±20 g<br>Best fit straight line, ±40 g                               |                       | ±0.02<br>±0.4<br>±1.5              |     | % FS<br>% FS<br>% FS                            |

| Bias                              |                                                                                                                               |                       |                                    |     |                                                 |

| In-Run Bias Stability             | 1 σ, y-axis and z-axis                                                                                                        |                       | 13                                 |     | μg                                              |

| Velocity Random Walk              | 1 σ                                                                                                                           |                       | 0.037                              |     | m/sec/√hr                                       |

| Error over Temperature            | -40°C ≤ $T_C$ ≤ +85°C, 1 σ                                                                                                    |                       | ±3                                 |     | mg                                              |

| Output Noise                      | No filtering                                                                                                                  |                       | 2.3                                |     | mg rms                                          |

| Noise Density                     | Bandwidth = 10 Hz to 40 Hz, no filtering                                                                                      |                       | 100                                |     | μg/√Hz rms                                      |

| 3 dB Bandwidth                    |                                                                                                                               |                       | 600                                |     | Hz                                              |

| Sensor Resonant Frequency         | Y-axis and z-axis                                                                                                             |                       | 5.65                               |     | kHz                                             |

|                                   | X-axis                                                                                                                        |                       | 5.25                               |     | kHz                                             |

| Parameter                                                                                                   | Test Conditions/Comments                                                                                                                                                     | Min                   | Typ | Max       | Unit            |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------|-----------------|

| TEMPERATURE SENSOR<br>Scale Factor                                                                          | Output = 0x0000 at 0°C ( $\pm 5^\circ\text{C}$ )                                                                                                                             |                       | 0.1 |           | °C/LSB          |

| LOGIC INPUTS <sup>4</sup><br>Input Voltage<br>High, $V_{IH}$<br>Low, $V_{IL}$                               |                                                                                                                                                                              | 2.0                   |     | 0.8       | V               |

| RST Pulse Width                                                                                             |                                                                                                                                                                              | 1                     |     |           | μs              |

| CS Wake-Up Pulse Width                                                                                      |                                                                                                                                                                              | 20                    |     |           | μs              |

| Input Current<br>Logic 1, $I_{IH}$<br>Logic 0, $I_{IL}$                                                     | $V_{IH} = 3.3\text{ V}$<br>$V_{IL} = 0\text{ V}$                                                                                                                             |                       | 10  |           | μA              |

| All Pins Except RST<br>RST Pin                                                                              |                                                                                                                                                                              |                       | 10  |           | μA              |

| Input Capacitance, $C_{IN}$                                                                                 |                                                                                                                                                                              | 0.33                  |     | 10        | mA              |

| DIGITAL OUTPUTS<br>Output Voltage<br>High, $V_{OH}$<br>Low, $V_{OL}$                                        | $I_{SOURCE} = 0.5\text{ mA}$<br>$I_{SINK} = 2.0\text{ mA}$                                                                                                                   | 2.4                   |     | 0.4       | V               |

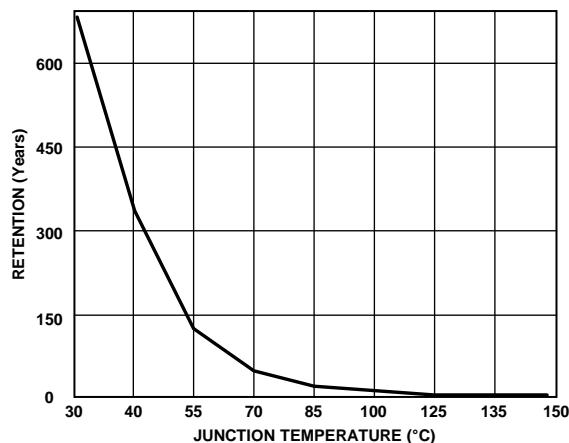

| FLASH MEMORY<br>Data Retention <sup>6</sup>                                                                 | Endurance <sup>5</sup><br>$T_J = 85^\circ\text{C}$                                                                                                                           | 10000<br>20           |     |           | Cycles<br>Years |

| FUNCTIONAL TIMES <sup>7</sup><br>Power-On Start-Up Time<br>Reset Recovery Time                              | Time until data is available<br>Register GLOB_CMD, Bit 7 = 1 (see 表 113)<br>RST pulled low, then restored to high <sup>8</sup>                                               | 259<br>198<br>198     |     |           | ms              |

| Factory Calibration Restore<br>Flash Memory Backup<br>Flash Memory Test Time<br>Self Test Time <sup>9</sup> | Register GLOB_CMD, Bit 1 = 1 (see 表 113)<br>Register GLOB_CMD, Bit 3 = 1 (see 表 113)<br>Register GLOB_CMD, Bit 4 = 1 (see 表 113)<br>Register GLOB_CMD, Bit 2 = 1 (see 表 113) | 142<br>72<br>32<br>14 |     |           | ms              |

| CONVERSION RATE<br>Initial Clock Accuracy<br>Sync Input Clock                                               |                                                                                                                                                                              | 2000<br>3<br>1.9      |     | 2.1       | SPS<br>%<br>kHz |

| POWER SUPPLY, VDD<br>Power Supply Current <sup>10</sup>                                                     | Operating voltage range<br>Normal mode, VDD = 3.3 V                                                                                                                          | 3.0<br>44             |     | 3.6<br>55 | V<br>mA         |

<sup>1</sup> 各レンジのスケール・ファクタは表 11 に記載されています。<sup>2</sup> この測定値は、ベストフィット直線モデルからの偏差に基づいています。<sup>3</sup> 特に指定のない限り、加速度センサーに関するすべての仕様は、 $\pm 8\text{ g}$  のフルスケール・レンジに対するものです。<sup>4</sup> デジタル入出力信号には 3.3 V システムを使用しています。<sup>5</sup> 書換え回数は JEDEC 規格 22、Method A117 に準拠し、 $-40^\circ\text{C}$ 、 $+25^\circ\text{C}$ 、 $+85^\circ\text{C}$ 、 $+125^\circ\text{C}$  で測定しています。<sup>6</sup> データ保持仕様は、JEDEC 規格 22、Method A117 に準拠した  $85^\circ\text{C}$  のジャンクション温度 ( $T_J$ ) を想定しています。データ保持寿命は  $T_J$  に伴って短くなります。<sup>7</sup> これらの時間には、全体の精度に影響を与える可能性がある、熱安定時間と内部フィルタ応答時間は含まれていません。<sup>8</sup> 正しくリセットを開始してデバイスを復帰させるには、RST ラインを少なくとも  $10\text{ }\mu\text{s}$  にわたってローに保持する必要があります。<sup>9</sup> 2000 Hz 未満の外部クロックを使用する場合、セルフ・テスト時間はこれより長くなる場合があります。<sup>10</sup> 初回起動時やリセットによる復帰時には、電源電流のトランジェントが 100 mA に達することがあります。

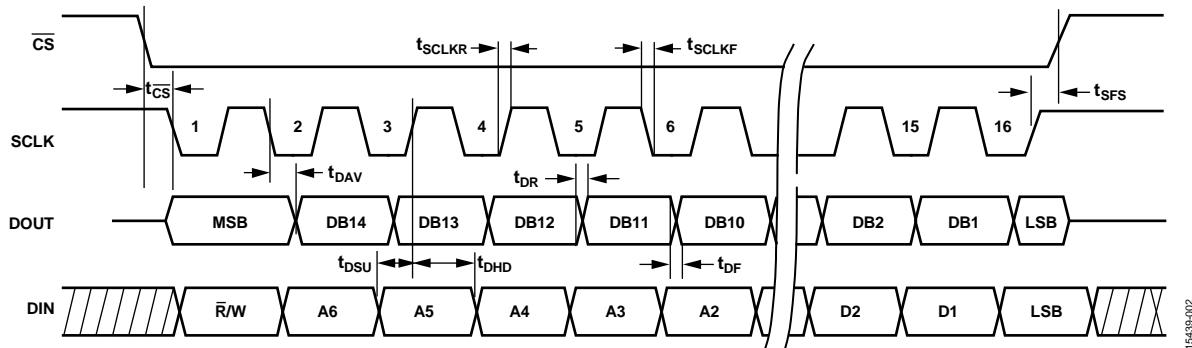

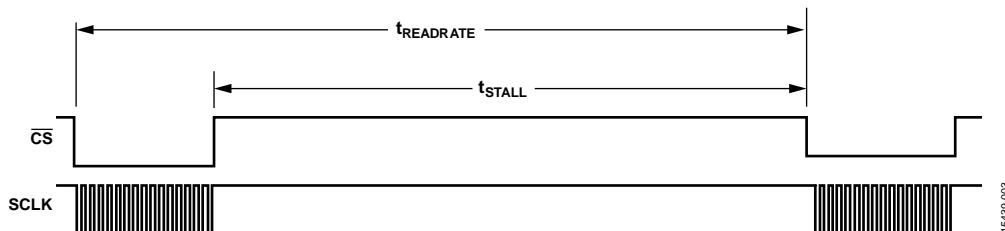

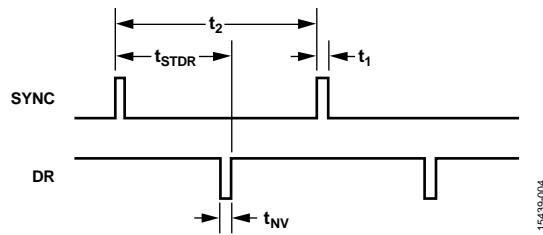

## タイミング仕様

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $VDD = 3.3\text{ V}$ 。

表 2.

| Parameter              | Description                                                                                                                                                                          | Normal Mode |     |      | Burst Read Mode  |     |      | Unit |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|------|------------------|-----|------|------|

|                        |                                                                                                                                                                                      | Min         | Typ | Max  | Min <sup>1</sup> | Typ | Max  |      |

| $f_{SCLK}$             | Serial clock                                                                                                                                                                         | 0.1         | 2   | 0.1  | 1                |     |      | MHz  |

| $t_{STALL}$            | Stall period between data                                                                                                                                                            | 16          |     | N/A  |                  |     |      | μs   |

| $t_{READRATE}$         | Read rate                                                                                                                                                                            | 24          |     |      |                  |     |      | μs   |

| $t_{CS}$               | Chip select to SCLK edge                                                                                                                                                             | 200         |     | 200  |                  |     |      | ns   |

| $t_{DAV}$              | DOUT valid after SCLK edge                                                                                                                                                           |             | 25  |      |                  | 25  |      | ns   |

| $t_{DSU}$              | DIN setup time before SCLK rising edge                                                                                                                                               | 25          |     | 25   |                  |     |      | ns   |

| $t_{DHD}$              | DIN hold time after SCLK rising edge                                                                                                                                                 | 50          |     | 50   |                  |     |      | ns   |

| $t_{SCLKR}, t_{SCLKF}$ | SCLK rise/fall times                                                                                                                                                                 |             | 5   | 12.5 |                  | 5   | 12.5 | ns   |

| $t_{DR}, t_{DF}$       | DOUT rise/fall times                                                                                                                                                                 |             | 5   | 12.5 |                  | 5   | 12.5 | ns   |

| $t_{SFS}$              | CS high after SCLK edge                                                                                                                                                              | 0           |     | 0    |                  |     |      | ns   |

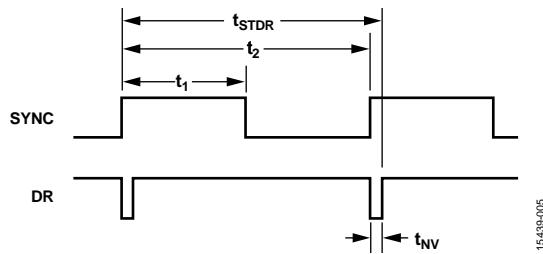

| $t_1$                  | Input sync positive pulse width; pulse sync mode,<br>Register MSC_CTRL, Bits[4:1] (binary, see 表 105)                                                                                | 5           |     | 5    |                  |     |      | μs   |

| $t_{STDTR}$            | Input sync to data ready valid transition<br>Direct sync mode, Register MSC_CTRL, Bits[4:2] (binary, see 表 105)<br>Pulse sync mode, Register MSC_CTRL, Bits[4:2] (binary, see 表 105) |             | 507 |      | 507              |     |      | μs   |

| $t_{NV}$               | Data invalid time                                                                                                                                                                    |             | 256 |      | 256              |     |      | μs   |

| $t_2$                  | Input sync period                                                                                                                                                                    | 20          |     | 20   |                  |     |      | μs   |

|                        |                                                                                                                                                                                      | 500         |     | 500  |                  |     |      | μs   |

<sup>1</sup> N/A は該当なしを意味します。

## タイミング図

図 2. SPI のタイミングとシーケンスの図

図 3. 待ち時間とデータ・レートのタイミング図

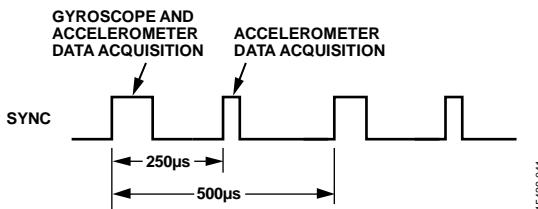

図4. 入力クロックのタイミング図

(パルス同期モード、MSC\_CTRL レジスタのビット [4:2] = 101 (バイナリ) )

図5. 入力クロックのタイミング図

(直接同期モード、MSC\_CTRL レジスタのビット [4:2] = 001 (バイナリ) )

## 絶対最大定格

表 3.

| Parameter                              | Rating                |

|----------------------------------------|-----------------------|

| Mechanical Shock Survivability         |                       |

| Any Axis, Unpowered                    | 2000 g                |

| Any Axis, Powered                      | 2000 g                |

| VDD to GND                             | -0.3 V to +3.6 V      |

| Digital Input Voltage to GND           | -0.3 V to VDD + 0.2 V |

| Digital Output Voltage to GND          | -0.3 V to VDD + 0.2 V |

| Calibration Temperature Range          | -40°C to +85°C        |

| Operating Temperature Range            | -40°C to +105°C       |

| Storage Temperature Range <sup>1</sup> | -65°C to +150°C       |

| Barometric Pressure                    | 2 bar                 |

<sup>1</sup> -40 °C 未満の低温、または +105 °C を超える高温下に長時間放置すると、工場出荷時のキャリブレーション精度に悪影響を与える可能性があります。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この仕様規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCB の熱設計には、細心の注意を払う必要があります。

ADIS16467 は多数の能動部品を含むマルチチップ・モジュールです。表 4 に示す値は、ADIS16467 内部の最も高温の部品の熱応答を、モジュールの全消費電力の範囲で示したものです。この方法では、周囲温度またはケース温度に基づいて、最も高いジャングルクション温度を簡単な方法で予測することができます。

例えば周囲温度が 70 °C の場合、ADIS16467 内部の最も高いジャングルクション温度 ( $T_J$ ) は 75.3 °C です。

$$T_J = \theta_{JA} \times VDD \times I_{DD} + 70 \text{ °C}$$

$$T_J = 36.5 \text{ °C/W} \times 3.3 \text{ V} \times 0.044 \text{ A} + 70 \text{ °C}$$

$$T_J = 75.3 \text{ °C}$$

表 4. 热抵抗

| Package Type         | $\theta_{JA}$ <sup>1</sup> | $\theta_{JC}$ <sup>2</sup> | Mass (g) |

|----------------------|----------------------------|----------------------------|----------|

| ML-14-6 <sup>3</sup> | 36.5°C/W                   | 16.9°C/W                   | 15       |

<sup>1</sup>  $\theta_{JA}$  は、1 立方フィートの密封容器内で測定された、自然対流でのジャングルクションから周囲への熱抵抗です。

<sup>2</sup>  $\theta_{JC}$  は、ジャングルクションからケースへの熱抵抗です。

<sup>3</sup> 热抵抗の値は、ADIS16467 を 2 層の金属層からなる厚さ 0.063 インチの FR4-08 PCB に取り付け、その内部の最高温度を直接測定した値に基づいています。

## ESD に関する注意

### ESD (静電放電) の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

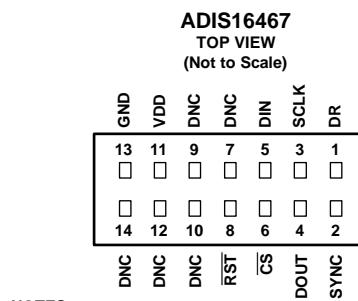

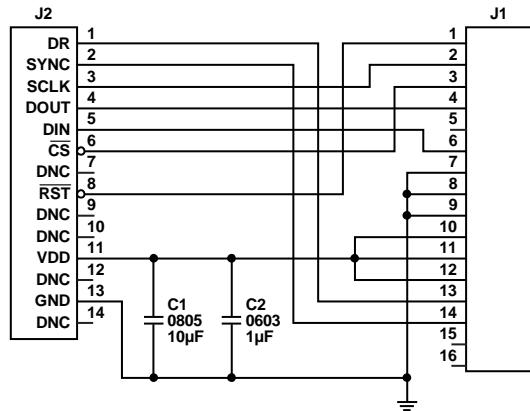

## ピン配置およびピン機能説明

## NOTES

1. THIS REPRESENTS THE PIN ASSIGNMENTS WHEN LOOKING DOWN AT THE CONNECTOR. SEE FIGURE 7.

2. MATING CONNECTOR:

SAMTEC CLM-107-02 SERIES OR EQUIVALENT.

3. DNC = DO NOT CONNECT.

図 6. ピン配置（底面の上面図）

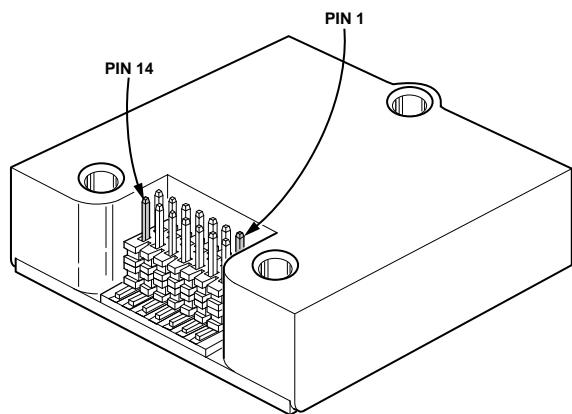

図 7. ピン配置（パッケージ全体図）

15439-007

表 5. ピン機能の説明

| Pin No. | Mnemonic | Type           | Description                              |

|---------|----------|----------------|------------------------------------------|

| 1       | DR       | Output         | データ・レディ・インジケータ。                          |

| 2       | SYNC     | Input/output   | 外部同期の入出力 (MSC_CTRL による)。表 105 を参照してください。 |

| 3       | SCLK     | Input          | SPI シリアル・クロック。                           |

| 4       | DOUT     | Output         | SPI データ出力。このピンは SCLK の立下がりエッジでクロック出力します。 |

| 5       | DIN      | Input          | SPI データ入力。このピンは SCLK の立上がりエッジでクロック入力します。 |

| 6       | CS       | Input          | SPI チップ・セレクト。                            |

| 7       | DNC      | Not applicable | 接続なし。このピンには接続しないでください。                   |

| 8       | RST      | Input          | リセット。                                    |

| 9       | DNC      | Not applicable | 接続なし。このピンには接続しないでください。                   |

| 10      | DNC      | Not applicable | 接続なし。このピンには接続しないでください。                   |

| 11      | VDD      | Supply         | 電源。                                      |

| 12      | DNC      | Not applicable | 接続なし。このピンには接続しないでください。                   |

| 13      | GND      | Supply         | 電源グラウンド。                                 |

| 14      | DNC      | Not applicable | 接続なし。このピンには接続しないでください。                   |

## 代表的な性能特性

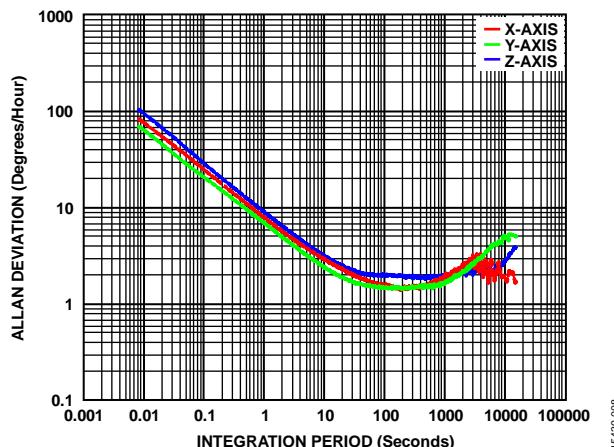

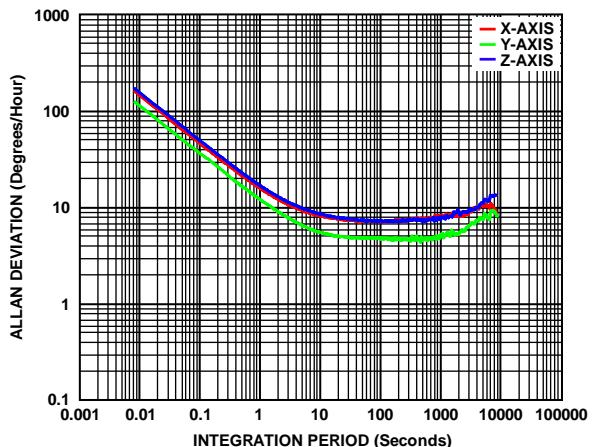

図 8. ジャイロ・センサーのアラン偏差、 $T_c = 25^{\circ}\text{C}$ 、

ADIS16467-1

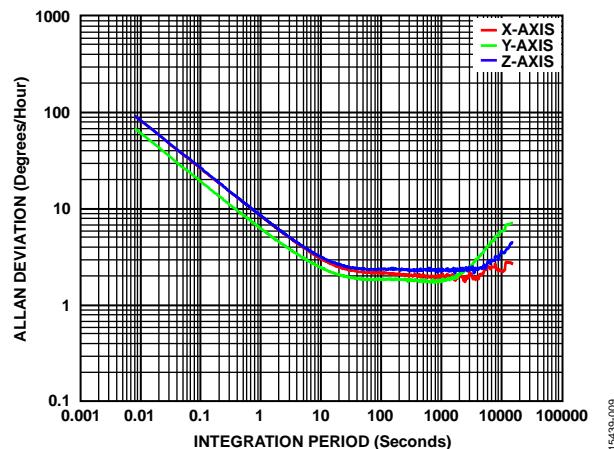

図 10. ジャイロ・センサーのアラン偏差、 $T_c = 25^{\circ}\text{C}$ 、

ADIS16467-3

図 9. ジャイロ・センサーのアラン偏差、 $T_c = 25^{\circ}\text{C}$ 、

ADIS16467-2

## 動作原理

### はじめに

ユーザ設定可能なすべての制御レジスタに工場出荷時のデフォルト構成を使用した場合、ADIS16467 は自動的に初期化を行い、補正されたセンサー・データのサンプリングと処理を行って出力レジスタに 2000 SPS のレートで出力するという連続プロセスを開始します。

### 慣性センサーのシグナル・チェーン

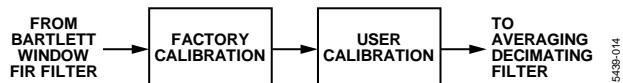

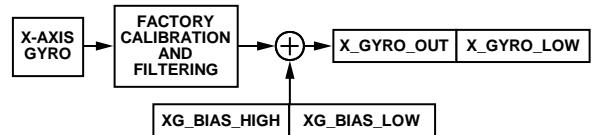

ADIS16467 が内蔵している慣性センサーの基本的なシグナル・チェーンを図 11 に示します。内部クロック・モード（デフォルト設定、表 105 の MSC\_CTRL レジスタのビット [4:2] を参照）で動作する場合、このシグナル・チェーンによって、出力データ・レジスタは 2000 SPS のレートで更新されます。

図 11. 慣性センサーの信号処理の流れ

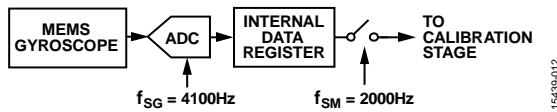

### ジャイロ・センサーのデータ・サンプリング

3 つのジャイロ・センサーによって、3 つの直交軸 (x, y, z) の周りの角速度測定が行われます。ADIS16467 が内部クロック・モード（デフォルト設定、表 105 の MSC\_CTRL レジスタのビット [4:2] を参照）で動作する場合の、各ジャイロ・センサーのデータ・サンプリング方法を図 12 に示します。各ジャイロ・センサーには、A/D コンバータ (ADC) と、データ・サンプリングを 4100 Hz ( $\pm 5\%$ ) のレートで駆動するサンプル・クロック ( $f_{SG}$ ) が備わっています。内蔵プロセッサは、各ジャイロ・センサーのこのデータを 2000 Hz のレート ( $f_{SM}$ ) で読み出し、処理します。

図 12. ジャイロ・センサーのデータ・サンプリング

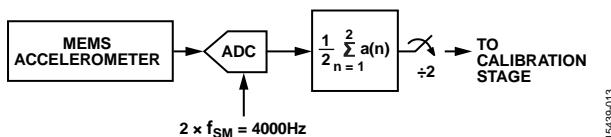

### 加速度センサーのデータ・サンプリング

3 つの加速度センサーによって、ジャイロ・センサーと同じ直交軸 (x, y, z) 方向の直線加速度測定が行われます。ADIS16467 が内部クロック・モード（デフォルト設定、表 105 の MSC\_CTRL レジスタのビット [4:2] を参照）で動作する場合の、各加速度センサーのデータ・サンプリング方法を図 13 に示します。

図 13. 加速度センサーのデータ・サンプリング

### 外部クロック・オプション

ADIS16467 は 3 通りの異なる動作モードを備えており、SYNC ピン経由で外部クロックによって内部処理レート（図 12 と図 13 の  $f_{SM}$ ）を制御するデバイスにも対応しています。MSC\_CTRL レジスタ（表 105 参照）のビット [4:2] に、これらの外部クロック・モードの設定オプションが用意されています。

### 慣性センサーのキャリブレーション

ジャイロ・センサーと加速度センサーに対して行われる慣性センサーのキャリブレーション機能には、工場出荷時のキャリブレーションとユーザ・キャリブレーションの 2 つの要素があります（図 14 参照）。

図 14. 慎性センサーのキャリブレーション過程

工場出荷時のジャイロ・センサーのキャリブレーションでは、次の相関式を各ジャイロ・センサーのデータに適用しています。

$$\begin{bmatrix} \omega_{XC} \\ \omega_{YC} \\ \omega_{ZC} \end{bmatrix} = \begin{bmatrix} m_{11} & m_{12} & m_{13} \\ m_{21} & m_{22} & m_{23} \\ m_{31} & m_{32} & m_{33} \end{bmatrix} \times \begin{bmatrix} \omega_X \\ \omega_Y \\ \omega_Z \end{bmatrix} + \begin{bmatrix} b_X \\ b_Y \\ b_Z \end{bmatrix} + \begin{bmatrix} l_{11} & l_{12} & l_{13} \\ l_{21} & l_{22} & l_{23} \\ l_{31} & l_{32} & l_{33} \end{bmatrix} \times \begin{bmatrix} a_{XC} \\ a_{YC} \\ a_{ZC} \end{bmatrix}$$

ここで

$\omega_{XC}$ ,  $\omega_{YC}$ ,  $\omega_{ZC}$  はジャイロ・センサーのキャリブレーション後の出力、

$m_{11}$ ,  $m_{12}$ ,  $m_{13}$ ,  $m_{21}$ ,  $m_{22}$ ,  $m_{23}$ ,  $m_{31}$ ,  $m_{32}$ ,  $m_{33}$  はスケールとアライメントの補正、

$\omega_X$ ,  $\omega_Y$ ,  $\omega_Z$  はジャイロ・センサーのキャリブレーション前の出力、

$b_X$ ,  $b_Y$ ,  $b_Z$  はバイアス補正、

$l_{11}$ ,  $l_{12}$ ,  $l_{13}$ ,  $l_{21}$ ,  $l_{22}$ ,  $l_{23}$ ,  $l_{31}$ ,  $l_{32}$ ,  $l_{33}$  は直線  $g$  補正、

$a_{XC}$ ,  $a_{YC}$ ,  $a_{ZC}$  は加速度センサーのキャリブレーション後の出力です。

この関係式の補正係数はすべて、各ジャイロ・センサーの応答をキャリブレーション温度範囲 ( $-40^{\circ}\text{C} \leq T_c \leq +85^{\circ}\text{C}$ ) にわたって複数の温度で直接測定した値に基づいています。これらの補正係数はフラッシュ・メモリ・バンクに保存されますが、測定用や設定用には使用できません。MSC\_CTRL レジスタのビット 7（表 105 参照）は、ジャイロ・センサーの工場出荷時のキャリブレーション値に対する唯一のユーザ設定オプション（直線  $g$  補正のオン／オフ制御）を提供します。ジャイロ・センサーに使用可能なユーザ・キャリブレーション・オプションの詳細については、図 37 を参照してください。

工場出荷時の加速度センサーのキャリブレーションでは、次の相関式を各加速度センサーのデータに適用しています。

$$\begin{bmatrix} a_{XC} \\ a_{YC} \\ a_{ZC} \end{bmatrix} = \begin{bmatrix} m_{11} & m_{12} & m_{13} \\ m_{21} & m_{22} & m_{23} \\ m_{31} & m_{32} & m_{33} \end{bmatrix} \times \begin{bmatrix} a_X \\ a_Y \\ a_Z \end{bmatrix} + \begin{bmatrix} b_X \\ b_Y \\ b_Z \end{bmatrix} +$$

$$\begin{bmatrix} 0 & p_{12} & p_{13} \\ p_{21} & 0 & p_{23} \\ p_{31} & p_{32} & 0 \end{bmatrix} \times \begin{bmatrix} \omega_{XC}^2 \\ \omega_{YC}^2 \\ \omega_{ZC}^2 \end{bmatrix}$$

ここで

$a_{XC}$ 、 $a_{YC}$ 、 $a_{ZC}$ は加速度センサーのキャリブレーション後の出力、 $m_{11}$ 、 $m_{12}$ 、 $m_{13}$ 、 $m_{21}$ 、 $m_{22}$ 、 $m_{23}$ 、 $m_{31}$ 、 $m_{32}$ 、 $m_{33}$ はスケールとアライメントの補正、 $a_X$ 、 $a_Y$ 、 $a_Z$ は加速度センサーのキャリブレーション前の出力、 $b_X$ 、 $b_Y$ 、 $b_Z$ はバイアス補正、 $p_{12}$ 、 $p_{13}$ 、 $p_{21}$ 、 $p_{23}$ 、 $p_{31}$ 、 $p_{32}$ は振動ポイント・アライメントの補正（図 40 参照）、 $\omega_{XC}^2$ 、 $\omega_{YC}^2$ 、 $\omega_{ZC}^2$ はジャイロ・センサーのキャリブレーション後の出力を二乗したものです。

この関係式の補正係数はすべて、各加速度センサーの応答をキャリブレーション温度範囲 ( $-40^{\circ}\text{C} \leq T_c \leq +85^{\circ}\text{C}$ ) にわたって複数の温度で直接測定した値に基づいています。これらの補正係数はフラッシュ・メモリ・バンクに保存されますが、測定用や設定用には使用できません。MSC\_CTRL レジスタのビット 6（表 105 参照）は、加速度センサーの工場出荷時のキャリブレーション値に対する唯一のユーザ設定オプション（振動ポイント・アライメント機能のオン／オフ制御）を提供します。加速度センサーに使用可能なユーザ・キャリブレーション・オプションの詳細については、図 38 を参照してください。

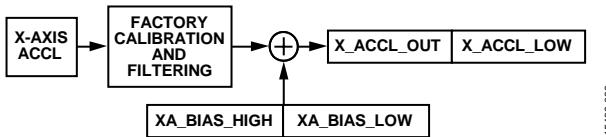

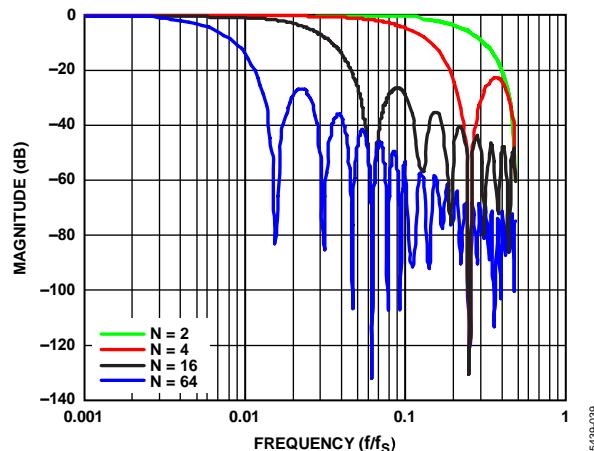

## バートレット・ウインドウ FIR (有限インパルス応答) フィルタ

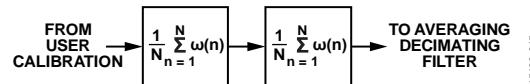

バートレット・ウインドウ FIR フィルタ（図 15 参照）では、2つの平均化フィルタ段が直列に構成されています。FILT\_CTRL レジスタ（表 101 参照）によって、このフィルタの構成が制御されます。

図 15. バートレット・ウインドウ FIR フィルタの信号経路

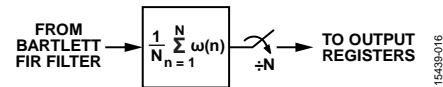

## 平均化／デシメーション・フィルタ

2段目のデジタル・フィルタで複数のサンプルが全体で平均化され、各レジスタが更新されます。このタイプのフィルタ構造では、平均化するサンプル数が出力データ・レジスタの更新レートの削減数と等しくなります。DEC\_RATE レジスタ（表 109 参照）によって、このフィルタの構成が制御されます。

図 16. 平均化／デシメーション・フィルタ

## レジスタ構造

ADIS16467 と外部プロセッサ間のすべての通信では、出力レジスタの内容の読み出し、または設定情報やコマンド情報の制御レジスタへの書き込みが行われます。出力データ・レジスタには、最新のセンサー・データ、エラー・フラグ、および識別情報が格納されます。制御レジスタには、サンプル・レート、フィルタリング、キャリブレーション、および診断オプションが格納されます。ユーザ・アクセスが可能な各レジスタは 2 バイト構成（上位および下位）で、それぞれに固有のアドレスがあります。すべてのユーザ・レジスタとそのアドレスの詳細な一覧については、表 8 を参照してください。

図 17. ADIS16467 の基本動作

## シリアル・ペリフェラル・インターフェース (SPI)

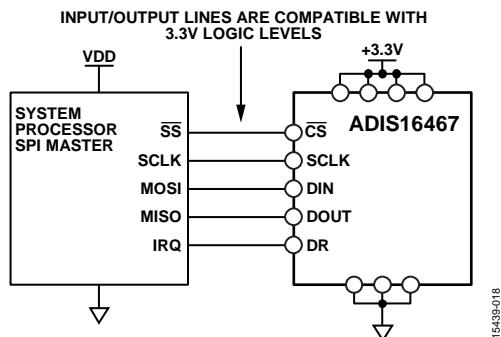

SPI は、ユーザ・レジスタへのアクセスを可能にします（表 8 参照）。図 18 に、ADIS16467 と SPI マスター・デバイス間の最も一般的な接続を示します。マスター・デバイスは、多くの場合、SPI 互換のインターフェースを持つ組み込みプロセッサです。この例では、SPI マスターは割込みサービス・ルーチンを使用して、データ・レディ (DR) 信号パルスを受信するたびにデータを取得します。

図 18. 電気接続図

表 6. 一般的な SPI マスター・ピンの記号と機能

| Mnemonic | Function                   |

|----------|----------------------------|

| SS       | Slave select               |

| SCLK     | Serial clock               |

| MOSI     | Master output, slave input |

| MISO     | Master input, slave output |

| IRQ      | Interrupt request          |

通常、組み込みプロセッサは、制御レジスタを使用してそのシリアル・ポートを設定し、ADIS16467 などの SPI スレーブ・デバイスと通信します。ADIS16467 の SPI プロトコルを記述する設定一覧を、表 7 に示します。通常、これらの設定は、ファームウェア・コマンドを使ってマスター・プロセッサの初期化ルーチンで行われ、設定内容は制御レジスタに書き込まれます。

表 7. 一般的なマスター・プロセッサの SPI 設定

| Processor Setting              | Description                            |

|--------------------------------|----------------------------------------|

| Master                         | ADIS16467 operates as slave            |

| SCLK $\leq$ 2 MHz <sup>1</sup> | Maximum serial clock rate              |

| SPI Mode 3                     | CPOL = 1 (polarity), CPHA = 1 (phase)  |

| MSB First Mode                 | Bit sequence, see Figure 23 for coding |

| 16-Bit Mode                    | Shift register and data length         |

<sup>1</sup> パースト・モード読出しへは、この値を 1 MHz 以下にする必要があります（詳細については表 2 を参照）。

## データ・レディ (DR)

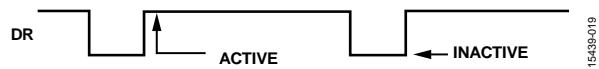

工場出荷時のデフォルト設定では、出力データ・レジスタの更新時に DR 信号を DR ピン（表 5 参照）にパルス出力するようになっています。この DR ピンを組み込みプロセッサのピンに接続すると、このパルスの 2 つ目のエッジでデータ取得がトリガれます。MSC\_CTRL レジスタのビット 0（表 105 参照）で、この信号の極性が制御されます。図 19 に、MSC\_CTRL レジスタのビット 0 = 1 の例を示します。この場合、データ取得は DR パルスの立上がりで開始することになります。

図 19. MSC\_CTRL レジスタのビット 0 = 1 (デフォルト) の場合のデータ・レディ

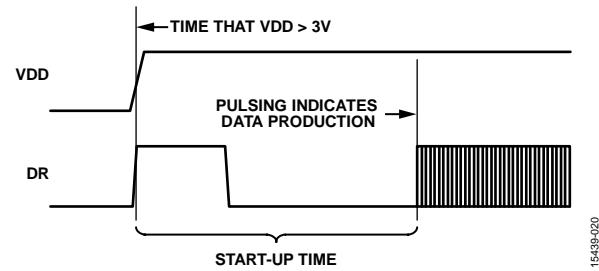

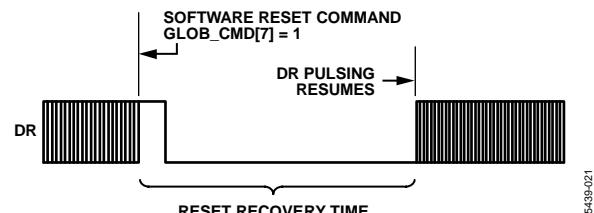

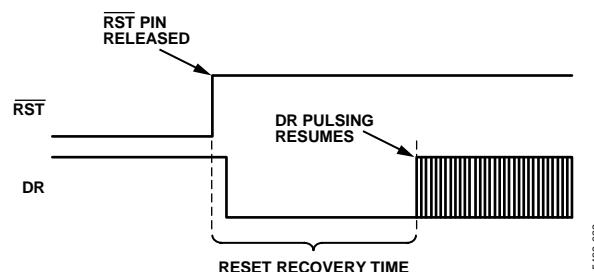

起動時やリセットからの復帰時、データの生成が始まる前に DR 信号に過渡応答が見られる場合があります。図 20 に起動時の DR 応答の例、図 21 と図 22 にリセット・コマンドからの復帰時の DR 応答の例を示します。

図 20. 起動時のデータ・レディ応答

図 21. リセット (GLOB\_CMD レジスタのビット 7 = 1) からの復帰中のデータ・レディ応答

図 22. リセット ( $\overline{RST} = 0$ ) からの復帰中のデータ・レディ応答

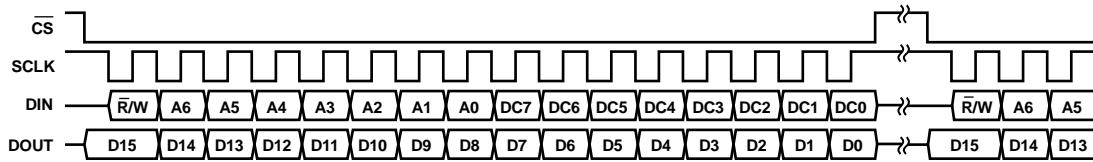

## NOTES

1. DOUT BITS ARE PRODUCED ONLY WHEN THE PREVIOUS 16-BIT DIN SEQUENCE STARTS WITH R/W = 0.

2. WHEN CS IS HIGH, DOUT IS IN A THREE-STATE, HIGH IMPEDANCE MODE, WHICH ALLOWS MULTIFUNCTIONAL USE OF THE LINE FOR OTHER DEVICES.

15439-023

図 23. SPI 通信のビット・シーケンス

図 24. バースト読出しシーケンス

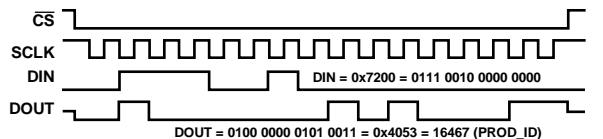

図 25. SPI の信号パターン (PROD\_ID レジスタの繰り返し読出し)

## センサー・データの読み出し

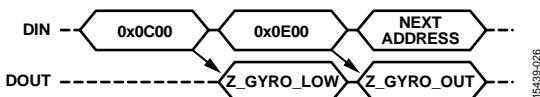

1つのレジスタを読み出すには、SPI 上に 2つの 16 ビット・サイクルが必要です。1つはレジスタの内容を要求するサイクル、もう1つはその内容を受信するサイクルです。SPI での読み出しが用いる 16 ビット・コマンド・コード (図 23 参照) は、読み出しひび (R/W = 0) 、レジスタのアドレス ([A6:A0]) 、8 個のドントケア・ビット ([DC7:DC0]) の3つの部分で構成されます。連続する 2つのレジスタ読み出しが含まれる例を、図 26 に示します。この例は、Z\_GYRO\_LOW レジスタの内容を要求するために DIN = 0x0C00 から始まり、Z\_GYRO\_OUT レジスタの内容を要求するために 0x0E00 がこれに続きます。また、図 26 のシーケンスは、完全に二重の動作モードも示します。すなわち、ADIS16467 は DIN で要求を受信する一方、同じ 16 ビット SPI サイクルの間に、DOUT への出力データの送信も行います。

図 26. SPI 読出しの例

繰り返しパターンで PROD\_ID レジスタを読み出すときの 4つの SPI 信号の例を、図 25 に示します (表 121 参照)。このパターンは、最初のサイクルを除き、信号が各 16 ビット・シーケンスで同一なので、SPI インターフェースの設定や通信のトラブルシューティング時に役立てるこどもできます。

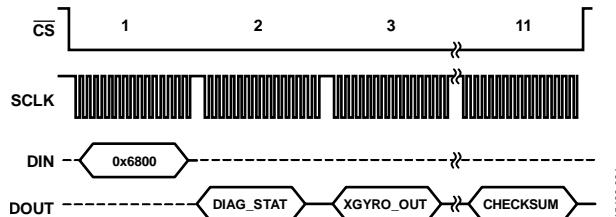

## バースト読出し機能

バースト読出し機能は、最大 1 MHz (SCLK) のレートで連続的に流れるビットを使用して、出力データ・レジスタ群を一括で読み出すための方法です。この方法では、各 16 ビット・セグメント間の待ち時間は不要です (図 3 参照)。図 24 に示すように、DIN = 0x6800 と設定してこのモードを開始し、次にこのシーケンスの中で DOUT から各レジスタの内容を読み出します。このとき、CS は 176 ビットのシーケンス全体にわたってローに保持されます。

バースト読出し応答でのレジスタのシーケンス (およびチェックサム値) は、ADIS16467 がどのサンプル・クロック・モード (MSC\_CTRL レジスタのビット [4:2]、表 105 参照) で動作しているかによって異なります。スケーリング同期モード (MSC\_CTRL レジスタのビット [4:2] = 010) で動作する場合を除くすべてのクロック・モードで、バースト読出し応答は次のレジスタおよび値で構成されます: DIAG\_STAT、X\_GYRO\_OUT、Y\_GYRO\_OUT、Z\_GYRO\_OUT、X\_ACCL\_OUT、Y\_ACCL\_OUT、Z\_ACCL\_OUT、TEMP\_OUT、DATA\_CNTR、およびチェックサム値。これらの場合、次の式を使用してチェックサム値を検証します。なお、式中の各バイオトは、独立した符号なしの 8 ビット数として扱います:

$$\begin{aligned}

\text{チェックサム} = & \text{DIAG\_STAT のビット } [15:8] + \text{DIAG\_STAT のビット } [7:0] + \\

& \text{X\_GYRO\_OUT のビット } [15:8] + \text{X\_GYRO\_OUT のビット } [7:0] + \\

& \text{Y\_GYRO\_OUT のビット } [15:8] + \text{Y\_GYRO\_OUT のビット } [7:0] + \\

& \text{Z\_GYRO\_OUT のビット } [15:8] + \text{Z\_GYRO\_OUT のビット } [7:0] + \\

& \text{X\_ACCL\_OUT のビット } [15:8] + \text{X\_ACCL\_OUT のビット } [7:0] + \\

& \text{Y\_ACCL\_OUT のビット } [15:8] + \text{Y\_ACCL\_OUT のビット } [7:0] + \\

& \text{Z\_ACCL\_OUT のビット } [15:8] + \text{Z\_ACCL\_OUT のビット } [7:0] + \\

& \text{TEMP\_OUT のビット } [15:8] + \text{TEMP\_OUT のビット } [7:0] + \\

& \text{DATA\_CNTR のビット } [15:8] + \text{DATA\_CNTR のビット } [7:0]

\end{aligned}$$

スケーリング同期モード (MSC\_CTRL レジスタのビット [4:2] = 010) で動作する場合は、バースト読出し応答は次のレジスタおよび値で構成されます :DIAG\_STAT、X\_GYRO\_OUT、Y\_GYRO\_OUT、Z\_GYRO\_OUT、X\_ACCL\_OUT、Y\_ACCL\_OUT、Z\_ACCL\_OUT、TEMP\_OUT、TIME\_STAMP、およびチェックサム値。この場合、次の式を使用してチェックサム値を検証します。なお、式中の各バイトは、独立した符号なしの 8 ビット数として扱います：

チェックサム = DIAG\_STAT のビット [15:8] + DIAG\_STAT のビット [7:0] +

X\_GYRO\_OUT のビット [15:8] + X\_GYRO\_OUT のビット [7:0]

+

Y\_GYRO\_OUT のビット [15:8] + Y\_GYRO\_OUT のビット [7:0]

+

Z\_GYRO\_OUT のビット [15:8] + Z\_GYRO\_OUT のビット [7:0]

+

X\_ACCL\_OUT のビット [15:8] + X\_ACCL\_OUT のビット [7:0]

+

Y\_ACCL\_OUT のビット [15:8] + Y\_ACCL\_OUT のビット [7:0] +

Z\_ACCL\_OUT のビット [15:8] + Z\_ACCL\_OUT のビット [7:0] +

TEMP\_OUT のビット [15:8] + TEMP\_OUT のビット [7:0] +

TIME\_STAMP のビット [15:8] + TIME\_STAMP のビット [7:0]

## デバイスの設定

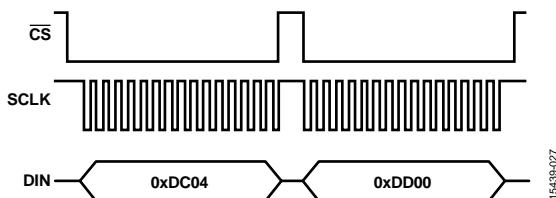

各設定レジスタは 16 ビット (2 バイト) で構成されます。ビット [7:0] には各レジスタの下位バイトが格納され、ビット [15:8] には上位バイトが格納されます。各バイトには、ユーザ・レジスタ・マップ内の固有アドレスが割り当てられます (表 8 参照)。レジスタの内容を更新するには、先に下位バイト、次に上位バイトのシーケンスで書き込む必要があります。レジスタに新しいデータ・バイトを書き込む SPI コマンドのコーディングは、3 つの部分からなります (図 23 参照)：書き込みビット (R/W = 1)、バイトのアドレス ([A6:A0])、およびその位置に書き込む新しいデータ ([DC7:DC0]) です。図 27 に、FILT\_CTRL レジスタに 0x0004 を書き込むコーディング例を示します (表 101 参照)。図 27 では、0xDC04 コマンドによって 0x04 がアドレス 0x5C (下位バイト) に書き込まれ、0xDD00 コマンドによって 0x00 がアドレス 0x5D (上位バイト) に書き込まれています。

図 27. FILT\_CTRL に 0x0004 を書き込むための SPI シーケンス

## メモリ構造

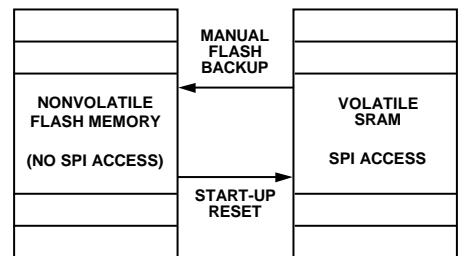

ADIS16467 のメモリ構造の機能図を図 28 に示します。フラッシュ・メモリ・バンクは、動作コード、ユニット固有のキャリブレーション係数、ユーザ設定値などで構成されます。初期化 (電力投入時またはリセット復帰時) 中に、この情報がフラッシュ・メモリから、スタティック・ランダム・アクセス・メモリ (SRAM) にロードされます。これにより、SPI ポートを介したレジスタへのアクセスを含むすべての通常動作がサポートされます。SPI を使用して設定レジスタに書込みを行うことで、レジスタの SRAM 位置指定は更新されますが、フラッシュ・メモリ・バンクの設定は自動的には更新されません。手動のフラッシュ・メモリ更新コマンド (GLOB\_CMD レジスタのビット 3、表 113 を参照) は、これらのすべての設定を一度にフラッシュ・メモリ・バンクに保存できる便利な方法です。表 8 の Flash Backup 列にある「yes」は、フラッシュ・メモリ・バンクのストレージ・サポート機能を持つレジスタを意味します。

図 28. SRAM とフラッシュ・メモリの図

## ユーザ・レジスタのメモリ・マップ

表 8. ユーザ・レジスタのメモリ・マップ (N/A は該当なしを示す)

| Name          | R/W | Flash Backup | Address      | Default          | Register Description                 |

|---------------|-----|--------------|--------------|------------------|--------------------------------------|

| Reserved      | N/A | N/A          | 0x00, 0x01   | N/A              | 予備                                   |

| DIAG_STAT     | R   | No           | 0x02, 0x03   | 0x0000           | 出力、システム・エラー・フラグ                      |

| X_GYRO_LOW    | R   | No           | 0x04, 0x05   | N/A              | 出力、x 軸ジャイロ・センサー、下位ワード                |

| X_GYRO_OUT    | R   | No           | 0x06, 0x07   | N/A              | 出力、x 軸ジャイロ・センサー、上位ワード                |

| Y_GYRO_LOW    | R   | No           | 0x08, 0x09   | N/A              | 出力、y 軸ジャイロ・センサー、下位ワード                |

| Y_GYRO_OUT    | R   | No           | 0x0A, 0x0B   | N/A              | 出力、y 軸ジャイロ・センサー、上位ワード                |

| Z_GYRO_LOW    | R   | No           | 0x0C, 0x0D   | N/A              | 出力、z 軸ジャイロ・センサー、下位ワード                |

| Z_GYRO_OUT    | R   | No           | 0x0E, 0x0F   | N/A              | 出力、z 軸ジャイロ・センサー、上位ワード                |

| X_ACCL_LOW    | R   | No           | 0x10, 0x11   | N/A              | 出力、x 軸加速度センサー、下位ワード                  |

| X_ACCL_OUT    | R   | No           | 0x12, 0x13   | N/A              | 出力、x 軸加速度センサー、上位ワード                  |

| Y_ACCL_LOW    | R   | No           | 0x14, 0x15   | N/A              | 出力、y 軸加速度センサー、下位ワード                  |

| Y_ACCL_OUT    | R   | No           | 0x16, 0x17   | N/A              | 出力、y 軸加速度センサー、上位ワード                  |

| Z_ACCL_LOW    | R   | No           | 0x18, 0x19   | N/A              | 出力、z 軸加速度センサー、下位ワード                  |

| Z_ACCL_OUT    | R   | No           | 0x1A, 0x1B   | N/A              | 出力、z 軸加速度センサー、上位ワード                  |

| TEMP_OUT      | R   | No           | 0x1C, 0x1D   | N/A              | 出力、温度                                |

| TIME_STAMP    | R   | No           | 0x1E, 0x1F   | N/A              | 出力、タイム・スタンプ                          |

| Reserved      | N/A | N/A          | 0x20, 0x21   | N/A              | 予備                                   |

| DATA_CNTR     | R   | No           | 0x22, 0x23   | N/A              | 新データ・カウンタ                            |

| X_DELTANG_LOW | R   | No           | 0x24, 0x25   | N/A              | 出力、x 軸角度変化、下位ワード                     |

| X_DELTANG_OUT | R   | No           | 0x26, 0x27   | N/A              | 出力、x 軸角度変化、上位ワード                     |

| Y_DELTANG_LOW | R   | No           | 0x28, 0x29   | N/A              | 出力、y 軸角度変化、下位ワード                     |

| Y_DELTANG_OUT | R   | No           | 0x2A, 0x2B   | N/A              | 出力、y 軸角度変化、上位ワード                     |

| Z_DELTANG_LOW | R   | No           | 0x2C, 0x2D   | N/A              | 出力、z 軸角度変化、下位ワード                     |

| Z_DELTANG_OUT | R   | No           | 0x2E, 0x2F   | N/A              | 出力、z 軸角度変化、上位ワード                     |

| X_DELTVEL_LOW | R   | No           | 0x30, 0x31   | N/A              | 出力、x 軸速度変化、下位ワード                     |

| X_DELTVEL_OUT | R   | No           | 0x32, 0x33   | N/A              | 出力、x 軸速度変化、上位ワード                     |

| Y_DELTVEL_LOW | R   | No           | 0x34, 0x35   | N/A              | 出力、y 軸速度変化、下位ワード                     |

| Y_DELTVEL_OUT | R   | No           | 0x36, 0x37   | N/A              | 出力、y 軸速度変化、上位ワード                     |

| Z_DELTVEL_LOW | R   | No           | 0x38, 0x39   | N/A              | 出力、z 軸速度変化、下位ワード                     |

| Z_DELTVEL_OUT | R   | No           | 0x3A, 0x3B   | N/A              | 出力、z 軸速度変化、上位ワード                     |

| Reserved      | N/A | N/A          | 0x3C to 0x3F | N/A              | 予備                                   |

| XG_BIAS_LOW   | R/W | Yes          | 0x40, 0x41   | 0x0000           | キャリブレーション、オフセット、ジャイロ・センサー、x 軸、下位ワード  |

| XG_BIAS_HIGH  | R/W | Yes          | 0x42, 0x43   | 0x0000           | キャリブレーション、オフセット、ジャイロ・センサー、x 軸、上位ワード  |

| YG_BIAS_LOW   | R/W | Yes          | 0x44, 0x45   | 0x0000           | キャリブレーション、オフセット、ジャイロ・センサー、y 軸、下位ワード  |

| YG_BIAS_HIGH  | R/W | Yes          | 0x46, 0x47   | 0x0000           | キャリブレーション、オフセット、ジャイロ・センサー、y 軸、上位ワード  |

| ZG_BIAS_LOW   | R/W | Yes          | 0x48, 0x49   | 0x0000           | キャリブレーション、オフセット、ジャイロ・センサー、z 軸、下位ワード  |

| ZG_BIAS_HIGH  | R/W | Yes          | 0x4A, 0x4B   | 0x0000           | キャリブレーション、オフセット、ジャイロ・センサー、z 軸、上位ワード  |

| XA_BIAS_LOW   | R/W | Yes          | 0x4C, 0x4D   | 0x0000           | キャリブレーション、オフセット、加速度センサー、x 軸、下位ワード    |

| XA_BIAS_HIGH  | R/W | Yes          | 0x4E, 0x4F   | 0x0000           | キャリブレーション、オフセット、加速度センサー、x 軸、上位ワード    |

| YA_BIAS_LOW   | R/W | Yes          | 0x50, 0x51   | 0x0000           | キャリブレーション、オフセット、加速度センサー、y 軸、下位ワード    |

| YA_BIAS_HIGH  | R/W | Yes          | 0x52, 0x53   | 0x0000           | キャリブレーション、オフセット、加速度センサー、y 軸、上位ワード    |

| ZA_BIAS_LOW   | R/W | Yes          | 0x54, 0x55   | 0x0000           | キャリブレーション、オフセット、加速度センサー、z 軸、下位ワード    |

| ZA_BIAS_HIGH  | R/W | Yes          | 0x56, 0x57   | 0x0000           | キャリブレーション、オフセット、加速度センサー、z 軸、上位ワード    |

| Reserved      | N/A | N/A          | 0x58 to 0x5B | N/A              | 予備                                   |

| FILT_CTRL     | R/W | Yes          | 0x5C, 0x5D   | 0x0000           | 制御、パートレット・ウインドウ FIR (有限インパルス応答) フィルタ |

| RANG_MDL      | R   | No           | 0x5E, 0x5F   | N/A <sup>1</sup> | 測定範囲 (モデル固有) 識別子                     |

| MSC_CTRL      | R/W | Yes          | 0x60, 0x61   | 0x00C1           | 制御、入出力およびその他各種オプション                  |

| UP_SCALE      | R/W | Yes          | 0x62, 0x63   | 0x07D0           | 制御、入力クロックのスケール・ファクタ、パルス毎秒 (PPS) モード  |

| DEC_RATE      | R/W | Yes          | 0x64, 0x65   | 0x0000           | 制御、デシメーション・フィルタ (出力データ・レート)          |

| Name         | R/W | Flash Backup | Address      | Default | Register Description            |

|--------------|-----|--------------|--------------|---------|---------------------------------|

| NULL_CNFG    | R/W | Yes          | 0x66, 0x67   | 0x070A  | 制御、バイアス推定時間                     |

| GLOB_CMD     | W   | No           | 0x68, 0x69   | N/A     | 制御、グローバル・コマンド                   |

| Reserved     | N/A | N/A          | 0x6A to 0x6B | N/A     | 予備                              |

| FIRM_REV     | R   | No           | 0x6C, 0x6D   | N/A     | ID、ファームウェア・リビジョン                |

| FIRM_DM      | R   | No           | 0x6E, 0x6F   | N/A     | ID、日付コード、日および月                  |

| FIRM_Y       | R   | No           | 0x70, 0x71   | N/A     | ID、日付コード、年                      |

| PROD_ID      | R   | No           | 0x72, 0x73   | 0x4053  | ID、デバイス番号                       |

| SERIAL_NUM   | R   | No           | 0x74, 0x75   | N/A     | ID、シリアル番号                       |

| USER_SCR_1   | R/W | Yes          | 0x76, 0x77   | N/A     | ユーザ・スクラッチ・レジスタ 1                |

| USER_SCR_2   | R/W | Yes          | 0x78, 0x79   | N/A     | ユーザ・スクラッチ・レジスタ 2                |

| USER_SCR_3   | R/W | Yes          | 0x7A, 0x7B   | N/A     | ユーザ・スクラッチ・レジスタ 3                |

| FLSHCNT_LOW  | R   | No           | 0x7C, 0x7D   | N/A     | 出力、フラッシュ・メモリ書き込みサイクル・カウンタ、下位バイト |

| FLSHCNT_HIGH | R   | No           | 0x7E, 0x7E   | N/A     | 出力、フラッシュ・メモリ書き込みサイクル・カウンタ、上位バイト |

<sup>1</sup> このレジスタのデフォルト値（モデル固有）については、表 102 を参照してください。

## ユーザ・レジスタ定義

### ステータス／エラー・フラグ・インジケータ (DIAG\_STAT)

表 9. DIAG\_STAT のレジスタ定義

| Addresses  | Default | Access | Flash Backup |

|------------|---------|--------|--------------|

| 0x02, 0x03 | 0x0000  | R      | No           |

表 10. DIAG\_STAT のビット割り当て

| Bits   | Description                                                                                                                                                                                                                    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:8] | 予備                                                                                                                                                                                                                             |

| 7      | クロック・エラー。「1」は、内部データ・サンプリング・クロック (f <sub>SM</sub> 、図 12 および図 13 参照) が外部クロックと同期していないことを示します。これは、スケーリング同期モード (MSC_CTRL レジスタのビット [4:2] = 010、表 105 参照) を使用している場合にのみ適用されます。このエラーが発生した場合、適切な範囲内で動作するように SYNC ピンのクロック信号の周波数を調整してください。 |

| 6      | メモリ故障。「1」はフラッシュ・メモリ・テスト (GLOB_CMD レジスタのビット 4、表 113 参照) に失敗したことを示します。このテストには、現在のフラッシュ・メモリの巡回冗長検査 (CRC) の計算と同じメモリの場所の初期プログラミング時 (生成プロセス中) の CRC 計算との比較が含まれます。このエラーが発生した場合、同じテストを繰り返します。それでもエラーが続く場合は ADIS16467 を交換してください。        |

| 5      | センサー故障。「1」は、セルフ・テスト (GLOB_CMD レジスタのビット 2、表 113 参照) の結果、少なくとも 1 つのセンサーが故障していることを示します。このエラーが発生した場合、同じテストを繰り返します。それでもエラーが続く場合は ADIS16467 を交換してください。このテストの実行中にデバイスを動かすと、誤って故障と判定される場合があります。                                        |

| 4      | スタンバイ・モード。「1」は、VDD と GND 間の電圧が 2.8 V 未満であることを示します。これはデータ処理が停止する原因となります。VDD が 250 ms の間 2.8 V 以上を維持すると、ADIS16467 は再初期化され、再びデータ生成を開始します。                                                                                         |

| 3      | SPI 通信エラー。「1」は、SCLK サイクルの合計数が 16 の整数倍でないことを示します。このエラーが発生した場合、その前の通信シーケンスを繰り返します。それでもエラーが続く場合、ADIS16467 がサポートしているシステムからの SPI 信号が弱い可能性があります。                                                                                     |

| 2      | フラッシュ・メモリ更新の故障。「1」は、最後に行行ったフラッシュ・メモリの更新 (GLOB_CMD レジスタのビット 3、表 113 参照) が失敗したことを示します。このエラーが発生した場合、VDD が 3 V 以上であることを確認し、更新を繰り返してみます。それでもエラーが続く場合は ADIS16467 を交換してください。                                                          |

| 1      | データバス・オーバーラン。「1」は、データバスの 1 つがオーバーラン状態になっていることを示します。このエラーが発生した場合、RST ピン (表 5 のピン 8 参照) または GLOB_CMD レジスタのビット 7 (表 113 参照) を使用してリセットを開始します。                                                                                      |

| 0      | 予備                                                                                                                                                                                                                             |

DIAG\_STAT レジスタ (表 9 と表 10 を参照) には、ADIS16467 の完全性と動作を監視するためのエラー・フラグが用意されています。このレジスタの内容を読み出すと、レジスタの全ビットが 0 になります。DIAG\_STAT のエラー・フラグはステッキーです。すなわち、フラグが 1 になると、読み出し要求によってそのフラグがクリアされるまで 1 を維持します。エラー状態が続く場合は、そのフラグ (ビット) が自動的にアラーム値である 1 に戻ります。

### ジャイロ・センサーのデータ

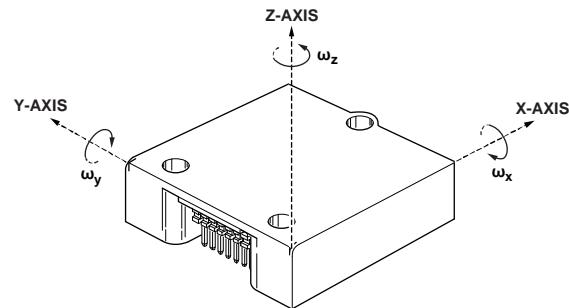

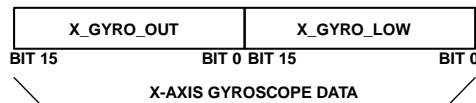

ADIS16467 のジャイロ・センサーは、3 本の直交軸 (x, y, z) 周りの回転角速度を測定します。ジャイロ・センサーの各軸の方向と、その各測定値が正の応答となる回転方向を図 29 に示します。

15439-029

図 29. ジャイロ・センサーの軸と極性の割り当て

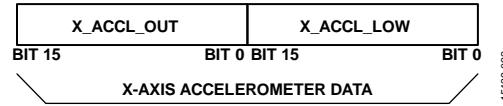

各ジャイロ・センサーには 2 つの出力データ・レジスタがあります。x 軸ジャイロ・センサー測定において、これら 2 つのレジスタを組み合わせて 32 ビットの 2 の補数データ・フォーマットを構成する方法を、図 30 に示します。このフォーマットは y 軸と z 軸にもあてはまります。

15439-030

図 30. ジャイロ・センサーの出力データ構造

### ジャイロ・センサーの測定範囲／スケール・ファクタ

表 11 に、ADIS16467 の各モデルにおける角速度 (ジャイロ・センサー) 測定の範囲とスケール・ファクタを示します。

表 11. ジャイロ・センサーの測定範囲とスケール・ファクタ

| Model           | Range, $\pm\omega_{MAX}$ (°/sec) | Scale Factor, $K_G$ (°/sec/LSB) |

|-----------------|----------------------------------|---------------------------------|

| ADIS16467-1BMLZ | $\pm 125$                        | 0.00625                         |

| ADIS16467-2BMLZ | $\pm 500$                        | 0.025                           |

| ADIS16467-3BMLZ | $\pm 2000$                       | 0.1                             |

### ジャイロ・センサーのデータ・フォーマット

16 ビットと 32 ビットの回転速度データのフォーマットを示すさまざまな数値の例を、表 12 と表 13 に示します。

表 12. 16 ビット・ジャイロ・センサー・データのフォーマット例

| Rotation Rate   | Decimal | Hex.   | Binary              |

|-----------------|---------|--------|---------------------|

| $+\omega_{MAX}$ | +20,000 | 0x4E20 | 0100 1110 0010 0000 |

| $+2 K_G$        | +2      | 0x0002 | 0000 0000 0000 0010 |

| $+K_G$          | +1      | 0x0001 | 0000 0000 0000 0001 |

| $0^{\circ}/sec$ | 0       | 0x0000 | 0000 0000 0000 0000 |

| $-K_G$          | -1      | 0xFFFF | 1111 1111 1111 1111 |

| $-2 K_G$        | -2      | 0xFFE  | 1111 1111 1111 1110 |

| $-\omega_{MAX}$ | -20,000 | 0xB1E0 | 1011 0001 1110 0000 |

表 13. 32 ピット・ジャイロ・センサー・データの

フォーマット例

| Rotation Rate (°/sec) | Decimal        | Hex.       |

|-----------------------|----------------|------------|

| + $\omega_{MAX}$      | +1,310,720,000 | 0x4E200000 |

| $+K_G/2^{15}$         | +2             | 0x00000002 |

| $+K_G/2^{16}$         | +1             | 0x00000001 |

| 0                     | 0              | 0x00000000 |

| $-K_G/2^{16}$         | -1             | 0xFFFFFFFF |

| $-K_G/2^{15}$         | -2             | 0xFFFFFFF0 |

| - $\omega_{MAX}$      | -1,310,720,000 | 0xB1E00000 |

### x 軸ジャイロ・センサー (X\_GYRO\_LOW および X\_GYRO\_OUT)

表 14. X\_GYRO\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x04, 0x05 | Not applicable | R      | No           |

表 15. X\_GYRO\_LOW のビット定義

| Bits   | Description               |

|--------|---------------------------|

| [15:0] | x 軸ジャイロ・センサー・データ、追加分解能ビット |

表 16. X\_GYRO\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x06, 0x07 | Not applicable | R      | No           |

表 17. X\_GYRO\_OUT のビット定義

| Bits   | Description                                                                   |

|--------|-------------------------------------------------------------------------------|

| [15:0] | x 軸ジャイロ・センサー・データ、上位ワード、2 の補数、0°/sec = 0x0000、1 LSB = $K_G$ (表 11 の $K_G$ を参照) |

X\_GYRO\_LOW レジスタ (表 14 と表 15 を参照) と X\_GYRO\_OUT レジスタ (表 16 と表 17 を参照) には、x 軸のジャイロ・センサー・データが格納されます。

### y 軸ジャイロ・センサー (Y\_GYRO\_LOW および Y\_GYRO\_OUT)

表 18. Y\_GYRO\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x08, 0x09 | Not applicable | R      | No           |

表 19. Y\_GYRO\_LOW のビット定義

| Bits   | Description               |

|--------|---------------------------|

| [15:0] | y 軸ジャイロ・センサー・データ、追加分解能ビット |

表 20. Y\_GYRO\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x0A, 0x0B | Not applicable | R      | No           |

表 21. Y\_GYRO\_OUT のビット定義

| Bits   | Description                                                                   |

|--------|-------------------------------------------------------------------------------|

| [15:0] | y 軸ジャイロ・センサー・データ、上位ワード、2 の補数、0°/sec = 0x0000、1 LSB = $K_G$ (表 11 の $K_G$ を参照) |

Y\_GYRO\_LOW レジスタ (表 18 と表 19 を参照) と Y\_GYRO\_OUT レジスタ (表 20 と表 21 を参照) には、y 軸のジャイロ・センサー・データが格納されます。

### z 軸ジャイロ・センサー (Z\_GYRO\_LOW および Z\_GYRO\_OUT)

表 22. Z\_GYRO\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x0C, 0x0D | Not applicable | R      | No           |

表 23. Z\_GYRO\_LOW のビット定義

| Bits   | Description               |

|--------|---------------------------|

| [15:0] | z 軸ジャイロ・センサー・データ、追加分解能ビット |

表 24. Z\_GYRO\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x0E, 0x0F | Not applicable | R      | No           |

表 25. Z\_GYRO\_OUT のビット定義

| Bits   | Description                                                                   |

|--------|-------------------------------------------------------------------------------|

| [15:0] | z 軸ジャイロ・センサー・データ、上位ワード、2 の補数、0°/sec = 0x0000、1 LSB = $K_G$ (表 11 の $K_G$ を参照) |

Z\_GYRO\_LOW レジスタ (表 22 と表 23 を参照) と Z\_GYRO\_OUT レジスタ (表 24 と表 25 を参照) には、z 軸のジャイロ・センサー・データが格納されます。

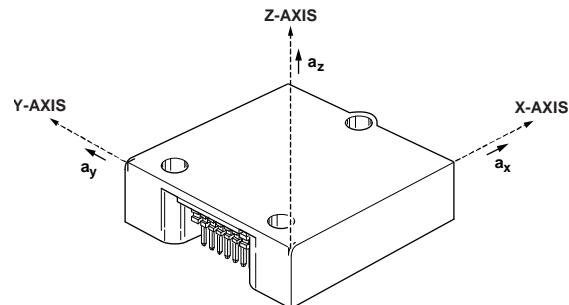

### 加速度データ

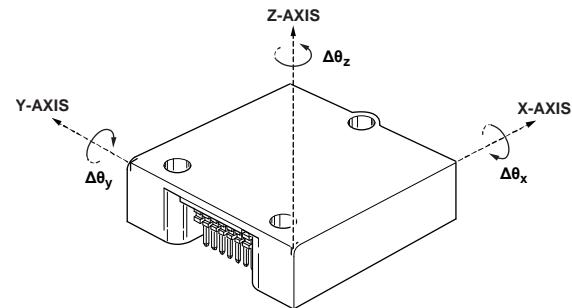

ADIS16467 の加速度センサーは、ジャイロ・センサーの回転軸 (x, y, z) と同じ定義の 3 本の直交軸に沿った動的加速度と静的加速度 (重力に対する応答) の両方を測定します。加速度センサーの各軸の方向と、その各測定値が正の応答となる加速度方向を図 31 に示します。

図 31. 加速度センサーの軸と極性の割り当て

各加速度センサーには 2 つの出力データ・レジスタがあります。x 軸加速度センサー測定において、これら 2 つのレジスタを組み合わせて 32 ビットの 2 の補数のデータ・フォーマットを構成する方法を、図 32 に示します。このフォーマットは y 軸と z 軸にもあてはまります。

図 32. 加速度センサーの出力データ構造

## 加速度センサーの分解能

16 ビットと 32 ビットの直線加速度データのフォーマットを示すさまざまな数値の例を、表 26 と表 27 に示します。

表 26. 16 ビット加速度センサー・データのフォーマット例

| Acceleration | Decimal | Hex.   | Binary              |

|--------------|---------|--------|---------------------|

| +40 g        | +32,000 | 0x7D00 | 0111 1101 0000 0000 |

| +2.5 mg      | +2      | 0x0002 | 0000 0000 0000 0010 |

| +1.25 mg     | +1      | 0x0001 | 0000 0000 0000 0001 |

| 0 mg         | 0       | 0x0000 | 0000 0000 0000 0000 |

| -1.25 mg     | -1      | 0xFFFF | 1111 1111 1111 1111 |

| -2.5 mg      | -2      | 0xFFFE | 1111 1111 1111 1110 |

| -40 g        | -32,000 | 0x8300 | 1000 0011 0000 0000 |

表 27. 32 ビット加速度センサー・データのフォーマット例

| Acceleration             | Decimal        | Hex.       |

|--------------------------|----------------|------------|

| +40 g                    | +2,097,152,000 | 0x7D000000 |

| +1.25/2 <sup>15</sup> mg | +2             | 0x00000002 |

| +1.25/2 <sup>16</sup> mg | +1             | 0x00000001 |

| 0                        | 0              | 0x00000000 |

| -1.25/2 <sup>16</sup> mg | -1             | 0xFFFFFFFF |

| -1.25/2 <sup>15</sup> mg | -2             | 0xFFFFFFF  |

| -40 g                    | -2,097,152,000 | 0x83000000 |

## x 軸加速度センサー (X\_ACCL\_LOW および X\_ACCL\_OUT)

表 28. X\_ACCL\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x10, 0x11 | Not applicable | R      | No           |

表 29. X\_ACCL\_LOW のビット定義

| Bits   | Description             |

|--------|-------------------------|

| [15:0] | x 軸加速度センサー・データ、追加分解能ビット |

表 30. X\_ACCL\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x12, 0x13 | Not applicable | R      | No           |

表 31. X\_ACCL\_OUT のビット定義

| Bits   | Description                                                      |

|--------|------------------------------------------------------------------|

| [15:0] | X 軸加速度センサー・データ、上位ワード、2 の補数、範囲 ±40 g、0 g = 0x0000、1 LSB = 1.25 mg |

X\_ACCL\_LOW レジスタ（表 28 と表 29 を参照）と X\_ACCL\_OUT レジスタ（表 30 と表 31 を参照）には、x 軸の加速度センサー・データが格納されます。

## y 軸加速度センサー (Y\_ACCL\_LOW および Y\_ACCL\_OUT)

表 32. Y\_ACCL\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x14, 0x15 | Not applicable | R      | No           |

表 33. Y\_ACCL\_LOW のビット定義

| Bits   | Description             |

|--------|-------------------------|

| [15:0] | y 軸加速度センサー・データ、追加分解能ビット |

表 34. Y\_ACCL\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x16, 0x17 | Not applicable | R      | No           |

表 35. Y\_ACCL\_OUT のビット定義

| Bits   | Description                                                      |

|--------|------------------------------------------------------------------|

| [15:0] | Y 軸加速度センサー・データ、上位ワード、2 の補数、範囲 ±40 g、0 g = 0x0000、1 LSB = 1.25 mg |

Y\_ACCL\_LOW レジスタ（表 32 と表 33 を参照）と Y\_ACCL\_OUT レジスタ（表 34 と表 35 を参照）には、y 軸の加速度センサー・データが格納されます。

## z 軸加速度センサー (Z\_ACCL\_LOW および Z\_ACCL\_OUT)

表 36. Z\_ACCL\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x18, 0x19 | Not applicable | R      | No           |

表 37. Z\_ACCL\_LOW のビット定義

| Bits   | Description             |

|--------|-------------------------|

| [15:0] | z 軸加速度センサー・データ、追加分解能ビット |

表 38. Z\_ACCL\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x1A, 0x1B | Not applicable | R      | No           |

表 39. Z\_ACCL\_OUT のビット定義

| Bits   | Description                                                      |

|--------|------------------------------------------------------------------|

| [15:0] | Z 軸加速度センサー・データ、上位ワード、2 の補数、範囲 ±40 g、0 g = 0x0000、1 LSB = 1.25 mg |

Z\_ACCL\_LOW レジスタ（表 36 と表 37 を参照）と Z\_ACCL\_OUT レジスタ（表 38 と表 39 を参照）には、z 軸の加速度センサー・データが格納されます。

## 内部温度 (TEMP\_OUT)

表 40. TEMP\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x1C, 0x1D | Not applicable | R      | No           |

表 41. TEMP\_OUT のビット定義

| Bits   | Description                              |

|--------|------------------------------------------|

| [15:0] | 温度データ、2 の補数、1 LSB = 0.1 °C、0 °C = 0x0000 |

TEMP\_OUT レジスタ（表 40 と表 41 を参照）には、ADIS16467 の内部温度の大まかな測定値がセットされています。このデータは、温度環境の相対的な変化を監視するのにきわめて有効です。

表 42. TEMP\_OUT のデータ・フォーマット例

| Temperature (°C) | Decimal | Hex.   | Binary              |

|------------------|---------|--------|---------------------|

| +105             | +1050   | 0x041A | 0000 0100 0001 1010 |

| +25              | +250    | 0x00FA | 0000 0000 1111 1010 |

| +0.2             | +2      | 0x0002 | 0000 0000 0000 0010 |

| +0.1             | +1      | 0x0001 | 0000 0000 0000 0001 |

| +0               | 0       | 0x0000 | 0000 0000 0000 0000 |

| +0.1             | -1      | 0xFFFF | 1111 1111 1111 1111 |

| +0.2             | -2      | 0xFFFE | 1111 1111 1111 1110 |

| -40              | -400    | 0xFE70 | 1111 1110 0111 0000 |

## タイム・スタンプ (TIME\_STAMP)

表 43. TIME\_STAMP のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x1E, 0x1F | Not applicable | R      | No           |

表 44. TIME\_STAMP のビット定義

| Bits   | Description                                            |

|--------|--------------------------------------------------------|

| [15:0] | SYNC ピンの最後のパルスからの時間、オフセット・バイナリ・フォーマット、1 LSB = 49.02 μs |

TIME\_STAMP レジスタ（表 43 と表 44 を参照）は、スケーリング同期モード（MSC\_CTRL レジスタのビット [4:2] = 010、表 105 参照）とともに機能します。TIME\_STAMP の 16 ビット数には、SYNC ピンのクロック信号の最後のエッジに関連する各データ更新において、最新のサンプルに関連付けられる時間が格納されます。例えば、UP\_SCALE レジスタ（表 107 参照）の値がスケール・ファクタ 20 を示し、DEC\_RATE = 0、外部 SYNC レート = 100 Hz である場合、タイム・スタンプ・シーケンスは、0 LSB、10 LSB、21 LSB、31 LSB、41 LSB、51 LSB、61 LSB、72 LSB、…、と続き、20 番目のサンプルは、194 LSB となります。つまり、最初の SYNC エッジからの時間は、0 μs、490 μs、…、9510 μs となります。

## データ更新カウンタ (DATA\_CNTR)

表 45. DATA\_CNTR のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x22, 0x23 | Not applicable | R      | No           |

表 46. DATA\_CNTR のビット定義

| Bits   | Description                 |

|--------|-----------------------------|

| [15:0] | データ更新カウンタ、オフセット・バイナリ・フォーマット |

ADIS16467 がパワー・オン・シーケンスにある場合、またはリセット・コマンドからの復帰状態にある場合、DATA\_CNTR（表 45 と表 46 を参照）は、0x0000 の値から始まり、出力レジスタに新たなデータがロードされるたびにインクリメントします。DATA\_CNTR の値が 0xFFFF に達した場合、次のデータ更新で 0x0000 に戻り、引き続き出力レジスタに新たなデータがロードされるたびにインクリメントします。

## 角度変化

各軸（x、y、z）周りの回転角速度（ジャイロ・センサー）の測定値に加えて、ADIS16467 は角度変化の測定も出力します。これはサンプル更新ごとの角度変位を計算したものです。

図 33. 角度変化の軸と極性割り当て

角度変化出力はジャイロ・センサー測定値の積分値を表し、3 つ の軸すべてについて以下の式を使用します（x 軸について例示）。

$$\Delta\theta_{x,nD} = \frac{1}{2 \times f_S} \times \sum_{d=0}^{D-1} (\omega_{x,nD+d} + \omega_{x,nD+d-1})$$

ここで

x は x 軸、

n はデシメーション・フィルタ前のサンプル時間、

D はデシメーション・レート（DEC\_RATE + 1、表 109 参照）、

f<sub>S</sub> はサンプル・レート、

d は総和公式の増分変数、

ω<sub>x</sub> は x 軸回りの回転速度（ジャイロ・センサー）です。

内部サンプル・クロックを使用する場合、f<sub>S</sub> の公称値は 2000 SPS です。この測定をより高精度に行うためには、DR ピンのデータ・レディ信号を使用して内部サンプル・レート（f<sub>S</sub>）を測定し（DEC\_RATE = 0x0000、表 108 参照）、このデータ・レディ周波数で（角度変化出力レジスタからの）角度変化結果を除し、それに 2000 を乗じます。角度変化測定時は、各軸につき 2 つの出力データ・レジスタを使用します。x 軸の角度変化測定において、これら 2 つのレジスタを組み合わせて 32 ビットの 2 の補数データ・フォーマットを構成する方法を、図 34 に示します。このフォーマットは y 軸と z 軸にもあてはまります。

図 34. 角度変化出力のデータ構造

## 角度変化の測定範囲

表 47 に、ADIS16467 の各モデルの測定範囲とスケール・ファクタを示します。

表 47. 角度変化の測定範囲とスケール・ファクタ

| Model           | Measurement Range, ±Δθ <sub>MAX</sub> (°) |

|-----------------|-------------------------------------------|

| ADIS16467-1BMLZ | ±360                                      |

| ADIS16467-2BMLZ | ±720                                      |

| ADIS16467-3BMLZ | ±2160                                     |

## x 軸角度変化 (X\_DELTANG\_LOW および X\_DELTANG\_OUT)

表 48. X\_DELTANG\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x24, 0x25 | Not applicable | R      | No           |

表 49. X\_DELTANG\_LOW のビット定義

| Bits   | Description      |

|--------|------------------|

| [15:0] | x 軸角度変化データ、下位ワード |

表 50. X\_DELTANG\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x26, 0x27 | Not applicable | R      | No           |

表 51. X\_DELTANG\_OUT のビット定義

| Bits   | Description                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------|

| [15:0] | x 軸角度変化データ、2 の補数、 $0^\circ = 0x0000$ 、1 LSB = $\Delta\theta_{MAX}/2^{15}$ ( $\Delta\theta_{MAX}$ については表 47 参照) |

X\_DELTANG\_LOW レジスタ（表 48 と表 49 を参照）と X\_DELTANG\_OUT レジスタ（表 50 と表 51 を参照）には、x 軸の角度変化データが格納されます。

## y 軸角度変化 (Y\_DELTANG\_LOW および Y\_DELTANG\_OUT)

表 52. Y\_DELTANG\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x28, 0x29 | Not applicable | R      | No           |

表 53. Y\_DELTANG\_LOW のビット定義

| Bits   | Description      |

|--------|------------------|

| [15:0] | y 軸角度変化データ、下位ワード |

表 54. Y\_DELTANG\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x2A, 0x2B | Not applicable | R      | No           |

表 55. Y\_DELTANG\_OUT のビット定義

| Bits   | Description                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------|

| [15:0] | y 軸角度変化データ、2 の補数、 $0^\circ = 0x0000$ 、1 LSB = $\Delta\theta_{MAX}/2^{15}$ ( $\Delta\theta_{MAX}$ については表 47 参照) |

Y\_DELTANG\_LOW レジスタ（表 52 と表 53 を参照）と Y\_DELTANG\_OUT レジスタ（表 54 と表 55 を参照）には、y 軸の角度変化データが格納されます。

## z 軸角度変化 (Z\_DELTANG\_LOW および Z\_DELTANG\_OUT)

表 56. Z\_DELTANG\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x2C, 0x2D | Not applicable | R      | No           |

表 57. Z\_DELTANG\_LOW のビット定義

| Bits   | Description      |

|--------|------------------|

| [15:0] | z 軸角度変化データ、下位ワード |

表 58. Z\_DELTANG\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x2E, 0x2F | Not applicable | R      | No           |

表 59. Z\_DELTANG\_OUT のビット定義

| Bits   | Description                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------|

| [15:0] | z 軸角度変化データ、2 の補数、 $0^\circ = 0x0000$ 、1 LSB = $\Delta\theta_{MAX}/2^{15}$ ( $\Delta\theta_{MAX}$ については表 47 参照) |

Z\_DELTANG\_LOW レジスタ（表 56 と表 57 を参照）と Z\_DELTANG\_OUT レジスタ（表 58 と表 59 を参照）には、z 軸の角度変化データが格納されます。

## 角度変化の分解能

16 ビットと 32 ビットの角度変化データのフォーマットを示すさまざまな数値の例を、表 60 と表 61 に示します。

表 60. 16 ビット角度変化データのフォーマット例

| Delta Angle (°)                               | Decimal | Hex.    | Binary              |

|-----------------------------------------------|---------|---------|---------------------|

| $\Delta\theta_{MAX} \times (2^{15}-1)/2^{15}$ | +32,767 | 0x7FFF  | 0111 1111 1110 1111 |

| $+\Delta\theta_{MAX}/2^{14}$                  | +2      | 0x0002  | 0000 0000 0000 0010 |

| $+\Delta\theta_{MAX}/2^{15}$                  | +1      | 0x0001  | 0000 0000 0000 0001 |

| 0                                             | 0       | 0x0000  | 0000 0000 0000 0000 |

| $-\Delta\theta_{MAX}/2^{15}$                  | -1      | 0xFFFF  | 1111 1111 1111 1111 |

| $-\Delta\theta_{MAX}/2^{14}$                  | -2      | 0xFFFFE | 1111 1111 1111 1110 |

| $-\Delta\theta_{MAX}$                         | -32,768 | 0x8000  | 1000 0000 0000 0000 |

表 61. 32 ビット角度変化データのフォーマット例

| Delta Angle (°)                                | Decimal        | Hex.       |

|------------------------------------------------|----------------|------------|

| $+\Delta\theta_{MAX} \times (2^{31}-1)/2^{31}$ | +2,147,483,647 | 0x7FFFFFFF |

| $+\Delta\theta_{MAX}/2^{30}$                   | +2             | 0x00000002 |

| $+\Delta\theta_{MAX}/2^{31}$                   | +1             | 0x00000001 |

| 0                                              | 0              | 0x00000000 |

| $-\Delta\theta_{MAX}/2^{31}$                   | -1             | 0xFFFFFFFF |

| $-\Delta\theta_{MAX}/2^{30}$                   | -2             | 0xFFFFFFF  |

| $-\Delta\theta_{MAX}$                          | -2,147,483,648 | 0x80000000 |

## 速度変化

各軸 (x、y、z) に沿った直線加速度の測定値に加えて、ADIS16467 はサンプル更新ごとの直線速度測定値の変化も計算します。

図 35. 速度変化の軸と極性割り当て

15x35-035

速度変化出力は加速度測定値の積分値を表し、3つの軸すべてについて以下の式を使用します（x軸について例示）。

$$\Delta V_{x,nD} = \frac{1}{2 \times f_S} \times \sum_{d=0}^{D-1} (a_{x,nD+d} + a_{x,nD+d-1})$$

ここで

xはx軸、

nはデシメーション・フィルタ前のサンプル時間、

Dはデシメーション・レート（DEC\_RATE + 1、表 109 参照）、

$f_S$ はサンプル・レート、

dは総和公式の増分変数、

$a_x$ はx軸加速度です。

内部サンプル・クロックを使用する場合、 $f_S$ の公称値は 2000 SPS です。この測定をより高精度に行うためには、DR ピンのデータ・レディ信号を使用して内部サンプル・レート ( $f_S$ ) を測定し (DEC\_RATE = 0x0000、表 108 参照)、このデータ・レディ周波数で（角度変化出力レジスタからの）角度変化結果を除し、それに 2000 を乗じます。速度変化測定期時は、各軸につき 2つの出力データ・レジスタを使用します。x軸の速度変化測定において、これら 2つのレジスタを組み合わせて 32 ビットの 2 の補数データ・フォーマットを構成する方法を、図 36 に示します。このフォーマットは y 軸と z 軸にもあてはまります。

図 36. 速度変化出力のデータ構造

## x軸速度変化（X\_DELTA\_VEL\_LOW および X\_DELTA\_VEL\_OUT）

表 62. X\_DELTA\_VEL\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x30, 0x31 | Not applicable | R      | No           |

表 63. X\_DELTA\_VEL\_LOW のビット定義

| Bits   | Description       |

|--------|-------------------|

| [15:0] | x軸速度変化データ、追加分能ビット |

表 64. X\_DELTA\_VEL\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x32, 0x33 | Not applicable | R      | No           |

表 65. X\_DELTA\_VEL\_OUT のビット定義

| Bits   | Description                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------|

| [15:0] | x軸速度変化データ、2の補数、範囲 ±400 m/sec、0 m/sec = 0x0000、1 LSB = 400 m/sec ÷ 2 <sup>15</sup> = 約 0.01221 m/sec |

X\_DELTA\_VEL\_LOW レジスタ（表 62 と表 63 を参照）と X\_DELTA\_VEL\_OUT レジスタ（表 64 と表 65 を参照）には、x軸の速度変化データが格納されます。

## y軸速度変化（Y\_DELTA\_VEL\_LOW および Y\_DELTA\_VEL\_OUT）

表 66. Y\_DELTA\_VEL\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x34, 0x35 | Not applicable | R      | No           |

表 67. Y\_DELTA\_VEL\_LOW のビット定義

| Bits   | Description       |

|--------|-------------------|

| [15:0] | y軸速度変化データ、追加分能ビット |

表 68. Y\_DELTA\_VEL\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x36, 0x37 | Not applicable | R      | No           |

表 69. Y\_DELTA\_VEL\_OUT のビット定義

| Bits   | Description                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------|

| [15:0] | y軸速度変化データ、2の補数、範囲 ±400 m/sec、0 m/sec = 0x0000、1 LSB = 400 m/sec ÷ 2 <sup>15</sup> = 約 0.01221 m/sec |

Y\_DELTA\_VEL\_LOW レジスタ（表 66 と表 67 を参照）と Y\_DELTA\_VEL\_OUT レジスタ（表 68 と表 69 を参照）には、y軸の速度変化データが格納されます。

## z軸速度変化（Z\_DELTA\_VEL\_LOW および Z\_DELTA\_VEL\_OUT）

表 70. Z\_DELTA\_VEL\_LOW のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x38, 0x39 | Not applicable | R      | No           |

表 71. Z\_DELTA\_VEL\_LOW のビット定義

| Bits   | Description       |

|--------|-------------------|

| [15:0] | z軸速度変化データ、追加分能ビット |

表 72. Z\_DELTA\_VEL\_OUT のレジスタ定義

| Addresses  | Default        | Access | Flash Backup |

|------------|----------------|--------|--------------|

| 0x3A, 0x3B | Not applicable | R      | No           |

表 73. Z\_DELTA\_VEL\_OUT のビット定義

| Bits   | Description                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------|

| [15:0] | z軸速度変化データ、2の補数、範囲 ±400 m/sec、0 m/sec = 0x0000、1 LSB = 400 m/sec ÷ 2 <sup>15</sup> = 約 0.01221 m/sec |

Z\_DELTA\_VEL\_LOW レジスタ（表 70 と表 71 を参照）と Z\_DELTA\_VEL\_OUT レジスタ（表 72 と表 73 を参照）には、z軸の速度変化データが格納されます。

## 速度変化の分解能

16 ビットと 32 ビットの速度変化データのフォーマットを示すさまざまな数値の例を、表 74 と表 75 に示します。

表 74. 16 ビット速度変化データのフォーマット例

| Velocity (m/sec)                  | Decimal | Hex.    | Binary              |

|-----------------------------------|---------|---------|---------------------|

| $+400 \times (2^{15} - 1)/2^{15}$ | +32,767 | 0x7FFF  | 0111 1111 1111 1111 |

| $+400/2^{14}$                     | +2      | 0x0002  | 0000 0000 0000 0010 |

| $+400/2^{15}$                     | +1      | 0x0001  | 0000 0000 0000 0001 |

| 0                                 | 0       | 0x0000  | 0000 0000 0000 0000 |

| $-400/2^{15}$                     | -1      | 0xFFFFF | 1111 1111 1111 1111 |

| $-400/2^{14}$                     | -2      | 0xFFFFE | 1111 1111 1111 1110 |

| -400                              | -32,768 | 0x8000  | 1000 0000 0000 0000 |

表 75. 32 ビット速度変化データのフォーマット例

| Velocity (m/sec)                  | Decimal        | Hex.       |

|-----------------------------------|----------------|------------|

| $+400 \times (2^{31} - 1)/2^{31}$ | +2,147,483,647 | 0x7FFFFFFF |

| $+400/2^{30}$                     | +2             | 0x00000002 |

| $+400/2^{31}$                     | +1             | 0x00000001 |

| 0                                 | 0              | 0x00000000 |

| $-400/2^{31}$                     | -1             | 0xFFFFFFFF |

| $-400/2^{30}$                     | -2             | 0xFFFFFFF  |

| -400                              | +2,147,483,648 | 0x80000000 |

## キャリブレーション

各慣性センサー（加速度センサーとジャイロ・センサー）のシグナル・チェーンには固有の補正式が使われていますが、これらの式は、-40 °C ~ +85 °C の温度範囲で個々の ADIS16467 に対し、バイアス、感度、アライメント、直線加速度に対する応答（ジャイロ・センサー）、振動ポイント（加速センサーの位置）など広範な特性評価を行うことによって得られたものです。これらの補正式自体にはアクセスできませんが、ユーザ・アクセス可能なレジスタを通じて、各センサーのバイアスを個別に調整することができます。これらの補正係数は、工場で導出されたシグナル・チェーンの補正式にそのまま従っており、内部サンプル・クロック使用時には 2000 Hz のレートで処理を行います。

## キャリブレーション、ジャイロ・センサーのバイアス（XG\_BIAS\_LOW および XG\_BIAS\_HIGH）

表 76. XG\_BIAS\_LOW のレジスタ定義

| Addresses  | Default | Access | Flash Backup |

|------------|---------|--------|--------------|

| 0x40, 0x41 | 0x0000  | R/W    | Yes          |

表 77. XG\_BIAS\_LOW のビット定義

| Bits   | Description                |

|--------|----------------------------|

| [15:0] | x 軸ジャイロ・センサーのオフセット補正、下位ワード |

表 78. XG\_BIAS\_HIGH のレジスタ定義

| Addresses  | Default | Access | Flash Backup |

|------------|---------|--------|--------------|

| 0x42, 0x43 | 0x0000  | R/W    | Yes          |

表 79. XG\_BIAS\_HIGH のビット定義

| Bits   | Description                  |

|--------|------------------------------|

| [15:0] | x 軸ジャイロ・センサーのオフセット補正係数、上位ワード |

XG\_BIAS\_LOW レジスタ（表 76 と表 77 を参照）と XG\_BIAS\_HIGH レジスタ（表 78 と表 79 を参照）を組み合わせると、x 軸ジャイロ・センサーのバイアスを調整できます。表 12 のデータ・フォーマット例は XG\_BIAS\_HIGH レジスタにも適用され、表 13 のデータ・フォーマット例は、XG\_BIAS\_LOW レジスタと XG\_BIAS\_HIGH レジスタを組み合わせて得られる 32 ビット数に適用されます。これら 2 つのレジスタの組み合わせ方法と x 軸ジャイロ・センサー測定への影響については、図 37 を参照してください。

15439-037

図 37. ジャイロ・センサーのユーザ・キャリブレーション信号バス

## キャリブレーション、ジャイロ・センサーのバイアス（YG\_BIAS\_LOW および YG\_BIAS\_HIGH）

表 80. YG\_BIAS\_LOW のレジスタ定義

| Addresses  | Default | Access | Flash Backup |

|------------|---------|--------|--------------|

| 0x44, 0x45 | 0x0000  | R/W    | Yes          |

表 81. YG\_BIAS\_LOW のビット定義

| Bits   | Description                |

|--------|----------------------------|

| [15:0] | y 軸ジャイロ・センサーのオフセット補正、下位ワード |

表 82. YG\_BIAS\_HIGH のレジスタ定義

| Addresses  | Default | Access | Flash Backup |

|------------|---------|--------|--------------|

| 0x46, 0x47 | 0x0000  | R/W    | Yes          |

表 83. YG\_BIAS\_HIGH のビット定義

| Bits   | Description                  |

|--------|------------------------------|

| [15:0] | y 軸ジャイロ・センサーのオフセット補正係数、上位ワード |

YG\_BIAS\_LOW レジスタ（表 80 と表 81 を参照）と YG\_BIAS\_HIGH レジスタ（表 82 と表 83 を参照）を組み合わせると、y 軸ジャイロ・センサーのバイアスを調整できます。表 12 のデータ・フォーマット例は YG\_BIAS\_HIGH レジスタにも適用され、表 13 のデータ・フォーマット例は、YG\_BIAS\_LOW レジスタと YG\_BIAS\_HIGH レジスタを組み合わせて得られる 32 ビット数に適用されます。このレジスタは、XG\_BIAS\_LOW レジスタと XG\_BIAS\_HIGH レジスタが x 軸のジャイロ・センサー測定値に影響を与えるのと同様に、y 軸のジャイロ・センサー測定値に影響を与えます（図 37 参照）。

## キャリブレーション、ジャイロ・センサーのバイアス（ZG\_BIAS\_LOW および ZG\_BIAS\_HIGH）