# 堅牢で低消費電力の産業用 10BASE-T1L イーサネット MAC-PHY

#### 特長

- ▶ 10BASE-T1L IEEE 802.3cg-2019 規格に準拠

- ▶ 1.0V/2.4V で最長 1700m のケーブル長に対応

- ▶ SPI を備えた MAC を内蔵

- ▶ OPEN Alliance 10BASE-T1x MAC-PHY シリアル・イン ターフェースに対応

- ▶ 16個のMACアドレス・フィルタ

- ▶ 28kBのバッファで高優先度キューおよび低優先度 キューに対応

- ▶ カット・スルーまたはストア・アンド・フォワード動作

- ▶ IEEE 1588 のタイム・スタンプに対応

- ▶ 統計カウンタ

- ▶ 低消費電力:単電源 50mW

- 診断機能

- ▶ TDR によるケーブル・フォルト検出

- ▶ MSE によるリンク品質インジケータ

- ▶ フレーム・ジェネレータおよびフレーム・チェッカ

- ▶ 複数のループバック・モード

- ▶ IEEE テスト・モードに対応

- ▶ 1.0V p-p および 2.4V p-p の送信レベルに対応

- ▶ MDIの極性検出および補正

- ▶ 2ピンMDI

- ▶ 内部終端抵抗およびハイブリッド

- オート・ネゴシエーション

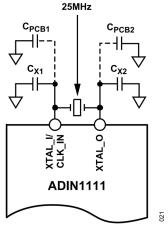

- ▶ 25MHzの水晶発振器または外部クロック入力

- ▶ EMC 試験規格

- ▶ IEC 61000-4-4 電気高速トランジェント(EFT) (±4kV)

- ▶ IEC 61000-4-2 ESD (±4kV の接触放電)

- ▶ IEC 61000-4-2 ESD (±8kV の気中放電)

- ▶ IEC 61000-4-6 伝導耐性(10V/m)

- ▶ IEC 61000-4-5 サージ(±4kV)

- ▶ IEC 61000-4-3 放射耐性(クラス A)

- ▶ EN 55032 放射エミッション (クラス B)

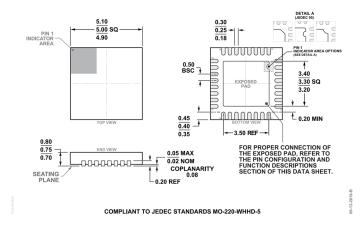

- ▶ 小型パッケージ: 32 ピン (5mm × 5mm) LFCSP

- ▶ 温度範囲

- ▶ 産業用:-40°C~+85°C

- ▶ 拡張: -40°C~+105°C

#### アプリケーション

- ▶ ビルディング・オートメーションおよび火災安全

- ▶ ファクトリ・オートメーション

- ▶ 状態監視および機械接続

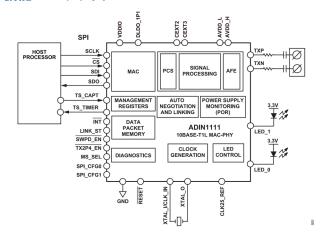

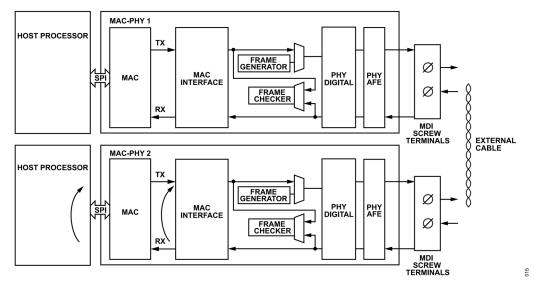

# 機能ブロック図

図 1. 機能ブロック図

# 概要

ADIN1111は、産業用イーサネット・アプリケーション向けに設計された超低消費電力で単一ポートの 10BASE-T1L トランシーバであり、長距離伝送用の10Mbpsシングル・ペア・イーサネット(SPE)に対するIEEE® 802.3cg-2019<sup>TM</sup>イーサネット規格に対応しています。メディア・アクセス制御(MAC)インターフェースを内蔵した ADIN1111 は、シリアル・ペリフェラル・インターフェース(SPI)を介して、様々なホスト・コントローラと直接接続できます。この SPI により、MAC を内蔵していない低消費電力のプロセッサを使用できるため、システム・レベルの総合的な消費電力を最小限に抑えることができます。ADIN1111は、ビルや工場内、そしてプロセス・オートメーション用に展開されるエッジ・ノード・センサーやフィールド計測器向けに設計されています。

デバイスは、1.8V または3.3V の単電源レールで動作し、1.0V と 2.4V のどちらにも対応できます。内蔵のハイブリッドおよび終端抵抗により、ADIN1111 は MDI インターフェースに直接接続できます。

ADIN1111 には電圧源モニタリング回路およびパワーオン・リセット (POR) 回路が内蔵されており、システム・レベルの堅牢性を高めています。また、MAC インターフェースとホスト・プロセッサとの間で通信を行うための 4 線式 SPI を備えています。

ADIN1111 は、 $5mm \times 5mm$  の 32 ピン・リード・フレーム・チップ・スケール・パッケージ [LFCSP] を採用しています。

#### ※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

# 目次

| 特長                  | 1 |

|---------------------|---|

| アプリケーション            | 1 |

| 機能ブロック図             | 1 |

| 概要                  | 1 |

| 仕様                  | 3 |

| タイミング特性             | 5 |

| パワーアップ・タイミング        | 5 |

| SPI                 | 5 |

| 絶対最大定格              | 7 |

| 熱抵抗                 | 7 |

| 静電放電 (ESD) 定格       | 7 |

| ESD に関する注意          | 7 |

| ピン配置およびピン機能の説明      | 8 |

| 代表的な性能特性10          | 0 |

| 動作原理1               | 1 |

| 電源ドメイン1             | 1 |

| アナログ・フロント・エンド1      | 1 |

| MAC1                | 1 |

| 送信振幅の設定1            | 1 |

| リーダー/フォロア設定1        | 1 |

| オート・ネゴシエーション12      | 2 |

| MDI 回路12            | 2 |

| リセット動作1:            | 3 |

| LED 機能14            | 4 |

| リンク・ステータス・ピン1:      | 5 |

| パワーダウン・モード1:        | 5 |

| ハードウェア設定ピン10        | 6 |

| ハードウェア設定ピンの機能10     | 6 |

| 10BASE-T1L リンクの確立15 | 8 |

| アンマネージド PHY 動作15    | 8 |

| マネージド PHY 動作           | 18  |

|------------------------|-----|

| オン・チップ診断               | 21  |

| ループバック・モード             | 21  |

| フレーム・ジェネレータとフレーム・チェッカ  | 22  |

| テスト・モード                | 23  |

| 時間領域反射率測定(TDR)         | 23  |

| リンク品質モニタリング            | 24  |

| アプリケーション情報             | 28  |

| システム・レベルのパワー・マネージメント   | 28  |

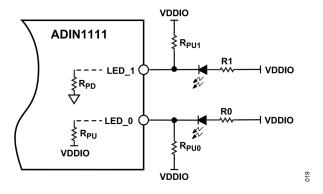

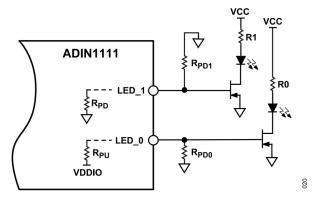

| LED 回路例                | 28  |

| 部品の推奨事項                | 29  |

| 802.1 AS 対応            | 30  |

| 電磁環境適合性(EMC)と電磁耐性(EMI) | 31  |

| MAC SPI                | 32  |

| SPI                    | 32  |

| MAC                    | 44  |

| レジスタ                   | 47  |

| SPI レジスタの詳細            | 47  |

| PHY 条項 22 レジスタの詳細      | 70  |

| PHY 条項 45 レジスタの詳細      | 73  |

| PCB レイアウトに関する推奨事項      | 108 |

| パッケージ・レイアウト            | 108 |

| 部品の配置と配線               | 108 |

| 水晶発振器の配置と配線            | 108 |

| PCB の層構成               | 108 |

| 外形寸法                   | 109 |

| オーダー・ガイド               | 109 |

| 評価用ボード                 | 109 |

# 改訂履歴

1/2025—Revision A: Initial Version

仕様

特に指定のない限り、AVDD\_H = AVDD\_L = VDDIO = 3.3V、仕様値はすべて−40℃~+105℃での値。

表 1.

| Parameter                                | Min            | Тур                 | Max         | Unit | Test Conditions/Comments                                                                             |

|------------------------------------------|----------------|---------------------|-------------|------|------------------------------------------------------------------------------------------------------|

| POWER REQUIREMENTS                       |                |                     |             |      |                                                                                                      |

| Supply Voltage Range                     |                |                     |             |      |                                                                                                      |

| AVDD_H                                   | 3.13           | 3.3                 | 3.46        | V    | 2.4 V p-p or 1.0 V p-p transmit level                                                                |

| AVDD_L                                   | 1.71           | 1.8 or 3.3          | 3.46        | V    |                                                                                                      |

| AVDD_H, AVDD_L                           | 1.71           | 1.8                 | 3.46        | V    | 1.0 V p-p transmit level                                                                             |

| VDDIO                                    | 1.71           | 1.8, 2.5, or<br>3.3 | 3.46        | V    |                                                                                                      |

| 1.0 V p-p Transmit Level (Single Supply) |                |                     |             |      | AVDD_H = AVDD_L = VDDIO = 1.8 V                                                                      |

| AVDD_x Supply Current, IAVDD             |                | 28                  |             | mA   |                                                                                                      |

| Power Consumption                        |                | 50                  |             | mW   | 100% data throughput, full activity                                                                  |

| 2.4 V p-p Transmit Level (Single Supply) |                |                     |             |      | AVDD_H = AVDD_L = VDDIO = 3.3 V                                                                      |

| AVDD_x Supply Current, I <sub>AVDD</sub> |                | 36                  |             | mA   |                                                                                                      |

| Power Consumption                        |                | 119                 |             | mW   | 100% data throughput, full activity                                                                  |

| 2.4 V p-p Transmit Level (Dual Supply)   |                |                     |             |      | AVDD_H = 3.3 V, AVDD_L = VDDIO = 1.8 V                                                               |

| AVDD_x Supply Current, I <sub>AVDD</sub> |                | 16.5                |             | mA   |                                                                                                      |

| VDDIO Supply Current, I <sub>VDDIO</sub> |                | 18                  |             | mA   |                                                                                                      |

| Power Consumption                        |                | 87                  |             | mW   | 100% data throughput, full activity                                                                  |

| ANALOG INPUTS AND OUTPUTS                |                |                     |             |      | υ το το του του του του του του του του                                                              |

| MDI Gain Offset                          | -7.5           |                     | +3.5        | %    |                                                                                                      |

| DIGITAL INPUTS/OUTPUTS                   |                |                     |             |      | Applies to SPI pins, SWPD_EN, TX2P4_EN, TS_TIMER/<br>MS_SEL, TS_CAPT, INT, LINK_ST, RESET, and LED_x |

| VDDIO = 3.3 V                            |                |                     |             |      |                                                                                                      |

| Input Low Voltage (V <sub>IL)</sub>      |                |                     | 0.8         | V    |                                                                                                      |

| Input High Voltage (V <sub>IH</sub> )    | 2.0            |                     |             | V    |                                                                                                      |

| Output Low Voltage (V <sub>OL</sub> )    |                |                     | 0.4         | V    | Output low current (I <sub>OL</sub> ) (minimum) = 2 mA                                               |

| Output High Voltage (V <sub>OH</sub> )   | 2.4            |                     |             | V    | Output high current (I <sub>OH</sub> ) (minimum) = 2 mA                                              |

| VDDIO = 2.5 V                            |                |                     |             |      | , s (di), (                                                                                          |

| V <sub>IL</sub>                          |                |                     | 0.7         | V    |                                                                                                      |

| V <sub>IH</sub>                          | 1.7            |                     |             | V    |                                                                                                      |

| V <sub>OL</sub>                          |                |                     | 0.4         | V    | I <sub>OL</sub> (minimum) = 2 mA                                                                     |

| V <sub>OH</sub>                          | 2.0            |                     |             | V    | I <sub>OH</sub> (minimum) = 2 mA                                                                     |

| VDDIO = 1.8 V                            |                |                     |             |      |                                                                                                      |

| V <sub>IL</sub>                          |                |                     | 0.3 × VDDIO | V    |                                                                                                      |

| V <sub>IH</sub>                          | 0.7 ×<br>VDDIO |                     |             | V    |                                                                                                      |

| $V_{OL}$                                 |                |                     | 0.2 × VDDIO | V    | I <sub>OL</sub> (minimum) = 2 mA                                                                     |

| V <sub>OH</sub>                          | 0.8 ×          |                     |             | V    | I <sub>OH</sub> (minimum) = 2 mA                                                                     |

| Oil                                      | VDDIO          |                     |             |      | On (                                                                                                 |

| RESET Deglitch Time                      | 0.3            | 0.5                 | 1           | μs   |                                                                                                      |

| LED OUTPUT                               |                |                     |             |      |                                                                                                      |

| Output Drive Current                     | 8              |                     |             | mA   | VDDIO = 3.3 V                                                                                        |

|                                          | 6              |                     |             | mA   | VDDIO = 2.5 V                                                                                        |

|                                          | 4              |                     |             | mA   | VDDIO = 1.8 V                                                                                        |

analog.com.jp Rev. A | 3 of 109

# 仕様

表 1. (続き)

| Parameter                                               | Min | Тур  | Max | Unit  | Test Conditions/Comments                                                                                   |

|---------------------------------------------------------|-----|------|-----|-------|------------------------------------------------------------------------------------------------------------|

| CLOCKS                                                  |     |      |     |       |                                                                                                            |

| External Crystal (XTAL)                                 |     |      |     |       | Requirements for external crystal used on the XTAL_I and XTAL_O pins                                       |

| Crystal Frequency                                       |     | 25   |     | MHz   |                                                                                                            |

| Crystal Frequency Tolerance                             | -30 |      | +30 | ppm   |                                                                                                            |

| Crystal Drive Level                                     |     | <200 |     | μW    |                                                                                                            |

| Crystal Equivalent Series Resistance (ESR)              |     |      | 60  | Ω     |                                                                                                            |

| XTAL_I, XTAL_O Input Capacitance (C <sub>IN,EQ</sub> )  |     | 1.5  |     | pF    | Equivalent parallel differential input capacitance looking into XTAL_x pins                                |

| Crystal Load Capacitance (C <sub>L</sub> ) <sup>1</sup> |     | 10   | 18  | pF    | Including printed circuit board (PCB) trace capacitance and XTAL_I, XTAL_O C <sub>IN,EQ</sub>              |

| Start-Up Time                                           |     |      | 2   | ms    | Crystal oscillator only                                                                                    |

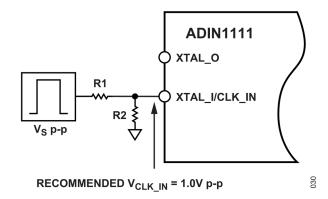

| Clock Input (CLK_IN)                                    |     |      |     |       |                                                                                                            |

| Clock Input Frequency                                   |     | 25   |     | MHz   | Requirements for external clock applied to XTAL_I pin, media independent interface (MII) mode              |

|                                                         |     | 50   |     | MHz   | Reduced media independent interface (RMII) mode                                                            |

| Clock Jitter                                            |     |      | 40  | ps    | RMS                                                                                                        |

| Clock Input Voltage Range                               | 0.8 |      | 2.5 | V p-p | AC-coupled sine or square wave at XTAL_I pin, see External 25 MHz Clock Input section for more information |

| Clock Input Duty Cycle                                  | 45  |      | 55  | %     |                                                                                                            |

| XTAL_I Input Impedance (Z <sub>IN,EQ</sub> )            |     |      |     |       |                                                                                                            |

| Driving Point Resistance R <sub>P</sub> <sup>2</sup>    |     | 6    |     | kΩ    | $R_P  C_P$                                                                                                 |

| Driving Point Capacitance C <sub>P</sub> <sup>2</sup>   |     | 3    |     | pF    |                                                                                                            |

| CLK25_REF Clock Output                                  |     |      |     |       |                                                                                                            |

| CLK25_REF Frequency                                     |     | 25   |     | MHz   |                                                                                                            |

| $V_{OH}$                                                |     | 1.05 |     | V     | Load 10 pF                                                                                                 |

| $V_{OL}$                                                |     | 0    |     | V     | Load 10 pF                                                                                                 |

| CLK25_REF Duty Cycle                                    | 45  |      | 55  | %     | Load 10 pF                                                                                                 |

| CLK25_REF Frequency Tolerance                           | -50 |      | +50 | ppm   |                                                                                                            |

$<sup>^1</sup>$   $C_L$  = ((C1 × C2)/(C1 + C2) +  $C_{STRAY}$ )、ここで  $C_{STRAY}$ は、配線やパッケージの寄生成分を含む浮遊容量です。

analog.com.jp Rev. A | 4 of 109

$<sup>^2</sup>$   $R_P$  および  $C_P$  は、AC グラウンドへの等価並列 RC 回路( $R_P \parallel R_C$ )の値であり、XTAL\_I/CLK\_IN ピンの駆動点のインピーダンスをモデル化しています。

# タイミング特性

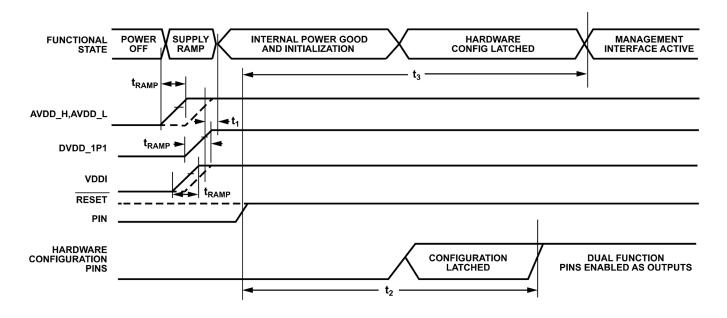

# パワーアップ・タイミング

表 2. パワーアップのタイミング

| Parameter         | Description                                               | Min | Тур | Max | Unit |

|-------------------|-----------------------------------------------------------|-----|-----|-----|------|

| t <sub>RAMP</sub> | Power supply ramp time                                    |     |     | 40  | ms   |

| t <sub>1</sub>    | Minimum time interval to internal power good <sup>1</sup> | 20  |     | 43  | ms   |

| $t_2$             | Hardware configuration latch time                         | 6   | 8   | 14  | μs   |

| $t_3$             | Management interface (SPI) active                         |     |     | 50  | ms   |

<sup>「</sup>最小タイム・インターバルは、立上がり閾値に到達する最後の電源を基準としています。特定の電源シーケンスは必要ありません。

図 2. パワーアップのタイミング図

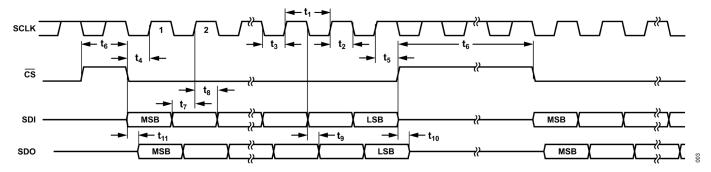

# SPI

表 3.

| Parameter <sup>1, 2</sup>    | Description                                          | Min | Тур | Max | Unit |  |

|------------------------------|------------------------------------------------------|-----|-----|-----|------|--|

| t <sub>1</sub>               | SCLK cycle time                                      | 40  |     |     | ns   |  |

| t <sub>2</sub>               | SCLK high time                                       | 17  |     |     | ns   |  |

| $t_3$                        | SCLK low time                                        | 17  |     |     | ns   |  |

| t <sub>4</sub>               | CS falling edge to SCLK rising edge setup time       | 17  |     |     | ns   |  |

| t <sub>5</sub>               | Last SCLK rising edge to CS rising edge              | 17  |     |     | ns   |  |

| t <sub>6</sub>               | CS high time                                         | 40  |     |     | ns   |  |

| t <sub>7</sub>               | Data setup time                                      | 5   |     |     | ns   |  |

| t <sub>8</sub>               | Data hold time                                       | 5   |     |     | ns   |  |

| t <sub>9</sub> <sup>3</sup>  | SCLK falling edge to SDO valid                       |     |     | 12  | ns   |  |

| t <sub>10</sub> <sup>3</sup> | CS rising edge to SDO tristate                       |     |     | 15  | ns   |  |

| t <sub>11</sub> <sup>3</sup> | CS falling edge to SDO valid (for readback MSB only) |     |     | 12  | ns   |  |

<sup>1</sup> 設計および特性評価により裏付けられています。製品テストの対象外です。

analog.com.jp Rev. A | 5 of 109

005

$<sup>^2</sup>$  すべての入力信号は、立上がり時間  $(t_R)$  = 立下がり時間  $(t_F)$  = 5ns (VDDIO の  $10\% \sim 90\%$ ) で仕様規定され、1.2V の電圧レベルを基準に時間測定されています。

<sup>&</sup>lt;sup>3</sup> SDO ピンの容量性負荷は 10pF です。

# タイミング特性

図 3. シリアル・インターフェースのタイミング図

analog.com.jp Rev. A | 6 of 109

# 絶対最大定格

特に指定のない限り、 $T_A = 25$ °C。

#### 表 4.

| <b>4</b> 寸.                                   |                                           |  |  |

|-----------------------------------------------|-------------------------------------------|--|--|

| Parameter                                     | Rating                                    |  |  |

| VDDIO to GND                                  | -0.3 V to +4 V                            |  |  |

| DLDO_1P1 to GND                               | -0.3 V to +1.35 V                         |  |  |

| AVDD_H, AVDD_L to GND                         | -0.3 V to +4 V                            |  |  |

| SPI <sup>1</sup> , ĪNT to GND                 | -0.3 V to VDDIO + 0.3 V                   |  |  |

| TXN, TXP to GND                               | -0.3 V to AVDD + 0.3 V                    |  |  |

| LED_x, RESET, LINK_ST to GND                  | -0.3 V to VDDIO + 0.3 V                   |  |  |

| XTAL_I/CLK_IN to GND                          | -0.3 V to 2.75 V                          |  |  |

| XTAL_O, CLK25_REF to GND                      | -0.3 V to 1.35 V                          |  |  |

| Operating Temperature Range (T <sub>A</sub> ) |                                           |  |  |

| Industrial                                    | -40°C to +105°C                           |  |  |

| Storage Temperature Range                     | -65°C to +150°C                           |  |  |

| Junction Temperature (T <sub>J</sub> maximum) | 125°C                                     |  |  |

| Power Dissipation                             | $(T_J \text{ maximum} - T_A)/\theta_{JA}$ |  |  |

| Lead Temperature                              | JEDEC industry standard                   |  |  |

| Soldering                                     | J-STD-020                                 |  |  |

<sup>「</sup>SPIピンの全リストについては、ピン配置およびピン機能の説明のセクションを参照してください。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

# 熱抵抗

θ<sub>JA</sub> は、1 立方フィートの密封容器内で測定された、自然対流下 におけるジャンクションと周囲温度の間の熱抵抗です。

表 5. 熱抵抗

| Package Type          | $\theta_{JA}^{1}$ | Unit |

|-----------------------|-------------------|------|

| CP-32-20 <sup>2</sup> | 44                | °C/W |

<sup>&</sup>lt;sup>1</sup>θ<sub>JA</sub>は最も厳しい条件、すなわち、表面実装パッケージ用回路基板にデ バイスをハンダ付けした状態で仕様規定されています。

# 静電放電(ESD)定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帯電デバイス・モデル(FICDM)。

#### ADIN1111 の ESD 定格

表 6. ADIN1111、32 ピン LFCSP

| ESD Model      | Withstand Threshold (V) | Class |

|----------------|-------------------------|-------|

| HBM            |                         |       |

| TXN, TXP Pins  | 8000                    | 3B    |

| All Other Pins | 2000                    | 2     |

| FICDM          | 1250                    | C3    |

# ESD に関する注意

ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

analog.com.jp Rev. A | 7 of 109

<sup>&</sup>lt;sup>2</sup> テスト条件 1: 熱抵抗のシミュレーション値は、サーマル・ビアを備えた JEDEC 2S2P サーマル・テスト・ボードを基準にしています。 JEDEC JESD-51 を参照してください。

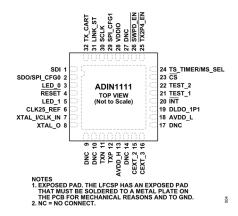

# ピン配置およびピン機能の説明

図 4. ピン配置

表 7. ピン機能の説明 (ハードウェア・ピン構成のグループ分けは変更される可能性があります)

| ピン番号                    | 記号 <sup>1</sup>              | PU/PD <sup>2</sup> | 説明                                                                                                                               |

|-------------------------|------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|

| クロック・インターフェース           |                              |                    |                                                                                                                                  |

| 6                       | CLK25_REF                    | N/A                | アナログ・リファレンス・クロック出力。水晶発振器からの 25MHz リファレンス・<br>クロックは、この CLK25_REF ピンで利用できます。                                                       |

| 7                       | XTAL_I/CLK_IN                | N/A                | 水晶発振器の入力(XTAL_I)。<br>シングルエンドの 25MHz リファレンス・クロック入力(CLK_IN)。                                                                       |

| 8                       | XTAL_O                       | N/A                | 水晶振動子出力。XTAL_I/CLK_IN でシングルエンドのリファレンス・クロックを使用する場合、XTAL_O はオープン・サーキットのままにします。外部 25MHz クロック入力のセクションを参照してください。                      |

| SPI                     |                              |                    |                                                                                                                                  |

| 1                       | SDI                          | PD                 | シリアル・データ入力。データは、クロックの各立上がりエッジで SDI ピンに入力<br>されます。                                                                                |

| 2                       | SDO/SPI_CFG0 <sup>3</sup>    | PD                 | シリアル・データ出力(SDO)。データは、クロックの各立下がりエッジで SDO<br>ピンに出力されます。<br>SPI プロトコル設定ピン 0(SPI_CFG0)。表 15 を参照してください。                               |

| 20                      | ĪNT                          | PU                 | 割込みピン出力。アクティブ・ローのオープンドレイン出力。INTのローは、マスク解除されている管理割込みを示します。このピンには、VDDIOへの 1.5kΩ プルアップ抵抗が必要です。                                      |

| 23                      | CS                           | PD                 | アクティブ・ローのチップ・リセット。                                                                                                               |

| 29                      | SPI_CFG1                     | PD                 | SPI プロトコル設定ピン 1。表 15 を参照してください。                                                                                                  |

| 30                      | SCLK                         | PD                 | シリアル・クロック入力。データは、クロックの各立上がりエッジでシフト・レジスタに入力されます。                                                                                  |

| タイム・スタンプ機能に<br>対応       |                              |                    |                                                                                                                                  |

| 24                      | TS_TIMER/MS_SEL <sup>3</sup> | PD                 | タイム・スタンプ・タイマー出力(TS_TIMER)。アプリケーション情報のセクションを参照してください。<br>リーダー/フォロアの選択(MS_SEL)。リーダーを優先する場合はハイ、フォロアを優先する場合はローに設定します。表 13 を参照してください。 |

| 32                      | TS_CAPT                      | PD                 | タイム・スタンプの取得、ADIN1111 への入力)。アプリケーション情報のセクションを参照してください。タイム・スタンプ機能を使用しない場合、内部にプルダウン抵抗があるため、このピンをオープンのままにしておくことができます。                |

| リセット                    |                              |                    |                                                                                                                                  |

| 4                       | RESET                        | PU                 | アクティブ・ロー入力。10µs を超える時間、ローに保持してください。内部にプルアップ抵抗があるため、RESETにはプルアップ抵抗は不要です。                                                          |

| メディア依存インターフェース<br>(MDI) |                              |                    |                                                                                                                                  |

| 11                      | TXN                          | N/A                | 送信/受信の負側ピン。                                                                                                                      |

| 12                      | TXP                          | N/A                | 送信/受信の正側ピン。                                                                                                                      |

analog.com.jp Rev. A | 8 of 109

# ピン配置およびピン機能の説明

表 7.ピン機能の説明(ピン配置のハードウェア上のグループ分けは変更される可能性があります)(続き)

| ピン番号              | 記号 <sup>1</sup>      | PU/PD <sup>2</sup> | 説明                                                                                                                                                                                                                                               |

|-------------------|----------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 設定/ステータス          |                      |                    |                                                                                                                                                                                                                                                  |

| 3                 | LED_0                | PU                 | 汎用LED用プログラマブルLEDインジケータ。LEDはアクティブ・ローです。LEDは、アクティブ・ハイでもアクティブ・ローでも動作可能です。デフォルトでは、リンクが確立されるとLED_0が点灯し、アクティビティがあると点滅するよう設定されています。LED機能のセクションを参照してください。                                                                                                |

| 31                | LINK_ST              | PD                 | リンク・ステータス出力。LINK_ST は、有効なリンクが確立されているかどうかを示します。LINK_ST はアクティブ・ハイです。                                                                                                                                                                               |

| 5                 | LED_1                | PD                 | 汎用 LED 用プログラマブル LED インジケータ。LED は、アクティブ・ハイでもアクティブ・ローでも動作可能です。デフォルトでは、LED_1 はディスエーブルです。LED 機能のセクションを参照してください。                                                                                                                                      |

| 25                | TX2P4_EN³            | PD                 | 送信レベル振幅用のハードウェア設定ピン。送信振幅が 1.0V p-p の場合にのみハイに設定します。送信振幅が 1.0V p-p および 2.4V p-p の場合はローに設定します。表14 を参照してください。                                                                                                                                        |

| 26                | SWPD_EN <sup>3</sup> | PD                 | ソフトウェア・パワーダウン設定。ローにセットすると、パワーアップ/リセット<br>後に PHY がソフトウェア・パワーダウン・モードになるよう設定されます。表 12<br>を参照してください。                                                                                                                                                 |

| LDO および REFERENCE |                      |                    |                                                                                                                                                                                                                                                  |

| 15                | CEXT_2               | N/A                | LDO 回路用外部デカップリング。このピンのできるだけ近くで、0.1µF のコンデンサをグラウンドに接続します。このピンを外部回路用電圧源として使用しないでください。                                                                                                                                                              |

| 16                | CEXT_3               | N/A                | LDO 回路用外部デカップリング。このピンのできるだけ近くで、1µF のコンデンサをグラウンドに接続します。このピンを外部回路用電圧源として使用しないでください。                                                                                                                                                                |

| 電源ピンおよびグラウンド・     |                      |                    |                                                                                                                                                                                                                                                  |

| ピン                |                      |                    |                                                                                                                                                                                                                                                  |

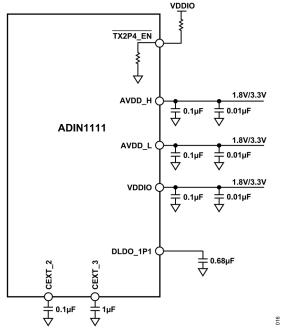

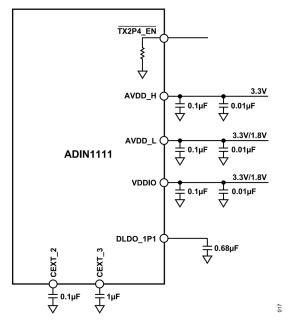

| 13                | AVDD_H               | N/A                | デバイス内の様々なアナログ回路用のアナログ電源電圧。この電源レールは、送信レベル設定に応じて $1.8V \sim 3.3V$ で供給できます。AVDD_H が $3.3V$ の場合、 $1.0V$ ppと $2.4V$ p-pの両方の送信動作モードに対応し、AVDD_H が $1.8V$ のみの場合は、 $1.0V$ p-p の送信動作モードにのみ対応します。このピンのできるだけ近くで、 $0.1\mu$ Fと $0.01\mu$ F のコンデンサをグラウンドに接続します。 |

| 18                | AVDD_L               | N/A                | 内部 LDO 回路用のアナログ電源電圧。この電源レールは 1.8V~3.3V で供給できます。AVDD_L は、長距離伝送アプリケーションでは AVDD_H レールに直結できます。また、低消費電力用に両電源で構成されている場合はより低電圧の別のレールに接続できます。このピンのできるだけ近くで、0.1µF と 0.01µF のコンデンサをグラウンドに接続します。                                                            |

| 19                | DLDO_1P1             | N/A                | デジタル・コア 1.1V 電源出力ピン。このピンのできるだけ近くで、0.68µF のコン<br>デンサを GND に接続します。                                                                                                                                                                                 |

| 28                | VDDIO                | N/A                | SPI 用の 3.3V、2.5V、または 1.8V のデジタル電力。このピンのできるだけ近くで、0.1µF と 0.01µF のコンデンサを GND に接続します。                                                                                                                                                               |

|                   | EP                   | N/A                | 露出パッド (EP)。この GND パドルはグラウンドに接続する必要があります。<br>LFCSP パッケージには、電気的な理由により GND に接続する必要があり、機械的な理由により PCB の金属面にハンダ付けする必要のある露出パッドがあります。露出 GND パッドの下に、4×4アレイのサーマル・ビアを設けることを推奨します。                                                                           |

| その他のピン            |                      |                    |                                                                                                                                                                                                                                                  |

| 9, 10, 14, 17, 27 | DNC                  | N/A                | 接続しないでください。これらのピンはオープン・サーキットのままにする必要が<br>あります。                                                                                                                                                                                                   |

| 21                | TEST1                | PU                 | このピンには、VDDIO への 1.5kΩ プルアップ抵抗が必要です。                                                                                                                                                                                                              |

| 22                | TEST2                | PU                 | このピンはオープン・サーキットのままにする必要があります。                                                                                                                                                                                                                    |

<sup>「</sup>ピンが機能信号とハードウェア・ピン設定信号を兼ねている場合、記号の末尾にハードウェア・ピン設定信号を付けています。このデータシートでは、これらのピンを機能信号名で表記しています。

analog.com.jp Rev. A | 9 of 109

$<sup>^2</sup>$  PU/PD は、内部/オン・チップのプルアップ抵抗またはプルダウン抵抗を意味します。内部のプルアップ抵抗またはプルダウン抵抗は事前に定義されており、ユーザが設定を変更することはできません。N/A は、該当なしを意味します。

$<sup>^3</sup>$  すべてのハードウェア設定ピンには、内部プルダウン抵抗があります。これらのピンに外部抵抗を接続しないデフォルト動作モードを表 10 に示します。 代替動作モードが必要な場合は、 $4.7 \mathrm{k}\Omega$  のプルアップ抵抗を使用してください。

# 代表的な性能特性

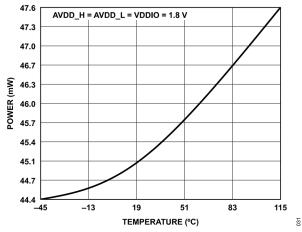

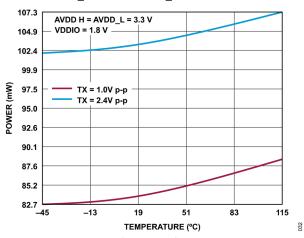

図 5. 消費電力と温度の関係、1.8V 単電源

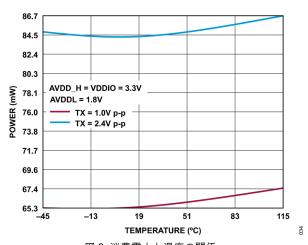

図 6. 消費電力と温度の関係、 AVDD\_H = 3.3V、VDDIO = 3.3V、AVDD\_L = 1.8V

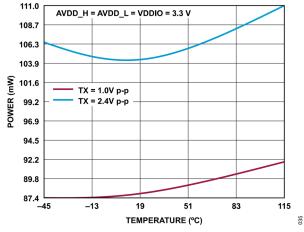

図 7. 消費電力と温度の関係、3.3V 単電源

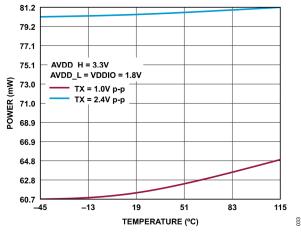

図 8. 消費電力と温度の関係、 AVDD\_H = 3.3V、AVDD\_L = VDDIO = 1.8V

図 9. 消費電力と温度の関係、 AVDD\_H = AVDD\_L = 3.3V、VDDIO = 1.8V

analog.com.jp Rev. A | 10 of 109

# 動作原理

ADIN1111 は、低消費電力の単一ポート 10Mb/s イーサネット MAC-PHY デバイスで、長距離伝送の 10Mbps シングル・ペア・イーサネットに対応する IEEE 802.3cg イーサネット規格に準拠しています。

ADIN1111 は以下のような機能を備えています。

- ▶ 関連する一般的なアナログ回路をすべて備えた 10BASE-TIL イーサネット PHY コアおよび MAC

- ▶ 入出力クロックのバッファ処理

- ▶ SPIおよびサブシステム・レジスタ

- ▶ リセットおよびクロックを管理する制御ロジック

- ▶ ハードウェア設定ピン

- ▶ 2個の設定可能な LED ピン

# 電源ドメイン

ADIN1111には、以下の3つの電源ドメインがあり、少なくとも1つの電源レールが必要です。

- ▶ AVDD\_H は、ADIN1111 のアナログ・フロント・エンド (AFE) 回路用のアナログ電源入力です。

- ▶ AVDD\_L は、内部 LDO 回路用のアナログ電源電圧です。 AVDD\_L は、単電源モードでは AVDD\_H レールに、低消費電力向けの両電源モードではより低電圧のレールに接続します。

- ▶ VDDIOにより、SPIの電圧源をADIN1111内の他の回路とは 独立して設定できます。VDDIOは、AVDD\_L レールに直接 接続できます。

単電源アプリケーションでは、 $AVDD_H$ 、 $AVDD_L$ 、VDDIO を同じ電源に接続します。使用する適切な電源電圧は、最終アプリケーションとケーブル長によって異なります。送信振幅電圧が 2.4V p-p と高い場合は  $AVDD_H = 3.3V$ 、送信振幅電圧が 1.0V p-p と低い場合は  $AVDD_H = 1.8V$  または 3.3V にする必要があります。

#### アナログ・フロント・エンド

アナログ・フロント・エンド (AFE) 段は、ハイブリッド段、 9 レベル DAC、ライン・ドライバ、アナログ受信フィルタ、入 カバッファ、ADC で構成されています。

ライン・ドライバは、MDI インターフェース・ピンである TXP および TXN を介して、ラインに信号を送信します。ハイブリッド段では、送信信号を MDI ピンで受信した信号から差し引くことで、シングル・ペア・ケーブルでの全 2 重動作を可能にします。

その後、受信信号はアナログ受信フィルタを通過し入力バッファに達した後、ADCに送られます。

#### MAC

ADINI111の MAC は 16 通りの MAC アドレスをサポートしています。また、MACには、低優先度受信先入れ先出し(FIFO)が 1 つ、高優先度受信 FIFO が 1 つ、送信 FIFO が 1 つあります。これらの FIFO は、汎用の SPI プロトコルを使用する場合はストア・アンド・フォワード・モードでデータを送信し、OPEN Alliance プロトコルを使用する場合はストア・アンド・フォワード・モードまたはカット・スルー・モードでデータを送信できます。

汎用バージョンと OPEN Alliance バージョンの SPI プロトコルが 使用できます。データは、汎用 SPI プロトコルでは SPI 半2重通 信で転送され、OPEN Alliance プロトコルでは全2重通信で転送 されます。MAC SPI のセクションを参照してください。

#### 割込み (INT)

ADIN1111 は、ユーザが選択した様々な条件に応じ、INTピンを使用してホスト・プロセッサに割込みを生成できます。割込みを生成するには、以下の条件が選択できます。

- ▶ リンク・ステータスの変化

- ▶ 受信 FIFO データが使用可能

- ▶ フレーム送信完了または送信領域が使用可能

- タイム・スタンプの取得

- ▶ 動作エラーの検出

- ▶ PHY 関連割込み

割込みが発生すると、システムは MAC ステータス・レジスタ (STATUSO および STATUSI) をポーリングすることで、割込みの発生源を特定できます。

# 送信振幅の設定

ADIN1111は、次の2つの送信振幅の動作モードに対応しています。

- ▶ 1.0V p-p および 2.4V p-p のモード (ハイ・レベル)

- ▶ 1.0V p-p のみのモード

ハイ・レベルの送信モードでは、ADIN1111 は 2.4V p-p と 1.0V p-p の両方の電圧レベルに対応できます。したがって、動作レベルは、リンク・パートナーの機能に基づき、オート・ネゴシエーション(有効な場合)中に自動的に設定されます。2.4V p-p の高レベル送信動作モードでは、AVDD\_H電源電圧を 3.3V にする必要があります。電源電圧が 3.3V 未満の場合、デバイスが正しく起動しない可能性があります。

動作モードは、TX2P4\_ENのハードウェア設定ピンで設定されます(送信振幅のセクションを参照)。また、ADIN1111は、このピンで設定されたレベルに基づき、オート・ネゴシエーション・プロセスで使用される送信レベル・レジスタ・ビットのデフォルト値を設定します。

ADIN1111 は、TX2P4\_ENピンがフローティング状態(内部プルダウン抵抗)にある場合、ハイ・レベル送信動作モードになるようデフォルト設定されています。

# リーダー/フォロア設定

10BASE-TIL 規格では、リーダー/フォロア・クロック方式を使用します。この方式は、一般的にエコー・キャンセル付きの全2重トランシーバ規格で使用されています。

10BASE-TIL リンクでは、1 つの PHY がリーダーに、他方の PHY がフォロアに指定されます。PHY がリーダーになるかフォロアになるかは、オート・ネゴシエーションで決まります。 リーダーとフォロアの割り当ては、一般的には重要ではありません。

analog.com.jp Rev. A | 11 of 109

## 動作原理

#### ソフトウェア設定

リーダーおよびフォロア設定ビット (CFG\_MST) を使用して PHY の役割を設定します。このビットは、オート・ネゴシエーションがディスエーブルされている場合にのみ使用します。それ以外の場合は、このビットはオート・ネゴシエーション・プロセス中にセットまたはリセットされます(オート・ネゴシエーションのセクションを参照)。

表 8. CFG MST の設定

| Bit Setting | Description     |

|-------------|-----------------|

| 0           | Prefer follower |

| 1           | Prefer leader   |

# オート・ネゴシエーション

ADINI111 は、IEEE 802.3 の条項 98 に準拠したオート・ネゴシェーション機能を使用しており、リンク・パートナーが共通の動作モードに合意できるよう、PHY 間の情報交換メカニズムを提供しています。オート・ネゴシエーション・プロセス中、PHY は自身の機能をアドバタイズし、リンク・パートナーから受信した機能と比較します。その結果、動作モードは、2 つのデバイスに共通の送信振幅モードとリーダー/フォロア優先度に設定されます。

リンクが切断された場合、オート・ネゴシエーション・プロセスは自動的に再起動します。オート・ネゴシエーションは、オート・ネゴシエーション制御レジスタのオート・ネゴシエーション再起動ビット(AN\_RESTART)に書き込むことでも要求できます。

オート・ネゴシエーション・プロセスは、交換されるページの数に応じて完了するまでに時間がかかりますが、リンクを確立するためには常に最も速い方法です。IEEE 802.3 規格の条項98には、オート・ネゴシエーションに関連したタイマーについての詳細が記載されています。

ADIN1111ではオート・ネゴシエーションはデフォルトでイネーブルされており、常にイネーブルしておくことを強く推奨します。

#### 送信振幅の決定

オート・ネゴシエーションを使用して、送信振幅を決定できます。 PHY は、ハードウェア設定を介して、1.0V p-p および2.4V p-p の 両方の送信レベルに対応するよう設定することも、1.0V p-p 送信レベルでのみ動作するよう設定することもできます(表 14 参照)。また、この設定は、10BASE-T1L のハイ・レベル送信動作モード機能(10BASE-T1L ハイ・レベル送信動作モード機能(10BASE-T1L ハイ・レベル送信動作モード要求(10BASE-T1L ハイ・レベル送信動作モードを用いてソフトウェア設定により行うこともできます。

2.4V p-p 送信レベルで動作させるには、ローカル PHY とリモート PHY の両方が 2.4V で動作可能であることをアドバタイズする必要があり、また、少なくとも 1 方の PHY が 2.4V p-p の送信レベルの動作を要求する必要があります。

1.0V p-p 送信レベル動作でのみ PHY を動作させる場合は、AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL ビットを0に設定し、2.4V p-p

送信レベル動作がアドバタイズされないようにします。この場合、オート・ネゴシエーションの結果は、リモートの PHY がアドバタイズする設定にかかわらず、1.0V p-p送信レベル動作のみになります。

#### リーダー/フォロアの決定

オート・ネゴシエーションは、リーダーかフォロアかのステータスを決定するためにも使用されます。PHYは、ハードウェア設定を介してリーダー優先またはフォロア優先となるよう設定できます(表 13 参照)。オート・ネゴシエーションがディスエーブルされている場合、MS\_SELハードウェア設定ピンがデフォルトのリーダー/フォロア選択を設定します。なお、ADIN1111の推奨使用方法は、オート・ネゴシエーションをイネーブルすることです。

オート・ネゴシエーション中、フォロア優先が選択され、リモート端がリーダー優先またはリーダー強制の場合、ローカルPHY はフォロアに(リモートはリーダーに)設定されます。リモート端がフォロア優先またはフォロア強制の場合、ローカルPHY はリーダーに(リモートはフォロアに)設定されます。

# MDI 回路

メディア依存インターフェース (MDI) は、ツイスト・ワイヤ・ペアを介して ADIN1111 をイーサネット・ネットワークに接続します。

ADIN1111には内部終端抵抗と内部ハイブリッドを備えた2ピン MDI があり、ツイスト・ワイヤ・ペアを介して ADIN1111 を イーサネット・ネットワークに直接接続できます。

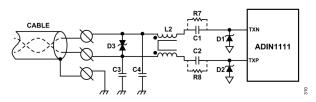

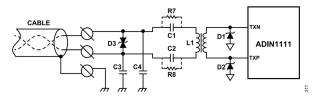

図10、図11、図12に、トポロジおよび各部品の値を示します。 部品値は以下のとおりです。

- ▶ D1、D2:保護用部品。低容量(5pF 未満)、低電圧(スタンドオフ電圧 3.3V 以上)の TVS。

- C1、C2:0.22μF、60V 定格。350μHの低インダクタンス・トランスを使用する場合、C1およびC2を0.47μFにする必要があります(IEEE 802.3のドループ仕様に適合させるため)。

- **R7、R8**: コンデンサ C1 および C2 の電荷ビルド・アップを 防ぐためのオプションの抵抗( $100k\Omega\sim M\Omega$ )。

- ▶ C3、C4:47pF~100pF、±5%の公差。

- ▶ D3:保護用部品。低容量 TVS (100pF 未満)。この TVS ダイオードは低容量であることが重要です。

- ▶ L1トランス:ガルバニック絶縁を可能にします。

- ▶ 100kHz~20MHzの周波数範囲で動作できることが必要です。

- ▶ インダクタンス > 350μH。

- ▶ L2 コモンモード・インダクタ: ≥220µH、低リーク・インダクタンス <0.5µH。</p>

- ▶ L3 電源インダクタ:高度物理層(APL)デバイスと非 APL デバイスの電源カップリング用。

- APL: 880μH 以上の差動動作で、最大 10%のドループを 実現。

- ▶ 220µH 以上の結合インダクタを推奨(共通磁気コア 上に2つのインダクタ)。

- ▶ あるいは、440µH以上の2つの個別インダクタ。

analog.com.jp Rev. A | 12 of 109

#### 動作原理

- 非 APL: 160μH 以上の差動動作で、最大約 25%のドループを実現。

- ▶ 47µH 以上の結合インダクタを推奨(共通磁気コアに 2つのインダクタ)。

- ▶ あるいは、100µH以上の2つの個別インダクタ。

MDI 伝送線上に絶縁トランスがあるため、トランスのインダクタンスと電源インダクタの合計差動インダクタンスの並列値が160μHを超える必要がある点に注意してください。

図 10. ADIN1111 に対し容量性結合をする代表的な MDI 回路

図 11. ADIN1111 に対しガルバニック絶縁をする代表的な MDI 回路

図 12. ADIN1111 に対し電源結合をする代表的な MDI 回路

#### リセット動作

ADIN1111は、次のチップ・リセットをサポートしています:

- ▶ パワーオン・リセット

- ▶ ハードウェア・リセット

- ▶ ソフトウェア・リセット

- ▶ MAC サブシステム・リセット

- ▶ PHY サブシステム・リセット

これらのリセットはすべて、PHY コアおよび MAC を含む ADIN1111 を既知の状態にします。MAC がリセットされるたび に、SDO ピンがプルダウンされ、TS\_TIMER ピンがロー状態に 駆動されます。

# パワーオン・リセット

ADIN1111は、すべての電源をモニタするための電源モニタ回路を搭載しています。パワーアップ時、ADIN1111は各電源が最小の立上がり閾値を超え電源が良好であると判断されるまで、ハードウェア・リセット状態に保持されます。

POR モジュールは、電源をモニタして 1 つ以上の電源が最小立下がり関値を下回ったかどうかを検出することによるブラウンアウト保護機能を備えています。ブラウンアウトが検出されると、デバイスは電源が良好になるまでハードウェア・リセット状態を維持します。

#### ハードウェア・リセット

ハードウェア・リセットは、パワーオン・リセット回路、また  $\overline{RESET}$  ピンをローにアサートすることで開始されます。  $\overline{RESET}$  ピンを  $10\mu s$  以上の間、ローにします。このピンにはデグリッチ回路が含まれており、 $0.3\mu s$  より短いパルスは除去されます。

RESETピンがアサート解除されると、すべての入出力(I/O)ピンがトライステート・モードに保持され、ハードウェア設定ピンがラッチされて、I/Oピンはそれぞれの機能モードに設定されます。すべての外部および内部電源が有効かつ安定な場合、水晶発振器回路がイネーブルされます。水晶発振器が起動し安定すると、フェーズ・ロック・ループ(PLL)がイネーブルされます。RESETピンがアサート解除されてから最大50ms後、すべての内部クロックが有効になり、内部ロジックはリセットから復帰し、すべての管理インターフェース・レジスタにアクセスして、デバイスをプログラムできるようになります。

#### ソフトウェア・リセット

チップ全体のソフトウェア・リセットは、RESET レジスタの SWRESET フィールドに 1 を書き込むことで開始できます。

SPIソフトウェア・リセットの開始時に送信が行われていた場合は、フレーム送信が突然停止し、ラントまたは巡回冗長検査(CRC)が不合格のフレームが送信される可能性があります。MAC-PHYがリセットされると、ADIN1111にはリンクを確立する用意が整います。

このソフトウェア・リセットが開始されると、ハードウェア・リセットとほぼ同様に、チップが完全に初期化されます。I/Oピンはトライステート・モードに保持され、ハードウェア設定ピンがラッチされて、I/Oピンはそれぞれの機能モードに設定されます。水晶発振器回路がイネーブルになり、水晶発振器が起動して安定するとPLLがイネーブルされます。SOFT\_RSTキーの書込み後約10ms(最大)経過すると、内部ロジックがリセットからリリースされ、すべての管理インターフェース・レジスタがアクセス可能になります。

# MAC サブシステム・リセット

MAC のみのソフトウェア・リセットは、必要なキー・ペアを SOFT RST レジスタに書き込むことで開始できます。

リセットは、約  $1.2\mu s$  の間適用されます。MAC サブシステム・リセットは、MAC と PHY の間の任意の送信/受信パケット交換を中断しますが、既存のリンクを切断したり、リンクの確立を妨げたりするようなことはありません。PHY 管理レジスタは初期化されません。

MACのみのソフトウェア・リセットをトリガするには、PHYがソフトウェア・パワーダウンの対象外であることが必要です。

analog.com.jp Rev. A | 13 of 109

## 動作原理

#### PHY サブシステム・リセット

PHY サブシステムは、ADIN1111の一部で、10BASE-TIL PHY トランシーバのアナログ回路とデジタル回路の両方を含んでいます。PHY サブシステムのリセットは、PHY サブシステム・リセット・レジスタ・ビット (CRSM\_PHY\_SUBSYS\_RST) をセットすることで開始されます。このビットがセットされると、PHY サブシステムがリセットされます。リセットは約 1.2μs の間適用され、その後、このビットはセルフ・クリアされます。PHY のデジタル回路がすべてリセットされ、すべてのアクティブなリンクが切断されます。このリセットにより管理レジスタが初期化されることはありません。また、すべての管理レジスタへのアクセスは、PHY サブシステムのリセットの間も可能で

す。これは短時間のリセットであり、デバイスのソフトウェア 初期化を継続しながらデバイスを既知の状態にする場合に使用 できます。

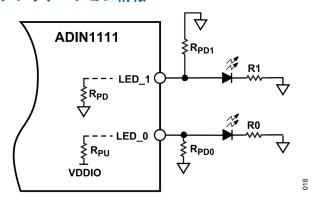

#### LED 機能

LED\_0 および LED\_1 は、LED 機能という特徴を利用し、ADIN1111の様々なアクティビティを表示するよう設定できます。 LED 機能は、LED0\_FUNCTION ビットおよび LED1\_FUNCTION ビットで設定できます(LED 制御レジスタのセクションを参照)。

**LEDx\_FUNCTION** の 7、8、9、10 (10 進数) のビット設定値は、**LED**モード 2 では使用できません。

表 9. LED x ピンの設定の概要

| Parameter                                  | LED_0                                                                                    | LED_1                                                                             |

|--------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Pin Number                                 | 3                                                                                        | 5                                                                                 |

| Internal Pull-Up or Pull-<br>Down Resistor | Pull-up                                                                                  | Pull-down                                                                         |

| Status at Power-Up or Reset                | Enabled                                                                                  | Disabled                                                                          |

| LED Pin Mux                                | Not applicable                                                                           | DIGIO_LED1_PINMUX bits (see the Pin Mux Configuration 1 Register section)         |

| Enable LED                                 | LED0_EN bit (see the LED Control Register section)                                       | LED1_EN bit (see the LED Control Register section)                                |

| LED Polarity                               | LED0_POLARITY bits (see the LED Polarity Register section)                               | LED1_POLARITY bits (see the LED Polarity Register section)                        |

| LED Mode                                   | LED0_MODE bit (see the LED Control Register section), default: LED Mode 1                | LED1_MODE bit (see the LED Control Register section), default: LED Mode 1         |

| LED Function <sup>1</sup>                  | LED0_FUNCTION bits (see the LED Control Register section), default: LINKUP_TXRX_ACTIVITY | LED1_FUNCTION bits (see the LED Control Register section), default: TXRX_ACTIVITY |

| LED Blink Rate                             | LED0_BLINK_TIME_CNTRL (see the LED_0 On/Off Blink Time Register section)                 | LED1_BLINK_TIME_CNTRL (see the LED 1 On/Off Blink Time Register section           |

| Maximum Current <sup>2</sup>               | 8 mA at 3.3 V                                                                            | 8 mA at 3.3 V                                                                     |

<sup>&</sup>lt;sup>1</sup> LEDx\_FUNCTION ビットの 7、8、9、10 (10 進数) の設定値は、LED モード 2 では使用できません。

analog.com.jp Rev. A | 14 of 109

$<sup>^2</sup>$ 表1を参照してください。

## 動作原理

#### 代表的な使用例

LED\_0 ピンおよび LED\_1 ピンは、外部 LED を接続して ADIN1111のリンク・ステータスや送受信アクティビティを示す ために使用できます。各 LED に割り当てるアクティビティは、 LED\_CNTRL で設定できます(LED 制御レジスタのセクションを参照)。

LED ピンは、超低消費電力の LED に適しています。 LED\_0 ピンと LED\_1 ピンの最大出力電流は、VDDIO = 3.3V の場合 8mA です。これより大きな LED 出力が必要な場合は、外部トランジスタを使用することを推奨します。

LED\_x ピンは、ホスト・コントローラの汎用入出力(GPIO)にも接続できます(パルス幅変調入力またはハードウェア割込みとして設定)。この設定は、ユーザ・インターフェースをすべて外部ホスト・コントローラで処理する必要があるアプリケーションにおいて有用です(例えば外部 LED モジュールやディスプレイ)。なお、この場合は、ADIN1111 の LED\_x ピンとコントローラの間に低抵抗値の抵抗を直列に配置し、過渡的なサージ電流を防ぐことを推奨します。

# LED ピンのマルチプレクス

内部マルチプレクサは、LED\_1ピンで LED\_1信号をイネーブルするよう設定する必要があります。LED\_1 はデフォルトではディスエーブルされており、DIGIO\_LED1\_PINMUX ビットでイネーブルできます(ピン・マルチプレクサ設定 1 レジスタのセクションを参照)。

LED 0 ピンはマルチプレクスする必要はありません。

# LED の極性

$LED_0$ ピンと  $LED_1$ ピンは、LED 極性モード機能を使用して、様々な LED 回路の極性に対応するよう設定できます(LED 極性 レジスタのセクションを参照)。LED ごとに次の 3 つの極性モードが使用できます。

- ▶ オートセンス (デフォルト)

- ▶ アクティブ・ハイ

- ▶ アクティブ・ロー

オートセンス・モードの場合、ADIN1111はパワーアップ時またはリセット時にピンを自動的に検出し、適切な極性設定を選択します。アクティブ・ハイ・モードの場合、ADIN1111はアノード側から LED を駆動するよう設定されます。アクティブ・ロー・モードの場合、ADIN1111はカソード側から LED を駆動するよう設定されます。

回路例については、LED回路例のセクションで説明します。

#### LED モード

$LED_0$ および  $LED_1$  のアクティビティ動作は、次の 2 つの LED モードを使用して設定できます。

- ▶ LED モード 1: 点滅のデューティ・サイクルは、それぞれ、 LED0\_BLINK\_TIME\_CNTRL レジスタ(LED\_0 オン/オフ点 滅 時間 レ ジ ス タ の セ ク シ ョ ン を 参 照 ) お よ び LED1\_BLINK\_TIME\_CNTRL レジスタ(LED 1 オン/オフ点 滅時間レジスタのセクションを参照)を用いて定義されます。

- ▶ LED モード 2: 点滅のデューティ・サイクルは、アクティビ ティ・レベル (%) に基づき、ADIN1111 によって自動的に 定義されます。

# リンク・ステータス・ピン

$LINK_ST$  ピンは、リンク・ステータス・ビット (AN\_LINK\_STATUS) がアサートされた場合にハイにアサートされ、ADIN1111とそのリンク・パートナーの間のリンクがアクティブになったことを示します。

デフォルトでは、LINK\_ST 信号はアクティブ・ハイであり、 DIGIO\_LINK\_ST\_POLARITY ビットを用いてアクティブ・ハイ またはアクティブ・ローに設定できます(ピン・マルチプレク サ設定1レジスタのセクションを参照)。

# パワーダウン・モード

ADIN1111 は次の2種類のパワーダウン・モードに対応しています。

- ▶ ハードウェア・パワーダウン

- ▶ ソフトウェア・パワーダウン

消費電力が最小になるモードはハードウェアのパワーダウン・モードであり、その場合、デバイスは完全にオフになり、アクセスできなくなります。

# ハードウェア・パワーダウン・モード

ハードウェア・パワーダウン・モードは、ADINI111の動作が不要で、消費電力を最小限に抑える必要がある場合に使用できます。RESETピンをアサートしてローに保持すると、ADINI111はハードウェア・パワーダウン・モードに入ります。このモードでは、すべてのアナログ回路とデジタル回路がディスエーブルされ、クロックはゲート・オフされ、すべてのI/Oピンがトライステート・モードに保持されて、唯一の電力は回路の漏れ電力となります。このモードでは、管理レジスタにはアクセスできません。

# ソフトウェア・パワーダウン・モード

ソフトウェア・パワーダウン・モードは、リンクを確立する前に ADIN1111 のレジスタを設定するために使用できます。 ADIN1111 は、SWPD\_ENピンを使ってリセット後にソフトウェア・パワーダウン・モードになるよう設定できます。また、ADIN1111 には、ソフトウェア・パワーダウン・ビット (CRSM\_SFT\_PD) をセットすることで、ソフトウェア・パワーダウン・モードになるよう命令を送ることもできます。

ソフトウェア・パワーダウン・ステータス・ビット (CRSM\_SFT\_PD\_RDY) は、デバイスがソフトウェア・パワーダウン状態にあることを示します。ソフトウェア・パワーダウン・モードでは、アナログ回路とデジタル回路は低消費電力状態になりますが、PLL はアクティブなままで、設定によっては出力クロックを供給できます。MDI ピンの信号またはエネルギーは無視され、リンクは確立しません。管理インターフェース・レジスタにはアクセスが可能で、ソフトウェアによりデバイスを設定できます。CRSM\_SFT\_PD ビットをクリアすると、ADIN1111はソフトウェア・パワーダウン・モードを終了します。この時点で、MAC-PHY はオート・ネゴシエーションを開始し、完了後にリンクの確立を試みます。

analog.com.jp Rev. A | 15 of 109

# ハードウェア設定ピン

ADIN1111は、ハードウェア設定ピンを使用して、アンマネージド構成またはマネージド構成で動作できます。

ハードウェア設定ピンは、代替のブートストラップ機能を備えた標準的なピンです。ADIN1111 は、パワーアップ後、ハードウェア・リセット後、またはソフトウェア・リセット後、直ちにハードウェア設定ピンのレベルを読み出し、それに応じてPHY 設定を構成します。ADIN1111 がアクティブになると、直ちにPHYでリンクの確立を試み、ハードウェア設定ピンはメインのピン機能として使用できるようになります。これらのピンは、アンマネージド構成またはマネージド構成で使用できます。

アンマネージド構成とは、ADIN1111の PHY パラメータがハードウェア設定ピンで設定されていることを意味します。このモードは、システムが、ソフトウェア制御を必要とせずにADIN1111のポート設定を静的に構成する必要がある場合に使用できます。

マネージド構成とは、SPI を介してソフトウェアにより ADIN1111の全制御を行うことを意味します。PHY および MAC 層はソフトウェアで設定できます。ハードウェア設定ピンは、外部ホストに接続することも、プルアップ/プルダウン抵抗を使ってハードウェア設定することもできます。ホスト・コントローラがアクティブな場合、パワーアップ後、ハードウェア・リセット後、またはソフトウェア・リセット後、ADIN1111の設定をハードウェア・ピンでオーバーライドできます。

# ハードウェア設定ピンの機能

ADIN1111のハードウェア設定ピンで以下の機能を設定できます。

- ▶ リセット後のソフトウェア・パワーダウン・モード

- ▶ 送信振幅の設定

- ▶ リーダー/フォロアの選択

- ▶ SPIプロトコルの設定

すべてのハードウェア設定ピンには、内部プルダウン抵抗があります。これらのピンに外部抵抗を接続しないデフォルト動作モードを表 10 に示します。代替動作モードが必要な場合は、 $4.7 \mathrm{k}\Omega$  のプルアップ抵抗を使用してください。

表 10. デフォルトのハードウェア設定モード

| Hardware Configuration Pin Function     | Default Mode                                |

|-----------------------------------------|---------------------------------------------|

| Software Power-Down Mode after<br>Reset | PHY in software power-down mode after reset |

| Leader/Follower Selection               | Prefer follower                             |

| Transmit Amplitude                      | 1.0 V p-p and 2.4 V p-p                     |

| SPI Protocol Configuration              | OPEN Alliance protocol with protection      |

#### 表 11. ハードウェア設定ピンの推奨制御

| Required Pin<br>Level | Managed Configuration<br>Options                                    | Unmanaged Configuration Options                       |

|-----------------------|---------------------------------------------------------------------|-------------------------------------------------------|

| High                  | 4.7 kΩ external pull-up resistor Host GPIO output high <sup>1</sup> | 4.7 kΩ external pull-up resistor                      |

| Low                   | External pull-down resistor<br>Host GPIO output low <sup>1</sup>    | External pull-down resistor Floating pin <sup>2</sup> |

#### 表 11. ハードウェア設定ピンの推奨制御(続き)

| Required Pin<br>Level | Managed Configuration<br>Options                           | Unmanaged Configuration Options |

|-----------------------|------------------------------------------------------------|---------------------------------|

|                       | Host GPIO tristated <sup>2</sup> Floating pin <sup>2</sup> |                                 |

<sup>1</sup> 低抵抗値の直列抵抗を推奨します。

# リセット後のソフトウェア・パワーダウン

リセット後にソフトウェア・パワーダウン・モードに入らないように ADIN1111 を設定している場合、リセット解除後にオート・ネゴシエーションを開始し、完了後にリンクの確立を試みます。リセット後にソフトウェア・パワーダウン・モードに入るように ADIN1111 を設定している場合、SPI 経由で設定されるまでソフトウェア・パワーダウン・モードのまま待機します。この時点で、PHY の構成はソフトウェアによってソフトウェア・パワーダウンを終了するように設定できます。

表 12. ソフトウェア・パワーダウン (ハードウェア構成)

| Software Power-Down Configuration      | SWPD_EN |

|----------------------------------------|---------|

| PHY in software power-down after reset | 0       |

| PHY not in software power-down         | 1       |

# リーダー/フォロアの優先順位

MS\_SEL ハードウェア設定ピンは、TS\_TIMER ピンと共有され、リーダー/フォロアのデフォルトの選択を設定します。パワーアップ時またはリセット時に MS\_SEL がローにプルダウンされていると、デバイスはデフォルトでフォロア優先に設定されます(内部プルダウン抵抗があるため、外部プルアップ抵抗がMS\_SEL ピンに接続されていない場合に該当)。パワーアップ時またはリセット時に MS\_SEL がハイにプルアップされていると、デバイスはデフォルトでリーダー優先に設定されます。

オート・ネゴシエーションがディスエーブルされている場合、MS\_SEL がデフォルトのリーダー/フォロア選択を行います。ADIN1111ではオート・ネゴシエーションはデフォルトでイネーブルされており、常にイネーブルしておくことを強く推奨します。

オート・ネゴシエーション中、フォロア優先が選択され、リモート端がリーダー優先またはリーダー強制の場合、ローカルPHYはフォロアに(リモート側はリーダーに)設定されます。リモート端がフォロア優先またはフォロア強制の場合、ローカルPHYはリーダーに(リモートはフォロアに)設定されます。

表 13. リーダー/フォロアの選択 (ハードウェア設定)

| Leader/Follower Selection | MS_SEL |

|---------------------------|--------|

| Prefer Follower Selection | 0      |

| Prefer Leader Selection   | 1      |

analog.com.jp Rev. A | 16 of 109

<sup>2</sup>外部プルダウン抵抗を推奨します。

#### ハードウェア設定ピン

#### 送信振幅

TX2P4\_ENハードウェア設定ピンを用いると、目的のアプリケーションに必要な送信振幅モードをユーザが設定できます(表 14 参照)。 $\overline{TX2P4\_EN}$ がローにプルダウンされている場合、ADIN1111は、デフォルトで 1.0V p-p と 2.4V p-p の両方の送信レベルをサポートし、使用するレベルはオート・ネゴシエーションによって決定されます。 $\overline{TX2P4\_EN}$ がハイにプルアップされている場合、ADIN1111はデフォルトで 2.4V p-p の送信動作モードをディスエーブルし、1.0V p-p の送信レベルでのみ動作するよう設定されます。 $\overline{TX2P4\_EN}$ がハイ(1.0V p-p のみ)に接続されている場合、SPIを介して関連するレジスタを変更することはできません。例えば、ADIN1111がハードウェア・ピンで 1.0V p-p レベルのみのモードに設定されている場合、2.4V p-p での動作はできません。

1.0V p-p の送信動作モードは、1.8V の低い AVDD\_H 電源電圧でも動作できます。

一方、2.4V p-p の高電圧の送信動作モードは、3.3V の高い AVDD\_H 電源電圧を必要とします。このモードは、ノイズ・レベルが高い産業用イーサネット環境で長いケーブルを使用する場合に適しています。

表 14. 送信振幅の設定(ハードウェア設定)

| Transmit Amplitude Selection | TX2P4_EN |

|------------------------------|----------|

| 1.0 V p-p or 2.4 V p-p       | 0        |

| 1.0 V p-p                    | 1        |

#### SPI プロトコルの設定

ADIN1111 では、CRC ありまたは CRC なしの汎用 SPI プロトコル、保護ありまたは保護なしの OPEN Alliance SPI プロトコルを使用できます。

表 15. SPI プロトコル(ハードウェア設定)

| SPI Protocol                     | SPI_CFG1 | SPI_CFG0 |

|----------------------------------|----------|----------|

| OPEN Alliance with Protection    | 0        | 0        |

| OPEN Alliance Without Protection | 0        | 1        |

| Generic SPI with 8-bit CRC       | 1        | 0        |

| Generic SPI Without 8-bit CRC    | 1        | 1        |

analog.com.jp Rev. A | 17 of 109

#### 10BASE-T1L リンクの確立

# アンマネージド PHY 動作

アンマネージド PHY アプリケーション、または PHY のソフトウェア・マネージメントが行われない簡易マネージド PHY アプリケーションでは、ハードウェア設定ピンが動作モードを決定します。 $\overline{TX2P4\_EN}$ ピンは、PHY が 1.0V p-p および 2.4V p-p の両方の送信レベル動作に対応することをアドバタイズする、または 1.0V p-p 送信レベル動作にのみ対応することをアドバタイズするよう設定できます。 $MS\_SEL$  ピンを用いると、フォロア優先またはリーダー優先をアドバタイズするよう PHY を設定できます。リセットが解除されたときに PHY がソフトウェア・パワーダウン・モードにならないよう、パワーアップ時およびリセット時に $\overline{SWPD\_EN}$ ピンをプルアップする必要があります。PHY のリセットが解除されると、ADIN1111 はオート・ネゴシエーションを開始し、完了後にリンクの確立を試行します。

簡易マネージド PHY では、ハードウェア設定ピンで PHY の動作を決定し、10BASE-TIL のリンクを確立できます。その後、ソフトウェアによって PHY の動作をモニタできます。

# マネージド PHY 動作

マネージド PHY アプリケーションでは、管理インターフェースを用いて PHY の動作を設定します。ハードウェア設定ピンを用いると、送信振幅やリーダー/フォロア設定を制御するレジスタのデフォルト値を設定できます。リセットが解除されたときに PHY がソフトウェア・パワーダウン・モードになるよう、パワーアップ時およびリセット時にSWPD\_ENピンをプルアップする必要があります。ソフトウェアが PHY を設定してソフトウェア・パワーダウン・モードを解除し、オート・ネゴシエーションを開始してリンクの確立を試行するまで、PHY はソフトウェア・パワーダウン・モードを維持します。

# パワーアップおよびリセットの完了

MACがリセットを終了したことを確認するには、PHY識別レジスタ (PHYID) を読み出します。レジスタのリセット値 (0x283BC91) が読み出せる場合は、デバイスはリセットを終了し、設定の準備が整っています。

次に、ホストは、STATUSO レジスタを読出し、RESETC フィールドが1であることを確認する必要があります。RESETCフィールドが0で、CONFIGO レジスタの SYNC フィールドが1の場合、MAC-PHY は既にホストによって設定済みであり、リセットされていない点に注意してください。この状態は、ホストがリセットされていても MAC-PHY はリセットされていないことを示している可能性があります。

STATUSO レジスタの RESETC フィールドに 1 を書き込んでこの フィールドをクリアすると、割込みピンがハイにアサートされます。

STATUS0 レジスタの PHYINT フィールドもアサートされます。このフィールドをクリアするには、対応するステータス・レジスタである PHY\_SUBSYS\_IRQ\_STATUS および CRSM\_IRQ\_STATUS をクリアあるいはマスクする必要があります。

システム・レディ・ビット (CRSM\_SYS\_RDY) も読み出すことができ、スタートアップ・シーケンスが完了しシステムの通常動作の準備が整っていることを確認できます。

ソフトウェア・パワーダウン・ステータス・ビット (CRSM\_SFT\_PD\_RDY) を読み出すことで、デバイスがソフトウェア・パワーダウン状態になっているかどうかを確認できます。このビットはSWPD\_ENハードウェア設定ピンによって設定されます。

#### MAC の初期化

パワーアップまたはリセット後、ADIN1111の MAC を設定します。必要に応じ IMASK0 レジスタと IMASK1 レジスタに書込みを行って割込みをイネーブルします。

CONFIGO および CONFIG2 に書き込むと、必要な MAC 機能を セットアップできます。例えば、OPEN Alliance のチャンク・サ イズを設定したり、必要に応じてカット・スルーをイネーブル したりできます。

MACを設定した後、CONFIGO レジスタの SYNC フィールドに 1 を書き込むことで、MAC 設定が完了したことを通知できます。

#### デバイスをリンク用に設定

パワーアップまたはリセット後、ADINIIII の PHY をリンクに 必要な動作に設定します。ADINIIIIは、ハードウェア設定ピン によってリンクに必要な設定が既に行われている場合もありますが、管理レジスタを使用することで、より柔軟な制御が可能になります。

オート・ネゴシエーション・プロセスを使用すると、ローカル PHY とリモート PHY の動作モードを一致させることができます。 例えば、オート・ネゴシエーションを使用すると、どのデバイ スがリーダーとして、どのデバイスがフォロアとして動作する かというモードを確実に一致させることができます。オート・ ネゴシエーションは、2 つの PHY 間で送信レベルを一致させる こともできます。

ADIN1111ではオート・ネゴシエーションはデフォルトでイネーブルされており、常にイネーブルしておくことを強く推奨します。オート・ネゴシエーションはIEEE 規格で定義され、PHY同士の堅牢なリンク動作を確保するためのメカニズムを多数備えており、リンクを最も速く確立できる方法です。

#### 送信レベル動作モードのアドバタイズ

10BASE-T1L 高電圧送信アビリティ読出し専用レジスタ・ビット (B10L\_TX\_LVL\_HI\_ABLE) が 1 にセットされ、AVDD\_H ピンに 3.3V の電源が供給されている場合、ADIN1111 は 1.0V p-pと 2.4V p-p のどちらの送信レベル動作にも対応します。送信レベルが高いほど長距離伝送に対応できますが、消費電力も大きくなります。ADIN1111 は、AVDD\_H ピンの電圧が 1.8V の場合、非常に低い消費電力で 1.0V p-p の送信レベル動作に対応できます

ADIN1111 は、1.0V p-p および 2.4V p-p の両方の送信レベル動作に対応する(B10L\_TX\_LVL\_HI\_ABLE=1 の場合)ことをアドバタイズするよう設定することも、1.0V p-p 送信レベル動作にのみ対応することをアドバタイズするよう設定することもできます。この設定を行うには、BASE-T1 オート・ネゴシエーション・アドバタイズメント・レジスタにある 10BASE-T1L ハイ・レベル送信動作モード・アビリティ・ビット( $AN_ADV_B10L_TX_LVL_HI_ABL$ )を用います。0 は 1.0 V p-p 送信レベルのみのモードに対応し、1 は 1.0V p-p と 2.4V p-p の両方の送信レベルに対応します。

analog.com.jp Rev. A | 18 of 109

#### 10BASE-T1L リンクの確立

また、ADIN1111は2.4V p-p 送信レベル動作のリクエストをアドバタイズするよう設定することもできます(B10L\_TX\_LVL\_HI\_ABLE = 1 の場合)。この設定は、10BASE-T1L ハイ・レベル送信動作モード・リクエスト・ビット(AN\_ADV\_B10L\_TX\_LVL\_HI\_REQ)を用いて行います。0は1.0 V p-p 送信レベルをリクエストし、1は2.4V p-p の送信レベルをリクエストします。

リンク・パートナーがアドバタイズした送信レベル・アビリティは、リンク・パートナーの 10BASE-TIL ハイ・レベル送信動作モード・アビリティ・レジスタ・ビット  $(AN\_LP\_ADV\_B10L\_TX\_LVL\_HI\_ABL)$  で読み出せます。リンク・パートナーがアドバタイズした送信レベル・リクエストは、リンク・パートナーの 10BASE-TIL ハイ・レベル送信動作モード・リクエスト・レジスタ・ビット  $(AN\_LP\_ADV\_B10L\_TX\_LVL\_HI\_REQ)$  で読み出せます。これらのビットは、オート・ネゴシエーション・プロセス中に更新され、オート・ネゴシエーション完了レジスタ・ビット  $(AN\_COMPLETE)$  がセットされると有効になります。

ローカル PHY またはリモートの PHY のいずれかがハイ・レベル (2.4V p-p) 送信動作モードに対応していないことをアドバタイズする場合、または、ローカル PHY とリモート PHY のどちらもハイ・レベル (2.4V p-p) 送信動作モードを要求するアドバタイズをしない場合は、1.0V p-p 送信レベルで動作します。

ローカルおよびリモートのどちらの PHY もハイ・レベル (2.4V p-p) 送信動作モードで送信できることをアドバタイズしている場合で、かつ、ローカルまたはリモートの PHY がハイ・レベル (2.4V p-p) 送信動作モードのリクエストをアドバタイズしている場合、2.4V p-p 送信レベルでの動作になります。

したがって、一方の PHY が 1.0V p-p 送信レベルで動作しなくてはならないようにすることは確実にできますが、2.4V p-p 送信レベルでの動作はリクエストすることしかできません。

表 16. オート・ネゴシエーションによる送信レベルの決定 1

| HI_ABL <sup>2</sup> | HI_REQ | LP_HI_ABL | LP_HI_REQ | Transmit Level |

|---------------------|--------|-----------|-----------|----------------|

| 0                   | Х      | 0         | Х         | 1.0 V p-p      |

| 1                   | X      | 0         | X         | 1.0 V p-p      |

| 0                   | X      | 1         | X         | 1.0 V p-p      |

| 1                   | 0      | 1         | 0         | 1.0 V p-p      |

| 1                   | 0      | 1         | 1         | 2.4 V p-p      |

| 1                   | 1      | 1         | 0         | 2.4 V p-p      |

| 1                   | 1      | 1         | 1         | 2.4 V p-p      |

|                     |        |           |           |                |

¹Xは、ドント・ケアを意味します。

AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL、AN\_ADV\_B10L\_TX\_LVL\_HI\_REQを指します。

# リーダー/フォロアのアドバタイズメント

10BASE-TIL 規格では、リーダー/フォロア・クロック・スキームと呼ばれるスキームを使用します。このスキームは、一般的にエコー・キャンセルを用いる全2重トランシーバ規格で使用されています。1つのPHYがリーダーに、他方のPHYがフォロアに指定されます。どちらのPHYがリーダーでどちらのPHYがフォロアになるかは、オート・ネゴシエーションで決まります。一般的にはどちらがどちらになっても重要ではありません。

ADIN1111のMS\_SELピンには内部プルダウン抵抗があり、PHYをフォロア優先でアドバタイズするようデフォルト設定されています。フォロア優先アドバタイズのデフォルト設定をそのまま使用するか、リーダー優先アドバタイズに設定することを推奨します。

PHY がリーダーとして動作することが必須である場合は、リーダー強制アドバタイズ設定を使用してください。ただし、この設定を使用する場合は注意が必要です。リモート端もリーダー強制に設定されていると、設定フォルトが生じ、オート・ネゴシエーションが失敗し、リンクが確立できなくなります。

強制 リーダー/フォロア 設定 レジスタ・ビット  $(AN\_ADV\_FORCE\_MS)$  を使用すると、リーダー/フォロア 設定を優先としてアドバタイズするか、強制値としてアドバタイズするかを次のように設定できます。0 ではリーダー/フォロア設定が優先モード、1 ではリーダー/フォロア設定が強制モードになります。

リーダー/フォロア設定レジスタ・ビット (AN\_ADV\_MST) を用いると、リーダー/フォロア設定をアドバタイズするよう PHY を設定できます。0ではフォロア、1ではリーダーです。

リンク・パートナーがアドバタイズするリーダー/フォロア設定は、リンク・パートナー強制リーダー/フォロア設定レジスタ・ビット(AN\_LP\_ADV\_FORCE\_MS)およびリンク・パートナー・リーダー/フォロア設定レジスタ・ビット(AN\_LP\_ADV\_MST)で読み出すことができます。これらのビットは、オート・ネゴシエーション・プロセス中に更新され、オート・ネゴシエーション完了レジスタ・ビット(AN COMPLETE)がセットされると有効になります。

ローカルPHYとリモートPHYの優先設定が同じ場合(例えば、どちらもフォロアまたはどちらもリーダー)、ランダム・プロセスでどちらをリーダー、どちらをフォロアにするかを決定します。一方のPHYが強制設定の場合は、両方のPHYが同じリーダー/フォロア設定であっても、その強制設定が優先されます。どちらのPHYも強制設定され同じリーダー/フォロア設定である場合には、設定フォルトが発生し、オート・ネゴシエーションは失敗します。

リーダー/フォロアの決定結果は、リーダー/フォロア決定結果レジスタ・ビット(AN\_MS\_CONFIG\_RSLTN)を読み出すことで確認できます。この結果は、PHY がフォロアかリーダーか、または、設定フォルトが発生しているかを示します。これらのビットは、オート・ネゴシエーション・プロセス中に更新され、オート・ネゴシエーション 完了 レジスタ・ビット(AN COMPLETE)がセットされると有効になります。

analog.com.jp Rev. A | 19 of 109

<sup>&</sup>lt;sup>2</sup> HI\_ABL、HI\_REQ、LP\_HI\_ABL、LP\_HI\_REQ は、それぞれ、アドバタ イズ・ビット AN\_LP\_ADV\_B10L\_TX\_LVL\_HI\_ABL、

AN\_LP\_ADV\_B10L\_TX\_LVL\_HI\_REQ,

#### 10BASE-T1L リンクの確立

表 17. オート・ネゴシエーションによるリーダー/フォロアの決定1

| Local           |            | Rei                | Remote        |                     | Remote              |

|-----------------|------------|--------------------|---------------|---------------------|---------------------|

| AN_ADV_FORCE_MS | AN_ADV_MST | AN_LP_ADV_FORCE_MS | AN_LP_ADV_MST | Leader/Fol          | lower Resolution    |

| 0               | 0          | 0                  | 0             | Leader/Follower     | Follower/Leader     |

| )               | 0          | 0                  | 1             | Follower            | Leader              |

| )               | 1          | 0                  | 0             | Leader              | Follower            |

| )               | 1          | 0                  | 1             | Leader/Follower     | Follower/Leader     |

| )               | X          | 1                  | 0             | Leader              | Follower            |

| )               | X          | 1                  | 1             | Follower            | Leader              |

| 1               | 0          | 0                  | X             | Follower            | Leader              |

| 1               | 1          | 0                  | X             | Leader              | Follower            |

| 1               | 0          | 1                  | 0             | Configuration Fault | Configuration Fault |

| 1               | 0          | 1                  | 1             | Follower            | Leader              |

|                 | 1          | 1                  | 0             | Leader              | Follower            |

|                 | 1          | 1                  | 1             | Configuration Fault | Configuration Fault |

¹Xは、ドント・ケアを意味します。

# オート・ネゴシエーションの完了

オート・ネゴシエーションが完了すると、オート・ネゴシエーション完了指示レジスタ・ビット(AN\_LINK\_GOOD)がセットされます。このビットは、オート・ネゴシエーション送信が完了したこと、イネーブルされた PHY 技術がリンクを確立中、または既に確立済みであることを示します。

オート・ネゴシエーションが完了しリンクが確立すると、オート・ネゴシエーション完了レジスタ・ビット(AN\_COMPLETE)が設定されます。このビットが 1 として読み出された場合、オート・ネゴシエーションが完了して PHY リンクが確立しており、AN\_ADV\_ABILITY レジスタ・ビットと AN\_LP\_ADV\_ABILITY レジスタ・ビットの内容が有効であることを示します。

#### リンク・ステータス

リンクのステータスは、リンク・ステータス・レジスタ・ビット (AN\_LINK\_STATUS) を読み出すことで判定できます。このビットはローにラッチされます。

このビットが 1 の場合、有効なリンクが確立されていることを示します。

このビットが 0 の場合は、最後の読出し以降にリンクが切断されています。このビットの読出し値が 0 の場合、リンク・ステータスを確認するために再度読み出す必要があります(ラッチ・ロー・レジスタのセクションを参照)。

リンクが切断されると、オート・ネゴシエーション・プロセスは自動的に再起動します。オート・ネゴシエーションは、オート・ネゴシエーション制御レジスタ(AN\_CONTROL)のオート・ネゴシエーション再起動ビット(AN\_RESTART)に書き込むことで要求し、再起動できます。

analog.com.jp Rev. A | 20 of 109

# オン・チップ診断

# ループバック・モード

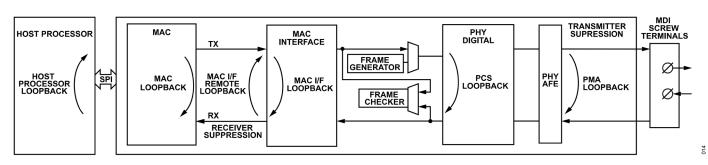

MAC-PHY の PHY コアには、以下のループバック・モードがあります。

- ▶ 物理メディア・アタッチメント (PMA) ループバック

- ▶ 物理コーディング・サブレイヤ (PCS) ループバック

- ▶ MACインターフェース・ループバック

- ▶ MACインターフェース・リモート・ループバック

これらのループバック・モードは、PHY内の様々な機能ブロックをテストおよび検証します。内蔵のフレーム・チェッカとフレーム・ジェネレータを使用すると、PHYコア内のデジタルおよびアナログ・データ・パスを完全に自己完結型でインサーキット・テストできます。必要なソフトウェアをホスト・プロセッサに実装することで、(PHYコアのみに限定されることなく)ADIN1111のMAC部を含むループバックを確立することもできます。

#### PMA ループバック

PMA ループバックの場合、MDI ピンをオープン・サーキットのままにして、未終端のコネクタまたはケーブルに送信します。最も正確な結果を得るためには、ケーブルを接続しないでおきます。PHY は、自身の送信からの反射を受信することで動作します。このループバックは、IEEE 802.3cg 規格副条項 146.5.6 のPMA ローカル・ループバックの実装を目的としたものです。

なお、10BASE-T1Lの PMA ループバックの場合、デバイスは強制リンク設定モード(オート・ネゴシエーションはディスエーブル)に設定する必要があります。B10L\_LB\_PMA\_LOC\_ENビット(B10L\_PMA\_CNTRL レジスタ)を設定すると、PMAループバックがイネーブルされます。

# PCS ループバック

PCS ループバック・モードは、PHY デジタル・ブロックの入力 段にある PCS ブロック内で送信データをレシーバにループバッ クします。B10L\_LB\_PCS\_EN ビット(B10L\_PCS\_CNTRL レジ スタ)を設定すると PCS ループバックがイネーブルされます。 PCS ループバック・モードがイネーブルされている場合、MDI ピンには信号が送信されません。

# MAC インターフェース・ループバック

MAC インターフェース・ループバック・モードでは、MAC インターフェースで受信したデータを SPI ホストにループバックします。MAC\_IF\_LB\_EN ビット(MAC\_IF\_LOOPBACK レジスタ)を設定すると MAC インターフェース・ループバックがイネーブルされます。同じレジスタ内のMAC\_IF\_LB\_TX\_SUP\_EN ビットがセットされている場合(デフォルトでセット)、MDI ピンへの信号の伝送が抑制されます。

# MAC インターフェース・リモート・ループバック

MAC インターフェース・リモート・ループバックでは、リモート PHY とのリンク・アップが必要で、リモート PHY から受信したデータを再びリモート PHY にループバックできます。このリンクを行うと、リモート PHY が適切なデータを受信することを確認することにより、リンクが完全であることをリモート PHY が検証できます。 MAC\_IF\_REM\_LB\_EN ビット(MAC\_IF\_LOOPBACK レジスタ)をセットすると、MAC インターフェース・リモート・ループバックが可能になります。同じレジスタ内でMAC\_IF\_REM\_LB\_RX\_SUP\_EN ビットされていると(デフォルトでセット)、PHY が受信したデータは抑制され MAC には送信されません。

# MAC ループバック

MAC ループバックでは、MAC 送信チャンネルで受信したデータを SPI ホストにループバックします。MAC ループバックは PI LOOP レジスタでイネーブルされます。

#### ホスト・プロセッサ・ループバック

ADIN1111 内の PHY コアに関連するループバック・モード以外に、ホスト・プロセッサを使用して完全なMACループバックを作成できます。完全な MAC ループバックでは、図 13 に示すように、MAC から受信したフレームはすべて MAC に戻されます。

図 13. ADIN1111 のループバック・モード

analog.com.jp Rev. A | 21 of 109

# オン・チップ診断

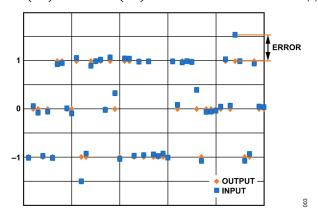

# フレーム・ジェネレータとフレーム・チェッカ

ADINI111は、フレームを生成し、受信したフレームを確認するように構成できます(図 14 を参照)。フレーム・ジェネレータとフレーム・チェッカを個別に使用して、フレームの生成またはフレームの確認ができます。あるいは、フレーム・ジェネレータとフレーム・チェッカを一緒に使用して、フレームの生成とフレームの確認を同時に行うことができます。フレームをリモート・エンドでループバックさせると、フレーム・チェッカを使用して ADIN1111 が生成したフレームを確認できます。

フレーム・ジェネレータをイネーブルした場合、PHY のデータ・ソースはMACではなくフレーム・ジェネレータから取得されます。

フレーム・ジェネレータの制御レジスタでは、送信するフレームのタイプ(ランダム・データやすべて 1 など)、フレーム長、および生成するフレーム数を設定します。

要求されたフレームの生成は、フレーム・ジェネレータをイネーブルする( $FG_EN$ )ことから始めます。フレームの生成が完了すると、フレーム・ジェネレータ完了ビットがセットされます( $FG_DONE$ )。

フレーム・チェッカは、フレーム・チェッカ・イネーブル・ビット(FC\_EN)を使用してイネーブルします。フレーム・チェッカは、MAC インターフェースまたは PHY のいずれかから受信したフレームを確認および分析するよう設定できます。これは、フレーム・チェッカ送信選択ビット(FC\_TX\_SEL)を使用して設定します。フレーム・チェッカは、受信したフレーム数、CRC エラー、およびその他の様々なフレーム・エラーを通知します。フレーム・チェッカ・フレーム・カウンタ・レジスタおよびフレーム・チェッカ・エラー・カウンタ・レジスタが、これらのイベントをカウントします。

フレーム・チェッカは CRC エラー数をカウントし、これらは受信エラー・カウンタ・レジスタ (RX\_ERR\_CNT) で通知されます。フレーム・チェッカ・エラー・カウンタとフレーム・チェッカ・フレーム・カウンタ間の同期を確保するために、受信エラー・カウンタ・レジスタが読み出されると、すべてのカ

ウンタがラッチされます。したがって、フレーム・チェッカを使用する際は、最初に受信エラー・カウンタを読み出し、次に他のすべてのフレーム・カウンタとエラー・カウンタを読み出します。受信フレーム・カウンタ・レジスタのラッチされたコピーは、FC\_FRM\_CNT\_HレジスタとFC\_FRM\_CNT\_Lレジスタで利用できます。

フレーム・チェッカは、CRC エラーに加えて、フレーム長エラー、フレーム・アライメント・エラー、シンボル・エラー、オーバーサイズ・フレーム・エラー、アンダーサイズ・フレーム・エラーをカウントします。フレーム・チェッカは、受信したフレームの他、フレーム内のニブル数が奇数であるフレームをカウントし、また、プリアンブル内のニブル数が奇数であるパケットをカウントします。フレーム・チェッカはまた、偽キャリア・イベント数(不正なストリーム開始区切り(SSD:start of stream delimiter)状態に入った回数)もカウントします。

# 2つの MAC-PHY を使用したリモート・ループバック によるフレーム・ジェネレータとフレーム・チェッカ

2つの MAC-PHY デバイスを使用すると、PHY コアから PHY コアへの接続を自己完結型で簡便に検証する方法を構成できます。あるいは、ホスト・プロセッサを用いてリモート端でループバックを実行することにより、完全なシグナル・チェーンを構成できます。図 14 に、各 MAC-PHY の設定概要を示します。外部ケーブルを両方のデバイス間に接続し、MAC-PHY 1 がフレーム・ジェネレータを使用してフレームを生成します。

テストを ADINI111 の PHY コア部分だけに限定する場合は、MAC-PHY 2 の MAC インターフェース・リモート・ループバック(MAC\_IF\_REM\_LB\_EN)をイネーブルします。MAC-PHY 1 によって発行されたフレームはケーブルを通って送信され、PHY 2 シグナル・チェーンを通過して PHY 2 MAC リモート・ループバックによって返され、ケーブルを介して再び戻されて、MAC-PHY 1 フレーム・チェッカによって確認されます。あるいは、MAC-PHY 1 からのフレームをリモート・デバイスのホスト・プロセッサまで送信して、そこから、MAC-PHY 2 の MACおよび PHY ブロックを通じてループバックし、MAC-PHY 1 に戻すこともできます。

図 14. セルフ・チェック用に 2 つの PHY 間で使用するリモート・ループバック

analog.com.jp Rev. A | 22 of 109

# オン・チップ診断

#### テスト・モード

ADIN1111 には、IEEE 802.3cg-2019 規格の副条項 146.5.2 に記載されたとおり、PHY ごとに複数のテスト・モードがあり、トランスミッタの波形、歪み、ジッタ、ドループのテストが行えます。これらのテスト・モードは、トランスミッタ回路に供給されたデータ・シンボルのみを変更し、トランスミッタおよびレシーバの電気特性やジッタ特性は通常動作から変わりません。

また、ADIN1111 は副条項 45.2.1.186a.2 に記載された送信ディスエーブル・モードにも対応しています。

表 18. ADIN1111 のテスト・モード一覧

| テスト・モード                                            | 説明                                                                                                                      |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| PMA Test Modes<br>(Subclause 146.5.2)              |                                                                                                                         |

| Test Mode 1                                        | トランスミッタ出力電圧およびタイミング・ジッタのテスト・モード。このモードが選択されている場合、ADIN1111 はデータ・シンボル・シーケンス (+1, -1) を繰り返し送信します。                           |

| Test Mode 2                                        | トランスミッタ出カドループ・テスト・モード。このモードでは、<br>ADIN1111 は 10 個の+1 シンボルを<br>送信し、その後に 10 個の-1 シンボルを<br>比を送信します。このシーケンスは<br>無限に繰り返されます。 |

| Test Mode 3                                        | アイドル・モード・テスト・モード<br>の通常動作。このモードでは、<br>ADIN1111 はデータを通常のフレー<br>ム間アイドル信号に設定し、非テス<br>ト動作時やリーダー・データ・モー<br>ド時と同様に送信します。      |

| Transmit Disable Mode<br>(Subclause 45.2.1.186a.2) | 送信経路と受信経路のどちらも通常動作モードと同じように機能しますが、送信するのは0シンボルのみです。このモードを使用すると、副条項146.8.3で規定されているMDIのリターン・ロスを測定できます。                     |

#### PMA テスト・モード 1~3 を有効化

ADIN1111 の各 PHY は、次の手順を使用していずれかの PMA テスト・モード (テスト・モード  $1\sim3$ ) に設定できます。

- 1. ソフトウェア・パワーダウン・コントロール・レジスタ (CRSM\_SFT\_PD\_CNTRL) の CRSM\_SFT\_PD ビットに 1 を 書き込んで、ソフトウェア・パワーダウン・モードを開始し ます。

- 2. システム・ステータス・レジスタ (CRSM\_STAT) の CRSM\_SFT\_PD\_RDY ビットを読み出し、ADIN1111がソフト ウェア・パワーダウン・モードになっていることを確認します。

- 3. BASE-T1 オート・ネゴシエーション・コントロール・レジスタ (AN\_CONTROL) の AN\_EN ビットに 0 を書き込んで、オート・ネゴシエーションをディスエーブルします。

- 4. オート・ネゴシエーション強制モード・イネーブル・レジスタ (AN\_FRC\_MODE\_EN) の AN\_FRC\_MODE\_EN ビットに 1 を書き込み、オート・ネゴシエーション強制モードをセットします。

- 5. 10BASE-TIL テスト・モード・コントロール・レジスタ (B10L\_TEST\_MODE\_CNTRL) の B10L\_TX\_TEST\_MODE ビットに該当する値を書き込んで、目的のテスト・モードを 選択します。

6. ソフトウェア・パワーダウン・コントロール・レジスタ (CRSM\_SFT\_PD\_CNTRL) の CRSM\_SFT\_PD ビットに 0 を 書き込んで、ソフトウェア・パワーダウン・モードを終了し ます。

表 19. PMA テスト・モードの設定

| PMA Test Mode | B10L_TX_TEST_MODE, Bits[15:13] (Binary) |

|---------------|-----------------------------------------|

| Test Mode 1   | 001                                     |

| Test Mode 2   | 010                                     |

| Test Mode 3   | 011                                     |

# 送信ディスエーブル・モードを有効化

ADIN1111 の各 PHY は、次の手順を使用して送信ディスエーブル・モードに設定できます。

- 1. ソフトウェア・パワーダウン・コントロール・レジスタ (CRSM\_SFT\_PD\_CNTRL) の CRSM\_SFT\_PD ビットに 1 を 書き込んで、ソフトウェア・パワーダウン・モードを開始します。

- 2. システム・ステータス・レジスタ (CRSM\_STAT) の CRSM\_SFT\_PD\_RDY ビットを読み出して、ADIN11111がソフトウェア・パワーダウン・モードに入っていることを確認します。

- 3. BASE-T1 オート・ネゴシエーション・コントロール・レジスタ (AN\_CONTROL) の AN\_EN ビットに 0 を書き込んで、オート・ネゴシエーションをディスエーブルします。

- 4. オート・ネゴシエーション強制モード・イネーブル・レジスタ (AN\_FRC\_MODE\_EN) の AN\_FRC\_MODE\_EN ビットに1を書き込み、オート・ネゴシエーション強制モードをセットします。

- 5. 10BASE-TIL PMA コントロール・レジスタ (B10L\_PMA\_CNTRL)の B10L\_TX\_DIS\_MODE\_EN ビット に1を書き込んで、送信ディスエーブル・モードをセットします。

- 6. ソフトウェア・パワーダウン・コントロール・レジスタ (CRSM\_SFT\_PD\_CNTRL) の CRSM\_SFT\_PD ビットに 0 を 書き込んで、ソフトウェア・パワーダウン・モードを終了し ます。

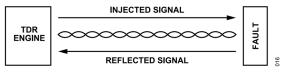

# 時間領域反射率測定(TDR)

10BASE-T1L 準拠の PHY が長いケーブルを通じた通信を可能とするならば、欠陥のあるケーブルのデバッグは、適切なツールなしではコストを要し困難なものになる可能性があります。これを緩和するため、アナログ・デバイセズの 10BASE-T1L 製品では、TDR エンジンを備えています。これは、ケーブルのフォルト検出、フォルト地点までの距離、およびケーブル長の推定を可能にします。

この診断ソリューションは、高精度のオン・チップ TDR エンジンと、ホスト・マイクロコントローラ上で実行される一連のアルゴリズムを組み合わせたもので、広範なケーブルに対応できる最大限の柔軟性と、より高度なケーブル診断機能を実現します。

図 15. ADIN1111 の TDR エンジン

analog.com.jp Rev. A | 23 of 109

# オン・チップ診断

#### TDR エンジンによるフォルト検出

アナログ・デバイセズのアルゴリズムの時間分解能は 8.3ns です。 これは、1m 未満の長さ分解能に相当し、精度 2%で最大 1600m のケーブル長が可能です。

このフォルト・ディテクタ・アルゴリズムは、ADIN1111 が MDI を介して別の PHY に物理的に接続されている場合でも、オープン・フォルトあるいは短絡フォルト状態を検出できます。この場合、リンク・パートナーの PHY が DME ページを送信している可能性があることを意味します。TDR の従来の方法では、他の信号源またはノイズも同じリンクにある場合に、フォルトを検出するのが困難です。これはアナログ・デバイセズのソリューションにはあてはまりません。そのため、このソリューションは、リモート・エンドを制御できない場合のデバッグに適しています。

フォルト検出アルゴリズムは、診断に必要な高レベルの関数を含む C コード・ライブラリとして提供されます。これらの関数は、高度な処理を利用しないよう最適化されているため、低消費電力のマイクロコントローラで実行できます。

フォルト検出には、1 つの関数呼び出しで十分です。関数はフォルトの種類と MDI コネクタからフォルトまでの距離(メートル単位)を返します。

フォルト検出 TDR ライブラリは、ADIN1100、ADIN1110、ADIN2111のランディング・ページ内にあるソフトウェアのセクションからリクエストできます。

#### TDR オフセットのキャリブレーション

ライブラリには、TDR 測定のオフセットをキャリブレーションする関数が含まれています。ライブラリにあるこの関数は、様々な MDI 回路によって信号経路内に変動する遅延が生じ、これによって長さ測定のオフセットが影響を受ける可能性のある場合に有用です。例えば、MDI に絶縁トランスを使用すると、数メートルの長さに匹敵する信号遅延を引き起こす可能性が極めて高くなります。

このキャリブレーションにはフォルト・ディテクタを稼働させる必要はなく、デフォルトで平均値が提供されます。ただし、精度が求められる場合には、ケーブルを短絡させることを推奨します。このキャリブレーションが必要な場合、実験室内で一度、特定の MDI 回路でキャリブレーションを実行し、オフセット値を不揮発性メモリに保存して後で使用することができます。

このキャリブレーションを実行するには、MDI ポートをオープンまたは短絡のままにする必要があります。MDI ポートには負荷やケーブルを接続しないでください。

#### ケーブルのキャリブレーション

デフォルトでは、アルゴリズムは IEEE 802.3cg 規格に準拠した 長距離伝送ケーブルに対応するよう最適化されています。ただし、挿入損失リターン・ロス、信号遅延特性が異なる多様なケーブル・タイプに対応するため、このライブラリには、どのケーブルでも動作できるようアルゴリズムを最適化し、長さをより正確に推定するために公称伝搬速度(NVP)を算出するキャリブレーション関数が備わっています。長さの精度は、主に NVP 値の精度に依存します。

このキャリブレーションを実行するには、既知の長さのケーブルを MDI ポートに接続し、末端をオープンまたは短絡状態にしておく必要があります。NVP 値は一般に 0.5~0.9 の範囲で、ケーブルの構造の特性を表すものです。一般的には約 0.65 の平均 NVP 値が前提とされます。このキャリブレーションは、フォルト・ディテクタを動作させるには不要ですが、高い長さ精度が必要な場合や、標準的でないケーブルを使用する場合には必要となります。与えられたケーブルについて実験室でこのキャリブレーションを行えば、その値を不揮発性メモリに保存できます。

これらの関数の使用に関する詳細については、C コード・ドライバを参照してください。

# フォルトまでの長さ/距離の精度

フォルトまでの距離あるいは長さの測定精度は、主に NVP 値によって決まります。この NVP 値は、NVP キャリブレーションを行うために使用するケーブル長の精度によって決まります。

表 20 には、種類や長さの異なるケーブルに対してフォルトを誘起し、そのフォルトまでの距離を測定した結果を示します。すべての場合について、アルゴリズムは、テスト時に誘起されたオープンまたは短絡状態を正しく検出しています。このテストで用いた Profibus PA ケーブルの NVP 値を大まかに見積もり、同じ値を Cat5E ケーブルおよび Cat6 ケーブルにも使用しています。

表 20. 様々なケーブルに対する長さ推定誤差

|                          | Estimated  | Length    |                    |

|--------------------------|------------|-----------|--------------------|

| Cable Type               | Length (m) | Error (%) | Note               |

| Fieldbus Type A - AWG 18 | 50.2       | 0.7       | NVP calibrated     |

| Fieldbus Type A - AWG 18 | 102.1      | 2.1       | NVP calibrated     |

| Fieldbus Type A - AWG 18 | 403.4      | 0.8       | NVP calibrated     |

| Fieldbus Type A - AWG 18 | 807.6      | 0.8       | NVP calibrated     |

| Fieldbus Type A - AWG 18 | 1045.3     | 1.0       | NVP calibrated     |

| Fieldbus Type A - AWG 18 | 1462.9     | 2.0       | NVP calibrated     |

| Cat5E                    | 133.1      | 2.4       | NVP not calibrated |

| Cat5E                    | 244.4      | 1.8       | NVP not calibrated |

| Cat6                     | 73.6       | 5.1       | NVP not calibrated |

| Cat6                     | 137.2      | 5.6       | NVP not calibrated |

# リンク品質モニタリング

ADIN1100、ADIN1101、ADIN11110、ADIN11111、ADIN2111は、PHY レシーバに示される SN 比 (SNR) に直接関連する、受信信号の平均二乗誤差 (MSE) を測定できます。MSE または SNR は、信号品質インジケータ (SQI) にマッピングでき、10BASE-T1L リンクのセグメント/チャンネル品質の全体的な評価に利用できます。

リンク品質は、ケーブル長、挿入損失、リターン・ロスなどのケーブル特性、ケーブル・シールドの有無や品質、接続状態、ケーブル・セグメント間の相互接続の数や品質、デバイスやケーブル周辺環境のノイズ・レベルなどの影響を受ける可能性があります。そのため、リンク品質はデバイス設計、製品テスト、システムへの導入時、更にはシステムの運用期間全体を通じて有用な情報を提供します。

analog.com.jp Rev. A | 24 of 109

# オン・チップ診断

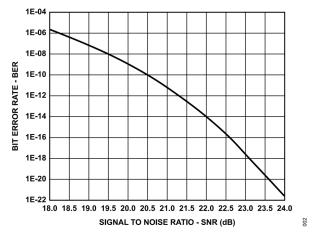

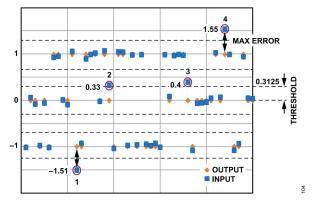

#### S/N 比およびビット・エラー・レート

通信チャンネルの SNR とビット・エラー・レート (BER) の間には統計的な関係があります。ホワイト・ノイズ下における SNR と 10BASE-TIL の BER との関係を図 16 に示します。

図 16. SNR と 10BASE-T1L の BER の間の統計的関係

IEEE 802.3cg-2019 規格は、関連するノイズがある場合でも 10BASE-T1Lの BER が  $10^9$ 以下であることを要求しています。 例えば、BER が  $10^9$ であるということは、連続する 10Mbps のデータにおいて、100秒ごとに 1 ビットのエラーが発生することを意味します。これは、図 16 に示すように、10BASE-T1L PHYでは約 20.0dB の SNR に相当します。

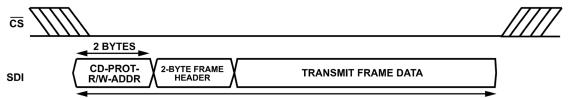

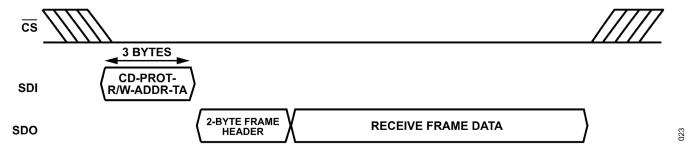

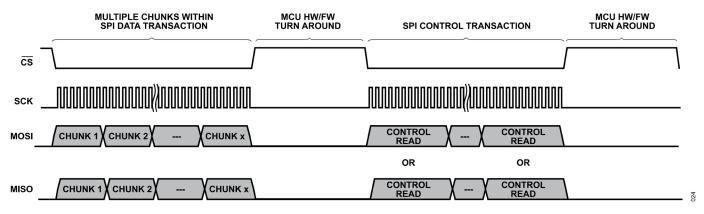

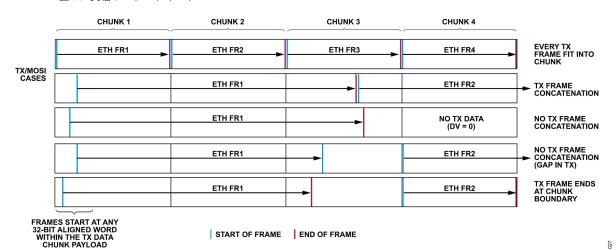

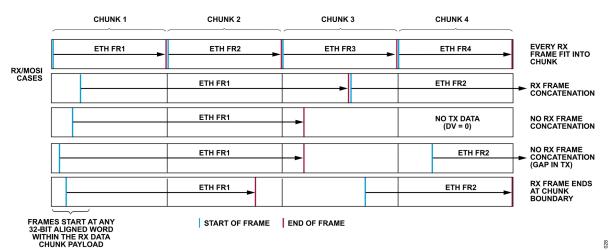

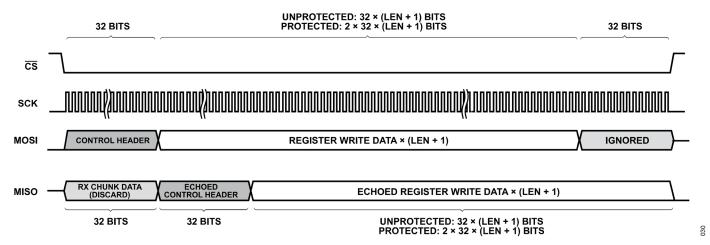

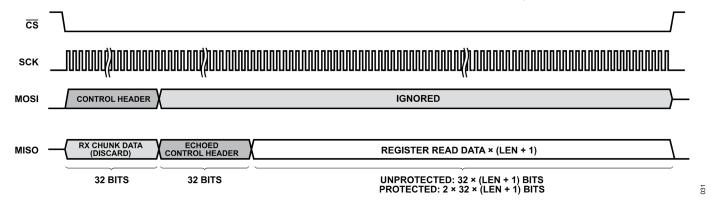

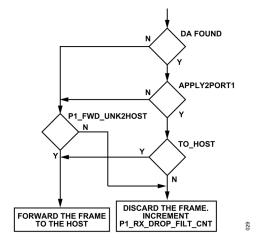

SNR が 21.0dB の場合、BER は  $10^{-11}$  となり、10,000 秒、すなわち 2½時間ごとに 1 ビットのエラーが発生する計算です。SNR が 22.0dB の場合、BER は  $10^{-14}$  となり、115 日に 1 ビットのエラーが発生する頻度に相当します。これらの例は、SNR が 10BASE-T1L イーサネットの信頼性に直結していることを示しています。