# オン抵抗 0.56Ω の高密度オクタル SPST スイッチ

#### 特長

- ▶ オン抵抗 0.56Ω (代表値)

- ▶ 大きな連続電流:最大 768mA

- 信号範囲全域での R<sub>ON</sub> 平坦性: 0.004Ω

- ▶ THD: 1kHz で-127dB

- ▶ デジタル信号および電源のスルー配線ピン

- ▶ 受動部品を内蔵

- ▶ エラー検出付き SPI

- ▶ ブレーク・ビフォア・メークのスイッチング動作が確保 されているため、スイッチを外部で配線することにより マルチプレクサ構成が可能

- ▶ ±20V と+36V ですべてを仕様規定

- ▶ 1.8V ロジックとの互換性あり、2.7V ≤ V<sub>L</sub> ≤ 3.3V (1.8V デバイスへの SPI リードバックを除く)

- ▶ 4mm×5mm×1.63mm、30ピンLGA

### アプリケーション

- ▶ ATE(自動試験装置)

- ▶ ソリッドステート・リレ一部品の置き換え

- ▶ リレー部品の置き換え

- ▶ 計測器

- ▶ データ・アクイジション

- ▶ アビオニクス (航空電子機器)

- ▶ オーディオ/ビデオでのスイッチング

- ▶ 通信システム

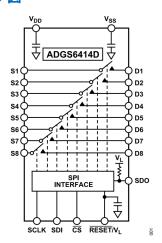

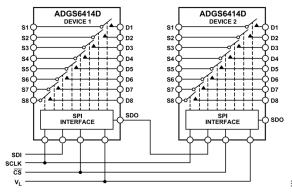

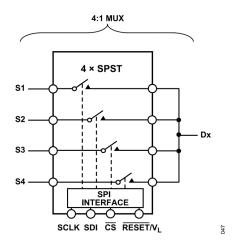

### 機能ブロック図

図 1. 機能ブロック図

### 概要

ADGS6414D<sup>1</sup> は、8 個の独立した低オン抵抗の単極単投(SPST)スイッチを内蔵し、 $4mm \times 5mm$ の 30 ピン LGA パッケージを採用しています。

ADGS6414Dは、プリント回路基板のスペースに制約があるシステムや、既存のシステム・フォーム・ファクタによって拡張が制限されるシステムにおいて、チャンネルの高密度化を実現します。

SPI デイジーチェーン・モードを使用すると、複数のADGS6414Dを組み合わせて、大規模スイッチ・マトリクスや高ファンアウト・アプリケーションなどのチャンネル数が非常に多いシステムを設計する場合に、独自のスルー配線ピンによりスペースを大幅に削減できます。電源デカップリング・コンデンサと SDO プルアップ抵抗を内蔵しているため、スペースを更に削減し、プリント回路基板を簡略化できます。

各スイッチ・チャンネルのオン抵抗が低い(代表値 0.56Ω)ため、放熱性が重要となるシステムでも電流密度を高くできます。また、スイッチ・チャンネルのオン抵抗プロファイルがアナログ入力範囲の全域で非常に平坦なため、高精度アナログ信号のスイッチング時に良好な線形性と低歪みが実現できます。

各スイッチの入力信号範囲は、VssからVpp-2Vです。各スイッチは、オンになると双方向に等しく良好に導通し、オフ状態では電源電圧までの信号レベルをブロックします。

SPIは、巡回冗長検査(CRC)エラーの検出、無効な読出し/書込みアドレスの検出、SCLKカウント・エラーの検出など、強力なエラー検出機能を備えています。

#### 製品のハイライト

- 1. SPI を搭載しているので、パラレル変換やロジック配線パターンの必要がなく、汎用入出力(GPIO)チャンネル数を削減します。

- 2. デイジーチェーン・モードでは、複数のデバイスを使用する 場合にロジック配線パターンを追加する必要がありません。

- 3. デジタル信号および電源のスルー配線により配線が容易になり、チャンネル密度を増加できます。

- 4. 受動部品が内蔵されているため、外付けの受動部品は不要で す。

- 5. CRC エラーの検出、無効な読出し/書込みアドレスの検出、 SCLK カウント・エラーの検出により、デジタル・インター フェースの信頼性が確保されます。

- 6. CRC エラー検出、無効な読出し/書込みアドレスの検出、 SCLK エラー検出などの機能があるため、安全性が不可欠な システムにおいて ADGS6414D を使用できます。

- 7. ADGS1414D および ADGS2414D とピン互換です。

<sup>1</sup>米国特許 10.642,769 および 11,222,834 により保護されています。

## 目次

| 特長                      |     |

|-------------------------|-----|

| アプリケーション                |     |

| 機能ブロック図                 |     |

| 概要                      |     |

| 製品のハイライト                |     |

| 仕様                      | 2   |

| 動作電源電圧                  | 1   |

| ±20V 両電源                | 3   |

| 36V 単電源                 |     |

| チャンネルごとの連続電流(SX または DX) | •   |

| タイミング特性                 | ;   |

| タイミング図                  | (   |

| 絶対最大定格1                 | 1 ( |

| 熱抵抗1                    | 1 ( |

| 静電放電(ESD)定格             | 1   |

| ESD に関する注意              | l ( |

| ピン配置およびピン機能の説明          | 1   |

| 代表的な性能特性1               | Ľ   |

| テスト回路                   | ľ   |

| 用語の定義2                  | 2   |

| 動作原理2                   | 2   |

| アドレス・モード2               | 2   |

| エラー検出機能2                | 2   |

| 巡回冗長検査 (CRC) エラーの検出2    | 22  |

| SCLK カウント・エラー検出2        | 2.  |

| 無効な読出し/書込みアドレス・エラー2     | 2.  |

| エラー・フラグ・レジスタのクリア       | 23 |

|------------------------|----|

| バースト・モード               | 23 |

| ソフトウェア・リセット            | 23 |

| デイジーチェーン・モード           | 23 |

| パワーオン・リセット             | 25 |

| アプリケーション情報             | 26 |

| 高電圧、高周波の信号のトラッキング      | 26 |

| システム・チャンネル密度           | 26 |

| スルー配線ピン                | 26 |

| 内蔵の受動部品                | 26 |

| ブレーク・ビフォア・メーク・スイッチング機能 | 27 |

| デジタル入力バッファ             | 27 |

| 電源レール                  | 27 |

| 電源の推奨事項                | 27 |

| 1.8V ロジックとの互換性         | 27 |

| レジスタの一覧                | 28 |

| レジスタの詳細                | 29 |

| スイッチ・データ・レジスタ          | 29 |

| エラー設定レジスタ              | 29 |

| エラー・フラグ・レジスタ           | 30 |

| バースト・イネーブル・レジスタ        | 30 |

| ソフトウェア・リセット・レジスタ       | 31 |

| 外形寸法                   | 32 |

| オーダー・ガイド               | 32 |

| 評価用ボード                 | 32 |

### 改訂履歴

12/2024—Revision 0: Initial Version

analog.com.jp Rev. 0 | 2 of 32

### 仕様

## 動作電源電圧

表 1. 動作電源電圧

| Supply Voltage | Min  | Max | Unit |

|----------------|------|-----|------|

| Dual Supply    | ±4.5 | ±22 | V    |

| Single Supply  | +5   | +40 | V    |

### ±20V 両電源

特に指定のない限り、 $V_{DD}$  = +20V ± 10%、 $V_{SS}$  = -20V ± 10%、 $V_L$  = 2.7V  $\sim$  5.5V、GND = 0V。

表 2. ±20V 両電源

| Parameter                                             | +25°C | -40°C to +85°C | -40°C to +125°C           | Unit   | Test Conditions/Comments                                                                   |

|-------------------------------------------------------|-------|----------------|---------------------------|--------|--------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                         |       |                |                           |        | V <sub>DD</sub> = +18V, V <sub>SS</sub> = -18V                                             |

| Analog Signal Range                                   |       |                | $V_{DD}$ – 2V to $V_{SS}$ | V      |                                                                                            |

| On Resistance, R <sub>ON</sub>                        | 0.56  |                |                           | Ω typ  | Source voltage, $(V_S) = -18V$ to +14.5V, source current, $(I_S) = -100$ mA, see Figure 35 |

|                                                       | 0.7   | 0.85           | 1.0                       | Ω max  |                                                                                            |

|                                                       | 0.6   |                |                           | Ω typ  | $V_S = -18V \text{ to } +15.5V, I_S = -100\text{mA}$                                       |

|                                                       | 0.75  | 0.9            | 1.05                      | Ω max  |                                                                                            |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 0.045 |                |                           | Ω typ  | $V_S = -18V \text{ to } +15.5V, I_S = -100\text{mA}$                                       |

|                                                       | 0.12  | 0.14           | 0.16                      | Ω max  |                                                                                            |

| On Resistance Flatness, R <sub>FLAT(ON)</sub>         | 0.004 |                |                           | Ω typ  | $V_S = -18V$ to +14.5V, $I_S = -100$ mA                                                    |

|                                                       | 0.035 | 0.035          | 0.035                     | Ω max  |                                                                                            |

|                                                       | 0.04  |                |                           | Ω typ  | $V_S = -18V$ to +15.5V, $I_S = -100$ mA                                                    |

|                                                       | 0.08  | 0.1            | 0.1                       | Ω max  |                                                                                            |

| EAKAGE CURRENTS                                       |       |                |                           |        | V <sub>DD</sub> = +22V, V <sub>SS</sub> = -22V                                             |

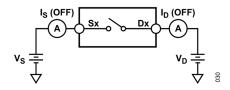

| Source Off Leakage, I <sub>S</sub> (Off)              | ±4    |                |                           | nA typ | $V_S$ = +15V/-15V, drain voltage, $V_D$ = -15V/+15V see Figure 36                          |

|                                                       | ±12.5 | +90/-14        | +400/-14                  | nA max |                                                                                            |

| Drain Off Leakage, ID (Off)                           | ±4    |                |                           | nA typ | $V_S = +15V/-15V$ , $V_D = -15V/+15V$ , see Figure 3                                       |

|                                                       | ±12.5 | +90/-14        | +400/-14                  | nA max |                                                                                            |

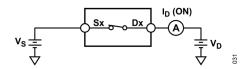

| Channel On Leakage, $I_D$ (On), $I_S$ (On)            | ±0.2  |                |                           | nA typ | $V_S = V_D = \pm 15V$ , see Figure 37                                                      |

|                                                       | ±1.3  | ±5             | +50/-5                    | nA max |                                                                                            |

| DIGITAL OUTPUT                                        |       |                |                           |        |                                                                                            |

| Output Voltage                                        |       |                |                           |        |                                                                                            |

| Low, V <sub>OL</sub>                                  |       |                | 0.4                       | V max  | Sink current, I <sub>SINK</sub> = 1mA                                                      |

|                                                       |       |                | 0.3                       | V max  | I <sub>SINK</sub> = 100μA                                                                  |

| High, V <sub>OH</sub>                                 |       |                | V <sub>L</sub> - 1.25V    | V min  | Source current, I <sub>SOURCE</sub> = 1mA                                                  |

|                                                       |       |                | V <sub>L</sub> - 0.125V   | V min  | I <sub>SOURCE</sub> = 100μA                                                                |

| Digital Output Capacitance, C <sub>OUT</sub>          | 4     |                |                           | pF typ |                                                                                            |

| DIGITAL INPUTS                                        |       |                |                           |        |                                                                                            |

| Input Voltage                                         |       |                |                           |        |                                                                                            |

| High, V <sub>INH</sub>                                |       |                | 2                         | V min  | $3.3V < V_L \le 5.5V$                                                                      |

|                                                       |       |                | 1.35                      | V min  | $2.7V \le V_L \le 3.3V$                                                                    |

| Low, $V_{INL}$                                        |       |                | 0.8                       | V max  | $3.3V < V_L \le 5.5V$                                                                      |

|                                                       |       |                | 0.8                       | V max  | $2.7V \le V_L \le 3.3V$                                                                    |

analog.com.jp Rev. 0 | 3 of 32

仕様

表 2. ±20V 両電源(続き)

| Parameter                                       | +25°C | -40°C to +85°C | -40°C to +125°C | Unit    | Test Conditions/Comments                                                                                          |

|-------------------------------------------------|-------|----------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------|

| Input Current                                   |       |                |                 |         |                                                                                                                   |

| Low, I <sub>INL</sub> or High, I <sub>INH</sub> | 0.001 |                |                 | μA typ  | Input voltage, $V_{IN}$ = ground voltage, $V_{GND}$ or $V_{L}$                                                    |

|                                                 |       |                | ±0.1            | μA max  |                                                                                                                   |

| Digital Input Capacitance, C <sub>IN</sub>      | 4     |                |                 | pF typ  |                                                                                                                   |

| DYNAMIC CHARACTERISTICS                         |       |                |                 | 1 71    |                                                                                                                   |

| On Time, t <sub>ON</sub>                        | 638   |                |                 | ns typ  | Load resistance, $R_L = 300\Omega$ , load capacitance, $C_L = 35pF$ , $V_S = 10V$ , see Figure 44                 |

|                                                 | 746   | 778            | 815             | ns max  |                                                                                                                   |

| Off Time, t <sub>OFF</sub>                      | 162   |                |                 | ns typ  | $R_L = 300\Omega$ , $C_L = 35pF$ , $V_S = 10V$ , see Figure 44                                                    |

|                                                 | 202   | 205            | 207             | ns max  |                                                                                                                   |

| Break-Before-Make Time Delay, $t_{\rm D}$       | 485   |                |                 | ns typ  | $R_L$ = 300 $\Omega$ , $C_L$ = 35pF, Source 1 voltage, $V_{S1}$ = Source 2 voltage, $V_{S2}$ = 10V, see Figure 43 |

|                                                 | 396   | 418            | 445             | ns min  |                                                                                                                   |

| Charge Injection, Q <sub>INJ</sub>              | -2.2  |                |                 | nC typ  | $V_S$ = 0V, source resistance $R_S$ = 0 $\Omega$ , $C_L$ = 1 nF, see Figure 45                                    |

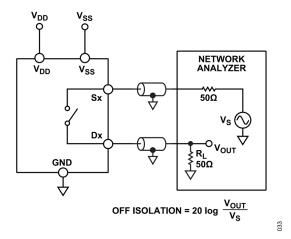

| Off Isolation                                   | -78   |                |                 | dB typ  | $R_L = 50\Omega$ , $C_L = 5pF$ , frequency, $f = 100kHz$ , see Figure 39                                          |

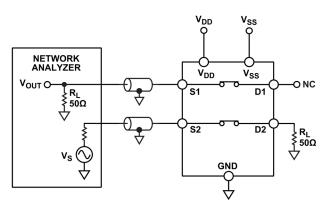

| Channel to Channel Crosstalk                    | -85   |                |                 | dB typ  | $R_L = 50\Omega$ , $C_L = 5pF$ , $f = 100kHz$ , see Figure 38                                                     |

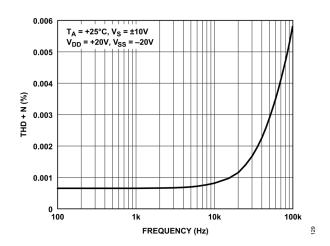

| Total Harmonic Distortion + Noise,<br>THD + N   | 0.001 |                |                 | % typ   | $R_L$ = 1k $\Omega$ , 20V p-p, f = 20Hz to 20kHz, see Figure 40                                                   |

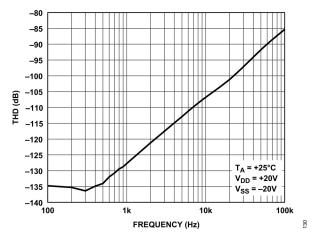

| Total Harmonic Distortion, THD                  | -128  |                |                 | dB typ  | $R_L = 1k\Omega$ , 20V p-p, f = 1kHz                                                                              |

|                                                 | -101  |                |                 | dB typ  | $R_L = 1k\Omega$ , 20V p-p, f = 20kHz                                                                             |

|                                                 | -85   |                |                 | dB typ  | $R_L = 1k\Omega$ , 20V p-p, f = 100kHz                                                                            |

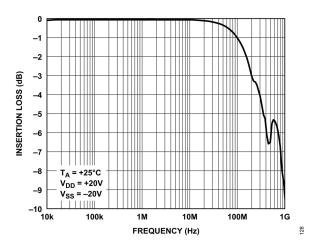

| −3dB Bandwidth                                  | 184   |                |                 | MHz typ | $R_L = 50\Omega$ , $C_L = 5pF$ , and signal = 0dBm, see Figure 41                                                 |

| Insertion Loss                                  | -0.06 |                |                 | dB typ  | $R_L = 50\Omega$ , $C_L = 5pF$ , $f = 1MHz$ , see Figure 41                                                       |

| Source Capacitance, C <sub>S</sub> (Off)        | 70    |                |                 | pF typ  | V <sub>S</sub> = 0V, f = 1MHz                                                                                     |

| Drain Capacitance, C <sub>D</sub> (Off)         | 70    |                |                 | pF typ  | $V_S = 0V, f = 1MHz$                                                                                              |

| C <sub>D</sub> (On), C <sub>S</sub> (On)        | 25    |                |                 | pF typ  | $V_S = 0V, f = 1MHz$                                                                                              |

| POWER REQUIREMENTS                              |       |                |                 |         | V <sub>DD</sub> = +22V, V <sub>SS</sub> = -22V                                                                    |

| Positive Supply Current, I <sub>DD</sub>        | 330   |                |                 | μA typ  | All switches open                                                                                                 |

| 117                                             |       |                | 440             | μA max  | '                                                                                                                 |

|                                                 | 350   |                |                 | μΑ typ  | All switches closed, V <sub>L</sub> = 5.5V                                                                        |

|                                                 |       |                | 460             | μA max  | , -                                                                                                               |

|                                                 | 350   |                |                 | μΑ typ  | All switches closed, V <sub>L</sub> = 2.7V                                                                        |

|                                                 |       |                | 460             | μA max  | , -                                                                                                               |

| Load Current, I <sub>L</sub>                    |       |                |                 |         |                                                                                                                   |

| Inactive                                        | 6.3   |                |                 | μA typ  | Digital inputs = 0V or V <sub>L</sub>                                                                             |

|                                                 |       |                | 8.5             | μA max  |                                                                                                                   |

|                                                 | 2.5   |                |                 | μA typ  | Digital inputs = 0V or 3V                                                                                         |

|                                                 |       |                | 4.0             | μA max  |                                                                                                                   |

| Inactive, SCLK = 1MHz                           | 14    |                |                 | μA typ  | $\overline{CS} = V_L$ and SDI = 0V or $V_L$ , $V_L = 5V$                                                          |

|                                                 | 7     |                |                 | μA typ  | $\overline{CS} = V_L$ and SDI = 0V or $V_L$ , $V_L = 3V$                                                          |

| SCLK = 50MHz                                    | 390   |                |                 | μA typ  | $\overline{CS} = V_1$ and SDI = 0V or $V_1$ , $V_1$ = 5V                                                          |

|                                                 | 210   |                |                 | μA typ  | $\overline{CS} = V_L$ and $SDI = 0V$ or $V_L$ , $V_L = 3V$                                                        |

| Inactive, SDI = 1MHz                            | 15    |                |                 | μA typ  | $\overline{CS}$ and $SCLK = 0V$ or $V_1$ , $V_1 = 5V$                                                             |

|                                                 | 7.5   |                |                 | μA typ  | $\overline{CS}$ and $SCLK = 0V$ or $V_1$ , $V_1 = 3V$                                                             |

| SDI = 25MHz                                     | 230   |                |                 | μΑ typ  | $\overline{CS}$ and $SCLK = 0V$ or $V_L$ , $V_L = 5V$                                                             |

| 05. 202                                         | 120   |                |                 | μΑ typ  | $\overline{CS}$ and $SCLK = 0V$ or $V_L$ , $V_L = 3V$                                                             |

analog.com.jp Rev. 0 | 4 of 32

## 仕様

表 2. ±20V 両電源(続き)

| Parameter                                | +25°C | -40°C to +85°C | −40°C to +125°C | Unit   | Test Conditions/Comments                                  |

|------------------------------------------|-------|----------------|-----------------|--------|-----------------------------------------------------------|

| Active at 50MHz                          | 7.0   |                |                 | mA typ | Digital inputs toggle between 0V and $V_L$ , $V_L = 5.5V$ |

|                                          |       |                | 9.0             | mA max |                                                           |

|                                          | 3.3   |                |                 | mA typ | Digital inputs toggle between 0V and $V_L$ , $V_L = 2.7V$ |

|                                          |       |                | 5.0             | mA max |                                                           |

| Negative Supply Current, I <sub>SS</sub> | 180   |                |                 | μA typ | Digital inputs = 0V or V <sub>L</sub>                     |

|                                          |       |                | 250             | μA max |                                                           |

## 36V 単電源

特に指定のない限り、 $V_{DD}$  = 36V ± 10%、 $V_{SS}$  = 0V、 $V_L$  = 2.7V  $\sim$  5.5V、GND = 0V。

表 3. 36V 単電源

| Parameter                                       | +25°C | -40°C to +85°C | -40°C to +125°C            | Unit   | Test Conditions/Comments                            |

|-------------------------------------------------|-------|----------------|----------------------------|--------|-----------------------------------------------------|

| ANALOG SWITCH                                   |       |                |                            |        | V <sub>DD</sub> = 32.4V, V <sub>SS</sub> = 0V       |

| Analog Signal Range                             |       |                | 0V to V <sub>DD</sub> - 2V | V      |                                                     |

| R <sub>ON</sub>                                 | 0.56  |                |                            | Ω typ  | $V_S = 0V$ to 28.9V, $I_S = -100$ mA, see Figure 35 |

|                                                 | 0.7   | 0.85           | 1.0                        | Ω max  |                                                     |

|                                                 | 0.6   |                |                            | Ω typ  | $V_S = 0V \text{ to } 29.9V, I_S = -100\text{mA}$   |

|                                                 | 0.75  | 0.9            | 1.05                       | Ω max  |                                                     |

| $\Delta R_{ON}$                                 | 0.045 |                |                            | Ω typ  | $V_S = 0V \text{ to } 29.9V, I_S = -100\text{mA}$   |

|                                                 | 0.12  | 0.14           | 0.16                       | Ω max  |                                                     |

| R <sub>FLAT (ON)</sub>                          | 0.004 |                |                            | Ω typ  | $V_S = 0V \text{ to } 28.9V, I_S = -100\text{mA}$   |

| (,                                              | 0.035 | 0.035          | 0.035                      | Ω max  |                                                     |

|                                                 | 0.04  |                |                            | Ω typ  | $V_S = 0V \text{ to } 29.9V, I_S = -100\text{mA}$   |

|                                                 | 0.08  | 0.1            | 0.1                        | Ω max  |                                                     |

| LEAKAGE CURRENTS                                |       |                |                            |        | V <sub>DD</sub> = 39.6V, V <sub>SS</sub> = 0V       |

| I <sub>S</sub> (Off)                            | ±4    |                |                            | nA typ | $V_S = 1V/30V, V_D = 30V/1V, \text{ see Figure 36}$ |

|                                                 | ±12.5 | +90/-14        | +400/-14                   | nA max |                                                     |

| I <sub>D</sub> (Off)                            | ±4    |                |                            | nA typ | $V_S = 1V/30V, V_D = 30V/1V, see Figure 36$         |

| ,                                               | ±12.5 | +90/-14        | +400/-14                   | nA max |                                                     |

| I <sub>D</sub> (On), I <sub>S</sub> (On)        | ±0.2  |                |                            | nA typ | $V_S = V_D = 1V/30V$ , see Figure 37                |

|                                                 | ±1.3  | ±5             | +50/-5                     | nA max |                                                     |

| DIGITAL OUTPUT                                  |       |                |                            |        |                                                     |

| Output Voltage                                  |       |                |                            |        |                                                     |

| Low, V <sub>OL</sub>                            |       |                | 0.4                        | V max  | I <sub>SINK</sub> = 1mA                             |

|                                                 |       |                | 0.3                        | V max  | I <sub>SINK</sub> = 100μA                           |

| High, V <sub>OH</sub>                           |       |                | V <sub>L</sub> - 1.25V     | V min  | I <sub>SOURCE</sub> = 1mA                           |

|                                                 |       |                | V <sub>L</sub> - 0.125V    | V min  | I <sub>SOURCE</sub> = 100µA                         |

| C <sub>OUT</sub>                                | 4     |                | _                          | pF typ |                                                     |

| DIGITAL INPUTS                                  |       |                |                            |        |                                                     |

| Input Voltage                                   |       |                |                            |        |                                                     |

| High, V <sub>INH</sub>                          |       |                | 2                          | V min  | $3.3V < V_1 \le 5.5V$                               |

|                                                 |       |                | 1.35                       | V min  | $2.7V \le V_{L} \le 3.3V$                           |

| Low, V <sub>INL</sub>                           |       |                | 0.8                        | V max  | $3.3V < V_L \le 5.5V$                               |

|                                                 |       |                | 0.8                        | V max  | $2.7V \le V_L \le 3.3V$                             |

| Input Current                                   |       |                |                            |        | _                                                   |

| Low, I <sub>INL</sub> or High, I <sub>INH</sub> | 0.001 |                |                            | μA typ | $V_{IN} = V_{GND}$ or $V_{L}$                       |

|                                                 |       |                | ±0.1                       | μA max | 55                                                  |

| C <sub>IN</sub>                                 | 4     |                |                            | pF typ |                                                     |

analog.com.jp Rev. 0 | 5 of 32

仕様

表 3. 36V 単電源(続き)

| Parameter                                | +25°C      | -40°C to +85°C | -40°C to +125°C | Unit             | Test Conditions/Comments                                                                                           |

|------------------------------------------|------------|----------------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------|

| DYNAMIC CHARACTERISTICS                  |            |                |                 |                  |                                                                                                                    |

| t <sub>ON</sub>                          | 490        |                |                 | ns typ           | $R_L = 300\Omega$ , $C_L = 35pF$ , $V_S = 18V$ , see Figure 44                                                     |

|                                          | 574        | 583            | 596             | ns max           |                                                                                                                    |

| t <sub>OFF</sub>                         | 256        |                |                 | ns typ           | $R_L = 300\Omega$ , $C_L = 35pF$ , $V_S = 18V$ , see Figure 44                                                     |

|                                          | 298        | 305            | 311             | ns max           |                                                                                                                    |

| $t_D$                                    | 294        |                |                 | ns typ           | $R_L = 300\Omega$ , $C_L = 35pF$ , $V_{S1} = V_{S2} = 18V$ , see                                                   |

|                                          |            |                |                 |                  | Figure 43                                                                                                          |

|                                          | 242        | 249            | 258             | ns min           |                                                                                                                    |

| $Q_{INJ}$                                | -2.0       |                |                 | nC typ           | $V_S = 18V, R_S = 0\Omega, C_L = 1nF$                                                                              |

| Off Isolation                            | -65        |                |                 | dB typ           | $R_L = 50\Omega$ , $C_L = 5pF$ , $f = 100kHz$ , see Figure 39                                                      |

| Channel to Channel Crosstalk             | -85        |                |                 | dB typ           | $R_L = 50\Omega$ , $C_L = 5pF$ , $f = 100kHz$ , see Figure 38                                                      |

| THD + N                                  | 0.005      |                |                 | % typ            | $R_L = 1k\Omega$ , 18V p-p, f = 20Hz to 20kHz,                                                                     |

|                                          |            |                |                 |                  | seeFigure 40                                                                                                       |

| THD                                      | -113       |                |                 | dB typ           | $R_L = 1k\Omega$ , 18V p-p, f = 1kHz                                                                               |

|                                          | -87        |                |                 | dB typ           | $R_L = 1k\Omega$ , 18V p-p, f = 20kHz                                                                              |

|                                          | <b>-72</b> |                |                 | dB typ           | $R_L = 1k\Omega$ , 18V p-p, f = 100kHz                                                                             |

| -3dB Bandwidth                           | 134        |                |                 | MHz typ          | $R_L$ = 50 $\Omega$ , $C_L$ = 5pF and signal = 0dBm, see Figure 41                                                 |

| Insertion Loss                           | -0.06      |                |                 | dB typ           | $R_L = 50\Omega$ , $C_L = 5pF$ , $f = 1MHz$ , see Figure 41                                                        |

| C <sub>S</sub> (Off)                     | 72         |                |                 | pF typ           | V <sub>S</sub> = 18V, f = 1MHz                                                                                     |

| C <sub>D</sub> (Off)                     | 72         |                |                 | pF typ           | V <sub>S</sub> = 18V, f = 1MHz                                                                                     |

| C <sub>D</sub> (On), C <sub>S</sub> (On) | 26         |                |                 | pF typ           | V <sub>S</sub> = 18V, f = 1MHz                                                                                     |

| POWER REQUIREMENTS                       |            |                |                 |                  | V <sub>DD</sub> = 39.6V                                                                                            |

| I <sub>DD</sub>                          | 330        |                |                 | μA typ           | All switches open                                                                                                  |

|                                          |            |                | 440             | μA max           | '                                                                                                                  |

|                                          | 350        |                |                 | μA typ           | All switches closed, V <sub>L</sub> = 5.5V                                                                         |

|                                          |            |                | 460             | μA max           |                                                                                                                    |

|                                          | 350        |                |                 | μA typ           | All switches closed, V <sub>L</sub> = 2.7V                                                                         |

|                                          |            |                | 460             | μA max           | , -                                                                                                                |

| I <sub>L</sub>                           |            |                |                 |                  |                                                                                                                    |

| Inactive                                 | 6.3        |                |                 | μA typ           | Digital inputs = 0V or V <sub>L</sub>                                                                              |

|                                          | 5.0        |                | 8.5             | µA max           | J.g.tan m.patto ov or v.                                                                                           |

|                                          | 2.5        |                |                 | μA typ           | Digital inputs = 0V or 3V                                                                                          |

|                                          | 2.0        |                | 4.0             | µA max           | 2.gran in parts of the control                                                                                     |

| Inactive, SCLK = 1MHz                    | 14         |                | •               | μA typ           | $\overline{CS} = V_1$ and SDI = 0V or $V_1$ , $V_1 = 5V$                                                           |

| madaro, oblik mine                       | 7          |                |                 | μA typ           | $\overline{CS} = V_L$ and SDI = 0V or $V_L$ , $V_L = 3V$                                                           |

| SCLK = 50MHz                             | 390        |                |                 | μA typ           | $\overline{CS} = V_L$ and SDI = 0V or $V_L$ , $V_L = 5V$                                                           |

| OOLIN - OOMI 12                          | 210        |                |                 | μA typ           | $\overline{CS} = V_L$ and SDI = 0V or $V_L$ , $V_L = 3V$                                                           |

| Inactive, SDI = 1MHz                     | 15         |                |                 | μΑ typ           | $\overline{\text{CS}}$ and SCLK = 0V or V <sub>L</sub> , V <sub>L</sub> = 5V                                       |

| mactive, ODI – TWITZ                     | 7.5        |                |                 | μΑ typ           | $\overline{\text{CS}}$ and $\overline{\text{SCLK}} = 0 \text{V or V}_L$ , $\overline{\text{V}}_L = 3 \text{V}$     |

| SDI = 25MHz                              | 230        |                |                 | μΑ typ           | $\overline{\text{CS}}$ and $\overline{\text{SCLK}} = 0 \text{V or V}_1, \text{V}_1 = 5 \text{V}$                   |

| ODI - ZOIVII IZ                          | 120        |                |                 | μΑ typ<br>μΑ typ | $\overline{\text{CS}}$ and $\overline{\text{SCLK}} = 0$ V of $\overline{\text{VL}}$ , $\overline{\text{VL}} = 3$ V |

| Active at 50MHz                          | 7.0        |                |                 | mA typ           | Digital inputs toggle between 0V and $V_L$ , $V_L = V_L$                                                           |

| Active at Joint 12                       | 7.0        |                |                 |                  | 5.5V                                                                                                               |

|                                          |            |                | 9.0             | mA max           |                                                                                                                    |

|                                          | 3.3        |                |                 | mA typ           | Digital inputs toggle between 0V and $V_L$ , $V_L$ = 2.7V                                                          |

|                                          |            |                | 5.0             | mA max           |                                                                                                                    |

analog.com.jp Rev. 0 | 6 of 32

### 仕様

# チャンネルごとの連続電流(SX または DX)

### 表 4.8 つのチャンネルがオン

| Parameter                                                       | 25°C | 85°C | 125°C | Unit       |

|-----------------------------------------------------------------|------|------|-------|------------|

| CONTINUOUS CURRENT, Sx OR Dx1                                   |      |      |       |            |

| $V_{DD} = +20V$ , $V_{SS} = -20V$ ( $\theta_{JA} = 56.74$ °C/W) | 439  | 232  | 112   | mA maximum |

| $V_{DD} = +36V$ , $V_{SS} = 0V$ ( $\theta_{JA} = 56.74$ °C/W)   | 439  | 232  | 112   | mA maximum |

<sup>&</sup>lt;sup>1</sup> Sx は S1~S8 ピン、Dx は D1~D8 ピンを表します。

### 表 5.1 つのチャンネルがオン

| Parameter                                                       | 25°C | 85°C | 125°C | Unit       |

|-----------------------------------------------------------------|------|------|-------|------------|

| CONTINUOUS CURRENT, Sx OR Dx1                                   |      |      |       |            |

| $V_{DD} = +20V$ , $V_{SS} = -20V$ ( $\theta_{JA} = 56.74$ °C/W) | 768  | 313  | 122   | mA maximum |

| $V_{DD} = +36V$ , $V_{SS} = 0V$ ( $\theta_{JA} = 56.74$ °C/W)   | 768  | 313  | 122   | mA maximum |

<sup>&</sup>lt;sup>1</sup> Sx は S1~S8 ピン、Dx は D1~D8 ピンを表します。

analog.com.jp Rev. 0 | 7 of 32

## 仕様

# タイミング特性

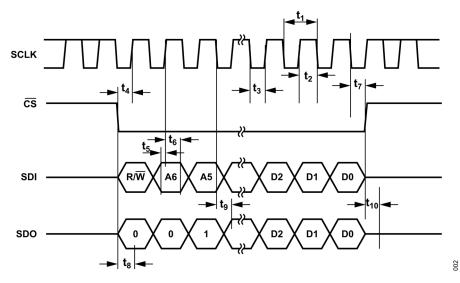

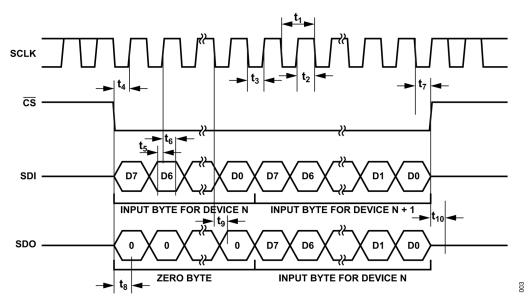

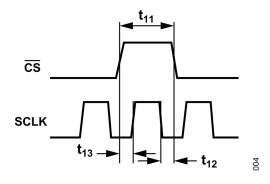

特に指定のない限り、 $V_L=2.7V\sim5.5V$ 、GND = 0V、すべての仕様で  $T_{MIN}\sim T_{MAX}$ 。 タイミング図については図  $2\sim$ 図 4 を参照してください。

表 6. タイミング特性

| Parameter              | Limit | Unit   | Test Conditions/Comments                |

|------------------------|-------|--------|-----------------------------------------|

| TIMING CHARACTERISTICS |       |        |                                         |

| t <sub>1</sub>         | 20    | ns min | SCLK period                             |

| t <sub>2</sub>         | 8     | ns min | SCLK high pulse width                   |

| $t_3$                  | 8     | ns min | SCLK low pulse width                    |

| $t_4$                  | 10    | ns min | CS falling edge to SCLK active edge     |

| t <sub>5</sub>         | 6     | ns min | Data setup time                         |

| t <sub>6</sub>         | 8     | ns min | Data hold time                          |

| t <sub>7</sub>         | 10    | ns min | SCLK active edge to rising edge         |

| t <sub>8</sub>         | 20    | ns max | CS falling edge to SDO data available   |

| $t_9^1$                | 30    | ns max | SCLK falling edge to SDO data available |

| t <sub>10</sub>        | 30    | ns max | CS rising edge to SDO returns to high   |

| t <sub>11</sub>        | 20    | ns min | CS high time between SPI commands       |

| t <sub>12</sub>        | 8     | ns min | CS falling edge to SCLK becomes stable  |

| t <sub>13</sub>        | 8     | ns min | CS rising edge to SCLK becomes stable   |

<sup>&</sup>lt;sup>1</sup> 20pF の負荷を接続して測定。SDO 使用時の最大 SCLK 周波数は to で決まります。

analog.com.jp Rev. 0 | 8 of 32

## 仕様

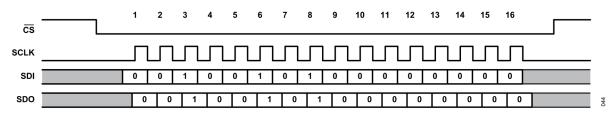

# タイミング図

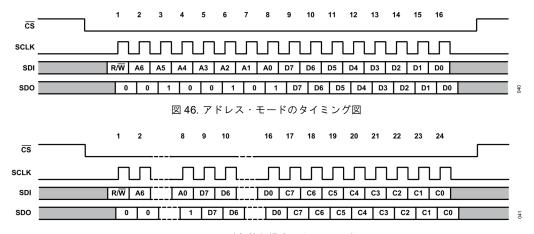

図 2. アドレス・モードのタイミング図

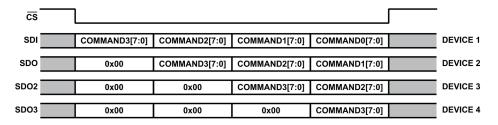

図 3. デイジーチェーンのタイミング図

図 4. SCLK と CS のタイミング関係

analog.com.jp Rev. 0 | 9 of 32

### 絶対最大定格

特に指定のない限り、 $T_A = 25$ °C。

表 7. 絶対最大定格

| Parameter                                  | Rating                                                                           |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------|--|--|

| V <sub>DD</sub> to V <sub>SS</sub>         | 46V                                                                              |  |  |

| V <sub>DD</sub> to GND                     | -0.3V to +46V                                                                    |  |  |

| V <sub>SS</sub> to GND                     | +0.3V to -46V                                                                    |  |  |

| V <sub>L</sub> to GND                      |                                                                                  |  |  |

| For $V_{DD} \le 5.5V$                      | -0.3V to V <sub>DD</sub> + 0.3V                                                  |  |  |

| For V <sub>DD</sub> > 5.5V                 | -0.3V to +6V                                                                     |  |  |

| SDO                                        | -0.3V to V <sub>L</sub> + 0.3V or 6mA, whichever occurs first                    |  |  |

| Analog Inputs <sup>1</sup>                 | V <sub>SS</sub> - 0.3V to V <sub>DD</sub> + 0.3V or 30mA, whichever occurs first |  |  |

| Digital Inputs <sup>1</sup>                | -0.3V to +6V                                                                     |  |  |

| Peak Current, Sx or Dx <sup>2</sup>        | 1180mA (pulsed at 1ms, 10% duty cycle maximum)                                   |  |  |

| Continuous Current, Sx or Dx <sup>2</sup>  | Data <sup>3</sup> + 15%                                                          |  |  |

| Temperature                                |                                                                                  |  |  |

| Operating Range                            | -40°C to +125°C                                                                  |  |  |

| Storage Range                              | -65°C to +150°C                                                                  |  |  |

| Junction                                   | 150°C                                                                            |  |  |

| Reflow Soldering Peak Temperature, Pb Free | As per JEDEC J-STD-020                                                           |  |  |

<sup>「</sup>デジタル Sx ピンおよび Dx ピンでの過電圧は、内部ダイオードにより クランプされます。電流は、規定された最大定格に制限してください。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

同時に複数の絶対最大定格を適用することはできません。

### 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接 関連しています。PCB の熱設計には、細心の注意を払う必要が あります。

$\theta_{JA}$  は、1 立方フィートの密閉容器内で測定された、自然対流での周囲とジャンクションの間の熱抵抗です。 $\theta_{JCB}$  はジャンクションとケース底面の間の熱抵抗です。

表 8. 熱抵抗

| Package Type <sup>1</sup> | $\theta_{JA}$ | $\theta_{JCB}$ | Unit |

|---------------------------|---------------|----------------|------|

| CC-30-3                   | 56.81         | 29.82          | °C/W |

<sup>1</sup> 熱抵抗のシミュレーション値は、9個のサーマル・ビアを備えた JEDEC 2S2Pサーマル・テスト・ボードに基づいています。JEDEC JESD-51を参照してください。

### 静電放電(ESD)定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起チャージ・デバイス・モデル(FICDM)。

#### ADGS6414D の ESD 定格

表 9. ADGS6414D、30 ピン LGA

| Package Type | Withstand Threshold (V) | Class |

|--------------|-------------------------|-------|

| HBM          | ±4000                   | 3A    |

| FICDM        | ±1250                   | C3    |

### ESDに関する注意

ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

<sup>&</sup>lt;sup>2</sup> Sx は S1~S8 ピン、Dx は D1~D8 ピンを表します。

<sup>3</sup>表4および表5を参照してください。

# ピン配置およびピン機能の説明

図 5. ピン配置

表 10. 端子説明

| ピン番号   | 記 <del>号</del>       | 説明                                                                                                                                                                      |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | D1                   | ドレイン端子 1。D1 ピンは、入力または出力に設定できます。                                                                                                                                         |

| 2      | D2                   | ドレイン端子 2。D2 ピンは、入力または出力に設定できます。                                                                                                                                         |

| 3      | S1                   | ソース端子 1。S1 ピンは、入力または出力に設定できます。                                                                                                                                          |

| 4      | S2                   | ソース端子 2。S2 ピンは、入力または出力に設定できます。                                                                                                                                          |

| 5      | Vss                  | 負電源の電位。単電源アプリケーションでは、Vss ピンをグラウンドに接続します。                                                                                                                                |

| 6      | S3                   | ソース端子 3。S3 ピンは、入力または出力に設定できます。                                                                                                                                          |

| 7      | S4                   | ソース端子 4。S4 ピンは、入力または出力に設定できます。                                                                                                                                          |

| 8      | D3                   | ドレイン端子 3。D3 ピンは、入力または出力に設定できます。                                                                                                                                         |

| 9      | D4                   | ドレイン端子 4。D4 ピンは、入力または出力に設定できます。                                                                                                                                         |

| 10, 30 | $V_{DD}$             | 正電源の電位。どちらのVDDピンも内部接続されています。                                                                                                                                            |

| 11, 29 | GND                  | グラウンド(OV)リファレンス。どちらの GND ピンも内部接続されています。                                                                                                                                 |

| 12, 28 | RESET/V <sub>L</sub> | RESET/ロジック電源入力 (VL) 。通常動作では、2.7V~5.5V の電源でRESET/VLを駆動します。<br>ハードウェア・リセットを完了するには、RESET/VLをローにプルダウンします。リセット後、すべてのスイッチは解放になり、該当するレジスタがデフォルト値に設定されます。RESETと VL は内部接続されています。 |

| 13     | SDO                  | シリアル・データ出力。多数のデバイスをデイジーチェーン接続したり、診断のためにレジスタに保存されているデータをリードバックしたりするには、SDOピンを使用します。シリアル・データはSCLKの立下がりエッジで伝搬されます。                                                          |

| 14, 26 | SCLK                 | シリアル・クロック入力。SCLKの立上がりエッジでデータがキャプチャされます。最大 50MHzの<br>レートでデータを転送できます。どちらの SCLK ピンも内部接続されています。                                                                             |

| 15, 25 | CS                   | アクティブ・ローの制御入力。CSは、入力データに対するフレーム同期信号です。どちらのCSピン<br>も内部接続されています。                                                                                                          |

| 16     | D5                   | ドレイン端子 5。D5 ピンは、入力または出力に設定できます。                                                                                                                                         |

| 17     | D6                   | ドレイン端子 6。D6 ピンは、入力または出力に設定できます。                                                                                                                                         |

| 18     | S5                   | ソース端子 5。S5 ピンは、入力または出力に設定できます。                                                                                                                                          |

| 19     | S6                   | ソース端子 6。S6 ピンは、入力または出力に設定できます。                                                                                                                                          |

| 20     | NIC                  | 内部接続なし。                                                                                                                                                                 |

| 21     | S7                   | ソース端子 7。S7 ピンは、入力または出力に設定できます。                                                                                                                                          |

| 22     | S8                   | ソース端子 8。S8 ピンは、入力または出力に設定できます。                                                                                                                                          |

| 23     | D7                   | ドレイン端子 7。D7 ピンは、入力または出力に設定できます。                                                                                                                                         |

| 24     | D8                   | ドレイン端子 8。D8 ピンは、入力または出力に設定できます。                                                                                                                                         |

| 27     | SDI                  | シリアル・データ入力。SCLKの立上がりエッジでデータがキャプチャされます。                                                                                                                                  |

|        | EPAD                 | 露出パッド。露出パッドは内部接続されています。ハンダ接続の信頼性を向上させ最大限の熱性能を得るため、この露出パッドを Vss に接続することを推奨します。                                                                                           |

analog.com.jp Rev. 0 | 11 of 32

### 代表的な性能特性

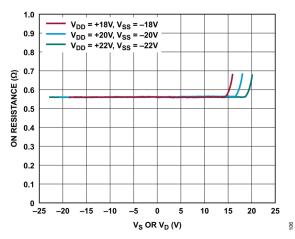

図 6. ±20V 両電源でのオン抵抗と Vs または VD の関係

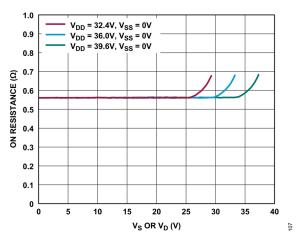

図 7. +36V 単電源でのオン抵抗と Vs または VD の関係

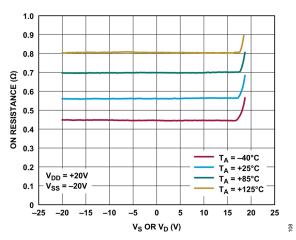

図 8. 様々な温度でのオン抵抗と  $V_S$  または  $V_D$  の関係、  $\pm 20V$  両電源

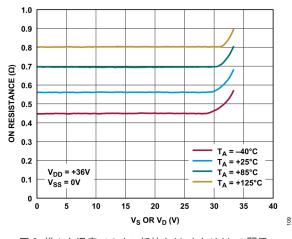

図 9. 様々な温度でのオン抵抗と Vs または V<sub>D</sub> の関係、 +36V 単電源

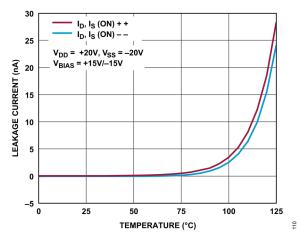

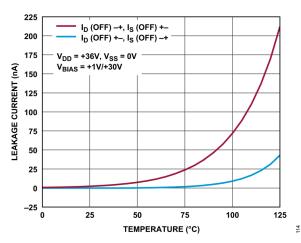

図 10. オン・リーク電流と温度の関係、±20V 両電源

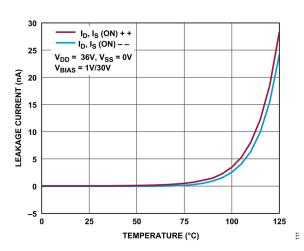

図 11. オン・リーク電流と温度の関係、+36V 単電源

analog.com.jp Rev. 0 | 12 of 32

### 代表的な性能特性

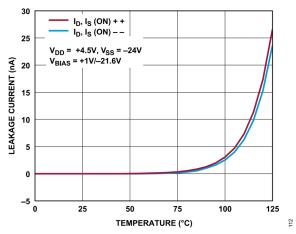

図 12. オン・リーク電流と温度の関係、+4.5V、-24V 両電源

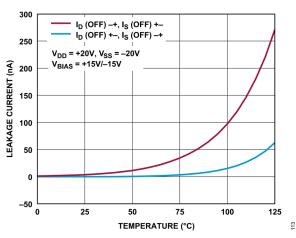

図 13. オフ・リーク電流と温度の関係、±20V 両電源

図 14. オフ・リーク電流と温度の関係、+36V 単電源

図 15. オフ・リーク電流と温度の関係、+4.5V、-24V 両電源

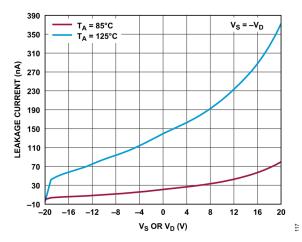

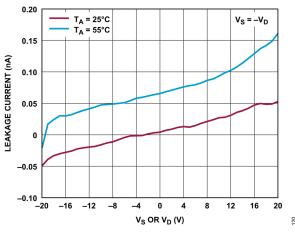

図 16. オフ・リーク電流とバイアス電圧の関係、±20V 両電源

図 17. オフ・リーク電流とバイアス電圧の関係、±20V 両電源

analog.com.jp Rev. 0 | 13 of 32

### 代表的な性能特性

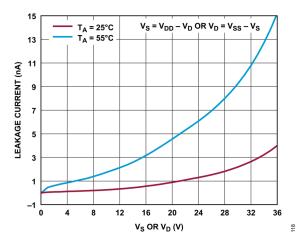

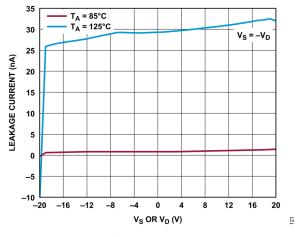

図 18. オフ・リーク電流とバイアス電圧の関係、+36V 単電源

図 19. オフ・リーク電流とバイアス電圧の関係、+36V 単電源

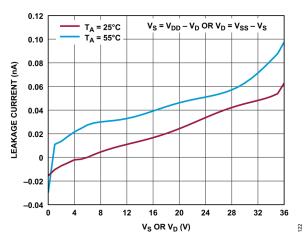

図 20. オン・リーク電流とバイアス電圧の関係、±20V 両電源

図 21. オン・リーク電流とバイアス電圧の関係、±20V 両電源

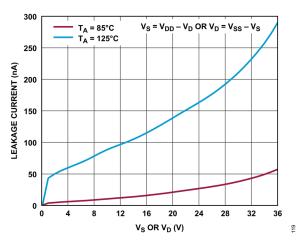

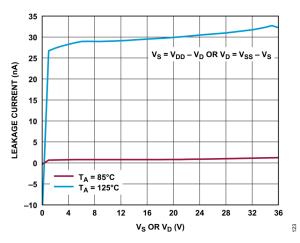

図 22. オン・リーク電流とバイアス電圧の関係、+36V 単電源

図 23. オン・リーク電流とバイアス電圧の関係、+36V 単電源

analog.com.jp Rev. 0 | 14 of 32

### 代表的な性能特性

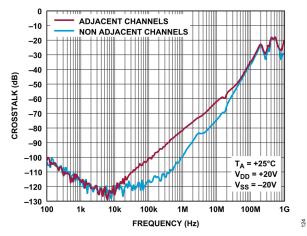

図 24. クロストークと周波数の関係、±20V 両電源

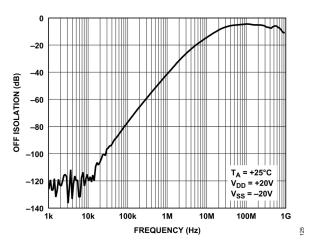

図 25. オフ・アイソレーションと周波数の関係、±20V 両電源

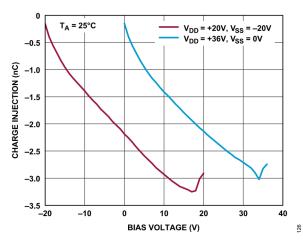

図 26. チャージ・インジェクションと Vs の関係

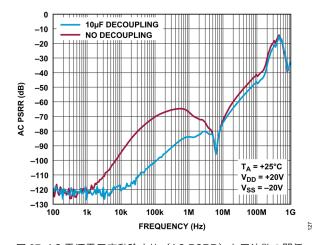

図 27. AC 電源電圧変動除去比(AC PSRR)と周波数の関係、 ±20V 両電源

図 28. 挿入損失と周波数の関係、±20V 両電源

図 29. THD + N と周波数の関係、±20V 両電源

analog.com.jp Rev. 0 | 15 of 32

### 代表的な性能特性

図 30. THD と周波数の関係、±20V 両電源

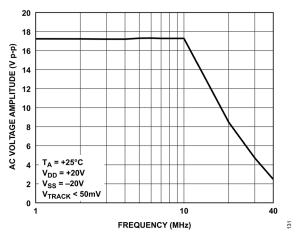

図 31. 大 AC 信号電圧と周波数の関係

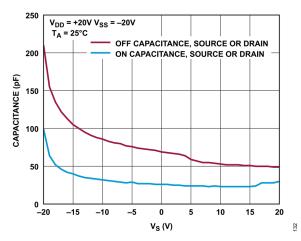

図 32. 容量と Vsの関係、±20V 両電源

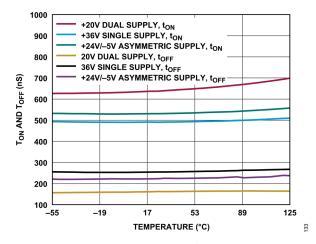

図 33. T<sub>ON</sub>/T<sub>OFF</sub> 時間と温度の関係、 単電源(SS)と両電源(DS)

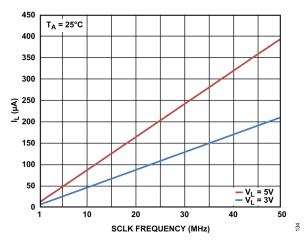

図 34.  $\overline{\text{CS}}$ がハイの場合の  $\mathbb{L}$   $\mathcal{E}$  SCLK 周波数の関係

analog.com.jp Rev. 0 | 16 of 32

### テスト回路

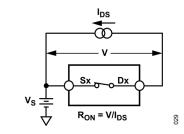

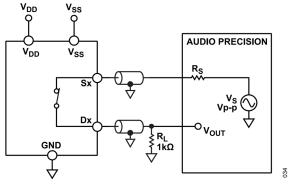

図 35. オン抵抗( $I_{DS}$  = ドレイン・ソース間電流)

図 36. オフ・リーク電流

図 37. オン・リーク電流

CHANNEL TO CHANNEL CROSSTALK = 20 log  $\frac{V_{OUT}}{V_S}$

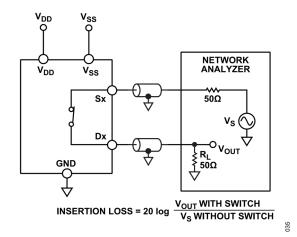

図 38. チャンネル間クロストーク

032

analog.com.jp Rev. 0 | 17 of 32

## テスト回路

図 39. オフ・アイソレーション

図 40. THD + N

analog.com.jp Rev. 0 | 18 of 32

### テスト回路

図 41. -3dB 帯域幅

#### NOTES

1. BOARD AND COMPONENT EFFECTS ARE NOT DE-EMBEDDED FROM THE AC PSRR MEASUREMENT.

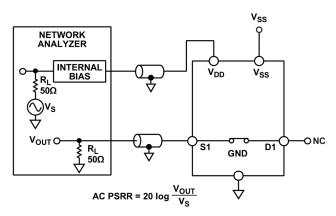

図 42. AC PSRR

036

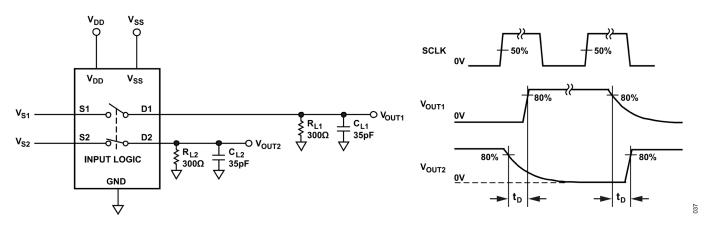

図 43. ブレーク・ビフォア・メークの遅延時間、t<sub>D</sub>

analog.com.jp Rev. 0 | 19 of 32

### テスト回路

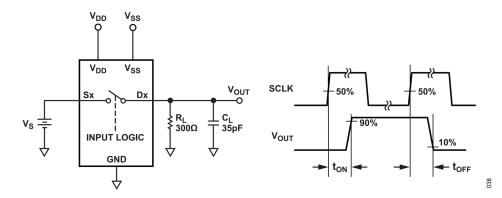

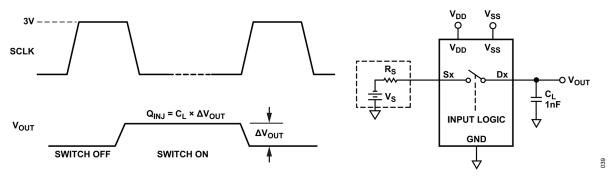

図 44. スイッチング時間、tonおよび toff

図 45. チャージ・インジェクション、 $Q_{INJ}$ ( $\Delta V_{OUT}$  = 出力電圧の変化)

analog.com.jp Rev. 0 | 20 of 32

#### 用語の定義

#### $I_{DD}$

正電源の電流。

#### Iss

負電源の電流。

### $V_D$ , $V_S$

端子 Dx と端子 Sx のアナログ電圧。

#### RON

端子 Dx と端子 Sx の間の抵抗。

#### $\Delta R_{ON}$

任意の2チャンネル間のRonの差。

#### R<sub>FLAT</sub> (ON)

仕様規定されたアナログ信号範囲におけるオン抵抗の最大値と 最小値の差として定義される抵抗値の平坦性。

#### Is (Off)

スイッチ・オフ時のソース・リーク電流。

#### I<sub>D</sub> (Off)

スイッチ・オフ時のドレイン・リーク電流。

#### $I_D$ (On), $I_S$ (On)

スイッチ・オン時のチャンネル・リーク電流。

#### $V_{INL}$

ロジック0の最大入力電圧。

#### $V_{\text{INH}}$

ロジック1の最小入力電圧。

#### I<sub>INL</sub>, I<sub>INH</sub>

デジタル入力のロー・レベルおよびハイ・レベルでの入力電流。

#### C<sub>D</sub> (Off)

スイッチ・オフ時のドレイン容量。グラウンドを基準として測 定。

### Cs (Off)

スイッチ・オフ時のソース容量。グラウンドを基準として測定。

### $C_D$ (On), $C_S$ (On)

スイッチ・オン時の容量。グラウンドを基準として測定。

#### CIN

デジタル入力容量。

#### Cout

デジタル出力容量。

#### ton

デジタル制御入力が印加されてから出力がオンになるまでの遅 延。

#### toff

デジタル制御入力が印加されてから出力がオフになるまでの遅 延。

### オフ・アイソレーション

オフ・スイッチから混入する不要な信号の大きさ。

#### チャージ・インジェクション

切替え中にデジタル入力からアナログ出力に転送されるグリッ チ・インパルスの大きさ。

#### クロストーク

寄生容量に起因し、あるチャンネルから別のチャンネルに混入 する不要な信号の大きさ。

#### -3dB 帯域幅

出力が 3dB 減衰する周波数。

#### オン応答

オン状態にあるスイッチの周波数応答。

### 挿入損失

スイッチのオン抵抗に起因する損失。

### 全高調波歪み+ノイズ (THD + N)

基本波成分に対する全高調波成分+信号ノイズの比。

#### AC 電源電圧変動除去比(AC PSRR)

変調振幅に対する出力信号の振幅の比。AC PSRR は、電源電圧 ピンに現れるノイズとスプリアス信号がスイッチ出力へ混入するのを防止するデバイスの能力を表します。デバイスの DC 電圧は、0.62Vp-p のサイン波で変調されます。

analog.com.jp Rev. 0 | 21 of 32

#### 動作原理

ADGS6414D は、エラー検出機能を備えたシリアル制御、オクタル SPST スイッチのセットです。SPI モード 0 および SPI モード 3 を ADGS6414D と組み合わせることができ、最大 50MHz の SCLK 周波数で動作します。ADGS6414D のデフォルトのモード はアドレス・モードです。このモードでは、 $\overline{CS}$ によって分割される 16 ビットの SPI コマンドでデバイスのレジスタにアクセスできます。CRC エラー検出が有効な場合は、SPI コマンドは 24 ビット・コマンドになります。その他のエラー検出機能には、SCLK カウント・エラーや無効な読出し/書込みエラーがあります。これらの SPI エラーが発生したかどうかを検出するには、エラー・フラグ・レジスタを読み出します。また、ADGS6414D は、バースト・モードとデイジーチェーン・モードでも動作します。

ADGS6414D のインターフェース・ピンは、 $\overline{\text{CS}}$ 、SCLK、SDI、および SDO です。SPI を使用する場合は $\overline{\text{CS}}$ をローにします。データは SCLK の立上がりエッジ発生時に SDI でキャプチャされ、SCLK の立下がりエッジ発生時に SDO で伝搬されます。

### アドレス・モード

アドレス・モードは、ADGS6414Dのパワーアップ時のデフォルト・モードです。アドレス・モードでは、 $\overline{\text{CS}}$ 立下がりエッジと後続の $\overline{\text{CS}}$ 立上がりエッジによって単一の SPI フレームが指定されます。SPI フレームは、16 SCLK サイクルで構成されます。アドレス・モードのタイミング図を図 46 に示します。最初の SDI ビットは、SPI コマンドが読出しコマンドまたは書込みコマンドのどちらであるかを示します。最初のビットが 0 に設定されている場合は、書込みコマンドが実行されます。最初のビットが1 に設定されている場合は、読出しコマンドが実行されます。次の7 ビットはターゲット・レジスタのアドレスを決定します。残りの8 ビットは、アドレス指定されたレジスタへ提供するデータです。読出しコマンド実行中のクロック・サイクルでは、SDO がアドレス指定されたレジスタに含まれるデータを伝搬するため、最後の8 ビットは無視されます。

SPI コマンドのターゲット・レジスタのアドレスは、8番目の SCLK 立上がりエッジで決定されます。このレジスタのデータは、SPIの読出し中に8~15番目のSCLK立下がりエッジでSDO から送出されます。レジスタへの書込みは、SPI の書込み中に16番目のSCLK立上がりエッジで行われます。

SPI コマンドの実行中、SDO は最初の 8 ビットで 8 つのアライメント・ビットを送信します。SDO で観察されるアライメント・ビットは、0x25 です。

### エラー検出機能

SPIでは、プロトコルと通信のエラーを検出できます。不正な SCLK カウント・エラー検出、無効な読出し/書込みアドレス・エラー検出、CRC エラー検出の 3 つのエラー検出機能があります。これらのエラー検出機能には、それぞれ、対応するイネーブル・ビットがエラー設定レジスタにあります。更に、エラー・フラグ・レジスタには、各エラー検出機能に対応するエラー・フラグ・ビットがあります。

### 巡回冗長検査(CRC)エラーの検出

CRC エラー検出機能では、有効な SPI フレームが 8 つの SCLK サイクル分だけ拡張されます。8 つの追加サイクルは、SPI フレームの CRC バイトを送信するために必要です。CRC バイトは、16 ビットのペイロードを使用して SPI ブロックによって計算されます。ペイロードは、 $R/\overline{W}$ ビット、レジスタ・アドレスのビット[6:0]、レジスタ・データのビット[7:0]で構成されます。SPI ブロックで使用される CRC 多項式は、 $x^8+x^2+x^1+1$ 、シード値は 0 です。CRC を有効にした場合のタイミング図については、図 47 を参照してください。レジスタへの書込みは、CRC エラー・チェックを有効にした場合に 24 番目の SCLK 立上がりエッジで発生します。

SPI の書込み中に、マイクロコントローラまたは CPU (中央処理装置) は、SDI 経由で CRC バイトを出力します。SPI ブロックは、24 番目の SCLK 立上がりエッジ直前に CRC バイトをチェックします。同じエッジで、SPI から不正な CRC バイトが受信されると、レジスタへの書込みは阻止されます。不正な CRC バイトが検出された場合、エラー・フラグ・レジスタの CRC エラー・フラグがアサートされます。

SPI の読出しを実行中、CRC バイトは SDO からマイクロコントローラに出力されます。

CRC エラー検出機能は、デフォルトでは無効になっています。 この機能はエラー設定レジスタで設定できます。

図 47. CRC が有効な場合のタイミング図

#### 動作原理

### SCLK カウント・エラー検出

SCLK カウント・エラー検出を使用すると、不正な SCLK サイクル数がマイクロコントローラまたは CPU から送信されたかどうかを検出できます。アドレス・モードで CRC を無効にすると、SCLK サイクルの発生回数は16回になります。検出される SCLK サイクルの回数が 16 以外の場合、SCLK カウントのエラー・フラグがエラー・フラグ・レジスタでアサートされます。デバイスによって受信される SCLK サイクルの回数が 16 未満の場合、レジスタ・マップへの書込みは発生しません。ADGS6414D によって受信される SCLK サイクルの回数が 16 を超える場合も、メモリ・マップへの書込みが 16 番目の SCLK 立上がりエッジで発生し、エラー・フラグ・レジスタでフラグがアサートされます。CRC を有効にすると、発生する SCLK サイクルの回数は 24です。SCLK カウント・エラー検出は、デフォルトで有効です。この機能はエラー設定レジスタで設定できます。

### 無効な読出し/書込みアドレス・エラー

存在しないレジスタ・アドレスが読出しまたは書込みのターゲットになると、無効な読出し/書込みアドレス・エラーが検出されます。更に、このエラーは、読出し専用レジスタに書出しが試行された場合にもアサートされます。無効な読出し/書込みアドレス・エラーが発生すると、エラー・フラグ・レジスタの無効な読出しおよび書込みアドレス・エラー・フラグがアサートされます。無効な読出し/書込みアドレスのエラーは、9番目のSCLK立上がりエッジで検出されます。つまり、無効なアドレスがターゲットになっている場合、レジスタへの書込みない発生しません。無効な読出し/書込みアドレス・エラー検出は、デフォルトで有効です。この機能はエラー設定レジスタで無効にできます。

## エラー・フラグ・レジスタのクリア

エラー・フラグ・レジスタをクリアするには、専用の 16 ビット SPI フレーム 0x6CA9 をデバイスに書き込みます。この SPI コマンドを実行しても、無効な  $R/\overline{W}$ アドレス・エラーはトリガされません。CRC が有効な場合、エラー・クリア・コマンドを正常に完了するため、CRC バイトも送信する必要があります。16 番目または 24 番目の SCLK 立上がりエッジで、エラー・フラグ・レジスタは 0 にリセットされます。

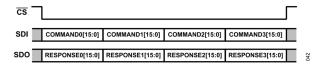

#### バースト・モード

無効な読出し/書込みアドレスおよび CRC のエラー・チェック機能は、バースト・モードの実行中もアドレス・モードでのエラー・チェック機能と同様に動作します。ただし、SCLK カウント・エラー検出の動作は若干異なります。特定の $\overline{CS}$ フレーム内で SCLK サイクルの合計がカウントされ、CRC を有効にした状態で合計が 16 または 24 の倍数でない場合、SCLK カウント・エラー・フラグがアサートされます。

図 48. バースト・モード・フレーム

### ソフトウェア・リセット

アドレス・モードの場合、レジスタ 0x0B をターゲットとする連続した2つの SPI コマンド (つまり 0xA3 と 0x05) を書き込むことでソフトウェア・リセットを起動できます。ソフトウェア・リセットの後に、すべてのレジスタ値がデフォルトに設定されます。

### デイジーチェーン・モード

デイジーチェーン設定では、複数の ADGS6414D デバイスを接続できます。図 49 に、このセットアップを示します。すべてのデバイスが同じ $\overline{CS}$ 、SCLK、 $V_L$  ラインを共有し、また、デバイスの SDO は次のデバイスの SDI に接続され、シフト・レジスタが作成されます。デイジーチェーン・モードでは、SDO は SDIの 8 サイクル遅延したバージョンになります。デイジーチェーン・モードでは、すべてのコマンドがスイッチ・データ・レジスタをターゲットにします。そのため、デイジーチェーン・モードでは設定を変更できません。

アドレス・モードの場合、ADGS6414D は、16 ビットの SPI コマンド、0x2500 を送信することによってのみ、デイジーチェーン・モードに移行できます(図 50 を参照)。ADGS6414D がこのコマンドを受信すると、SDO のアライメント・ビットが 0x25 であるため、デバイスの SDO が同じコマンドを送信します。これにより、デイジーチェーン接続された複数のデバイスを単一の SPI フレームでデイジーチェーン・モードに移行できます。デイジーチェーン・モードを終了するには、ハードウェア・リセットが必要です。

代表的なデイジーチェーン SPI フレームのタイミング図については、図 51 を参照してください。 $\overline{\text{CS}}$ がハイになると、デバイス1 はコマンド 0、ビット[7:0]をスイッチ・データ・レジスタに書き込み、デバイス2 はコマンド 1、ビット[7:0]をスイッチに書き込みます。残りのデバイスも同様にコマンドを実行します。SPI ブロックでは、SDI から受信した最後の8 ビットを使用してスイッチが更新されます。デイジーチェーン・モードに移行した後、チェーン内の各デバイスに搭載されたSDO によって送信される最初の8 ビットは 0x00 です。 $\overline{\text{CS}}$ がハイになっても、内部シフト・レジスタ値は 0 にリセットされません。

SCLK 立上がりエッジでは、SDIからデータが読み取られます。 一方、SCLK 立下がりエッジでは、SDO からデータが伝搬されます。

#### 動作原理

図 49. デイジーチェーン構成で接続された 2 個の ADGS6414D デバイス

図 50. デイジーチェーン・モードに移行する SPI コマンド

NOTES

1. SDO2 AND SDO3 ARE THE OUTPUT COMMANDS FROM DEVICE 2 AND DEVICE 3, RESPECTIVELY.

図 51. デイジーチェーン・モードで 4 個の ADGS6414D デバイスが接続される SPI フレームの例

analog.com.jp Rev. 0 | 24 of 32

### 動作原理

### パワーオン・リセット

ADGS6414D のデジタル・セクションは、 $V_L$  の電源投入時に初期化フェーズを実行します。この初期化は、ハードウェアまたはソフトウェアのリセット後にも発生します。 $V_L$  の電源投入またはリセットの後、少なくとも 120 $\mu$ s 経過してから SPI コマンドを発行するようにしてください。120 $\mu$ s の初期化フェーズでは、 $V_L$  がドロップアウトしないよう注意してください。ドロップアウトすると、ADGS6414D が異常な動作をする可能性があるためです。

analog.com.jp Rev. 0 | 25 of 32

### アプリケーション情報

### 高電圧、高周波の信号のトラッキング

図 31 に、ADGS6414D が安定して動作できる電圧範囲とそれに対応する周波数を示します。この図のトラッキング電圧 (VTRACK) は、ソース電圧とドレイン電圧の差を示しており、その値は与えられた振幅および周波数に対し 50mV 未満です。電圧が高く周波数が高い信号の場合、周波数は 10MHz 未満であることが必要です。必要な周波数が 10MHz を超える場合は、信号の完全性を維持するため信号範囲を適宜小さくしてください。

### システム・チャンネル密度

ADGS6414Dの機能セットでは、大きなシステム・チャンネル密度が可能です。これらの機能には、デジタル信号および電源のスルー配線ピンや、内蔵受動部品があります。

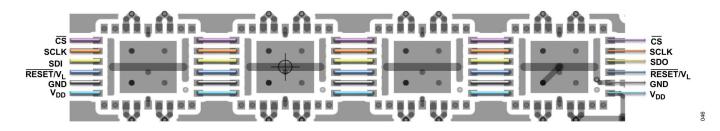

#### スルー配線ピン

複数の ADGS6414D デバイスを 1 つのシステムで使用する場合、スルー配線ピンによってレイアウトのチャンネル密度を増大できます。スルー配線ピンを使用すると、デバイス間の電源やデジタル・ラインの受け渡しが容易にできます。 $V_{DD}$ 、 $\overline{RESET}/V_L$ 、GND の電源ラインや SCLK、 $\overline{CS}$ 、SDI、SDO のデジタル・ライ

ンは、パッケージの上部と下部の両方のピンで使用できます。これらのスルー配線ピンによって PCB 配線が簡素化でき、多数の ADGS6414D を相互に接続する場合にビアの必要性を減少できます。図 52 に、デイジーチェーン・モードに構成された 4 個の ADGS6414D デバイスのスルー配線ピンを使用して、レイアウトの全体的なサイズを縮小した例を示します。

#### 内蔵の受動部品

図 52 のレイアウトには外付けの受動部品がないことに注意してください。ADGS6414D では、 $V_{DD}$ 、 $V_{SS}$ 、 $\overline{RESET}/V_L$  の電源用にデカップリング・コンデンサが内蔵されています。そのため、デカップリング・コンデンサを外付けする必要がなく、ADGS6414Dシステム全体のフットプリントを縮小できます。ノイズに非常に敏感なアプリケーション用にデカップリングを追加する必要がある場合は、外付けのデカップリング・コンデンサを追加してください。図 27 に、外付けデカップリング・コンデンサがある場合とない場合での AC PSRR 性能を示します。また、ADG6414Dには、 $V_L$ と SDOピンの間にプルアップ抵抗が内蔵されています。

図 52. 配線ピンを使用し、外付けの受動部品を使用しないレイアウト例

analog.com.jp Rev. 0 | 26 of 32

### アプリケーション情報

## ブレーク・ビフォア・メーク・スイッチング機能

ADGS6414Dは、ブレーク・ビフォア・メークのスイッチング動作を行います。この機能により、デバイスをマルチプレクサ・アプリケーションで使用できます。デバイスをマルチプレクサとして使用するには、図 53 に示すように、デバイスを目的のマルチプレクサ構成に外部配線します。

図 53.4:1 Mux に構成された SPI コントロール・スイッチ

### デジタル入力バッファ

デジタル入力ピン( $\overline{\text{CS}}$ 、SCLK、SDI)には入力バッファがあります。これらのバッファは、常にアクティブです。そのため、 $\overline{\text{CS}}$ がアクティブであるかどうかに関係なく、SCLK または SDIがトグルすると、VL 電源から電流が流れます。この電流引き込みの代表値については、仕様のセクションと図 34 を参照してください。

#### 電源レール

ADGS6414D は $\pm$ 4.5V $\sim$  $\pm$ 22V のバイポーラ電源で動作できます。  $V_{DD}$ の電源と  $V_{SS}$ の電源は対称である必要はありません。ただし、  $V_{DD}$ と  $V_{SS}$ の電圧差が 44V を超えてはなりません。ADGS6414D は、 $V_{SS}$ を GND に接続して 5V $\sim$ 40V の単電源で動作することもできます。  $V_L$ に供給できる電圧範囲は 2.7V $\sim$ 5.5V です。デバイスは $\pm$ 20V、 $\pm$ 36V のアナログ電圧範囲で仕様規定されています。

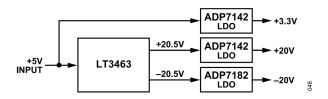

#### 電源の推奨事項

アナログ・デバイセズでは、高性能シグナル・チェーンの条件 を満たせるよう、広範なパワー・マネージメント製品を提供し ています。

バイポーラ電源ソリューションの例を図 54 に示します。LT3463 (デュアル・スイッチング・レギュレータ) は、典型的なシグナル・チェーンでの ADGS6414D、アンプ、高精度コンバータ向けに正と負の電源レールを生成します。図 54 に示すように、オプションで 2 つの低ドロップアウト・レギュレータ (LDO)、ADP7142 (正のLDO) と ADP7182 (負のLDO) があります。これらの LDO を使用すると、極めて小さなノイズにも敏感なアプリケーションで LT3463 の出力リップルを削減できます。

ADP7142 を使用すると、ADGS6414D 内のデジタル回路に電力を供給するのに必要な  $V_L$ 電圧を生成できます。

図 54. バイポーラ電源ソリューション

表 11. 推奨されるパワー・マネージメント・デバイス

| Product | Description                                              |

|---------|----------------------------------------------------------|

| LT3463  | Dual micropower, DC to DC converter with Schottky diodes |

| ADP7142 | 40V, 200mA, low noise, CMOS, LDO linear regulator        |

| ADP7182 | -28V, -200mA, low noise, LDO linear regulator            |

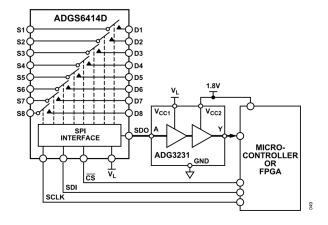

### 1.8V ロジックとの互換性

ADGS6414D の SDI、 $\overline{\text{CS}}$ 、SCLK の各デジタル入力は、 $V_L$  が 2.7V $\sim$ 3.3V の場合、1.8V ロジックに対応可能です。

SDO デジタル出力レベルは、 $V_L$ の電圧に比例します。例えば、 $V_L=3V$ の場合、SDO のロジック・ハイは、約3Vです。1.8V ロジックを使用するコントローラ・デバイスで ADGS6414D から SPI リードバックを実行する場合、コントローラのデジタル・ピンが 1.8V を超えるデジタル入力信号を許容できない場合、問題が発生する可能性があります。

図 55 は、ADG3231 レベル変換器を使用して、マイクロコントローラや FPGA(フィールド・プログラマブル・ゲート・アレイ)などの 1.8V ロジック・ポートを持つデバイスで 1.8V の SPIリードバックを実行する方法を示すものです。ADGS6414D の SDO とマイクロコントローラまたは FPGA の間に ADG3231 を配置します。ADG3231 の電源  $V_{CCI}$  に ADGS6414D の  $V_L$  の電圧を供給し、 $V_{CC2}$ をマイクロコントローラまたは FPGA の 1.8V 電源に接続します。このようにすることで、ADG3231 は SDO のロジック・レベルを  $V_L$  から 1.8V に変換します。

このソリューションが必要となるのは、1.8V のマイクロコントローラまたは FPGA が 1.8V を超えるデジタル入力信号を許容できない場合のみです。

図 55. ADG3231 を使用して 1.8V SPI リードバックを実行

# レジスタの一覧

表 12. レジスタの一覧

| Reg. | Name        | Bit 7    | Bit 6                  | Bit 5  | Bit 4  | Bit 3  | Bit 2       | Bit 1         | Bit 0        | Default | R/W |

|------|-------------|----------|------------------------|--------|--------|--------|-------------|---------------|--------------|---------|-----|

| 0x01 | SW_DATA     | SW8_EN   | SW7_EN                 | SW6_EN | SW5_EN | SW4_EN | SW3_EN      | SW2_EN        | SW1_EN       | 0x00    | R/W |

| 0x02 | ERR_CONFIG  | Reserved |                        |        |        |        | RW_ERR_EN   | SCLK_ERR_EN   | CRC_ERR_EN   | 0x06    | R/W |

| 0x03 | ERR_FLAGS   |          | Reserved               |        |        |        | RW_ERR_FLAG | SCLK_ERR_FLAG | CRC_ERR_FLAG | 0x00    | R   |

| 0x05 | BURST_EN    |          | Reserved BURST_MODE_EN |        |        |        |             |               | 0x00         | R/W     |     |

| 0x0B | SOFT_RESETB |          | SOFT_RESETB            |        |        |        |             |               | 0x00         | W       |     |

analog.com.jp Rev. 0 | 28 of 32

### レジスタの詳細

## スイッチ・データ・レジスタ

アドレス: 0x01、リセット: 0x00、レジスタ名: SW\_DATA

スイッチ・データ・レジスタを使用して、ADGS6414Dの8個のスイッチのステータスを制御します。

表 13. SW DATA のビットの説明

| ビット | ビット名   | 設定 | 説明                         | デフォルト | アクセス |

|-----|--------|----|----------------------------|-------|------|

| 7   | SW8_EN |    | スイッチ 8 の SW8_EN ビットをイネーブル。 | 0x0   | R/W  |

|     |        | 0  | スイッチ 8 オープン。               |       |      |

|     |        | 1  | スイッチ8クローズ。                 |       |      |

| 6   | SW7_EN |    | スイッチ 7 の SW7_EN ビットをイネーブル。 | 0x0   | R/W  |

|     |        | 0  | スイッチ 7 オープン。               |       |      |

|     |        | 1  | スイッチ7クローズ。                 |       |      |

| 5   | SW6_EN |    | スイッチ 6 の SW6_EN ビットをイネーブル。 | 0x0   | R/W  |

|     |        | 0  | スイッチ 6 オープン。               |       |      |

|     |        | 1  | スイッチ6クローズ。                 |       |      |

| 4   | SW5_EN |    | スイッチ 5 の SW5_EN ビットをイネーブル。 | 0x0   | R/W  |

|     |        | 0  | スイッチ 5オープン。                |       |      |

|     |        | 1  | スイッチ 5 クローズ。               |       |      |

| 3   | SW4_EN |    | スイッチ 4 の SW4_EN ビットをイネーブル。 | 0x0   | R/W  |

|     |        | 0  | スイッチ4オープン。                 |       |      |

|     |        | 1  | スイッチ4クローズ。                 |       |      |

| 2   | SW3_EN |    | スイッチ 3 の SW3_EN ビットをイネーブル。 | 0x0   | R/W  |

|     |        | 0  | スイッチ 3 オープン。               |       |      |

|     |        | 1  | スイッチ 3 クローズ。               |       |      |

| 1   | SW2_EN |    | スイッチ 2 の SW2_EN ビットをイネーブル。 | 0x0   | R/W  |

|     |        | 0  | スイッチ 2 オープン。               |       |      |

|     |        | 1  | スイッチ2クローズ。                 |       |      |

| 0   | SW1_EN |    | スイッチ 1 の SW1_EN ビットをイネーブル。 | 0x0   | R/W  |

|     |        | 0  | スイッチ 1 オープン。               |       |      |

|     |        | 1  | スイッチ 1 クローズ。               |       |      |

### エラー設定レジスタ

### アドレス: 0x02、リセット: 0x06、レジスタ名: ERR\_CONFIG

エラー設定レジスタを使用して、必要に応じて関連するエラー検出機能を有効または無効にします。

### 表 14. ERR CONFIG のビットの説明

| ビット   | ビット名        | 設定 | 説明                                                                                                                                                                                                                                                                      | デフォルト | アクセス |

|-------|-------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| [7:3] | Reserved    |    | ビット[7:3]は予備。ビット[7:3]は0に設定します。                                                                                                                                                                                                                                           | 0x0   | R    |

| 2     | RW_ERR_EN   | 0  | RW_ERR_EN ビットをイネーブルして、無効な読出しおよび書込みアドレスを検出。<br>ディスエーブル。                                                                                                                                                                                                                  | 0x1   | R/W  |

| 1     | SCLK_ERR_EN | 0  | イネーブル。  SCLK_ERR_EN ビットをイネーブルして、SPI フレームの正しい SCLK サイクル数を検出。CRC が無効で、バースト・モードが無効の場合、SCLK サイクルの回数は16になるはずです。CRC が有効で、バースト・モードが無効の場合、SCLK サイクルの回数は24になるはずです。CRC が無効で、バースト・モードが有効の場合、SCLK サイクルの回数は16の倍数になります。CRC が有効で、バースト・モードが有効の場合、SCLK サイクルの回数は24の倍数になります。ディスエーブル。イネーブル。 |       | R/W  |

| 0     | CRC_ERR_EN  | 0  | CRC_ERR_EN ビットをイネーブルして、CRC エラーを検出。有効な場合の SPI フレームは 24 ビットです。<br>ディスエーブル。<br>イネーブル。                                                                                                                                                                                      | 0x0   | R/W  |

analog.com.jp Rev. 0 | 29 of 32

### レジスタの詳細

### エラー・フラグ・レジスタ

### アドレス: 0x03、リセット: 0x00、レジスタ名: ERR\_FLAGS

エラー・フラグ・レジスタを使用すると、エラーが発生したかどうかを判断できます。エラー・フラグ・レジスタをクリアするには、16 ビットの専用 SPI コマンド 0x6CA9 をデバイスに書き込みます。この SPI コマンドを実行しても、無効な  $R/\overline{W}$ アドレス・エラーはトリガされません。CRC が有効な場合、エラー・フラグ・レジスタのクリア・コマンドを正常に完了するには、SPI の書込みで正しい CRC バイトを挿入する必要があります。

#### 表 15. ERR FLAGS のビット説明

| ビット   | ビット名          | 設定 | 説明                                                                                                                             | デフォルト | アクセス |

|-------|---------------|----|--------------------------------------------------------------------------------------------------------------------------------|-------|------|

| [7:3] | Reserved      |    | ビット[7:3]は予備で、0に設定します。                                                                                                          | 0x0   | R    |

| 2     | RW_ERR_FLAG   |    | 無効な読出しおよび書込みアドレスのエラー・フラグ。ターゲット・アドレスが存在しない場合、SPI 読出しでエラー・フラグがアサートされます。また、SPI 書込みのアドレスが存在しない場合、または読出し専用である場合にも、エラー・フラグがアサートされます。 | 0x0   | R    |

|       |               | 0  | エラーなし。                                                                                                                         |       |      |

|       |               | 1  | エラー。                                                                                                                           |       |      |

| 1     | SCLK_ERR_FLAG |    | SPI フレームの SCLK サイクルの数が正しいかどうかを検出するためのエラー・フラグ。                                                                                  | 0x0   | R    |

|       |               | 0  | エラーなし。                                                                                                                         |       |      |

|       |               | 1  | エラー。                                                                                                                           |       |      |

| 0     | CRC_ERR_FLAG  |    | レジスタ書込みで CRC エラーが発生したかどうかを判断するエラー・フラグ。                                                                                         | 0x0   | R    |

|       |               | 0  | エラーなし。                                                                                                                         |       |      |

|       |               | 1  | エラー。                                                                                                                           |       |      |

### バースト・イネーブル・レジスタ

### アドレス: 0x05、リセット: 0x00、レジスタ名: BURST\_EN

バースト・イネーブル・レジスタを使用すると、バースト・モードを有効または無効にできます。バースト・モードを有効にすると、 $\overline{\text{CS}}$ をアサート解除せずに、複数の連続する SPI コマンドを送信できます。

#### 表 16. BURST ENのビット説明

| ビット   | ビット名        | 設定 | 説明                            | デフォルト | アクセス |

|-------|-------------|----|-------------------------------|-------|------|

| [7:1] | Reserved    |    | ビット[7:1]は予備。ビット[7:1]は0に設定します。 | 0x0   | R    |

| 0     | BURST_MODE_ |    | バースト・モード・イネーブル・ビット。           | 0x0   | R/W  |

|       | EN          | 0  | ディスエーブル。                      |       |      |

|       |             | 1  | イネーブル。                        |       |      |

analog.com.jp Rev. 0 | 30 of 32

### レジスタの詳細

## ソフトウェア・リセット・レジスタ

### アドレス: 0x0B、リセット: 0x00、レジスタ名: SOFT\_RESETB

ソフトウェア・リセットを実行するには、ソフトウェア・リセット・レジスタを使用します。このレジスタに 0xA3、0x05 の順に連続的に書込みを実行すると、デバイスのレジスタはデフォルト状態にリセットされます。

### 表 17. SOFT\_RESETB のビット説明

| ビット   | ビット名        | 設定 | 説明                                                                  | デフォルト | アクセス |

|-------|-------------|----|---------------------------------------------------------------------|-------|------|

| [7:0] | SOFT_RESETB |    | ソフトウェア・リセットを実行するには、SOFT_RESETB レジスタに 0xA3、0x05<br>の順に連続的に書込みを実行します。 | 0x0   | W    |

analog.com.jp Rev. 0 | 31 of 32

ADGS6414D -タシート

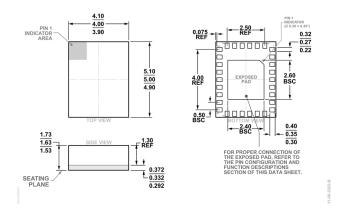

### 外形寸法

図 56. 30 端子ランド・グリッド・アレイ [LGA] (CC-30-3) 4mm × 5mm ボディ、1.63mm パッケージ高 寸法:mm

### オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description              | Packing Quantity | Package Option |

|--------------------|-------------------|----------------------------------|------------------|----------------|

| ADGS6414DBCCZ      | -40°C to +125°C   | 30-lead LGA (4mm × 5mm × 1.63mm) | Tray, 490        | CC-30-3        |

| ADGS6414DBCCZ-RL7  | -40°C to +125°C   | 30-lead LGA (4mm × 5mm × 1.63mm) | Reel, 1000       | CC-30-3        |

<sup>1</sup> Z = RoHS 準拠製品。

### 評価用ボード

表 18. 評価用ボード

| Model <sup>1</sup> | Description      |

|--------------------|------------------|

| EVAL-ADGS6414DARDZ | Evaluation Board |

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠製品。