# データシート ADG1634L

## 4.7Ω R<sub>ON</sub>、1.2Vおよび1.8V JEDECロジック準拠のクワッドSPDTスイッチ

### 特長

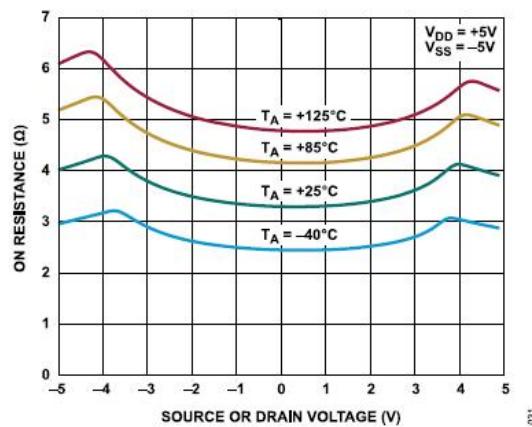

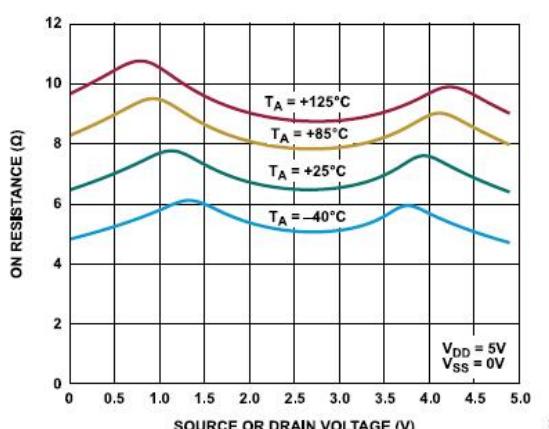

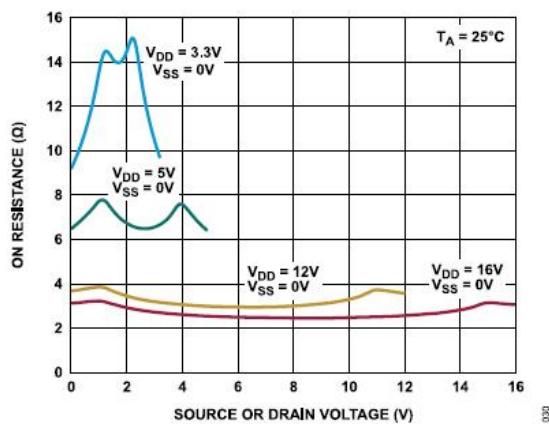

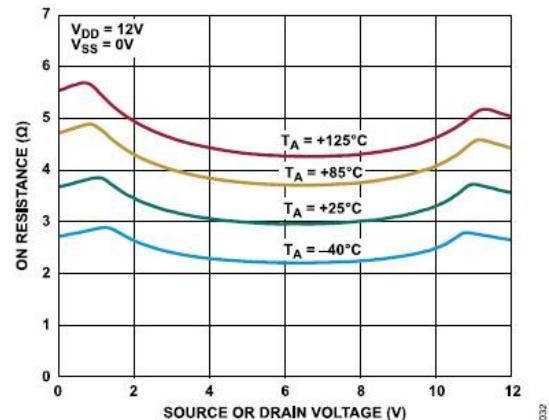

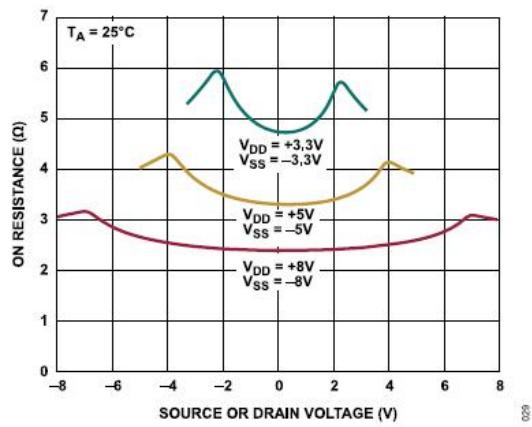

- ▶ オン抵抗 : 4.7Ω (代表値、±5V両電源、25°C)

- ▶ オン抵抗平坦性 : 1.2Ω (±5V両電源、25°C)

- ▶ ±5V、+12V、+5V、+3.3Vの電源で仕様規定

- ▶ 両電源動作 : ±3.3V~±8V

- ▶ 単電源動作 : 3.3V~16V

- ▶ 低ロジック・レベルとの互換性を確保するVL電源

- ▶ 1.8V JEDEC規格に準拠

- ▶ 1.2V JEDEC規格に準拠

- ▶ レールtoレール動作

- ▶ 24ピン、4mm × 4mm、LFCSP

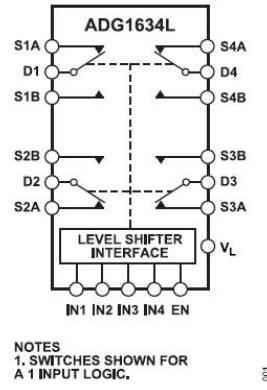

### 機能ブロック図

図 1.

### 製品のハイライト

1. 温度範囲全域で8.2Ωの最大オン抵抗。

2. 最小の歪み。

3. 低ロジック・レベルとの互換性を確保するVL電源。

4. 1.2Vと1.8Vの両方のロジック・レベルでJEDEC規格に準拠。

5. デジタル入力がフロート状態の場合はスイッチをオフにする機能をサポート。

6. 24ピン、4mm × 4mm、LFCSP。

### アプリケーション

- ▶ 通信システム

- ▶ 医療用システム

- ▶ オーディオ信号のルーティング

- ▶ ビデオ信号のルーティング

- ▶ ATE (自動試験装置)

- ▶ データ・アクイジション・システム

- ▶ バッテリ駆動のシステム

- ▶ FPGAおよびマイクロコントローラ・システム

- ▶ サンプル&ホールド・システム

- ▶ リレー部品の置き換え

### 概要

ADG1634Lは、個別に選択可能な4個のシングルポール・ダブル・スロー (SPDT) スイッチで構成されるモノリシックの工業用 CMOS (iCMOS®) アナログ・スイッチです。

全てのチャンネルはブレークビフォアメークの切替え動作を行うため、チャンネル切替え時の瞬間的な短絡を防ぎます。

ADG1634Lをイネーブルまたはディスエーブルするには、EN入力を使用します。ディスエーブルされると、全てのチャンネルがオフになります。このスイッチはロジック1のEN入力でイネーブルされ、INx入力によって各SPDTスイッチの状態が決まります (表12を参照)。

このスイッチは、オン抵抗とオン抵抗平坦性が極めて低いため、低歪みが重要となるデータ・アクイジション・アプリケーションやゲイン・スイッチング・アプリケーションに最適なソリューションです。また、iCMOS構造により消費電力が極めて少ないため、携帯型の計測器やバッテリ駆動の計測器に最適です。

外部VL電源を使用することで、低ロジック制御にも柔軟に対応できます。ADG1634Lは、1.2Vと1.8Vの両方のJEDEC規格に準拠しています。

Rev. 0

文書に関するご意見

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。

※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

テクニカルサポート

## 目次

|                              |    |                                                                             |    |

|------------------------------|----|-----------------------------------------------------------------------------|----|

| 特長                           | 1  | テスト回路                                                                       | 16 |

| アプリケーション                     | 1  | 用語の定義                                                                       | 18 |

| 概要                           | 1  | 動作原理                                                                        | 19 |

| 機能ブロック図                      | 1  | スイッチ・アーキテクチャ                                                                | 19 |

| 製品のハイライト                     | 1  | V <sub>L</sub> による柔軟性                                                       | 19 |

| 仕様                           | 3  | 1.2Vおよび1.8V JEDEC準拠                                                         | 19 |

| 動作電源電圧                       | 3  | 初期化時間                                                                       | 19 |

| ±15V両電源                      | 3  | 既知の状態のスイッチ                                                                  | 19 |

| +12V単電源                      | 4  | アプリケーション情報                                                                  | 20 |

| 5Vの単電源                       | 6  | フィールド・プログラマブル・ゲート・アレイ (FPGA) の低ロジック対応                                       | 20 |

| 3.3V単電源                      | 7  | V <sub>OH</sub> とV <sub>INH</sub> 、およびV <sub>OL</sub> とV <sub>INL</sub> の関係 | 20 |

| チャンネルごとの連続電流 (SxA、SxB、またはDx) | 9  | 電源レール                                                                       | 20 |

| 絶対最大定格                       | 10 | 電源の推奨事項                                                                     | 21 |

| 熱抵抗                          | 10 | 外形寸法                                                                        | 22 |

| 静電放電 (ESD) 定格                | 10 | オーダー・ガイド                                                                    | 22 |

| ESDに関する注意                    | 10 | 評価用ボード                                                                      | 22 |

| ピン配置とピン機能の説明                 | 11 |                                                                             |    |

| 代表的な性能特性                     | 12 |                                                                             |    |

## 改訂履歴

4/2022-Revision 0: Initial Version

## 仕様

## 動作電源電圧

表 1.

| パラメータ           | 最小値                   | 代表値 | 最大値         | 単位 | テスト条件／コメント                           |

|-----------------|-----------------------|-----|-------------|----|--------------------------------------|

| SUPPLY VOLTAGE  | $\pm 3.3$             |     | $\pm 8$     | V  | $V_{DD} \sim V_{SS}$                 |

|                 |                       |     |             |    | $V_{DD} \sim GND, V_{SS} = GND = 0V$ |

| DIGITAL VOLTAGE | Single<br>1.1<br>1.65 |     | 1.3<br>1.95 | V  | $V_L \sim GND, V_{INx} = 1.2V$ ロジック  |

|                 |                       |     |             |    | $V_L \sim GND, V_{INx} = 1.8V$ ロジック  |

## ±15V両電源

特に指定のない限り、 $V_{DD} = +5V \pm 10\%$ 、 $V_{SS} = -5V \pm 10\%$ 、 $GND = 0V$ 、 $V_L = 1.1V \sim 1.95V$ 。

表 2.

| パラメータ                                                       | +25°C                    | -40°C ~ +85°C        | -40°C ~ +125°C       | 単位                                                           | テスト条件／コメント                                               |

|-------------------------------------------------------------|--------------------------|----------------------|----------------------|--------------------------------------------------------------|----------------------------------------------------------|

| ANALOG SWITCH                                               |                          |                      |                      |                                                              |                                                          |

| Analog Signal Range                                         |                          |                      |                      |                                                              | $V_{DD} = +4.5V, V_{SS} = -4.5V$                         |

| On Resistance, $R_{ON}$                                     | 4.7                      |                      |                      | V<br>$\Omega$ typ                                            | $V_S = \pm 4.5V, I_S = -10mA$ 、図22を参照                    |

| On-Resistance Match Between Channels, $\Delta R_{ON}$       | 5.2<br>0.12              | 7.2<br>0.25          | 8.2<br>0.35          | $\Omega$ max<br>$\Omega$ typ<br>$\Omega$ max<br>$\Omega$ typ | $V_S = \pm 4.5V, I_S = -10mA$                            |

| On-Resistance Flatness, $R_{FLAT(ON)}$                      | 1.2<br>1.5               | 1.9                  | 2.1                  | $\Omega$ typ<br>$\Omega$ max                                 | $V_S = \pm 4.5V, I_S = -10mA$                            |

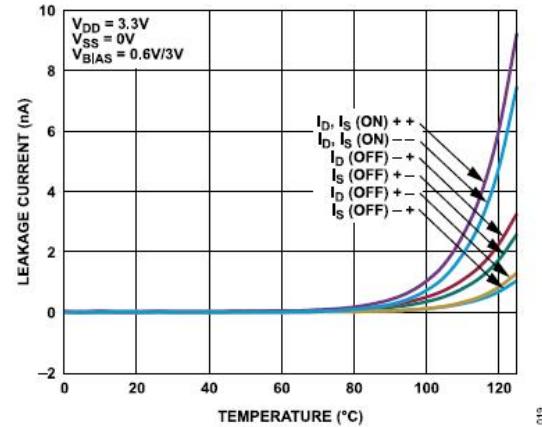

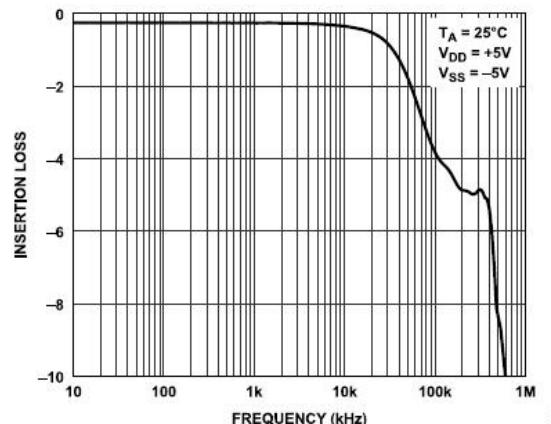

| LEAKAGE CURRENTS                                            |                          |                      |                      |                                                              |                                                          |

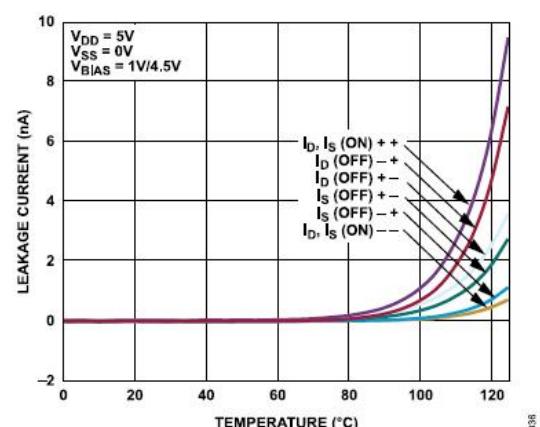

| Source Off, $I_S$ (Off)                                     | $\pm 0.01$               |                      |                      | nA typ                                                       | $V_{DD} = +5.5V, V_{SS} = -5.5V$                         |

| Drain Off, $I_D$ (Off)                                      | $\pm 0.15$<br>$\pm 0.02$ | $\pm 1.5$<br>$\pm 2$ | $\pm 12$<br>$\pm 20$ | nA max<br>nA typ<br>nA max<br>nA typ                         | $V_S = +4.5V \sim -4.5V, V_D = -4.5V \sim +4.5V$ 、図23を参照 |

| Drain Channel On, $I_D$ (On), Source Channel On, $I_S$ (On) | $\pm 0.15$<br>$\pm 0.02$ | $\pm 2$<br>$\pm 2$   | $\pm 20$<br>$\pm 20$ | nA max<br>nA typ<br>nA max                                   | $V_S = +4.5V \sim -4.5V, V_D = -4.5V \sim +4.5V$ 、図24を参照 |

| DIGITAL INPUTS                                              |                          |                      |                      |                                                              |                                                          |

| Input High Voltage, $V_{INH}$                               |                          |                      | 0.65 $\times V_L$    | V min                                                        |                                                          |

| Input Low Voltage, $V_{INL}$                                |                          |                      | 0.35 $\times V_L$    | V max                                                        |                                                          |

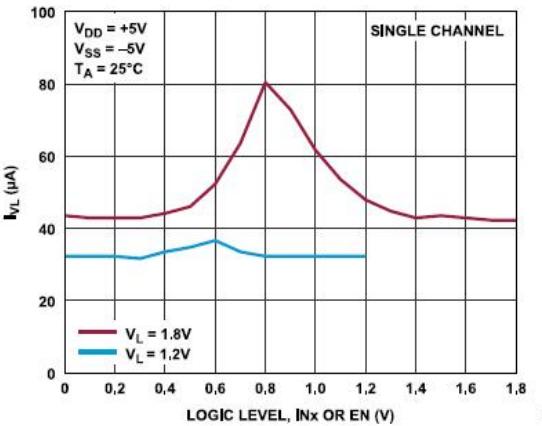

| Input High Current, $I_{INH}$                               | 55                       |                      |                      | $\mu A$ typ                                                  | $V_{INx}$ 電圧( $V_{INx} = V_L = 1.8V$ )、動作原理のセクションを参照     |

|                                                             |                          | 40                   | 90                   | $\mu A$ max<br>$\mu A$ typ                                   | $V_{INx} = V_L = 1.2V$ 、動作原理のセクションを参照                    |

| Input Low Current, $I_{INL}$                                | 0.2                      |                      | 65                   | $\mu A$ max<br>$\mu A$ typ                                   | $V_{INx} = 0V$                                           |

| Digital Input Capacitance, $C_{IN}$                         | 5                        |                      | 0.8                  | $\mu A$ max<br>pF typ                                        |                                                          |

## 仕様

表 2.

| パラメータ                                                              | +25°C | -40°C~+85°C | -40°C~+125°C | 単位      | テスト条件／コメント                                                        |

|--------------------------------------------------------------------|-------|-------------|--------------|---------|-------------------------------------------------------------------|

| DYNAMIC CHARACTERISTICS                                            |       |             |              |         |                                                                   |

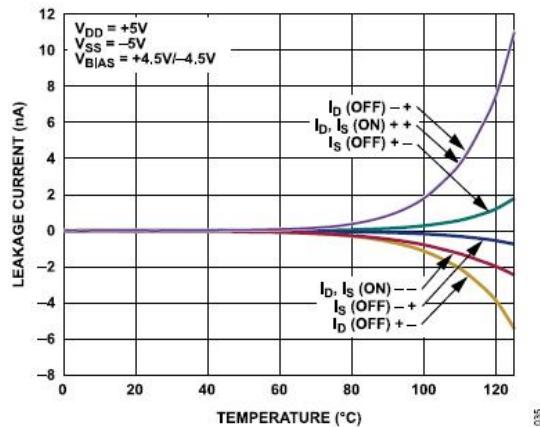

| Transition Time, $t_{TRANSITION}$                                  | 174   |             |              | ns typ  | $R_L = 300\Omega$ 、 $C_L = 35\text{ pF}$<br>$V_S = 2.5V$ 、図25を参照  |

| Enable Delay On Time, $t_{ON}$ (EN)                                | 220   | 251         | 271          | ns max  | $R_L = 300\Omega$ , $C_L = 35 \text{ pF}$<br>$V_S = 2.5V$ 、図27を参照 |

| Enable Delay Off Time, $t_{OFF}$ (EN)                              | 161   | 224         | 241          | ns typ  | $R_L = 300\Omega$ , $CL = 35 \text{ pF}$                          |

| Break-Before-Make Time Delay, $t_{BBM}$                            | 190   |             |              | ns max  | $V_S = 2.5V$ 、図27を参照                                              |

| Break-Before-Make Time Delay, $t_{BBM}$                            | 241   | 266         | 288          | ns typ  | $R_L = 300 \Omega$ , $CL = 35 \text{ pF}$                         |

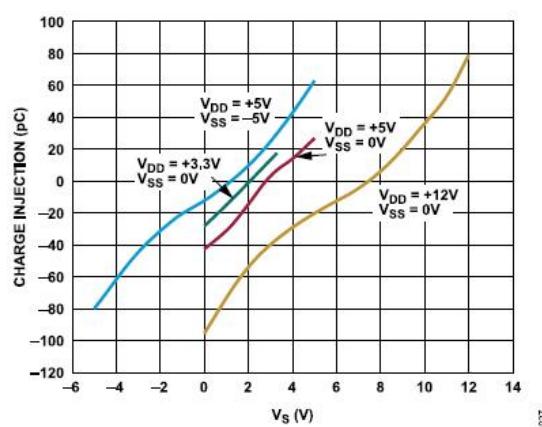

| Charge Injection, $Q_{INJ}$                                        | 43    |             | 29           | ns min  | $S1x$ 電圧( $V_{S1x}$ ) = $S2x$ 電圧( $V_{S2x}$ ) = 2.5V、<br>図26を参照   |

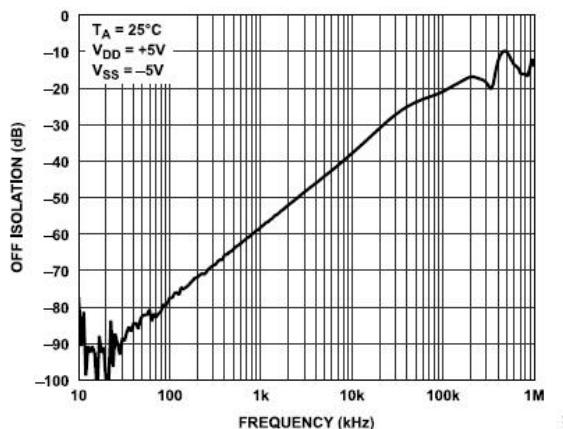

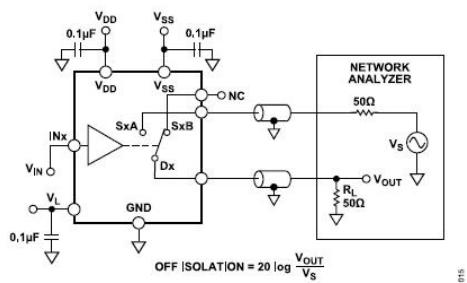

| Off Isolation                                                      | -12.5 |             |              | pC typ  | $V_S = 0V$ 、ソース抵抗 ( $RS$ ) = 0Ω、 $C_L = 1\text{nF}$ 、図28を参照       |

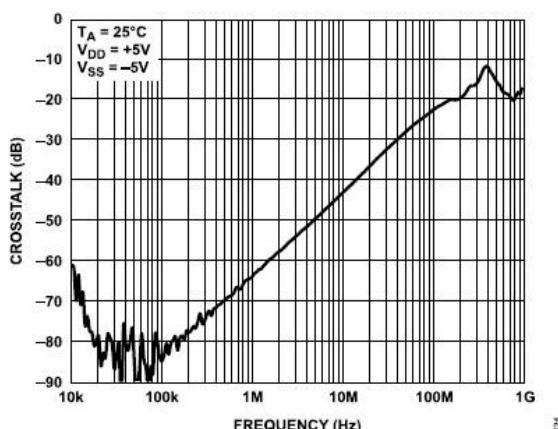

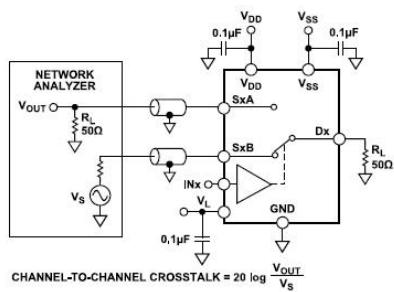

| Channel-to-Channel Crosstalk                                       | -58   |             |              | dB typ  | $RL = 50\Omega$ , $C_L = 5\text{ pF}$ 、周波数= 1MHz、<br>図29を参照       |

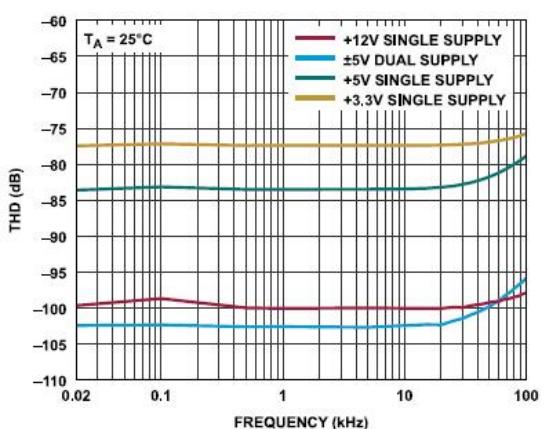

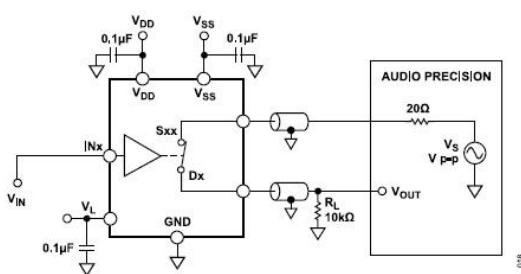

| Total Harmonic Distortion, THD                                     | -64   |             |              | dB typ  | $RL = 50\Omega$ , $C_L = 5\text{ pF}$ 、周波数= 1MHz、<br>図31を参照       |

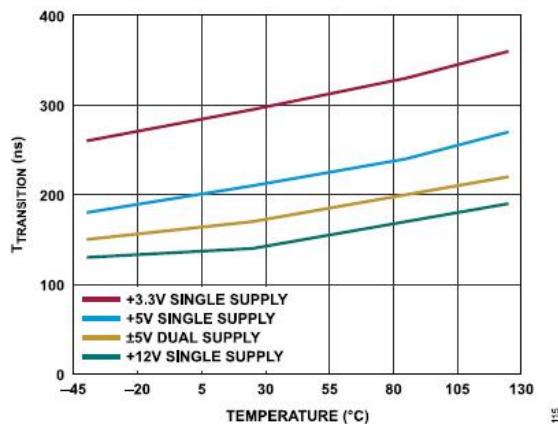

| -3 dB Bandwidth                                                    | -102  |             |              | dB typ  | $RL = 10k\Omega$ , $V_S = 5V$ p-p、周波数= 1kHz~<br>20kHz、図20参照       |

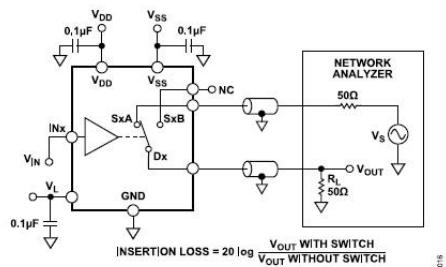

| Insertion Loss                                                     | -95   |             |              | dB typ  | $RL = 10k\Omega$ , $V_S = 5V$ p-p、周波数= 100kHz、<br>図20参照           |

| Source Off Capacitance, $C_S$ (Off)                                | 0.002 |             |              | % typ   | $RL = 10 k\Omega$ , $V_S = 5V$ p-p、周波数= 100kHz、<br>図32を参照         |

| Drain Off Capacitance, $C_D$ (Off)                                 | 77    |             |              | MHz typ | $RL = 50\Omega$ , $C_L = 5\text{ pF}$ 、図30を参照                     |

| Drain On Capacitance $C_D$ (On), Source On Capacitance, $C_S$ (On) | 0.26  |             |              | dB typ  | $RL = 50\Omega$ , $C_L = 5\text{ pF}$ 、図30を参照                     |

| Source On Capacitance, $C_S$ (On)                                  | 19    |             |              | pF typ  | $V_S = 0V$ 、周波数= 1MHz                                             |

| Drain On Capacitance $C_D$ (On)                                    | 33    |             |              | pF typ  | $V_S = 0V$ 、周波数= 1MHz                                             |

| POWER REQUIREMENTS                                                 | 57    |             |              | pF typ  | $V_S = 0V$ 、周波数= 1MHz                                             |

| Positive Supply Current ( $I_{DD}$ )                               | 50    |             |              | μA typ  | $V_{DD} = +5.5V$ 、 $V_{SS} = -5.5V$<br>$V_{INx} = 0V$ または $V_L$   |

| Negative Supply Current ( $I_{SS}$ )                               | 0.001 | 90          |              | μA max  | $V_{INx} = 0V$ または $V_L$                                          |

| Digital Supply Current ( $I_{VL}$ )                                | 45    | 1           |              | μA typ  | $V_{INx} = V_L = 1.8V$                                            |

|                                                                    | 30    | 70          |              | μA max  | $V_{INx} = V_L = 1.2 V$                                           |

|                                                                    |       | 55          |              | μA typ  |                                                                   |

|                                                                    |       |             |              | μA max  |                                                                   |

## +12V单電源

特に指定のない限り、 $V_{DD} = 12V \pm 10\%$ 、 $V_{SS} = 0V$ 、 $GND = 0V$ 、 $V_L = 1.1V \sim 1.95V$ 。

表 3.

| パラメータ                   | +25°C | -40°C~+85°C | -40°C~+125°C    | 単位    | テスト条件／コメント                                  |

|-------------------------|-------|-------------|-----------------|-------|---------------------------------------------|

| ANALOG SWITCH           |       |             |                 |       |                                             |

| Analog Signal Range     |       |             | 0 V to $V_{DD}$ | V     |                                             |

| On Resistance, $R_{ON}$ | 4.1   |             |                 | Ω typ | $V_S = 0V \sim 10V$ 、 $I_S = -10mA$ 、図22を参照 |

|                         | 4.6   | 6.6         | 7.6             | Ω max | $V_{DD} = 10.8V$ 、 $V_{SS} = 0V$            |

## 仕様

表 3.

| パラメータ                                                              | +25°C      | -40°C~+85°C | -40°C~+125°C      | 単位           | テスト条件／コメント                                                                   |

|--------------------------------------------------------------------|------------|-------------|-------------------|--------------|------------------------------------------------------------------------------|

| On-Resistance Match Between Channels, $\Delta R_{ON}$              | 0.12       |             |                   | $\Omega$ typ | $V_S = 10V, I_S = -10mA$                                                     |

|                                                                    | 0.25       | 0.3         | 0.35              | $\Omega$ max |                                                                              |

| On-Resistance Flatness, $R_{FLAT(ON)}$                             | 1          |             |                   | $\Omega$ typ | $V_S = 0V \sim 10V, I_S = -10mA$                                             |

|                                                                    | 13         | 1.7         | 2                 | $\Omega$ max |                                                                              |

| LEAKAGE CURRENTS                                                   |            |             |                   |              |                                                                              |

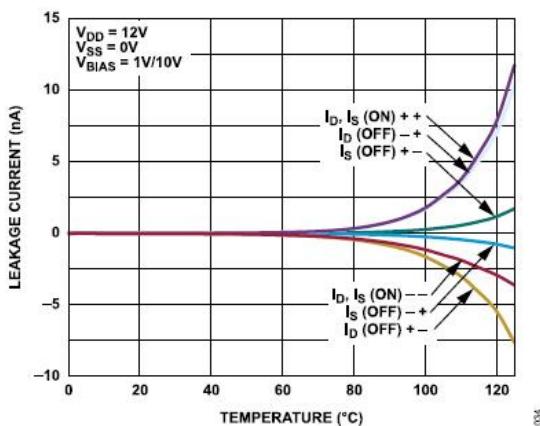

| Source Off, $I_S$ (Off)                                            | $\pm 0.01$ |             |                   | nA typ       | $V_{DD} = 13.2V, V_{SS} = 0V$                                                |

|                                                                    |            | $\pm 0.15$  | $\pm 1.5$         | nA max       | $V_S = 1V/10V, V_D = 10V/1V, \text{図23を参照}$                                  |

| Drain Off, $I_D$ (Off)                                             | $\pm 0.02$ |             |                   | nA typ       | $V_S = 1V/10V, V_D = 10V/1V, \text{図23を参照}$                                  |

|                                                                    | $\pm 0.15$ | $\pm 2$     | $\pm 20$          | nA max       |                                                                              |

| Drain Channel On, $I_D$ (On), Source Channel On, $I_S$ (On)        | $\pm 0.02$ |             |                   | nA typ       | $V_S = V_D = 1V \text{または} 10V, \text{図24を参照}$                               |

|                                                                    | $\pm 0.15$ | $\pm 2$     | $\pm 20$          | nA max       |                                                                              |

| DIGITAL INPUTS                                                     |            |             |                   |              |                                                                              |

| Input High Voltage, $V_{INH}$                                      |            |             | 0.65 $\times V_L$ | V min        |                                                                              |

|                                                                    |            |             |                   | V max        |                                                                              |

| Input Low Voltage, $V_{INL}$                                       |            | 55          |                   | $\mu A$ typ  | $V_{IN} = V_L = 1.8V, \text{動作原理のセクションを参照}$                                  |

|                                                                    |            | 40          | 90                | $\mu A$ max  |                                                                              |

| Input High Current, $I_{INH}$                                      |            |             |                   | $\mu A$ typ  | $V_{IN} = V_L = 1.2V, \text{動作原理のセクションを参照}$                                  |

|                                                                    |            | 0.2         | 65                | $\mu A$ max  |                                                                              |

| Input Low Current, $I_{INL}$                                       |            |             |                   | $\mu A$ typ  | $V_{IN} = 0V$                                                                |

|                                                                    |            | 5           | 0.8               | $\mu A$ max  |                                                                              |

|                                                                    |            |             |                   | pF typ       |                                                                              |

| DYNAMIC CHARACTERISTICS                                            |            |             |                   |              |                                                                              |

| Transition Time, $t_{TRANSITION}$                                  | 145        |             |                   | ns typ       | $R_L = 300 \Omega, C_L = 35pF$                                               |

|                                                                    | 185        | 208         | 231               | ns max       | $V_S = 8V, \text{図25を参照}$                                                    |

| Enable Delay On Time, $t_{ON}$ (EN)                                | 127        |             |                   | ns typ       | $R_L = 300\Omega, C_L = 35pF$                                                |

|                                                                    | 154        | 166         | 177               | ns max       | $V_S = 8V, \text{図27を参照}$                                                    |

| Enable Delay Off Time, $t_{OFF}$ (EN)                              | 159        |             |                   | ns typ       | $R_L = 300\Omega, C_L = 35pF$                                                |

|                                                                    | 195        | 218         | 241               | ns max       | $V_S = 8V, \text{図27を参照}$                                                    |

| Break-Before-Make Time Delay, $t_{BBM}$                            | 44         |             |                   | ns typ       | $R_L = 300\Omega, C_L = 35pF$                                                |

|                                                                    |            |             | 30                | ns min       | $V_{S1} = V_{S2} = 8V, \text{図26を参照}$                                        |

| Charge Injection, $Q_{INJ}$                                        | -12.4      |             |                   | pC typ       | $V_S = 6V, R_S = 0\Omega, C_L = 1nF, \text{図28を参照}$                          |

|                                                                    | -58        |             |                   | dB typ       | $R_L = 50\Omega, C_L = 5pF, \text{周波数} = 1MHz, \text{図29を参照}$                |

| Channel-to-Channel Crosstalk                                       | -64        |             |                   | dB typ       | $R_L = 50\Omega, C_L = 5pF, f = 1MHz, \text{図31を参照}$                         |

|                                                                    | -99        |             |                   | dB typ       | $R_L = 10k\Omega, V_S = 5V p-p, \text{周波数} = 1kHz \sim 20kHz, \text{図20を参照}$ |

| Total Harmonic Distortion, THD                                     | -97        |             |                   | dB typ       | $R_L = 10 k\Omega, V_S = 5V p-p, \text{周波数} = 100kHz, \text{図20を参照}$         |

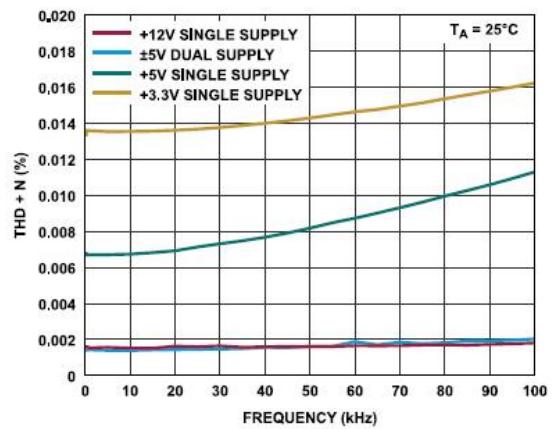

|                                                                    | 0.0018     |             |                   | % typ        | $R_L = 10 k\Omega, V_S = 5V p-p, \text{周波数} = 100kHz, \text{図32を参照}$         |

| -3 dB Bandwidth                                                    | 77         |             |                   | MHz typ      | $R_L = 50\Omega, C_L = 5pF, \text{図30を参照}$                                   |

| Insertion Loss                                                     | -0.21      |             |                   | dB typ       | $R_L = 50\Omega, C_L = 5pF, \text{図30を参照}$                                   |

| Source Off Capacitance, $C_S$ (Off)                                | 19         |             |                   | pF typ       | $V_S = 6V, \text{周波数} = 1MHz$                                                |

| Drain Off Capacitance, $C_D$ (Off)                                 | 32         |             |                   | pF typ       | $V_S = 6V, \text{周波数} = 1MHz$                                                |

| Drain On Capacitance $C_D$ (On), Source On Capacitance, $C_S$ (On) | 56         |             |                   | pF typ       | $V_S = 6V, \text{周波数} = 1MHz$                                                |

## 仕様

表 3.

| パラメータ                            | +25°C | -40°C~+85°C | -40°C~+125°C | 単位                         | テスト条件／コメント                                 |

|----------------------------------|-------|-------------|--------------|----------------------------|--------------------------------------------|

| POWER REQUIREMENTS               |       |             |              |                            |                                            |

| Positive Current, $I_{DD}$       | 55    |             | 95           | $\mu A$ typ<br>$\mu A$ max | $V_{DD} = 12V$<br>$V_{INx} = 0V$ または $V_L$ |

| Digital Supply Current, $I_{VL}$ | 45    |             | 70           | $\mu A$ typ<br>$\mu A$ max | $V_{INx} = V_L = 1.8V$                     |

|                                  | 30    |             | 55           | $\mu A$ typ<br>$\mu A$ max | $V_{INx} = V_L = 1.2V$                     |

## 5Vの单電源

特に指定のない限り、 $V_{DD} = 5V \pm 10\%$ 、 $V_{SS} = 0V$ 、 $GND = 0V$ 、 $V_L = 1.1V \sim 1.95V$ 。

表 4.

| パラメータ                                                       | +25°C      | -40°C~+85°C       | -40°C~+125°C | 単位           | テスト条件／コメント                                   |

|-------------------------------------------------------------|------------|-------------------|--------------|--------------|----------------------------------------------|

| ANALOG SWITCH                                               |            |                   |              |              |                                              |

| Analog Signal Range                                         |            | 0 to $V_{DD}$     |              | V            |                                              |

| On Resistance, $R_{ON}$                                     | 8.5        |                   |              | $\Omega$ typ | $V_S = 0V \sim 4.5V$ 、 $I_S = -10mA$ 、図22を参照 |

|                                                             | 10         | 12.5              | 14           | $\Omega$ max | $V_{DD} = 4.5V$ 、 $V_{SS} = 0V$              |

| On-Resistance Match Between Channels, $\Delta R_{ON}$       | 0.15       |                   |              | $\Omega$ typ | $V_S = 0V \sim 4.5V$ 、 $I_S = -10mA$         |

|                                                             | 0.3        | 0.35              | 0.4          | $\Omega$ max |                                              |

| On-Resistance Flatness, $R_{FLAT(ON)}$                      | 2          |                   |              | $\Omega$ typ | $V_S = 0V \sim 4.5V$ 、 $I_S = -10mA$         |

|                                                             | 2.6        | 3                 | 3.3          | $\Omega$ max |                                              |

| LEAKAGE CURRENTS                                            |            |                   |              |              |                                              |

| Source Off, $I_S$ (Off)                                     | $\pm 0.01$ |                   |              | $nA$ typ     | $V_{DD} = 5.5V$ 、 $V_{SS} = 0V$              |

|                                                             | $\pm 0.15$ | $\pm 1.5$         | $\pm 12$     | $nA$ max     | $V_S = 1V/4.5V$ 、 $V_D = 4.5V/1V$ 、図23を参照    |

| Drain Off, $I_D$ (Off)                                      | $\pm 0.02$ |                   |              | $nA$ typ     | $V_S = 1V/4.5V$ 、 $V_D = 4.5V/1V$ 、図23を参照    |

|                                                             | $\pm 0.15$ | $\pm 2$           | $\pm 20$     | $nA$ max     |                                              |

| Drain Channel On, $I_D$ (On), Source Channel On, $I_S$ (On) | $\pm 0.02$ |                   |              | $nA$ typ     | $V_S = V_D = 1V$ または $4.5V$ 、図24を参照          |

|                                                             | $\pm 0.15$ | $\pm 2$           | $\pm 20$     | $nA$ max     |                                              |

| DIGITAL INPUTS                                              |            |                   |              |              |                                              |

| Input High Voltage, $V_{INH}$                               |            | 0.65 $\times V_L$ |              | V min        |                                              |

| Input Low Voltage, $V_{INL}$                                |            | 0.35 $\times V_L$ |              | V max        |                                              |

| Input High Current, $I_{INH}$                               | 55         |                   |              | $\mu A$ typ  | $V_{INx} = V_L = 1.8V$ 、動作原理のセクションを参照        |

|                                                             | 40         | 90                |              | $\mu A$ max  |                                              |

|                                                             |            | 65                |              | $\mu A$ typ  | $V_{INx} = V_L = 1.2V$ 、動作原理のセクションを参照        |

| Input Low Current, $I_{INL}$                                | 0.2        |                   |              | $\mu A$ typ  | $V_{INx} = 0V$                               |

|                                                             |            | 0.8               |              | $\mu A$ max  |                                              |

| Digital Input Capacitance, $C_{IN}$                         | 5          |                   |              | pF typ       |                                              |

| DYNAMIC CHARACTERISTICS                                     |            |                   |              |              |                                              |

| Transition Time, $t_{TRANSITION}$                           | 218        |                   |              | ns typ       | $R_L = 300\Omega$ 、 $C_L = 35pF$             |

|                                                             | 274        | 314               | 342          | ns max       | $V_S = 2.5V$ 、図25を参照                         |

| Enable Delay On Time, $t_{ON}$ (EN)                         | 190        |                   |              | ns typ       | $R_L = 300\Omega$ 、 $C_L = 35pF$             |

|                                                             | 247        | 273               | 294          | ns max       | $V_S = 2.5V$ 、図27を参照                         |

| Enable Delay Off Time, $t_{OFF}$ (EN)                       | 220        |                   |              | ns typ       | $R_L = 300\Omega$ 、 $C_L = 35pF$             |

|                                                             | 271        | 308               | 336          | ns max       | $V_S = 2.5V$ 、図27を参照                         |

## 仕様

表 4.

| パラメータ                                                               | +25°C | -40°C~+85°C | -40°C~+125°C | 単位      | テスト条件／コメント                                                               |

|---------------------------------------------------------------------|-------|-------------|--------------|---------|--------------------------------------------------------------------------|

| Break-Before-Make Time Delay, $t_{BBM}$                             | 55    |             | 36           | ns typ  | $R_L = 300 \Omega$ 、 $C_L = 35\text{pF}$                                 |

|                                                                     |       |             |              | ns min  | $V_{S1} = V_{S2} = 2.5\text{V}$ 、図26を参照                                  |

| Charge Injection, $Q_{INJ}$                                         | -5    |             |              | pC typ  | $V_S = 2.5\text{V}$ 、 $R_S = 0\Omega$ 、 $C_L = 1\text{nF}$ 、図28を参照       |

| Off Isolation                                                       | -58   |             |              | dB typ  | $R_L = 50\Omega$ 、 $C_L = 5\text{pF}$ 、周波数=1MHz、図29を参照                   |

| Channel-to-Channel Crosstalk                                        | -64   |             |              | dB typ  | $R_L = 50\Omega$ 、 $C_L = 5\text{pF}$ 、周波数=1MHz、図31を参照                   |

| Total Harmonic Distortion (THD)                                     | -83   |             |              | dB typ  | $R_L = 10\text{k}\Omega$ 、周波数=1kHz~20kHz、 $V_S = 3.5\text{V}$ p-p、図20を参照 |

|                                                                     | -80   |             |              | dB typ  | $R_L = 10\text{k}\Omega$ 、周波数=100kHz、 $V_S = 3.5\text{V}$ p-p、図20を参照     |

| Total Harmonic Distortion Plus Noise (THD + N)                      | 0.011 |             |              | % typ   | $R_L = 10\text{k}\Omega$ 、周波数=100kHz、 $V_S = 3.5\text{V}$ p-p、図32を参照     |

| -3 dB Bandwidth                                                     | 77    |             |              | MHz typ | $R_L = 50\Omega$ 、 $C_L = 5\text{pF}$ 、図30を参照                            |

| Insertion Loss                                                      | -0.44 |             |              | dB typ  | $R_L = 50\Omega$ 、 $C_L = 5\text{pF}$ 、図30を参照                            |

| Source Off Capacitance, $C_S$ (Off)                                 | 21    |             |              | pF typ  | $V_S = 2.5\text{V}$ 、周波数=1MHz                                            |

| Drain Off Capacitance, $C_D$ (Off)                                  | 37    |             |              | pF typ  | $V_S = 2.5\text{V}$ 、周波数=1MHz                                            |

| Drain On Capacitance, $C_D$ (On), Source On Capacitance, $C_S$ (On) | 62    |             |              | pF typ  | $V_S = 2.5\text{V}$ 、周波数=1MHz                                            |

| POWER REQUIREMENTS                                                  |       |             |              |         | $V_{DD} = 5.5\text{V}$ 、 $V_{SS} = 0\text{V}$                            |

| Positive Current, $I_{DD}$                                          | 50    |             |              | μA typ  | $V_{INx} = V_L = 0\text{V}$                                              |

|                                                                     |       | 90          |              | μA max  |                                                                          |

| Digital Supply Current, $I_{VL}$                                    | 45    |             |              | μA typ  | $V_{INx} = V_L = 1.8\text{V}$                                            |

|                                                                     |       | 70          |              | μA max  |                                                                          |

|                                                                     | 30    |             |              | μA typ  | $V_{INx} = V_L = 1.2\text{V}$                                            |

|                                                                     |       | 55          |              | μA max  |                                                                          |

## 3.3V单電源

特に指定のない限り、 $V_{DD} = 3.3\text{V}$ 、 $V_{SS} = 0\text{V}$ 、 $GND = 0\text{V}$ 、 $V_L = 1.1\text{V} \sim 1.95\text{V}$ 。

表 5.

| パラメータ                                                       | +25°C      | -40°C~+85°C   | -40°C~+125°C | 単位     | テスト条件／コメント                                                                                                  |

|-------------------------------------------------------------|------------|---------------|--------------|--------|-------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                               |            |               |              |        |                                                                                                             |

| Analog Signal Range                                         |            | 0 to $V_{DD}$ |              | V      |                                                                                                             |

| On Resistance, $R_{ON}$                                     | 13.5       | 15            | 16.5         | Ω typ  | $V_S = 0\text{V} \sim V_{DD}$ 、 $I_S = -10\text{mA}$ 、図22を参照、 $V_{DD} = 3.3\text{V}$ 、 $V_{SS} = 0\text{V}$ |

| On-Resistance Match Between Channels, $\Delta R_{ON}$       | 0.25       | 0.28          | 0.3          | Ω typ  | $V_S = 0\text{V} \sim V_{DD}$ 、 $I_S = -10\text{mA}$                                                        |

| On-Resistance Flatness, $R_{FLAT(ON)}$                      | 5          | 5.5           | 6.5          | Ω typ  | $V_S = 0\text{V} \sim V_{DD}$ 、 $I_S = -10\text{mA}$                                                        |

| LEAKAGE CURRENTS                                            |            |               |              |        | $V_{DD} = 3.6\text{V}$ 、 $V_{SS} = 0\text{V}$                                                               |

| Source Off, $I_S$ (Off)                                     | $\pm 0.01$ |               |              | nA typ | $V_S = 0.6\text{V}/3\text{V}$ 、 $V_D = 3\text{V}/0.6\text{V}$ 、図23を参照                                       |

|                                                             | $\pm 0.15$ | $\pm 1.5$     | $\pm 12$     | nA max |                                                                                                             |

| Drain Off, $I_D$ (Off)                                      | $\pm 0.02$ |               |              | nA typ | $V_S = 0.6\text{V}/3\text{V}$ 、 $V_D = 3\text{V}/0.6\text{V}$ 、図23を参照                                       |

|                                                             | $\pm 0.15$ | $\pm 2$       | $\pm 20$     | nA max |                                                                                                             |

| Drain Channel On, $I_D$ (On), Source Channel On, $I_S$ (On) | $\pm 0.02$ |               |              | nA typ | $V_S = V_D = 0.6\text{V}$ または $3\text{V}$ 、図24を参照                                                           |

|                                                             | $\pm 0.15$ | $\pm 2$       | $\pm 20$     | nA max |                                                                                                             |

## 仕様

表 5.

| パラメータ                                                               | +25°C | -40°C ~ +85°C | -40°C ~ +125°C | 単位      | テスト条件／コメント                                                                 |

|---------------------------------------------------------------------|-------|---------------|----------------|---------|----------------------------------------------------------------------------|

| <b>DIGITAL INPUTS</b>                                               |       |               |                |         |                                                                            |

| Input High Voltage, $V_{INH}$                                       |       |               | 0.65 × $V_L$   | V min   |                                                                            |

| Input Low Voltage, $V_{INL}$                                        |       |               | 0.35 × $V_L$   | V max   |                                                                            |

| Input High Current, $I_{INH}$                                       | 55    |               |                | μA typ  | $V_{INx} = V_L = 1.8V$ 、 <a href="#">動作原理のセクション</a> を参照                    |

|                                                                     |       | 40            | 90             | μA max  |                                                                            |

|                                                                     |       |               |                | nA typ  | $V_{INx} = V_L = 1.2V$ 、 <a href="#">動作原理のセクション</a> を参照                    |

|                                                                     |       |               | 65             | μA max  |                                                                            |

| Input Low Current, $I_{INL}$                                        | 0.2   |               |                | μA typ  | $V_{INx} = 0V$                                                             |

|                                                                     |       |               | 0.8            | μA max  |                                                                            |

| Digital Capacitance, $C_{IN}$                                       | 5     |               |                | pF typ  |                                                                            |

| <b>DYNAMIC CHARACTERISTICS</b>                                      |       |               |                |         |                                                                            |

| Transition Time, $t_{TRANSITION}$                                   | 300   |               |                | ns typ  | $R_L = 300\Omega$ 、 $C_L = 35pF$                                           |

|                                                                     | 397   | 449           | 477            | ns max  | $V_S = 1.5V$ 、 <a href="#">図25</a> を参照                                     |

| Enable Delay On Time, $t_{ON}$ (EN)                                 | 307   |               |                | ns typ  | $R_L = 300\Omega$ 、 $C_L = 35pF$                                           |

|                                                                     | 420   | 437           | 495            | ns max  | $V_S = 1.5V$ 、 <a href="#">図27</a> を参照                                     |

| Enable Delay Off Time, $t_{OFF}$ (EN)                               | 293   |               |                | ns typ  | $R_L = 300\Omega$ 、 $C_L = 35pF$                                           |

|                                                                     | 337   | 414           | 443            | ns max  | $V_S = 1.5V$ 、 <a href="#">図27</a> を参照                                     |

| Break-Before-Make Time Delay, $t_{BBM}$                             | 78    |               | 51             | ns typ  | $R_L = 300\Omega$ 、 $C_L = 35pF$                                           |

|                                                                     |       |               |                | ns min  | $V_{S1} = V_{S2} = 1.5V$ 、 <a href="#">図26</a> を参照                         |

| Charge Injection, $Q_{INJ}$                                         | -10   |               |                | pC typ  | $V_S = 1.5V$ 、 $R_S = 0\Omega$ 、 $C_L = 1nF$ 、 <a href="#">図28</a> を参照     |

| Off Isolation                                                       | -58   |               |                | dB typ  | $R_L = 50\Omega$ 、 $C_L = 5pF$ 、周波数=1MHz、 <a href="#">図29</a> を参照          |

| Channel-to-Channel Crosstalk                                        | -64   |               |                | dB typ  | $R_L = 50\Omega$ 、 $C_L = 5pF$ 、周波数=1MHz、 <a href="#">図31</a> を参照          |

| Total Harmonic Distortion, THD                                      | -77   |               |                | % typ   | $R_L = 10k\Omega$ 、周波数=1kHz~20kHz、 $V_S = 2V$ p-p、 <a href="#">図20</a> を参照 |

|                                                                     | -76   |               |                | % typ   | $R_L = 10k\Omega$ 、周波数=100kHz、 $V_S = 2V$ p-p、 <a href="#">図20</a> を参照     |

| Total Harmonic Distortion Plus Noise, THD + N                       | 0.016 |               |                | % typ   | $R_L = 10k\Omega$ 、周波数=100kHz、 $V_S = 2V$ p-p、 <a href="#">図32</a> を参照     |

| -3 dB Bandwidth                                                     | 83    |               |                | MHz typ | $R_L = 50\Omega$ 、 $C_L = 5pF$ 、 <a href="#">図30</a> を参照                   |

| Insertion Loss                                                      | -1.15 |               |                | dB typ  | $R_L = 50\Omega$ 、 $C_L = 5pF$ 、 <a href="#">図30</a> を参照                   |

| Source Off Capacitance, $C_S$ (Off)                                 | 22    |               |                | pF typ  | $V_S = 1.5V$ 、周波数=1MHz                                                     |

| Drain Off Capacitance, $C_D$ (Off)                                  | 39    |               |                | pF typ  | $V_S = 1.5V$ 、周波数=1MHz                                                     |

| Drain On Capacitance, $C_D$ (On), Source On Capacitance, $C_S$ (On) | 64    |               |                | pF typ  | $V_S = 1.5V$ 、周波数=1MHz                                                     |

| <b>POWER REQUIREMENTS</b>                                           |       |               |                |         |                                                                            |

| Positive Current, $I_{DD}$                                          | 45    |               |                | μA typ  | $V_{DD} = 3.6V$                                                            |

|                                                                     |       | 90            |                | μA max  | $V_{INx} = V_L = 0V$                                                       |

| Digital Supply Current, $I_{VL}$                                    | 45    |               |                | μA typ  | $V_{INx} = V_L = 1.8V$                                                     |

|                                                                     |       | 75            |                | μA max  |                                                                            |

|                                                                     | 30    |               | 55             | μA typ  | $V_{INx} = V_L = 1.2V$                                                     |

|                                                                     |       |               |                | μA max  |                                                                            |

## 仕様

### チャンネルごとの連続電流 (SxA、SxB、またはDx)

表 6. 4つのチャンネルがオン

| パラメータ                                                                                       | 25°C | 85°C | 125°C | 単位         |

|---------------------------------------------------------------------------------------------|------|------|-------|------------|

| CONTINUOUS CURRENT, SxA, SxB, OR Dx <sup>1</sup> ( $\theta_{JA} = 49.181^\circ\text{C/W}$ ) |      |      |       |            |

| $V_{DD} = +5 \text{ V}, V_{SS} = -5 \text{ V}$                                              | 186  | 118  | 69    | mA maximum |

| $V_{DD} = 12 \text{ V}, V_{SS} = 0 \text{ V}$                                               | 197  | 123  | 70    | mA maximum |

| $V_{DD} = 5 \text{ V}, V_{SS} = 0 \text{ V}$                                                | 143  | 96   | 60    | mA maximum |

| $V_{DD} = 3.3 \text{ V}, V_{SS} = 0 \text{ V}$                                              | 118  | 82   | 54    | mA maximum |

1 SxAはS1A～S4Aピン、SxBはS1B～S4Bピン、DxはD1～D4ピンを表します。

表 7. 1つのチャンネルがオン

| パラメータ                                                                                      | 25°C | 85°C | 125°C | 単位         |

|--------------------------------------------------------------------------------------------|------|------|-------|------------|

| CONTINUOUS CURRENT, SxA, SxB, OR Dx <sup>1</sup> ( $\theta_{JA} = 49.18^\circ\text{C/W}$ ) |      |      |       |            |

| $V_{DD} = +5 \text{ V}, V_{SS} = -5 \text{ V}$                                             | 340  | 184  | 85    | mA maximum |

| $V_{DD} = 12 \text{ V}, V_{SS} = 0 \text{ V}$                                              | 359  | 191  | 86    | mA maximum |

| $V_{DD} = 5 \text{ V}, V_{SS} = 0 \text{ V}$                                               | 262  | 154  | 79    | mA maximum |

| $V_{DD} = 3.3 \text{ V}, V_{SS} = 0 \text{ V}$                                             | 215  | 133  | 74    | mA maximum |

1 SxAはS1A～S4Aピン、SxBはS1B～S4Bピン、DxはD1～D4ピンを表します。

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 8. 絶対最大定格

| Parameter                                             | Rating                                                                                |

|-------------------------------------------------------|---------------------------------------------------------------------------------------|

| $V_{DD}$ to $V_{SS}$                                  | 18 V                                                                                  |

| $V_{DD}$ to GND                                       | -0.3 V to +18 V                                                                       |

| $V_{SS}$ to GND                                       | +0.3 V to -18 V                                                                       |

| $V_L$ to GND                                          | -0.3 V to +2.25 V                                                                     |

| Analog Inputs <sup>1</sup>                            | $V_{SS} - 0.3 \text{ V}$ to $V_{DD} + 0.3 \text{ V}$ or 30 mA, whichever occurs first |

| Digital Inputs <sup>2</sup>                           | GND - 0.3 V to 2.25 V or 30 mA, whichever occurs first                                |

| Peak Current, SxA, SxB or Dx <sup>3</sup>             | 317 mA (pulsed at 1 ms, 10% duty-cycle maximum)                                       |

| Continuous Current, SxA, SxB, or Dx Pins <sup>4</sup> | Data + 15%                                                                            |

| Temperature                                           |                                                                                       |

| Operating Range                                       | -40°C to +125°C                                                                       |

| Storage Range                                         | -65°C to +150°C                                                                       |

| Junction                                              | 150°C                                                                                 |

| Reflow Soldering Peak, Pb free                        | 260°C                                                                                 |

1 アナログ入力ピンSxA、SxBおよびDxでの過電圧は、内部ダイオードによりクランプされます。電流は、仕様規定された最大定格に制限してください。

2 デジタル入力ピンINxでの過電圧は、内部ダイオードによりクランプされます。

3 SxAはS1A～S4Aピン、SxBはS1B～S4Bピン、DxはD1～D4ピンを表します。

4 表6および表7を参照してください。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。これはストレス定格のみを定めたものであり、本規格の動作セクションに記載する規定値以上でデバイスが正常に動作することを示唆するものではありません。長時間にわたり最大動作条件を超えて動作させると、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCBの熱設計には、細心の注意を払う必要があります。

$\theta_{JA}$ は、1立方フィートの密閉容器内で測定された、自然体流での周囲とジャンクションの間の熱抵抗です。 $\theta_{JC}$ は、ジャンクションとケースの間の熱抵抗です。

表 9. 热抵抗

| Package Type          | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|-----------------------|---------------|---------------|------|

| CP-24-17 <sup>1</sup> | 49.18         | 9.35          | °C/W |

1 热抵抗のシミュレーション値は、サーマル・ピアのないJEDEC 2S2Pサーマル・テスト・ボードに基づいています。

## 静電放電（ESD）定格

以下のESD情報は、ESDに敏感なデバイスを取り扱うために示したものですが、対象はESD保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001準拠の人体モデル（HBM）。

ANSI/ESDA/JEDEC JS-002準拠の電界誘起帯電デバイス・モデル（FICDM）。

## ADG1634LのESD定格

表 10. ADG1634L、24ピンLFCSP

| ESD Model        | Withstand Threshold (V) | Class |

|------------------|-------------------------|-------|

| HBM <sup>1</sup> | ±3000                   | 2     |

| FICDM            | ±1250                   | C3    |

1 入出力ポートから電源、入出力ポートから入出力ポート、およびその他すべての入力における値です。

## ESDに関する注意

### ESD（静電放電）の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

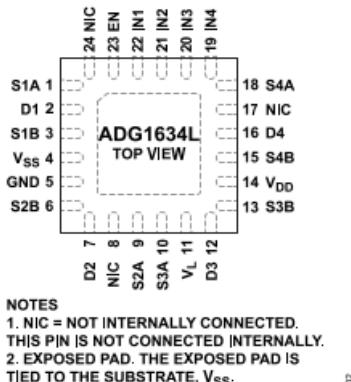

## ピン配置とピン機能の説明

図 2. ピン配置

表 11. ピン機能の説明

| ピン番号           | 記号              | 説明                                                                                                            |

|----------------|-----------------|---------------------------------------------------------------------------------------------------------------|

| 1              | S1A             | ソース端子1A。S1Aは、入力または出力に設定できます。                                                                                  |

| 2              | D1              | ドレイン端子1。D1は、入力または出力に設定できます。                                                                                   |

| 3              | S1B             | ソース端子1B。S1Bは、入力または出力に設定できます。                                                                                  |

| 4              | V <sub>ss</sub> | 負電源の電位。単電源アプリケーションでは、V <sub>ss</sub> ピンはグラウンドに接続できます。                                                         |

| 5              | GND             | グラウンド (0V) 基準電位。                                                                                              |

| 6              | S2B             | ソース端子2B。S2Bは、入力または出力に設定できます。                                                                                  |

| 7              | D2              | ドレイン端子2。D2は、入力または出力に設定できます。                                                                                   |

| 8、17、24        | NIC             | 内部では未接続。このピンは内部接続されていません。                                                                                     |

| 9              | S2A             | ソース端子2A。S2Aは、入力または出力に設定できます。                                                                                  |

| 10             | S3A             | ソース端子3A。S3Aは、入力または出力に設定できます。                                                                                  |

| 11             | V <sub>L</sub>  | ロジック制御電源電位。                                                                                                   |

| 12             | D3              | ドレイン端子3。D3は、入力または出力に設定できます。                                                                                   |

| 13             | S3B             | ソース端子3B。S3Bは、入力または出力に設定できます。                                                                                  |

| 14             | V <sub>dd</sub> | 正電源の電位。                                                                                                       |

| 15             | S4B             | ソース端子4B。S4Bは、入力または出力に設定できます。                                                                                  |

| 16             | D4              | ドレイン端子4。D4は、入力または出力に設定できます。                                                                                   |

| 18             | S4A             | ソース端子4A。S4Aは、入力または出力に設定できます。                                                                                  |

| 19             | IN4             | ロジック制御入力4。                                                                                                    |

| 20             | IN3             | ロジック制御入力3。                                                                                                    |

| 21             | IN2             | ロジック制御入力2。                                                                                                    |

| 22             | IN1             | ロジック制御入力1。                                                                                                    |

| 23             | EN              | アクティブ・ハイのデジタル入力。ENピンがロー・レベルになると、デバイスはディスエーブルされ、すべてのスイッチがオフになります。ENピンがハイ・レベルになると、INxロジック入力によってオンになるスイッチが決まります。 |

| Not applicable | EPAD            | 露出パッド。露出パッドはサブストレート (V <sub>ss</sub> ) に接続してください。                                                             |

表 12. 真理値表

| EN | INx        | SxA | SxB |

|----|------------|-----|-----|

| 0  | Don't care | Off | Off |

| 1  | 0          | Off | On  |

| 1  | 1          | On  | Off |

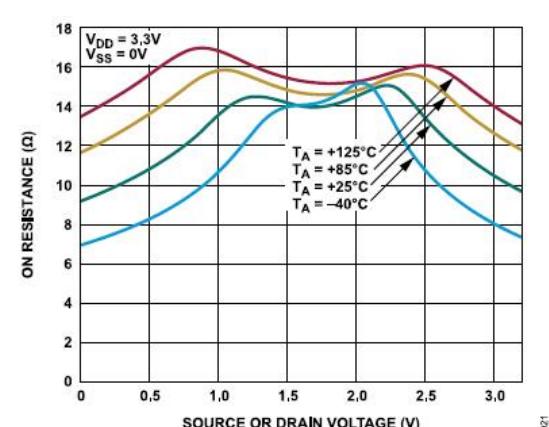

## 代表的な性能特性

## 代表的な性能特性

## 代表的な性能特性

図 15.  $T_{TRANSITION}$  の温度特性

図 18. 揿入損失の周波数特性

図 16. オフ・アイソレーションの周波数特性

図 19. THD+N の周波数特性

図 17. クロストークの周波数特性

図 20. THD の周波数特性

## 代表的な性能特性

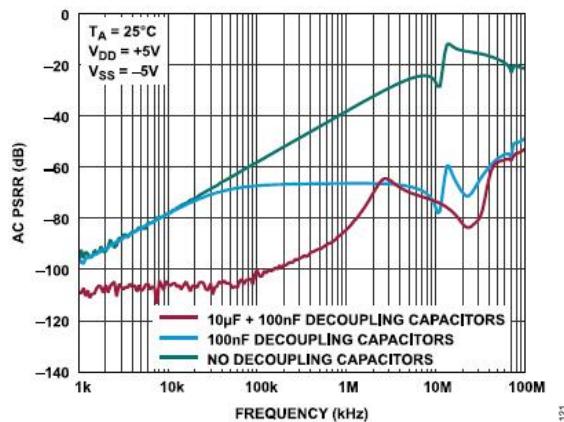

図 21. AC PSRR の周波数特性

## テスト回路

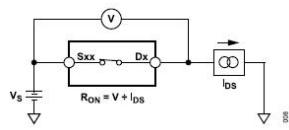

図 22. オン抵抗

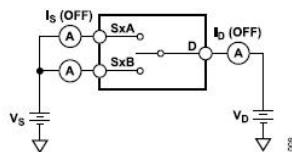

図 23. オフ・リーク

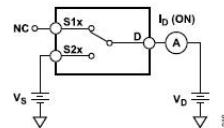

図 24. オン・リーク

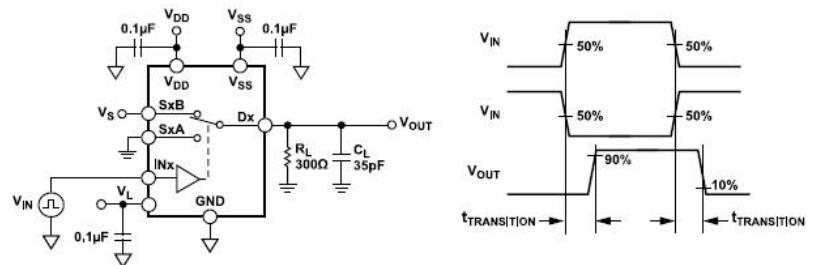

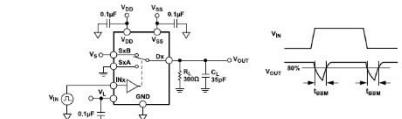

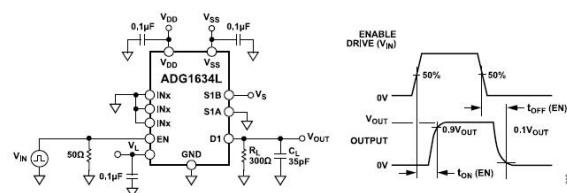

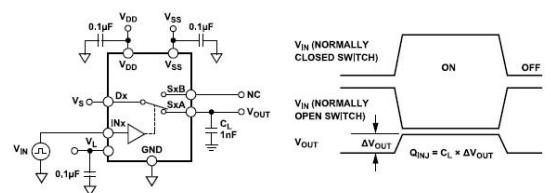

図 25. 遷移時間  $t_{TRANSITION}$  ( $V_{IN}$ は入力電圧、 $V_{OUT}$ は出力電圧)図 26. ブレークビフォアメークの遅延、 $t_{BBM}$ 図 27. イネーブル遅延時間（オンの場合） $t_{ON}$  (EN) およびイネーブル遅延時間（オフの場合） $t_{OFF}$  (EN)

図 28. チャージ・インジェクション

## テスト回路

図 29. オフ・アイソレーション

図 30. 帯域幅

図 31. チャンネル間クロストーク

図 32. THD +ノイズ

## 用語の定義

### **R<sub>ON</sub>**

端子Dと端子Sの間の抵抗。

### **ΔR<sub>ON</sub>**

任意の2チャンネル間のR<sub>ON</sub>の差。

### **R<sub>FLAT (ON)</sub>**

測定されたオン抵抗の最大値と最小値の差として表現される抵抗値の平坦性。

### **I<sub>s Off</sub>**

スイッチがオフの時のソース・リーク電流。

### **I<sub>b Off</sub>**

スイッチがオフの時のドレイン・リーク電流。

### **I<sub>b (On)</sub> および I<sub>s (On)</sub>**

スイッチがオンの時のチャンネルのドレイン・リーク電流とソース・リーク電流。

### **V<sub>D</sub> および V<sub>S</sub>**

端子Dと端子Sのアナログ電圧。

### **C<sub>s (Off)</sub> および C<sub>D (Off)</sub>**

オフ状態でのチャンネルのソース容量とドレイン容量。

### **C<sub>D (On)</sub> および C<sub>s (On)</sub>**

スイッチ・オン状態でのドレイン容量とソース容量。

### **C<sub>IN</sub>**

デジタル入力容量。

### **t<sub>ON (EN)</sub>**

ENデジタル入力立ち上がりの50%のポイントからスイッチ・オン状態の90%に達するポイント間の遅延時間。

### **t<sub>OFF (EN)</sub>**

ENデジタル入力立下りの50%のポイントからスイッチ・オフ状態の10%に達するポイント間の遅延時間。

### **t<sub>TRANSITION</sub>**

あるアドレス状態から別のアドレス状態へ切り替わるときの、デジタル入力の50%のポイントから出力がスイッチ・オン条件(90%)またはスイッチ・オフ条件(10%)に達するまでの遅延時間。

### **t<sub>BBM</sub>**

あるアドレス状態から別のアドレス状態へ切り替わるときの、両方のスイッチングの80%ポイント間で測定されるオフ時間。

### **V<sub>INL</sub>**

ロジック0の最大入力電圧。

### **V<sub>INH</sub>**

ロジック1の最小入力電圧。

### **I<sub>INH</sub>**

デジタル入力がハイの時の入力電流。

### **I<sub>INL</sub>**

デジタル入力がローの時の入力電流。

### **I<sub>DD</sub>**

正側電源電流。

### **I<sub>SS</sub>**

負側電源電流。

### **I<sub>VL</sub>**

デジタル電源電流。

### **オフ・アイソレーション**

オフ・チャンネルから混入する不要な信号の大きさ。

### **チャンネル間クロストーク**

オフ・スイッチから混入する不要な信号の大きさ。

### **チャージ・インジェクション**

スイッチング中にデジタル入力からアナログ出力に転送されるグリッチ・インパルスの大きさ。

### **帯域幅**

出力が3dB減衰する周波数。

### **挿入損失**

スイッチのオン抵抗に起因する損失。

### **全高調波歪み (THD)**

THDは、基本周波数の電力に対する、すべての高調波成分における電力の総和の比率です。

### **全高調波歪み+ノイズ (THD + N)**

基本波成分に対する全高調波成分+信号ノイズの比。

### **AC電源電圧変動除去比 (AC PSRR)**

電源電圧ピンに現れるカップリング・ノイズとスプリアス信号がスイッチ出力へ混入するのを防止するデバイスの能力を表します。デバイスのDC電圧は、0.115V p-pのサイン波で変調されます。変調振幅に対する出力信号振幅の比がAC PSRRです。

## 動作原理

### スイッチ・アーキテクチャ

ADG1634Lは、低ロジック制御可能な4個のSPDTスイッチで構成されています。これらのスイッチは、 $V_L$ 入力に応じて1.2Vまたは1.8Vロジックに対応します。

### $V_L$ による柔軟性

外部 $V_L$ 電源を使用することで、低ロジック・レベルにも柔軟に対応できます。スイッチを動作させるには、1.2Vと1.8Vのロジック動作のそれぞれにおいて以下の $V_L$ 条件を満足しなければなりません。

- ▶ 1.2Vロジック :  $V_L = 1.1V \sim 1.3V$

- ▶ 1.8Vロジック :  $V_L = 1.65V \sim 1.95V$

### 1.2Vおよび1.8V JEDEC準拠

ADG1634Lのデジタル入力閾値は、1.2Vと1.8Vの両方のJEDEC規格（通常範囲）に準拠しています。デジタル入力閾値の規格に準拠しているため、有効なロジック電源範囲で動作している場合、低電圧CMOSロジックとの互換性を確保できます。

1.2Vおよび1.8Vロジック・レベルでのスイッチのデジタル入力条件は、次のとおりです。

- ▶  $V_{INH} = 0.65 \times V_L$

- ▶  $V_{INL} = 0.35 \times V_L$

### 初期化時間

ADG1634Lのデジタル・セクションは、 $V_{DD}$ 、 $V_{SS}$ 、および $V_L$ の電源投入時に初期化フェーズを実行します。 $V_{DD}$ 、 $V_{SS}$ 、および $V_L$ の電源投入後、最低 $50\mu s$ が経過したこと、およびINx入力を印加する前に $V_{DD}$ 、 $V_{SS}$ 、および $V_L$ が低下していないことを確認してください。

### 既知の状態のスイッチ

ADG1634Lのスイッチは、INxピンがフロート状態のときにはオフになります。これにより、不要な信号がスイッチを通過してしまうことを防止します。この機能を備えているため、外付けのプルダウン抵抗は必要ありません。ADG1634Lは、 $I_{INH}$ の半分までのリード電流に対してフロート状態のINx入力をプルダウンすることができます。

## アプリケーション情報

### フィールド・プログラマブル・ゲート・アレイ (FPGA) の低ロジック対応

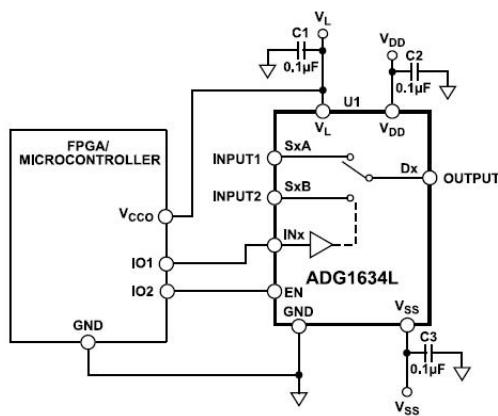

図33に、FPGAまたはマイクロコントローラと一緒にADG1634Lを使用する場合の代表的なアプリケーションを示します。使いやすくなるため、柔軟性に優れたV<sub>L</sub>ピンはデジタル電源電圧（V<sub>CCO</sub>）に、INx入力は直接デジタルIOポートに接続できるようになっています。

図 33. 代表的なアプリケーション

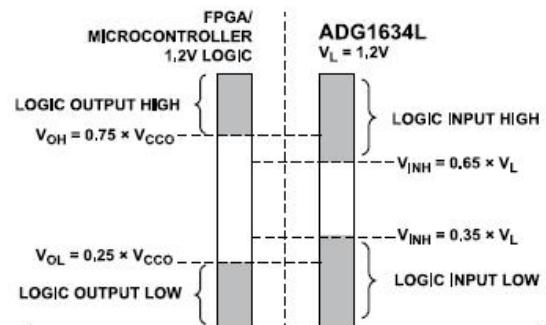

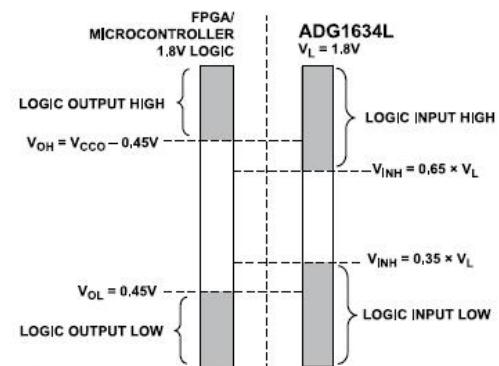

ADG1634Lは1.2Vおよび1.8V JEDEC規格に準拠しているため、ロジック入力の仕様（V<sub>INH</sub>とV<sub>INL</sub>）は、FPGAまたはマイクロコントローラのデジタル出力の仕様（V<sub>OH</sub>の最小値とV<sub>OL</sub>の最大値）を満足しています。一般的な組み合わせではロジック・レベルの互換性は確保されないため、組み合わせによるリスクが発生します。ADG1634Lは、幅広く採用されている1.2Vおよび1.8Vロジック・レベルの両方の規格に準拠しているため、このようなリスクは発生しません。

### V<sub>OH</sub>とV<sub>INH</sub>、およびV<sub>OL</sub>とV<sub>INL</sub>の関係

FPGAまたはマイクロコントローラのロジック出力ハイ（V<sub>OH</sub>）が入力のロジック・ハイ（V<sub>INH</sub>）より高いことを確認してください。また、FPGAまたはマイクロコントローラのロジック出力ロー（V<sub>OL</sub>）が入力のロジック・ロー（V<sub>INL</sub>）より低いことを確認してください。

図34に、FPGAまたはマイクロコントローラのV<sub>OH</sub>およびV<sub>OL</sub>と、ADG1634LのINx入力（V<sub>INH</sub>およびV<sub>INL</sub>）の間における1.2Vロジック準拠の関係を示します。

図 34. V<sub>OH</sub>とV<sub>INH</sub>、およびV<sub>OL</sub>とV<sub>INL</sub>の間の1.2Vロジック互換性

図35に、FPGAまたはマイクロコントローラのV<sub>OH</sub>およびV<sub>OL</sub>と、ADG1634LのINx入力（V<sub>INH</sub>およびV<sub>INL</sub>）の間における1.8Vロジック準拠の関係を示します。

図 35. V<sub>OH</sub>とV<sub>INH</sub>、およびV<sub>OL</sub>とV<sub>INL</sub>の間の1.8Vロジック互換性

### 電源レール

ADG1634Lを正常に動作させるには、V<sub>DD</sub>、V<sub>SS</sub>、およびV<sub>L</sub>電源ピンに少なくとも0.1μFと10μFのデカップリング・コンデンサが必要です。

ADG1634Lは、±3.3V～±8VのV<sub>DD</sub>およびV<sub>SS</sub>両電源で動作します。また、3.3V～16VのV<sub>DD</sub>単電源と1.1V～1.95VのV<sub>L</sub>で動作させることもできます。ただし、絶対最大定格のセクションに示したとおり、V<sub>DD</sub>～V<sub>SS</sub>の範囲は18Vを超えてはなりません。また、V<sub>L</sub>の範囲は2.25Vを超えてはなりません。

## アプリケーション情報

### 電源の推奨事項

アナログ・デバイセズでは、ほとんどの高性能シグナル・チェーンの条件を満たす広範なパワー・マネージメント製品を提供しています。

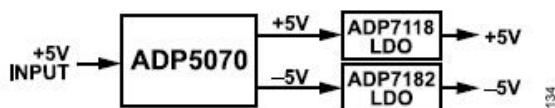

対称バイポーラ電源ソリューションの例を図36に示します。

ADP5070（デュアル・スイッチング・レギュレータ）は、ADG1634L向けに正と負の電源レールを生成します。図36に示すように、正の低ドロップアウト（LDO）レギュレータADP7118と負のLDOレギュレータADP7182の2つのLDOを使用すると、極めて小さなノイズにも敏感なアプリケーションでADP5070の出力リップルを削減できます。

図 36. バイポーラ電源のソリューション

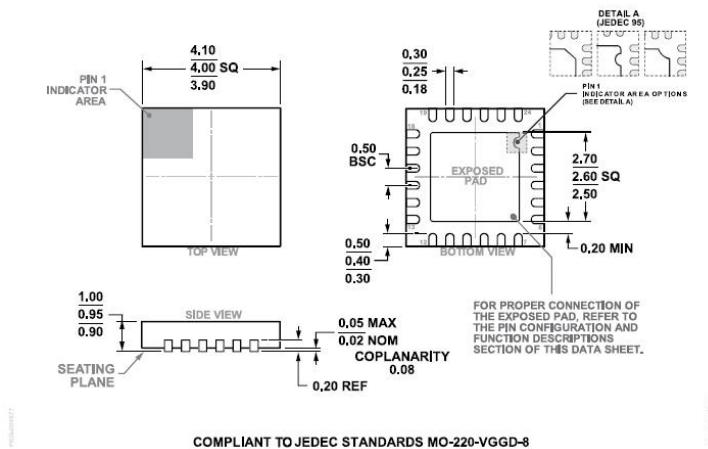

## 外形寸法

図 37. 24ピン・リード・フレーム・チップ・スケール・パッケージ [LFCSP]

4mm × 4mmボディ、0.95mmパッケージ高

(CP-24-17)

寸法 : mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description | Packing Quantity | Package Option |

|--------------------|-------------------|---------------------|------------------|----------------|

| ADG1634LYCPZ-REEL7 | -40°C to +125°C   | 24-Lead LFCSP       | CP-24-17         | Reel, 1500     |

1 Z = RoHS準拠製品。

## 評価用ボード

| Model <sup>1</sup> | Description      |

|--------------------|------------------|

| EVAL-ADG1634LEBZ   | Evaluation Board |

1 Z = RoHS準拠製品。