# データシート ADEMA124/ADEMA127

## SPI を備えた同時サンプリング 4 チャンネル／7 チャンネル ΣΔ ADC

### 特長

- ▶ 4 チャンネルまたは 7 チャンネルの高性能同時サンプリング Σ-Δ ADC

- ▶ SN 比 : 最大 105dB

- ▶ プログラマブルなサンプリング・レート : 最大 64kSPS

- ▶ 広い入力電圧範囲 :  $\pm 1.2V_{PK}$ 、848mVRMS フルスケール

- ▶ 高インピーダンス、差動入力

- ▶ 内部電圧リファレンス温度係数 : 5ppm/ $^{\circ}C$  (代表値)

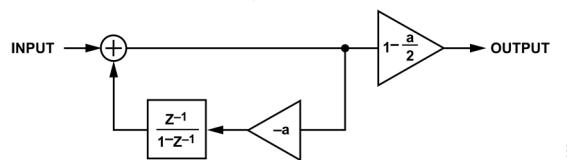

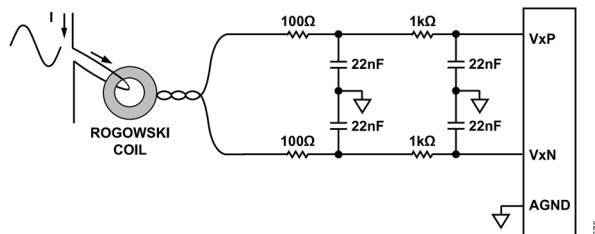

- ▶ ロゴスキー・コイル用のデジタル積分器およびハイパス・フィルタを内蔵

- ▶ 高速スタートアップ : 有効な電源供給後 0.5ms 以内に初回サンプリングを実行

- ▶ 改ざん検知モード、バッテリ・バックアップに適した低消費電力

- ▶ 双方向巡回冗長検査 (CRC) およびデイジーチェーン機能を備えた 4 線式 SPI

- ▶ 複数の ADC デバイスのシンプルな同期

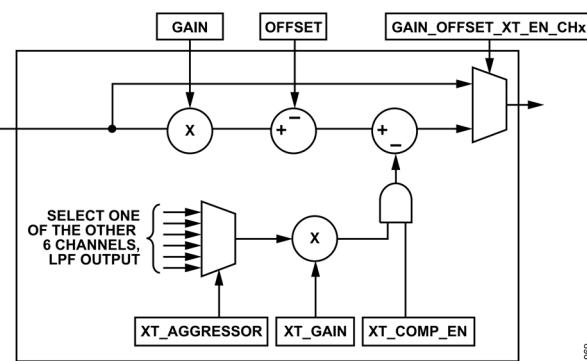

- ▶ チャンネルごとにゲイン、位相、オフセットを補償

- ▶ SPI 読出し可能な一意の部品 ID レジスタ

- ▶ 消費電力 : 7 チャンネル ADC でわずか 18mW

- ▶ 広い動作温度範囲 : -40°C ~ +125°C

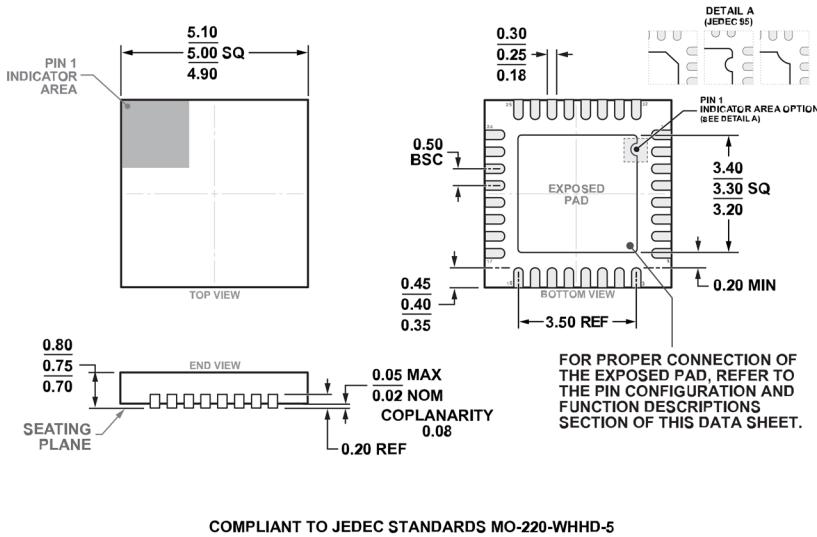

- ▶ 小型の 32 ピン、5mm × 5mm LFCSP

### アプリケーション

- ▶ 多相電力量計

- ▶ 単相 3 線電力量計

- ▶ 分岐回路モニタリング

- ▶ 配電ユニット

- ▶ 電力品質モニタリング

- ▶ サーキット・ブレーカ

- ▶ 保護リレー

- ▶ 電気自動車用電源装置

### 概要

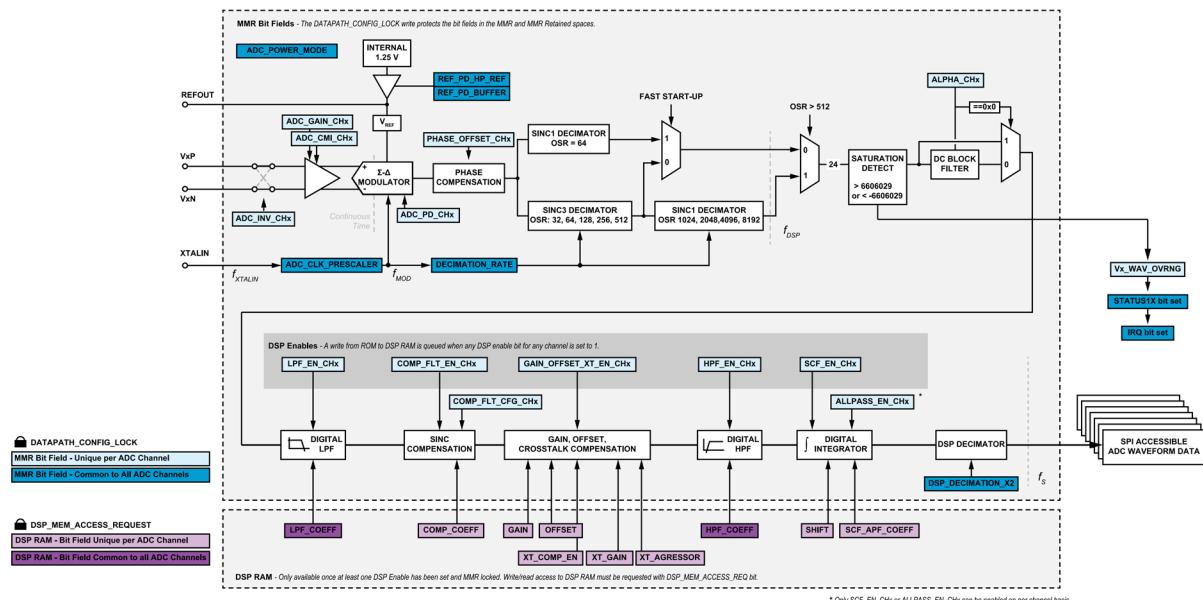

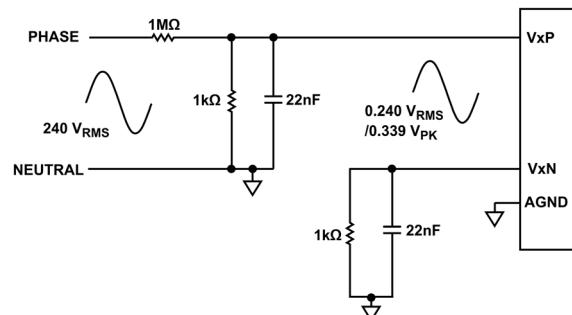

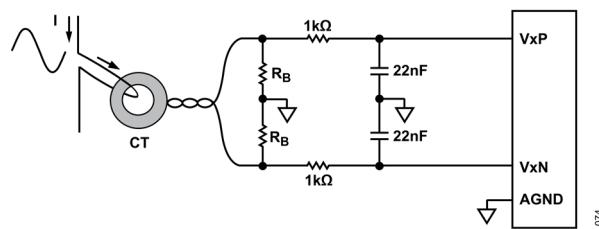

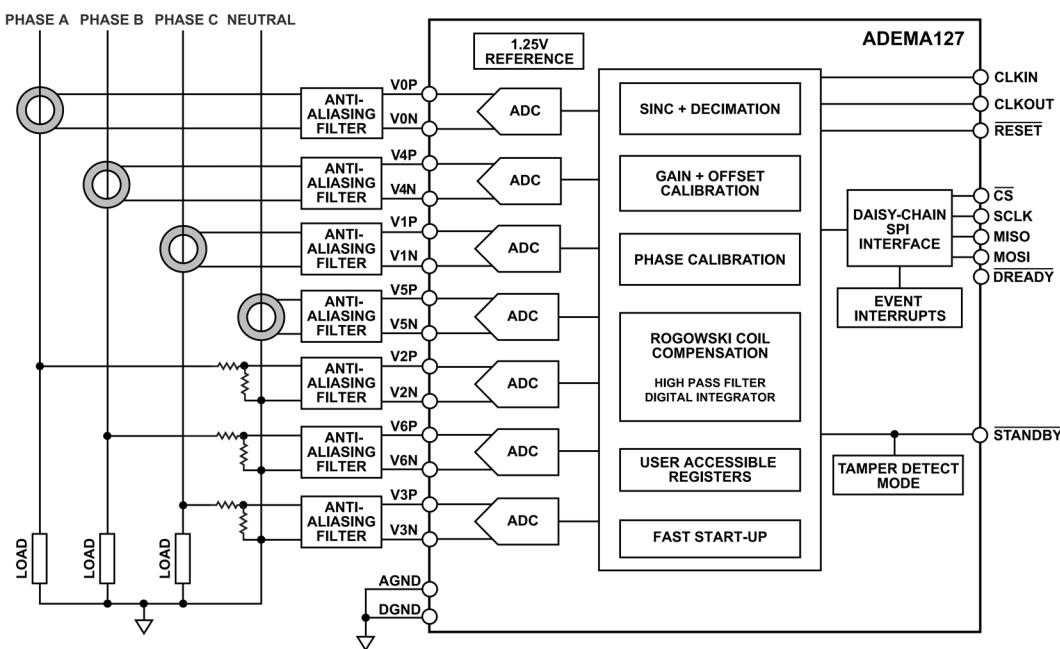

ADEMA124/ADEMA127 は、4 チャンネルおよび 7 チャンネルの同時サンプリング 24 ビット・シグマ・デルタ A/D コンバータ (ADC) であり、多相または単相 3 線式の電力量計アプリケーションに最適です。ADEMA124/ADEMA127 は、分圧器やシャント、およびカレント・トランス (CT) やロゴスキー・コイルなどの絶縁型電流センサーと互換性があります。

ADEMA124/ADEMA127 には、ADC チャンネルごとにゲイン、位相、オフセット補償を可能にする、独立したハードウェア・フィルタおよび DSP (デジタル信号処理) フィルタが内蔵されています。また、ADEMA124/ADEMA127 は、積分器や 2 次ハイパス・フィルタなど、ロゴスキー・センサーの合理的な実装を可能にする専用の補償機能およびデジタル信号処理機能も備えています。一般的な使用事例に対応した DSP フィルタ係数は自動的に読み込まれ、フィルタ特性のカスタマイズに利用可能です。

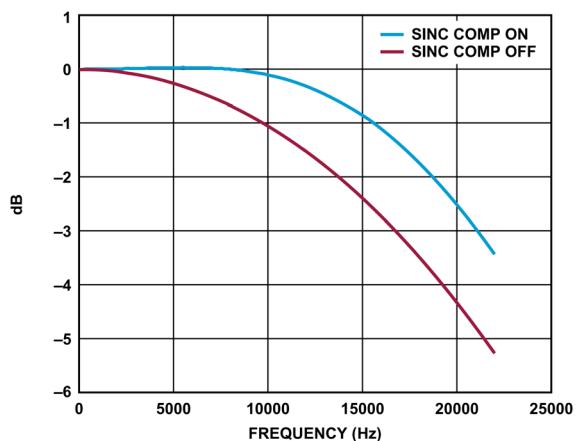

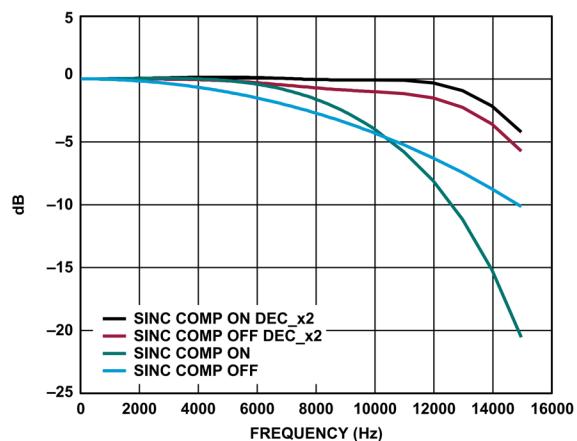

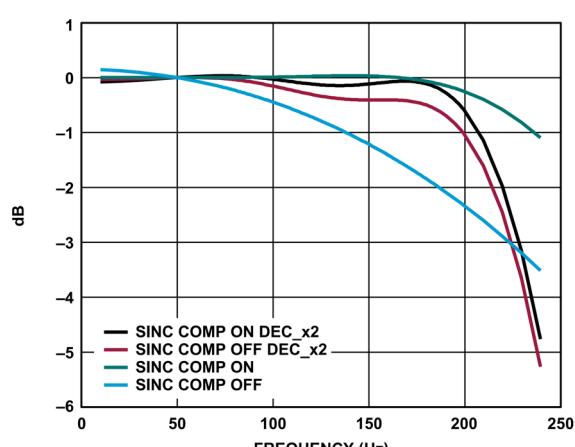

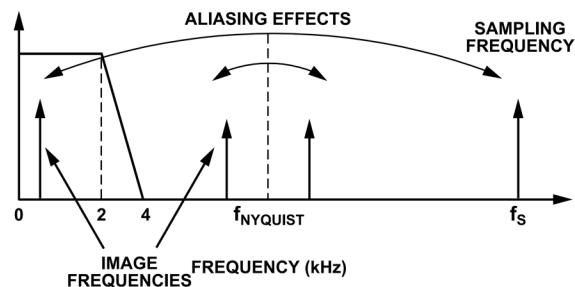

sinc 補償、LPF、および DSP のデシメーション率 2 の機能により、所定の出力サンプル・レートで使用可能なアナログ帯域幅が最大で 70% 拡張されます。帯域幅が広いため、ADEMA124/ADEMA127 は、IEC 61000-4-30 電力品質クラス A およびクラス S のメータに適しています。ADEMA124/ADEMA127 は、IEC 62053-21、IEC 62053-22、OIML R46ANSI、C12.20 の有効電力量規格、および IEC 62053-23、IEC 62053-24、EN 50470-3 の無効電力量規格に適合したシステムで使用できます。0.5ms の高速スタートアップ時間により、特にロゴスキー・センサーと組み合わせて、サーキット・ブレーカや保護リレーにも使用可能です。

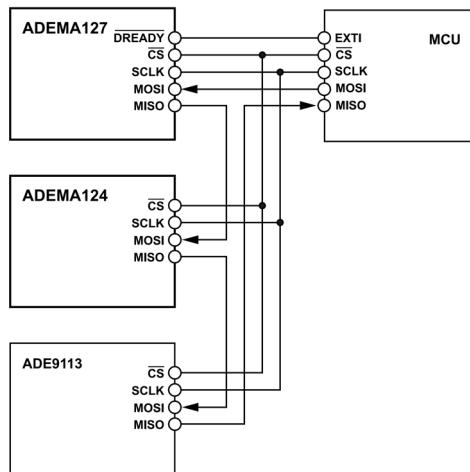

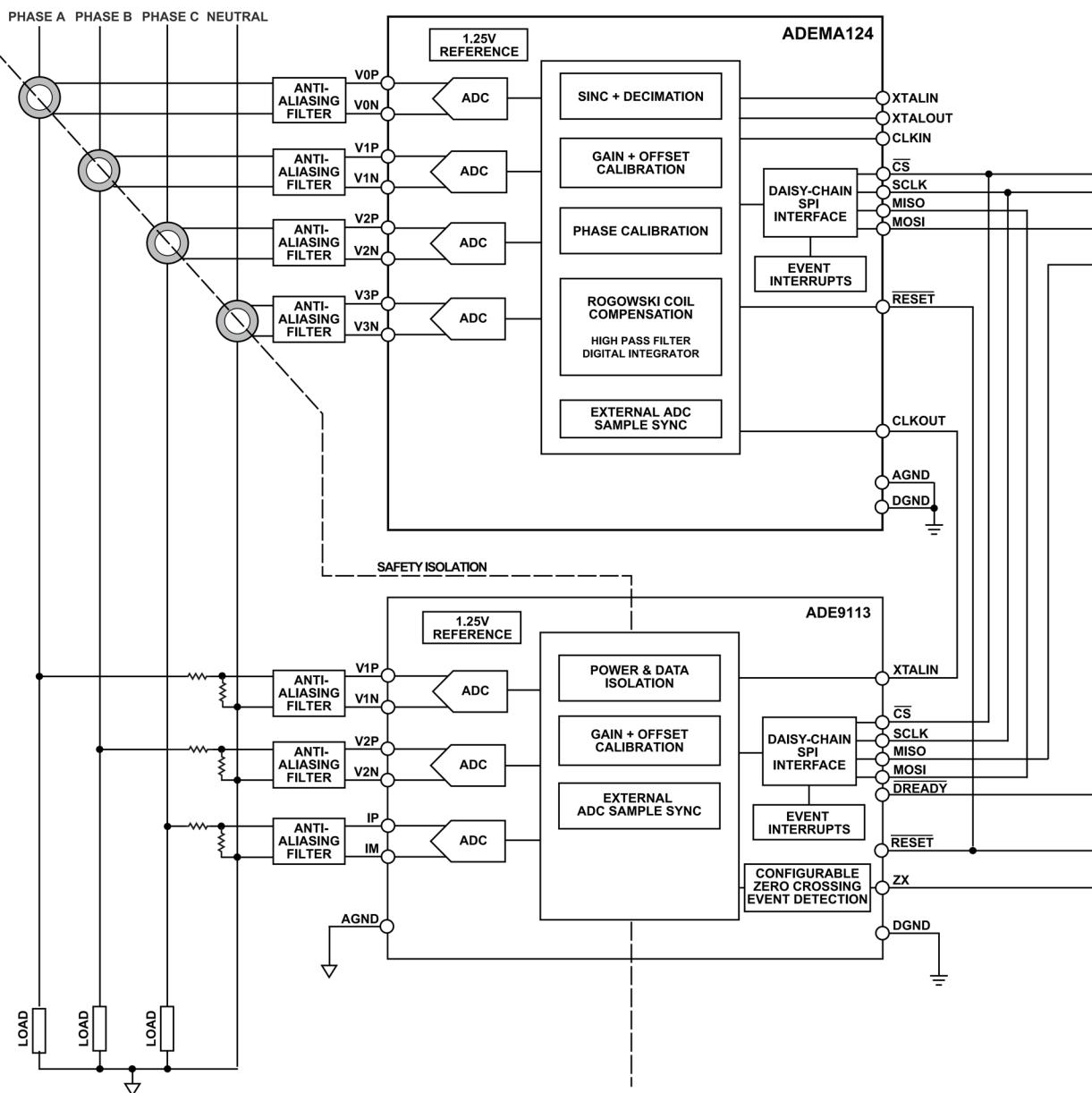

ADEMA124/ADEMA127 は、設定およびデータ取得を行うための柔軟な SPI インターフェースを備えています。デイジーチェーン SPI インターフェースにより、互換性のある複数の ADC を单一の SPI ポートで同時に処理できるため、ホスト・マイクロコントローラ上のピン数を大幅に節約できます。更に、SPI ポートには 2 チャンネルおよび 3 チャンネルの絶縁型 ADC (ADE9112/ADE9113) をデイジーチェーン接続できます。ADC の波形データの整合性を維持するために、独立した巡回冗長検査 (CRC) を使用して、SPI パケットの送受信時のエラーや、設定レジスタの偶発的な変更を検出することができます。

表 1. 製品比較

| Model    | 24-Bit ADC Channels |

|----------|---------------------|

| ADEMA124 | 4                   |

| ADEMA127 | 7                   |

## 目次

|                       |    |                     |    |

|-----------------------|----|---------------------|----|

| 特長                    | 1  | SPI 互換通信            | 24 |

| アプリケーション              | 1  | データバス設定             | 32 |

| 概要                    | 1  | 設定プロセッサ             | 38 |

| 機能ブロック図               | 3  | ステータス・レジスタおよび IRQ   | 39 |

| 仕様                    | 4  | CRC 保護              | 40 |

| 帯域幅およびパスバンド平坦性        | 7  | センサーと ADC のインターフェース | 42 |

| タイミング仕様               | 8  | 水晶発振器／外部クロック        | 43 |

| 絶対最大定格                | 9  | 複数デバイスの同期           | 44 |

| 熱抵抗                   | 9  | 消費電力                | 45 |

| ESD に関する注意            | 9  | 多相電力量計              | 46 |

| ピン配置およびピン機能の説明        | 10 | 単相 3 線電力量計          | 48 |

| 代表的な性能特性              | 12 | ハードウェア識別子           | 49 |

| テスト回路                 | 17 | SPI でアクセス可能なアドレス    | 50 |

| 用語の定義                 | 18 | レジスタの一覧             | 51 |

| 動作原理                  | 19 | レジスタの詳細             | 54 |

| ゲインおよびオフセットの補正        | 19 | DSP RAM の一覧         | 69 |

| クイック・スタート・ガイド         | 19 | DSP RAM の詳細         | 72 |

| アプリケーション情報            | 20 | 外形寸法                | 77 |

| スタートアップのシーケンスおよびタイミング | 20 | オーダー・ガイド            | 77 |

| 動作モード                 | 21 | 評価用ボード              | 77 |

## 改訂履歴

7/2025—Revision 0: Initial Version

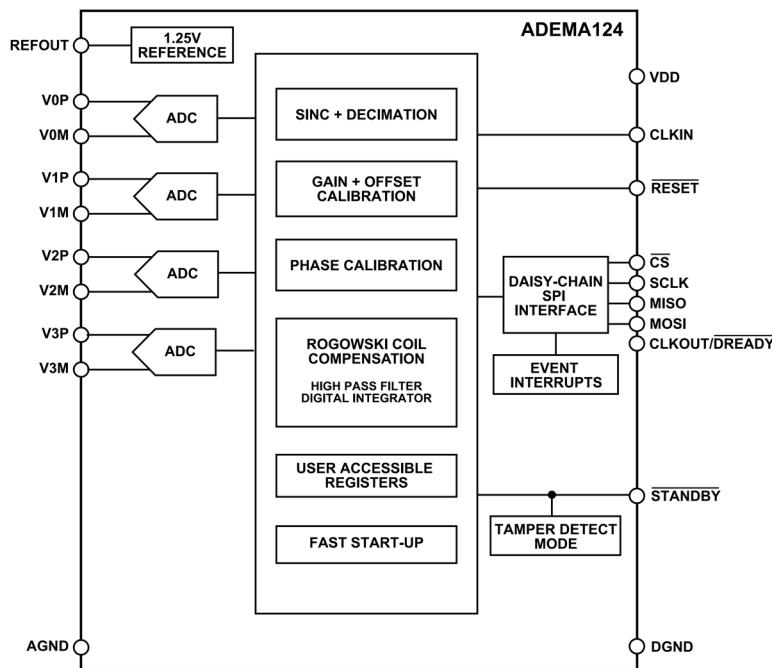

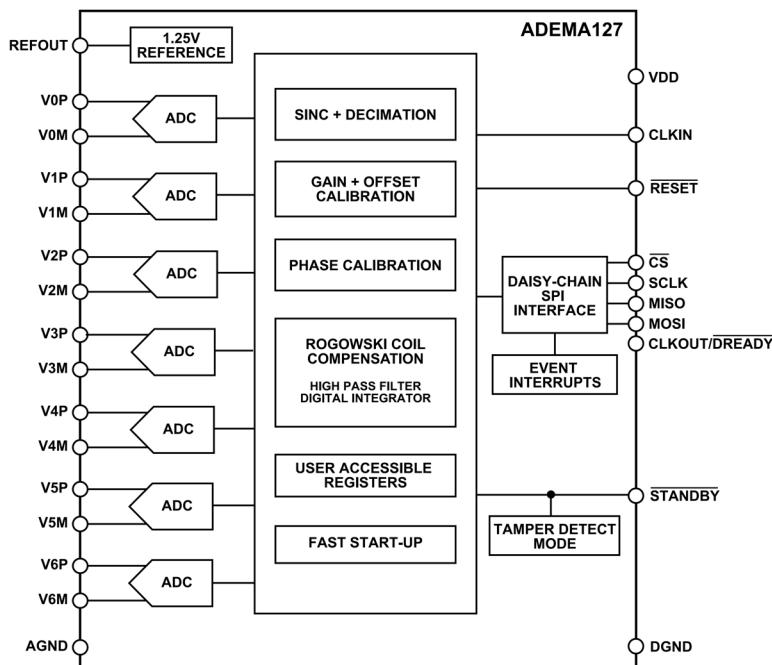

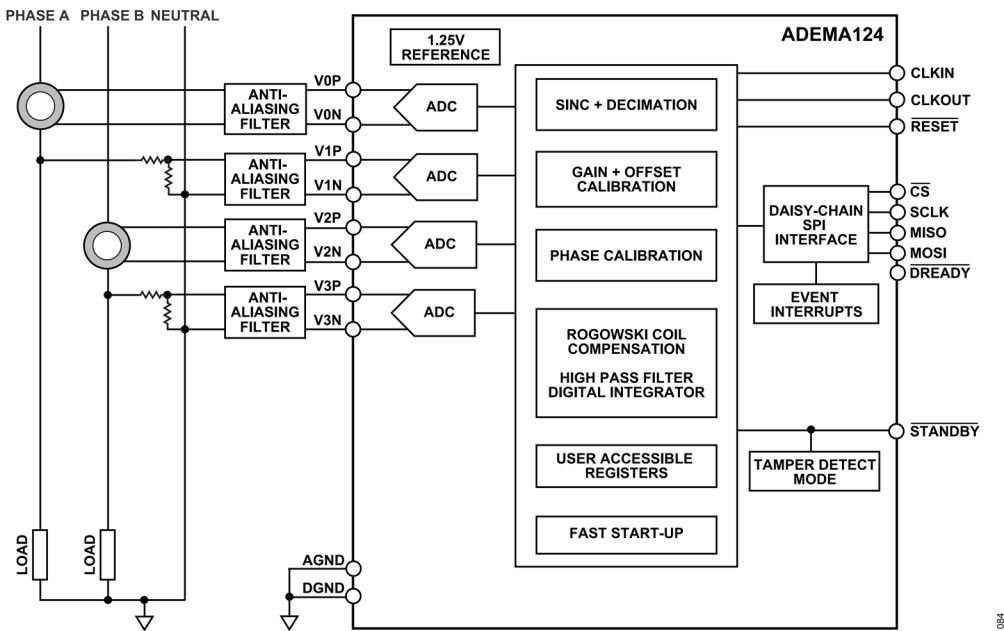

## 機能ブロック図

図 1. ADEMA124 の機能ブロック図

図 2. ADEMA127 の機能ブロック図

## 仕様

$V_{DD} = 3.3V \pm 10\%$ 、 $GND = 0V$ 、内蔵リファレンス、 $f_{XTALIN} = 16.384MHz$ 、 $T_{MIN} \sim T_{MAX} = -40^\circ C \sim +125^\circ C$ 、 $T_A = 25^\circ C$ （代表値の場合）。出力レート 4kHz。特に指定のない限り、各値はフル性能モード（ $ADC\_POWER\_MODE = 11$ ）でのものです。

表 2. 電気的特性

| Parameter                               | Min  | Typ   | Max  | Unit                   | Test Conditions/Comments                                                                         |

|-----------------------------------------|------|-------|------|------------------------|--------------------------------------------------------------------------------------------------|

| POWER SUPPLY                            |      |       |      |                        |                                                                                                  |

| Start-Up Inrush <sup>1</sup>            |      | 55    |      | mA                     | Includes required decoupling capacitors                                                          |

| ADEMA124                                |      |       |      |                        |                                                                                                  |

| High Resolution                         |      | 9.9   | 11.2 | mA                     | All DSP filters enabled, $f_{XTALIN} = 16.384MHz$ , $f_{MOD} = 2.048MHz$ , $f_s = 64kSPS$        |

| Default Configuration                   |      | 4.2   | 4.9  | mA                     | No DSP filters enabled, $f_{XTALIN} = 16.384MHz$ , $f_{MOD} = 2.048MHz$ , $f_s = 32kSPS$         |

| Low Power                               |      | 1.8   | 2.3  | mA                     | $f_{XTALIN} = 2.048MHz$ , $f_{MOD} = 256kHz$ , DSP off, $f_s = 1kSPS$ , $ADC\_POWER\_MODE = 0x0$ |

| Standby/Reset Mode                      |      | 4     |      | $\mu W$                |                                                                                                  |

| Tamper Detect Mode                      |      | 11.25 |      | mW                     | 2 ADC channels active                                                                            |

| ADEMA127                                |      |       |      |                        |                                                                                                  |

| High Resolution                         |      | 11.5  | 13.1 | mA                     | All DSP filters enabled, $f_{XTALIN} = 16.384MHz$ , $f_{MOD} = 2.048MHz$ , $f_s = 64kSPS$        |

| Default Configuration                   |      | 5.4   | 6.3  | mA                     | DSP off, $f_{XTALIN} = 16.384MHz$ , $f_{MOD} = 2.048MHz$ , $f_s = 32kSPS$                        |

| Low Power                               |      | 2.2   | 2.8  | mA                     | $f_{XTALIN} = 2.048MHz$ , $f_{MOD} = 256kHz$ , DSP off, $f_s = 1kSPS$ , $ADC\_POWER\_MODE = 0x0$ |

| Standby/Reset Mode                      |      | 4     |      | $\mu W$                |                                                                                                  |

| Tamper Detect Mode                      |      | 12.5  |      | mW                     | 4 ADC channels active                                                                            |

| INTERNAL VOLTAGE REFERENCE <sup>2</sup> |      |       |      |                        |                                                                                                  |

| Voltage Reference                       |      | 1.25  |      | V                      | $V_{REF}$                                                                                        |

| Temperature Coefficient                 |      | 5     | 15   | $ppm/\text{ }^\circ C$ |                                                                                                  |

| EXTERNAL VOLTAGE REFERENCE              |      |       |      |                        |                                                                                                  |

| Input Voltage (REFOUT)                  |      | 1.25  |      | V                      | $V_{REF}$                                                                                        |

| Input Impedance (REFOUT)                |      | 20    |      | k $\Omega$             |                                                                                                  |

| TEMPERATURE RANGE                       |      |       |      |                        |                                                                                                  |

| Operating Range                         | -40  |       | +125 | $^\circ C$             |                                                                                                  |

| ANALOG INPUTS                           |      |       |      |                        |                                                                                                  |

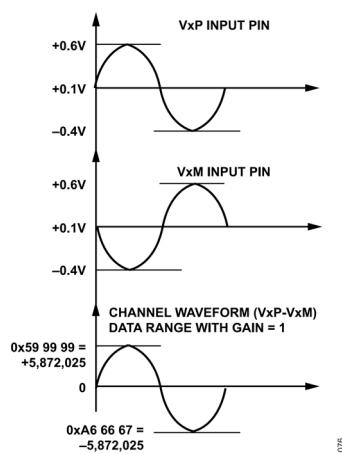

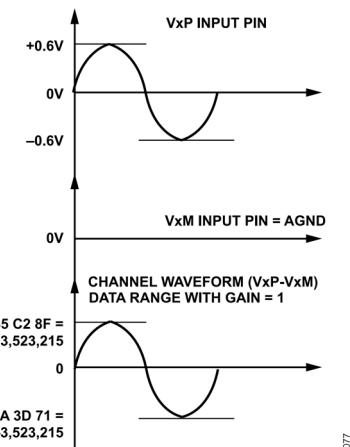

| Differential Voltage Range              |      |       |      |                        | $V_{xP} - V_{xN}$                                                                                |

| 1x Gain                                 | -1.2 |       | +1.2 | V                      | $ADC\_GAIN\_CHx = 0$                                                                             |

| 2x Gain                                 | -0.6 |       | +0.6 | V                      | $ADC\_GAIN\_CHx = 1$                                                                             |

| Common-Mode Range                       |      |       |      |                        | $(V_{xP} + V_{xN})/2$                                                                            |

| $ADC\_CMI\_CHx = 0$                     | -0.1 |       | +0.1 | V                      | Input from CT or voltage divider                                                                 |

| $ADC\_CMI\_CHx = 1$                     | 0.9  |       | 1.2  | V                      | Input from preamplifier with DC offset                                                           |

| Single-Ended Voltage Range              |      |       |      |                        | Pseudodifferential connection, voltage on the pin with respect to AGND (AGND = DGND)             |

| 1x Gain                                 | -0.6 |       | +0.6 | V                      | Full-scale without clipping, $ADC\_CMI\_CHx = 0$ , $ADC\_GAIN\_CHx = 0$                          |

| 2x Gain                                 | -0.3 |       | +0.3 | V                      | Full-scale without clipping, $ADC\_CMI\_CHx = 0$ , $ADC\_GAIN\_CHx = 1$                          |

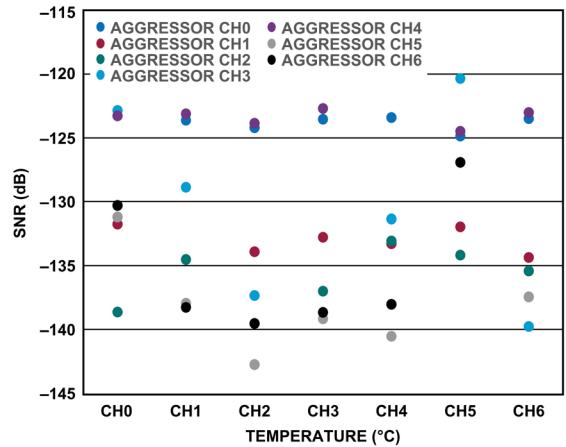

| Crosstalk                               |      |       |      |                        | Aggressor channels at full-scale                                                                 |

| 1x Gain                                 |      |       | -120 | dB                     |                                                                                                  |

| 2x Gain                                 |      |       | -120 | dB                     |                                                                                                  |

## 仕様

表 2. 電気的特性（続き）

| Parameter                                                                  | Min  | Typ       | Max  | Unit    | Test Conditions/Comments                   |

|----------------------------------------------------------------------------|------|-----------|------|---------|--------------------------------------------|

| Differential Input Impedance                                               |      |           |      |         |                                            |

| 1x Gain                                                                    |      | 150       |      | kΩ      |                                            |

| 2x Gain                                                                    |      | 75        |      | kΩ      |                                            |

| ADC Offset Error                                                           |      |           |      |         |                                            |

| 1x Gain                                                                    | -150 | ±20       | 150  | µV      |                                            |

| 2x Gain                                                                    | -150 | ±45       | 150  | µV      |                                            |

| ADC Offset Drift over Temperature                                          |      |           | 150  | nV/°C   |                                            |

| ADC Gain Error                                                             | -2.0 | ±0.1      | +2.0 | %       | Not including anti-aliasing filter         |

| ADC Gain Drift over Temperature                                            |      | 5         |      | ppm/°C  | Without internal reference                 |

| ADC Gain Drift over Temperature                                            |      | 2         | 10   | ppm/°C  | With internal reference                    |

| ADC Transfer Function                                                      |      |           |      |         | 1.25V internal reference                   |

| 1x Gain                                                                    |      | 4,772,275 |      | codes/V |                                            |

| 2x Gain                                                                    |      | 9,543,472 |      | codes/V |                                            |

| Tamper Detect Mode                                                         |      |           |      |         |                                            |

| Total Unadjusted Error (TUE)                                               | -2   |           | +2   | %FSR    |                                            |

| POWER-SUPPLY REJECTION RATIO (PSRR)/<br>COMMON-MODE REJECTION RATIO (CMRR) |      |           |      |         |                                            |

| PSRR                                                                       |      | 120       |      | dB      | 120mV <sub>RMS</sub> 50Hz contaminated VDD |

| CMRR                                                                       |      |           |      |         |                                            |

| 1x Gain                                                                    |      | 110       |      | dB      | ADC_CMI_CHx = 0                            |

| 1x Gain                                                                    |      | 95        |      | dB      | ADC_CMI_CHx = 1                            |

| 2x Gain                                                                    |      | 110       |      | dB      | ADC_CMI_CHx = 0                            |

| ADC PERFORMANCE                                                            |      |           |      |         | f <sub>MOD</sub> = 2.048MHz                |

| 32kSPS                                                                     |      |           |      |         |                                            |

| Signal-to-Noise Ratio (SNR)                                                |      |           |      |         |                                            |

| 1x Gain                                                                    |      | 97        |      | dBFS    | Figure 25, Figure 27                       |

| 2x Gain                                                                    |      | 97        |      | dBFS    |                                            |

| Signal-to-Noise and Distortion Ratio (SINAD)                               |      |           |      |         |                                            |

| 1x Gain                                                                    |      | 95        |      | dBFS    |                                            |

| 2x Gain                                                                    |      | 87        |      | dBFS    |                                            |

| Total Harmonic Distortion (THD)                                            |      |           |      |         |                                            |

| 1x Gain                                                                    |      | -98       |      | dBFS    | Figure 26, Figure 28                       |

| 2x Gain                                                                    |      | -88       |      | dBFS    |                                            |

| Spurious-Free Dynamic Range (SFDR)                                         |      |           |      |         |                                            |

| 1x Gain                                                                    |      | 100       |      | dBFS    |                                            |

| 2x Gain                                                                    |      | 89        |      | dBFS    |                                            |

| 4kSPS                                                                      |      |           |      |         |                                            |

| SNR                                                                        |      |           |      |         |                                            |

| 1x Gain                                                                    |      | 102       |      | dBFS    |                                            |

| 2x Gain                                                                    |      | 101       |      | dBFS    |                                            |

| SINAD                                                                      |      |           |      |         |                                            |

| 1x Gain                                                                    |      | 98        |      | dBFS    |                                            |

| 2x Gain                                                                    |      | 90        |      | dBFS    |                                            |

| THD                                                                        |      |           |      |         |                                            |

| 1x Gain                                                                    |      | -101      |      | dBFS    |                                            |

| 2x Gain                                                                    |      | -90       |      | dBFS    |                                            |

| SFDR                                                                       |      |           |      |         |                                            |

| 1x Gain                                                                    |      | 104       |      | dBFS    |                                            |

| 2x Gain                                                                    |      | 92        |      | dBFS    |                                            |

## 仕様

表 2. 電気的特性（続き）

| Parameter                                             | Min    | Typ    | Max    | Unit | Test Conditions/Comments                                       |

|-------------------------------------------------------|--------|--------|--------|------|----------------------------------------------------------------|

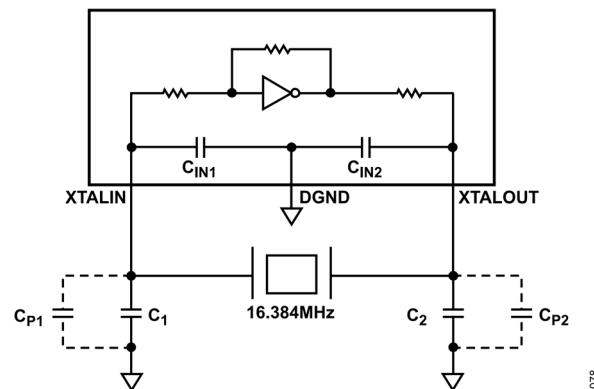

| CRYSTAL OSCILLATOR                                    |        |        |        |      |                                                                |

| Nominal Crystal Frequency                             | 12.288 |        | 16.384 | MHz  |                                                                |

| Internal Capacitance on CLKIN, CLKOUT                 |        | 3.5    |        | pF   |                                                                |

| Internal Feedback Resistance between CLKIN and CLKOUT |        | 2.5    |        | MΩ   |                                                                |

| Transconductance ( $g_m$ )                            | 6      | 8      |        | mA/V |                                                                |

| EXTERNAL CLOCK INPUT                                  |        |        |        |      |                                                                |

| Input Clock Frequency                                 | 0.3    | 16.384 | 16.547 | MHz  |                                                                |

| XTALIN Duty Cycle                                     | 45     |        | 55     | %    |                                                                |

| With XTALOUT Routed to Other Devices                  | 47.5   |        | 52.5   | %    |                                                                |

| XTALIN Pulse Width                                    | 28     |        |        | ns   |                                                                |

| CLOCK OUTPUT                                          |        |        |        |      |                                                                |

| XTALIN to CLKOUT Propagation Delay                    |        | 6      |        | ns   | CLKOUT_EN = 1<br>ADC_POWER_MODE = 0b11                         |

| OUTPUT SAMPLE RATE                                    |        |        | 2.048  | MHz  |                                                                |

| ΣΔ Modulator Frequency ( $f_{MOD}$ )                  |        |        | 64     | kSPS |                                                                |

| DSP Frequency ( $f_{DSP}$ )                           |        |        |        |      |                                                                |

| LOGIC INPUTS - XTALIN Pin                             |        |        |        |      |                                                                |

| Input High Voltage, $V_{INH}$                         | 1.2    |        |        | V    |                                                                |

| Input Low Voltage, $V_{INL}$                          |        | 0.5    |        | V    |                                                                |

| LOGIC INPUTS - MOSI, SCLK, CS, STDBY, and RESET Pins  |        |        |        |      |                                                                |

| Input High Voltage, $V_{INH}$                         | 2.0    |        |        | V    |                                                                |

| Input Low Voltage, $V_{INL}$                          |        | 0.8    |        | V    |                                                                |

| Input Current, $I_{IN}$ (MOSI, SCLK, CS)              |        | 8      |        | μA   | Integrated pull-up                                             |

| Input Current, $I_{IN}$ (STDBY, and RESET)            |        | 200    |        | nA   |                                                                |

| LOGIC OUTPUTS - CLKOUT/DREADY, and MISO Pins          |        |        |        |      |                                                                |

| Output High Voltage, $V_{OH}$                         | 2.4    |        |        |      | Source current ( $I_{SOURCE}$ ) = 3.5mA                        |

| Output Low Voltage, $V_{OL}$                          |        | 0.4    |        |      | Sink current ( $I_{SINK}$ ) = 3.5mA                            |

| LOW DROPOUT REGULATORS (LDOs)                         |        |        |        |      |                                                                |

| ALDOOUT                                               |        | 1.9    |        | V    |                                                                |

| VLDOOUT                                               |        | 1.9    |        | V    |                                                                |

| UNDERVOLTAGE LOCKOUT <sup>1</sup>                     |        |        |        |      |                                                                |

| Positive VDD Threshold                                |        | 2.8    |        | V    | UVLO<br>Rising supply voltage enable threshold,<br>$V_{UVLO+}$ |

| Negative VDD Threshold                                | 2.2    |        |        | V    | Falling supply voltage lockout threshold,<br>$V_{UVLO-}$       |

| VDD Hysteresis                                        |        | 14     |        | mV   | UVLO hysteresis, $V_{UVLO\_HYS}$                               |

<sup>1</sup> 設計により裏付けられています。製品テストは実施していません。<sup>2</sup> リファレンス温度係数は、チャンネル・ゲインを最適化するために、製品テスト時に調整しています。

## 仕様

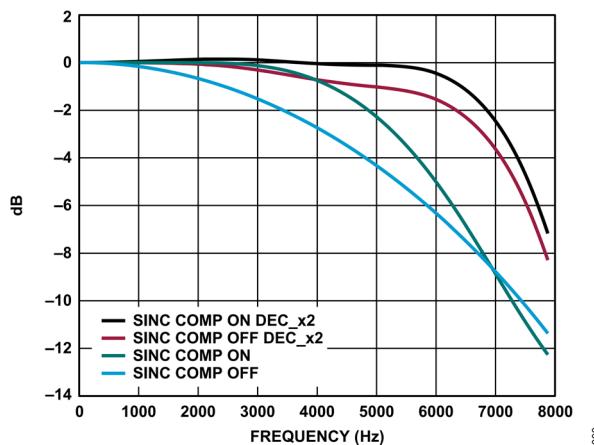

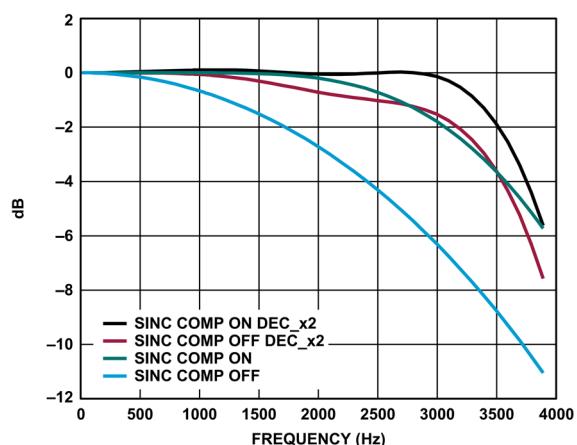

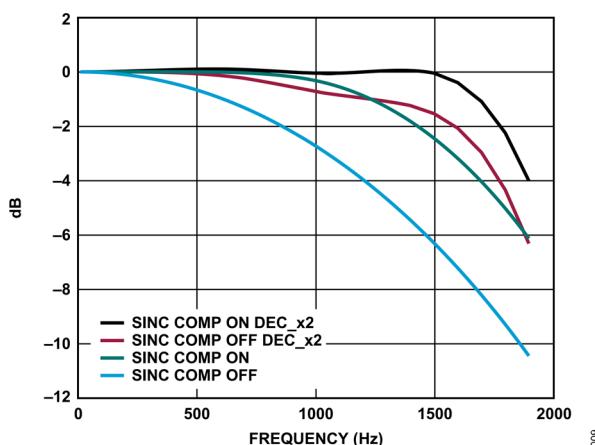

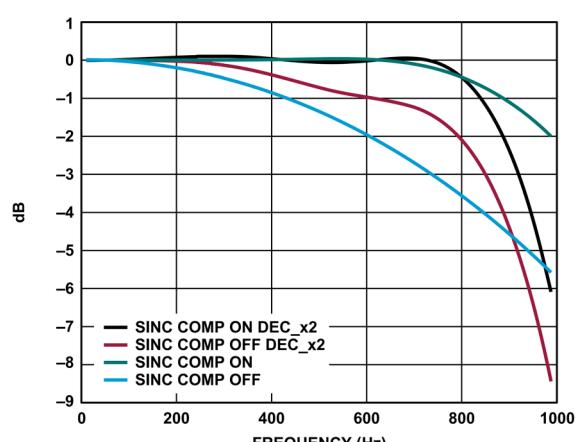

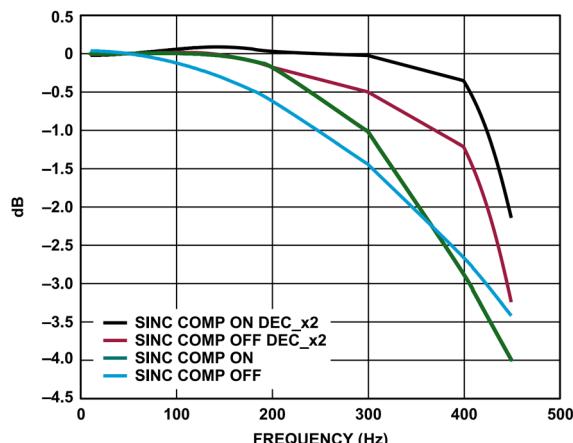

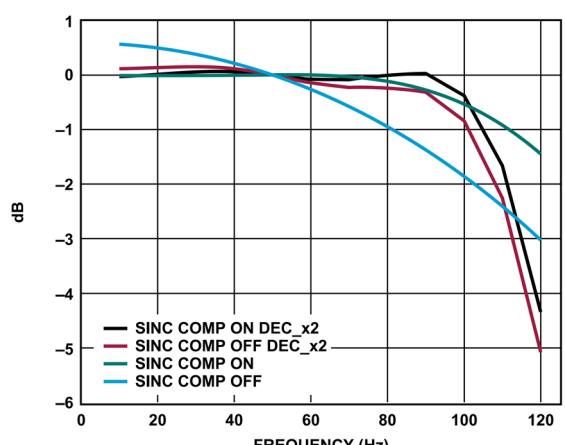

## 帯域幅およびパスバンド平坦性

すべての仕様は、 $f_{XTALIN} = 16.384\text{MHz}$  およびデフォルト DSP フィルタ係数に対する代表値です。

表 3. 帯域幅およびパスバンド平坦性特性

| Parameter                   | Sinc Decimation Only | Sinc Compensation | Sinc Compensation and LPF | Sinc Compensation, LPF, and DSP Decimate-by-2 | Comment                          |

|-----------------------------|----------------------|-------------------|---------------------------|-----------------------------------------------|----------------------------------|

| Output Bandwidth (-3dB)     |                      |                   |                           |                                               |                                  |

| 64kSPS                      | 17,000               | 21,000            | 14,500                    | N/A <sup>1</sup>                              | ADC Output Bandwidth<br>Figure 7 |

| 32kSPS                      | 8,400                | 9,300             | 7,150                     | 14,500                                        | Figure 10                        |

| 16kSPS                      | 4,200                | 5,300             | 3,650                     | 7,200                                         | Figure 8                         |

| 8kSPS                       | 2,100                | 3,400             | 1,850                     | 3,650                                         | Figure 11                        |

| 4kSPS                       | 1,050                | 1,600             | 920                       | 1,850                                         | Figure 9                         |

| 2kSPS                       | 740                  | > $f_s/2$         | 465                       | 920                                           | Figure 12                        |

| 1kSPS                       | 420                  | 410               | 250                       | 465                                           | Figure 13                        |

| 500SPS                      | 225                  | > $f_s/2$         | 125                       | 230                                           | Figure 15                        |

| 250SPS                      | 120                  | > $f_s/2$         | 58                        | 115                                           | Figure 14                        |

| Pass-Band Flatness (-0.1dB) |                      |                   |                           |                                               | ADC Pass-Band Flatness           |

| 64kSPS                      | 3,100                | 10,000            | 11,000                    | N/A <sup>1</sup>                              | Figure 7                         |

| 32kSPS                      | 1,600                | 4,800             | 4,600                     | 11,000                                        | Figure 10                        |

| 16kSPS                      | 800                  | 2,900             | 2,950                     | 4,600                                         | Figure 8                         |

| 8kSPS                       | 400                  | 1,800             | 1,700                     | 3,300                                         | Figure 11                        |

| 4kSPS                       | 200                  | 850               | 850                       | 1,650                                         | Figure 9                         |

| 2kSPS                       | 150                  | 700               | 385                       | 760                                           | Figure 12                        |

| 1kSPS                       | 94                   | 180               | 180                       | 420                                           | Figure 13                        |

| 500SPS                      | 70                   | 185               | 104                       | 115                                           | Figure 15                        |

| 250SPS                      | 55                   | 80                | 31 <sup>2</sup>           | 95                                            | Figure 14                        |

<sup>1</sup> N/A は該当なしを意味します。これは有効な設定ではありません。

<sup>2</sup> 10Hz を基準としています。

## 仕様

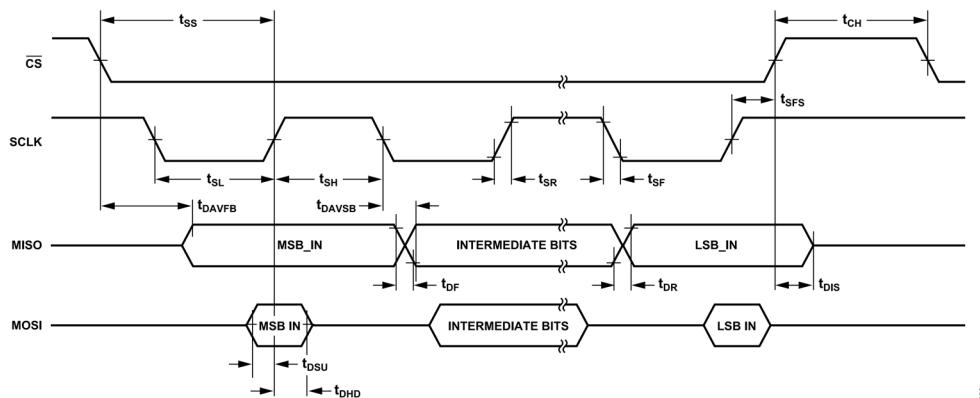

## タイミング仕様

特に指定のない限り、 $V_{DD} = 3.3V \pm 10\%$ 、 $AGND = 0V$ 、 $DGND = 0V$ 、内蔵リファレンス、 $f_{XTALIN} = 16.384MHz$ 、 $T_{MIN} \sim T_{MAX} = -40^{\circ}C \sim +125^{\circ}C$ 。

表 4. SPI インターフェースのタイミング・パラメータ

| Parameter <sup>1</sup>                                          | Symbol      | Min | Max    | Unit |

|-----------------------------------------------------------------|-------------|-----|--------|------|

| $\overline{CS}$ to SCLK Positive Edge                           | $t_{SS}$    | 10  |        | ns   |

| SCLK Frequency <sup>2</sup>                                     | $f_{SCLK}$  | 250 | 22,000 | kHz  |

| SCLK Duty Cycle                                                 |             | 40  | 60     | %    |

| SCLK Low Pulse Width                                            | $t_{SL}$    | 20  |        | ns   |

| SCLK High Pulse Width                                           | $t_{SH}$    | 20  |        | ns   |

| Data Output Valid After $\overline{CS}$ Edge                    | $t_{DAVFB}$ |     | 20     | ns   |

| Subsequent Data Output Valid after SCLK Edge                    | $t_{DAVSB}$ |     | 20     | ns   |

| Data Input Setup Time before SCLK Edge                          | $t_{DSU}$   | 10  |        | ns   |

| Data Input Hold Time after SCLK Edge                            | $t_{DHD}$   | 10  |        | ns   |

| Data Output Fall Time                                           | $t_{DF}$    |     | 10     | ns   |

| Data Output Rise Time                                           | $t_{DR}$    |     | 10     | ns   |

| SCLK Rise Time                                                  | $t_{SR}$    |     | 5      | ns   |

| SCLK Fall Time                                                  | $t_{SF}$    |     | 5      | ns   |

| MISO Disable after $\overline{CS}$ Rising Edge                  | $t_{DIS}$   |     | 20     | ns   |

| $\overline{CS}$ High after SCLK Edge                            | $t_{SFS}$   |     | 10     | ns   |

| $\overline{CS}$ High Time between SPI Transactions <sup>3</sup> | $t_{CH}$    | 400 |        | ns   |

<sup>1</sup> 仕様は、設計および特性評価により裏付けられていますが、製品テストは実施していません。

<sup>2</sup>  $f_{SCLK}$  は  $1.4 \times f_{XTALIN}$  未満であることが必要です。

<sup>3</sup>  $f_{XTALIN} < 16.384MHz$  の場合、 $t_{CH}$  は  $6/f_{XTALIN}$  より長いことが必要です。詳細については、SPI 互換通信のセクションを参照してください。

図 3. SPI のタイミング、SPI モード 3 (CPOL = 1 および CHPA = 1)

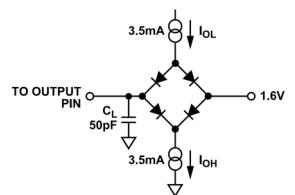

図 4. タイミング仕様評価用の負荷回路

## 絶対最大定格

表 5. ADEMA124/ADEMA127 の絶対最大定格

| Parameter                                    | Rating                   |

|----------------------------------------------|--------------------------|

| $V_{DD}$ to DGND                             | -0.3V to +3.7V           |

| Analog Input Voltage                         |                          |

| $V_{0P}$ and $V_{0M}$ to DGND                | -1.7V to +2V             |

| $V_{1P}$ and $V_{1M}$ to DGND                | -1.7V to +2V             |

| $V_{2P}$ and $V_{2M}$ to DGND                | -1.7V to +2V             |

| $V_{3P}$ and $V_{3M}$ to DGND                | -1.7V to +2V             |

| $V_{4P}$ and $V_{4M}$ to DGND                | -1.7V to +2V             |

| $V_{5P}$ and $V_{5M}$ to DGND                | -1.7V to +2V             |

| $V_{6P}$ and $V_{6M}$ to DGND                | -1.7V to +2V             |

| Digital Input Voltage                        |                          |

| MOSI, SCLK, CS, XTALIN, STDBY, RESET to DGND | -0.3V to $V_{DD}$ + 0.3V |

| Digital Output Voltage                       |                          |

| CLKOUT/DREADY, MISO, XTALOUT to DGND         | -0.3V to $V_{DD}$ + 0.3V |

| Reference Voltage                            |                          |

| REFOUT to DGND                               | -0.3V to +2.2V           |

| Temperature                                  |                          |

| Operating                                    | -40°C to +125°C          |

| Storage Range                                | -65°C to +150°C          |

| Lead (Soldering, 10sec) <sup>1</sup>         | 260°C                    |

| Moisture Sensitivity Level                   | MSL 3                    |

<sup>1</sup> RoHS適合デバイスのハンダ付け処理に使用するリフロー・プロファイルは、JEDECのJ-STD-020D.1に従うことを推奨します。この規格の最新版については、JEDECを参照してください。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCBの熱設計には細心の注意を払う必要があります。

$\theta_{JA}$ は、1立方フィートの密閉容器内で測定された、自然流での周囲とジャンクションの間の熱抵抗です。 $\theta_{JC}$ は、ジャンクションとケースの間の熱抵抗です。

表 6. 热抵抗

| Package Type <sup>1</sup> | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|---------------------------|---------------|---------------|------|

| CP-32-20                  | 31.73         | 25.60         | °C/W |

<sup>1</sup> テスト条件 1：熱抵抗のシミュレーション値は、2S2P JEDEC PCB の使用によって決定します。

## ESDに関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能の説明

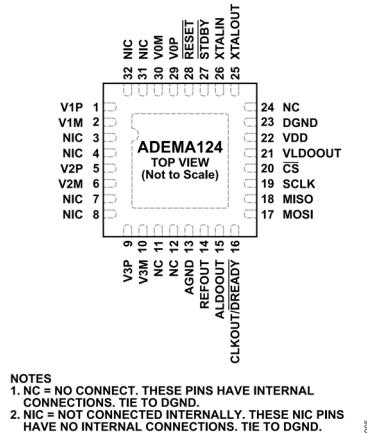

図 5. ADEMA124 のピン配置

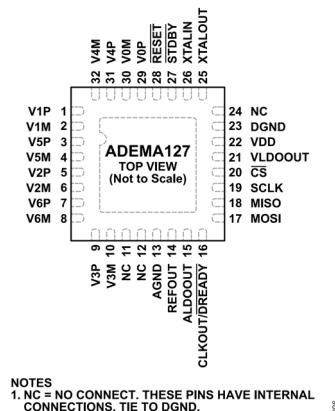

図 6. ADEMA127 のピン配置

表 7. ピン機能の説明

| ピン番号               |          |          |                                                                                                                                                                                                                                                              |

|--------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADEMA124           | ADEMA127 | 記号       | 説明                                                                                                                                                                                                                                                           |

| 1, 2               | 1, 2     | V1P, V1M | ADC チャンネル 1 用のアナログ入力。                                                                                                                                                                                                                                        |

| 3, 4, 7, 8, 31, 32 |          | NIC      | 内部接続されていません。これらの NIC ピンは内部接続されていません。DGND に接続します。                                                                                                                                                                                                             |

|                    | 3, 4     | V5P, V5M | ADC チャンネル 5 用のアナログ入力。                                                                                                                                                                                                                                        |

| 5, 6               | 5, 6     | V2P, V2M | ADC チャンネル 2 用のアナログ入力。                                                                                                                                                                                                                                        |

|                    | 7, 8     | V6P, V6M | ADC チャンネル 6 用のアナログ入力。                                                                                                                                                                                                                                        |

| 9, 10              | 9, 10    | V3P, V3M | ADC チャンネル 3 用のアナログ入力。                                                                                                                                                                                                                                        |

| 11, 12             | 11, 12   | NC       | 接続なし。これらのピンは内部接続されています。DGND に接続します。                                                                                                                                                                                                                          |

| 13                 | 13       | AGND     | アナログ・グラウンド・リファレンス。DGND に接続します。                                                                                                                                                                                                                               |

| 14                 | 14       | REFOUT   | このピンから内蔵電圧リファレンスにアクセスできます。内蔵リファレンスの公称値は 1.25V です。REFOUT ピンは、0.1μF のコンデンサと 2.2μF のコンデンサを用いて DGND とデカップリングします。これらのコンデンサはできるだけ近付けて配置します。<br>外部回路で内蔵電圧リファレンスを使用するには、バッファが必要です。<br>外部電圧リファレンスをこのピンに接続することもできます。詳細については、 <a href="#">電圧リファレンス</a> のセクションを参照してください。 |

| 15                 | 15       | ALDOOUT  | アナログ低ドロップアウト (LDO) レギュレータの 1.9V 出力。<br>このピンは 0.22μF のコンデンサで DGND とデカップリングします。ALDOOUT ピンには外部負荷回路を接続しないでください。                                                                                                                                                  |

## ピン配置およびピン機能の説明

表 7. ピン機能の説明（続き）

| ピン番号     |                  |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADEMA124 | ADEMA127         | 記号                           | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16       | 16               | CLKOUT/DREADY                | <p>データ・レディ、アクティブ・ロー (<math>\overline{\text{DREADY}}</math>)。<math>\overline{\text{DREADY}}</math>ピンは、新しいADCサンプルが読み出し可能であることを示すアクティブ・ローの信号を発生し、また、ADC出力周波数に同期しています。この信号を用いるとADC出力の読み出しを同期できます。</p> <p><math>\overline{\text{DREADY}}</math>がこのピンのデフォルト機能です。リセット後の最初の立ち上がりエッジで、SPIポートがコマンドに対する準備ができていることを通知します。立ち下がりエッジは、ADCサンプルがCCMで読み出し可能であることを示します。<a href="#">図 38</a>を参照してください。</p> <p>ADEMA124/ADEMA127がTDMで動作している場合、<math>\overline{\text{DREADY}}</math>を割込みピンとして設定できます。詳細については、<a href="#">改ざん検知モード</a>のセクションを参照してください。</p> <p>クロック出力 (CLKOUT)。CLKOUT_ENビットによって設定されるピン機能です。CLKOUT機能が選択された場合、ADEMA124/ADEMA127はXTALINピンのコントローラ・クロックに同期したデジタル信号を発生します。他のデバイスにクロックを供給するには、CLKOUTを使用します。</p> |

| 17       | 17               | MOSI                         | SPIポートのデータ入力。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18       | 18               | MISO                         | SPIポートのデータ出力。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 19       | 19               | SCLK                         | SPIポートのシリアル・クロック入力。すべてのシリアル・データ転送は、このクロックに同期します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 20       | 20               | $\overline{\text{CS}}$       | SPIポートのチップ・セレクト。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21       | 21               | VLDOOUT                      | デジタル低ドロップアウト (LDO) レギュレータの1.9V出力。<br>このピンは0.22 $\mu\text{F}$ のコンデンサでDGNDとデカッピングします。VLDOOUTピンには外部負荷回路を接続しないでください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22       | 22               | VDD                          | 電源電圧、3.3V $\pm$ 10%。このピンは0.1 $\mu\text{F}$ のコンデンサと2.2 $\mu\text{F}$ のコンデンサでDGNDとデカッピングします。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 23       | 23               | DGND                         | デジタル・グラウンド・リファレンス。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24       | 24               | NC                           | 接続なし。このピンは、内部接続されています。DGNDに接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 25       | 25               | XTALOUT                      | クリスタル出力。 <a href="#">表 2</a> に示すトランスクンダクタンス ( $g_m$ )に基づいてクリスタルを選択してください。クリスタルをXTALINピンとXTALOUTピンの間に接続すると、ADEMA124/ADEMA127にクロック源を供給できます。<br>XTALOUTピンを使用しない場合は、フローティング状態にする必要があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26       | 26               | XTALIN                       | コントローラ・クロック入力。<br>他のデバイスから供給されるCLKOUT信号などの外部クロックは、このロジック入力に供給できます。<br>あるいは、XTALINピンとXTALOUTピンの間にクリスタルを接続することもできます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27       | 27               | $\overline{\text{STDBY}}$    | アクティブ・ローのスタンバイ入力。このピンには外部プルアップが必要であり、使用しない場合はVDDに接続する必要があります。詳細については、 <a href="#">スタンバイ・モード</a> のセクションを参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 28       | 28               | $\overline{\text{RESET}}$    | アクティブ・ローのリセット入力。このピンには外部プルアップが必要であり、使用しない場合はVDDに接続する必要があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 29, 30   | 29, 30<br>31, 32 | V0P, V0M<br>V4P, V4M<br>EPAD | ADCチャンネル0用のアナログ入力。<br>ADCチャンネル4用のアナログ入力。<br>露出パッド (EP)。露出パッドはDGNDに接続する必要があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 代表的な性能特性

図 7. 64kSPS での帯域幅

図 10. 32kSPS での帯域幅

図 8. 16kSPS での帯域幅

図 11. 8kSPS での帯域幅

図 9. 4kSPS での帯域幅

図 12. 2kSPS での帯域幅

## 代表的な性能特性

図 13. 1kSPS での帯域幅

013

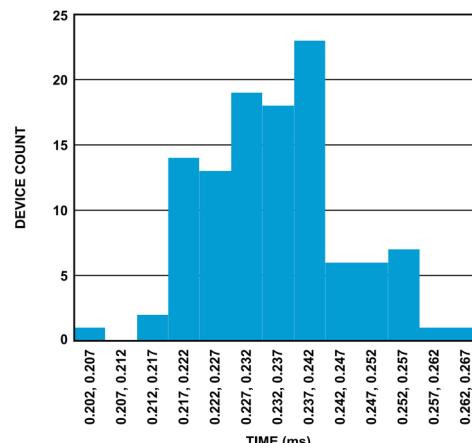

図 16. 高速スタートアップ時間のヒストグラム

016

図 14. 250kSPS での帯域幅

014

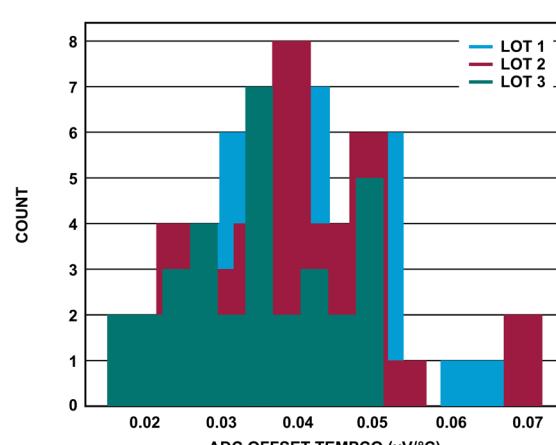

図 17. 入力オフセット電圧と温度のヒストグラム

017

図 15. 500kSPS での帯域幅

015

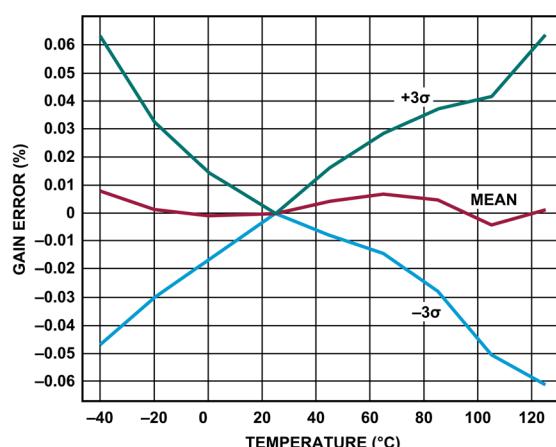

図 18. ゲイン誤差と温度の関係

018

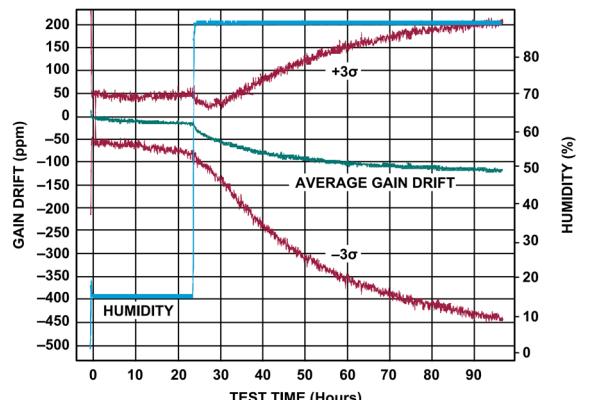

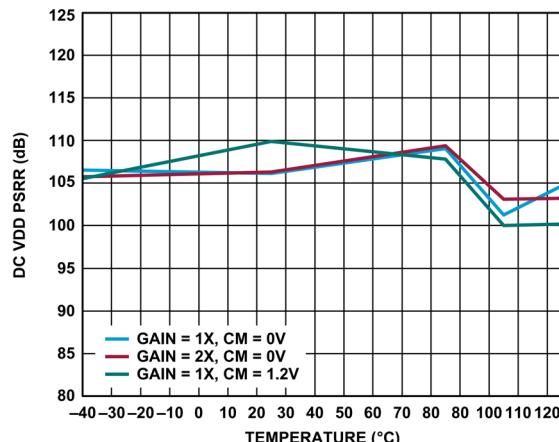

## 代表的な性能特性

図 19. ゲイン・ドリフトと湿度の関係、平均値および $\pm 3\sigma$

図 22. DC VDD PSRR と温度の関係、フルパワー動作モード

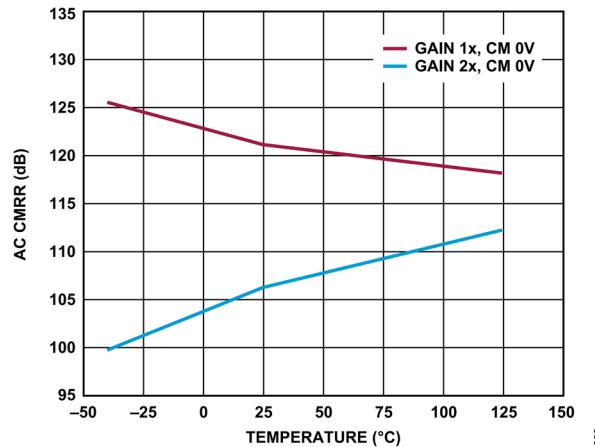

図 20. AC CMRR と VDD の関係、50Hz、 $V_{DD} = 3.3V$ 、フルパワー動作モード

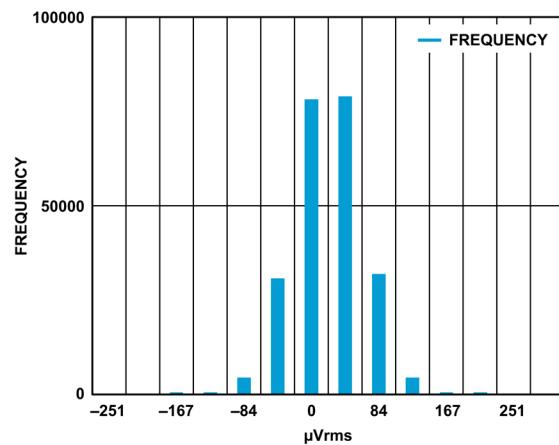

図 23. シングル・デバイスのノイズ・ヒストグラム、32kSPS、入力短絡、ゲイン = 1

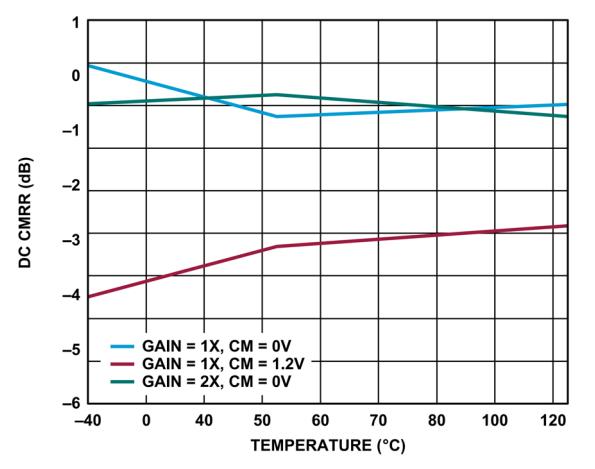

図 21. DC CMRR と温度の関係、フルパワー動作モード

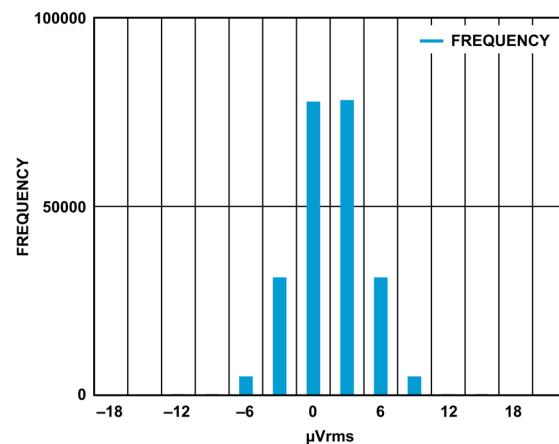

図 24. シングル・デバイスのノイズ・ヒストグラム、4kSPS、ADC 入力短絡、ゲイン = 1

## 代表的な性能特性

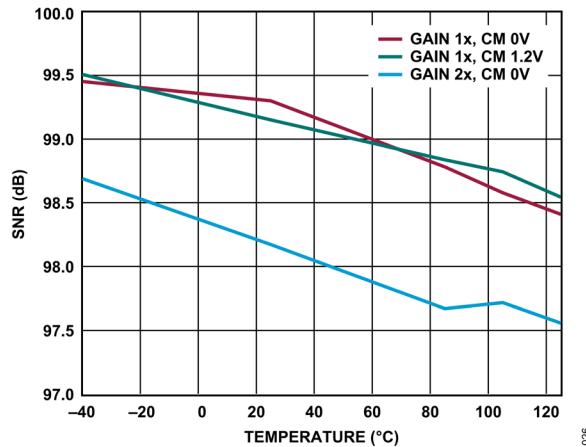

図 25. SNR と温度の関係、32kSPS

026

図 26. THD と温度の関係、32kSPS

027

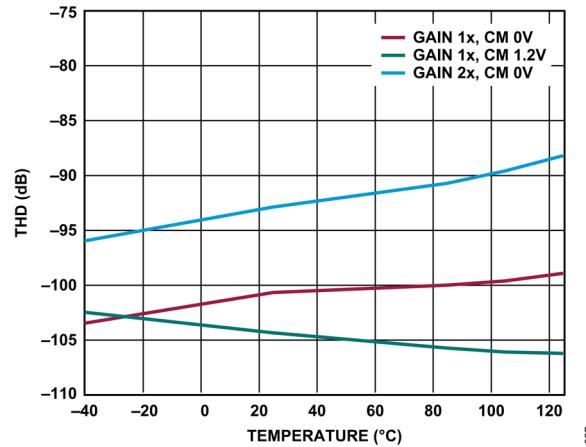

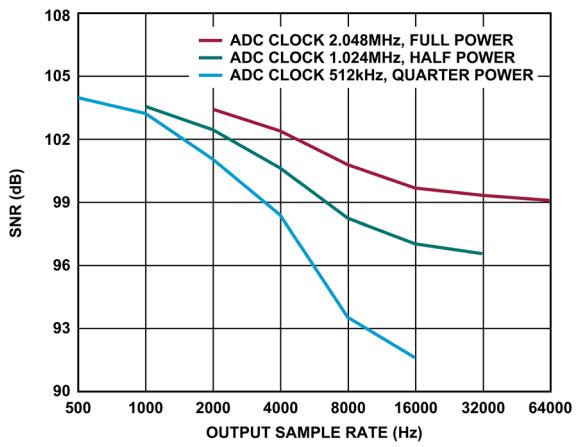

図 27. SNR と OSR の関係、ゲイン = 1

028

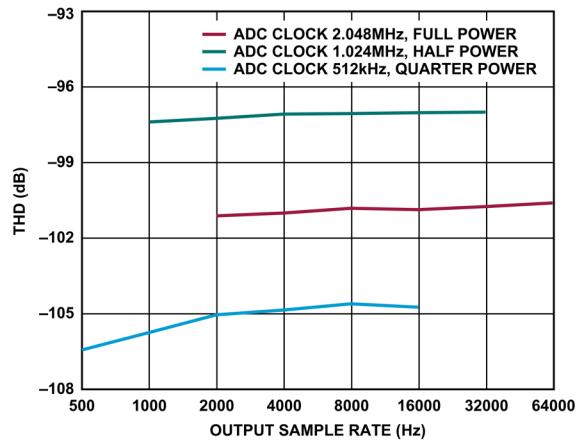

図 28. THD と OSR の関係、ゲイン = 1

029

図 29. クロストークとチャンネルの関係、

ゲイン = 1x、コモンモード = 0V

030

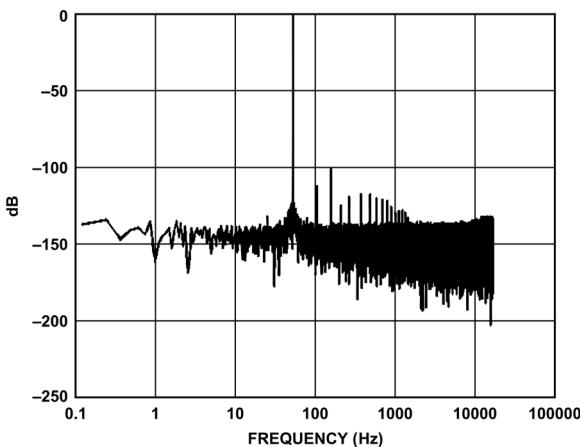

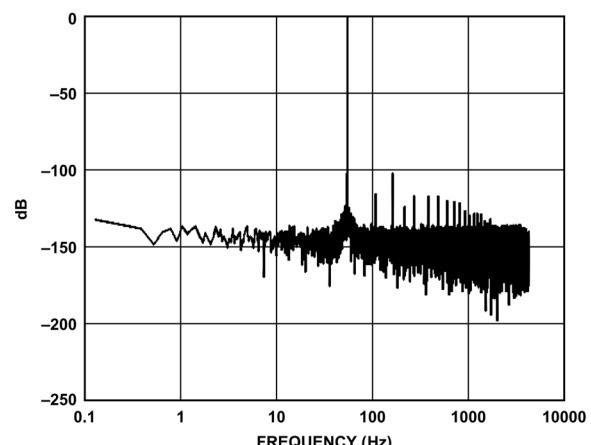

図 30. 50Hz 入力、高速フーリエ変換 (FFT)、

32kSPS、sinc3のみ

031

## 代表的な性能特性

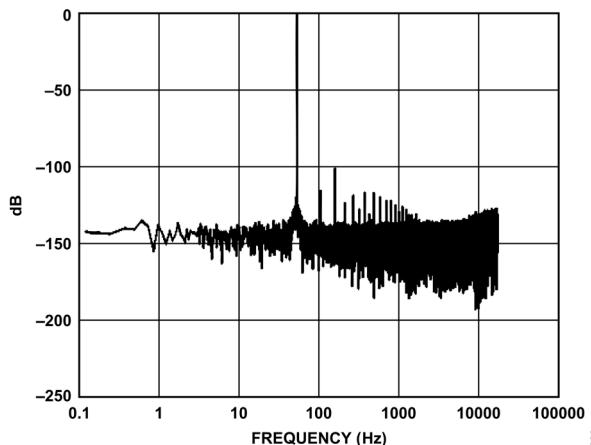

図 31. 50Hz 入力、FFT、32kSPS、DSP sinc 補償、

デジタル LPF、2 のデシメーションを有効化

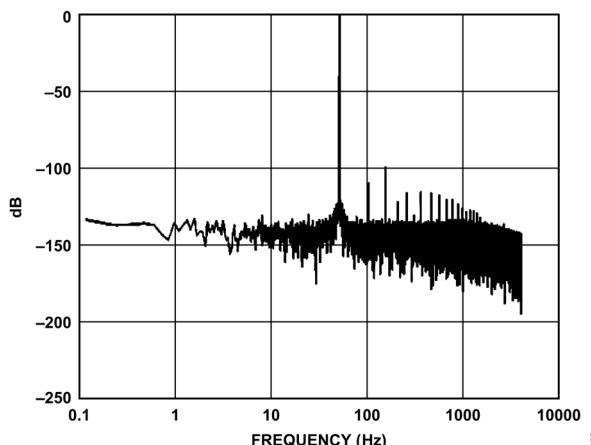

図 32. 50Hz 入力、FFT、8kSPS、sinc3 のみ

図 33. 50Hz 入力、FFT、8kSPS、DSP sinc 補償、

デジタル LPF、2 のデシメーションを有効化

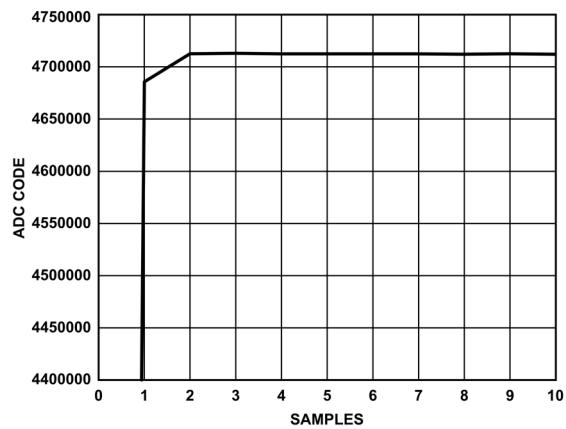

図 34. サンプル数の特定のゲイン誤差への収束、リセットから

CCM、 $f_{XTALIN} = 16.384\text{MHz}$ 、ゲイン=1x、1VDC 入力

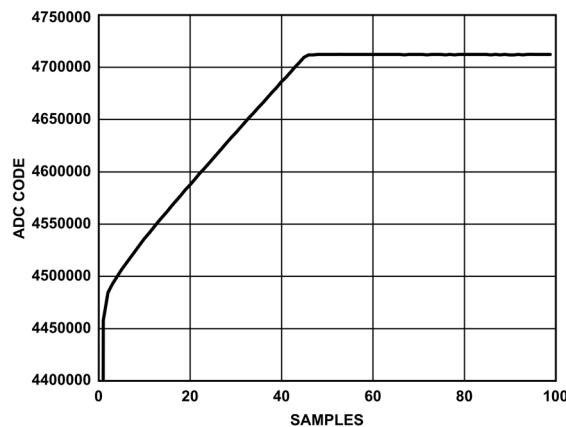

図 35. サンプル数の特定のゲイン誤差への収束、TDM から

CCM、 $f_{XTALIN} = 16.384\text{MHz}$ 、ゲイン=1x、1VDC 入力

## テスト回路

047

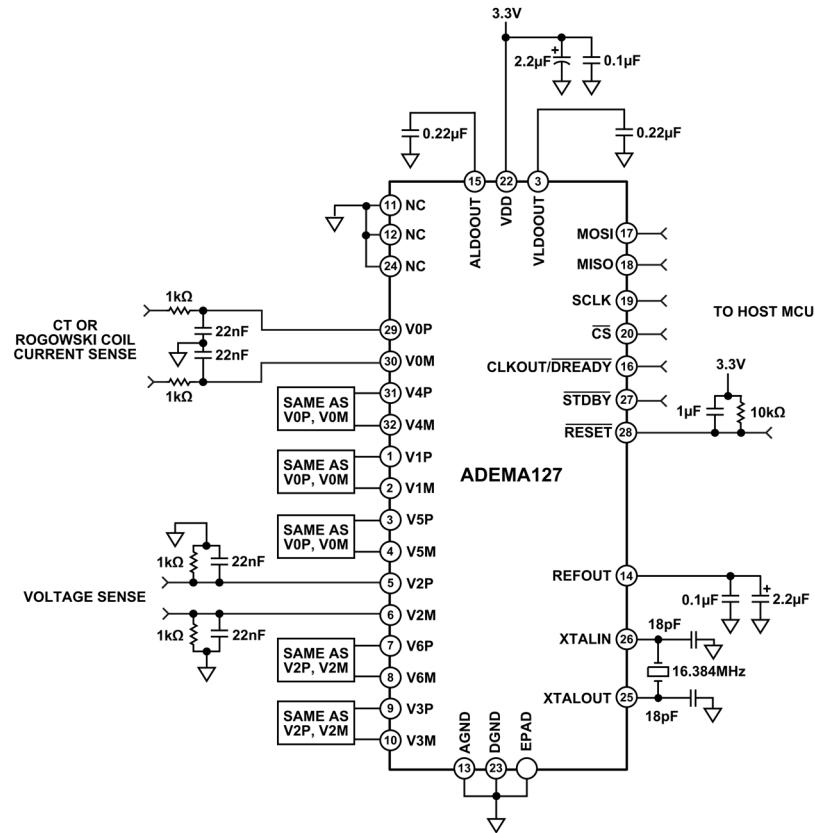

図 36. ADEMA127 のテスト回路、3 相の電圧および電流

## 用語の定義

### クロストーク

クロストークの測定は、1つのチャンネルを接地し、他のすべてのチャンネルにフルスケールの 50Hz 信号または 60Hz 信号を加えることによって行います。クロストークは、接地された ADC 出力値と、その ADC フルスケール出力値の比です。ADC 出力は 100 秒間取得されます。クロストークの単位はデシベルです。

### 差動入力インピーダンス (DC)

差動入力インピーダンスは、VxP と VxM のペア間のインピーダンスを表します。その値は、表 2 の差動入力インピーダンス仕様に示すように、ADC\_GAIN\_CHx のゲイン選択に応じて変化します。

### ADC オフセット誤差

ADC オフセット誤差は、両方の入力を AGND に接続した状態で測定した ADC 出力コードの平均と、理想 ADC 出力コード 0 の差です。ADC オフセットの単位は、 $\mu\text{V}$  です。

### 温度に対する ADC オフセット・ドリフト

ADC オフセット・ドリフトは、温度に対するオフセットの変化量です。オフセット値を  $-40^\circ\text{C}$ 、 $+25^\circ\text{C}$ 、 $+125^\circ\text{C}$  で測定し、次式に従って温度に対するオフセット・ドリフトを計算します。

$$\text{Drift} = \max\left(\left|\frac{\text{Offset}(-40^\circ\text{C}) - \text{Offset}(+25^\circ\text{C})}{(-40^\circ\text{C} - +25^\circ\text{C})}\right|, \left|\frac{\text{Offset}(+125^\circ\text{C}) - \text{Offset}(+25^\circ\text{C})}{(+125^\circ\text{C} - +25^\circ\text{C})}\right|\right) \quad (1)$$

オフセット・ドリフトの単位は  $\text{nV}/^\circ\text{C}$  です。

### ADC ゲイン誤差

ADC のゲイン誤差は、外部電圧リファレンスに 1.25V を使用したときの、測定 ADC 出力コード（からオフセットを引いた値）と理想出力コードの差を表します。この差はコード理想値のパーセンテージとして表されます。1つのチャンネルの総合ゲイン誤差を表します。

### 温度に対する ADC ゲイン・ドリフト

この温度係数には、外部電圧リファレンスに 1.25V を使用した場合の ADC ゲインの温度に対する変化が含まれます。この係数は、1つの電流または電圧チャンネルの総合温度係数を表します。1.25V の外部電圧リファレンス使用時は、 $-40^\circ\text{C}$ 、 $+25^\circ\text{C}$ 、 $+125^\circ\text{C}$  における ADC ゲインを測定し、次式に従って温度係数を計算します。

$$\text{Drift} = \max\left(\left|\frac{\text{Gain}(-40^\circ\text{C}) - \text{Gain}(+25^\circ\text{C})}{\text{Gain}(+25^\circ\text{C}) \times (-40^\circ\text{C} - +25^\circ\text{C})}\right|, \left|\frac{\text{Gain}(+125^\circ\text{C}) - \text{Gain}(+25^\circ\text{C})}{\text{Gain}(+25^\circ\text{C}) \times (+125^\circ\text{C} - +25^\circ\text{C})}\right|\right) \quad (2)$$

ゲイン・ドリフトの単位は  $\text{ppm}/^\circ\text{C}$  です。

### AC 電源電圧変動除去比 (PSRR)

AC PSRR は、DC 電源電圧を公称値 ( $V_{\text{NOM}}$ ) にして AC 変調を行い、入力を接地した場合の測定誤差を、指示値に対するパーセンテージとして定量化するものです。AC PSRR を測定するには、公称電源電圧 3.3V ( $V_1$ ) で 20 秒間サンプルを収集し、別の AC 信号 (50Hz で 120mV<sub>rms</sub>) を電源に加えて、2 セット目 ( $V_2$ ) を収集します。以上より、PSRR は、 $\text{PSRR} = 20\log_{10}(V_2/V_1)$  で表されます。

### SN 比 (SNR)

SN 比は、50Hz 信号を入力することによって計算され、また、サンプルは 8 秒間取得されます。表 1 に ADC 出力帯域幅 (-3dB) として示されている帯域幅までの各周波数の振幅が計算されます。SN 比を決定するには、50Hz での信号を他のすべての周波数における電力の合計と比較し、その高調波からの電力を除去します。SN 比の値はデシベル単位で表されます。

### 信号ノイズ + 歪み (SINAD)

SINAD は、50Hz 信号を入力することによって計算され、また、サンプルは 8 秒間取得されます。SINAD を決定するには、50Hz での信号を他のすべての周波数における電力の合計と比較します。SINAD の単位はデシベル (dB) です。

### 全高調波歪み (THD)

THD は、50Hz 信号を入力することによって計算され、また、サンプルは 8 秒間にわたり取得されます。THD を決定するには、この帯域幅までの 50Hz 高調波の振幅の 2 乗和平方根を取ります。THD の単位はデシベル (dB) です。

### スプリアスフリー・ダイナミック・レンジ (SFDR)

SFDR は、50Hz 信号を入力することによって計算され、また、サンプルは 8 秒間にわたり取得されます。SFDR を決定するには、50Hz の高調波ではない最大信号の振幅を記録します。SFDR の単位はデシベル (dB) です。

### ADC パスバンド平坦性

ADC の出力が 50Hz のリファレンス信号入力の 0.1dB 以内に収まる帯域幅。

### ADC 出力帯域幅

ADC 出力帯域幅は -3dB 以下の帯域幅で、sinc3 のデジタル・フィルタリングおよび DSP 機能を有効化することによって得られます。

## 動作原理

正確な測定、リアルタイム・モニタリング、電力量の流れの包括的な管理は、配電ネットワーク全体にわたって必要とされます。ADEMA124 と ADEMA127 は、特に電力量計に最適な機能を持つよう設計された、4 チャンネルおよび 7 チャンネルの同時サンプリング ADC です。すべての ADC チャンネルに、完全差動入力、同一のダイナミック・レンジ、プログラマブル・ゲイン、独立した 24 ビット・シグマ・デルタ ADC が備わっています。ADEMA124/ADEMA127 の各 ADC チャンネルは、シャントおよびカレント・トランス (CT) を直接サポートでき、デジタル積分器、HPF、ロゴスキュー・センサーを内蔵しています。

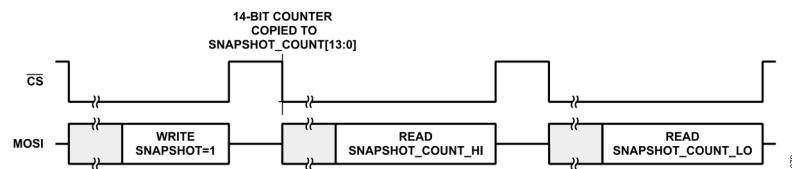

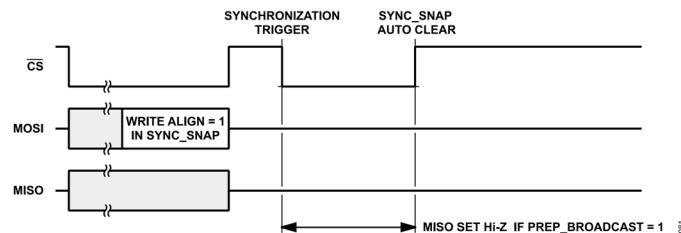

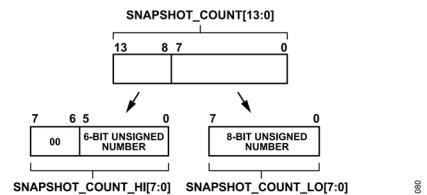

ADEMA124/ADEMA127 ADC は、電力量計システムにおける、柔軟でスケーラブルな部品です。デイジーチェーン通信インターフェースによってシステムのアーキテクチャが簡素化され、また、このインターフェースによってマイクロコントローラが一連の ADEMA124/ADEMA127 を、それらが 1 つのデバイスであるかのように処理できます。複数の ADC の同期は簡素化され、各 ADC の SYNC\_SNAP レジスタへの 1 回の SPI 書込みとそれに続く CS ピンの同時アサートを行うだけで済みます。内蔵のゲイン、位相、オフセット補償機能やその他の DSP 機能によって、ホスト・マイクロコントローラの処理リソースが低減され、また、処理された ADC 波形サンプルが直ちにシステムで使用できるようになります。

DSP のデシメーション率 2 の機能によってより広い帯域幅が可能となり、高調波を高い信頼性で測定できるようになります。そのため、再生可能エネルギー・リソースに対する優れた電力品質分析、グリッドを介したより効率的な配電、デバイスの長寿命化が実現できます。

## ゲインおよびオフセットの補正

ゲインおよびオフセットの補正是、計量システムにおいて、広く必要とされるものです。ADEMA124/ADEMA127 は、各 ADC チャンネルに対しゲインおよびオフセット・キャリブレーションのビット・フィールドを備えているため、ホスト・マイクロコントローラに必要となる処理負荷を軽減します。

## クイック・スタート・ガイド

ADEMA124/ADEMA127 に 3.3V の電源とクロックが供給されると、ADC は直ちに図 38 に示すデフォルト設定に従ってサンプルの生成を開始します。ADEMA124/ADEMA127 との通信はすべて、SPI ポートを介して行われます。詳細については、[高速スタートアップ](#) のセクションを参照してください。

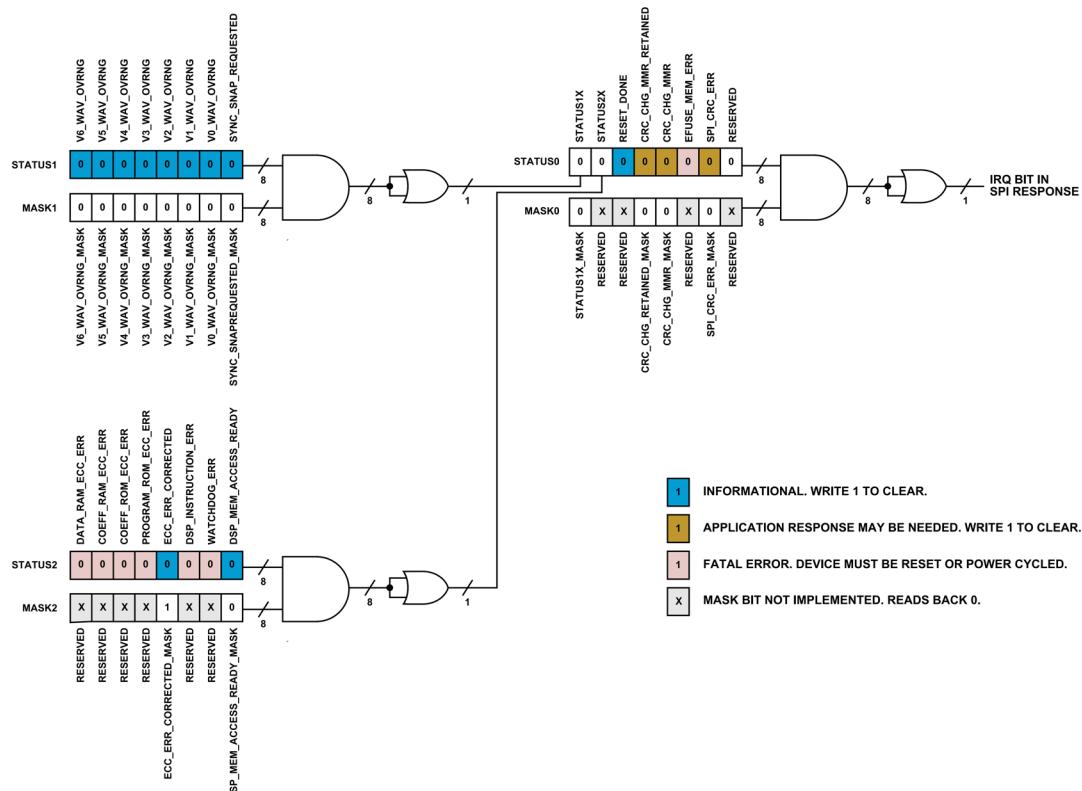

代表的な使用事例では、有効な電源とクロックを供給し、データバスを設定し、その設定を書込みロックし、その後 DREADY ピンがローに遷移するのに呼応して ADC 波形データを収集します。ADC 波形サンプルはロング・フォーマットの SPI 操作で取得するのが効率的です。CRC チェックサム、STATUS0 レジスタ、STATUS1 レジスタが、すべてのチャンネルからロング・フォーマット SPI 応答で ADC 波形データと共に返されます。推奨する繰り返しコマンドは、STATUS2 レジスタのロング・フォーマット SPI 読出しです。それによって、ADEMA124/ADEMA127 のすべてのステータス情報がマイクロコントローラへ継続的に返されます。

DATAPATH\_CONFIG\_LOCK および DSP\_MEM\_ACCESS\_REQ には複数の機能がありますが、どちらのビットも、デフォルトでその空間を保護する SPI 書込みロックです。これらのビットの機能の詳細は、[設定ロックおよびアクセス・ビット](#) のセクションで説明します。ADEMA124/ADEMA127 には、SCRATCH と呼ばれる 8 ビットのレジスタがあります。これは、書き込み保護がされておらず、テスト SPI 書込みやテスト SPI 読出しに使用できます。[通信デバッグ機能](#) のセクションで説明するように、24 ビット ADC 波形サンプルを検証するためのデバッグ機能があり、波形はシステムによって高い信頼度で取得されます。

DSP RAM のすべての値は、MMR になんらかの設定が行われると上書きされます。ADEMA124/ADEMA127 を設定するには、MMR のアドレスを DSP RAM のアドレスよりも前に設定する必要があります。DSP RAM に読み込まれるすべてのデフォルト DSP フィルタ係数は、通常 16.384MHz の fXTALIN に基づいています。この DSP 係数は変更できます。

ロック・キーを WR\_LOCK に書き込むことで、ADEMA124/ADEMA127 設定レジスタへの意図しない SPI 書込みが行われるのを防ぐことができます。設定が変更されると STATUS0 の CRC\_CHG ビットがハイにセットされ、マイクロコントローラによってモニタできます。

## アプリケーション情報

### スタートアップのシーケンスおよびタイミング 高速スタートアップ

ADEMA124/ADEMA127 は、有効な電源が与えられると直ちに、サンプリングと波形データ生成を開始します。ADC は、有効なクロック入力信号が供給されるか、外付けクリスタルが用いられ、**RESET**ピンと**STDBY**ピンのどちらもアサートされていない必要があります。

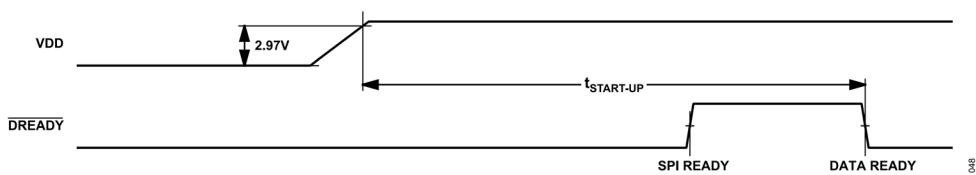

スタートアップを図 37 に示します。高速スタートアップ時間は、VDD 電源が最小有効供給レベルに達してから最初のデータ・サンプルが出来可能になるまでの時間として定義されます。**DREADY**ピンのローからハイへの最初の遷移は、SPI ポートが通信に使用できることを示します。**DREADY**ピンのハイからローへの最初の遷移は、最初の ADC サンプル・セットが出力可

能になったことを示します。最初の SPI 読出しは、どの ADC 波形データでも 0x00 を返します。最初の ADC サンプル・セットが必要な場合、**DREADY**ピンの最初の立上がりエッジで SPI ポートを読み出してください。その後、ADC サンプルの最初のセットは、**DREADY**ピンのハイからローへの最初の変換時に出力され読み出せます。データ・セットからの最初の 2 つの ADC 波形は、デシメーション係数が 64 で、レイテンシのより小さい sinc1 フィルタを通過します。

ADEMA124/ADEMA127 は、外部クロックを供給した場合、VDD が 90% になったときから 0.5ms 以内 ( $t_{START-UP}$ ) に有効な ADC サンプルを生成します。有効な ADC サンプルは 15ms で生成されますが、このとき、外部クリスタルからクロックを発生するために、ADEMA124/ADEMA127 は水晶発振器回路を最初に始動しなくてはなりません。

図 37. 高速スタートアップのタイミング

## アプリケーション情報

### 動作モード

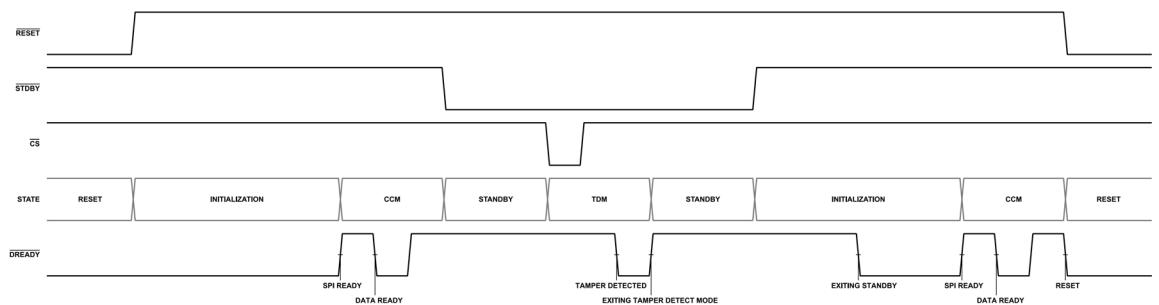

ADEMA124/ADEMA127 には、連続変換モード（CCM）、スタンバイ・モード、改ざん検知モード（TDM）の 3 つの動作モードがあります。CCM は、パワーアップ後またはリセット後に ADEMA124/ADEMA127 が入るデフォルト・モードです。SPI 通信はアクティブになり、ADC サンプルは CCM で設定されたサンプリング・レートで出力可能です。CCM の詳細については、[連続変換モード](#)のセクションを参照してください。

**STDBY** ピンをローにセットすることによって、CCM からスタンバイ・モードに入ることができます。このモードでは、SPI 通信は利用できませんが、ADEMA124/ADEMA127 の消費電力は大幅に低減します。スタンバイ・モードの詳細については、[スタンバイ・モード](#)のセクションを参照してください。

TDM には、スタンバイ・モードからのみ入ることができます。TDM は、CCM にフルパワーを投じることなく、設定可能閾値を超える信号の存在をチェックする手段を提供します。TDM の詳細については、[改ざん検知モード](#)のセクションを参照してください。

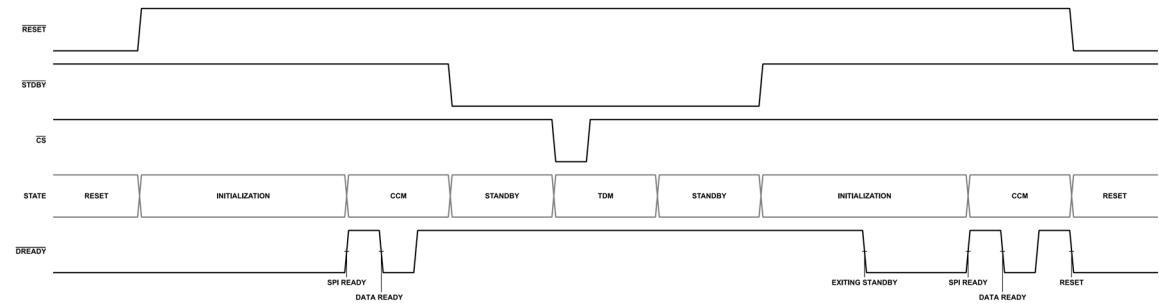

**DREADY** ピンの 2 つの動作モードを、それぞれ図 38 と図 39 に示します。ノイズの多い環境での EMC 対策として **DREADY** ピンの配線パターンに抵抗を配置する必要がある場合は、プルダウン抵抗を使用してください。**DREADY** ピンにプルアップ抵抗は配置しないでください。

図 38. **DREADY** ピンのデフォルト動作 (**TDM\_DREADYB\_EN** = 1)

図 39. **DREADY** ピンの動作 (**TDM\_DREADYB\_EN** = 0)

## アプリケーション情報

### 連続変換モード

VDD 電源が有効であり、RESET ピンと STDBY ピンのどちらもアサートされていない場合、CCM が、ADEMA124/ADEMA127 のデフォルトの動作モードです。

SPI ポートは CCM でのみ有効です。図 38 および図 39 に示すように、ADEMA124/ADEMA127 は、CCM に入ったこと SPI ポートが使用可能であることを DREADY ピンの最初の立上がりエッジで通知します。

### スタンバイ・モード

スタンバイ・モードは低消費電力のアイドル状態です。STDBY ピンをローにセットすることで、ADEMA124/ADEMA127 は CCM からスタンバイ・モードに入ります。スタンバイ・モードを終了するには STDBY ピンをハイにセットします。

ADEMA124/ADEMA127 がスタンバイ・モードになっている間、SPI ポートは使用できません。ADEMA124/ADEMA127 がスタンバイ・モードかどうかによらず、表 27 に示すレジスタの設定はすべて、保持されます。表 28 に示すレジスタは、スタンバイ・モードの終了時にデフォルト値にリセットされ、再設定が必要になります。

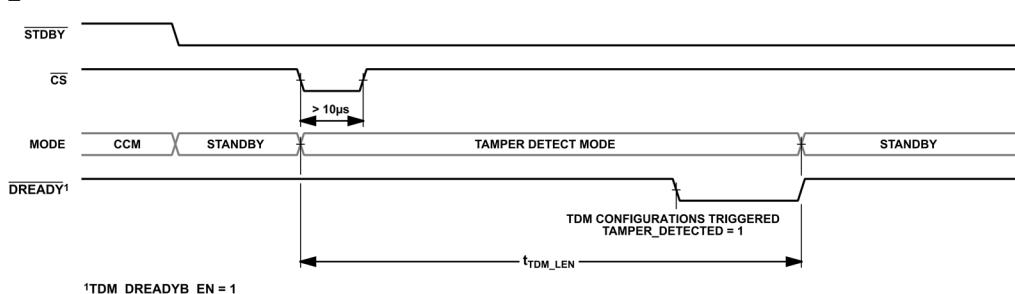

### 改ざん検知モード

TDM は、システムが著しく低いパワー・バジェットの下で動作している間の負荷電流の検出を可能にします。ADC\_PD レジスタでアクティブに設定された ADC チャンネルは、ADEMA124/ADEMA127 が TDM になっている間、設定可能デジタル入力として動作します。設定された条件が満たされると、TAMPER\_DETECTED ビット・フィールドがセットされ、オプションで DREADY ピンを用いてシステムに割込みを送信することができます。

TDM サイクルの継続時間は TDM\_LEN ビット・フィールドで設定されます。TDM では、ADEMA124/ADEMA127 のサンプル・レートは 7.227kS/s に固定されます。TDM サイクルの間、サンプル・クロックは内部で生成されます。クリスタルや外部クロックの信号は無視されます。TDM では外部電圧リファレンスは使用しないでください。

入力閾値は、12 ビットの TDM\_THRSH ビット・フィールドで設定されます。TDM\_THRSH の値は、11 ビット左にシフトされ、

24 ビットの ADC データ値の絶対値と比較されます。TDM\_THRSH の設定値は全チャンネルで共有され、絶対検出レベルを設定します。入力閾値を超えるサンプルがカウントされ、連続的に TDM\_NUM 設定値と比較されます。各チャンネルは、入力閾値を超える固有のサンプル数を保持しており、TDM\_NUM 設定値に合致すると内部フラグをセットします。これらのフラグは、TDM\_ALLCH ビットの設定に従って論理 AND または論理 OR にルーティングされ、改ざん検知をトリガします。

改ざん検知は常に TAMPER\_DETECTED ビットに書き込まれます。この設定値は、ビットが SPI 書込みによってクリアされるか、ADEMA124/ADEMA127 がリセットされるまで継続されます。TDM\_DREADYB\_EN ビットは、図 40 に示すように、ADEMA124/ADEMA127 が DREADY ピンをローにセットすることによって同時にシステムに通知するよう設定します。改ざん検知が最後のサンプルでトリガされると、DREADY ピンは 6μs 以上の間ローを保持し、TDM サイクルの最後にハイに遷移します。

ADEMA124/ADEMA127 は、スタンバイ・モードからのみ TDM サイクルに入ります。TDM の設定は、ADEMA124/ADEMA127 がスタンバイ・モードになる前に完了しておく必要があります。STDBY ピンがローになっている状態で、CS ピンを 10μs 以上アサートすると TDM サイクルへの移行がトリガされます。

ADEMA124/ADEMA127 が TDM サイクルを終了したとき、CS ピンと STDBY ピンのどちらもローのままである場合、新しい TDM サイクルが開始されます。新しい TDM サイクルは、スタンバイ・モードの間に新たに CS をアサートすることによっても開始できます。STDBY ピンの状態、CS ピンの状態、あるいは改ざんが検知されたかどうかに関わらず、TDM サイクルはその全体が完了するまで続行されます。

ADC\_PD、TDM\_LEN、TDM\_THRSH、TDM\_NUM、TDM\_ALLCH の各ビット・フィールドの設定値を表 29 に示します。

TDM では、外付けの REFOUT コンデンサは放電されます。図 35 に、ADEMA124/ADEMA127 が TDM サイクルを終了した後直ちに CCM に移行する場合の、充電中の REFOUT コンデンサの様子および指定されたゲイン精度への収束の様子を示します。

図 40. TDM への移行とイベント検出

## アプリケーション情報

### ソフトウェア・リセット

SWRST レジスタは、ソフトウェア・リセット機能を管理します。このレジスタが 0xD6 のソフトウェア・リセット・コマンド値にセットされている場合、ADEMA124/ADEMA127 はソフトウェア・リセット状態になります。この状態では、すべてのレジスタがデフォルト値にリセットされます。ソフトウェア・リセットが終了すると、SWRST レジスタは自動的にクリアされ、STATUS0 レジスタの RESET\_DONE ビットがセットされます。WR\_LOCK レジスタのロック・キーがセットされている場合、SWRST レジスタは書き込み保護されています。ソフトウェア・リセットを開始する前にまずこのレジスタのロックを解除してください。WR\_LOCK の詳細については、[完全設定ロック](#)のセクションを参照してください。

SPI ポートが準備できている（レディになっている）ことが DREADY ピンによって示されるまで、SPI コマンドを書き込まないでください。SPI レディを [図 38](#) に示します。ソフトウェア・リセット処理中に後続の SPI コマンドを開始しようとすると、SPI トランザクションに問題が生じます。ADEMA124/ADEMA127 では、制御ブロック、レギュレータ、リファレンスはソフトウェア・リセットの影響を受けません。

ソフトウェア・リセット後、[スタートアップのシーケンスおよびタイミング](#)のセクションに示した手順の 1 つを実行して ADEMA124/ADEMA127 を初期化する必要があります。リセットされると、デフォルトの保持 MMR および MMR 値が復元されます。DSP フィルタが有効化され DATAPATH\_CONFIG\_LOCK ビットがサイクル動作している場合、DSP RAM の値はデフォルト値に再初期化されます。

### ハードウェア・リセット

RESET ピンがローになると、ADEMA124/ADEMA127 はリセット状態に移行します。デバイスがリセット状態を終了すると、保持 MMR および MMR レジスタはすべて、デフォルト値に初期化されます。DSP フィルタが有効化されると、DSP RAM 値が初期化されます。

## アプリケーション情報

### SPI 互換通信

SPI ポートは、SCLK、MOSI、MISO、 $\overline{CS}$  の各ピン、および一般的には ADC 波形データを取得するために呼び出す DREADY ピンで構成されています。すべての設定と ADC 波形データ取得動作は、SPI ポートを通じて行われます。

ADEMA124/ADEMA127 は、SPI モード 3、つまり、CPOL = 1 および CPHA = 1 でのみ動作します。すべてのデータ転送動作は、SCLK ピンにルーティングされるシリアル・クロック信号に同期します。SPI ポートがサポートするシリアル・クロック周波数の最大値および最小値は、表 4 に示す SCLK 周波数  $f_{SCLK}$  のパラメータで仕様規定されています。

ADEMA124/ADEMA127 の SPI ポートとの間で行われるデータ伝送の完全性は、双方用 CRC によって保護されます。ADEMA124/ADEMA127 に送信されるコマンドは常に 32 ビットであり、8 ビットの CRC が含まれます。受信 SPI コマンドの CRC がそのコマンドに対し計算した値と一致しない限り、コマンドは実行されません。コマンド応答は、次の SPI フレームで返され、その応答から計算された 16 ビットの CRC で終了します。8 ビット CRC が一致しない場合にはアラートも含まれます。通信エラー検出スキームはデフォルトで有効化されていますが、無効化することも無視することもできます。CRC の計算および使用法の詳細については、CRC 保護のセクションを参照してください。

インターフェースが柔軟であるため、このデバイスは、個別対応のセクションで示すようにマイクロコントローラに接続することも、デイジーチェーンのセクションで示すようにデイジーチェーンで接続することもできます。デイジーチェーン構成では、複数のデバイスをマイクロコントローラによって 1 つのデバイスのように処理できます。各 ADEMA124/ADEMA127 デバイスが個別対応されているか、デイジーチェーンの 1 メンバーとなっているかを示すのに必要な設定はありません。

DREADY ピンは、ADEMA124/ADEMA127 とマイクロコントローラとの間の効率的な SPI 通信を可能にします。パワーアップ時、DREADY ピンの最初の立上がりエッジは、SPI ポートに

SPI コマンドの受信準備ができていることを示します。その後、DREADY の立下がりエッジで、マイクロコントローラによって取得される新たな ADC サンプル・セットを出力できることが示されます。標準的な 16.384MHz のクロック周波数で動作する場合、DREADY は 15ns の間、ローのままになります。DREADY ピンのデフォルト動作を図 39 に示します。

$\overline{CS}$  ピンがハイからローに遷移すると、ADC 波形データを含む SPI 応答パケットは、バッファにラッピングされ、SCLK に合わせてシフト・アウトされます。DREADY ピンが次にハイからローへ遷移するまでに転送が開始されていない ADC 波形データは、上書きされます。

### コマンドおよび応答

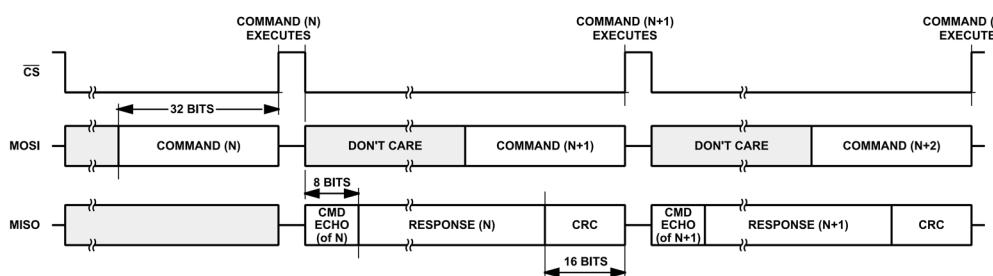

ADEMA124/ADEMA127 の通信スキームは、全 2 重通信が可能です。図 41 に示すように、以前のコマンドに対する応答がシフト・アウトされている間に、新しいコマンドが ADEMA124/ADEMA127 デバイスにシフト・インされます。最初に SPI フレームの最上位ビットが ADEMA124/ADEMA127 MOSI ピンで受信されます。

$\overline{CS}$  ピンがローからハイに遷移すると SPI コマンドが実行されます。SPI コマンド・ビット・フィールドは、 $\overline{CS}$  ピンの遷移前に受信した最後の 32 ビットとして解釈されます。SPI コマンドの構成要素のビット・フィールドを図 42 に、詳細を表 8 に示します。

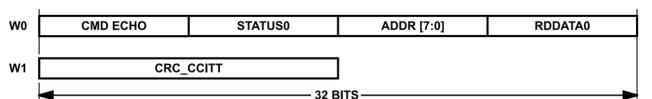

SPI コマンド応答は、直後の SPI フレームで送信されます。SPI コマンド・エコーのビット・フィールドは、各応答の最初のバイトを補うものです。この 8 ビットのコマンド・エコーは、その前のコマンドが正しく解釈されたことを確認するために使用できます。SPI コマンド・エコーの構成要素のビット・フィールドを図 43 に、詳細を表 9 に示します。

その他のコマンド応答は、ADEMA124/ADEMA127 に発せられた個々のコマンドに応じて異なります。表 10 にコマンド応答をまとめます。すべての応答フレームは、応答フレームから計算された 16 ビットの CRC で終了します。

図 41. シングル・デバイスとの全 2 重通信

652

図 42. SPI コマンドのビット・フィールド

653

図 43. SPI コマンド・エコーのビット・フィールド

## アプリケーション情報

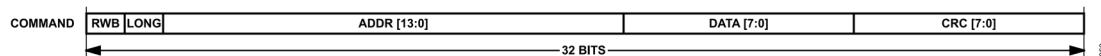

表 8. SPI コマンドのビット・フィールド

| ビット・フィールド位置 | ビット・フィールド名 | 説明                                                                                                               |

|-------------|------------|------------------------------------------------------------------------------------------------------------------|

| 31          | RWB        | SPI 読出し動作を実行する場合、このビットを 1 にセットします。<br>SPI 書込み動作を実行する場合は、このビットを 0 にクリアします。                                        |

| 30          | LONG       | ロング・フレーム構造の場合は、このビットを 1 にセットします。<br>ショート・フレーム構造の場合は、このビットを 0 にクリアします。デイジーチェーン接続されたデバイスに対しては、ショート・フレームはサポートされません。 |

| [29:16]     | ADDR[13:0] | 読み出しまだ書込みされるレジスタの 14 ビットのアドレス。                                                                                   |

| [15:8]      | DATA[7:0]  | 書込み動作が実行された場合のデータ・ペイロード。                                                                                         |

| [7:0]       | CRC[7:0]   | コマンド・フレーム・コンテンツの 8 ビット CRC による保護。詳細については、 <a href="#">SPI コマンドの CRC のセクション</a> を参照してください。                        |

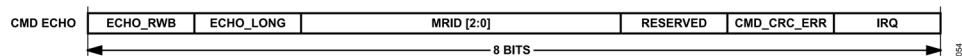

表 9. SPI コマンド・エコーのビット・フィールド

| ビット・フィールド位置 | ビット・フィールド名  | 説明                                                                                                                                                                    |

|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7           | ECHO_RWB    | 最後に発せられたコマンドのエコー。SPI 読出し動作の場合は 1。<br>SPI 書込み動作の場合は 0。                                                                                                                 |

| 6           | ECHO_LONG   | 要求されたコマンドのエコーのフォーマット。<br>ロング・フォーマットの場合は 1。<br>ショート・フォーマットの場合は 0。                                                                                                      |

| [5:3]       | MRID[2:0]   | 要求されたアドレスのあるメモリ領域を示します。<br>レジスタ・マップ (0x0000~0x00FF) の場合は 000。<br>DSP RAM (0x0400~0x07FF) の場合は 001。<br>010 予約済み。<br>011 予約済み。<br>100 予約済み。<br>101 予約済み。<br>111 予約済み。   |

| 2           | RSRVD       | 予約済み。このビットは 0 にセットされます。                                                                                                                                               |

| 1           | CMD_CRC_ERR | 対応するコマンド・フレームに対する CRC チェック。<br>0 は、コマンド・フレーム CRC チェックに合格したことを示します。<br>1 は、コマンド・フレーム CRC チェックに不合格であることを示します。詳細については、 <a href="#">SPI コマンド応答の CRC のセクション</a> を参照してください。 |

| 0           | IRQ         | コマンド応答割込みビット。<br>0 は、生起された割込みがないことを示します。<br>1 は、マスク不能な割込みまたは設定された割込みが生起されたことを示します。詳細については、 <a href="#">ステータス・レジスタおよび IRQ のセクション</a> を参照してください。                        |

表 10. 応答フレームの種類

| 応答の種類             | 説明                                                                                                                          |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| デフォルト応答           | PoR リリースと MCLK オンの間で送信。                                                                                                     |

| ロング読出し応答          | デバイスの全 ADC チャンネルの 24 ビット波形サンプルに加え、アドレスおよびアドレス+1 のレジスタのリードバック値。詳細については、 <a href="#">ロング・フォーマット動作</a> のセクションを参照してください。        |

| ロング書き込み応答         | デバイスの全 ADC チャンネルの 24 ビット波形サンプルに加え、書き込みアドレスのエコーおよびそのアドレスのレジスタのリードバック値。詳細については、 <a href="#">ロング・フォーマット動作</a> のセクションを参照してください。 |

| ショート読出し応答         | アドレスおよびアドレス+1 のレジスタのリードバック値。詳細については、 <a href="#">ショート・フォーマット動作</a> のセクションを参照してください。                                         |

| チャンネル・データのショート読出し | 選択したチャンネルからの 24 ビット波形サンプル。詳細については、 <a href="#">ショート・フォーマット動作</a> のセクションを参照してください。                                           |

| ショート書き込み応答        | 書き込みアドレスのエコーおよびそのレジスタのリードバック値。詳細については、 <a href="#">ショート・フォーマット動作</a> のセクションを参照してください。                                       |

| コマンド・エラー応答        | コマンド・フレームが無効であることが判明した場合に送信。詳細については、 <a href="#">SPI コマンド・エラー応答フレーム</a> のセクションを参照してください。                                    |

## アプリケーション情報

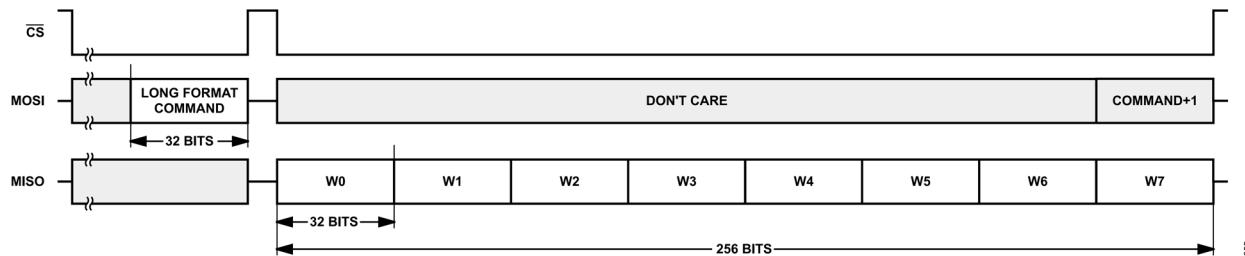

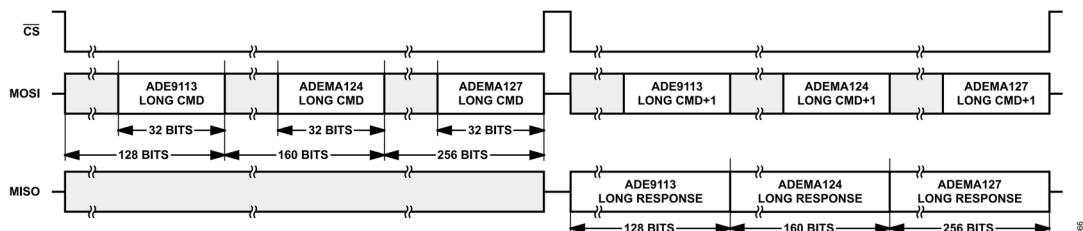

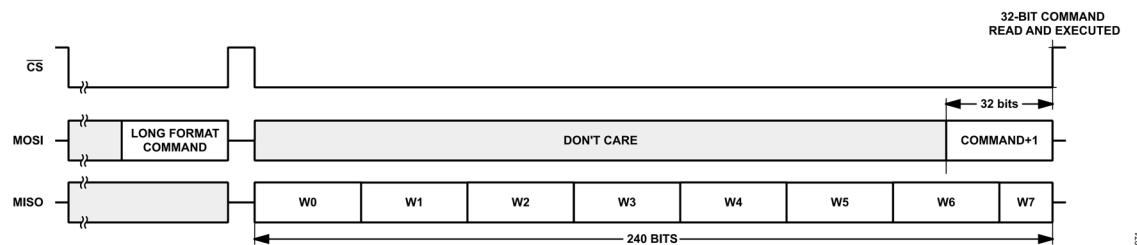

### ロング・フォーマット動作

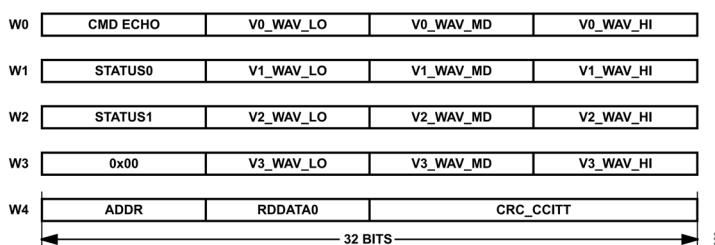

すべてのロング・フォーマット応答には、すべての ADC チャンネルからの 24 ビット波形データ・レジスタと、STATUS0 レジスタおよび STATUS1 レジスタの内容が含まれています。ADC 波形データは、24 ビットの 2 の補数表示です。ADC 波形レジスタからのバイトが、リトルエンディアン・フォーマットで Vx\_WAV\_LO、Vx\_WAV\_MD、Vx\_WAV\_HI に伝送されます。標準的な CCM 動作には、STATUS2 のロング・フォーマット読出しが推奨 SPI トランザクションです。すべての ADC データとステータス情報が返されるためです。

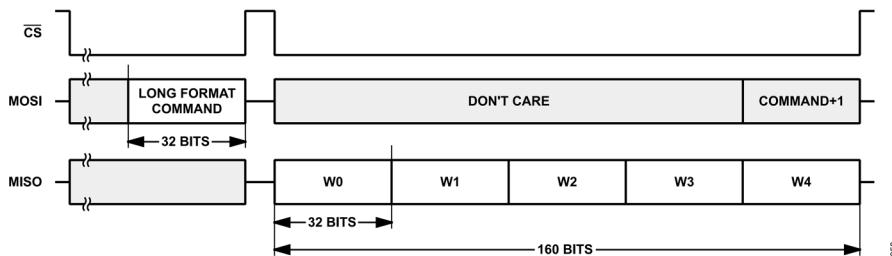

ADEMA127 は、256 ビットのロング・フォーマット応答が可能です。ADEMA124 のロング・フォーマット応答は 160 ビットです。デイジーチェーン接続された ADEMA124/ADEMA127 デバイスは、ロング・フォーマット動作でのみ通信する必要があります。

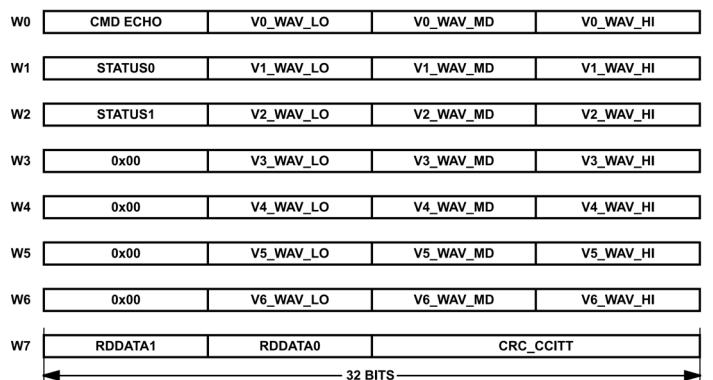

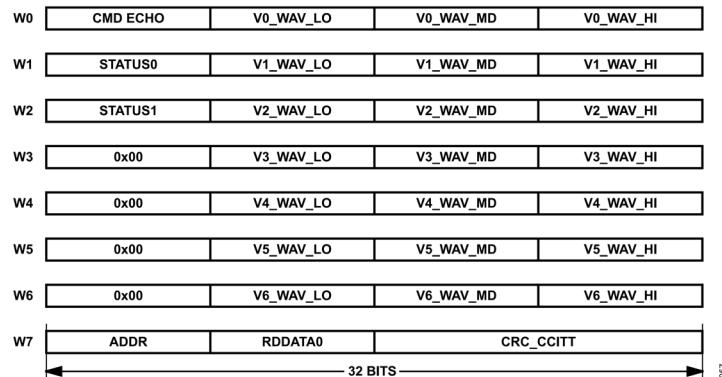

ADEMA127 のロング読み出し応答フレームの構造を以下の図 45 に示します。ADEMA127 のロング書き込み応答フレームの構造を図 46 に示します。

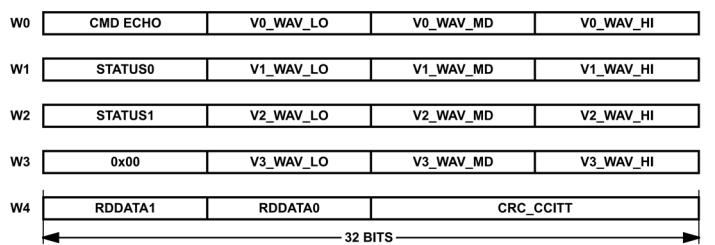

ADEMA124 のロング・フォーマット・コマンドおよび応答を図 47 に示します。ADEMA124 のロング読み出し応答フレームの構造を図 48 に示します。ADEMA124 のロング書き込み応答フレームの構造を図 49 に示します。

図 44. ADEMA127 のロング・フォーマット

図 45. ADEMA127 のロング・フォーマット読み出し応答パケット

図 46. ADEMA127 のロング・フォーマット書き込み応答パケット

## アプリケーション情報

表 11. ADEMA127 のロング・フォーマット応答のビット・フィールド

| Bit Field Location | Long Read Bit Field Name    | Long Write Bit Field Name   | Description                                                                  |

|--------------------|-----------------------------|-----------------------------|------------------------------------------------------------------------------|

| [255:248]          | CMD ECHO [7:0]              | CMD ECHO [7:0]              | For more details, see <a href="#">Figure 43 and Table 9</a> .                |

| [247:224]          | ADC V0 Waveform Data [23:0] | ADC V0 Waveform Data [23:0] |                                                                              |

| [223:216]          | STATUS0 [7:0]               | STATUS0 [7:0]               | For more details, see <a href="#">Table 30</a> .                             |

| [215:192]          | ADC V1 Waveform Data [23:0] | ADC V1 Waveform Data [23:0] |                                                                              |

| [191:184]          | STATUS1 [7:0]               | STATUS1 [7:0]               | For more details, see <a href="#">Table 30</a> .                             |

| [183:160]          | ADC V2 Waveform Data [23:0] | ADC V2 Waveform Data [23:0] |                                                                              |

| [159:152]          | RESERVED [7:0]              | RESERVED [7:0]              | 0x00 is transmitted.                                                         |

| [151:128]          | ADC V3 Waveform Data [23:0] | ADC V3 Waveform Data [23:0] |                                                                              |

| [127:120]          | RESERVED [7:0]              | RESERVED [7:0]              | 0x00 is transmitted.                                                         |

| [119:96]           | ADC V4 Waveform Data [23:0] | ADC V4 Waveform Data [23:0] |                                                                              |

| [95:88]            | RESERVED [7:0]              | RESERVED [7:0]              | 0x00 is transmitted.                                                         |

| [87:64]            | ADC V5 Waveform Data [23:0] | ADC V5 Waveform Data [23:0] |                                                                              |

| [63:56]            | RESERVED [7:0]              | RESERVED [7:0]              | 0x00 is transmitted.                                                         |

| [55:32]            | ADC V6 Waveform Data [23:0] | ADC V6 Waveform Data [23:0] |                                                                              |

| [31:24]            | RDDATA1 [7:0]               | -                           | Readback value at the requested address+1.                                   |

|                    | -                           | ADDR [7:0]                  | LSB of requested write address echoed back.                                  |

| [23:16]            | RDDATA0 [7:0]               | RDDATA0 [7:0]               | Readback value at the requested address.                                     |

| [15:0]             | CRC_CCITT [15:0]            | CRC_CCITT [15:0]            | For more details, see the <a href="#">SPI Command Response CRC section</a> . |

図 47. ADEMA124 のロング・フォーマット

図 48. ADEMA124 のロング・フォーマット読出し応答パケット

図 49. ADEMA124 のロング・フォーマット書き込み応答パケット

## アプリケーション情報

表 12. ADEMA124 のロング・フォーマット応答のビット・フィールド

| Bit Field Location | Long Read Bit Field Name    | Long Write Bit Field Name   | Description                                                                   |

|--------------------|-----------------------------|-----------------------------|-------------------------------------------------------------------------------|

| [159:152]          | CMD ECHO [7:0]              | CMD ECHO [7:0]              | For more details, see <a href="#">Figure 43</a> and <a href="#">Table 9</a> . |

| [151:128]          | ADC V0 Waveform Data [23:0] | ADC V0 Waveform Data [23:0] |                                                                               |

| [127:120]          | STATUS0 [7:0]               | STATUS0 [7:0]               | For more details, see <a href="#">Table 30</a> .                              |

| [119:96]           | ADC V1 Waveform Data [23:0] | ADC V1 Waveform Data [23:0] |                                                                               |

| [95:88]            | STATUS1 [7:0]               | STATUS1 [7:0]               | For more details, see <a href="#">Table 30</a> .                              |

| [87:64]            | ADC V2 Waveform Data [23:0] | ADC V2 Waveform Data [23:0] |                                                                               |

| [63:56]            | RESERVED [7:0]              | RESERVED [7:0]              | 0x00 is transmitted.                                                          |

| [55:32]            | ADC V3 Waveform Data [23:0] | ADC V3 Waveform Data [23:0] |                                                                               |

| [31:24]            | RDDATA1 [7:0]               | -                           |                                                                               |

|                    | -                           | ADDR [7:0]                  | LSB of requested write address echoed back.                                   |

| [23:16]            | RDDATA0 [7:0]               | RDDATA0 [7:0]               |                                                                               |

| [15:0]             | CRC_CCIT [15:0]             | CRC_CCIT [15:0]             | For more details, see the <a href="#">SPI Command Response CRC</a> section.   |

## アプリケーション情報

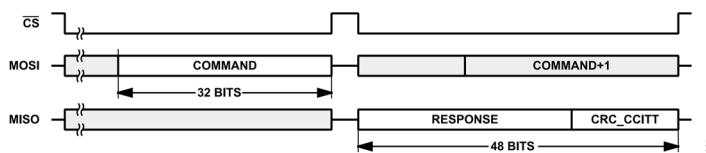

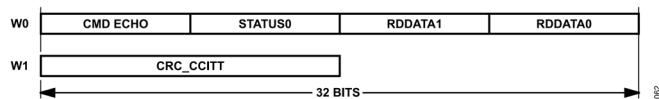

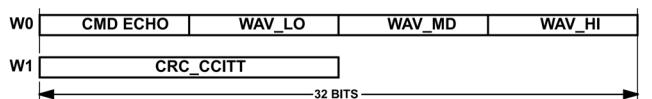

### ショート・フォーマット動作

ショート応答のフレームは、ADEMA124 と ADEMA127 のどちらのデバイスについても 48 ビットです。ショート・フレーム応答は、すべての ADC チャンネルからの ADC 波形データを伝搬するわけではなく、シングル・デバイスのデバイス設定やステータス・クエリをより迅速に行うために用いられます。

ショート・フォーマット動作は、[個別対応](#)のセクションに示すように、個別に対応するデバイスに対してのみ使用可能であり、デイジーチェーン接続のデバイスに対してはサポートしていません。

ショート書込み応答パケットに対する CRC\_CCITT は、ビット [47:16]について計算されます。

図 50. ショート・フォーマット

図 51. ショート読出し応答パケット

図 52. ADC 波形レジスタのショート読出し応答パケット

図 53. ショート書込み応答パケット

### SPI コマンド・エラー応答フレーム

ADEMA124/ADEMA127 が SPI コマンドに CRC ミスマッチがあることを検出した場合、コマンド・エラー応答フレームがその後のフレームで送信されます。コマンド・エラー応答はロング・フォーマット・フレームです。[図 43](#) および[表 9](#) に示すように、CRC 割込みビットがコマンド応答内にセットされます。

なお、次に要求された SPI フレームがショート・フォーマット・フレームの場合、マイクロコントローラは、ショート・フォーマット応答の受信を予想して、エラー応答を 48 ビットの断片に縮小する可能性があります。ショート・フォーマット応答でも、ロング・フォーマット応答でも、最初の 8 ビットは、コマンド・エコーであり、ここに CMD\_CRC\_ERR ビットが含まれます。CMD\_CRC\_ERR ビットがセットされている場合、ホストは、残りのパケットを破棄する必要があります。

## アプリケーション情報

### 通信デバッグ機能

ADEMA124/ADEMA127 には、専用の SCRATCH レジスタがあり、これを用いることでテスト書き込み動作およびテスト読み出し動作が可能です。ハードウェア・リセット、ソフトウェア・リセット、あるいはスタンバイ・モードへの移行によってデフォルト値にリセットされない限り、各レジスタの内容が、ADEMA124/ADEMA127 によって変更されることはありません。

ADEMA124/ADEMA127 には、ADC データの取得のデバッグに役立つ、スタティック・モードとカウント・モードの 2 つのモードがあります。スタティック・モードとカウント・モードは、CONFIG0 レジスタの STREAM\_DBG ビットに書き込みを行うことで有効化できます。これらのモードは、SPI ロング・フォーマットと SPI ショート・フォーマットのどちらの動作にも使用できます。

スタティック・モードが有効な場合、ADC 波形レジスタは、ADEMA124/ADEMA127 の DSP チャンネルによって更新されることはありません。ADC 波形レジスタは、SPI コマンドによって値が上書きされるまで、最後の ADC サンプルを保持します。このモードは、ホスト・ファームウェアによりデータ・ストリームから ADC サンプルが正しく引き出されていることを検証するのに用います。

ADC 波形レジスタに値を書き込んで保持するには、以下の手順を実行します。

1. STREAM\_DBG をスタティック・モードに設定します。

2. DREADYピンがローになるまで待機します。

3. 必要な値を ADC 波形データ・レジスタに書き込みます。

4. 設定されたサンプル・レートに従ってDREADYがアサートされます。

カウント・モードでは、ADC 波形レジスタをそのレジスタの最後の値からインクリメントし始めます。カウント・モードを用いるのは、直後の ADC サンプルがホスト・ファームウェアによってキャプチャされ、失われたり複製されたりしていないことを確認するためです。なお、連続的な波形を ADC 波形レジスタに書き込む場合、予期せぬインクリメントを防ぐために、DREADY信号に同期させるよう注意してください。

ADC 波形レジスタに値を書き込んでインクリメントを開始するには、以下の手順を実行します。

1. STREAM\_DBG をスタティック・モードに設定します。

2. DREADYピンがローになるまで待機します。

3. 必要な値を ADC 波形データ・レジスタに書き込みます。

4. STREAM\_DBG をカウント・モードに設定します。

5. 設定されたサンプル・レートに従ってDREADYがアサートされます。DREADYのアサートごとに、すべての ADC 波形レジスタは 1 ずつインクリメントします。

STREAM\_DBG を通常動作モードにするか ADEMA124/ADEMA127 をリセットして、デバッグ・モードを終了します。

表 13. STREAM\_DBG ビットの構成

| STREAM_DBG | Data Mode   |

|------------|-------------|

| 0b00       | Normal Mode |

| 0b01       | Static Mode |

| 0b10       | Count Mode  |

## アプリケーション情報

### デイジーチェーン

双方向のシリアル・ポート・インターフェース (SPI) は、デイジーチェーン接続に対応しており、必要なマイクロコントローラのピン数を減らしながら、すべてのレジスタにアクセスできます。SPIデイジーチェーン構成の場合、接続されているすべてのデバイスからのCS信号が共有されます。