# 45MHz～1218MHz、 CATVパワー・ダブラ・ハイブリッド

## データシート

## ADCA3992

### 特長

高 RF 出力 : 76.8dBmV の総複合電力

DPD の最適化

高ゲイン : 1218MHz で 26.7dB

超低歪み

低ノイズ指数 : 45MHz で 3dB、1218MHz で 4.5dB

無条件に安定

トランジエントおよびサージ保護

V<sub>CC</sub> の範囲 : 24V～34V

設定可能な DC 電流 : 300mA～550mA (最大)

業界標準規格の 8 ピン SOT115J モジュール・

パッケージ

### アプリケーション

45MHz～1218MHz のケーブル TV (CATV) インフラ

ストラクチャ・アンプ・システム

Remote PHY (物理層) およびファイバ・ディープ・

ノード

DOCSIS® 3.1 準拠

### 概要

ADCA3992 は、広範囲にわたるバイアス条件用に最適化された高ゲインのパワー・ダブラ・ハイブリッド・アンプで、高い電力効率と柔軟性を提供します。ADCA3992 は、消費電力を最大限に低減したデジタル・プリディストーション (DPD) ノード設計への使用に最適です。このデバイスは、ガリウム・ヒ素 (GaAs) 擬似格子整合型高電子移動度トランジスタ (pHEMT) ダイと窒化ガリ

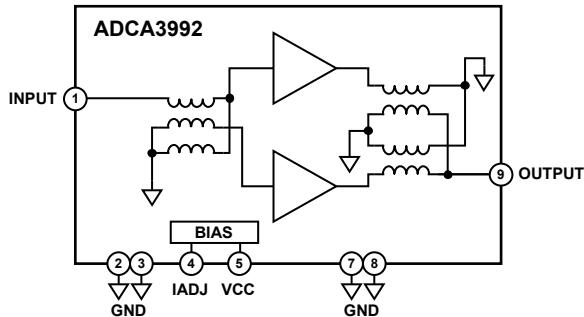

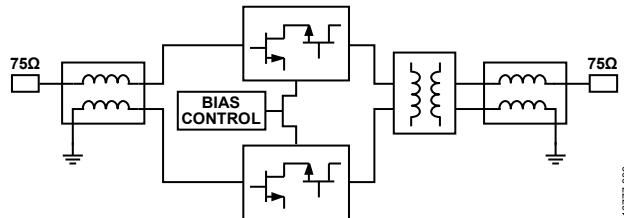

### 機能ブロック図

図 1.

ウム (GaN) HEMT ダイを組み合わせて使用し、超高 RF 出力 (最大 76.8dBmV の複合電力、または 67dBmV の仮想レベル) を実現しています。DC 電流および電源電圧は、幅広い出力レベルにわたって歪み性能と消費電力の最適な兼ね合いが得られるように、外部で調整可能です。ADCA3992 は、業界標準規格の SOT115J パッケージを採用しています。

## 目次

|                            |   |                      |   |

|----------------------------|---|----------------------|---|

| 特長 .....                   | 1 | 絶対最大定格.....          | 4 |

| アプリケーション .....             | 1 | ESD に関する注意.....      | 4 |

| 機能ブロック図 .....              | 1 | ピン配置およびピン機能の説明 ..... | 5 |

| 概要 .....                   | 1 | 代表的な性能特性 .....       | 6 |

| 改訂履歴 .....                 | 2 | 動作原理.....            | 7 |

| 仕様 .....                   | 3 | アプリケーション情報 .....     | 8 |

| 性能概要 .....                 | 3 | 外形寸法.....            | 9 |

| 歪みデータ (40MHz~550MHz) ..... | 3 | オーダー・ガイド .....       | 9 |

## 改訂履歴

1/2020-Revision 0: 初版

## 仕様

## 性能概要

特に指定がない限り、電源電圧 ( $V_{CC}$ ) = 34V、フランジ温度 ( $T_{FLANGE}$ ) = 35°C、ソース・インピーダンス ( $Z_S$ ) = 負荷インピーダンス ( $Z_L$ ) = 75Ω。

表 1.

| Parameter                                   | Symbol                   | Min | Typ  | Max | Unit | Test Conditions/Comments                    |

|---------------------------------------------|--------------------------|-----|------|-----|------|---------------------------------------------|

| POWER GAIN                                  | $S_{21}$                 |     | 24.2 |     | dB   | $f = 45 \text{ MHz}$                        |

|                                             |                          |     | 26.7 |     | dB   | $f = 1218 \text{ MHz}$                      |

| SLOPE OF STRAIGHT LINE <sup>1</sup>         | SL                       |     | 2.5  |     | dB   | $f = 45 \text{ MHz to } 1218 \text{ MHz}$   |

| FLATNESS OF FREQUENCY RESPONSE <sup>2</sup> |                          |     | 0.8  |     | dB   | $f = 45 \text{ MHz to } 1218 \text{ MHz}$   |

| REVERSE ISOLATION                           | $S_{12}$                 |     | -30  |     | dB   | $f = 45 \text{ MHz to } 1218 \text{ MHz}$   |

| RETURN LOSS                                 |                          |     |      |     |      |                                             |

| Input                                       | $S_{11}$                 |     | -26  |     | dB   | $f = 45 \text{ MHz to } 320 \text{ MHz}$    |

|                                             |                          |     | -25  |     | dB   | $f = 320 \text{ MHz to } 640 \text{ MHz}$   |

|                                             |                          |     | -24  |     | dB   | $f = 640 \text{ MHz to } 870 \text{ MHz}$   |

|                                             |                          |     | -28  |     | dB   | $f = 870 \text{ MHz to } 1000 \text{ MHz}$  |

|                                             |                          |     | -24  |     | dB   | $f = 1000 \text{ MHz to } 1218 \text{ MHz}$ |

| Output                                      | $S_{22}$                 |     | -25  |     | dB   | $f = 45 \text{ MHz to } 320 \text{ MHz}$    |

|                                             |                          |     | -21  |     | dB   | $f = 320 \text{ MHz to } 640 \text{ MHz}$   |

|                                             |                          |     | -20  |     | dB   | $f = 640 \text{ MHz to } 870 \text{ MHz}$   |

|                                             |                          |     | -23  |     | dB   | $f = 870 \text{ MHz to } 1000 \text{ MHz}$  |

|                                             |                          |     | -24  |     | dB   | $f = 1000 \text{ MHz to } 1218 \text{ MHz}$ |

| NOISE FIGURE                                | NF                       |     | 3    |     | dB   | $f = 45 \text{ MHz}$                        |

|                                             |                          |     | 4.5  |     | dB   | $f = 1218 \text{ MHz}$                      |

| SUPPLY                                      |                          |     |      |     |      |                                             |

| Maximum Operating Voltage                   | $V_{CC}$                 |     | 34   |     | V    | Can be biased down to 24 V                  |

| DC Current (Total)                          | $I_{CC \text{ (TOTAL)}}$ |     | 535  | 550 | mA   | Can be biased between 300 mA and 550 mA     |

<sup>1</sup> 勾配は、開始周波数でのゲインと停止周波数でのゲインの変化として定義されます。

<sup>2</sup> 周波数応答の平坦性は、直線の勾配の偏差として定義されます。

## 歪みデータ (40MHz~550MHz)

特に指定がない限り、 $V_{CC} = 34V$ 、 $T_{FLANGE} = 35^\circ\text{C}$ 、 $Z_S = Z_L = 75\Omega$ 。

表 2.

| Parameter                        | Symbol | Min | Typ  | Max | Unit | Test Conditions/Comments                                                                                                                  |

|----------------------------------|--------|-----|------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| DISTORTION                       |        |     |      |     |      | Channel power ( $V_0$ ) = 63 dBmV at 1218 MHz, 22 dB extrapolated tilt, 79 channels plus 111 digital channels (-6 dB offset) <sup>1</sup> |

| Composite Triple Beat            | CTB    |     | -80  |     | dBc  | CTB is defined by the National Cable and Telecommunications Association (NCTA)                                                            |

| Crossmodulation                  | XMOD   |     | -74  |     | dBc  | XMOD is measured at baseband (selective voltmeter method) referenced to 100% modulation of the carrier being tested.                      |

| Composite Second Order           | CSO    |     | -80  |     | dBc  | CSO parameter (sum and difference products) is defined by the NCTA                                                                        |

| Carrier to Intermodulation Noise | CIN    |     | 62   |     | dB   | CIN is defined by ANSI/SCTE 17 (test procedure for carrier to noise)                                                                      |

| TOTAL COMPOSITE POWER            | TCP    |     | 76.8 |     | dBmV | See Figure 7 and Figure 8                                                                                                                 |

<sup>1</sup> 79 アナログ・チャンネル + 111 デジタル・チャンネル、NTSC (National Television System Committee) 周波数ラスター = 55.25MHz~547.25MHz、等価なアナログ搬送波に対して-6dB のオフセット、22dB の外挿傾斜。

## 絶対最大定格

表 3.

| Parameter                           | Rating          |

|-------------------------------------|-----------------|

| VCC, IADJ                           |                 |

| DC Supply over Voltage (5 minute)   | 38 V            |

| RF Input Power                      | 75 dBmV         |

| Operating Temperature Ranges        |                 |

| Ambient ( $T_A$ )                   | -30°C to +85°C  |

| Flange ( $T_{FLANGE}$ )             | -30°C to +100°C |

| Storage Temperature ( $T_S$ ) Range | -40°C to +100°C |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

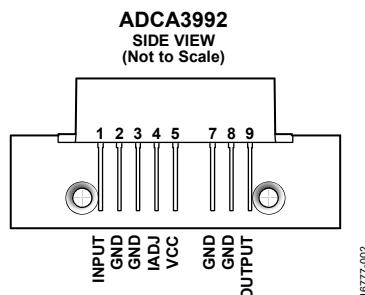

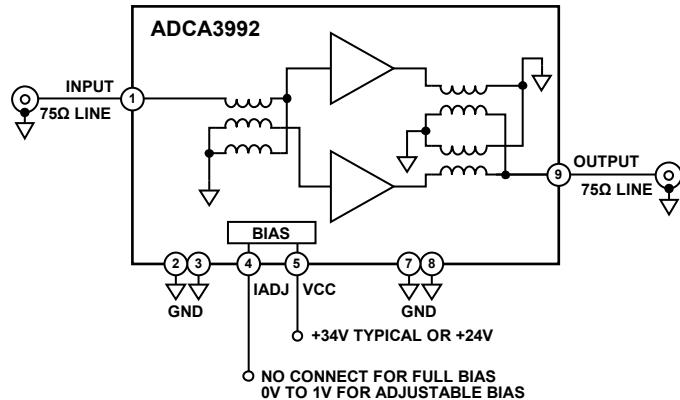

## ピン配置およびピン機能の説明

図 2. ピン配置

表 4. ピン機能の説明

| ピン番号       | 記号     | 説明                                                       |

|------------|--------|----------------------------------------------------------|

| 1          | INPUT  | RF 入力。                                                   |

| 2, 3, 7, 8 | GND    | グラウンド。                                                   |

| 4          | IADJ   | バイアス制御ピン。フル・バイアス動作ではこのピンをフロート状態にします。このピンには負電圧をかけないでください。 |

| 5          | VCC    | 正の電源電圧。34V (代表値)。このピンは最低 24V までバイアス可能です。                 |

| 9          | OUTPUT | RF 出力。                                                   |

## 代表的な性能特性

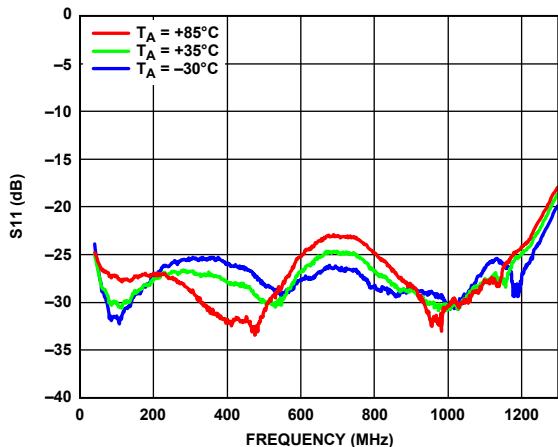

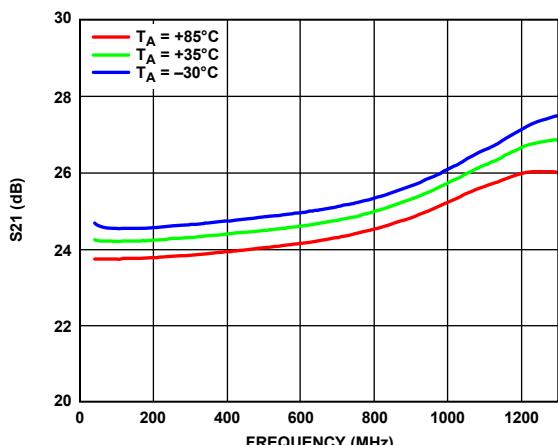

特に指定がない限り、 $V_{CC} = 34V$ 、 $T_{FLANGE} = 35^{\circ}C$ 、 $Z_S = Z_L = 75\Omega$ 。

図3. 様々な温度での入力リターン・ロス (S11) と周波数の関係

図4. 様々な温度でのゲイン (S21) と周波数の関係

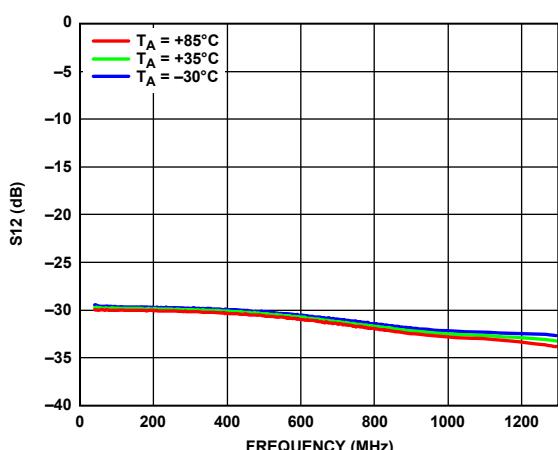

図5. 様々な温度でのリバース・アイソレーション (S12) と周波数の関係

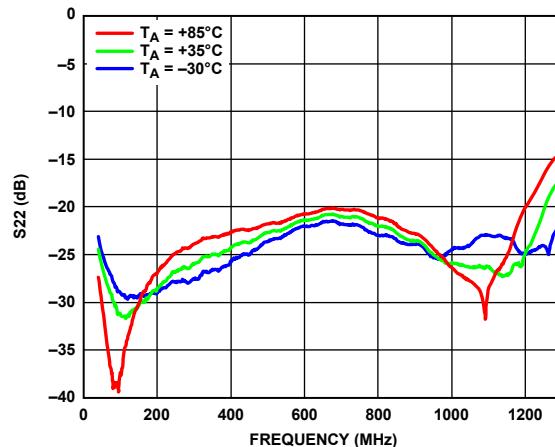

図6. 様々な温度での出力リターン・ロス (S22) と周波数の関係

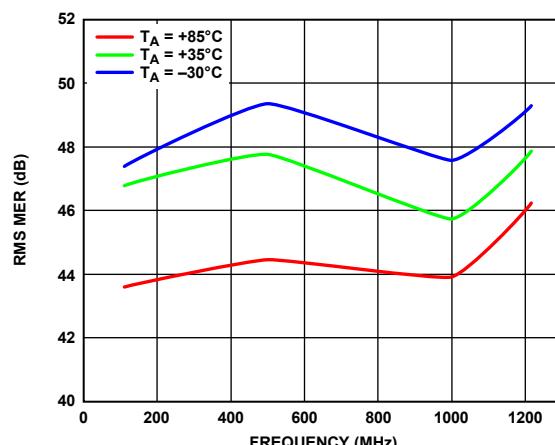

図7. 様々な温度でのRMS変調誤差比 (MER) と周波数の関係、1218MHzで $V_0 = 61\text{dBmV}$ 、23dBの外挿傾斜、190デジタル・チャンネル、総複合電力 = 76.8dBmV

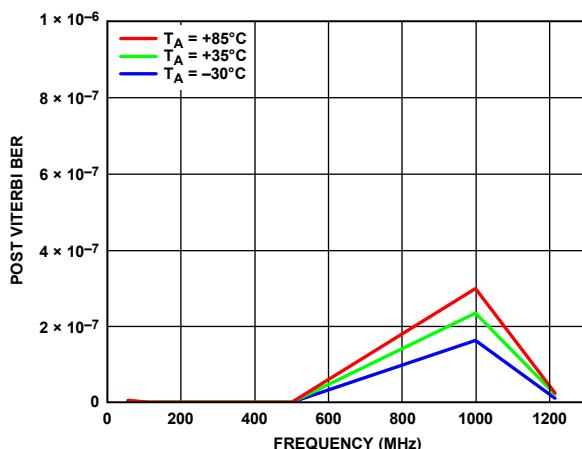

図8. 様々な温度でのポスト・ビタビ・ビット誤り率 (BER) と周波数の関係、1218MHzで $V_0 = 61\text{dBmV}$ 、23dBの外挿傾斜、190デジタル・チャンネル、総複合電力 = 76.8dBmV、積分時間 10 秒

## 動作原理

ADCA3992 は、CATV アプリケーション用に設計された  $75\Omega$  入出力整合モジュールです。ADCA3992 は、カスコード電界効果トランジスタ (FET) 帰還アンプを A 級 プッシュプル構成で使用します。カスコード段の下半分はシングルダイのリニア FET プロセスで実装され、寄生容量を最小限に抑えることで高ゲインを実現しています。カスコードの上側デバイスはリニア GaN プロセスで実装され、非常に高い RF 電圧を発生します。動作周波数範囲は 45MHz～1218MHz です。

ADCA3992 モジュールは、内部でバランを使用して入力信号を平衡信号に変換し、アクティブ段に供給します。出力インピーダンス・トランスとバランの組み合わせにより、平衡 GaN 信号を不平衡  $75\Omega$  出力に変換します。また、出力トランスは DC 電流をアクティブ段に供給し、アクティブなデバイスから入力される 2 次歪み積を相殺します。

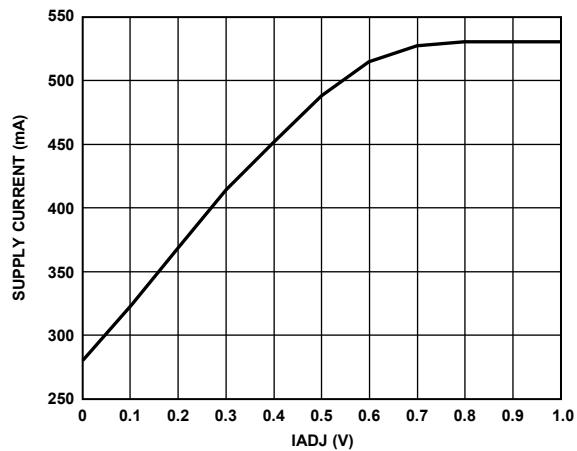

このモジュールは制御ピン (IADJ) を備えており、このピンとグラウンドの間に抵抗を接続するか、または正電圧を使用することにより、デバイスの DC 電流消費を低バイアスからフル・バイアスまでの範囲で設定できます。

16777-009

図 9. 簡略化した回路図

## アプリケーション情報

ADCA3992 を動作させるための基本的な接続方法を図 11 に示します。ADCA3992 の入力ピン（1 番ピン）と出力ピン（9 番ピン）は、いずれも  $75\Omega$  にマッチします。5 番ピンは VCC ピンです。このピンは通常動作では  $34V$  を必要としますが、低消費電力動作では最低  $24V$  まで対応します。フル・バイアス動作では、IADJ ピン（4 番ピン）をオープンのままにすることを推奨します。ADCA3992 の電源電流をバイアス制御するには、IADJ ピンに  $0V \sim 1V$  の外部制御電圧を印加します。図 10 に、ADCA3992 の電源電流と IADJ ピンの制御電圧の関係を示します。

16777-011

図 10. 電源電流と IADJ の関係

16777-010

図 11. 基本的な接続方法

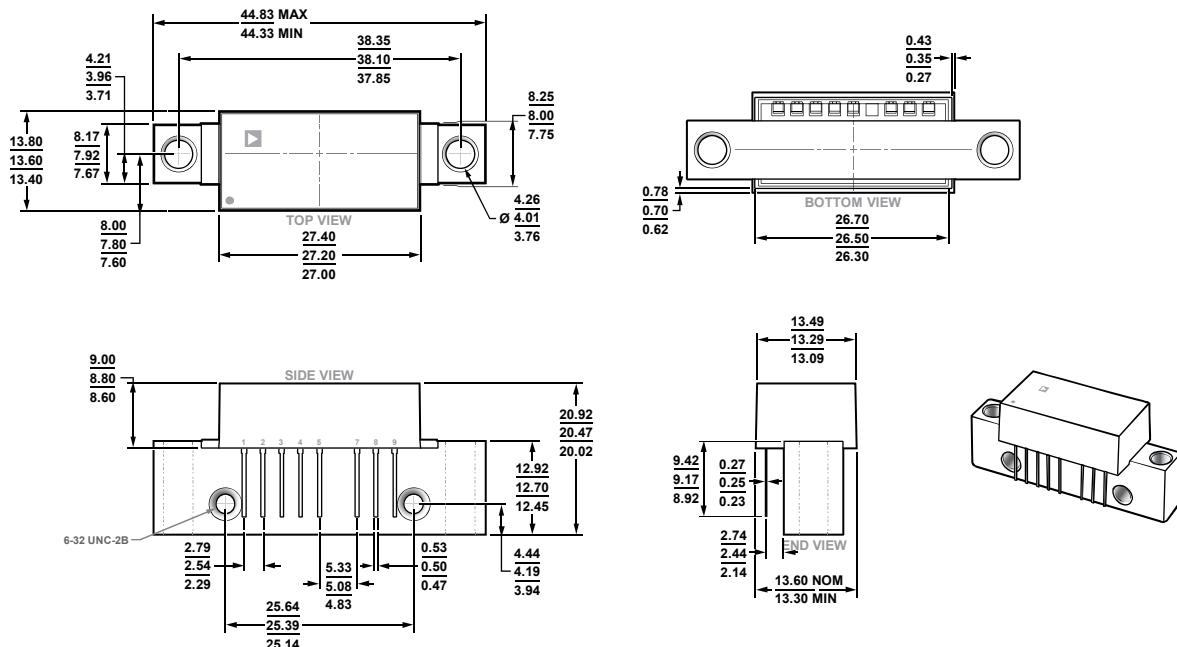

外形寸法

図 12. 8 ピン SOT115J モジュール・パッケージ [MODULE] (ML-8-1) 尺寸 (ミリ単位)

オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                                       | Package Option |

|--------------------|-------------------|-----------------------------------------------------------|----------------|

| ADCA3992AMLZ       | -30°C to +100°C   | 8-Pin SOT115J Module Package [MODULE], Box with 25 Pieces | ML-8-1         |

<sup>1</sup> Z = RoHS 準拠製品