# DOCSIS 3.1 パワー・ダブラ・アンプ 45MHz～1218MHz

データシート

ADCA3270

## 特長

RFCM3327、RFCM3328 とピン互換

総複合電力 : 73dBmV

高パワー・ゲイン : 1218MHz で 25dB

優れた直線性 :

超低歪み

複合 3 次 (CTB) : -80dBc (代表値)

複合 2 次 (CSO) : -80dBc (代表値)

搬送波対相互変調ノイズ比 : 59dB (代表値)

低ノイズ指数 : 45MHz で 3dB (代表値)、1218MHz で 4dB (代表値)

無条件で安定動作

設定可能な電流値 : 24V で 350mA～480mA

温度モニタ内蔵

9 端子、熱強化型チップ・アレイ・スマール・アウトライン・リードなしキャビティ [LGA\_CAV]

## 概要

アナログ・デバイセズの ADCA3270 は、パワー・ゲインが 25dB の 24V パワー・ダブラ型モノリシック・マイクロ波 IC (MMIC) です。このデバイスは、ガリウム・ヒ素 (GaAs) 技術、擬似格子整合型高電子トランジスタ (pHEMT) 技術、窒化ガリウム (GaN) HEMT 技術による高度な回路設計手法を使用して、高い RF 出力 (18dB のチルト条件で 73dBmV の最大複合電力) を実現します。DC 電流と供給電圧を外部で調整することにより、出力レベルの全範囲にわたって消費電力に対する歪み特性を最適化することができます。ADCA3270 は高いゲインを実現し、DOCSIS 3.1 インフラストラクチャ機器の設計と製造を簡素化します。

ADCA3270 は、業界標準のフットプリントを持つ 9 端子、熱強化型チップ・アレイ・スマール・アウトライン・リードなしキャビティ [LGA\_CAV] を採用しています。

## アプリケーション

45MHz～1218MHz の CATV (ケーブル・テレビ)

インフラストラクチャ用アンプ・システム

リモート物理層 (PHY)

DOCSIS 3.1 準拠

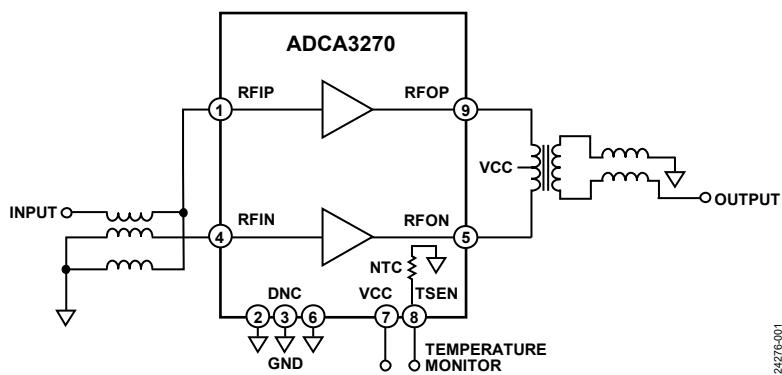

## 機能ブロック図

24276-001

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

Rev. 0

©2021 Analog Devices, Inc. All rights reserved.

アナログ・デバイセズ株式会社

|                                                   |                   |

|---------------------------------------------------|-------------------|

| 本社／〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F   | 電話 03 (5402) 8200 |

| 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F                 | 電話 06 (6350) 6868 |

| 名古屋営業所／〒451-6038 愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F | 電話 052 (569) 6300 |

## 目次

|                                   |   |                               |    |

|-----------------------------------|---|-------------------------------|----|

| 特長 .....                          | 1 | 代表的な性能特性 .....                | 7  |

| アプリケーション .....                    | 1 | S パラメータ .....                 | 7  |

| 概要 .....                          | 1 | 9dB チルト性能 .....               | 8  |

| 機能ブロック図 .....                     | 1 | 18dB チルト性能 .....              | 9  |

| 改訂履歴 .....                        | 2 | 動作原理 .....                    | 10 |

| 仕様 .....                          | 3 | アプリケーション情報 .....              | 11 |

| 一般的な性能 .....                      | 3 | ADCA3270 の温度検出モニタ .....       | 11 |

| 歪みデータ（すべてのデジタル・チャンネル・プラン） .....   | 3 | 熱に対する考慮事項 .....               | 11 |

| 歪みデータ（ミックスド・シグナル・チャンネル・プラン） ..... | 4 | ハンダ処理情報と推奨 PCB ランド・パターン ..... | 11 |

| 絶対最大定格 .....                      | 5 | ADCA3270 のバイアス電流 .....        | 12 |

| 熱抵抗 .....                         | 5 | 外形寸法 .....                    | 14 |

| 静電放電（ESD）定格 .....                 | 5 | オーダー・ガイド .....                | 14 |

| ESD に関する注意 .....                  | 5 |                               |    |

| ピン配置およびピン機能の説明 .....              | 6 |                               |    |

## 改訂履歴

7/2021—Revision 0: Initial Version

## 仕様

### 一般的の性能

特に指定のない限り、電源電圧 ( $V_{CC}$ ) = 24V、露出パッド温度 ( $T_{PADDLE}$ ) = 35°C、ソース・インピーダンス ( $Z_S$ ) = 負荷インピーダンス ( $Z_L$ ) = 75Ω、DC 電流 ( $I_{CC}$ ) = 480mA。

表 1.

| パラメータ                                       | 記号                  | Min                             | Typ        | Max          | 単位 | テスト条件／コメント                                                                                              |

|---------------------------------------------|---------------------|---------------------------------|------------|--------------|----|---------------------------------------------------------------------------------------------------------|

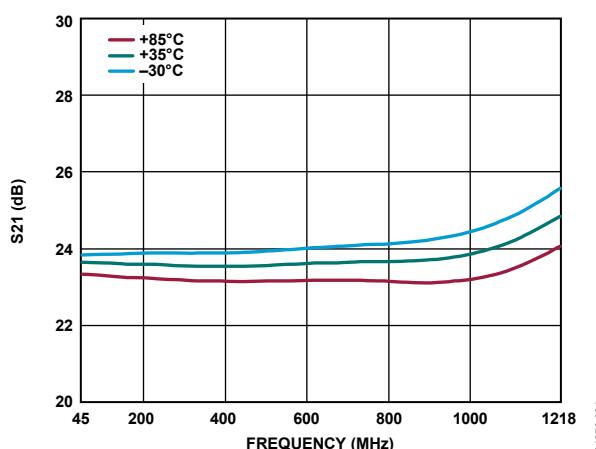

| POWER GAIN                                  | S21                 | 22.0<br>23.0                    | 23.6<br>25 | 25.0<br>26.5 | dB | 周波数 45MHz (図 4 を参照)<br>周波数 1218MHz (図 4 を参照)                                                            |

| SLOPE STRAIGHT LINE <sup>1</sup>            |                     |                                 | 2.0        |              | dB | 周波数 45MHz~1218MHz                                                                                       |

| FLATNESS OF FREQUENCY RESPONSE <sup>2</sup> |                     |                                 | 0.75       |              | dB | 周波数 45MHz~1218MHz                                                                                       |

| REVERSE ISOLATION                           | S12                 |                                 | 28         |              | dB | 周波数 45MHz~1218MHz (図 5 を参照)                                                                             |

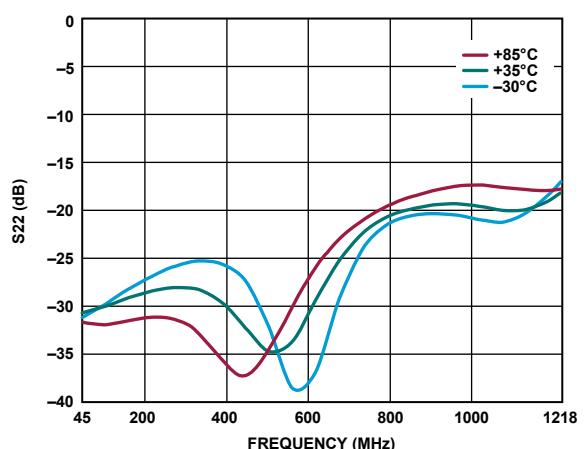

| RETURN LOSS                                 |                     |                                 |            |              |    | 図 3 と 図 6 参照                                                                                            |

| Input                                       | S11                 | -20<br>-15<br>-12<br>-12<br>-12 |            |              | dB | 周波数 45MHz~320MHz<br>周波数 320MHz~640MHz<br>周波数 640MHz~870MHz<br>周波数 870MHz~1000MHz<br>周波数 1000MHz~1218MHz |

| Output                                      | S22                 | -20<br>-20<br>-20<br>-20<br>-18 |            |              | dB | 周波数 45MHz~320MHz<br>周波数 320MHz~640MHz<br>周波数 640MHz~870MHz<br>周波数 870MHz~1000MHz<br>周波数 1000MHz~1218MHz |

| NOISE FIGURE                                |                     |                                 | 3<br>4     |              | dB | 周波数 45MHz<br>周波数 1218MHz                                                                                |

| SUPPLY                                      |                     |                                 |            |              |    |                                                                                                         |

| Voltage                                     | $V_{CC}$            | 18                              | 24         | 26           | V  | 電源電圧はアプリケーションに応じて調整できます (アプリケーション情報のセクションを参照してください)                                                     |

| DC Current (Total)                          | $I_{CC}$<br>(TOTAL) | 350                             | 480        | 500          | mA | 350mA~480mA の範囲でバイアスできます (アプリケーション情報のセクションを参照してください)                                                    |

| RF Input Bias Voltage                       | $V_{BIAS}$          |                                 | 1.08       |              | V  |                                                                                                         |

<sup>1</sup> 直線勾配は、開始周波数におけるゲインと停止周波数におけるゲインの差として定義されます。

<sup>2</sup> 周波数応答の平坦度は、開始周波数と停止周波数間の任意の周波数におけるゲインと、開始周波数におけるゲインと停止周波数におけるゲインの間に引いた基準直線の間の差として定義されます。

### 歪みデータ (すべてのデジタル・チャンネル・プラン)

特に指定のない限り、 $V_{CC}$  = 24V、 $T_{PADDLE}$  = 35°C、 $Z_S$  =  $Z_L$  = 75Ω。

表 2.

| パラメータ                 | 記号  | Min                  | Typ | Max                 | 単位   | テスト条件／コメント                                                                                                                   |

|-----------------------|-----|----------------------|-----|---------------------|------|------------------------------------------------------------------------------------------------------------------------------|

| TOTAL COMPOSITE POWER | TCP | 73                   |     |                     | dBmV | 18dB チルト、57MHz から 1215MHz までの 190 デジタル (256QAM) チャンネル                                                                        |

|                       |     | 73                   |     |                     | dBmV | 9dB チルト、57MHz から 1215MHz までの 190 デジタル (256QAM) チャンネル                                                                         |

| ERROR RATES           |     |                      |     |                     |      |                                                                                                                              |

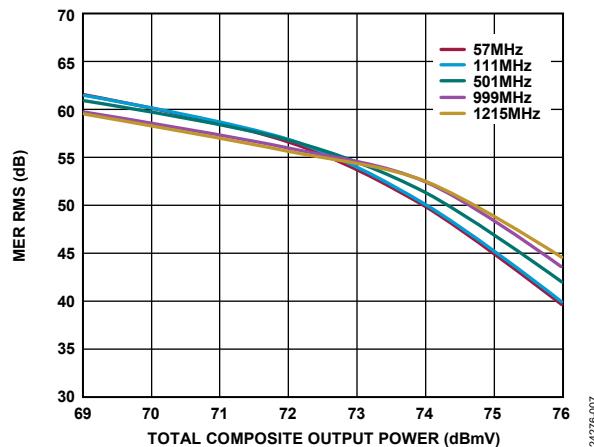

| Modulation Error Rate | MER | 47                   |     |                     | dB   |                                                                                                                              |

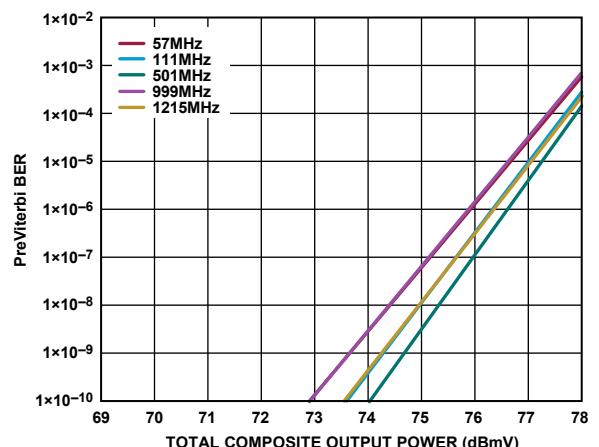

| Bit Error Rate        | BER | $<1 \times 10^{-10}$ |     | $<1 \times 10^{-9}$ |      | ポスト・ビタビ、18dB チルト、57MHz から 1215MHz までの 190 デジタル (256QAM) チャンネル<br>プリ・ビタビ、9dB チルト、57MHz から 1215MHz までの 190 デジタル (256QAM) チャンネル |

## 歪みデータ（ミックスド・シグナル・チャンネル・プラン）

特に指定のない限り、 $V_{CC} = 24V$ 、 $T_{FLANGE} = 35^{\circ}C$ 、 $Z_S = Z_L = 75\Omega$ 。

表 3.

| パラメータ                            | 記号  | Min | Typ | Max | 単位  | テスト条件／コメント                                                                                                                                                               |

|----------------------------------|-----|-----|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DISTORTION                       |     |     |     |     |     | TCP = 72.4dBmV、アナログおよびデジタル・チャンネル・プランは 18dB の外挿チルトで構成、79 の連続波チャンネルと 111 のデジタル・チャンネル、55.25MHz～547.25MHz の NTSC (National Television System Committee) 周波数ラスター範囲、-6dB オフセット |

| Composite Triple Beat            | CTB | -80 |     |     | dBc | NCTA (National Cable and Telecommunications Association) による定義                                                                                                           |

| Composite Second-Order           | CSO | -80 |     |     | dBc | NCTA による定義                                                                                                                                                               |

| Carrier to Intermodulation Noise |     | 59  |     |     | dB  | ANSI/SCTE (American National Standard/Society of Cable Telecommunications Engineers) 17 (搬送波対ノイズ比のテスト手順) による定義                                                           |

## 絶対最大定格

表 4.

| Parameter                                                                              | Rating          |

|----------------------------------------------------------------------------------------|-----------------|

| $V_{CC}$                                                                               |                 |

| DC Supply over Voltage (5 minute)                                                      | 30 V            |

| RF Input Voltage ( $RF_{INPUT}$ ), Single Tone                                         | 75 dBmV         |

| Temperature                                                                            |                 |

| Operating Range, $T_{PADDLE}$                                                          | -30°C to +110°C |

| Peak Reflow (Moisture Sensitivity Level (MSL) 3)                                       | 260°C           |

| Junction ( $T_J$ ) to Maintain 1 Million Hour Mean Time to Failure (MTTF)              | 170°C           |

| Nominal Junction ( $T_J$ )                                                             |                 |

| $T_{PADDLE} = 110^\circ\text{C}$ , $I_{CC} = 480 \text{ mA}$ , $V_{CC} = 24 \text{ V}$ | 144°C           |

| Storage ( $T_S$ ) Range                                                                | -40°C to +150°C |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCB の熱設計には、細心の注意を払う必要があります。

$\theta_{JC}$  は、PHEMT デバイスの動作部分から、デバイス取り付け領域に最も近いパッケージの外側表面（ケース底面の露出パッド）までの熱抵抗です。詳細については、[熱に対する考慮事項](#)のセクションを参照してください。

表 5. 热抵抗

| Package Type | $\theta_{JC}^1$ | Unit |

|--------------|-----------------|------|

| CE-9-2       | 2.9             | °C/W |

<sup>1</sup> 热抵抗 ( $\theta_{JC}$ ) は  $T_{PADDLE}$  とデバイス内部のジャンクション温度 ( $T_J$ ) の間で定義されます。

### 静電放電 (ESD) 定格

以下の ESD 情報は、ESD に敏感なデバイスを ESD に対して保護された環境においてのみ取り扱う場合のものです。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

### ADCA3270 の ESD 定格

表 6. ADCA3270、6 端子 LGA\_CAV

| ESD Model | Withstand Threshold (V) | Class            |

|-----------|-------------------------|------------------|

| HBM       | 500                     | Class 1B, passed |

### ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

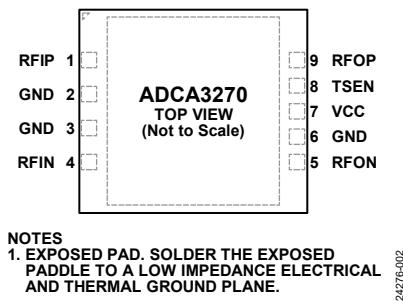

## ピン配置およびピン機能の説明

図 2. ピン配置

表 7. ピン機能の説明

| ピン番号    | 記号         | 概要                                             |

|---------|------------|------------------------------------------------|

| 1, 4    | RFIP, RFIN | RF 差動入力。                                       |

| 2, 3, 6 | GND        | グラウンド。                                         |

| 5, 9    | RFON, RFOP | RF 差動出力。                                       |

| 7       | VCC        | 正側（供給）電源電圧、24V（代表値）。                           |

| 8       | TSEN       | 温度検出ピン。                                        |

|         |            | 露出パッド。露出パッドは電気抵抗と熱抵抗の低いグラウンド・プレーンにハンダ付けしてください。 |

## 代表的な性能特性

特に指定のない限り、 $V_{CC} = 24V$ 、 $T_{PADDLE} = 35^{\circ}\text{C}$ 、 $Z_S = Z_L = 75\Omega$ 。

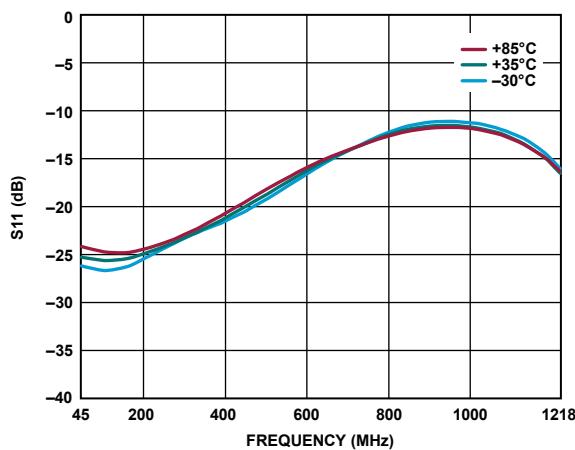

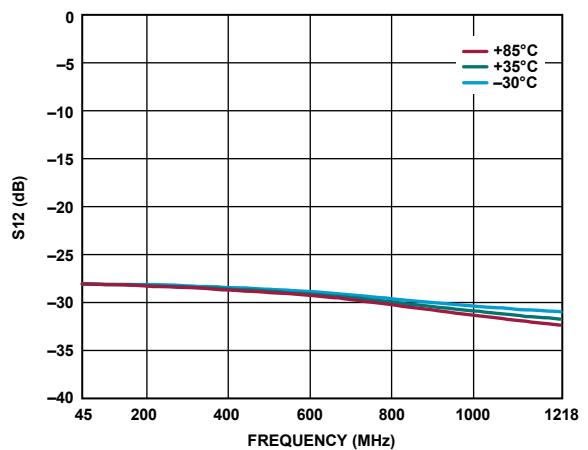

### S パラメータ

図 3. 様々な温度での S11 の周波数特性

図 5. 様々な温度での S12 の周波数特性

図 4. 様々な温度での S21 の周波数特性

図 6. 様々な温度での S22 の周波数特性

## 9dB チルト性能

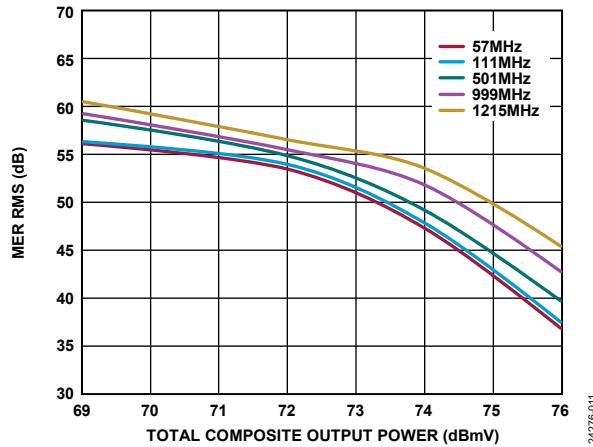

9dB 外挿チルトと 190 デジタル・チャンネル (256QAM、ITU-T J.83 Annex B)。

図 7. 様々な周波数における MER RMS と

総複合出力電力の関係、35°C、9dB チルト

図 9. 様々な周波数におけるプリ・ビタビ BER と

総複合出力電力の関係、35°C、9dB チルト

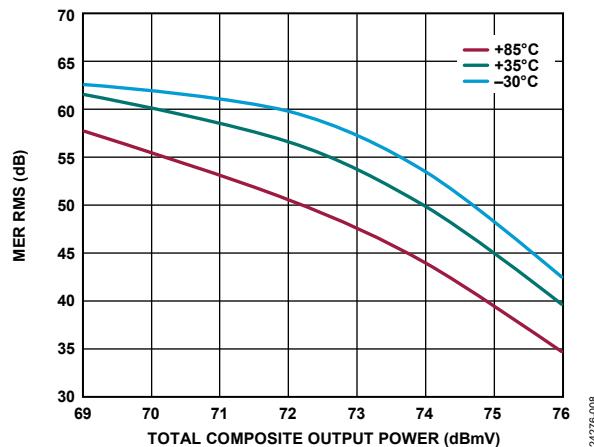

図 8. 様々な温度における MER RMS と総複合出力電力の関係、

57MHz、9dB チルト

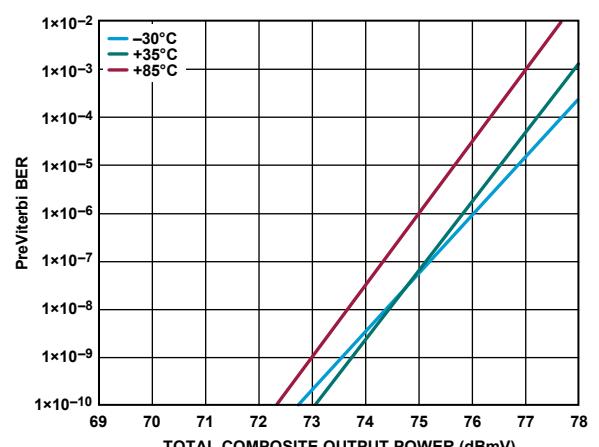

図 10. 様々な温度におけるプリ・ビタビ BER と

総複合出力電力の関係、57MHz、9dB チルト

## 18dB チルト性能

18dB 外挿チルトと 190 デジタル・チャンネル (256QAM、ITU-T J.83 Annex B)

図 11. 様々な周波数における MER RMS と

総複合出力電力の関係、35°C、18dB チルト

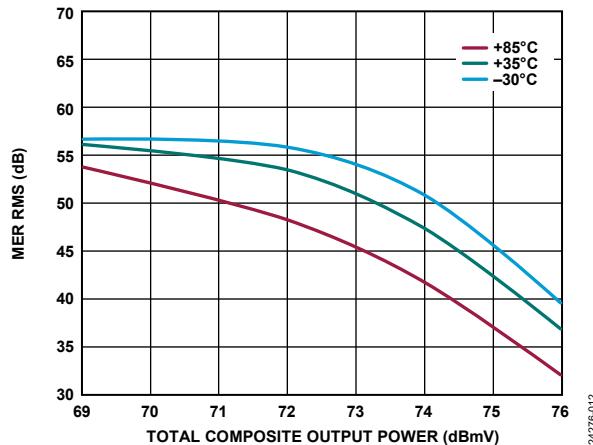

図 12. 様々な温度における MER RMS と

総複合出力電力の関係、57MHz、18dB チルト

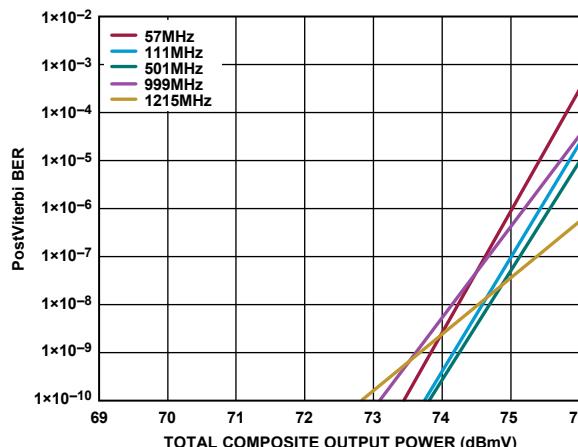

図 13. 様々な周波数におけるポスト・ビタビ BER と

総複合出力電力の関係、35°C、18dB チルト

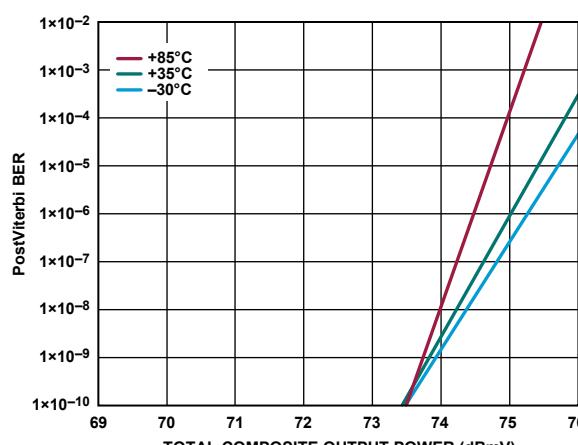

図 14. 様々な温度におけるポスト・ビタビ BER と

総複合出力電力の関係、57MHz、18dB チルト

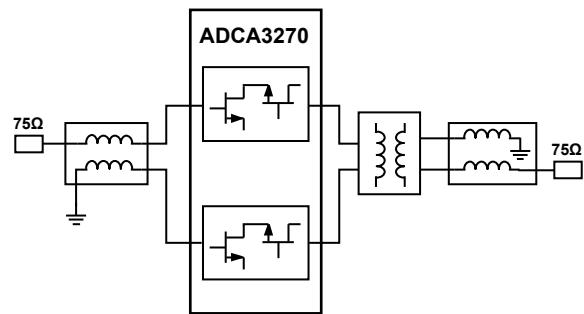

## 動作原理

ADCA3270 は、LGA\_CAV パッケージに収納されたバランスド・アンプです。アプリケーション回路を使用することで、ADCA3270 は  $75\Omega$  にマッチングされた入出力インピーダンスとインターフェース接続でき、CATV アプリケーション用に設計されたモジュールに対応できるようになります。ADCA3270 は、クラス A プッシュ・プル構成のカスコード型電界効果トランジスタ (FET) 帰還アンプを使用しています。カスコード段の下側半分は寄生成分を最小限に抑えるシングルダイ・リニア FET プロセスで実装されているので、高いゲインが実現されています。カスコードの上側デバイスは、高いRF電圧スイングが可能なリニア GaN プロセスを使って実装されています。動作周波数は 45MHz～1218MHz です。

ADCA3270 は無条件に安定であるため、DOCSIS 3.1 規格とそれ以前の DOCSIS 規格を対象としたシステム内で安定した動作が確保できます。

図 15. 簡略化した回路図

24276015

## アプリケーション情報

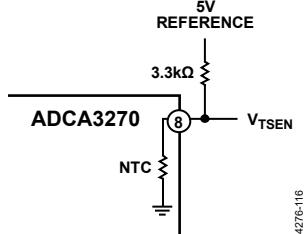

### ADCA3270 の温度検出モニタ

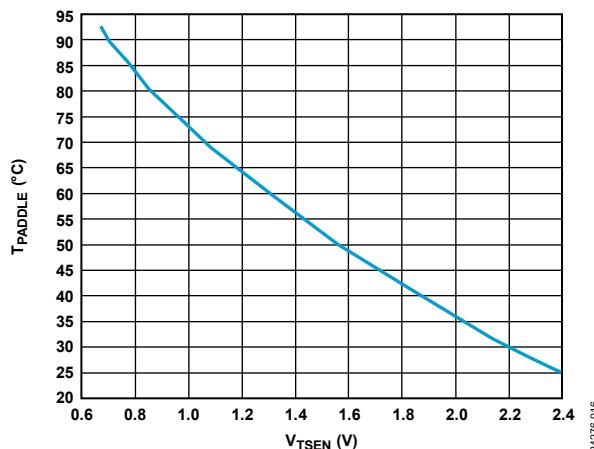

ADCA3270 には、負の温度係数 (NTC) を持つサーミスタが内部に実装されており、これを抵抗分圧器の下段として使用することで、LGA\_CAV パッケージのグラウンド温度  $T_{PADDLE}$  と相關する電圧を出力します。図 16 に示すように構成すると、 $V_{TSEN}$  と  $T_{PADDLE}$  の間の関係（代表値）は図 17 のようになります。

図 16. 推奨される NTC の構成

図 17.  $T_{PADDLE}$  と  $V_{TSEN}$  の関係

### 熱に対する考慮事項

ADCA3270 は、熱効率に優れた 9 端子チップ・アレイ・スマート・アウトライン・リードなしキャビティ [LGA\_CAV] を採用しています。熱抵抗  $\theta_{JC}$  は  $2.9^{\circ}\text{C}/\text{W}$  で、これはパッケージ底面の露出パッドによって定まります。最適な熱性能を得るために、できるだけ多くのサーマル・ビアを LGA\_CAV パッケージの露出パッド下に配置することを推奨します。更に、最適性能を得るために、これらのビアには熱伝導率の高いペーストを充填することを推奨します。また、ADCA3270 下のビア・アレイは、システム・シャーシの台座など、外部のヒート・シンクに接続することを推奨します。

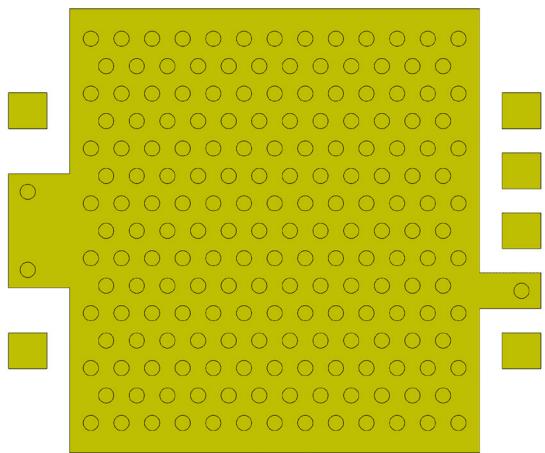

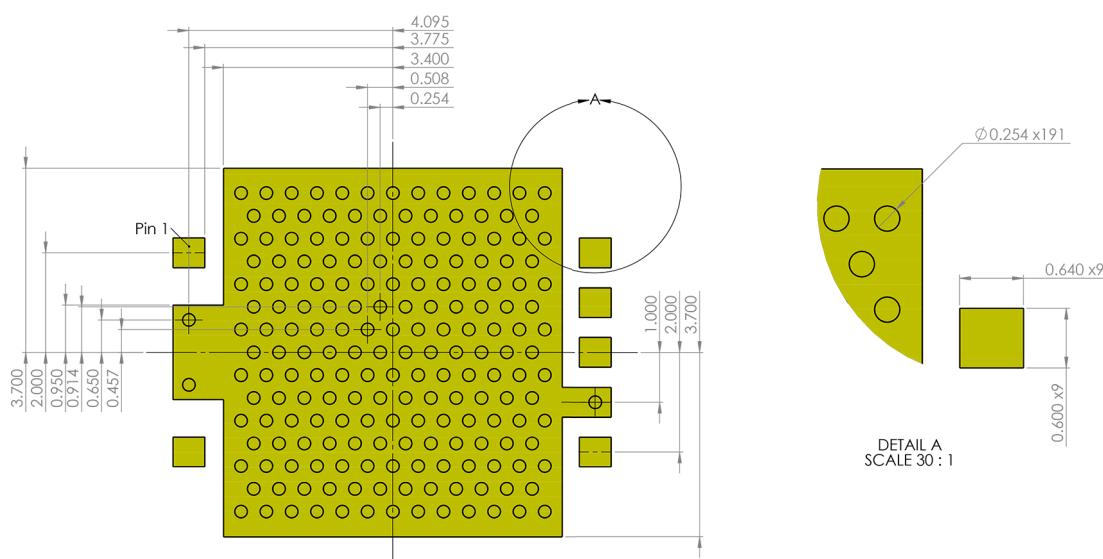

### ハンダ処理情報と推奨 PCB ランド・パターン

ADCA3270 の推奨ランド・パターンを図 18 に示します。熱抵抗を最小限に抑えるため、LGA\_CAV パッケージ ( $9.00\text{mm} \times 8.00\text{mm}$ ) の露出パッドは、ピン 2、3、6 と一緒にグランド・プレーンにハンダ付けします。188 個のサーマル・ビアを露出パッドの下にアレイ上に配置して、放熱性を向上させています。1 列が 13 個のビアと 12 個のビアを交互に配置することでエリア内のビア数を最大化しています。また、パッド下のエリアは、PCB 最下層のグラウンドに接続されています。グラウンド層が複数ある場合は、各グラウンド層をビアで接続してください。PCB の外側の層には、2 オンス以上の銅を使用してください。ビア・ホール壁面の平均メッキ厚は最小でも  $0.001$  インチ以上が必要です。また、AE3030 (Tatsuta 社製) などの導電ペーストを充填し、メッキで覆うことを推奨します。推奨の PCB フットプリント設計を図 19 に示します。

図 18. 推奨されるランド・パターン

ADCA3270 を使用して熱性能を最適化するための詳細については、AN-1604 アプリケーション・ノート、LFCSP パッケージおよびフランジ・パッケージに収容された RF アンプの温度管理計算を参照してください。

図 19. 推奨される PCB レイアウト (寸法: mm)

24276-19

## ADCA3270 のバイアス電流

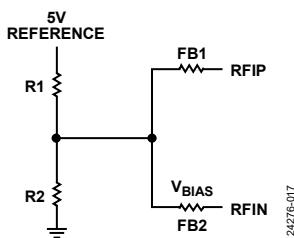

ADCA3270 は汎用性に優れた回路設計を採用しており、VCC (ピン 7) に接続する電源電圧、RFIP (ピン 1) と RFIN (ピン 4) に接続するバイアス制御電圧 ( $V_{BIAS}$ ) を設定することで、あらゆるアプリケーションにおいて消費電力を最適化できます。図 20 に示すように、高精度の 5V リファレンスと抵抗分圧器 ( $R1$  および  $R2$ ) を使用して  $I_{CC}$  を調整することを推奨します。電圧は、フェライト・ビーズ (FB1 および FB2) を介して各入力に接続します。パワー・アンプに RF を供給するために使用するバランの DC 出力は、コンデンサを使用してブロックしてください。

図 20. バイアス制御電圧の設定

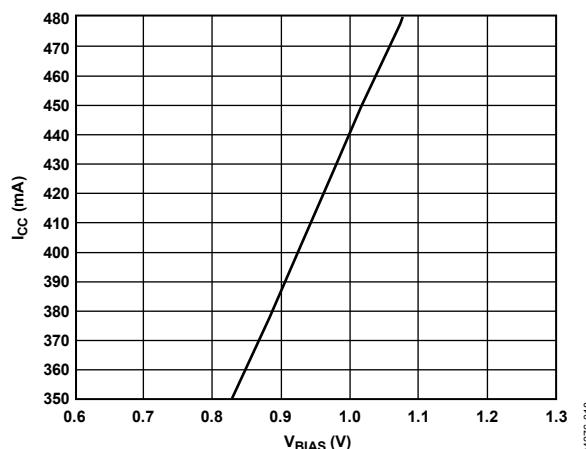

図 21 は、 $V_{BIAS}$  に対する  $I_{CC}$  の代表的な伝達関数を示しています。これを用いて、380mA～480mA の範囲で  $I_{CC}$  を調整できます。

図 21.  $I_{CC}$  と  $V_{BIAS}$  の関係

24276-016

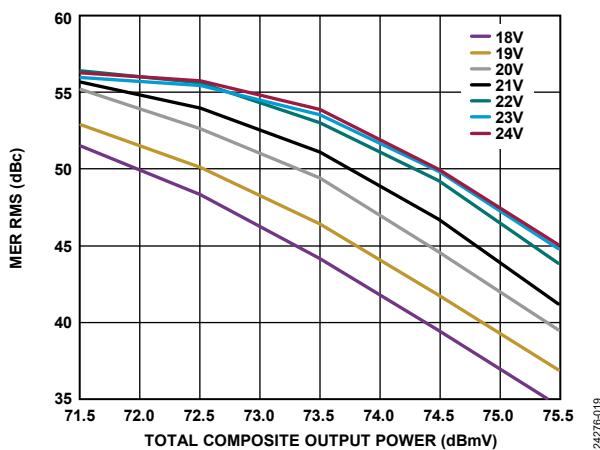

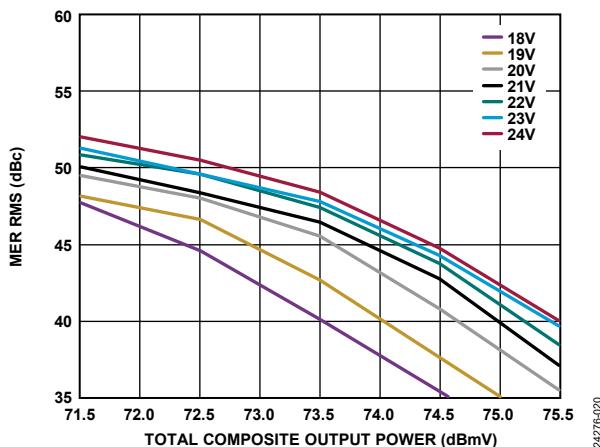

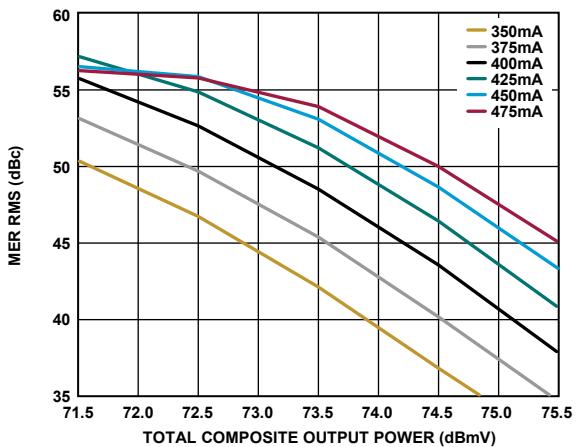

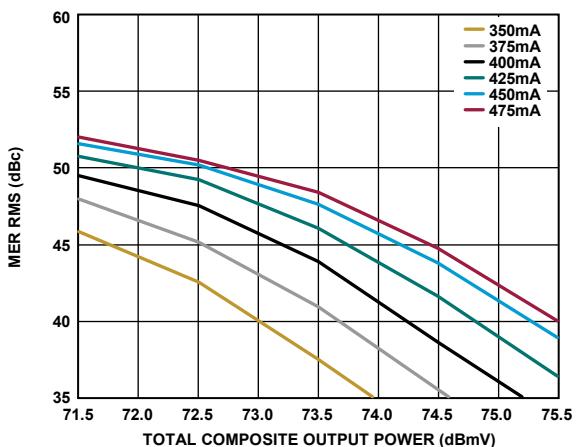

図 22 と図 23 は、様々な電源電圧設定に対する MER 性能のトレードオフを表しています。図 24 と図 25 は、様々なバイアス電流設定に対する変調誤差比性能のトレードオフを表しています。

図 22. MER RMS と総複合出力電力の関係、

I<sub>CC</sub> = 475mA、V<sub>CC</sub> = 18V~24V、1V ステップ、9dB チルト

図 23. MER RMS と総複合出力電力の関係、

I<sub>CC</sub> = 475mA、V<sub>CC</sub> = 18V~24V、1V ステップ、22dB チルト

図 24. MER RMS と総複合出力電力の関係、V<sub>CC</sub> = 24V、

350mA~475mA の範囲で 25mA ステップ、9dB チルト

図 25. MER RMS と総複合出力電力の関係、V<sub>CC</sub> = 24V、

350mA~475mA の範囲で 25mA ステップ、22dB チルト

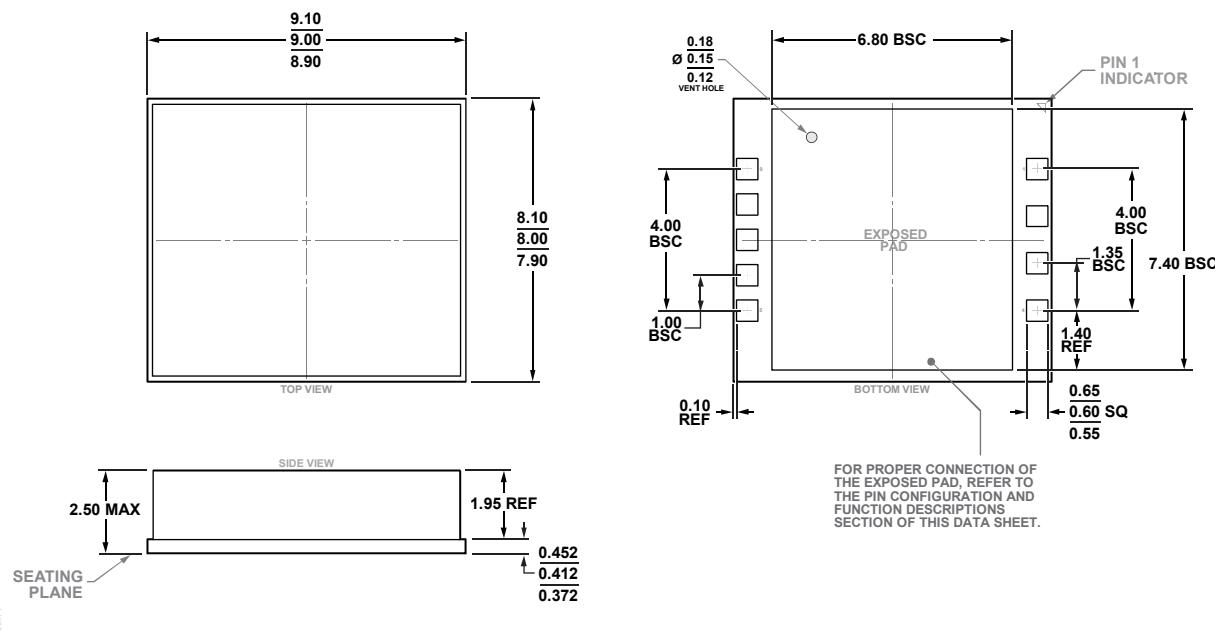

## 外形寸法

図 26. 9 端子チップ・アレイ・スマール・アウトライン・リードなしキャビティ [LGA\_CAV]

9.00mm × 8.00mm ボディ、2.50mm パッケージ高

(CE-9-2)

寸法 : mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                                          | Package Option |

|--------------------|-------------------|--------------------------------------------------------------|----------------|

| ADCA3270ACEZ       | -30°C to +110°C   | 9-Terminal Chip Array Small Outline No Lead Cavity [LGA_CAV] | CE-9-2         |

| ADCA3270ACEZ-R7    | -30°C to +110°C   | 9-Terminal Chip Array Small Outline No Lead Cavity [LGA_CAV] | CE-9-2         |

| ADCA3270-EVALZ     |                   | Evaluation Board                                             |                |

<sup>1</sup> Z = RoHS 準拠製品