## 3ADC、1DACの低消費電力コーデック、オーディオ/FastDSP付き

### 特長

- ▶ プログラマブルなFastDSPオーディオ処理エンジン

- ▶ 最大768kHzのサンプル・レート

- ▶ バイクワッド・フィルタ、リミッタ、ボリューム制御、ミキシング

- ▶ 低遅延の24ビットADCおよびDAC

- ▶ 106dBのS/N比（A特性重み付けフィルタを使用してADCを通した信号）

- ▶ 110dBの合計S/N比（A特性重み付けフィルタを使用してDACとヘッドフォンを通した信号）

- ▶ シリアル・ポートのサンプル・レート：8kHz～768kHz

- ▶ アナログtoアナログの遅延：5μs

- ▶ 13段のイコライザに適用可能なプログラマブルな倍精度MACエンジン

- ▶ 3つのアナログ入力（2つの差動および1つのシングルエンド）、マイクロフォン入力またはライン入力として設定可能

- ▶ アナログ差動オーディオ出力、ライン出力またはヘッドフォン・ドライバとして設定可能

- ▶ PLLは30kHz～27MHzの任意の入力クロック・レートに対応

- ▶ 自動キャリブレーションの対応した内蔵RC発振器

- ▶ 1チャンネルASRCI、3チャンネルASRCO

- ▶ シリアル・オーディオ・ポートはI2S、左詰め、または最大16チャンネルのTDM（TDM16）に対応

- ▶ 柔軟なルーティングが可能な2個のインターポレータと4個のデシメータ

- ▶ 電源

- ▶ アナログAVDD：1.8V（代表値）

- ▶ デジタルI/O IOVDD：1.8V～3.3V

- ▶ ヘッドフォンHPVDD：1.8V（代表値）

- ▶ ヘッドフォンHPVDD\_L：1.2V～1.8V

- ▶ 制御／通信インターフェース

- ▶ I<sup>2</sup>C、SPI、またはUART

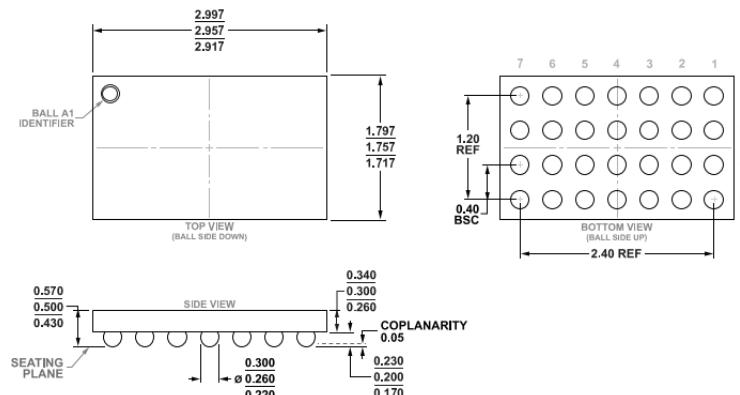

- ▶ 28ポール、0.4mmピッチ、2.957mm × 1.757mm WLCSP

### 概要

**ADAU1850**は、1つのデジタル・シグナル・プロセッサを内蔵した3入力、1出力のコーデックです。アナログ入力からDSPコアを経由してアナログ出力にいたる経路は、低遅延に最適化されておりノイズ・キャンセリング・イヤフォンに最適です。ADAU1850は、少数の受動部品を追加するだけでフル機能のイヤフォン・ソリューションを実現します。

ADAU1850は、28ポール、2.957 mm × 1.757 mmの小型ウェーハ・レベル・チップ・スケール・パッケージ（WLCSP）を採用しています。

### アプリケーション

- ▶ ノイズ・キャンセリング機能を備えたハンドセット、ヘッドセット、ヘッドフォン

- ▶ Bluetoothアクティブ・ノイズ・キャンセリング（ANC）機能を備えたハンドセット、ヘッドセット、ヘッドフォン

- ▶ 個人向けナビゲーション機器

- ▶ デジタル・ステレオ・カメラおよびビデオ・カメラ

- ▶ 楽器用エフェクト・プロセッサ

- ▶ マルチメディア・スピーカ・システム

- ▶ スマートフォン

## 目次

|              |    |                |    |

|--------------|----|----------------|----|

| 特長           | 1  | 静電放電 (ESD) 定格  | 14 |

| アプリケーション     | 1  | ESDに関する注意      | 14 |

| 概要           | 1  | ピン配置およびピン機能の説明 | 15 |

| 機能ブロック図      | 3  | 代表的な性能特性       | 17 |

| 仕様           | 4  | 動作原理           | 24 |

| アナログ性能の仕様    | 4  | アプリケーション情報     | 25 |

| デジタル入出力の仕様   | 9  | 電源のバイパス・コンデンサ  | 25 |

| 電源仕様         | 9  | レイアウト          | 25 |

| パワーダウン電流     | 9  | グラウンド接続        | 25 |

| 代表的な消費電力     | 10 | 外形寸法           | 26 |

| デジタル・フィルタ    | 10 | オーダー・ガイド       | 26 |

| デジタル・タイミング仕様 | 11 | 評価用ボード         | 26 |

| 絶対最大定格       | 14 |                |    |

| 熱抵抗          | 14 |                |    |

## 改訂履歴

### 5/2022—Rev. 0 to Rev. A

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| Changes to Features Section                                               | 1  |

| Changes to Figure 1                                                       | 3  |

| Changes to Table 1                                                        | 4  |

| Change to Figure 6                                                        | 15 |

| Change to Figure 12                                                       | 17 |

| Changes to Figure 14 and Figure 18                                        | 18 |

| Change to Figure 41                                                       | 22 |

| Changes to Figure 43, Figure 45, Figure 46 Caption, and Figure 47 Caption | 23 |

| Changes to Theory of Operation Section                                    | 24 |

### 7/2021—Revision 0: Initial Version

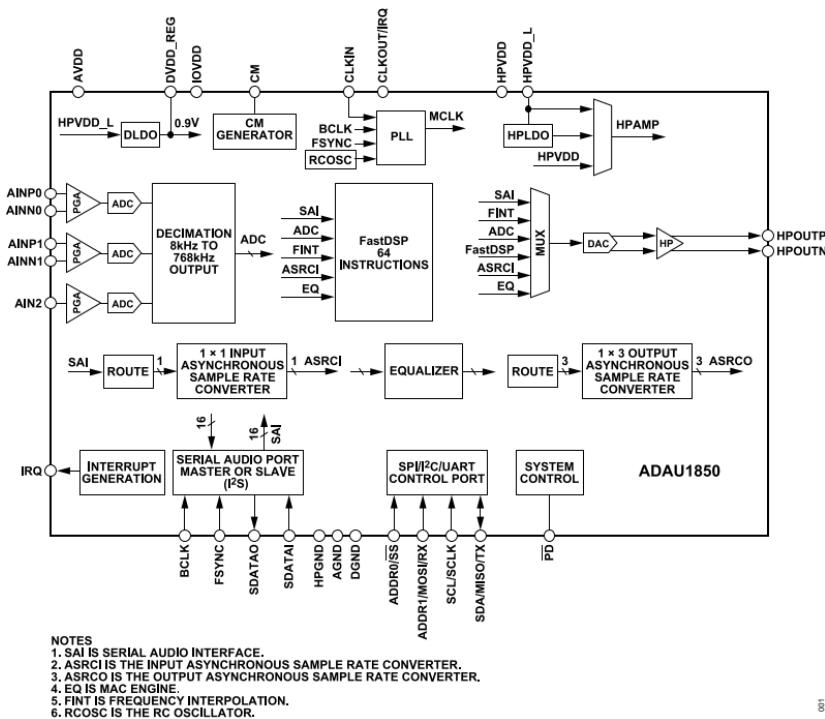

## 機能ブロック図

001

図 1.

## 仕様

特に指定のない限り、マスター・クロック = 24.576MHz、シリアル入力サンプル・レート = 48kHz、測定帯域幅 = 20Hz~20kHz、ワード幅 = 24ビット、周囲温度 (TA) = 25°C、ライン出力負荷 = 10kΩ。

### アナログ性能の仕様

電源電圧：特に指定のない限り、AVDD = HPVDD = IOVDD = 1.8V、HPVDD\_L = 1.2V。

表 1.

| パラメータ <sup>1</sup>                                    | テスト条件/コメント                      | 最小値    | 代表値 | 最大値 | 単位    |

|-------------------------------------------------------|---------------------------------|--------|-----|-----|-------|

| ANALOG-TO-DIGITAL CONVERTERS (ADCs)                   |                                 |        |     |     |       |

| ADC Resolution                                        | 全ADC                            | 24     |     |     | Bits  |

| Digital Gain Step                                     |                                 | 0.375  |     |     | dB    |

| Digital Gain Range                                    |                                 | -71.25 | +24 |     | dB    |

| INPUT RESISTANCE ( $R_{IN}$ )                         |                                 |        |     |     |       |

| Single-Ended Line Input                               | 非音声ウェイクアップ・モード                  | 9      |     |     | kΩ    |

|                                                       | 音声ウェイクアップ・モード                   | 18     |     |     | kΩ    |

| Differential Line Input                               | 非音声ウェイクアップ・モード                  | 36     |     |     | kΩ    |

|                                                       | 音声ウェイクアップ・モード                   | 36     |     |     | kΩ    |

| Programmable Gain Amplifier (PGA) Single-Ended Inputs | PGAハイ $R_{IN}$ 、通常、0dBゲイン       | 20.6   |     |     | kΩ    |

|                                                       | PGAハイ $R_{IN}$ 、通常、24dBゲイン      | 2.4    |     |     | kΩ    |

|                                                       | PGAローラー $R_{IN}$ 、拡張、0dBゲイン     | 10.3   |     |     | kΩ    |

|                                                       | PGAローラー $R_{IN}$ 、拡張、24dBゲイン    | 1.2    |     |     | kΩ    |

| PGA Differential Inputs                               | PGAハイ $R_{IN}$ 、通常、0dBゲイン       | 41.2   |     |     | kΩ    |

|                                                       | PGAハイ $R_{IN}$ 、通常、24dBゲイン      | 4.8    |     |     | kΩ    |

|                                                       | PGAローラー $R_{IN}$ 、拡張、0dBゲイン     | 20.6   |     |     | kΩ    |

|                                                       | PGAローラー $R_{IN}$ 、拡張、24dBゲイン    | 2.4    |     |     | kΩ    |

| SINGLE-ENDED LINE INPUT                               | PGAx_EN = 0およびPGAx_SLEW_DIS = 1 |        |     |     |       |

| Full-Scale Input Voltage                              | 0dBFS                           | 0.49   |     |     | V rms |

|                                                       | 0dBFS                           | 1.39   |     |     | V p-p |

| Dynamic Range <sup>2</sup>                            | 20Hz~20kHz、-60dBの入力             |        |     |     |       |

| With A-Weighted Filter (RMS)                          | 強化性能                            | 102    |     |     | dB    |

|                                                       | 通常性能                            | 102    |     |     | dB    |

|                                                       | 節電                              | 101    |     |     | dB    |

|                                                       | 音声ウェイクアップ                       | 95     |     |     | dB    |

| With Flat 20 Hz to 20 kHz Filter                      | 強化性能                            | 98     |     |     | dB    |

|                                                       | 通常性能                            | 98     |     |     | dB    |

|                                                       | 節電                              | 97     |     |     | dB    |

|                                                       | 音声ウェイクアップ                       | 94     |     |     | dB    |

| Signal-to-Noise Ratio (SNR) <sup>3</sup>              |                                 |        |     |     |       |

| With A-Weighted Filter (RMS)                          | 強化性能                            | 102    |     |     | dB    |

|                                                       | 通常性能                            | 102    |     |     | dB    |

|                                                       | 節電                              | 101    |     |     | dB    |

|                                                       | 音声ウェイクアップ                       | 95     |     |     | dB    |

| With Flat 20 Hz to 20 kHz Filter                      | 強化性能                            | 98     |     |     | dB    |

|                                                       | 通常性能                            | 98     |     |     | dB    |

|                                                       | 節電                              | 97     |     |     | dB    |

|                                                       | 音声ウェイクアップ                       | 94     |     |     | dB    |

## 仕様

表 1.

| パラメータ <sup>1</sup>                          | テスト条件/コメント                                                  | 最小値  | 代表値 | 最大値 | 単位    |

|---------------------------------------------|-------------------------------------------------------------|------|-----|-----|-------|

| Interchannel Gain Mismatch                  |                                                             | 40   |     |     | dB    |

| Total Harmonic Distortion + Noise (THD + N) | 20Hz～20kHz、-1dB フルスケール出力<br>強化性能<br>通常性能<br>節電<br>音声ウェイクアップ | -81  | -81 | -81 | dBFS  |

| Offset Error                                |                                                             | ±0.3 |     |     | mV    |

| Gain Error                                  |                                                             | ±0.2 |     |     | dB    |

| Interchannel Isolation                      | CMコンデンサ = 1μF                                               | 100  |     |     | dB    |

| Power Supply Rejection Ratio (PSRR)         | CMコンデンサ = 1μF<br>100mV p-p (1kHz時)<br>100mV p-p (10kHz時)    | 60   | 60  | 40  | dB    |

| DIFFERENTIAL LINE INPUT                     | PGAx_EN = 0、PGAx_SLEW_DIS = 1                               |      |     |     |       |

| Full-Scale Input Voltage                    | 0dBFS                                                       | 0.98 |     |     | V rms |

|                                             | 0dBFS                                                       | 2.78 |     |     | V p-p |

| Dynamic Range <sup>1</sup>                  | 20Hz～20kHz、-60dBの入力                                         |      |     |     |       |

| With A-Weighted Filter (RMS)                | 強化性能<br>通常性能<br>節電<br>音声ウェイクアップ                             | 106  | 106 | 100 | dB    |

| With Flat 20 Hz to 20 kHz Filter            | 強化性能<br>通常性能<br>節電<br>音声ウェイクアップ                             | 103  | 103 | 103 | dB    |

|                                             |                                                             | 99   |     |     | dB    |

| Signal-to-Noise Ratio (SNR) <sup>3</sup>    |                                                             |      |     |     |       |

| With A-Weighted Filter (RMS)                | 強化性能<br>通常性能<br>節電<br>音声ウェイクアップ                             | 106  | 106 | 100 | dB    |

| With Flat 20 Hz to 20 kHz Filter            | 強化性能<br>通常性能<br>節電<br>音声ウェイクアップ                             | 103  | 103 | 103 | dB    |

|                                             |                                                             | 99   |     |     | dB    |

| Interchannel Gain Mismatch                  |                                                             | 40   |     |     | dB    |

| Total Harmonic Distortion + Noise (THD + N) | 20Hz～20kHz、-1dB フルスケール出力<br>強化性能<br>通常性能<br>節電<br>音声ウェイクアップ | -96  | -96 | -96 | dBFS  |

| Offset Error                                |                                                             | ±0.2 |     |     | mV    |

| Gain Error                                  |                                                             | ±0.2 |     |     | dB    |

| Interchannel Isolation                      | CMコンデンサ = 1μF                                               | 100  |     |     | dB    |

| Power Supply Rejection Ratio (PSRR)         | CMコンデンサ = 1μF<br>100mV p-p (1kHz時)<br>100mV p-p (10kHz時)    | 70   | 70  | 65  | dB    |

## 仕様

表 1.

| パラメータ <sup>1</sup>                  | テスト条件/コメント          | 最小値  | 代表値   | 最大値 | 単位 |

|-------------------------------------|---------------------|------|-------|-----|----|

| SINGLE-ENDED PGA INPUT              | PGAx_EN = 1         |      |       |     |    |

| Full-Scale Input Voltage            | 0dBFS               | 0.49 | V rms |     |    |

|                                     | 0dBFS               | 1.39 | V p-p |     |    |

| Dynamic Range <sup>2</sup>          | 20Hz~20kHz、-60dBの入力 |      |       |     |    |

| With A-Weighted Filter (RMS)        | 強化性能                | 101  | dB    |     |    |

|                                     | 通常性能                | 100  | dB    |     |    |

|                                     | 節電                  | 100  | dB    |     |    |

|                                     | 音声ウェイクアップ           | 94   | dB    |     |    |

| With Flat 20 Hz to 20 kHz Filter    | 強化性能                | 97   | dB    |     |    |

|                                     | 通常性能                | 96   | dB    |     |    |

|                                     | 節電                  | 96   | dB    |     |    |

|                                     | 音声ウェイクアップ           | 94   | dB    |     |    |

| Signal-to-Noise Ratio <sup>3</sup>  |                     |      |       |     |    |

| With A-Weighted Filter (RMS)        | 強化性能                | 101  | dB    |     |    |

|                                     | 通常性能                | 100  | dB    |     |    |

|                                     | 節電                  | 100  | dB    |     |    |

|                                     | 音声ウェイクアップ           | 94   | dB    |     |    |

| With Flat 20 Hz to 20 kHz Filter    | 強化性能                | 97   | dB    |     |    |

|                                     | 通常性能                | 96   | dB    |     |    |

|                                     | 節電                  | 96   | dB    |     |    |

|                                     | 音声ウェイクアップ           | 94   | dB    |     |    |

| Total Harmonic Distortion + Noise   | 20Hz~20kHz、-1dBFS   |      |       |     |    |

|                                     | 強化性能                | -81  | dBFS  |     |    |

|                                     | 通常性能                | -81  | dBFS  |     |    |

|                                     | 節電                  | -81  | dBFS  |     |    |

|                                     | 音声ウェイクアップ           | -81  | dBFS  |     |    |

| PGA Gain Range                      |                     | 0    | 24    |     | dB |

| PGA Gain Variation                  |                     |      |       |     |    |

| With 0 dB Setting                   | 標準偏差                | 0.05 | dB    |     |    |

| With 24 dB Setting                  | 標準偏差                | 0.15 | dB    |     |    |

| Interchannel Gain Mismatch          |                     | 50   | mdB   |     |    |

| Offset Error                        |                     | 0.3  | mV    |     |    |

| Gain Error                          |                     | ±0.2 | dB    |     |    |

| Interchannel Isolation              | CMコンデンサ = 1μF       | 83   | dB    |     |    |

| Power Supply Rejection Ratio (PSRR) | CMコンデンサ = 1μF       |      |       |     |    |

|                                     | 100mV p-p (1kHz時)   | 60   | dB    |     |    |

|                                     | 100mV p-p (10kHz時)  | 50   | dB    |     |    |

| DIFFERENTIAL PGA INPUT              | PGAx_EN = 1         |      |       |     |    |

| Full-Scale Input Voltage            | 0dBFS               | 0.98 | V rms |     |    |

|                                     | 0dBFS               | 2.78 | V p-p |     |    |

| Dynamic Range <sup>1</sup>          | 20Hz~20kHz、-60dBの入力 |      |       |     |    |

| With A-Weighted Filter (RMS)        | 強化性能                | 104  | dB    |     |    |

|                                     | 通常性能                | 103  | dB    |     |    |

## 仕様

表 1.

| パラメータ <sup>1</sup>                  | テスト条件/コメント                                                         | 最小値                                                | 代表値 | 最大値 | 単位    |

|-------------------------------------|--------------------------------------------------------------------|----------------------------------------------------|-----|-----|-------|

| With Flat 20 Hz to 20 kHz Filter    | 節電<br>音声ウェイクアップ<br>強化性能<br>通常性能<br>節電<br>音声ウェイクアップ                 | 103<br>97<br>102<br>101<br>101<br>96               |     |     | dB    |

| Signal-to-Noise Ratio <sup>3</sup>  | 強化性能<br>通常性能<br>節電<br>音声ウェイクアップ<br>強化性能<br>通常性能<br>節電<br>音声ウェイクアップ | 104<br>103<br>103<br>97<br>102<br>101<br>101<br>96 |     |     | dB    |

| With A-Weighted Filter (RMS)        | 20Hz～20kHz、-1dBFS                                                  |                                                    |     |     | d     |

| With Flat 20 Hz to 20 kHz Filter    | 強化性能<br>通常性能<br>節電<br>音声ウェイクアップ                                    | 103<br>101<br>101<br>96                            |     |     | dB    |

| Total Harmonic Distortion + Noise   | 20Hz～20kHz、-1dBFS<br>強化性能<br>通常性能<br>節電<br>音声ウェイクアップ               | -95<br>-95<br>-95<br>-93                           |     |     | dBFS  |

| PGA Gain Range                      | 0                                                                  | 24                                                 |     |     | dB    |

| PGA Gain Variation                  |                                                                    |                                                    |     |     |       |

| With 0 dB Setting                   | 標準偏差                                                               | 0.05                                               |     |     | dB    |

| With 24 dB Setting                  | 標準偏差                                                               | 0.15                                               |     |     | dB    |

| Interchannel Gain Mismatch          |                                                                    | 0.04                                               |     |     | mdB   |

| Offset Error                        |                                                                    | ±0.2                                               |     |     | mV    |

| Gain Error                          |                                                                    | ±0.2                                               |     |     | dB    |

| Interchannel Isolation              | CMコンデンサ = 1μF                                                      | 100                                                |     |     | dB    |

| Power Supply Rejection Ratio (PSRR) | CMコンデンサ = 1μF<br>100mV p-p (1kHz時)<br>100mV p-p (10kHz時)           | 70<br>65                                           |     |     | dB    |

| DIGITAL-TO-ANALOG CONVERTERS (DACs) |                                                                    |                                                    |     |     |       |

| Internal Converter Resolution       | 全D/Aコンバータ (DAC)                                                    | 24                                                 |     |     | Bits  |

| Digital Gain                        |                                                                    |                                                    |     |     |       |

| Step                                |                                                                    | 0.375                                              |     |     | dB    |

| Range                               |                                                                    | -71.25                                             | +24 |     | dB    |

| Ramp Rate                           |                                                                    | 4.5                                                |     |     | dB/ms |

| DAC DIFFERENTIAL OUTPUT             |                                                                    |                                                    |     |     |       |

| Full-Scale Output Voltage           | 差動動作<br>DACに対し0dBFS                                                | 1.0 V                                              |     |     | Vrms  |

| Dynamic Range <sup>2</sup>          | 20Hz～20kHz、-60dBの入力                                                |                                                    |     |     |       |

| With A-Weighted Filter (RMS)        | 強化性能<br>通常性能                                                       | 110<br>105                                         |     |     | dB    |

| With Flat 20 Hz to 20 kHz Filter    | 強化性能<br>通常性能                                                       | 107<br>102                                         |     |     | dB    |

## 仕様

表 1.

| パラメータ <sup>1</sup>                           | テスト条件/コメント                              | 最小値  | 代表値    | 最大値  | 単位    |

|----------------------------------------------|-----------------------------------------|------|--------|------|-------|

| Signal-to-Noise Ratio <sup>3</sup>           | 20Hz～20kHz                              |      |        |      |       |

| With A-Weighted Filter (RMS)                 | 強化性能                                    | 110  |        |      | dB    |

|                                              | 通常性能                                    | 105  |        |      | dB    |

| With Flat 20 Hz to 20 kHz Filter             | 強化性能                                    | 107  |        |      | dB    |

|                                              | 通常性能                                    | 102  |        |      | dB    |

| Total Harmonic Distortion + Noise Level      | ヘッドフォン・モード                              |      |        |      |       |

| 32 Ω Load                                    | -15dBFS入力、出力電力 ( $P_{OUT}$ ) = 1mW、強化性能 | -96  |        |      | dBV   |

|                                              | -15dBFS入力、 $P_{OUT}$ = 1mW、通常性能         | -85  |        |      | dBV   |

|                                              | -1dBFS入力、強化性能                           | -89  |        |      | dBV   |

|                                              | -1dBFS入力、通常性能                           | -80  |        |      | dBV   |

| 24 Ω Load                                    | -2dBFS入力、強化性能                           | -89  |        |      | dBV   |

|                                              | -2dBFS入力、通常性能                           | 80   |        |      | dBV   |

| 16 Ω Load                                    | -3dBFS入力、強化性能                           | -89  |        |      | dBV   |

|                                              | -3dBFS入力、通常性能                           | -80  |        |      | dBV   |

| 32 Ω Load                                    | 低電圧モード、 $P_{OUT}$ = 10mW、強化性能           | 30   |        |      | mW    |

| Gain Error                                   |                                         | ±2.5 |        |      | %     |

| DC Offset                                    |                                         | ±0.1 |        |      | mV    |

| Power Supply Rejection Ratio                 | CMコンデンサ = 1μF                           |      |        |      |       |

| HPVDD                                        | 100mV p-p (1kHz時)                       | 80   |        |      | dB    |

|                                              | 100mV p-p (10kHz時)                      | 80   |        |      | dB    |

| HPVDD_L (Low Dropout Regulator (LDO) Bypass) | 100mV p-p (1kHz時)                       | 85   |        |      | dB    |

|                                              | 100mV p-p (10kHz時)                      | 85   |        |      | dB    |

| AVDD Undervoltage Trip Point                 |                                         | 1.5  |        |      | V     |

| CM REFERENCE                                 | CMピン                                    |      |        |      |       |

| Output                                       |                                         | 0.85 |        |      | V     |

| Source Impedance                             |                                         | 5    |        |      | kΩ    |

| PHASE LOCKED LOOP (PLL)                      |                                         |      |        |      |       |

| Input Frequency                              | 入力プリスケール後                               | 0.03 | 36     |      | MHz   |

| Output Frequency                             |                                         |      | 24.576 |      | MHz   |

| Fractional Limits                            | フラクショナル・モード、フラクショナル部分 (分子 (N) / 分母 (M)) | 0.1  | 0.9    |      |       |

| Integer Limits                               | フラクショナル・モード、インテジャー部分                    | 2    | 3072   |      |       |

| Lock Time                                    | 48kHz入力                                 |      | 6.5    |      | ms    |

|                                              | 12.288MHz入力                             |      | 0.46   | 0.55 | ms    |

| INTERNAL RC OSCILLATOR                       |                                         |      |        |      |       |

| Output Frequency                             | パワーオン後                                  | 21   | 30     |      | MHz   |

| DVDD REGULATOR                               |                                         |      |        |      |       |

| Line Regulation                              |                                         | 1    |        |      | mV/V  |

| Load Regulation                              |                                         | 0.5  |        |      | mV/mA |

1 レジスタの詳細については、ADAU1850ハードウェア・リファレンス・マニュアルを参照してください。

2 ダイナミック・レンジは、-60dBFSの信号が存在する場合の対象帯域でのノイズおよび高調波電力の総和とフルスケール電力レベルとの比で、単位はデシベルです。

3 S/N比は、信号が存在しない場合の対象帯域での全ノイズ電力の総和とフルスケール電力レベルとの比で、単位はデシベルです。

## 仕様

### デジタル入出力の仕様

特に指定のない限り、 $-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ 、 $\text{IOVDD} = 1.8\text{V} \sim 3.3\text{V}$ 。

表 2.

| パラメータ               | 記号       | テスト条件／コメント                                         | 最小値         | 代表値          | 最大値 | 単位 |

|---------------------|----------|----------------------------------------------------|-------------|--------------|-----|----|

| INPUT VOLTAGE       |          |                                                    |             |              |     |    |

| High                | $V_{IH}$ |                                                    |             |              |     | V  |

| Low                 | $V_{IL}$ |                                                    |             |              |     | V  |

| INPUT LEAKAGE       |          |                                                    |             |              |     |    |

| High                | $V_{IH}$ | $\text{IOVDD} = 1.8\text{V}, V_{IH} = 1.1\text{V}$ |             |              | 10  | V  |

| Low                 | $V_{IL}$ | $V_{IL} = 0.45\text{V}$                            |             |              | 10  | V  |

| OUTPUT VOLTAGE HIGH | $V_{OH}$ |                                                    |             |              |     |    |

| Drive Strength      |          |                                                    |             |              |     |    |

| Low                 |          | 出力ハイ電流 ( $I_{OH}$ ) = 1mA                          | 0.7 × IOVDD | 0.83 × IOVDD |     | V  |

| High                |          | $I_{OH} = 3\text{mA}$                              | 0.7 × IOVDD | 0.83 × IOVDD |     | V  |

| OUTPUT VOLTAGE LOW  | $V_{OL}$ |                                                    |             |              |     |    |

| Drive Strength      |          |                                                    |             |              |     |    |

| Low                 |          | 出力ロー電流 ( $I_{OL}$ ) = 1mA                          | 0.1 × IOVDD | 0.3 × IOVDD  |     | V  |

| High                |          | $I_{OL} = 3\text{mA}$                              | 0.1 × IOVDD | 0.3 × IOVDD  |     | V  |

| INPUT CAPACITANCE   |          |                                                    |             |              | 5   | pF |

### 電源仕様

電源電圧：特に指定のない限り、 $\text{AVDD} = \text{HPVDD} = \text{IOVDD} = 1.8\text{V}$ 。デジタル入出力（I/O）ラインに25pFの負荷を使用。

表 3.

| Parameter       | Min  | Typ | Max   | Unit |

|-----------------|------|-----|-------|------|

| SUPPLIES        |      |     |       |      |

| AVDD Voltage    | 1.7  | 1.8 | 1.98  | V    |

| HPVDD Voltage   | 1.7  | 1.8 | 1.98  | V    |

| IOVDD Voltage   | 1.62 |     | 3.63  | V    |

| HPVDD_L Voltage | 1.17 |     | HPVDD | V    |

### ノーワードダウン電流

電源電圧： $\text{AVDD} = \text{HPVDD} = \text{IOVDD} = 1.8\text{V}$ 、 $\text{HPVDD\_L} = 1.2\text{V}$ 。PLLをディスエーブルかつバイパス。

表 4.

| Parameter                        | AVDD Current |     |     | DVDD Current |     |     | IOVDD Current |     |     | Unit |

|----------------------------------|--------------|-----|-----|--------------|-----|-----|---------------|-----|-----|------|

|                                  | Min          | Typ | Max | Min          | Typ | Max | Min           | Typ | Max |      |

| PD PIN LOW (HARDWARE POWER-DOWN) | 4.4          |     |     | 2.1          |     |     | 0.7           |     |     | μA   |

| POWER_EN = 0                     |              |     |     |              |     |     |               |     |     |      |

| No Keep Alives                   | 75           |     |     | 187          |     |     | 23            |     |     | μA   |

| KEEP_MEM = 1                     | 75           |     |     | 187          |     |     | 23            |     |     | μA   |

## 代表的な消費電力

内部クロック = 24.576MHz、PLLディスエーブル、AVDD = HPVDD = IOVDD = 1.8V、HPVDD\_L = 1.2V（外部供給）。該当の場合、ADC0およびADC1は192kHzの差動モードで動作、ADC2は192kHzで動作。FastDSP™は192kHzで動作（27ビット精度のバイクワッド・フィルタ）。DACは192kHzで動作、DAC\_LPM = 0。1つのシリアル・ポート入出力をスレーブに設定し、32Ωのヘッドフォン負荷を使用。DVDD電流はHPVDD\_Lピンで測定、DAC HPAMP（ヘッドフォン・アンプ）は通常電圧モードで動作。静止電流（無信号）。

表 5. 様々な構成での電源電流

| ADC Channels | DAC Channels | ASRCI/ ASRCO Channels | FastDSP Instructions | Interpolator/ Decimator Channels | Equalizer | DVDD Current (mA) | AVDD Current (mA) | IOVDD Current (mA) |

|--------------|--------------|-----------------------|----------------------|----------------------------------|-----------|-------------------|-------------------|--------------------|

| 2            | 1            | 0/0                   | 32                   | 0                                | 0         | 1.051             | 2.326             | 0.024              |

| 3            | 1            | 1/3                   | 40                   | 0                                | 1         | 2.221             | 2.733             | 0.154              |

| 1            | 1            | 1/1                   | 0                    | 0                                | 1         | 1.052             | 1.818             | 0.090              |

| 2            | 1            | 1/0                   | 32                   | 0                                | 1         | 1.643             | 2.327             | 0.024              |

| 0            | 1            | 1/0                   | 0                    | 0                                | 1         | 0.846             | 0.995             | 0.024              |

異なる電力モードでの代表的なアクティブ・ノイズ・キャンセリング（ANC）設定。マスタ・クロック = 24.576MHz（PLLをバイパスかつディスエーブル）。AVDD = HPVDD = IOVDD = 1.8V、HPVDD\_L = 1.2V（外部供給）。2つのADCはPGAを用いず、差動モードに設定。DACは低電圧モード（HPVDD\_Lから供給）で差動ヘッドフォン動作に設定。DAC出力の負荷は32Ω、1mW出力でDAC\_LPM = 0。FastDSPは32個の命令（27ビット精度のバイクワッド・フィルタ）を192kHzで実行。DVDD電流はHPVDD\_Lピンで測定されます。

表 6.

| Operating Voltage                      | Power Management Setting                 | Typical Current (mA) |       |       | Total Power Consumption (mW) |

|----------------------------------------|------------------------------------------|----------------------|-------|-------|------------------------------|

|                                        |                                          | AVDD                 | DVDD  | IOVDD |                              |

| AVDD = IOVDD = 1.8 V<br>HPVDD_L = 1.2V | ADC power saving mode, DAC normal mode   | 1.513                | 5.961 | 0.024 | 9.92                         |

|                                        | ADC power saving mode, DAC enhanced mode | 1.966                | 6.007 | 0.024 | 10.79                        |

## デジタル・フィルタ

表 7.

| パラメータ                                   | テスト条件/コメント                                                                                | 最小値  | 代表値            | 最大値            | 単位   |

|-----------------------------------------|-------------------------------------------------------------------------------------------|------|----------------|----------------|------|

| ADC INPUT TO DAC OUTPUT PATH            |                                                                                           |      |                |                |      |

| Pass-Band Ripple                        | DC～20kHz、サンプリング周波数 ( $f_s$ ) = 192kHz (ADC_FCOMP = 1、DAC_FCOMP = 1)                       |      |                | ±0.02          | dB   |

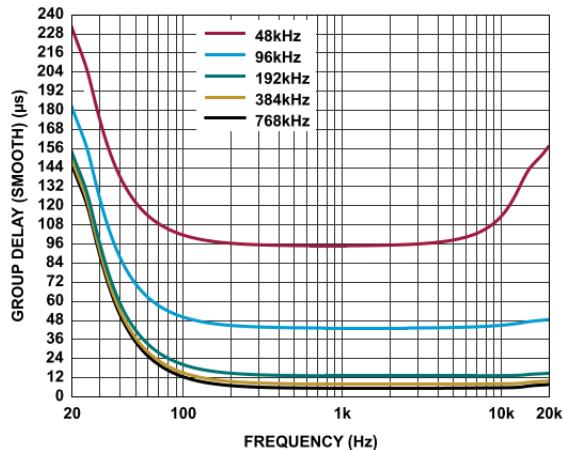

| Group Delay <sup>1</sup>                | $f_s = 192\text{kHz}$<br>$f_s = 384\text{kHz}$<br>$f_s = 768\text{kHz}$                   |      | 12.9           |                | μs   |

|                                         |                                                                                           |      | 7.5            |                | μs   |

|                                         |                                                                                           |      | 5              |                | μs   |

| SAMPLE RATE CONVERTER                   |                                                                                           |      |                |                |      |

| Pass Band                               | FSYNC < 63kHz<br>63kHz < FSYNC < 112kHz<br>FSYNC > 112kHz                                 |      |                | 0.475 × $f_s$  | kHz  |

|                                         |                                                                                           |      |                | 0.4286 × $f_s$ | kHz  |

|                                         |                                                                                           |      | 0.2383 × $f_s$ |                | kHz  |

| Audio Band Ripple                       | 20Hz～20kHz                                                                                | -0.1 | +0.1           |                | dB   |

| Input and Output Sample Frequency Range |                                                                                           | 7    | 224            |                | kHz  |

| Dynamic Range                           | ASRCx_LPM = 0<br>ASRCx_LPM = 1<br>ASRCx_LPM_II = 1                                        |      | 130            |                | dB   |

|                                         |                                                                                           |      | 130            |                | dB   |

|                                         |                                                                                           |      | 130            |                | dB   |

| THD + N                                 | 20Hz～20kHz、入力周波数の代表値は1kHz、最大値は20kHz<br>ASCRx_LPM = 0<br>ASCRx_LPM = 1<br>ASCRx_LPM_II = 1 |      | -130           | -120           | dBFS |

|                                         |                                                                                           |      | -120           | -110           | dBFS |

|                                         |                                                                                           |      | -115           | -90            | dBFS |

| Start-Up Time to Lock                   |                                                                                           |      |                | 25             | ms   |

1 ゼロ命令を使用してFastDSPで測定した群遅延。

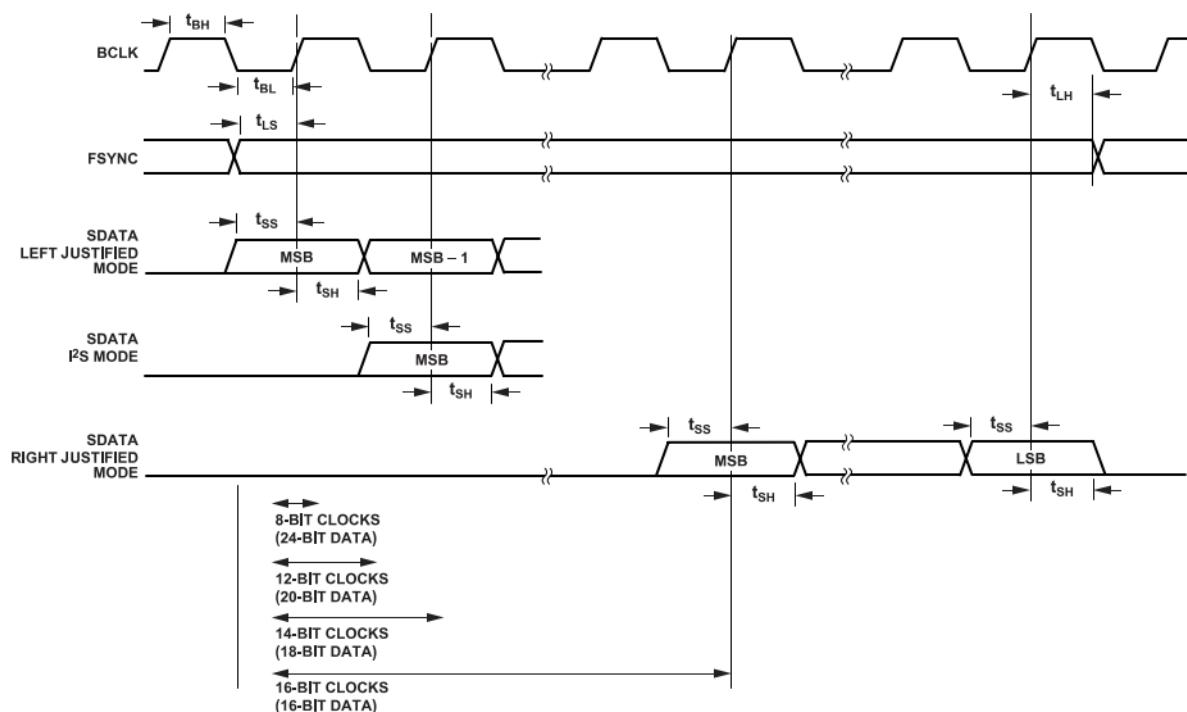

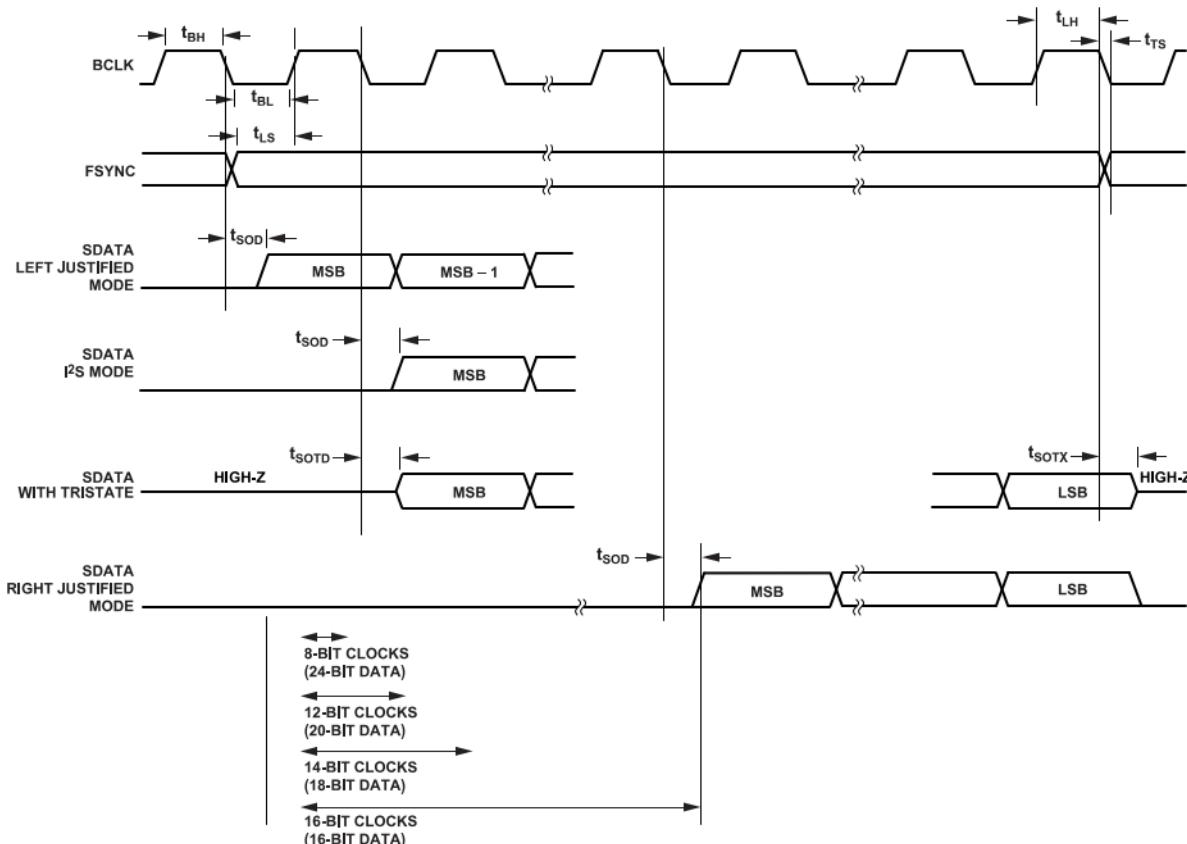

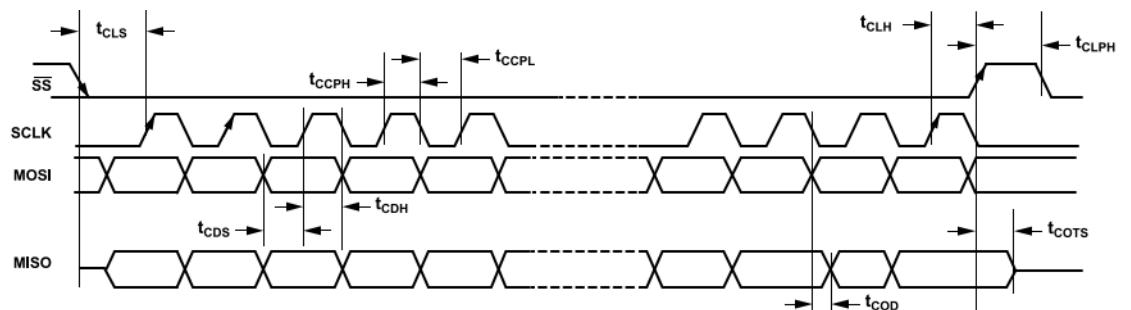

## デジタル・タイミング仕様

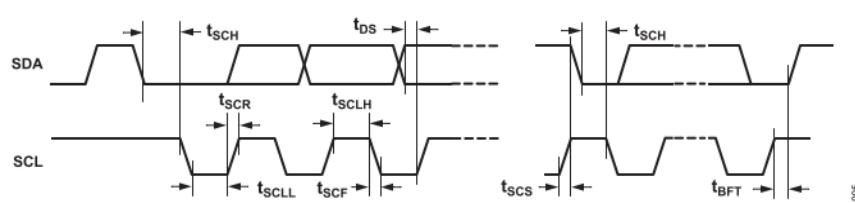

$-40^{\circ}\text{C} < T_{\text{A}} < +85^{\circ}\text{C}$ 、 $\text{IOVDD} = 1.8\text{V} \sim 3.3\text{V}$ 。SCL/SCLKなどの多機能ピンは、1つの機能のみが該当する場合には、その1つの機能（例：SCLK）で表しています。ピン名と説明の全リストについては、[ピン配置およびピン機能の説明](#)のセクションを参照してください。

表 8. デジタル・タイミング

| Parameter                              | Min   | Typ | Max    | Unit          | Description                                                                            |

|----------------------------------------|-------|-----|--------|---------------|----------------------------------------------------------------------------------------|

| MASTER CLOCK                           |       |     |        |               |                                                                                        |

| $t_{\text{MPI}}$                       | 0.037 |     | 33.3   | $\mu\text{s}$ | CLKIN period<br>30 kHz to 27 MHz input clock using PLL in integer mode                 |

| $t_{\text{MPF}}$                       | 0.037 |     | 1.0    | $\mu\text{s}$ | 1 MHz to 27 MHz input clock using PLL in fractional mode                               |

| SERIAL PORT                            |       |     |        |               | See <a href="#">Figure 2</a> and <a href="#">Figure 3</a>                              |

| $t_{\text{BL}}$                        | 18    |     |        | ns            | BCLK low pulse width (master and slave modes)                                          |

| $t_{\text{BH}}$                        | 18    |     |        | ns            | BCLK high pulse width (master and slave modes)                                         |

| $f_{\text{BCLK}}$                      | 0.512 |     | 24.576 | MHz           | BCLK frequency                                                                         |

| $t_{\text{LS}}$                        | 3     |     |        | ns            | FSYNC setup, time to BCLK rising (slave mode)                                          |

| $t_{\text{LH}}$                        | 5     |     |        | ns            | FSYNC hold, time from BCLK rising (slave mode)                                         |

| $f_{\text{SYNC}}$                      | 8     |     | 768    | kHz           | FSYNC frequency                                                                        |

| $t_{\text{SS}}$                        | 3     |     |        | ns            | SDATAI setup, time to BCLK rising (master and slave modes)                             |

| $t_{\text{SH}}$                        | 10    |     |        | ns            | SDATAI hold, time from BCLK rising (master and slave modes)                            |

| $t_{\text{TS}}$                        |       | 6   |        | ns            | BCLK falling to FSYNC timing skew (master mode)                                        |

| $t_{\text{SOD}}$                       | 0     | 16  |        | ns            | SDATAO delay, time from BCLK falling (master and slave modes), IOVDD at 1.62 V minimum |

|                                        | 0     | 32  |        | ns            | SDATAO delay, time from BCLK falling (master and slave modes), IOVDD at 1.1 V minimum  |

| $t_{\text{SOTD}}$                      | 0     | 16  |        | ns            | BCLK falling to SDATAO driven in tristate mode                                         |

| $t_{\text{SOTX}}$                      | 0     | 16  |        | ns            | BCLK falling to SDATAO tristated in tristate mode                                      |

| SERIAL PERIPHERAL INTERFACE (SPI) PORT |       |     |        |               | See <a href="#">Figure 4</a>                                                           |

| $f_{\text{SCLK}}$                      |       | 24  |        | MHz           | SCLK frequency                                                                         |

| $t_{\text{CCPL}}$                      | 15    |     |        | ns            | SCLK pulse width low                                                                   |

| $t_{\text{COPH}}$                      | 15    |     |        | ns            | SCLK pulse width high                                                                  |

| $t_{\text{CLS}}$                       | 4     |     |        | ns            | $\overline{\text{SS}}$ setup, time to SCLK rising                                      |

| $t_{\text{CLH}}$                       | 18    |     |        | ns            | $\overline{\text{SS}}$ hold, time from SCLK rising                                     |

| $t_{\text{CLPH}}$                      | 10    |     |        | ns            | $\overline{\text{SS}}$ pulse width high                                                |

| $t_{\text{CDS}}$                       | 8     |     |        | ns            | MOSI setup, time to SCLK rising                                                        |

| $t_{\text{CDH}}$                       | 6     |     |        | ns            | MOSI hold, time from SCLK rising                                                       |

| $t_{\text{COD}}$                       |       | 17  |        | ns            | MISO delay, time from SCLK falling                                                     |

| $t_{\text{COTS}}$                      |       | 24  |        | ns            | MISO high-Z, time from $\overline{\text{SS}}$ rising                                   |

| I <sup>2</sup> C PORT                  |       |     |        |               | See <a href="#">Figure 5</a>                                                           |

| $f_{\text{SCL}}$                       |       | 1   |        | MHz           | SCL frequency                                                                          |

| $t_{\text{SCLH}}$                      | 0.26  |     |        | $\mu\text{s}$ | SCL high                                                                               |

| $t_{\text{SCLL}}$                      | 0.5   |     |        | $\mu\text{s}$ | SCL low                                                                                |

| $t_{\text{SCS}}$                       | 0.26  |     |        | $\mu\text{s}$ | SCL rise setup time (to SDA falling), relevant for repeated start condition            |

| $t_{\text{SCR}}$                       |       | 120 |        | ns            | SCL and SDA rise time, load capacitance ( $C_{\text{LOAD}}$ ) = 400 pF                 |

| $t_{\text{SCH}}$                       | 0.26  |     |        | $\mu\text{s}$ | SCL fall hold time (from SDA falling), relevant for start condition                    |

| $t_{\text{DS}}$                        | 50    |     |        | ns            | SDA setup time (to SCL rising)                                                         |

表 8. デジタル・タイミング

| Parameter                          | Min | Typ | Max   | Unit          | Description                                                      |

|------------------------------------|-----|-----|-------|---------------|------------------------------------------------------------------|

| $t_{SCF}$                          |     |     | 120   | ns            | SCL and SDA fall time, $C_{LOAD} = 400 \text{ pF}$               |

| $t_{BFT}$                          | 0.5 |     |       | $\mu\text{s}$ | SCL rise setup time (to SDA rising), relevant for stop condition |

| UART                               |     |     | 1.152 | Mbps          | Baud rate                                                        |

| $\overline{\text{PD}} \text{ PIN}$ |     |     |       |               |                                                                  |

| $t_{RLPW}$                         | 20  |     |       | ns            | $\overline{\text{PD}}$ low pulse width                           |

## デジタル・タイミング図

図 2. シリアル入力ポートのタイミング図

002

図 3. シリアル出力ポートのタイミング図

図 4. SPIポートのタイミング図

図 5. I<sub>2</sub>Cポートのタイミング図

## 絶対最大定格

表 9.

| Parameter                     | Rating                 |

|-------------------------------|------------------------|

| Supply                        |                        |

| Power (AVDD, HPVDD, HPVDD_L)  | -0.3 V to +1.98 V      |

| IOVDD                         | -0.3 V to +3.63 V      |

| Input                         |                        |

| Current (Except Supply Pins)  | $\pm 20 \text{ mA}$    |

| Analog Voltage (Signal Pins)  | -0.3 V to AVDD + 0.3 V |

| Digital Voltage (Signal Pins) | -0.3 to IOVDD + 0.3 V  |

| Temperature                   |                        |

| Operating Range (Case)        | -40°C to +85°C         |

| Storage Range                 | -65°C to +150°C        |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。これはストレス定格のみを定めたものであり、本規格の動作セクションに記載する規定値以上でデバイスが正常に動作することを示唆するものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCBの熱設計には、細心の注意を払う必要があります。

$\theta_{JA}$ は、1立方フィートの密閉容器内で測定された自然対流下でのジャンクションと周囲の間の熱抵抗です。 $\theta_{JC}$ は、ジャンクションとケースの間の熱抵抗です。

表 10. 热抵抗

| Package Type | $\theta_{JA}^1$ | $\theta_{JC}^1$ | Unit |

|--------------|-----------------|-----------------|------|

| CB-28-5      | 94              | 1.1             | °C/W |

1 热抵抗のシミュレーション値は、2つのサーマル・ピアを備えたJEDEC 2S2Pサーマル・テスト・ボードに基づいています。 $\theta_{JA}$ および $\theta_{JC}$ は、自然対流冷却下にある4層PCBに関するJESD51-9に従って決定されます。

### 静電放電 (ESD) 定格

以下のESD情報は、ESDに敏感なデバイスを取り扱うために示したものですが、対象はESD保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002準拠の電界誘起帶電デバイス・モデル (FICDM) と帶電デバイスモデル (CDM)。

### ADAU1850のESD定格

表 11. ADAU1850、28ポールWLCSP

| ESD Model | Withstand Threshold (V) | Class Level |

|-----------|-------------------------|-------------|

| HBM       | 1000                    | 1C          |

| CDM       | 500                     | C2a         |

### ESDに関する注意

#### ESD（静電放電）の影響を受けやすいデバイスです。

帯電したデバイスおよび回路基板は、検出されることなく放電されることがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電にさらされた場合は損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

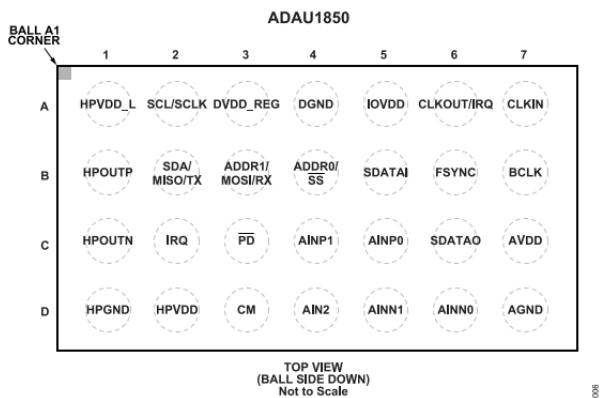

## ピン配置およびピン機能の説明

図 6. ピン配置（上面図）

表 12. ピン機能の説明

| ピン番号 | 記号            | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                           |

|------|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | HPVDD_L       | D_IO             | ヘッドフォン・アンプ電力、1.2Vアナログ電源。このピンは、10μFのコンデンサを使用してHPGNDからデカップリングします。このピンにいたるPCBパターンは、ヘッドフォン出力の駆動に必要な電流の大きさに応じて、広くする必要があります。                                                                                       |

| A2   | SCL/SCLK      | PWR              | I <sup>2</sup> Cクロック (SCL)。デバイスがI <sup>2</sup> C制御モードの場合、このピンは常にオープンコレクタ入力です。このピンに接続するラインには2.0kΩのプルアップ抵抗が必要です。                                                                                               |

|      |               |                  | SPIクロック (SCLK)。このピンは連続的に動作させることも、SPIトランザクション間でゲート・オフすることもできます。                                                                                                                                               |

| A3   | DVDD_REG      | PWR              | 内部DVDDレギュレータの電源出力。1μFのコンデンサと0.1μFのコンデンサを使用して、このピンをDGNDからデカップリングします。                                                                                                                                          |

| A4   | DGND          | PWR              | デジタル・グラウンド。AGNDピンとDGNDピンは、まとめて共通グランド・プレーンに接続できます。                                                                                                                                                            |

| A5   | IOVDD         | PWR              | デジタル入力ピンおよび出力ピンの電源。デジタル出力ピンにはIOVDDから供給します。この電源によりデジタル入力ピンに印加できる最大入力電圧が決まります。このピンから引き出される電流は、デジタル出力の負荷に依存するため、変動します。IOVDDは、0.1μF以上のコンデンサを使用してDGNDからデカップリングします。                                                |

| A6   | CLKOUT/IRQ    | D_OUT            | クロック出力 (CLKOUT)。CLKOUTはこの多機能ピンのデフォルト機能です。<br>割込み要求出力 (IRQ)。                                                                                                                                                  |

| A7   | CLKIN         | D_IN             | クロック入力。                                                                                                                                                                                                      |

| B1   | HPOUTP        | A_OUT            | 非反転ヘッドフォン出力。                                                                                                                                                                                                 |

| B2   | SDA/MISO/TX   | D_IO             | I <sup>2</sup> Cデータ (SDA)。このピンは双方向のオープンコレクタです。このピンに接続するラインには2.0kΩのプルアップ抵抗が必要です。<br>SPIデータ出力 (MISO)。このSPIデータ出力は、レジスタおよびメモリ・ロケーションをリードバックするために用います。SPI読出しが非アクティブな場合、MISOは3ステートとなります。<br>UARTポート・データ送信／出力 (TX)。 |

| B3   | ADDR1/MOSI/RX | D_IN             | I <sup>2</sup> Cアドレス1 (ADDR1)。<br>SPIデータ入力 (MOSI)。<br>UARTポート・データ送信／入力 (RX)。                                                                                                                                 |

| B4   | ADDR0/SS      | D_IN             | I <sup>2</sup> Cアドレス0 (ADDR0)。<br>SPIラッチ信号 (SS)。このピンは、SPIトランザクションの開始時にローに、トランザクションの終了時にハイになります。SPIトランザクションの開始時に送信されるアドレスと読出し／書き込みビットに応じて、各SPIトランザクションの終了までのSCLKサイクル数が異なる場合があります。                             |

| B5   | SDATAI        | D_IN             | シリアル・オーディオ・ポート入力データ。                                                                                                                                                                                         |

| B6   | FSYNC         | D_IN             | シリアル・オーディオ・ポートのフレーム同期／左右クロック。                                                                                                                                                                                |

| B7   | BCLK          | D_IN             | シリアル・オーディオ・ポートのビット・クロック。                                                                                                                                                                                     |

| C1   | HPOUTN        | A_OUT            | 反転ヘッドフォン出力。                                                                                                                                                                                                  |

| C2   | IRQ           | D_OUT            | 割込み要求出力。                                                                                                                                                                                                     |

| C3   | PD            | D_IN             | アクティブ・ローのパワーダウン。すべてのアナログおよびデジタル回路がパワーダウンします。このピンには内部にプルダウン抵抗があります。そのため、電力が電源ピンに印加されるときに入力信号がフローティング状態であると、ADAU1850はパワーダウン・モードを維持します。                                                                         |

| C4   | AINP1         | A_IN             | ADC1非反転入力。                                                                                                                                                                                                   |

## ピン配置およびピン機能の説明

表 12. ピン機能の説明

| ピン番号 | 記号     | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                   |

|------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C5   | AINP0  | A_IN             | ADC0非反転入力。                                                                                                                                                                                           |

| C6   | SDATAO | D_OUT            | シリアル・オーディオ・ポートの出力データ。                                                                                                                                                                                |

| C7   | AVDD   | PWR              | 1.8Vアナログ電源。このピンは、10μFのコンデンサを使用してAGNDからデカップリングします。                                                                                                                                                    |

| D1   | HPGND  | PWR              | ヘッドフォン・アンプのグラウンド。                                                                                                                                                                                    |

| D2   | HPVDD  | PWR              | ヘッドフォン・アンプ電力、1.8Vアナログ電源。このピンは、10μFのコンデンサを使用してHPGNDからデカップリングします。このピンにいたるPCBパターンは、ヘッドフォン出力の駆動に必要な電流の大きさに応じて、広くする必要があります。                                                                               |

| D3   | CM     | A_OUT            | 0.85V（公称値）に固定されたコモンモード・リファレンス。ADCとDACの間のクロストークを低減するために、このピンとグラウンドの間に1μFのデカップリング・コンデンサを接続する必要があります。コンデンサの材料は重要ではありません。このピンを用いて外部アナログ回路をバイアスすることができます。ただし、これらの回路がCMから電流を引き出さない場合に限ります（例えばオペアンプの非反転入力）。 |

| D4   | AIN2   | A_IN             | ADC2の入力。ADC2はシングルエンド入力のADCです。                                                                                                                                                                        |

| D5   | AINN1  | A_IN             | ADC1反転入力。                                                                                                                                                                                            |

| D6   | AINN0  | A_IN             | ADC0反転入力。                                                                                                                                                                                            |

| D7   | AGND   | PWR              | アナログ・グラウンド。AGNDピンとDGNDピンは、まとめて共通グランド・プレーンに直接接続できます。                                                                                                                                                  |

1 D\_IOはデジタル入出力、PWRは電源、A\_OUTはアナログ出力、D\_INはデジタル入力、D\_OUTはデジタル出力、A\_INはアナログ入力を意味します。D\_IOはデジタル入出力、PWRは電源、A\_OUTはアナログ出力、D\_INはデジタル入力、A\_INはアナログ入力を意味します。

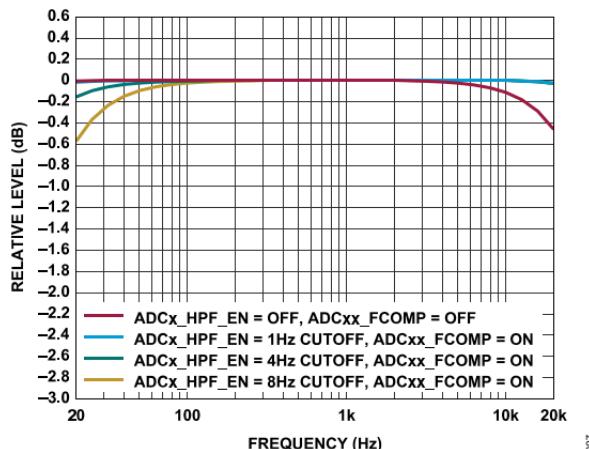

## 代表的な性能特性

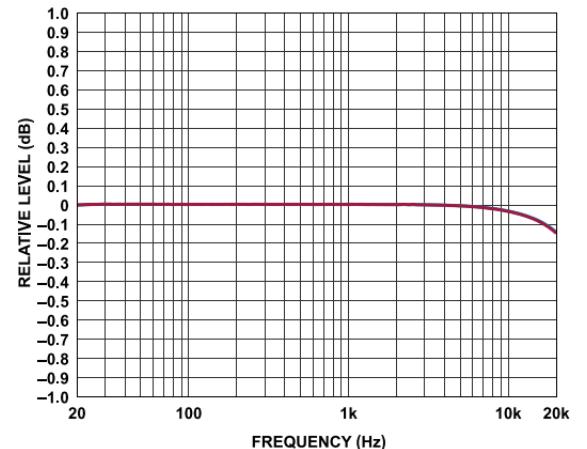

図7. 周波数応答、 $f_S = 48\text{kHz}$ 、-20dBV入力、信号経路 = AINx～SDATAO、PGAなし、ADC0およびADC1は差動モード、ADC2はシングルエンド・モード

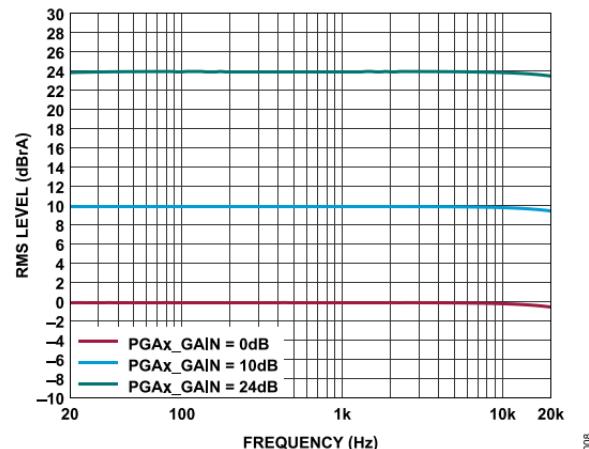

図8. 周波数応答、 $f_S = 48\text{kHz}$ 、信号経路 = AINx～SDATAO、PGAのゲイン設定値 (0dB、10dB、24dB) を基準とする出力

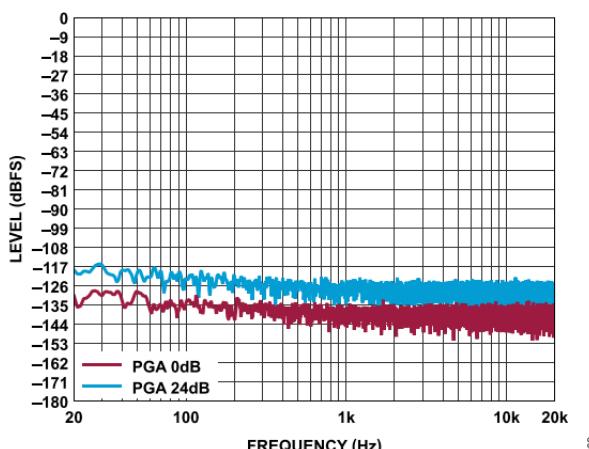

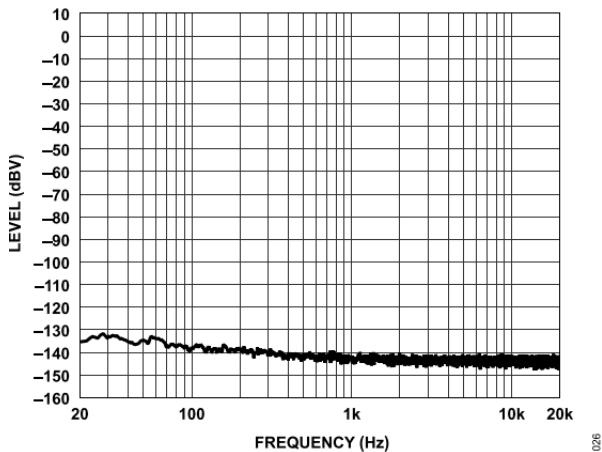

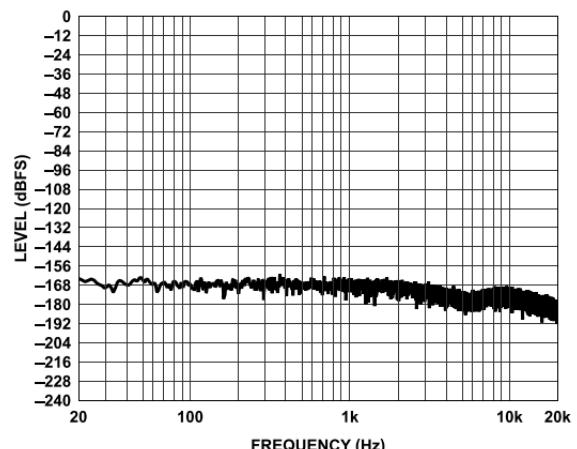

図9. FFT、無信号、 $f_S = 48\text{kHz}$ 、信号経路 = AINx～SDATAO、PGA = 0dBおよび24dB (PGAx\_GAIN) 、ADC0およびADC1は差動モード

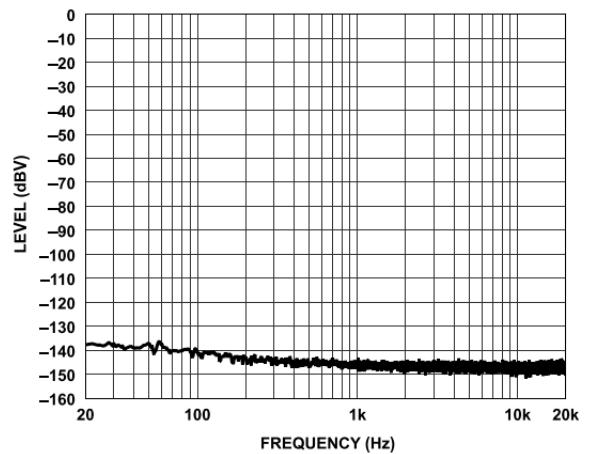

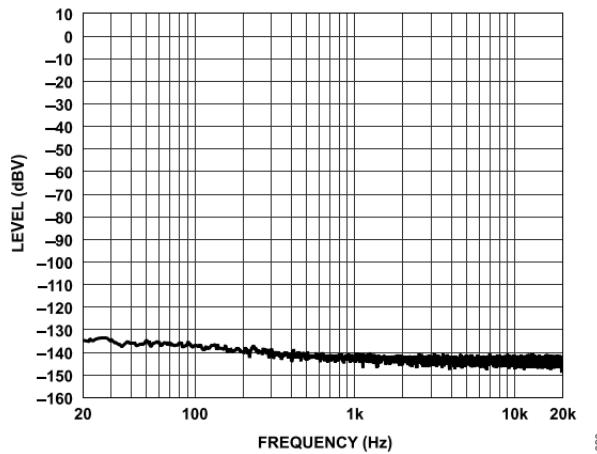

図10. FFT、無信号、 $f_S = 48\text{kHz}$ 、信号経路 = AINx～SDATAO、PGA = 0dBおよび24dB (PGAx\_GAIN) 、ADC2はシングルエンド・モード

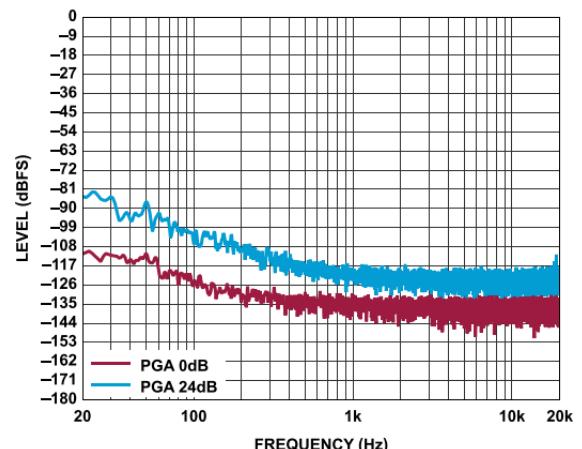

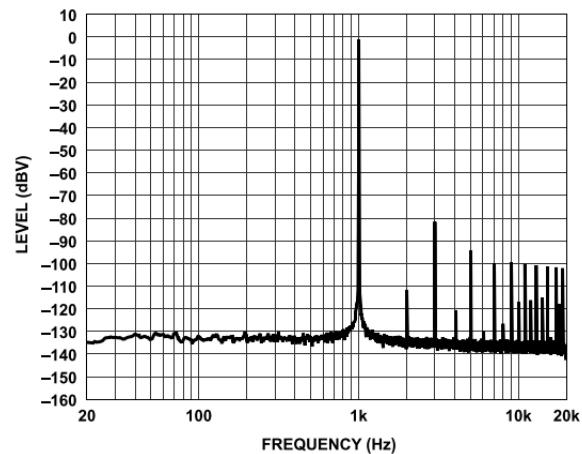

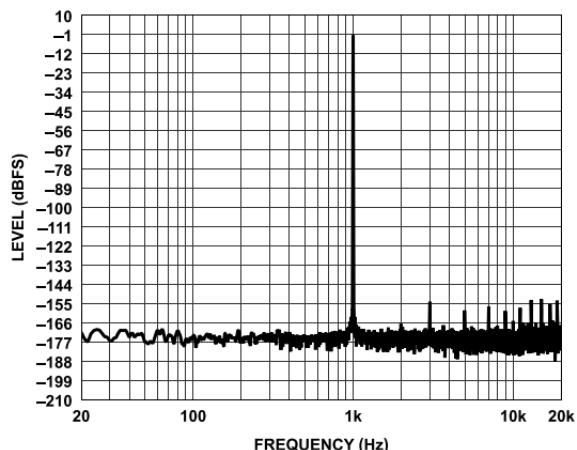

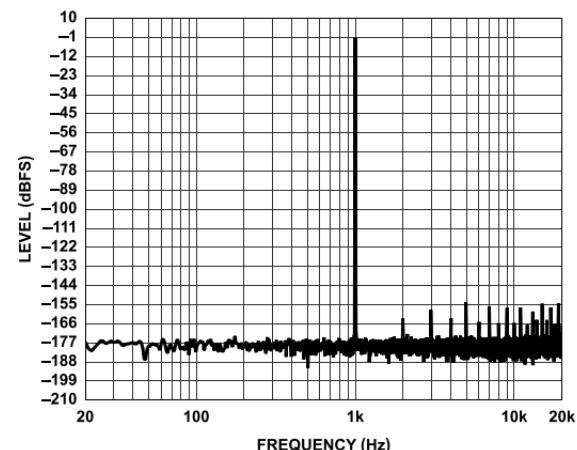

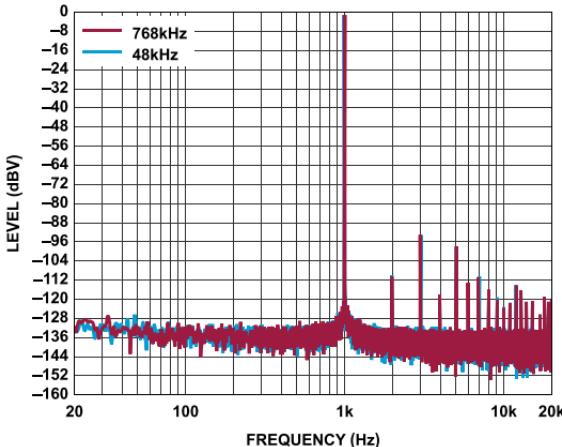

図11. FFT、-7dBV入力、-1dBFS出力、 $f_S = 48\text{kHz}$ 、信号経路 = AINx～SDATAO、PGAなし、ADC0およびADC1は差動モード

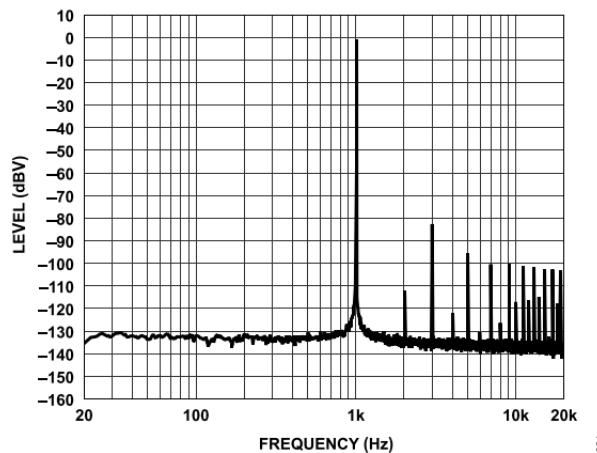

図12. FFT、-7dBV入力、-1dBFS出力、 $f_S = 48\text{kHz}$ 、信号経路 = AINx～SDATAO、PGAなし、ADC2はシングルエンド・モード

## 代表的な性能特性

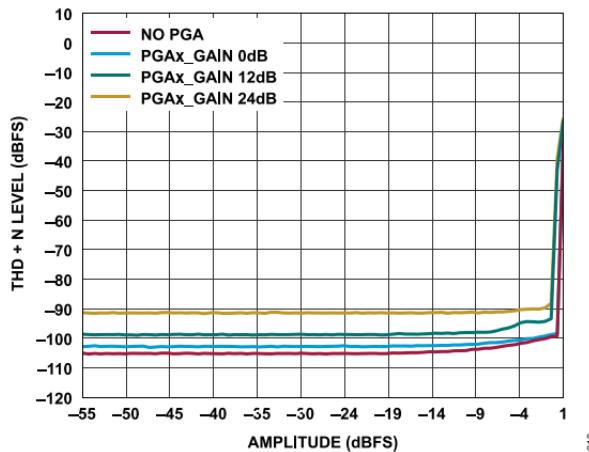

図13. THD + Nのレベルと振幅の関係、 $f_S = 48\text{ kHz}$ 、信号経路 = AINx～SDATAO、PGAなしおよびPGAゲイン設定 (0dB, 12dB, 24dB) 、ADC0およびADC1は差動モード

図14. THD + Nのレベルと振幅の関係、 $f_S = 48\text{ kHz}$ 、信号経路 = AINx～SDATAO、PGAなしおよびPGAゲイン設定 (0dB, 12dB, 24dB) 、ADC2はシングルエンド・モード

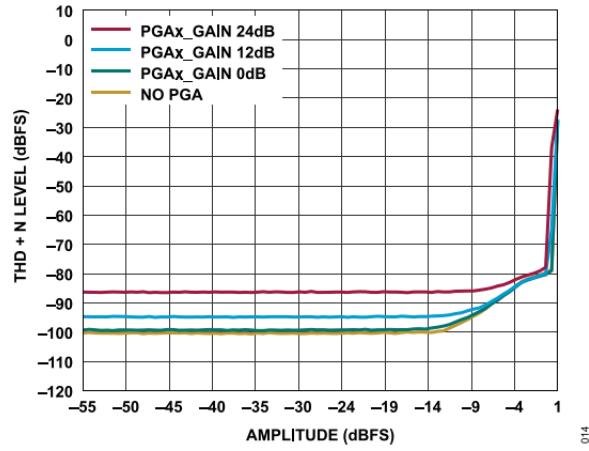

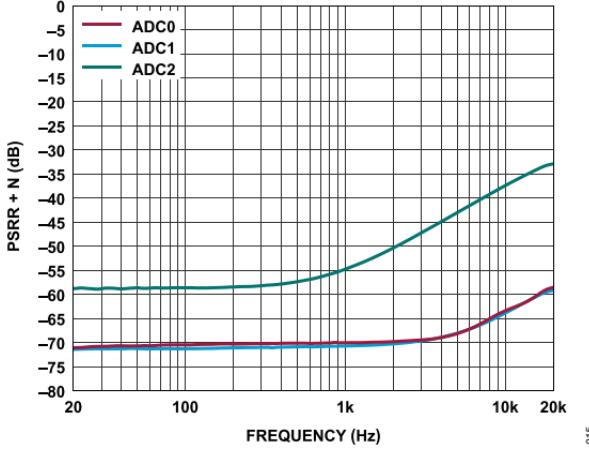

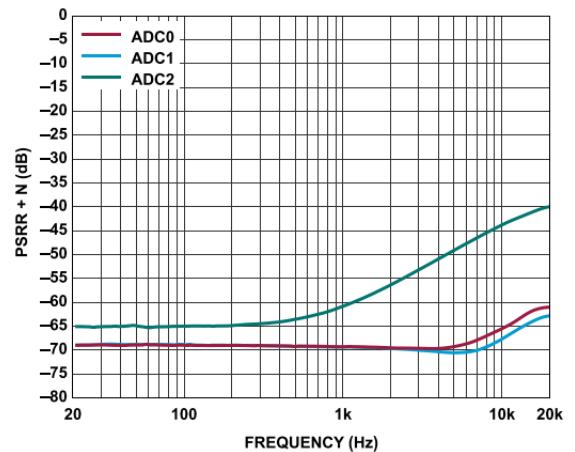

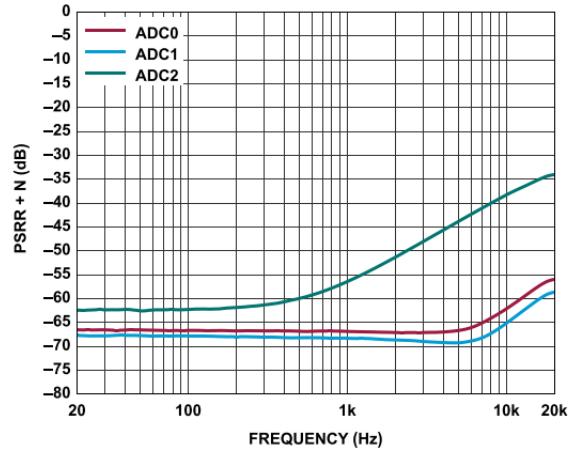

図15. PSRR + N、信号経路 = AINx～SDATAO、 $f_S = 48\text{ kHz}$ 、AVDDに100mV p-pのリップル入力、PGAなし、ADC0およびADC1は差動モード、ADC2はシングルエンド・モード

図16. PSRR + N、信号経路 = AINx～SDATAO、 $f_S = 48\text{ kHz}$ 、AVDDに100mV p-pのリップル入力、PGA = 0dB、ADC0およびADC1は差動モード、ADC2はシングルエンド・モード

図17. PSRR + N、信号経路 = AINx～SDATAO、 $f_S = 48\text{ kHz}$ 、AVDDに100mV p-pのリップル入力、PGA = 10dB、ADC0およびADC1は差動モード、ADC2はシングルエンド・モード

図18. PSRR、信号経路 = SDATAI～ヘッドフォン出力、 $f_S = 48\text{ kHz}$ 、HPVDD\_Lに100mV p-pのリップル入力、負荷 = 32Ω

## 代表的な性能特性

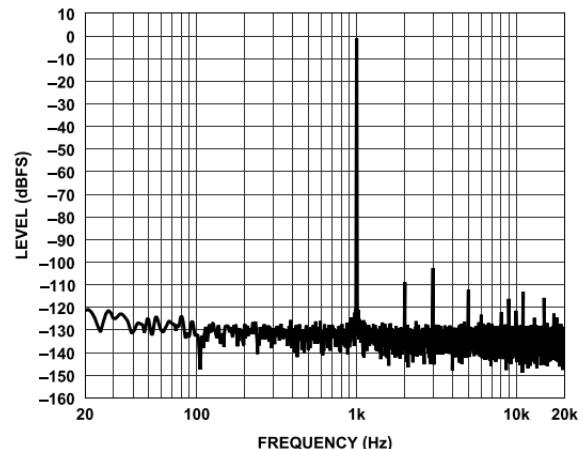

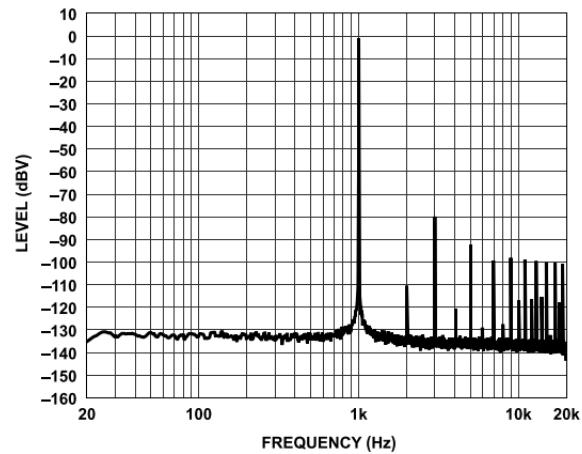

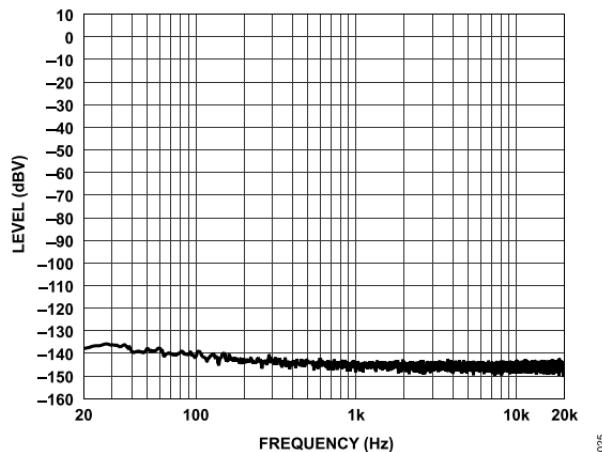

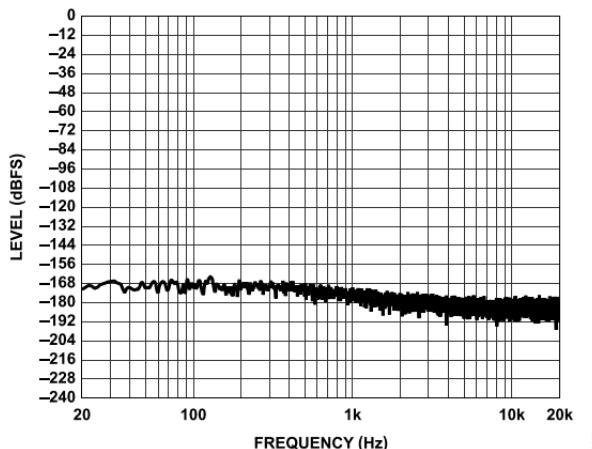

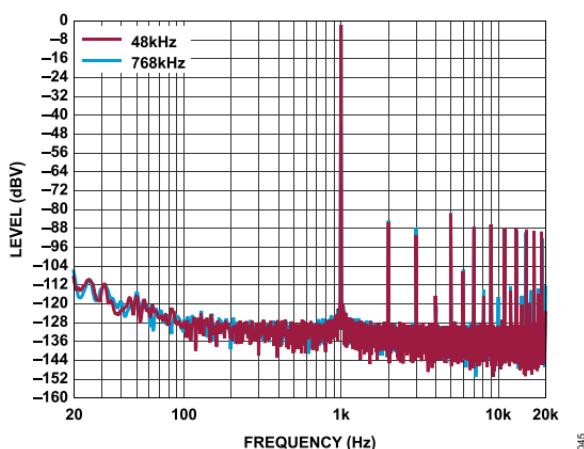

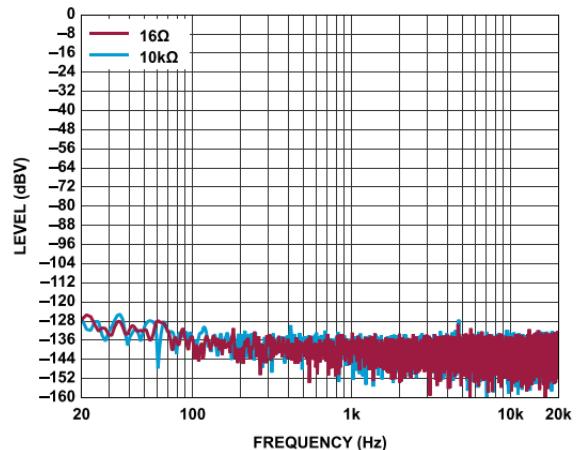

図19. FFT、無信号、 $f_S = 48\text{kHz}$ 、信号経路 = SDATAI～ヘッドフォン出力、ヘッドフォン・モード、負荷 =  $16\Omega$

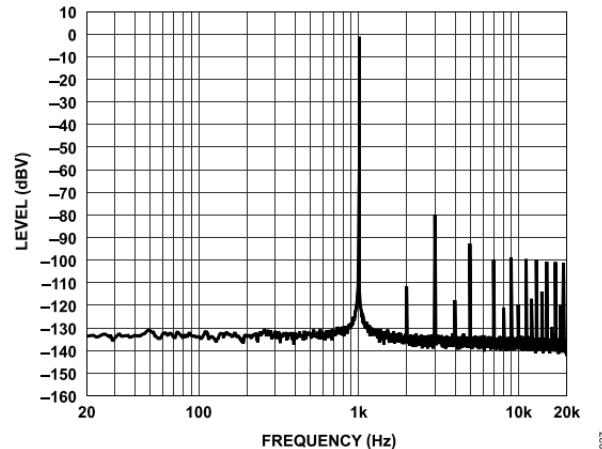

図20. FFT、無信号、 $f_S = 48\text{kHz}$ 、信号経路 = SDATAI～ヘッドフォン出力、ライン出力モード、負荷 =  $10\text{k}\Omega$

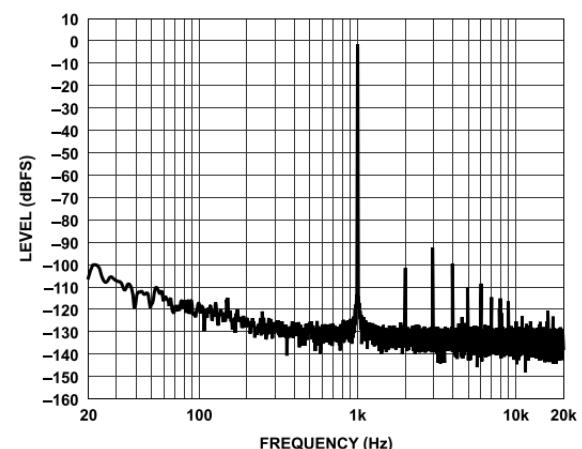

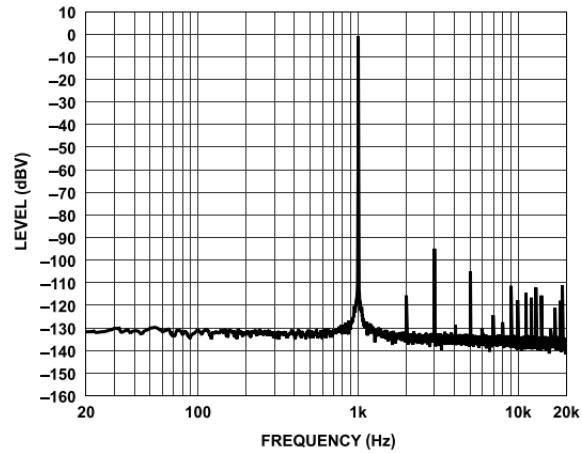

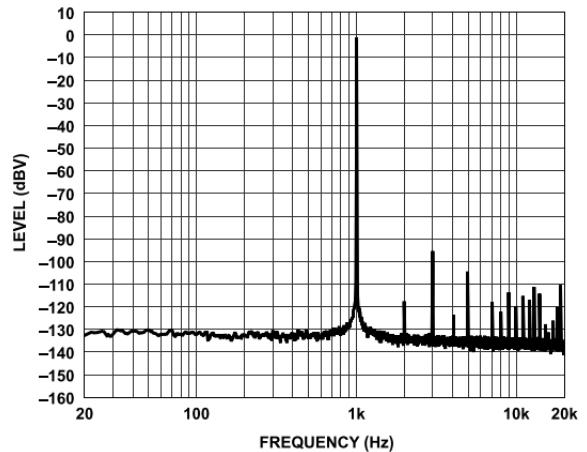

図21. FFT、-1dBFS、 $f_S = 48\text{kHz}$ 、信号経路 = SDATAI～ヘッドフォン出力、ヘッドフォン・モード、負荷 =  $32\Omega$

図22. FFT、-1dBFS、 $f_S = 48\text{kHz}$ 、信号経路 = SDATAI～ヘッドフォン出力、ヘッドフォン・モード、負荷 =  $24\Omega$

図23. FFT、-1dBFS、 $f_S = 48\text{kHz}$ 、信号経路 = SDATAI～ヘッドフォン出力、ヘッドフォン・モード、負荷 =  $16\Omega$

図24. FFT、-1dBFS、 $f_S = 48\text{kHz}$ 、信号経路 = SDATAI～ヘッドフォン出力、ライン出力モード、負荷 =  $10\text{k}\Omega$

## 代表的な性能特性

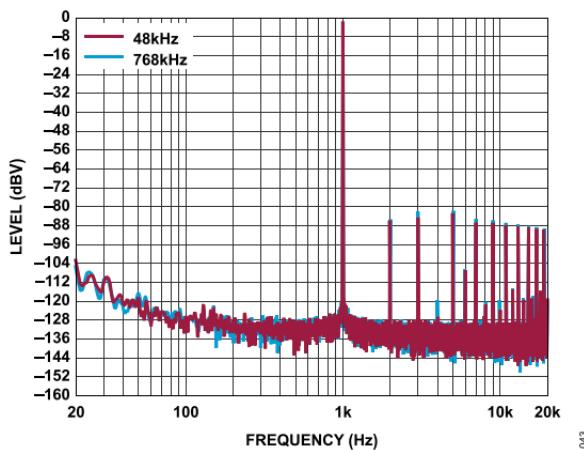

図25. FFT、無信号、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI～インターポレータ～FastDSR～ヘッドフォン出力、ヘッドフォン・モード、負荷 =  $16\Omega$

図26. FFT、無信号、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI～インターポレータ～FastDSP～ヘッドフォン出力、ライン出力モード、負荷 =  $10\text{k}\Omega$

図27. FFT、-1dBFS、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI～インターポレータ～FastDSR～ヘッドフォン出力、ヘッドフォン・モード、負荷 =  $16\Omega$

図28. FFT、-1dBFS、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI～インターポレータ～FastDSP～ヘッドフォン出力、ライン出力モード、負荷 =  $10\text{k}\Omega$

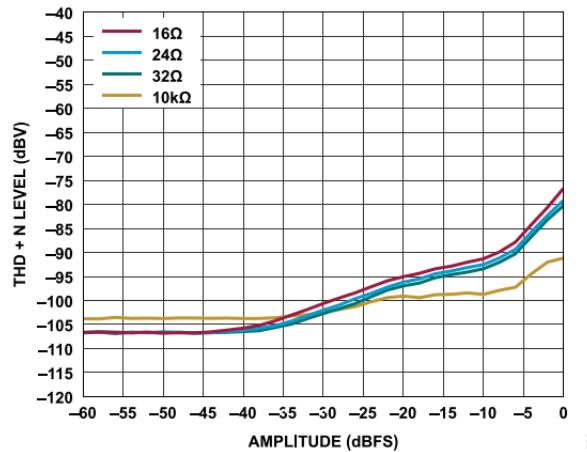

図29. THD + N レベルと入力振幅の関係、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI～ヘッドフォン出力 ( $16\Omega$ ,  $24\Omega$ ,  $32\Omega$ ) または ライン出力モード ( $10\text{k}\Omega$ )

図30. 相対レベルと周波数の関係、 $f_s = 48\text{kHz}$ 、信号経路 = SDATAI～ヘッドフォン出力 ( $16\Omega$ ) または ライン出力モード ( $10\text{k}\Omega$ )

## 代表的な性能特性

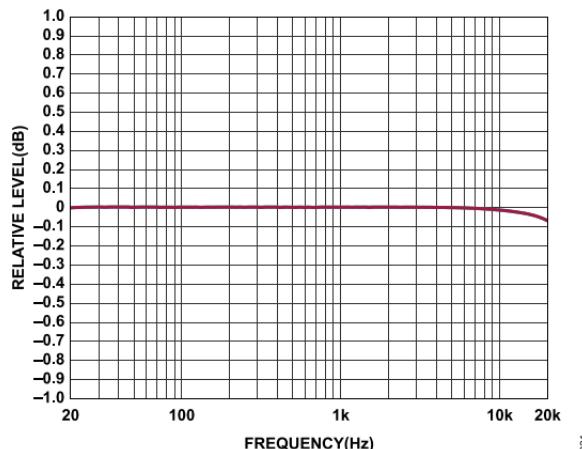

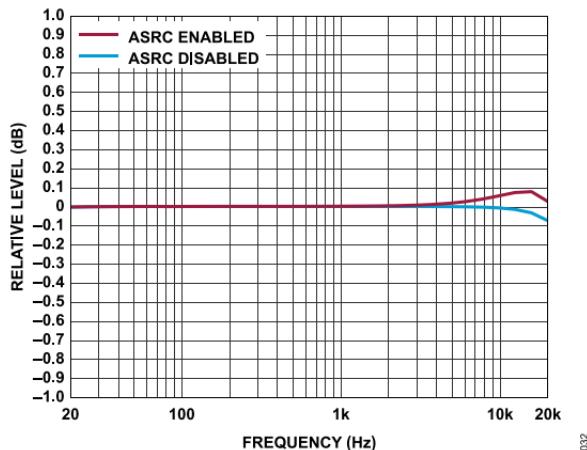

図31. 相対レベルと周波数の関係、 $f_s = 768\text{kHz}$ 、信号経路 = SDATAI～インターポレータ～FastDSP～ヘッドフォン出力 ( $16\Omega$ ) またはライン出力モード (10kΩ)

図32. 相対レベルと周波数の関係、全体を通して  $f_s = 48\text{kHz}$  (FastDSP = 768kHzは除く) 、信号経路 = SDATAI～ASRCI～イコライザ～インターポレータ～FastDSP～デシメータ～ASRCO～SDATAO

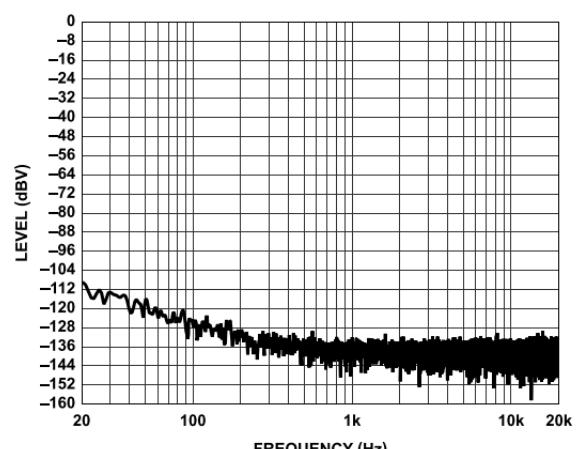

図33. FFT、無信号、全体を通して  $f_s = 48\text{kHz}$  (FastDSP = 768kHzは除く) 、信号経路 = SDATAI～ASRCI～イコライザ～インターポレータ～FastDSP～デシメータ～ASRCO～SDATAO

図34. FFT、無信号、全体を通して  $f_s = 48\text{kHz}$  (FastDSP = 768kHzは除く) 、信号経路 = SDATAI～イコライザ～インターポレータ～FastDSP～ヘッドフォン出力 ( $16\Omega$ )

図35. FFT、-1dBFS、全体を通して  $f_s = 48\text{kHz}$  (FastDSP = 768kHzは除く) 、信号経路 = SDATAI～ASRCI～イコライザ～インターポレータ～FastDSP～デシメータ～ASRCO～SDATAO

図36. FFT、-1dBFS、全体を通して  $f_s = 48\text{kHz}$  (FastDSP = 768kHzは除く) 、信号経路 = SDATAI～イコライザ～インターポレータ～FastDSP～デシメータ～SDATAO

## 代表的な性能特性

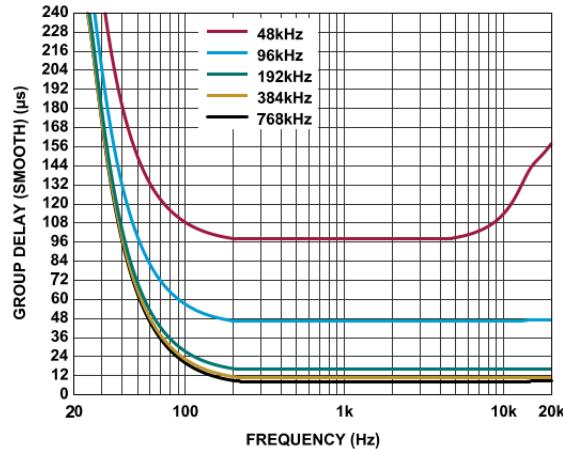

037

図37. 群遅延（スムージング）と周波数の関係、 $f_s = 192\text{kHz} \sim 768\text{kHz}$ 、信号経路 = AINx～FastDSP～ヘッドフォン出力モードまたはライン出力モード、ADC0およびADC1は差動モード

038

図38. 群遅延（スムージング）と周波数の関係、 $f_s = 192\text{kHz} \sim 768\text{kHz}$ 、信号経路 = AINx～FastDSP～ヘッドフォン出力モードまたはライン出力モード、ADC2はシングルエンド・モード

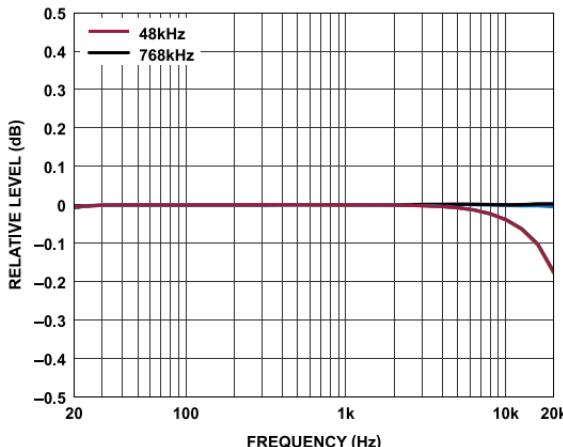

039

図39. 相対レベルと周波数の関係、ヘッドフォン・モード（16Ω）またはライン出力モード（10kΩ）、 $f_s = 48\text{kHz}$ および768kHz、信号経路 = AINx～DAC、ADC0およびADC1は差動モード、ADC2はシングルエンド・モード

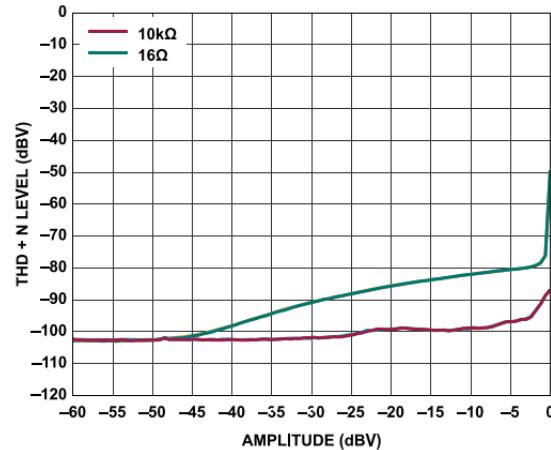

040

図40. THD + N レベルと振幅の関係、 $f_s = 48\text{kHz} \sim 768\text{kHz}$ 、信号経路 = AINx～ヘッドフォン・モード（16Ω）またはライン出力モード（10kΩ）、ADC0およびADC1は差動モード

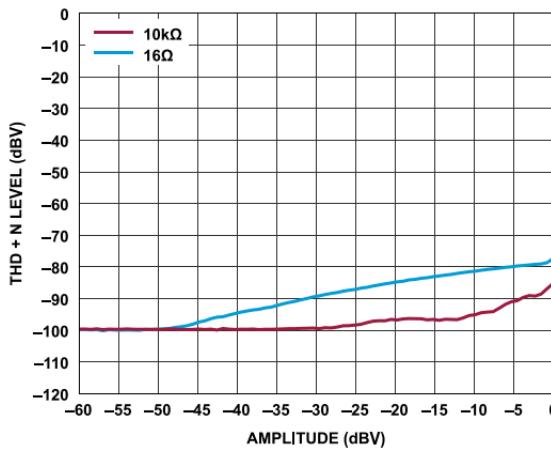

041

図41. THD + N レベルと振幅の関係、 $f_s = 48\text{kHz} \sim 768\text{kHz}$ 、信号経路 = AINx～ヘッドフォン・モード（16Ω）またはライン出力モード（10kΩ）、ADC2はシングルエンド・モード

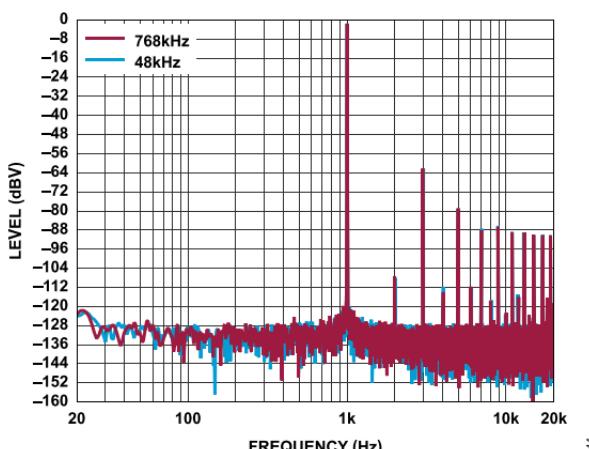

042

図42. FFT、-1dBV、ライン出力モード、負荷 = 10kΩ、 $f_s = 48\text{kHz} \sim 768\text{kHz}$ 、信号経路 = AINx～DAC、ADC0およびADC1は差動モード

## 代表的な性能特性

## 動作原理

ADAU1850は、最適化されたオーディオ処理コアを備えた低消費電力のオーディオ・コーデックで、高品質オーディオ、低消費電力、小型サイズ、低遅延を必要とするノイズ・キャンセリング・アプリケーションに最適です。シリアル・オーディオ・ポートは、I<sup>2</sup>S、左詰め、右詰め、時分割多重（TDM）の各モードに対応でき、3ステート出力であるためデジタル・オーディオ・データとインターフェースできます。AVDDおよびHPVDDの動作電圧は1.8Vです。また、内部レギュレータを使用してデジタル電源電圧を生成できます。

入力信号経路は柔軟な設定が可能で、差動またはシングルエンドのアナログ・マイクロフォン入力を受け入れることができます。AIN2は、シングルエンド・アナログ・マイクロフォン入力にのみ対応します。各入力信号には固有のプログラマブル・ゲイン・アンプ（PGA）があり、ボリュームの調整が可能です。

ADCおよびDACは高品質の24ビット・シグマデルタ（Σ-Δ）コンバータで、12kHz～768kHzの範囲で選択可能なサンプリング・レートで動作します。またADCは音声ウェイクアップ・モードの場合、8kHzまたは16kHzのサンプリング・レートにも対応します。ADCとDACには、カットオフ周波数が1Hz、4Hz、または8Hzのハイパス・フィルタがオプションで備わっており、また、細かいステップのデジタル・ソフト・ボリューム制御機能があります。

DAC出力は、インピーダンスが16Ω以上のヘッドフォン・イヤピース・スピーカを差動で駆動できます。また、出力が10kΩ以上の差動負荷の場合、ライン出力モードに変更するオプションもあります。

FastDSPコアは、このコーデックをノイズ・キャンセリング用に最適化する、縮小命令セットを備えています。プログラムとパラメータのRAMは、[Lark Studio](#)のグラフィカル・ユーザ・インターフェース（GUI）を用いて構築された、カスタム・オーディオ処理信号フローでロードできます。パラメータ・ランダム・アクセス・メモリ（RAM）に保存された値は、個々の信号処理ブロックを制御します。

制御ポートを通じてコアのプログラミングと制御を行うには、[Lark Studio GUI](#)を用います。このGUIを使用して、信号フローの設計および調整と共に、ADAU1850のすべてのレジスタを設定できます。デジタルまたはアナログのオーディオ処理の知識のある人なら誰でも、GUIでデジタル・シグナル・プロセッサ（DSP）の信号フローを設計してそのフローを対象アプリケーションにエクスポートできます。また、このインターフェースは、経験を積んだDSPプログラマによる設計の制御に対応できる柔軟性とプログラマビリティを備えています。[Lark Studio GUI](#)では、ユーザは、グラフィカル・ブロック（バイクロック・フィルタ、ボリューム調整、算術演算など）の接続や設計のコンパイルができ、また、制御ポートを介してプログラム・ファイルとパラメータ・ファイルをADAU1850のメモリにロードできます。

ADAU1850は、外部クロックまたは内部RC発振器をマスター・クロック源として用います。外部クロックを使用する場合、ADAU1850は、オンチップのバイパス可能なフラクショナルPLLを用いることで、広い範囲の入力クロックから内部クロックを生成できます。PLLの入力は30kHz～27MHzが可能です。

ADAU1850は2.957mm × 1.757mmの小型28ポールWLCSPパッケージを採用しています。

## アプリケーション情報

### 電源のバイパス・コンデンサ

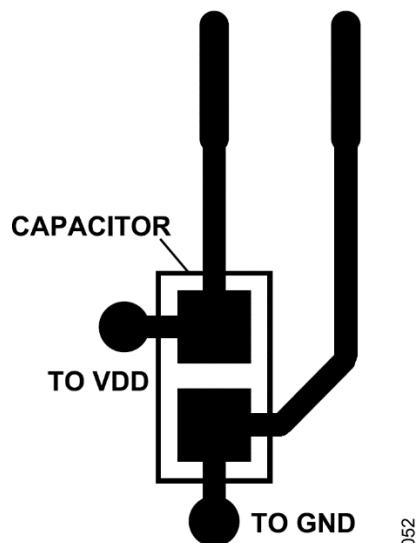

各アナログおよびデジタル電源ピンは、1個の $0.1\mu\text{F}$ コンデンサを用いて、最も近い位置にある適切なグラウンド・ピンにバイパスします。図48では、VDDはすべての電源（IOVDD、AVDD、HPVDD、HPVDD\_L）を示しています。また、常にコンデンサの両側接続部分ができるだけ短くし、ビアを使用せずに1つのレイヤ上でパターンをルーティングしてください。最大限の効果を得るために、コンデンサは電源ピンおよびグラウンド・ピンから等距離に配置します。等距離に配置することができない場合は、電源ピンに多少近づけて配置してください。放熱のための接続はコンデンサの反対側のグランド・プレーンで行ってください。

ボード上の各電源信号は、1つのバルク・コンデンサ（ $10\mu\text{F}$ ～ $47\mu\text{F}$ ）でバイパスします。

図48. 電源バイパス・コンデンサの推奨レイアウト

### レイアウト

HPVDD電源およびHPVDD\_L電源はヘッドフォン・アンプ用です。ヘッドフォン・アンプをイネーブルする場合、このピンへのPCBパターンは、他のピンへのパターンよりも幅広にして、電流伝搬能力を高めることが必要です。ヘッドフォン出力ラインには、幅広のパターンを使用してください。

### グラウンド接続

アプリケーションのレイアウトでは、単一のグランド・プレーンを使用してください。アナログ信号経路の部品はデジタル信号から離して配置してください。

## 外形寸法

07/27/2021-A

図49. 28ボール、ウェーハ・レベル・チップ・スケール・パッケージ [WLCSP]

(CB-28-5)

寸法 : mm

更新 : 2021年7月27日

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                           | Packing Quantity | Package Option |

|--------------------|-------------------|-----------------------------------------------|------------------|----------------|

| ADAU1850BCBZRL     | -40°C to +85°C    | 28-Ball WLCSP (2.957 mm × 1.757 mm × 0.50 mm) | Reel, 5000       | CB-28-5        |

1 Z = RoHS準拠製品。

## 評価用ボード

| Model <sup>1</sup> | Description      |

|--------------------|------------------|

| EVAL-ADAU1850EBZ   | Evaluation Board |

1 Z = RoHS準拠製品。

I<sup>2</sup>Cは、Philips Semiconductors（現在のNXP Semiconductors）が独自に開発した通信プロトコルです。