# クワッド、14ビット、4MSPS、同時サンプリング、 μModule データ・アクイジション・ソリューション

## 特長

- 容易に導入可能な μModule® データ・アクイジション・システム

- ディスクリート・ソリューションと比較してフットプリントを 1/11 に削減

- 重要な受動部品を統合

- 5V 単電源動作

- 14 ビットのノードミス・コードを確保

- オーバーサンプリング機能搭載

- 2 ビットの分解能増強

- 範囲外インジケータ (ALERT)

- INL : ±0.3LSB (代表値)、±1LSB (最大値)

- S/N 比 (代表値)

- 85dB (ゲイン = 1.0、 $f_{IN}$  = 1kHz)

- 92.4dB (OSR = ×8、ゲイン = 1.0、 $f_{IN}$  = 1kHz)

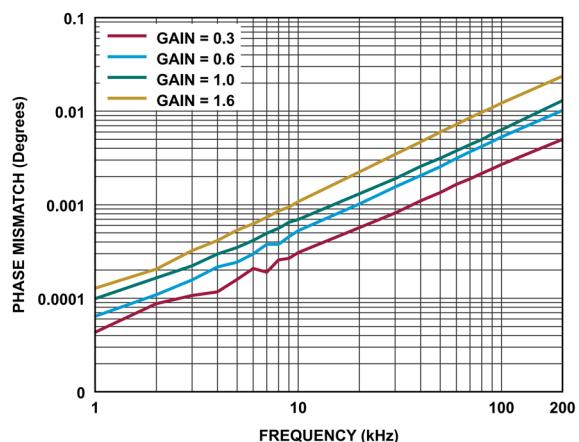

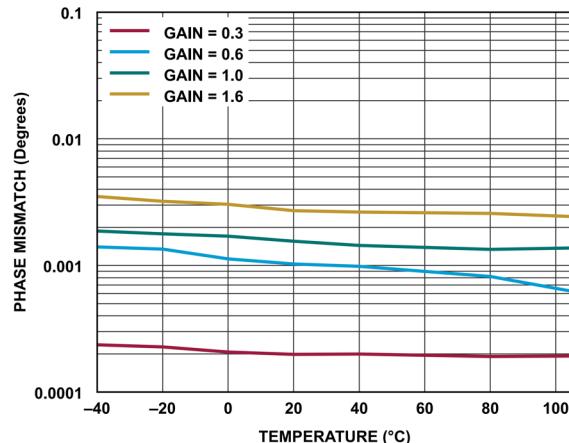

- チャンネル間の位相整合 : 0.005° (代表値) ( $f_{IN}$  = 20kHz)

- ドリフト 3ppm/°C (代表値) の高精度リファレンスを内蔵

- ゲイン誤差 : 0.003% (代表値)

- ゲイン・ドリフト : 0.8ppm/°C (代表値)

- VCM 生成機能を備えた内部バッファを内蔵

- 信号スケーリング機能付きの完全差動 ADC ドライバを内蔵

- 広い入力コモンモード電圧範囲

- 高い同相ノイズ除去性能

- シングルエンド/差動変換

- ピン選択可能な入力範囲 (オーバーレンジ付き)

- 入力範囲 : ±2V、±3.3V、±5.5V、±11V

- ゲイン/減衰 : G = 0.3、0.6、1.0、1.6

- 高速シリアル・インターフェース

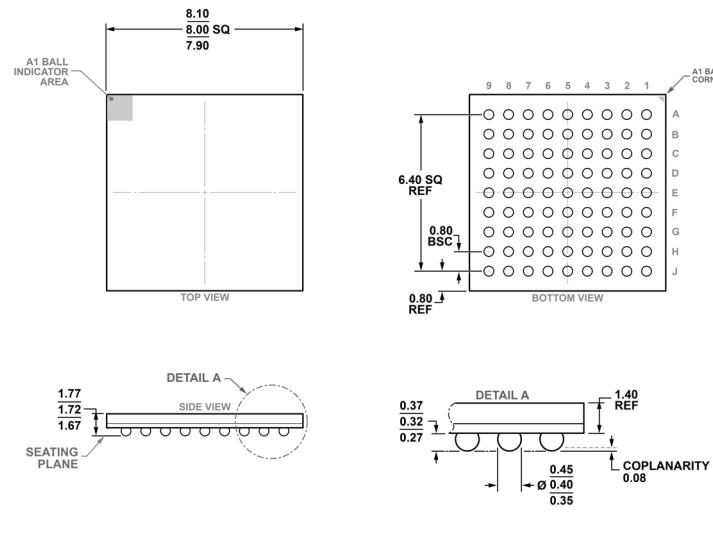

- 8mm × 8mm、0.8mm ピッチ、81 ポール CSP\_BGA パッケージ

## アプリケーション

- 実験室グレードのバッテリ・テスト・システム

- モータ・コントロールの電流検出

- モータ・コントロールのポジション・フィードバック

- ソナー

- 電力品質モニタリング

- データ・アクイジション・システム

- エルビウム添加ファイバ増幅器 (EDFA) アプリケーション

- I/Q 復調

## 概要

ADAQ4381-4 は、部品の選択、最適化、およびレイアウトに関するシグナル・チェーン設計上の課題を設計者からデバイスへと移転することによって、高精度測定システムの開発サイクルを短縮できる、4 チャンネルの高精度データ・アクイジション (DAQ) シグナル・チェーン μModule ソリューションです。

ADAQ4381-4 はシステム・イン・パッケージ (SIP) 技術を採用しており、複数の共通信号処理および調整ブロックを 1 つのデバイスに統合することで、エンド・システムの部品点数を削減します。これらのブロックには、クワッド・チャンネルの高分解能 14 ビット 4MSPS 同時サンプリング SAR ADC、低ノイズの完全差動 ADC ドライバ・アンプ、3.3V 高精度電圧リファレンス、低ノイズ・バッファ・アンプ、低ドロップアウトのリニア・レギュレータが含まれています。

ADAQ4381-4 はオーバーサンプリング・ブロックを内蔵することで、低帯域幅でのダイナミック・レンジを向上させノイズを低減しています。オーバーサンプリングにより分解能を最大 2 ビット増強できます。ADC ドライバの帰還ループを柔軟に設定できるので、ゲインや減衰の 4 段階の調整が可能な他、完全差動入力構成またはシングルエンド/差動入力構成を使用できます。

ADAQ4381-4 は、アナログ・デバイセズの iPassives® 技術を採用しており、優れたマッチング特性とドリフト特性を備えた重要な受動部品も内蔵しています。これにより温度に依存する誤差源を最小限に抑え、最適なシグナル・チェーン性能を実現します。

ADAQ4381-4 は、小型 (8mm × 8mm × 0.8mm ピッチ) の 81 ボール CSP\_BGA パッケージに収められており、パフォーマンスを犠牲にすることなくコンパクトな設計を可能にし、エンド・システムの部品表管理を簡素化します。ADAQ4381-4 の最適な性能は 5V 単電源による動作で確保されており、必要なすべてのバイパスとデカッピング・コンデンサがこのパッケージに含まれています。ADAQ4381-4 システムの集積レベルによって設計上の多くの課題が解決され、マルチチャンネル・アプリケーション向けのコンパクトでシンプルなソリューションを実現できます。

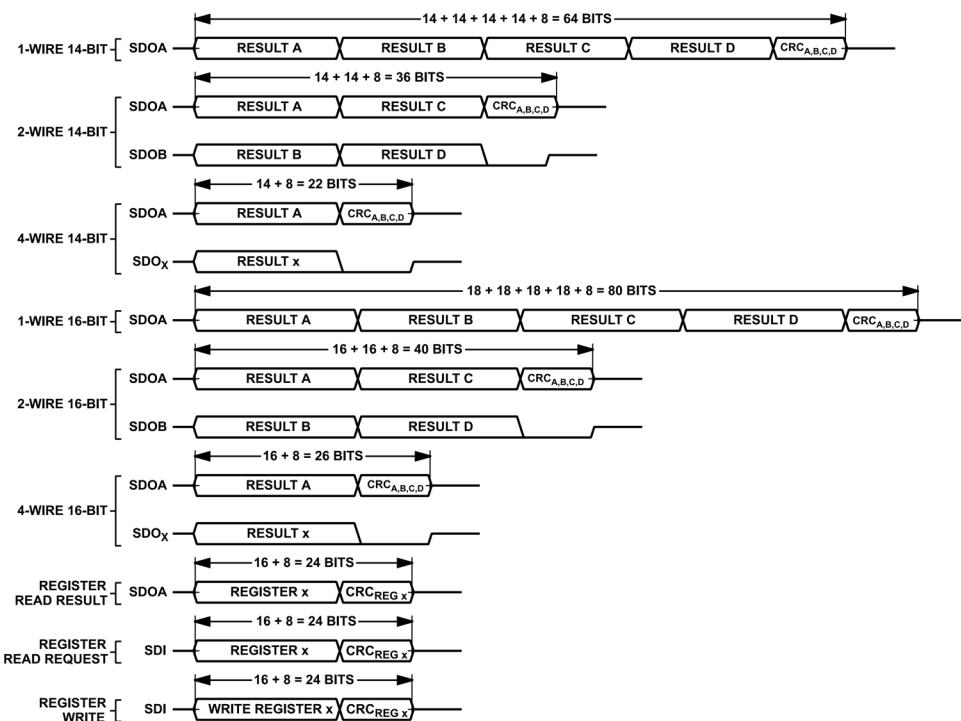

変換結果は、より高いスループットを求める場合は 4 線式モードで同時に、低スループットが許容される場合は 1 線シリアル・モードでクロック出力できます。また、別個のロジック電源を使用することにより、1.8V、2.5V、3.3V のインターフェースに対応します。ADAQ4381-4 は -40°C ~ +105°C の温度範囲で動作するように仕様規定されています。

表 1. μModule データ・アクイジション・ソリューション

| Type   | 500 kSPS | 1 MSPS to 2 MSPS                   | 4 MSPS     |

|--------|----------|------------------------------------|------------|

| 14-bit |          |                                    | ADAQ4381-4 |

| 16-bit | ADAQ7988 | ADAQ4370-4<br>ADAQ7980<br>ADAQ4001 | ADAQ4380-4 |

| 18-bit |          | ADAQ4003                           |            |

## 目次

|                |    |

|----------------|----|

| 特長             | 1  |

| アプリケーション       | 1  |

| 概要             | 1  |

| 代表的なアプリケーション図  | 3  |

| 仕様             | 4  |

| タイミング仕様        | 8  |

| 絶対最大定格         | 11 |

| 熱抵抗            | 11 |

| 静電放電定格         | 11 |

| ESD に関する注意     | 11 |

| ピン配置およびピン機能の説明 | 12 |

| 代表的な性能特性       | 14 |

| 用語の定義          | 20 |

| 動作原理           | 22 |

| 回路説明           | 22 |

| 伝達関数           | 23 |

| アプリケーション情報     | 24 |

| 代表的な接続図        | 24 |

| ADC ドライバ       | 28 |

| 内部リファレンス       | 29 |

| 内部 LDO         | 30 |

| 電源とデカップリング     | 30 |

| ADC の動作モード     | 31 |

|                     |    |

|---------------------|----|

| オーバーサンプリング          | 31 |

| 分解能増強               | 33 |

| アラート                | 33 |

| 電力モード               | 33 |

| ソフトウェア・リセット         | 34 |

| 診断セルフ・テスト           | 34 |

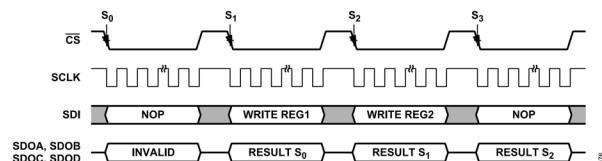

| インターフェース            | 35 |

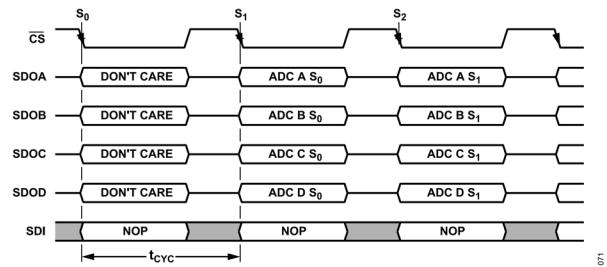

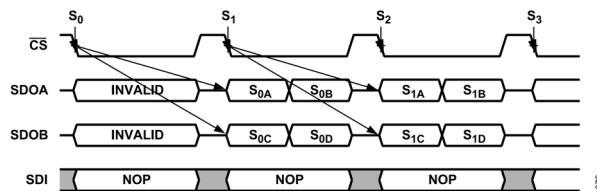

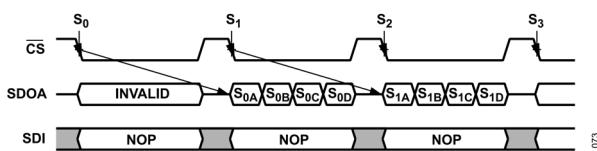

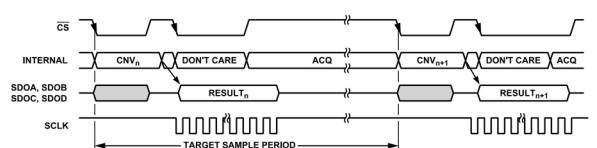

| 変換結果の読み出し           | 35 |

| 低遅延リードバック           | 36 |

| デバイス・レジスタからの読み出し    | 36 |

| デバイス・レジスタへの書き込み     | 36 |

| CRC                 | 37 |

| レジスタ                | 39 |

| レジスタのアドレス指定         | 39 |

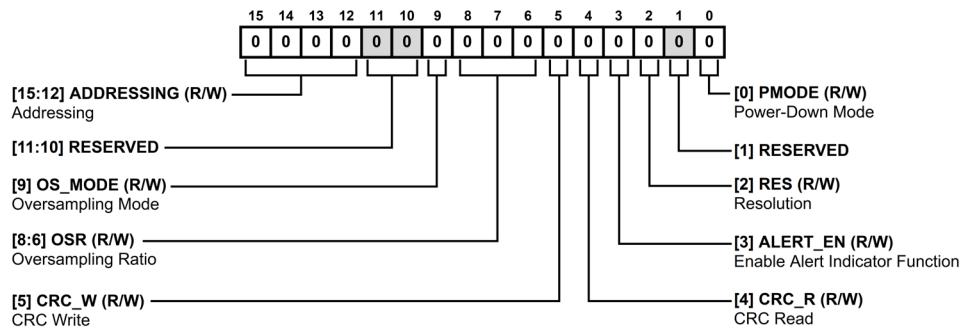

| Configuration1 レジスタ | 40 |

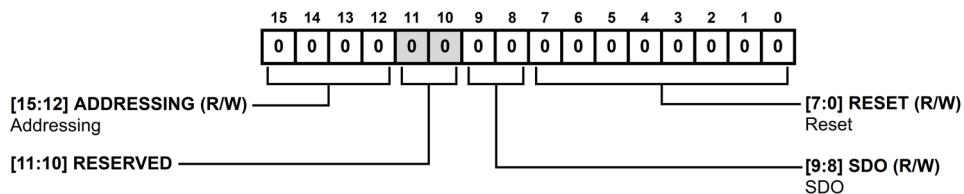

| Configuration2 レジスタ | 41 |

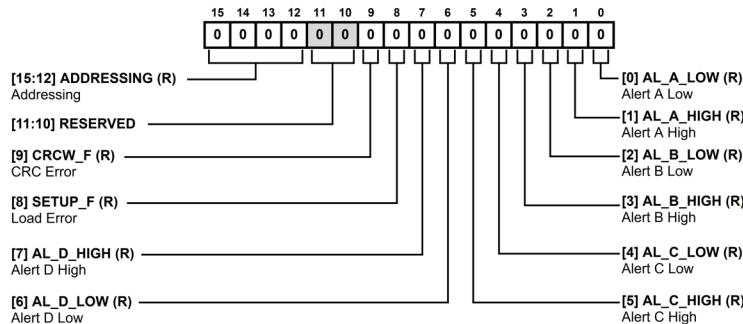

| アラート表示レジスタ          | 42 |

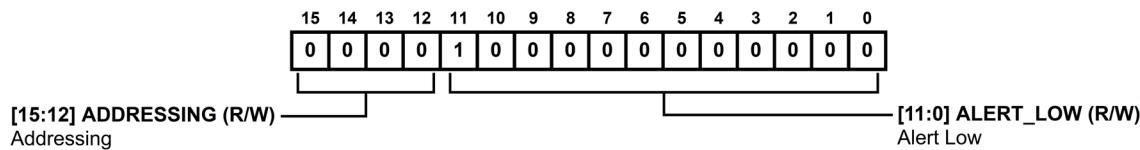

| アラート下限閾値レジスタ        | 43 |

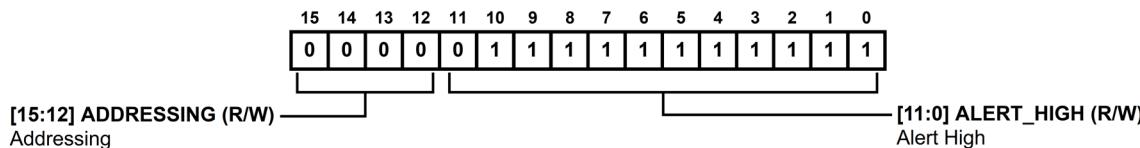

| アラート上限閾値レジスタ        | 43 |

| レイアウトのガイドライン        | 44 |

| 外形寸法                | 45 |

| オーダー・ガイド            | 45 |

| 評価用ボード              | 45 |

## 改訂履歴

10/2024—Revision 0: Initial Version

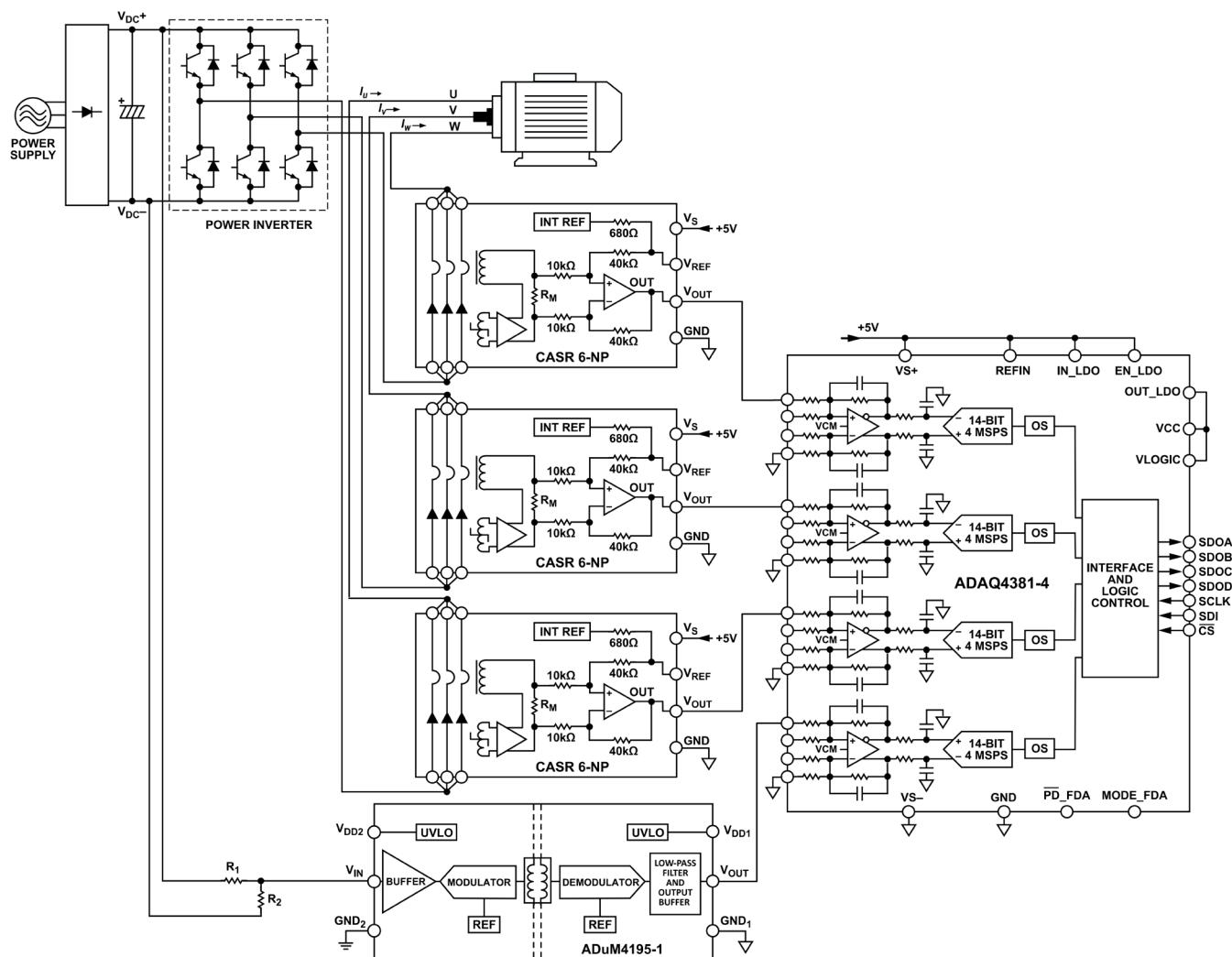

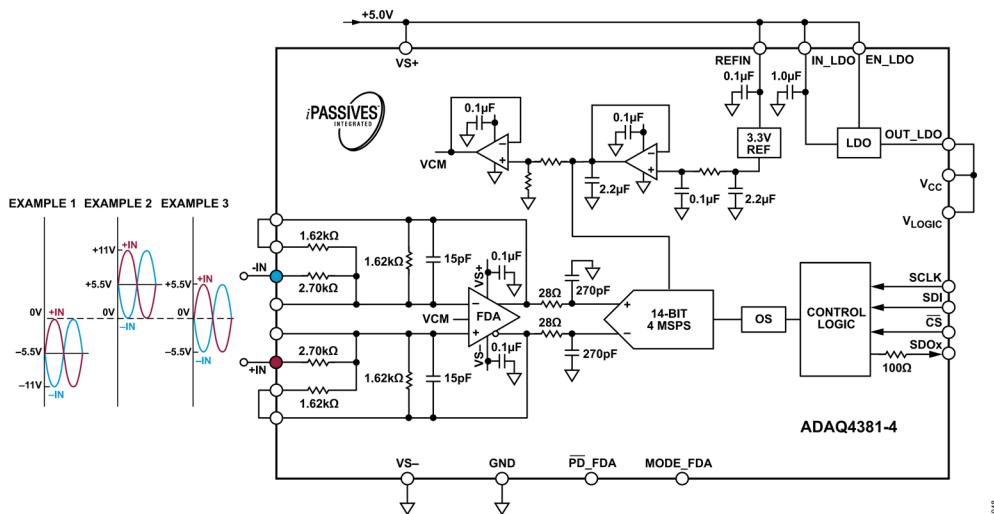

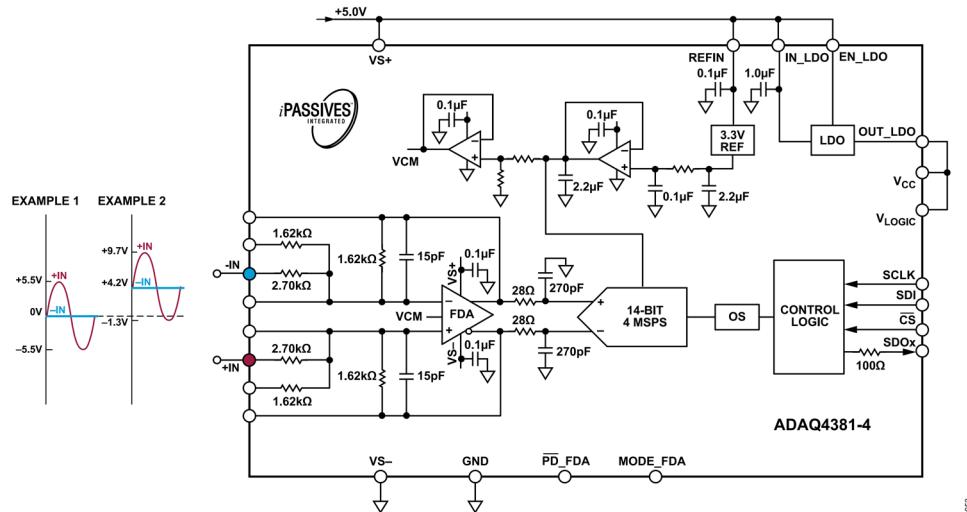

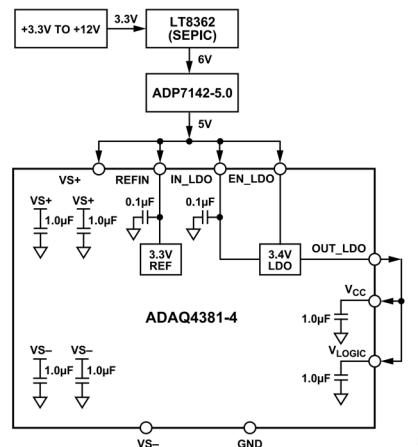

## 代表的なアプリケーション図

図 1. ADAQ4381-4 を使用したサーボモータ制御のための高精度電流および電圧センシング

## 仕様

特に指定がない限り、 $V_{S+} = REFIN = IN\_LDO = EN\_LDO = 5V \pm 5\%$ 、 $V_{CC} = V_{LOGIC} = 3.45V$  (OUT\_LDO) 、 $V_{S-} = 0V$ 、リファレンス電圧 ( $V_{REF}$ ) = 内部 3.3V、 $f_{SAMPLE} = 4MSPS$ 、完全差動入力構成、フルパワー動作モード、 $T_A = 25^\circ C$ 、オーバーサンプリングなし。

表 2. 電気仕様

| Parameter                                               | Test Conditions/Comments                                                                                                                                                          | Min                            | Typ                                                   | Max   | Unit              |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------|-------|-------------------|

| RESOLUTION                                              |                                                                                                                                                                                   | 14                             |                                                       |       | Bits              |

| ANALOG INPUT CHARACTERISTICS                            |                                                                                                                                                                                   |                                |                                                       |       |                   |

| Differential Input Voltage Range, $V_{IN}$ <sup>1</sup> | Gain = 0.3, $V_{IN} = 22V$ p-p<br>Gain = 0.6, $V_{IN} = 11V$ p-p<br>Gain = 1.0, $V_{IN} = 6.6V$ p-p<br>Gain = 1.6, $V_{IN} = 4.125V$ p-p                                          | -11<br>-5.5<br>-3.3<br>-2.0625 | +11<br>+5.5<br>+3.3<br>+2.0625                        |       | V                 |

| Input Resistance, $R_{IN}$                              | Fully differential input configuration<br>Gain = 0.3, 0.6<br>Gain = 1.0<br>Gain = 1.6<br>Single-ended input configuration<br>Gain = 0.3<br>Gain = 0.6<br>Gain = 1.0<br>Gain = 1.6 |                                | 5.40<br>3.24<br>2.026<br>3.05<br>3.32<br>2.16<br>1.46 |       | kΩ                |

| Input Capacitance                                       | IN <sub>X+</sub> , IN <sub>X-</sub>                                                                                                                                               | 2                              |                                                       |       | pF                |

| THROUGHPUT                                              |                                                                                                                                                                                   |                                |                                                       |       |                   |

| Complete Cycle                                          |                                                                                                                                                                                   | 250                            |                                                       |       | ns                |

| Conversion Time                                         |                                                                                                                                                                                   |                                | 190                                                   |       | ns                |

| Acquisition Phase                                       |                                                                                                                                                                                   | 110                            |                                                       |       | ns                |

| Conversion Rate                                         |                                                                                                                                                                                   |                                | 4                                                     |       | MSPS              |

| SAMPLING DYNAMICS                                       |                                                                                                                                                                                   |                                |                                                       |       |                   |

| Aperture Delay                                          |                                                                                                                                                                                   | 2                              |                                                       |       | ns                |

| Aperture Delay Match                                    |                                                                                                                                                                                   | 46.8                           | 145                                                   |       | ps                |

| Aperture Jitter                                         |                                                                                                                                                                                   | 20                             |                                                       |       | ps                |

| OVERALL SYSTEM DC ACCURACY                              |                                                                                                                                                                                   |                                |                                                       |       |                   |

| No Missing Codes                                        |                                                                                                                                                                                   | 14                             |                                                       |       | Bits              |

| Differential Nonlinearity Error (DNL)                   | All gains, $V_{S-} = 0V$                                                                                                                                                          | -0.99                          | ±0.4                                                  | +1    | LSB               |

| Integral Nonlinearity Error (INL) <sup>2</sup>          | All gains, $V_{S-} = 0V$                                                                                                                                                          | -1                             | ±0.3                                                  | +1    | LSB               |

| Gain Error                                              | Gain = 0.3                                                                                                                                                                        | -0.15                          | ±0.002                                                | +0.15 | %FS               |

|                                                         | Gain = 0.6, 1.0, 1.6                                                                                                                                                              | -0.05                          | ±0.003                                                | +0.05 | %FS               |

| Gain Error Drift                                        | All gains                                                                                                                                                                         |                                | ±0.8                                                  |       | ppm/°C            |

| Offset Error, Referred to Output (RTO)                  | Gain = 0.3                                                                                                                                                                        | -0.65                          | ±0.17                                                 | +0.65 | mV                |

|                                                         | Gain = 0.6                                                                                                                                                                        | -0.6                           | ±0.16                                                 | +0.6  | mV                |

|                                                         | Gain = 1.0                                                                                                                                                                        | -0.75                          | ±0.15                                                 | +0.75 | mV                |

|                                                         | Gain = 1.6                                                                                                                                                                        | -0.9                           | ±0.13                                                 | +0.9  | mV                |

| Offset Error Drift                                      | All gains                                                                                                                                                                         | -2.0                           | ±0.5                                                  | +2.0  | μV/°C             |

| Common-Mode Rejection Ratio (CMRR)                      | $\Delta V_{ICM}/\Delta V_{OSDIFF}$                                                                                                                                                | 80                             |                                                       |       | dB                |

| Power-Supply Rejection Ratio                            | $V_{S+}$ , REFIN, IN_LDO = 4.75 V to 5.25 V, $V_{S-} = GND$                                                                                                                       | 95                             |                                                       |       | dB                |

| OVERALL SYSTEM AC ACCURACY <sup>3</sup>                 | Fully differential and single-ended input configuration                                                                                                                           |                                |                                                       |       |                   |

| Dynamic Range                                           | $V_{IN} = -60$ dBFS, $f_{IN} = 1$ kHz                                                                                                                                             |                                |                                                       |       |                   |

|                                                         | Gain = 0.3, 0.6                                                                                                                                                                   | 85.3                           |                                                       |       | dB                |

|                                                         | Gain = 1.0, 1.6                                                                                                                                                                   | 85.1                           |                                                       |       | dB                |

| Total RMS Noise, Referred to Output (RTO)               | $V_{IN} = -60$ dBFS, $f_{IN} = 1$ kHz                                                                                                                                             |                                |                                                       |       |                   |

|                                                         | Gain = 0.3, 0.6                                                                                                                                                                   | 126.7                          |                                                       |       | μV <sub>RMS</sub> |

|                                                         | Gain = 1.0, 1.6                                                                                                                                                                   | 129.7                          |                                                       |       | μV <sub>RMS</sub> |

## 仕様

表 2. 電気仕様 (続き)

| Parameter                              | Test Conditions/Comments                                                                       | Min                                     | Typ    | Max                    | Unit  |                               |

|----------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------|--------|------------------------|-------|-------------------------------|

| Signal-to-Noise Ratio                  | $V_{IN} = -0.5 \text{ dBFS}, f_{IN} = 1 \text{ kHz}$                                           |                                         |        |                        |       |                               |

|                                        | Gain = 0.3, 0.6                                                                                | 84.1                                    | 85.1   |                        | dB    |                               |

|                                        | Gain = 1.0, 1.6                                                                                | 84.0                                    | 85.0   |                        | dB    |                               |

|                                        | Gain = 1.0, rolling average OSR = 8x, RES = 1                                                  |                                         | 92.4   |                        | dB    |                               |

|                                        | Gain = 1.0, $f_{IN} = 100 \text{ kHz}$ , full power mode                                       |                                         | 84.9   |                        | dB    |                               |

|                                        | Gain = 1.0, $f_{IN} = 200 \text{ kHz}$ , full power mode                                       |                                         | 84.8   |                        | dB    |                               |

| Signal-to-Noise + Distortion (SINAD)   | $V_{IN} = -0.5 \text{ dBFS}, f_{IN} = 1 \text{ kHz}$                                           |                                         |        |                        |       |                               |

|                                        | Gain = 0.3, 0.6                                                                                | 84.0                                    | 85.0   |                        | dB    |                               |

|                                        | Gain = 1.0, 1.6                                                                                | 83.9                                    | 84.9   |                        | dB    |                               |

|                                        | Gain = 1.0, $f_{IN} = 100 \text{ kHz}$ , full power mode                                       |                                         | 84.7   |                        | dB    |                               |

|                                        | Gain = 1.0, $f_{IN} = 200 \text{ kHz}$ , full power mode                                       |                                         | 84.4   |                        | dB    |                               |

|                                        | $V_{IN} = -0.5 \text{ dBFS}, f_{IN} = 1 \text{ kHz}$                                           |                                         |        |                        |       |                               |

| Total Harmonic Distortion              | All gains                                                                                      |                                         | -108   |                        | dB    |                               |

| Spurious-Free Dynamic Range            | $V_{IN} = -0.5 \text{ dBFS}, f_{IN} = 1 \text{ kHz}$                                           |                                         |        |                        |       |                               |

| -3 dB Bandwidth                        | All gains                                                                                      | 109                                     |        |                        | dB    |                               |

| Channel-to-Channel Isolation           | Gain = 0.3                                                                                     | 12.5                                    |        |                        | MHz   |                               |

| Channel-to-Channel Phase Matching      | Gain = 0.6, 1.0, 1.6                                                                           | 5.8                                     |        |                        | MHz   |                               |

| REFERENCE CHARACTERISTICS              | $V_{REFIN}$                                                                                    | Internal-reference supply voltage       | 4.5    | 5.0                    | 5.5   | V                             |

|                                        | $I_{REFIN}$                                                                                    | Internal-reference supply current       |        | 350                    | 600   | $\mu\text{A}$                 |

|                                        | $V_{REFSENSE}$                                                                                 | Internal-reference output voltage sense |        | 3.3                    |       | V                             |

| $V_{REF}$ Temperature Coefficient      | -40°C to +105°C                                                                                |                                         | 3.285  |                        | 3.315 | V                             |

| $V_{REF}$ Line Regulation              | $TCV_{OUT}$                                                                                    |                                         |        | 3                      | 10    | $\text{ppm}/^{\circ}\text{C}$ |

| $V_{REF}$ Load Regulation              | $-40^{\circ}\text{C} \leq T_A \leq +105^{\circ}\text{C}$                                       |                                         |        | 1.2                    | 5     | $\text{ppm}/\text{V}$         |

| $V_{REF}$ Noise                        |                                                                                                |                                         |        | 3                      | 8     | $\text{ppm}/\text{mA}$        |

| Output Voltage Hysteresis <sup>4</sup> | $V_{REF}$ Noise                                                                                |                                         |        | 9                      |       | $\mu\text{V}_{\text{RMS}}$    |

|                                        | $\Delta V_{OUT\_HYS}$                                                                          |                                         |        |                        |       | ppm                           |

|                                        | $\Delta T = 25^{\circ}\text{C} \text{ to } -40^{\circ}\text{C} \text{ to } 25^{\circ}\text{C}$ |                                         |        | 43                     |       | ppm                           |

|                                        | $\Delta T = 25^{\circ}\text{C} \text{ to } 105^{\circ}\text{C} \text{ to } 25^{\circ}\text{C}$ |                                         |        | -50                    |       | ppm                           |

|                                        | $\Delta T = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}$                              |                                         |        | 8                      |       | ppm                           |

| LDO CHARACTERISTICS                    |                                                                                                |                                         |        |                        |       |                               |

| IN_LDO Voltage Range                   |                                                                                                |                                         | 4.5    | 5.0                    | 5.5   | V                             |

| IN_LDO Supply Current                  | $I_{OUT\_LDO} = 150 \text{ mA}$                                                                |                                         |        | 130                    | 190   | $\mu\text{A}$                 |

| OUT_LDO Voltage                        | Internal LDO Output                                                                            | 3.35                                    | 3.45   | 3.55                   |       | V                             |

| Maximum Output Current                 |                                                                                                |                                         |        | 150                    |       | mA                            |

| Shutdown Current                       | IN_LDO = GND                                                                                   |                                         | 0.1    | 1                      |       | $\mu\text{A}$                 |

| Load Regulation                        | $I_{OUT\_LDO} = 1 \text{ mA} \text{ to } 150 \text{ mA}$                                       |                                         | 0.0005 |                        |       | $\%/\text{mA}$                |

| Start-Up Time                          |                                                                                                |                                         | 350    |                        |       | $\mu\text{s}$                 |

| Thermal Shutdown Threshold             |                                                                                                |                                         | 150    |                        |       | °C                            |

| Thermal Shutdown Hysteresis            |                                                                                                |                                         | 15     |                        |       | °C                            |

| DIGITAL INPUTS (SCLK, SDI, CS)         | Logic levels                                                                                   |                                         |        |                        |       |                               |

| Input Voltage Low ( $V_{IL}$ )         |                                                                                                |                                         |        | 0.2 $\times V_{LOGIC}$ |       | V                             |

| Input Voltage High ( $V_{IH}$ )        |                                                                                                |                                         |        | 0.8 $\times V_{LOGIC}$ |       | V                             |

| Input Current Low ( $I_{IL}$ )         |                                                                                                | -1                                      |        | +1                     |       | $\mu\text{A}$                 |

| Input Current High ( $I_{IH}$ )        |                                                                                                | -1                                      |        | +1                     |       | $\mu\text{A}$                 |

## 仕様

表 2. 電気仕様 (続き)

| Parameter                                      | Test Conditions/Comments                       | Min               | Typ     | Max  | Unit    |

|------------------------------------------------|------------------------------------------------|-------------------|---------|------|---------|

| DIGITAL OUTPUTS (SDOA, SDOB, SDOC, SDOD/ALERT) |                                                |                   |         |      |         |

| Output Coding                                  |                                                | Twos complement   |         |      | Bits    |

| Output Low Voltage ( $V_{OL}$ )                | Current sink ( $I_{SINK}$ ) = +300 $\mu$ A     |                   | 0.4     |      | V       |

| Output High Voltage ( $V_{OH}$ )               | Current source ( $I_{SOURCE}$ ) = -300 $\mu$ A | $V_{LOGIC} - 0.3$ |         |      | V       |

| Floating-State Leakage Current                 |                                                |                   | $\pm 1$ |      | $\mu$ A |

| Floating-State Output Capacitance              |                                                | 10                |         |      | pF      |

| POWER-DOWN/MODE SIGNALING                      | $PD\_FDA/MODE\_FDA$                            |                   |         |      |         |

| Low                                            | Disabled, low power mode                       | <1                |         |      | V       |

| High                                           | Enabled, full power mode                       | >1.5              |         |      | V       |

| POWER SUPPLY REQUIREMENTS                      |                                                |                   |         |      |         |

| Operating Voltage Range                        |                                                |                   |         |      |         |

| $V_{CC}$                                       |                                                | 3.4               |         | 3.6  | V       |

| $V_{LOGIC}$                                    |                                                | 1.65              |         | 3.6  | V       |

| $V_{S+}$ <sup>5</sup>                          |                                                | 4.5               | 5.0     | 5.5  | V       |

| $V_{S-}$                                       |                                                | -5                |         | 0    | V       |

| ADAQ4381-4 Current Draw                        | $V_{CC} = V_{LOGIC} = 3.45$ V, $V_S = 5$ V     |                   |         |      |         |

| $I_{VCC}$                                      | $V_{CC}$ supply current                        |                   |         |      |         |

|                                                | Normal mode (Dynamic)                          | 38                | 42      |      | mA      |

|                                                | Normal mode (Static)                           | 1.8               | 2.3     |      | mA      |

|                                                | Shutdown mode                                  | 101               | 200     |      | $\mu$ A |

| $I_{VLOGIC}$                                   | $V_{LOGIC}$ supply current                     |                   |         |      |         |

|                                                | Normal mode (Dynamic)                          | 7.3               | 9       |      | mA      |

|                                                | Normal mode (Static)                           | 10                | 200     |      | nA      |

|                                                | Shutdown mode                                  | 10                | 200     |      | nA      |

| $I_{VS+}/I_{VS-}$                              | $V_{S+}/V_{S-}$ supply current                 |                   |         |      |         |

|                                                | Full power mode                                | 25                | 28      |      | mA      |

|                                                | Low power mode                                 | 15                | 18      |      | mA      |

| ADAQ4381-4 Power Dissipation                   | $V_{CC} = V_{LOGIC} = 3.45$ V, $V_S = 5$ V     |                   |         |      |         |

| $P_{VCC}$                                      | $V_{CC}$ power                                 |                   |         |      |         |

|                                                | Normal mode (Dynamic)                          | 130               | 155     |      | mW      |

|                                                | Normal mode (Static)                           | 6                 | 8       |      | mW      |

| $P_{VLOGIC}$                                   | $V_{LOGIC}$ power                              |                   |         |      |         |

|                                                | Normal mode (Dynamic)                          | 25                | 28      |      | mW      |

|                                                | Normal mode (Static)                           | 36                | 720     |      | nW      |

| $P_{VS+}/P_{VS-}$                              | $V_{S+}/V_{S-}$ power                          |                   |         |      |         |

|                                                | Full power mode                                | 125               | 135     |      | mW      |

|                                                | Low power mode                                 | 75                | 80      |      | mW      |

| Total Power Dissipation                        | ADAQ4381-4 power dissipation                   |                   |         |      |         |

|                                                | Dynamic, full power mode                       | 280               | 318     |      | mW      |

|                                                | Dynamic, low power mode                        | 230               | 263     |      | mW      |

| TEMPERATURE RANGE                              |                                                |                   |         |      |         |

| Specified Performance                          | $T_{MIN}$ to $T_{MAX}$ <sup>6</sup>            | -40               |         | +105 | °C      |

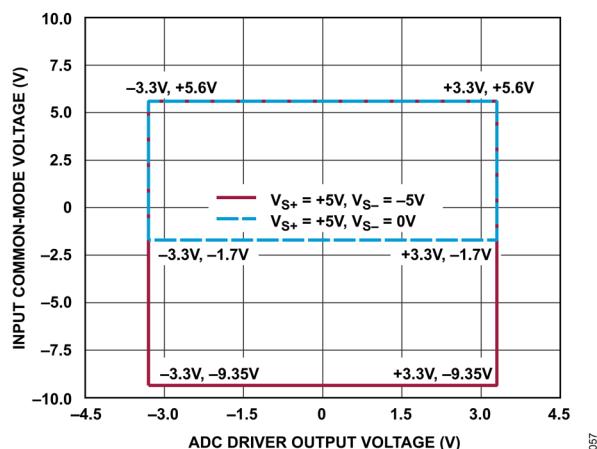

<sup>1</sup> 絶対差動入力範囲  $V_{IN}$  は、図 48～図 55 に示すような許容入力コモンモード電圧範囲内に収める必要があります。 $V_{IN}$  は、使用する電源レール  $V_S+$  および  $V_S-$  に依存します。

<sup>2</sup> 絶対差動入力範囲  $V_{IN}$  をフルスケールの 95% 以内に制限することで、ADC ドライバには  $V_S = 0$  V で十分なフットルームが確保され、仕様規定された性能を達成することができます。

## 仕様

<sup>3</sup>特に指定のない限り、デシベルで表記されるすべての AC 仕様は、フルスケール入力レンジ (FSR) を基準とし、フルスケールより 0.5dB 低い入力信号でテストされたものです。

<sup>4</sup>出力電圧のヒステリシスはパッケージの応力によって生じますが、この応力は、その IC がそれまで置かれていた環境が、現在より高温だったのか低温だったのかによって異なります。出力電圧は常に 25°C で測定しますが、連続測定時は、IC に高温限界値または低温限界値までの温度サイクルを実行してから測定を行います。ヒステリシスは、高温または低温の 3 つの温度サイクルの平均値に対する最大の出力変化を測定します。適切な温度管理 (20°C ~ 30°C の動作温度) の下で保管されている計測器の場合、通常は支配的な誤差要因とはなりません。代表的なヒステリシスは、1 回の熱サイクルごとに事前に調整された、25°C → 低温 → 25°C、または 25°C → 高温 → 25°C の最も厳しい条件での値です。

<sup>5</sup>最大動作電源電圧  $V_S$  ( $V_{S+} - V_{S-}$ ) は 10V を超えてはなりません。

<sup>6</sup>ADAQ4381-4 の性能は、拡張工業用温度範囲  $T_{CASE} = -40^\circ\text{C} \sim +105^\circ\text{C}$  の全体に対して評価されています。

## 仕様

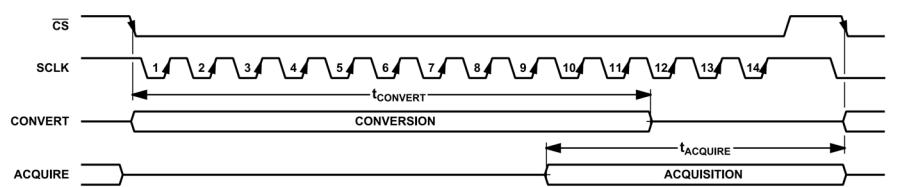

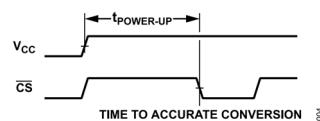

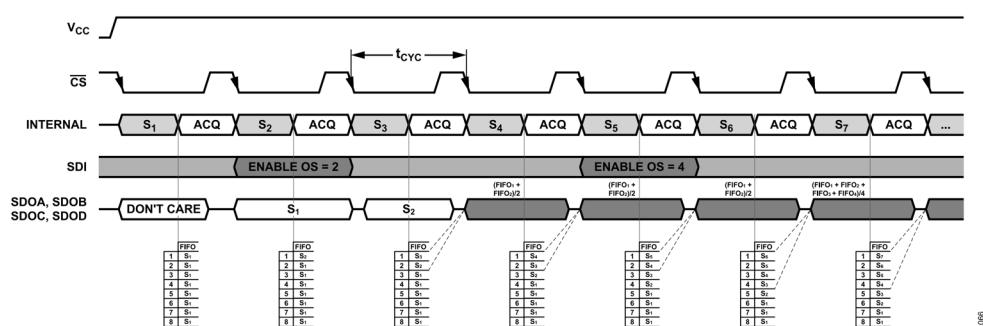

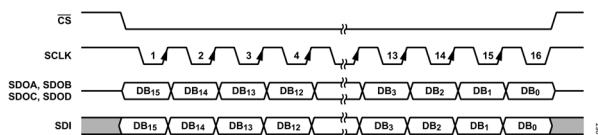

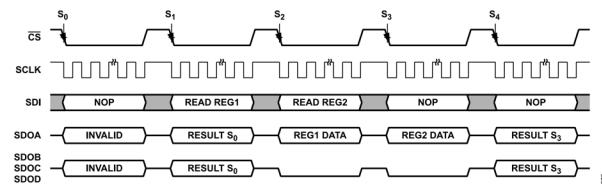

## タイミング仕様

特に指定のない限り、 $V_{CC} = 3.0V \sim 3.6V$ 、 $V_{LOGIC} = 1.65V \sim 3.6V$ 、 $V_{REF} = 3.3V$ 、 $T_A = -40^\circ C \sim +105^\circ C$ 、 $C_{LOAD\_SDO} = 30pF$ 。

表 3. デジタル・インターフェースのタイミング

| Parameter         | Min  | Typ                                   | Max | Unit | Description                                                                                   |

|-------------------|------|---------------------------------------|-----|------|-----------------------------------------------------------------------------------------------|

| $t_{CYC}$         | 250  |                                       |     | ns   | Time between conversions                                                                      |

| $t_{SCLKED}$      | 5    |                                       |     | ns   | $\overline{CS}$ falling edge to first SCLK falling edge                                       |

| $t_{SCLK}$        | 12.5 |                                       |     | ns   | SCLK period                                                                                   |

| $t_{SCLKH}$       | 5.5  |                                       |     | ns   | SCLK high time                                                                                |

| $t_{SCLKL}$       | 5.5  |                                       |     | ns   | SCLK low time                                                                                 |

| $t_{CSH}$         | 10   |                                       |     | ns   | $\overline{CS}$ pulse width                                                                   |

| $t_{QUIET}$       | 10   |                                       |     | ns   | Interface quiet time prior to conversion                                                      |

| $t_{SDOEN}$       |      |                                       |     |      | $\overline{CS}$ low to SDOx enabled                                                           |

|                   |      | 5.5                                   |     | ns   | $V_{LOGIC} \geq 1.75V$                                                                        |

|                   |      | 7.6                                   |     | ns   | $V_{LOGIC} < 1.75V$                                                                           |

| $t_{SDOH}$        | 3    |                                       |     | ns   | SCLK rising edge to SDOx hold time                                                            |

| $t_{SDOS}$        |      |                                       |     |      | SCLK rising edge to SDOx setup time                                                           |

|                   |      | 5.5                                   |     | ns   | $V_{LOGIC} \geq 2.1V$                                                                         |

|                   |      | 7.5                                   |     | ns   | $1.65V \leq V_{LOGIC} < 2.1V$                                                                 |

| $t_{SDOT}$        |      | 8                                     |     | ns   | $\overline{CS}$ rising edge to SDOx high impedance                                            |

| $t_{SDIS}$        | 4    |                                       |     | ns   | SDI setup time prior to SCLK falling edge                                                     |

| $t_{SDIH}$        | 4    |                                       |     | ns   | SDI hold time after SCLK falling edge                                                         |

| $t_{SCLKCS}$      | 0    |                                       |     | ns   | SCLK rising edge to $\overline{CS}$ rising edge                                               |

| $t_{CONVERT}$     |      | 190                                   |     | ns   | Conversion time                                                                               |

| $t_{ACQUIRE}$     | 110  |                                       |     | ns   | Acquire time                                                                                  |

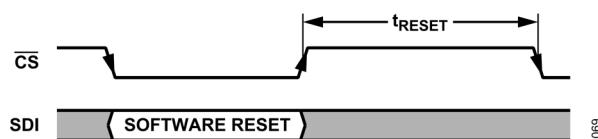

| $t_{RESET}$       |      | 250                                   |     | ns   | Valid time to start conversion after soft reset                                               |

|                   |      | 800                                   |     | ns   | Valid time to start conversion after hard reset                                               |

| $t_{POWER-UP}$    |      |                                       |     |      | Supply active to conversion                                                                   |

|                   |      | 5                                     |     | ms   | First conversion allowed                                                                      |

|                   |      | 5                                     |     | ms   | Settled to within 1%                                                                          |

| $t_{REGWRITE}$    |      | 5                                     |     | ms   | Supply active to register read write access allowed                                           |

| $t_{STARTUP}$     |      |                                       |     |      | Exiting shutdown mode to conversion                                                           |

|                   |      | 10                                    |     | μs   | Settled to within 1%                                                                          |

| $t_{CONVERT0}$    | 6    | 8                                     | 10  | ns   | Conversion time for first sample in OS normal mode                                            |

| $t_{CONVERTx}$    |      | $t_{CONVERT0} + (250 \times (x - 1))$ |     | ns   | Conversion time for $x^{\text{th}}$ sample in OS normal mode                                  |

| $t_{ALERTS}$      |      |                                       | 220 | ns   | Time from $\overline{CS}$ to $\overline{\text{ALERT}}$ indication                             |

| $t_{ALERTC}$      |      |                                       | 10  | ns   | Time from $\overline{CS}$ to $\overline{\text{ALERT}}$ clear                                  |

| $t_{ALERTS\_NOS}$ |      |                                       | 20  | ns   | Time from internal conversion with exceeded threshold to $\overline{\text{ALERT}}$ indication |

## 仕様

## タイミング図

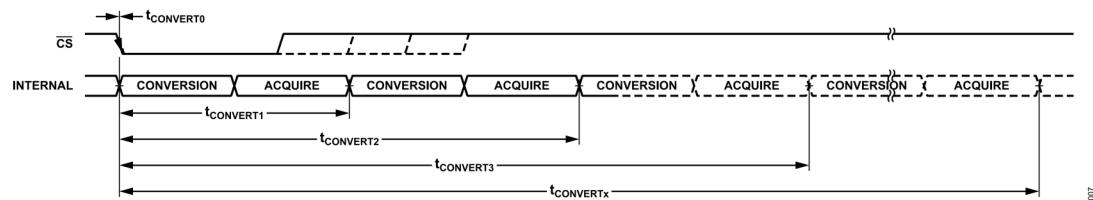

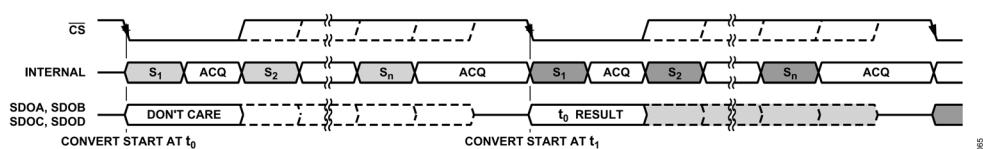

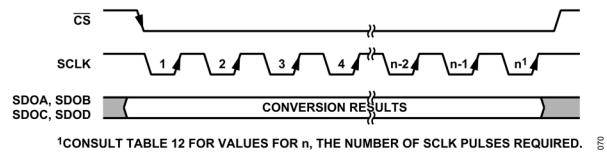

図 2. シリアル・インターフェースのタイミング図

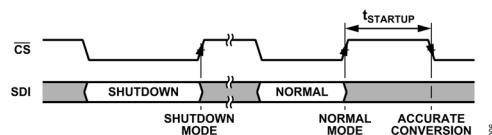

図 3. 内部変換取得のタイミング

図 4. 変換までのパワーアップ時間

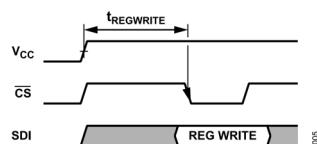

図 5. レジスタの読み書きアクセスまでのパワーアップ時間

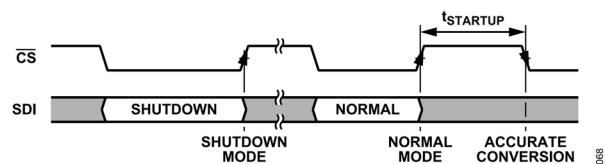

図 6. シャットダウン・モードからノーマル・モードへの遷移タイミング

## 仕様

図 7. OS ノーマル・モードでの変換タイミング

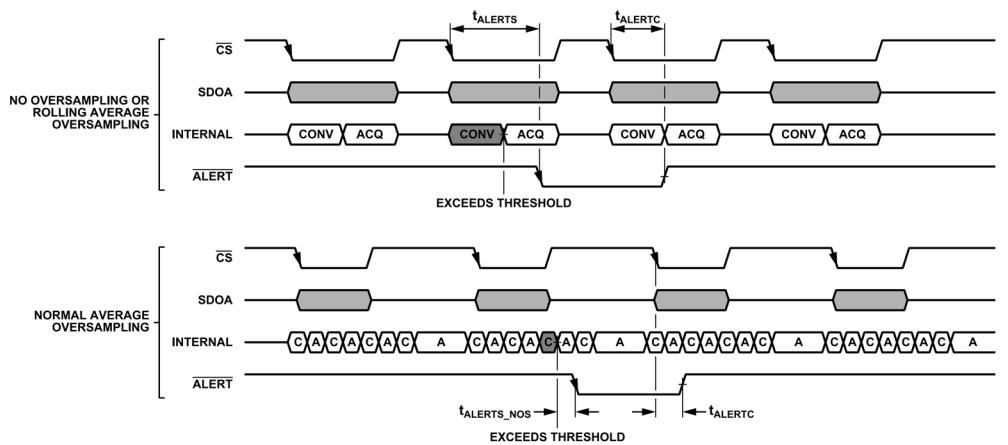

図 8.  $\overline{\text{ALERT}}$  のタイミング

## 絶対最大定格

表 4. 絶対最大定格

| Parameter                                                                                              | Rating                               |

|--------------------------------------------------------------------------------------------------------|--------------------------------------|

| Analog Inputs<br>IN <sub>X</sub> 1+, IN <sub>X</sub> 1-, IN <sub>X</sub> 2+, IN <sub>X</sub> 2- to GND | -12.5 V to +12.5 V or $\pm 10$ mA    |

| Supply Voltages<br>V <sub>S</sub>                                                                      | 11 V                                 |

| IN_LDO to GND                                                                                          | -0.3 V to +6.5 V                     |

| EN_LDO to GND                                                                                          | -0.3 V to +6.5 V                     |

| V <sub>LOGIC</sub> to GND                                                                              | -0.3 V to +4 V                       |

| V <sub>CC</sub> to GND                                                                                 | -0.3 V to +4 V                       |

| REFIN to GND                                                                                           | -0.3 V to +38 V                      |

| Digital Inputs to GND                                                                                  | -0.3 V to V <sub>LOGIC</sub> + 0.3 V |

| Digital Outputs to GND                                                                                 | -0.3 V to V <sub>LOGIC</sub> + 0.3 V |

| Temperature<br>Storage Range                                                                           | -65°C to +150°C                      |

| Junction                                                                                               | 125°C                                |

| Lead Soldering                                                                                         | 260°C reflow as per JEDEC J-STD-020  |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意を払う必要があります。θ<sub>JA</sub> は、1 立方フィートの密封容器内で測定された、自然対流下でのジャンクションから周囲への熱抵抗です。θ<sub>JB</sub> は、ジャンクションから基板への熱抵抗です。θ<sub>JC</sub> は、ジャンクションからケースへの熱抵抗です。

表 5. 热抵抗

| Package | Type <sup>1</sup> | θ <sub>JA</sub> | θ <sub>JC_TOP</sub> | θ <sub>JC_BOTTOM</sub> | θ <sub>JB</sub> | Ψ <sub>JT</sub> | Ψ <sub>JB</sub> | Unit |

|---------|-------------------|-----------------|---------------------|------------------------|-----------------|-----------------|-----------------|------|

| BC-81-7 |                   | 27.2            | 38.1                | 10.4                   | 11.9            | 5.7             | 12.0            | °C/W |

<sup>1</sup> テスト条件 1：熱抵抗のシミュレーション値は、ビアを備えた 2S2P の JEDEC PCB を使用した場合の値です。ただし、θ<sub>JC\_TOP</sub> では 1S0P の JEDEC PCB を使用しています。

特に指定のない限り、表 5 に仕様規定されている熱抵抗値は、JEDEC 仕様に基づいてシミュレーションされており、JESD51-12 に従って使用する必要があります。

## 静電放電定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帶電デバイス・モデル (FICDM)。

## ADAQ4381-4 の ESD 定格

表 6. ADAQ4381-4、81 ボール CSP\_BGA

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | $\pm 2000$              | 2     |

| FICDM     | $\pm 500$               | C2B   |

## ESD に関する注意

|                                                                                   |                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p>ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することができます。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。</p> |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## ピン配置およびピン機能の説明

## NOTES

1. DNC = DO NOT CONNECT. LEAVE THESE PINS FLOATING/UNCONNECTED.

88

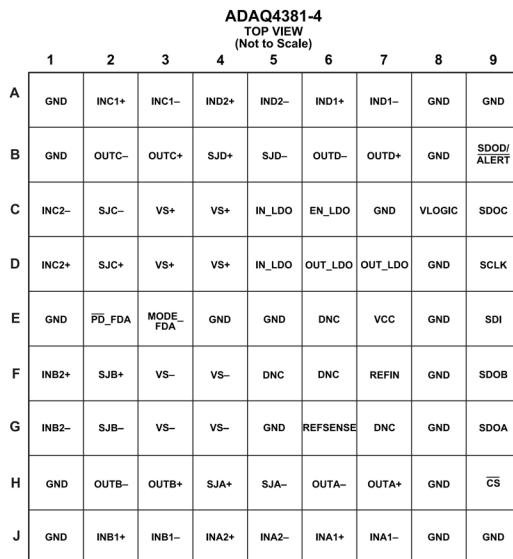

図 9. ピン配置

表 7. ピン機能の説明

| ピン番号                                                                       | 記号         | タイプ <sup>1</sup> | 説明                                                                                                                                                                            |

|----------------------------------------------------------------------------|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A8, A9, B1, B8, C7, D8, E1, E4, E5, E8, F8, G5, G8, H1, H8, J1, J8, J9 | GND        | P                | 電源グラウンド。                                                                                                                                                                      |

| A2                                                                         | INC1+      | AI               | チャンネル C の 1.62kΩ ゲイン抵抗ネットワークへの正側入力。                                                                                                                                           |

| A3                                                                         | INC1-      | AI               | チャンネル C の 1.62kΩ ゲイン抵抗ネットワークへの負側入力。                                                                                                                                           |

| A4                                                                         | IND2+      | AI               | チャンネル D の 2.70kΩ ゲイン抵抗ネットワークへの正側入力。                                                                                                                                           |

| A5                                                                         | IND2-      | AI               | チャンネル D の 2.70kΩ ゲイン抵抗ネットワークへの負側入力。                                                                                                                                           |

| A6                                                                         | IND1+      | AI               | チャンネル D の 1.62kΩ ゲイン抵抗ネットワークへの正側入力。                                                                                                                                           |

| A7                                                                         | IND1-      | AI               | チャンネル D の 1.62kΩ ゲイン抵抗ネットワークへの負側入力。                                                                                                                                           |

| B2                                                                         | OUTC-      | AO <sup>2</sup>  | チャンネル C の ADC ドライバの負側出力。                                                                                                                                                      |

| B3                                                                         | OUTC+      | AO <sup>2</sup>  | チャンネル C の ADC ドライバの正側出力。                                                                                                                                                      |

| B4                                                                         | SJD+       | AI               | チャンネル D の ADC ドライバの正側入力サミング・ノード。                                                                                                                                              |

| B5                                                                         | SJD-       | AI               | チャンネル D の ADC ドライバの負側入力サミング・ノード。                                                                                                                                              |

| B6                                                                         | OUTD-      | AO <sup>2</sup>  | チャンネル D の ADC ドライバの負側出力                                                                                                                                                       |

| B7                                                                         | OUTD+      | AO <sup>2</sup>  | チャンネル D の ADC ドライバの正側出力。                                                                                                                                                      |

| B9                                                                         | SDOD/ALERT | DO               | シリアル・データ出力 D / ALERT。このピンは、シリアル・データ出力ピン、またはアラート表示出力ピンとして機能します。<br>SDOD: このピンは、変換結果にアクセスするためのシリアル・データ出力ピンとして機能します。<br>ALERT: このピンは、アラート・ピンとして機能し、ローになることで変換結果が設定閾値を超えたことを示します。 |

| C1                                                                         | INC2-      | AI               | チャンネル C の 2.70kΩ ゲイン抵抗ネットワークへの負側入力。                                                                                                                                           |

| C2                                                                         | SJC-       | AI               | チャンネル C の ADC ドライバの負側入力サミング・ノード。                                                                                                                                              |

| C3, C4, D3, D4                                                             | VS+        | P                | アンプの正側電源。これらのピンは内部でグラウンドとの間でデカップリングされています。デカップリング・コンデンサの追加が、必要でない場合もあります。                                                                                                     |

| C5, D5                                                                     | IN_LDO     | P                | 内蔵 LDO の入力電圧。VS+ (あるいは 3.6V < IN_LDO < 5.5V となる電源) に接続します。このピンは内部でグラウンドとの間でデカップリングされています。デカップリング・コンデンサの追加が、必要でない場合もあります。                                                      |

| C6                                                                         | EN_LDO     | P                | LDO イネーブル。内蔵 LDO をイネーブル場合は、IN_LDO または VS+に接続します。それ以外の場合は、GND に接続します。                                                                                                          |

| C8                                                                         | VLOGIC     | P                | ADC ロジック・インターフェースの電源電圧。このピンは内部でグラウンドとの間でデカップリングされています。デカップリング・コンデンサの追加が、必要でない場合もあります。                                                                                         |

## ピン配置およびピン機能の説明

表 7. ピン機能の説明（続き）

| ピン番号           | 記号       | タイプ <sup>1</sup> | 説明                                                                                                                                                                   |

|----------------|----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C9             | SDOC     | DO               | シリアル・データ出力 C。このピンは、変換結果およびレジスタの内容にアクセスするためのシリアル・データ出力ピンとして機能します。                                                                                                     |

| D1             | INC2+    | AI               | チャンネル C の 2.70kΩ ゲイン抵抗ネットワークへの正側入力。                                                                                                                                  |

| D2             | SJC+     | AI               | チャンネル C の ADC ドライバの正側入力サミング・ノード。                                                                                                                                     |

| D6, D7         | OUT_LDO  | P                | 内蔵 LDO の出力電圧。このピンの電圧は 3.45V（代表値）です。                                                                                                                                  |

| D9             | SCLK     | DI               | シリアル・クロック入力。このシリアル・クロック入力は、ADC とのデータ転送に使用します。                                                                                                                        |

| E2             | PD_FDA   | P                | アクティブ・ロー。ADC ドライバをパワーダウン（ディスエーブル）するには、このピンを GND に接続します。通常動作では、VS+に接続します。                                                                                             |

| E3             | MODE_FDA | P                | ADC ドライバの電力モード。VS+に接続すると、フルパワー動作モードになります。GND に接続すると、ローパワー動作モードになります。                                                                                                 |

| E6, F5, F6, G7 | DNC      | N/A <sup>3</sup> | 接続禁止。これらのピンはフロート状態／無接続にしておきます。                                                                                                                                       |

| E7             | VCC      | P                | ADC アナログ電源電圧。このピンは内部でグラウンドとの間でデカッピングされています。デカッピング・コンデンサの追加が、必要でない場合もあります。                                                                                            |

| E9             | SDI      | DI               | シリアル・データ入力。このピンは、内蔵コントロール・レジスタに書き込まれたデータを提供します。                                                                                                                      |

| F1             | INB2+    | AI               | チャンネル B の 2.70kΩ ゲイン抵抗ネットワークへの正側入力。                                                                                                                                  |

| F2             | SJB+     | AI               | チャンネル B の ADC ドライバの正側入力サミング・ノード。                                                                                                                                     |

| F3, F4, G3, G4 | VS-      | P                | アンプの負側電源。これらのピンは内部でグラウンドとの間でデカッピングされています。デカッピング・コンデンサの追加が、必要でない場合もあります。                                                                                              |

| F7             | REFIN    | P                | 内部リファレンス電源電圧。通常動作では、VS+に接続します。このピンは内部でグラウンドとの間でデカッピングされています。デカッピング・コンデンサの追加が、必要でない場合もあります。                                                                           |

| F9             | SDOB     | DO               | シリアル・データ出力 B。このピンは、変換結果およびレジスタの内容にアクセスするためのシリアル・データ出力ピンとして機能します。                                                                                                     |

| G1             | INB2-    | AI               | チャンネル B の 2.70kΩ ゲイン抵抗ネットワークへの負側入力。                                                                                                                                  |

| G2             | SJB-     | AI               | チャンネル B の ADC ドライバの負側入力サミング・ノード。                                                                                                                                     |

| G6             | REFSENSE | AO <sup>2</sup>  | リファレンス出力センス・ピン。<br>正確なゲイン・キャリブレーションのため、このピンを使用して内部 3.3V リファレンスの実電圧レベルを計測します。使用しない場合は、このピンをフローティング状態／無接続にします。<br>システムの安定性を確保するため、このピンに接続する容量性負荷が 1μF を超えることがないようにします。 |

| G9             | SDOA     | DO               | シリアル・データ出力 A。このピンは、変換結果およびレジスタの内容にアクセスするためのシリアル・データ出力ピンとして機能します。                                                                                                     |

| H2             | OUTB-    | AO <sup>2</sup>  | チャンネル B の ADC ドライバの負側出力。                                                                                                                                             |

| H3             | OUTB+    | AO <sup>2</sup>  | チャンネル B の ADC ドライバの正側出力。                                                                                                                                             |

| H4             | SJA+     | AI               | チャンネル A の ADC ドライバの正側入力サミング・ノード。                                                                                                                                     |

| H5             | SJA-     | AI               | チャンネル A の ADC ドライバの負側入力サミング・ノード。                                                                                                                                     |

| H6             | OUTA-    | AO <sup>2</sup>  | チャンネル A の ADC ドライバの負側出力。                                                                                                                                             |

| H7             | OUTA+    | AO <sup>2</sup>  | チャンネル A の ADC ドライバの正側出力。                                                                                                                                             |

| H9             | CS       | DI               | チップ・セレクト入力。アクティブ・ローのロジック入力。この入力は、ADAQ4381-4 の変換開始とシリアル・データ転送のフレーミングの 2 通りの機能を提供します。                                                                                  |

| J2             | INB1+    | AI               | チャンネル B の 1.62kΩ ゲイン抵抗ネットワークへの正側入力。                                                                                                                                  |

| J3             | INB1-    | AI               | チャンネル B の 1.62kΩ ゲイン抵抗ネットワークへの負側入力。                                                                                                                                  |

| J4             | INA2+    | AI               | チャンネル A の 2.70kΩ ゲイン抵抗ネットワークへの正側入力。                                                                                                                                  |

| J5             | INA2-    | AI               | チャンネル A の 2.70kΩ ゲイン抵抗ネットワークへの負側入力。                                                                                                                                  |

| J6             | INA1+    | AI               | チャンネル A の 1.62kΩ ゲイン抵抗ネットワークへの正側入力。                                                                                                                                  |

| J7             | INA1-    | AI               | チャンネル A の 1.62kΩ ゲイン抵抗ネットワークへの負側入力。                                                                                                                                  |

<sup>1</sup> AI はアナログ入力、AO はアナログ出力、P は電源、DI はデジタル入力、DO はデジタル出力です。<sup>2</sup> アナログ出力ピンは、電圧のモニタリングと計測、および ADAQ4381-4 のゲイン設定にのみ使用します。外部から駆動しないでください。<sup>3</sup> N/A は該当なしを意味します。

## 代表的な性能特性

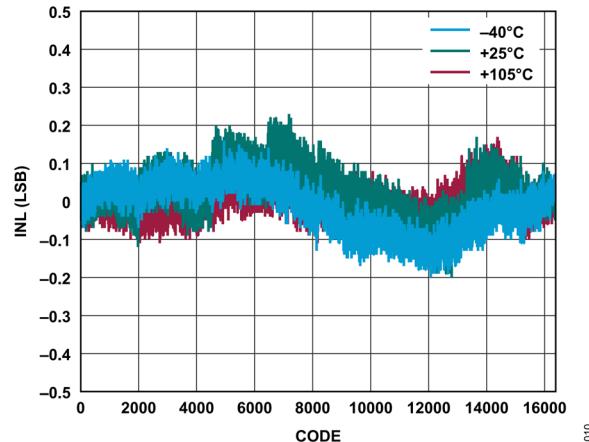

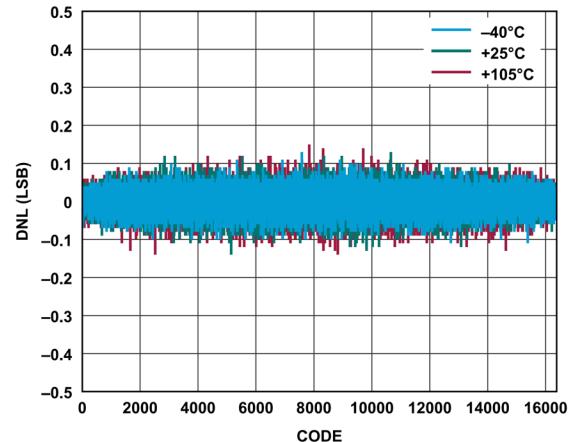

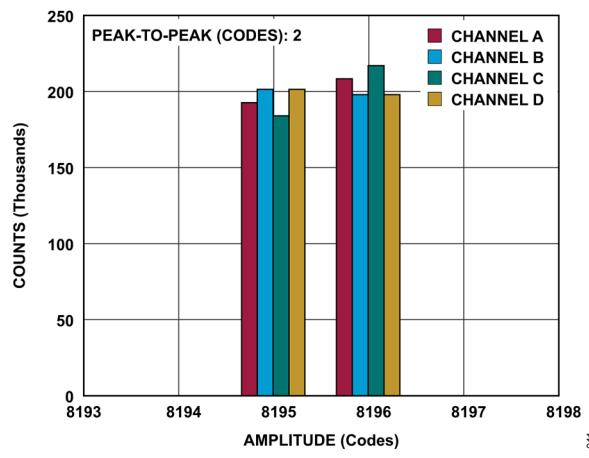

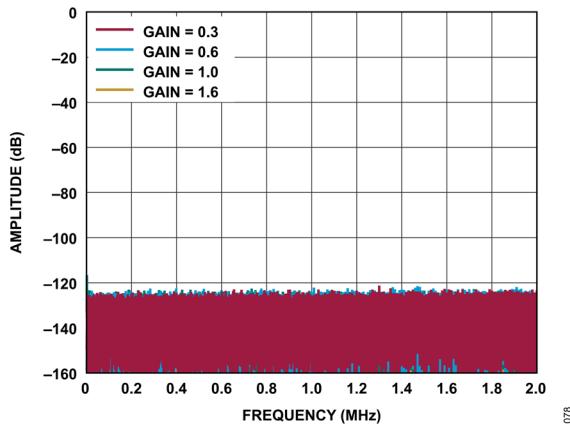

特に指定がない限り、 $V_S = \text{REFIN} = \text{IN\_LDO} = \text{EN\_LDO} = 5V$ 、 $V_{CC} = V_{LOGIC} = 3.45V$ 、リファレンス電圧 ( $V_{REF}$ ) = 内部 3.3V、 $f_{SAMPLE} = 4\text{MSPS}$ 、完全差動入力構成、フルパワー動作モード、 $T_A = 25^\circ\text{C}$ 、オーバーサンプリングなし。

図 10. 様々な温度での INL とコードの関係、ゲイン = 1.0

図 13. 様々な温度での DNL とコードの関係、ゲイン = 1.0

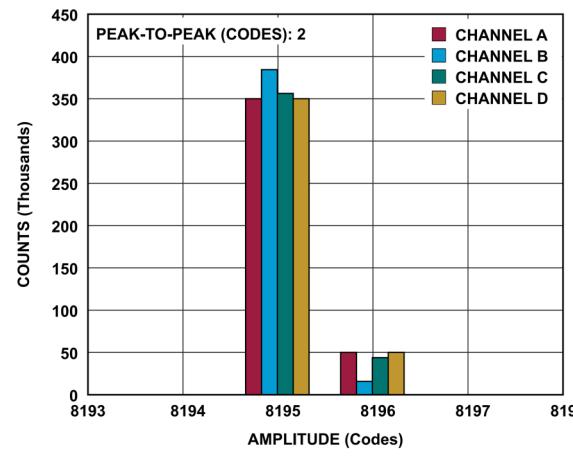

図 11. コード遷移時の DC 入力のヒストグラム

図 14. コード中心での DC 入力のヒストグラム

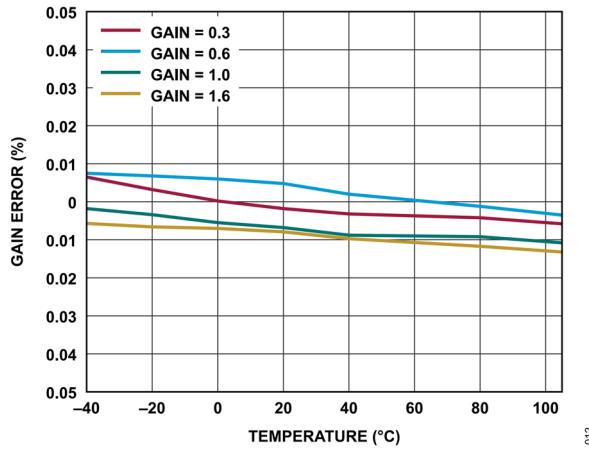

図 12. ゲイン誤差と温度の関係

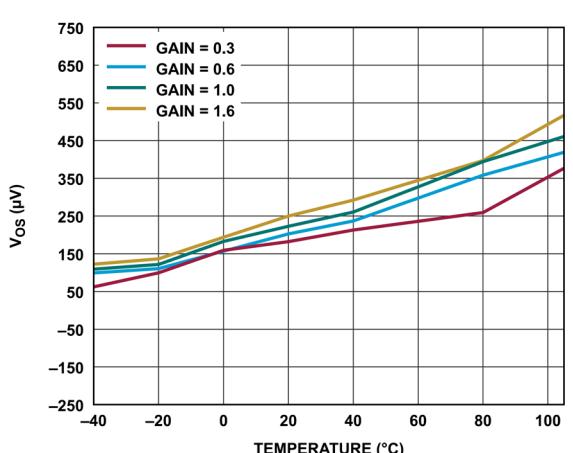

図 15. オフセット誤差と温度の関係

## 代表的な性能特性

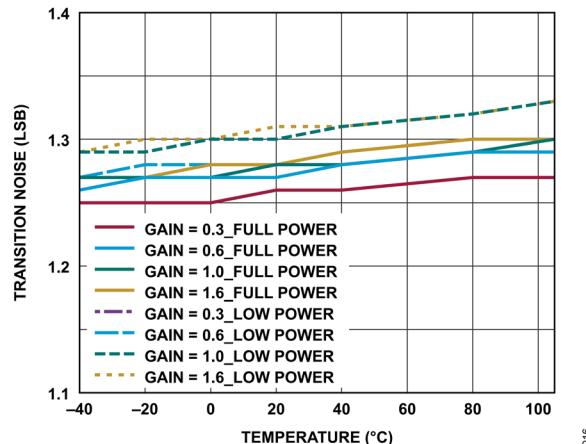

図 16. 遷移ノイズの温度特性

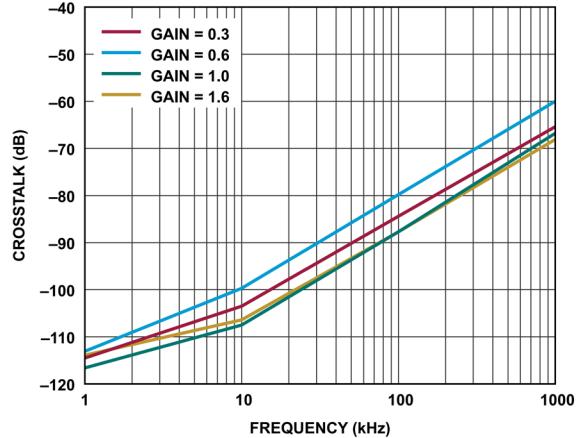

図 19. チャンネル間アイソレーションと周波数の関係

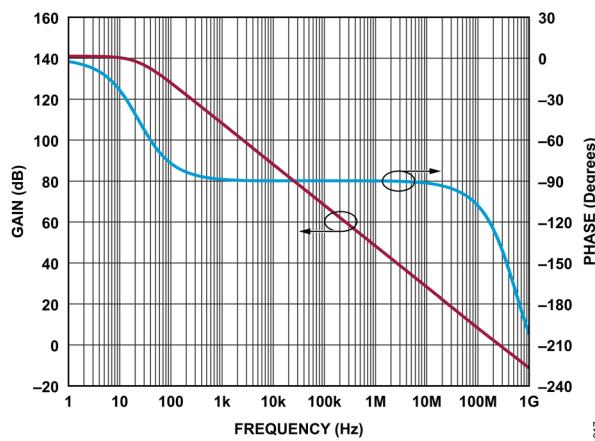

図 17. ADC ドライバのオープンループ・ゲインおよび位相と周波数の関係

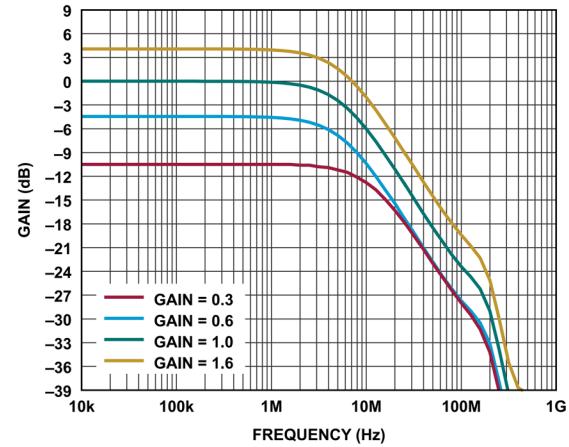

図 20. ADC ドライバのクローズドループ・ゲインと周波数の関係

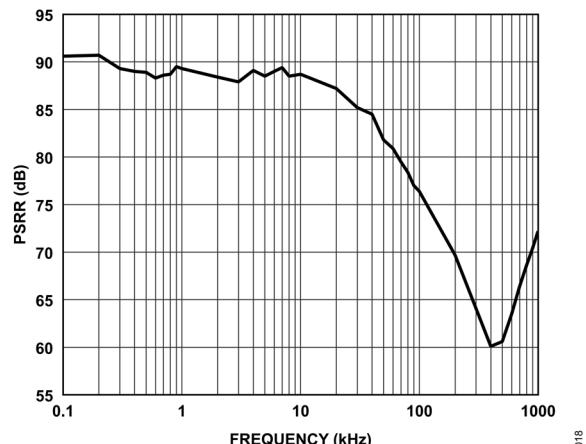

図 18. PSRR と周波数の関係

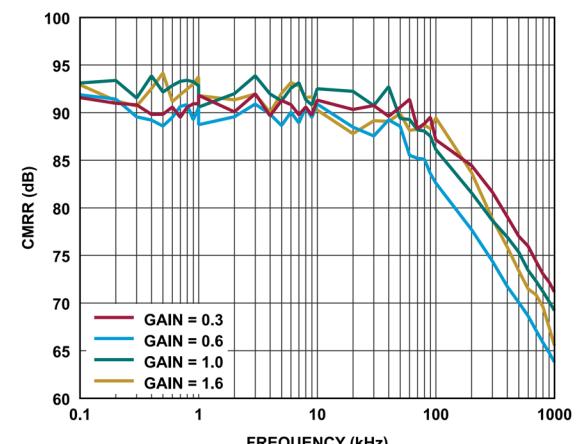

図 21. CMRR と周波数の関係

## 代表的な性能特性

図 22. チャンネル間の位相マッチングと周波数の関係

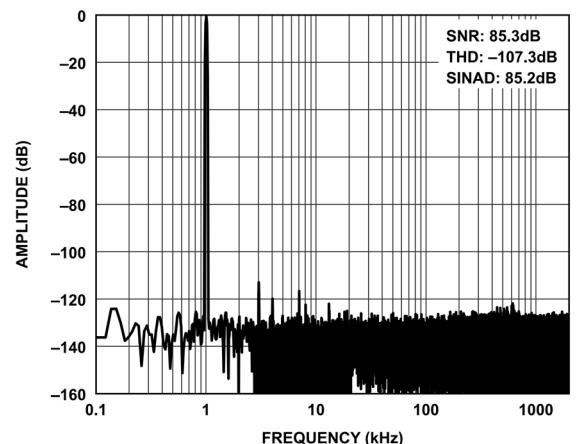

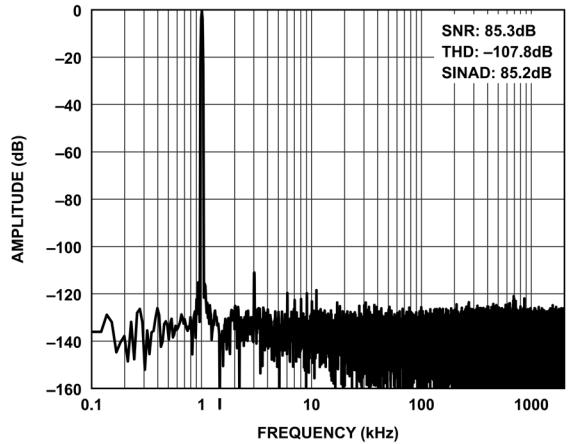

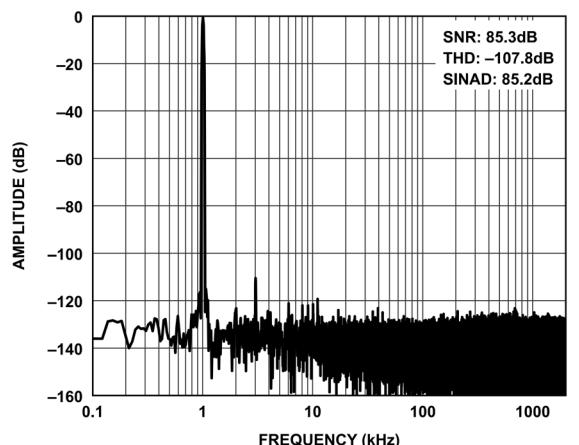

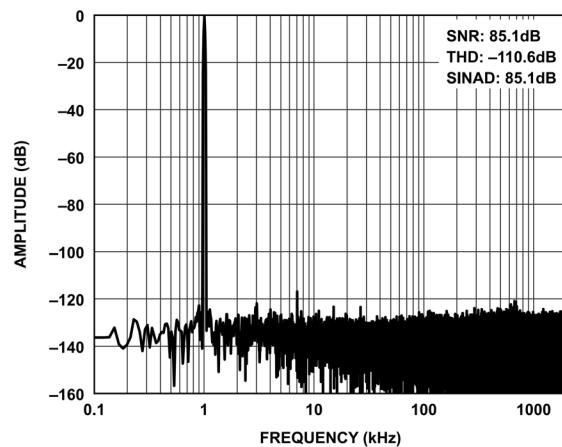

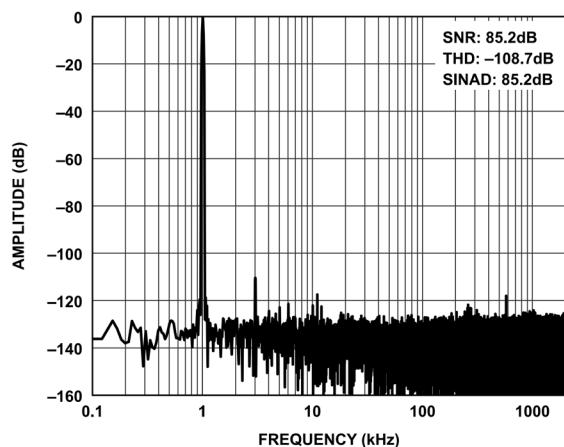

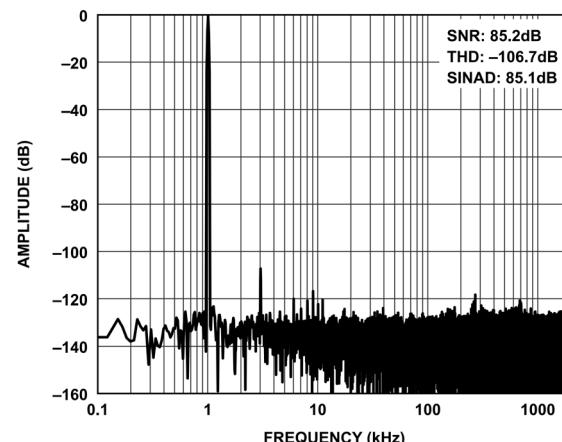

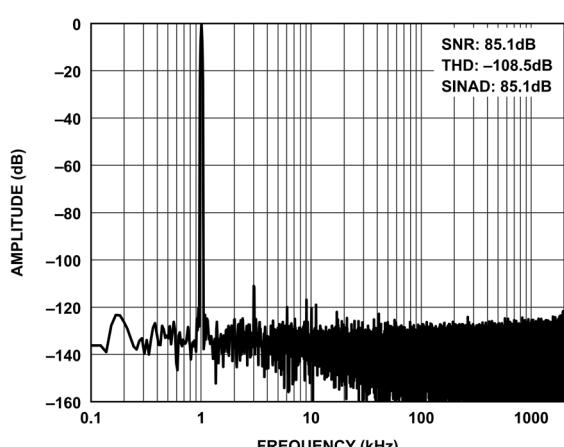

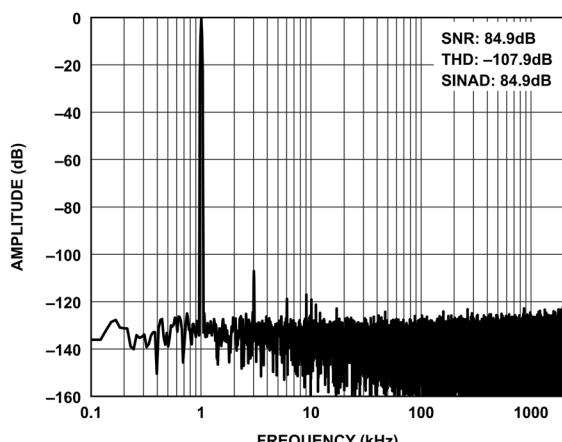

図 25. チャンネル間の位相マッチングと温度の関係、 $f_{IN} = 20\text{kHz}$ 図 23. 1kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 0.3、差動入力、フルパワー動作モード図 26. 1kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 0.3、シングルエンド入力、フルパワー動作モード図 24. 1kHz、-0.5dBFS 入力トーン FFT、

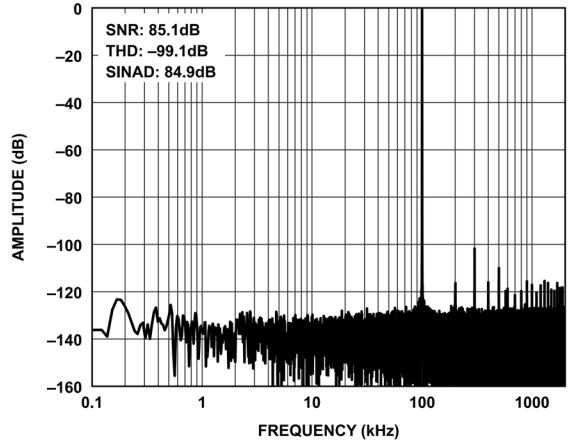

ゲイン = 0.3、差動入力、ローパワー動作モード図 27. 100kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 0.3、差動入力、通常消費電力モード

## 代表的な性能特性

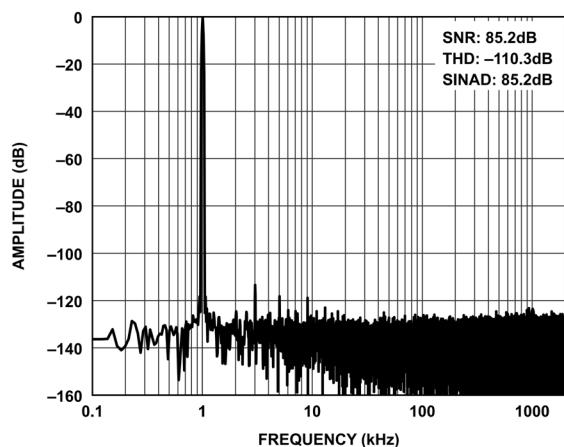

図 28. 1kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 0.6、差動入力、通常消費電力モード

028

図 31. 1kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 0.6、シングルエンド入力、ローパワー動作モード

031

図 29. 1kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 1.0、差動入力、通常消費電力モード

029

図 32. 1kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 1.0、シングルエンド入力、通常消費電力モード

032

図 30. 1kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 1.6、差動入力、通常消費電力モード

030

図 33. 1kHz、-0.5dBFS 入力トーン FFT、

ゲイン = 1.6、シングルエンド入力、低消費電力モード

033

## 代表的な性能特性

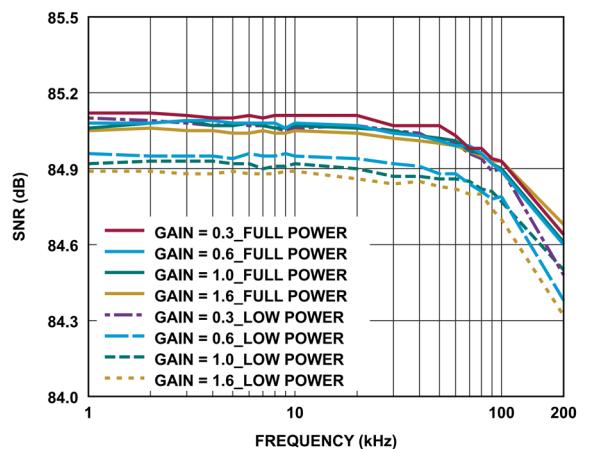

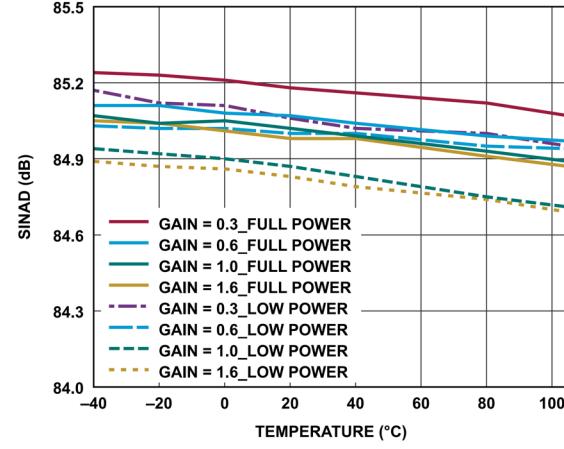

図 34. S/N 比と周波数の関係

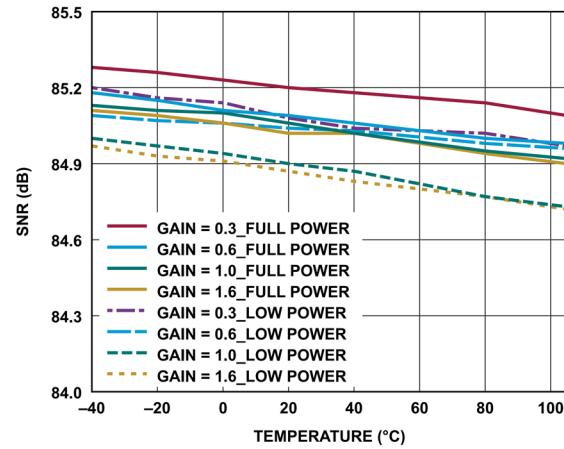

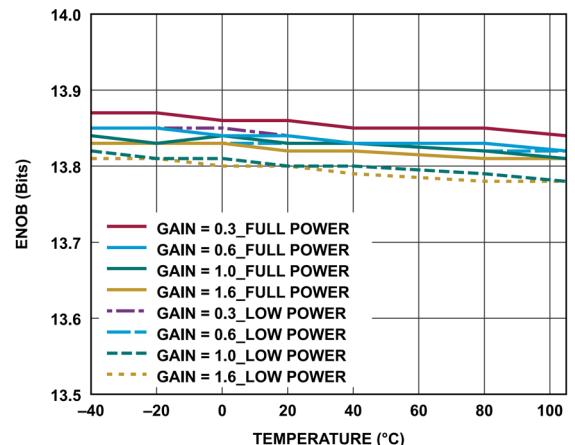

図 37. S/N 比と温度の関係、 $f_{IN} = 1\text{kHz}$

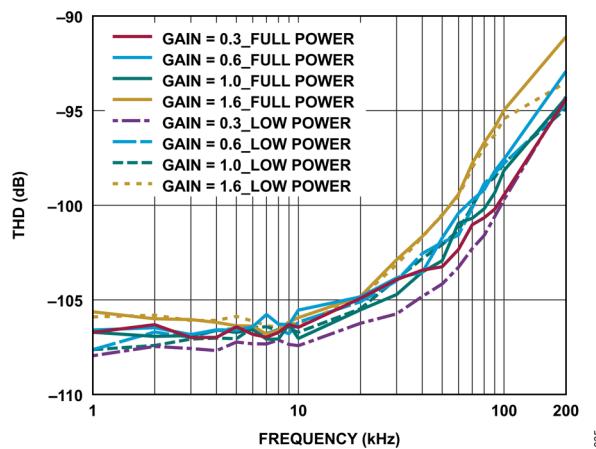

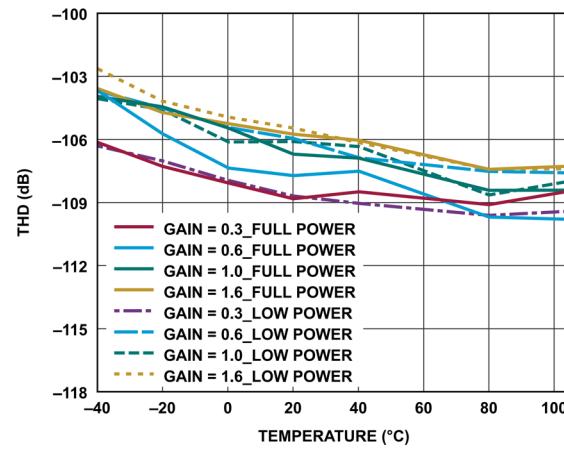

図 35. THD と周波数の関係

図 38. THD と温度の関係、 $f_{IN} = 1\text{kHz}$

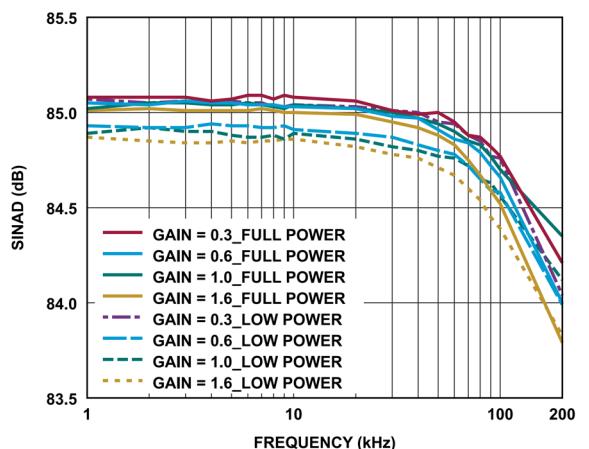

図 36. SINAD と周波数の関係

図 39. SINAD と温度の関係、 $f_{IN} = 1\text{kHz}$

## 代表的な性能特性

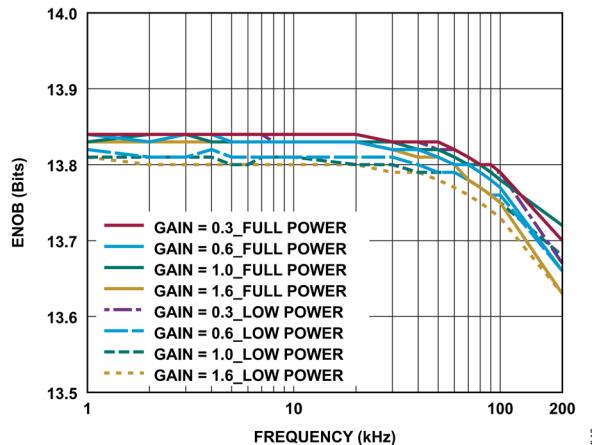

図 40. ENOB と周波数の関係

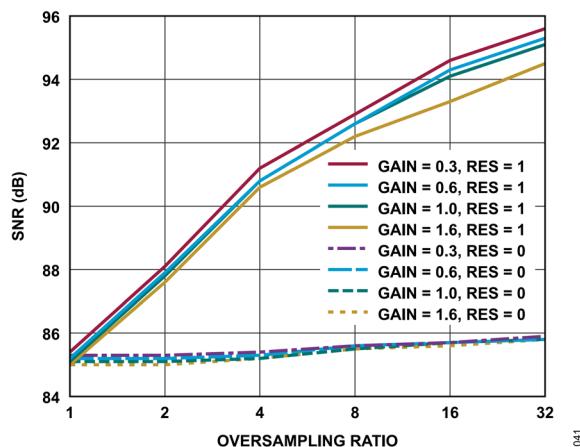

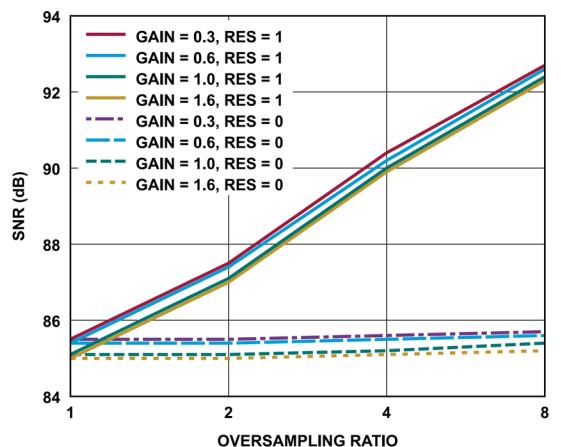

図 43. ENOB と温度の関係、 $f_{IN} = 1\text{kHz}$ 図 41. S/N 比と相加平均オーバーサンプリングの関係、 $f_{IN} = 1\text{kHz}$ 図 44. S/N 比と移動平均オーバーサンプリングの関係、 $f_{IN} = 1\text{kHz}$

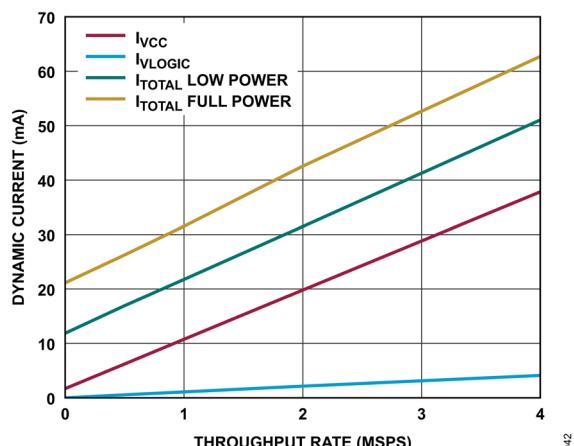

図 42. 動的電流とスループット・レートの関係

図 45. 出力オーバードライブ回復、ゲイン = 0.6

## 用語の定義

### 差動電圧

差動電圧は、2つのノードの電圧の差です。例えば、差動入力電圧（あるいは入力差動モード電圧）は次のように定義されます。

$$V_{IN,dm} = V_{AINA+} - V_{AINA-} \quad (1)$$

ここで、 $V_{AINA+}$  と  $V_{AINA-}$  は AINA+ 端子と AINA- 端子の共通リファレンスを基準とする電圧です。

### コモンモード電圧 (CMV)

コモンモード電圧は、2つのノードの電圧の平均です。入力コモンモード電圧は、次のように定義されます。

$$V_{IN,cm} = (V_{AINA+} + V_{AINA-})/2 \quad (2)$$

### 積分非直線性 (INL)

INL は、負のフルスケールと正のフルスケールを結ぶ直線と個々のコードとの偏差です。最初のコード遷移より  $1\frac{1}{2}$ LSB だけ手前の点を負のフルスケールとして使います。正のフルスケールは、最後のコード遷移を  $1\frac{1}{2}$ LSB 上回ったレベルとして定義されます。偏差は各々のコードの中央から真の直線までの距離として測定されます。

### 微分非直線性 (DNL)

理想的な ADC では、コード遷移は 1LSB ごとに生じます。DNL とは、この理想値からの最大偏差のことです。一般にはノード・ミス・コードが確保される分解能として仕様規定されます。

### オフセット誤差

最初の遷移はアナログ・グラウンドより  $1\frac{1}{2}$ LSB 上のレベルで発生します。オフセット誤差は、理想的なミッドスケール入力電圧 (0V) と、ミッドスケール出力コードを生成する実際の電圧との差です。

### オフセット誤差ドリフト

オフセット誤差ドリフトは、 $1^{\circ}\text{C}$  の温度変化に起因するオフセット誤差変化とフルスケール・コード範囲の比です。オフセット誤差ドリフトは次式のように  $1^{\circ}\text{C}$  あたりの ppm 値 (ppm/ $^{\circ}\text{C}$ ) で表されます。

$$\begin{aligned} \text{Offset Error Drift (ppm}/^{\circ}\text{C}) &= 10^6 \times \\ &(\text{Offset Error}_{T_{MAX}} - \text{Offset Error}_{T_{MIN}}) \quad (3) \\ &/ (T_{MAX} - T_{MIN}) \end{aligned}$$

ここで、

$T_{MAX} = 105^{\circ}\text{C}$

$T_{MIN} = -40^{\circ}\text{C}$

### ゲイン誤差

最初の遷移 (100…000 から 100…001) は負の公称フルスケールより  $1\frac{1}{2}$ LSB 上のレベルで発生する必要があります。最後の遷移 (011…110 から 011…111) は、公称フルスケールより  $1\frac{1}{2}$ LSB 低いアナログ電圧で発生します。ゲイン誤差とは、最後の遷移における実際のレベルと最初の遷移における実際のレベルとの差が、理想値レベルの差とどれだけ異なるかを示すものです。ゲイン誤差は次式のようにパーセンテージで表されます。

$$\begin{aligned} \text{Gain Error} (\%) &= 100 \times ((PFS - NFS)_{\text{ACTUAL\_CODE}} \\ &- (PFS - NFS)_{\text{IDEAL\_CODE}}) \\ &/ ((PFS - NFS)_{\text{IDEAL\_CODE}}) \quad (4) \end{aligned}$$

ここで、

$PFS$  は正のフルスケール

$NFS$  は負のフルスケール

### ゲイン誤差ドリフト

ゲイン誤差ドリフトは、 $1^{\circ}\text{C}$  の温度変化に起因するゲイン誤差変化とフルスケール範囲の比です。ゲイン誤差ドリフトは次式のように  $1^{\circ}\text{C}$  あたりの ppm 値 (ppm/ $^{\circ}\text{C}$ ) で表されます。

$$\begin{aligned} \text{Gain Error Drift (ppm}/^{\circ}\text{C}) &= 10^6 \times \\ &(\text{Gain Error}_{T_{MAX}} - \text{Gain Error}_{T_{MIN}}) / \\ &(T_{MAX} - T_{MIN}) \quad (5) \end{aligned}$$

ここで、

$T_{MAX} = 105^{\circ}\text{C}$

$T_{MIN} = -40^{\circ}\text{C}$

### 温度係数 (TCV<sub>OUT</sub>)

温度係数は、デバイスの周囲温度が変化した場合の出力電圧の変化を、 $25^{\circ}\text{C}$  での出力電圧で正規化して表します。このパラメータはボックス法を使用して規定されています。

$$\begin{aligned} \text{TCV}_{\text{OUT}} &= \\ &\left[ \frac{\max\{V_{\text{OUT}}(T_1, T_2, T_3)\} - \min\{V_{\text{OUT}}(T_1, T_2, T_3)\}}{V_{\text{OUT}}(T_2) \times (T_3 - T_1)} \right] \times 10^6 \quad (6) \end{aligned}$$

ここで、

$\text{TCV}_{\text{OUT}}$  の単位は ppm/ $^{\circ}\text{C}$

$V_{\text{OUT}}(T_x)$  は  $T_x$  における出力電圧

$T_1 = -40^{\circ}\text{C}$

$T_2 = +25^{\circ}\text{C}$

$T_3 = +105^{\circ}\text{C}$

## 用語の定義

### 長期ドリフト ( $\Delta V_{OUT\_LTD}$ )

長期ドリフトは、時間の経過とともに出力電圧のシフト量を表します。これは公称出力値からの差を ppm 単位で表したもので

$$\Delta V_{OUT\_LTD} = \left[ \frac{V_{OUT}(t_1) - V_{OUT}(t_0)}{V_{OUT}(t_0)} \right] \times 10^6 \quad (7)$$

ここで、

$\Delta V_{OUT\_LTD}$  の単位は ppm

$V_{OUT}(t_0)$  は計測開始時の出力電圧

$V_{OUT}(t_1)$  は計測終了時の出力電圧

### 熱ヒステリシス ( $\Delta V_{OUT\_HYS}$ )

熱ヒステリシスは、デバイスが指定された温度サイクルを経た後の出力電圧の変化を表します。これは公称出力値からの差を ppm 単位で表したもので

$$\Delta V_{OUT\_HYS} = \left[ \frac{V_{OUT1\_25^\circ C} - V_{OUT2\_25^\circ C}}{V_{OUT1\_25^\circ C}} \right] \times 10^6 \quad (8)$$

ここで、

$\Delta V_{OUT\_HYS}$  の単位は ppm

$V_{OUT1\_25^\circ C}$  は  $25^\circ C$  での出力電圧

$V_{OUT2\_25^\circ C}$  は、温度サイクルを経た後の出力電圧

### S/N 比 (SNR)

S/N 比は、ナイキスト周波数を下回るすべてのスペクトル成分（高調波と DC を除く）の実効値総和に対する実際の入力信号の実効値の比です。S/N 比の値はデシベル単位で表されます。

### 全高調波歪み (THD)

THD は、フルスケール入力信号の実効値に対する最初の 5 次高調波成分の実効値総和の比率で、単位はデシベルです。

### 信号ノイズ + 歪み (SINAD) 比

SINAD は、ナイキスト周波数を下回るすべてのスペクトル成分の実効値総和（高調波成分は含むが、直流成分は除く）に対する実際の入力信号の実効値の比です。SINAD の値はデシベル単位で表されます。

### 有効ビット数 (ENOB)

ENOB は、サイン波入力による分解能の測定値です。ENOB と SINAD の関係は次式で表されます：

$$ENOB = \frac{SINAD_{dB} - 1.76}{6.02} \quad (9)$$

ここで、ENOB の単位はビットです。

### スプリアスフリー・ダイナミック・レンジ (SFDR)

SFDR は、入力信号の実効値振幅とピーク・スプリアス信号との差で、単位はデシベル (dB) です。

### 同相モード除去比 (CMRR)

CMRR は、入力にコモンモード電圧として印加された周波数 f、振幅 100mV p-p の正弦波の電力と、μModule の出力に現れた周波数 f の電力との比です。

$$CMRR(dB) = 10\log(P_{\mu Module\_IN}/P_{\mu Module\_OUT}) \quad (10)$$

ここで、

$P_{\mu Module\_IN}$  は入力に印加された周波数 f のコモンモード電力

$P_{\mu Module\_OUT}$  は、μModule の出力に現れた周波数 f の電力

### 電源電圧変動除去比 (PSRR)

PSRR は、VS+、REFIN、IN\_LDO 電源電圧として印加された 5V を中心とする周波数 f、振幅 500mV p-p の正弦波の電力と、μModule 出力の周波数 f の電力との比です。

$$PSRR(dB) = 10\log(P_{\mu Module\_IN}/P_{\mu Module\_OUT}) \quad (11)$$

ここで、

$P_{\mu Module\_IN}$  は VS+、REFIN、IN\_LDO の各ピンでの周波数 f の電力

$P_{\mu Module\_OUT}$  は、μModule の出力に現れた周波数 f の電力

### アーチャ・ジッタ

アーチャ・ジッタは、アクイジション性能の尺度で、入力の立ち上がりエッジから入力信号が変換のために保持されるまでの時間です。

### アーチャ・ジッタ

アーチャ・ジッタはアーチャ・ジッタの変動です。

## 動作原理

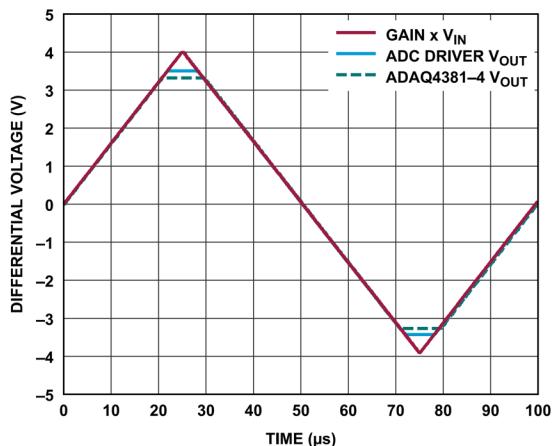

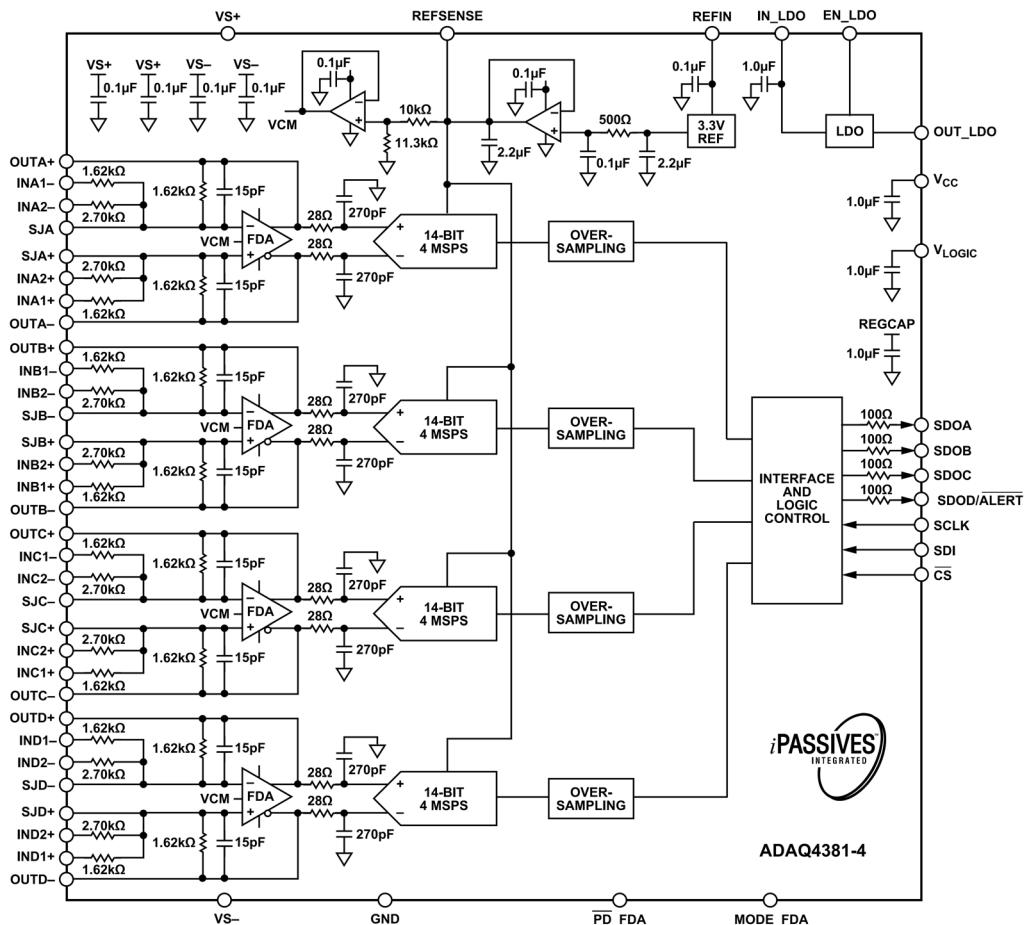

図 46. ADAQ4381-4 μModule の簡略ブロック図

## 回路説明

ADAQ4381-4 μModule SIP は、同時サンプリング SAR アーキテクチャを採用した高速、高精度のクワッド DAQ シグナル・チェーンです。図 46 に示すように、ADAQ4381-4 μModule DAQ システムは、クワッド 14 ビット SAR ADC、広帯域幅の完全差動 ADC ドライバ、高精度低ノイズ 3.3V リファレンス、低ノイズの安定したリファレンス・バッファ、3.4V LDO と共に、性能を最適化して 0.3、0.6、1.0、1.6 のゲインをピンによって選択できるようにするために必要となる重要な高精度受動部品を含めて構成されています。回路内のすべての能動部品および  $\pm 0.005\%$  に整合された iPassives® 薄膜抵抗はアナログ・デバイセズによる設計で、仕様に規定された高い精度を実現し、温度に依存する誤差源を最小限に抑えるために、工場出荷時にキャリブレーションされています。

ADAQ4381-4 は、4MSPS という高スループット・レートで全チャンネルを同時に変換します。ADAQ4381-4 はオーバーサンプリング・ブロックを内蔵することで、更に低帯域幅でのダイナミック・レンジを向上させ、ノイズを低減しています。詳細については、[ADC の動作モード](#)のセクションを参照してください。ADC の電圧ピンに必要となるデカップリング・コンデンサは、すべて BGA パッケージ内に組み込まれています。外付けのコンデンサは必要ありません。

## 動作原理

### 伝達関数

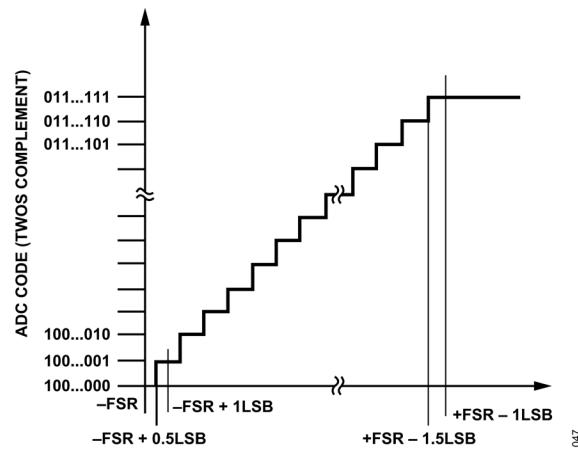

ADAQ4381-4 は 3.3V の内部リファレンスを使用します。ADAQ4381-4 は、アナログ入力 (IN<sub>x+</sub>と IN<sub>x-</sub>) 間の差動電圧をデジタル出力に変換します。

変換結果は MSB ファーストで、2 の補数で表されます。LSB の大きさは  $(2 \times V_{REF})/2^N$  (N は ADC の分解能) です。ADC の分解能は、選択したデバイスの分解能と分解能増強モードが有効かどうかによって決まります。表 8 に、分解能に対応する LSB の大きさの電圧値を示します。

ADAQ4381-4 の理想伝達特性を図 47 に示します。

表 8. LSB の大きさ

| Resolution | 3.3 V Reference | Unit |

|------------|-----------------|------|

| 14-bit     | 402.8           | µV   |

| 16-bit     | 100.7           | µV   |

図 47. ADC の理想的な伝達関数

(フルスケール・レンジ (FSR))

## アプリケーション情報

## 代表的な接続図

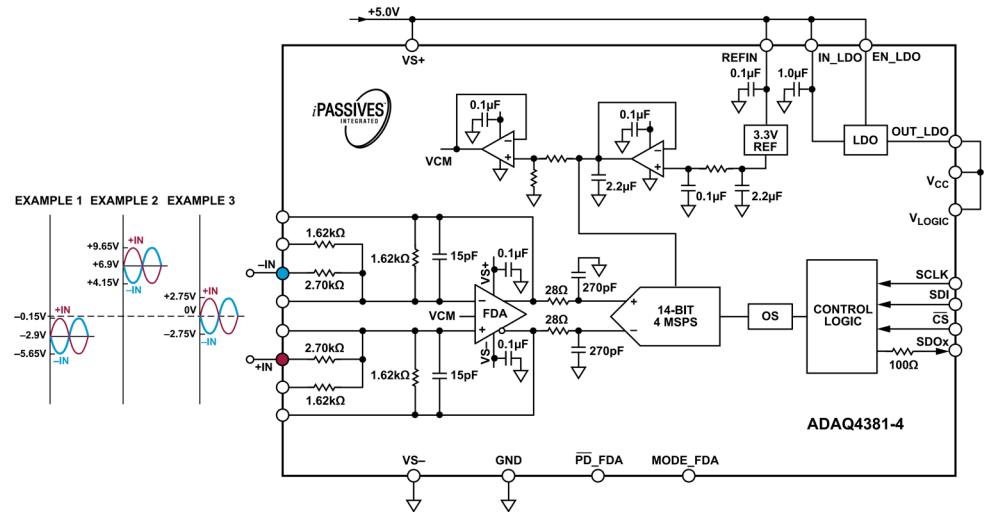

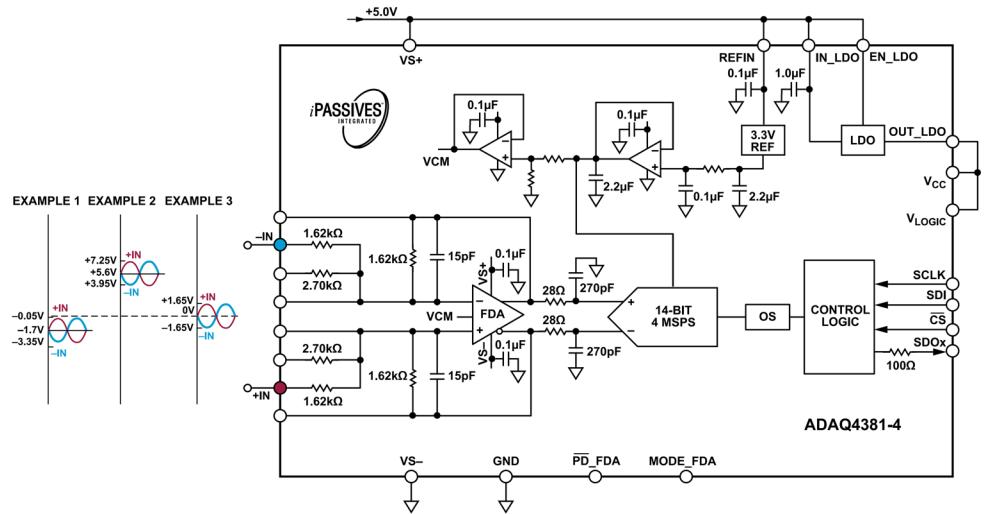

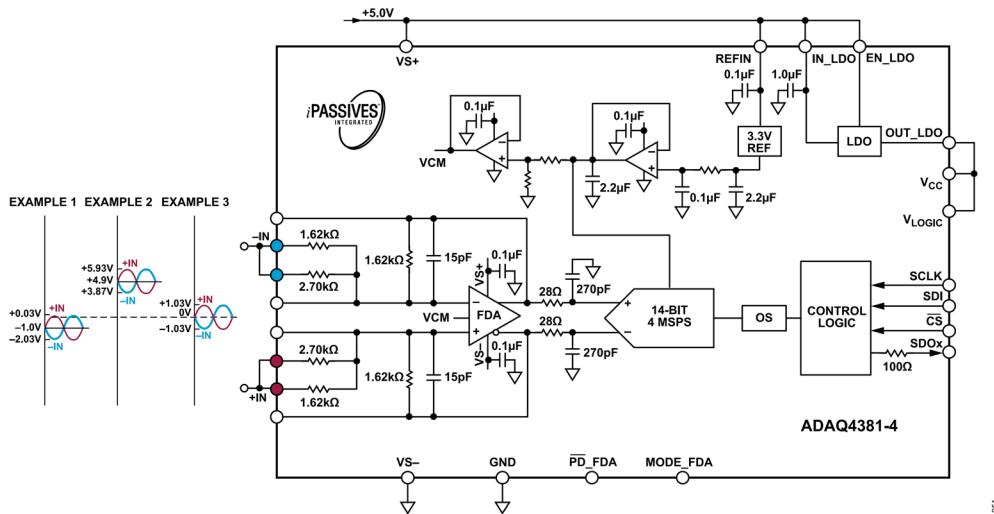

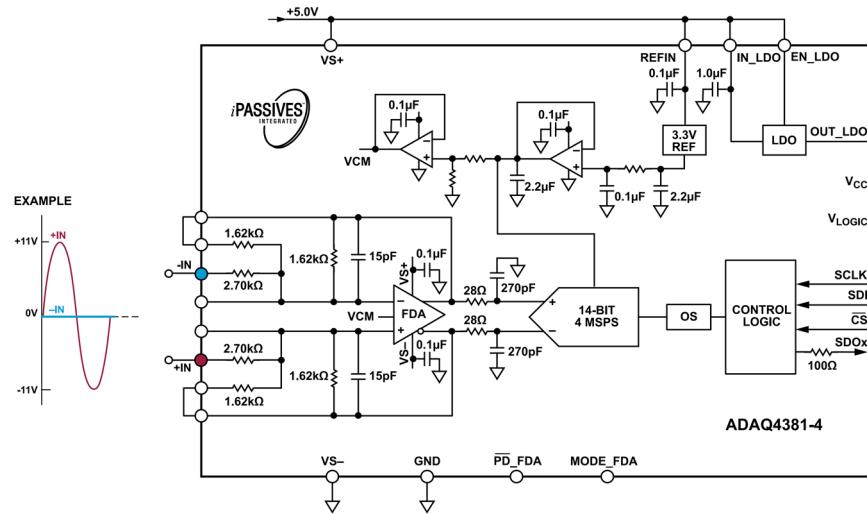

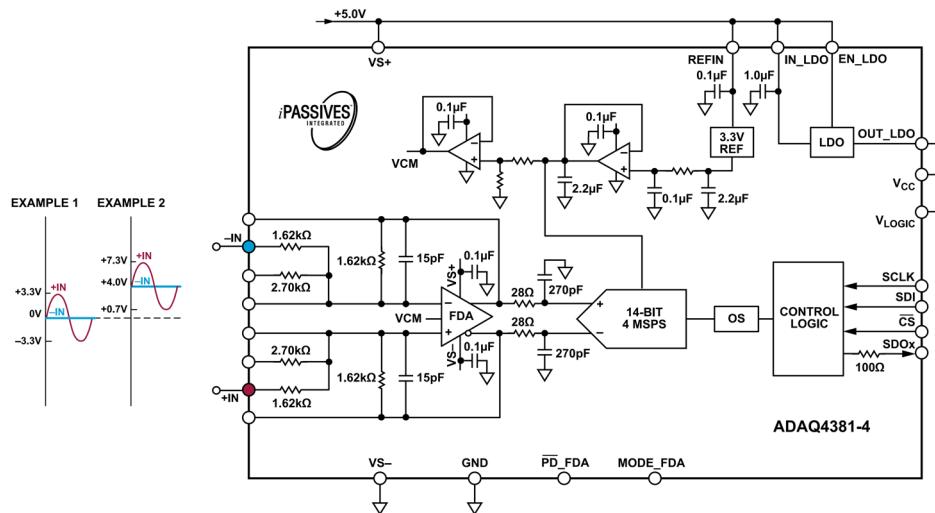

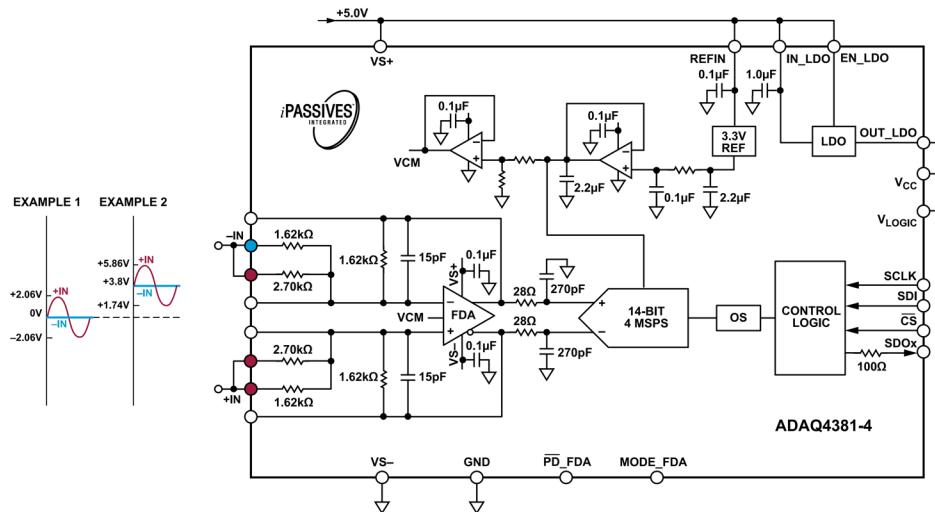

図 48 から図 55 までは、差動またはシングルエンドの入力信号と 4 つのゲイン設定との組み合わせを様々なコモンモード電圧で使用した場合の、ADAQ4381-4 の各チャンネルの代表的な接続図を示しています。

表 9. ゲイン設定と入力範囲

| Gain | Input Range         | Input Signal on Pins       | Test Conditions                                                                                    |

|------|---------------------|----------------------------|----------------------------------------------------------------------------------------------------|

| 0.3  | $\pm 11\text{ V}$   | IN2+, IN2-                 | Connect IN1+ to OUT-, and IN1- to OUT+. See Figure 48 and Figure 52.                               |

| 0.6  | $\pm 5.5\text{ V}$  | IN2+, IN2-                 | Connect IN1+, IN1-. Leave OUT+ and OUT- floating. See Figure 49 and Figure 53.                     |

| 1.0  | $\pm 3.3\text{ V}$  | IN1+, IN1-                 | Leave IN2+, IN2-. OUT+ and OUT- floating. See Figure 50 and Figure 54.                             |

| 1.6  | $\pm 2.06\text{ V}$ | IN1+ or IN2+, IN1- or IN2- | Connect IN1+ to IN2+, and IN1- to IN2-. Leave OUT+ and OUT- floating. See Figure 51 and Figure 55. |

ADAQ4381-4 の 4 つの差動チャンネルは幅広い入力電圧範囲に対応し、幅広いコモンモード範囲を備えているため、様々な信号の変換が可能です。差動電圧とコモンモード電圧の範囲は、チャンネルごとのゲイン設定に大きく依存します。

図 48. 完全差動入力構成、ゲイン = 0.3、 $\pm 11\text{ V}$  入力、 $V_S = 5\text{ V}$ 図 49. 完全差動入力構成、ゲイン = 0.6、 $\pm 5.5\text{ V}$  入力、 $V_S = 5\text{ V}$

## アプリケーション情報

図 50. 完全差動入力構成、ゲイン = 1.0、 $\pm 3.3V$  入力、 $V_S = 5V$ 図 51. 完全差動入力構成、ゲイン = 1.6、 $\pm 2.06V$  入力、 $V_S = 5V$

## アプリケーション情報

図 52. シングルエンド入力構成、ゲイン = 0.3、±11V 入力、VS = 5V

図 53. シングルエンド入力構成、ゲイン = 0.6、±5.5V 入力、VS = 5V

## アプリケーション情報

図 54. シングルエンド入力構成、ゲイン = 1.0、 $\pm 3.3V$  入力、 $V_S = 5V$ 図 55. シングルエンド入力構成、ゲイン = 1.6、 $\pm 2.06V$  入力、 $V_S = 5V$

## アプリケーション情報

## ADC ドライバ

ADAQ4381-4 μModule には、ADC ドライバとして 4 系統の低ノイズ、完全差動アンプと、それぞれのゲイン・ネットワークの受動部品が内蔵されています。これらの ADC ドライバには、フルパワー動作モードとローパワー動作モードの 2 つの電力モードがあります。フルパワー動作モードでは、ADAQ4381-4 は最適な性能で動作しますが、わずかに消費電力が高くなります。ローパワー動作モードでは、ADAQ4381-4 の電力消費が 20% 低減します。

## 入力コモンモード電圧

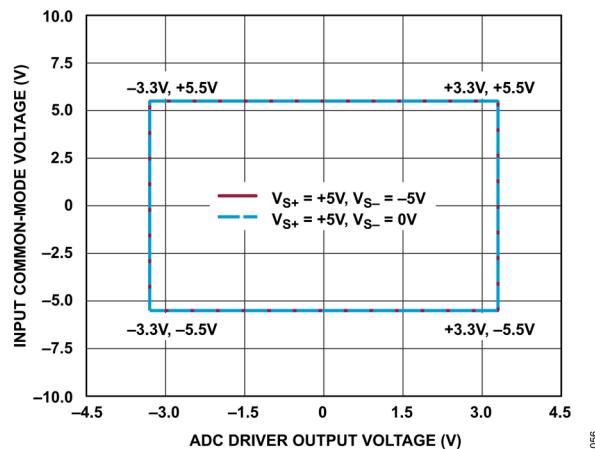

ADAQ4381-4 の入力コモンモード電圧範囲 (ICMVR) は ADC ドライバのゲインに大きく依存します。ゲインの設定とオプションを、表 9 に詳しく示しています。各ゲインでの ICMVR は異なり、フロントエンドでの幅広い入力電圧範囲に対応します。適切な動作を確保するためには、差動入力電圧の絶対値とは別に、入力コモンモード電圧についても考慮が必要です。図 56 と図 57 は、それぞれ  $G = 0.3$ 、 $G = 1$  での ADAQ4381-4 の ICMVR を示しています。

図 56. 入力コモンモード電圧と ADC ドライバ出力電圧の関係、

ゲイン = 0.3、 $\pm 11$ V の差動入力

図 57. 入力コモンモード電圧と ADC ドライバ出力電圧の関係、

ゲイン = 1.0、 $\pm 3.3$ V の差動入力

## アプリケーション回路の入力インピーダンスの計算

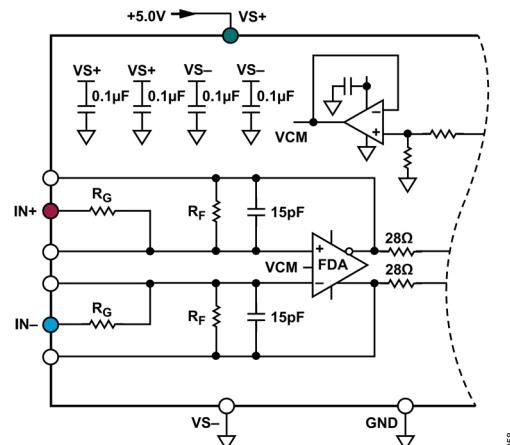

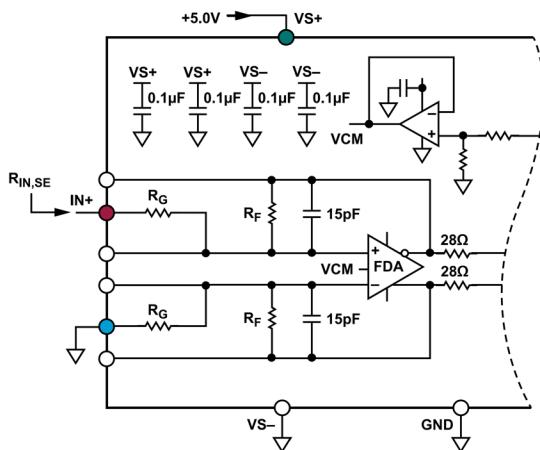

有効入力インピーダンスは、信号源がシングルエンドか差動かによって異なります。図 58 に示すような平衡差動入力信号の場合、入力間 (IN+ と IN-) の入力インピーダンス ( $R_{IN,dm}$ ) は、次式で表されます。

$$R_{IN,dm} = 2 \times R_G \quad (12)$$

図 58. ADAQ4381-4 の完全差動入力構成

図 59 に示すようなシングルエンド入力信号の場合、入力インピーダンスは次式のようになります。

$$R_{IN,SE} = \frac{R_G}{1 - \frac{R_F}{2(R_G + R_F)}} \quad (13)$$

図 59. ADAQ4381-4 のシングルエンド入力構成

回路の入力インピーダンスは、インバータとして接続された一般的なオペアンプよりも実効的に高くなります。これは、差動出力電圧の一部が入力にコモンモード信号として現れ、入力抵抗  $R_G$  両端の電圧をある程度ブーストするからです。

## アプリケーション情報

## シングルエンド入力の終端

入力を駆動する回路の出力インピーダンスが非常に低い場合は、ADAQ4381-4 の入力 IN+ と IN- の追加的な終端処理は必要ありません。しかし、駆動側回路の抵抗が無視できないほど高い場合には、ADAQ4381-4 の入力にバランス回路を追加することをアノログ・デバイセズでは推奨しています。シングルエンド入力動作の場合に入力を適切に終端する手法については、アプリケーション・ノート 1026：高速差動 ADC ドライバの設計についての考察を参照してください。

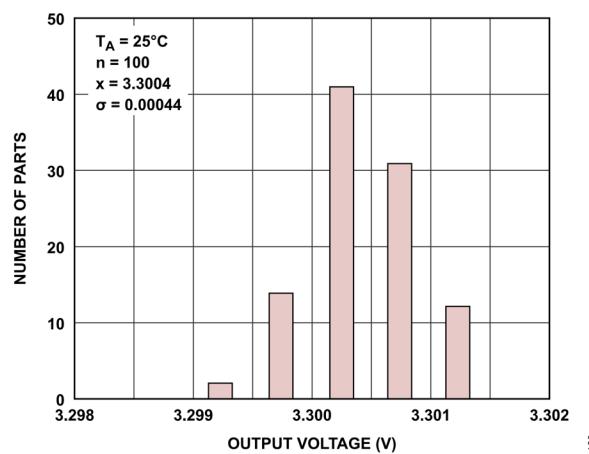

## 内部リファレンス

ADAQ4381-4 μModule は、高精度で低ノイズ、低ドリフト（代表値 3ppm/°C）の精密電圧リファレンスを内蔵しています。最適な性能を得るために、REFIN を安定した 5V 電源に接続します。安定動作のためのバイパス・コンデンサと負荷コンデンサは μModule パッケージに内蔵されているため、外付けのコンデンサは不要です。このリファレンスの 3.3V 出力は ADC のリファレンスと ADC ドライバの VCM として使用されます。

REFSENSE ピンは内部リファレンス回路の一部です。ADC リファレンス入力とリファレンス・バッファの出力である点に直接接続されています。システムの別の部分でリファレンスもしくは電圧源として REFSENSE ピンを使用することは推奨されておらず、ADAQ4381-4 の性能の劣化につながる場合があります。このピンは正確なゲイン補正のためにのみ使用し、それ以外の目的で接続しないようにしてください。

周囲温度における内部リファレンスの初期電圧精度を図 60 に示します。100 ユニットのサンプルでの REFSENSE 出力電圧は 3.3V を中心とし、平均値は 3.3004V になっています。

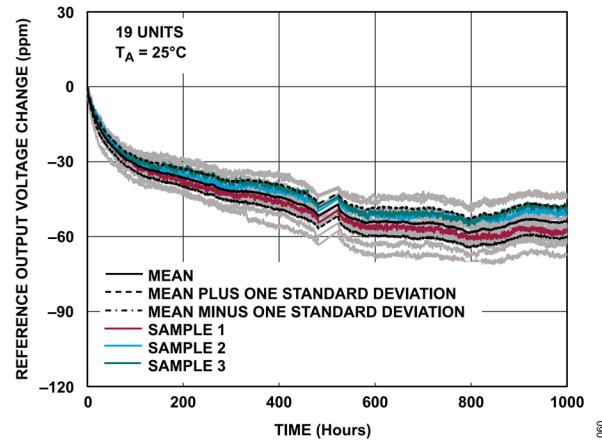

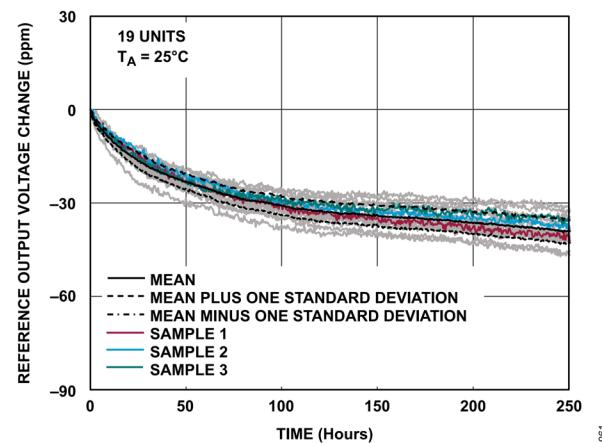

## 長期ドリフト

ADAQ4381-4 の長期ドリフトを調べる目的で、1000 時間に超える時間にわたり複数のユニットで出力電圧の変化を計測しました。実際的なシステム・アプリケーションを再現するため、19 個のデバイスを標準的なリフロー・プロファイルで FR4 PCB にハンダ付けして、ドリフト・データを取得しました。安定度が非常に高いオイル槽に基板を浸して、温度を定期的に 25°C に制御

し、出力を定期的にスキャンして高精度計測システムで測定しました。

図 61 は ADAQ4381-4 の内部 3.3V リファレンスの長期ドリフトを示しており、800 時間後の出力電圧のドリフトは 54ppm です。図 62 に示すように、0 時間から 250 時間の間には出力電圧に大きなシフトが確認されます。この平均ドリフトは 39ppm で、1000 時間に観察される全ドリフトの 72%を初期ドリフトが占めています。

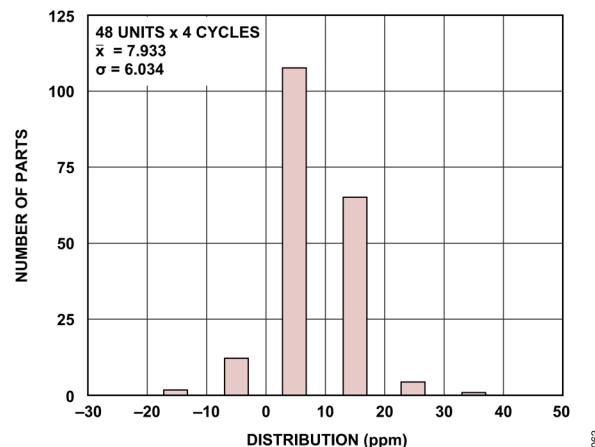

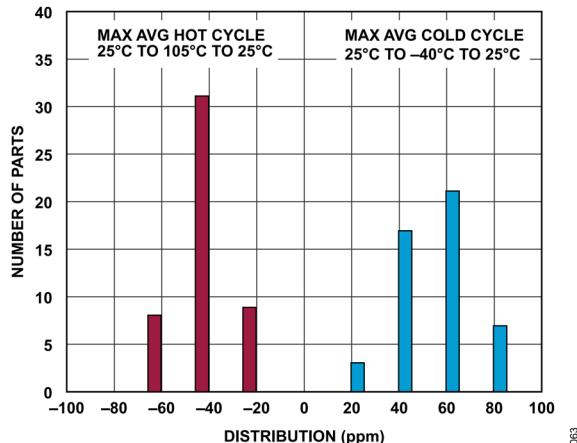

## 熱ヒステリシス

長期ドリフトのセクションで説明した経時的な安定性に加え、熱ヒステリシス、つまり温度サイクルに対する安定性を知ることも有用です。熱ヒステリシスは、周囲温度が変化した後に室温に戻った場合に、信号振幅が当初の値までどの程度正確に戻るかを示すものです。

## アプリケーション情報

図 63. フル・サイクル 4 回後のリファレンス出力の電圧ヒステリシス

図 63 は、室温から $-40^{\circ}\text{C}$  と $+105^{\circ}\text{C}$  を経て室温に戻るまでのフル温度サイクルを 4 回繰り返した場合のヒステリシスを示すものです。フル・サイクル 4 回後の出力のヒステリシスは代表値で 8ppm です。図 64 のヒストグラムは、デバイスを半サイクルだけ繰り返した場合の方がヒステリシスが大きいことを示しています。室温から $105^{\circ}\text{C}$  を経て室温に戻るサイクルでは代表値 $-50\text{ppm}$ 、室温から $-40^{\circ}\text{C}$  を経て室温に戻るサイクルでは代表値 43ppm です。

図 64. 半サイクルでのリファレンス出力の電圧ヒステリシス

## 内部 LDO

ADAQ4381-4  $\mu$ Module は LDO レギュレータを内蔵しています。これを使用するためには、IN\_LDO と EN\_LDO を 5V に接続します。入力バイパス・コンデンサは  $\mu$ Module 内に内蔵されており、外付けのバイパス・コンデンサは不要です。LDO の出力は、ADC の VCC と VLOGIC の電源レールへの給電を目的としています。通常動作時には、VCC と VLOGIC を直接 OUT\_LDO に接続します。外付けのコンデンサは不要です。アプリケーションで VCC と VLOGIC に外付けの電源が必要であれば、EN\_LDO を GND に接続して内部 LDO をディスエーブルします。

## 電源とデカップリング

ADAQ4381-4 には 6 つの独立した電源 (VS+、VS-、REFIN、IN\_LDO、VCC、VLOGIC) があり、それぞれアナログ回路とデジタル・インターフェースに電力を供給します。各電源ピンの詳細な説明については、表 7 を参照してください。ADAQ4381-4 は、5V の単電源動作で最適な性能が確保されています。デカップリング・コンデンサが ADAQ4381-4 の内部回路に含まれているため、これらの電源ピンのデカップリングは必要でない場合もあります。更に、ADAQ4381-4 の内部リファレンスとリファレンス・バッファも、グラウンドとの間でデカップリングされています。REFSENSE ピンへの外付けデカップリング・コンデンサの追加は必要ありません。

ADAQ4381-4 の推奨電源関連製品を図 65 に示します。詳細については、製品ウェブサイトに掲載されている ADAQ4381-4 LTPowerPlanner を参照してください。

図 65. ADAQ4381-4 の電源に関する推奨

## パワーアップ

絶対最大定格のセクションに記載されている最大電圧の関係を遵守してください。ADAQ4381-4 は電源シーケンスによって容易に損傷することはありません。図 65 は、VCC と VLOGIC のパワーアップに内部 LDO を使用する推奨の電源構成を示しています。ADAQ4381-4 は電源シーケンシングに対して堅牢ですが、アプリケーションで外部の VCC と VLOGIC が必要な場合には、VCC と VLOGIC の電源を先にオンにし、続いて VS+ と VS-、最後に REFIN の電源をオンにするのが最も好ましいシーケンスです。VCC と VLOGIC はどちらを先にパワーアップしても構いません。アナログ信号とデジタル信号は、リファレンス供給後に印加する必要があります。

ADAQ4381-4 では、VCC と VLOGIC に印加してから ADC の変換結果が安定するまでに  $t_{\text{POWER-UP}}$  の時間が必要です。パワーアップ時の推奨シグナル・コンディションについては、図 4 を参照してください。パワーアップ時にはピンをハイにプルアップし、パワーアップ後にソフトウェア・リセットすることを推奨します。この時間中の変換結果は、データシートの仕様を満たすことが保証されないため、無視してください。

## ADC の動作モード

ADAQ4381-4 には、デバイスの動作モードを制御できる設定レジスタがいくつか内蔵されています。

### オーバーサンプリング

オーバーサンプリングは、ADC の結果の精度を向上させるために広く使用されている手法です。アナログ入力サンプルを複数取得して平均化することで、ADC の量子化ノイズや熱ノイズ (kTC) に由来するノイズ成分を除去します。ADAQ4381-4には、オンチップのオーバーサンプリング機能があり、相加平均と移動平均の 2 つのオーバーサンプリング・モードをユーザ設定可能です。

このオーバーサンプリング機能は、[Configuration1 レジスタ](#)の OS\_MODE ビットと OSR ビットをプログラムして設定します。

### 相加平均オーバーサンプリング

相加平均オーバーサンプリング・モードは、出力データ・レートが低くなることが許容され、かつ、S/N 比やダイナミック・レンジが高いことが必要なアプリケーションで使用できます。相加平均には、多数のサンプリングを行い、それらを加算し、その結果をサンプリング数で除するというプロセスが含まれます。このプロセスの結果がデバイスから出力されます。プロセスが完了すると、サンプリングしたデータはクリアされます。

相加平均オーバーサンプリング・モードは、OS\_MODE ビットをロジック 0 にし、OSR ビットを有効な非ゼロ値とすることで設定されます。デジタル・フィルタのオーバーサンプリング比は、オーバーサンプリング・ビットである OSR を使用して制御します。

各種オーバーサンプリング・レートを選択するためのオーバーサンプリング・ビットのデコードを表 10 に示します。出力結果は、16 ビットの分解能で示されます。これ以上の分解能が必要な場合は、[Configuration1 レジスタ](#)の分解能増強ビット (RES) を設定することで実現できます。詳細については、[分解能増強](#)のセクションを参照してください。