# 14 ビット高速 DAC を内蔵した 110V 高電圧、1A 大電流の任意波形発生器

## 特長

- 広い高電圧供給範囲:  $\pm 12V \sim \pm 55V$

- 高い出力能力

- 出力電圧範囲: 最大  $\pm 40V$

- 高出力の電流駆動: 1A 連続

- 高スルーレート: 1000pF の負荷に対して  $1800V/\mu s$  以上

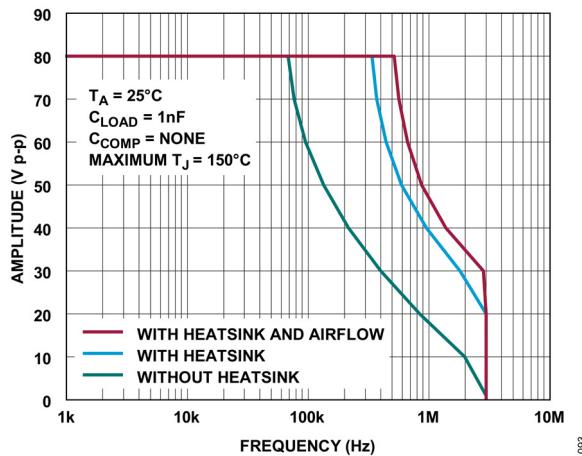

- 大信号の帯域幅: 1MHz

- 豊富なプログラミングと診断機能

- 14 ビット分解能の任意波形生成 (AWG) モード

- 16 レベルのアナログ・パターン生成 (APG) モード

- デジタル的にプログラマブルな電流、電圧、サーマル・フォルトのモニタリングと保護

- シャットダウン・モードを備えたプログラマブルな供給電流

- デザインイン・フレンドリー

- 外部補償とスルーモードにより容量性負荷を制限なく駆動

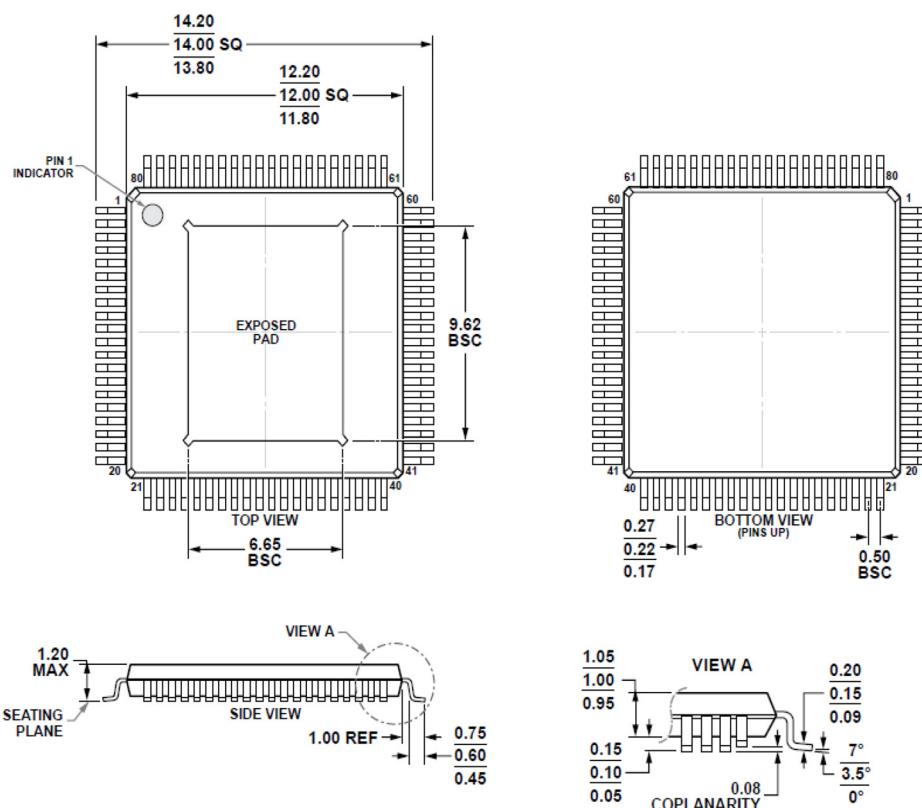

- パッケージ: 80 ピン、12mm × 12mm の TQFP

- 取り付け式ヒートシンク用に EPAD が上向きに配置されたパッケージ

- 動作温度範囲:  $-40^{\circ}C \sim +85^{\circ}C$

## アプリケーション

- 自動試験装置 (ATE)

- ディスプレイ・パネルの形成およびテスト

- ピエゾ素子ドライバ

- プログラマブル電源

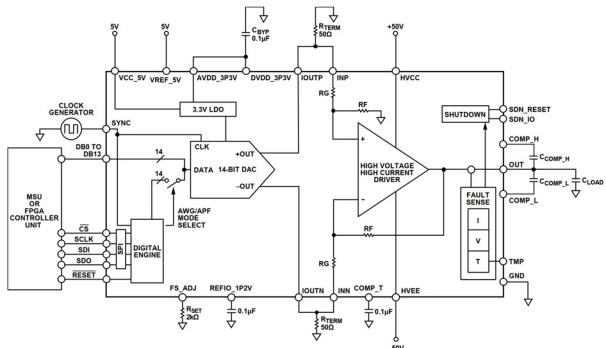

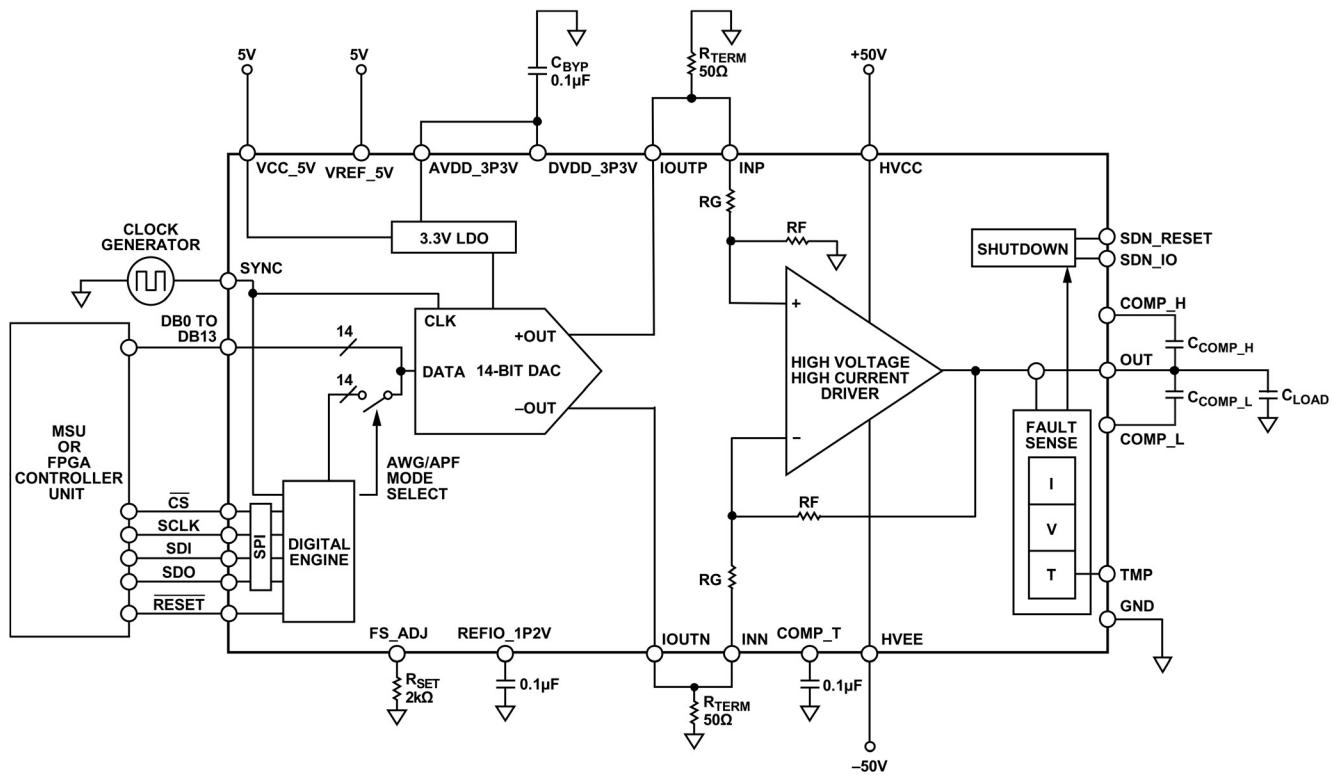

図 1. 簡略化した機能ブロック図

## 概要

AD8460 は、「ビット・イン、パワー・アウト」の高電圧、高出力の高速ドライバで、容量性負荷に対し高電圧（最大  $\pm 40V$ ）で大きな出力電流（最大  $\pm 1A$ ）と高いスルーレート（最大  $\pm 1800V/\mu s$ ）を実現できるよう最適化されています。14 ビット高速 DAC、高電圧、高出力電流 (HV-HI) のアナログ・ドライバとフォルト・モニタリングおよび保護回路を組み合わせた AD8460 は、任意波形生成 (AWG)、プログラマブル電源、高電圧の自動試験装置 (ATE) など、高出力のアプリケーションに最適です。

アナログ・デバイセズが独自に開発した高電圧 BCDMOS プロセス、革新的な高電圧アキテクチャ、熱強化型パッケージが、この高性能ドライバを可能にしています。デジタル・エンジンには、ユーザ設定可能な機能、例えば、デジタル入力のモード、プログラマブルな電源電流、フォルト・モニタリングの他、出力電流、出力電圧、ジャンクション温度に対するプログラマブルな保護設定機能が実装されています。アナログ機能によって機能性が拡張され、例えば、無制限の容量性負荷駆動、プログラマブルなシャットダウン遅延、フルスケール調整が外部補償によって可能になります。AD8460 は最大  $\pm 55V$  の高電圧両電源と 5V の低電圧单電源で動作します。

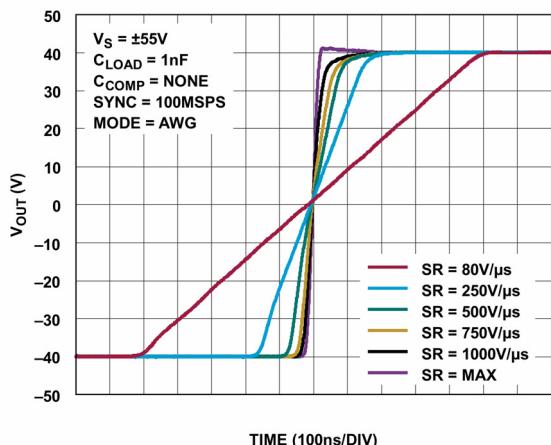

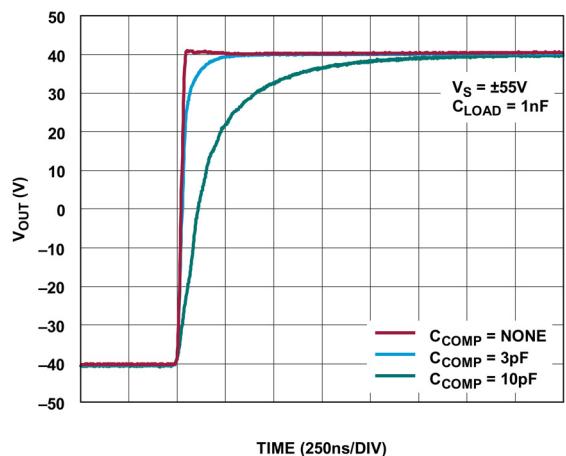

図 2. 大信号パルス応答と外部スルーモードによるエッジ速度の関係

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

Rev. 0

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 機能ブロック図

図 3. 機能ブロック図

## 目次

|                       |    |                           |    |

|-----------------------|----|---------------------------|----|

| 特長                    | 1  | アナログ・パターン生成 (APG)         | 32 |

| アプリケーション              | 1  | 任意波形生成 (AWG)              | 33 |

| 概要                    | 1  | プリディストーションおよび調整可能入力エッジ速度  | 33 |

| 機能ブロック図               | 2  | 出力電流駆動                    | 34 |

| 改訂履歴                  | 4  | フォルト・モニタリングおよび保護          | 34 |

| 仕様                    | 5  | フォルト始動型シャットダウン保護機能        | 36 |

| タイミング図                | 11 | シャットダウン保護設定               | 36 |

| 絶対最大定格                | 12 | 過電流保護のプログラミング             | 36 |

| 熱抵抗                   | 13 | 過電圧保護のプログラミング             | 37 |

| 静電放電 (ESD) 定格         | 13 | 過熱保護のプログラミング              | 38 |

| ピン配置およびピン機能の説明        | 14 | シャットダウン閾値設定のプログラミング       | 38 |

| 代表的な性能曲線の解釈           | 17 | シャットダウン制御 (SDN_IO)        | 39 |

| 代表的な性能特性              | 17 | 遅延シャットダウン                 | 39 |

| 用語の定義                 | 26 | 手動サーマル・シャットダウン            | 40 |

| アラーム                  | 26 | パワーオン・リセット (POR) およびRESET | 41 |

| アナログ・パターン生成 (APG) モード | 26 | スリープ制御およびその他のレジスタ関連機能     | 41 |

| 任意波形生成 (AWG) モード      | 26 | スリープ制御                    | 41 |

| 保護装備                  | 26 | その他の機能                    | 42 |

| 保護解除                  | 26 | スルー・ブースト                  | 42 |

| フォルト                  | 26 | サーマル・モニタリング (TMP)         | 42 |

| 保護システム                | 26 | 出力補償 (COMP_H および COMP_L)  | 42 |

| 予約済み                  | 26 | 温度補償 (COMP_T)             | 43 |

| 安全動作領域 (SOA)          | 26 | プログラマブル静止電流               | 43 |

| シャットダウンおよびスリープ        | 26 | アプリケーション情報                | 45 |

| スルー・ブースト              | 27 | 温度管理                      | 45 |

| スパン                   | 27 | PCB の熱設計                  | 45 |

| 動作原理                  | 28 | 消費電力                      | 45 |

| 概要                    | 28 | 安全動作領域                    | 46 |

| 初期パワーアップ              | 29 | DC SOA                    | 47 |

| 電源とデカップリング            | 29 | 動的 SOA                    | 47 |

| VREF_5V               | 29 | 負荷が 1nF を超える場合の動的ピーク電流の制限 | 48 |

| 電源シーケンス               | 30 | フルスケール調整                  | 48 |

| リファレンス動作              | 30 |                           |    |

| 入力と動作モード              | 31 |                           |    |

---

|                                     |    |

|-------------------------------------|----|

| フルスケールの縮小 .....                     | 49 |

| レイアウト .....                         | 50 |

| 最上位レベルのデジタル・レジスタ割当て .....           | 51 |

| デバイス制御レジスタの概要とマップ .....             | 52 |

| 制御レジスタの詳細 .....                     | 55 |

| HVDAC データ・レジスタ (パターン・メモリ) の概要 ..... | 63 |

| HVDAC データ・レジスタ (パターン・メモリ) の詳細 ..... | 67 |

| 外形寸法 .....                          | 74 |

| オーダー・ガイド .....                      | 74 |

| 評価用ボード .....                        | 74 |

## 改訂履歴

10/2023—Rev. 0

## 仕様

表 1. 電気的特性

(特に指定のない限り、HVCC = +50V、HVEE = -50V、SET\_IQ = 0x00、VCC\_5V = +5V、VREF\_5V = +5V、REFIO\_1P2V = +1.2V、RTERM = 50Ω、FS\_ADJ への RSET = 2kΩ、COMP\_L、COMP\_H = 0pF、CLOAD = 1nF、Tc = 30°C。)

| PARAMETER                           | SYMBOL                       | CONDITIONS/COMMENTS                                                                               | MIN | TYP         | MAX  | UNITS    |

|-------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------|-----|-------------|------|----------|

| DYNAMIC PERFORMANCE                 |                              |                                                                                                   |     |             |      |          |

| Small Signal Bandwidth              | $f_{3\text{db}}$             | $V_{\text{OUT}} = 0.1 \text{ V p-p}, T_J = 85^\circ\text{C}$ .<br>See <a href="#">Figure 27</a> . |     | 4.3         |      | MHz      |

| Large Signal Bandwidth <sup>1</sup> |                              | $V_{\text{OUT}} = 80 \text{ V p-p}$ . See <a href="#">Figure 26</a>                               |     | 1           |      | MHz      |

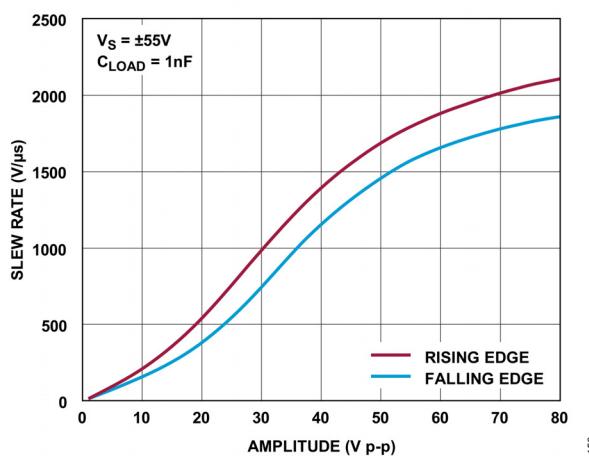

| Slew Rate, 20% to 80%               | $SR_{\text{RISE}}$           | $V_{\text{OUT}} = 80 \text{ V p-p}$ . See <a href="#">Figure 8</a> .                              |     | 2100        |      | V/μs     |

|                                     | $SR_{\text{FALL}}$           | $V_{\text{OUT}} = 80 \text{ V p-p}$ . See <a href="#">Figure 9</a> .                              |     | 1800        |      | V/μs     |

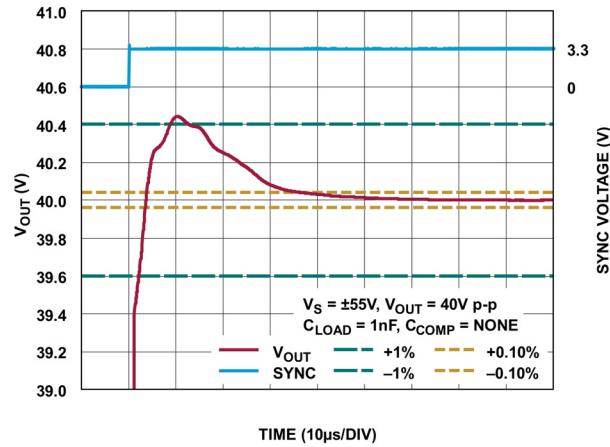

| Output 1% Settling Time             | $t_{\text{ST}}$              | $V_{\text{OUT}} = 40 \text{ V p-p}$ . See <a href="#">Figure 4</a> .                              |     | 13.5        |      | μs       |

| Output 0.1% Settling Time           | $t_{\text{ST}}$              | $V_{\text{OUT}} = 40 \text{ V p-p}$ . See <a href="#">Figure 4</a> .                              |     | 39.5        |      | μs       |

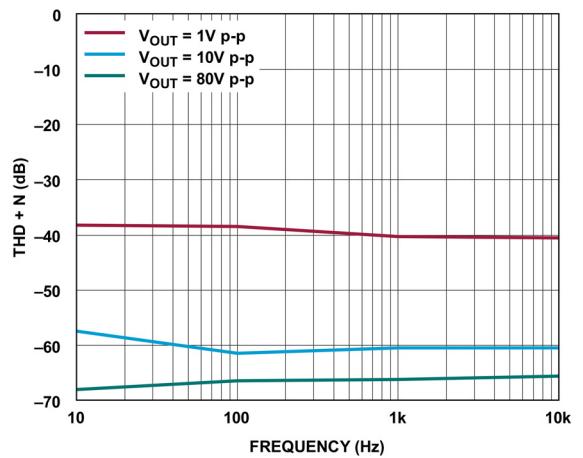

| NOISE/DISTORTION PERFORMANCE        |                              |                                                                                                   |     |             |      |          |

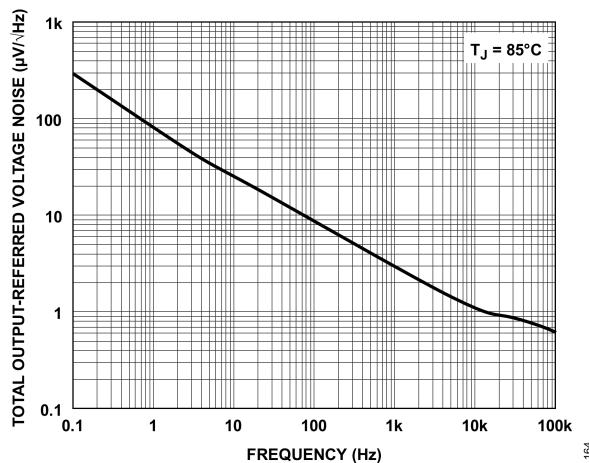

| Output Noise Spectral Density       | $V_N$                        | $C_{\text{LOAD}} = 0 \text{ nF}, T_J = 85^\circ\text{C}, f = 100 \text{ kHz}$                     |     | 0.6         |      | μV/√Hz   |

| Harmonic Distortion, HD2/HD3        |                              | $V_{\text{OUT}} = 80 \text{ V p-p}, 1 \text{ kHz}$                                                |     | -66         |      | dBc      |

|                                     |                              | $V_{\text{OUT}} = 80 \text{ V p-p}, 100 \text{ kHz}$                                              |     | -70         |      | dBc      |

| OUTPUT DC ACCURACY <sup>2</sup>     |                              |                                                                                                   |     |             |      |          |

| Output Offset Error                 | $V_{\text{OS}}$              |                                                                                                   |     | 4           | 25   | mV       |

|                                     | $V_{\text{OS\_TC}}$          | $T_c = 30^\circ\text{C} \text{ to } 85^\circ\text{C}$                                             |     | 0.16        |      | mV/°C    |

| Gain Error <sup>3</sup>             | $V_{\text{GAIN\_ERROR}}$     | $V_{\text{OUT}} = 80 \text{ V p-p}$                                                               |     | 0.24        | 0.45 | % FSR    |

|                                     | $V_{\text{GAIN\_ERROR\_TC}}$ | $T_c = 30^\circ\text{C} \text{ to } 85^\circ\text{C}$                                             |     | 0.002       |      | % FSR/°C |

| Integral Nonlinearity               | INL                          |                                                                                                   | -17 | +3/-8       | 12   | LSB      |

| Differential Nonlinearity           | DNL                          |                                                                                                   | -10 | +0.3/-4     | 4    | LSB      |

| OUTPUT CHARACTERISTICS              |                              |                                                                                                   |     |             |      |          |

| Output Voltage Range <sup>4</sup>   | $V_{\text{OUT}}$             |                                                                                                   |     | ±40         |      | V        |

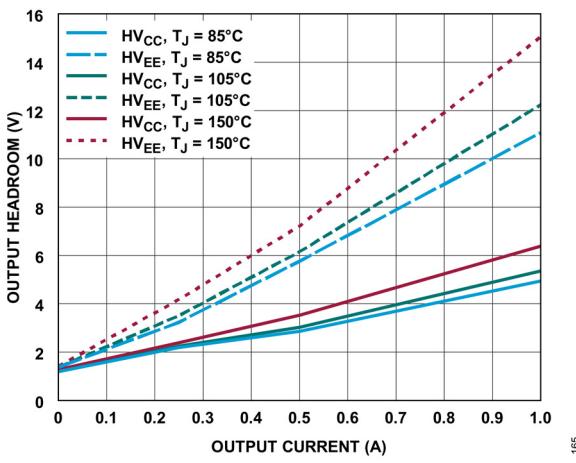

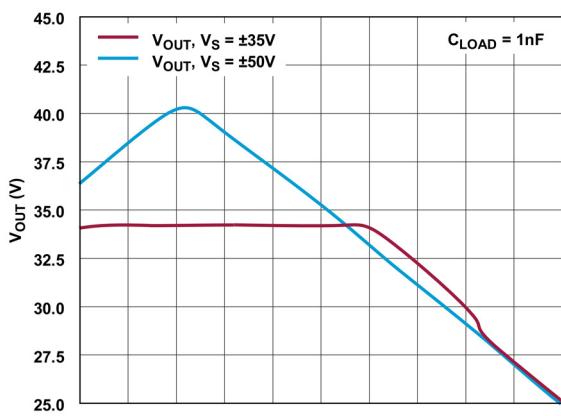

| Output Headroom                     | $V_{\text{OUT\_H}}$          | $I_{\text{OUT}} = 0.25 \text{ A}, T_J = 85^\circ\text{C}$ . See <a href="#">Figure 43</a> .       |     | HVCC - 2.2  |      | V        |

|                                     |                              | $I_{\text{OUT}} = 1 \text{ A}, T_J = 85^\circ\text{C}$ . See <a href="#">Figure 43</a> .          |     | HVCC - 5    |      | V        |

| Output Footroom                     | $V_{\text{OUT\_L}}$          | $I_{\text{OUT}} = -0.25 \text{ A}, T_J = 85^\circ\text{C}$ . See <a href="#">Figure 43</a> .      |     | HVEE + 3.3  |      | V        |

|                                     |                              | $I_{\text{OUT}} = -1 \text{ A}, T_J = 85^\circ\text{C}$ . See <a href="#">Figure 43</a> .         |     | HVEE + 11.1 |      | V        |

(特に指定のない限り、HVCC = +50V、HVEE = -50V、SET\_IQ = 0x00、VCC\_5V = +5V、VREF\_5V = +5V、REFIO\_1P2V = +1.2V、RTERM = 50Ω、FS\_ADJ への RSET = 2kΩ、COMP\_L、COMP\_H = 0pF、CLOAD = 1nF、TC = 30°C。)

| PARAMETER                                            | SYMBOL                    | CONDITIONS/COMMENTS                                                        | MIN   | TYP      | MAX                | UNITS |

|------------------------------------------------------|---------------------------|----------------------------------------------------------------------------|-------|----------|--------------------|-------|

| Continuous Output Current Drive <sup>5</sup>         | I <sub>OUT</sub>          |                                                                            |       | 1        |                    | A     |

| Peak Instantaneous Output Current Drive <sup>6</sup> | I <sub>OUT</sub>          |                                                                            |       | 2.6/-2.2 |                    | A     |

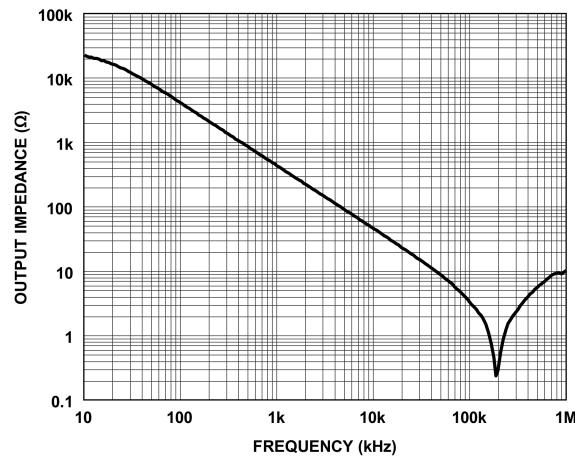

| Output Resistance During Shutdown                    | Z <sub>OUT_SDN</sub>      | See <i>Figure 47</i> .                                                     |       | 27       |                    | kΩ    |

| IOUTP, IOUTN                                         |                           |                                                                            |       |          |                    |       |

| Compliance Range                                     | V <sub>IOUTP_N</sub>      |                                                                            | -1    |          | 1.25               | V     |

| REFERENCE INPUT                                      |                           |                                                                            |       |          |                    |       |

| Input Range                                          | VREF_5V <sup>7</sup>      |                                                                            |       | 5        |                    | V     |

| Input Range                                          | REFIO_1P2V                |                                                                            | 0.12  | 1.2      | 1.25               | V     |

| Input Resistance                                     | VREF_5V                   |                                                                            |       | 34       |                    | kΩ    |

|                                                      | REFIO_1P2V                | Average input resistance over REFIO_1P2V input range.                      |       | 15       |                    | kΩ    |

| REFERENCE OUTPUT                                     |                           |                                                                            |       |          |                    |       |

| Output Voltage                                       | REFIO_1P2V                |                                                                            | 1.195 | 1.22     | 1.245              | V     |

|                                                      |                           | T <sub>C</sub> = 30°C to 85°C                                              |       | 17       |                    | µV/°C |

| Output Current Drive                                 |                           |                                                                            |       | 100      |                    | µA    |

| SDN_IO SPECIFICATIONS                                |                           |                                                                            |       |          |                    |       |

| Output Voltage Range                                 | SDN_IO                    | SDN_IO Floating                                                            | 0     |          | V <sub>CC_5V</sub> | V     |

| Shutdown Threshold                                   | SDN_IO <sub>RISING</sub>  |                                                                            | 2.54  | 2.56     | 2.57               | V     |

|                                                      | SDN_IO <sub>FALLING</sub> |                                                                            | 2.45  | 2.47     | 2.48               | V     |

| Output Current Drive Sink                            | SDN_IO <sub>SNK</sub>     |                                                                            |       | -180     |                    | µA    |

| Output Current Drive Source                          | SDN_IO <sub>SRC</sub>     |                                                                            |       | 180      |                    | µA    |

| Turn Off Time                                        | SDN_IO <sub>TOFF</sub>    | SDN_IO > SDN_IO <sub>RISING</sub> to shutdown. See <i>DELAYED SHUTDOWN</i> |       | 400      |                    | ns    |

| DC OVERCURRENT PROTECTION                            |                           |                                                                            |       |          |                    |       |

| Sourcing Setpoint Range Max                          |                           |                                                                            |       | 1        |                    | A     |

| Sourcing Code Range                                  |                           |                                                                            | 0x06  |          | 0x40               |       |

| Sinking Setpoint Range Max                           |                           |                                                                            |       | -1       |                    | A     |

(特に指定のない限り、HVCC = +50V、HVEE = -50V、SET\_IQ = 0x00、VCC\_5V = +5V、VREF\_5V = +5V、REFIO\_1P2V = +1.2V、RTERM = 50Ω、FS\_ADJ への RSET = 2kΩ、COMP\_L、COMP\_H = 0pF、CLOAD = 1nF、TC = 30°C。)

| PARAMETER                                               | SYMBOL                              | CONDITIONS/COMMENTS     | MIN  | TYP    | MAX  | UNITS  |

|---------------------------------------------------------|-------------------------------------|-------------------------|------|--------|------|--------|

| Sinking Code Range                                      |                                     |                         | 0x40 |        | 0x06 |        |

| Setpoint Resolution                                     |                                     |                         |      | 15.625 |      | mA/lsb |

| Setpoint Accuracy                                       |                                     | Code = 0x06, 93.75 mA   |      | 3.6    |      | %      |

| DC OVERVOLTAGE PROTECTION                               |                                     |                         |      |        |      |        |

| Positive Voltage Setpoint Range Max                     |                                     |                         |      | 55     |      | V      |

| Positive Code Range                                     |                                     |                         | 0x01 |        | 0x1C |        |

| Negative Voltage Setpoint Range Max                     |                                     |                         |      | -55    |      | V      |

| Negative Code Range                                     |                                     |                         | 0x1C |        | 0x01 |        |

| Setpoint Resolution                                     |                                     |                         |      | 1.953  |      | V/lsb  |

| Setpoint Accuracy                                       |                                     | Code = 0x10, 31.25 V    |      | 1.4    |      | %      |

| DC OVERTEMPERATURE PROTECTION                           |                                     |                         |      |        |      |        |

| Setpoint Range <sup>8</sup>                             |                                     | Max                     |      | 150    |      | °C     |

| Setpoint Range                                          |                                     | Min                     |      | 20     |      | °C     |

| Code Range                                              |                                     |                         | 0x2C |        | 0x40 |        |

| Setpoint Resolution                                     |                                     |                         |      | 6.51   |      | °C/lsb |

| Setpoint Accuracy                                       |                                     | Code = 0x40, TJ = 150°C |      | 2.3    |      | %      |

| TEMPERATURE MONITOR SPECIFICATIONS                      |                                     |                         |      |        |      |        |

| Initial Voltage                                         | TMP_V <sub>INITIAL</sub>            | T <sub>J</sub> = 30°C   | 1.75 | 1.78   | 1.81 | V      |

| Scaling                                                 | TMP_TC                              |                         |      | 6      |      | mV/°C  |

| SYNC INPUT <sup>9,10</sup>                              |                                     |                         |      |        |      |        |

| Input High Voltage                                      | V <sub>IH</sub> <sub>SYNC</sub>     |                         | 2    |        | 3.47 | V      |

| Input Low Voltage                                       | V <sub>IL</sub> <sub>SYNC</sub>     |                         | 0    |        | 0.8  | V      |

| Input Current                                           | I <sub>L</sub> <sub>SYNC</sub>      |                         | -1   |        | 1    | μA     |

| Input Capacitance                                       | C <sub>SYNC</sub>                   |                         |      | 12     |      | pF     |

| PARALLEL INTERFACE INPUTS (DB0 to DB13) <sup>9,10</sup> |                                     |                         |      |        |      |        |

| Input High Voltage                                      | V <sub>IH</sub> <sub>PARALLEL</sub> |                         | 2    |        | 3.47 | V      |

| Input Low Voltage                                       | V <sub>IL</sub> <sub>PARALLEL</sub> |                         | 0    |        | 0.8  | V      |

| Input Current                                           | I <sub>L</sub> <sub>PARALLEL</sub>  |                         | -1   |        | 1    | μA     |

| Input Capacitance                                       | C <sub>PARALLEL</sub>               |                         |      | 8      |      | pF     |

| SPI INTERFACE INPUTS (SCLK, SDI, CS) <sup>9,10</sup>    |                                     |                         |      |        |      |        |

| Input High Voltage                                      | V <sub>IH</sub> <sub>SPI</sub>      |                         | 2.4  |        | 3.47 | V      |

(特に指定のない限り、HVCC = +50V、HVEE = -50V、SET\_IQ = 0x00、VCC\_5V = +5V、VREF\_5V = +5V、REFIO\_1P2V = +1.2V、RTERM = 50Ω、FS\_ADJ への RSET = 2kΩ、COMP\_L、COMP\_H = 0pF、CLOAD = 1nF、TC = 30°C。)

| PARAMETER                                  | SYMBOL                   | CONDITIONS/COMMENTS                                  | MIN   | TYP   | MAX  | UNITS |

|--------------------------------------------|--------------------------|------------------------------------------------------|-------|-------|------|-------|

| Input Low Voltage                          | VIL <sub>SPI</sub>       |                                                      | 0     |       | 0.8  | V     |

| Input Current                              | I <sub>L_SPI</sub>       |                                                      | -1    |       | 1    | µA    |

| Input Capacitance                          | C <sub>SPI</sub>         |                                                      |       | 5     |      | pF    |

| SPI INTERFACE OUTPUT (SDO) <sup>9,10</sup> |                          |                                                      |       |       |      |       |

| Output High Voltage                        | VOH <sub>SDO</sub>       |                                                      | 2.4   |       | 3.31 | V     |

| Output Low Voltage                         | VOL <sub>SDO</sub>       |                                                      | 0     |       | 0.4  | V     |

| High Impedance Input Current               | I <sub>L_SDO</sub>       |                                                      | -60   |       | 60   | µA    |

| Output Capacitance                         | C <sub>SDO</sub>         |                                                      |       | 5     |      | pF    |

| RESET DIGITAL INPUT <sup>9,10</sup>        |                          |                                                      |       |       |      |       |

| Input High Voltage                         | VIH <sub>RESET</sub>     |                                                      | 2.4   |       | 3.47 | V     |

| Input Low Voltage                          | VIL <sub>RESET</sub>     |                                                      | 0     |       | 0.8  | V     |

| Input Current                              | I <sub>L_RESET</sub>     |                                                      | -1    |       | 1    | µA    |

| Input Capacitance                          | C <sub>RESET</sub>       |                                                      |       | 5     |      | pF    |

| Minimum Duration                           |                          |                                                      |       | 10    |      | ns    |

| SDN_RESET Specifications <sup>9,10</sup>   |                          |                                                      |       |       |      |       |

| Input High Voltage                         | VIH <sub>SDN_RESET</sub> |                                                      | 2.4   |       | 3.47 | V     |

| Input Low Voltage                          | VIL <sub>SDN_RESET</sub> |                                                      | 0     |       | 0.8  | V     |

| Input Current                              | I <sub>L_SDN_RESET</sub> |                                                      | -10   |       | 10   | µA    |

| Input Capacitance                          | C <sub>SDN_RESET</sub>   |                                                      |       | 5     |      | pF    |

| POWER SUPPLIES                             |                          |                                                      |       |       |      |       |

| Operation Range                            | HVCC                     |                                                      | 12    |       | 55   | V     |

|                                            | HVEE                     |                                                      | -55   |       | -12  | V     |

|                                            | VCC_5V                   |                                                      | 4.9   | 5     | 5.5  | V     |

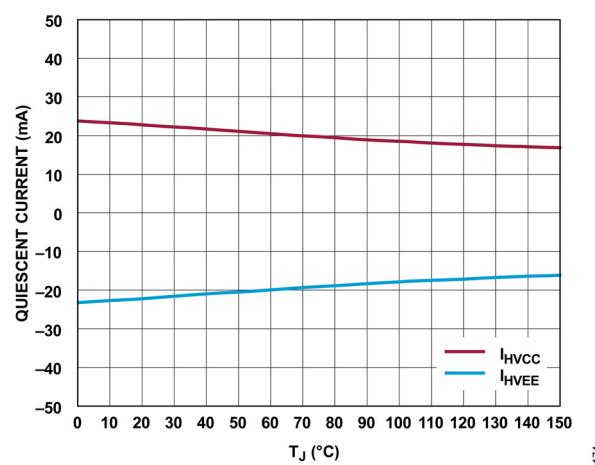

| Quiescent Current (Enabled)                | I <sub>HVCC</sub>        | See <a href="#">PROGRAMMABLE QUIESCENT CURRENT</a> . |       | 22.5  | 26.5 | mA    |

|                                            | I <sub>HVEE</sub>        | See <a href="#">PROGRAMMABLE QUIESCENT CURRENT</a> . | -26.5 | -22.5 |      | mA    |

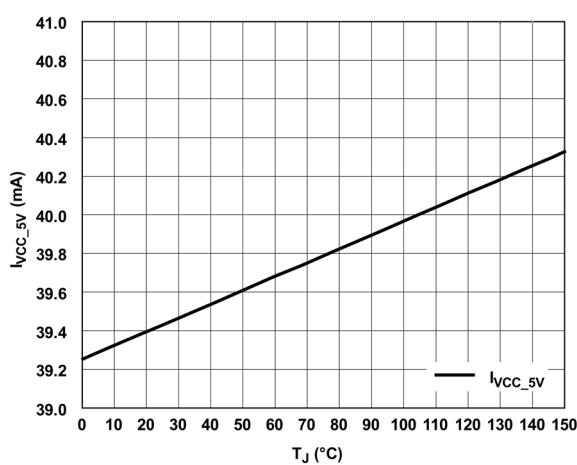

|                                            | I <sub>VCC_5V</sub>      |                                                      |       | 39    | 41.5 | mA    |

(特に指定のない限り、HVCC = +50V、HVEE = -50V、SET\_IQ = 0x00、VCC\_5V = +5V、VREF\_5V = +5V、REFIO\_1P2V = +1.2V、RTERM = 50Ω、FS\_ADJ への RSET = 2kΩ、COMP\_L、COMP\_H = 0pF、CLOAD = 1nF、TC = 30°C。)

| PARAMETER                       | SYMBOL                 | CONDITIONS/COMMENTS                 | MIN  | TYP  | MAX  | UNITS |

|---------------------------------|------------------------|-------------------------------------|------|------|------|-------|

| Quiescent Current<br>(Shutdown) | I <sub>HVCC</sub>      |                                     |      | 120  | 160  | µA    |

|                                 |                        | HVCC = +12 V                        |      | 80   |      | µA    |

|                                 | I <sub>HVEE</sub>      |                                     | -160 | -120 |      | µA    |

|                                 |                        | HVEE = -12 V                        |      | -80  |      | µA    |

| Power Supply Rejection<br>Ratio | I <sub>VCC_5V</sub>    |                                     |      | 10.5 | 13.5 | mA    |

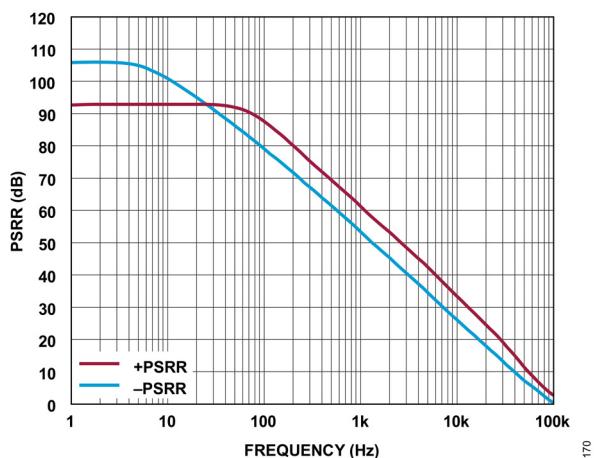

|                                 | PSRR <sub>HVCC</sub>   | HVCC = +12 V to +55 V, HVEE = -50V  |      | 93   |      | dB    |

|                                 | PSRR <sub>HVEE</sub>   | HVCC = +50 V, HVEE = -12 V to -55 V |      | 106  |      | dB    |

|                                 | PSRR <sub>VCC_5V</sub> | VCC_5V = 4.9 V to +5.5 V            |      | 86   |      | dB    |

<sup>1</sup> 大信号帯域幅は、熱設計による制限を受ける場合があります。 [温度管理](#) のセクションを参照してください。

<sup>2</sup> これらの仕様は AD8460 の出力に対するものです。

<sup>3</sup> FSR = フルスケール・レンジ

<sup>4</sup> この出力電圧振幅は、デバイスのデフォルト構成により設定されます。

<sup>5</sup> 詳細については、[温度管理](#) のセクションを参照してください。

<sup>6</sup> AD8460 では、1kHz、80Vp-p の方形波により 1nF の負荷を駆動して製品寿命試験を行っています。

<sup>7</sup> このピンにおける電源変動の影響についての詳細は、[VREF\\_5V](#) のセクションを参照してください。

<sup>8</sup> 絶対最大ジャンクション温度は 150°C です。

<sup>9</sup> 設計と特性評価により性能は確保されていますが、出荷テストは行われていません。

<sup>10</sup> T<sub>J</sub> = 30°C ~ 105°C

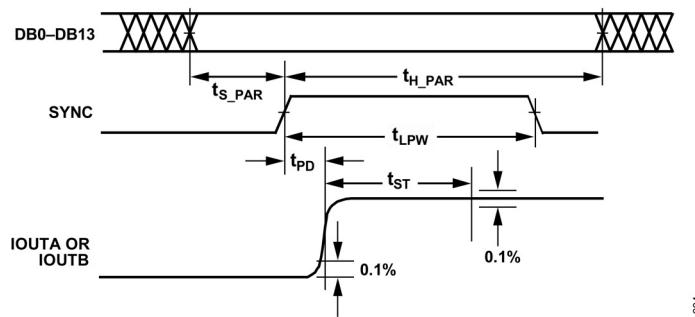

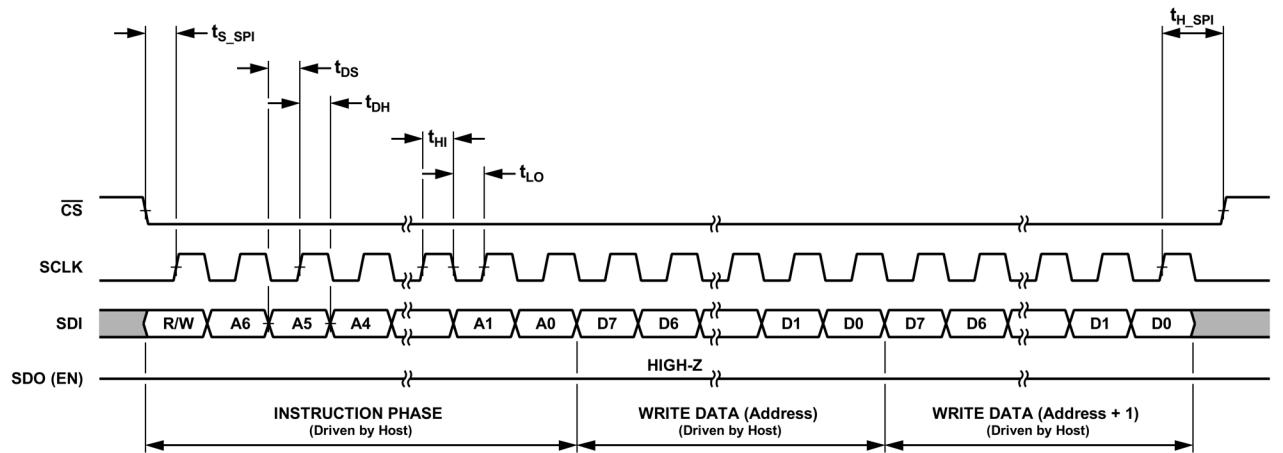

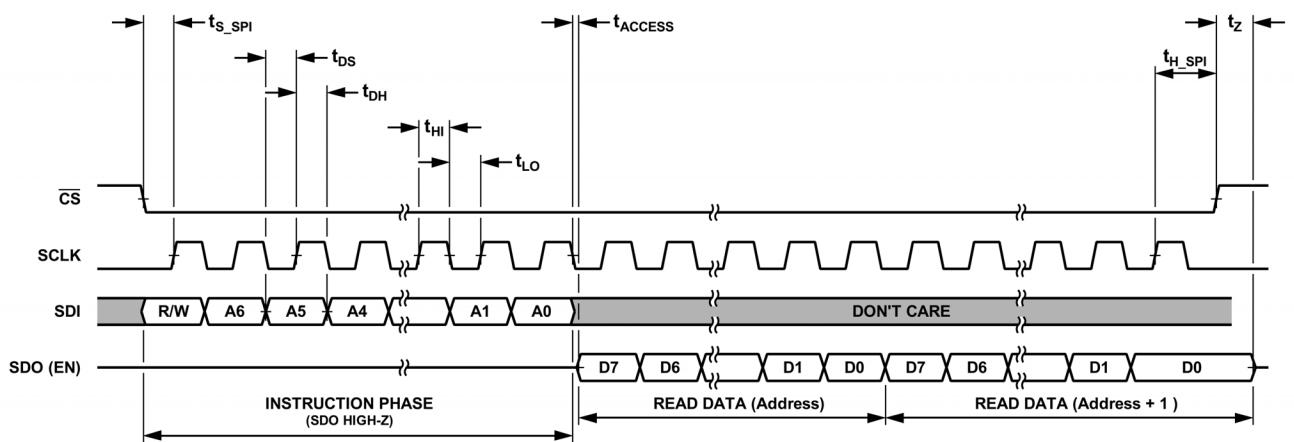

表 2. タイミング特性

(特に指定のない限り、HVCC = +50V、HVEE = -50V、SET\_IQ = 0x00、VCC\_5V = +5V、VREF\_5V = +5V、REFIO\_1P2V = +1.2V、RTERM = 50Ω、FS\_ADJ への RSET = 2kΩ、COMP\_L、COMP\_H = 0pF、CLOAD = 1nF、TJ = 30°C~105°C。)

| PARAMETER                    | SYMBOL              | CONDITIONS/COMMENTS                          | MIN | TYP | MAX | UNITS |

|------------------------------|---------------------|----------------------------------------------|-----|-----|-----|-------|

| SYNC CLOCK RATE <sup>1</sup> |                     |                                              |     |     |     |       |

| Maximum Clock Rate           | SYNC <sub>AWG</sub> | AWG Mode (Parallel Data Inputs) <sup>2</sup> |     | 100 |     | MHz   |

|                              | SYNC <sub>APG</sub> | APG Mode (Serial Data Inputs)                |     | 20  |     | MHz   |

| PARALLEL TIMING <sup>1</sup> |                     |                                              |     |     |     |       |

| Input Setup Time             | t <sub>S_PAR</sub>  |                                              | 4   |     |     | ns    |

| Input Hold Time              | t <sub>H_PAR</sub>  |                                              | 4   |     |     | ns    |

| Latch Pulse Width            | t <sub>LPW</sub>    |                                              | 4   |     |     | ns    |

| Output Propagation Delay     | t <sub>PD</sub>     |                                              |     | 45  |     | ns    |

| SPI TIMING <sup>1</sup>      |                     |                                              |     |     |     |       |

| SCLK Frequency               | f <sub>SCLK</sub>   |                                              |     |     | 20  | MHz   |

| Pulse Width High             | t <sub>HI</sub>     |                                              | 24  |     |     | ns    |

| Pulse Width Low              | t <sub>LO</sub>     |                                              | 20  |     |     | ns    |

| Setup CS to SCLK Edge        | t <sub>S_SPI</sub>  |                                              | 5   |     |     | ns    |

| Hold SCLK to CS High         | t <sub>H_SPI</sub>  |                                              | 5   |     |     | ns    |

| Setup Time SDI to SCLK High  | t <sub>DS</sub>     |                                              | 5   |     |     | ns    |

| Hold Time SDI to SCLK Low    | t <sub>DH</sub>     |                                              | 5   |     |     | ns    |

| Data Valid SCLK to SDO       | t <sub>ACCESS</sub> |                                              |     |     | 10  | ns    |

| SDO Data Release             | t <sub>Z</sub>      |                                              |     |     | 10  | ns    |

<sup>1</sup> 設計と特性評価により性能は確保されていますが、出荷テストは行われていません。

<sup>2</sup> 実現可能な最大出力周波数の詳細については、図 26 および温度管理のセクションを参照してください。

## タイミング図

図4. 並列入力のタイミング図

図5. SPIのタイミング図（書き込み動作）

図6. SPIのタイミング図（読み出し動作）

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 3. 絶対最大定格

| PARAMETER                                   | RATING                                                   |

|---------------------------------------------|----------------------------------------------------------|

| HVCC to HVEE                                | 115V                                                     |

| OUT                                         | HVEE - 0.3V to HVCC + 0.3V                               |

| COMP_H                                      | HVCC - 5V to HVCC + 0.3V                                 |

| COMP_L                                      | HVEE - 0.3V to HVEE + 5V                                 |

| COMP_T to GND                               | -0.3V to VCC_5V + 0.3V                                   |

| VCC_5V to GND                               | -0.3V to +6V                                             |

| SYNC, DB0 – DB13 to GND                     | -0.3V to DVDD_3P3V + 0.3V                                |

| VREF_5V to GND                              | -0.3V to VCC_5V + 0.3V or +5.85 V<br>(whichever is less) |

| DVDD_3P3V to GND                            | -0.3V to 3.6V                                            |

| AVDD_3P3V to GND                            | -0.3V to 3.6V                                            |

| SCLK, /CS, SDIO, SDO to GND                 | -0.3V to VCC_5V + 0.3V                                   |

| REFIO_1P2V to GND                           | -0.3V to AVDD_3P3V + 0.3V                                |

| FS_ADJ to GND                               | -0.3V to AVDD_3P3V + 0.3V                                |

| IOUTP, IOUTN to GND                         | -1V to AVDD_3P3V + 0.3V                                  |

| SYNC Clock to GND                           | -0.3V to DVDD_3P3V + 0.3V                                |

| RESET to GND                                | -0.3V to VCC_5V + 0.3V                                   |

| SDN_IO, SDN_RESET to GND                    | -0.3V to VCC_5V + 0.3V                                   |

| TMP to GND                                  | -0.3V to VCC_5V + 0.3V                                   |

| Storage Temperature Range                   | -65°C to +150°C                                          |

| Operating Temperature Range <sup>1</sup>    | -40°C to +85°C                                           |

| Junction Temperature ( $T_J$ ) <sup>2</sup> | +150°C                                                   |

| Peak Solder Reflow Temperature <sup>3</sup> | IPC/JEDEC J-STD-020                                      |

<sup>1</sup>  $T_J \leq 150^\circ\text{C}$  であることが条件です。

<sup>2</sup> 絶対最大ジャンクション温度定格付近の  $T_J$  で長時間動作させると、デバイスの経年劣化が加速されます。適切な温度管理を確実に行ってください。

<sup>3</sup> RoHS 準拠の組み立て (20 秒～40 秒)

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上のデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

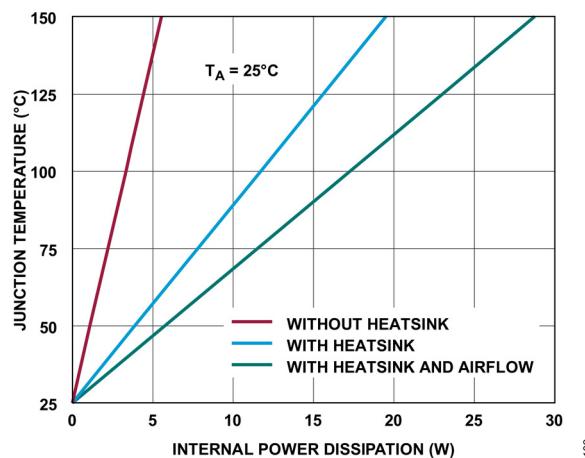

## 熱抵抗

熱性能は、PCB の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意が必要です。ジャンクション温度 ( $T_J$ ) を絶対最大定格未満に維持するには、一般的に温度管理手法を用いることが必要です。詳細については、[温度管理](#)のセクションを参照してください。

$\theta_{JA}$ は自然対流でのジャンクションと周囲の間の熱抵抗値、 $\theta_{JC}$ はジャンクションとケースの間の熱抵抗値です。

表 4. 热抵抗

| Package Type <sup>1</sup> | $\theta_{JA}$ <sup>2</sup> | $\theta_{JC}$ <sup>3</sup> | $\theta_{JC}$ <sup>2</sup> | Unit |

|---------------------------|----------------------------|----------------------------|----------------------------|------|

| 80-Lead TQFP (SV-80-7)    | 39.5                       | 1.1                        | 2.3                        | °C/W |

<sup>1</sup> 热抵抗シミュレーション値は、JEDEC JESD-51に基づいたものです。 $\theta_{JA}$ はヒートシンクを用い空気流がある場合の値です。[温度管理](#)のセクションを参照してください。

<sup>2</sup> ダイ全体でのディレーティングを含みます。

<sup>3</sup> ダイ全体での消費電力に相当します。

## 静電放電 (ESD) 定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帯電デバイス・モデル (FICDM)。

表 5. AD8460 80 ピン TQFP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | ± 1000                  | 1C    |

| FICDM     | ± 1000                  | C3    |

## ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

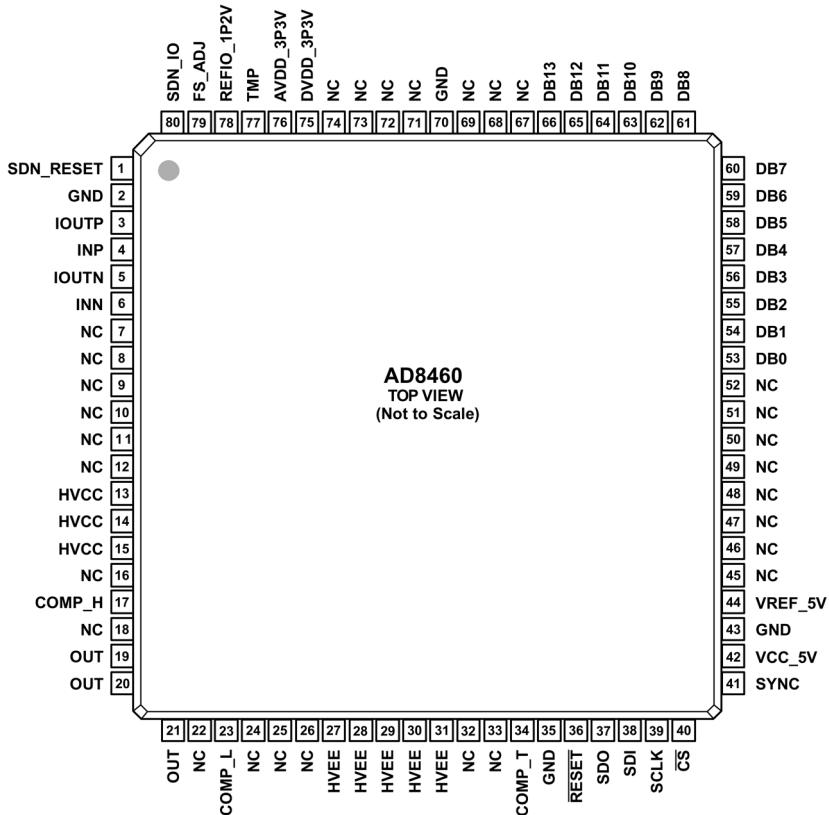

## ピン配置およびピン機能の説明

## NOTES

1. NC = NO CONNECT. DO NOT CONNECT. THIS PIN SHOULD BE SOLDERED DOWN ONTO A FLOATING PAD.

2. EXPOSED THERMAL PAD, ELECTRICALLY CONNECTED TO GND INTERNALLY. CONNECT TO EXTERNAL HEAT SINK (GROUNDED OR FLOATING) FOR THERMAL MANAGEMENT.

007

図 7. 上面図（1番ピンが左上で反時計回りにピン番号が増加）

表 6. ピン機能の説明

| 端子      | 名称        | 説明                                                                               |

|---------|-----------|----------------------------------------------------------------------------------|

| 1       | SDN_RESET | シャットダウン・リセット入力（アクティブ・ハイ）。                                                        |

| 2       | GND       | グラウンド（アナログおよびデジタル）。                                                              |

| 3       | IOUTP     | DAC の電流出力。INP に接続します。IOUTP と GND の間には、公差が 0.1% の 50Ω 高精度低ドリフト抵抗を外付けする必要があります。    |

| 4       | INP       | 高電圧ドライバの非反転入力。IOUTP に接続します。                                                      |

| 5       | IOUTN     | DAC の相補的電流出力。INN に接続します。IOUTN と GND の間には、公差が 0.1% の 50Ω 高精度低ドリフト抵抗を外付けする必要があります。 |

| 6       | INN       | 高電圧ドライバの反転入力。IOUTN に接続します。                                                       |

| 7 to 12 | NC        | 接続しません。このピンは、フローティング・パッドに半田付けする必要があります。                                          |

|          |                           |                                                                                                                                          |

|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 13 to 15 | HVCC                      | 高電圧正側電源。                                                                                                                                 |

| 16       | NC                        | 接続しません。このピンは、フローティング・パッドに半田付けする必要があります。                                                                                                  |

| 17       | COMP_H                    | ハイ・サイドの補償。容量性負荷の駆動条件に応じて、このピンは開放状態のままにするか、コンデンサを介して OUT に接続します。詳細については、 <a href="#">出力補償 (COMP_H および COMP_L)</a> のセクションを参照してください。        |

| 18       | NC                        | 接続しません。このピンは、フローティング・パッドに半田付けする必要があります。                                                                                                  |

| 19 to 21 | OUT                       | 高電圧アナログ出力。                                                                                                                               |

| 22       | NC                        | 接続しません。このピンは、フローティング・パッドに半田付けする必要があります。                                                                                                  |

| 23       | COMP_L                    | ロー・サイドの補償。容量性負荷の駆動条件に応じて、このピンは開放状態のままにするか、コンデンサを介して OUT に接続します。詳細については、 <a href="#">出力補償 (COMP_H および COMP_L)</a> のセクションを参照してください。        |

| 24 to 26 | NC                        | 接続しません。これらのピンは、フローティング・パッドに半田付けする必要があります。                                                                                                |

| 27 to 31 | HVEE                      | 高電圧負側電源。                                                                                                                                 |

| 32 to 33 | NC                        | 接続しません。これらのピンは、フローティング・パッドに半田付けする必要があります。                                                                                                |

| 34       | COMP_T                    | 温度モニタの補償。GND との間に $0.1\mu\text{F}$ のコンデンサを接続します。                                                                                         |

| 35       | GND                       | グラウンド (アナログおよびデジタル)。                                                                                                                     |

| 36       | $\overline{\text{RESET}}$ | デジタル・リセット (アクティブ・ロー、3.3V ロジック)。                                                                                                          |

| 37       | SDO                       | SPI シリアル・データ出力 (3.3V ロジック)。                                                                                                              |

| 38       | SDI                       | SPI シリアル・データ入力 (3.3V ロジック)。                                                                                                              |

| 39       | SCLK                      | SPI シリアル・クロック入力 (3.3V ロジック)。                                                                                                             |

| 40       | $\overline{\text{CS}}$    | SPI チップ・セレクト入力 (アクティブ・ロー、3.3V ロジック)。                                                                                                     |

| 41       | SYNC                      | 内部 DAC データ用の同期クロック入力 (3.3V ロジック)。                                                                                                        |

| 42       | VCC_5V                    | 低電圧電源 (5V)。                                                                                                                              |

| 43       | GND                       | グラウンド (アナログおよびデジタル)。                                                                                                                     |

| 44       | VREF_5V                   | アナログ低電圧および保護閾値 DAC 用のリファレンス電圧。VREF_5V は、外部の 5V リファレンスまたは VCC_5V (精度は低下) に接続します。電源シーケンスの詳細については、 <a href="#">VREF_5V</a> のセクションを参照してください。 |

| 45 to 52 | NC                        | 接続しません。このピンは、フローティング・パッドに半田付けする必要があります。                                                                                                  |

| 53       | DB0                       | DAC LSB (3.3V ロジック)。AWG モードのデータ入力。APG モードでは DB0 を NC または開放状態にする必要があります。                                                                  |

| 54 to 65 | DB1 to DB12               | DAC データ・ビット[1:12] (3.3V ロジック)。AWG モードのデータ入力。APG モードでは DB1~DB12 を NC または開放状態にする必要があります。                                                   |

| 66       | DB13                      | DAC MSB (3.3V ロジック)。AWG モードのデータ入力。APG モードでは DB13 を NC または開放状態にする必要があります。                                                                 |

| 67 to 69 | NC                        | 接続しません。これらのピンは、フローティング・パッドに半田付けする必要があります。                                                                                                |

| 70       | GND                       | グラウンド (アナログおよびデジタル)。                                                                                                                     |

| 71 to 74 | NC                        | 接続しません。このピンは、フローティング・パッドに半田付けする必要があります。                                                                                                  |

| 75       | DVDD_3P3V                 | デジタル電源のバイパス。AVDD_3P3V に直接接続します。GND との間に $0.1\mu\text{F}$ のコンデンサが必要です。                                                                    |

|    |            |                                                                                                                    |

|----|------------|--------------------------------------------------------------------------------------------------------------------|

| 76 | AVDD_3P3V  | アナログ電源のバイパス。内蔵 3.3V LDO の出力。GND との間に $0.1\mu\text{F}$ のコンデンサが必要です。                                                 |

| 77 | TMP        | ジャンクション温度モニタの出力電圧。                                                                                                 |

| 78 | REFIO_1P2V | 内蔵 DAC 用のリファレンス入力／出力。外部 1.2V リファレンス出力に接続、または 1.2V リファレンス出力の出力に接続（精度は低下）します。GND との間に $0.1\mu\text{F}$ のコンデンサが必要です。  |

| 79 | FS_ADJ     | DAC のフルスケール電流出力の調整。GND との間に $2\text{k}\Omega$ の抵抗が必要です。フルスケール調整の詳細については、 <a href="#">フルスケール調整</a> のセクションを参照してください。 |

| 80 | SDN_IO     | シャットダウン入力／出力（シャットダウン・アクティブ・ハイ）。シャットダウンを遅延させるには GND との間にコンデンサを接続します。                                                |

|    | EPAD       | 露出サーマル・パッド。内部で GND に電気的に接続されています。温度管理を行うには、外部の（接地またはフローティング状態の）ヒートシンクに接続します。                                       |

## 代表的な性能曲線の解釈

AD8460 の性能パラメータは、基本的にジャンクション温度 ( $T_J$ ) に依存します。この温度は、周囲温度 ( $T_A$ ) より著しく高くなる場合があります。そのため、温度に関係した AD8460 の代表的な性能の曲線 (TPC) はすべて、TMP ピンを通じて測定できる  $T_J$  の関数として ( $T_J$  を下部の横軸として) 表されます。ダイ温度の直接測定に関する詳細は [サーマル・モニタリング \(TMP\)](#) のセクションを参照してください。

完全な描像を提供するために、代替スケールとして  $T_A$  を上部の横軸に示しています。TMP ピンをモニタしていない場合は、 $T_A$  のスケールを参照してジャンクション温度を推定してください。 $T_J$  と  $T_A$  の関係は、デフォルトの温度管理設定、および各プロットで指定されたテスト条件に対し有効です。 $T_J$ 、 $T_A$ 、消費電力の間の関係については、[温度管理](#)のセクションを参照してください。

最後に、温度に基づく TPC の各曲線には、実線部と破線部の両方がある点に注意してください。実線部は、推奨するパッシブ・ヒートシンク構成を用いた場合に示される代表的な性能を表します。破線部は、強制の空冷や液体冷却のようなアクティブな温度管理を用いた場合に実現できる代表的な性能を表します。詳細については、[温度管理](#)のセクションを参照してください。

## 代表的な性能特性

特に指定のない限り、HVCC = +50V、HVEE = -50V、SET\_IQ = 0x00、VCC\_5V = +5V、VREF\_5V = +5V、REFIO\_1P2V = +1.2V、RTERM = 50Ω、FS\_ADJ への RSET = 2kΩ、COMP\_L、COMP\_H = 0pF、CLOAD = 1nF、TC = 30°C。

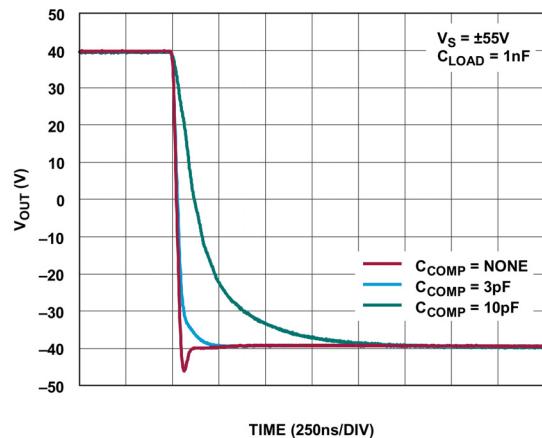

図 8. 大信号パルス応答と  $C_{COMP}$  の関係、

立上がりエッジ、 $C_{LOAD} = 1nF$

108

図 9. 立下がりエッジ – 大信号パルス応答と  $C_{COMP}$  の関係、

立下がりエッジ、 $C_{LOAD} = 1nF$

109

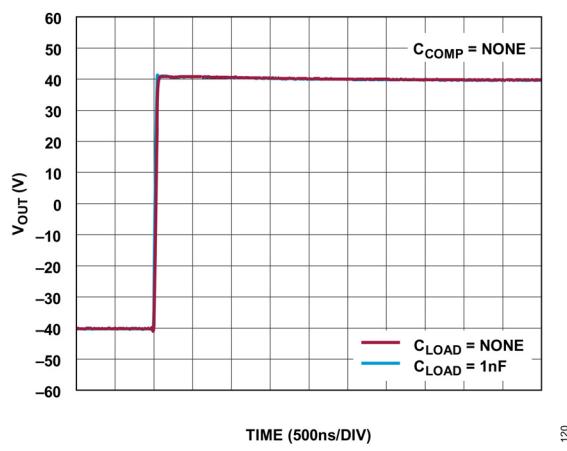

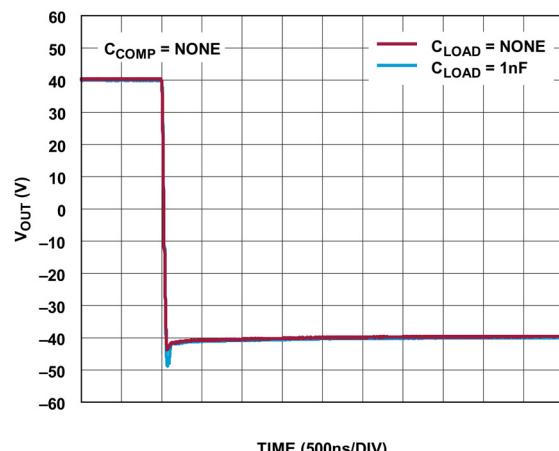

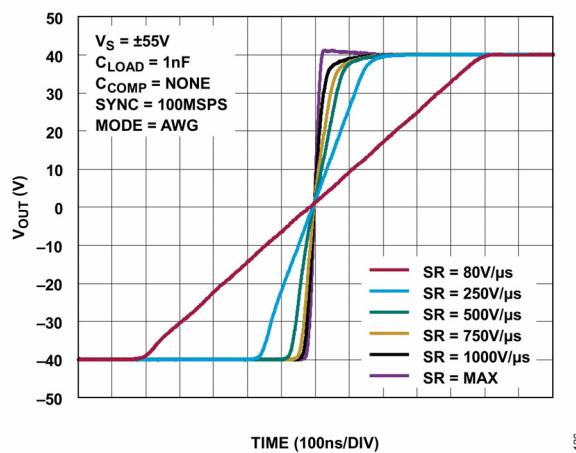

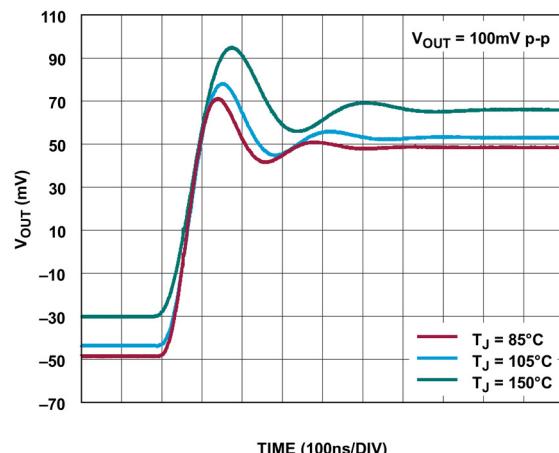

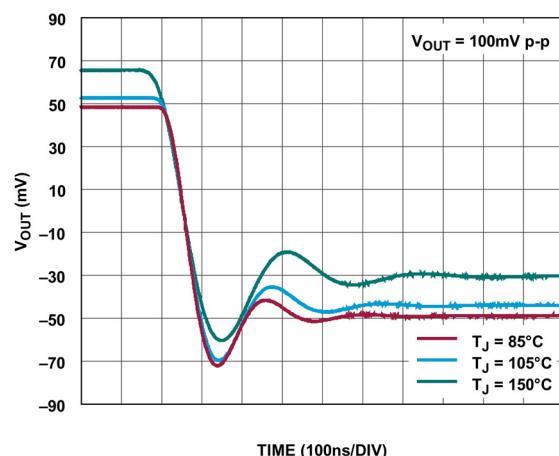

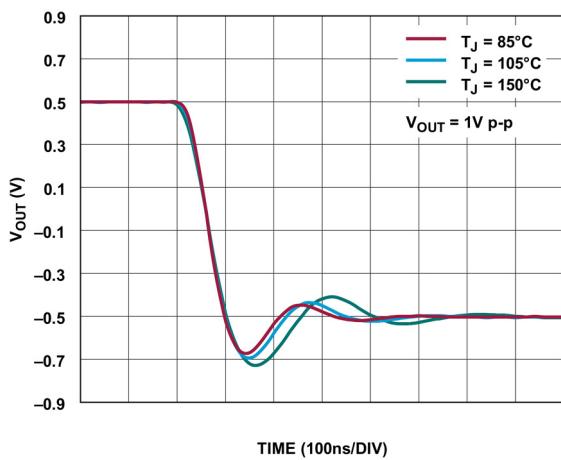

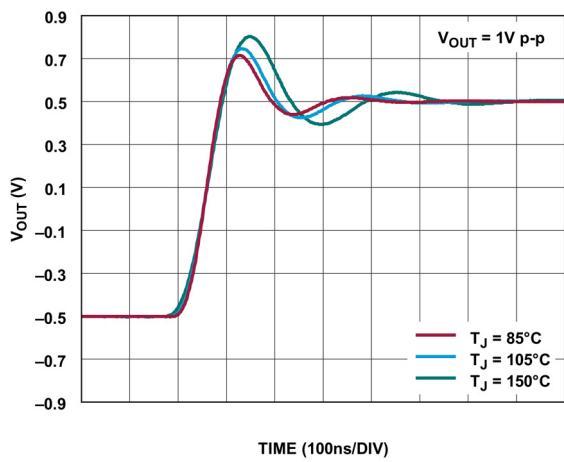

図 10. 大信号パルス応答と  $C_{LOAD}$  の関係、立上がりエッジ図 11. 大信号パルス応答と  $C_{LOAD}$  の関係、立下がりエッジ図 12. 大信号パルス応答とエッジ速度の関係、 $C_{LOAD} = 1nF$ 、 $C_{COMP} = \text{なし}$ 図 13. 小信号パルス応答と温度の関係、立上がりエッジ、 $V_{OUT} = 100mV$  p-p

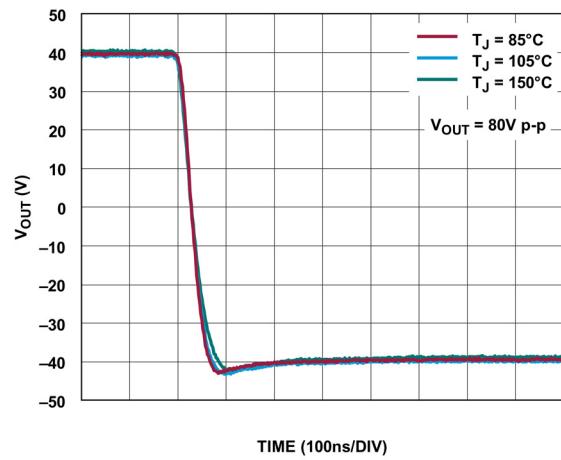

図 14. 大信号パルス応答と温度の関係、立上がりエッジ

図 15. 小信号パルス応答と温度の関係、立下がりエッジ、 $V_{OUT} = 100mV$  p-p

図 16. 大信号パルス応答と温度の関係、立下がりエッジ

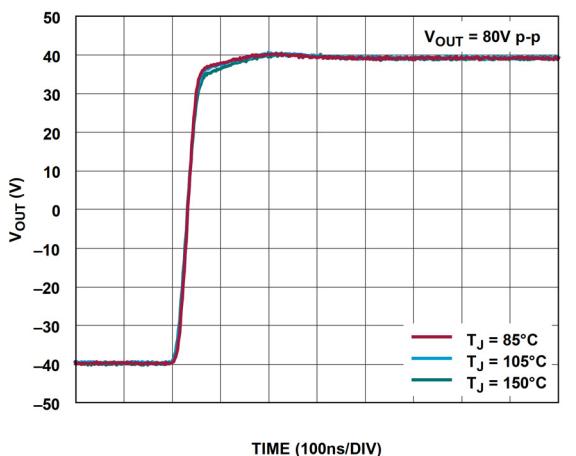

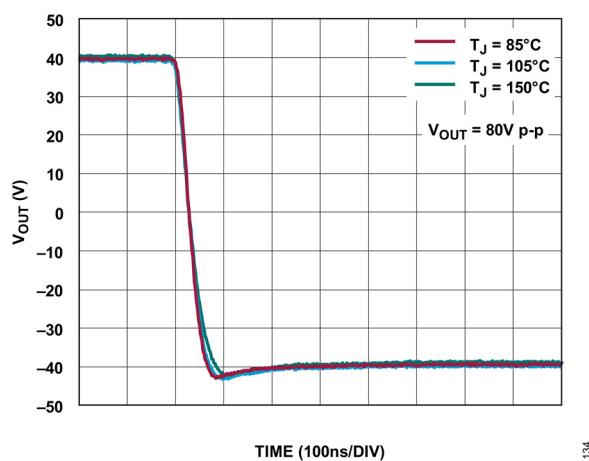

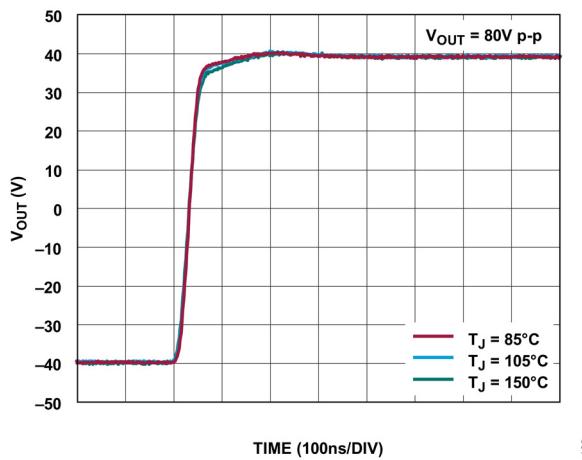

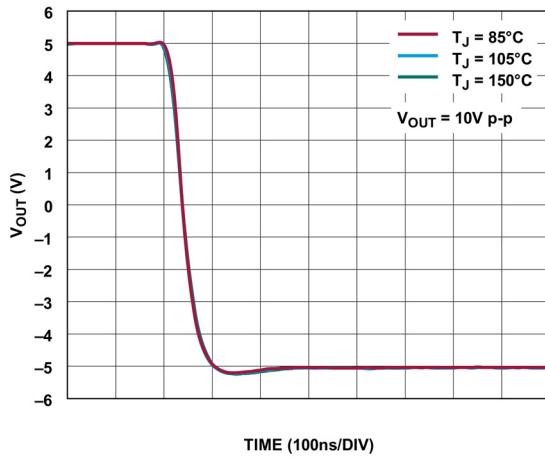

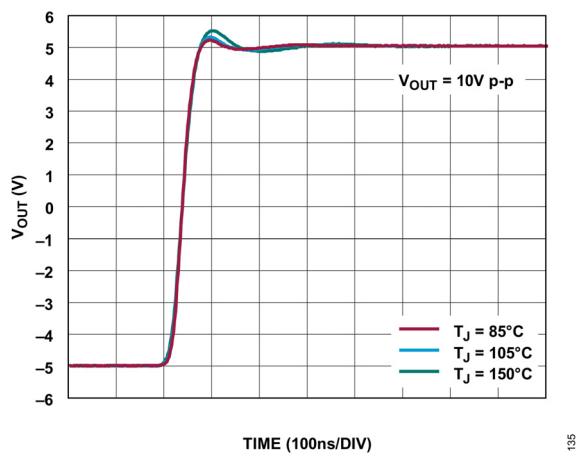

図 17. パルス応答と温度の関係、立下がりエッジ、 $V_{OUT} = 80V$  p-p図 18. パルス応答と温度の関係、立上がりエッジ、 $V_{OUT} = 80V$  p-p図 19. パルス応答と温度の関係、立下がりエッジ、 $V_{OUT} = 10V$  p-p図 20. パルス応答と温度の関係、立上がりエッジ、 $V_{OUT} = 10V$  p-p図 21. パルス応答と温度の関係、立下がりエッジ、 $V_{OUT} = 1V$  p-p

図 22. パルス応答と温度の関係、立上がりリエッジ、 $V_{OUT} = 1V$  p-p

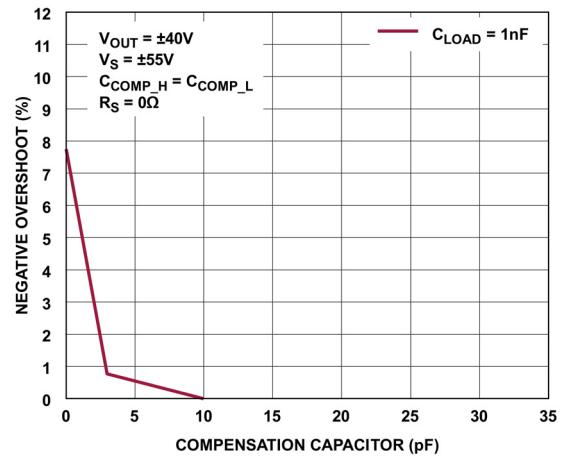

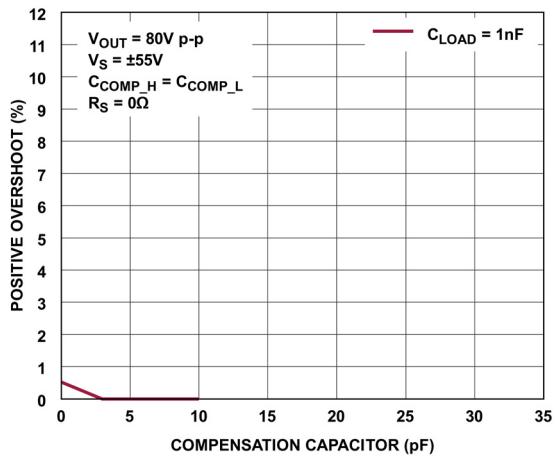

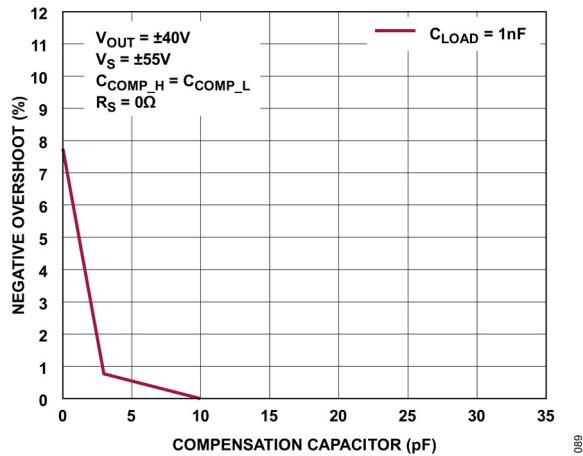

図 23. 大信号パルス応答のオーバーシュートと  $C_{LOAD}$  および  $C_{COMP}$  の関係、負のオーバーシュート

図 24. 大信号パルス応答のオーバーシュートと  $C_{LOAD}$  および  $C_{COMP}$  の関係、正のオーバーシュート

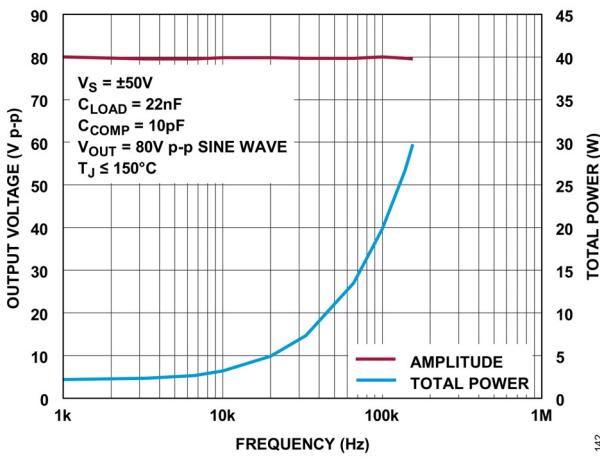

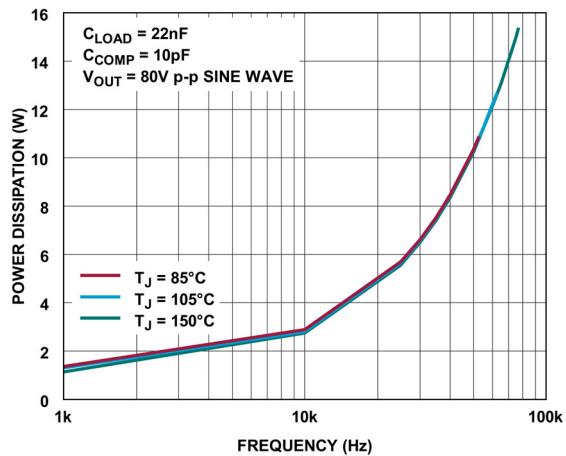

図 25. 大信号帯域幅、 $C_{LOAD} = 22nF$ 、 $C_{COMP} = 10pF$

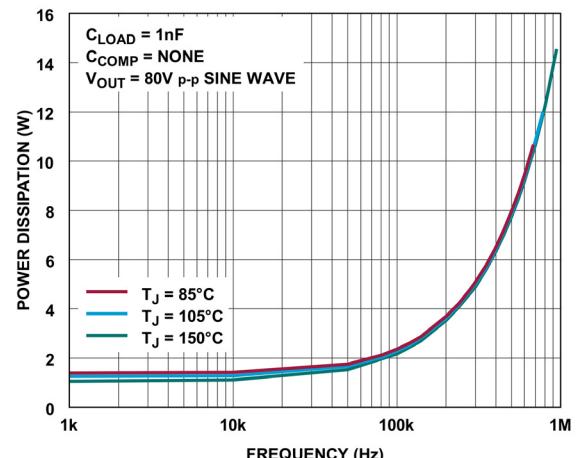

図 26. 大信号帯域幅、 $C_{LOAD} = 1nF$ 、 $C_{COMP} = なし$

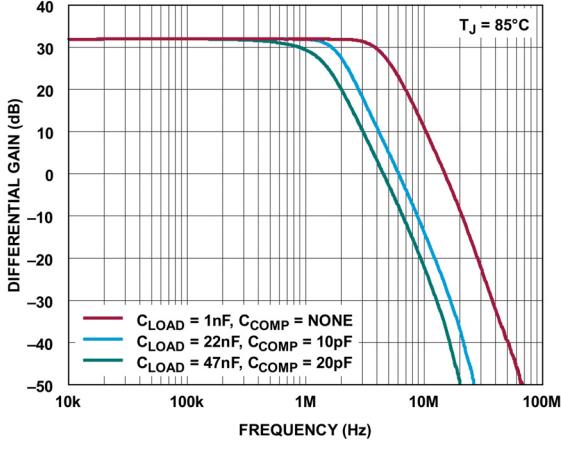

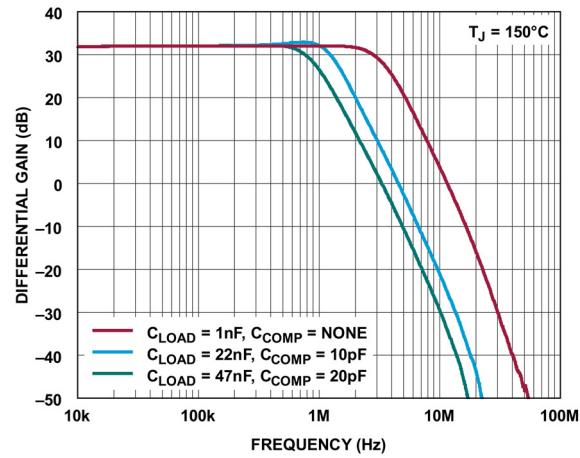

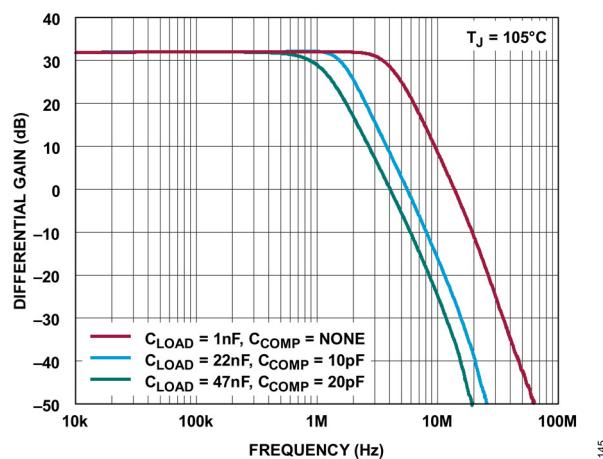

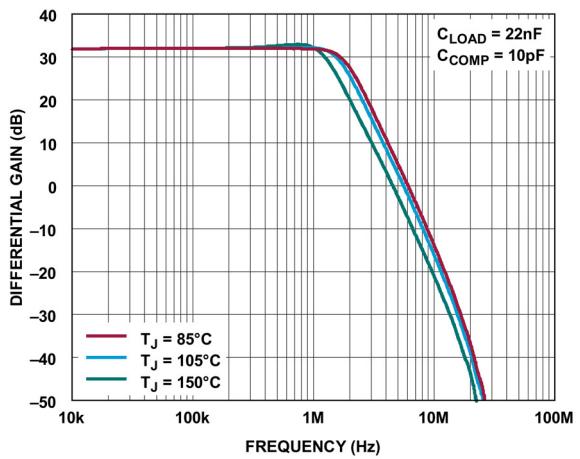

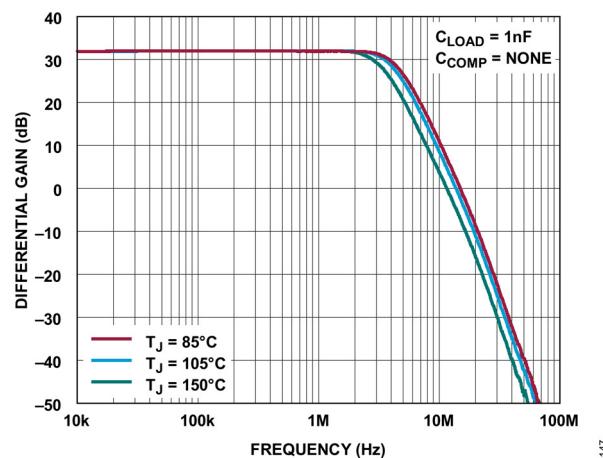

図 27. 小信号周波数応答と  $C_{LOAD}$  の関係、 $T_J = 85^{\circ}\text{C}$

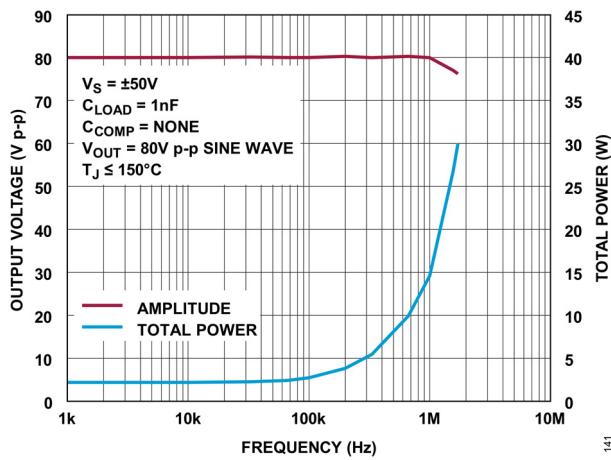

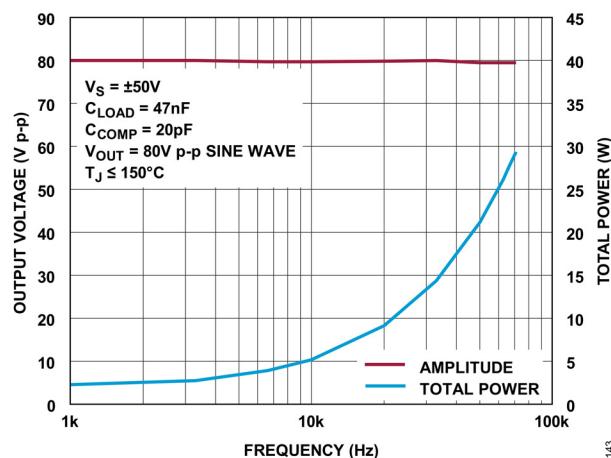

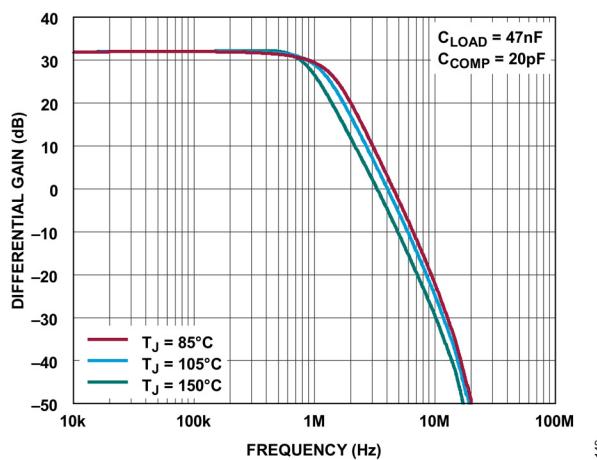

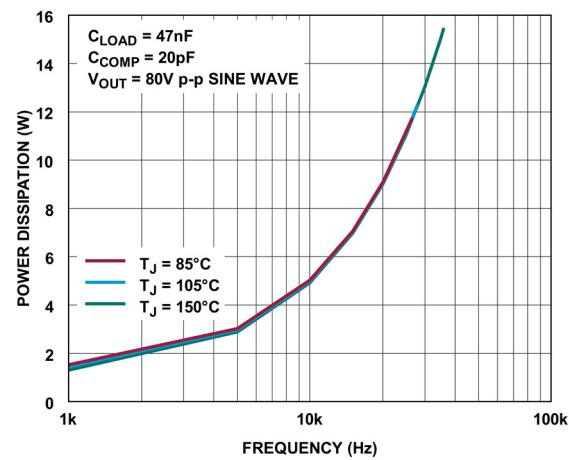

図 28. 大信号帯域幅、 $C_{LOAD} = 47\text{nF}$ 、 $C_{COMP} = 20\text{pF}$ 図 29. 小信号周波数応答と  $C_{LOAD}$  の関係、 $T_J = 150^\circ\text{C}$ 図 30. 小信号周波数応答と  $C_{LOAD}$  の関係、 $T_J = 105^\circ\text{C}$ 図 31. 小信号周波数応答と温度の関係、 $C_{LOAD} = 22\text{nF}$ 、 $C_{COMP} = 10\text{pF}$ 図 32. 小信号周波数応答と温度の関係、 $C_{LOAD} = 1\text{nF}$ 、 $C_{COMP} = \text{なし}$ 図 33. 大信号周波数応答と温度の関係、 $C_{LOAD} = 1\text{nF}$ 、 $C_{COMP} = \text{なし}$

図 34. 小信号周波数応答と温度の関係、

$C_{LOAD} = 47\text{nF}$ 、 $C_{COMP} = 20\text{pF}$

図 35. 大信号周波数応答と温度の関係、

$C_{LOAD} = 47\text{nF}$ 、 $C_{COMP} = 20\text{pF}$

図 36. 大信号周波数応答と温度の関係、

$C_{LOAD} = 22\text{nF}$ 、 $C_{COMP} = 10\text{pF}$

図 37. 0.1%および1%までのセトリング・タイム、

$V_{OUT} = 40\text{Vp-p}$ 、 $V_S = \pm 55\text{V}$ 、 $C_{LOAD} = 1\text{nF}$ 、 $C_{COMP} = \text{なし}$

図 38. スレー・レートと出力振幅の関係

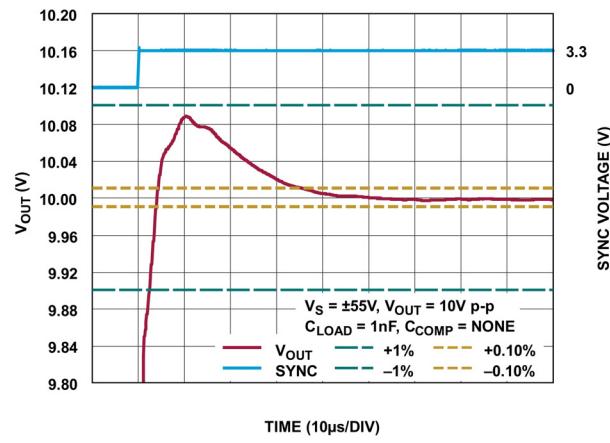

図 39. 0.1%および1%までのセトリング・タイム、

$V_{OUT} = 10\text{Vp-p}$ 、 $V_S = \pm 55\text{V}$ 、 $C_{LOAD} = 1\text{nF}$ 、 $C_{COMP} = \text{なし}$

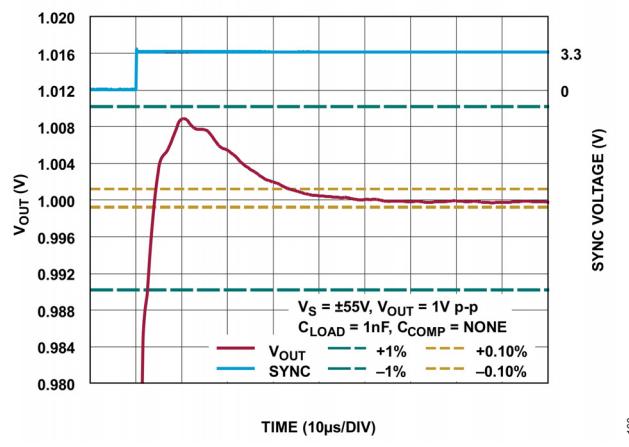

図 40. 0.1%および1%までのセッティング・タイム、

$V_{OUT} = 1\text{V p-p}$ 、 $V_S = \pm 55\text{V}$ 、 $C_{LOAD} = 1\text{nF}$ 、 $C_{COMP} = \text{なし}$

図 41. 異なる大出力振幅での全高調波歪み + ノイズ (THD + N)

と周波数の関係

図 42. 合計出力ノイズと周波数の関係

図 43. 出力ヘッドルームと出力電流および温度の関係

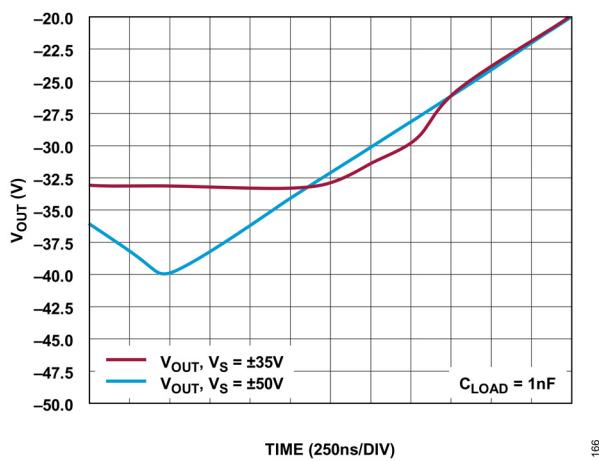

図 44. 出力オーバードライブ回復と時間の関係、立上がり

図 45. 出力オーバードライブ回復と時間の関係、立下がり

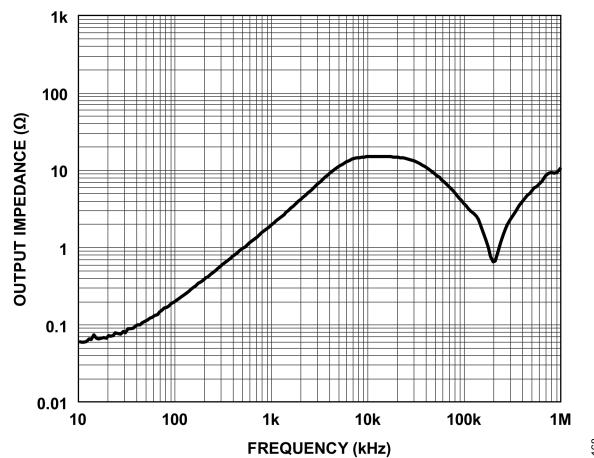

図 46. 出力インピーダンスと周波数の関係、イネーブル

図 47. 出力インピーダンスと周波数の関係、ディスエーブル

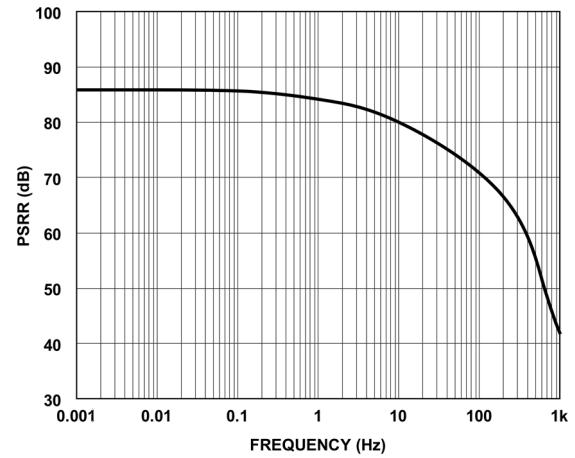

図 48. PSRR と周波数の関係、HVCC および HVEE、 $V_S = \pm 50V$

図 49. PSRR と周波数の関係、VCC\_5V、VCC\_5V = 5V

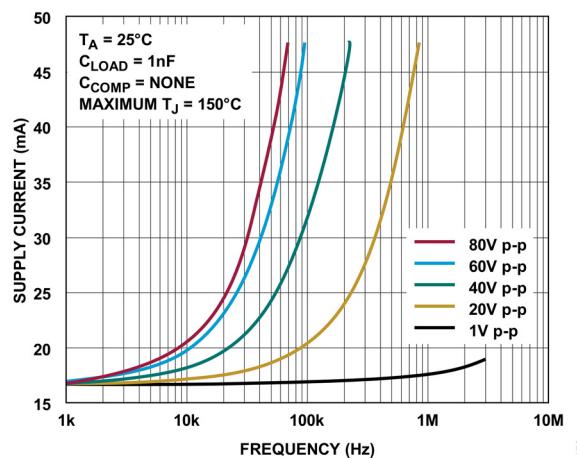

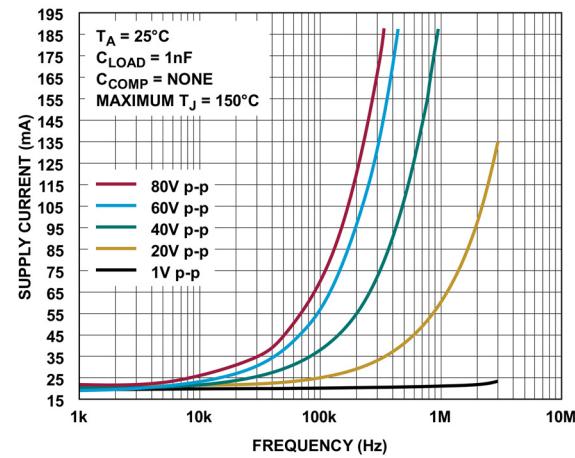

図 50. 供給電流および振幅と周波数の関係、方形波、ヒートシンクなし、 $C_{LOAD} = 1nF$ 、 $C_{COMP} = \text{なし}$ 図 51. 供給電流および振幅と周波数の関係、方形波、ヒートシンクあり、 $C_{LOAD} = 1nF$ 、 $C_{COMP} = \text{なし}$

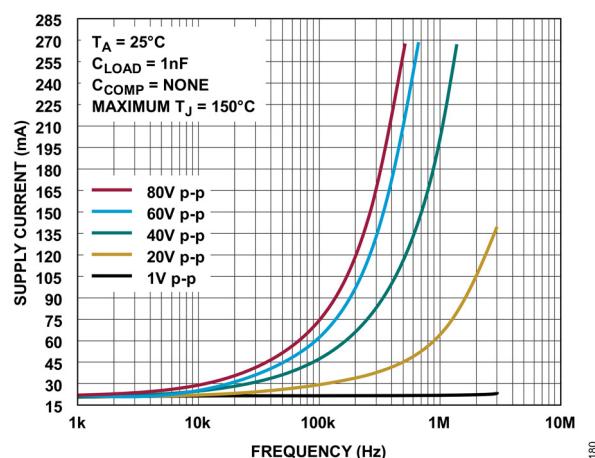

図 52. 供給電流および振幅と周波数の関係、方形波、ヒートシンクおよび空気流あり、 $C_{LOAD} = 1\text{nF}$ 、 $C_{COMP} = \text{なし}$

図 53. ジャンクション温度と内部消費電力の関係

図 54. 高電圧の自己消費供給電流と温度の関係、 $V_S = \pm 50\text{V}$

図 55.  $VCC\_5V$  の自己消費供給電流と温度の関係、 $VCC\_5V = 5\text{V}$

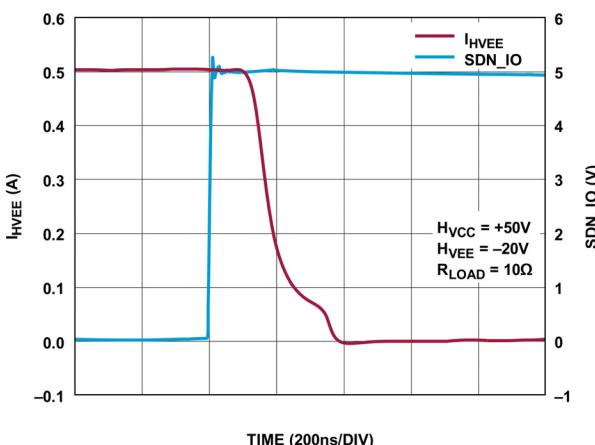

図 56. シャットダウン応答と時間の関係

図 57. シャットダウン応答と SDNIO 容量の関係

## 用語の定義

### アラーム

アラームは、保護システムでモニタリングされている、過電流（ソースまたはシンク）、過電圧（正または負）、過熱の 5 通りのフォルト状態のいずれかを検知した場合に発せられます。アラーム・フラグは、フォルト・クリア時に自動クリアするか、フォルト発生の証拠としてアラーム状態をラッチするかをカスタマイズできます。アラームをラッチした場合、これをクリアする必要があります。

### アナログ・パターン生成 (APG) モード

APG モードは、デジタル・パターン発生器の動作に似ています。AD8460 では、最大 16 個のシーケンシャルな要素からなるアナログ・パターンを生成でき、各要素には、デジタル電圧（ロジック状態）ではなくアナログ電圧が含まれています。各アナログ電圧値は 14 ビットのデータで表されます。電圧データは、ドライバ出力を更新する前に、シリアル・ペリフェラル・インターフェイス (SPI) を介してパターン・メモリにシリアルに読み込まれます。APG モードは、シーケンシャルな電圧レベルで構成される単純な反復波形に推奨されます。

### 任意波形生成 (AWG) モード

AWG モードは、任意波形発生器の動作に似ています。デジタル・データが並列状態で DAC に送られ、ドライバ出力がデータ転送と同期して更新されるため、波形をリアルタイムで生成できます。AWG モードは、複雑な波形、あるいは反復性のない波形に推奨されます。

### 保護装備

保護システムを装備することは、アラーム状態を検知しデバイスをシャットダウンするモードにドライバを置くことです。

### 保護解除

ドライバを保護解除することは、アラーム状態を無視してデバイスをシャットダウンしない状態に置くことです。ドライバが保護解除されている場合、フォルトに対して保護されず損傷の可能性があるため、極めて大きな注意を払う必要があります。

### フォルト

フォルトは、保護システムが検出可能な 5 つの過負荷状態のいずれかです。いずれのフォルトもアラームを引き起こします。ただし、強制的にデバイスをシャットダウンさせるためには、アラームが一定の最小時間（ユーザによる調整が可能）存続する必要があります。

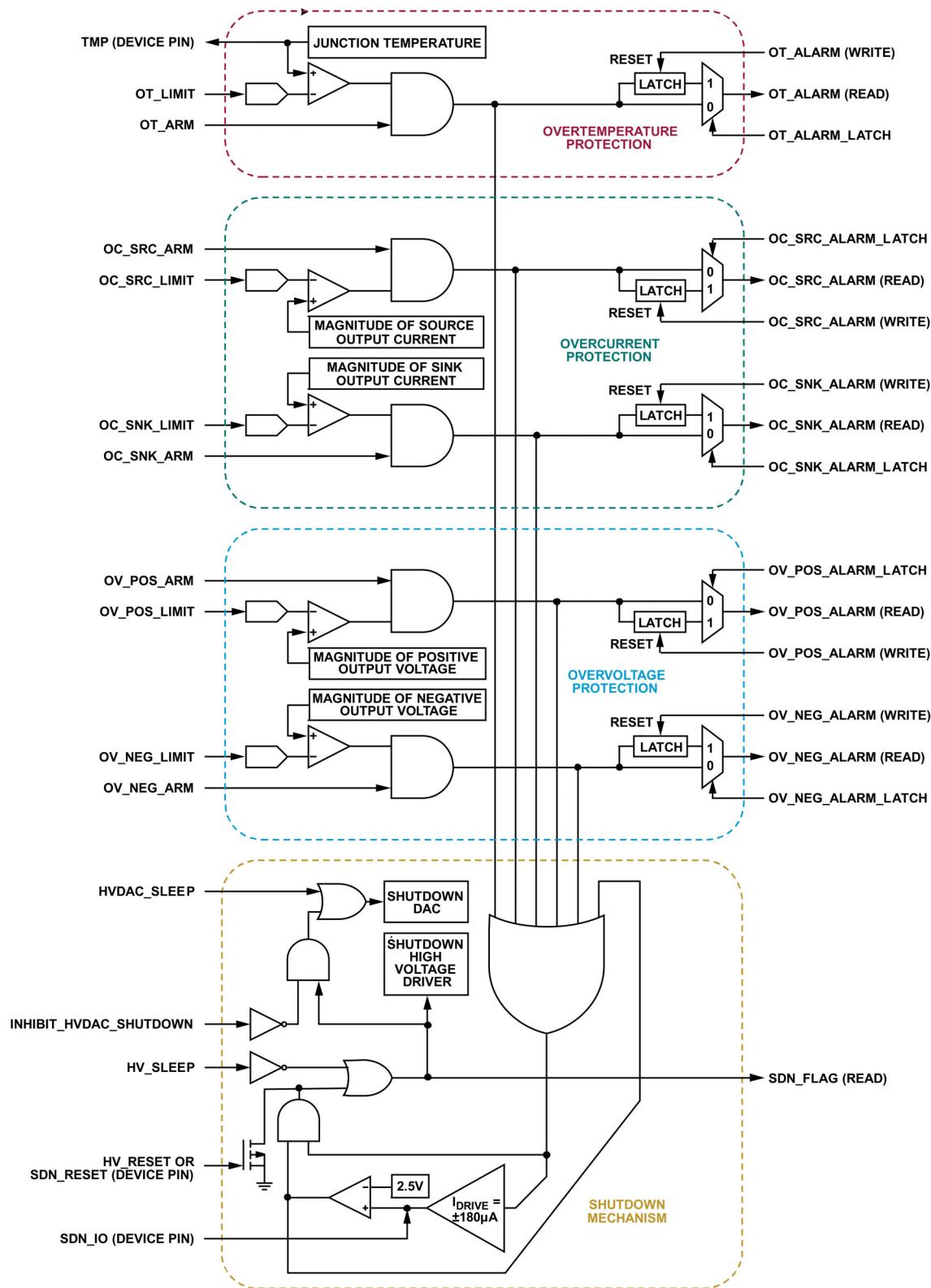

### 保護システム

保護システムは、制限設定 DAC、コンパレータ、およびユーザが指定した制限値に従ってフォルトを検出するロジック・ゲートで構成されています。基本機能を示すブロック図については図 64 を参照してください。

### 予約済み

予約済みとは、ユーザが呼び出すことのできない内部レジスタを指します。

### 安全動作領域 (SOA)

安全動作領域は、過熱による損傷を防ぐためにユーザが管理しなくてはならないパラメータによって制限された、2 次元のエンベロープです。

### シャットダウンおよびスリープ

シャットダウンとスリープはどちらも、出力がフローティング状態（高インピーダンス）となることを特徴とするインアクティビティの状態を指し、消費電力を大幅に減少させます。シャットダウンは、ユーザが SDN\_IO をハイにパルス駆動することで起動されるか、十分な時間が経過した後のアラームに応答した保護システムによって起動されます。SDN\_IO に何らかの寄生容量または追加容量がある場合は、SDN\_IO の電圧が閾値電圧未満になるまで待ってからシャットダウンの終了を試行してください。シャットダウンを終了するには、次の 3 つの方法のいずれかを用います。

- ▶ SDN\_RESET をハイにパルス駆動し、その後ローのままにする。

- ▶ 2 つの SPI コマンド（ハイに駆動後、ローに駆動）を用いて HV\_RESET ビットをハイにパルス駆動する。

- ▶ SDN\_IO をローにパルス駆動した後、フローティング状態にする。

スリープは、シャットダウンのようなインアクティビティの非ラッチ状態のことを言います。ただし、これは SPI コマンドを通じて起動 ( $HV\_SLEEP = 0$ ) や終了 ( $HV\_SLEEP = 1$ ) が行われます。スリープは、フォルトによる起動かユーザによる起動かを問わず、**SDN\_IO** シャットダウン・メカニズムを用いるすべてのコマンドに取って代わります。保護システムおよびシャットダウン・メカニズムのロジック図については、[図 64](#) を参照してください。

## スルー・ブースト

スルー・ブーストは、高速の信号遷移時に供給電流を増加させることで、従来の高速アンプに見られるような連続的な電力消費の不利益を被ることなく、出力スルーを高速化できるという、AD8460 の設計上の特長を指すものです。

## スパン

スパンは、出力の最大値と最小値の差を指します。AD8460 の公称スパンは、80V ( $+40V - (-40V)$ ) です。

## 動作原理

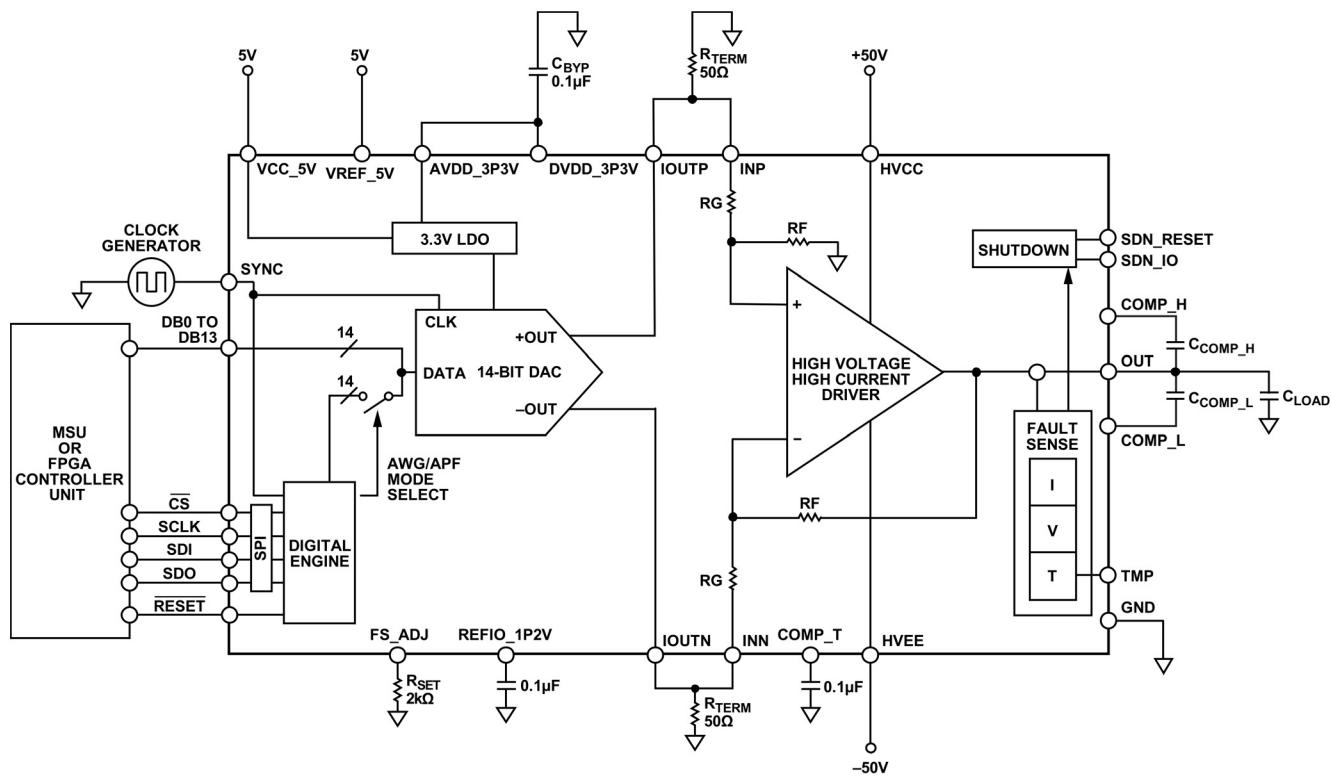

078

図 58. AD8460 の標準的な構成

## 概要

AD8460 は、「ビット・イン、パワー・アウト」の高電圧、高出力の高速ドライバで、容量性負荷に対し高電圧（最大±40V）で大きな出力電流（最大±1A）と高いスルーレート（最大±1800V/μs）を実現できるよう最適化されています。14ビット高速DAC、高電圧、高出力電流（HV-HI）のアナログ・ドライバとフォルト・モニタリングおよび保護回路を組み合わせたAD8460は、任意波形生成（AWG）、プログラマブル電源、高電圧の自動試験装置（ATE）など、高出力のアプリケーションに最適です。

システムへの入力は、14ビットのデジタルDACコードとして供給されます。デバイスは、アナログ・パターン生成（APG）モードまたは任意波形生成（AWG）モードのいずれかで動作できます。APGモードでは、SPI通信を用いて最大16通りのレベルをデジタル・レジスタに書き込み、SYNCにクロック同期して出力を更新し、それぞれ表中の次のレベルにシリアルに進行します。AWGモードでは、DACが14個の並列デジタル入力DB0～DB13を用い、SYNCにクロック同期して出力を更新します。入力と動作モードのセクションを参照してください。

設定可能なDACパラメータであるRSETおよびVREFIO\_1P2Vを用い、RTERM = 50Ωとすると、ドライバ出力の伝達関数は、次式に等しくなります。

$$V_{OUT} = \left( 80 V \times \left( \frac{DAC\ CODE}{2^{14}} \right) - 40 V \right) \times \left( \frac{2 k\Omega}{R_{SET}} \right) \times \left( \frac{V_{REFIO\ 1P2V}}{1.2 V} \right)$$

一般的な値である、VREFIO\_1P2V = 1.2VおよびRSET = 2kΩを用い、RTERM = 50Ωとすると、ドライバ出力の伝達関数は次のように簡略化できます。

$$V_{OUT} = \left( 80 V \times \left( \frac{DAC\ CODE}{2^{14}} \right) - 40 V \right)$$

最大出力振幅は内部 DAC 設定によって実現されます。フルスケール調整のセクションを参照してください。

AD8460 では、HVCC および HVEE に高電圧両電源（最大±55V）、VCC\_5V に低電圧単電源（5V）が必要です。デバイスは、LDO 出力から 3.3V を内部生成し AVDD\_3P3V に出力します。また、DVDD\_3P3V は内部デジタル電源バイパス・ポイントで、AVDD\_3P3V に接続する必要があります。電源とデカッピングのセクションを参照してください。

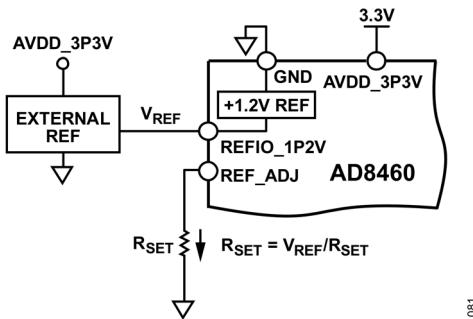

アナログ低電圧および保護閾値 DAC にリファレンス電圧を供給するために、VREF\_5V には 5V のリファレンスが必要です。VREF\_5V は、外部の 5V リファレンスまたは VCC\_5V（精度は低下）に接続します。AD8460 では、高速 DAC にリファレンス電圧を供給するために、REFIO\_1P2V に 1.2V のリファレンスを使用します。REFIO\_1P2V は、外部の 1.2V リファレンスに接続します。あるいは、1.2V の内部リファレンスを用いる場合は開放状態にします。ただし、この場合は精度が低下します。リファレンス動作のセクションを参照してください。FS\_ADJ に接続された外部抵抗  $R_{SET}$  により、内部 DAC のリファレンス電流  $I_{REF}$  が設定されます。図 58 のように、 $R_{SET}=2\text{k}\Omega$  の場合、DAC のフルスケールの相補的出力電流は公称値 20mA に設定されます。フルスケール調整のセクションを参照してください。

DAC および高電圧大電流（HV-HI）出力ドライバは、ハイ・サイドでは IOUTP ピンと INP ピン、ロー・サイドでは IOUTN ピンと INN ピンを通じて外部に接続できます。終端抵抗 ( $R_{TERM}$ ) は、HV-HI ドライバへの入力を設定します。 $R_{TERM}$  には、高精度  $50\Omega$  の抵抗を用いることを推奨します。 $R_{TERM}$  の%公差は、出力に発生する可能性のある誤差に対応します。通常、精度とコストのバランスの取れたシステムには、0.1%の公差が推奨されます。より高精度のシステムには 0.01%の公差を推奨します。

駆動能力の他、AD8460 は、フォルト・モニタリングや負荷保護に関連する機能一式を備えています。デバイスには、最大ジャンクション温度  $150^{\circ}\text{C}$  で 2.5V というように、ジャンクション温度を示す電圧を出力するジャンクション温度モニタ機能があります。デジタル・エンジンでは、プログラマブルな出力電流制限（ソース電流やシンク電流）、プログラマブルな出力電圧制限（正電圧や負電圧）、プログラマブルな温度制限（最大ジャンクション温度）が可能です。シャットダウン保護設定のセクションを参照してください。

## 初期パワーアップ

### 電源とデカッピング

AD8460 では、HVCC および HVEE に±12V～±50V の範囲の高電圧両電源、VCC\_5V に 5V の低電圧単電源が必要です。すべての電源ピンは、 $0.1\mu\text{F}$  の高品質低 ESR コンデンサを用いて、グラウンドにバイパスしてください。

バイパス・コンデンサは、電源ピンにできるだけ近付けて配置し、PCB のアナログ・グランド・プレーンに短距離で直接接続します。更に、各高電圧源とグラウンドの間に  $1.2\mu\text{F}$  のセラミック・コンデンサを 4 個配置することによって、低周波数の良好なバイパスが可能となり、スルー・レートの速い大信号に対応するのに必要な電流を供給することができます。高電圧源の配線には、低インダクタンスのプレーンを推奨します。

AVDD\_3P3V は、3.3V 内部 LDO 用のアナログ電源バイパス・ポイントです。AVDD\_3P3V には、AVDD\_3P3V と GND の間に  $0.1\mu\text{F}$  のバイパス・コンデンサが必要です。AVDD\_3P3V は DVDD\_3P3V に接続します。

### VREF\_5V

VREF\_5V は、内部アラーム閾値 DAC 用のリファレンス電圧を設定します。このピンはバイアスが必要です。高精度の 5V リファレンス IC を推奨します。あるいは、VREF\_5V を VCC\_5V に接続することもできます（精度は低下します）。

精度の低下した VREF\_5V リファレンスは、内部 LDO リファレンス電圧をシフトさせ、SDN\_IO のシャットダウン電圧、過電圧、および加熱閾値が表に仕様規定されている値から変動する原因となります。例えば、公差が 1% の 5V リファレンスを VREF\_5V に用いた場合、これらのレベルは代表値から 1% 変化する可能性があります。

VCC\_5V と VREF\_5V のパワーオンの順序は、HV-HI ドライバの初期状態に影響します。電源シーケンスのセクションを参照してください。

## 電源シーケンス

DVDD\_3P3V を AVDD\_3P3V に接続してからパワーアップする必要があります。高電圧電源 (HVCC および HVEE) と VCC\_5V には個別に任意の順序で給電できます。

AD8460 は、シャットダウン・モードまたはアクティブ・モードでパワーアップできます。シャットダウン・モードで AD8460 をパワーアップすることを推奨します。これは、VCC\_5V に給電してから VREF\_5V に給電することで実行できます。シャットダウン・モードでの初期パワーアップ後、SDN\_IO ピンをローにプルダウンすることで確実に AD8460 がオンになるようにします。続いて、SDN\_IO ピンを開放状態にすることで、AD8460 をオンにしたままフォルト・モニタリングおよび保護機能を効果的にできます。パワーダウン時は、最初に VREF\_5V をパワーダウンしてから VCC\_5V をダウントします。

VCC\_5V が VREF\_5V に接続された状態でパワーオンされた場合は、デバイスは、ドライバをイネーブル、DAC をディスエーブルした状態でパワーオンします。出力電圧が高電圧でパワーオンする可能性があるため、アクティブ・モードでのパワーアップには特別の注意が必要です。これにより、大出力電流が発生する可能性があります。

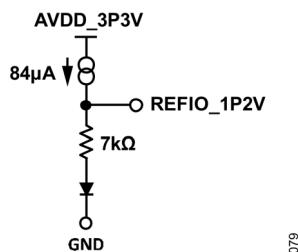

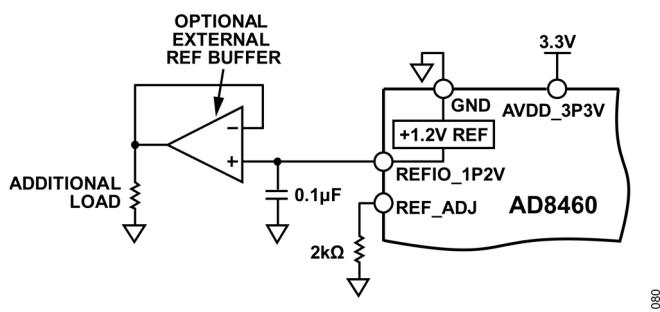

## リファレンス動作

AD8460 の内蔵 DAC には、1.2V の内蔵バンドギャップ・リファレンスが備わっています。この内部リファレンスはディスエーブルできませんが、出力精度を向上するために外部リファレンスで容易にオーバーライドできます。図 59 にバンドギャップ・リファレンスの代表的回路を示します。REFIO\_1P2V ピンは、内部リファレンスを用いるか外部リファレンスを用いるかに応じて、出力または入力のいずれかの役割をします。内部リファレンスを用いるには、0.1μF のコンデンサで REFIO\_1P2V ピンを GND とデカッピングするだけです。内部リファレンス電圧は REFIO\_1P2V に出力されます。REFIO\_1P2V の電圧を回路内の別の場所で使用する必要がある場合は、入力バイアス電流が 100nA 未満の外部バッファ・アンプを用いる必要があります。図 60 に、バッファ付き内部リファレンス構成の例を示します。

図 59. 内部リファレンスの代表的回路

図 60. バッファ付き内部リファレンス構成

外部リファレンスは、図 61 に示すように、REFIO\_1P2V に印加できます。外部リファレンスは、精度やドリフト性能を向上するために一定のリファレンス電圧を供給するものであっても、ゲイン制御を行うために変化するリファレンス電圧を供給するものであってもかまいません。なお、内部リファレンスがオーバーライドされるため  $0.1\mu\text{F}$  の補償コンデンサは不要で、REFIO\_1P2V の入力インピーダンスが比較的高いため外部リファレンスによる負荷が最小限に抑えられる点に注意してください。

図 61. 外部リファレンス構成

## 入力と動作モード

AD8460 は、アナログ・パターン生成 (APG) モードまたは任意波形生成 (AWG) モードのいずれかで波形を生成できます。

APG モードが用いられるのは、必要な波形が一連のシーケンシャルな DC 電圧レベルであって、エッジ速度制御は必要条件ではない場合です。APG モードでは、最大 16 通りの離散的な DC 電圧レベルからなるパターンが、SPI を通じてパターン・メモリにシリアルに読み込まれます。パターンが読み込まれた後、SYNC を用いてパターン・データをクロックに同期して出力します。14 ビットのデータが SYNC の立上がりエッジで DAC にラッチされ、データ・ポインタは後続の立下がりエッジで次のレジスタに進みます。パターン・メモリの最後のデータが DAC に送られた後、データ・ポインタは最初のデータ・レジスタに戻り、SYNC にクロックが供給される限りそのパターンが繰り返されます。APG モードでは、パラレル・データ・ポート (DB13~DB0 ピン) を開放状態にする必要があります。これらのピンはデジタル・エンジンによって内部駆動されるためです。

AWG モードでは、目的の波形を示す 14 ビットの入力データがパラレル・インターフェイス (DB13~DB0 ピン) を通じて読み込まれ、SYNC の立上がりエッジでクロックに同期して入力されます。これは、出力を更新するための一般的な並列モードの高速 DAC 使用法に対応します。AWG モードが用いられるのは、複雑な波形、特定のエッジ速度、あるいはデジタル・プリディストーションが必要な場合です。表 7 に、APG および AWG の入力モードの比較を示します。

表 7. APG および AWG の入力モードの比較

| Mode | Input Type         | Output Waveform   | Adjustable Edge Speed | Pre-distortion       |

|------|--------------------|-------------------|-----------------------|----------------------|

| APG  | Serial through SPI | Pulses            | Limited to 16 levels  | Limited to 16 levels |

| AWG  | Parallel           | Complex waveforms | Yes                   | Yes                  |

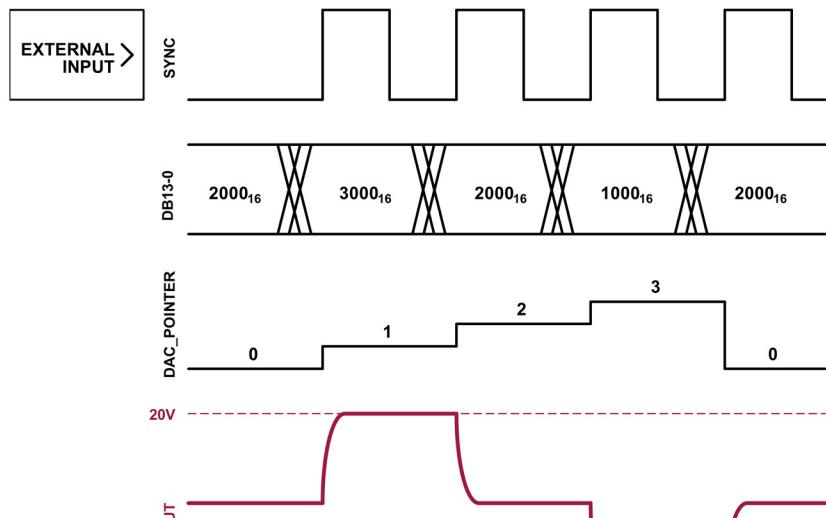

## アナログ・パターン生成 (APG)

APG モードを有効化するには、CTRL\_REG\_02 レジスタの APG\_MODE\_ENABLE ビットを 1 に、CTRL\_REG\_00 レジスタの WAVE\_GEN\_MODE ビットを 1 に設定します。

パターンは非リアルタイムで生成され、データが SPI を介してパターン・メモリにシリアルに読み込まれてから、ドライバ出力が更新されます。SYNC 信号は、HVDAC\_DATA\_REGMAP のパターン・メモリの値に基づき立上がりエッジで DAC 入力をロードし、立下がりエッジでドライバ出力を更新します。SYNC がパルス駆動されていれば、このパターンが繰り返されます。APG モードの最大 SYNC レートは 20MHz です。

HVDAC\_DATA\_REGMAP では、14 ビットの各データが、下位のバイトと上位のバイトを構成する 2 つの 8 ビット・レジスタの組み合せに保存されます。例えば、パターンの最初のレベルは、HVDAC\_DATA\_BYTE\_00 および HVDAC\_DATA\_BYTE\_01 に保存されます。最初のレベルが 14 ビットのバイナリ・シーケンス  $b_{13}b_{12}b_{11}b_{10}b_9b_8b_7b_6b_5b_4b_3b_2b_1b_0$  であれば、HVDAC\_DATA\_BYTE\_00 には 8 個の下位ビット (バイナリ  $b_7b_6b_5b_4b_3b_2b_1b_0$ ) が含まれ、HVDAC\_DATA\_BYTE\_01 には 8 個の上位ビット (バイナリ  $b_9b_8b_{13}b_{12}b_{11}b_{10}b_9b_8$ ) が含まれます。ここで、最初の 2 ビットは予約済みです。パターンの 2 つめのレベルは HVDAC\_DATA\_BYTE\_02 および HVDAC\_DATA\_BYTE\_03 で、以下、同様に続きます。

デフォルトのパターン・メモリ値は、図 62 に示すように、上下±20V のシーケンシャルな 4 レベルの階段波形で、周波数は SYNC のクロック・レートで定義されます。これらのデフォルト値は、SPI を介して上書きできます。APG モードは、最大 16 個のシーケンシャルな電圧レベルからなるアナログ・パターンを生成します。各電圧レベルのパルス幅は、SYNC のクロック・レートで定義され、次式で計算できます。

$$\text{Pulse Width} = \frac{1}{\text{SYNC Clock Rate}} \cdot \frac{1}{\# \text{ of Sequential Voltage Levels}}$$

SYNC のクロック・レートが 1MHz で出力が 2 レベルのシーケンシャル・パルスであると仮定すると、パルス幅は以下のとおりです。

$$\text{Pulse Width} = \frac{1}{1 \text{ MHz}} \cdot \frac{1}{2} = 0.5 \mu\text{s}$$

図 62. APG モードのリファレンス例

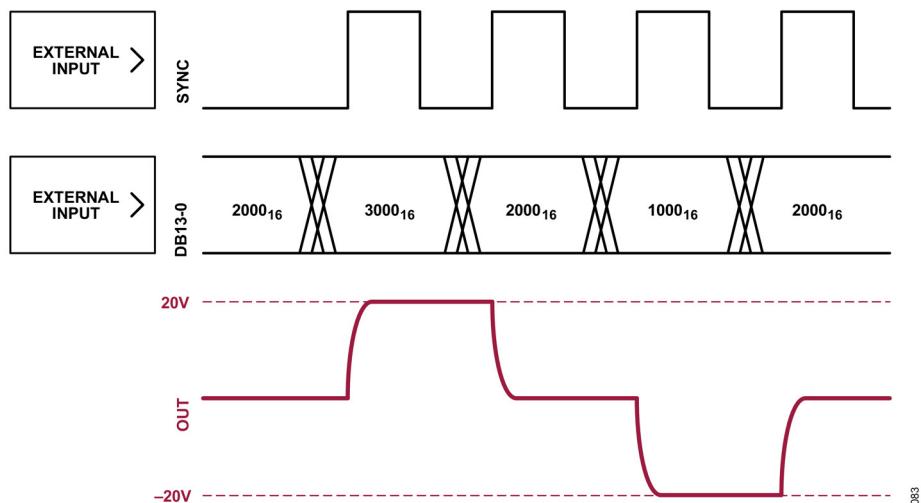

## 任意波形生成 (AWG)

デフォルトでは、AD8460 は AWG モードでパワーオンします。

AWG モードを選択するには、CTRL\_REG\_02 レジスタの APG\_MODE\_ENABLE ビットを 0 にクリアし、CTRL\_REG\_00 レジスタの WAVE\_GEN\_MODE ビットを 0 にクリアします。波形はリアルタイムで生成され、データはパラレル・データ・ポートを通じてレジスタに読み込まれます。SYNC 信号はその立上がりエッジで HVDAC をロードし、立下がりエッジでドライバ出力を更新します。AWG モードの最大 SYNC レートは 100MHz です。

AWG モードでは、動作は本質的に高速 DAC の動作です。ユーザが 14 ビットの並列データを DB0～DB13 のピンに供給し、SYNC クロックを供給します。データの供給は通常、ユーザの FPGA (フィールド・プログラマブル・ゲート・アレイ) を通じて行われます。

図 63. AWG モードのリファレンス例

## プリディストーションおよび調整可能入力エッジ速度

容量性負荷、ケーブル長、エッジ速度は、オーバーシュートやリンギングなどの AD8460 のトランジエントなセトリング特性に、歪みをもたらす可能性があります。AWG モードでは、ユーザが波形データを変更してこの歪みを最小限に抑えることができます。この変更には、逆特性を追加して応答の形を改善することや、入力エッジをより低速にするよう調整することなどがあります。

プリディストーション機能は入力波形にアンダーシュートを生じさせ、これを用いることで所定の負荷に対するオーバーシュートを補償できます。これは、AWG モードでも APG モードでも行うことができますが、AWG モードのほうが分解能が高く、そのため、最も単純な波形を除くすべての波形でより良い歪み補償が可能です。

AWG モードでは、APG モードで使用できるクロック速度より高速の SYNC クロックを用いて、より高いサンプル・レートで DAC に入力データを供給できます。そのため、ユーザは、入力エッジをより小さなステップに形成できます。ステップ幅を増加させることで、入力エッジ速度を任意のユーザ指定値に調整できます。エッジ速度を遅くすると、所定の容量性負荷に対するオーバーシュートを減少できます。

エッジ・イベント時に必要なステップ数は式 1 で計算できます。

$$n_{STEPS} = \frac{AMPLITUDE_{P-P} (V) \times f_{SYNC} (MHz)}{EDGE SPEED \left( \frac{V}{\mu s} \right)} \quad (\text{Eq. 1})$$

クロックが 100MHz でステップが 80V の場合、100 ステップが必要です。線形出力を生じさせるには、ステップあたりのビット数は  $[2^{14}/n_{steps}]$  で、この場合、163 です。ステート・マシンを HDL に実装してエッジ・イベントを制御できます。あるいは、エッジをより長いコード・パターンの一部とすることもできます。エッジ速度の例を、[代表的な性能特性](#) のセクションの図 12 に示します。

## 出力電流駆動

AD8460 の出力段は、2 重拡散金属酸化膜半導体 (DMOS) 高電圧トランジスタをカスコード接続して構築されており、容量性負荷に大電流を供給できるよう最適化されています。最大  $1800\text{V}/\mu\text{s}$  のエッジ速度を生成し、適切な温度管理を行いながら  $\pm 1\text{A}$  を連続的に供給するよう設計されています。AD8460 のデフォルトのヒートシンクは、Wakefield-Vette の P/N 518-95AB で、消費電力の高いアプリケーションではアクティブ冷却が推奨されます。熱関連の詳細については [温度管理](#) のセクションを参照してください。

AD8460 の保護システムは、設定自由度が高いため、多様なアプリケーションに適しています。アプリケーションに対し最大の柔軟性を実現するため、AD8460 は、出力電流（ソースおよびシンク）、出力電圧（正および負）、ダイ温度を個別にモニタする機能を内蔵しており、ドライバとその負荷を 5 種類のフォルトから保護します。詳細については、[フォルト・モニタリングおよび保護](#) のセクションを参照してください。

デフォルトでは、AD8460 の保護機能は無効化するよう設定されています。保護機能を有効化しプログラムするには SPI を使用します。過熱シャットダウンを手動で行うには、SDN\_IO ピンを TMP に接続します。シャットダウンの応答時間は、SDN\_IO ピンのコンデンサで調整できます。遅延シャットダウンおよび手動サーマル・シャットダウンについては、[シャットダウン制御 \(SDN\\_IO\)](#) のセクションを参照してください。

## フォルト・モニタリングおよび保護

フォルト・モニタリングおよび保護機能は、閾値を設定し、フォルト・タイプごとに保護システムを装備することで有効化できます。必要な保護を行うための閾値は SPI でプログラムできます。プログラムされた閾値を超えるとアラームが生じ、AD8460 がシャットダウンします。図 64 に、フォルト・モニタリングおよび保護の制御ロジックを示します。

モニタリングされる 5 通りのフォルトにはそれぞれ、関連する次の 4 つのデジタル・レジスタがあります。

1. プログラマブル閾値。閾値は、0x08 (CTL\_REG\_08) レジスタ～0x0C (CTL\_REG\_12) レジスタのビット[6:0]でプログラムできます。範囲と分解能の設定については、[シャットダウン保護設定](#) のセクションを参照してください。

2. ARM。ARM は、0x08 (CTL\_REG\_08) レジスタ～0x0C (CTL\_REG\_12) レジスタのビット[7]でプログラムできます。対応する ARM を 1 に設定すると、アラームに対応してシャットダウンするよう保護システムに指示します。対応する ARM を 0 に設定すると、保護システムを解除して、アラームが生じてもシャットダウンしないようにします。ARM が 0 の場合、フォルトに対する保護はありません。

3. ALARM インジケータ・フラグ。ALARM インジケータ・フラグは、レジスタ 0x0E (CTRL\_REG\_14) を介して読み出しとクリアができます。ALARM インジケータ・フラグは、保護システムが装備されているときにフォルトが発生すると、保護システムによって 1 に設定されます。フォルト状態が続く限り ALARM は 1 のままとなり、フォルト状態がクリアされると 0 に戻ります。ALARM によってドライバが強制的にシャットダウンすると、ドライバはフォルト状態がクリアされ ALARM フラグがリセットしても、シャットダウン状態のままとなります。ALARM の各ビットは、フォルト状態のステータスを示します。ALARM がクリアされると、それ以前にどのフォルトが発生したかを判別することができなくなることもあります。トランジエント・フォルト検出については、[ALARM\\_LATCH](#) 機能を参照してください。ALARM インジケータ・フラグをクリアするには、対応する ALARM レジスタ・ビットに 1 を書き込みます。

4. ALARM\_LATCH は、ユーザによって設定され、任意の ALARM フラグをラッチして、発生する可能性のあるトランジエント・フォルトの証拠を保存できます。ALARM\_LATCH は、レジスタ 0x0D (CTRL\_REG\_13) を通じてプログラムできます。ALARM\_LATCH がイネーブルされていて ALARM インジケータ・フラグがトリガされた場合、関連するフォルト状態がクリアされても ALARM インジケータ・フラグは残ります。これはトランジエント・フォルトを特定するのに役立ちます。ALARM\_LATCH フラグをクリアするには、対応する ALARM\_LATCH レジスタ・ビットに 0 を書き込みます。

084

図 64. フォルト・モニタリングおよび保護の制御ロジック

## フォルト始動型シャットダウン保護機能

AD8460 には、SDN\_IO を介する、消費電力を抑えるシャットダウン機能が備わっています。シャットダウンは、消費電力を抑えるためにユーザーによって始動するか、損傷を防止するための AD8460 の保護システムによって始動されるフォルトによって始動できます。ユーザー始動型のシャットダウンの詳細については、[シャットダウン制御 \(SDN\\_IO\)](#) のセクションを参照してください。AD8460 は、以下の 5 つの動作状態を内部でモニタしており、いずれかのプログラマブル・アラーム制限を超えた場合にシャットダウンするよう設定できます。

- ▶ 過電流ソース制限 (最大+1A)

- ▶ 過電流ソース制限 (最大+1A)

- ▶ 正過電圧制限 (最大+55V)

- ▶ 負過電圧制限 (最大-55V)

- ▶ ジャンクション過熱制限 ( $T_J = 20^\circ\text{C} \sim T_J = 150^\circ\text{C}$ )

[表 24](#)～[表 28](#)、または、これらの制限に割り当てられたレジスタ・アドレスを参照してください。

5 つの内部フォルト・モニタはどれも、アラーム状態が検出されると SDN\_IO ピンをハイにラッチします。ラッチ状態は、フォルト状態がクリアされ AD8460 が再イネーブルされるまで保持されます。

シャットダウン後にドライバを再イネーブルするには、2 つの SPI (ハイに駆動後、ローに駆動) を用いて HV\_RESET ビットをハイにパルス駆動します。また、SDN\_RESET をハイにパルス駆動してそれをローのままにするか、SDN\_IO をローにプルダウンして SDN\_IO ピンをフローティング状態にすることでも、AD8460 を再イネーブルできます。これにより、フォルト・モニタリングおよび保護を再イネーブルできます。SDN\_IO をローにパルス駆動するために用いるデジタル・リソースは、SDN\_IO のハイ状態をオーバーライドできるよう、約 180 $\mu\text{A}$  の駆動能力があることが必要です。詳細については、[シャットダウン制御 \(SDN\\_IO\)](#) のセクションを参照してください。

## シャットダウン保護設定

シャットダウン保護機能のコード範囲は、デバイスの動作範囲を超えていません。この範囲は、シャットダウン制御が最も重要な場合に、直線性およびデバイスの制限値での正確さを最適化するよう選択されます。[表 9](#)～[表 11](#) の値は、必要なトリガ・ポイントより小さな値でトリガするように丸められた値で、コードから閾値への変換係数に基づいた正確な値ではない点に注意してください。

[表 8](#) に、シャットダウンの範囲と分解能を示します。

表 8. シャットダウン保護の範囲および分解能

| FAULT TYPE      | NOMINAL RANGE                   | NOMINAL RESOLUTION |

|-----------------|---------------------------------|--------------------|

| Overcurrent     | $\pm 1 \text{ A}$               | 15.625 mA          |

| Oervoltage      | $\pm 55 \text{ V}$              | 1.953V             |

| Overtemperature | Up to $T_J = 150^\circ\text{C}$ | 6.51°C             |

## 過電流保護のプログラミング

過電流保護の閾値プログラミングの分解能 (1LSB) は、15.625mA が公称値です。

コードを電流閾値に変換するには：

$$\text{Current Threshold (mA)} = \text{Code}_{\text{Decimal}}(\text{LSB}) \times 15.625 \left( \frac{\text{mA}}{\text{LSB}} \right)$$

電流をコードに変換するには：

$$\text{Code}_{\text{Decimal}}(\text{LSB}) = \frac{15.625 \left( \frac{\text{mA}}{\text{LSB}} \right)}{\text{Current Threshold (mA)}}$$

ユーザが目的の電流をコードに変換する場合（10 進数）、計算値を最も近い整数値になるよう切り捨てます。その整数値をコードから電流閾値への変換式に代入すると、実際の温度閾値を決定できます。

一般的な動作電流に対応した代表的な閾値コードについては表 9 を参照してください。

シャットダウン閾値設定を正しくプログラムする方法については、シャットダウン閾値設定のプログラミングのセクションを参照してください。

表 9. 動作電流の代表的な閾値コード

| BINARY CODE | HEXADECIMAL VALUE | DECIMAL VALUE | CURRENT (mA) |

|-------------|-------------------|---------------|--------------|

| 0000011     | 0x03              | 3             | 50           |

| 0000110     | 0x06              | 6             | 100          |

| 0010011     | 0x13              | 19            | 300          |

| 0100000     | 0x21              | 32            | 500          |

| 1000000     | 0x40              | 64            | 1000         |

### 過電圧保護のプログラミング

過電圧保護の閾値プログラミングの分解能（1 LSB）は、1.953V が公称値です。

コードを電圧閾値に変換するには：

$$Voltage\ Threshold\ (V) = Code_{Decimal}(LSB) \times 1.953 \left( \frac{V}{LSB} \right)$$

電圧をコードに変換するには：

$$Code_{Decimal}(LSB) = \frac{1.953 \left( \frac{V}{LSB} \right)}{Voltage\ Threshold\ (V)}$$

ユーザが目的の電圧をコードに変換する場合（10 進数）、計算値を最も近い整数値になるよう切り捨てます。その整数値をコードから電圧閾値への変換式に代入すると、実際の温度閾値を決定できます。

一般的な動作電圧に対応した代表的な閾値コードについては表 10 を参照してください。

シャットダウン閾値設定を正しくプログラムする方法については、シャットダウン閾値設定のプログラミングのセクションを参照してください。

表 10. 動作電圧の代表的な閾値コード

| BINARY CODE | HEXADECIMAL CODE | DECIMAL CODE | VOLTAGE (V) |

|-------------|------------------|--------------|-------------|

| 0000101     | 0x05             | 5            | 10          |

| 0001010     | 0x0A             | 10           | 20          |

| 0001111     | 0x0F             | 15           | 30          |

| 0010100     | 0x14             | 20           | 40          |

| BINARY CODE | HEXADECIMAL CODE | DECIMAL CODE | VOLTAGE (V) |

|-------------|------------------|--------------|-------------|

| 00111100    | 0x1C             | 28           | 55          |

### 過熱保護のプログラミング

過熱保護の閾値プログラミングの分解能 (1LSB) は、6.51°C が公称値です。

コードを温度に変換するには：

$$\text{Temperature Threshold (°C)} = \text{Code}_{\text{Decimal}}(\text{LSB}) * 6.51 \left( \frac{\text{°C}}{\text{LSB}} \right) - 266.64 \text{ (°C)}$$

温度をコードに変換するには：

$$\text{Code}_{\text{Decimal}}(\text{LSB}) = \text{Temperature Threshold (°C)} + \frac{266.64 \text{ (LSB)}}{6.51 \left( \frac{\text{°C}}{\text{LSB}} \right)}$$

ユーザが目的の温度をコードに変換する場合 (10 進数)、計算値を最も近い整数値になるよう切り捨てます。その整数値をコードから温度への変換式に代入すると、実際の温度閾値を決定できます。

一般的な動作温度に対応した代表的な閾値コードについては表 11 を参照してください。

シャットダウン閾値設定を正しくプログラムする方法については、[シャットダウン閾値設定のプログラミング](#)のセクションを参照してください。

表 11. 動作温度の代表的な閾値コード

| BINARY CODE | HEXADECIMAL VALUE | DECIMAL VALUE | KELVIN TEMPERATURE | CELSIUS TEMPERATURE |

|-------------|-------------------|---------------|--------------------|---------------------|

| 0101100     | 0x2C              | 44            | 293                | 20                  |

| 0110110     | 0x36              | 54            | 358                | 85                  |

| 0111001     | 0x39              | 57            | 377                | 104                 |

| 0111011     | 0x3B              | 59            | 396                | 123                 |

| 1000000     | 0x40              | 64            | 423                | 150                 |

### シャットダウン閾値設定のプログラミング

表 18 のレジスタ・マップは、8 ビットのレジスタ CTRL\_REG\_08～CTRL\_REG\_12 を用いて、5 種の内部フォルト・モニタを装備し、目的の閾値をプログラムできることを示しています。これらの内部フォルト・モニタリング・レジスタでは、ビット 7 を用いて保護機能のオン／オフを切り換え、ビット[6:0]を用いてアラーム閾値を設定します。表 9～表 11 のバイナリ・コードは、レジスタをフォルト・モニタリング用にプログラムする場合はビット[6:0]であり、計算にはビット 7 は含まれない点に注意してください。

閾値設定を正しく内部フォルト・モニタリング・レジスタにプログラムし、各フォルト・モニタリング機能をオンにするには、次のステップの手順を実行します。

- ▶ ビット[6:0]を必要な閾値コードにプログラムします。

- ▶ ビット[7]を 1 にプログラムして保護をイネーブルし、再度、ビット[6:0]に必要な閾値コードを書き込みます。

## シャットダウン制御 (SDN\_IO)

SDN\_IO がハイの場合、HV-HI 出力ドライバはディスエーブルされます。初期パワーアップのセクションで説明したように、出力ドライバがシャットダウン・モードになるように SDN\_IO をハイにしてパワーアップし、AD8460 の必要な設定を SPI を通じて書き込んだら SDN\_IO をローにすることを推奨します。続いて、SDN\_IO ピンを開放状態にすることで、AD8460 をオンにしたままフォルト・モニタリングおよび保護機能を有効にできます。SDN\_IO のハイ状態をオーバーライドするために、SDN\_IO は約 180 $\mu$ A の電流をシンクします。

SDN\_IO が開放状態の場合、ドライバは SPI コマンドで制御されます。SDN\_IO には入力機能と出力機能の両方があります。ユーザは SDN\_IO ピンを駆動して、アンプのイネーブル/ディスエーブルまたは SDN\_IO のモニタリングができます。SDN\_IO が開放状態になってるか、マイクロコントローラの GPIO などの高インピーダンス・デジタル・ピンに接続されている場合、SDN\_IO は内部アラーム状態のいずれかのフラグとして機能します。

SDN\_IO がハイにプルアップされると、AD8460 の HVCC および HVEE 電源の電流は、約 120 $\mu$ A に減少し、内部高電圧ドライバはディスエーブルされます。出力は高インピーダンス (約 27k $\Omega$ ) になります。シャットダウン状態はラッチされ、SDN\_IO が開放状態になってもドライバはシャットダウンしたままになります。AD8460 をシャットダウン状態からイネーブルするには、SDN\_IO をローにプルダウンし、次いで、SDN\_IO を開放状態にしてシャットダウン保護機能を有効化することが必要です。

SDN\_IO がローのままの場合、出力は連続的にイネーブルされ、シャットダウンはできません。この場合、デバイスは過大なストレスから保護されないため、注意が必要です。SDN\_IO をローのままにすると、シャットダウン保護機能は無効化されます。

## 遅延シャットダウン

ユーザは、SDN\_IO とグラウンドの間に外部コンデンサを用いることで AD8460 のシャットダウン応答時間に遅延を加えて、ノイズ耐性を向上できます。目的の遅延時間が、180 $\mu$ A の一定電流下で SDN\_IO の電圧が 0V から閾値電圧 2.5V まで増加するのに必要な時間に等しくなるよう、コンデンサの値を選択します。このコンデンサ値  $C_{SDNIO}$  は、次の関係に従って計算できます。

$$C_{SDNIO} = \frac{(180 \mu A \times t)}{2.5 V}$$

ここで、 $t$  が目的の遅延時間です。

注：選択した遅延は、内部検出されるすべてのアラーム（電流、電圧、温度）に適用されます。

例えば、短時間の電流スパイクまたは電圧スパイクがシャットダウンの原因となるないよう 5 $\mu$ s の遅延を追加するには、SDN\_IO とグラウンドの間に次の値のコンデンサが必要です。

$$C_{SDNIO} = \frac{(180 \mu A \times 5 \mu s)}{2.5 V} = 360 pF$$

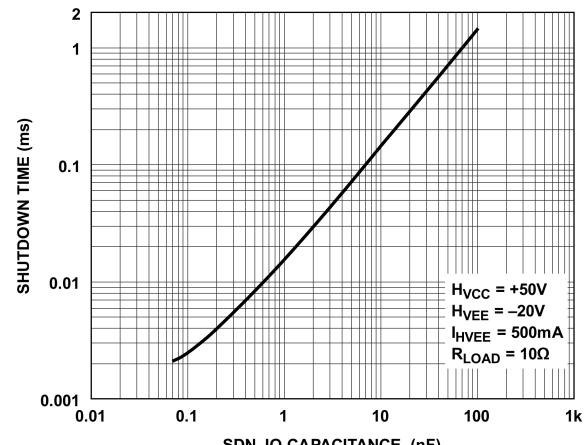

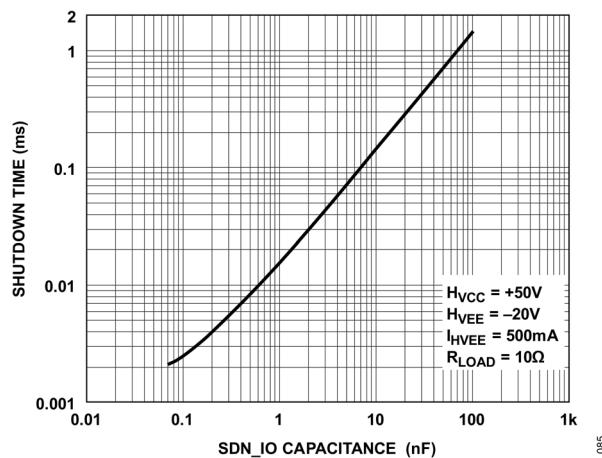

PCB の寄生容量がシャットダウン応答時間に影響する点に注意してください。図 65 に示す値は、SDN\_IO ピンの合計容量で、PCB の寄生容量と追加したコンデンサが含まれます。この例では、5 $\mu$ s より短い時間のアラーム状態はシャットダウンを引き起こしません。図 65 に AD8460 の応答時間と様々な容量の関係を示します。

遅延シャットダウンを実行する場合は、アラームのラッチが特に役立ちます。上述の例では、5 $\mu$ s より短い時間のフォルトはシャットダウンを引き起こしませんが、トラブルシューティングのためにはフォルトの発生が関心の対象となる場合があります。ALARM\_LATCH が真 (1) の場合、イベントが短時間であるためにシャットダウンを引き起こさない場合でも、SPI を介して対応する ALARM フラグの状態をポーリングし、フォルトが発生したかどうかを知ることができます。

図 65. シャットダウン応答時間と様々な  $C_{SDN\_IO}$  の関係

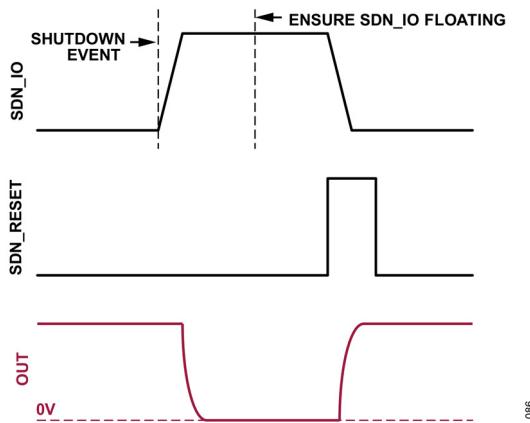

図 66. シャットダウン応答シーケンス

### 手動サーマル・シャットダウン

AD8460 には、SPI 通信やプログラミングを行うことなく、 $T_J = 150^\circ\text{C}$  で手動のサーマル・シャットダウンができるオプション機能が備わっています。この手動シャットダウン機能は、サーマル・シャットダウンに対してのみ有効です。過電流および過電圧保護に対しては、依然として SPI 通信およびプログラミングが必要です。

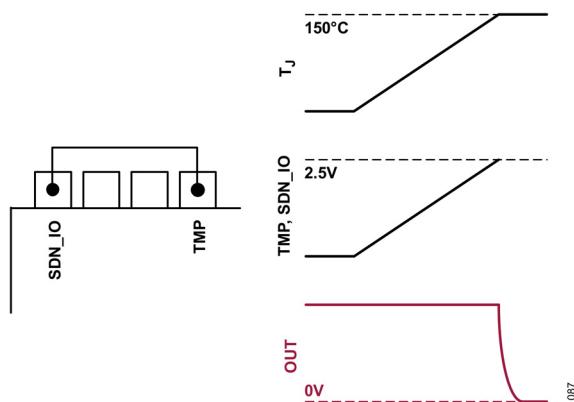

手動サーマル・シャットダウンをイネーブルするには、図 67 に示すように、TMP を直接 SDN\_IO に接続します。この構成では、 $T_J = \text{約 } 150^\circ\text{C}$  となると、TMP ピンのアナログ出力電圧が SDN\_IO のロジック・ハイ閾値に達し、シャットダウン・モードが起動します。AD8460 は、ダイ温度が  $150^\circ\text{C}$  未満に冷却されても自動ではリセットされません。電源または SDN\_IO ピンのシーケンスをやり直すまで、シャットダウンのままとなります。

図 67. 手動サーマル・シャットダウン用の TMP ピンと SDN\_IO ピンの設定

## パワーオン・リセット (POR) およびRESET

AD8460 は、パワーオン時にデジタル・リセットを実行します。パワーオン・リセット (POR) では、AD8460 をパワーオンする間に、すべてのアラーム閾値を含むすべてのデジタル・レジスタをデフォルト値にリセットします。デフォルトでは、パワーオン時には保護システムは無効化されます。アラーム閾値が設定され保護システムが有効になる前にデバイスを動作させる場合は、注意が必要です。デフォルトへのリセットは、SOFT\_RESET レジスタ・ビットを用いることで、任意のタイミングでコマンド指示することもできます。SOFT\_RESET の詳細については表 22 を参照してください。

デフォルトのパワーオン設定は次のとおりです。

- ▶ ドライバ出力はイネーブル

- ▶ 保護システムはディスエーブル

- ▶ 波形生成モードは AWG に設定

- ▶ パターン・メモリには単純なデモ用パターンがロード

- ▶ 公称静止電流

- ▶ DAC はシャットダウン

RESETをローにし、次いでハイにすることで、手動 POR を実行できます。この場合、すべてのデジタル・レジスタはデフォルト値にリセットされます。

## スリープ制御およびその他のレジスタ関連機能

### スリープ制御

HV\_SLEEP : HV\_SLEEP レジスタ (0x00、ビット 4) をローに設定すると、高電圧ドライバがスリープ・モードになります。HVCC および HVEE の電源電流は約  $120\mu\text{A}$  に低下し、OUT は高インピーダンス状態 (約  $27\text{k}\Omega$ ) になります。スリープ・モードは SPI コマンドを介してのみ始動できます。HV\_SLEEP レジスタ・ビットをハイに設定すると、ドライバはアクティブ状態に復帰します。スリープ・モード時は、出力段が高インピーダンスになっていることに注意してください。容量性負荷を駆動する場合、負荷コンデンサの放電に伴って出力電圧がドリフトします。

HVDAC\_SLEEP : このレジスタを用いると、ユーザは HVDAC をシャットダウンして電力を節約できます。VCC\_5V の電源電流は  $10.5\text{mA}$  に低下し、HVCC および HVEE の電源電流は  $120\mu\text{A}$  に低下します。HVDAC\_SLEEP では、スリープ・モードになっているときに HV\_SLEEP の間のみ、中程度の節電を追加することができます。初期パワーオン時または起動時には、HVDAC はデフォルトでスリープ・モードになります。

INHIBIT\_HVDAC\_SHUTDOWN : デフォルトでは、シャットダウンがコマンド指示されている場合、HVDAC は HV ドライバと共にシャットダウンします。INHIBIT\_HVDAC\_SHUTDOWN を用いると、シャットダウン・コマンドがあっても HVDAC をパワーアップ状態に保つオプションが可能になります。

## その他の機能

AD8460 に備わっている、特定のアプリケーションで有用となる可能性のあるその他の機能は次のとおりです。

- ▶ CHIP\_ID : この読み出し専用レジスタには、コード 0x46 が格納されています。

- ▶ DIE\_REV : この 4 ビットの読み出し専用レジスタには、コード 0x4 が格納されています。

## スルー・ブースト

AD8460 の出力アンプは、高速信号の忠実度を向上するために、スルー・ブースト・アキテクチャを採用しています。スルー・ブーストは強度可変のメカニズムで、HV ドライバ内のオペアンプへの入力で検出された瞬時差動電圧に比例して静止電流を増加させます。電圧帰還オペアンプと同様、負帰還を通じて各入力はほぼ等しい値に維持されます。急速に変化する入力に出力が追従できない（帰還ループ機能が一時的に混乱している）場合、各入力の値が一時的に異なり始めます。この差動信号により、電源電流を増加するようスルー・ブースト回路が誘導され、出力のスルーを高速にし、乱れた帰還信号を復元します。

この追加電流は通常 50ns～100ns の間必要ですが、その間の消費電力は著しく増加します。その結果発生する追加自己加熱の量は、信号の動的振る舞いに依存します。例えば、周期が 10μs の 100kHz の方形波では、有効なスルー・ブーストは波形周期の 1% でしかないため、全体的な消費電力の増加はわずかです。

動的な安全動作領域 (SOA) は [安全動作領域 \(SOA\)](#) のセクションに示されています。この動的な SOA は、パルス応答での出力振幅と最大入力／出力周波数の関係を表すものです。スルー・ブーストが頻繁に行われる場合、高周波の方形波が必要となるため、消費電流は急激に増加し、デバイスが動的 SOA の範囲外になってしまう可能性があります。動的 SOA 曲線を拡大するには、温度管理を追加するか入力／出力のエッジ速度を制限します。これによって、スルー・ブースト回路で生成される電流を制限し、内部の消費電力を低減します。

## サーマル・モニタリング (TMP)

AD8460 のダイ温度のモニタリングは、GND を基準として TMP ピンの電圧を測定することで行われます。このピンのアナログ出力電圧はダイ温度に比例しており、次の式を用いて摂氏温度に変換されます。

$$T ({}^{\circ}\text{C}) = \frac{(VTMP - 1.6 \text{ V})}{6 \frac{\text{mV}}{{}^{\circ}\text{C}}}$$

より正確に温度を測定するには、室温で TMP ピンのワンタイム・キャリブレーションを行います。

AD8460 のサーマル・モニタリング機能は、どの過熱シャットダウン閾値とも独立しており、TMP が SDN\_IO に接続されているかどうかに関わらず使用できます。注：TMP を SDN\_IO に接続された状態でモニタする場合、ユーザのモニタリング回路によって高インピーダンスを維持する必要があります。それによって、測定値のロードを行ってもシャットダウン機能と干渉しません。SDN\_IO の高インピーダンスを維持できないと、サーマル・シャットダウンができなくなるため、AD8460 が損傷する可能性があります。

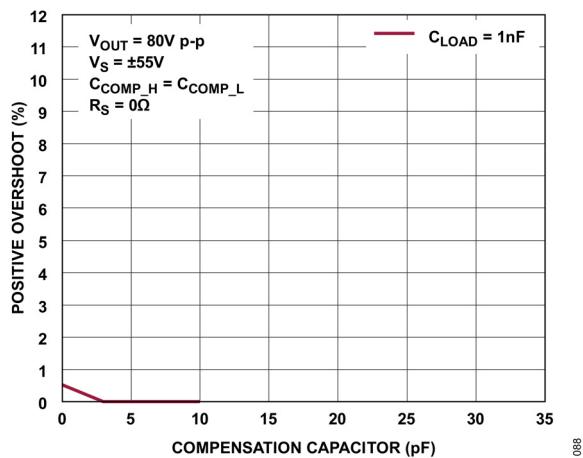

## 出力補償 (COMP\_H および COMP\_L)

COMP\_H ピンと COMP\_L ピンによって、様々な容量性負荷に対するパルス応答を最適化できます。COMP\_H と OUT の間および COMP\_L と OUT の間にコンデンサを配置すると、ステップ応答におけるオーバーシュートを低減できます。補償コンデンサの選択についての詳細は、[図 68](#) および [図 69](#) を参照してください。出力信号のフルスケール範囲に対応するため、これらのコンデンサは高電圧タイプであることが必要です。±50V の公称電源で動作させる場合は 100V 以上のコンデンサを推奨します。電源が±55V に引き上げられると、それに応じて、使用的コンデンサの最低電圧定格は 110V に増加します。

図 68. 大信号パルス応答のオーバーシュートと  $C_{LOAD}$  および  $C_{COMP}$  の関係、正のオーバーシュート図 69. 大信号パルス応答のオーバーシュートと  $C_{LOAD}$  および  $C_{COMP}$  の関係、負のオーバーシュート

## 温度補償 (COMP\_T)

COMP\_T とグラウンドの間には  $0.1\mu\text{F}$  のコンデンサを配置します。この補償コンデンサは、ジャンクション温度モニタとして TMP の出力を安定化するために必要です。

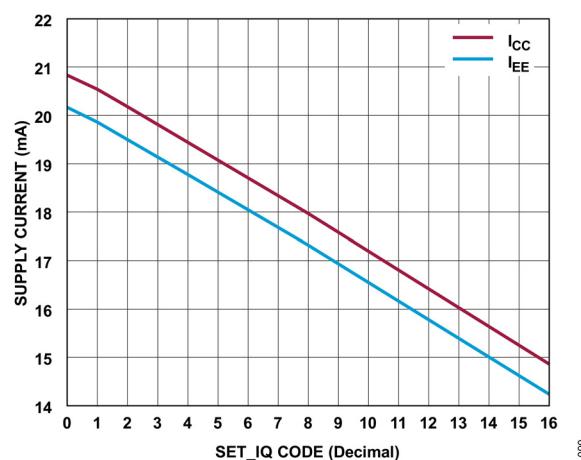

## プログラマブル静止電流

最大の動的性能を必要としないアプリケーションでは、静止消費電流を低減できます。少ない供給電流をプログラムすることで、速度、スルーレート、セトリング・タイム、容量性負荷駆動、およびノイズと引き換えに、消費電力とジャンクション温度を低減できます。

この機能は CTRL\_REG\_04:SET\_IQ で制御され、供給電流を公称供給電流より上または下に調整することができます。MSB は供給電流の極性を設定します。つまり、0 の場合は供給電流が減少し、1 の場合は供給電流が増加します。それ以外のビット[6:0]は、コード範囲全体にわたり、供給電流の単調ながら非線形の制御を行います。SET\_IQ = 0x00 でデバイスの供給電流は公称値であり、そこからビット[6:0]を制限値である SET\_IQ = 0x7F まで増加させることができます。その時点で、デバイスの供給電流がゼロとなり、静止電流のないシャットダウン状態となります。SET\_IQ = 0x80 でデバイスの供給電流は再度公称値になり、そこからビット[6:0]を SET\_IQ = 0xFF まで増加させることができます。この時点でデバイスは公称供給電流の約 2 倍になります。供給電流を増加したことによる熱の影響を考慮すると、供給電流を増加する場合には、特別に大きな注意が必要です。この場合、自己加熱によりジャンクション温度が増加する可能性があり、適切にモニタする必要があります。

図 70. 静止電流とコードの関係

## アプリケーション情報

## 温度管理

## PCB の熱設計

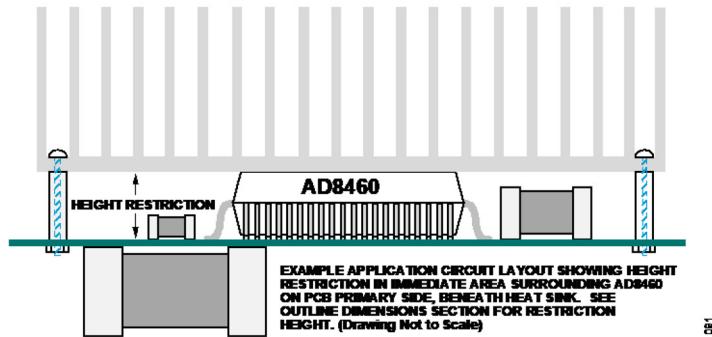

EPADを上向きに配置したAD8460の革新的なパッケージは、PCBレイアウトにおける温度管理上の制約を大幅に緩和します。EPADを下向きに配置した一般的なパッケージでは、銅でビアを充填するか、高価な固形のコイン状の銅をPCBに押し付けることで、基板下部にあるヒートシンクへの熱伝導を確保する必要があります。EPADを上向きに配置することで、ヒートシンクをAD8460の上面に取り付けられるため、PCBの二次側の部品スペースを空いた状態にでき、また基板を通じて熱を放散させる必要がなくなります。推奨ヒートシンクをPCBに確実に取り付けるには、4個の小さな取り付け穴が必要で、これらの穴はAD8460の隣接領域の外側に配置されます。PCBの一次側におけるヒートシンク下の領域の部品の高さは、図71に示すように、AD8460の最低高さより低いことが必要です。

図71. ヒートシンク下の部品高さ制限

熱伝導を最大限に高めるには、図71に示すように、高熱伝導性のサーマル・インターフェイス材料(TIM)を用いて、ヒートシンクをEPADに取り付けます。

## 消費電力

デフォルトのヒートシンクを用い、静止状態かつ最大電源電圧の場合、AD8460の消費電力は約2.475Wで、これは、周囲温度より15.84°Cの温度上昇をもたらします。

負荷条件がより大きくなると、ダイ温度の上昇も大きくなります。TMPピンにて $T_J$ を継続的にモニタし、様々な内部消費電力レベルにおいてダイ温度を管理することを推奨します。あるいは、ヒートシンクを用いずに一定の電力レベルで動作させる場合は、22.6°C/Wというパッケージの $\theta_{JA}$ に基づいてダイ温度を推定することもできます。AD8460の熱的なセットアップがヒートシンクを用いるものである場合、ジャンクションと周囲の間の熱抵抗 $\theta_{JA\_SYSTEM}$ は(推奨ヒートシンクのWakefield-Vette P/N 518-95ABおよびヒートシンク・コンパウンドTIM GC ElectronicsタイプZ9を用いた場合)、6.4°C/Wになります。次の式は、指定された消費電力および周囲温度でのジャンクション温度を計算するために用いる基本式です。

$$T_J = \theta_{JA\_SYSTEM} * P_{DISS} + T_A$$

例えば、EVAL-AD8460SDZのサーマル・スタックアップにヒートシンクとTIMを用い、周囲温度が25°Cで内部消費電力が10Wの場合、予想される $T_J$ の到達温度は次のとおりです。

$$25\text{ }^{\circ}\text{C} + (6.4\text{ }^{\circ}\text{C}/\text{W} \times 10\text{ W}) = 89\text{ }^{\circ}\text{C}$$

内部消費電力を約19.5Wにすると、自然対流下でデフォルトのヒートシンクを用いた場合、 $T_J$ が最大定格値である150°Cとなる点に注意してください。

熱抵抗値は、指定消費電力に対しサーマル・スタックアップの一部の温度がどの程度上昇するかを、効果的に示します。以下の式は、サーマル・ペーストおよびヒートシンクを用いたサーマル・スタックアップに対する、ジャンクションと周囲の間の熱抵抗を定める基本式です。 $\theta_{JA\_SYSTEM}$  は、ユーザの熱的条件を満たすよう設計する必要があります。ジャンクションとケースの間の熱抵抗 ( $\theta_{JC}$ ) およびサーマル・インターフェイス材料の熱抵抗 ( $\theta_{TIM}$ ) を用いると、必要なヒートシンクの熱抵抗 ( $\theta_{HS}$ ) が次式で計算できます。

$$\theta_{HS} = \left( \frac{T_J - T_A}{P_{DISS}} \right) - (\theta_{JC} + \theta_{TIM})$$

$$\theta_{JA\_SYSTEM} = \theta_{HS} + \theta_{JC} + \theta_{TIM}$$

高いデューティ・サイクルで最大の電力供給を行う高性能アプリケーションでは、アクティブ冷却を行って  $\theta_{JA\_SYSTEM}$  を効果的に減少させ、また、 $T_J$  を継続的にモニタする必要があります。

消費電力の少ないアプリケーションの場合、あるいは強制空冷を用いる場合は、より小さなヒートシンクで十分な場合もあります。

表 12 に、 $T_A = 25^\circ\text{C}$  で評価用ボード EVAL-AD8460SDZ を用いた場合の、様々な条件下での熱抵抗を示します。使用したファンは Sunon Fans EE80251S2-1000U-999 で空気流は 37CFM です。使用したヒートシンクは Wakefield-Vette P/N 518-95AB です。TIM は GC Electronics のタイプ Z9 ヒートシンク・コンパウンドです。

表 12. EVAL-AD8460SDZ の様々なサーマル・スタックアップに対する  $\theta_{JA\_SYSTEM}$

| Heatsink | Air flow | $\theta_{JA\_SYSTEM}$ (°C/W) |

|----------|----------|------------------------------|

| No       | No       | 22.6                         |

| Yes      | No       | 6.4                          |

|          | Yes      | 4.4                          |

## 安全動作領域

安全動作領域 (SOA) は、様々な条件下でのデバイスの電力処理能力を表すものです。AD8460 は、主にスルーブースト回路と出力段で電力を消費します。SOA 曲線は、PCB、ヒートシンク、気流、周囲温度などの設計条件によって異なります。更に、すべての SOA 曲線はダイの高熱部に関連してディレーティングされます。通常、電力はデバイスのダイ全体にわたり均一に消費されると仮定しますが、実際には、電力はアプリケーションに応じて特定の領域に集中して消費されます。大消費電力アプリケーションでは、アンプの出力段のトランジスタが負荷駆動時に電力を消費する部分であるため、出力段が一般的に高熱部の存在する場所となります。半導体素子の寿命を確保するため、SOA のグラフを用いて、特定のアプリケーションごとに最適な温度を見積もることを推奨します。公開されている DC SOA 曲線および動的 SOA 曲線の範囲内に確実に収まるように AD8460 を使用し、また、TMP ピンの電圧を用いてジャンクション温度をモニタしてください ( $V_{TMP} \leq 2.5\text{V}$ )。

150°C の最大ジャンクション温度またはその付近で AD8460 を長時間使用すると、熱的なストレスが増大するため、期待される製品寿命が減少する原因となる可能性があります。

様々な構成での AD8460 の熱性能を評価できるよう、AD8460 のシミュレーション用の熱モデルが公開される予定です。

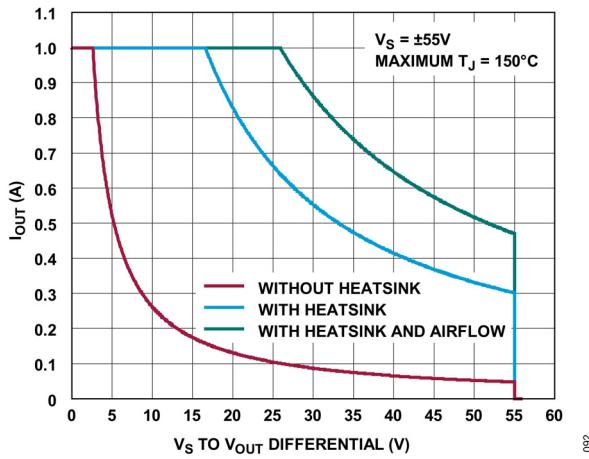

## DC SOA

図 72 は、DC の安全動作領域 (SOA) が、出力電流と出力段の電源電圧差 ( $V_S$  と  $V_{OUT}$  の差) の関係を示す曲線であり、それより下の領域でアンプは安全なジャンクション温度 ( $T_J$ ) で動作できることを示しています。図 72 の曲線より下の領域は、 $T_J \leq 150^\circ\text{C}$  を維持する、AD8460 評価用ボードを使用するための AD8460 の動作領域を示します。

図 72. ヒートシンクを使用しない場合、デフォルトのヒートシンクを使用した場合、デフォルトのヒートシンクとファンを使用した場合の  $T_A = 25^\circ\text{C}$  における DC SOA

すべての試験は、ラボの自然対流下で行われました。いずれの試験事例においても強制空冷を用いると、 $\theta_{JA}$  が低下し、対応する曲線は右上方向に移動し、SOA が拡張します。AD8460 評価用ボードの詳細については、AD8460 ユーザ・ガイドを参照してください。図 72 において、1A を示す横方向の直線は、AD8460 の出力電流駆動です。曲線部では、ジャンクション温度 ( $T_J$ ) が  $150^\circ\text{C}$  以下となる一定の消費電力が維持されます。X 軸は、関連する出力トランジスタで発生する出力段  $V_{CE}$  ( $HVCC - V_{OUT}$  または  $V_{OUT} - HVEE$ ) で、55V の最大  $V_{CE}$  で終了します。

## 動的 SOA

図 73 は、絶対最大温度を超えることなく連続的に生成できる最大方形波振幅を示すもので、指定の容量性負荷と指定のヒートシンクを用いて周波数に対してプロットされています。

図 73. ヒートシンクを使用しない場合、デフォルトのヒートシンクを使用した場合、デフォルトのヒートシンクとファンを使用した場合の、 $C_{LOAD} = 1\text{nF}$ 、 $T_A = 25^\circ\text{C}$  における DC SOA

スルーブーストのセクションで、どのようにして高スルーレート時に AD8460 が著しく大きな動的供給電流を消費するかを説明しています。特定の周波数（負荷に依存）を超えると、絶対最大ジャンクション温度未満にはとどまるものの、上下のフルスケールまでスルーブーストするのに必要な消費電力がデバイスの放散能力を超えます。更なる温度管理を行えば、SOA を拡大できます。

## 負荷が 1nF を超える場合の動的ピーク電流の制限

温度管理のセクションで述べた適切な温度管理を仮定すれば、設計上、AD8460 は連続的に 1A を駆動できます。