## 目次

|                   |    |                  |    |

|-------------------|----|------------------|----|

| 特長                | 1  | デジタル・インターフェース    | 28 |

| アプリケーション          | 1  | ハードウェア・モード       | 28 |

| 概要                | 1  | ソフトウェア・モード       | 29 |

| 機能ブロック図           | 1  | リセット機能           | 29 |

| 改訂履歴              | 2  | ピン機能の概要          | 30 |

| 仕様                | 3  | デジタル・インターフェース    | 31 |

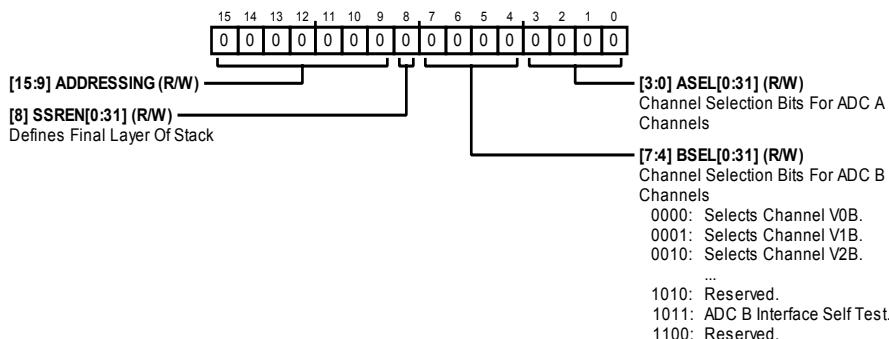

| タイミング仕様           | 6  | チャンネル選択          | 31 |

| 絶対最大定格            | 10 | パラレル・インターフェース    | 32 |

| 熱抵抗               | 10 | シリアル・インターフェース    | 33 |

| ESD に関する注意        | 10 | シーケンサ            | 36 |

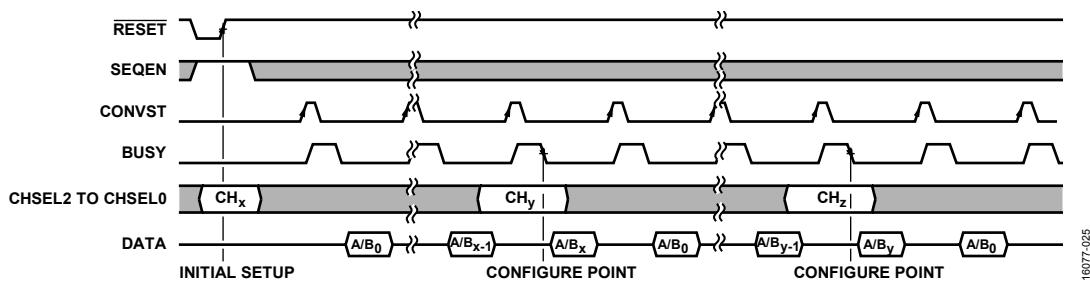

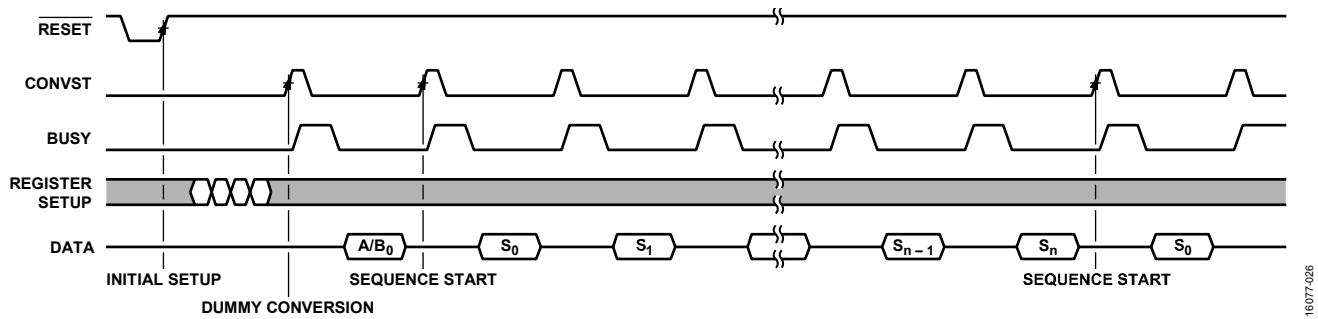

| ピン配置およびピン機能の説明    | 11 | ハードウェア・モード・シーケンサ | 36 |

| 代表的な性能特性          | 15 | ソフトウェア・モード・シーケンサ | 36 |

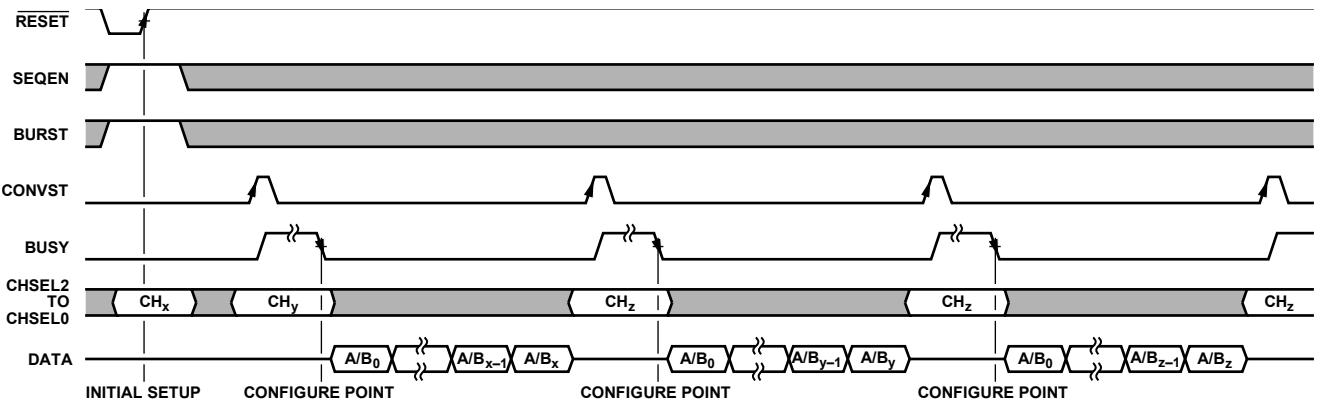

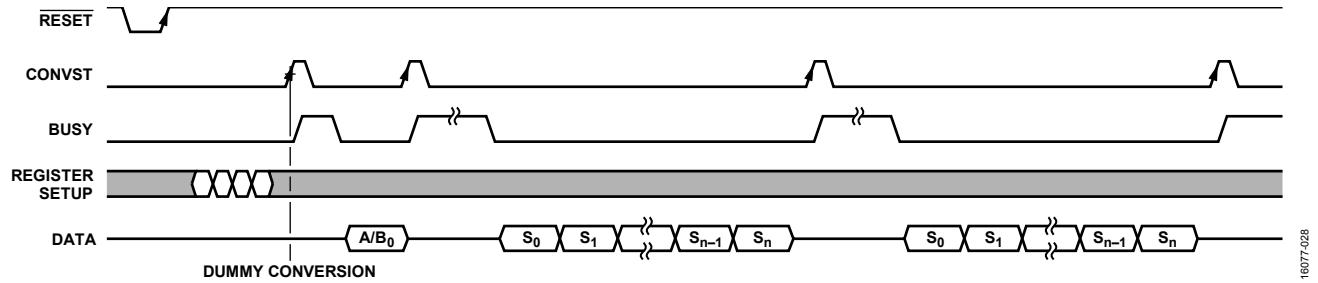

| 用語の定義             | 21 | バースト・シーケンサ       | 37 |

| 動作原理              | 23 | 診断機能             | 39 |

| コンバータの詳細          | 23 | 診断チャンネル          | 39 |

| アナログ入力            | 23 | インターフェース・セルフ・テスト | 39 |

| ADC の伝達関数         | 24 | CRC              | 39 |

| 内部リファレンス／外部リファレンス | 24 | レジスタの一覧          | 41 |

| シャットダウン・モード       | 25 | レジスタのアドレス指定      | 42 |

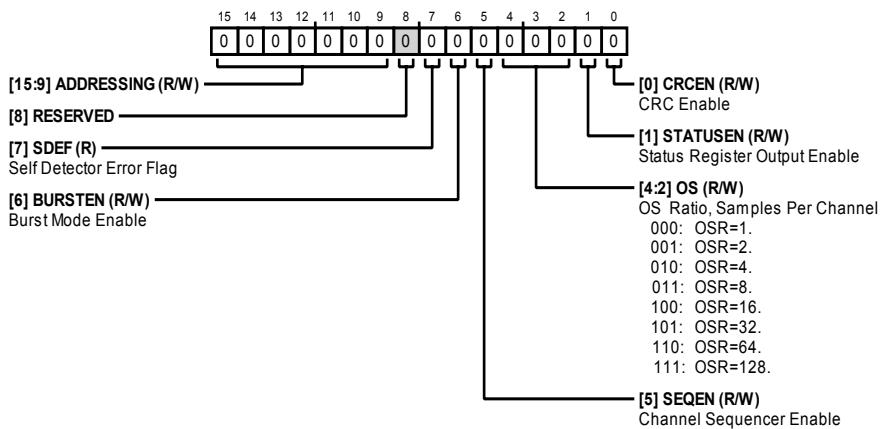

| デジタル・フィルタ         | 25 | 設定レジスタ           | 43 |

| アプリケーション情報        | 26 | チャンネル・レジスタ       | 44 |

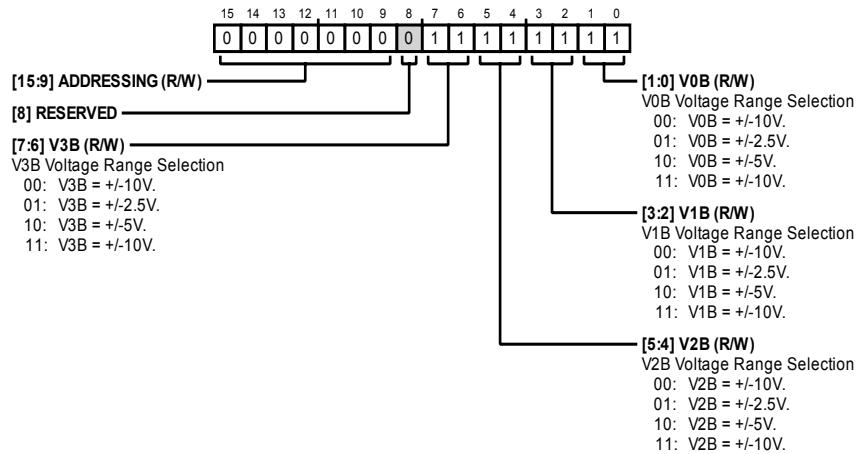

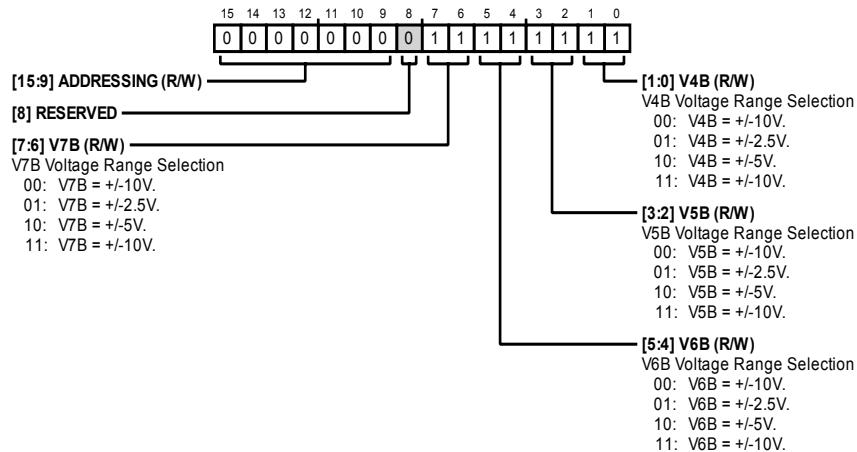

| 機能の概要             | 26 | 入力レンジ・レジスタ       | 45 |

| 電源                | 26 | シーケンサ・スタック・レジスタ  | 49 |

| 代表的な接続            | 26 | ステータス・レジスタ       | 50 |

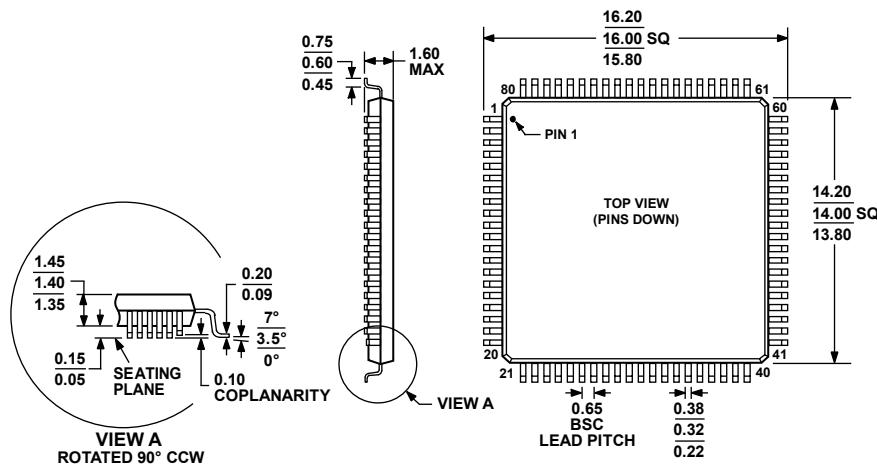

| デバイスの設定           | 28 | 外形寸法             | 51 |

| 動作モード             | 28 | オーダー・ガイド         | 51 |

| 内部リファレンス／外部リファレンス | 28 |                  |    |

## 改訂履歴

7/2017—Revision 0: Initial Version

## 仕様

特に指定のない限り、 $V_{REF} = 2.5$  V 外部／内部、 $V_{CC} = 4.75$  V ~ 5.25 V、 $V_{DRIVE} = 2.3$  V ~ 3.6 V、サンプリング周波数 ( $f_{SAMPLE}$ ) = 1 MSPS、 $T_A = -40$  °C ~ +125 °C。

表 1.

| Parameter                                           | Test Conditions/Comments                                                                                                                                                              | Min  | Typ   | Max   | Unit             |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------------------|

| DYNAMIC PERFORMANCE                                 |                                                                                                                                                                                       |      |       |       |                  |

| Signal-to-Noise Ratio (SNR) <sup>1,2</sup>          | $f_{IN} = 1$ kHz sine wave, unless otherwise noted<br>No oversampling, ±10 V range<br>OSR = 2, ±10 V range, <sup>3</sup> $f_{SAMPLE} = 500$ kSPS<br>OSR = 4, ±10 V range <sup>3</sup> | 84.5 | 85    | 85.3  | dB               |

|                                                     | No oversampling, ±5 V range                                                                                                                                                           | 84   | 84.5  | 85.5  | dB               |

|                                                     | No oversampling, ±2.5 V range                                                                                                                                                         | 83   | 83.5  | 84.5  | dB               |

| Signal-to-Noise-and-Distortion (SINAD) <sup>1</sup> | No oversampling, ±10 V range                                                                                                                                                          | 84   | 84.5  | 85.5  | dB               |

|                                                     | No oversampling, ±5 V range                                                                                                                                                           | 83.5 | 84    | 84.5  | dB               |

|                                                     | No oversampling, ±2.5 V range                                                                                                                                                         | 82.5 | 83.5  | 84.5  | dB               |

| Dynamic Range                                       | No oversampling, ±10 V range                                                                                                                                                          |      | 85.5  |       | dB               |

|                                                     | No oversampling, ±5 V range                                                                                                                                                           |      | 85.1  |       | dB               |

|                                                     | No oversampling, ±2.5 V range                                                                                                                                                         |      | 84.5  |       | dB               |

| Total Harmonic Distortion (THD) <sup>1</sup>        | No oversampling, ±10 V range                                                                                                                                                          |      | -103  | -93.5 | dB               |

|                                                     | No oversampling, ±5 V range                                                                                                                                                           |      | -100  |       | dB               |

|                                                     | No oversampling, ±2.5 V range                                                                                                                                                         |      | -97   |       | dB               |

| Peak Harmonic or Spurious Noise <sup>1</sup>        |                                                                                                                                                                                       |      | -103  |       | dB               |

| Intermodulation Distortion (IMD) <sup>1</sup>       | $f_a = 1$ kHz, $f_b = 1.1$ kHz                                                                                                                                                        |      |       |       |                  |

| Second-Order Terms                                  |                                                                                                                                                                                       |      | -105  |       | dB               |

| Third-Order Terms                                   |                                                                                                                                                                                       |      | -113  |       | dB               |

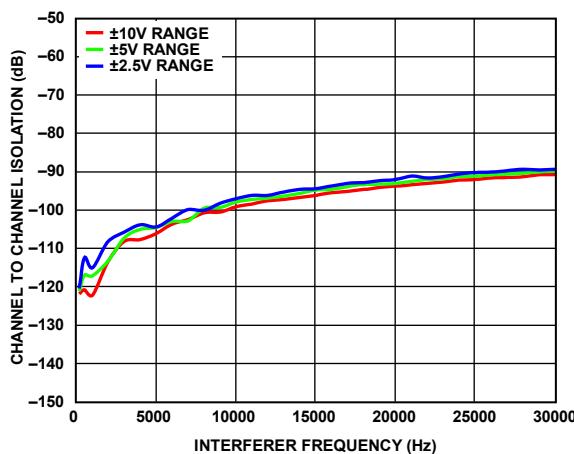

| Channel to Channel Isolation <sup>1</sup>           | $f_{IN}$ on unselected channels up to 5 kHz                                                                                                                                           |      | -106  |       | dB               |

| ANALOG INPUT FILTER                                 |                                                                                                                                                                                       |      |       |       |                  |

| Full Power Bandwidth                                | -3 dB, ±10 V range                                                                                                                                                                    | 39   |       |       | kHz              |

|                                                     | -3 dB, ±5 V/+2.5 V range                                                                                                                                                              | 33   |       |       | kHz              |

|                                                     | -0.1 dB                                                                                                                                                                               | 5.5  |       |       | kHz              |

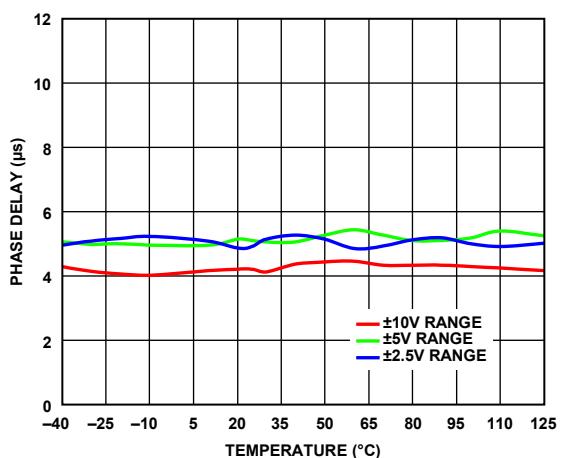

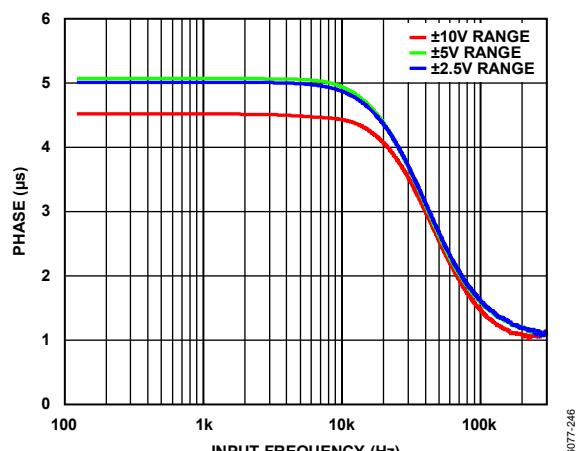

| Phase Delay <sup>1,3</sup>                          | ±10 V range                                                                                                                                                                           | 4.4  | 6     |       | μs               |

|                                                     | ±5 V range                                                                                                                                                                            | 5    |       |       | μs               |

|                                                     | ±2.5 V range                                                                                                                                                                          | 4.9  |       |       | μs               |

| Drift <sup>1,3</sup>                                | ±10 V range                                                                                                                                                                           |      | ±0.55 | +5    | ns/°C            |

| Matching (Dual Simultaneous Pair) <sup>1,3</sup>    | ±10 V range                                                                                                                                                                           | 4.4  | 100   |       | ns               |

|                                                     | ±5 V range                                                                                                                                                                            | 4.7  |       |       | ns               |

|                                                     | ±2.5 V range                                                                                                                                                                          | 4.1  |       |       | ns               |

| DC ACCURACY                                         |                                                                                                                                                                                       |      |       |       |                  |

| Resolution                                          | No missing codes                                                                                                                                                                      | 14   |       |       | Bits             |

| Differential Nonlinearity (DNL) <sup>1</sup>        |                                                                                                                                                                                       |      | ±0.1  | ±0.99 | LSB <sup>4</sup> |

| Integral Nonlinearity (INL) <sup>1</sup>            |                                                                                                                                                                                       |      | ±0.3  | ±1    | LSB              |

| Total Unadjusted Error (TUE)                        | ±10 V range                                                                                                                                                                           |      | ±1.5  |       | LSB              |

|                                                     | ±5 V range                                                                                                                                                                            |      | ±2    |       | LSB              |

|                                                     | ±2.5 V range                                                                                                                                                                          |      | ±2.5  |       | LSB              |

| Positive Full-Scale Error (PFS) <sup>5</sup>        |                                                                                                                                                                                       |      |       |       |                  |

| External Reference                                  | ±10 V range                                                                                                                                                                           |      | ±1.25 | ±8    | LSB              |

|                                                     | ±5 V range                                                                                                                                                                            |      | ±1    |       | LSB              |

|                                                     | ±2.5 V range                                                                                                                                                                          |      | ±0.5  |       | LSB              |

| Internal Reference                                  | ±10 V range                                                                                                                                                                           |      | ±1.25 |       | LSB              |

| Parameter                                         | Test Conditions/Comments                   | Min   | Typ   | Max   | Unit   |

|---------------------------------------------------|--------------------------------------------|-------|-------|-------|--------|

| Drift <sup>3</sup>                                | External reference                         |       | ±2    | ±5    | ppm/°C |

|                                                   | Internal reference                         |       | ±3    | ±10   | ppm/°C |

| Matching <sup>1</sup>                             | ±10 V range                                | 1     | 3     |       | LSB    |

|                                                   | ±5 V range                                 | 1     |       |       | LSB    |

|                                                   | ±2.5 V range                               | 1     |       |       | LSB    |

| Bipolar Zero Code Error <sup>1</sup>              | ±10 V range                                | ±0.15 | ±2.5  |       | LSB    |

|                                                   | ±5 V range                                 | ±0.2  | ±2.5  |       | LSB    |

|                                                   | ±2.5 V range                               | ±0.7  | ±3.5  |       | LSB    |

| Drift <sup>3</sup>                                | ±10 V range                                | ±1.5  | ±21   |       | µV/°C  |

|                                                   | ±5 V range                                 | ±1    |       |       | µV/°C  |

|                                                   | ±2.5 V range                               | ±0.5  |       |       | µV/°C  |

| Matching <sup>1</sup>                             | ±10 V range                                | ±0.5  | ±2.5  |       | LSB    |

|                                                   | ±5 V range                                 | ±0.75 |       |       | LSB    |

|                                                   | ±2.5 V range                               | ±0.75 |       |       | LSB    |

| Negative Full-Scale (NFS) Error <sup>1,5</sup>    | External reference                         |       |       |       |        |

|                                                   | ±10 V range                                | ±1    | ±8    |       | LSB    |

|                                                   | ±5 V range                                 | ±0.75 |       |       | LSB    |

|                                                   | ±2.5 V range                               | ±1.5  |       |       | LSB    |

|                                                   | Internal reference                         |       |       |       |        |

| Drift <sup>3</sup>                                | ±10 V range                                | ±1    |       |       | LSB    |

|                                                   | External reference                         | ±2    | ±5    |       | ppm/°C |

|                                                   | Internal reference                         | ±4    | ±10   |       | ppm/°C |

| Matching <sup>1</sup>                             | ±10 V range                                | 1     | 3     |       | LSB    |

|                                                   | ±5 V range                                 | 1     |       |       | LSB    |

|                                                   | ±2.5 V range                               | 2     |       |       | LSB    |

| ANALOG INPUT                                      |                                            |       |       |       |        |

| Input Voltage Ranges                              | Software/hardware selectable, ±10 V range  |       |       | ±10   | V      |

|                                                   | Software/hardware selectable, ±5 V range   |       |       | ±5    | V      |

|                                                   | Software/hardware selectable, ±2.5 V range |       |       | ±2.5  | V      |

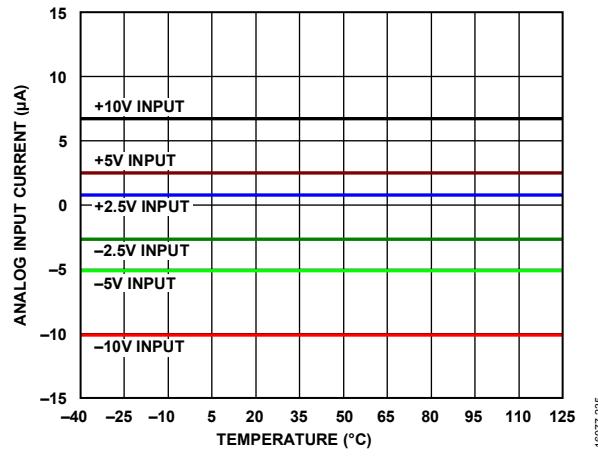

| Analog Input Current                              | ±10 V range, see Figure 34                 |       | ±10.5 |       | µA     |

|                                                   | ±5 V range, see Figure 34                  |       | ±6.5  |       | µA     |

|                                                   | ±2.5 V range, see Figure 34                |       | ±4    |       | µA     |

| Input Capacitance <sup>6</sup>                    |                                            |       | 10    |       | pF     |

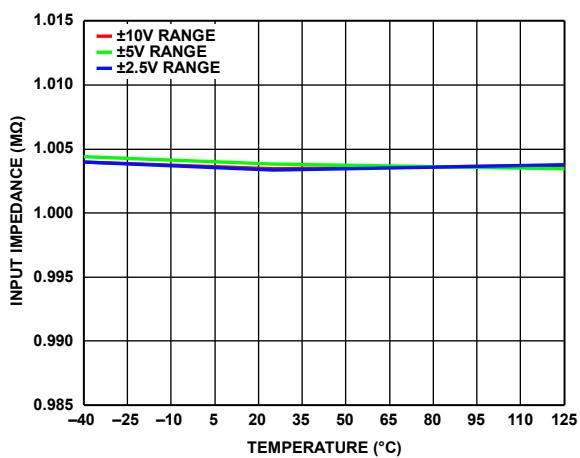

| Input Impedance                                   | See the Analog Input section               | 0.85  | 1     |       | MΩ     |

| Input Impedance Drift <sup>3</sup>                |                                            |       |       | 25    | ppm/°C |

| REFERENCE INPUT/OUTPUT                            |                                            |       |       |       |        |

| Reference Input Voltage Range                     | See the ADC Transfer Function section      | 2.495 | 2.5   | 2.505 | V      |

| DC Leakage Current                                |                                            |       |       | ±1    | µA     |

| Input Capacitance <sup>6</sup>                    | REFSEL = 1                                 |       | 7.5   |       | pF     |

| Reference Output Voltage                          | Measured at REFINOUT                       | 2.495 |       | 2.505 | V      |

| Reference Temperature Coefficient <sup>3</sup>    |                                            | ±2    | ±15   |       | ppm/°C |

| LOGIC INPUTS                                      |                                            |       |       |       |        |

| Input Voltage                                     |                                            |       |       |       |        |

| High (V <sub>INH</sub> )                          | V <sub>DRIVE</sub> = 2.7 V to 3.6 V        | 2     |       |       | V      |

|                                                   | V <sub>DRIVE</sub> = 2.3 V to 2.7 V        | 1.7   |       |       | V      |

| Low (V <sub>INL</sub> )                           | V <sub>DRIVE</sub> = 2.7 V to 3.6 V        |       | 0.8   |       | V      |

|                                                   | V <sub>DRIVE</sub> = 2.3 V to 2.7 V        |       | 0.7   |       | V      |

| Input Current (I <sub>IN</sub> )                  |                                            |       |       | ±1    | µA     |

| Input Capacitance (C <sub>IN</sub> ) <sup>6</sup> |                                            |       | 5     |       | pF     |

| Parameter                                      | Test Conditions/Comments            | Min               | Typ         | Max     | Unit    |

|------------------------------------------------|-------------------------------------|-------------------|-------------|---------|---------|

| LOGIC OUTPUTS                                  |                                     |                   |             |         |         |

| Output Voltage                                 |                                     |                   |             |         |         |

| High ( $V_{OH}$ )                              | $I_{SOURCE} = 100 \mu A$            | $V_{DRIVE} - 0.2$ |             |         | V       |

| Low ( $V_{OL}$ )                               | $I_{SINK} = 100 \mu A$              |                   | 0.4         |         | V       |

| Floating State Leakage Current                 |                                     |                   | $\pm 0.005$ | $\pm 1$ | $\mu A$ |

| Floating State Output Capacitance <sup>6</sup> |                                     |                   | 5           |         | pF      |

| Output Coding                                  | Twos complement                     |                   |             |         |         |

| CONVERSION RATE                                |                                     |                   |             |         |         |

| Conversion Time                                | Per channel pair                    |                   | 0.5         |         | $\mu s$ |

| Acquisition Time                               | Per channel pair                    |                   | 0.5         |         | $\mu s$ |

| Throughput Rate                                | Per channel pair                    |                   | 1           |         | MSPS    |

| POWER REQUIREMENTS                             |                                     |                   |             |         |         |

| $V_{CC}$                                       |                                     | 4.75              | 5.25        |         | V       |

| $V_{DRIVE}$                                    |                                     | 2.3               | 3.6         |         | V       |

| $I_{VCC}$                                      |                                     |                   |             |         |         |

| Normal Mode                                    |                                     |                   |             |         |         |

| Static                                         |                                     | 37                | 57          |         | mA      |

| Operational                                    | $f_{SAMPLE} = 1 \text{ MSPS}$       | 42                | 65          |         | mA      |

| Shutdown Mode                                  |                                     | 28                |             |         | $\mu A$ |

| $I_{DRIVE}$                                    | Digital inputs = 0 V or $V_{DRIVE}$ |                   |             |         |         |

| Normal Mode                                    |                                     |                   |             |         |         |

| Static                                         |                                     | 0.3               | 0.75        |         | mA      |

| Operational                                    | $f_{SAMPLE} = 1 \text{ MSPS}$       | 2.4               | 3.2         |         | mA      |

| Shutdown Mode                                  |                                     | 20                |             |         | $\mu A$ |

| Power Dissipation                              |                                     |                   |             |         |         |

| Normal Mode                                    |                                     |                   |             |         |         |

| Static                                         |                                     | 185               | 300         |         | mW      |

| Operational                                    | $f_{SAMPLE} = 1 \text{ MSPS}$       | 230               | 350         |         | mW      |

| Shutdown Mode                                  |                                     | 0.25              |             |         | mW      |

<sup>1</sup>用語の定義のセクションを参照してください。

<sup>2</sup>オーバーサンプリングを有効にすることで、85.3 dBのS/N比を実現できます。この値は手動モードで有効です。バースト・モードでは、この値が約1 dB低下します。

<sup>3</sup>出荷テストの対象外です。初期リリース時のサンプル・テストにより、適合性が確保されています。

<sup>4</sup> LSBは最下位ビットを意味します。 $\pm 2.5 \text{ V}$ の入力レンジでは、1 LSB =  $305.175 \mu \text{V}$ です。 $\pm 5 \text{ V}$ の入力レンジでは、1 LSB =  $610.351 \mu \text{V}$ です。 $\pm 10 \text{ V}$ の入力レンジでは、1 LSB =  $1.220 \text{ mV}$ です。

<sup>5</sup>内部リファレンスの正と負のフルスケール誤差には、リファレンス誤差は含まれません。

<sup>6</sup>シミュレーション・データによって裏付けられています。

## タイミング仕様

## 共通タイミング仕様

特に指定のない限り、 $V_{CC} = 4.75 \text{ V} \sim 5.25 \text{ V}$ 、 $V_{DRIVE} = 2.3 \text{ V} \sim 3.6 \text{ V}$ 、 $V_{REF} = 2.5 \text{ V}$  外部リファレンス／内部リファレンス、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 。インターフェースのタイミングは、30pFの負荷容量 ( $C_{LOAD}$ ) を使用してテストされ、 $V_{DRIVE}$  とシリアル・インターフェースの負荷容量に依存します（表 15 参照）。

表 2.

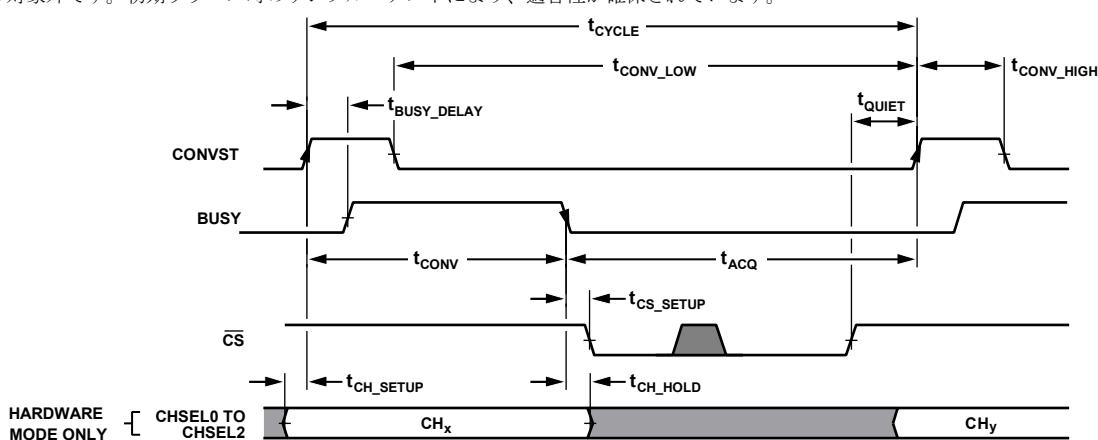

| Parameter <sup>1</sup> | Min  | Typ | Max | Unit | Description                                                                                            |

|------------------------|------|-----|-----|------|--------------------------------------------------------------------------------------------------------|

| $t_{CYCLE}$            | 1    |     |     | μs   | Minimum time between consecutive CONVST rising edges (excluding burst and oversampling modes)          |

| $t_{CONV\_LOW}$        | 50   |     |     | ns   | CONVST low pulse width                                                                                 |

| $t_{CONV\_HIGH}$       | 50   |     |     | ns   | CONVST high pulse width                                                                                |

| $t_{BUSY\_DELAY}$      |      | 32  |     | ns   | CONVST high to BUSY high (manual mode)                                                                 |

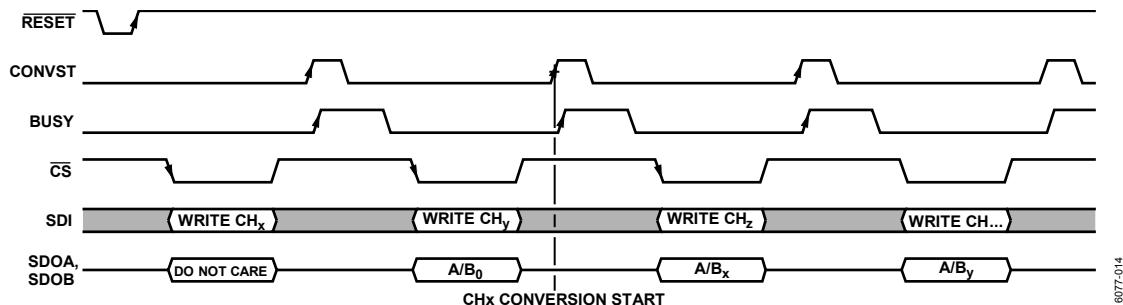

| $t_{CS\_SETUP}$        | 20   |     |     | ns   | BUSY falling edge to $\overline{CS}$ falling edge setup time                                           |

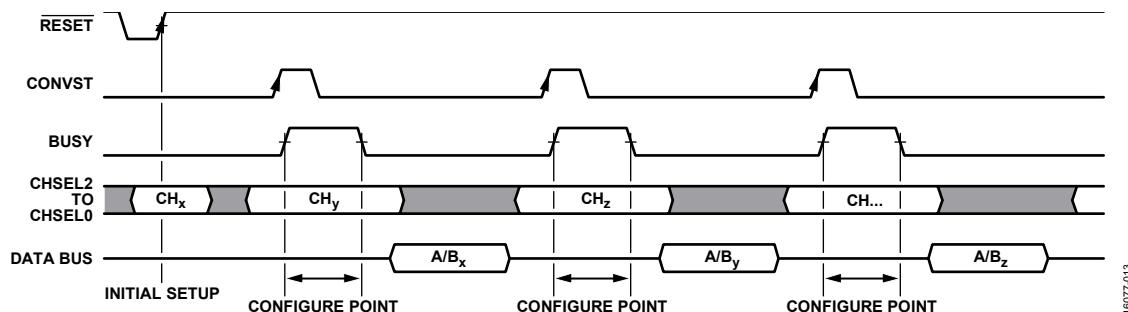

| $t_{CH\_SETUP}$        | 50   |     |     | ns   | Channel select setup time in hardware mode for CHSELx                                                  |

| $t_{CH\_HOLD}$         | 20   |     |     | ns   | Channel select hold time in hardware mode for CHSELx                                                   |

| $t_{CONV}$             | 475  | 520 |     | ns   | Conversion time for the selected channel pair                                                          |

| $t_{ACQ}$              | 480  |     |     | ns   | Acquisition time for the selected channel pair                                                         |

| $t_{QUIET}$            | 50   |     |     | ns   | CS rising edge to next CONVST rising edge                                                              |

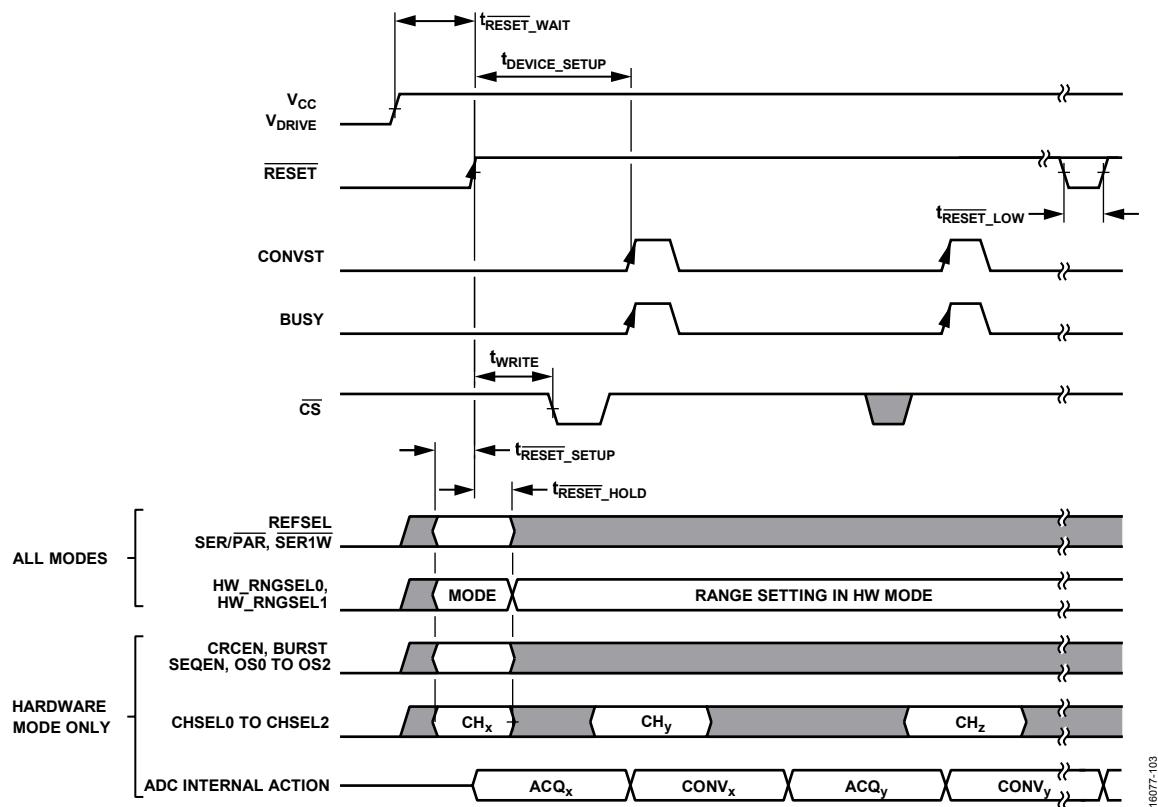

| $t_{RESET\_LOW}$       |      |     |     |      |                                                                                                        |

| Partial Reset          | 40   | 500 |     | ns   | Partial $\overline{RESET}$ low pulse width                                                             |

| Full Reset             | 1.2  |     |     | μs   | Full $\overline{RESET}$ low pulse width                                                                |

| $t_{DEVICE\_SETUP}$    |      |     |     |      |                                                                                                        |

| Partial Reset          | 50   |     |     | ns   | Time between partial $\overline{RESET}$ high and CONVST rising edge                                    |

| Full Reset             | 15   |     |     | ms   | Time between full $\overline{RESET}$ high and CONVST rising edge                                       |

| $t_{WRITE}$            |      |     |     |      |                                                                                                        |

| Partial Reset          | 50   |     |     | ns   | Time between partial $\overline{RESET}$ high and $\overline{CS}$ for write operation                   |

| Full Reset             | 240  |     |     | μs   | Time between full $\overline{RESET}$ high and $\overline{CS}$ for write operation                      |

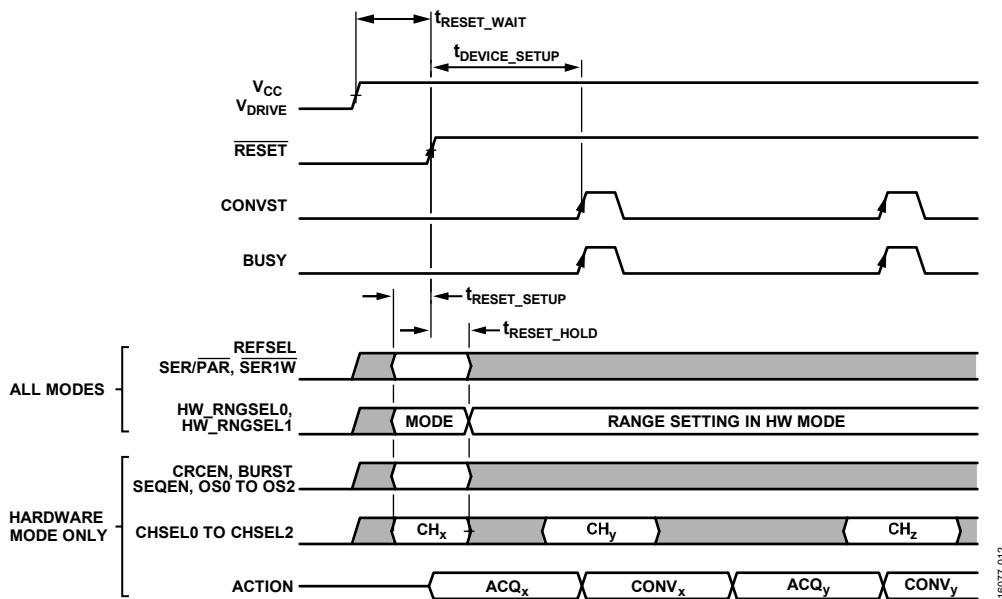

| $t_{RESET\_WAIT}$      | 1    |     |     | ms   | Time between stable $V_{CC}/V_{DRIVE}$ and release of $\overline{RESET}$ (see 図 51)                    |

| $t_{RESET\_SETUP}$     |      |     |     |      | Time prior to release of $\overline{RESET}$ that queried hardware inputs must be stable for (see 図 51) |

| Partial Reset          | 10   |     |     | ns   |                                                                                                        |

| Full Reset             | 0.05 |     |     | ms   |                                                                                                        |

| $t_{RESET\_HOLD}$      |      |     |     |      | Time after release of $\overline{RESET}$ that queried hardware inputs must be stable for (see 図 51)    |

| Partial Reset          | 10   |     |     | ns   |                                                                                                        |

| Full Reset             | 0.24 |     |     | ms   |                                                                                                        |

<sup>1</sup> 出荷テストの対象外です。初期リリース時のサンプル・テストにより、適合性が確保されています。

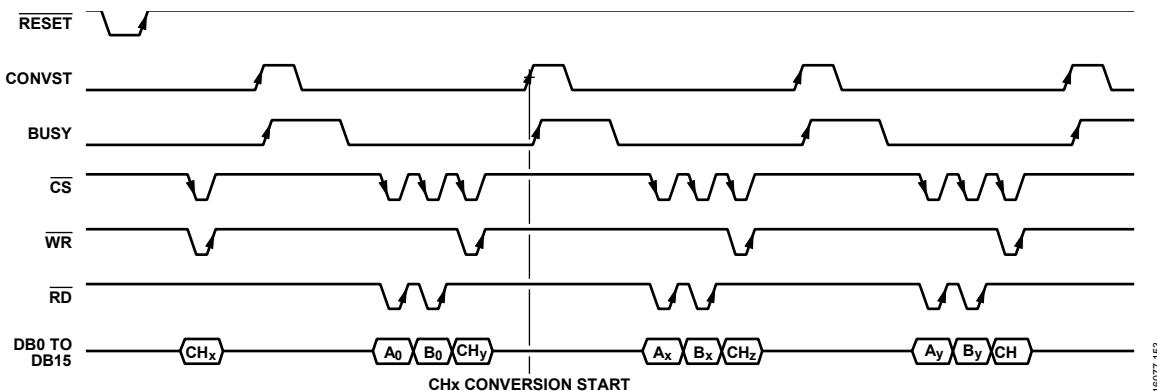

16077-102

図 2. すべてのインターフェースに共通のタイミング図

図 3. リセット・タイミング

## パラレル・モードのタイミング仕様

表 3.

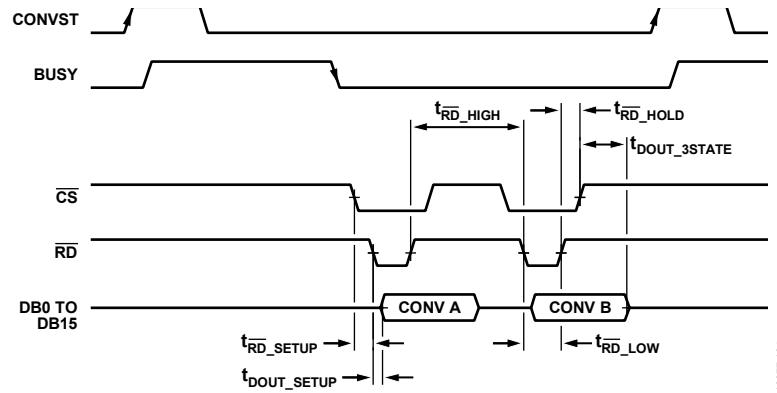

| Parameter          | Min | Typ | Max | Unit | Description                                                          |

|--------------------|-----|-----|-----|------|----------------------------------------------------------------------|

| $t_{RD\_SETUP}$    | 10  |     |     | ns   | CS falling edge to RD falling edge setup time                        |

| $t_{RD\_HOLD}$     | 10  |     |     | ns   | RD rising edge to CS rising edge hold time                           |

| $t_{RD\_HIGH}$     | 10  |     |     | ns   | RD high pulse width                                                  |

| $t_{RD\_LOW}$      | 30  |     |     | ns   | RD low pulse width                                                   |

| $t_{DOUT\_SETUP}$  |     | 30  |     | ns   | Data access time after falling edge of RD                            |

| $t_{DOUT\_3STATE}$ |     | 11  |     | ns   | CS rising edge to DBx high impedance                                 |

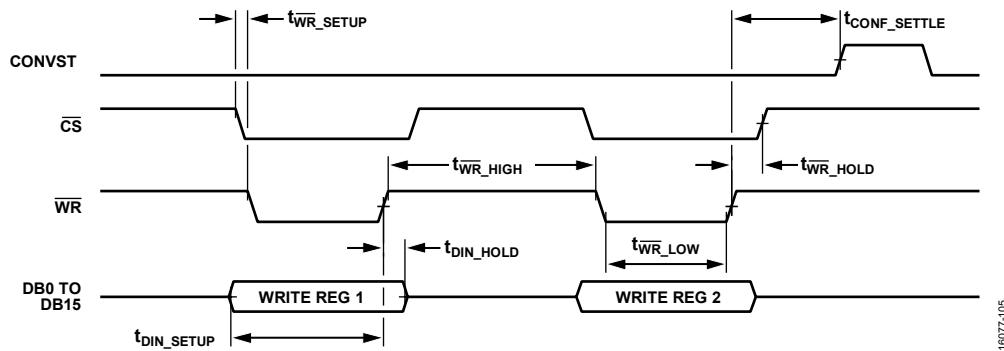

| $t_{WR\_SETUP}$    | 10  |     |     | ns   | CS to WR setup time                                                  |

| $t_{WR\_HIGH}$     | 20  |     |     | ns   | WR high pulse width                                                  |

| $t_{WR\_LOW}$      | 30  |     |     | ns   | WR low pulse width                                                   |

| $t_{WR\_HOLD}$     | 10  |     |     | ns   | WR hold time                                                         |

| $t_{DIN\_SETUP}$   | 30  |     |     | ns   | Configuration data to WR setup time                                  |

| $t_{DIN\_HOLD}$    | 10  |     |     | ns   | Configuration data to WR hold time                                   |

| $t_{CONF\_SETTLE}$ | 20  |     |     | ns   | Configuration data settle time, WR rising edge to CONVST rising edge |

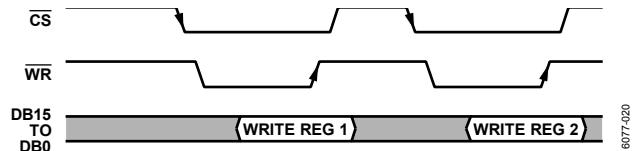

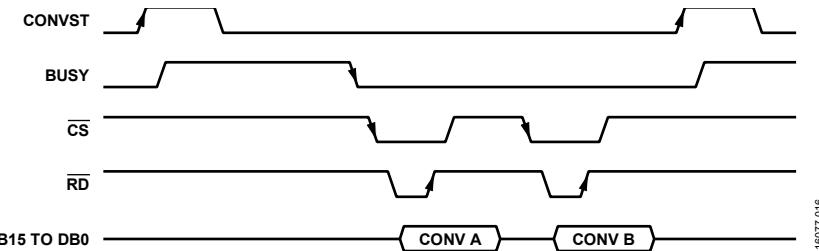

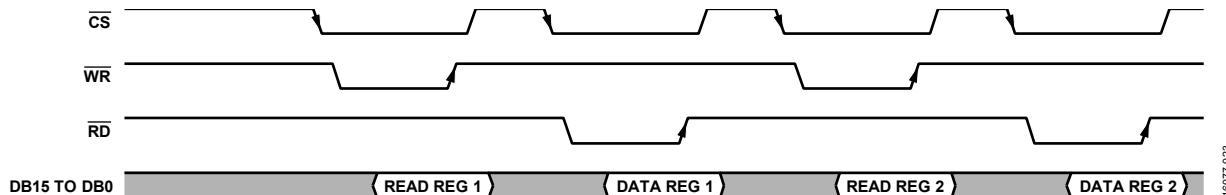

図 4. パラレル読み出しのタイミング図

図 5. パラレル書き込みのタイミング図

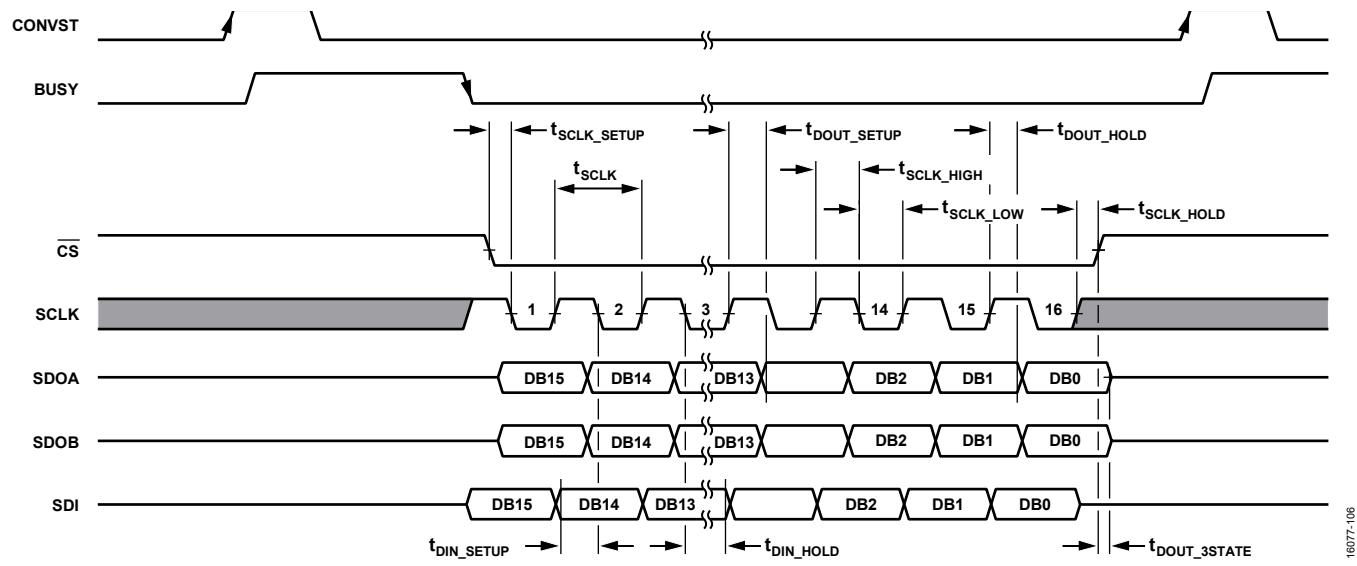

### シリアル・モードのタイミング仕様

表 4.

| Parameter                            | Min                 | Typ   | Max | Unit | Description                                                                 |

|--------------------------------------|---------------------|-------|-----|------|-----------------------------------------------------------------------------|

| f <sub>SCLK</sub> <sup>1</sup>       |                     | 40/50 |     | MHz  | SCLK frequency                                                              |

| t <sub>SCLK</sub>                    | 1/f <sub>SCLK</sub> |       |     |      | Minimum SCLK period                                                         |

| t <sub>SCLK_SETUP</sub> <sup>1</sup> | 10.5                |       |     | ns   | CS to SCLK falling edge setup time, V <sub>DRIVE</sub> above 3 V            |

|                                      | 13.5                |       |     | ns   | CS to SCLK falling edge setup time, V <sub>DRIVE</sub> above 2.3 V          |

| t <sub>SCLK_HOLD</sub>               | 10                  |       |     | ns   | SCLK to CS rising edge hold time                                            |

| t <sub>SCLK_LOW</sub>                | 8                   |       |     | ns   | SCLK low pulse width                                                        |

| t <sub>SCLK_HIGH</sub>               | 9                   |       |     | ns   | SCLK high pulse width                                                       |

| t <sub>DOUT_SETUP</sub> <sup>1</sup> |                     | 9     |     | ns   | Data out access time after SCLK rising edge, V <sub>DRIVE</sub> above 3 V   |

|                                      |                     | 11    |     | ns   | Data out access time after SCLK rising edge, V <sub>DRIVE</sub> above 2.3 V |

| t <sub>DOUT_HOLD</sub>               | 4                   |       |     | ns   | Data out hold time after SCLK rising edge                                   |

| t <sub>DIN_SETUP</sub>               | 10                  |       |     | ns   | Data in setup time before SCLK falling edge                                 |

| t <sub>DIN_HOLD</sub>                | 8                   |       |     | ns   | Data in hold time after SCLK falling edge                                   |

| t <sub>DOUT_3STATE</sub>             |                     | 10    |     | ns   | CS rising edge to SDOx high impedance                                       |

<sup>1</sup> V<sub>DRIVE</sub> と C<sub>LOAD</sub> に依存する (表 15 参照)。

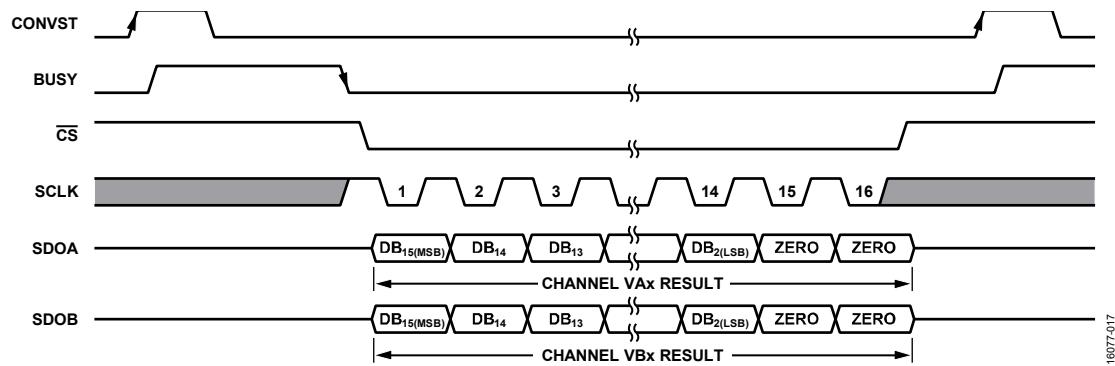

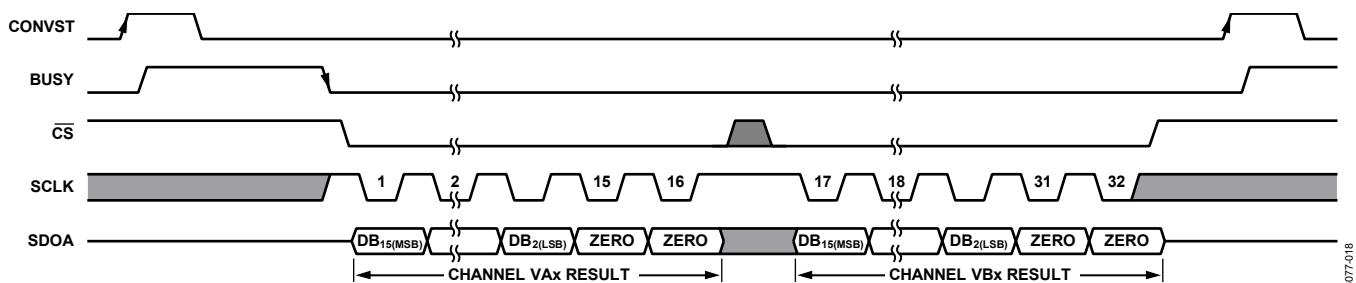

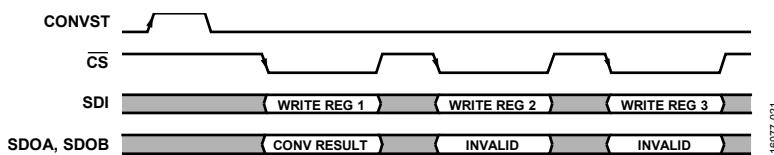

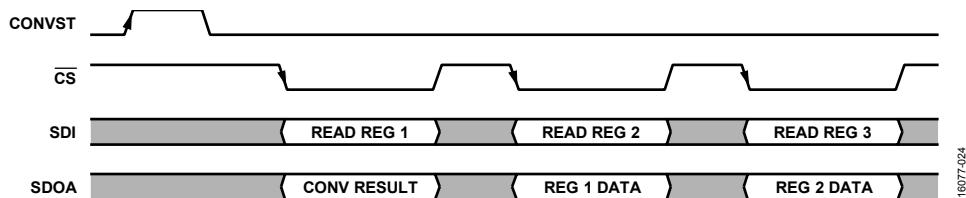

図 6. シリアルのタイミング図

16077-106

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 5.

| Parameter                                             | Rating                        |

|-------------------------------------------------------|-------------------------------|

| $V_{CC}$ to AGND                                      | -0.3 V to +7 V                |

| $V_{DRIVE}$ to AGND                                   | -0.3 V to $V_{CC} + 0.3$ V    |

| Analog Input Voltage to AGND <sup>1</sup>             | $\pm 21$ V                    |

| Digital Input Voltage to AGND                         | -0.3 V to $V_{DRIVE} + 0.3$ V |

| Digital Output Voltage to AGND                        | -0.3 V to $V_{DRIVE} + 0.3$ V |

| REFINOUT to AGND                                      | -0.3 V to $V_{CC} + 0.3$ V    |

| Input Current to Any Pin Except Supplies <sup>1</sup> | $\pm 10$ mA                   |

| Operating Temperature Range                           | -40°C to +125°C               |

| Storage Temperature Range                             | -65°C to +150°C               |

| Junction Temperature                                  | 150°C                         |

| Soldering Reflow                                      |                               |

| Pb/Sn Temperature (10 sec to 30 sec)                  | 240 (+0)°C                    |

| Pb-Free Temperature                                   | 260 (+0)°C                    |

| ESD                                                   |                               |

| All Pins Except Analog Inputs                         | 2 kV                          |

| Analog Input Pins Only                                | 8 kV                          |

<sup>1</sup> 最大 100 mA までの過渡電流では SCR ラッチアップは生じません。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCB の熱設計には、細心の注意が必要です。

$\theta_{JA}$  は、1 立方フィートの密閉容器内で測定される、周囲温度とジャンクション温度の間の熱抵抗です。 $\theta_{JC}$  は、ジャンクション温度とケース温度の間の熱抵抗です。

表 6. 热抵抗

| Package Type         | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|----------------------|---------------|---------------|------|

| ST-80-2 <sup>1</sup> | 41            | 7.5           | °C/W |

<sup>1</sup> 热抵抗のシミュレーション値は、JEDEC 2S2P サーマル・テスト・ボードに基づいています。JEDEC JESD51 を参照。

## ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

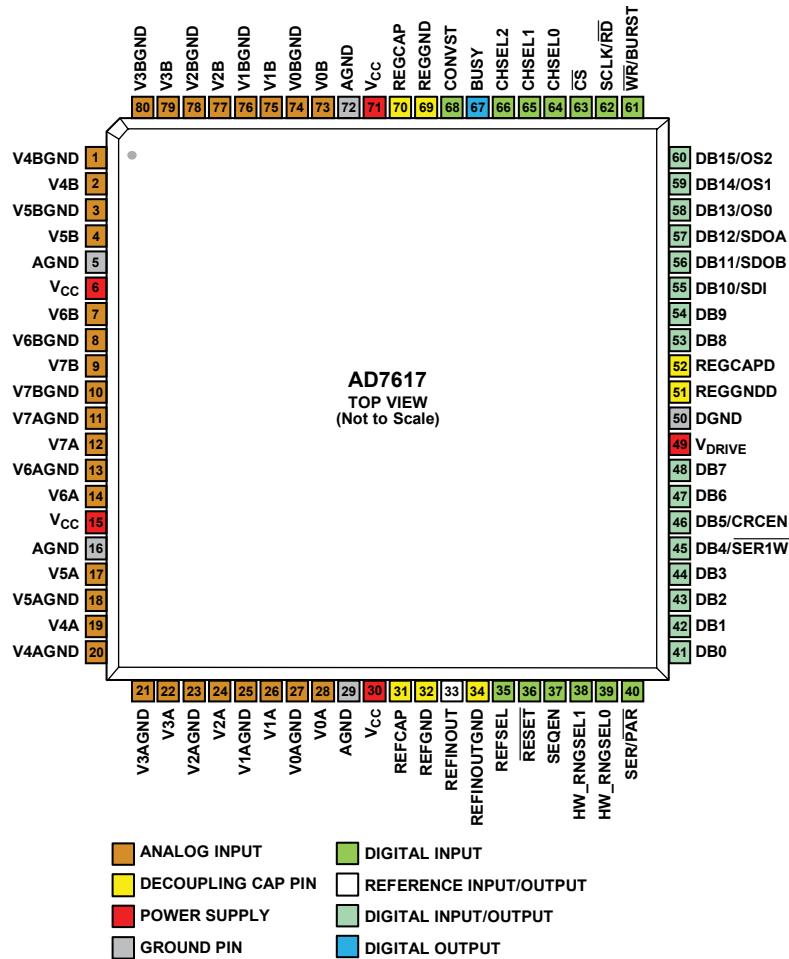

## ピン配置およびピン機能の説明

図 7. ピン配置

16077-005

表 7. ピン機能の説明

| ピン番号             | タイプ <sup>1</sup> | 記号 <sup>2</sup> | 説明                                                                                                                                 |

|------------------|------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1                | AI GND           | V4BGND          | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V4B に対応します。                                                                                          |

| 2                | AI               | V4B             | チャンネル 4、ADC B のアナログ入力                                                                                                              |

| 3                | AI GND           | V5BGND          | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V5B に対応します。                                                                                          |

| 4                | AI               | V5B             | チャンネル 5、ADC B のアナログ入力                                                                                                              |

| 5, 16、<br>29、72  | GND              | AGND            | アナログ電源のグラウンド・ピン                                                                                                                    |

| 6, 15、<br>30, 71 | P                | V <sub>CC</sub> | アナログ電源電圧は 4.75 V ~ 5.25 V です。この電源電圧は、内部フロントエンド・アンプと ADC コアに供給されます。0.1 $\mu$ F と 10 $\mu$ F のコンデンサを並列に接続して、これらのピンを AGND にデカッピングします。 |

| 7                | AI               | V6B             | チャンネル 6、ADC B のアナログ入力                                                                                                              |

| 8                | AI GND           | V6BGND          | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V6B に対応します。                                                                                          |

| 9                | AI               | V7B             | チャンネル 7、ADC B のアナログ入力                                                                                                              |

| 10               | AI GND           | V7BGND          | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V7B に対応します。                                                                                          |

| 11               | AI GND           | V7AGND          | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V7A に対応します。                                                                                          |

| 12               | AI               | V7A             | チャンネル 7、ADC A のアナログ入力                                                                                                              |

| 13               | AI GND           | V6AGND          | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V6A に対応します。                                                                                          |

| 14               | AI               | V6A             | チャンネル 6、ADC A のアナログ入力                                                                                                              |

| 17               | AI               | V5A             | チャンネル 5、ADC A のアナログ入力                                                                                                              |

| 18               | AI GND           | V5AGND          | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V5A に対応します。                                                                                          |

| 19               | AI               | V4A             | チャンネル 4、ADC A のアナログ入力                                                                                                              |

| 20               | AI GND           | V4AGND          | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V4A に対応します。                                                                                          |

| ピン番号            | タイプ <sup>1</sup> | 記号 <sup>2</sup>       | 説明                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21              | AI GND           | V3AGND                | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V3A に対応します。                                                                                                                                                                                                                                                                                                                                                |

| 22              | AI               | V3A                   | チャンネル 3、ADC A のアナログ入力                                                                                                                                                                                                                                                                                                                                                                    |

| 23              | AI GND           | V2AGND                | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V2A に対応します。                                                                                                                                                                                                                                                                                                                                                |

| 24              | AI               | V2A                   | チャンネル 2、ADC A のアナログ入力                                                                                                                                                                                                                                                                                                                                                                    |

| 25              | AI GND           | V1AGND                | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V1A に対応します。                                                                                                                                                                                                                                                                                                                                                |

| 26              | AI               | V1A                   | チャンネル 1、ADC A のアナログ入力                                                                                                                                                                                                                                                                                                                                                                    |

| 27              | AI GND           | V0AGND                | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V0A に対応します。                                                                                                                                                                                                                                                                                                                                                |

| 28              | AI               | V0A                   | チャンネル 0、ADC A のアナログ入力                                                                                                                                                                                                                                                                                                                                                                    |

| 31              | CAP              | REFCAP                | リファレンス・バッファの強制／検出ピン。REFCAP ピンのできるだけ近くに等価直列抵抗 (ESR) の小さな $10\ \mu\text{F}$ の X5R セラミック・コンデンサを配置し、このピンを REFGND にデカッピングしてください。このピンの標準電圧は $4.096\ \text{V}$ です。                                                                                                                                                                                                                              |

| 32              | CAP              | REFGND                | リファレンスのグラウンド・ピン。このピンは AGND に接続します。                                                                                                                                                                                                                                                                                                                                                       |

| 33              | REF              | REFINOUT              | リファレンス入力／リファレンス出力。REFSEL ピンをロジック・ハイに設定した場合は、この REF ピンから $2.5\ \text{V}$ の内部リファレンスを外部で使用できます。逆に、REFSEL ピンをロジック・ローに設定して内部リファレンスをイネーブルにすることで、 $2.5\ \text{V}$ の外部リファレンスをこのピンに印加できます。内部、外部のいずれのリファレンスを選択しても、このピンにはデカッピングが必要です。REFINOUT ピンと REFINOUTGND ピンの間で、REFINOUT ピンのできるだけ近くに $100\ \text{nF}$ の X7R コンデンサを接続します。外部リファレンスを使用する場合は、 $10\ \text{k}\Omega$ の直列抵抗をこのピンに接続し、リファレンス信号を帯域制限します。 |

| 34              | CAP              | REFINOUTGND           | リファレンス入力、リファレンス出力のグラウンド・ピン                                                                                                                                                                                                                                                                                                                                                               |

| 35              | DI               | REFSEL                | 内部リファレンス／外部リファレンスの選択入力。REFSEL はロジック入力です。このピンをロジック・ハイに設定すると、内部リファレンスが選択されイネーブルになります。このピンをロジック・ローにすると、内部リファレンスがディスエーブルになりますので、外部リファレンス電圧を REFINOUT ピンに印加する必要があります。信号状態はフル・リセットの解除時にラッチされ、再設定するには再度フル・リセットする必要があります。                                                                                                                                                                        |

| 36              | DI               | RESET                 | リセット入力。RESET とグラウンドの間に $100\ \mu\text{F}$ 以上の出力コンデンサを接続してください。フル・リセットまたはパーシャル・リセットを選択できます。リセットのタイプは RESET パルスの長さによって決まります。RESET をローに維持すると、デバイスはシャットダウン・モードに移行します。詳細については、リセット機能のセクションを参照してください。                                                                                                                                                                                          |

| 37              | DI               | SEQEN                 | チャンネル・シーケンサ・イネーブル入力（ハードウェア・モードのみ）。SEQEN をローにすると、シーケンサはディスエーブルになります。<br>SEQEN をハイにすると、シーケンサはイネーブルになります（ハードウェア・モードでは機能が制限されます）。詳細については、シーケンサのセクションを参照してください。信号状態はフル・リセットの解除時にラッチされ、再設定するには再度フル・リセットする必要があります。<br>ソフトウェア・モードでは、このピンを DGND に接続する必要があります。                                                                                                                                     |

| 38、39           | DI               | HW_RNGSEL1、HW_RNGSEL0 | ハードウェア／ソフトウェアのモード選択、ハードウェア・モードでのレンジ選択入力。ハードウェア／ソフトウェアのモード選択はフル・リセット時にラッチされます。ハードウェア・モードでのレンジ選択はラッチされません。<br>HW_RNGSELx = 00: ソフトウェア・モード。AD7617 はソフトウェア・レジスタを使用して設定されます。<br>HW_RNGSELx = 01: ハードウェア・モード。アナログ入力レンジは $\pm 2.5\ \text{V}$ 。<br>HW_RNGSELx = 10: ハードウェア・モード。アナログ入力レンジは $\pm 5\ \text{V}$ 。<br>HW_RNGSELx = 11: ハードウェア・モード。アナログ入力レンジは $\pm 10\ \text{V}$ 。                     |

| 40              | DI               | SER/PAR               | シリアル／パラレルのインターフェース選択入力。ロジック入力。このピンをロジック・ローに接続すると、パラレル・インターフェースが選択されます。このピンをロジック・ハイに接続すると、シリアル・インターフェースが選択されます。信号状態はフル・リセットの解除時にラッチされ、再設定するには再度フル・リセットする必要があります。                                                                                                                                                                                                                          |

| 41、42、<br>43、44 | DO/DI            | DB0、DB1、<br>DB2、DB3   | パラレル入出力のデータ・ビット 0 ~ データ・ビット 3。パラレル・モードでは、DB2 が 14 ビットの変換結果の LSB になり、DB0 と DB1 出力がゼロになります。ソフトウェア・パラレル・モードでは、DB0、DB1、DB2、DB3 がレジスタ書き込み／読み出し動作の 4 つの LSB になります。ハードウェア・パラレル・モードでは、DB0 と DB1 をフロート状態のままにするか、 $10\ \text{k}\Omega$ のプルダウン抵抗経由で DGND に接続できます。詳細については、パラレル・インターフェースのセクションを参照してください。シリアル・モードでは、これらのピンを DGND に接続する必要があります。                                                         |

| ピン番号     | タイプ <sup>1</sup> | 記号 <sup>2</sup>                    | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45       | DO/DI            | DB4/SER1W                          | パラレル入出力データ・ビット4／シリアル出力の選択。パラレル・モードでは、このピンは3ステートのパラレル・デジタル入出力ピンとして機能します。詳細については、パラレル・インターフェースのセクションを参照してください。<br>シリアル・モードでは、このピンを使用してシリアル出力を SDOA と SDOB の両方で動作させるか、SDOA でのみ動作させるか決定します。SER1W がローの場合、シリアル出力は SDOA でのみ動作します。SER1W がハイの場合、シリアル出力は SDOA と SDOB の両方で動作します。信号状態はフル・リセットの解除時にラッピングされ、再設定するには再度フル・リセットする必要があります。                                                                                                                           |

| 46       | DO/DI            | DB5/CRCEN                          | パラレル入出力データ・ビット5／巡回冗長性チェック（CRC）イネーブル入力。パラレル・モードでは、このピンは3ステートのパラレル・デジタル入出力として機能します。シリアル・モードでは、このピンはCRCイネーブル入力として機能します。CRCENの信号状態はフル・リセット解除時にラッピングされ、再設定するには再度フル・リセットする必要があります。詳細については、デジタル・インターフェースのセクションを参照してください。<br>シリアル・モードでは、CRCENがローの場合、変換結果の後にCRCワードはありません。CRCENがハイの場合、CHSELxによって設定される最後の変換ワードの後にCRCワードが続きます。詳細については、CRCのセクションを参照してください。                                                                                                      |

| 47、48    | DO/DI            | DB6、DB7                            | ソフトウェア・モードでは、このピンを DGND に接続する必要があります。<br>パラレル入出力のデータ・ビット6およびデータ・ビット7。SER/PAR=0の場合、これらのピンは3ステートのパラレル・デジタル入出力として機能します。詳細については、パラレル・インターフェースのセクションを参照してください。シリアル・モードでは、SER/PAR=1の場合、これらのピンを DGND に接続する必要があります。                                                                                                                                                                                                                                        |

| 49       | P                | V <sub>DRIVE</sub>                 | ロジック電源入力。このピンに供給される電圧（2.3 V～3.6 V）により、インターフェースの動作電圧が決まります。このピンの公称電圧は、ホスト・インターフェースの電源電圧と同じです。0.1 μF と 10 μF のコンデンサを並列に接続して、このピンをデカッピングします。                                                                                                                                                                                                                                                                                                          |

| 50       | GND              | DGND                               | デジタル・グラウンド。このピンは、AD7617 の全デジタル回路に対するグラウンド基準ポイントになります。DGND ピンはシステムの DGND プレーンに接続する必要があります。                                                                                                                                                                                                                                                                                                                                                          |

| 51       | CAP              | REGGNDD                            | REGCAPD（ピン 52）に接続されるデジタル低ドロップアウト（LDO）レギュレータのグラウンド。                                                                                                                                                                                                                                                                                                                                                                                                 |

| 52       | CAP              | REGCAPD                            | 内蔵デジタル・レギュレータの電圧出力に対するデカッピング・コンデンサ・ピン。10 μF のコンデンサを使用して、この出力ピンを REGGNDD へ個別にデカッピングします。このピンの標準電圧は 1.89 V です。                                                                                                                                                                                                                                                                                                                                        |

| 53、54    | DO/DI            | DB8、DB9                            | パラレル入出力のデータ・ビット9およびデータ・ビット8。SER/PAR=0の場合、これらのピンは3ステートのパラレル・デジタル入出力として機能します。詳細については、パラレル・インターフェースのセクションを参照してください。                                                                                                                                                                                                                                                                                                                                   |

| 55       | DO/DI            | DB10/SDI                           | シリアル・モードでは、SER/PAR=1の場合、これらのピンを DGND に接続する必要があります。<br>パラレル入出力データ・ビット DB10／シリアル・データ入力。SER/PAR=0の場合、このピンは3ステートのパラレル・デジタル入出力として機能します。詳細については、パラレル・インターフェースのセクションを参照してください。ハードウェア・シリアル・モードでは、このピンを DGND に接続します。                                                                                                                                                                                                                                        |

| 56       | DO/DI            | DB11/SDOB                          | シリアル・モードでは、SER/PAR=1の場合、このピンは SPI インターフェースのデータ入力として機能します。<br>パラレル入出力データ・ビット11／シリアル・データ出力 B。SER/PAR=0の場合、このピンは3ステートのパラレル・デジタル入出力として機能します。詳細については、パラレル・インターフェースのセクションを参照してください。                                                                                                                                                                                                                                                                      |

| 57       | DO/DI            | DB12/SDOA                          | シリアル・モードでは、SER/PAR=1で DB4/SER1W=1の場合、このピンは SDOB として機能し、シリアル変換データを出力します。<br>パラレル入出力データ・ビット12／シリアル・データ出力 A。SER/PAR=0の場合、このピンは3ステートのパラレル・デジタル入出力として機能します。詳細については、パラレル・インターフェースのセクションを参照してください。                                                                                                                                                                                                                                                        |

| 58、59、60 | DO/DI            | DB13/OS0、<br>DB14/OS1、<br>DB15/OS2 | シリアル・モードでは、SER/PAR=1の場合、このピンは SDOA として機能し、シリアル変換データを出力します。<br>パラレル入出力データ・ビット13、データ・ビット14、データ・ビット15／オーバーサンプリング比の選択。SER/PAR=0の場合、これらのピンは3ステートのパラレル・デジタル入出力として機能します。詳細については、パラレル・インターフェースのセクションを参照してください。                                                                                                                                                                                                                                             |

| 61       | DI               | WR/BURST                           | シリアル・ハードウェア・モードでは、これらのピンでオーバーサンプリングの設定を制御します。信号状態はフル・リセットの解除時にラッピングされ、再設定するには再度フル・リセットする必要があります。詳細については、デジタル・フィルタのセクションを参照してください。<br>ソフトウェア・シリアル・モードでは、これらのピンを DGND に接続する必要があります。<br>書き込み／バースト・モード・イネーブル。<br>ソフトウェア・パラレル・モードでは、このピンがパラレル・インターフェースの WR として機能します。<br>ハードウェアのパラレル・モードまたはシリアル・モードでは、このピンでバースト・モードを有効にします。信号状態はフル・リセットの解除時にラッピングされ、再設定するには再度フル・リセットする必要があります。詳細については、バースト・シーケンサのセクションを参照してください。<br>ソフトウェア・シリアル・モードでは、このピンを DGND に接続します。 |

| ピン番号     | タイプ <sup>1</sup> | 記号 <sup>2</sup>              | 説明                                                                                                                                                                                                                                              |

|----------|------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 62       | DI               | SCLK/RD                      | シリアル・クロック入力/パラレル・データ読み出し制御入力。シリアル・モードでは、このピンがデータ転送用のシリアル・クロック入力として機能します。CS の立ち上がりエッジが発生すると、SDOA と SDOB のデータ出力ラインが 3 ステートから抜け出し、変換結果の MSB がクロック・アウトされます。SCLK の立ち上がりエッジで、後続のすべてのデータ・ビットが SDOA と SDOB のシリアル・データ出力にクロック・アウトされます。                    |

| 63       | DI               | CS                           | パラレル・モードで CS と RD の両方がロジック・ローの場合、出力バスはイネーブルになります。チップ・セレクト。このアクティブ・ローのロジック入力により、データ転送がフレーム化されます。                                                                                                                                                 |

|          |                  |                              | パラレル・モードでは、CS と RD の両方がロジック・ローの場合、DBx 出力バスがイネーブルになり、変換結果がパラレルのデータ・バス・ラインに出力されます。                                                                                                                                                                |

| 64、65、66 | DI               | CHSEL0、<br>CHSEL1、<br>CHSEL2 | シリアル・モードでは、CS によってシリアル読み出し転送がフレーム化され、シリアル出力データの MSB がクロック・アウトされます。                                                                                                                                                                              |

|          |                  |                              | チャンネル選択入力 0 ~ 入力 2。ハードウェア・モードでは、これらの入力によって、チャンネル・グループ A とチャンネル・グループ B の次の変換の入力チャンネルが選択されます。例えば、CHSELx = 0x000 は次回の変換に V0A と V0B を選択し、CHSELx = 0x001 は次回の変換に V1A と V1B を選択します。                                                                   |

| 67       | DO               | BUSY                         | ソフトウェア・モードでは、これらのピンを DGND に接続する必要があります。                                                                                                                                                                                                         |

|          |                  |                              | ビギー出力。このピンは、CONVST の立ち上がりエッジ後にロジック・ハイに遷移し、変換プロセスが開始されたことを示します。現在選択されているチャンネルの変換処理が完了するまで、BUSY 出力はハイを維持します。BUSY の立ち上がりエッジは、変換データが出力データ・レジスタにラッピングされ、読み出しが可能になったことを知らせます。BUSY がローに戻った後でデータを読み出す必要があります。BUSY 信号がハイの間は、CONVST の立ち上がりエッジによる影響はありません。 |

| 68       | DI               | CONVST                       | チャンネル・グループ A とチャンネル・グループ B の変換開始入力。このロジック入力によって、アナログ入力チャンネルの変換が開始されます。                                                                                                                                                                          |

|          |                  |                              | CONVST がローからハイに遷移すると、選択されたアナログ入力ペアに対する変換が開始します。バースト・モードとオーバーサンプリング・モードが無効になっている場合は、CONVST がローからハイに遷移するたびに 1 つのチャンネル・ペアが変換されます。シーケンサ・モードにおいて、バースト・モードまたはオーバーサンプリングが有効になっている場合、必要な変換回数を実行するには、CONVST がローからハイに 1 回だけ遷移する必要があります。                   |

| 69       | CAP              | REGGND                       | 内部アナログ・レギュレータのグラウンド。このピンはシステムの AGND プレーンに接続する必要があります。                                                                                                                                                                                           |

| 70       | CAP              | REGCAP                       | 内部アナログ・レギュレータの電圧出力に対するデカップリング・コンデンサ・ピン。10 $\mu$ F のコンデンサを使用して、この出力ピンを REGGND へ個別にデカップリングします。このピンの標準電圧は 1.87 V です。                                                                                                                               |

| 73       | AI               | V0B                          | チャンネル 0、ADC B のアナログ入力                                                                                                                                                                                                                           |

| 74       | AI GND           | V0BGND                       | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V0B に対応します。                                                                                                                                                                                                       |

| 75       | AI               | V1B                          | チャンネル 1、ADC B のアナログ入力                                                                                                                                                                                                                           |

| 76       | AI GND           | V1BGND                       | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V1B に対応します。                                                                                                                                                                                                       |

| 77       | AI               | V2B                          | チャンネル 2、ADC B のアナログ入力                                                                                                                                                                                                                           |

| 78       | AI GND           | V2BGND                       | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V2B に対応します。                                                                                                                                                                                                       |

| 79       | AI               | V3B                          | チャンネル 3、ADC B のアナログ入力                                                                                                                                                                                                                           |

| 80       | AI GND           | V3BGND                       | アナログ入力のグラウンド・ピン。このピンはアナログ入力ピン V3B に対応します。                                                                                                                                                                                                       |

<sup>1</sup> AI はアナログ入力、GND はグラウンド、P は電源、CAP はデカップリング・コンデンサ、REF はリファレンス入出力、DI はデジタル入力、DO はデジタル出力です。

<sup>2</sup> このデータシートでは、SER/PAR などの複数の機能を備えたピンは、全機能を表すピン名で表記しているか、あるいは SER のように該当する機能のピン名のみで表記しています。

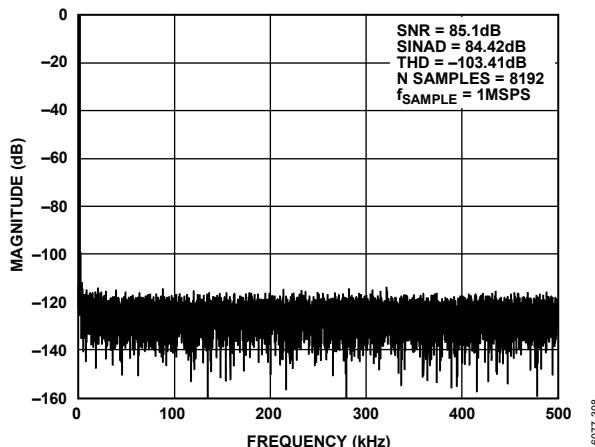

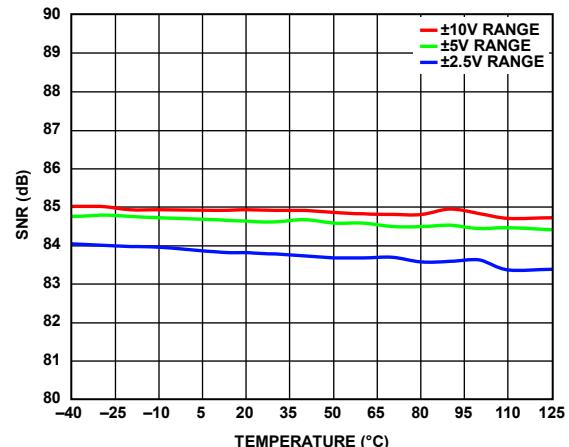

## 代表的な性能特性

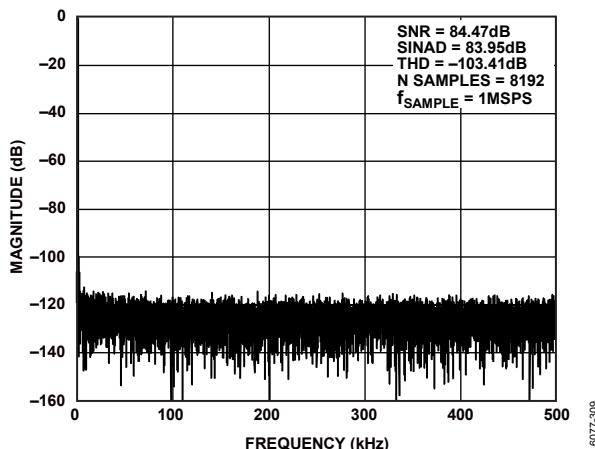

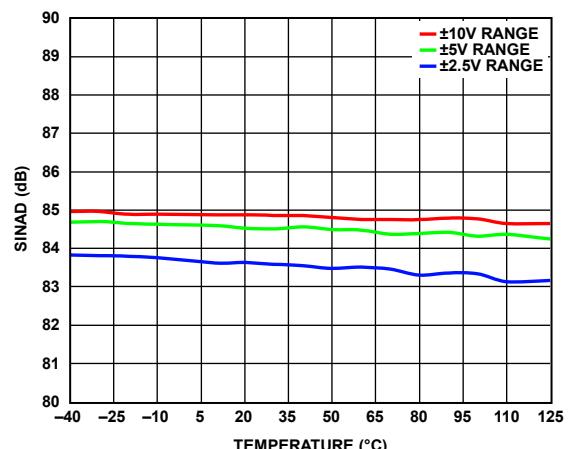

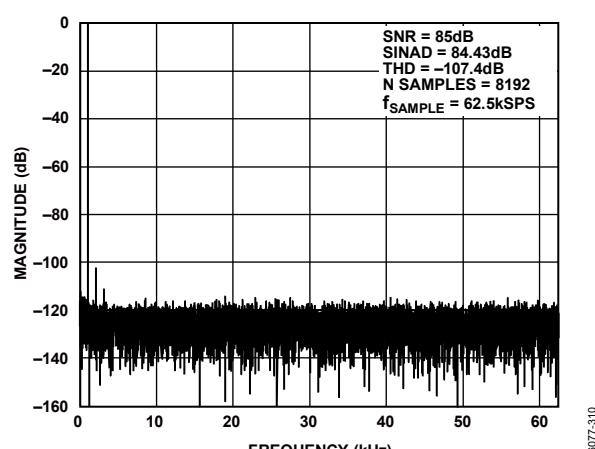

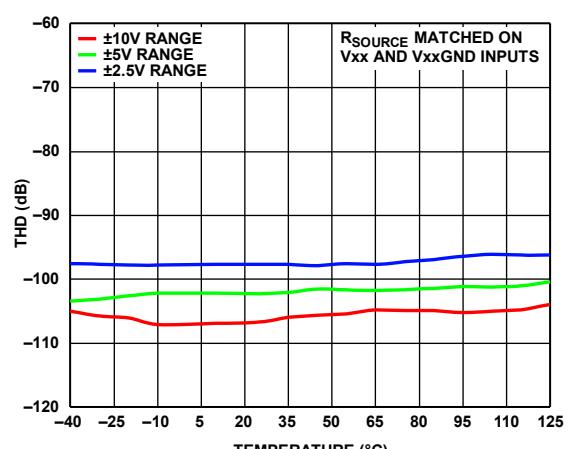

特に指定のない限り、 $V_{REF} = 2.5$  V 内部、 $V_{CC} = 5$  V、 $V_{DRIVE} = 3.3$  V、 $f_{SAMPLE} = 1$  MSPS、 $f_{IN} = 1$  kHz、 $T_A = 25$  °C。

図 8. 高速フーリエ変換 (FFT) 、 $\pm 10$  V レンジ

図 11. SNR と温度の関係

図 9. FFT、 $\pm 5$  V レンジ

図 12. SINAD と温度の関係

図 10. FFT バースト・モード、 $\pm 10$  V レンジ

図 13. THD と温度の関係

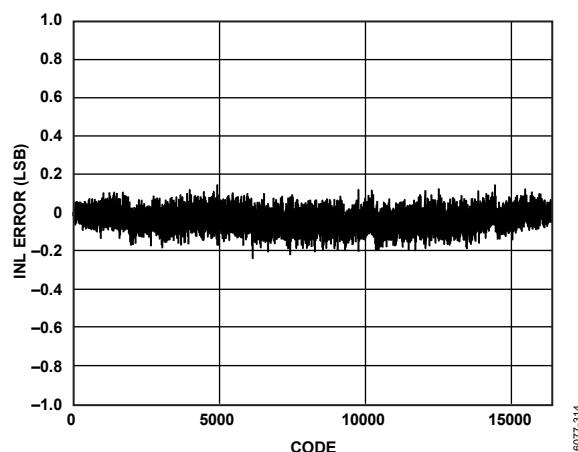

図 14. 標準 INL 誤差、±10 V レンジ

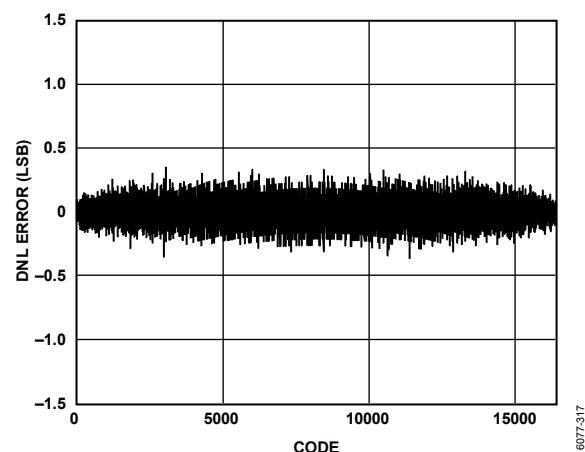

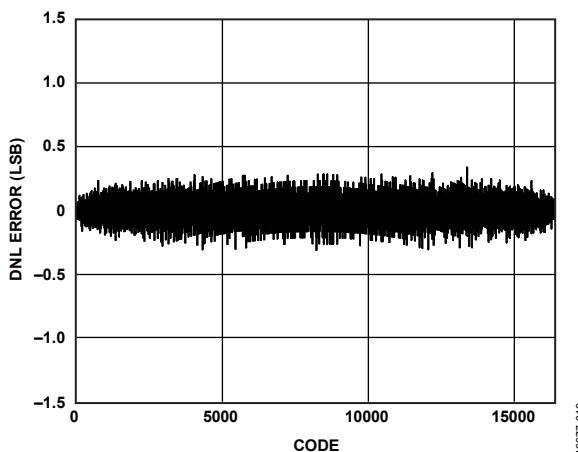

図 17. 標準 DNL 誤差、±5 V レンジ

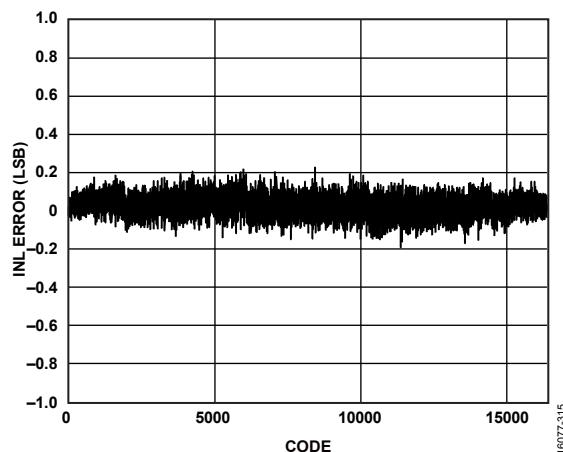

図 15. 標準 INL 誤差、±5 V レンジ

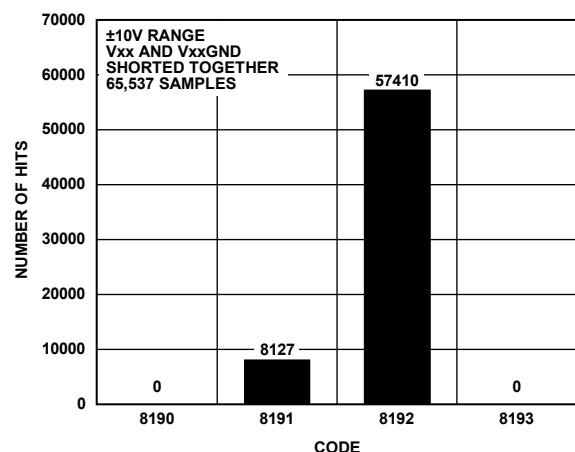

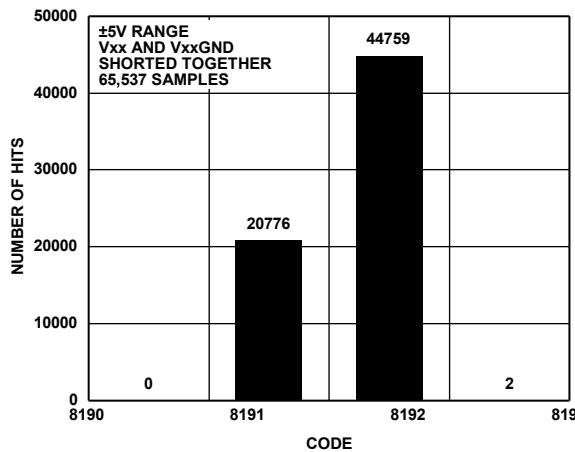

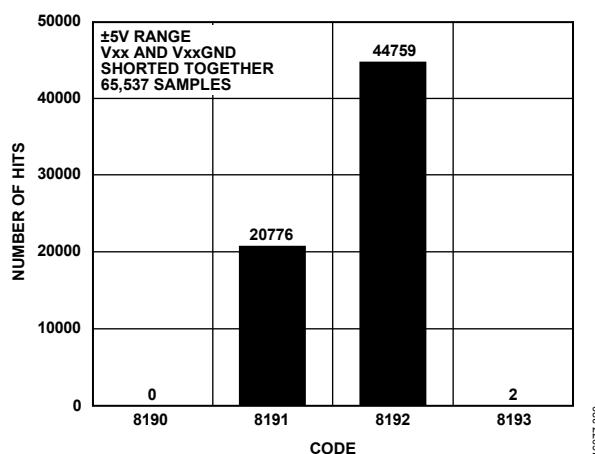

図 18. コード中央値での DC ヒストグラム、±10 V レンジ

図 16. 標準 DNL 誤差、±10 V レンジ

図 19. コード中央値での DC ヒストグラム、±5 V レンジ

図 20. コード中央値での DC ヒストグラム、 $\pm 2.5$  V レンジ

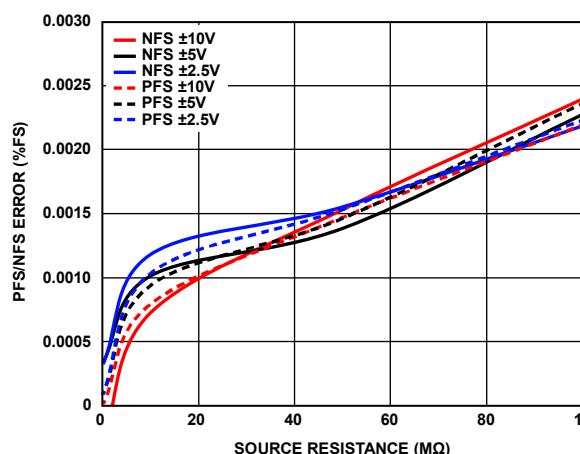

図 23. PFS/NFS 誤差とソース抵抗の関係

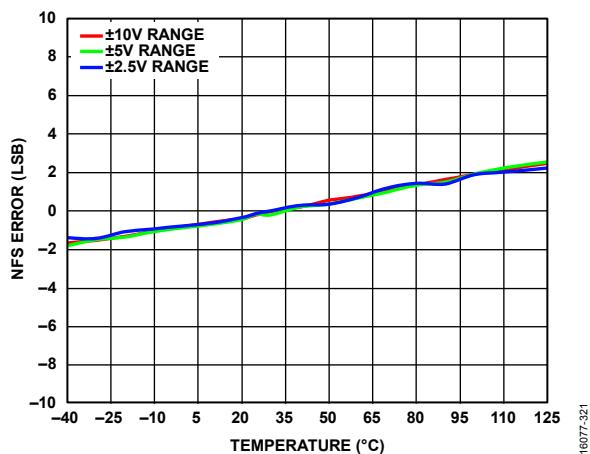

図 21. NFS 誤差と温度の関係

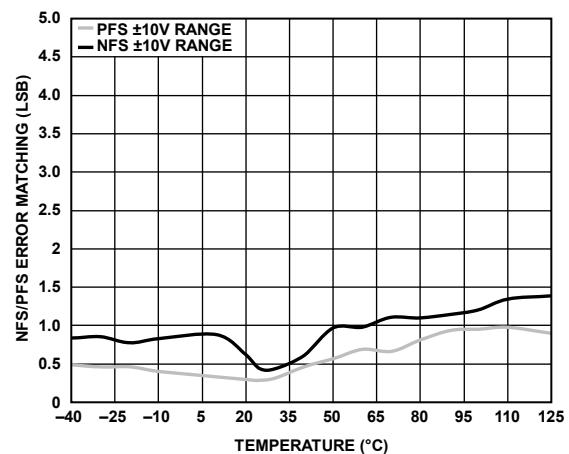

図 24. NFS/PFS 誤差マッチングと温度の関係

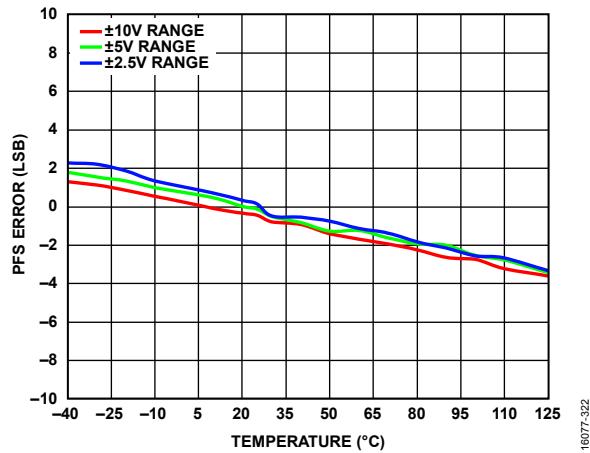

図 22. PFS 誤差と温度の関係

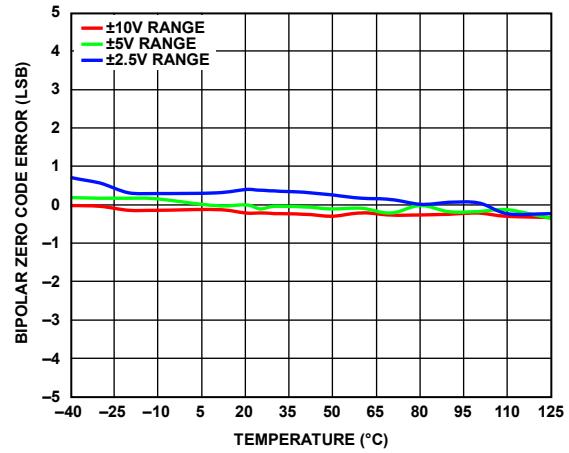

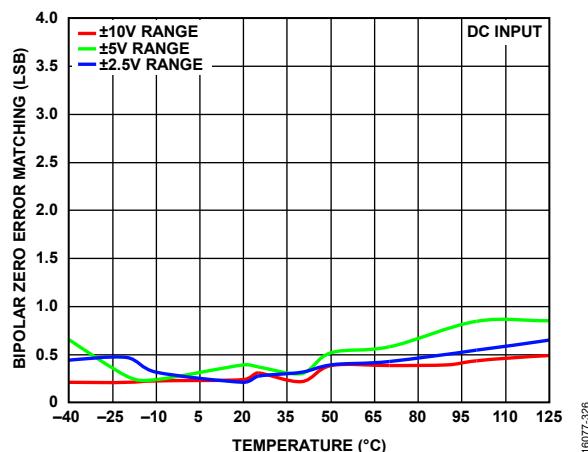

図 25. バイポーラ・ゼロ・コード誤差と温度の関係

図 26. バイポーラ・ゼロ・コード誤差マッチングと温度の関係

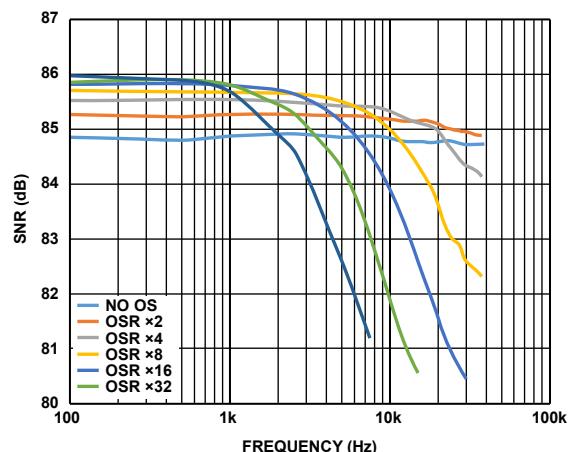

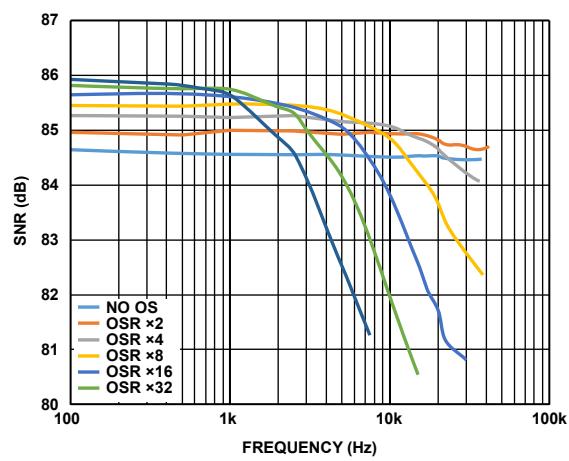

図 29. 各種オーバーサンプリング・レートでの SNR と入力周波数の関係、±10 V レンジ

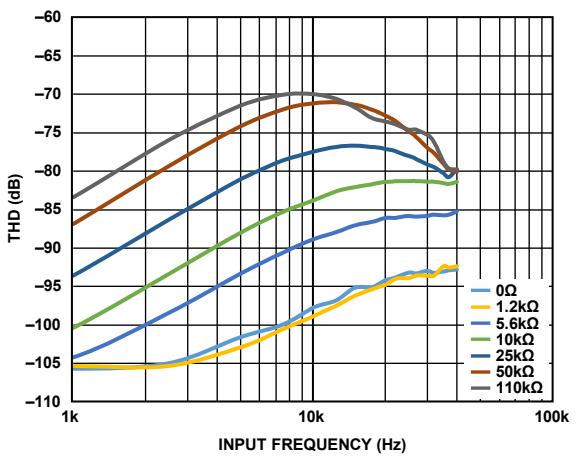

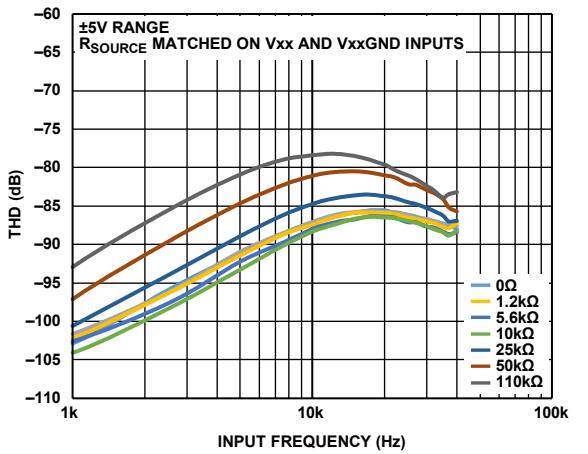

図 27. 各種ソース・インピーダンスでの THD と入力周波数の関係、±10 V レンジ

図 30. 各種オーバーサンプリング・レートでの SNR と入力周波数の関係、±5 V レンジ

図 28. 各種ソース・インピーダンスでの THD と入力周波数の関係、±5 V レンジ

図 31. チャンネル間アイソレーションと干渉周波数の関係

図 32. 位相遅延と温度の関係

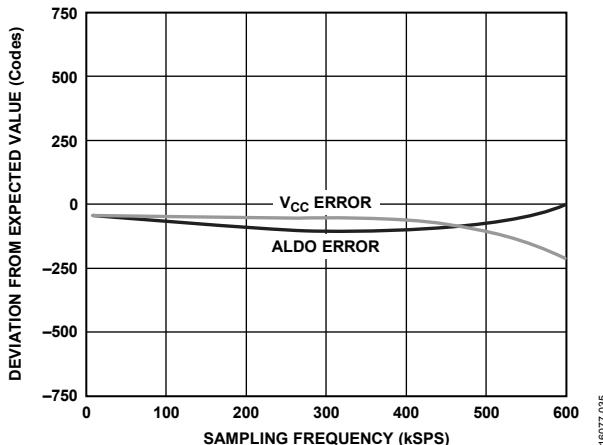

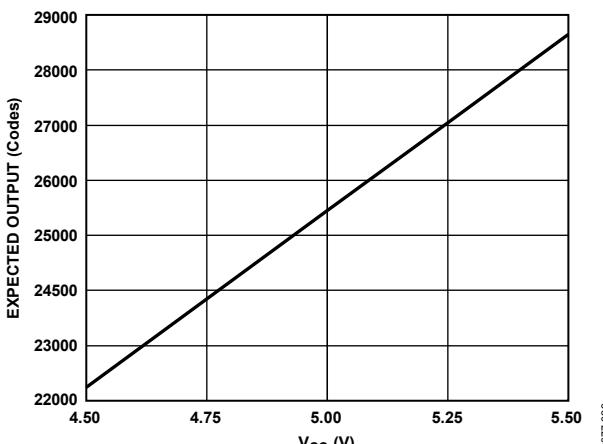

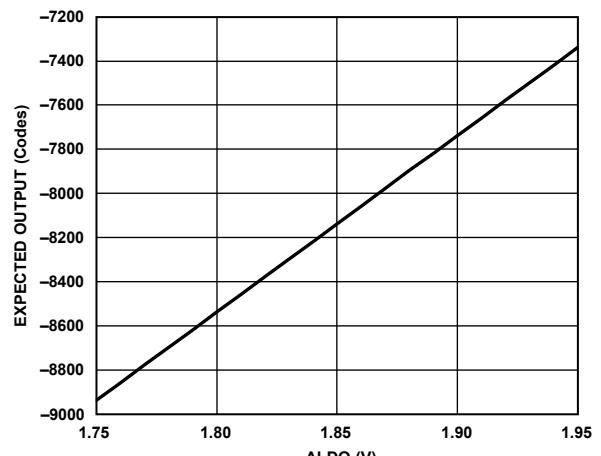

16077-232

図 35. 入力インピーダンスと温度の関係

16077-335

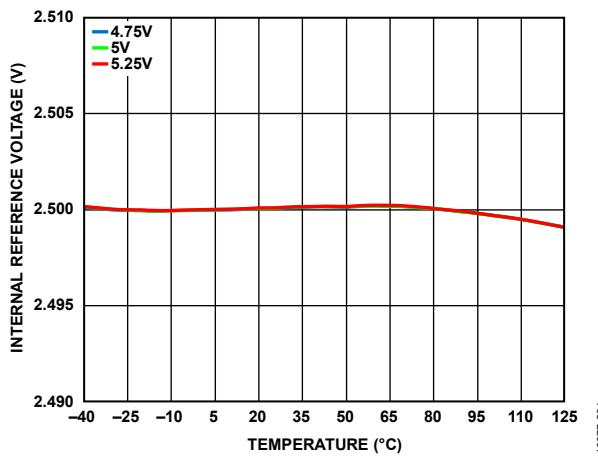

図 33. 各種電源電圧での内部リファレンス電圧と温度の関係

16077-234

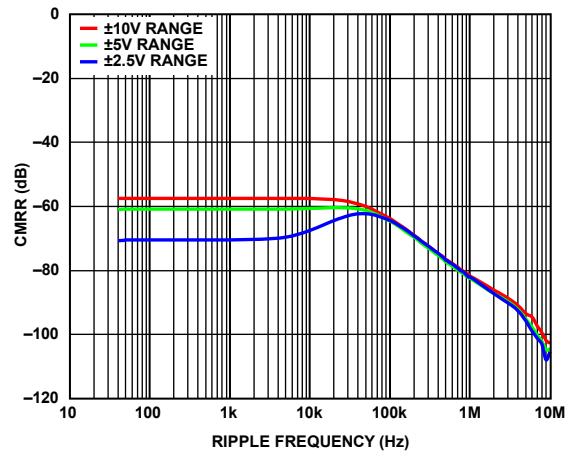

図 36. CMRR 対リップル周波数

16077-237

図 34. 各種電源電圧でのアナログ入力電流と温度の関係

16077-235

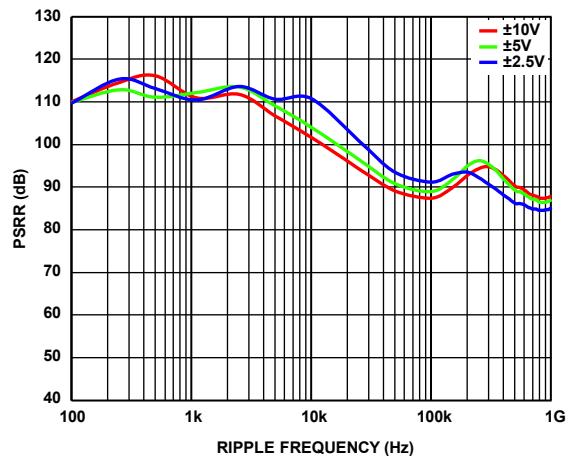

図 37. PSRR とリップル周波数の関係

16077-237

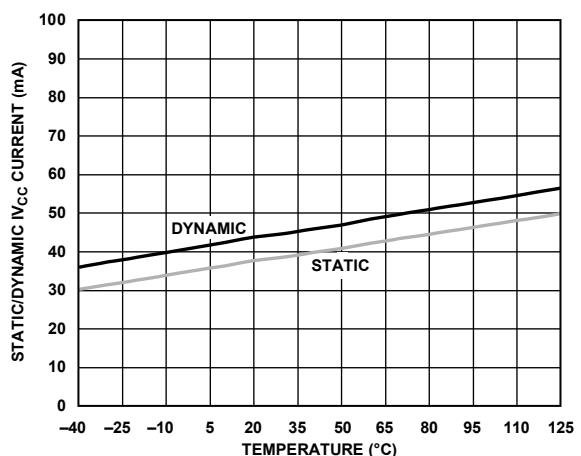

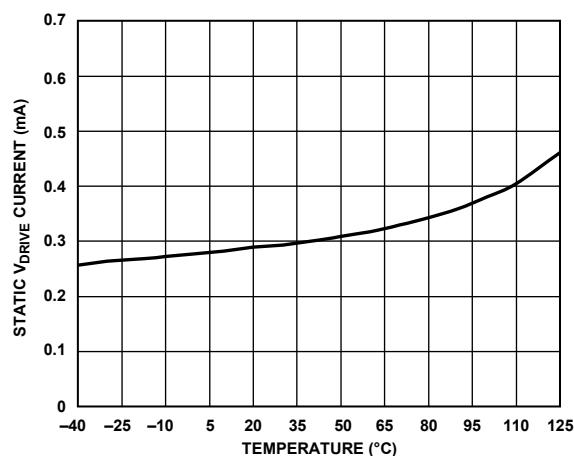

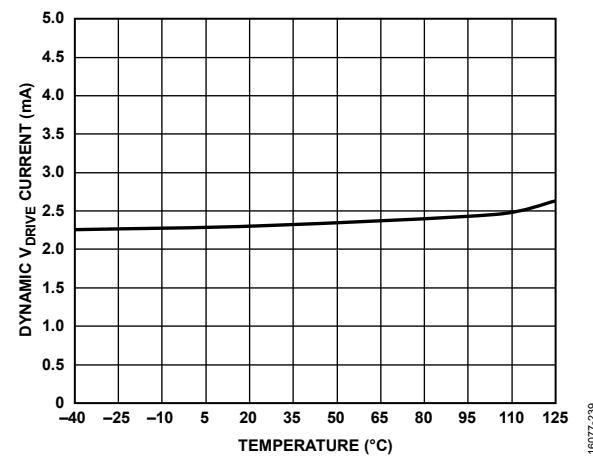

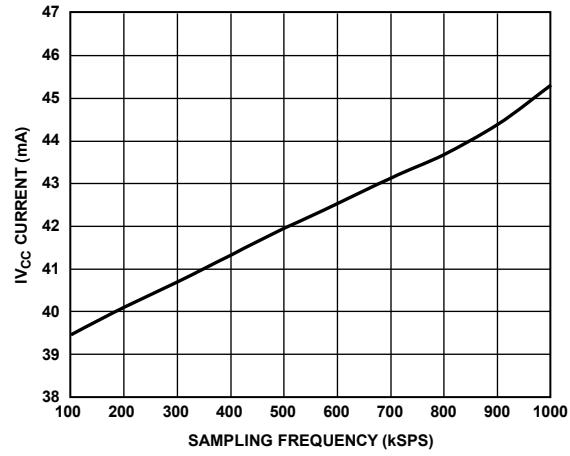

図 38. スタティック／ダイナミック  $V_{CC}$  電流と温度の関係図 40. スタティック  $V_{DRIVE}$  電流と温度の関係図 39. ダイナミック  $V_{DRIVE}$  電流と温度の関係図 41.  $V_{CC}$  電流とサンプリング周波数の関係

## 用語の定義

### 積分非直線性 (INL)

ADC 伝達関数の両端を結ぶ直線からの最大許容誤差です。伝達関数の両端は、ゼロ・スケール(最初のコード遷移より  $\frac{1}{2}$  LSB 下)とフルスケール(最後のコード遷移より  $\frac{1}{2}$  LSB 上)です。

### 微分非直線性 (DNL)

ADC の 2 つの隣接コード間における 1 LSB 変化の測定値と理論値の差です。

### バイポーラ・ゼロ・コード誤差

バイポーラ・ゼロ・コード誤差は(すべて 1 からすべて 0 への)ミッドスケール遷移の理想値からの偏差(0 V -  $\frac{1}{2}$  LSB)です。

### バイポーラ・ゼロ・コード誤差マッチング

バイポーラ・ゼロ・コード誤差マッチングは、2つの入力チャンネル間のバイポーラ・ゼロ・コード誤差の絶対差です。

### 正のフルスケール (PFS) 誤差

正のフルスケール誤差は、バイポーラ・ゼロ・コード誤差の調整後、理想的な最後のコード遷移(10V -  $1\frac{1}{2}$  LSB (9.99954)、5V -  $1\frac{1}{2}$  LSB (4.99977)、2.5V -  $1\frac{1}{2}$  LSB (2.49989))からの実際の最後のコード遷移の偏差です。正のフルスケール誤差には、内部リフレンス・バッファの寄与も含まれます。

### 正のフルスケール誤差マッチング

正のフルスケール誤差マッチングは、2つの入力チャンネル間の正のフルスケール誤差の絶対差です。

### 負のフルスケール (NFS) 誤差

負のフルスケール誤差は、バイポーラ・ゼロ・コード誤差の調整後、理想的な最初のコード遷移(-10 V +  $1\frac{1}{2}$  LSB (-9.99985)、-5 V +  $1\frac{1}{2}$  LSB (-4.99992)、-2.5 V +  $1\frac{1}{2}$  LSB (-2.49996))からの実際の最初のコード遷移の偏差です。負のフルスケール誤差には、内部リフレンス・バッファの寄与も含まれます。

### 負のフルスケール誤差マッチング

負のフルスケール誤差マッチングは、2つの入力チャンネル間の負のフルスケール誤差の絶対差です。

### 信号ノノイズ + 歪み (SINAD)

SINAD は、A/D コンバータ出力での信号対(ノイズ + 歪み)比の測定値です。信号は正弦波の rms 値で、ノイズはサンプリング周波数の  $1/2$  ( $f_s/2$ ) までの非基本波信号の rms 和です(DC 以外の高調波を含む)。

### S/N 比 (SNR)

SNR は、ADC 出力で測定された信号とノイズの比です。信号は基本波の rms 振幅で表します。ノイズは  $1/2$  サンプリング周波数 ( $f_s/2$ ) までの非基本波の総和で表します(DC を除く)。

この比はデジタル化における量子化レベル数に依存し、レベル数が大きいほど、量子化ノイズは小さくなります。正弦波入力の理想的な N ビット・コンバータにおける SNR の理論値は次式で与えられます。

$$S/N \text{ 比} = (6.02N + 1.76) \text{ dB}$$

したがって、14 ビット・コンバータの場合、SNR は 86 dB になります。

### 全高調波歪み (THD)

THD は最初の 5 つの高調波成分の rms 和とフルスケール入力信号の rms 値との比で、デシベル(dB)で表されます。

### ピーク高調波またはスプリアス・ノイズ

基本波 rms 値に対する ADC 出力スペクトル内(DC を除いて  $f_s/2$  まで)で次に大きい成分の rms 値の比。一般に、この値はスペクトルに含まれる最大の高調波によって決まりますが、高調波がノイズ・フロアに埋まっている ADC ではノイズ・ピークによって決まります。

### 相互変調歪み

2つの周波数  $f_a$  と  $f_b$  の正弦波で構成される入力により、あらゆる非線形アクリティブ・デバイスで、 $mfa \pm nfb$ (ここで、 $m, n = 0, 1, 2, 3$ ) の和と差の周波数による歪み積が発生します。相互変調歪み項とは、 $m$  も  $n$  も 0 ではない項です。例えば、2次の項は  $(fa + fb)$  と  $(fa - fb)$  を含み、3次の項は  $(2fa + fb)$ 、 $(2fa - fb)$ 、 $(fa + 2fb)$ 、および  $(fa - 2fb)$  を含みます。

相互変調歪みの計算は THD の仕様に従い、基本波の和の rms 振幅に対する個々の歪み積の rms 総和の比で、デシベル(dB)で表します。

### 電源電圧変動除去比 (PSRR)

電源の変化はコンバータの直線性ではなく、フルスケール遷移に影響を与えます。電源電圧変動除去は、電源電圧の公称値からの変化によるフルスケール遷移点の最大変化量です。PSRR は、フルスケール周波数  $f$  の ADC の出力電力と、ADC の  $V_{CC}$  電源に印加された周波数  $f_s$  の 100 mV p-p 正弦波の電力の比で定義されます。

$$PSRR \text{ (dB)} = 10\log(P_f/P_s)$$

ここで、

$P_f$  は周波数  $f$  の ADC の出力電力に等しくなります。

$P_s$  は  $V_{CC}$  電源にカップリングした周波数  $f_s$  の電力です。

**AC 同相ノイズ除去比 (AC CMRR)**

AC CMRR は、コモンモード電圧  $V_{xx}$  と  $V_{xxGND}$  に印加された周波数  $f_s$  のサイン波の電力に対する、周波数  $f$  の ADC 出力電力の比として定義されます。

$$AC\ CMRR\ (dB) = 10\log(P_f/P_{f_s})$$

ここで、

$P_f$  は周波数  $f$  の ADC の出力電力です。

$P_{f_s}$  は周波数  $f_s$  の ADC の出力電力です。

**チャンネル間アイソレーション**

チャンネル間アイソレーションはすべての入力チャンネル間のクロストーク・レベルの大きさです。この値を測定するには、選択されていない入力チャンネルすべてに最大 160 kHz のサイン波信号を入力し、1 kHz のサイン波信号が印加されているチャンネルでフルスケール信号の減衰量を調べます。

**位相遅延**

位相遅延は、コンバータによって入力をサンプリングした時点から、ADC で結果を読み出すまでの絶対的な時間遅延です。これには、デバイスのアナログ・フロントエンドによる遅延も含まれます。

**位相遅延ドリフト**

位相遅延ドリフトは、デバイスの動作温度全体にわたる単位温度あたりの位相遅延の変化量です。

**位相遅延マッチング**

位相遅延マッチングは、同時にサンプリングされたペア間で観測される最大位相遅延です。

## 動作原理

### コンバータの詳細

AD7617 は、高速、低電力、電荷再配分式 SAR ADC を採用したデータ・アクイジション・システムで、16 個のアナログ入力チャンネルにおけるデュアル同時サンプリングが可能です。AD7617 のアナログ入力は、真のバイポーラ・アナログ入力信号に対応します。アナログ入力レンジは  $\pm 10\text{ V}$ 、 $\pm 5\text{ V}$ 、 $\pm 2.5\text{ V}$  から選択できます。AD7617 は 5 V の単電源で動作します。

AD7617 の搭載機能には、入力クランプ保護、入力信号スケーリング・アンプ、一次アンチエイリアシング・フィルタ、オンチップ・リファレンス、リファレンス・バッファ、デュアル高速 ADC、デジタル・フィルタ、フレキシブルなシーケンサ、および高速パラレル/シリアル・インターフェースがあります。

AD7617 は、HW\_RNGSELx ピンを制御することで、ハードウェア・モードまたはソフトウェア・モードで動作します。ハードウェア・モードでは、AD7617 はピン制御によって設定されます。ソフトウェア・モードでは、AD7617 はシリアルまたはパラレルのインターフェースを介してアクセスする制御レジスタによって設定されます。

### アナログ入力

#### アナログ入力チャンネルの選択

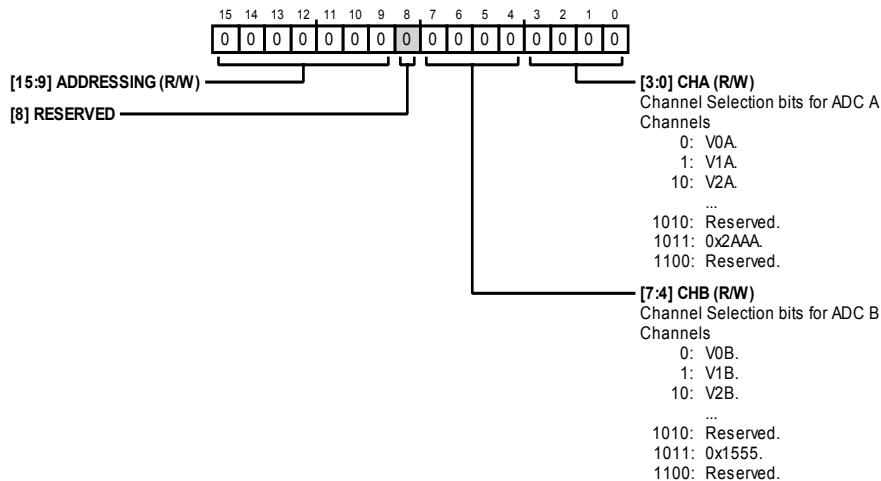

AD7617 は、同時サンプリングのデュアル 14 ビット ADC を内蔵しています。各 ADC には、8 つのアナログ入力チャンネルがあり、合計で 16 個のアナログ入力があります。さらに、AD7617 は、V<sub>cc</sub> 電源をモニタするためのオンチップ診断チャンネルおよび調整可能なオンチップの低ドロップアウト・レギュレータを搭載しています。ハードウェア・モードで CHSELx ピンを制御するか、ソフトウェア・モードでチャンネル・レジスタを制御することにより、変換に使用するチャンネルを選択できます。診断チャンネルをサンプリングするには、ソフトウェア・モードにする必要があります。チャンネルは動的に選択するか、あるいは AD7617 に内蔵されたシーケンサによって、変換に使用するチャンネルをあらかじめプログラムすることもできます。ハードウェア・モードでは、同時サンプリングは対応する A チャンネルまたは B チャンネルに制限されます。つまり、チャンネル V0A は常にチャンネル V0B と一緒にサンプリングされます。ソフトウェア・モードでは、任意の A チャンネルと任意の B チャンネルを選択して同時サンプリングできます。

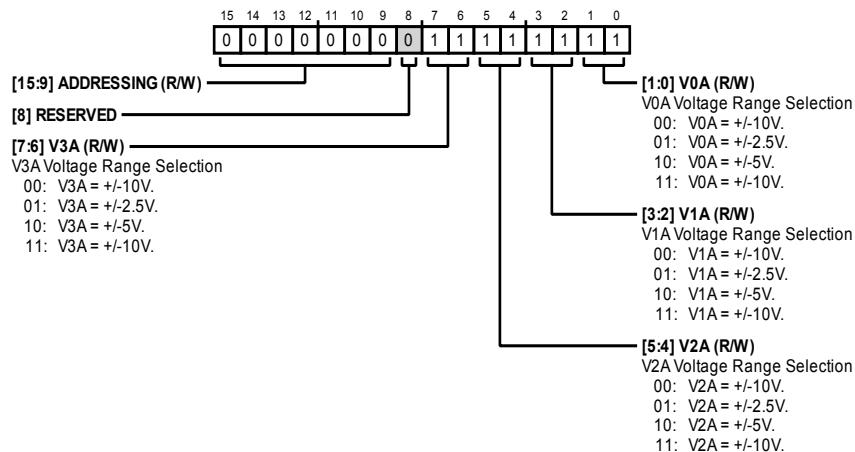

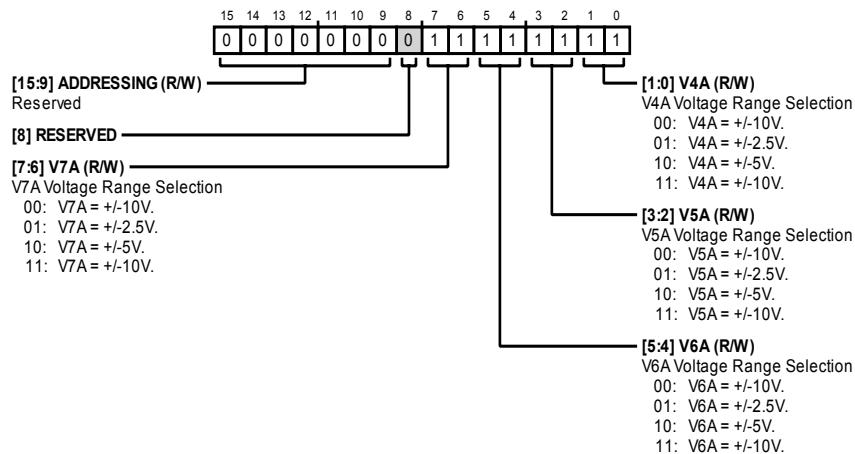

### アナログ入力レンジ

AD7617 は真のバイポーラ、シングルエンド入力電圧に対応できます。レンジ選択ピン (HW\_RNGSEL0 および HW\_RNGSEL1) のロジック・レベルにより、全アナログ入力チャンネルのアナログ入力レンジが決まります。両方のレンジ選択ピンがロジック・ローに接続されている場合、アナログ入力レンジは入力レンジ・レジスタを介してソフトウェア・モードで決定されます (詳細については、レジスタの一覧セクションを参照)。ソフトウェア・モードでは、チャンネルごとに個別のアナログ入力レンジを設定できます。

表 8. アナログ入力レンジの選択

| Analog Input Range                       | HW_RNGSEL1 | HW_RNGSEL0 |

|------------------------------------------|------------|------------|

| Configured via the Input Range Registers | 0          | 0          |

| $\pm 2.5\text{ V}$                       | 0          | 1          |

| $\pm 5\text{ V}$                         | 1          | 0          |

| $\pm 10\text{ V}$                        | 1          | 1          |

ハードウェア・モードでは、これらのピンでのロジック変化がアナログ入力レンジに直ちに影響を与えます。ただし、通常のアクイジション時間の要件に加えて、約 120  $\mu\text{s}$  のセトリング時間がかかります。システム信号に必要な入力レンジに応じて、レンジ選択ピンをハードワイヤ接続する方法が推奨されます。

### アナログ入力インピーダンス

AD7617 の低ドリフト・アナログ入力インピーダンスは  $1\text{ M}\Omega$  に固定されており、AD7617 のサンプリング周波数によって変化することは 없습니다。このアナログ入力インピーダンスは高いので、AD7617 の前段にドライバ・アンプは不要となり、ソースまたはセンサーを直結できます。

### アナログ入力クランプ保護

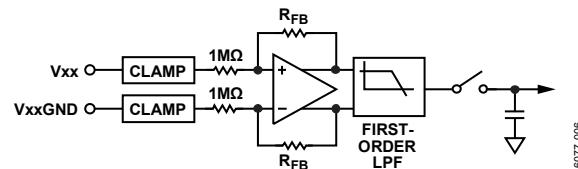

AD7617 のアナログ入力回路を図 42 に示します。AD7617 の各アナログ入力はクランプ保護回路を備えています。 $+5\text{ V}$  の単電源動作にもかかわらず、このアナログ入力クランプ保護により  $-20\text{ V}$  ～ $+20\text{ V}$  の入力過電圧が許容されます。

図 42. アナログ入力回路

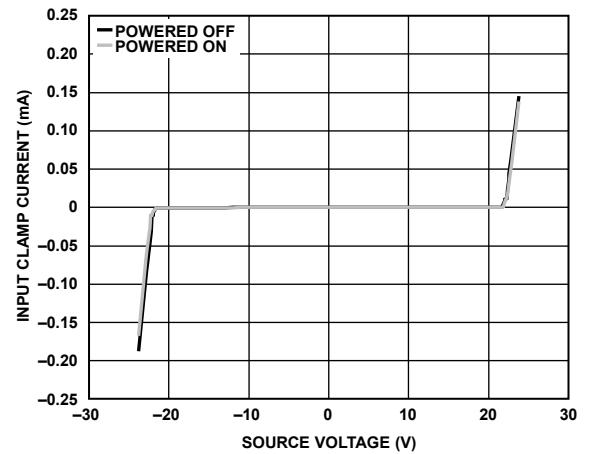

クランプ回路の入力クランプ電流のソース電圧特性を図 43 に示します。 $-20\text{ V}$  ～ $+20\text{ V}$  のソース電圧では、クランプ回路に電流は流れません。 $+20\text{ V}$  を上回るか  $-20\text{ V}$  を下回る入力電圧では、AD7617 のクランプ回路がオンになります。

図 43. 入力保護クランプのプロファイル、入力クランプ電流とソース電圧の関係

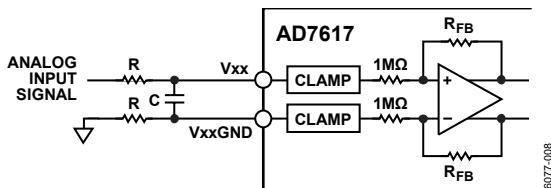

アナログ入力チャンネルに直列抵抗を接続して、 $+20\text{ V}$  を上回るか  $-20\text{ V}$  を下回る入力電圧に対する電流を  $\pm 10\text{ mA}$  に制限します。アナログ入力チャンネル、VxA または VxB に直列抵抗を挿入するアプリケーションでは、アナログ入力のグラウンド・チャンネル VxAGND または VxBGND に対応する抵抗が必要になります (図 44 を参照)。

VxAGND または VxBGND のチャンネルに対応する抵抗がないと、オフセット誤差が生じます。この入力過電圧クランプ保護回路を使用して、過渡過電圧から AD7617 を保護します。通常の動作状態またはパワーダウン状態で、クランプ保護回路がアクティブな状態のまま AD7617 を長時間放置することは推奨されません。

図 44. アナログ入力の入力抵抗マッチング

### アナログ入力のアンチエイリアス・フィルタ

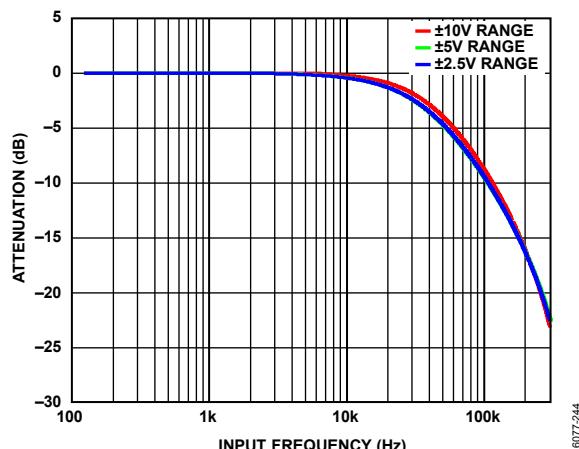

AD7617 には、アナログ・アンチエイリアス・フィルタ（1 次バターワース）も備わっています。アナログ・アンチエイリアス・フィルタの周波数応答と位相応答をそれぞれ図 45 と図 46 に示します。 $\pm 10\text{ V}$  レンジでの標準コーナー周波数は 39 kHz で、 $\pm 5\text{ V}$  レンジでは 33kHz です。

図 45. アナログ・アンチエイリアス・フィルタの周波数応答

図 46. アナログ・アンチエイリアス・フィルタの位相応答

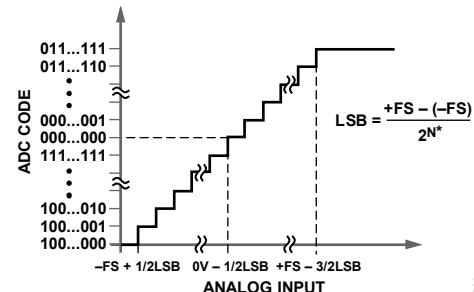

### ADC の伝達関数

AD7617 の出力コーディングは 2 の補数です。コード遷移は LSB の連続する整数値の中間（1/2 LSB、3/2 LSB）で発生します。AD7617 では、LSB のサイズはフルスケール・レンジ  $\div 16,384$  になります。AD7617 の理想的な伝達特性を図 47 と図 9 に示します。LSB のサイズは、選択されたアナログ入力レンジに依存します。

\*WHERE N IS THE NUMBER OF BITS OF THE CONVERTER

図 47. 伝達特性

表 9.

| Range              | +FS             | Midscale | -FS             | LSB                        |

|--------------------|-----------------|----------|-----------------|----------------------------|

| $\pm 10\text{ V}$  | $+10\text{ V}$  | 0 V      | $-10\text{ V}$  | $+1220\text{ }\mu\text{V}$ |

| $\pm 5\text{ V}$   | $+5\text{ V}$   | 0 V      | $-5\text{ V}$   | $+610\text{ }\mu\text{V}$  |

| $\pm 2.5\text{ V}$ | $+2.5\text{ V}$ | 0 V      | $-2.5\text{ V}$ | $+305\text{ }\mu\text{V}$  |

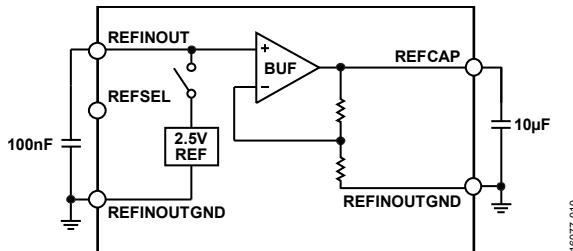

### 内部リファレンス／外部リファレンス

AD7617 は、内部または外部のどちらのリファレンスでも動作可能です。このデバイスには、2.5 V のバンドギャップ・リファレンスが内蔵されています。内部で 4.096 V のリファレンスを生成する 2.5 V リファレンスを REFINOUT ピンから取り出すことができます。あるいは、2.5 V の外部リファレンスを AD7617 に印加することもできます。外部から印加する 2.5 V のリファレンス電圧も内部バッファを使用して 4.096 V に増幅されます。この 4.096 V のバッファ付きリファレンスは SAR ADC によって使用されます。

REFSEL ピンはロジック入力ピンです。このピンを使用すれば、内部リファレンスまたは外部リファレンスを選択できます。このピンをロジック・ハイにすると、内部リファレンスが選択されインエーブルになります。このピンをロジック・ローにすると、内部リファレンスがディスエーブルになるので、外部リファレンス電圧を REFINOUT ピンに印加する必要があります。

内蔵リファレンス・バッファは常にインエーブルになります。フル・リセット後、AD7617 は REFSEL ピンによって選択されたリファレンス・モードで動作します。内部、外部のいずれのリファレンス・オプションでも、REFINOUT ピンにはデカッピングが必要です。REFINOUT ピンと REFOUTGND ピンには、100 nF の X7R セラミック・コンデンサが必要です。

AD7617には、リファレンス電圧をほぼ4.096 Vに増幅するよう構成されたリファレンス・バッファが内蔵されています。REFCAPとREFGNDの間には10 $\mu$ FのX5Rセラミック・コンデンサが必要です。REFINOUTピンで使用できるリファレンス電圧は2.5 Vです。AD7617を外部リファレンス・モードに設定すると、REFINOUTピンの入力インピーダンスが高くなります。

システム内の他の場所に内部リファレンスを印加する場合は、まず外部でバッファを追加する必要があります。

図 48. リファレンス回路

## シャットダウン・モード

RESETピンを1.2  $\mu$ s以上ローに保つと、AD7617はシャットダウン・モードに移行します。RESETピンをローからハイにすると、シャットダウン・モードから通常モードに移行します。

AD7617をシャットダウン・モードにした場合、消費電流は48  $\mu$ A(代表値)になり、デバイスへの書き込みを実行するまでのパワーアップ時間は約240  $\mu$ sになります。変換を実行するまでのパワーアップ時間は15 msです。シャットダウン・モードでは、すべての回路がパワーダウン状態になり、すべてのレジスタがクリアされデフォルト値にリセットされます。

## デジタル・フィルタ

AD7617はオプションのデジタル1次Sincフィルタを内蔵しており、低速スループット・レートを使用するアプリケーション、または高SNRやダイナミック・レンジを必要とするアプリケーションで使用します。

デジタル・フィルタのOSRは、オーバーサンプリング・ピンOS2～OS0(OSx)を使用してハードウェアで制御するか、あるいは設定レジスタ内のOSビットを介してソフトウェアで制御します。

ソフトウェア・モードでは、設定レジスタのOSビットを設定すると、すべてのチャンネルでオーバーサンプリングが有効になります。ハードウェア・モードでは、フル・リセットが解除された時点のOSx信号により、使用するOSRが決定されます。

各種オーバーサンプリング・レートを選択するためのオーバーサンプリング・ビットのデコードを表10に示します。オーバーサンプリング機能に加え、出力結果は14ビットの分解能にデシメートルされます。

OSxピン/OSビットでOS比を8に設定すると、選択されたチャンネルの最初のサンプルが次回のCONVSTの立上がりエッジでサンプリングされます。そのチャンネルの残りの7つのサンプルは、内部で生成されたサンプリング信号でサンプリングされます。次に、これらのサンプルを平均化することでSNR性能が改善されます。OS比の増加に伴い、-3 dBの周波数が減少し、許容サンプリング周波数も減少します。変換時間はオーバーサンプリング・レートの増加に伴い延長され、BUSY信号もオーバーサンプリング・レートに比例して変化します。アクイジション時間と変換時間はオーバーサンプリング・レートに合わせて直線的に増加します。

オーバーサンプリングがシーケンサによってイネーブルになっている場合、またはバースト・モードになっている場合は、あるチャンネルで追加サンプルを収集してから、シーケンサが次のチャンネルに進みます。

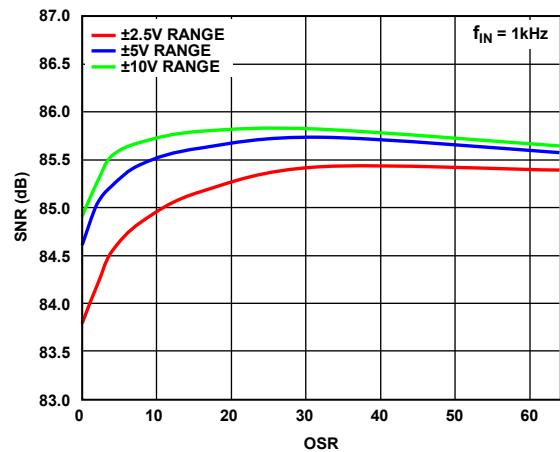

許容される各オーバーサンプリング・レートに対するデバイスの標準SNR性能を表10に示します。デバイスの3つの入力レンジに対する入力トーンとして1kHzの正弦波を使用しました。SNR対OSRのプロットを図49に示します。

図 49. アナログ入力のレンジ全体にわたる標準 SNR 対 OSR

表 10. オーバーサンプリング・ビットのデコード

| OSx Pins/OS Bits | OSR             | Typical SNR (dB) |            |             | -3 dB Bandwidth (kHz) |

|------------------|-----------------|------------------|------------|-------------|-----------------------|

|                  |                 | ±2.5 V Range     | ±5 V Range | ±10 V Range |                       |

| 000              | No oversampling | 83.8             | 84.6       | 84.9        | 37                    |

| 001              | 2               | 84.2             | 85.0       | 85.3        | 36.5                  |

| 010              | 4               | 84.5             | 85.2       | 85.5        | 35                    |

| 011              | 8               | 84.9             | 85.5       | 85.7        | 30.5                  |

| 100              | 16              | 85.2             | 85.6       | 85.8        | 22                    |

| 101              | 32              | 85.4             | 85.7       | 85.8        | 13.2                  |

| 110              | 64              | 85.4             | 85.6       | 85.6        | 7.2                   |

| 111              | 128             | 84.7             | 85.1       | 85.2        | 3.6                   |

## アプリケーション情報

### 機能の概要

AD7617には、ハードウェア・モードとソフトウェア・モードの2つの動作モードがあります。さらに、いずれのモードについても、通信インターフェースにシリアルまたはパラレルを選択できます。選択する動作モードとインターフェースによっては、利用できない機能があります。ハードウェアのシリアル・モードとパラレル・モードでは機能が制限されますが、ソフトウェアのシリアル・モードとパラレル・モードでは機能をフルに利用できます。各動作モードで使用可能な機能を表11に示します。

### 電源

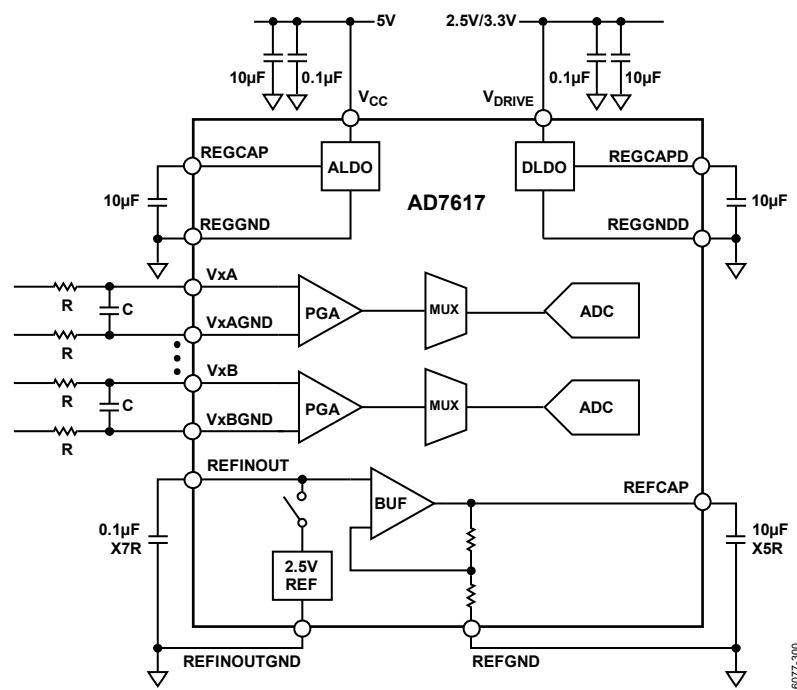

AD7617には2つの独立した電源  $V_{CC}$  と  $V_{DRIVE}$  があり、それぞれアナログ回路とデジタル・インターフェースに供給されます。100 nFのコンデンサと10  $\mu$ Fのコンデンサを並列に接続して、 $V_{CC}$  電源と  $V_{DRIVE}$  電源の両方をデカッピングします。

さらに、これらの電源は2つの内部LDOレギュレータによって安定化されます。通常、アナログLDO(ALDO)は1.87 Vの電圧を供給します。REGCAPピンとREGGNDピンの間に10  $\mu$ Fのコンデンサを接続してALDOをデカッピングします。通常、

表 11. 機能マトリックス

| Functionality                    | Operation Mode <sup>1</sup>    |                       |                                |                       |

|----------------------------------|--------------------------------|-----------------------|--------------------------------|-----------------------|

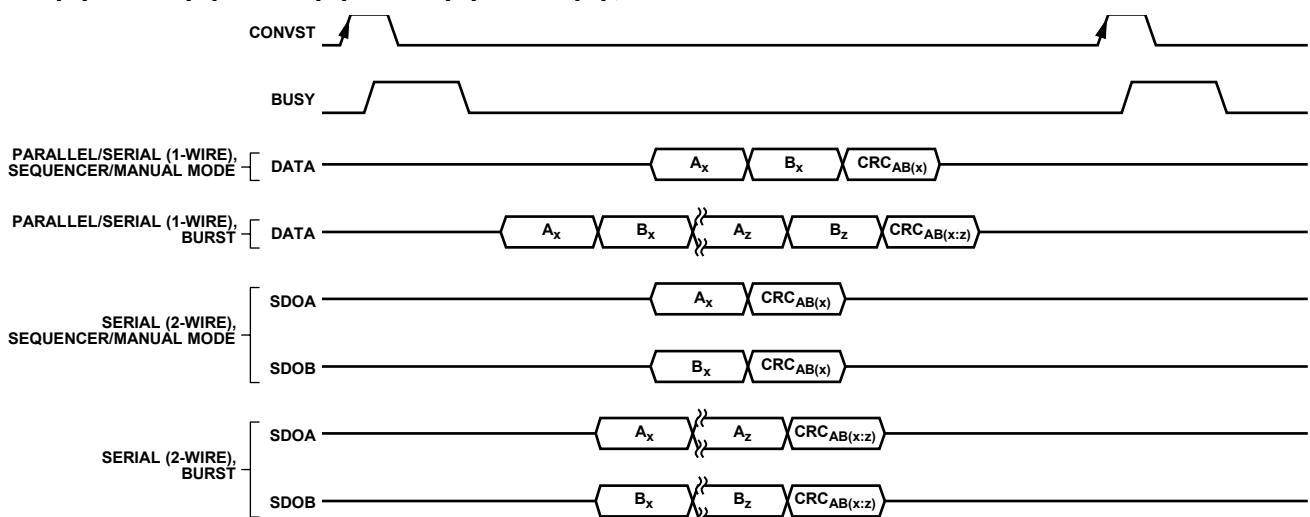

|                                  | Software Mode, HW_RNGSELx = 00 |                       | Hardware Mode, HW_RNGSELx ≠ 00 |                       |