## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2023年9月5日現在、アナログ・デバイセズ株式会社で確認した誤りを記したもので

す。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2023年9月5日

製品名：AD7380-4

対象となるデータシートのリビジョン(Rev)：Rev.0

訂正箇所：19ページ、右の段、アラートの欄、下から8行目

### 【誤】

「ALERT レジスタのアラート・・・」

### 【正】

「アラート報知レジスタ (alert indication register) のアラート・・・」

アナログ・デバイセズ株式会社

本社／〒105-6891 東京都港区海岸1-16-1

ニューピア竹芝サウスタワービル

電話 03 (5402) 8200

大阪営業所／〒532-0003 大阪府大阪市淀川区富原3-5-36

新大阪トラストタワー

電話 06 (6350) 6868

# 差動入力、外部リファレンス、同時サンプリングの16ビット・クワッドSAR ADC

## データシート

## AD7380-4

### 特長

- 16ビットADCファミリ

- クワッド同時サンプリング

- 完全差動アナログ入力

- 高スループット・レート: 4MSPS

- S/N比: 92dB (VREF = 3.3V、代表値)

- オーバーサンプリング機能搭載

- S/N比: 97.7dB (OSR = 8×、RES = 1、代表値)

- 2ビットの分解能増強

- 範囲外インジケータ (ALERT)

- INL: 3LSB (最大)

- 高速シリアル・インターフェース

- 温度範囲: -40°C~125°C

- 4mm × 4mm、24ピンLFCSPパッケージ

### アプリケーション

- モータ・コントロールのポジション・フィードバック

- モータ・コントロールの電流検出

- データ・アクイジション・システム

- エルビウム添加ファイバ増幅器 (EDFA) アプリケーション

- 同相および直交位相の復調

### 概要

AD7380-4は、16ビット対応のクワッド同時サンプリング高速逐次比較レジスタ (SAR) A/Dコンバータ (ADC) で、3.3Vの電源で動作し、スループット・レートは最大4MSPSです。差動アナログ入力は広い範囲のコモンモード電圧を入力でき、CSの立下がりエッジでサンプリングと変換を実行します。

AD7380-4にはオーバーサンプリング・ブロックが内蔵されており、低い帯域幅でのダイナミック・レンジを向上させノイズを低減しています。オーバーサンプリングにより分解能を最大2ビット増強できます。REFINピンのリファレンス電圧は2.5V~3.3Vが可能です。

変換プロセスとデータ・アクイジションでは標準的なコントロール入力を使用しているため、マイクロプロセッサやデジタル・シグナル・プロセッサ (DSP) と容易にインターフェース接続できます。変換結果は、高いスループットでは4線モード、低スループットが許容される場合は1線式シリアル・モードを使用して、同時にクロック出力できます。また、別個のロジック電源を使用することにより、1.8V、2.5V、3.3Vのインターフェースに対応できます。

AD7380-4は、24ピン・リード・フレーム・チップ・スケール・パッケージ (LFCSP) を採用し、-40°C~+125°Cの温度範囲で仕様規定されています。

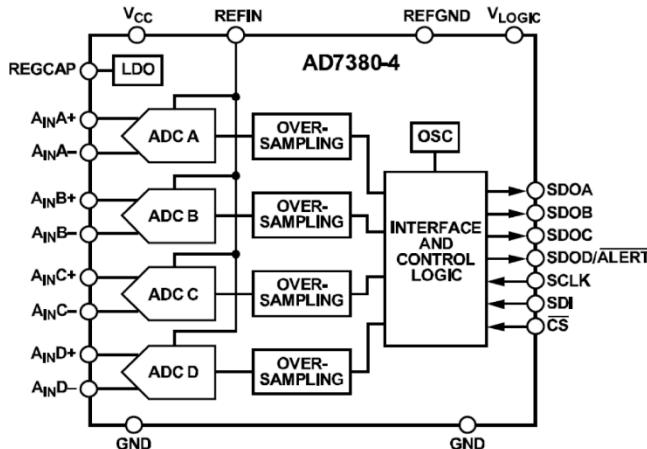

### 機能ブロック図

図 1.

表 1. 関連デバイス

| No. of Channels | Input Type   | 16 Bits                    | 14 Bits  | 12 Bits |

|-----------------|--------------|----------------------------|----------|---------|

| 4               | Differential | AD7380-4<br>AD7389-4       | AD7381-4 |         |

| 2               | Differential | AD7380<br>AD4680<br>AD4681 | AD7381   |         |

|                 | Single-ended | AD7386                     | AD7387   | AD7388  |

### 製品のハイライト

- クワッド同時サンプリングおよび変換。

- ピン互換の製品ファミリ。

- 16ビットで4MSPSの高スループット。

- 省スペースの4mm × 4mm LFCSP。

- オーバーサンプリング・ブロック内蔵により、ダイナミック・レンジが向上し、ノイズが抑制され、SCLKの速度条件が緩和。

- コモンモード電圧範囲の広い差動アナログ入力。

- サンプリング・コンデンサの容量が小さいため、アンプの駆動負荷が低減。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は英語版資料が古い場合があります。最新の内容については、英語版をご参照ください。

Rev. 0

アナログ・デバイセズ株式会社

本社／〒105-6891

大阪営業所／〒532-0003

名古屋営業所／〒451-6038

東京都港区海岸1-16-1 ニューピア竹芝サウスタワー10F

電話03 (5402) 8200

大阪府大阪市淀川区宮原3-5-36 新大阪トラストタワー10F

電話06 (6350) 6868

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F

電話052 (569) 6300

## 目次

|                |    |                      |    |

|----------------|----|----------------------|----|

| 特長             | 1  | オーバーサンプリング           | 17 |

| アプリケーション       | 1  | 分解能増強                | 19 |

| 概要             | 1  | アラート                 | 19 |

| 機能ブロック図        | 1  | 電力モード                | 20 |

| 製品のハイライト       | 1  | 外部リファレンス             | 20 |

| 改訂履歴           | 2  | ソフトウェア・リセット          | 20 |

| 仕様             | 3  | 診断セルフ・テスト            | 20 |

| タイミング仕様        | 5  | インターフェース             | 21 |

| 絶対最大定格         | 8  | 変換結果の読出し             | 21 |

| 熱抵抗            | 8  | 低遅延リードバック            | 22 |

| 静電放電 (ESD) 定格  | 8  | デバイス・レジスタからの読出し      | 23 |

| ESDに関する注意      | 8  | デバイス・レジスタへの書き込み      | 23 |

| ピン配置およびピン機能の説明 | 9  | CRC                  | 23 |

| 代表的な性能特性       | 10 | レジスタ                 | 26 |

| 用語の定義          | 13 | アドレス指定レジスタ           | 26 |

| 動作原理           | 14 | CONFIGURATION 1 レジスタ | 27 |

| 回路説明           | 14 | CONFIGURATION 2 レジスタ | 28 |

| コンバータの動作       | 14 | アラート表示レジスタ           | 28 |

| アナログ入力構造       | 14 | アラート下限閾値レジスタ         | 29 |

| ADCの伝達関数       | 15 | アラート上限閾値レジスタ         | 30 |

| アプリケーション情報     | 16 | 外形寸法                 | 31 |

| 電源             | 16 | オーダー・ガイド             | 31 |

| パワーアップ         | 16 |                      |    |

| 動作モード          | 17 |                      |    |

## 改訂履歴

1/2022-Rev. 0: Initial Version

## 仕様

特に指定のない限り、 $V_{CC} = 3.0V \sim 3.6V$ 、 $V_{LOGIC} = 1.65V \sim 3.6V$ 、外部リファレンス電圧 ( $V_{REF} = 2.5V$ )、 $f_{SAMPLE} = 4MSPS$ 、 $T_A = -40^{\circ}C \sim +125^{\circ}C$ 、オーバーサンプリング無効。

表 2.

| パラメータ                                           | テスト条件/コメント                                            | 最小値        | 代表値                  | 最大値             | 単位                             |

|-------------------------------------------------|-------------------------------------------------------|------------|----------------------|-----------------|--------------------------------|

| RESOLUTION                                      |                                                       | 16         |                      |                 | Bits                           |

| THROUGHPUT                                      |                                                       |            |                      |                 |                                |

| Conversion Rate ( $f_{SAMPLE}$ )                |                                                       |            | 4                    |                 | MSPS                           |

| ANALOG INPUT                                    |                                                       |            |                      |                 |                                |

| Voltage Range                                   | $A_{INX+} - A_{INX-}$                                 | $-V_{REF}$ | $+V_{REF}$           |                 | V                              |

| Absolute Input Voltage                          | $A_{INX+}, A_{INX-}$                                  | -0.1       | $V_{REF} + 0.1$      |                 | V                              |

| Common-Mode Input Range                         | $A_{INX+}, A_{INX-}$                                  | 0.2        | $V_{REF} \times 0.5$ | $V_{REF} - 0.2$ | V                              |

| Analog Input Common-Mode Rejection Ratio (CMRR) | $f_{IN} = 500\text{ kHz}$                             |            | -76                  |                 | dB                             |

| DC Leakage Current                              |                                                       |            | 0.1                  | 1               | $\mu\text{A}$                  |

| Input Capacitance                               | Track mode                                            |            | 18                   |                 | pF                             |

|                                                 | Hold mode                                             |            | 5                    |                 | pF                             |

| DC ACCURACY                                     |                                                       |            |                      |                 |                                |

| No Missing Codes                                |                                                       | 16         |                      |                 | Bits                           |

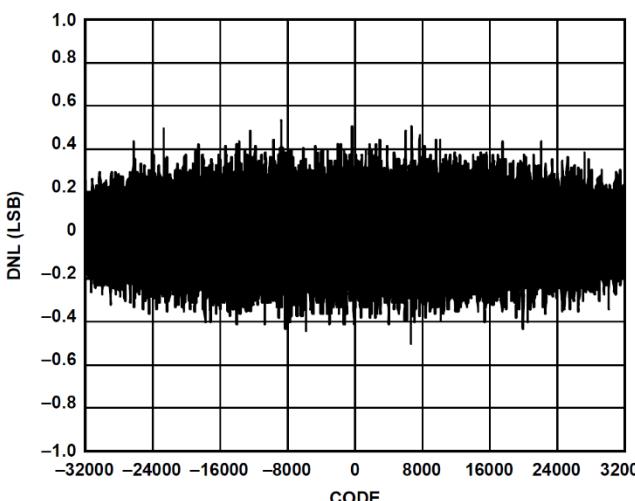

| Differential Nonlinearity (DNL) Error           |                                                       | -1.0       | $\pm 0.5$            | +1.0            | LSB                            |

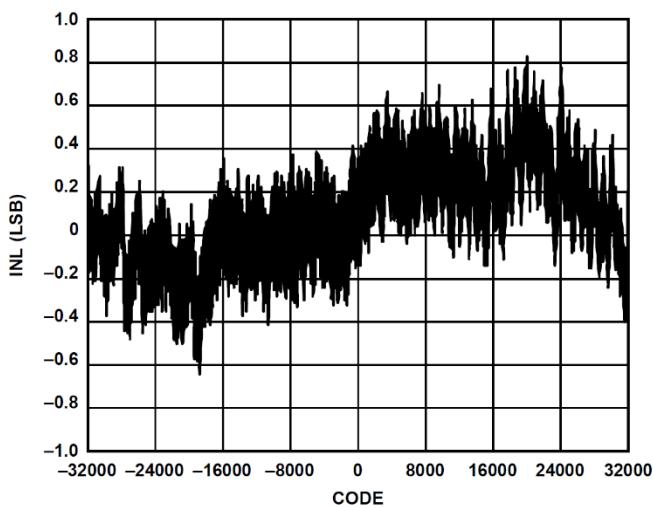

| Integral Nonlinearity (INL) Error               |                                                       | -3.0       | $\pm 1$              | +3.0            | LSB                            |

| Gain Error                                      |                                                       | -0.015     | $\pm 0.001$          | +0.015          | % FS1                          |

| Gain Error Temperature Drift                    |                                                       | -5         | $\pm 1$              | +5              | ppm/ $^{\circ}\text{C}$        |

| Gain Error Match                                |                                                       | -0.015     | $\pm 0.01$           | +0.015          | % FS                           |

| Offset Error                                    |                                                       | -0.75      | $\pm 0.1$            | +0.75           | mV                             |

| Zero Error Temperature Drift                    |                                                       | -1         | $\pm 0.5$            | +1              | $\mu\text{V}/^{\circ}\text{C}$ |

| Zero Error Match                                |                                                       | -0.75      | $\pm 0.5$            | +0.75           | mV                             |

| AC ACCURACY                                     |                                                       |            |                      |                 |                                |

| Dynamic Range                                   | $f_{IN} = 1\text{ kHz}$<br>$V_{REF} = 3.3\text{ V}$   |            | 93                   |                 | dB                             |

|                                                 |                                                       |            | 91.3                 |                 | dB                             |

| Oversampled Dynamic Range                       | $OSR = 4 \times$ 、 $RES = 1$ (10進数)                   |            | 97.4                 |                 | dB                             |

| Signal-to-Noise Ratio (SNR)                     | $V_{REF} = 3.3\text{ V}$                              | 89         | 92                   |                 | dB                             |

|                                                 |                                                       | 87.5       | 90.5                 |                 | dB                             |

|                                                 | 移動平均 $OSR = 8 \times$ 、 $RES = 1$ (10進数)              |            | 97.7                 |                 | dB                             |

|                                                 | $f_{IN} = 100\text{ kHz}$                             |            | 89.2                 |                 | dB                             |

| Spurious-Free Dynamic Range (SFDR)              |                                                       |            | -110                 |                 | dB                             |

| Total Harmonic Distortion (THD)                 |                                                       |            | -110                 |                 | dB                             |

| Signal-to-Noise-and-Distortion (SINAD) Ratio    | $f_{IN} = 100\text{ kHz}$<br>$V_{REF} = 3.3\text{ V}$ | 88.5       | 91.5                 |                 | dB                             |

|                                                 |                                                       | 87         | 90                   |                 | dB                             |

| Channel to Channel Isolation                    |                                                       |            | -104.7               |                 | dB                             |

|                                                 |                                                       |            | -126                 |                 | dB                             |

| POWER SUPPLIES                                  |                                                       |            |                      |                 |                                |

| $I_{VCC}$                                       |                                                       |            | 38                   | 42              | mA                             |

| Normal Mode (Operational)                       |                                                       |            |                      |                 |                                |

| Power Dissipation                               |                                                       |            | 163.1                | 180.2           | mW                             |

| $P_{TOTAL}$                                     |                                                       |            |                      |                 |                                |

| $P_{VCC}$                                       |                                                       |            | 136.8                | 151.2           | mW                             |

| Normal Mode (Operational)                       |                                                       |            |                      |                 |                                |

1 これらの仕様には、全温度範囲の変動が含まれていますが、外部リファレンスによる誤差の影響は含まれていません。

特に指定のない限り、 $V_{CC} = 3.0V \sim 3.6V$ 、 $V_{LOGIC} = 1.65V \sim 3.6V$ 、外部 $V_{REF} = 2.5V$ 、 $T_A = -40^{\circ}C \sim +125^{\circ}C$ 、オーバーサンプリング無効。

表 3.

| パラメータ                                          | テスト条件/コメント                                  | 最小値                                           | 代表値             | 最大値     | 単位         |

|------------------------------------------------|---------------------------------------------|-----------------------------------------------|-----------------|---------|------------|

| SAMPLING DYNAMICS                              |                                             |                                               |                 |         |            |

| Input Bandwidth                                | -0.1dBとなる周波数<br>-3dBとなる周波数                  | 6.6<br>26.8                                   |                 |         | MHz<br>MHz |

| Aperture Delay                                 |                                             | 2                                             |                 |         | ns         |

| Aperture Delay Match                           |                                             | 46.8                                          | 145             |         | ps         |

| Aperture Jitter                                |                                             | 20                                            |                 |         | ps         |

| REFERENCE INPUT                                |                                             |                                               |                 |         |            |

| $V_{REF}$ Input Voltage Range                  | 外部リファレンス                                    | 2.49                                          | 3.4             |         | V          |

| $V_{REF}$ Input Current                        | 外部リファレンス                                    | 0.9                                           | 1.2             |         | mA         |

| DIGITAL INPUTS (SCLK, SDI, $\overline{CS}$ )   |                                             |                                               |                 |         |            |

| Logic Levels                                   |                                             |                                               |                 |         |            |

| Input Voltage Low ( $V_{IL}$ )                 | $V_{LOGIC} < 2.3V$                          |                                               | 0.45            |         | V          |

|                                                | $V_{LOGIC} \geq 2.3V$                       |                                               | 0.7             |         | V          |

| Input Voltage High ( $V_{IH}$ )                | $V_{LOGIC} < 2.3V$<br>$V_{LOGIC} \geq 2.3V$ | $V_{LOGIC} - 0.45V$<br>$0.8 \times V_{LOGIC}$ |                 |         | V          |

| Input Current Low ( $I_{IL}$ )                 |                                             | -1                                            | +1              |         | $\mu A$    |

| Input Current High ( $I_{IH}$ )                |                                             | -1                                            | +1              |         | $\mu A$    |

| DIGITAL OUTPUTS (SDOA, SDOB, SDOC, SDOD/ALERT) |                                             |                                               |                 |         |            |

| Output Coding                                  |                                             |                                               | Twos complement |         | Bits       |

| Output Voltage Low ( $V_{OL}$ )                | 電流シンク ( $I_{SINK} = 300\mu A$ )             |                                               | 0.4             |         | V          |

| Output Voltage High ( $V_{OH}$ )               | 電流ソース ( $I_{SOURCE} = -300\mu A$ )          | $V_{LOGIC} - 0.3$                             |                 |         | V          |

| Floating State Leakage Current                 |                                             |                                               |                 | $\pm 1$ | $\mu A$    |

| Floating State Output Capacitance              |                                             |                                               | 10              |         | pF         |

| POWER SUPPLIES                                 |                                             |                                               |                 |         |            |

| $V_{CC}$                                       |                                             | 3.0<br>外部リファレンス = 3.3V                        | 3.3<br>3.3      | 3.6     | V<br>V     |

| $V_{LOGIC}$                                    |                                             | 1.65                                          |                 | 3.6     | V          |

| $V_{CC}$ Supply Current ( $I_{VCC}$ )          |                                             |                                               | 1.7             | 2       | mA         |

| Normal Mode (Static)                           |                                             |                                               | 101             | 200     | $\mu A$    |

| Shutdown Mode                                  |                                             |                                               |                 |         |            |

| $V_{LOGIC}$ Current ( $I_{VLOGIC}$ )           | 正のフルスケールでのアナログ入力                            |                                               | 10              | 200     | nA         |

| Normal Mode (Static)                           |                                             |                                               | 7.3             | 8       | mA         |

| Normal Mode (Operational)                      |                                             |                                               | 10              | 200     | nA         |

| Shutdown Mode                                  |                                             |                                               |                 |         |            |

| Power Dissipation                              |                                             |                                               |                 |         |            |

| $V_{CC}$ Power ( $P_{VCC}$ )                   |                                             |                                               | 6.1             | 7.2     | mW         |

| Normal Mode (Static)                           |                                             |                                               | 363.6           | 720     | $\mu W$    |

| Shutdown Mode                                  |                                             |                                               |                 |         |            |

| $V_{LOGIC}$ Power ( $P_{VLOGIC}$ )             | 正のフルスケールでのアナログ入力                            |                                               | 36              | 720     | nW         |

| Normal Mode (Static)                           |                                             |                                               | 26.3            | 29      | mW         |

| Normal Mode (Operational)                      |                                             |                                               | 36              | 720     | nW         |

| Shutdown Mode                                  |                                             |                                               |                 |         |            |

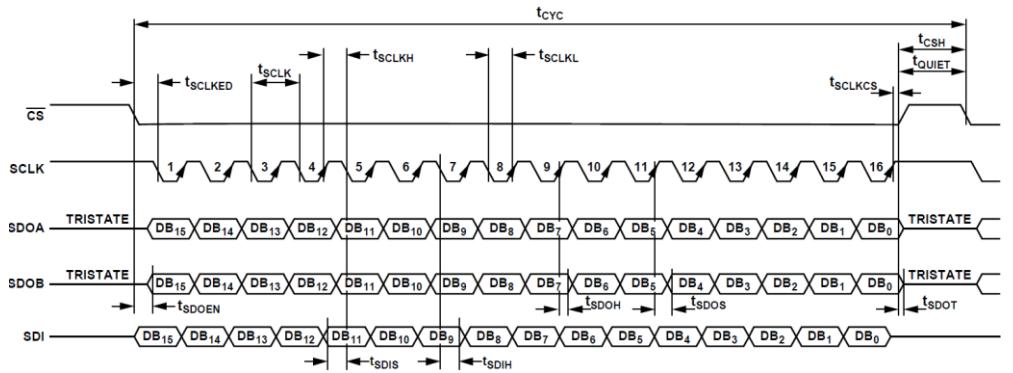

## タイミング仕様

特に指定のない限り、 $V_{CC} = 3.0V \sim 3.6V$ 、 $V_{LOGIC} = 1.65V \sim 3.6V$ 、 $V_{REF} = 2.5V$ 、 $T_A = -40^{\circ}C \sim +125^{\circ}C$ 。パラメータの説明で、多機能ピンの特定の機能について示している箇所では、「ALERT」のように、仕様に関係するピン名のみを示しています。多機能ピンのすべての機能を含むピン名については、ピン配置およびピン機能の説明のセクションを参照してください。

表 4.

| Parameter         | Min  | Typ                                   | Max | Unit    | Description                                                                          |

|-------------------|------|---------------------------------------|-----|---------|--------------------------------------------------------------------------------------|

| $t_{CYC}$         | 250  |                                       |     | ns      | Time between conversions                                                             |

| $t_{SCLKED}$      | 5    |                                       |     | ns      | $\overline{CS}$ falling edge to first SCLK falling edge                              |

| $t_{SCLK}$        | 12.5 |                                       |     | ns      | SCLK period                                                                          |

| $t_{SCLKH}$       | 5.5  |                                       |     | ns      | SCLK high time                                                                       |

| $t_{SCLKL}$       | 5.5  |                                       |     | ns      | SCLK low time                                                                        |

| $t_{CSH}$         | 20   |                                       |     | ns      | $\overline{CS}$ pulse width                                                          |

| $t_{QUIET}$       | 20   |                                       |     | ns      | Interface quiet time prior to conversion                                             |

| $t_{SDOEN}$       |      | 5.5                                   |     | ns      | $\overline{CS}$ low to SDOA and SDOB enabled                                         |

| $t_{SDOH}$        | 3    |                                       |     | ns      | SCLK rising edge to SDOA and SDOB hold time                                          |

| $t_{SDOS}$        |      | 5                                     |     | ns      | SCLK rising edge to SDOA and SDOB setup time                                         |

| $t_{SDOT}$        |      | 8                                     |     | ns      | $\overline{CS}$ rising edge to SDOA and SDOB high impedance                          |

| $t_{SDIS}$        | 4    |                                       |     | ns      | SDI setup time prior to SCLK falling edge                                            |

| $t_{SDIH}$        | 4    |                                       |     | ns      | SDI hold time after SCLK falling edge                                                |

| $t_{SCLKCS}$      | 0    |                                       |     | ns      | SCLK rising edge to $\overline{CS}$ rising edge                                      |

| $t_{CONVERT}$     |      | 190                                   |     | ns      | Conversion time                                                                      |

| $t_{ACQUIRE}$     | 110  |                                       |     | ns      | Acquire time                                                                         |

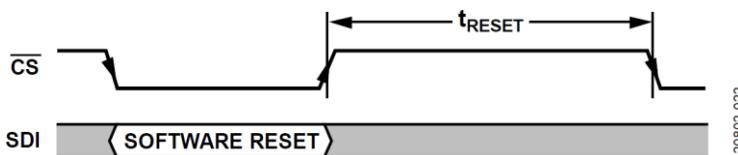

| $t_{RESET}$       |      | 250                                   |     | ns      | Valid time to start conversion after soft reset                                      |

|                   |      | 800                                   |     | ns      | Valid time to start conversion after hard reset                                      |

| $t_{POWERUP}$     |      |                                       | 5   | ms      | Supply active to conversion                                                          |

|                   |      |                                       | 5   | ms      | First conversion allowed                                                             |

|                   |      |                                       | 5   | ms      | Settled to within 1% with external reference                                         |

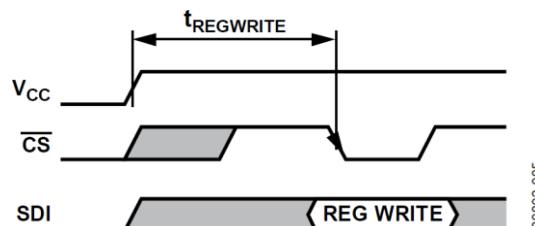

| $t_{REGWRITE}$    |      |                                       | 5   | ms      | Supply active to register read write access allowed                                  |

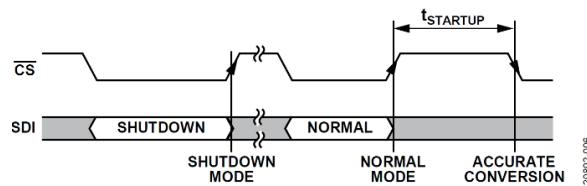

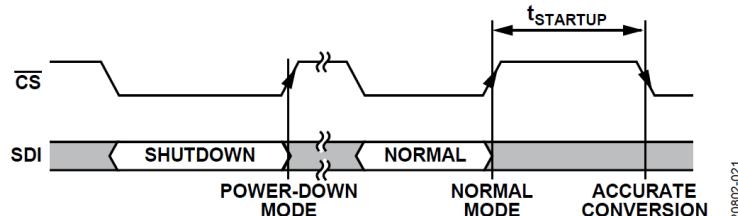

| $t_{STARTUP}$     |      |                                       | 10  | $\mu$ s | Exiting shutdown mode to conversion                                                  |

|                   |      |                                       | 10  | $\mu$ s | Settled to within 1% with external reference                                         |

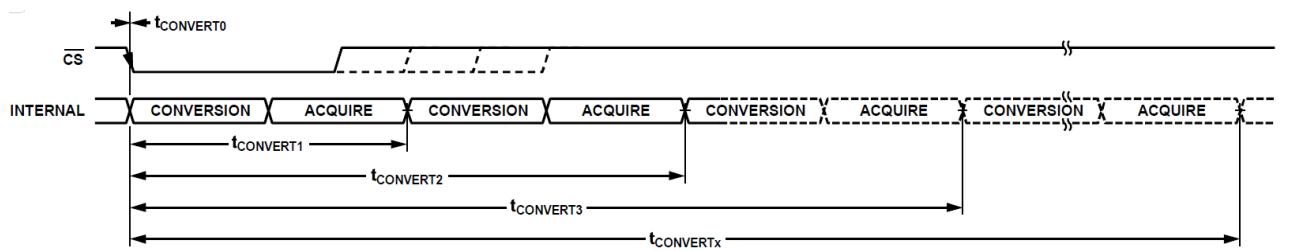

| $t_{CONVERTO}$    | 6    | 8                                     | 10  | ns      | Conversion time for first sample in oversampling (OS) normal mode                    |

| $t_{CONVERTx}$    |      | $t_{CONVERTO} + (320 \times (x - 1))$ |     | ns      | Conversion time for $x^{\text{th}}$ sample in OS normal mode, 4 MSPS, 16-bit devices |

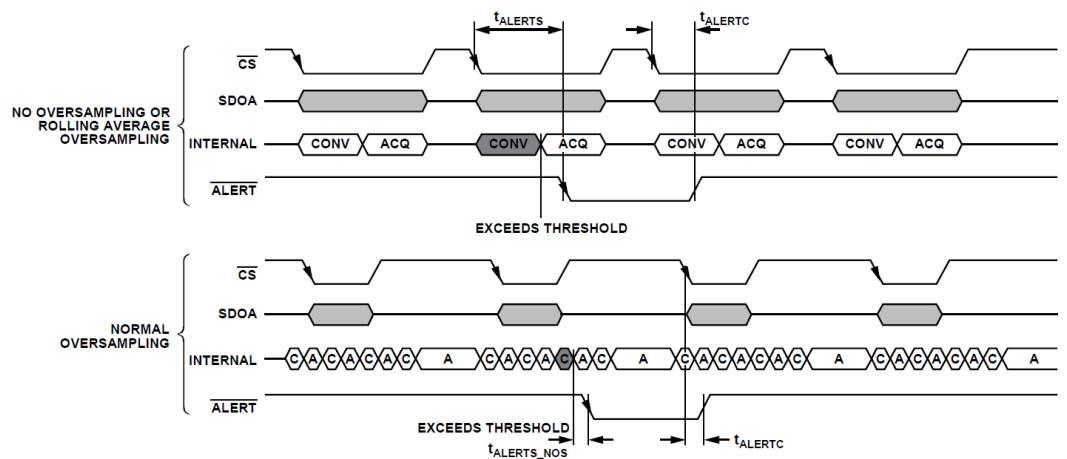

| $t_{ALERTS}$      |      |                                       | 220 | ns      | Time from $\overline{CS}$ to ALERT indication                                        |

| $t_{ALERTC}$      |      |                                       | 10  | ns      | Time from $\overline{CS}$ to ALERT clear                                             |

| $t_{ALERTS\_NOS}$ |      |                                       | 20  | ns      | Time from internal conversion with exceeded threshold to ALERT indication            |

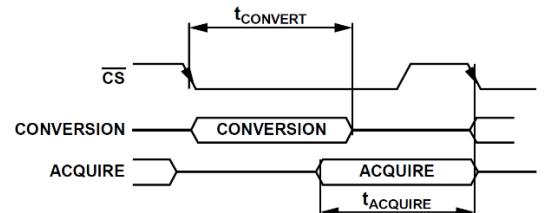

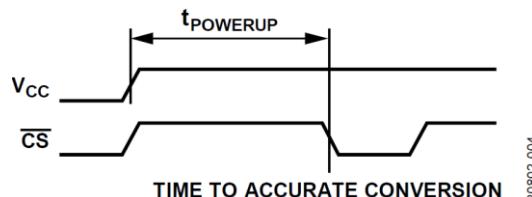

## タイミング図

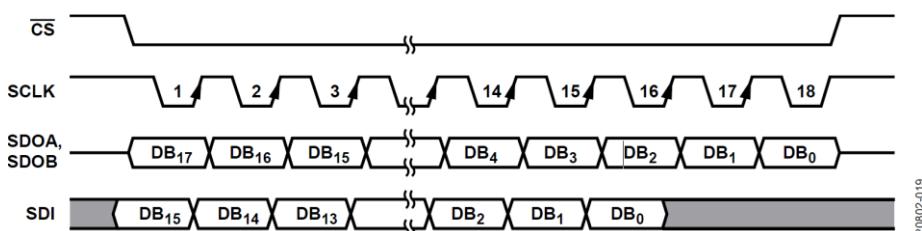

図2. シリアル・インターフェースのタイミング図

図3. 内部変換取得時間

図4. 変換までのパワーアップ時間

図5. レジスタの読み書きアクセスまでのパワーアップ時間

図6. シャットダウン・モードからノーマル・モードまでの時間

図7. OSノーマル・モードでの変換タイミング

図8.  $\overline{\text{ALERT}}$ のタイミング

20802-008

## 絶対最大定格

表 5.

| Parameter                                | Rating                                           |

|------------------------------------------|--------------------------------------------------|

| $V_{CC}$ to GND                          | -0.3 V to +4 V                                   |

| $V_{LOGIC}$ to GND                       | -0.3 V to +4 V                                   |

| Analog Input Voltage to GND              | -0.3 V to $V_{REF} + 0.3$ V, or $V_{CC} + 0.3$ V |

| Digital Input Voltage to GND             | -0.3 V to $V_{LOGIC} + 0.3$ V                    |

| Digital Output Voltage to GND            | -0.3 V to $V_{LOGIC} + 0.3$ V                    |

| REFIN Input to GND                       | -0.3 V to $V_{CC} + 0.3$ V                       |

| Input Current to Any Pin Except Supplies | $\pm 10$ mA                                      |

| Temperature                              |                                                  |

| Operating Temperature Range              | -40°C to +125°C                                  |

| Storage Temperature Range                | -65°C to +150°C                                  |

| Maximum Junction Temperature             | 150°C                                            |

| Pb-Free Soldering Reflow Temperature     | 260°C                                            |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。これはストレス定格のみを定めたものであり、本規格の動作セクションに記載する規定値以上でデバイスが正常に動作することを示唆するものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCBの熱設計には、細心の注意を払う必要があります。

$\theta_{JA}$ は、1立方フィートの密閉容器内で測定された、自然対流での周囲とジャンクションの間の熱抵抗です。 $\theta_{JC}$ は、ジャンクションとケースの間の熱抵抗です。

表 6. 热抵抗

| Package Type          | $\theta_{JA}$ | $\theta_{JC}$     | Unit |

|-----------------------|---------------|-------------------|------|

| CP-24-25 <sup>1</sup> | 48.4          | 0.43 <sup>2</sup> | °C/W |

1 テスト条件1：熱抵抗のシミュレーション値は、4つのサーマル・ビアを備えたJEDEC 2S2Pサーマル・テスト・ボードに基づいています。JEDEC JESDS1を参照してください。

2 テスト条件2：冷却板をパッケージの表面に取り付け、露出パッドで測定しています。

### 静電放電（ESD）定格

以下のESD情報は、ESDに敏感なデバイスを取り扱うために示したものですが、対象はESD保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001準拠の人体モデル（HBM）。

ANSI/ESDA/JEDEC JS-002準拠の電界誘起帶電デバイス・モデル（FICDM）。

### AD7380-4のESD定格

表 7. AD7380-4、24ピンLFCSP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | $\pm 4000$              | 3A    |

| FICDM     | $\pm 1250$              | C3    |

### ESDに関する注意

ESD（静電放電）の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

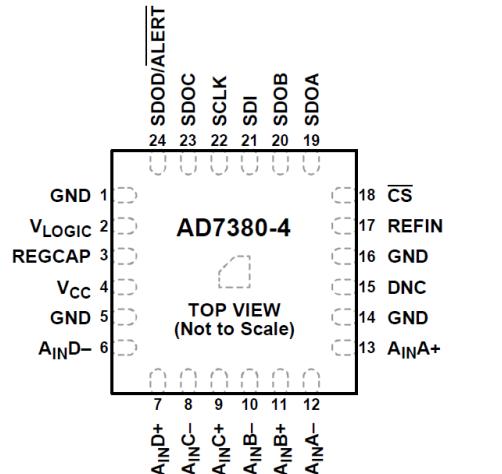

## ピン配置およびピン機能の説明

## NOTES

1. DNC = DO NOT CONNECT.

2. EXPOSED PAD. FOR CORRECT OPERATION OF THE DEVICE THE EXPOSED PAD MUST BE CONNECTED TO GND.

20802-009

図9. ピン配置

表 8. ピン機能の説明

| ピン番号           | 記号                                     | 説明                                                                                                                                                                          |

|----------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 5, 14, 16   | GND                                    | グラウンド基準ポイント。これらのピンは、デバイスの全回路に対するグラウンド基準ポイントです。                                                                                                                              |

| 2              | V <sub>LOGIC</sub>                     | ロジック・インターフェースの電源電圧 (1.65V~3.6V)。このピンは1μFのコンデンサを使用してGNDからデカッピングします。                                                                                                          |

| 3              | REGCAP                                 | 内蔵レギュレータの電圧出力に対するデカッピング・コンデンサ・ピン。このピンは1μFのコンデンサを使用してGNDからデカッピングします。このピンの標準電圧は1.9Vです。                                                                                        |

| 4              | V <sub>CC</sub>                        | 電源入力電圧。3.0 V~3.6 V。このピンは1μFのコンデンサを使用してGNDからデカッピングします。                                                                                                                       |

| 6, 7           | A <sub>IND</sub> -, A <sub>IND</sub> + | ADC Dのアナログ入力。これらのアナログ入力は完全差動ペアを構成します。                                                                                                                                       |

| 8, 9           | A <sub>INC</sub> -, A <sub>INC</sub> + | ADC Cのアナログ入力。これらのアナログ入力は完全差動ペアを構成します。                                                                                                                                       |

| 10, 11         | A <sub>INB</sub> -, A <sub>INB</sub> + | ADC Bのアナログ入力。これらのアナログ入力は完全差動ペアを構成します。                                                                                                                                       |

| 12, 13         | A <sub>INA</sub> -, A <sub>INA</sub> + | ADC Aのアナログ入力。これらのアナログ入力は完全差動ペアを構成します。                                                                                                                                       |

| 15             | DNC                                    | 何も接続しないでください。                                                                                                                                                               |

| 17             | REFIN                                  | リファレンス入力。2.5V~3.3Vの外部リファレンスをこのピンに入力できます。このピンにはデカッピングが必要です。このピンとGNDの間には1μFのコンデンサを接続します。                                                                                      |

| 18             | CS                                     | チップ・セレクト入力。アクティブ・ローのロジック入力。この入力は、AD7380-4の変換開始とシリアル・データ転送のフレーミングの2通りの機能を提供します。                                                                                              |

| 19             | SDOA                                   | シリアル・データ出力A。このピンは、変換結果およびレジスタの内容にアクセスするためのシリアル・データ出力ピンとして機能します。                                                                                                             |

| 20             | SDOB                                   | シリアル・データ出力B。このピンは、変換結果にアクセスするためのシリアル・データ出力ピンとして機能します。                                                                                                                       |

| 21             | SDI                                    | シリアル・データ入力。このピンは、内蔵コントロール・レジスタに書き込まれたデータを提供します。                                                                                                                             |

| 22             | SCLK                                   | シリアル・クロック入力。このシリアル・クロック入力は、ADCとの間のデータ転送に使用します。                                                                                                                              |

| 23             | SDOC                                   | シリアル・データ出力C。このピンは、変換結果およびレジスタの内容にアクセスするためのシリアル・データ出力ピンとして機能します。                                                                                                             |

| 24             | SDOD/ALERT                             | シリアル・データ出力D/アラート表示出力。このピンは、シリアル・データ出力ピン、またはアラート表示出力ピンとして機能できます。<br>SDOD。このピンは、変換結果にアクセスするためのシリアル・データ出力ピンとして機能します。<br>ALERT。このピンは、ローになることで変換結果が設定閾値を超えたことを示すアラート・ピンとして機能します。 |

| Not applicable | EPAD                                   | 露出パッド。デバイスを正しく動作させるために、露出パッドをGNDに接続する必要があります。                                                                                                                               |

## 代表的な性能特性

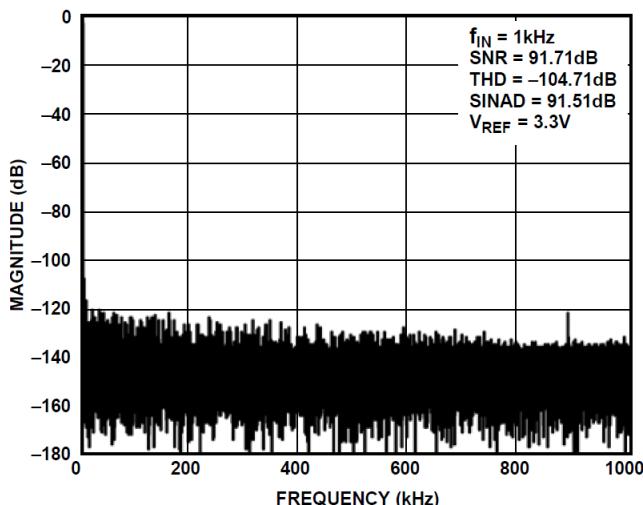

図10. 高速フーリエ変換 (FFT) 、外部リファレンス電圧 = 3.3V

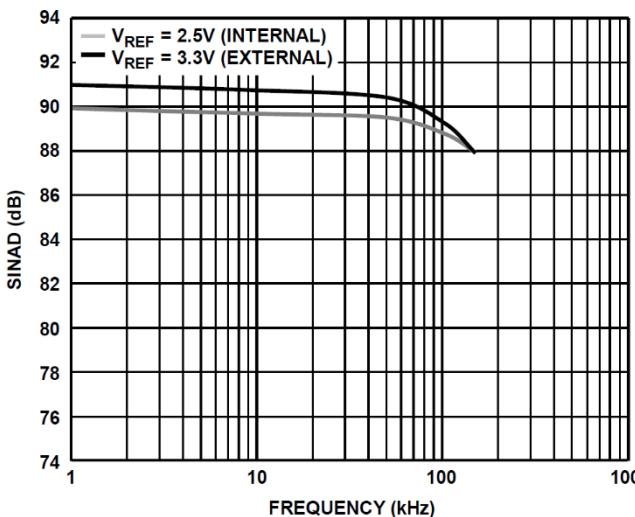

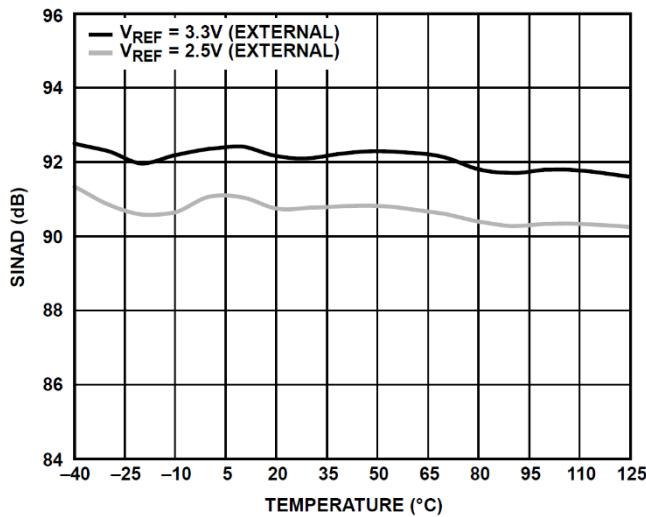

図13. SINADと周波数の関係

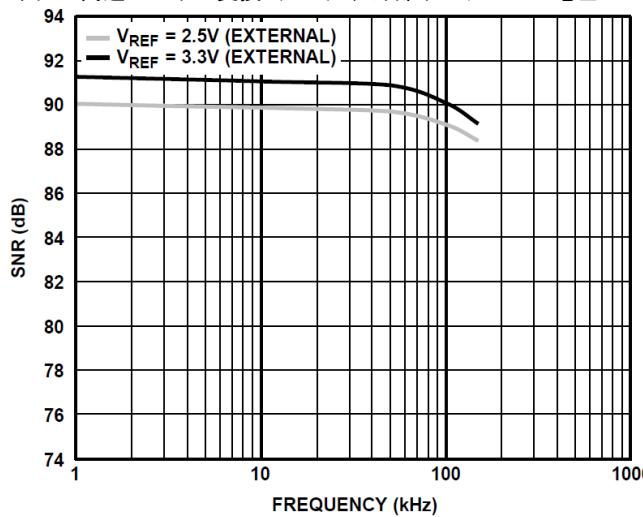

図11. SNRと周波数の関係

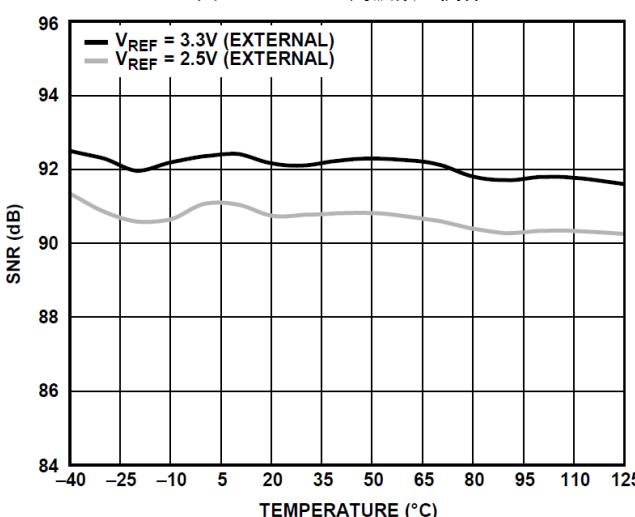

図14. S/N比と温度の関係

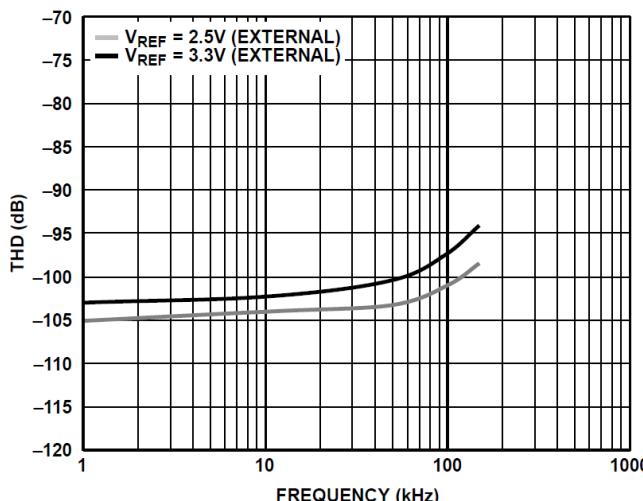

図12. THDと周波数の関係

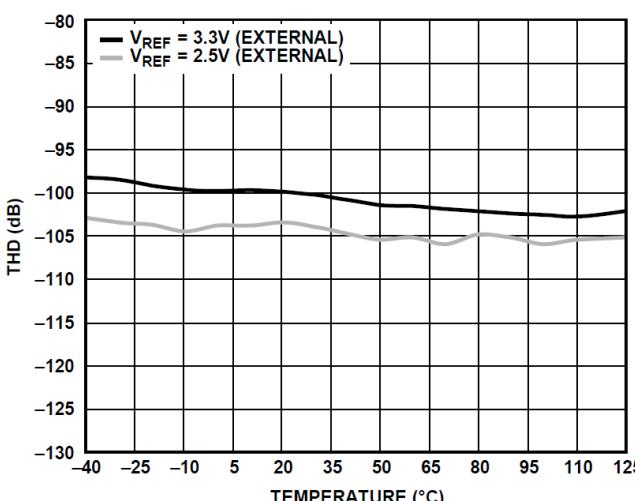

図15. THDと温度の関係

図16. SINADと温度の関係

20802-116

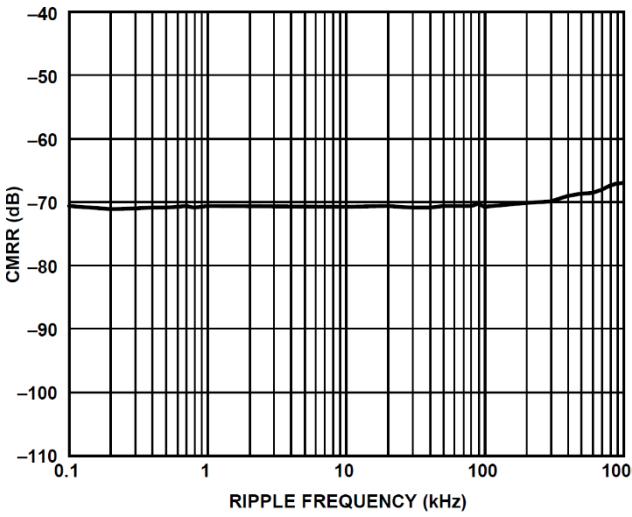

図19. CMRRとリップル周波数の関係

20802-119

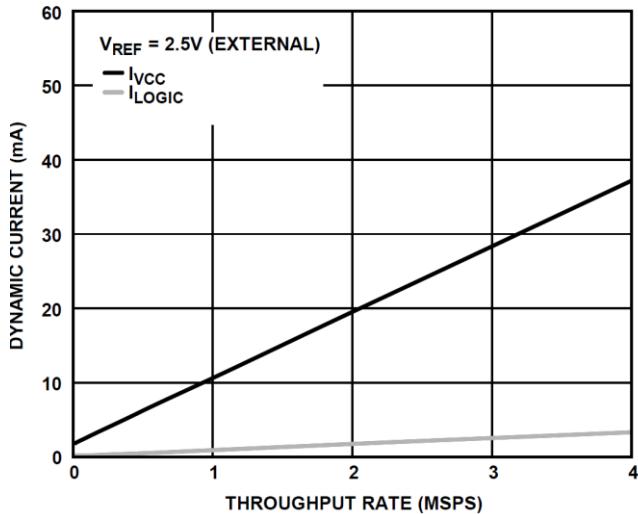

図17.動的電流とスループット・レートの関係

20802-117

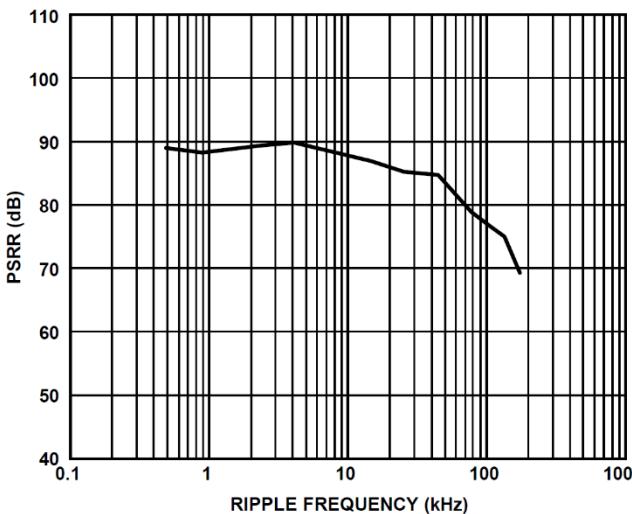

図20. PSRRとリップル周波数の関係

20802-120

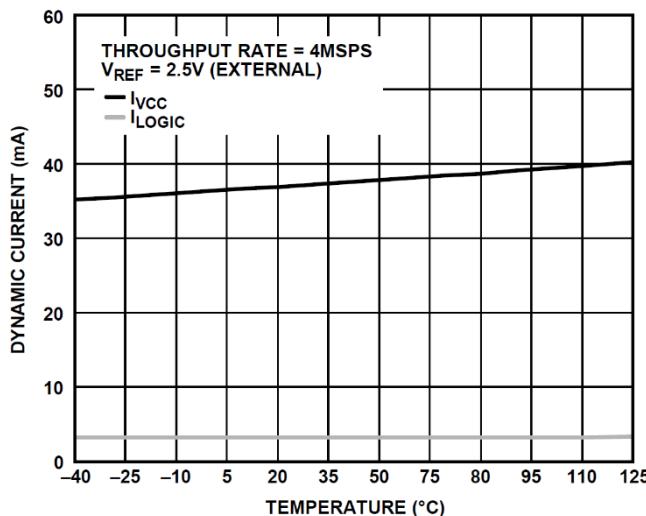

図18.動的電流と温度の関係

20802-118

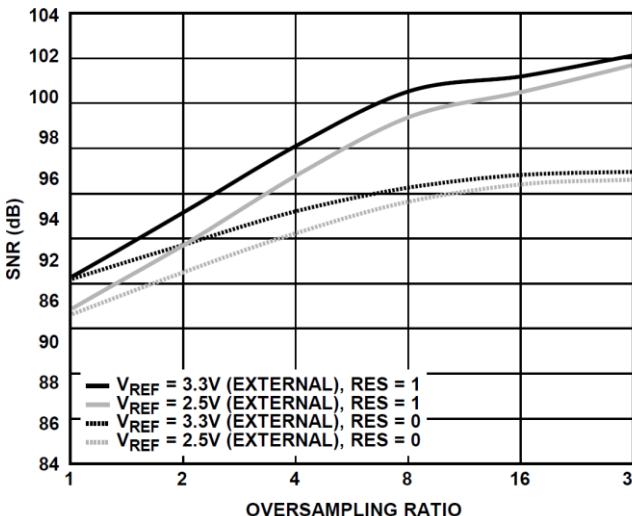

図21.相加平均オーバーサンプリング

20802-121

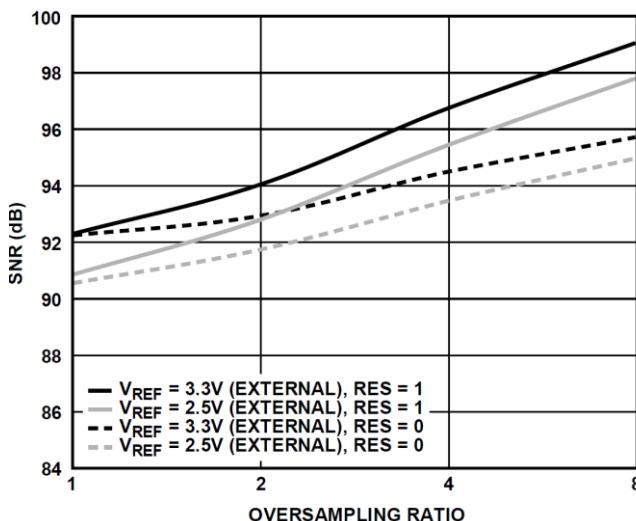

図22. 移動平均オーバーサンプリング

図24. DNLとコードの関係

図23. INLとコードの関係

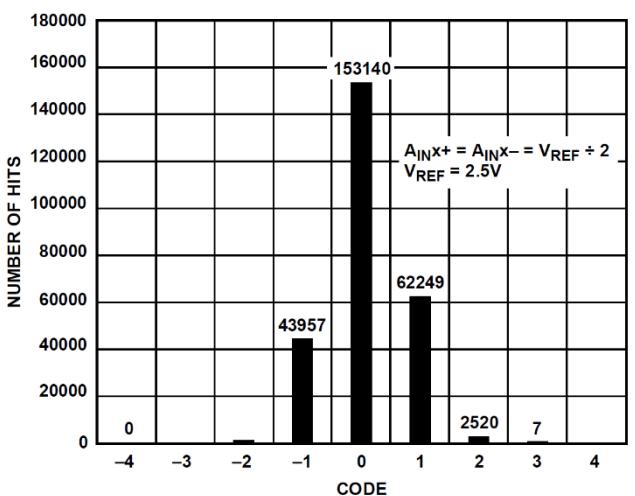

図25. ヒストグラム

## 用語の定義

### 微分非直線性 (DNL)

理想的なADCでは、コード遷移は1LSBだけ離れた位置で発生します。DNLとは、この理想値からの最大偏差のことです。多くの場合、DNLはノー・ミス・コードが確保される分解能で仕様規定されます。

### 積分非直線性 (INL)

INLは、負のフルスケールと正のフルスケールを結ぶ直線と個々のコードとの偏差です。最初のコード遷移より $\frac{1}{2}$ LSBだけ手前の点を負のフルスケールとして使います。正のフルスケールは、最後のコード遷移を $1\frac{1}{2}$ LSB上回ったレベルとして定義されます。偏差は各々のコードの中央から真の直線までの距離として測定されます。

### ゲイン誤差

最初の遷移 (100…000から100…001) は負の公称フルスケールより $\frac{1}{2}$ LSB上のレベルで発生します。最後の遷移 (011…110から011…111) は、公称フルスケールより $1\frac{1}{2}$ LSB低いアナログ電圧で発生します。ゲイン誤差とは、最後の遷移の実際のレベルと最初の遷移の実際のレベルとの差が、理論値レベルの差とどれだけ異なるかを示すものです。

### ゲイン誤差ドリフト

1°Cの温度変化あたりのゲイン誤差の変化。

### ゲイン誤差マッチング

ゲイン誤差マッチングは、負のフルスケール誤差の入力チャンネル間の差と正のフルスケール誤差の入力チャンネル間の差です。

### ゼロ誤差

ゼロ誤差は、理想的なミッドスケール電圧 (0V) とミッドスケール出力コード (0LSB) を生成する実際の電圧との差です。

### ゼロ誤差温度ドリフト

ゼロ誤差温度ドリフトは、1°Cの温度変化あたりのゼロ誤差の変化です。

### ゼロ誤差マッチング

ゼロ誤差マッチングは、入力チャンネル間のゼロ誤差の差です。

### S/N比 (SNR)

S/N比は、ナイキスト周波数を下回るすべてのスペクトル成分（高調波成分と直流成分を除く）の実効値総和に対する実際の入力信号の実効値の比です。S/N比の単位はデシベルです。

### スプリアスフリー・ダイナミック・レンジ (SFDR)

SFDRは、入力信号の実効値振幅とピーク・スプリアス信号との差で、単位はデシベル (dB) です。

### 全高調波歪み (THD)

THDは、フルスケール入力信号の実効値に対する最初の5個の高調波成分による実効値総和の比率で、単位はデシベルです。

### 信号ノノイズ+歪み (SINAD) 比

SINADは、ナイキスト周波数を下回るすべてのスペクトル成分の実効値総和（高調波成分は含むが、直流成分は除く）に対する実際の入力信号の実効値の比です。SINADの単位はデシベルです。

### 同相ノイズ除去比 (CMRR)

CMRRは、 $A_{INx+}$ と $A_{INx-}$ のコモンモード電圧に印加された周波数fの200mVp-pサイン波の電力に対する、周波数fのADC出力電力の比です。CMRRはデシベルで表されます。

$$CMRR = 10\log(P_{ADC\_IN}/P_{ADC\_OUT})$$

ここで、

$P_{ADC\_IN}$ は $A_{INx+}$ および $A_{INx-}$ 入力に印加される周波数fのコモンモード電力、

$P_{ADC\_OUT}$ は、周波数fでのADCの出力電力です。

### アーチャ・遅延

アーチャ遅延は、アクイジション性能の尺度で、 $\overline{CS}$ 入力の立下りエッジから入力信号が変換のために保持されるまでの時間です。

### アーチャ・ジッタ

アーチャ・ジッタはアーチャ遅延の変動です。

## 動作原理

### 回路説明

AD7380-4は、高速で完全差動の16ビット・クロックSAR A/Dコンバータです。このデバイスは、3.0V～3.6Vの電源で動作し、最大4MSPSのスループット・レートを特長としています。

AD7380-4は、逐次比較ADC4個と、個別のデータ出力ピン4本を備えたシリアル・インターフェース1個で構成されています。24ピンLFCSPに収容されており、各種代替ソリューションに比べてスペースを大幅に節約できるという利点をもたらします。

データにはデバイスのシリアル・インターフェースを介してアクセスできます。インターフェースは、2つ、4つまたは1つのシリアル出力で動作できます。AD7380-4は、2.5V～V<sub>CC</sub>の範囲の外部リファレンス電圧値を用います。差動アナログ入力範囲はV<sub>CM</sub> ± V<sub>REF</sub>/2です。

AD7380-4は、オーバーサンプリング・ブロックを内蔵することで性能を向上させています。相加平均オーバーサンプリング・モードと移動平均オーバーサンプリング・モードを使用可能です。変換の間の消費電力を節約できるパワーダウン・オプションも備わっています。デバイスの設定は、インターフェースのセクションで説明するように、標準的なシリアル・インターフェースを介して行なうことができます。

### コンバータの動作

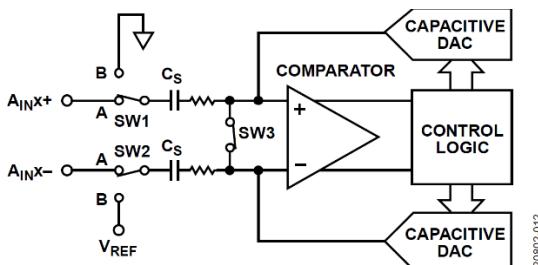

AD7380-4には4個の逐次比較ADCがあり、それぞれが2個の容量性DACを中心に構成されています。図26にこれらのADCの1つのアクイジション・フェーズの簡略化回路図、図27に変換フェーズの簡略化回路図を示します。ADCは、コントロール・ロジック、SAR、2個の容量性DACで構成されています。図26（アクイジション・フェーズ）では、SW3は閉じて、SW1とSW2は位置Aにあります。コンパレータは平衡状態を維持しており、サンプリング・コンデンサ（C<sub>S</sub>）アレイは入力で差動信号を取得できます。

図26. ADCアクイジション・フェーズ

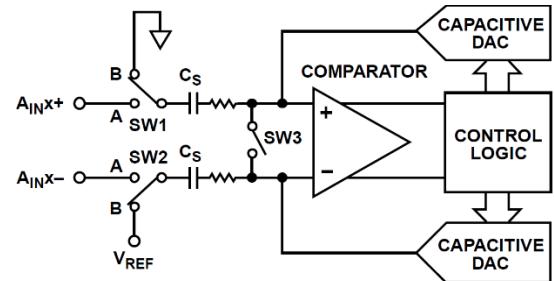

ADCが変換を開始すると（図27）、SW3が開いて、SW1とSW2が位置Bに移動し、コンパレータが非平衡状態になります。変換を開始すると、入力は両方とも切断されます。コントロール・ロジックと電荷再分配式DACを使って、サンプリング・コンデンサ・アレイに対して一定量の電荷を加算および減算して、コンパレータを平衡状態に戻すようにします。コンパレータが均衡状態に戻ると、変換が完了します。コントロール・ロジックはADCの出力コードを生成します。A\_INX+ピンおよびA\_INX-ピンの駆動源の出力インピーダンスはマッチングさせる必要があります。マッチングしていない場合、2つの入力のセトリング・タイムが異なり、誤差が生じます。

図27. ADC変換フェーズ

### アナログ入力構造

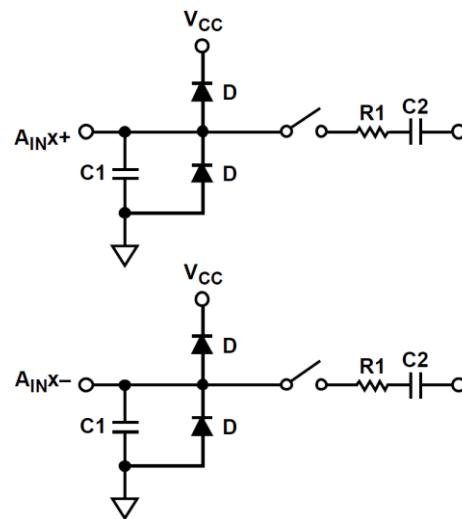

図28に、AD7380-4のアナログ入力構造の等価回路を示します。4個のダイオードにより、アナログ入力のESD保護機能を実現しています。アナログ入力信号が電源レールを300mV以上上回ることのないよう、注意する必要があります。この制限を超えると、ダイオードが順方向バイアスとなり、基板への導通が発生します。各ダイオードがデバイスに回復不能な損傷を与えない最大電流は10mAです。

図28に示すコンデンサC1は通常3pFで、主にピン容量によって決まります。抵抗R1はスイッチのオン抵抗で構成される集中定数コンポーネントです。この抵抗の値は通常約200Ωです。C2コンデンサはADCのサンプリング・コンデンサで、容量は15pF（代表値）です。

図28. 等価アナログ入力回路、変換フェーズ-スイッチ開、トラック・フェーズ-スイッチ閉

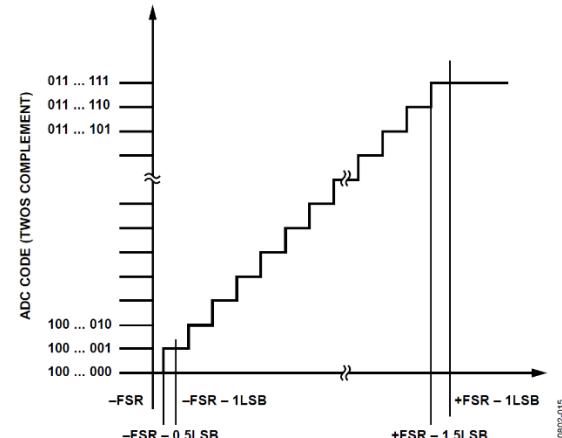

## ADCの伝達関数

AD7380-4では、2.5V～3.3Vのリファレンスを使用します。AD7380-4は、アナログ入力 ( $A_{INX+}$ および $A_{INX-}$ ) の差動電圧をデジタル出力に変換します。

変換結果はMSBファーストで、2の補数で表されます。 LSBの大きさは $(2 \times V_{REF})/2^N$ で、NはADCの分解能です。 ADCの分解能は、選択したデバイスの分解能と分解能増強モードが有効かどうかによって決まります。表9に、異なる分解能と異なるリファレンス電圧に対するLSBの大きさを、マイクロボルト単位で示します。

AD7380-4の理想伝達特性を図29に示します。

図29. ADCの理想的な伝達関数 (FSRはフルスケール・レンジ)

表 9. LSBの大きさ

| Resolution (Bits) | 2.5 V Reference ( $\mu$ V) | 3.3 V Reference ( $\mu$ V) |

|-------------------|----------------------------|----------------------------|

| 16                | 76.3                       | 100.7                      |

| 18                | 19.1                       | 25.2                       |

NOTES

1.  $V_-$  IS THE EXTERNAL SUPPLY VOLTAGE (-2.5V) FOR THE DRIVER AMPLIFIER.

2. PLACE DECOUPLING CAPACITORS CLOSE TO (IDEALLY, RIGHT UP AGAINST)

THE DEVICE SUPPLY PINS AND REFERENCE PIN.

20802-016

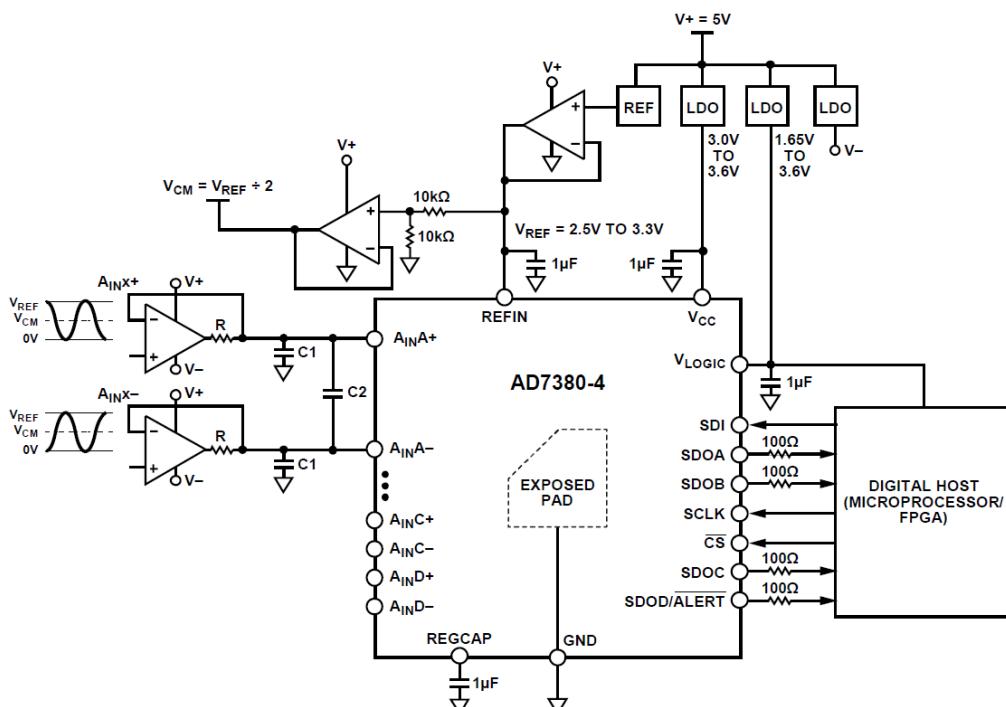

図30. 代表的なアプリケーション回路

## アプリケーション情報

AD7380-4の代表的なアプリケーション回路を図30に示します。図に示すように、V<sub>CC</sub>ピン、V<sub>LOGIC</sub>ピン、REGCAPピン、REFINピンを適切なデカップリング・コンデンサを用いてデカップリングします。露出パッドはデバイス上の回路のグラウンド基準ポイントとなるもので、ボードのグラウンドに接続する必要があります。

差動RCフィルタをアナログ入力に配置することで最適な性能を確保できます。代表的なアプリケーションでは、R = 33Ω、C<sub>1</sub> = 68pF、C<sub>2</sub> = 68pFとすることを推奨します。このRCの組み合わせは、AD7380-4の全チャンネルに対し同じである必要があります。

AD7380-4の4つの差動チャンネルは0V～V<sub>REF</sub>の入力電圧範囲に対応し、幅広いコモンモード電圧範囲を備えているため、様々な信号の変換が可能です。これらのアナログ入力ピン (A<sub>INX±</sub>) は、アンプを使用して容易に駆動できます。表10に、このアプリケーションに最適で付加価値を高める推奨ドライバ・アンプを示します。

AD7380-4の性能は、デジタル・インターフェースのノイズの影響を受ける可能性があります。この影響はボード・レイアウトと設計に依存します。デジタル・ラインとデジタル・インターフェースの距離を最小にするか、100Ωの抵抗をSDOAピン、SDOBピン、SDOCピン、SDOD/ALERTピンの近くに直列に配置して、AD7380-4にカップリングするデジタル・インターフェースからのノイズを抑制します。

AD7380-4のリファレンス電圧は2.5V～3.3Vの範囲です。ADR4533またはADR4525は、超低ノイズで高精度の電圧リファレンスで、AD7380-4のREFINピンの駆動用として推奨できます。1μFのリザーバ・コンデンサをREFINとグラウンドの間に接続することを推奨します。この外部リファレンス電圧をアプリケーション内の別の回路で用いる場合、例えば、ドライバ・アンプのコモンモード電圧として用いる場合、安定したリファレンスを実現するためにADA4807-2などのバッファ・アンプを用いることを推奨します。

### 電源

代表的なアプリケーションでは、図30のよう、AD7380-4の回路はシステムに給電する5V (V+) 電源で駆動できます。この5V (V+) は、ADP7104で供給できます。ADCドライバには、5V (V+) と反転チャージ・ポンプADP5600からの-2.5V (V-) が供給されます。このADP5600は5Vを-5Vに変換し、次いでこれをADP7182低ノイズ電圧レギュレータに送り-2.5Vを出力します。2つの個別の電源が低ドロップアウト・レギュレータから引き出され、AD7380-4のアナログ回路用のV<sub>CC</sub>電源およびデジタル・インターフェース用のV<sub>LOGIC</sub>電源に供給されます。ADP166のような静止電流が極めて小さいLDOレギュレータは、代表的なV<sub>CC</sub>およびV<sub>LOGIC</sub>レベルである1.2V～3.3Vの範囲の固定電圧を出力する最適な電源です。V<sub>CC</sub>電源とV<sub>LOGIC</sub>電源は1μFのコンデンサを使用して個別にデカップリングする必要があります。更に、LDOレギュレータもAD7380-4に電力を供給します。この内部レギュレータは、デバイスの内部使用専用に1.9V電源を供給します。REGCAPピンは、1μFのコンデンサでGNDからデカップリングします。

### パワーアップ

AD7380-4は、電源シーケンシングによって容易に損傷することはありません。V<sub>CC</sub>およびV<sub>LOGIC</sub>には、どのシーケンスでも印加できます。外部リファレンスは、V<sub>CC</sub>およびV<sub>LOGIC</sub>供給後に印加する必要があります。アナログ信号とデジタル信号は、外部リファレンス供給後に印加する必要があります。

AD7380-4では、V<sub>CC</sub>およびV<sub>LOGIC</sub>に印加してからADCの変換結果が安定するまでに、t<sub>POWERUP</sub>の時間が必要です。セットアップ時間が経過する前にAD7380-4にインターフェース接続を行っても、ADCの動作に悪影響はありません。パワーアップ時の推奨シグナル・コンディションについては図4を参照してください。パワーアップ後にソフトウェア・リセットを行うことを強く推奨します（詳細についてはソフトウェア・リセットのセクションを参照）。ただし、この間の変換結果は、データシートの仕様を満足していない可能性があります。

表 10. シグナル・チェーンの部品

| Companion Devices  | Part Name                 | Description                                                  | Typical Application                      |

|--------------------|---------------------------|--------------------------------------------------------------|------------------------------------------|

| ADC Driver         | <a href="#">ADA4896-2</a> | 1 nV/√Hz, rail to rail output amplifier                      | Precision, low noise, high frequency     |

|                    | <a href="#">ADA4940-2</a> | Ultra low power, full differential, low distortion amplifier | Precision, low density, low power        |

|                    | <a href="#">ADA4807-2</a> | 1 mA, rail to rail output amplifier                          | Precision, low power, high frequency     |

| External Reference | <a href="#">ADR4525</a>   | Ultralow noise, high accuracy voltage reference              | 2.5 V reference voltage                  |

|                    | <a href="#">ADR4533</a>   | Ultralow noise, high accuracy voltage reference              | 3.3 V reference voltage                  |

| Reference Buffer   | <a href="#">ADA4807-2</a> | 1 mA, rail to rail output amplifier                          | Precision, low power, high frequency     |

| LDO Regulator      | <a href="#">ADP166</a>    | Very low quiescent, 150 mA LDO regulator                     | 3.0 V to 3.6 V supply for VCC and VLOGIC |

|                    | <a href="#">ADP7104</a>   | 500 mA low noise, CMOS LDO regulator                         | 5 V supply                               |

|                    | <a href="#">ADP7182</a>   | Low noise line regulator                                     | -2.5 V supply for ADC driver amplifier   |

|                    | <a href="#">ADP5600</a>   | Interleaved inverting charge pump with negative LDO          | Voltage inverter for negative supply     |

## 動作モード

AD7380-4には、デバイスの動作モードを制御できる設定レジスタがいくつか内蔵されています。

### オーバーサンプリング

オーバーサンプリングは、アナログ電子機器において広く使用されている手法で、ADCの結果の精度を向上することができます。アナログ入力サンプルを複数取得して平均化することで、ADCの量子化ノイズや熱ノイズ (kTCノイズ) に由来するノイズ成分を削減します。AD7380-4には、オーバーサンプリング機能が内蔵されており、相加平均と移動平均の2つのオーバーサンプリング・モードをユーザ設定可能です。

このオーバーサンプリング機能は、CONFIGURATION 1レジスタのOS\_MODEビットとOSRビットをプログラムして設定します。

### 相加平均オーバーサンプリング

相加平均オーバーサンプリング・モードは、出力データ・レートが低くなることが許容されるアプリケーションと、S/N比やダイナミック・レンジが高いことが必要なアプリケーションで使用できます。相加平均には、多数のサンプリングを行い、それらを加算し、その結果をサンプリング数で除するというプロセスが含まれます。このプロセスの結果がデバイスから出力されます。プロセスが完了すると、サンプリングしたデータはクリアされます。

表 11. 相加平均オーバーサンプリングの概要

| OSR, Bits[2:0] | OS Ratio | SNR (dB Typical)         |                |                          |                | Data Output Rate (kSPS Maximum) |  |

|----------------|----------|--------------------------|----------------|--------------------------|----------------|---------------------------------|--|

|                |          | 2.5 V External Reference |                | 3.3 V External Reference |                |                                 |  |

|                |          | RES = 0                  | RES = 1        | RES = 0                  | RES = 1        |                                 |  |

| 000            | No OS    | 90.8                     | 90.8           | 92.5                     | 92.5           | 4000                            |  |

| 001            | 2        | 92                       | 93             | 94                       | 95.5           | 1500                            |  |

| 010            | 4        | 94                       | 96.5           | 95.2                     | 98.2           | 750                             |  |

| 011            | 8        | 95.8                     | 99.2           | 96.3                     | 100.5          | 375                             |  |

| 100            | 16       | 96.3                     | 100.4          | 96.8                     | 101.2          | 187.5                           |  |

| 101            | 32       | 96                       | 101.2          | 97                       | 102.2          | 93.75                           |  |

| 110            | Invalid  | Not applicable           | Not applicable | Not applicable           | Not applicable | Not applicable                  |  |

| 111            | Invalid  | Not applicable           | Not applicable | Not applicable           | Not applicable | Not applicable                  |  |

図31. 相加平均オーバーサンプリングの動作

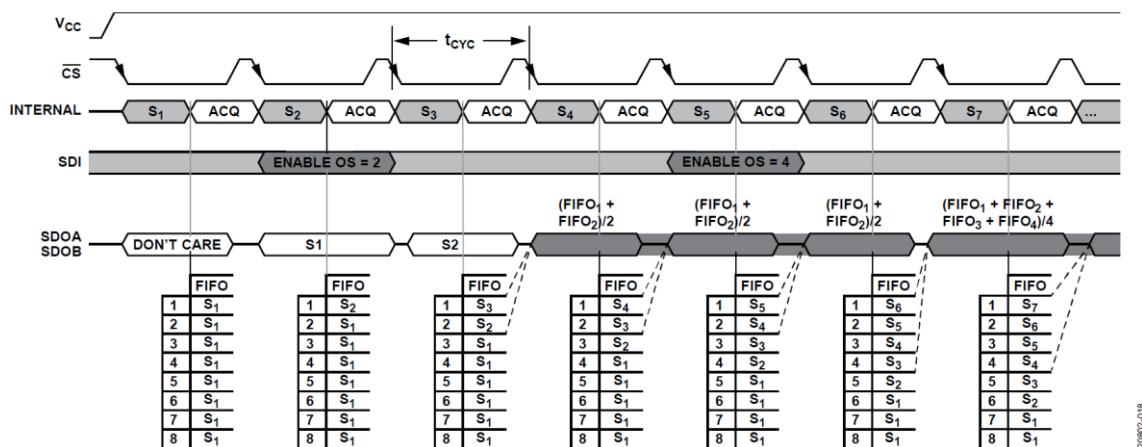

## 移動平均オーバーサンプリング

移動平均オーバーサンプリング・モードは、出力データ・レートを高くすることが必要なアプリケーションと、S/N比やダイナミック・レンジが高いことが必要なアプリケーションで使用できます。移動平均オーバーサンプリングは、多数のサンプリングを行い、それらを加算し、その結果をサンプリング数で除するというプロセスで構成されます。このプロセスの結果がデバイスから出力されます。プロセスが完了しても、サンプリングしたデータはクリアされません。移動平均オーバーサンプリング・モードでは、平均計算において、最新のサンプルの先入れ先出し (FIFO) バッファを使用し、それによりADCスループット・レートと出力データ・レートを同じ状態に維持できます。

移動平均オーバーサンプリング・モードは、OS\_MODEビットをロジック1にし、OSRビットを有効な非ゼロ値とすることで設定されます。デジタル・フィルタのオーバーサンプリング比は、オーバーサンプリング・ビットOSRを使用して制御します（表12参照）。

各種オーバーサンプリング・レートを選択するためのオーバーサンプリング・ビットのデコードを表12に示します。出力結果は、AD7380-4用に16ビットの分解能にデシメートされます。必要に応

表 12. 移動平均オーバーサンプリングの概要

| OSR, Bits[2:0] | OS Ratio        | SNR (dB Typical)         |                |                          |                | Data Output Rate (kSPS Maximum) |  |

|----------------|-----------------|--------------------------|----------------|--------------------------|----------------|---------------------------------|--|

|                |                 | 2.5 V External Reference |                | 3.3 V External Reference |                |                                 |  |

|                |                 | RES = 0                  | RES = 1        | RES = 0                  | RES = 1        |                                 |  |

| 000            | No oversampling | 91                       | 91             | 92.5                     | 92.5           | 4000                            |  |

| 001            | 2               | 92                       | 93             | 93                       | 94             | 4000                            |  |

| 010            | 4               | 94                       | 95.4           | 95                       | 97             | 4000                            |  |

| 011            | 8               | 95.5                     | 98             | 97                       | 99             | 4000                            |  |

| 110            | Invalid         | Not applicable           | Not applicable | Not applicable           | Not applicable | Not applicable                  |  |

| 111            | Invalid         | Not applicable           | Not applicable | Not applicable           | Not applicable | Not applicable                  |  |

図32. 移動平均オーバーサンプリング・モードの設定

## 分解能増強

AD7380-4の分解能と出力データ・サイズのデフォルト値は16ビットです。内蔵のオーバーサンプリング機能を有効化すると、このデフォルトの分解能を上回るADC性能が可能になります。この性能向上を実現するために、2ビットの分解能を追加することができます。CONFIGURATION 1レジスタのRESビットをロジック1に設定し、AD7380-4を有効なオーバーサンプリング・モードにした場合、AD7380-4の変換結果のサイズは18ビットになります。このモードでは、AD7380-4のデータを伝搬するために18SCLKサイクルが必要です。

## アラート

アラート機能は範囲外インジケータで、変換結果が範囲を外れたことを示す初期インジケータとして使用できます。変換結果レジスタの値がアラート上限閾値レジスタのアラート上限値を超えた場合、またはアラート下限閾値レジスタのアラート下限値を下回った場合にアラート・イベントがトリガされます。アラート上限閾値レジスタとアラート下限閾値レジスタは、すべてのADCに共通です。閾値を設定する際には、アラートの上限閾値は常に下限閾値より大きな値にする必要があります。詳細なアラート情報には、アラート表示レジスタでアクセスできます。

このレジスタにはADCあたり2つのステータス・ビットがあり、1つは上限、もう1つは下限に対応しています。すべてのADCのア

ラート信号の論理ORにより、共通のアラート値が作成されます。この値は、SDOD/ALERTピンのALERT機能で出力されるよう設定できます。SDOD/ALERTピンは、CONFIGURATION 1レジスタおよびCONFIGURATION 2レジスタの次のビットを設定することで、ALERTに設定できます。

- SDOビットを0b10以外の任意の値に設定。

- ALERT\_ENビットを1に設定。

- アラート上限閾値レジスタとアラート下限閾値レジスタに有効な値を設定。

アラート表示機能はオーバーサンプリング（移動平均モード、相加平均モード、および非オーバーサンプリング・モード）で使用できます。

SDOD/ALERTピンのアラート機能は、変換の終了時に更新されます。ALERTレジスタのアラート表示ステータス・ビットも更新され、次の変換の終了前に読み出す必要があります。

アラート表示レジスタのビット[7:0]は、アラート表示レジスタの内容を読み出すとクリアされます。SDOD/ALERTピンのアラート機能は、CSの立下がりエッジでクリアされます。ソフトウェア・リセットを発行しても、アラート表示レジスタのアラート・ステータスをクリアできます。

ALERTのタイミング図については、図8を参照してください。

図33. 分解能増強

20802-019

## 電力モード

AD7380-4では、ノーマル・モードとシャットダウン・モードの2つの電力モードをCONFIGURATION 1レジスタで設定できます。これらの動作モードによって、柔軟なパワー・マネージメント・オプションが提供されるため、様々なアプリケーション条件に対して消費電力とスループット・レートの比を最適化できます。

AD7380-4の電力モードを設定するには、CONFIGURATION 1レジスタのPMODEビットをプログラムします。PMODEをロジック0に設定するとノーマル・モード、ロジック1に設定するとシャットダウン・モードになります。

### ノーマル・モード

スループット・レートを最高速にするには、AD7380-4をノーマル・モードに維持します。AD7380-4内の全プロックが常にフルパワーとなり、ADC変換は必要に応じてCSの立下がりエッジで開始できます。AD7380-4が変換を行っていない場合は、デバイスは静的モードになり、消費電力は自動的に削減されます。変換を実行するには、追加電流が必要となります。そのため、AD7380-4の消費電力はスループットに応じて増加します。

### シャットダウン・モード

スループット・レートを下げて消費電力を抑制する必要がある場合は、シャットダウン・モードを使用します。シャットダウン・モードにするには、各変換の間にADCをパワーダウンするか、高スループット・レートで一連の変換を実行した後、これらのバースト変換の間に比較的長い時間ADCをパワーダウンします。AD7380-4がシャットダウン・モードになると、すべてのアナログ回路がパワーダウンされます。シリアル・インターフェースはシャットダウン・モードの間もアクティブ状態のままなので、AD7380-4はシャットダウン・モードを終了することができます。

シャットダウン・モードに移行するには、CONFIGURATION 1レジスタの電力モード設定ビットPMODEに書き込みを行います。

AD7380-4は停止し、消費電流が削減されます。シャットダウン・モードを終了しノーマル・モードに戻るには、CONFIGURATION 1レジスタのPMODEビットをロジック0に設定します。すべての

レジスタ設定は、シャットダウン・モードを開始しても終了しても変わりません。シャットダウン・モードの終了後、回路がオンになってから変換を開始するまでには、十分な時間が必要です。

## 外部リファレンス

ADC変換時、AD7380-4のコアはREFINピンの電圧を参照します。AD7380-4のリファレンス電圧は、REFINピンを通じて駆動されます。このピンには2.5V～3.3Vの電圧範囲で供給できます。外部リファレンス電圧は、最大電流が1.2mAであるAD7380-4を駆動できるだけの電流を流せる必要があります。REFINピンには1μFのコンデンサを接続することを推奨します。推奨する外部電圧リファレンスは、2.5Vの場合はADR4525、3.3Vの場合はADR4533です。

## ソフトウェア・リセット

AD7380-4には、ソフト・リセットとハード・リセットの2つのリセット・モードがあります。リセットは、CONFIGURATION 2レジスタのリセット・ビットに書き込むことで開始できます。

ソフト・リセットは、設定可能なレジスタの内容を保持しますが、インターフェースとADCプロックを更新します。すべての内蔵ステート・マシンは再初期化され、オーバーサンプリング・プロックとFIFOは消去されます。アラート表示レジスタはクリアされます。リファレンスとLDOレギュレータの電源は供給されたままでです。

ハード・リセットでは、ソフト・リセットでリセットされるプロックの他、すべてのユーザ・レジスタがデフォルト状態にリセットされ、内部発振器プロックもリセットされます。

## 診断セルフ・テスト

AD7380-4は、POR後またはソフトウェア・ハード・リセット後に診断セルフ・テストを実行し、設定が正しくデバイスにロードされるようにします。

セルフ・テストの結果は、アラート表示レジスタのSETUP\_Fビットに示されます。SETUP\_Fビットがロジック1にセットされた場合、診断セルフ・テストは不合格です。不合格になった場合、ソフトウェア・ハード・リセットが実行され、AD7380-4のレジスタはデフォルト状態にリセットされます。

図34. シャットダウン・モード動作

図35. ソフトウェア・リセット動作

## インターフェース

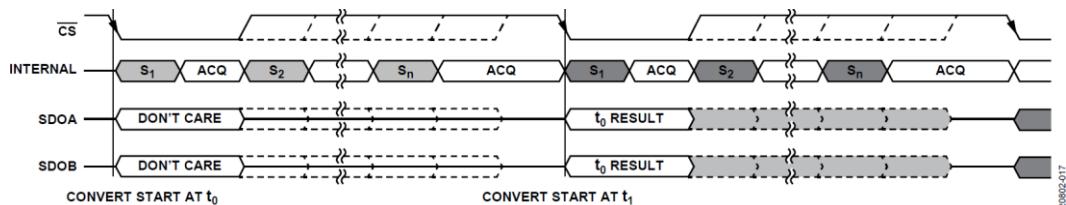

AD7380-4へのインターフェース接続は、シリアル・インターフェースを通じて行います。インターフェースは、 $\overline{CS}$ 、SCLK、SDOA、SDOB、SDOC、SDOD、SDIで構成されています。多機能ピンの特定の機能について説明した箇所では、「SDOD」のように、仕様に関係するピン名のみを示しています。多機能ピンのすべての機能を含むピン名については、ピン配置およびピン機能の説明のセクションを参照してください。

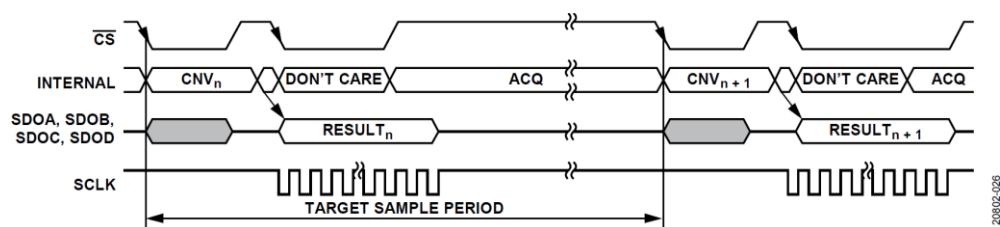

$\overline{CS}$ 信号は、シリアル・データ転送をフレーミングし、ADC変換プロセスを開始します。 $\overline{CS}$ の立下がりエッジは、アナログ入力がサンプリングされた時点でトラック&ホールドをホールド・モードにし、バスはスリーステートから取られます。ADCの変換動作は内部発振器によって駆動され、SCLK信号には依存しません。

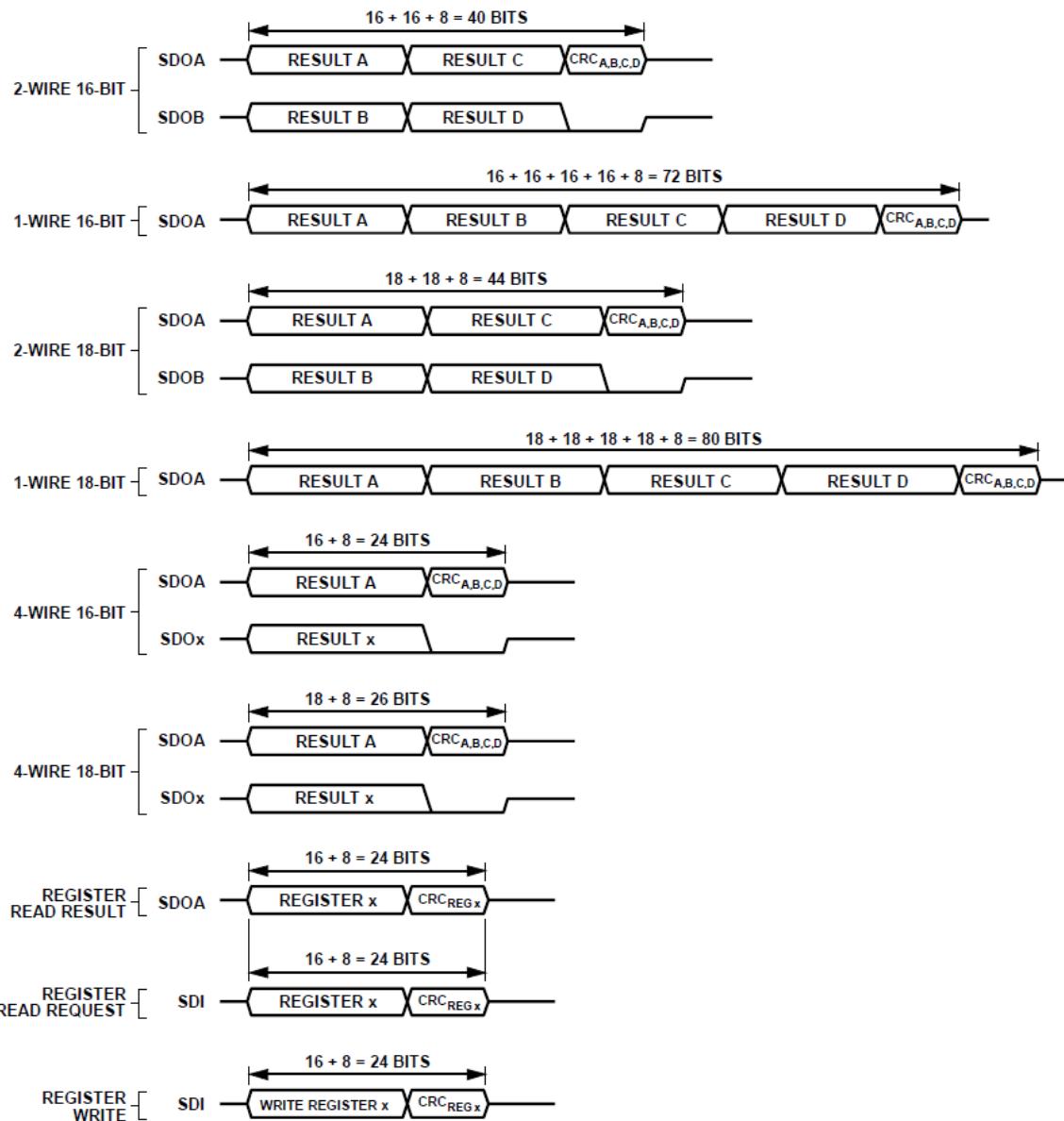

SCLK信号は、SDOA、SDOB、SDOC、SDOD、SDIの各信号を通じて、データをデバイスに同期させたり、同期を解除したりします。レジスタからの読み書きを行うには、16SCLKサイクル以上が必要です。変換の読み出しに必要なSCLKサイクルの最小数は、デバイスの分解能と構成設定に依存します（表13参照）。

AD7380-4には、SDOA、SDOB、SDOC、SDODの4本のシリアル出力ピンがあります。CONFIGURATION 2レジスタのSDOビットを設定することで、2線モード、1線モード、あるいは4線モードに設定できます。最大スループットを実現するには、2線モードまたは4線モードで使用して変換結果を読み出す必要があります。スループットを下げる必要がある場合や、オーバーサンプリングを使用する場合は、SDOA信号のみを使用する1線モードで変換結果を読み出すことができます。

分解能増強モードが有効な状態で、SPI読み出しやSPI書き込み、オーバーサンプリング・モードに巡回冗長性チェック（CRC）動作を設定すると、インターフェースの動作が変わることがあります。正しい動作を確保するためにはCRCのセクションを参照してください。

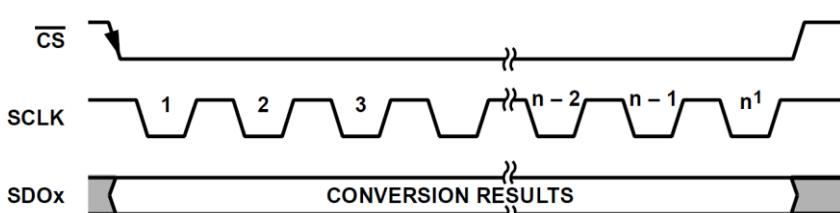

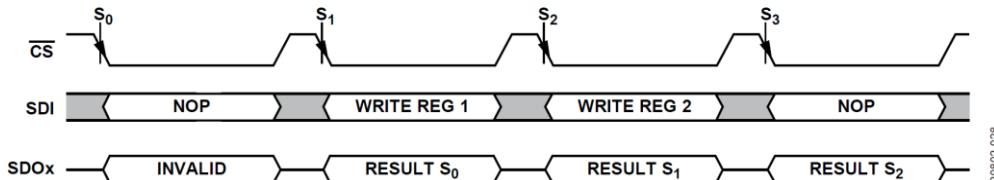

### 変換結果の読み出し

$\overline{CS}$ 信号によって変換プロセスが開始されます。 $\overline{CS}$ 信号がハイからローに遷移すると、ADC A、ADC B、ADC C、ADC Dの4つのADCが同時に変換を開始します。AD7380-4には1サイクルのリードバック遅延があります。そのため、変換結果は次のSPIアクセス

で使用できます。次いで、 $\overline{CS}$ 信号をローで受けると、変換結果がシリアル出力ピンにクロックに同期して出力されます。次の変換もこの時点で開始されます。

変換結果は、AD7380-4の16ビットの結果としてデバイスからシフト出力されます。変換結果のMSBは、 $\overline{CS}$ の立下がりエッジでシフト出力されます。その他のデータは、シリアル・クロック（SCLK）入力の制御の下でデバイスからシフト出力されます。データはSCLKの立上がりエッジでシフト出力され、データ・ビットは立上がりエッジと立下がりエッジの両方で有効です。SCLKの最後の立下がりエッジの後、再度 $\overline{CS}$ をハイで受けると、シリアル・データ出力ピンは高インピーダンス状態に戻ります。

変換結果をシリアル・データ出力ピンに伝搬するのに必要なSCLKサイクル数は、設定されるシリアル動作モード、および分解能増強モードが有効かどうかによって異なります（詳細は、図36および表13を参照）。CRC読み出しが有効になっている場合、CRC情報を伝搬するには、追加のSCLKパルスが必要です。詳細についてはCRCのセクションを参照してください。

$\overline{CS}$ 信号によって変換が開始され、データがフレーミングされるため、すべてのデータ・アクセスは1つのフレーム内で完了する必要があります。

表 13. 変換結果の読み出しに必要なSCLKサイクル数（n）

| Interface Configuration | Resolution Boost Mode | CRC Read | No. of SCLK Cycles |

|-------------------------|-----------------------|----------|--------------------|

| 4-Wire                  | Disabled              | Disabled | 16                 |

|                         |                       | Enabled  | 24                 |

|                         | Enabled               | Disabled | 18                 |

|                         |                       | Enabled  | 26                 |

| 2-Wire                  | Disabled              | Disabled | 32                 |

|                         |                       | Enabled  | 40                 |

|                         | Enabled               | Disabled | 36                 |

|                         |                       | Enabled  | 44                 |

| 1-Wire                  | Disabled              | Disabled | 64                 |

|                         |                       | Enabled  | 72                 |

|                         | Enabled               | Disabled | 72                 |

|                         |                       | Enabled  | 80                 |

1CONSULT TABLE 12 FOR VALUES FOR n, THE NUMBER OF SCLK PULSES REQUIRED.

図36. 変換結果の読み出し

20802-223

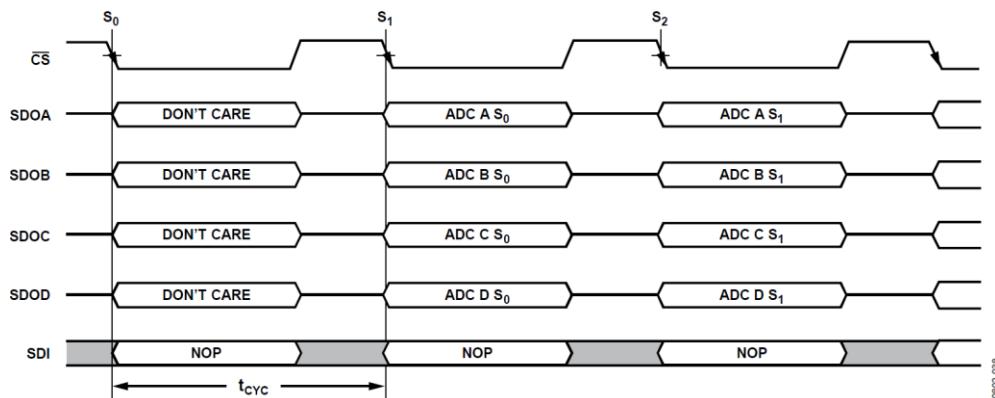

### シリアル4線モード

4線モードに設定するには、CONFIGURATION 2レジスタのSDOビットを0b10に設定します。4線モードでは、ADC Aの変換結果がSDOA、ADC Bの変換結果がSDOB、ADC Cの変換結果がSDOC、ADC Dの変換結果がSDODに出力されます。

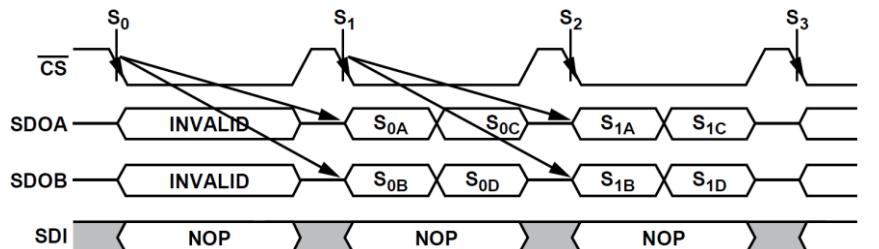

### シリアル2線モード

2線モードに設定するには、CONFIGURATION 2レジスタのSDOビットを0b00に設定します。2線モードでは、ADC AとADC Cの変換結果がSDOAに出力されます。ADC BとADC Dの変換結果はSDOBに出力されます。

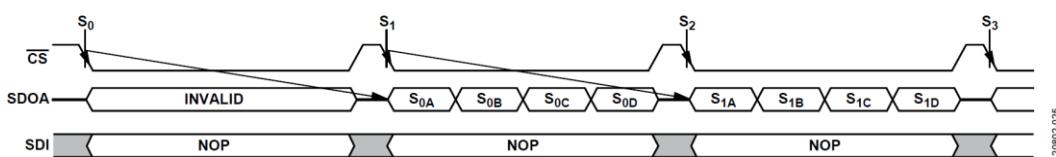

### シリアル1線モード

スループット・レートが遅くても構わないアプリケーションや、相加平均オーバーサンプリングを使用するアプリケーションで

は、1線モードで動作するようシリアル・インターフェースを設定できます。1線モードでは、ADC A、ADC B、ADC C、ADC Dの変換結果がSDOAに出力されます。すべてのデータを伝搬するには、追加のSCLKサイクルが必要です。まずADC Aのデータが出力され、次いでADC B、ADC C、ADC Dの変換結果が出力されます。

### 低遅延リードバック

AD7380-4のインターフェースには、図38に示すように、1サイクル分の遅延があります。低スループット・レートで動作するアプリケーションの場合、変換結果の読み出しの遅延を減少できます。変換時間 ( $t_{CONVERT}$ ) の終了後、変換を開始した最初の $\overline{CS}$ パルス後の2番目の $\overline{CS}$ パルスを使用して、変換結果をリードバックできます。この動作を図40に示します。

図37. 変換結果の読み出し、4線モード

図38. 変換結果の読み出し、2線モード

図39. 変換結果の読み出し、1線モード

図40. 低スループットでの低遅延

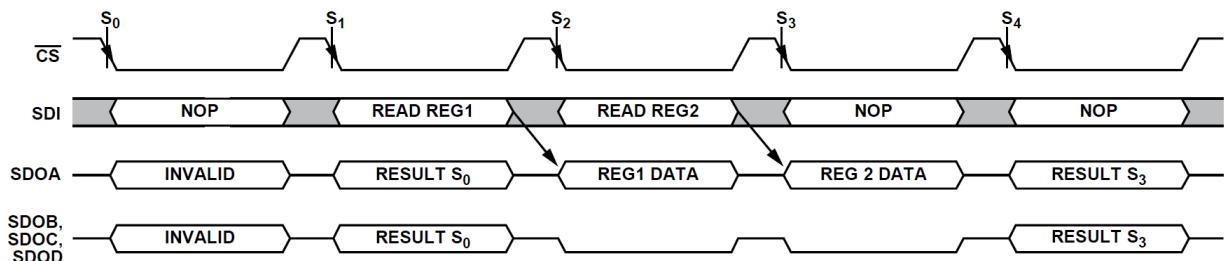

## デバイス・レジスタからの読出し

デバイス内のすべてのレジスタは、シリアル・インターフェースを介して読み出すことができます。レジスタを読み出すには、レジスタの読み出しコマンドを発行した後、有効なコマンドまたは無操作コマンド (NOP) のいずれかの追加SPIコマンドを発行します。読み出しコマンドのフォーマットを表16に示します。読み出しコマンドを選択するには、ビットD15を0に設定する必要があります。ビット[D14:D12]には、レジスタのアドレスが格納されます。後続の12ビット (ビット[D11:D0]) は無視されます。

## デバイス・レジスタへの書き込み

AD7380-4のすべてのリード/ライト・レジスタには、シリアル・インターフェースを介して書き込むことができます。SPIの書き込みアクセスの長さは、CRCの書き込み機能によって決まります。SPIアクセスは、CRCの書き込みが無効な場合は16ビット、CRC書き込みが有効な場合は24ビットです。書き込みコマンドのフォーマットを表16に示します。書き込みコマンドを選択するには、ビットD15を1に設定する必要があります。ビット[D14:D12]には、レジスタのアドレスが格納されます。後続の12ビット (ビット[D11:D0]) には、選択したレジスタに書き込むデータが格納されます。

## CRC

AD7380-4にはCRCチェックサム・モードがあり、これを使用してデータ伝送中のエラーを検出することで、インターフェースの堅牢性を向上させることができます。CRC機能は、SPIインターフェースの読み出しと書き込みに対して個別に選択できます。例えば、SPI書き込みにはCRC機能を有効化してデバイス設定の予期しない変更を防止する一方、SPI読み出しに対してはCRC機能を有効化せずに高いスループットを維持することができます。CRC機能は、CONFIGURATION 1レジスタのCRC\_WビットとCRC\_Rビットを設定することで制御できます。

### CRC読み出し

有効化すると、変換結果またはレジスタ読み出しに8ビットからなるCRCが付加されます。CRCはADC A、ADC B、ADC C、ADC Dの変換結果で計算され、SDOAに出力されます。また、CRCはレジスタ読み出し出力についても計算され、付加されます。

CRC読み出し機能は、2線SPIモード、1線SPIモード、4線SPIモード、分解能増強モードで使用できます。

図41. レジスタ読み出し

図42. レジスタ書き込み

**CRC書き込み**

CRC書き込み機能を有効化するには、CONFIGURATION 1レジスタのCRC\_Wビットを1に設定する必要があります。CRC\_Wビットを1に設定してCRC機能を有効化するには、リクエスト・フレームに有効なCRCが付加されていることが必要です。

CRC機能が有効化されると、有効なCRCコマンドを備えていない限りすべてのレジスタ書き込みリクエストは無視されます。有効なCRCは、CRC書き込み機能を有効にする場合にも無効にする場合にも必要です。

**CRC多項式**

CRCチェックサム計算では、常に多項式 $x^8 + x^2 + x + 1$ が使用されます。

チェックサムを生成するには、4つのチャンネルの16ビット・データの変換結果を結合し、64ビットのデータ・ストリームを作成します。この64ビット・データの8個のMSBが反転され、8ビット

分だけデータが付加され8個のロジック0で終わる数が作成されます。多項式のMSBが、データの最も左のロジック1と隣り合うように、多項式の値の位置決めを実行します。次に、排他的論理和(XOR)関数をデータに適用してより短い数値を新たに生成し、再度、多項式のMSBが、得られたデータの最も左にあるロジック1と隣り合うように、多項式の値の位置決めを実行します。このプロセスを、元のデータが多項式の値(8ビット・チェックサム)よりも小さくなるまで繰り返します。

例えば、AD7380-4の多項式が100000111で、4つのチャンネルの元の値が0xAAAA、0x5555、0xAAAA、0x5555であるとします。データの8個のMSBが反転されます。次に、データが追加され、右に8個の0を含むようになります。最後のXOR操作では、計算結果(余り)が多項式より小さくなっています。

したがって、この余りが、仮定したデータのCRCとなります。

**表 14. 4チャンネル、16ビット・データのCRC計算の例**

| Data         | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | X <sup>1</sup> |   |   |

|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------------|----------------|----------------|----------------|----------------|----------------|---|---|

| Process Data | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1              | 0              | 0              | 0              | 0              | 0              | 0 |   |

|              | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |   |   |   |   |   |   |   |   |   |   |   |                |                |                |                |                |                |   |   |

|              |   | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |   |   |   |   |   |   |   |   |   |   |                |                |                |                |                |                |   |   |

|              |   | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |   |   |   |   |   |   |   |   |   |   |   |                |                |                |                |                |                |   |   |

|              |   |   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |   |   |   |   |   |   |   |   |   |                |                |                |                |                |                |   |   |

|              |   |   |   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |   |   |   |   |   |   |   |   |                |                |                |                |                |                |   |   |

|              |   |   |   |   | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |   |   |   |   |   |   |   |                |                |                |                |                |                |   |   |

|              |   |   |   |   |   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |   |   |   |   |   |   |                |                |                |                |                |                |   |   |

|              |   |   |   |   |   |   | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0              | 1              | 0              | 0              | 0              | 0              | 0 |   |

|              |   |   |   |   |   |   |   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |   |   |   |                |                |                |                |                |                |   |   |

|              |   |   |   |   |   |   |   |   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |   |   |                |                |                |                |                |                |   |   |

|              |   |   |   |   |   |   |   |   |   | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0              | 1              | 0              | 0              | 0              | 0              |   |   |

|              |   |   |   |   |   |   |   |   |   |   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0              | 1              | 1              | 1              | 1              | 1              |   |   |

|              |   |   |   |   |   |   |   |   |   |   |   | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1              | 1              | 0              | 0              | 0              | 0              | 0 |   |

|              |   |   |   |   |   |   |   |   |   |   |   |   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1              | 1              | 0              | 0              | 0              | 0              | 0 |   |

|              |   |   |   |   |   |   |   |   |   |   |   |   |   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1              | 1              | 1              | 0              | 0              | 0              | 0 | 0 |

| CRC          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                |                |                |                |                |                |   |   |

1 Xは、ドント・ケアを意味します。

20002-000

図43. CRCの動作

## レジスタ

AD7380-4にはデバイス設定用に、ユーザ設定可能なレジスタが内蔵されています。表15に、AD7380-4で使用可能な全レジスタの概要を示します。

レジスタは、読み出し／書き込み (R/W) または読み出し専用 (R) です。書き込み専用レジスタへの読み出しリクエストは無視されます。読み出し専用レジスタへの書き込みリクエストは無視されます。NOPレジスタと予備レジスタへの書き込みは無視されます。NOPレジスタまたは予備レジスタへの読み出しリクエストは無操作とみなされ、次のSPIフレームで送信されるデータは変換結果となります。

表 15. レジスタの説明

| Reg | Name                 | Bits   | Bit 15    | Bit 14         | Bit 13                | Bit 12   | Bit 11    | Bit 10                 | Bit 9     | Bit 8          | Reset      | R/W    |     |

|-----|----------------------|--------|-----------|----------------|-----------------------|----------|-----------|------------------------|-----------|----------------|------------|--------|-----|

|     |                      |        | Bit 7     | Bit 6          | Bit 5                 | Bit 4    | Bit 3     | Bit 2                  | Bit 1     | Bit 0          |            |        |     |

| 0x1 | Configuration 1      | [15:8] | WR        |                | ADDRESSING            |          |           | RESERVED               |           | OS_MODE        | OSR, Bit 2 |        |     |

|     |                      | [7:0]  |           | OSR, Bits[1:0] | CRC_W                 | CRC_R    | ALERTEN   | RES                    | RESERVED  | PMODE          |            |        |     |

| 0x2 | Configuration 2      | [15:8] | WR        |                | ADDRESSING            |          |           | RESERVED               |           | SDO, Bits[1:0] |            | 0x0000 | R/W |

|     |                      | [7:0]  |           |                | RESET, Bits[7:0]      |          |           |                        |           |                |            |        |     |

| 0x3 | Alert                | [15:8] | WR        |                | ADDRESSING            |          |           | RESERVED               |           | CRCW_F         | SETUP_F    | 0x0000 | R   |

|     |                      | [7:0]  | AI_D_HIGH | AI_D_LOW       | AI_C_HIGH             | AI_C_LOW | AI_B_HIGH | AI_B_LOW               | AI_A_HIGH | AI_A_LOW       |            |        |     |

| 0x4 | Alert Low threshold  | [15:8] | WR        |                | ADDRESSING            |          |           | ALERT_LOW, Bits[11:8]  |           |                |            | 0x0800 | R   |

|     |                      | [7:0]  |           |                | ALERT_LOW, Bits[7:0]  |          |           |                        |           |                |            |        |     |

| 0x5 | Alert high threshold | [15:8] | WR        |                | ADDRESSING            |          |           | ALERT_HIGH, Bits[11:8] |           |                |            | 0x07FF | R/W |

|     |                      | [7:0]  |           |                | ALERT_HIGH, Bits[7:0] |          |           |                        |           |                |            |        |     |

## アドレス指定レジスタ

AD7380-4でのシリアル・レジスタ転送は、16のSCLKサイクルで構成されます。デバイスに書き込まれた4つのMSBがデコードされ、どのレジスタのアドレスが指定されているかが判定されます。この4つのMSBは、レジスタ・アドレス (REGADDR)、ビット[2:0]、および読み出し／書き込みビット (WR) で構成されます。レジスタ・アドレス・ビットは、どのオンチップ・レジスタが選択されるかを指定します。アドレス指定されたレジスタが有効な書き込みレジスタの場合、WRビットは、指定されたレジスタにSDI入力の残りの12ビット・データをロードするかどうかを決めます。WRビットが1の場合、レジスタ選択ビットによって指定されたレジスタにビットがロードされます。WRビットが0の場合、このコマンドは読み出しリクエストとみなされます。アドレス指定されたレジスタのデータは、次の読み出し操作中に読み出することができます。

表 16. アドレス指定レジスタのフォーマット

| MSB |                    |     |     |     |     |    |    |    |    |    |    |    |    |    | LSB              |

|-----|--------------------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|------------------|

| D15 | D14                | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0               |

| WR  | REGADDR, Bits[2:0] |     |     |     |     |    |    |    |    |    |    |    |    |    | Data, Bits[11:0] |

表 17. アドレス指定レジスタのビットの説明

| ビット        | ビット名    | 説明                                                                                                                                                                                                                                          |

|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15        | WR      | このビットに1が書き込まれていると、このレジスタのビット[11:0]をREGADDRで指定されるレジスタに書き込みます（ただし、そのレジスタのアドレスが有効な場合）。<br>代わりに、0が書き込まれていると、次にSDOAピンに送信するデータを指定されたレジスタから読み出します（ただし、そのレジスタのアドレスが有効な場合）。                                                                          |

| D14 to D12 | REGADDR | WR = 1の場合、REGADDRの内容によって、表15に示したレジスタの中から選択されます。<br>WR = 0でREGADDRビットに有効なレジスタ・アドレスが格納されている場合、指定されたレジスタの内容が次のインターフェース・アクセス時にSDOAピンに出力されます。<br>WR = 0でREGADDRに0x0, 0x6, 0x7のいずれかが格納されている場合、SDIラインの内容は無視され、次のインターフェース・アクセスによって、変換結果がリードバックされます。 |

| D11 to D0  | Data    | WRビットが1でREGADDRビットに有効なアドレスが格納されている場合、これらのビットは、REGADDRビットによって指定されたレジスタに書き込まれます。                                                                                                                                                              |

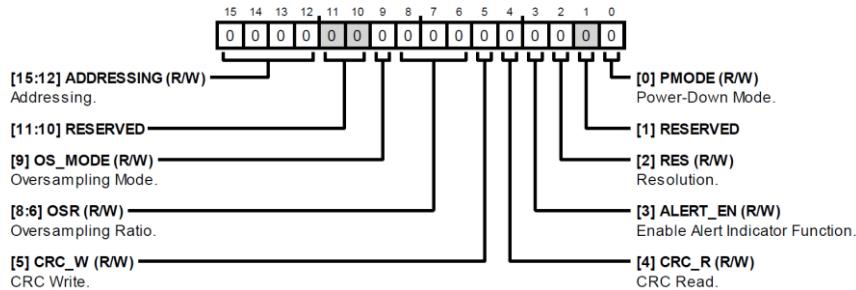

## CONFIGURATION 1レジスタ

表 18. CONFIGURATION 1レジスタのビットの説明

| ビット     | ビット名       | 説明                                                                                                                                                                                                                                         | リセット | アクセス |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| [15:12] | ADDRESSING | アドレス指定。ビット[15:12]によって、該当するレジスタのアドレスが指定されます。詳細については、アドレス指定レジスタのセクションを参照してください。                                                                                                                                                              | 0x0  | R/W  |

| [11:10] | RESERVED   | 予備。                                                                                                                                                                                                                                        | 0x0  | R    |

| 9       | OS_MODE    | オーバーサンプリング・モード。ADCのオーバーサンプリング・モードを設定します。<br>0 : 相加平均。<br>1 : 移動平均。                                                                                                                                                                         | 0x0  | R/W  |

| [8:6]   | OSR        | オーバーサンプリング比。該当するモードのすべてのADCのオーバーサンプリング比を設定します。相加平均モードでは、2×、4×、8×、16×、32×のオーバーサンプリング比に対応します。移動平均モードでは、2×、4×、8×のオーバーサンプリング比に対応します。<br>000 : 無効。<br>001 : 2×。<br>010 : 4×。<br>011 : 8×。<br>100 : 16×。<br>101 : 32×。<br>110 : 無効。<br>111 : 無効。 | 0x0  | R/W  |

| 5       | CRC_W      | CRC書き込み。SDIインターフェースのCRC機能を制御します。このビットを0から1にセットする場合、コマンドの後に有効なCRCを追加してこの設定ビットをセットする必要があります。有効なCRCが受信されない場合、フレーム全体が無視されます。ビットが1にセットされている場合、CRCではこれを0にクリアする必要があります。<br>0 : CRC機能なし。<br>1 : CRC機能。                                             | 0x0  | R/W  |

| 4       | CRC_R      | CRC読み出し。SDOインターフェースのCRC機能を制御します。<br>0 : CRC機能なし。<br>1 : CRC機能。                                                                                                                                                                             | 0x0  | R/W  |

| 3       | ALERT_EN   | アラート表示機能を有効化。SDOビットが01の場合に、このビットが機能します。それ以外の場合、ALERT_ENビットは無視されます。<br>0: SDOB.<br>1: ALERT.                                                                                                                                                | 0x0  | R/W  |

| 2       | RES        | 分解能。変換結果のデータ・サイズを設定します。OSR = 0の場合、これらのビットは無視され、分解能はデフォルトの分解能に設定されます。<br>0 : 通常分解能。<br>1 : 2ビット高い分解能。                                                                                                                                       | 0x0  | R/W  |

| 1       | Reserved   | 予備。                                                                                                                                                                                                                                        | 0x0  | R    |

| 0       | PMODE      | パワーダウン・モード。電力モードを設定します。<br>0 : ノーマル・モード。<br>1 : シャットダウン・モード。                                                                                                                                                                               | 0x0  | R/W  |

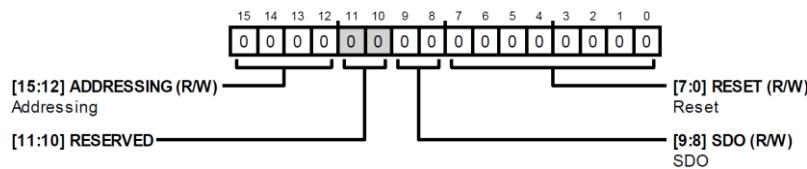

## CONFIGURATION 2レジスタ

表 19. CONFIGURATION 2レジスタのビットの説明

| ビット     | ビット名       | 説明                                                                                                                                                                                                            | リセット | アクセス |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| [15:12] | ADDRESSING | アドレス指定ビット。これらのビットによって、該当するレジスタのアドレスが指定されます。詳細については、 <a href="#">アドレス指定レジスタのセクション</a> を参照してください。                                                                                                               | 0x0  | R/W  |

| [11:10] | RESERVED   | 予備。                                                                                                                                                                                                           | 0x0  | R    |

| [9:8]   | SDO        | SDO。変換結果のシリアル・データ出力。<br>00 : 2線出力。変換データはSDOAおよびSDOBの両方に出力されます。<br>01 : 1線出力。変換データはSDOAのみに出力されます。<br>10 : 4線。変換データはSDOA、SDOB、SDOC、SDOD/ALERTに変換されます。<br>11 : 1線。変換データはSDOAのみに出力されます。                           | 0x0  | R/W  |

| [7:0]   | RESET      | リセット。<br>0x3C : ソフト・リセットを実行します。一部のブロックが更新されます。レジスタの内容は変わりません。アラート表示レジスタがクリアされ、オーバーサンプリング保存された変数やアクティブ・ステート・マシンは消去されます。<br>0xFF : ハード・リセットを実行します。デバイス内の可能なブロックはすべてリセットされます。レジスタの内容はデフォルトに戻ります。その他の値はすべて無視されます。 | 0x0  | R/W  |

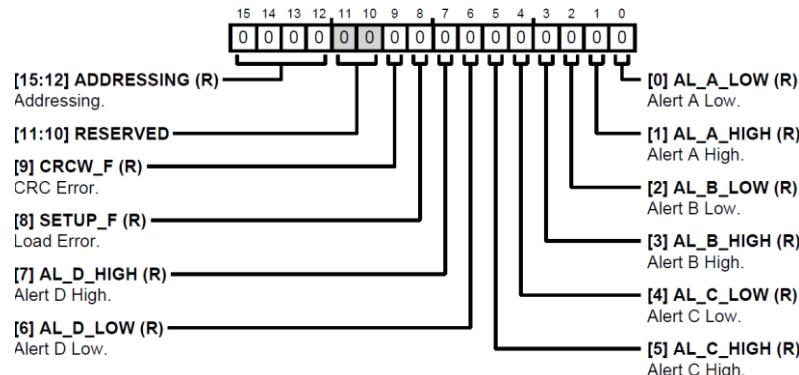

## アラート表示レジスタ

表 20. アラート表示レジスタのビットの説明

| ビット     | ビット名       | 説明                                                                                                                                                                                                | リセット | アクセス |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| [15:12] | ADDRESSING | アドレス指定。ビット[15:12]によって、該当するレジスタのアドレスが指定されます。詳細については、アドレス指定レジスタのセクションを参照してください。                                                                                                                     | 0x0  | R    |

| [11:10] | RESERVED   | 予備。                                                                                                                                                                                               | 0x0  | R    |

| 9       | CRCW_F     | CRCエラー。レジスタ書き込みコマンドがCRCエラーのために失敗したこと示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>0 : CRCエラーはありません。<br>1 : CRCエラー。                                                                       | 0x0  | R    |

| 8       | SETUP_F    | ロード・エラー。SETUP_Fは、起動時にデバイス設定データが正しく読み込まれなかったことを示します。このビットは、アラート表示レジスタの読み出し時にはクリアされません。このビットをクリアし、デバイスのセットアップを再起動するには、CONFIGURATION 2レジスタを介したハード・リセットが必要です。<br>0 : セットアップ・エラーなし。<br>1 : セットアップ・エラー。 | 0x0  | R    |

| 7       | AL_D_HIGH  | アラートDハイ。このアラート表示ハイ・ビットは、各入力チャンネルの変換結果がアラート上限閾値レジスタの設定値を超えているかどうかを示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>1 : アラート表示。<br>0 : アラート表示なし。                                              | 0x0  | R    |

表 20. アラート表示レジスタのビットの説明

| ビット | ビット名      | 説明                                                                                                                                                  | リセット | アクセス |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| 6   | AL_D_LOW  | アラートDロー。このアラート表示ロー・ビットは、各入力チャンネルの変換結果がアラート下限閾値レジスタの設定値を超えてるかどうかを示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>0 : アラート表示なし。<br>1 : アラート表示。 | 0x0  | R    |

| 5   | AL_C_HIGH | アラートCハイ。このアラート表示ハイ・ビットは、各入力チャンネルの変換結果がアラート上限閾値レジスタの設定値を超えてるかどうかを示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>1 : アラート表示。<br>0 : アラート表示なし。 | 0x0  | R    |

| 4   | AL_C_LOW  | アラートCロー。このアラート表示ロー・ビットは、各入力チャンネルの変換結果がアラート下限閾値レジスタの設定値を超えてるかどうかを示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>1 : アラート表示。<br>0 : アラート表示なし。 | 0x0  | R    |

| 3   | AL_B_HIGH | アラートBハイ。このアラート表示ハイ・ビットは、各入力チャンネルの変換結果がアラート上限閾値レジスタの設定値を超えてるかどうかを示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>1 : アラート表示。<br>0 : アラート表示なし。 | 0x0  | R    |

| 2   | AL_B_LOW  | アラートBロー。このアラート表示ロー・ビットは、各入力チャンネルの変換結果がアラート下限閾値レジスタの設定値を超えてるかどうかを示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>1 : アラート表示。<br>0 : アラート表示なし。 | 0x0  | R    |

| 1   | AL_A_HIGH | アラートAハイ。このアラート表示ハイ・ビットは、各入力チャンネルの変換結果がアラート上限閾値レジスタの設定値を超えてるかどうかを示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>0 : アラート表示なし。<br>1 : アラート表示。 | 0x0  | R    |

| 0   | AL_A_LOW  | アラートAロー。このアラート表示ロー・ビットは、各入力チャンネルの変換結果がアラート下限閾値レジスタの設定値を超えてるかどうかを示します。このフォルト・ビットはスティッキーで、レジスタが読み出されるまでセットされたままになります。<br>1 : アラート表示。<br>0 : アラート表示なし。 | 0x0  | R    |

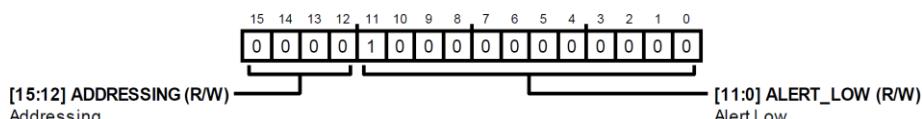

### アラート下限閾値レジスタ

表 21. アラート下限閾値レジスタのビットの説明

| ビット     | ビット名       | 説明                                                                                                                                                                   | リセット  | アクセス |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| [15:12] | ADDRESSING | アドレス指定。ビット[15:12]によって、該当するレジスタのアドレスが指定されます。詳細については、アドレス指定レジスタのセクションを参照してください。                                                                                        | 0x0   | R/W  |

| [11:0]  | ALERT_LOW  | アラート・ロー。ALERT_LOWのビット[11:0]は、内部アラート・ロー・レジスタのMSB (D[15:4]) に移動します。内部レジスタの残りのビット、D[3:0]は、0x0に固定されます。変換結果がアラート下限閾値レジスタの値を下回るとアラートをセットし、アラート下限閾値レジスタの値を上回るとアラートは無効になります。 | 0x800 | R/W  |

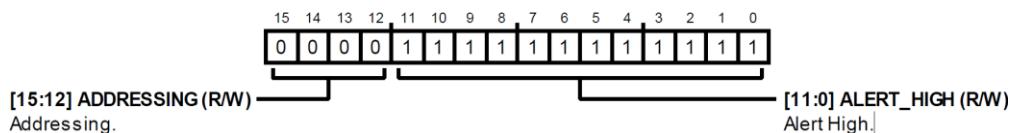

## アラート上限閾値レジスタ

表 22. アラート上限閾値レジスタのビットの説明

| ビット     | ビット名        | 説明                                                                                                                                                                      | リセット   | アクセス |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [15:12] | ADDRESSING  | アドレス指定。ビット[15:12]によって、該当するレジスタのアドレスが指定されます。詳細については、アドレス指定レジスタのセクションを参照してください。                                                                                           | 0x0    | R/W  |

| [11:0]  | ALERT_HIGHT | アラート・ハイ。ALERT_HIGHTのビットD[11:0]は、内部アラート・ハイ・レジスタのMSB (D[15:4]) に移動します。内部レジスタの残りのビット、D[3:0]は、0xFに固定されます。変換結果がアラート上限閾値レジスタの値を上回るとアラートをセットし、アラート上限閾値レジスタの値を下回るとアラートは無効になります。 | 0xFFFF | R/W  |

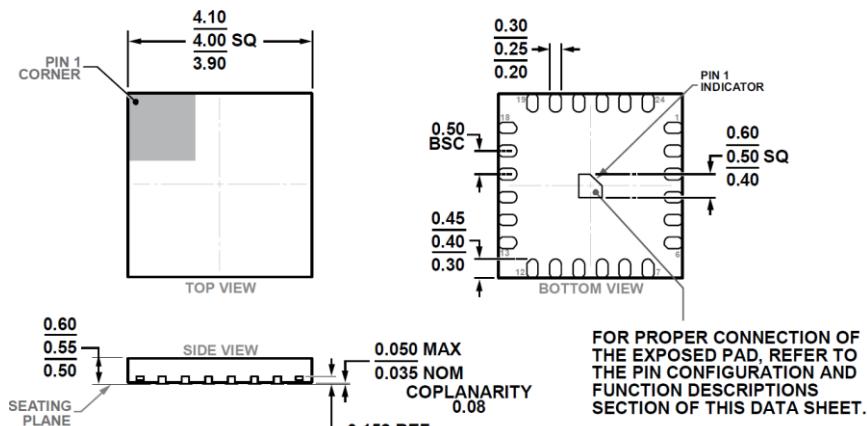

## 外形寸法

COMPLIANT TO JEDEC STANDARDS MO-248-UGGD

01-30-2017A

図 44. 24ピン・リード・フレーム・チップ・スケール・パッケージLFCSP

4mm × 4mmボディ、0.55mmパッケージ高

(CP-24-25)

寸法 : mm

## オーダー・ガイド

| Model <sup>1,2</sup> | Resolution | Temperature Range | Package Description                           | Package Option |

|----------------------|------------|-------------------|-----------------------------------------------|----------------|

| AD7380-4BCPZ         | 16-Bit     | −40°C to +125°C   | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-25       |

| AD7380-4BCPZ-RL      | 16-Bit     | −40°C to +125°C   | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-25       |

| AD7380-4BCPZ-RL7     | 16-Bit     | −40°C to +125°C   | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-25       |

| EVAL-AD7380-4FMCZ    |            |                   | AD7380-4 Evaluation Board                     |                |

| EVAL-SDP-CH1Z        |            |                   | Evaluation Board Controller                   |                |

1 Z = RoHS準拠製品。