# バッファ付き 8 チャンネル同時サンプリング、 20 ビットの 250kSPS DAS

## 特長

- ▶ フル機能の 20 ビット・データ・アクイジション・システム

- ▶ 内部バッファされた 8 個のチャンネルの同時サンプリング

- ▶ チャンネルあたり 250kSPS のスループット

- ▶ 同相電圧範囲が広い差動入力

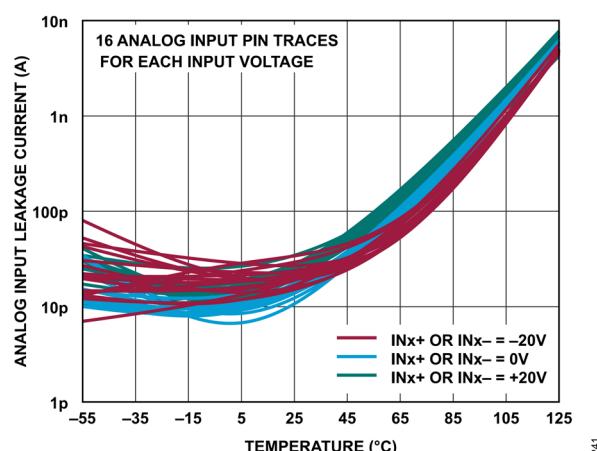

- ▶ 25°C で  $\pm 75\text{pA}$  (代表値) の入力リーク電流

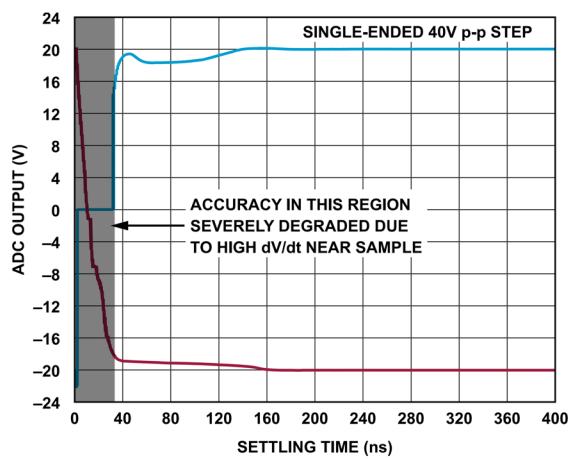

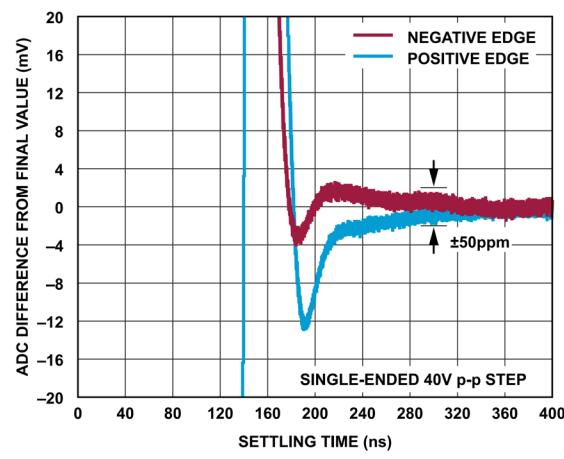

- ▶ 300ns 未満のフルスケール入力ステップ・セトリング・タイム

- ▶ リファレンスとリファレンス・バッファを内蔵 (4.096V)

- ▶ 電源デカッピング・コンデンサを内蔵

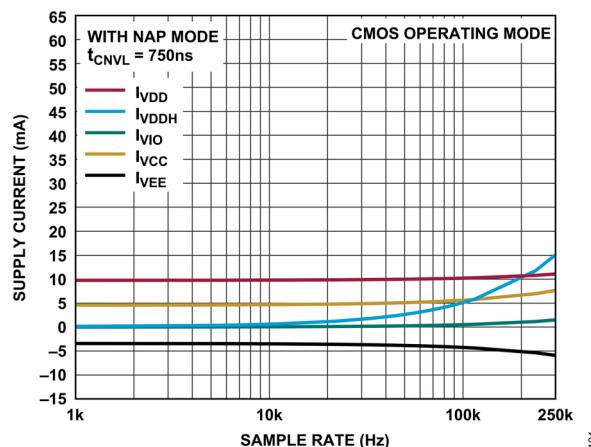

- ▶ 250kSPS でチャンネルあたり 27mW (消費電力はスループットに比例)

- ▶ 最小限の外部シグナル・コンディショニング

- ▶ シームレス・ハイ・ダイナミック・レンジ

- ▶ サンプルごと、チャンネルごとにゲイン範囲を自動設定

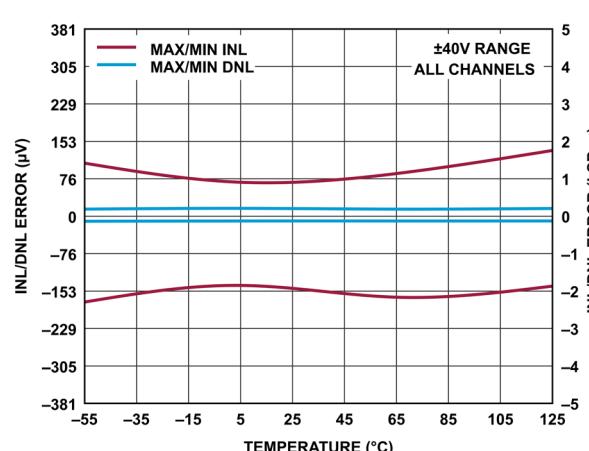

- ▶ ppm レベルの INL を維持

- ▶ チャンネルごとの SoftSpan 入力レンジ (バイポーラまたはユニポーラ)

- ▶  $\pm 40\text{V}$ 、 $\pm 25\text{V}$ 、 $\pm 20\text{V}$ 、 $\pm 12.5\text{V}$ 、 $\pm 10\text{V}$ 、 $\pm 6.25\text{V}$ 、 $\pm 5\text{V}$ 、 $\pm 2.5\text{V}$

- ▶ 0V~40V、25V、20V、12.5V、10V、6.25V、5V、2.5V

## 機能ブロック図

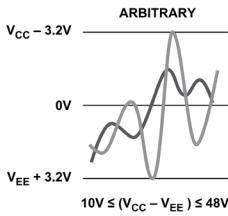

### DIFFERENTIAL INPUTS INx+/INx- WITH WIDE INPUT COMMON MODE RANGE

### EXAMPLE USE CASES

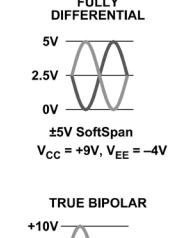

### FULLY DIFFERENTIAL

5V

2.5V

0V

$\pm 5\text{V}$  SoftSpan

$V_{CC} = +9\text{V}$ ,  $V_{EE} = -4\text{V}$

### TRUE BIPOLAR

+10V

0V

-10V

$\pm 10\text{V}$  SoftSpan

$V_{CC} = +14\text{V}$ ,  $V_{EE} = -14\text{V}$

### SEAMLESS HIGH DYNAMIC RANGE

$\pm 40\text{V}$  SoftSpan

SHDR OFF

75 $\mu\text{V}$  rms

SHDR ON

0V TO 40V SoftSpan

$V_{CC} = +44\text{V}$ ,  $V_{EE} = -4\text{V}$

### UNIPOLAR

+40V

0V

0V TO 40V SoftSpan

$V_{CC} = +44\text{V}$ ,  $V_{EE} = -4\text{V}$

### ANALOG INPUT (VIN+ - VIN-)

-40 0 40

ANALOG INPUT (VIN

## 目次

|                     |    |

|---------------------|----|

| 特長                  | 1  |

| アプリケーション            | 1  |

| 機能ブロック図             | 1  |

| 概要                  | 3  |

| 関連製品                | 3  |

| 仕様                  | 4  |

| タイミング仕様             | 13 |

| 絶対最大定格              | 18 |

| ジャンクション温度           | 18 |

| 熱特性                 | 18 |

| 静電放電 (ESD) 定格       | 18 |

| ESD に関する注意          | 18 |

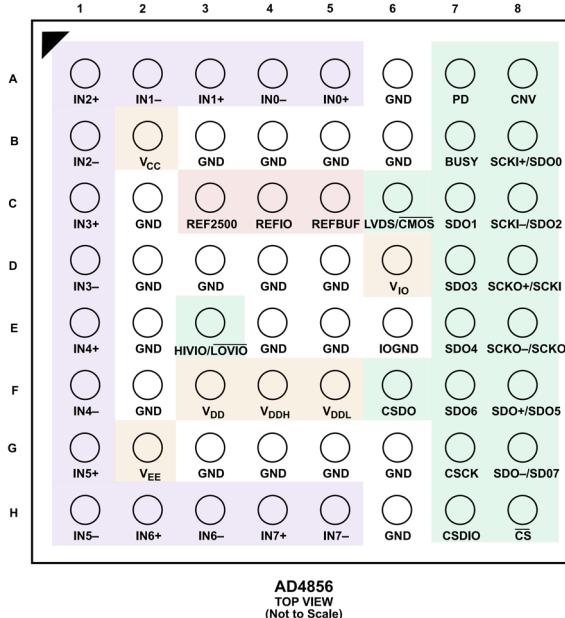

| ピン配置およびピン機能の説明      | 19 |

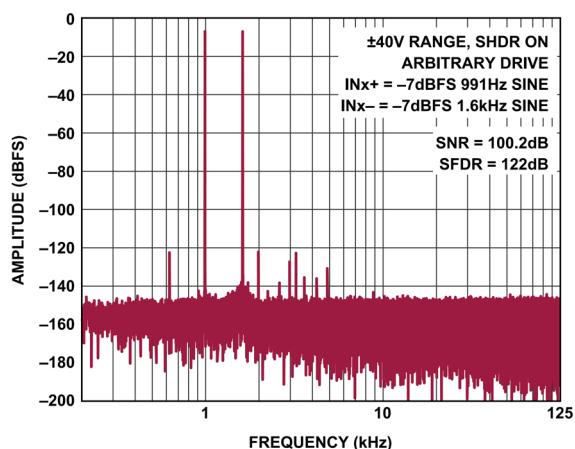

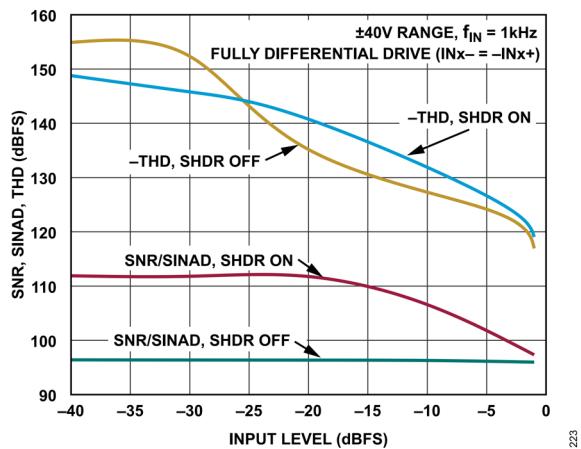

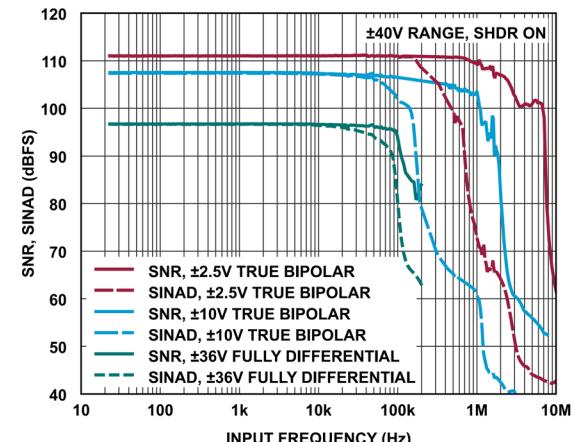

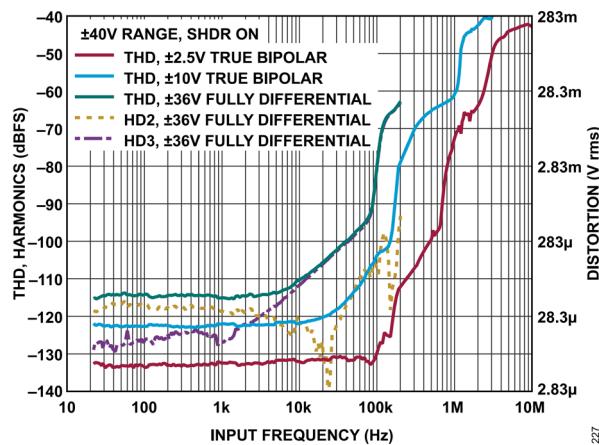

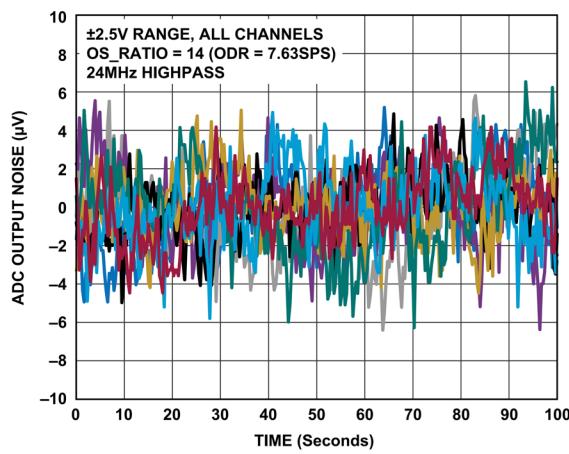

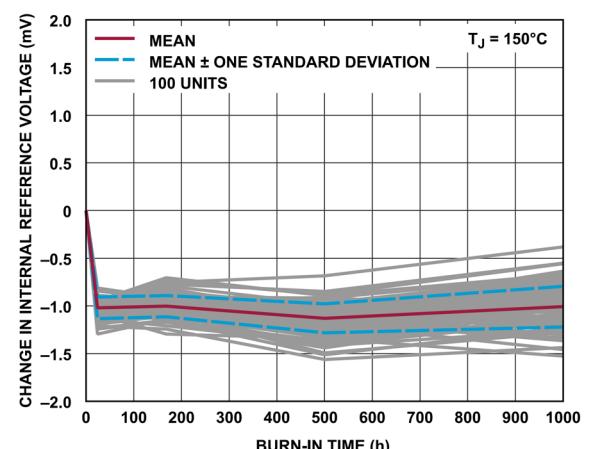

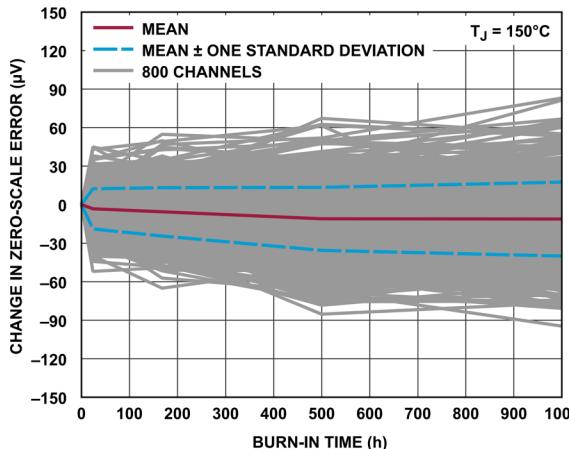

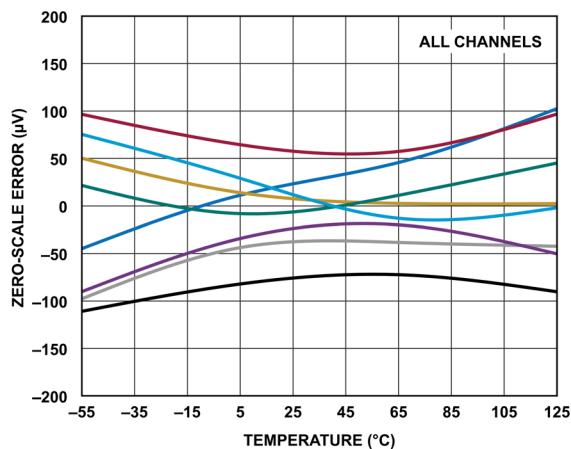

| 代表的な性能特性            | 22 |

| 用語の定義               | 29 |

| 動作原理                | 30 |

| 概要                  | 30 |

| コンバータの動作            | 30 |

| 伝達関数                | 30 |

| SoftSpan            | 31 |

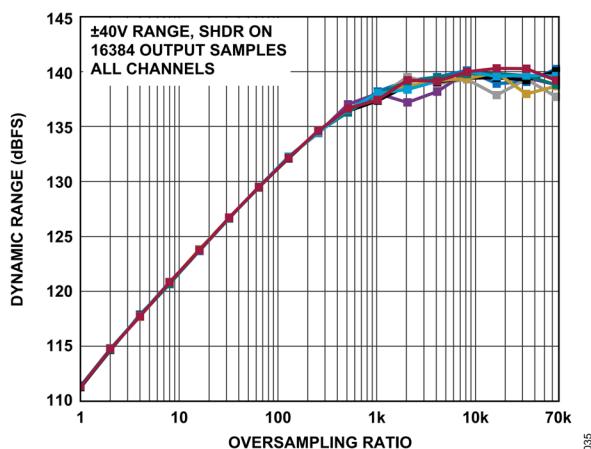

| シームレス・ハイ・ダイナミック・レンジ | 31 |

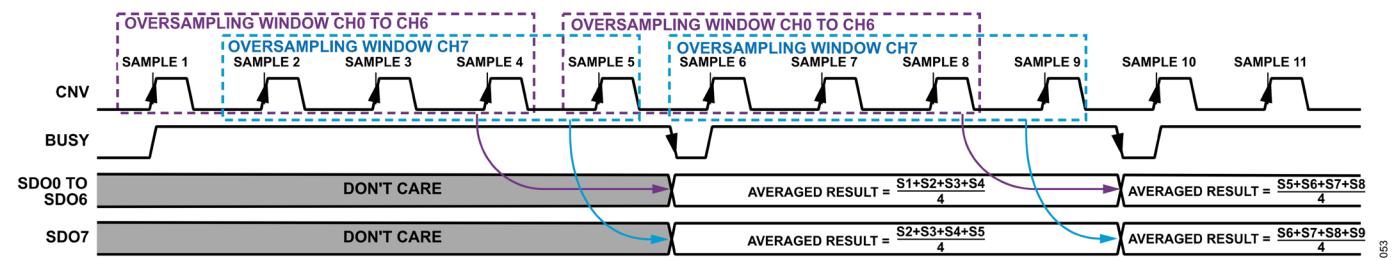

| デジタル処理機能            | 31 |

| アプリケーション情報          | 36 |

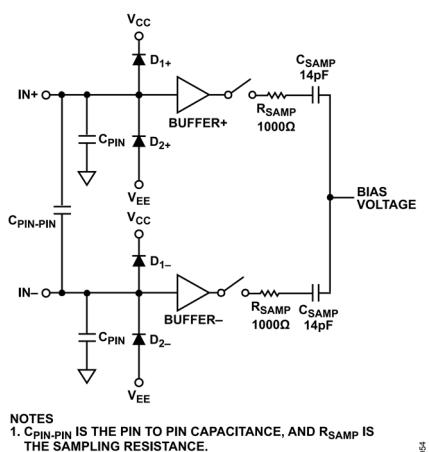

| バッファされたアナログ入力       | 36 |

| アナログ入力駆動回路          | 36 |

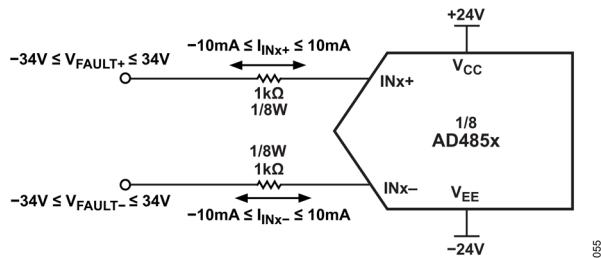

| アナログ入力のオーバードライブ耐性   | 36 |

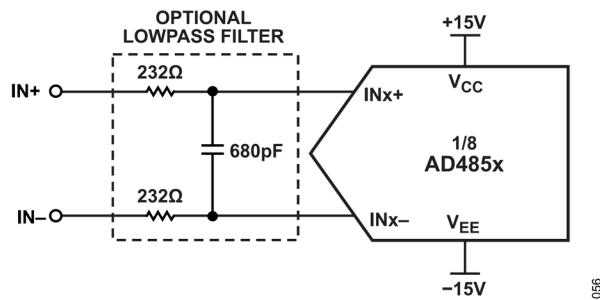

| アナログ入力のフィルタ処理       | 37 |

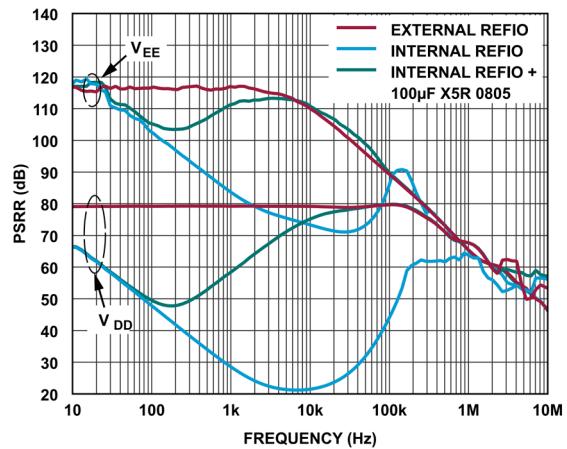

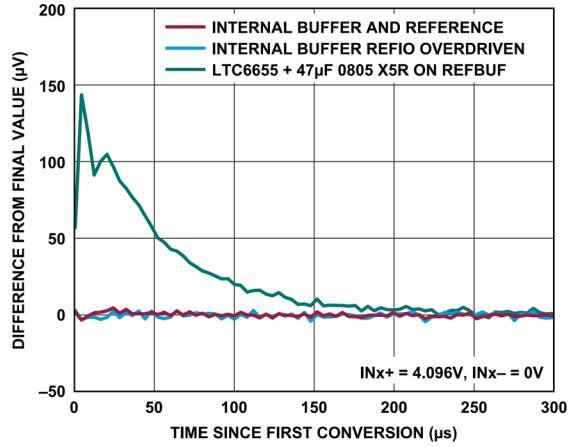

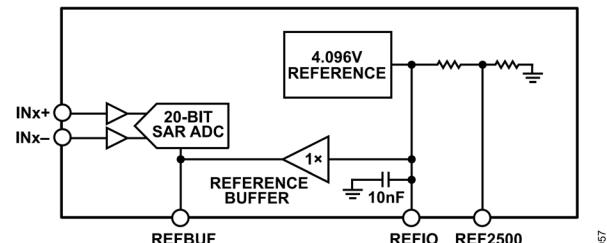

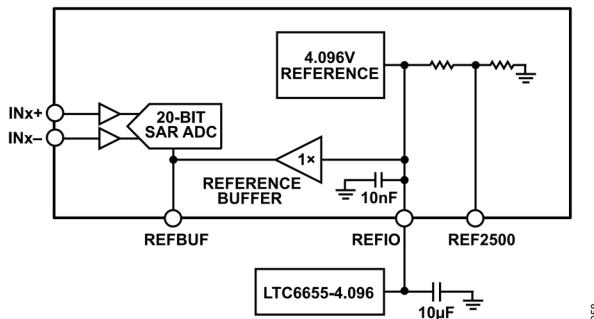

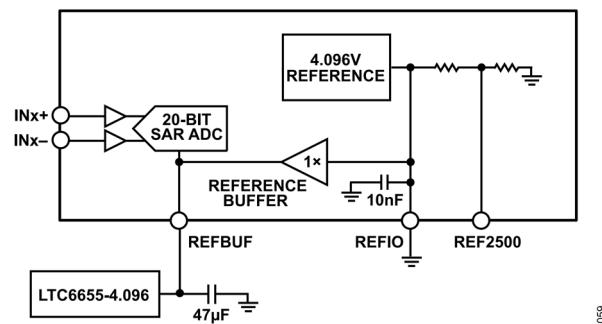

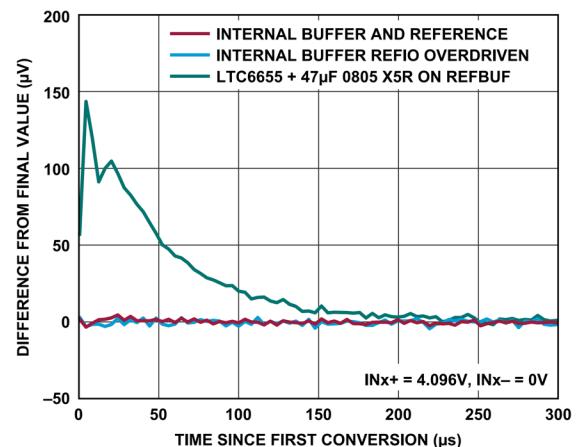

| DAS リファレンス          | 37 |

| 電力に関する考慮事項          | 38 |

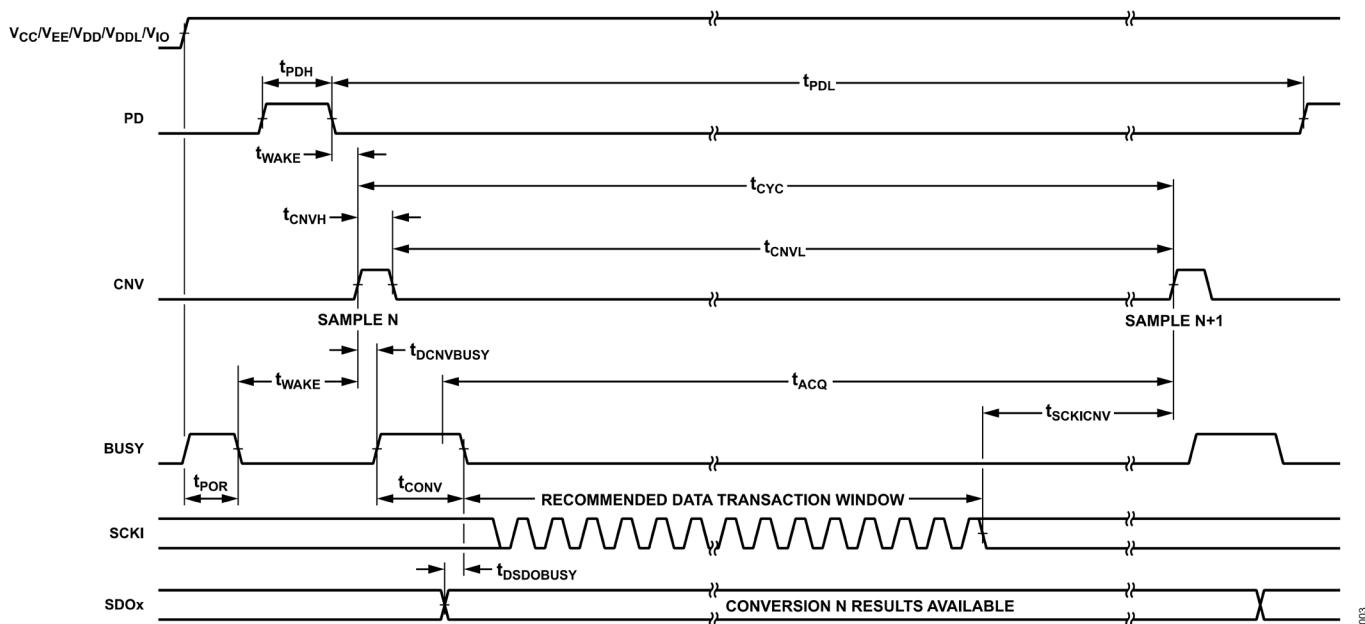

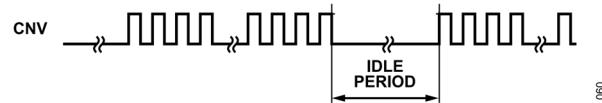

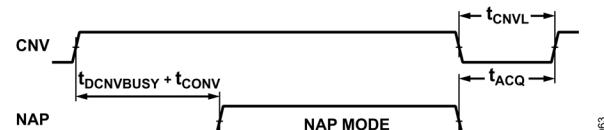

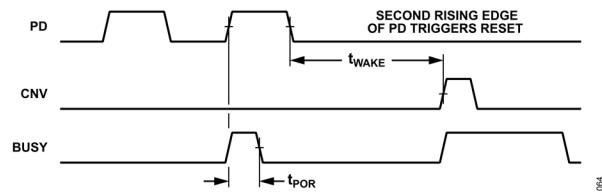

| タイミングと制御            | 39 |

| デジタル・インターフェース       | 41 |

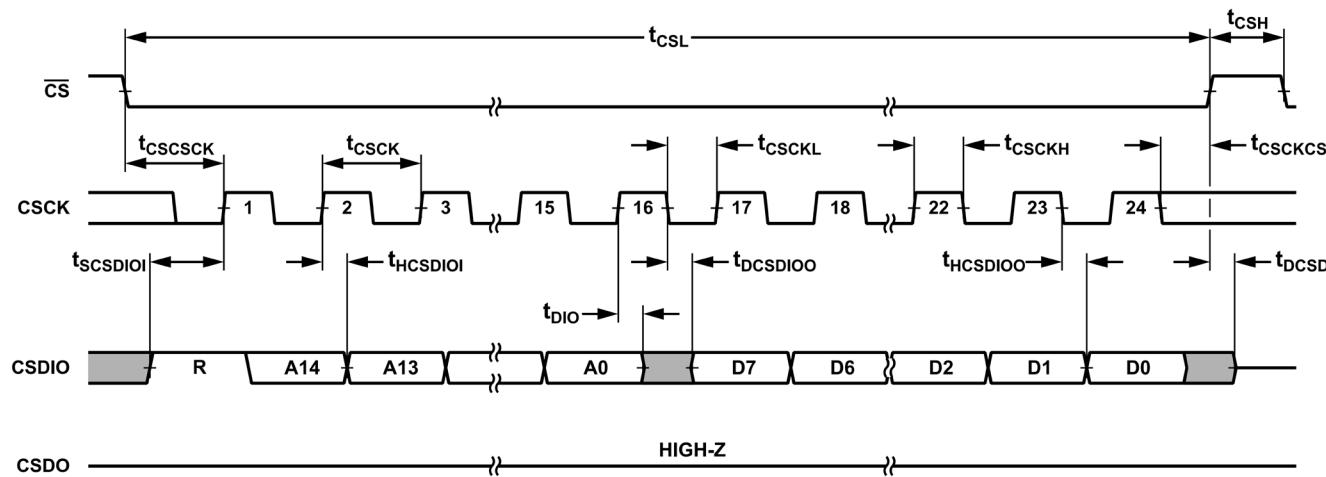

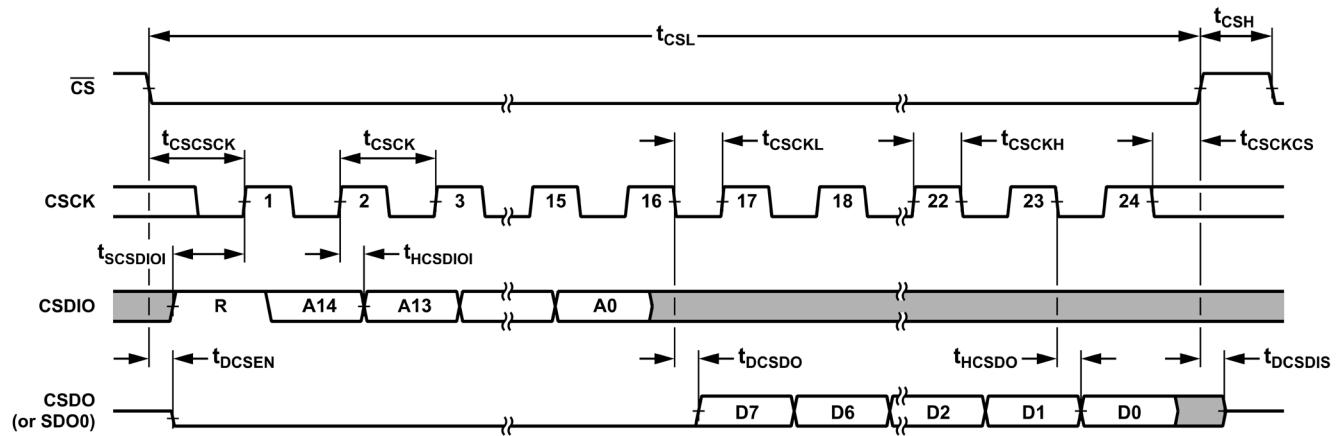

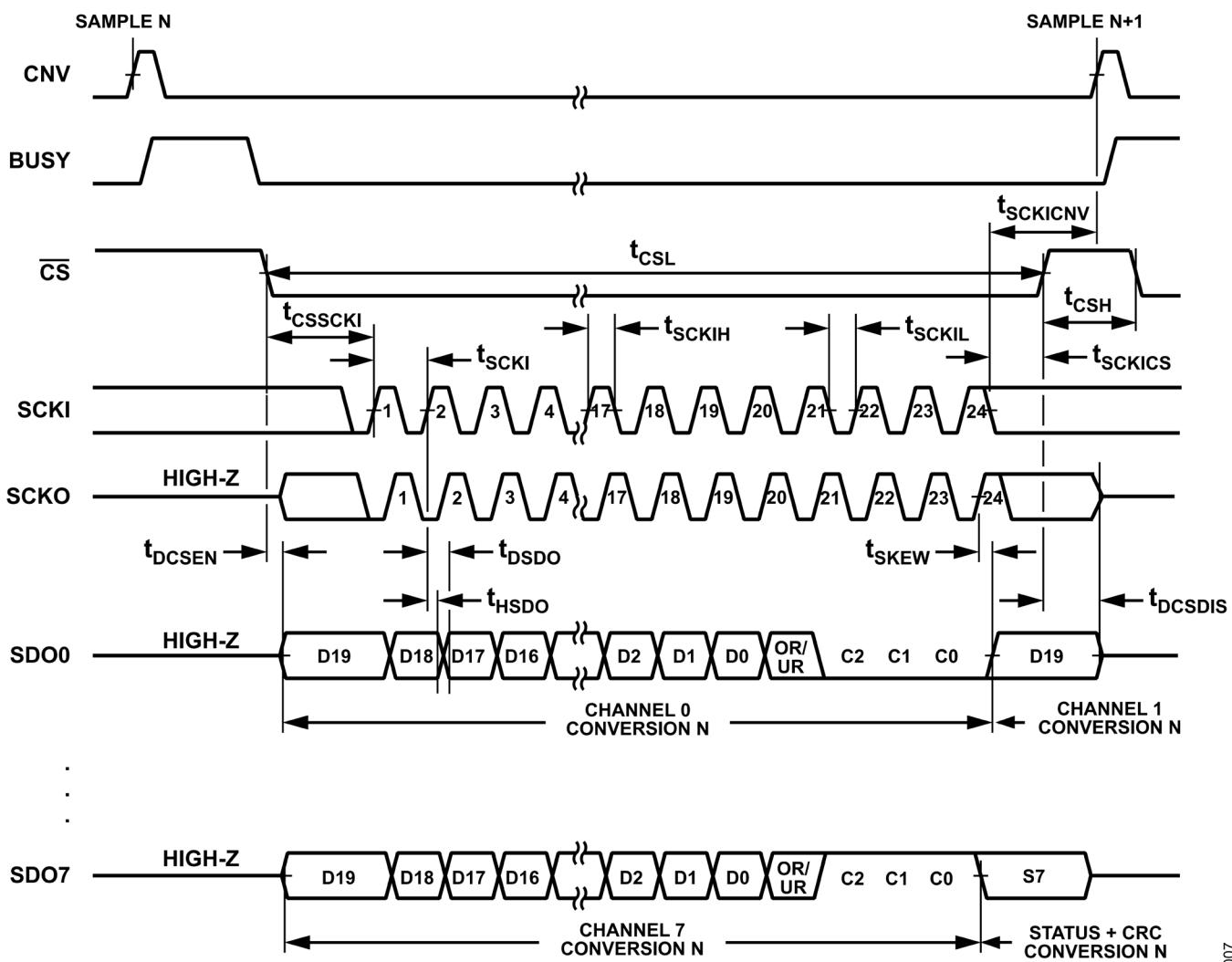

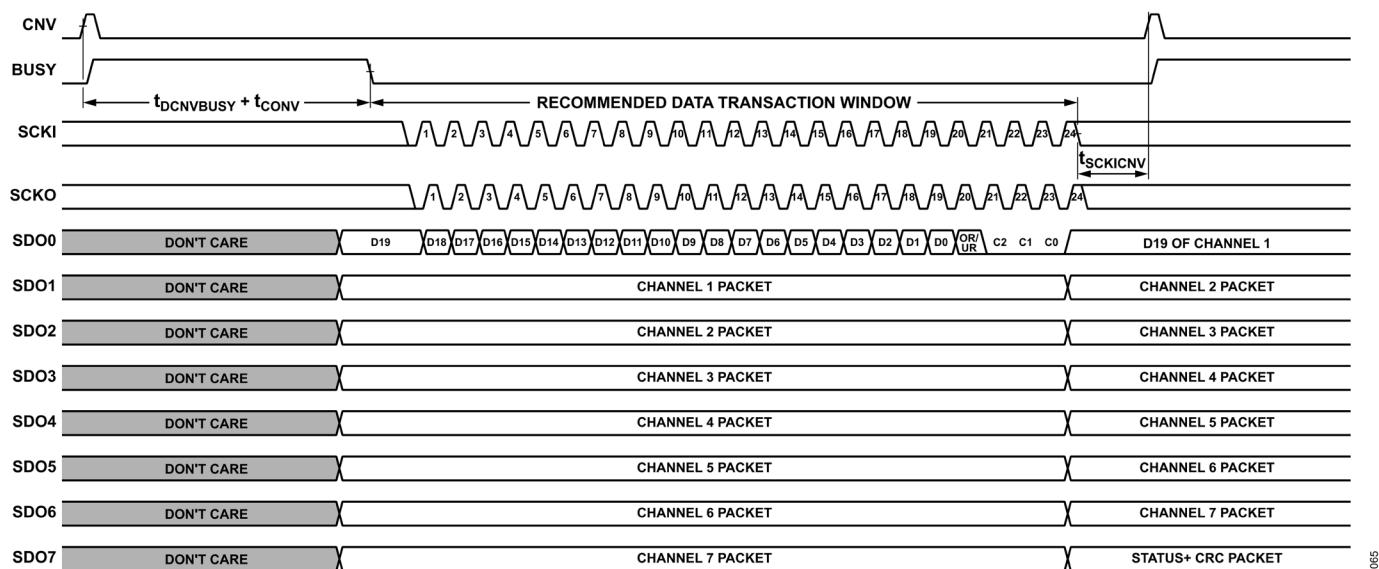

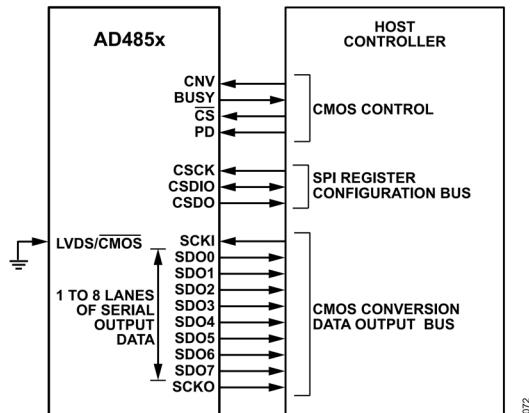

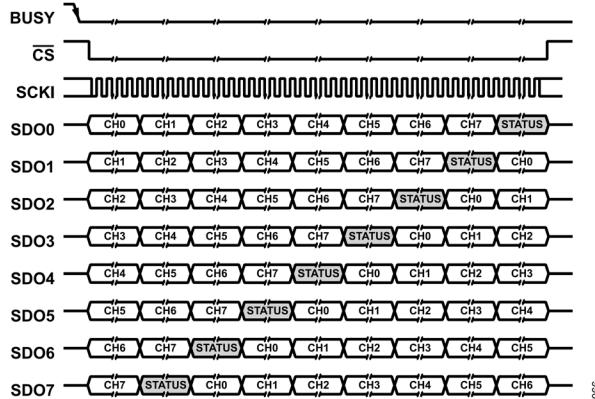

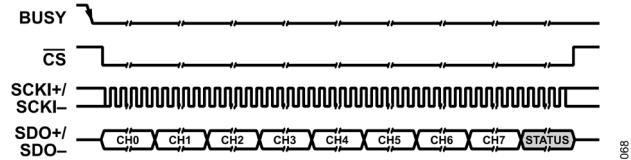

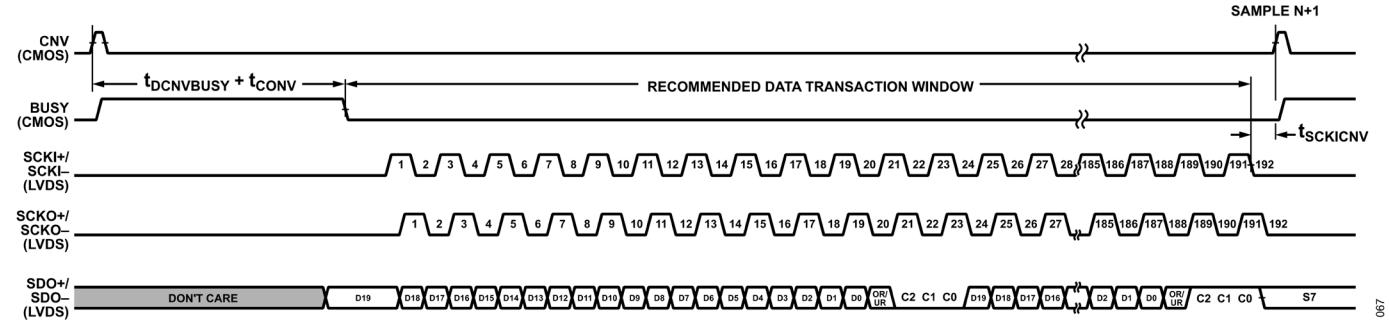

| CMOS 変換データ出力モード     | 41 |

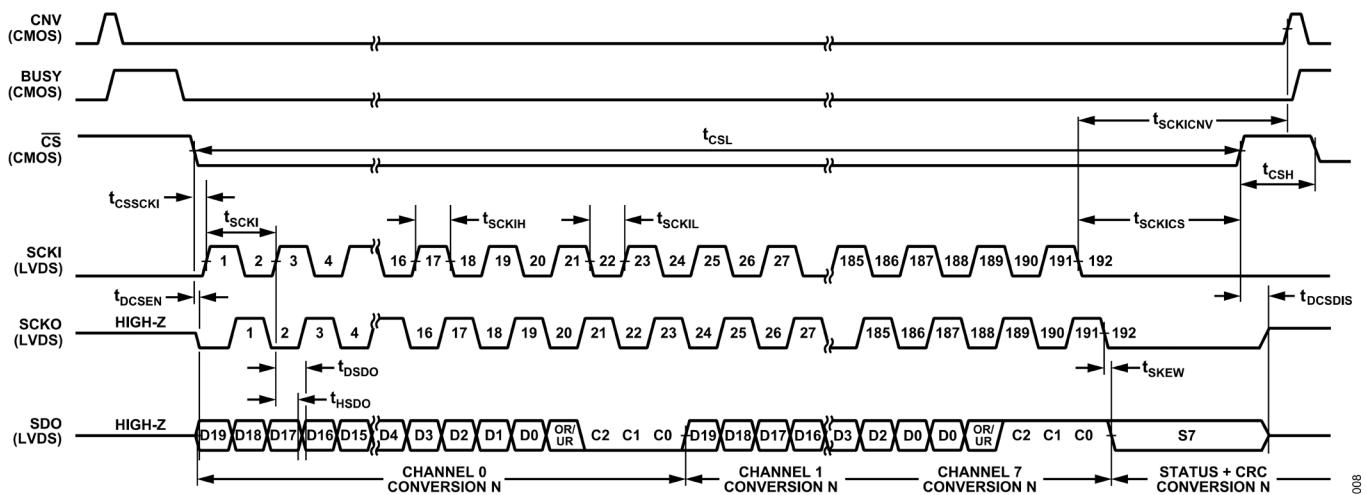

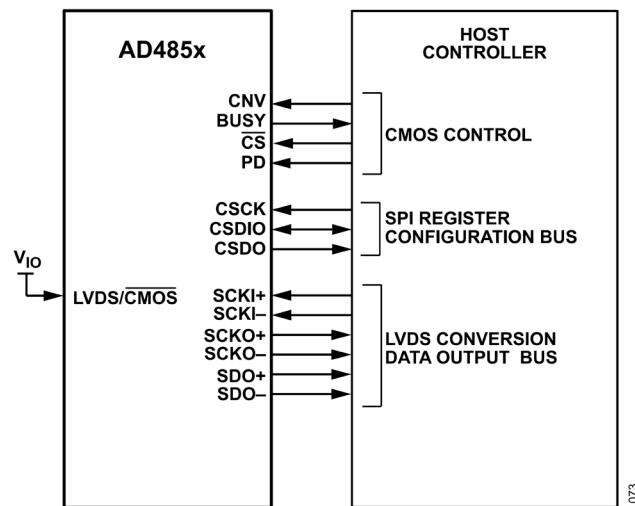

| LVDS 変換データ出力モード     | 42 |

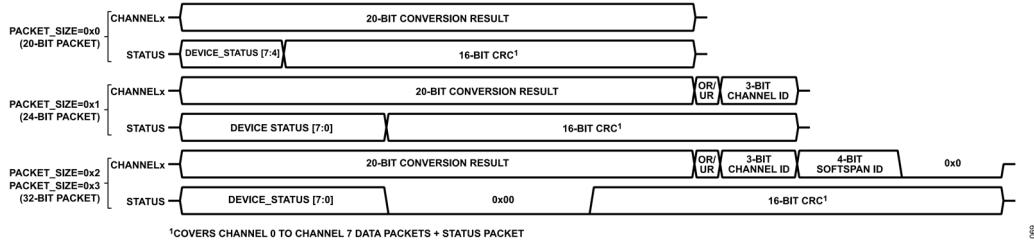

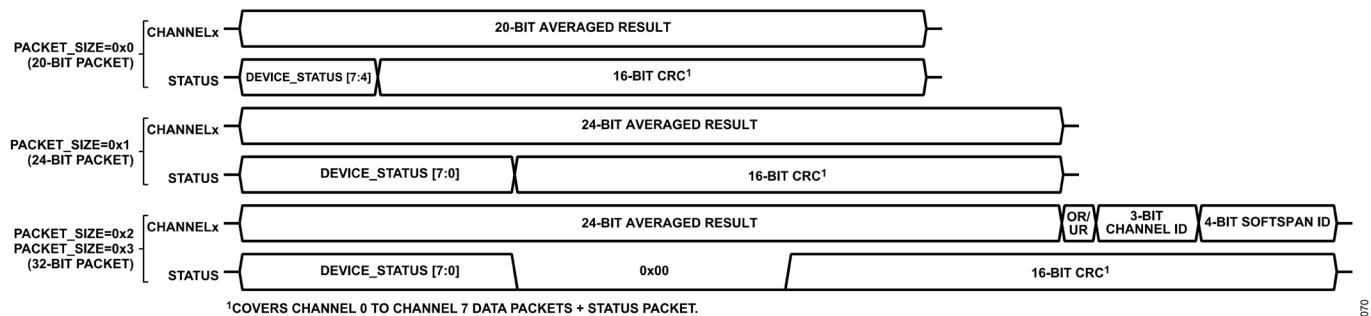

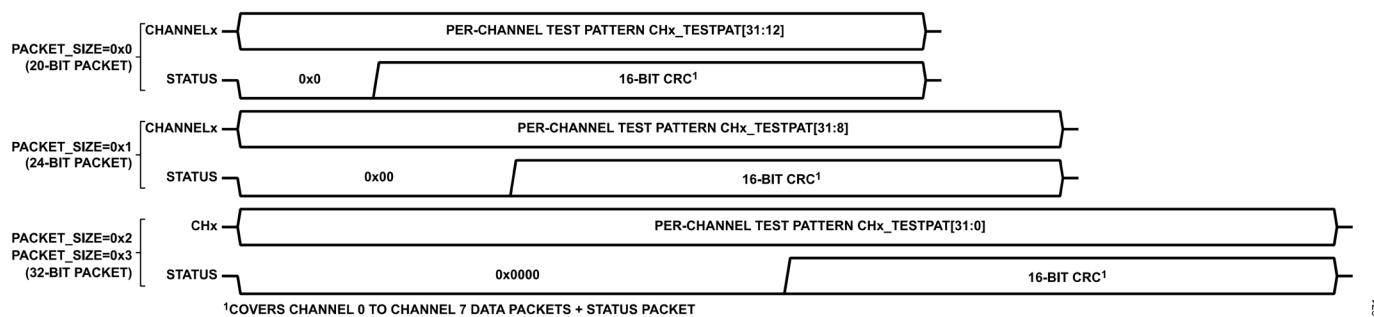

| パケット・フォーマット         | 44 |

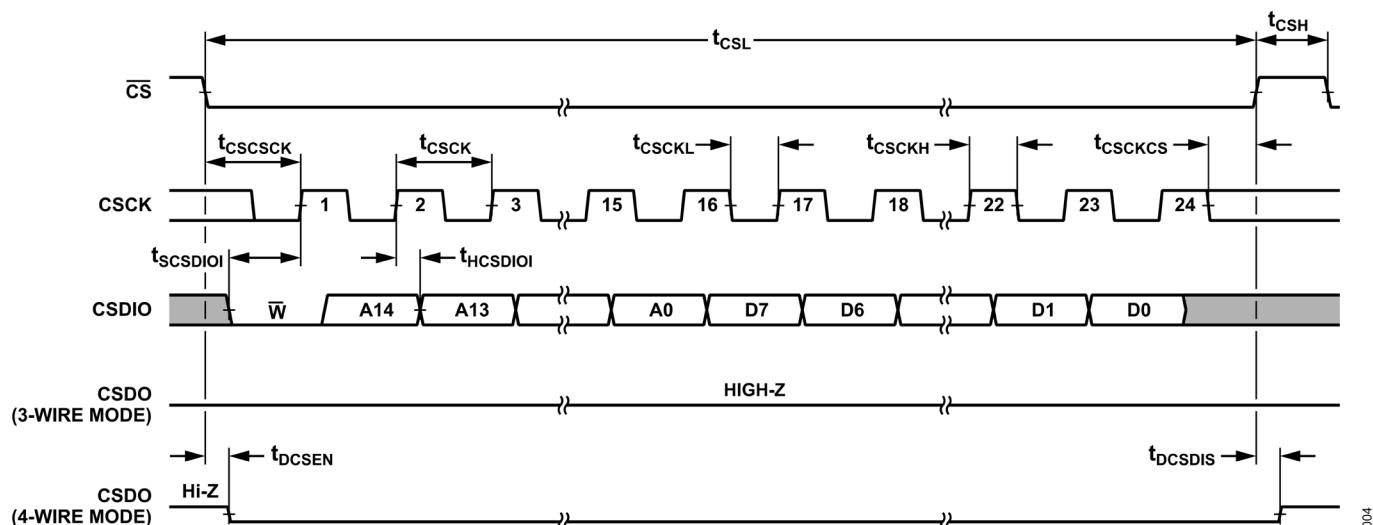

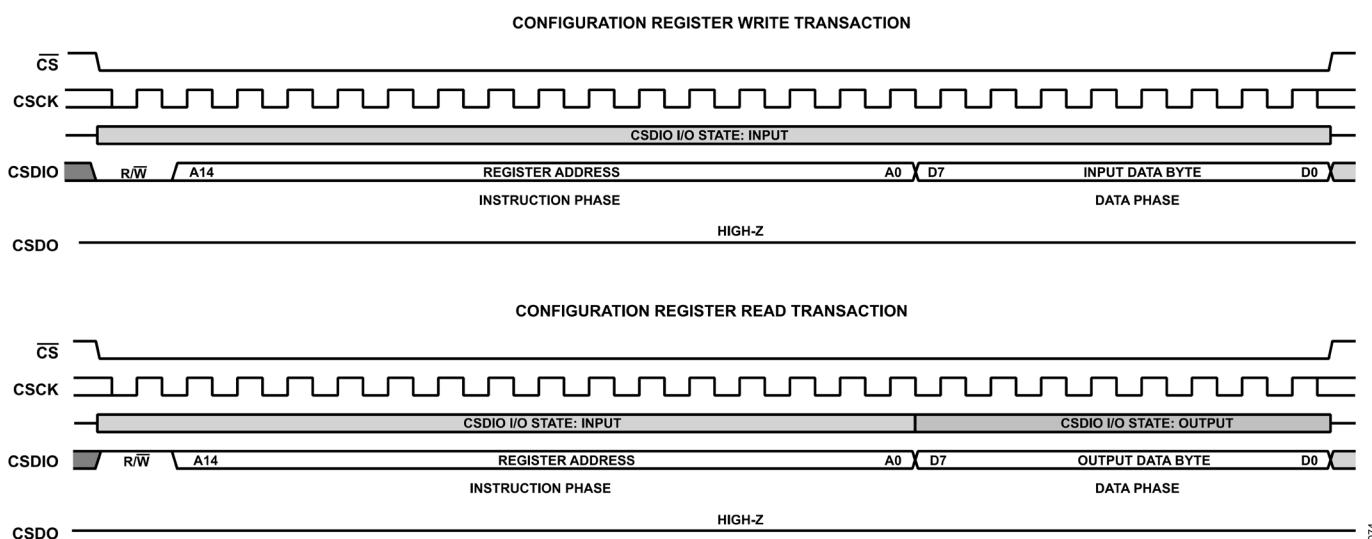

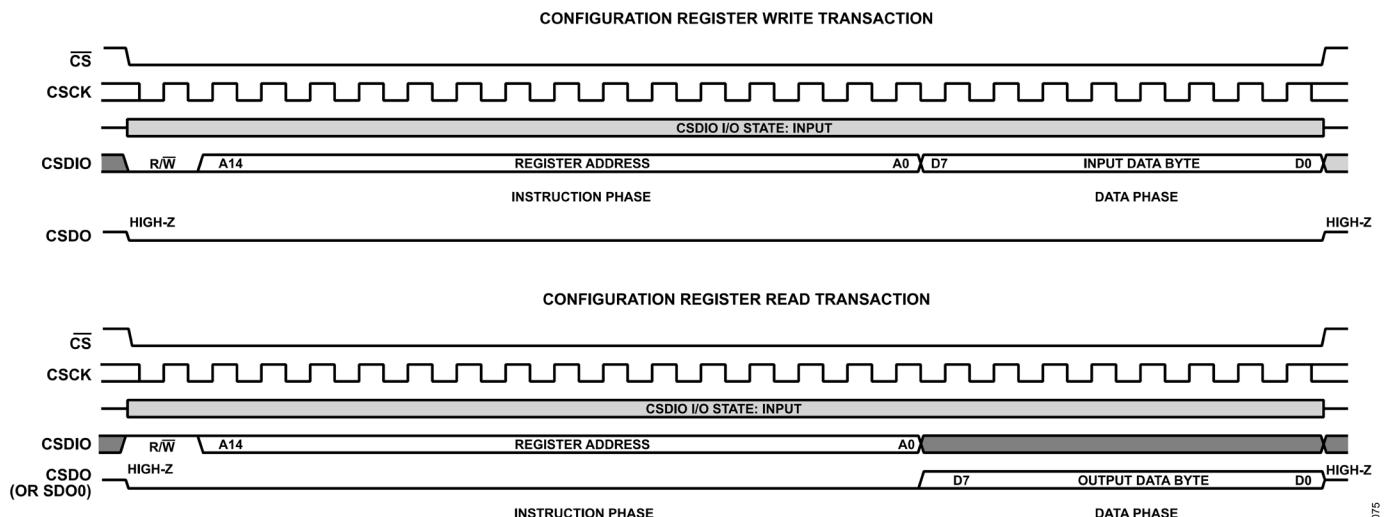

| SPI レジスタ設定バス        | 47 |

| レジスタの一覧             | 50 |

|                          |    |

|--------------------------|----|

| レジスタの詳細                  | 54 |

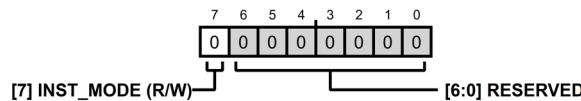

| SPI 設定 A レジスタ            | 54 |

| SPI 設定 B レジスタ            | 55 |

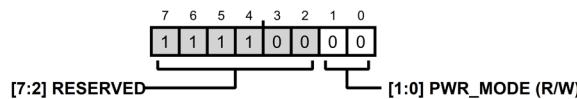

| デバイス設定レジスタ               | 55 |

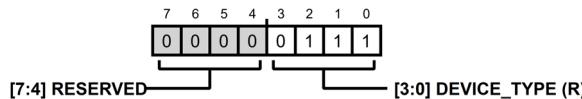

| デバイス・タイプ・レジスタ            | 55 |

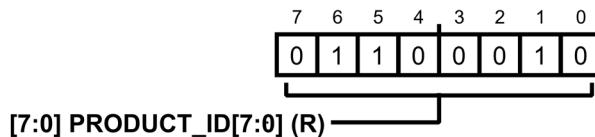

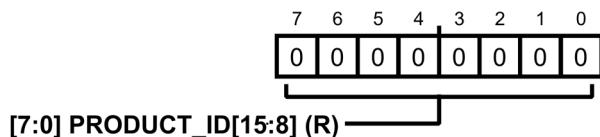

| 製品 ID ロー・レジスタ            | 56 |

| 製品 ID ハイ・レジスタ            | 56 |

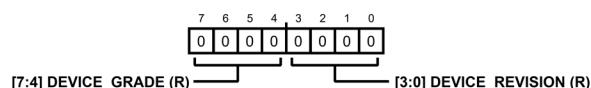

| デバイス・グレード・レジスタ           | 56 |

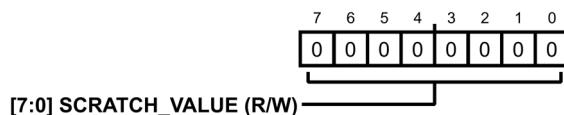

| スクラッチ・パッド・レジスタ           | 56 |

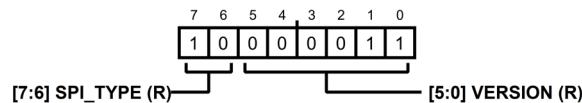

| SPI リビジョン・レジスタ           | 57 |

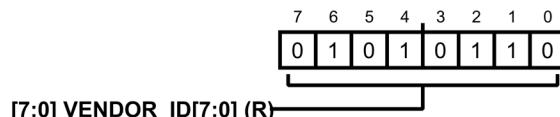

| ベンダ ID ロー・レジスタ           | 57 |

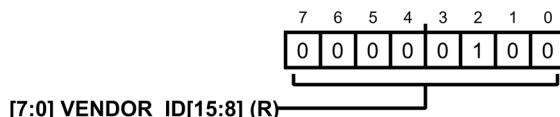

| ベンダ ID ハイ・レジスタ           | 57 |

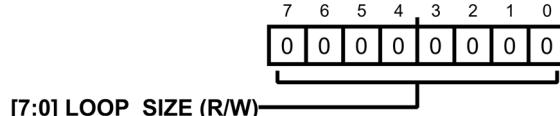

| ループ設定 A レジスタ             | 57 |

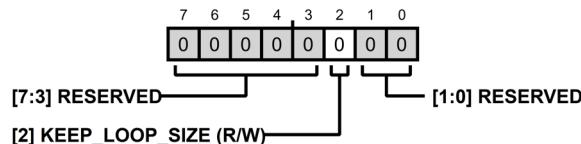

| ループ設定 B レジスタ             | 58 |

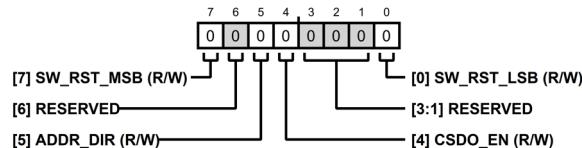

| SPI 設定 C レジスタ            | 58 |

| SPI ステータス・レジスタ           | 59 |

| SPI 設定 D レジスタ            | 59 |

| デバイス・ステータス・レジスタ          | 60 |

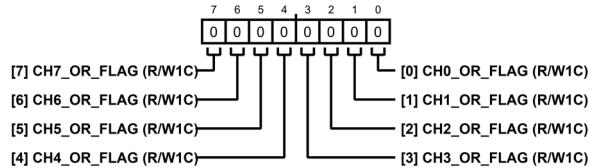

| チャンネル・オーバーレンジ・ステータス・レジスタ | 61 |

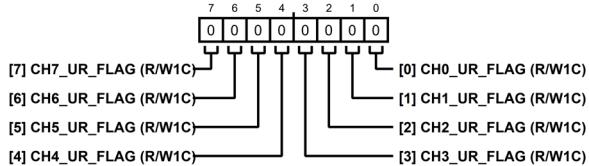

| チャンネル・アンダーレンジ・ステータス・レジスタ | 61 |

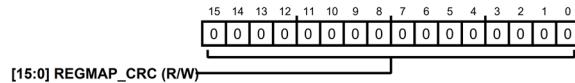

| レジスタ・マップ CRC             | 62 |

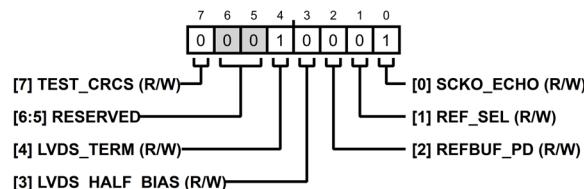

| デバイス制御レジスタ               | 62 |

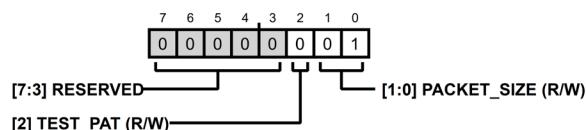

| パケット・フォーマット・レジスタ         | 63 |

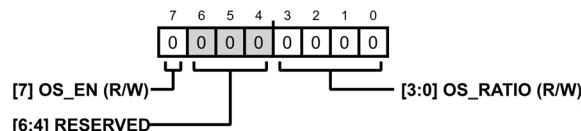

| オーバーサンプル制御レジスタ           | 63 |

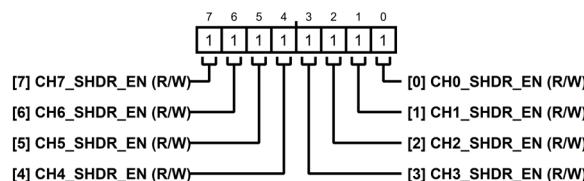

| シームレス・ハイ・ダイナミック・レンジ・レジスタ | 64 |

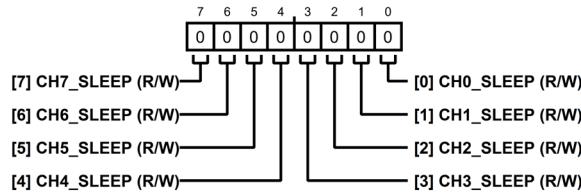

| チャンネル・スリープ・レジスタ          | 65 |

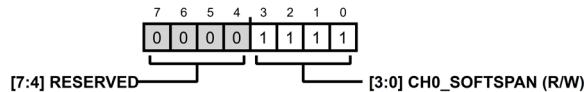

| チャンネル 0 SoftSpan レジスタ    | 65 |

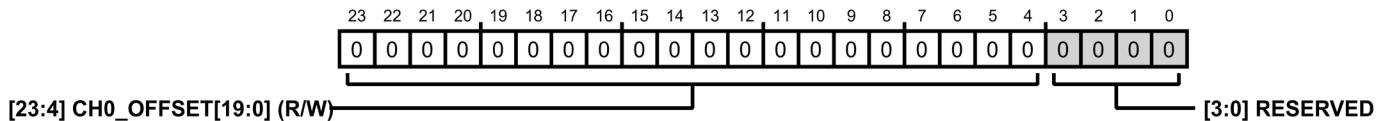

| チャンネル 0 オフセット・レジスタ       | 66 |

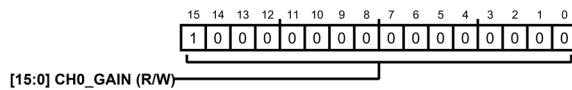

| チャンネル 0 ゲイン・レジスタ         | 66 |

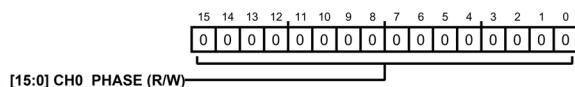

| チャンネル 0 位相レジスタ           | 66 |

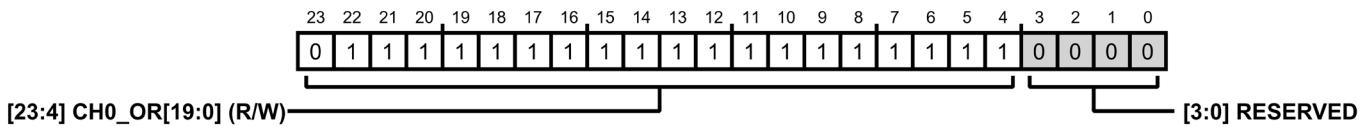

| チャンネル 0 オーバーレンジ制限レジスタ    | 67 |

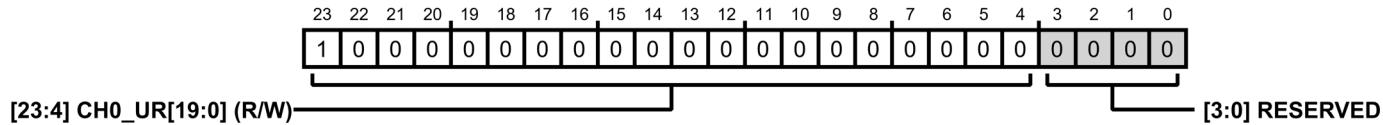

| チャンネル 0 アンダーレンジ制限レジスタ    | 67 |

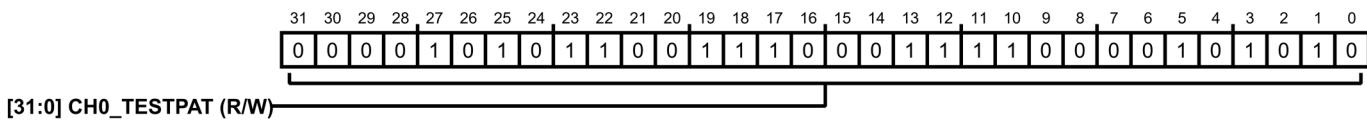

| チャンネル 0 テスト・パターン・レジスタ    | 67 |

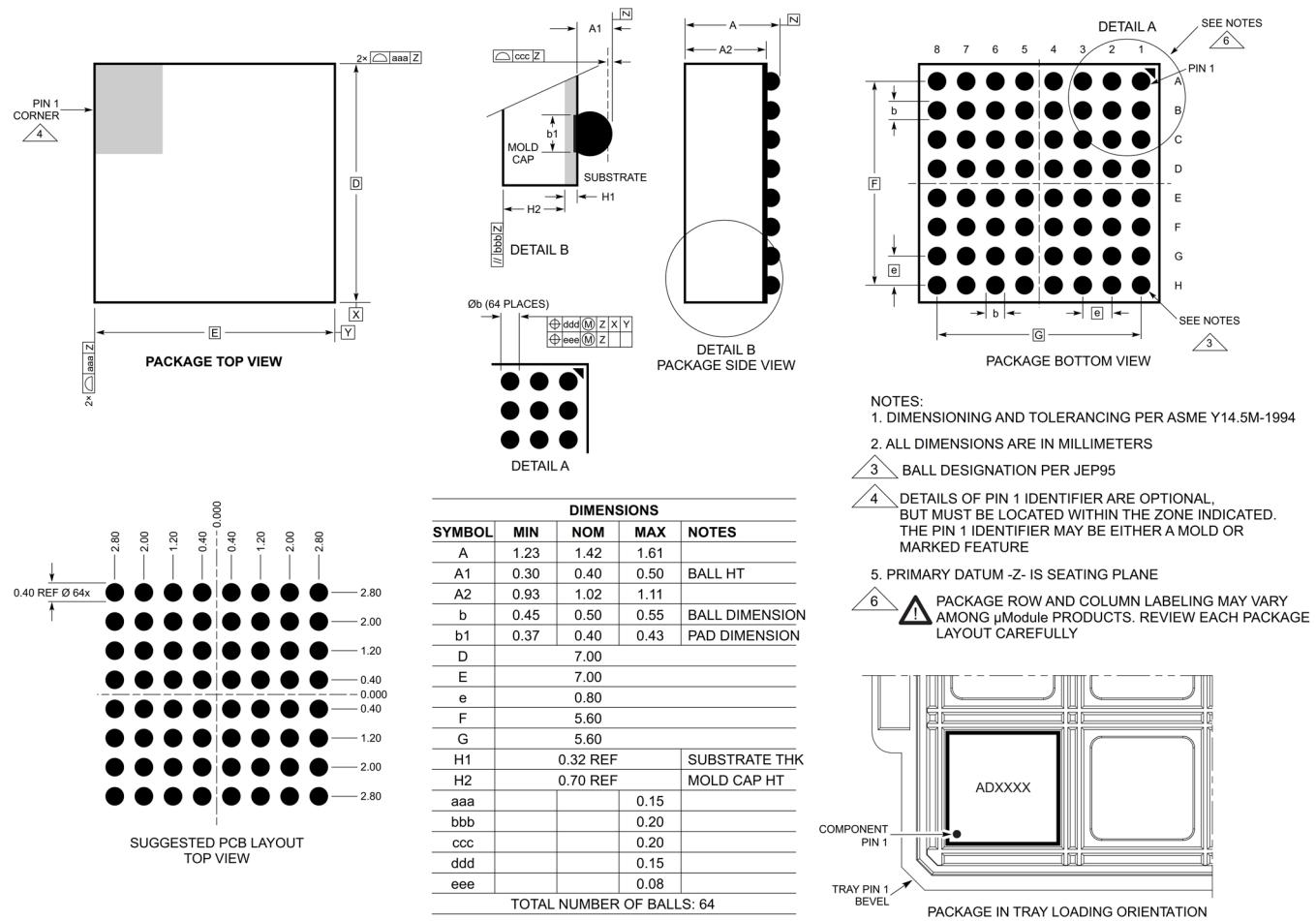

| 外形寸法                     | 68 |

| オーダー・ガイド                 | 68 |

| 評価用ボード                   | 68 |

## 改訂履歴

8/2024—Revision 0: Initial Version

## 概要

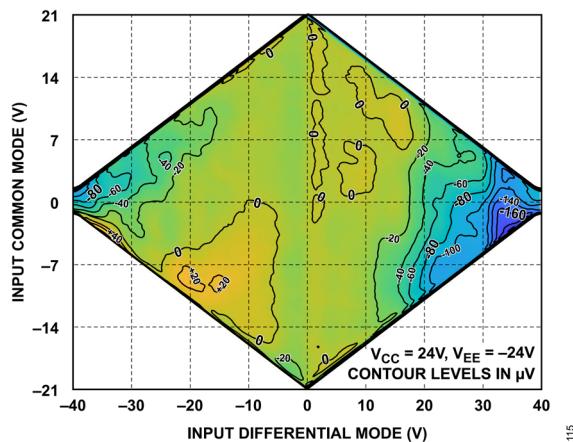

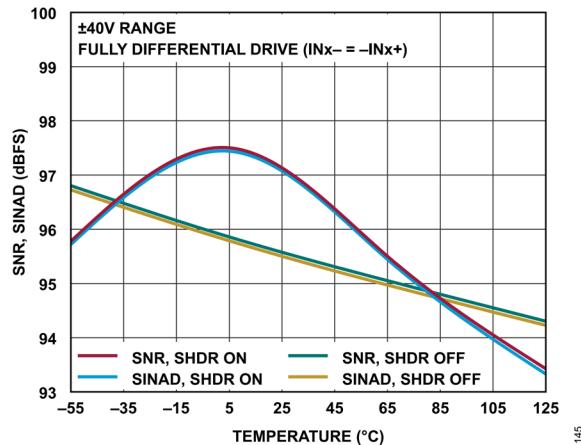

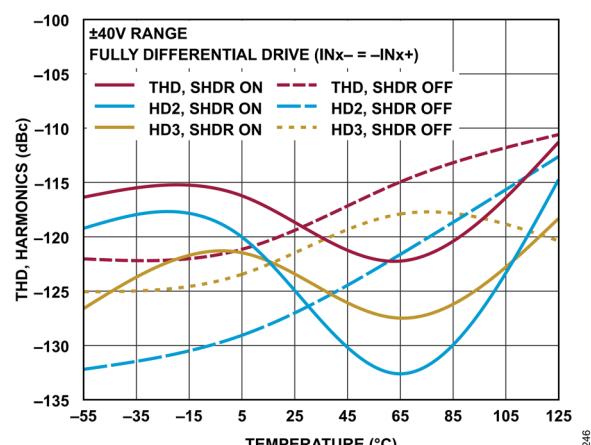

AD4856 は、8 チャンネルすべてでバッファ付きの同時サンプリングが可能な 20 ビット 250kSPS のデータ・アクイジション・システム (DAS) で、同相電圧範囲の広い差動入力を備えています。その機能アーキテクチャを図 1 に示します。5V の低電圧かつ柔軟な入力バッファの電源で動作し、高精度、低ドリフトの内蔵リファレンスおよびリファレンス・バッファを用いている AD4856 は、各チャンネルの SoftSpan レンジを個別に設定できるため、アプリケーション固有の信号振幅に対応可能で、追加の外部シグナル・コンディショニングを最小限に抑えることができます。シングル変換のダイナミック・レンジを更に拡大するために、AD4856 はシームレス・ハイ・ダイナミック・レンジ (SHDR) 技術を採用しています。これを有効にすると、チャンネルの入力信号経路ゲインがサンプルごとに自動的に最適化されるため、直線性に影響を及ぼすことなく各サンプルのコンバータ・ノイズを最小限に抑えることができます。

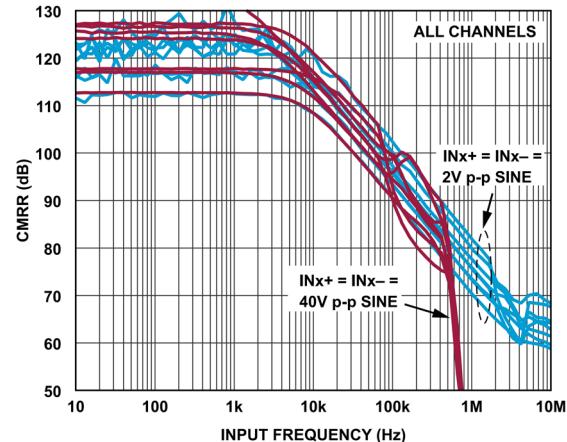

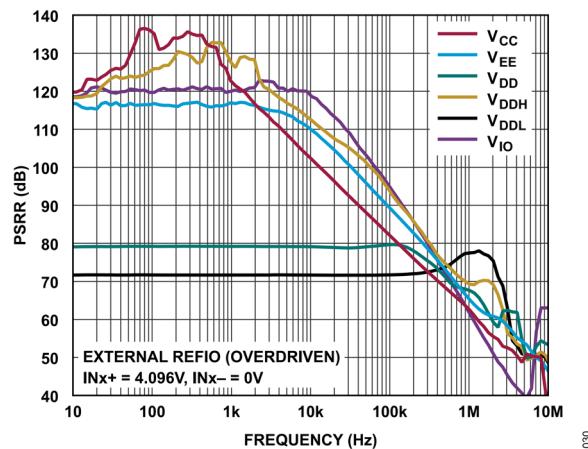

AD4856 は、11MHz の帯域幅、ピコアンペアの入力アナログ・バッファ、広い入力同相電圧範囲、120dB の同相モード除去比 (CMRR) を備えているため、DAS は INx+ および INx- での任意の振幅の入力信号を直接デジタル化できます。その入力信号の柔軟性により、 $\pm 160\mu\text{V}$  の積分非直線性 (INL) 、20 ビットでのノーミス・コード、97.2dB の S/N 比 (SNR) 、111.4dB のダイナミック・レンジと相まって、AD4856 は、高い正確性、スループット、および精度をコンパクトなソリューション・フットプリントで実現するアプリケーションに最適な選択肢となっています。24 ビットのオーバーサンプリングを有効化すれば、S/N 比およびダイナミック・レンジを更に向上できます。オプションでチャンネルごとにオフセット、ゲイン、位相を調整できるため、DAS の上流で生じるシステムレベルの誤差を補正し、また、除去することができます。

AD4856 は、シリアル・ペリフェラル・インターフェース (SPI) レジスタ設定バス (0.9V~5.25V) を備えており、低電圧差動シグナリング・バス (LVDS) と相補型金属酸化膜半導体 (CMOS) 変換データ出力バスの両方に対応できます。これらのバスの選択には LVDS/CMOS ピンを使用します。CMOS モードでは 1~8 本のデータ出力ラインを使用できるため、バスの幅およびスループットを最適化できます。

**7.00mm × 7.00mm、64 ボール・グリッド・アレイ (BGA)**

を採用した AD4856 には、重要な電源およびリファレンスのバイパス・コンデンサが内蔵されているため、ソリューション全体のフットプリントと部品数を最小限に抑えることができ、アプリケーションのプリント回路基板 (PCB) レイアウトによる影響を低減できます。本デバイスは、拡張工業用温度範囲  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  にわたって動作します。

このデータシートでは、LVDS/CMOS などの多機能ピンについて、ピン名全体を表記する場合と、ピンが持つ機能の 1 つを表記する場合があることに注意してください。例えば、LVDS 機能のみが関連する場合は、LVDS と表記されます。

## 関連製品

- ▶ **電圧リファレンス** : [LTC6655-4.096](#) または [ADR4540](#)

- ▶ **電源ソリューション** : [LT1761](#)、[LT8330](#)、[LT3042](#)

## 仕様

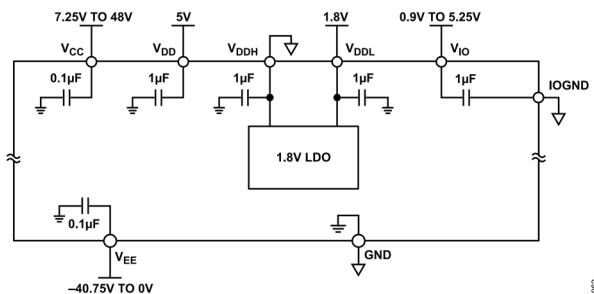

$V_{EE} = -40.75V \sim 0V$ 、 $V_{CC} = 7.25V \sim 48V$ 、 $(V_{CC} - V_{EE}) = 10V \sim 48V$ 、 $V_{DD} = 5V$ 、 $V_{DDH} = 2.5V$ 、 $1.8V$  の低ドロップアウト (LDO) レギュレータをイネーブル、 $V_{IO} = 0.9V \sim 5.25V$ 。特に指定のない限り、全チャンネルがサンプリング周波数 ( $f_s$ ) = 250kSPS で変換、内蔵リファレンスおよびリファレンス・バッファをイネーブル、全 SoftSpan レンジ、SoftSpan 15 および SoftSpan 13 では完全差動入力信号駆動、その他のバイポーラまたはユニポーラの SoftSpan レンジでは真のバイポーラまたはユニポーラ信号駆動、すべての仕様は  $T_{MIN} \sim T_{MAX}$ 。代表値は  $T_A = 25^\circ C$  での値です。

表 1. 仕様

| Parameter                                           | Test Conditions/Comments                                                             | Min                      | Typ         | Max                       | Unit    |

|-----------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------|-------------|---------------------------|---------|

| RESOLUTION                                          |                                                                                      | 20                       |             |                           | Bits    |

| ANALOG INPUTS                                       |                                                                                      |                          |             |                           |         |

| Absolute Input Voltage                              | $V_{INx+}$ <sup>1</sup> , $V_{INx-}$ <sup>2</sup> to $V_{CC}$ and $V_{EE}$           | $V_{EE} + 3.2$           |             | $V_{CC} - 3.2$            | V       |

| Differential Input Range                            | $(V_{INx+} - V_{INx-})$ , $V_{REF}$ <sup>3</sup> = $V_{REFBUF}$ <sup>4</sup> / 1.024 | $-10 \times V_{REF}$     |             | $+10 \times V_{REF}$      | V       |

|                                                     | SoftSpan 15: $\pm 10 \times V_{REF}$ range                                           | 0                        |             | $10 \times V_{REF}$       | V       |

|                                                     | SoftSpan 14: 0 V to $10 \times V_{REF}$ range                                        | -6.25 $\times V_{REF}$   |             | $+6.25 \times V_{REF}$    | V       |

|                                                     | SoftSpan 13: $\pm 6.25 \times V_{REF}$ range                                         | 0                        |             | $6.25 \times V_{REF}$     | V       |

|                                                     | SoftSpan 12: 0 V to $6.25 \times V_{REF}$ range                                      | -5 $\times V_{REF}$      |             | $+5 \times V_{REF}$       | V       |

|                                                     | SoftSpan 11: $\pm 5 \times V_{REF}$ range                                            | 0                        |             | $3.125 \times V_{REF}$    | V       |

|                                                     | SoftSpan 10: 0 V to $5 \times V_{REF}$ range                                         | -2.5 $\times V_{REF}$    |             | $+3.125 \times V_{REF}$   | V       |

|                                                     | SoftSpan 9: $\pm 3.125 \times V_{REF}$ range                                         | 0                        |             | $1.5625 \times V_{REF}$   | V       |

|                                                     | SoftSpan 8: 0 V to $3.125 \times V_{REF}$ range                                      | -1.25 $\times V_{REF}$   |             | $+1.5625 \times V_{REF}$  | V       |

|                                                     | SoftSpan 7: $\pm 2.5 \times V_{REF}$ range                                           | 0                        |             | $0.625 \times V_{REF}$    | V       |

|                                                     | SoftSpan 6: 0 V to $2.5 \times V_{REF}$ range                                        | -0.625 $\times V_{REF}$  |             | $+0.625 \times V_{REF}$   | V       |

|                                                     | SoftSpan 5: $\pm 1.5625 \times V_{REF}$ range                                        | 0                        |             | $0.3125 \times V_{REF}$   | V       |

|                                                     | SoftSpan 4: 0 V to $1.5625 \times V_{REF}$ range                                     | -0.3125 $\times V_{REF}$ |             | $0.15625 \times V_{REF}$  | V       |

|                                                     | SoftSpan 3: $\pm 1.25 \times V_{REF}$ range                                          | 0                        |             | $0.0625 \times V_{REF}$   | V       |

|                                                     | SoftSpan 2: 0 V to $1.25 \times V_{REF}$ range                                       | -0.125 $\times V_{REF}$  |             | $0.03125 \times V_{REF}$  | V       |

|                                                     | SoftSpan 1: $\pm 0.625 \times V_{REF}$ range                                         | 0                        |             | $0.015625 \times V_{REF}$ | V       |

|                                                     | SoftSpan 0: 0 V to $0.625 \times V_{REF}$ range                                      | -0.0625 $\times V_{REF}$ |             | $0.003125 \times V_{REF}$ | V       |

| Common-Mode Input Range                             | $V_{CM}$ <sup>5</sup> = $(V_{INx+} + V_{INx-})/2$                                    | $V_{EE} + 3.2$           |             | $V_{CC} - 3.2$            | V       |

| CMRR                                                | $V_{CM} = 36 V$ p-p, 200 Hz sine, SHDR on                                            | 100                      | 120         |                           | dB      |

| Differential Input Overdrive Tolerance <sup>6</sup> | $(V_{INx+} - V_{INx-})$                                                              | $-(V_{CC} - V_{EE})$     |             | $(V_{CC} - V_{EE})$       | V       |

| Input Overdrive Current Tolerance <sup>6</sup>      | $V_{INx+}, V_{INx-} > V_{CC}$                                                        |                          |             | 10                        | mA      |

| Input Leakage Current                               | $V_{INx+}, V_{INx-} < V_{EE}$                                                        | 0                        |             |                           | mA      |

| Input Resistance                                    | $V_{INx+}, V_{INx-} = V_{CC}$ to $V_{EE}$                                            | -40                      | $\pm 0.075$ | +40                       | nA      |

| Input Capacitance                                   | $R_{INx+}$ <sup>7</sup> , $R_{INx-}$ <sup>8</sup> for each pin                       |                          | 1000        |                           | GW      |

|                                                     | $C_{INx+}$ <sup>9</sup> , $C_{INx-}$ <sup>10</sup> for each pin                      |                          | 4           |                           | pF      |

| DC ACCURACY                                         |                                                                                      |                          |             |                           |         |

| No Missing Codes                                    |                                                                                      | 20                       |             |                           | Bits    |

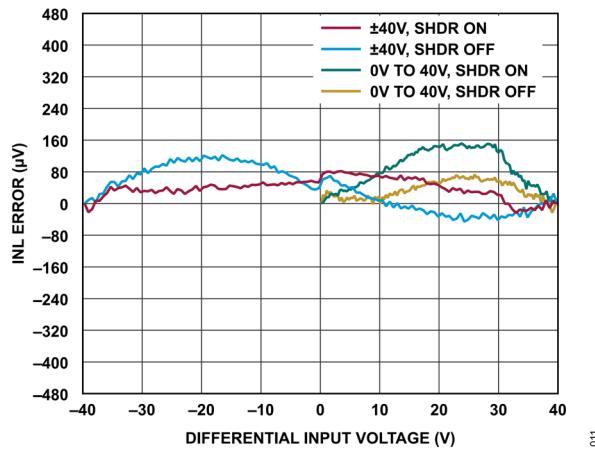

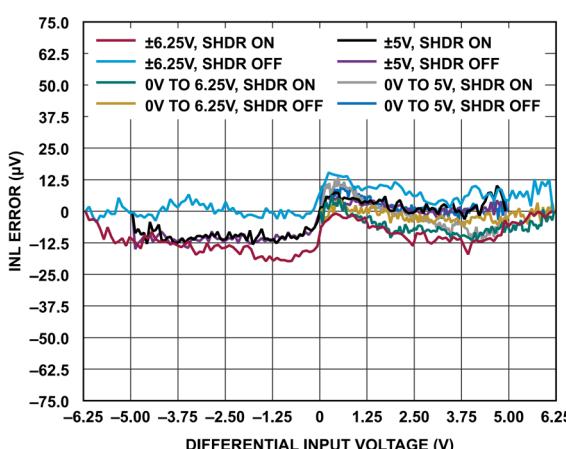

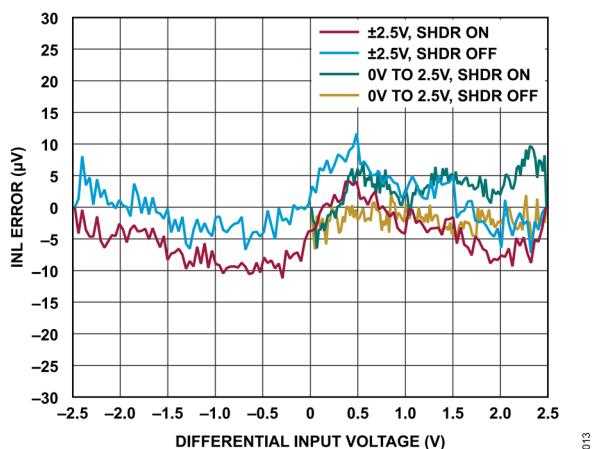

| INL Error                                           | SHDR on                                                                              |                          |             |                           |         |

|                                                     | SoftSpan 15 and SoftSpan 14: $\pm 40 V$ and 0 V to 40 V ranges                       | -725                     | $\pm 160$   | +725                      | $\mu V$ |

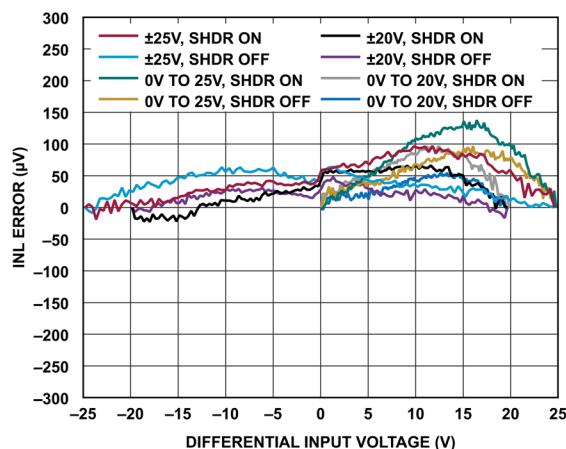

|                                                     | SoftSpan 13 and SoftSpan 12: $\pm 25 V$ and 0 V to 25 V ranges                       | -400                     | $\pm 100$   | +400                      | $\mu V$ |

|                                                     | SoftSpan 11 and SoftSpan 10: $\pm 20 V$ and 0 V to 20 V ranges                       | -400                     | $\pm 100$   | +400                      | $\mu V$ |

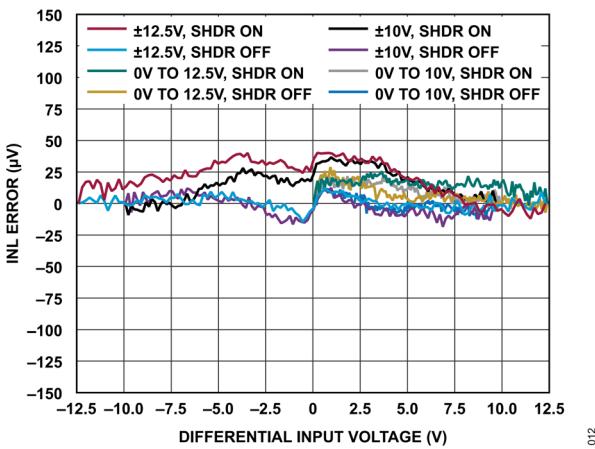

|                                                     | SoftSpan 9 and SoftSpan 8: $\pm 12.5 V$ and 0 V to 12.5 V ranges                     | -275                     | $\pm 50$    | +275                      | $\mu V$ |

|                                                     | SoftSpan 7 and SoftSpan 6: $\pm 10 V$ and 0 V to 10 V ranges                         | -220                     | $\pm 50$    | +220                      | $\mu V$ |

|                                                     | SoftSpan 5 and SoftSpan 4: $\pm 6.25 V$ and 0 V to 6.25 V ranges                     | -120                     | $\pm 25$    | +120                      | $\mu V$ |

## 仕様

表 1. 仕様 (続き)

| Parameter                               | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Typ                                                                                                                                                                                                                | Max         | Unit                                                                                                                                         |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

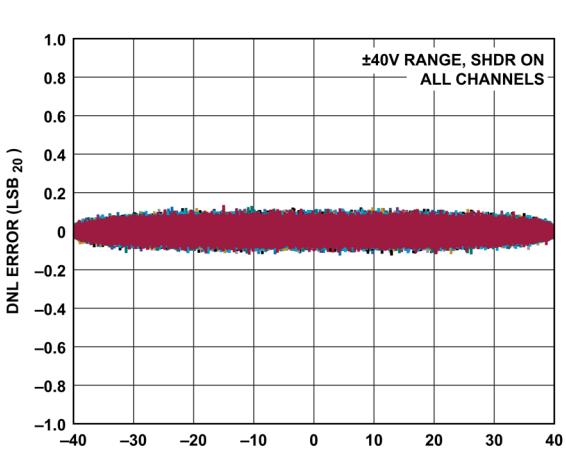

| Differential Nonlinearity (DNL) Error   | SoftSpan 3 and SoftSpan 2: $\pm 5$ V and 0 V to 5 V ranges<br>SoftSpan 1 and SoftSpan 0: $\pm 2.5$ V and 0 V to 2.5 V ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -100<br>-55<br>-0.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\pm 25$<br>$\pm 15$<br>$\pm 0.2$                                                                                                                                                                                  | +100<br>+55 | $\mu$ V<br>$\mu$ V                                                                                                                           |

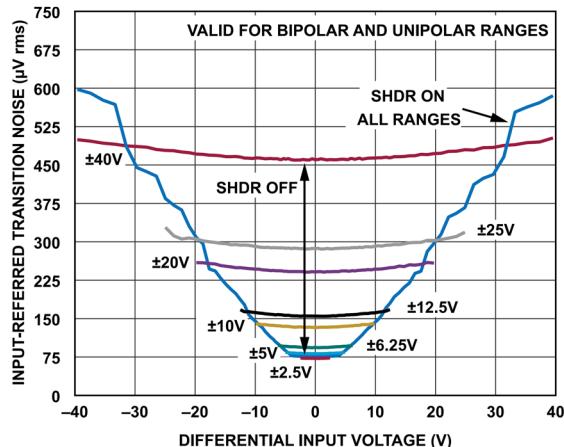

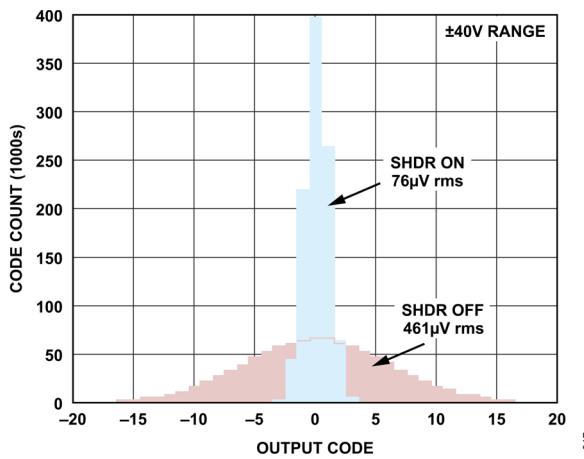

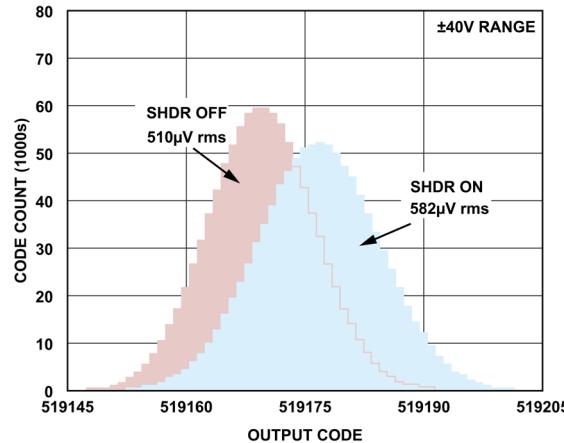

| Transition Noise <sup>11</sup>          | SHDR on, near zero-scale<br><br>SHDR off, near zero-scale<br>SoftSpan 15 and SoftSpan 14: $\pm 40$ V and 0 V to 40 V ranges<br>SoftSpan 13 and SoftSpan 12: $\pm 25$ V and 0 V to 25 V ranges<br>SoftSpan 11 and SoftSpan 10: $\pm 20$ V and 0 V to 20 V ranges<br>SoftSpan 9 and SoftSpan 8: $\pm 12.5$ V and 0 V to 12.5 V ranges<br>SoftSpan 7 and SoftSpan 6: $\pm 10$ V and 0 V to 10 V ranges<br>SoftSpan 5 and SoftSpan 4: $\pm 6.25$ V and 0 V to 6.25 V ranges<br>SoftSpan 3 and SoftSpan 2: $\pm 5$ V and 0 V to 5 V ranges<br>SoftSpan 1 and SoftSpan 0: $\pm 2.5$ V and 0 V to 2.5 V ranges |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73<br>461<br>287<br>241<br>155<br>133<br>94<br>81<br>73                                                                                                                                                            |             | $\mu$ V<br>RMS<br>$\mu$ V<br>RMS<br>$\mu$ V<br>RMS<br>$\mu$ V<br>RMS<br>$\mu$ V<br>RMS<br>$\mu$ V<br>RMS<br>$\mu$ V<br>RMS<br>$\mu$ V<br>RMS |

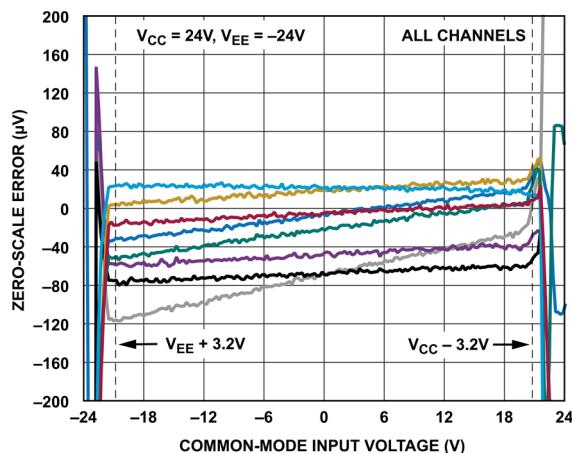

| Zero-Scale Error                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -700                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\pm 100$                                                                                                                                                                                                          | +700        | $\mu$ V                                                                                                                                      |

| Zero-Scale Error Drift                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\pm 1.5$                                                                                                                                                                                                          |             | $\mu$ V/°C                                                                                                                                   |

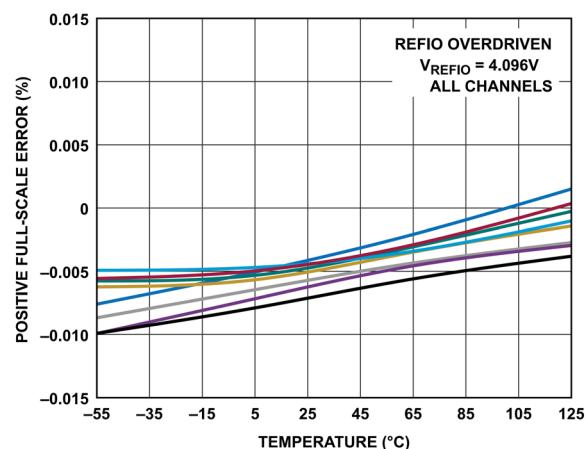

| Full-Scale Error <sup>12</sup>          | $V_{REFIO} = 4.096$ V, REFIO overdriven <sup>13</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -0.035                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\pm 0.01$                                                                                                                                                                                                         | +0.035      | %FS                                                                                                                                          |

| Full-Scale Error Drift <sup>12</sup>    | $V_{REFIO} = 4.096$ V, REFIO overdriven <sup>13</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\pm 1.5$                                                                                                                                                                                                          |             | ppm/°C                                                                                                                                       |

| AC ACCURACY <sup>14</sup>               | Dynamic Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SHDR on/off<br>SoftSpan 15: $\pm 40$ V range<br>SoftSpan 14: 0 V to 40 V range<br>SoftSpan 13: $\pm 25$ V range<br>SoftSpan 12: 0 V to 25 V range<br>SoftSpan 11: $\pm 20$ V range<br>SoftSpan 10: 0 V to 20 V range<br>SoftSpan 9: $\pm 12.5$ V range<br>SoftSpan 8: 0 V to 12.5 V range<br>SoftSpan 7: $\pm 10$ V range<br>SoftSpan 6: 0 V to 10 V range<br>SoftSpan 5: $\pm 6.25$ V range<br>SoftSpan 4: 0 V to 6.25 V range<br>SoftSpan 3: $\pm 5$ V range<br>SoftSpan 2: 0 V to 5 V range<br>SoftSpan 1: $\pm 2.5$ V range<br>SoftSpan 0: 0 V to 2.5 V range | 111.4/95.8<br>105.4/89.8<br>107.6/95.8<br>101.6/89.8<br>105.7/95.4<br>99.7/89.4<br>101.6/95.1<br>95.6/89.1<br>99.7/94.5<br>93.7/88.5<br>95.7/93.4<br>89.7/87.4<br>93.7/92.7<br>87.7/86.7<br>87.7/87.7<br>81.7/81.7 |             | dB                                                                                                                                           |

| Oversampled Dynamic Range <sup>15</sup> | OSR = 2<br>OSR = 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Dynamic Range + 3<br>Dynamic Range + 15                                                                                                                                                                            |             | dB                                                                                                                                           |

## 仕様

表 1. 仕様 (続き)

| Parameter                                    | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                                                                                                                                                                                                                                                                                                                  | Typ                                                                                                                                                                                                                                                                                                                                                | Max | Unit |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

| Signal-to-Noise-and-Distortion (SINAD) Ratio | OSR = 1024<br>SHDR on, input frequency ( $f_{IN}$ ) = 1 kHz, -1 dBFS<br>SoftSpan 15: ±40 V range<br>SoftSpan 14: 0 V to 40 V range<br>SoftSpan 13: ±25 V range<br>SoftSpan 12: 0 V to 25 V range<br>SoftSpan 11: ±20 V range<br>SoftSpan 10: 0 V to 20 V range<br>SoftSpan 9: ±12.5 V range<br>SoftSpan 8: 0 V to 12.5 V range<br>SoftSpan 7: ±10 V range<br>SoftSpan 6: 0 V to 10 V range<br>SoftSpan 5: ±6.25 V range<br>SoftSpan 4: 0 V to 6.25 V range<br>SoftSpan 3: ±5 V range<br>SoftSpan 2: 0 V to 5 V range<br>SoftSpan 1: ±2.5 V range<br>SoftSpan 0: 0 V to 2.5 V range<br>SHDR off, $f_{IN}$ = 1 kHz, -1 dBFS<br>SoftSpan 15: ±40 V range<br>SoftSpan 14: 0 V to 40 V range<br>SoftSpan 13: ±25 V range<br>SoftSpan 12: 0 V to 25 V range<br>SoftSpan 11: ±20 V range<br>SoftSpan 10: 0 V to 20 V range<br>SoftSpan 9: ±12.5 V range<br>SoftSpan 8: 0 V to 12.5 V range<br>SoftSpan 7: ±10 V range<br>SoftSpan 6: 0 V to 10 V range<br>SoftSpan 5: ±6.25 V range<br>SoftSpan 4: 0 V to 6.25 V range<br>SoftSpan 3: ±5 V range<br>SoftSpan 2: 0 V to 5 V range<br>SoftSpan 1: ±2.5 V range<br>SoftSpan 0: 0 V to 2.5 V range |                                                                                                                                                                                                                                                                                                                                                      | Dynamic Range + 27                                                                                                                                                                                                                                                                                                                                 |     | dB   |

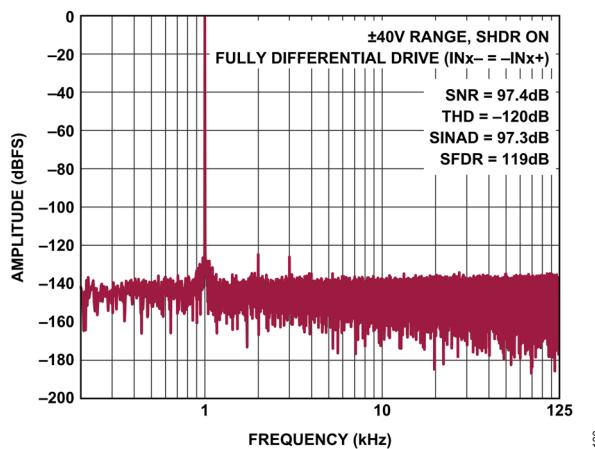

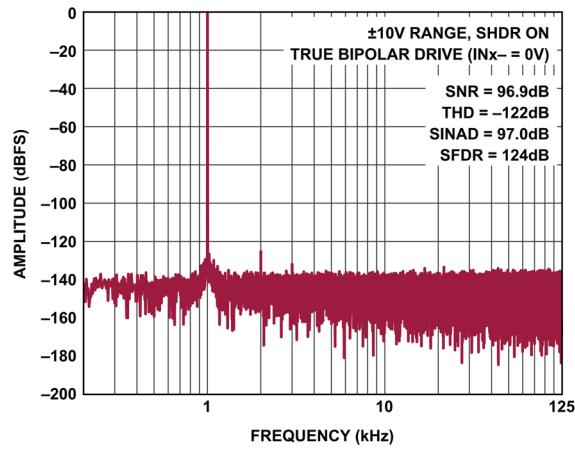

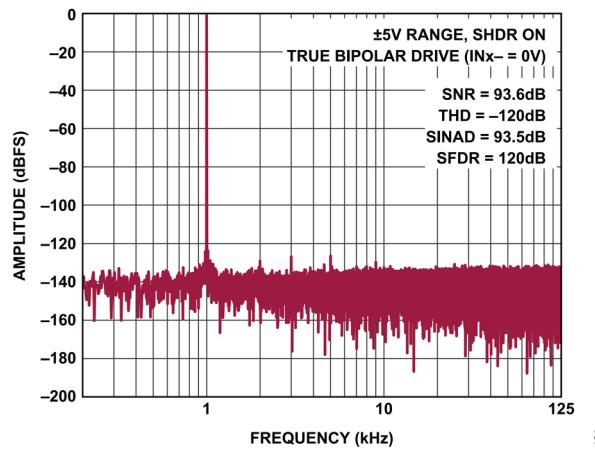

| Signal-to-Noise Ratio (SNR)                  | SHDR on, $f_{IN}$ = 1 kHz, -1 dBFS<br>SoftSpan 15: ±40 V range<br>SoftSpan 14: 0 V to 40 V range<br>SoftSpan 13: ±25 V range<br>SoftSpan 12: 0 V to 25 V range<br>SoftSpan 11: ±20 V range<br>SoftSpan 10: 0 V to 20 V range<br>SoftSpan 9: ±12.5 V range<br>SoftSpan 8: 0 V to 12.5 V range<br>SoftSpan 7: ±10 V range<br>SoftSpan 6: 0 V to 10 V range<br>SoftSpan 5: ±6.25 V range<br>SoftSpan 4: 0 V to 6.25 V range<br>SoftSpan 3: ±5 V range<br>SoftSpan 2: 0 V to 5 V range<br>SoftSpan 1: ±2.5 V range<br>SoftSpan 0: 0 V to 2.5 V range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90.9<br>85.3<br>92.6<br>86.4<br>93.5<br>87.2<br>94.3<br>88.2<br>94.1<br>88.1<br>92.4<br>86.8<br>91.1<br>85.4<br>85.3<br>79.7<br>93.1<br>87.1<br>93.2<br>87.3<br>92.9<br>86.9<br>92.6<br>86.7<br>92.2<br>86.2<br>91.2<br>85.4<br>90.3<br>84.6<br>85.3<br>79.7<br>90.9<br>85.3<br>92.6<br>86.4<br>93.6<br>87.2<br>94.3<br>88.2<br>94.1<br>88.1<br>92.5 | 97.2<br>92<br>97.4<br>92.0<br>97.9<br>92.0<br>97.2<br>91.5<br>96.6<br>90.9<br>94.6<br>88.7<br>93.1<br>87.3<br>87.3<br>81.6<br>95.3<br>89.4<br>95.3<br>89.4<br>95.0<br>89.0<br>94.7<br>88.8<br>94.2<br>88.2<br>93.1<br>87.2<br>92.3<br>86.5<br>87.4<br>81.6<br>97.2<br>92.0<br>97.4<br>92.0<br>97.9<br>92.0<br>97.2<br>91.5<br>96.6<br>90.9<br>94.6 |     | dB   |

## 仕様

表 1. 仕様 (続き)

| Parameter                          | Test Conditions/Comments              | Min  | Typ  | Max | Unit |

|------------------------------------|---------------------------------------|------|------|-----|------|

|                                    | SoftSpan 4: 0 V to 6.25 V range       | 86.8 | 88.7 |     | dB   |

|                                    | SoftSpan 3: $\pm 5$ V range           | 91.2 | 93.1 |     | dB   |

|                                    | SoftSpan 2: 0 V to 5 V range          | 85.5 | 87.3 |     | dB   |

|                                    | SoftSpan 1: $\pm 2.5$ V range         | 85.4 | 87.3 |     | dB   |

|                                    | SoftSpan 0: 0 V to 2.5 V range        | 79.8 | 81.6 |     | dB   |

|                                    | SHDR off, $f_{IN} = 1$ kHz, $-1$ dBFS |      |      |     |      |

|                                    | SoftSpan 15: $\pm 40$ V range         | 93.2 | 95.3 |     | dB   |

|                                    | SoftSpan 14: 0 V to 40 V range        | 87.1 | 89.4 |     | dB   |

|                                    | SoftSpan 13: $\pm 25$ V range         | 93.2 | 95.3 |     | dB   |

|                                    | SoftSpan 12: 0 V to 25 V range        | 87.3 | 89.4 |     | dB   |

|                                    | SoftSpan 11: $\pm 20$ V range         | 92.9 | 95.0 |     | dB   |

|                                    | SoftSpan 10: 0 V to 20 V range        | 86.9 | 89.0 |     | dB   |

|                                    | SoftSpan 9: $\pm 12.5$ V range        | 92.7 | 94.7 |     | dB   |

|                                    | SoftSpan 8: 0 V to 12.5 V range       | 86.8 | 88.8 |     | dB   |

|                                    | SoftSpan 7: $\pm 10$ V range          | 92.2 | 94.2 |     | dB   |

|                                    | SoftSpan 6: 0 V to 10 V range         | 86.2 | 88.2 |     | dB   |

|                                    | SoftSpan 5: $\pm 6.25$ V range        | 91.2 | 93.1 |     | dB   |

|                                    | SoftSpan 4: 0 V to 6.25 V range       | 85.4 | 87.2 |     | dB   |

|                                    | SoftSpan 3: $\pm 5$ V range           | 90.4 | 92.3 |     | dB   |

|                                    | SoftSpan 2: 0 V to 5 V range          | 84.7 | 86.5 |     | dB   |

|                                    | SoftSpan 1: $\pm 2.5$ V range         | 85.4 | 87.4 |     | dB   |

|                                    | SoftSpan 0: 0 V to 2.5 V range        | 79.8 | 81.6 |     | dB   |

| Total Harmonic Distortion (THD)    | $f_{IN} = 1$ kHz, $-1$ dBFS           |      |      |     |      |

|                                    | SoftSpan 15: $\pm 40$ V range         | -117 | -99  |     | dB   |

|                                    | SoftSpan 14: 0 V to 40 V range        | -109 | -95  |     | dB   |

|                                    | SoftSpan 13: $\pm 25$ V range         | -117 | -100 |     | dB   |

|                                    | SoftSpan 12: 0 V to 25 V range        | -111 | -98  |     | dB   |

|                                    | SoftSpan 11: $\pm 20$ V range         | -114 | -99  |     | dB   |

|                                    | SoftSpan 10: 0 V to 20 V range        | -112 | -99  |     | dB   |

|                                    | SoftSpan 9: $\pm 12.5$ V range        | -114 | -100 |     | dB   |

|                                    | SoftSpan 8: 0 V to 12.5 V range       | -113 | -100 |     | dB   |

|                                    | SoftSpan 7: $\pm 10$ V range          | -115 | -100 |     | dB   |

|                                    | SoftSpan 6: 0 V to 10 V range         | -113 | -100 |     | dB   |

|                                    | SoftSpan 5: $\pm 6.25$ V range        | -115 | -99  |     | dB   |

|                                    | SoftSpan 4: 0 V to 6.25 V range       | -113 | -99  |     | dB   |

|                                    | SoftSpan 3: $\pm 5$ V range           | -114 | -97  |     | dB   |

|                                    | SoftSpan 2: 0 V to 5 V range          | -113 | -97  |     | dB   |

|                                    | SoftSpan 1: $\pm 2.5$ V range         | -109 | -92  |     | dB   |

|                                    | SoftSpan 0: 0 V to 2.5 V range        | -110 | -92  |     | dB   |

| Spurious-Free Dynamic Range (SFDR) | $f_{IN} = 1$ kHz, $-1$ dBFS           |      |      |     |      |

|                                    | SoftSpan 15: $\pm 40$ V range         | 101  | 119  |     | dB   |

|                                    | SoftSpan 14: 0 V to 40 V range        | 99   | 113  |     | dB   |

|                                    | SoftSpan 13: $\pm 25$ V range         | 101  | 119  |     | dB   |

|                                    | SoftSpan 12: 0 V to 25 V range        | 103  | 115  |     | dB   |

|                                    | SoftSpan 11: $\pm 20$ V range         | 103  | 119  |     | dB   |

|                                    | SoftSpan 10: 0 V to 20 V range        | 103  | 116  |     | dB   |

|                                    | SoftSpan 9: $\pm 12.5$ V range        | 104  | 119  |     | dB   |

|                                    | SoftSpan 8: 0 V to 12.5 V range       | 104  | 116  |     | dB   |

## 仕様

表 1. 仕様 (続き)

| Parameter                                                | Test Conditions/Comments                                                                                                                                                                                                                                                                                      | Min                                                | Typ                                                  | Max        | Unit                                         |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------|------------|----------------------------------------------|

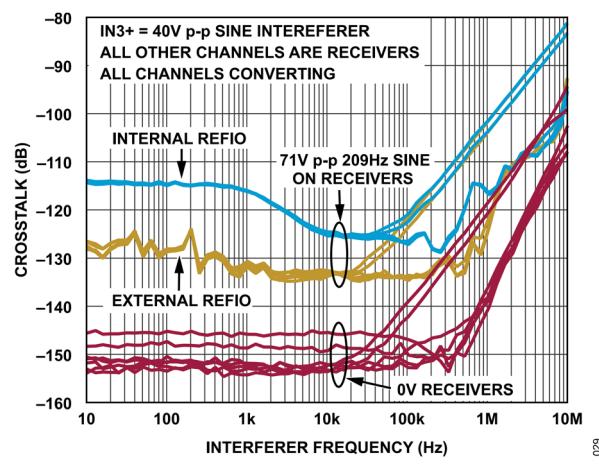

| Channel-to-Channel Crosstalk                             | SoftSpan 7: $\pm 10$ V range<br>SoftSpan 6: 0 V to 10 V range<br>SoftSpan 5: $\pm 6.25$ V range<br>SoftSpan 4: 0 V to 6.25 V range<br>SoftSpan 3: $\pm 5$ V range<br>SoftSpan 2: 0 V to 5 V range<br>SoftSpan 1: $\pm 2.5$ V range<br>SoftSpan 0: 0 V to 2.5 V range<br>All channels converting <sup>16</sup> | 105<br>105<br>103<br>103<br>101<br>101<br>96<br>96 | 119<br>116<br>118<br>117<br>117<br>117<br>111<br>113 | -120<br>11 | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| -3 dB Small-Signal Input Bandwidth                       |                                                                                                                                                                                                                                                                                                               |                                                    | 1                                                    | 300        | MHz<br>ps                                    |

| Aperture Delay                                           |                                                                                                                                                                                                                                                                                                               |                                                    | 1                                                    | 1          | ps RMS                                       |

| Aperture Delay Matching                                  |                                                                                                                                                                                                                                                                                                               |                                                    | 300                                                  | 300        | ns                                           |

| Aperture Jitter                                          |                                                                                                                                                                                                                                                                                                               |                                                    | 1                                                    | 1          | ns                                           |

| Full-Scale Input Step Settling Time                      | Full-scale step, 50 ppm settling                                                                                                                                                                                                                                                                              |                                                    |                                                      | 300        | ns                                           |

| INTERNAL REFERENCE ENABLED                               |                                                                                                                                                                                                                                                                                                               |                                                    |                                                      |            |                                              |

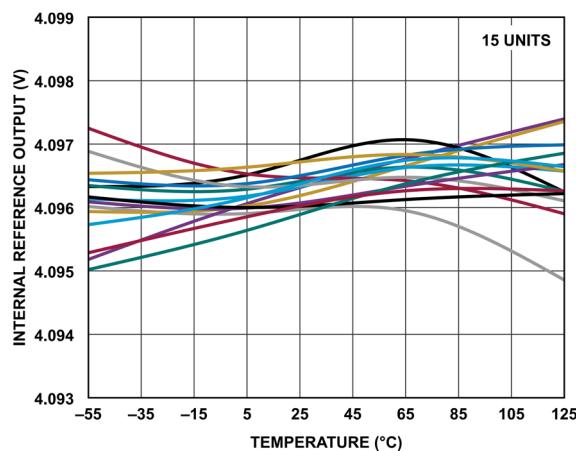

| Internal Reference Output Voltage ( $V_{REFIO}$ )        | $T_A = 25^\circ\text{C}$                                                                                                                                                                                                                                                                                      | 4.093                                              | 4.096                                                | 4.099      | V                                            |

| Internal Reference Temperature Coefficient <sup>17</sup> |                                                                                                                                                                                                                                                                                                               | -10                                                | $\pm 2$                                              | +10        | ppm/ $^\circ\text{C}$                        |

| Internal Reference Line Regulation                       | $V_{DD} = 4.75$ V to 5.25 V                                                                                                                                                                                                                                                                                   |                                                    | 50                                                   |            | $\mu\text{V/V}$                              |

| REFIO Output Resistance                                  |                                                                                                                                                                                                                                                                                                               |                                                    | 58                                                   |            | $\Omega$                                     |

| REFIO Output Capacitance                                 |                                                                                                                                                                                                                                                                                                               |                                                    | 10                                                   |            | nF                                           |

| INTERNAL REFERENCE DISABLED                              | REFIO overdriven <sup>13</sup>                                                                                                                                                                                                                                                                                |                                                    |                                                      |            |                                              |

| REFIO Input Voltage ( $V_{REFIO}$ )                      |                                                                                                                                                                                                                                                                                                               | 4.071                                              | 4.096                                                | 4.121      | V                                            |

| REFIO Input Resistance                                   |                                                                                                                                                                                                                                                                                                               |                                                    | 38                                                   |            | k $\Omega$                                   |

| REFIO Input Capacitance                                  |                                                                                                                                                                                                                                                                                                               |                                                    | 10                                                   |            | nF                                           |

| REFERENCE BUFFER ENABLED                                 |                                                                                                                                                                                                                                                                                                               |                                                    |                                                      |            |                                              |

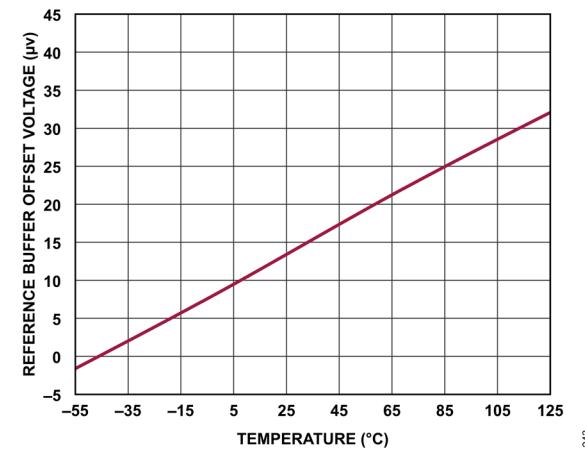

| Reference Buffer Offset Voltage ( $V_{OS}$ )             | $V_{OS} = (V_{REFBUF} - V_{REFIO})$ , $T_A = 25^\circ\text{C}$                                                                                                                                                                                                                                                | -100                                               | $\pm 20$                                             | +100       | $\mu\text{V}$                                |

| Reference Buffer Offset Voltage Drift                    |                                                                                                                                                                                                                                                                                                               |                                                    | $\pm 0.5$                                            |            | $\mu\text{V}/^\circ\text{C}$                 |

| REFERENCE BUFFER DISABLED                                | REFBUF overdriven <sup>18</sup>                                                                                                                                                                                                                                                                               |                                                    |                                                      |            |                                              |

| REFBUF Input Voltage ( $V_{REFBUF}$ )                    |                                                                                                                                                                                                                                                                                                               | 4.071                                              | 4.096                                                | 4.121      | V                                            |

| REFBUF Input Current ( $I_{REFBUF}$ ) <sup>19</sup>      | $V_{REFBUF} = 4.096$ V, $f_S = 250$ kSPS<br>$V_{REFBUF} = 4.096$ V, not converting                                                                                                                                                                                                                            |                                                    | 2.5<br>2.2                                           | 3.4        | mA<br>mA                                     |

| SCALED REFERENCE OUTPUT                                  |                                                                                                                                                                                                                                                                                                               |                                                    |                                                      |            |                                              |

| REF2500 Output Voltage ( $V_{REF2500}$ )                 | $T_A = 25^\circ\text{C}$                                                                                                                                                                                                                                                                                      | 2.497                                              | 2.5                                                  | 2.503      | V                                            |

| REF2500 Temperature Coefficient <sup>17</sup>            |                                                                                                                                                                                                                                                                                                               | -10                                                | $\pm 2$                                              | +10        | ppm/ $^\circ\text{C}$                        |

| REF2500 Output Resistance                                |                                                                                                                                                                                                                                                                                                               |                                                    | 26                                                   |            | k $\Omega$                                   |

## 仕様

表 1. 仕様 (続き)

| Parameter                                        | Test Conditions/Comments                                                                       | Min                  | Typ                  | Max            | Unit      |

|--------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------|-----------|

| CMOS DIGITAL INPUTS                              |                                                                                                |                      |                      |                |           |

| Input Voltage High ( $V_{IH}$ )                  |                                                                                                | 0.8                  |                      |                | V         |

| CNV                                              |                                                                                                | 4                    |                      |                | V         |

| HIVIO/LOVIO                                      |                                                                                                | $0.85 \times V_{IO}$ |                      |                | V         |

| All Other Pins                                   |                                                                                                |                      |                      |                | V         |

| Input Voltage Low ( $V_{IL}$ )                   |                                                                                                |                      |                      |                |           |

| CNV                                              |                                                                                                |                      | 0.4                  |                | V         |

| HIVIO/LOVIO                                      |                                                                                                |                      | 1                    |                | V         |

| All Other Pins                                   |                                                                                                |                      | $0.15 \times V_{IO}$ |                | V         |

| Digital Input Current ( $I_{IN}$ )               |                                                                                                |                      |                      |                |           |

| CNV                                              |                                                                                                | -100                 |                      | +100           | $\mu A$   |

| HIVIO/LOVIO                                      |                                                                                                | -10                  |                      | +10            | $\mu A$   |

| All Other Pins                                   |                                                                                                | -10                  |                      | +10            | $\mu A$   |

| Digital Input Capacitance ( $C_{IN}$ )           |                                                                                                |                      | 2                    |                | $pF$      |

| CMOS DIGITAL OUTPUTS                             |                                                                                                |                      |                      |                |           |

| Output Voltage High ( $V_{OH}$ )                 | Source current ( $I_{SOURCE}$ ) = 500 $\mu A$                                                  | $V_{IO} - 0.2$       |                      |                | V         |

| Output Voltage Low ( $V_{OL}$ )                  | Sink current ( $I_{SINK}$ ) = 500 $\mu A$                                                      |                      |                      | 0.2            | V         |

| High-Z Output Leakage Current ( $I_{OZ}$ )       |                                                                                                | -10                  |                      | +10            | $\mu A$   |

| LVDS DIGITAL INPUTS                              |                                                                                                |                      |                      |                |           |

| Differential Input Voltage ( $V_{ID}$ )          | $\overline{CS} = 0 V$ , $V_{ICM} = 1.2 V$ , termination enabled <sup>20</sup>                  | $\pm 200$            | $\pm 350$            | $\pm 600$      | $mV$      |

| Differential Termination Resistance ( $R_{ID}$ ) |                                                                                                | 95                   | 107                  | 120            | $\Omega$  |

| Common-Mode Input Voltage ( $V_{ICM}$ )          | $\overline{CS} = V_{IO}$ or termination disabled <sup>20</sup><br>$1.71 V \leq V_{IO} < 2.5 V$ |                      | 10                   |                | $M\Omega$ |

| Common-Mode Input Current ( $I_{ICM}$ )          | $2.5 V \leq V_{IO} \leq 5.25 V$                                                                | 0.3                  | 1.2                  | $V_{IO} - 0.3$ | V         |

| Common-Mode Input Current ( $I_{ICM}$ )          |                                                                                                | 0.3                  | 1.2                  | 2.2            | V         |

| Common-Mode Input Current ( $I_{ICM}$ )          |                                                                                                | -10                  |                      | +10            | $\mu A$   |

| LVDS DIGITAL OUTPUTS                             |                                                                                                |                      |                      |                |           |

| Differential Output Voltage ( $V_{OD}$ )         | 100 $\Omega$ differential termination, full-bias mode <sup>20</sup>                            | $\pm 260$            | $\pm 330$            | $\pm 400$      | $mV$      |

| Common-Mode Output Voltage ( $V_{OCM}$ )         | 100 $\Omega$ differential termination, half-bias mode <sup>20</sup>                            | $\pm 135$            | $\pm 185$            | $\pm 235$      | $mV$      |

| High-Z Output Leakage Current ( $I_{OZ}$ )       | 100 $\Omega$ differential termination                                                          | 1.1                  | 1.25                 | 1.4            | V         |

| High-Z Output Leakage Current ( $I_{OZ}$ )       |                                                                                                | -10                  |                      | +10            | $\mu A$   |

| POWER SUPPLY VOLTAGES                            |                                                                                                |                      |                      |                |           |

| $V_{CC}$                                         |                                                                                                | 7.25                 |                      | 48             | V         |

| $V_{EE}$                                         |                                                                                                | -40.75               |                      | 0              | V         |

| $V_{CC} - V_{EE}$                                |                                                                                                | 10                   |                      | 48             | V         |

| $V_{DD}$                                         |                                                                                                | 4.75                 | 5.0                  | 5.25           | V         |

| $V_{DDH}$                                        | Disables 1.8 V LDO regulator                                                                   |                      | 0                    |                | V         |

| $V_{DDH}$                                        | Enables 1.8 V LDO regulator                                                                    | 2.2                  |                      | 5.25           | V         |

| $V_{DDL}$                                        | Supplied externally, 1.8 V LDO regulator disabled                                              | 1.71                 | 1.8                  | 1.89           | V         |

| $V_{DDL}$                                        | Supplied by 1.8 V LDO regulator, no external connection                                        |                      | 1.8                  |                | V         |

| $V_{IO}$                                         |                                                                                                |                      |                      |                |           |

| CMOS Conversion Data Output                      | $HIVIO/\overline{LOVIO} = V_{DD}$                                                              | 1.71                 |                      | 5.25           | V         |

| CMOS Conversion Data Output                      | $HIVIO/\overline{LOVIO} = GND$                                                                 | 0.9                  |                      | 1.89           | V         |

## 仕様

表 1. 仕様 (続き)

| Parameter                               | Test Conditions/Comments                                                 | Min  | Typ  | Max  | Unit |

|-----------------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| LVDS Conversion Data Output             | HIVIO/LOVIO = $V_{DD}$                                                   | 1.71 |      | 5.25 | V    |

|                                         | HIVIO/LOVIO = GND                                                        | 1.71 |      | 1.89 | V    |

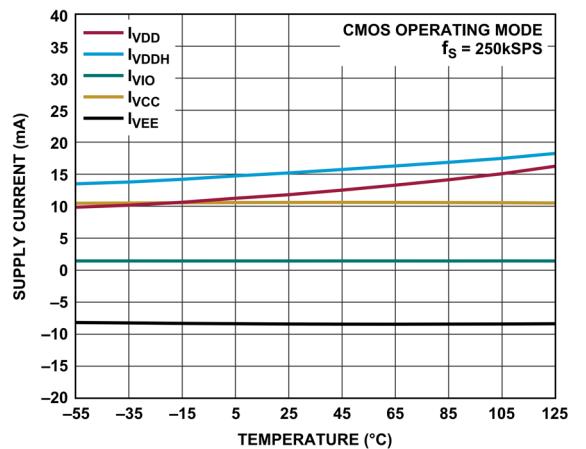

| POWER SUPPLY CURRENTS                   |                                                                          |      |      |      |      |

| CMOS Conversion Data Output             | 25 pF load on CMOS outputs                                               |      |      |      |      |

| Operating Mode <sup>21</sup>            | $f_S = 250$ kSPS, all channels converting                                |      |      |      |      |

| $I_{V_{CC}}$ Current ( $I_{V_{CC}}$ )   | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       |      | 10.7 | 14.1 | mA   |

|                                         | $V_{CC} = +15$ V, $V_{EE} = -15$ V                                       |      | 10.3 |      | mA   |

|                                         | $V_{CC} = +8.2$ V, $V_{EE} = -3.2$ V                                     |      | 9.8  |      | mA   |

| $I_{V_{EE}}$ Current ( $I_{V_{EE}}$ )   | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       | -12  | -8.7 |      | mA   |

|                                         | $V_{CC} = +15$ V, $V_{EE} = -15$ V                                       |      | -8.2 |      | mA   |

|                                         | $V_{CC} = +8.2$ V, $V_{EE} = -3.2$ V                                     |      | -7.6 |      | mA   |

| $I_{V_{DD}}$ Current ( $I_{V_{DD}}$ )   | Reference and reference buffer enabled                                   |      | 12.2 | 18.7 | mA   |

|                                         | $V_{REFIO} = 4.096$ V, REFIO overdriven <sup>13</sup>                    |      | 10.2 |      | mA   |

|                                         | $V_{REFBUF} = 4.096$ V, REFBUF overdriven <sup>18</sup>                  |      | 1.9  |      | mA   |

| $I_{V_{DDH}}$ Current ( $I_{V_{DDH}}$ ) | $V_{DDH} = 2.5$ V, 1.8 V LDO regulator enabled                           |      | 15   | 20.5 | mA   |

| $I_{V_{DDL}}$ Current ( $I_{V_{DDL}}$ ) | $V_{DDH} = \text{GND}$ , 1.8 V LDO regulator disabled, $V_{DDL} = 1.8$ V |      | 14.5 | 20   | mA   |

| $I_{V_{IO}}$ Current ( $I_{V_{IO}}$ )   | $V_{IO} = 2.5$ V                                                         |      | 1.4  | 1.9  | mA   |

| Acquisition Mode                        |                                                                          |      |      |      |      |

| $I_{V_{CC}}$                            | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       |      | 9.4  |      | mA   |

| $I_{V_{EE}}$                            | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       |      | -7.4 |      | mA   |

| $I_{V_{DD}}$                            | Reference and reference buffer enabled                                   |      | 10.8 |      | mA   |

|                                         | $V_{REFIO} = 4.096$ V, REFIO overdriven <sup>13</sup>                    |      | 8.8  |      | mA   |

|                                         | $V_{REFBUF} = 4.096$ V, REFBUF overdriven <sup>18</sup>                  |      | 1.4  |      | mA   |

| $I_{V_{DDH}}$                           | $V_{DDH} = 2.5$ V, 1.8 V LDO regulator enabled                           |      | 72   |      | µA   |

| $I_{V_{DDL}}$                           | $V_{DDH} = \text{GND}$ , 1.8 V LDO regulator disabled, $V_{DDL} = 1.8$ V |      | 16   |      | µA   |

| $I_{V_{IO}}$                            | $V_{IO} = 2.5$ V                                                         |      | 1    |      | µA   |

| Nap Mode                                |                                                                          |      |      |      |      |

| $I_{V_{CC}}$                            | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       |      | 4.5  |      | mA   |

| $I_{V_{EE}}$                            | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       |      | -3.3 |      | mA   |

| $I_{V_{DD}}$                            | Reference and reference buffer enabled                                   |      | 10.3 |      | mA   |

|                                         | $V_{REFIO} = 4.096$ V, REFIO overdriven <sup>13</sup>                    |      | 8.3  |      | mA   |

|                                         | $V_{REFBUF} = 4.096$ V, REFBUF overdriven <sup>18</sup>                  |      | 1.0  |      | mA   |

| $I_{V_{DDH}}$                           | $V_{DDH} = 2.5$ V, 1.8 V LDO regulator enabled                           |      | 72   |      | µA   |

| $I_{V_{DDL}}$                           | $V_{DDH} = \text{GND}$ , 1.8 V LDO regulator disabled, $V_{DDL} = 1.8$ V |      | 16   |      | µA   |

| $I_{V_{IO}}$                            | $V_{IO} = 2.5$ V                                                         |      | 1    |      | µA   |

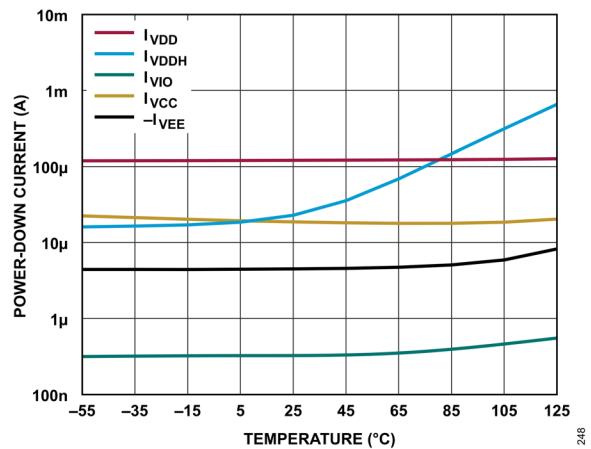

| Power-Down Mode                         |                                                                          |      |      |      |      |

| $I_{V_{CC}}$                            | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       |      | 18   |      | µA   |

| $I_{V_{EE}}$                            | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       |      | -4   |      | µA   |

| $I_{V_{DD}}$                            |                                                                          |      | 130  |      | µA   |

| $I_{V_{DDH}}$                           | $V_{DDH} = 2.5$ V, 1.8 V LDO regulator enabled                           |      | 30   |      | µA   |

| $I_{V_{DDL}}$                           | $V_{DDH} = \text{GND}$ , 1.8 V LDO regulator disabled, $V_{DDL} = 1.8$ V |      | 16   |      | µA   |

| $I_{V_{IO}}$                            | $V_{IO} = 2.5$ V                                                         |      | 1    |      | µA   |

| LVDS Conversion Data Output             | 100 $\Omega$ differential load on LVDS outputs                           |      |      |      |      |

| Operating Mode                          | $f_S = 250$ kSPS, all channels converting                                |      |      |      |      |

| $I_{V_{CC}}$                            | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       |      | 10.7 | 14.1 | mA   |

|                                         | $V_{CC} = +15$ V, $V_{EE} = -15$ V                                       |      | 10.3 |      | mA   |

|                                         | $V_{CC} = +8.2$ V, $V_{EE} = -3.2$ V                                     |      | 9.8  |      | mA   |

| $I_{V_{EE}}$                            | $V_{CC} = +24$ V, $V_{EE} = -24$ V                                       | -12  | -8.7 |      | mA   |

## 仕様

表 1. 仕様 (続き)

| Parameter                   | Test Conditions/Comments                                                                                                   | Min | Typ  | Max  | Unit |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| $I_{V_{DD}}$                | $V_{CC} = +15\text{ V}, V_{EE} = -15\text{ V}$                                                                             |     | -8.2 |      | mA   |

|                             | $V_{CC} = +8.2\text{ V}, V_{EE} = -3.2\text{ V}$                                                                           |     | -7.6 |      | mA   |

|                             | Reference and reference buffer enabled                                                                                     |     | 13.7 | 20.4 | mA   |

|                             | $V_{REFIO} = 4.096\text{ V}$ , REFIO overdriven <sup>13</sup>                                                              |     | 11.7 |      | mA   |

|                             | $V_{REFBUF} = 4.096\text{ V}$ , REFBUF overdriven <sup>18</sup>                                                            |     | 3.4  |      | mA   |

| $I_{V_{DDH}}$               | $V_{DDH} = 2.5\text{ V}$ , 1.8 V LDO regulator enabled                                                                     |     | 23.5 | 31   | mA   |

| $I_{V_{DDL}}$               | $V_{DDH} = \text{GND}$ , 1.8 V LDO regulator disabled, $V_{DDL} = 1.8\text{ V}$                                            |     | 23   | 30.5 | mA   |

| $I_{V_{IO}}$                | $V_{IO} = 2.5\text{ V}$                                                                                                    |     | 22   | 165  | μA   |

| Acquisition Mode            |                                                                                                                            |     |      |      |      |

| $I_{V_{CC}}$                | $V_{CC} = +24\text{ V}, V_{EE} = -24\text{ V}$                                                                             |     | 9.4  |      | mA   |

| $I_{V_{EE}}$                | $V_{CC} = +24\text{ V}, V_{EE} = -24\text{ V}$                                                                             |     | -7.4 |      | mA   |

| $I_{V_{DD}}$                | Reference and reference buffer enabled                                                                                     |     | 11.6 |      | mA   |

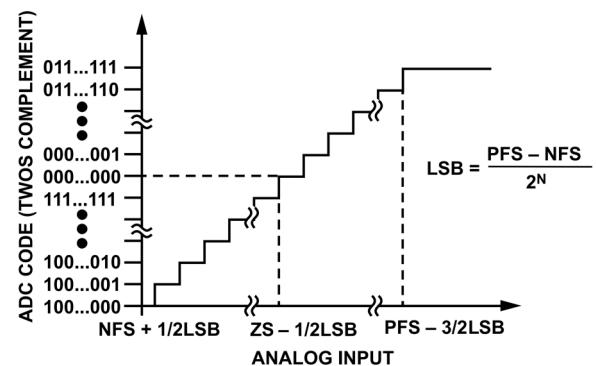

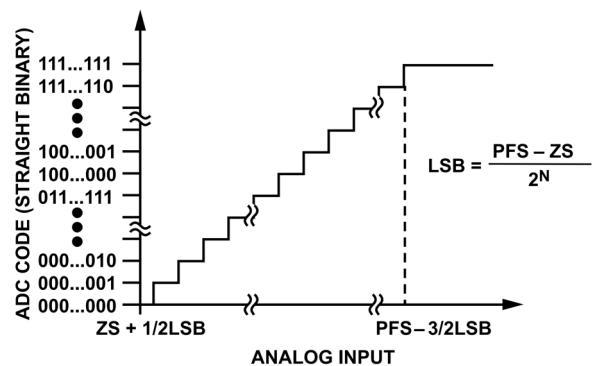

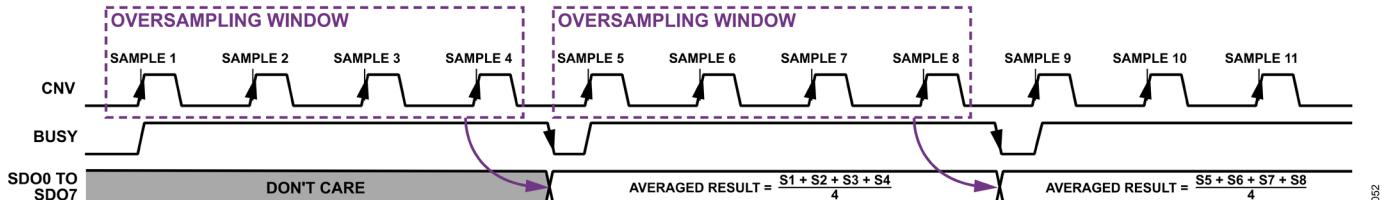

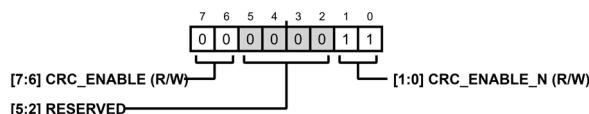

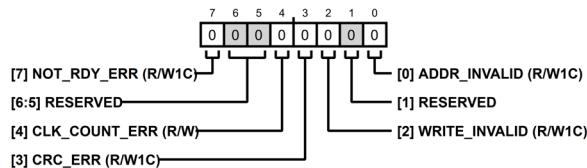

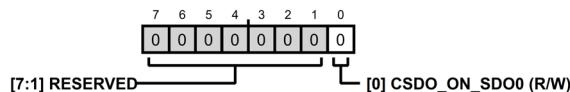

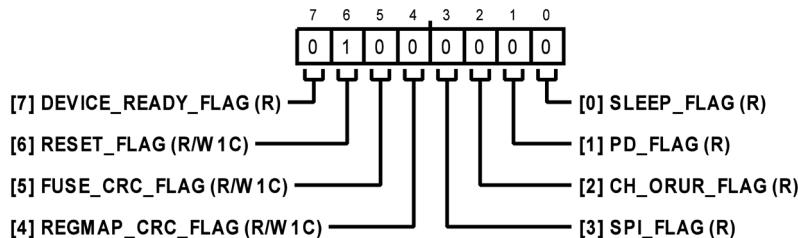

|                             | $V_{REFIO} = 4.096\text{ V}$ , REFIO overdriven <sup>13</sup>                                                              |     | 9.6  |      | mA   |