# 24 ビット、62.5kSPS、マルチチャンネル、 低ノイズ高精度シグマデルタ型 ADC

## 特長

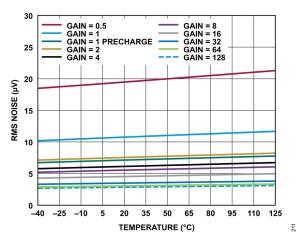

- ▶ 入力換算ノイズ: 10nV (3.8SPS、ゲイン = 128)

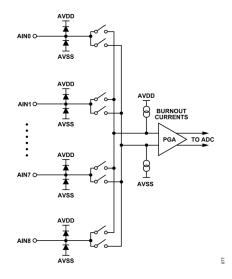

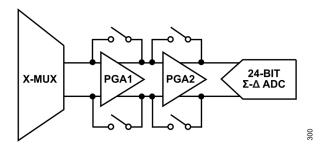

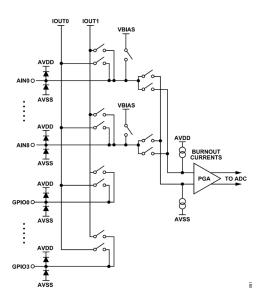

- ▶ クロスポイント・マルチプレクサ・アナログ入力

- ▶ 4個の差動入力/8個の疑似差動入力

- ▶ 超低ノイズの内蔵 PGA (ゲイン: 0.5~128)

- ▶ 出力データレート: 3.8SPS~62.5kSPS

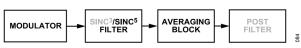

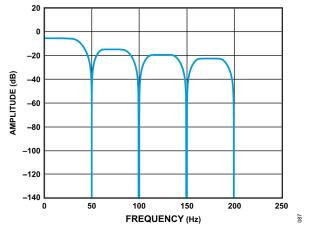

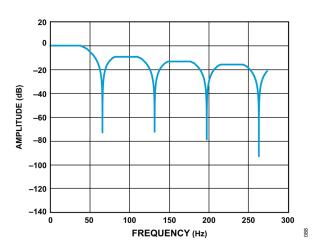

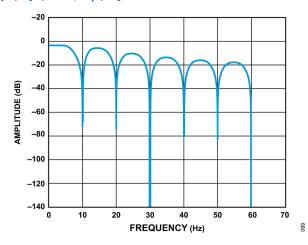

- ▶ 柔軟なデジタル・フィルタ

- ▶ 低遅延 sinc フィルタ

- ▶ 50Hz/60Hz を同時に除去

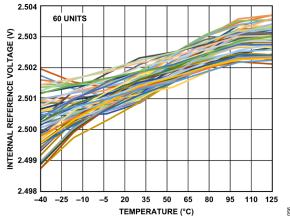

- ▶ ドリフト 5ppm/°C (代表値)のバンド・ギャップ・ リファレンス

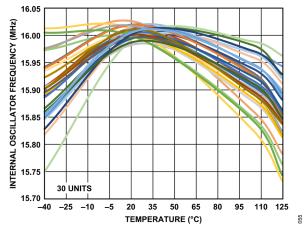

- ▶ 内部発振器

- ▶ アナログ電源: 4.75V~5.25V、または±2.5V

- ▶ デジタル電源: 1.7V~5.25V

- ▶ マッチングがとれたプログラマブルな励起電流源

- ▶ ローサイド・パワー・スイッチ

- ▶ オン・チップ・バイアス電圧発生器

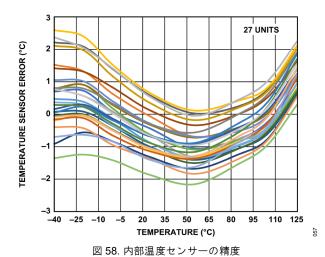

- ▶ 内部温度センサー

- ▶ 4つの汎用入出力

- ▶ 内部およびシステム・キャリブレーション

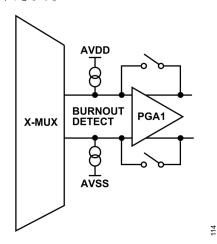

- ▶ センサー・バーンアウト検出

- ▶ 診断機能

- ▶ チャンネルごとに設定

- ▶ 柔軟な自動チャンネル・シーケンサ

- ▶ 3線式または4線式のシリアル・インターフェース (シュミット・トリガ付き SCLK)▶ SPI、QSPI、MICROWIRE、DSP 互換

- データ・ストリーミング用の TDM 互換インターフェース

- ▶ 性能温度範囲: -40°C~+105°C

- ▶ 動作温度範囲: -40°C~125°C

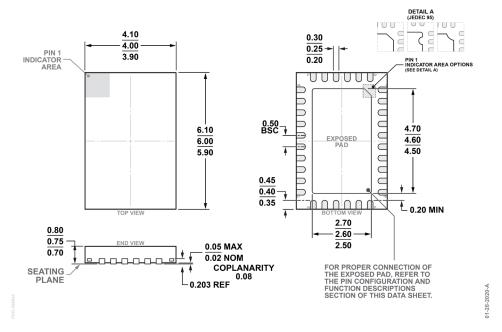

- ▶ 32 ピン、4mm×6mm LFCSP パッケージを採用

## アプリケーション

- ▶ 工業用プロセス制御: PLC/DCS モジュール

- ▶ 温度計測

- ▶ 圧力計測

- ▶ 医療および科学計測器

- ▶ クロマトグラフィ

- ▶ 環境モニタリング

- ▶ 電子テストおよび計測

- ▶ 計測器

- ▶ 秤量計

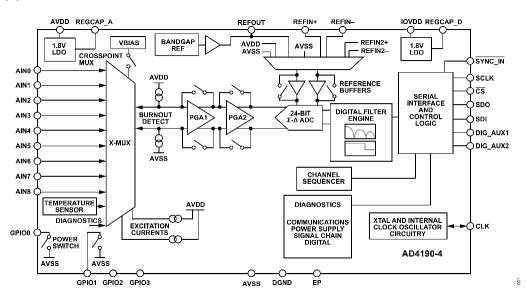

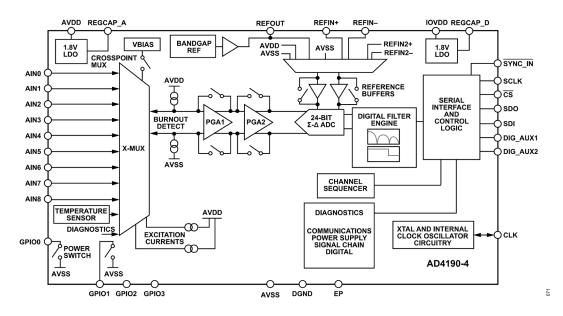

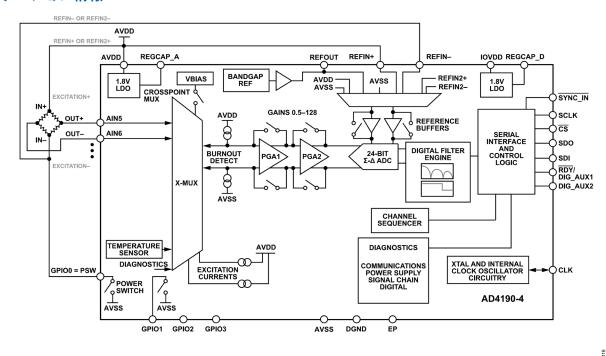

## 機能ブロック図

図 1. AD4190-4 の機能ブロック図

## 目次

| 特長                                                              |                                                          |

|-----------------------------------------------------------------|----------------------------------------------------------|

| アプリケーション                                                        | 1                                                        |

| 機能ブロック図                                                         | 1                                                        |

| 概要                                                              | 4                                                        |

| 仕様                                                              | 5                                                        |

| タイミング特性                                                         | 10                                                       |

| タイミング図                                                          | 11                                                       |

| 絶対最大定格                                                          |                                                          |

| <b>熱抵抗</b>                                                      |                                                          |

| 静電放電(ESD)定格                                                     |                                                          |

| ESD に関する注意                                                      |                                                          |

| ピン配置およびピン機能の説明                                                  |                                                          |

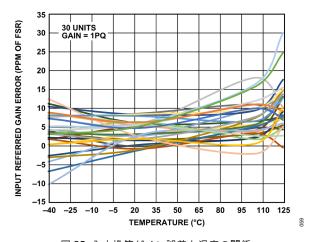

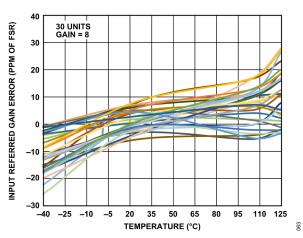

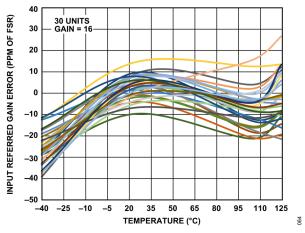

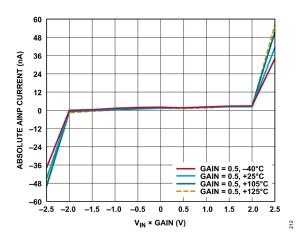

| 代表的な性能特性                                                        |                                                          |

|                                                                 |                                                          |

| 実効値およびノイズ性能                                                     |                                                          |

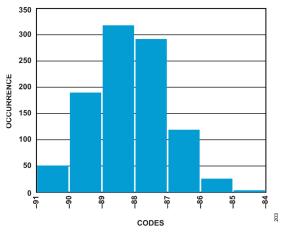

| sinc <sup>5</sup> + 平均化                                         |                                                          |

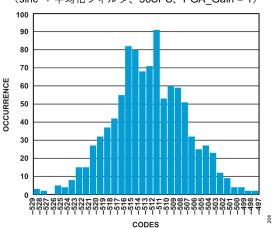

| sinc <sup>3</sup>                                               |                                                          |

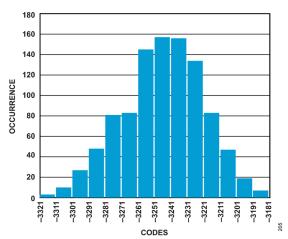

| ポスト・フィルタ                                                        |                                                          |

|                                                                 |                                                          |

| 動作原理                                                            |                                                          |

| 概要                                                              |                                                          |

| 電源                                                              |                                                          |

| デジタル・コミュニケーション                                                  |                                                          |

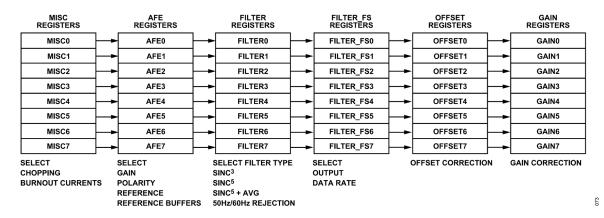

| 設定の概要                                                           |                                                          |

| ADC 回路情報                                                        | 39                                                       |

|                                                                 |                                                          |

| アナログ入力チャンネル                                                     |                                                          |

| 外部マルチプレクサの制御                                                    | 39                                                       |

| 外部マルチプレクサの制御<br>プログラマブル・ゲイン・アンプ(PGA)                            | 39                                                       |

| 外部マルチプレクサの制御                                                    | 39                                                       |

| 外部マルチプレクサの制御<br>プログラマブル・ゲイン・アンプ(PGA)<br>リファレンス<br>バイポーラ/ユニポーラ設定 | 39<br>39<br>39                                           |

| 外部マルチプレクサの制御<br>プログラマブル・ゲイン・アンプ(PGA)<br>リファレンス                  | 39<br>39<br>39                                           |

| 外部マルチプレクサの制御<br>プログラマブル・ゲイン・アンプ(PGA)<br>リファレンス<br>バイポーラ/ユニポーラ設定 | 39<br>39<br>40<br>40                                     |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>40                                     |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>40<br>41                               |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>41<br>41<br>41                         |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>41<br>41<br>41                         |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>41<br>41<br>41<br>42                   |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>41<br>41<br>42<br>42                   |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>41<br>41<br>42<br>42                   |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>41<br>41<br>42<br>42<br>42<br>42       |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>41<br>41<br>42<br>42<br>42<br>42<br>43 |

| 外部マルチプレクサの制御                                                    | 39<br>39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43 |

| 外部マルチプレクサの制御                                                    | 39394041414242424343                                     |

| 外部マルチプレクサの制御                                                    | 39394041414242424545                                     |

| 外部マルチプレクサの制御                                                    | 393940414142424243434545                                 |

| 外部マルチプレクサの制御                                                    | 393940414142424243454545                                 |

| 外部マルチプレクサの制御                                                    | 393940414142424243454545                                 |

| 外部マルチプレクサの制御                                                    | 39394041414242424345454545                               |

|   | 連続読出し                   | .52 |

|---|-------------------------|-----|

|   | 連続送信                    | .53 |

|   | SPI フレーム同期              | .53 |

|   | デバイスの識別                 | .55 |

|   | デバイスのリセット               | .55 |

|   | IO の駆動強度                | .55 |

|   | SDO_RDYB_DLY            | .55 |

| A | DC の同期                  | .56 |

|   | 標準同期                    | .56 |

|   | 代替同期                    | .56 |

|   | 複数の AD4190-4 デバイスの同期    | .57 |

| 診 | 断機能                     | .58 |

|   | デバイス・エラー                | .58 |

|   | リファレンス検出                | .58 |

|   | リファレンス過電圧/低電圧の検出        | .58 |

|   | 変換エラー                   | .58 |

|   | アナログ入力過電圧/低電圧検出         | .58 |

|   | 励起電流コンプライアンス            | .58 |

|   | 電源モニタ                   | .58 |

|   | LDO モニタリング              | .58 |

|   | SPI SCLK カウンタ           | .59 |

|   | SPI 読出し/書込みエラー          | .59 |

|   | ノット・レディ・エラー             | .59 |

|   | チェックサム保護                | .59 |

|   | メモリ・マップ・チェックサム保護        | .61 |

|   | バーンアウト電流                | .61 |

|   | プルアップ電流                 | .62 |

|   | 温度センサー                  | .62 |

| グ | ゚ヲウンディングとレイアウト          | .63 |

| ア | プリケーション情報               | .64 |

|   | 重量計                     | .64 |

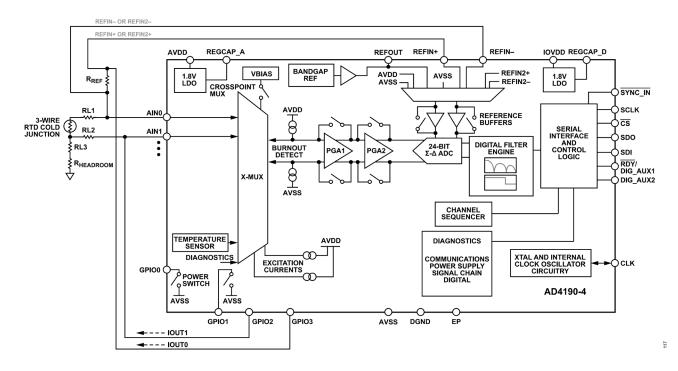

|   | RTD を使用した温度計測           |     |

| 内 | 蔵レジスタ・マップ               | .67 |

|   | INTERFACE_CONFIG_A レジスタ | .70 |

|   | INTERFACE_CONFIG_B レジスタ | .70 |

|   | DEVICE_CONFIG レジスタ      | .70 |

|   | CHIP_TYPE レジスタ          |     |

|   | PRODUCT_ID_L レジスタ       | .71 |

|   | PRODUCT_ID_H レジスタ       | .71 |

|   | CHIP_GRADE レジスタ         |     |

|   | SCRATCH_PAD レジスタ        |     |

|   | SPI_REVISION レジスタ       |     |

|   | VENDOR_L レジスタ           |     |

|   | VENDOR_H レジスタ           |     |

|   | INTERFACE_CONFIG_C レジスタ |     |

|   | INTERFACE_STATUS_A レジスタ | .73 |

|   | CTATUC LONG A           | 7/  |

| DATA_16B レジスタ         | 74 |

|-----------------------|----|

| DATA_16B_STATUS レジスタ  | 75 |

| DATA_24B レジスタ         | 75 |

| DATA_24B_STATUS レジスタ  | 75 |

| DATA_PER_CHANNEL レジスタ | 76 |

| PIN_MUXING レジスタ       | 76 |

| CLOCK_CTRL レジスタ       | 77 |

| STANDBY_CTRL レジスタ     | 78 |

| POWER_DOWN_SW レジスタ    | 78 |

| ADC_CTRL レジスタ         | 79 |

| ERROR_EN レジスタ         | 81 |

| ERROR レジスタ            | 82 |

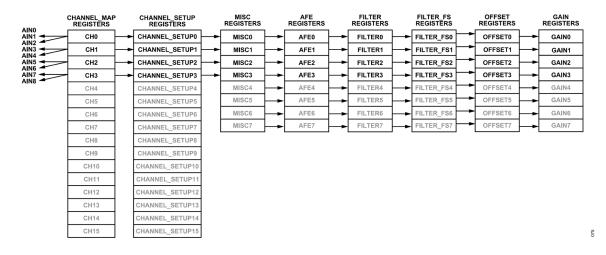

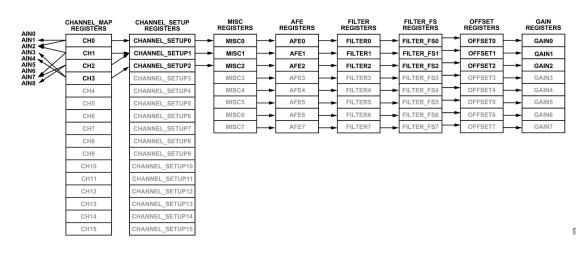

| CHANNEL_EN レジスタ       | 83 |

| CHANNEL_SETUP レジスタ    | 83 |

| CHANNEL_MAP レジスタ      | 84 |

| MISC (各種設定) レジスタ      | 86 |

| AFE レジスタ              | 87 |

|-----------------------|----|

| FILTER レジスタ           | 88 |

| FILTER_FS レジスタ        | 88 |

| オフセット・レジスタ            | 89 |

| ゲイン・レジスタ              | 89 |

| REF_CONTROL レジスタ      | 89 |

| V_BIAS レジスタ           | 90 |

| I_PULLUP レジスタ         | 90 |

| CURRENT_SOURCE レジスタ   | 91 |

| GPIO_MODE レジスタ        | 92 |

| GPIO_OUTPUT_DATA レジスタ | 93 |

| GPIO_INPUT_DATA レジスタ  | 93 |

| 外形寸法                  | 94 |

| オーダー・ガイド              | 94 |

| 評価用ボード                | 94 |

## 改訂履歴

1/2025—Revision 0: Initial Version

### 概要

AD4190-4 は、高精度計測アプリケーション向けの低ノイズ、完全統合型アナログ・フロント・エンドです。このデバイスには、低ノイズ、24 ビット  $\Sigma$ - $\Delta$  アナログ・デジタル・コンバータ (ADC) が搭載されており、4個の差動入力、または8個のシングルエンド入力または疑似差動入力を持つように構成できます。 オン・チップの低ノイズ・ゲイン段により、小振幅の信号をこの ADC に直接入力できます。

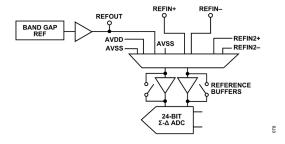

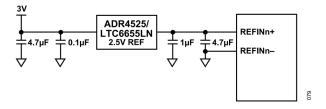

AD4190-4 により、最高レベルのシグナル・チェーン集積化を実現できます。このデバイスは内部リファレンスを備えています。また、2 つの外部差動リファレンスにも対応し、これらは内部でバッファ処理が可能です。その他の主要な内蔵機能は次のとおりです。

- ▶ プログラマブル・ゲイン・アンプ (PGA)。ゲインがプログラマブル (0.5~128) であることから、この PGA は、抵抗ブリッジ、熱電対、測温抵抗体 (RTD) など低出力振幅のトランスジューサに直接インターフェースできます。

- ▶ PGA は広いコモンモード入力範囲を備えているため、広い 範囲で変化する入力コモンモードに対しマージンを大きくと ることができます。

- ▶ 低ドリフトで十分にマッチングがとれた高精度電流源。励起電流源を使用して、2線式、3線式、4線式のRTDまたはブリッジ型センサーを励起できます。励起電流出力オプションには、10μA、50μA、100μA、250μA、500μA、1mA、1.5mAがあります。より大きな電流が必要な場合は、電流を追加することもできます。

- ▶ ローサイド・パワー・スイッチ (PDSW) を使用して、変換と変換の間にブリッジ・センサーをパワーダウンします。

- ▶ 熱電対用電圧バイアス (VBIAS ソースがチャンネルのコモンモード電圧を(AVDD + AVSS)/2 に設定)。

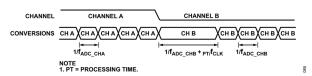

- ▶ スマート・シーケンサにより、イネーブルされた各事前設定 チャンネルを予め定めた順序で変換できるため、トランス ジューサ、システム・チェック、診断計測を混在させて順次 実施できます。このシーケンサにより、設定を変更するため にデバイスとのシリアル・インターフェース通信を繰り返し 行う必要がなくなります。このシーケンスでは 16 チャンネルを設定できます。これらのチャンネルはそれぞれ、ゲイン、 フィルタ・タイプ、出力データレート、バッファリング、およびリファレンス源を選択できる 8 つのユーザ定義の ADC セットアップから選択します。

AD4190-4 には、充実した機能セットの一部として広範な診断機能も備えています。診断機能には、巡回冗長性チェック (CRC)、シグナル・チェーン・チェック、シリアル・インターフェース・チェックなどがあり、より信頼性の高いソリューションになっています。

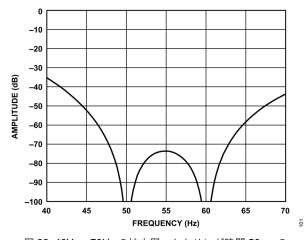

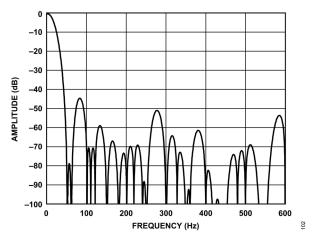

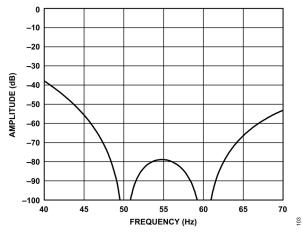

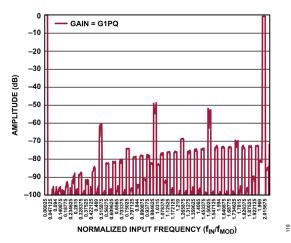

また、このデバイスは、複数のフィルタ・オプションを備えているので、柔軟性が非常に高くなっています。より高速のセトリングを可能にする sinc フィルタを内蔵する他、50Hz と 60Hz を同時に除去できる複数のオプションも備えています。

このデバイスは、4.75V~5.25V のアナログ単電源または 2.5V のバイポーラ電源で動作します。デジタル電源の範囲は 1.7V~5.25V です。このデバイスは、-40°C~+105°C の温度範囲で仕様規定されています。AD4190-4 は 32 ピン LFCSP パッケージに収められています。

analog.com.jp Rev. 0 | 4 of 94

## 仕様

特に指定のない限り、AVDD = 4.75V~5.25V、IOVDD = 1.7V~5.25V、AVSS = DGND = 0V、REFIN+ = 2.5V(外部リファレンス)、REFIN- = AVSS、MCLK = 16MHz、 $T_A = T_{MIN} \sim T_{MAX}$ ( $-40^{\circ}C \sim +105^{\circ}C$ )。

表 1. 仕様

| Parameter <sup>1</sup>                          | Test Conditions/Comments                           | Min             | Min Typ Max      |              | Unit       |

|-------------------------------------------------|----------------------------------------------------|-----------------|------------------|--------------|------------|

| ADC SPEED CODING AND PERFORMANCE                |                                                    |                 |                  |              |            |

| Output Data Rate (ODR)                          |                                                    |                 |                  |              |            |

| Sinc <sup>5</sup>                               |                                                    | 976.5           |                  | 62,500       | SPS        |

| Sinc <sup>5</sup> + Avg                         |                                                    | 3.8             |                  | 62,500       | SPS        |

| Sinc <sup>3</sup>                               |                                                    | 3.8             |                  | 62,500       | SPS        |

| 50Hz/60Hz Post Filters                          |                                                    | 16.67           | 20               | 25           | SPS        |

| No Missing Codes <sup>2</sup>                   |                                                    | 24              |                  |              | Bits       |

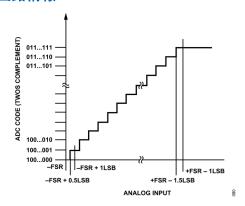

| Data output coding                              | Bipolar mode                                       | 2s complement   |                  |              |            |

| 3                                               | Unipolar mode                                      | Straight binary |                  |              |            |

| Resolution                                      |                                                    |                 | nd Noise Perform | ance section |            |

| Noise                                           |                                                    |                 | nd Noise Perform |              |            |

| ACCURACY                                        |                                                    |                 |                  |              |            |

| Gains                                           |                                                    |                 | 0.5, 1, 2, 4, 8, |              |            |

| Cams                                            |                                                    |                 | 16, 32, 64, 128  |              |            |

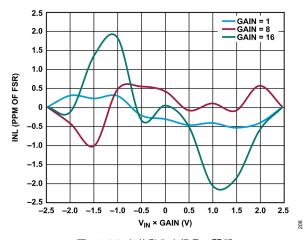

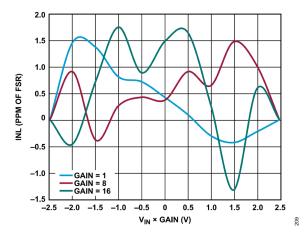

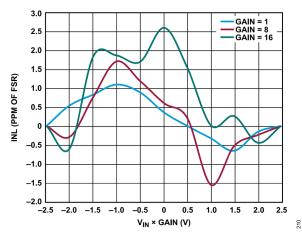

| Integral Nonlinearity (INL)                     | Gain = 1, Gain = 1 precharge                       |                 | ±1               |              | ppm of FSR |

| g                                               | All other gains                                    |                 | ±3               |              | ppm of FSR |

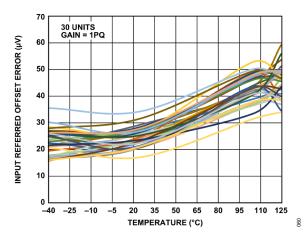

| Precalibration Offset Error <sup>3</sup>        | Gain = 1 precharge                                 |                 | ±30              |              | μV         |

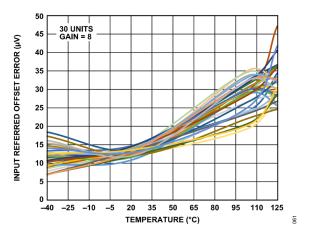

| 1 Todalistation Chook End                       | Gain < 16                                          |                 | ±(15 + (40/      |              | μV         |

|                                                 | Juli 10                                            |                 | gain))           |              | P V        |

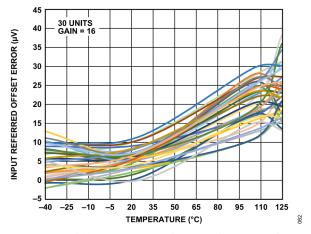

|                                                 | Gain ≥ 16                                          |                 | ±6               |              | μV         |

| Offset Error Drift vs. Temperature <sup>2</sup> | Gain = 1 precharge                                 |                 | ±20              |              | nV/°C      |

| Chook End. Sink to Tomporatare                  | Gain < 8                                           | ±50/gain        |                  |              | nV/°C      |

|                                                 | Gain = 8, 16, 32                                   |                 | ±20              |              | nV/°C      |

|                                                 | Gain = 64, 128                                     |                 | ±20              |              | nV/°C      |

| Gain Error <sup>3</sup>                         | Gain = 1 precharge, T <sub>A</sub> = 25°C          |                 | ±10              |              | ppm of FSR |

| Call Life                                       | All other gains, $T_A = 25^{\circ}C$               |                 |                  | ppm of FSR   |            |

| Gain Error Drift vs. Temperature <sup>2</sup>   | All gains                                          |                 | ±0.5             |              | ppm/°C     |

| REJECTION                                       | All gallis                                         |                 | 10.0             |              | ррпії С    |

| DC Power Supply Rejection                       | V = 1V/gain All aupplies                           |                 |                  |              |            |

| DC Power Supply Rejection                       | V <sub>IN</sub> = 1V/gain, All supplies Gain = 0.5 |                 | 98               |              | dB         |

|                                                 |                                                    |                 |                  |              |            |

|                                                 | Gain = 1 precharge and Gains of 1 to 8             |                 | 104              |              | dB         |

|                                                 | Gain of 16 to 128                                  |                 | 116              |              | dB         |

| Common-Mode Rejection <sup>4</sup>              |                                                    |                 | 110              |              | ub         |

| At DC                                           | V <sub>IN</sub> = 1V/gain<br>Gain = 0.5            |                 | 106              |              | dB         |

| ALDC                                            |                                                    | 106<br>108      |                  | dB           |            |

|                                                 | Gain = 1 precharge and Gains of 1 to 8             |                 | 100              |              | UD UD      |

|                                                 | Gains of 16 to 128                                 |                 | 125              |              | dB         |

| At 50Hz, 60Hz                                   | 50ms settling post filter, 50Hz ±                  |                 | 120              |              | dB         |

| At 30112, 00112                                 | 1Hz and 60Hz ± 1Hz                                 |                 | 120              |              | ub         |

| Normal Mode Rejection <sup>2</sup>              | 50Hz ± 1Hz and 60Hz ± 1Hz                          |                 |                  |              |            |

| Tomai mode regioner                             | Internal clock, 50ms settling post                 |                 | 89               |              | dB         |

|                                                 | filter                                             |                 |                  |              |            |

|                                                 | External clock, 50ms settling                      |                 | 90               |              | dB         |

|                                                 | post filter                                        |                 | - •              |              |            |

| ANALOG INPUTS                                   |                                                    |                 |                  |              |            |

analog.com.jp Rev. 0 | 5 of 94

## 仕様

表 1. 仕様(続き)

| Parameter <sup>1</sup>                        | Test Conditions/Comments                                                                                                                                                 | Min         | Тур  | Max                     | Unit   |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------------------------|--------|

| Differential Input Voltage Range <sup>5</sup> | internal reference                                                                                                                                                       |             |      | +V <sub>REF</sub> /gain | V      |

| Single-Ended Input Voltage Range              |                                                                                                                                                                          | 0           |      | V <sub>REF</sub> /Gain  | V      |

| Absolute AIN Voltage Limits <sup>2</sup>      |                                                                                                                                                                          | AVSS        |      | AVDD                    | V      |

| Input Capacitance                             |                                                                                                                                                                          |             | 8    |                         | pF     |

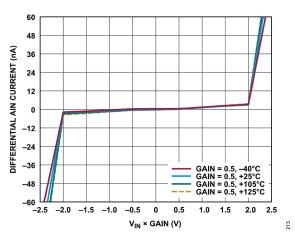

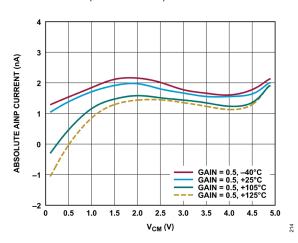

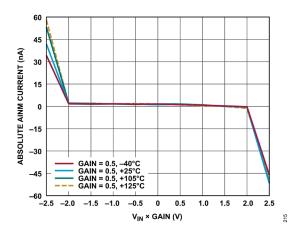

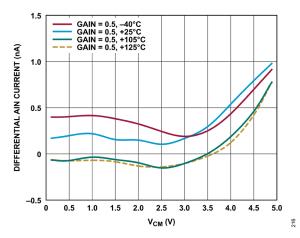

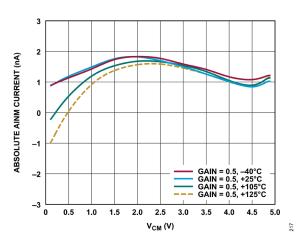

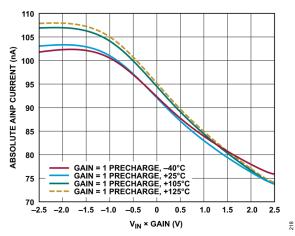

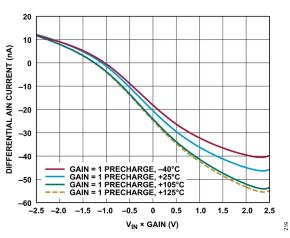

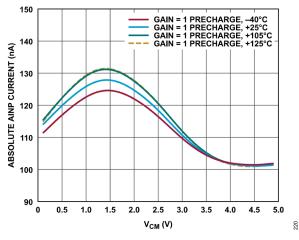

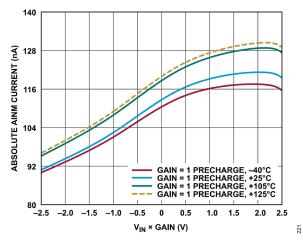

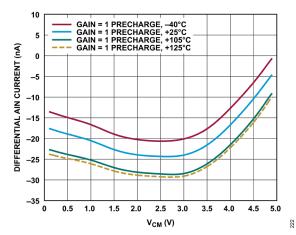

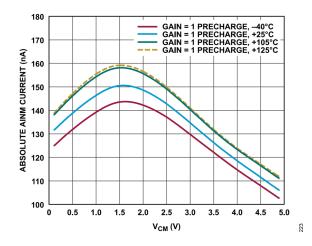

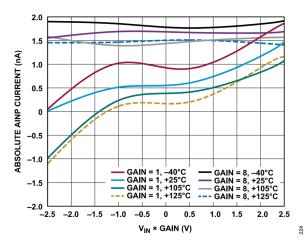

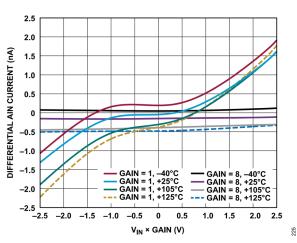

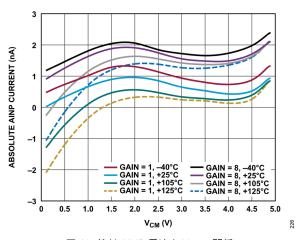

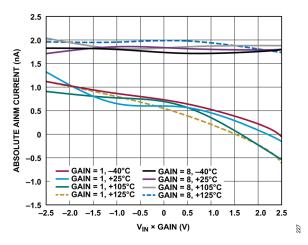

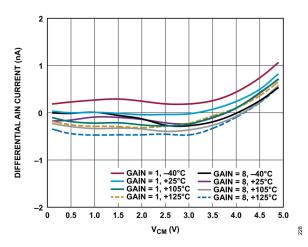

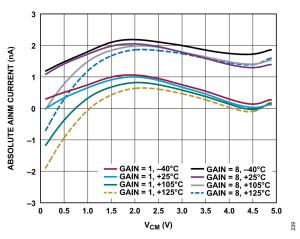

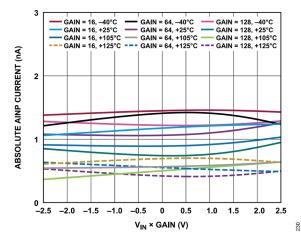

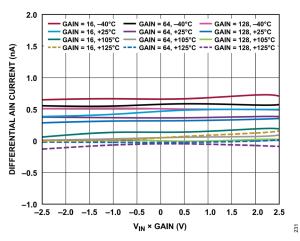

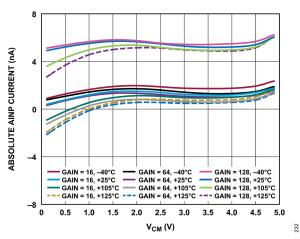

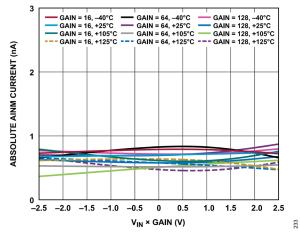

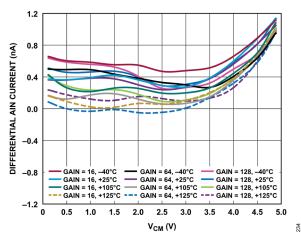

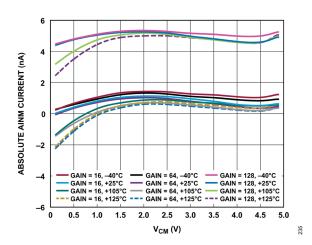

| Analog Input Current                          | Absolute input current measured with AIN between AVSS + 0.1V and AVDD - 0.1V  Differential input current measured with full-scale input, V <sub>CM</sub> = (AVDD+AVSS)/2 |             |      |                         |        |

| Gain = 1 precharge                            |                                                                                                                                                                          |             |      |                         |        |

| Absolute Input Current                        |                                                                                                                                                                          |             | ±140 |                         | nA     |

| Differential Input Current                    |                                                                                                                                                                          |             | ±28  |                         | nA     |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                                                                                                          |             | 280  |                         | pA/°C  |

| Gain = 1                                      |                                                                                                                                                                          |             |      |                         | i.     |

| Absolute Input Current                        |                                                                                                                                                                          |             | ±2   |                         | nA     |

| Differential Input Current                    |                                                                                                                                                                          |             | ±2   |                         | nA     |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                                                                                                          |             | 12   |                         | pA/°C  |

| Gain = 0.5                                    |                                                                                                                                                                          |             |      |                         | p      |

| Absolute Input Current                        |                                                                                                                                                                          |             | ±2   |                         | nA     |

| Differential Input Current                    |                                                                                                                                                                          |             | ±4   |                         | nA     |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                                                                                                          |             | 30   |                         | pA/°C  |

| Gain = 128                                    |                                                                                                                                                                          |             | 00   |                         | pr v O |

| Absolute Input Current                        |                                                                                                                                                                          |             | ±2   |                         | nA     |

| Differential Input Current                    |                                                                                                                                                                          |             | ±2   |                         | nA     |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                                                                                                          |             | 40   |                         | pA/°C  |

| All other gains                               |                                                                                                                                                                          |             | -10  |                         | pr v O |

| Absolute Input Current                        |                                                                                                                                                                          |             | ±2   |                         | nA     |

| Differential Input Current                    |                                                                                                                                                                          |             | ±2   |                         | nA     |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                                                                                                          |             | 70   |                         | pA/°C  |

| ITERNAL REFERENCE                             | 100nF external capacitor to                                                                                                                                              |             |      |                         | pri o  |

| TENIAL NEI ENEMOL                             | AVSS                                                                                                                                                                     |             |      |                         |        |

| Initial Accuracy <sup>6</sup>                 | REFOUT with respect to AVSS, T <sub>A</sub> = 25°C                                                                                                                       |             | 2.5  |                         | V      |

| Temperature Coefficient                       |                                                                                                                                                                          |             | ±5   |                         | ppm/°C |

| Reference Load Current, I <sub>LOAD</sub>     |                                                                                                                                                                          |             | 10   |                         | mA     |

| Thermal Hysteresis                            | Cycle of 25°C, +75°C, -25°C, +25°C                                                                                                                                       |             | 44   |                         | ppm    |

| Power Supply Rejection                        | AVDD (line regulation)                                                                                                                                                   |             | 100  |                         | dB     |

| Load Regulation                               | $\Delta V_{OUT}/\Delta I_{LOAD}$                                                                                                                                         |             | 12   |                         | ppm/mA |

| Voltage Noise                                 | e <sub>N</sub> , 0.1Hz to 10Hz, 2.5V reference                                                                                                                           |             | 4.5  |                         | μV rms |

| Voltage Noise Density                         | e <sub>N</sub> , 1kHz, 2.5V reference                                                                                                                                    |             | 215  |                         | nV/√Hz |

| Turn-On Settling Time                         | 100nF REFOUT capacitor                                                                                                                                                   |             | 200  |                         | μs     |

| Short-Circuit Current, I <sub>SC</sub>        | ·                                                                                                                                                                        |             | 28   |                         | mA     |

| XTERNAL REFERENCE INPUTS                      |                                                                                                                                                                          |             |      |                         |        |

| Differential Input Range <sup>2</sup>         | V <sub>REF</sub> = REF+ - REF-                                                                                                                                           | 1           | 2.5  | AVDD - AVSS             | V      |

| Absolute Voltage Limits <sup>2</sup>          | , ser                                                                                                                                                                    |             |      |                         |        |

| Reference Buffers Disabled                    |                                                                                                                                                                          | AVSS - 0.05 |      | AVDD + 0.05             | V      |

analog.com.jp Rev. 0 | 6 of 94

## 仕様

表 1. 仕様(続き)

| Parameter <sup>1</sup>                           | Test Conditions/Comments                    | Min  | Тур            | Max         | Unit          |

|--------------------------------------------------|---------------------------------------------|------|----------------|-------------|---------------|

| Reference Buffers Enabled                        | Full buffer or precharge buffer             | AVSS |                | AVDD        | V             |

| REFIN Input Current (Reference Buffers Disabled) |                                             |      |                |             |               |

| Reference Input Current                          |                                             |      | ±22            |             | μ <b>Α</b> /V |

| Reference Input Current Drift                    | External clock                              |      | ±1.2           |             | nA/V/°C       |

| 110000000 mpat 0anon 2m                          | Internal clock                              |      | ±6             |             | nA/V/°C       |

| Reference Buffers Enabled                        | internal olook                              |      | 20             |             | 117 0 77 3    |

| Reference Input Current                          | Precharge buffer                            |      | ±6             |             | μA            |

| Neierence input Gurrent                          | Full buffer                                 |      | ±55            |             | nA            |

| Defended land Comment Drift                      |                                             |      |                |             |               |

| Reference Input Current Drift                    | Precharge buffer                            |      | 40             |             | nA/°C         |

|                                                  | Full Buffer                                 |      | 1.25           |             | nA/°C         |

| Normal Mode Rejection                            | See the Rejection parameter                 |      |                |             |               |

| BIAS                                             |                                             |      |                |             |               |

| Output voltage setting                           |                                             |      | (AVDD +        |             | V             |

|                                                  |                                             |      | AVSS)/2        |             |               |

| Output Impedance                                 |                                             |      | 1              |             | kΩ            |

| Start-up time                                    | Dependent on the capacitance                |      | 9              |             | μs/nF         |

|                                                  | connected to AINn                           |      |                |             |               |

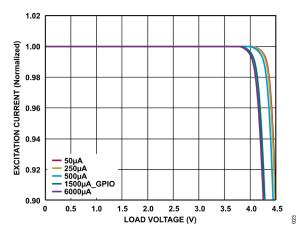

| XCITATION CURRENTS                               |                                             |      |                |             |               |

| Current Settings                                 |                                             |      | 10, 50, 100,   |             | μΑ            |

|                                                  |                                             |      | 250, 500, 1000 | ),          |               |

| •                                                |                                             |      | 1500           |             |               |

| Output Compliance <sup>2</sup>                   | 10μΑ, 50μΑ, 100μΑ, 1%                       |      |                | AVDD - 1.25 | V             |

|                                                  | accuracy                                    |      |                |             |               |

|                                                  | 250μA/500μA/1mA/1.5mA, 1%                   |      |                | AVDD – 1.45 | V             |

|                                                  | accuracy                                    |      |                |             |               |

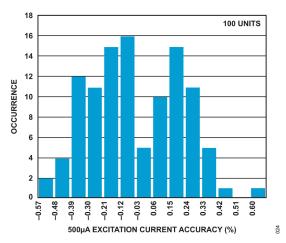

| Initial Accuracy                                 | $T_A = 25^{\circ}C, 10\mu A$                |      | ±3             |             | %             |

|                                                  | $T_A = 25^{\circ}C, 50\mu A, 100\mu A$      |      | ±0.1           |             | %             |

|                                                  | $T_A = 25^{\circ}C, >100\mu A$              |      | ±0.2           |             | %             |

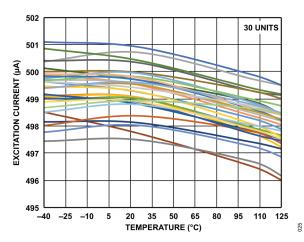

| Drift <sup>2</sup>                               | 10μΑ                                        |      | ±20            |             | ppm/°C        |

|                                                  | 50μΑ, 100μΑ                                 |      | ±5             |             | ppm/°C        |

|                                                  | >100µA                                      |      | ±25            |             | ppm/°C        |

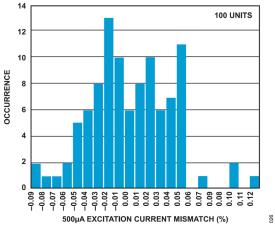

| Current Mismatch                                 |                                             |      |                |             |               |

| Same Current Matching <sup>2</sup>               | 10µA                                        |      | ±1.3           |             | %             |

| Č                                                | All other currents                          |      | ±0.1           |             | %             |

| Different Current Matching                       |                                             |      | ±1             |             | %             |

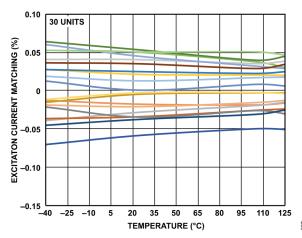

| Drift Matching <sup>2</sup>                      | Current sources at the same                 |      |                |             | "             |

| Diff. Matoring                                   | value                                       |      |                |             |               |

|                                                  | 10μΑ                                        |      | ±3             |             | ppm/°C        |

|                                                  | 50μΑ, 100μΑ, 250μΑ                          |      | ±2             |             | ppm/°C        |

|                                                  | All other currents                          |      | ±1             |             | ppm/°C        |

| Line Population (AVDD)                           | AVDD = 5V ± 5%                              |      | ±1<br>150      |             | 1             |

| Line Regulation (AVDD)                           |                                             |      |                |             | ppm/V         |

| Load Regulation                                  | >10µA                                       |      | 40             |             | ppm/V         |

| Start-up time                                    | $R_{LOAD} = 1k\Omega$ , $C_{LOAD} =$        |      | 7              |             | μs            |

|                                                  | 0pF Dependent on the load connected to AINn |      |                |             |               |

| EMPERATURE SENSOR                                | CONNECTED TO VIIAN                          |      |                |             |               |

|                                                  | A4                                          |      | .0             |             |               |

| Accuracy                                         | After user calibration at 25°C              |      | ±2             |             | °C            |

| Sensitivity                                      |                                             |      | 477            |             | μV/K          |

| OW-SIDE POWER SWITCH                             |                                             |      |                |             |               |

| Ron                                              |                                             |      | 10             |             | Ω             |

analog.com.jp Rev. 0 | 7 of 94

## 仕様

表 1. 仕様(続き)

| Parameter <sup>1</sup>                                   | Test Conditions/Comments    | Min           | Тур         | Max          | Unit |

|----------------------------------------------------------|-----------------------------|---------------|-------------|--------------|------|

| Current Through Switch <sup>2</sup>                      |                             |               | 25          |              | mA   |

| PULL-UP CURRENTS                                         |                             |               |             |              |      |

| Source Current                                           |                             |               | 100         |              | nA   |

| BURNOUT CURRENTS                                         |                             |               |             |              |      |

| Source/Sink Current                                      |                             |               | ±0.1, 2, 10 |              | μA   |

| Accuracy                                                 | Sinking/Sourcing            |               |             |              | F    |

|                                                          | ±0.1µA                      |               | 25          |              | %    |

|                                                          | ±2μA, ±10μA                 |               | 10          |              | %    |

| GENERAL-PURPOSE I/O (GPIO0 to GPIO3) <sup>2</sup>        | With respect to AVSS        |               |             |              | ,,,  |

| Input Mode Leakage Current                               | Than toopoot to 7 th oo     | -1            |             | +1           | μA   |

| Floating State Output Capacitance                        |                             | '             | 5           | .,           | pF   |

| Output High Voltage, V <sub>OH</sub>                     | I <sub>SOURCE</sub> = 200µA | AVSS + 4      | V           |              | V    |

| Output Low Voltage, V <sub>OL</sub>                      | I <sub>SINK</sub> = 800μA   | 7,000 . 4     |             | AVSS + 0.4   | V    |

| Input High Voltage, V <sub>IH</sub>                      | ISINK - OOOPA               | AVSS + 3      |             | AV00 1 0.4   | V    |

| Input Low Voltage, V <sub>IL</sub>                       |                             | AV33 1 3      |             | AVSS + 0.7   | V    |

| DIAGNOSTIC TRIP POINTS                                   |                             |               |             | AV33 + 0.1   | V    |

|                                                          |                             | 0.6           |             | 0.05         | V    |

| Reference Detect Level                                   |                             | 0.6           |             | 0.85         | V    |

| Reference/AIN OV/UV Trip Level                           |                             | AV/DD + 0.005 |             |              | N/   |

| Overvoltage                                              |                             | AVDD + 0.065  |             | AV / O.O O.O | V    |

| Undervoltage                                             |                             |               |             | AVSS - 0.065 | V    |

| Reference/AIN OV/UV Clear Level                          |                             | AV/DD : 0.045 |             |              | l v  |

| Overvoltage                                              |                             | AVDD + 0.015  |             | AV /00 0.04  | V    |

| Undervoltage                                             | 40. 44. 400. 4              | N/DD 4.0      |             | AVSS - 0.01  | V    |

| Excitation Current Source Compliance                     | 10μA to 100μA               | AVDD - 1.3    |             | AVDD - 0.8   | V    |

| W2071 2 1 1                                              | >100µA                      | AVDD - 1.6    |             | AVDD - 1     | V    |

| ALDO Trip Point                                          |                             |               | 1.5         |              | V    |

| DLDO Trip Point                                          |                             |               | 1.6         |              | V    |

| CLOCK                                                    |                             |               |             |              |      |

| Internal Clock                                           |                             |               |             |              |      |

| Frequency                                                |                             |               | 16          |              | MHz  |

| Duty Cycle                                               |                             |               | 50:50       |              | %    |

| External Clock (CLK)                                     |                             | 1             | 16          | 17           | MHz  |

| Minimum Low Time                                         |                             | 27.6          |             |              | ns   |

| Minimum High Time                                        |                             | 27.6          |             |              | ns   |

| LOGIC INPUTS <sup>2</sup>                                |                             |               |             |              |      |

| Input High Voltage, V <sub>INH</sub>                     |                             | 0.8 × IOVDD   |             |              | V    |

| Input Low Voltage, V <sub>INL</sub>                      |                             |               |             | 0.2 × IOVDD  | V    |

| Hysteresis                                               |                             |               | 0.04        |              | V    |

| Leakage Currents                                         | SYNC_IN Pin                 |               |             | +15          | uA   |

|                                                          | All other pins              | -1            |             | +1           | uA   |

| Input Capacitance                                        | All digital inputs          |               | 10          |              | pF   |

| LOGIC OUTPUT <sup>2</sup> (CLK, DIG_AUX1, DIG_AUX2, SDO) |                             |               |             |              |      |

| Output High Voltage, V <sub>OH</sub> <sup>2</sup>        | I <sub>SOURCE</sub> = 1mA   | 0.8 × IOVDD   |             |              | V    |

| Output Low Voltage, V <sub>OL</sub> <sup>2</sup>         | I <sub>SINK</sub> = 2mA     |               |             | 0.4          | V    |

| Leakage Current                                          | Floating state              | -1            |             | +1           | μA   |

| Output Capacitance                                       | Floating state              |               | 10          |              | pF   |

| SYSTEM CALIBRATION <sup>2</sup>                          |                             |               |             |              |      |

| Full-Scale (FS) Calibration Limit                        |                             |               |             | 1.05 × FS    | V    |

analog.com.jp Rev. 0 | 8 of 94

## 仕様

表 1. 仕様(続き)

| Parameter <sup>1</sup>              | Test Conditions/Comments                                           | Min        | Тур  | Max      | Unit |

|-------------------------------------|--------------------------------------------------------------------|------------|------|----------|------|

| Zero-Scale Calibration Limit        |                                                                    | −1.05 × FS |      |          | V    |

| Input Span                          |                                                                    | 0.8 × FS   |      | 2.1 × FS | V    |

| POWER REQUIREMENTS                  |                                                                    |            |      |          |      |

| Power Supply Voltage                |                                                                    |            |      |          |      |

| AVDD to AVSS                        |                                                                    | 4.75       |      | 5.25     | V    |

| AVSS to DGND                        |                                                                    | -2.625     |      | 0        | V    |

| IOVDD to DGND                       |                                                                    | 1.7        |      | 5.25     | V    |

| IOVDD to AVSS                       | For AVSS < DGND                                                    |            |      | 6.35     | V    |

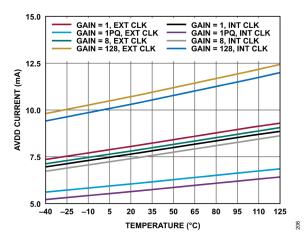

| POWER SUPPLY CURRENTS <sup>7</sup>  |                                                                    |            |      |          |      |

| AVDD Current, External Reference    |                                                                    |            |      |          |      |

| Gain = 1 precharge                  |                                                                    |            | 5    |          | mA   |

| Gain < 16 except Gain = 1 precharge |                                                                    |            | 7    |          | mA   |

| Gain ≥ 16                           |                                                                    |            | 10   |          | mA   |

| I <sub>AVDD</sub> Increase Due To   |                                                                    |            |      |          |      |

| Both Reference Buffers              |                                                                    |            |      |          |      |

| Precharge                           |                                                                    |            | 0.7  |          | mA   |

| Full Buffer                         |                                                                    |            | 1.7  |          | mA   |

| Internal Reference                  |                                                                    |            | 0.5  |          | mA   |

| Diagnostics                         |                                                                    |            | 0.1  |          | mA   |

| Excitation Currents                 |                                                                    |            | 0.06 |          | mA   |

| VBIAS                               |                                                                    |            | 0.05 |          | mA   |

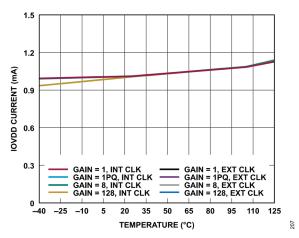

| IOVDD Current                       | External clock                                                     |            | 1    |          | mA   |

|                                     | Internal clock                                                     |            | 1.3  |          | mA   |

| AVDD Standby Mode                   | LDOs on only                                                       |            | 70   |          | μA   |

| AVDD Power-Down Mode                |                                                                    |            | 0.2  |          | μA   |

| IOVDD Standby Mode                  | LDOs on only                                                       |            | 15   |          | μA   |

| IOVDD Power-Down Mode               |                                                                    |            | 8.0  |          | μA   |

| POWER DISSIPATION <sup>7</sup>      | IOVDD = 5.25V, AVDD = 5.25V                                        |            |      |          |      |

| Full Operating Mode                 | Gain = 1, reference buffers disabled, external clock and reference |            | 32   |          | mW   |

|                                     | Gain > 16, reference buffers enabled, internal clock and reference |            | 71   |          | mW   |

| Standby Mode                        | LDOs on only                                                       |            | 447  |          | μW   |

| Power-Down Mode                     |                                                                    |            | 5.25 |          | μW   |

<sup>1</sup> 温度範囲は-40°C~+105°Cです。

analog.com.jp Rev. 0 | 9 of 94

<sup>2</sup> これらの仕様は、製品テストを受けたものではありませんが、製品の初期リリース時に特性評価データで裏付けられています。

<sup>&</sup>lt;sup>3</sup> オフセット誤差は、システム・キャリブレーションまたは内部ゼロスケール・キャリブレーションに従って選択されたプログラム済み ODR のノイズの程度です。システム・フルスケール・キャリブレーションにより、プログラム済み ODR のノイズと同等レベルにまでゲイン誤差が減少します。

$<sup>^4</sup>$  AINP と AINM の最小電圧と最大電圧は、AVSS + 0.1V および AVDD - 0.1V です。

<sup>&</sup>lt;sup>5</sup> 差動アナログ入力の最大許容範囲は±(AVDD − 0.65V)/ゲイン、シングルエンド・アナログ入力の最大許容範囲は 0V~(AVDD − 0.65V)/ゲインで、高いリファレンス電圧を用いた場合に該当します。

<sup>6</sup>この仕様には、湿度感度レベル (MSL) プリコンディショニングの影響が含まれています。

<sup>&</sup>lt;sup>7</sup>これは、REFOUT、励起電流、デジタル出力のピンに負荷が接続されていないときの仕様です。 デジタル入力は IOVDD または DGND に接続します。

## 仕様

## タイミング特性

特に指定のない限り、IOVDD = 1.7V~5.25V(IOVDD < 3V の場合は DIG\_OUT\_STR ビットをセット)、DGND = 0V、入力ロジック 0 = 0V、入力ロジック 1 = IOVDD、 $C_{LOAD}$  = 20pF。

表 2. タイミング特性

| Parameter                     | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Test Conditions/Comments <sup>1, 2</sup>                                                                                                                                                                                                          |

|-------------------------------|----------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK                          |                                              |        |                                                                                                                                                                                                                                                   |

| $t_3$                         | 25                                           | ns min | SCLK high pulse width                                                                                                                                                                                                                             |

| $t_4$                         | 25                                           | ns min | SCLK low pulse width                                                                                                                                                                                                                              |

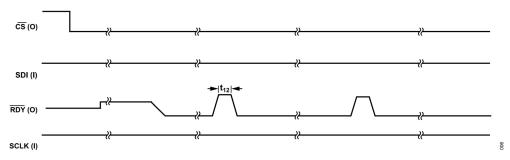

| t <sub>12</sub>               | 8.25/f <sub>MOD</sub>                        | ns min | $\overline{RDY}$ high time if $\overline{RDY}$ is low and the next conversion is available( $f_{MOD} = MCLK/8$ )                                                                                                                                  |

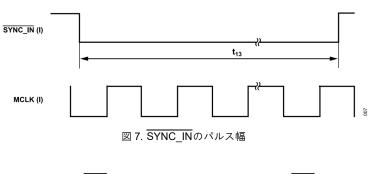

| t <sub>13</sub>               | 2/MCLK                                       | ns min | SYNC_IN low pulse width                                                                                                                                                                                                                           |

| READ OPERATION                |                                              |        |                                                                                                                                                                                                                                                   |

| t <sub>1</sub>                | 0                                            | ns min | CS falling edge to SDO active time                                                                                                                                                                                                                |

|                               | 12.5                                         | ns max | 4.75V < IOVDD ≤ 5.25V                                                                                                                                                                                                                             |

|                               | 17.5                                         | ns max | 3V ≤ IOVDD ≤ 4.75V                                                                                                                                                                                                                                |

|                               | 25                                           | ns max | 1.7V ≤ IOVDD < 3V                                                                                                                                                                                                                                 |

| $t_2^3$                       | 5                                            | ns min | SCLK active edge to data valid delay <sup>4</sup>                                                                                                                                                                                                 |

|                               | 12.5                                         | ns max | 4.75V < IOVDD ≤ 5.25V                                                                                                                                                                                                                             |

|                               | 17.5                                         | ns max | 3V ≤ IOVDD ≤ 4.75V                                                                                                                                                                                                                                |

|                               | 25                                           | ns max | 1.7V ≤ IOVDD < 3V                                                                                                                                                                                                                                 |

| t <sub>5</sub> <sup>5</sup>   | 2.5                                          | ns min | Bus relinquish time after $\overline{\text{CS}}$ inactive edge                                                                                                                                                                                    |

|                               | 20                                           | ns max |                                                                                                                                                                                                                                                   |

| $t_6$                         | 5                                            | ns min | SCLK inactive edge to CS inactive edge                                                                                                                                                                                                            |

| t <sub>7</sub>                | 9                                            | ns min | SCLK inactive edge to $\overline{RDY}$ high. SDO and $\overline{RDY}$ use separate pins or SDO and $\overline{RDY}$ share a pin with Bit SDO_RDYB_DLY cleared. Shared pin returns to functioning as $\overline{RDY}$ after the SCLk inactive edge |

| t <sub>7A</sub>               | t <sub>5</sub>                               | ns min | Data valid after $\overline{\text{CS}}$ inactive edge (when SDO and $\overline{\text{RDY}}$ share a pin). Bit SDO_RDYB_DLY is set. Shared pin continues to function as SDO until $\overline{\text{CS}}$ is taken high                             |

| WRITE OPERATION               |                                              |        |                                                                                                                                                                                                                                                   |

| t <sub>8</sub>                | 0                                            | ns min | CS falling edge to SCLK active edge setup time <sup>4</sup>                                                                                                                                                                                       |

| t <sub>9</sub>                | 8                                            | ns min | Data valid to SCLK edge setup time                                                                                                                                                                                                                |

| t <sub>10</sub>               | 8                                            | ns min | Data valid to SCLK edge hold time                                                                                                                                                                                                                 |

| t <sub>11</sub>               | 5                                            | ns min | CS rising edge to SCLK edge hold time                                                                                                                                                                                                             |

| CONTINUOUS TRANSMIT OPERATION |                                              |        |                                                                                                                                                                                                                                                   |

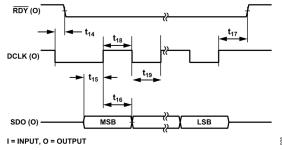

| t <sub>14</sub>               | 2                                            | ns max | DCLK active edge to RDY falling edge setup time                                                                                                                                                                                                   |

| t <sub>15</sub>               |                                              |        | Difference between (data valid to DCLK edge setup time) and DCLK low time                                                                                                                                                                         |

|                               | t <sub>DCLK_LOW</sub> - 1                    | ns max | 4.75V < IOVDD ≤ 5.25V                                                                                                                                                                                                                             |

|                               | t <sub>DCLK_LOW</sub> - 3.5                  | ns max | 3V ≤ IOVDD ≤ 4.75V                                                                                                                                                                                                                                |

|                               | t <sub>DCLK_LOW</sub> - 2.5                  | ns max | 1.7V ≤ IOVDD < 3V                                                                                                                                                                                                                                 |

| t <sub>16</sub>               | t <sub>DCLK_HIGH</sub> - 3.5                 | ns max | Difference between (data valid to DCLK edge hold time) and DCLK high time                                                                                                                                                                         |

| t <sub>17</sub>               | 3.5                                          | ns min | DCLK rising edge to RDY high time                                                                                                                                                                                                                 |

| t <sub>18</sub>               |                                              |        | Difference between DCLK high pulse width and applied external MCLK high time. Valid for divide by 1 option                                                                                                                                        |

|                               | -2                                           | ns max | 4.75V < IOVDD ≤ 5.25V                                                                                                                                                                                                                             |

|                               | -6.5                                         | ns max | 3V ≤ IOVDD ≤ 4.75V                                                                                                                                                                                                                                |

|                               | -4                                           | ns max | 1.7V ≤ IOVDD < 3V                                                                                                                                                                                                                                 |

| t <sub>19</sub>               |                                              |        | Difference between DCLK low pulse width and applied external MCLK low time. Valid for divide by 1 option                                                                                                                                          |

|                               | 1.5                                          | ns max | 4.75V < IOVDD ≤ 5.25V                                                                                                                                                                                                                             |

|                               | 3.5                                          | ns max | 3V ≤ IOVDD ≤ 4.75V                                                                                                                                                                                                                                |

analog.com.jp Rev. 0 | 10 of 94

### 仕様

表 2. タイミング特性(続き)

| Parameter | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Test Conditions/Comments <sup>1, 2</sup> |

|-----------|----------------------------------------------|--------|------------------------------------------|

|           | 2                                            | ns max | 1.7V ≤ IOVDD < 3V                        |

<sup>1</sup>初回リリース時のサンプル・テストにより、適合性が確保されています。

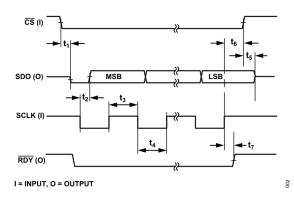

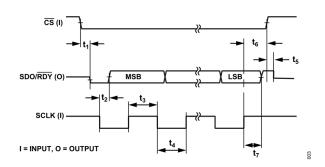

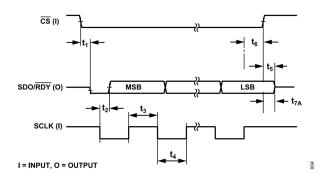

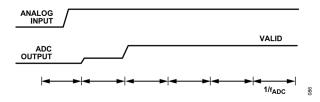

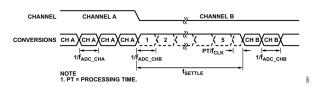

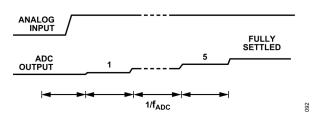

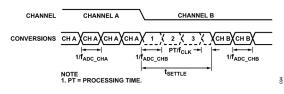

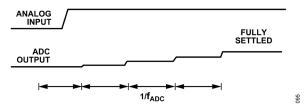

## タイミング図

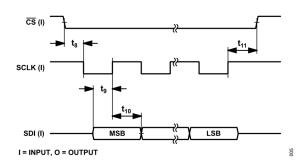

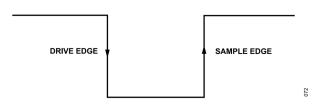

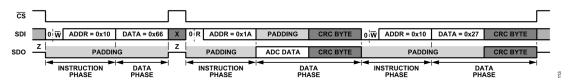

図 2. 読出しサイクルのタイミング図(SDO と $\overline{RDY}$ が別々のピンを使用)

図 3. 読出しサイクルのタイミング図(SDO\_RDYB\_DLY ビットがクリアされた状態で SDO と $\overline{\text{RDY}}$ が同じピンを共用)

図 4. 読出しサイクルのタイミング図 (SDO RDYB DLY ビットがセットされた状態で SDO とRDYが同じピンを共用)

analog.com.jp Rev. 0 | 11 of 94

<sup>&</sup>lt;sup>2</sup> 図 4 と図 5 を参照してください。

$<sup>^3</sup>$  このパラメータは、出力が  $V_{OL}$  リミットまたは  $V_{OH}$  リミットを超えるために要する時間で定義されています。

<sup>&</sup>lt;sup>4</sup> SCLK のアクティブ・エッジとは、SCLK の立下がりエッジを意味します。

<sup>&</sup>lt;sup>5</sup>RDYはデータ・レジスタの読出し後にハイに戻ります。シングル変換モードおよび連続変換モードでは、RDYがハイ・レベルの間に、必要ならば同一データを再度読み出すことができますが、2回目以降の読出しは、次の出力更新が近いところで行わないように注意してください。連続読出し機能を有効化すると、デジタル・ワードは1回しか読み出すことができません。

## 仕様

図 5. 書込みサイクルのタイミング図

図 6. 最初にRDYがローで、次の変換が可能な場合に、DOUT/RDYがハイになる時間

図 8. 連続送信

analog.com.jp Rev. 0 | 12 of 94

#### 絶対最大定格

特に指定のない限り、 $T_A = 25$ °C。

表 3. 絶対最大定格

| Parameter                          | Rating                |

|------------------------------------|-----------------------|

| AVDD to AVSS                       | -0.3V to +6.5V        |

| AVDD to DGND                       | -0.3V to +6.5V        |

| IOVDD to DGND                      | -0.3V to +6.5V        |

| IOVDD to AVSS                      | -0.3V to +7.5V        |

| AVSS to DGND                       | -3.25V to +0.3V       |

| Analog Input Voltage to AVSS       | -0.3V to AVDD + 0.3V  |

| Reference Input Voltage to AVSS    | -0.3V to AVDD + 0.3V  |

| GPIO Input Voltage to AVSS         | -0.3V to AVDD + 0.3V  |

| GPIO Output Voltage to AVSS        | -0.3V to AVDD + 0.3V  |

| REFOUT to AVSS                     | -0.3V to AVDD + 0.3V  |

| Digital Input Voltage to DGND      | -0.3V to IOVDD + 0.3V |

| Digital Output Voltage to DGND     | -0.3V to IOVDD + 0.3V |

| Analog Input/Digital Input Current | 10mA                  |

| Temperature                        |                       |

| Operating Range                    | -40°C to +105°C       |

| Storage Range                      | -65°C to +150°C       |

| Maximum Junction                   | 150°C                 |

| Lead Soldering, Reflow             | 260°C                 |

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

#### 熱抵抗

熱性能は、プリント回路基板(PCB)の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意を払う必要があります。 $\theta_{IA}$  は、1 立方フィートの密封容器内で測定された、自然対流下でのジャンクションから周囲への熱抵抗です。 $\theta_{IB}$  は、ジャンクションから基板への熱抵抗です。 $\theta_{IC}$  は、ジャンクションからケースへの熱抵抗です。表 4 に規定されている熱抵抗値は、JEDEC 仕様に基づいて計算されたものであり、JESD51-12に従って使用してください。最も厳しい条件でのジャンクション温度が記載されています。表 4 の値は、自然対流の試験環境での標準的な JEDEC 2S2P 熱試験ボードに基づいて計算したものです。詳細については、JEDEC JESD51 シリーズを参照してください。

表 4. 熱抵抗

| Package Type | $\theta_{JA}$ | $\theta_{JB}$ | θ <sub>JC_TOP</sub> | Unit |

|--------------|---------------|---------------|---------------------|------|

| CP-32-34     | 39.49         | 9.93          | 14.86               | °C/W |

## 静電放電(ESD)定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起チャージ・デバイス・モデル(FICDM)。

#### AD4190-4 の ESD 定格

表 5. AD4190-4、32 ピン LFCSP

| ESD Model | Withstand Threshold (kV) | Class |

|-----------|--------------------------|-------|

| HBM       | 4                        | 3A    |

| FICDM     | 1.25                     | C3    |

## ESDに関する注意

ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

analog.com.jp Rev. 0 | 13 of 94

## ピン配置およびピン機能の説明

NOTE

1. EXPOSED PAD. CONNECT THE EXPOSED PAD TO AVSS.

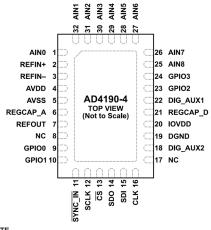

図 9. ピン配置

## 表 6.ピン機能の説明

| ピン番号 | 記号        | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | AIN0      | アナログ入力 0/励起電流/バイアス電圧。この入力ピンは、差動入力または疑似差動入力の正端子または負端子になるよう CHANNEL_MAPn レジスタで設定されます。あるいは、いずれかの内部プログラマブル励起電流源からこのピンに出力できます。アナログ電源レールの中間のバイアス電圧をこのピンで出力できます。                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2    | REFIN+    | 正のリファレンス入力。外部リファレンスを、REFIN+と REFIN-の間に印加します。REFIN+の範囲は AVDD〜AVSS + 1V です。公称リファレンス電圧(REFIN+ - REFIN-)は 2.5V ですが、デバイスは 1V〜AVDD の範囲のリファレンスで動作します。                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3    | REFIN-    | 負のリファレンス入力。このリファレンス入力の範囲は AVSS~AVDD - 1V です。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4    | AVDD      | アナログ電源電圧。これは AVSS を基準としています。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5    | AVSS      | アナログ電源電圧。AVDD の電圧は、AVSS を基準としています。AVDD と AVSS の差は 4.75V~5.25V の範囲であることが必要です。AVSS を 0V よりも低くして、AD4190-4 にバイポーラ電源を供給することもできます。例えば、AVSS を-2.5V に、AVDDを+2.5V にそれぞれ接続すると、ADC に±2.5V を供給できます。                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6    | REGCAP_A  | アナログ低ドロップアウト (LDO) レギュレータの出力。このピンは、1μF のコンデンサと 0.1μF のコンデンサを並列に接続して、AVSS とデカップリングします。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

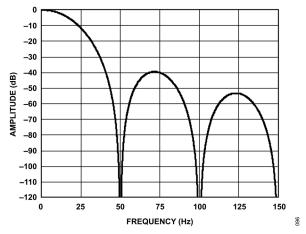

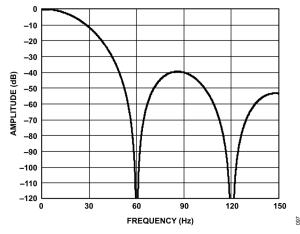

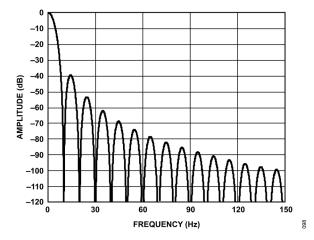

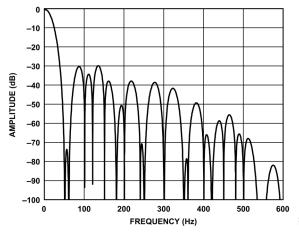

| 7    | REFOUT    | 内部リファレンス出力。これは AVSS を基準としています。内部 2.5V 電圧リファレンスのバッファ付き出力をこのピンに出力できます。このピンは、0.1µF のコンデンサを用いて AVSS とデカップリングします。                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |