## 20 ビット、20MSPS、差動 SAR ADC

### 特長

- ▶ 高性能

- ▶ スループット : 20MSPS、77.50ns の変換レイテンシ

- ▶ INL :  $\pm 4\text{ppm}$  (代表値)、 $\pm 8\text{ppm}$  (最大値)

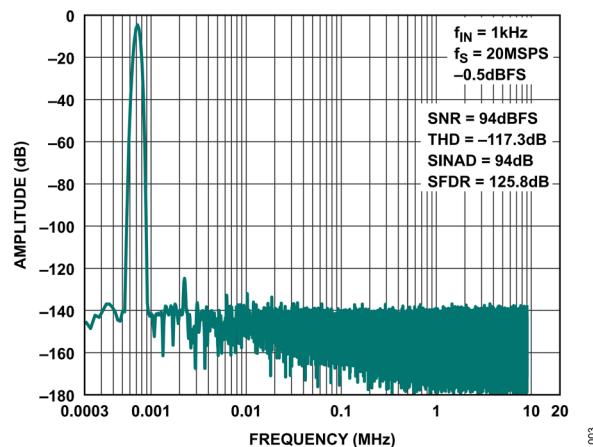

- ▶ ダイナミック・レンジ : 94.6dBFS

- ▶ SNR/THD

- ▶  $f_{IN} = 1\text{kHz}$  で、94dB (代表値) / -117.3dB (代表値)

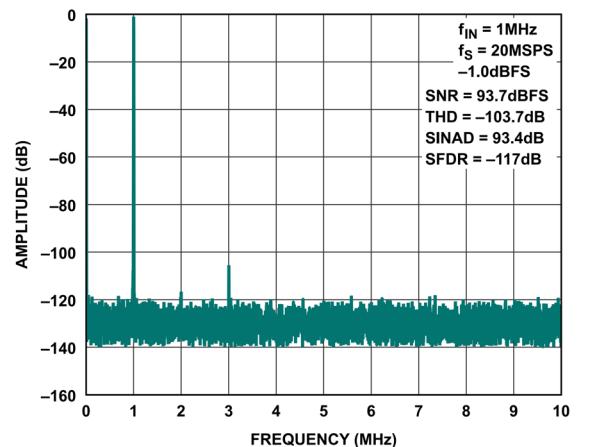

- ▶  $f_{IN} = 1\text{MHz}$  で、93.7dB (代表値) / -103.7dB (代表値)

- ▶ ノイズ・スペクトル密度 : -164.6dBFS/Hz

- ▶ 20 ビット分解能、ノードミッシング・コード

- ▶ 低消費電力

- ▶ 20MSPS、-0.5dBFS 正弦波入力で 68.6mW (代表値)

- ▶ Easy Drive、完全差動入力

- ▶ 6V p-p 差動入力レンジ

- ▶ 連続信号アクイジション

- ▶ 線形特性を持つ  $5\mu\text{A}/\text{MSPS}$  の入力電流

- ▶ 低ドリフトのリファレンス・バッファおよびデカップリングを内蔵

- ▶  $V_{CM}$  生成を内蔵

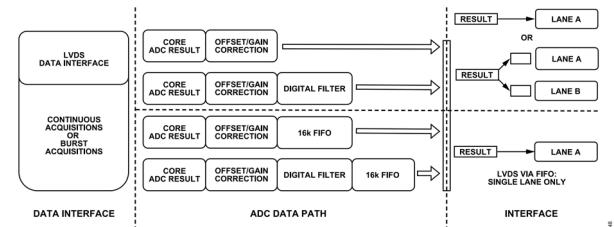

- ▶ デジタル機能とデータ・インターフェース

- ▶ 変換結果 FIFO、16K サンプル深さ

- ▶ 最大  $2^{10}$  デシメーションのデジタル平均化フィルタ

- ▶ SPI 設定

- ▶ データ・インターフェースを設定可能

- ▶ シングル・レーン、DDR、シリアル LVDS、レーンあたり 400Mbps

- ▶ デュアル・レーン、DDR、シリアル LVDS、レーンあたり 200Mbps

- ▶ シングル／クワッド・レーン SPI データ・インターフェース

- ▶ パッケージ

- ▶ 49 ポール、5mm × 5mm CSP\_BGA、0.65mm ピッチ

- ▶ 電源デカップリング・コンデンサを内蔵

- ▶ 動作温度範囲 : -40°C ~ +85°C

### アプリケーション

- ▶ デジタル・イメージング

- ▶ バッテリのセル解析

- ▶ 分光分析

- ▶ ATE (自動試験装置)

- ▶ 高速データ・アクイジション

- ▶ デジタル制御ループ、ハードウェア・イン・ザ・ループ

- ▶ 電力品質の解析

- ▶ ソース計測ユニット

- ▶ 電子顕微鏡と X 線顕微鏡

- ▶ レーダー・レベル測定

- ▶ 非破壊検査

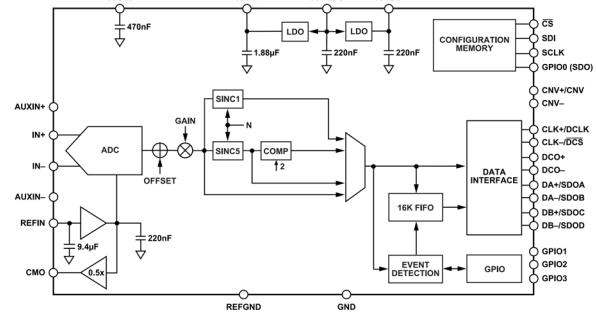

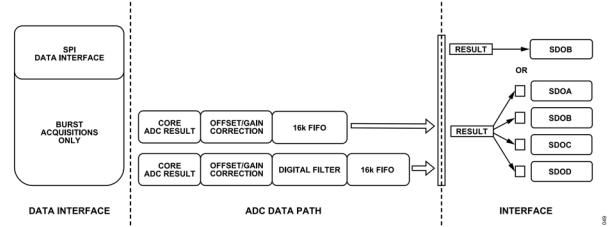

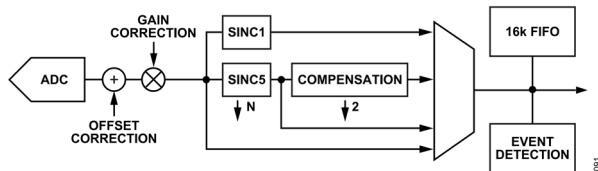

### 機能ブロック図

図 1. AD4081 の機能ブロック図

### 概要

AD4081 は、高速、低ノイズ、低歪み、20 ビット、Easy Drive の逐次比較レジスタ (SAR) A/D コンバータ (ADC) です。AD4081 は、1MHz を超える信号周波数で高い性能 (信号ノイズ + 歪み (SINAD) 比 > 90dBFS) を維持することにより、様々な高精度で広帯域幅のデータ・アクイジション・アプリケーションに対応できます。入力アンチエイリアス・フィルタ設計の簡素化は、内蔵デジタル・フィルタリングおよびデシメーションと共にオーバーサンプリングを適用して、AD4081 の最低レイテンシが不要なアプリケーションに対して、ノイズを低減し、出力データレートを下げるこによって実現できます。

AD4081 の Easy Drive 機能は、シグナル・チェーンの複雑さと消費電力の両方を低減すると同時に、チャンネル密度の向上と関連部品の選択の柔軟性を実現します。本製品の入力構造は、入力に依存する信号電流を最小化するように設計されているため、コンバータによって発生するセトリング・アーティファクトが軽減されます。連続アクイジション・アーキテクチャにより、変換サイクル全体にわたってセトリングが可能になり、他の高速データ・コンバータと比較して、ADC ドライバ・セトリングおよび帯域幅条件が緩和されます。

AD4081 には、低ドリフトのリファレンス・バッファ、ADC コアおよびデジタル・インターフェース電源レールを生成するための低ドロップアウト (LDO) レギュレータ、およびデジタル・ホスト上の負荷を大幅に低減できる 16K 結果データの先入れ先出し (FIFO) など、データ・コンバータの統合を簡素化するいくつかの要素があります。更に、最適な性能を確保し、プリント基板 (PCB) のレイアウトを簡素化し、ソリューション全体のフットプリントを縮小するために、重要な電源およびリファレンス・デカップリング・コンデンサがパッケージに内蔵されています。

## 目次

|                      |    |                             |    |

|----------------------|----|-----------------------------|----|

| 特長                   | 1  | ソフトウェア・リセット                 | 26 |

| アプリケーション             | 1  | アプリケーション情報                  | 28 |

| 機能ブロック図              | 1  | 代表的なアプリケーション図               | 28 |

| 概要                   | 1  | アナログ・フロント・エンドの設計            | 29 |

| 仕様                   | 3  | リファレンス回路の設計                 | 30 |

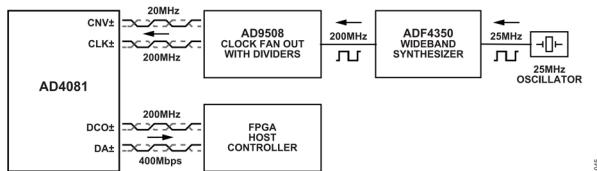

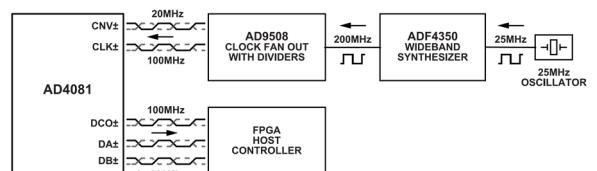

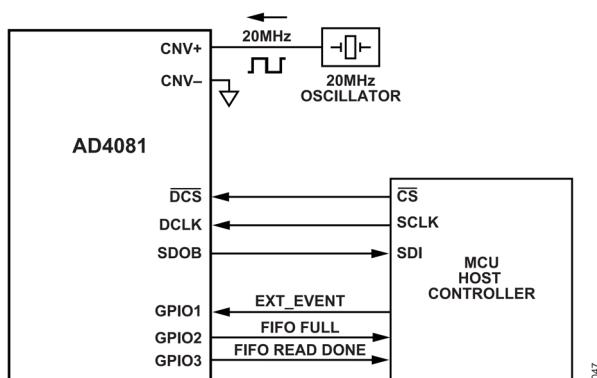

| タイミング仕様              | 6  | データ・インターフェースのクロッキング・ソリューション | 30 |

| 絶対最大定格               | 8  | 電源ソリューション                   | 31 |

| 熱抵抗                  | 8  | デジタル・インターフェース               | 32 |

| 静電放電（ESD）定格          | 8  | 概要                          | 32 |

| ESDに関する注意            | 8  | SPI設定インターフェース               | 32 |

| ピン配置およびピン機能の説明       | 9  | LVDSデータ・インターフェース            | 44 |

| 代表的な性能特性             | 12 | SPIデータ・インターフェース             | 51 |

| 用語の定義                | 17 | GPIOピン                      | 52 |

| 動作原理                 | 18 | デジタル機能                      | 54 |

| 製品の概要                | 18 | 概要                          | 54 |

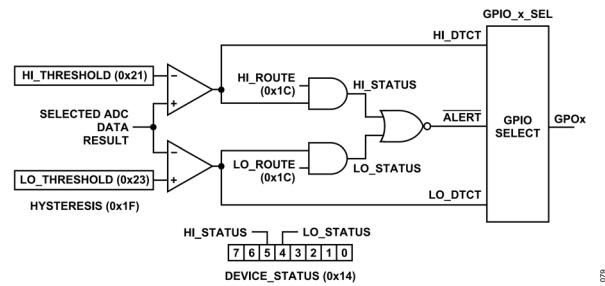

| コンバータの動作             | 18 | イベント検出                      | 54 |

| 伝達関数                 | 19 | 結果 FIFO                     | 56 |

| Easy Drive アナログ入力    | 19 | デジタル・フィルタ                   | 64 |

| リファレンス・バッファとコモンモード出力 | 21 | システム誤差補正係数                  | 71 |

| 電源                   | 21 | レイアウトのガイドライン                | 72 |

| 内部安定化電源の構成           | 22 | 設定レジスタ                      | 73 |

| 外部生成化電源の構成           | 22 | レジスタの詳細                     | 75 |

| パワーオン・リセット（POR）モニタ   | 23 | 外形寸法                        | 95 |

| 電源シーケンス              | 23 | オーダー・ガイド                    | 95 |

| 省電力動作モード             | 25 | 評価用ボード                      | 95 |

## 改訂履歴

7/2025—Revision 0: Initial Version

## 仕様

特に指定のない限り、VDD33 = 3.3V ± 5%、VDDLDO = 1.5V~2.7V、VDD11 = 1.1V ± 5%、IOVDD = 1.1V – 5%~1.2V + 5%、電圧リファレンス入力 ( $V_{REFIN}$ ) = 3.0V、サンプリング周波数 ( $f_S$ ) = 20MHz、 $T_A = T_{MIN} \sim T_{MAX}$ 。

表 1. 仕様

| Parameter                              | Test Conditions/Comments                                                                      | Min                  | Typ           | Max                  | Unit    |

|----------------------------------------|-----------------------------------------------------------------------------------------------|----------------------|---------------|----------------------|---------|

| RESOLUTION                             |                                                                                               | 20                   |               |                      | Bits    |

| ANALOG INPUT                           |                                                                                               |                      |               |                      |         |

| Absolute Operating Input Voltage       | Voltage at input, referred to GND                                                             | -0.1                 |               | VDD33 + 0.1          | V       |

| Differential Input Voltage Range       | IN+ voltage – IN- voltage                                                                     | - $V_{REFIN}$        |               | + $V_{REFIN}$        | V       |

| Common-Mode Input Range                |                                                                                               | $V_{REFIN}/2 - 0.05$ | $V_{REFIN}/2$ | $V_{REFIN}/2 + 0.05$ | V       |

| DC PERFORMANCE                         |                                                                                               |                      |               |                      |         |

| No Missing Codes                       |                                                                                               | 20                   |               |                      | Bits    |

| Differential Nonlinearity (DNL)        |                                                                                               | ±0.3                 | ±0.99         |                      | LSB     |

| Integral Nonlinearity (INL)            |                                                                                               | ±4                   | ±8            |                      | ppm     |

| Transition Noise                       |                                                                                               | 6.9                  |               |                      | LSB RMS |

| Gain Error                             | $T_A = 25^\circ C$                                                                            | 0.0024               | ±0.03         |                      | %FS     |

| Gain Error Drift                       | $T_A = -40^\circ C$ to $+85^\circ C$                                                          | 0.27                 |               |                      | ppm/°C  |

| Zero Error                             | $T_A = 25^\circ C$                                                                            | 25                   |               |                      | μV      |

| Zero-Error Drift                       | $T_A = -40^\circ C$ to $+85^\circ C$                                                          | 0.03                 |               |                      | ppm/°C  |

| Power Supply Rejection                 | VDD33 = 3.3V ± 5%                                                                             | -89                  |               |                      | dB      |

|                                        | VDD11 = 1.1V ± 5%                                                                             | -68                  |               |                      | dB      |

| Low Frequency Noise                    | Bandwidth = 0.1Hz to 10Hz                                                                     | 179                  |               |                      | nV RMS  |

| AC PERFORMANCE                         |                                                                                               |                      |               |                      |         |

| Dynamic Range                          |                                                                                               | 94.6                 |               |                      | dB      |

| Noise Spectral Density (NSD)           |                                                                                               | -164.6               |               |                      | dBFS/Hz |

| Total RMS Noise                        | Bandwidth = 10MHz                                                                             | 39.4                 |               |                      | μV RMS  |

| Signal-to-Noise Ratio (SNR)            | Voltage magnitude ( $V_{MAG}$ ) = -0.5dBFS, input frequency ( $f_{IN}$ ) = 1kHz               | 92.8                 | 94            |                      | dB      |

|                                        | $V_{MAG} = -1\text{dBFS}, f_{IN} = 1\text{MHz}$                                               | 93.7                 |               |                      | dB      |

|                                        | Sinc5 + compensation filter, decimate by 8, $V_{MAG} = -0.5\text{dBFS}, f_{IN} = 1\text{kHz}$ | 102.2                | 102.8         |                      | dB      |

| Total Harmonic Distortion (THD)        | $V_{MAG} = -0.5\text{dBFS}, f_{IN} = 1\text{kHz}$                                             |                      | -117.3        | -108                 | dB      |

|                                        | $V_{MAG} = -1\text{dBFS}, f_{IN} = 1\text{MHz}$                                               |                      | -103.7        |                      | dB      |

| Signal-to-Noise-and-Distortion (SINAD) | $V_{MAG} = -0.5\text{dBFS}, f_{IN} = 1\text{kHz}$                                             | 94                   |               |                      | dB      |

|                                        | $V_{MAG} = -0.5\text{dBFS}, f_{IN} = 1\text{MHz}$                                             | 93.4                 |               |                      | dB      |

| Spurious-Free Dynamic Range            | $V_{MAG} = -0.5\text{dBFS}, f_{IN} = 1\text{kHz}$                                             | 125.8                |               |                      | dB      |

|                                        | $V_{MAG} = -0.5\text{dBFS}, f_{IN} = 1\text{MHz}$                                             | 114.3                |               |                      | dB      |

| -3dB Bandwidth                         | Input at IN+ and IN-, no external filter                                                      | 272                  |               |                      | MHz     |

| Intermodulation Distortion (IMD)       | Frequency A ( $f_A$ ) = 1.0MHz, Frequency B ( $f_B$ ) = 800kHz                                |                      |               |                      |         |

| Second-Order IMD (IMD2)                |                                                                                               | -108.4               |               |                      | dB      |

| Third-Order IMD (IMD3)                 |                                                                                               | -98.7                |               |                      | dB      |

| Power Supply Rejection                 | Ripple voltage = 50mV p-p, $f = 1\text{kHz}$                                                  |                      |               |                      |         |

| VDD33                                  |                                                                                               | -92.6                |               |                      | dB      |

| VDD11                                  |                                                                                               | -81.1                |               |                      | dB      |

| REFERENCE INPUT                        |                                                                                               |                      |               |                      |         |

| $V_{REFIN}$ Range                      |                                                                                               | 2.995                | 3.0           | 3.005                | V       |

| $V_{REFIN}$ Current                    |                                                                                               | -0.3                 |               | +1                   | μA/MSPS |

|                                        | $T_A = 25^\circ C$                                                                            | -7                   |               | +20                  | μA      |

| $V_{REFIN}$ Leakage Current            | Converter Idle                                                                                | -2                   |               | +2                   | μA      |

## 仕様

表 1. 仕様 (続き)

| Parameter                                                            | Test Conditions/Comments                                                                        | Min           | Typ  | Max                 | Unit           |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------|------|---------------------|----------------|

| COMMON-MODE OUTPUT (CMO)                                             |                                                                                                 |               |      |                     |                |

| Absolute Output Voltage                                              | $V_{REFIN} = 3.0V$                                                                              | 1.48          |      | 1.51                | V              |

| Noise                                                                | Bandwidth = 7.4MHz                                                                              |               | 71   |                     | $\mu V$ RMS    |

| Noise Spectral Density                                               |                                                                                                 |               | 26.1 |                     | $nV/\sqrt{Hz}$ |

| LOW DROPOUT REGULATORS (VDD11, IOVDD)                                |                                                                                                 |               |      |                     |                |

| Input Voltage Range (VDDLDO)                                         |                                                                                                 | 1.4           |      | 2.7                 | V              |

| Output Voltage                                                       | $T_A = 25^\circ C$ , VDDLDO = 1.8V                                                              |               | 1.1  |                     | V              |

| Start-Up Time                                                        |                                                                                                 |               | 10   |                     | $\mu s$        |

| LOW VOLTAGE DIFFERENTIAL SIGNALING (LVDS) INPUT AND OUTPUT (EIA-644) |                                                                                                 |               |      |                     |                |

| Data Format                                                          | Serial LVDS data output                                                                         |               |      | Twos complement     |                |

| LVDS Inputs (CLK $\pm$ and CNV $\pm$ )                               | IOVDD supply domain inputs                                                                      |               |      |                     |                |

| Common-Mode Input Voltage ( $V_{ICM}$ )                              | Default setting                                                                                 | 700           |      | 1400                | mV             |

| Differential Input Voltage ( $V_{IDIFF}$ )                           | Default setting                                                                                 | 100           |      | 600                 | mV             |

| LVDS Outputs (DCO $\pm$ , DA $\pm$ , and DB $\pm$ )                  | IOVDD supply domain outputs, differential termination, load resistance ( $R_L$ ) = 100 $\Omega$ |               |      |                     |                |

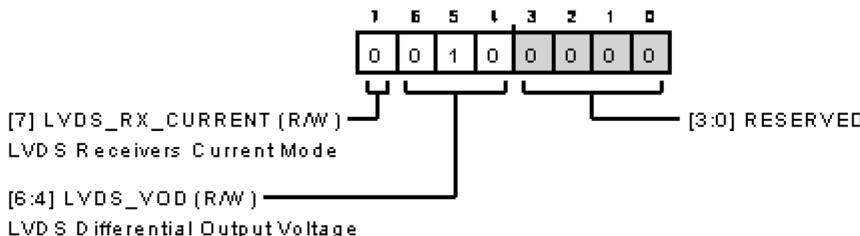

| Common-Mode Output Voltage ( $V_{OCM}$ )                             | LVDS_VOD = 001b                                                                                 | 915           | 927  | 935                 | mV             |

|                                                                      | LVDS_VOD = 010b (default)                                                                       | 840           | 851  | 860                 | mV             |

|                                                                      | LVDS_VOD = 100b                                                                                 | 695           | 706  | 715                 | mV             |

| Differential Output Voltage ( $V_{ODIFF}$ )                          | LVDS_VOD = 001b                                                                                 | 370           | 382  | 430                 | mV             |

|                                                                      | LVDS_VOD = 010b (default)                                                                       | 500           | 510  | 570                 | mV             |

|                                                                      | LVDS_VOD = 100b                                                                                 | 735           | 745  | 840                 | mV             |

| DIGITAL INPUTS (CNV, CS, SCLK, and SDI)                              | VDD11 supply domain inputs                                                                      |               |      |                     |                |

| Input Voltage Tolerance                                              |                                                                                                 | 0             |      | 2.5                 |                |

| Logic Levels                                                         |                                                                                                 |               |      |                     |                |

| Input Low Voltage ( $V_{IL}$ )                                       |                                                                                                 | 0             |      | 0.36 $\times$ VDD11 |                |

| Input High Voltage ( $V_{IH}$ )                                      |                                                                                                 | 0.92          |      | 2.5                 |                |

| DIGITAL INPUTS (GPIOx, DC $\bar{S}$ , and DCLK)                      | IOVDD supply domain inputs                                                                      |               |      |                     |                |

| Input Voltage Tolerance                                              |                                                                                                 | 0             |      | 1.26                | V              |

| Logic Levels                                                         |                                                                                                 |               |      |                     |                |

| $V_{IL}$                                                             |                                                                                                 | 0             |      | 0.36 $\times$ IOVDD | V              |

| $V_{IH}$                                                             |                                                                                                 | 0.92          |      | IOVDD               | V              |

| Input Current                                                        |                                                                                                 |               |      |                     |                |

| Input Low Current ( $I_{IL}$ )                                       |                                                                                                 | -1            |      | +1                  | $\mu A$        |

| Input High Current ( $I_{IH}$ )                                      |                                                                                                 | -1            |      | +1                  | $\mu A$        |

| Input Pin Capacitance                                                |                                                                                                 |               | 4.5  |                     | pF             |

| DIGITAL OUTPUTS (GPIOx)                                              | IOVDD supply domain outputs                                                                     |               |      |                     |                |

| Logic Levels                                                         |                                                                                                 |               |      |                     |                |

| Output Low Voltage ( $V_{OL}$ )                                      | Sink current ( $I_{SINK}$ ) = 500 $\mu A$                                                       | 0             |      | 0.15                | V              |

| Output High Voltage ( $V_{OH}$ )                                     | Source current ( $I_{SOURCE}$ ) = 500 $\mu A$                                                   | IOVDD - 0.115 |      | IOVDD               | V              |

| DIGITAL OUTPUTS (SDOx)                                               | IOVDD supply domain outputs.                                                                    |               |      |                     |                |

| Data Format                                                          | Configured as serial data output                                                                |               |      | Twos complement     |                |

| Logic Levels                                                         |                                                                                                 |               |      |                     |                |

| $V_{OL}$                                                             | $I_{SINK} = 500\mu A$                                                                           | 0             |      | 0.15                | V              |

| $V_{OH}$                                                             | $I_{SOURCE} = 500\mu A$                                                                         | IOVDD - 0.115 |      | IOVDD               | V              |

## 仕様

表 1. 仕様（続き）

| Parameter             | Test Conditions/Comments                    | Min   | Typ  | Max   | Unit |

|-----------------------|---------------------------------------------|-------|------|-------|------|

| POWER SUPPLIES        |                                             |       |      |       |      |

| VDD33                 |                                             | 3.135 | 3.30 | 3.465 | V    |

| VDDLDO                |                                             | 1.4   |      | 2.7   | V    |

| VDD11                 | Applied externally, LDO disabled            | 1.045 | 1.10 | 1.155 | V    |

| IOVDD                 | Applied externally, LDO disabled            | 1.045 | 1.10 | 1.26  | V    |

| Operating Current     | LVDS_CNV_EN = 0                             |       |      |       |      |

| Static                | Converter and interface idle, FIFO disabled |       |      |       |      |

| VDD33                 |                                             | 5.4   | 7.14 |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 16.4  | 23   |       | mA   |

| IOVDD                 |                                             | 5.2   | 6    |       | mA   |

| VDDLDO                | VDD11 LDO enabled                           | 21.5  | 26.5 |       | mA   |

| Dynamic               | DC input signal                             |       |      |       |      |

| VDD33                 |                                             | 11.8  | 13.2 |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 21.8  | 27   |       | mA   |

| IOVDD                 |                                             | 8.1   | 8.6  |       | mA   |

| VDDLDO                | VDD11 LDO enabled                           | 29.8  | 35.5 |       | mA   |

| Dynamic               | -0.5dBFS sine-wave input signal             |       |      |       |      |

| VDD33                 |                                             | 11    | 12.3 |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 21.7  | 27   |       | mA   |

| IOVDD                 |                                             | 7.7   | 8.7  |       | mA   |

| VDDLDO                | VDD11 LDO enabled                           | 28    | 33.5 |       | mA   |

| Standby Mode          | LVDS_SELF_CLK_MODE disabled                 |       |      |       |      |

| VDD33                 |                                             | 1.4   | 1.9  |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 2     | 4.4  |       | mA   |

| IOVDD                 |                                             | 99    | 315  |       | μA   |

| VDDLDO                | VDD11 LDO enabled                           | 1.7   | 3.9  |       | mA   |

| Sleep Mode            | LVDS_SELF_CLK_MODE disabled                 |       |      |       |      |

| VDD33                 |                                             | 0.6   | 0.9  |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 1.2   | 3.7  |       | mA   |

| IOVDD                 |                                             | 60    | 299  |       | μA   |

| VDDLDO                | VDD11 LDO enabled                           | 1.5   | 4.5  |       | mA   |

| Power Dissipation     |                                             |       |      |       |      |

| Static                | VDD11 LDO disabled                          | 41.6  | 58.9 |       | mW   |

| Dynamic               | DC input signal                             | 71.8  | 87.8 |       | mW   |

| Dynamic               | -0.5dBFS sine-wave input signal             | 68.6  | 84.8 |       | mW   |

| Standby Mode          | VDD11 LDO disabled                          | 6.9   | 12.1 |       | mW   |

| Sleep Mode            | VDD11 LDO disabled                          | 3.4   | 7.8  |       | mW   |

| TEMPERATURE RANGE     |                                             |       |      |       |      |

| Specified Performance | T <sub>MIN</sub> to T <sub>MAX</sub>        | -40   |      | +85   | °C   |

## 仕様

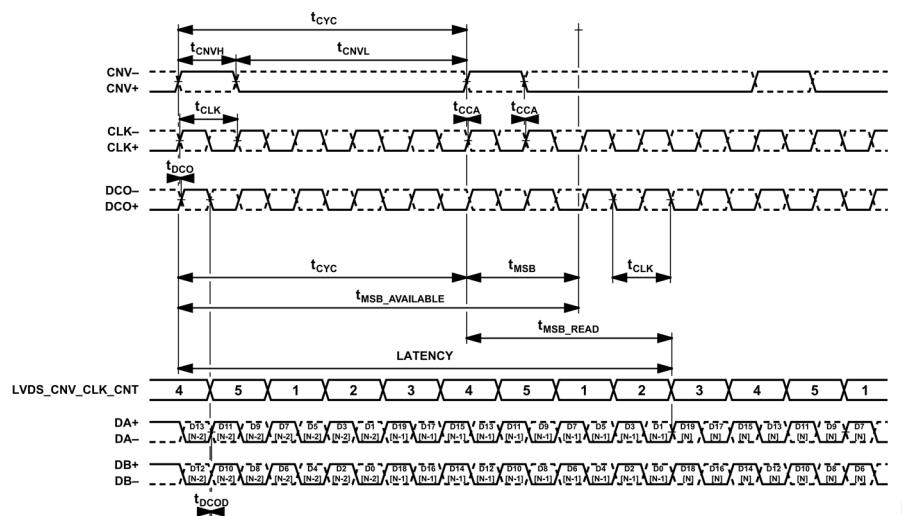

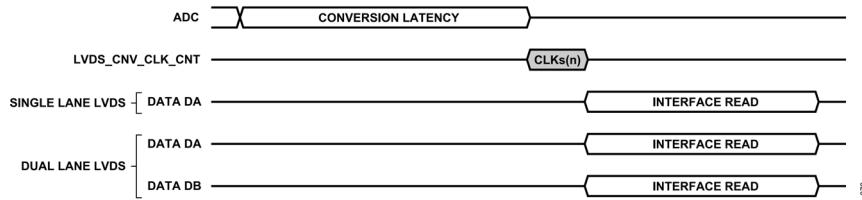

## タイミング仕様

特に指定のない限り、VDD33 = 3.3V ± 5%、VDDLDO = 1.5V~2.7V、VDD11 = 1.1V ± 5%、IOVDD = 1.1V – 5%~1.2V + 5%、VREFIN = 3.0V、fs = 20MHz、TA = TMIN~TMAX。

表 2. タイミング仕様

| Parameter                                                        | Symbol               | Min                     | Typ                                                                    | Max                                  | Unit |

|------------------------------------------------------------------|----------------------|-------------------------|------------------------------------------------------------------------|--------------------------------------|------|

| Sampling Frequency                                               | f <sub>S</sub>       | 1.25                    |                                                                        | 20                                   | MHz  |

| Conversion Time                                                  | t <sub>CONV</sub>    | 50                      |                                                                        | 800                                  | ns   |

| Acquisition Phase                                                | t <sub>ACQ</sub>     | t <sub>CYC</sub>        |                                                                        |                                      | ns   |

| Conversion Cycle Period                                          | t <sub>CYC</sub>     | t <sub>CONV</sub>       |                                                                        |                                      | ns   |

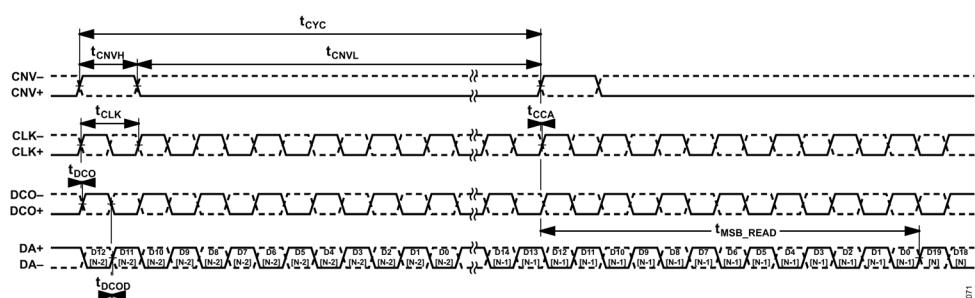

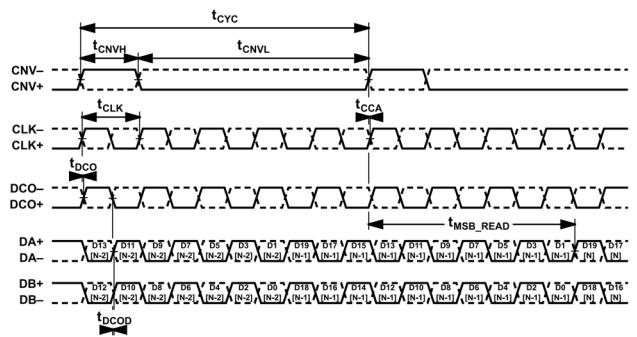

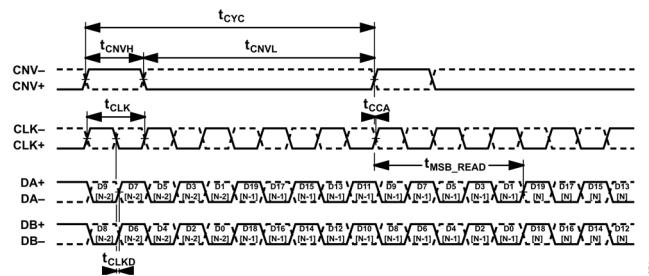

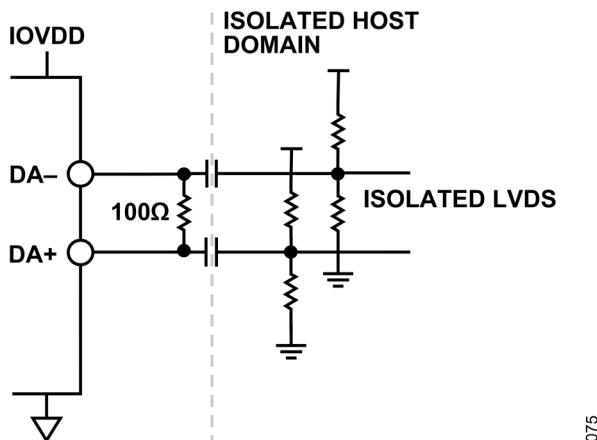

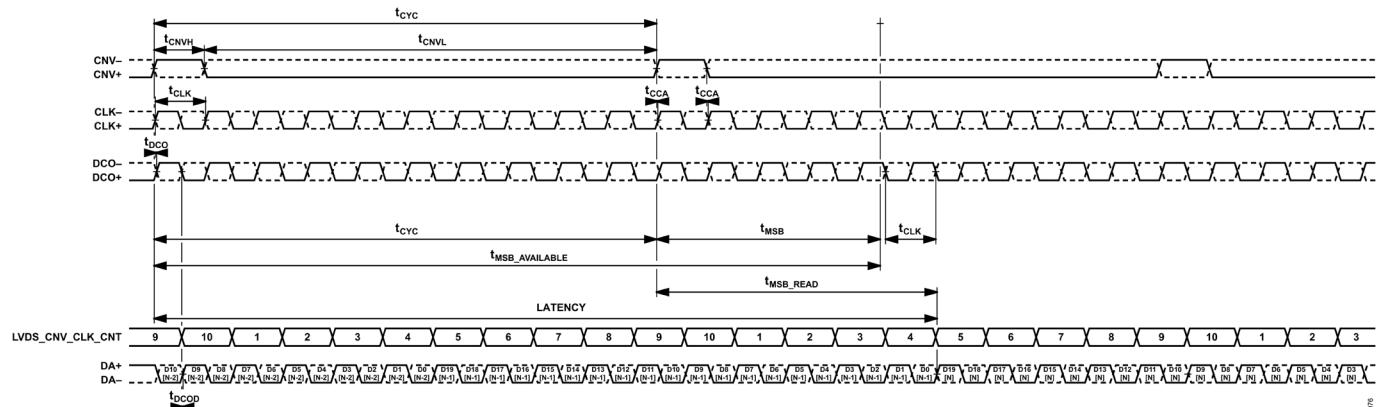

| LVDS Data Interface                                              |                      |                         |                                                                        |                                      |      |

| Data Interface Clock Count                                       | N                    |                         |                                                                        | 10                                   |      |

| Active Data Lane Count                                           | L                    |                         |                                                                        | 2                                    |      |

| CNV± High Time                                                   | t <sub>CNVH</sub>    | t <sub>CLK</sub>        | 5 × t <sub>CLK</sub>                                                   | t <sub>CYC</sub> – t <sub>CNVL</sub> | ns   |

| CNV± Low Time                                                    | t <sub>CNVL</sub>    | t <sub>CLK</sub>        | 5 × t <sub>CLK</sub>                                                   | t <sub>CYC</sub> – t <sub>CNVH</sub> | ns   |

| CNV± Edge to CLK± Rising Edge Alignment                          | t <sub>CCA</sub>     |                         |                                                                        | 535                                  | ps   |

| CNV± to Dx± (MSB) Ready                                          | t <sub>MSB</sub>     |                         |                                                                        |                                      |      |

| Gain Error Correction Enabled                                    |                      |                         | 20.5                                                                   | 22.4                                 | ns   |

| Gain Error Correction Disabled                                   |                      |                         | 15.7                                                                   | 18                                   | ns   |

| CLK± Period                                                      | t <sub>CLK</sub>     | 5                       |                                                                        | t <sub>CYC</sub> × L/N               | ns   |

| CLK± Frequency                                                   | f <sub>CLK</sub>     |                         | 1/t <sub>CLK</sub>                                                     | 200                                  | MHz  |

| CLK± to Dx± Delay                                                | t <sub>CLKD</sub>    | 1                       |                                                                        | 2.1                                  | ns   |

| CLK± to DCO± Delay (Echo Clock Mode)                             | t <sub>DCO</sub>     | 1                       |                                                                        | 2                                    | ns   |

| DCO± to Dx± Delay (Echo Clock Mode)                              | t <sub>DCOD</sub>    | 0.02                    |                                                                        | 1                                    | ns   |

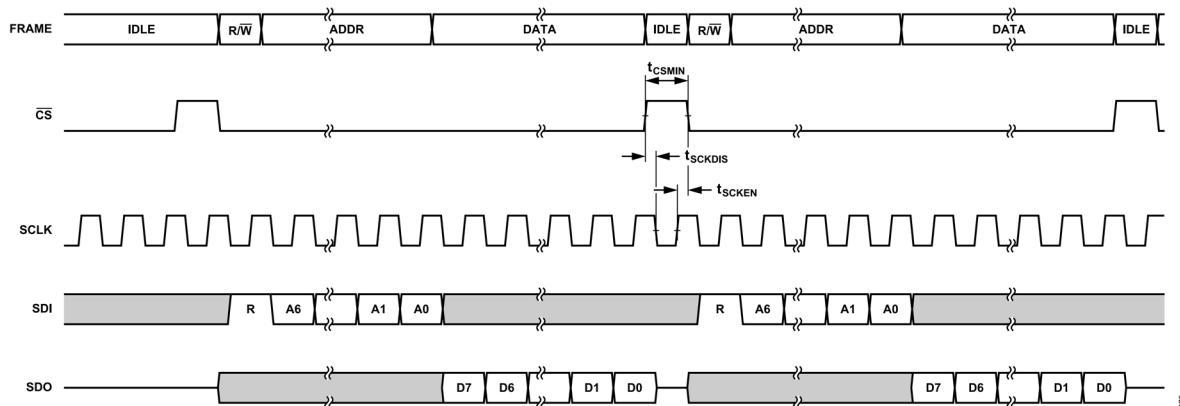

| Serial Peripheral Interface (SPI) Data Interface                 |                      |                         |                                                                        |                                      |      |

| Data Interface Clock Count, Single Conversion Result             | M                    |                         |                                                                        | 24                                   |      |

| Active Data Lane Count                                           | C                    |                         | 1                                                                      | 4                                    |      |

| Data Interface Chip Select Falling Edge (DCS) to SDOB Data Valid | t <sub>DEN</sub>     | 5                       | 6                                                                      |                                      | ns   |

| Data Interface Clock Period (DCLK)                               | t <sub>DCK</sub>     | 20                      |                                                                        |                                      | ns   |

| Data Interface Clock Low Pulse Width (DCLKL)                     | t <sub>DCKL</sub>    | t <sub>DCK</sub> × 0.45 |                                                                        |                                      | ns   |

| Data Interface Clock High Pulse Width (DCLKH)                    | t <sub>DCLKH</sub>   | t <sub>DCK</sub> × 0.45 |                                                                        |                                      | ns   |

| Data Interface Clock Falling Edge to Data Remains Valid Delay    | t <sub>DHSDO</sub>   | 5                       |                                                                        |                                      | ns   |

| Data Interface Clock Falling Edge to Data Valid Delay            | t <sub>DDSDO</sub>   |                         |                                                                        | 9.6                                  | ns   |

| DCLK Rising to Data Interface Chip Select Falling                | t <sub>DCKEN</sub>   | 0                       |                                                                        |                                      | ns   |

| Data Interface Chip Select High to DCLK Disabled                 | t <sub>DCLKDIS</sub> | 0                       |                                                                        |                                      | ns   |

| Data Interface Chip Select High Between Frames                   | t <sub>DCSMIN</sub>  |                         | (t <sub>DCKEN</sub> + t <sub>DCLKDIS</sub> ) + 0.5 × t <sub>DCLK</sub> |                                      | ns   |

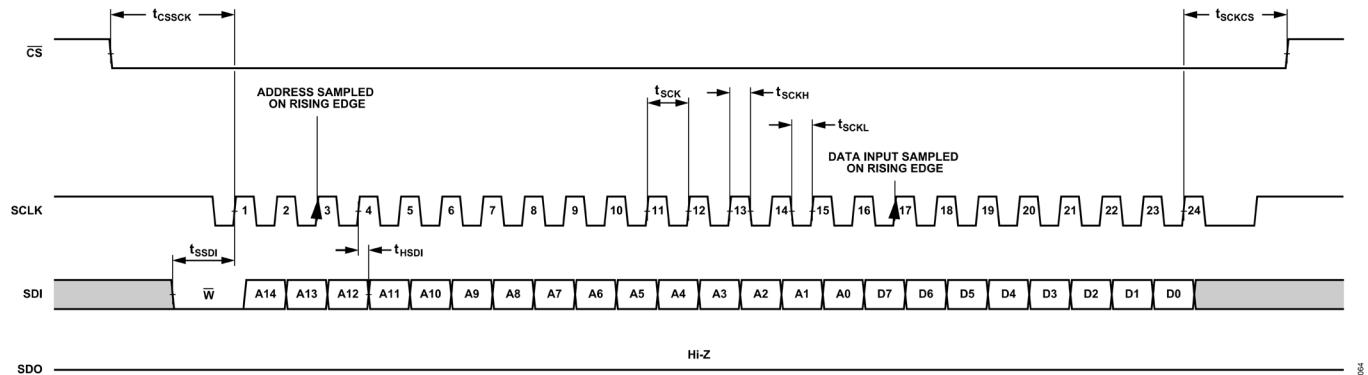

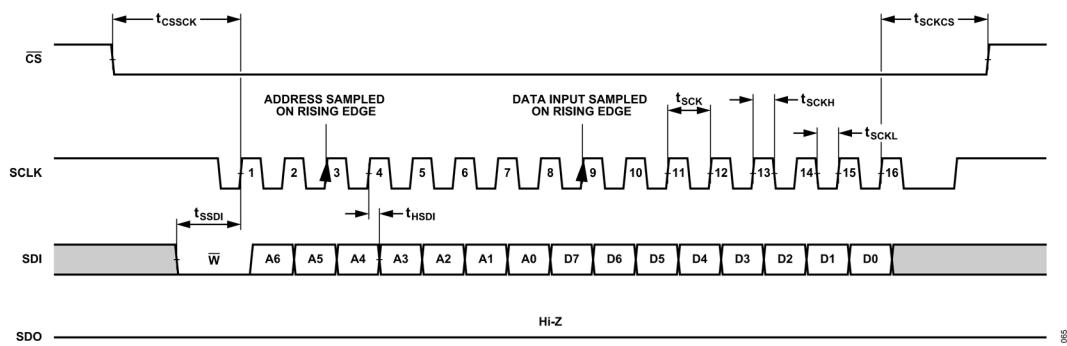

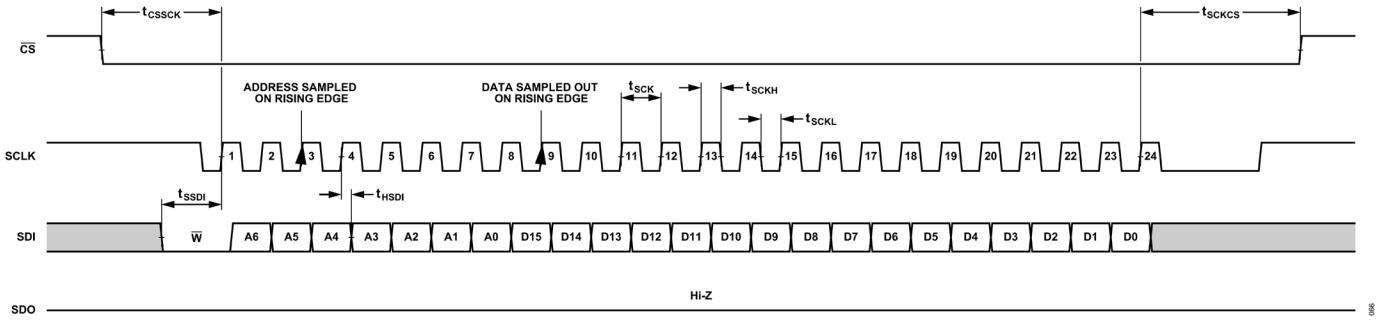

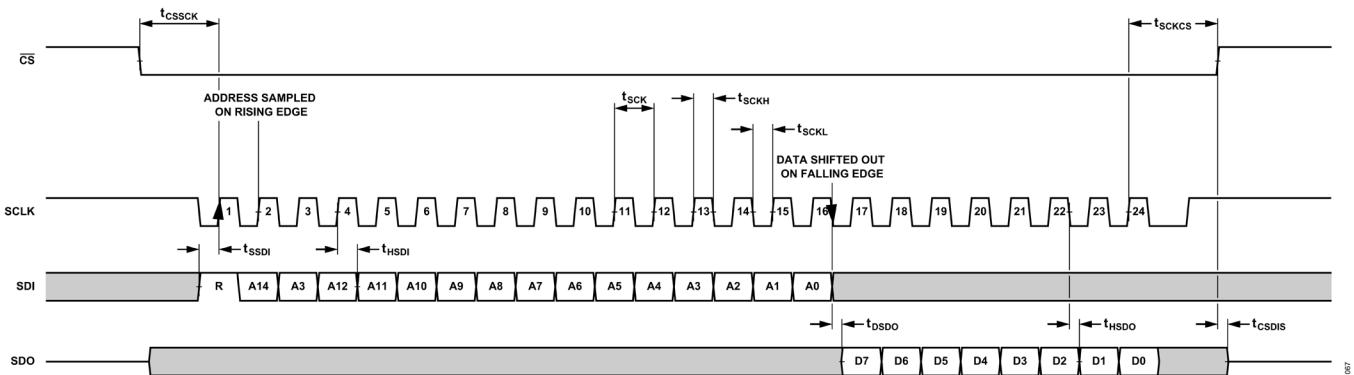

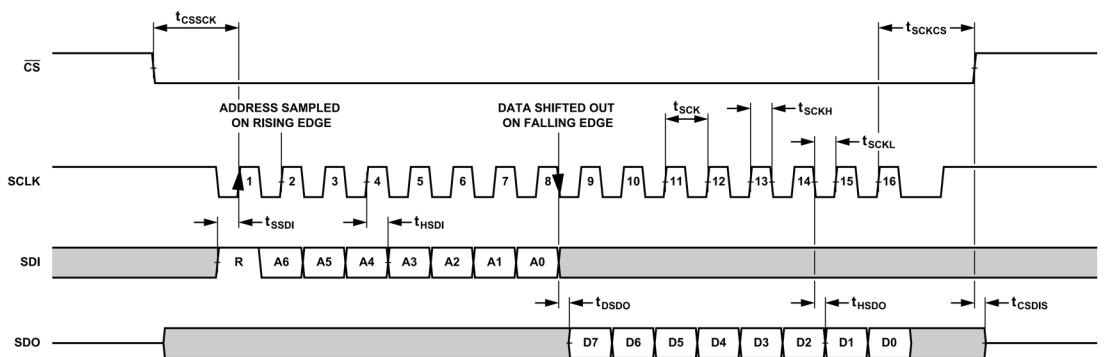

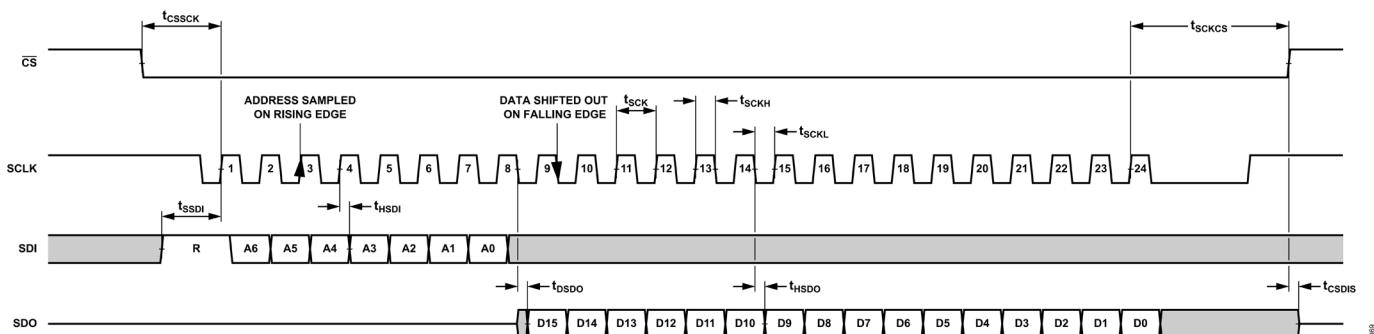

| Serial Configuration Interface                                   |                      |                         |                                                                        |                                      |      |

| SCLK Period                                                      | t <sub>SCK</sub>     | 20                      |                                                                        |                                      | ns   |

| SCLK Low Pulse Width                                             | t <sub>SCKL</sub>    | t <sub>SCK</sub> × 0.45 |                                                                        |                                      | ns   |

| SCLK High Pulse Width                                            | t <sub>SCKH</sub>    | t <sub>SCK</sub> × 0.45 |                                                                        |                                      | ns   |

| SCLK Falling Edge to Data Remains Valid Delay                    | t <sub>HSDO</sub>    | 0.7                     |                                                                        |                                      | ns   |

| SCLK Falling Edge to Data Valid Delay                            | t <sub>DSDO</sub>    |                         |                                                                        | 14.5                                 | ns   |

| CS Falling Edge to SCLK                                          | t <sub>CSSCK</sub>   | 0                       |                                                                        |                                      | ns   |

| Last SCLK to CS Rising                                           | t <sub>SCKCS</sub>   | 0                       |                                                                        |                                      | ns   |

| SDI Valid Setup Time Before SCLK Rising Edge                     | t <sub>SSDI</sub>    | 1                       |                                                                        |                                      | ns   |

| SDI Valid Hold Time After SCLK Rising Edge                       | t <sub>HSDI</sub>    | 0                       |                                                                        |                                      | ns   |

| SCLK Rising to Data Interface Chip Select Falling                | t <sub>SCKEN</sub>   | 0                       |                                                                        |                                      | ns   |

## 仕様

表 2. タイミング仕様（続き）

| Parameter                                               | Symbol          | Min                | Typ                                             | Max                | Unit |

|---------------------------------------------------------|-----------------|--------------------|-------------------------------------------------|--------------------|------|

| Data Interface Chip Select High to SCLK Disabled        | $t_{SCKDIS}$    | 0                  |                                                 |                    | ns   |

| Data Interface Chip Select High to SDO Disabled         | $t_{CSDIS}$     |                    |                                                 | 10.3               | ns   |

| Data Interface Chip Select High Between Frames          | $t_{CSMIN}$     |                    | $(t_{SCKEN} + t_{SCKDIS}) + 0.5 \times t_{SCK}$ |                    | ns   |

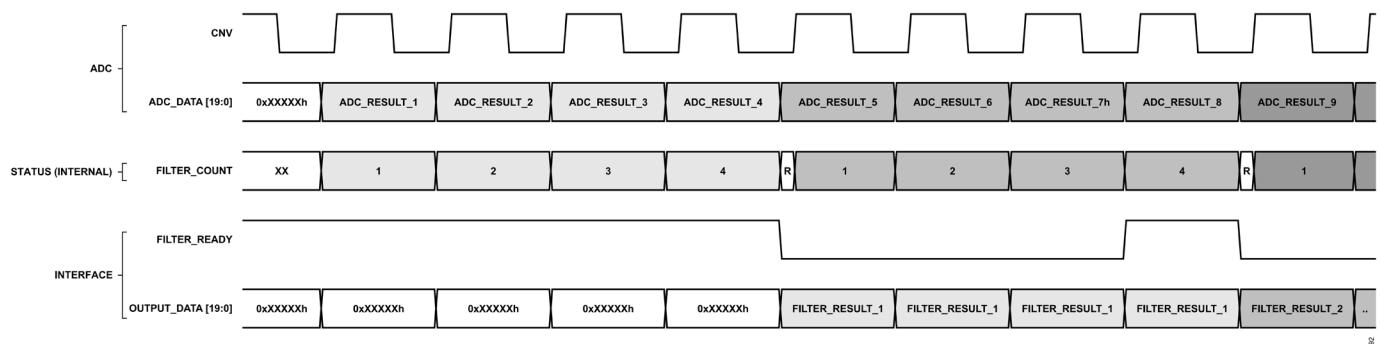

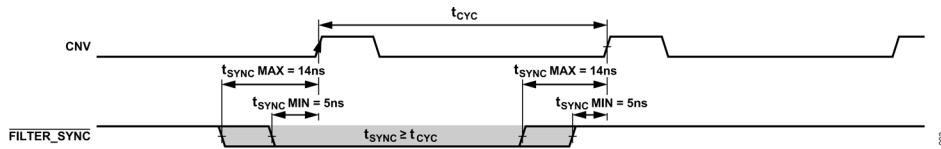

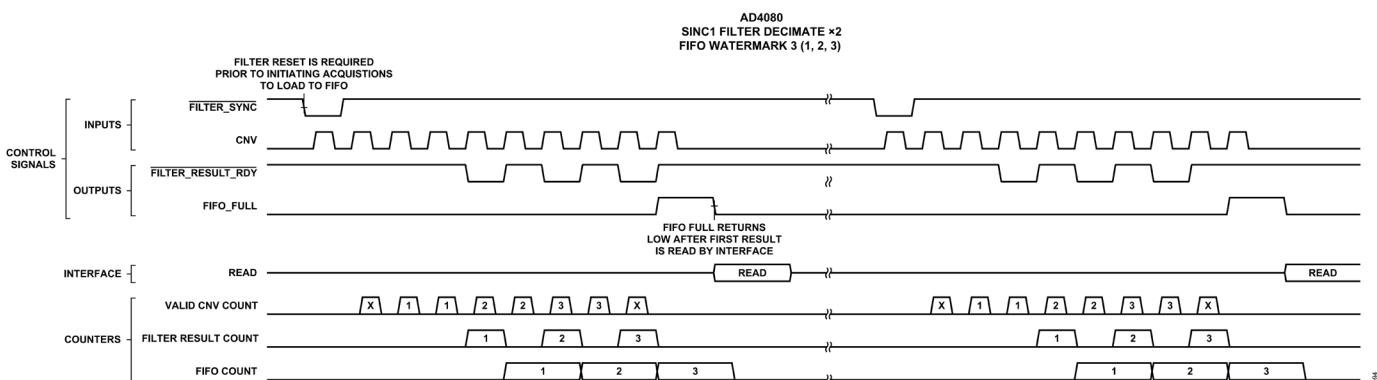

| Digital Filter                                          |                 |                    |                                                 |                    |      |

| $\overline{FILT\_SYNC}$ Rising Edge to CNV Rising Edge  | $t_{SYNC\ MAX}$ |                    | $t_{CYC} - 5$                                   |                    | ns   |

| CNV Rising Edge to $\overline{FILT\_SYNC}$ Falling Edge | $t_{SYNC\ MIN}$ |                    | 3                                               |                    | ns   |

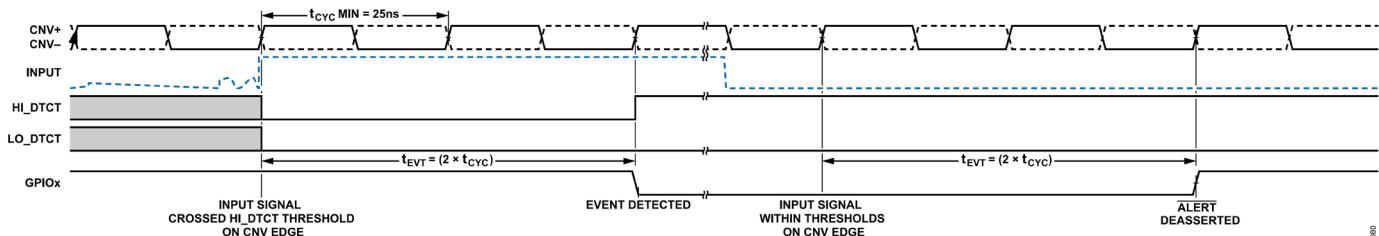

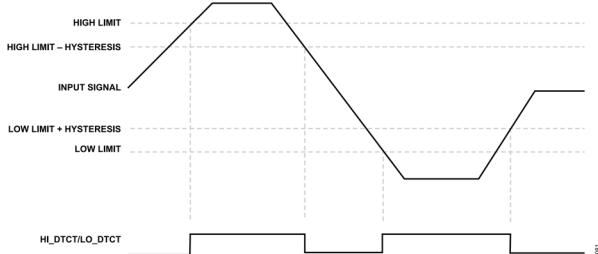

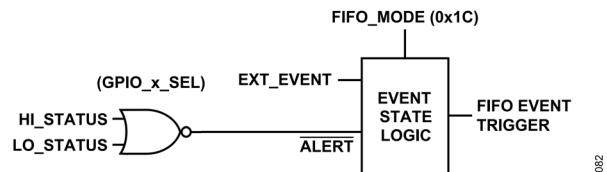

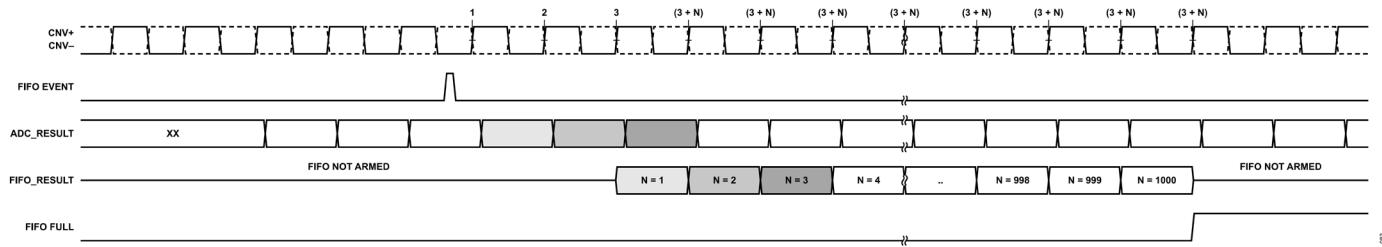

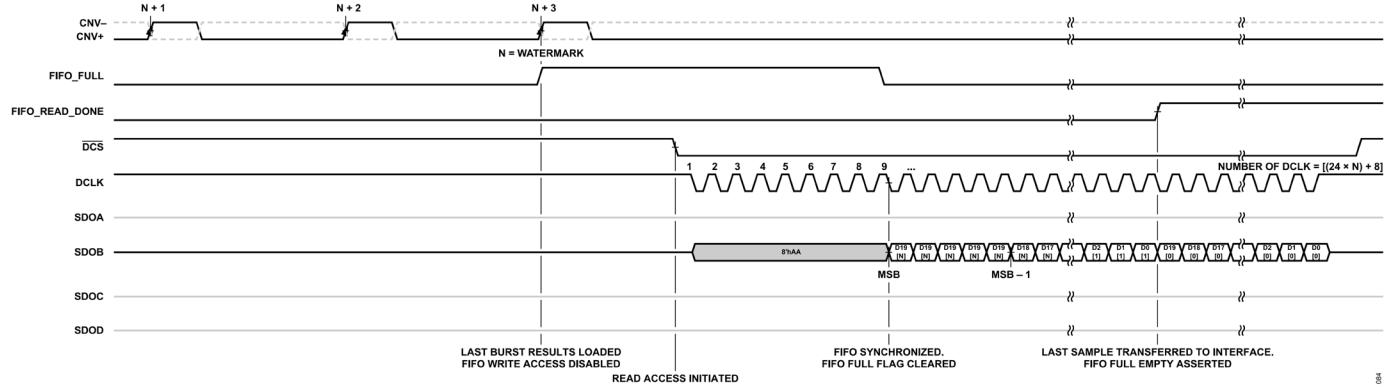

| Event Detection                                         |                 |                    |                                                 |                    |      |

| Input Threshold Crossed to $\overline{ALERT}$ Asserted  | $t_{EVT}$       | $2 \times t_{CYC}$ |                                                 | $3 \times t_{CYC}$ |      |

## 絶対最大定格

表 3. 絶対最大定格

| Parameter                                                 | Rating          |

|-----------------------------------------------------------|-----------------|

| Analog Inputs<br>IN+, AUXIN+, IN-, and AUXIN- to GND      | -0.3V to +3.6V  |

| Analog Output<br>CMO                                      | -0.3V to +3.6V  |

| Supply Voltage<br>REFIN and VDD33 to GND                  | -0.3V to +3.6V  |

| VDDLDO to GND                                             | -0.3V to +2.75V |

| VDD11 to GND                                              | -0.3V to +1.26V |

| IOVDD to GND                                              | -0.3V to +1.26V |

| Digital Inputs and Outputs                                |                 |

| Inputs (CNV $\pm$ and CLK $\pm$ ) to GND                  | -0.3V to +2.75V |

| LVDS OUTPUT (DCO $\pm$ , DA $\pm$ , and DB $\pm$ ) to GND | -0.3V to +1.26V |

| CS, SCLK, and SDI to GND                                  | -0.3V to +2.75V |

| GPIO0, GPIO1, GPIO2, and GPIO3 to GND                     | -0.3V to +1.26V |

| Temperature                                               |                 |

| Storage Range                                             | -55°C to +150°C |

| Operating Range                                           | -40°C to +85°C  |

| Maximum Reflow (Package) as per JEDEC J-STD-020           | 260°C           |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上のデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意を払う必要があります。

表 4. 热抵抗

| Package | Type    | $\theta_{JA}$ <sup>1</sup> | $\Psi_{JT}$ <sup>1</sup> | $\Psi_{JB}$ <sup>1</sup> | $\theta_{JB}$ <sup>2</sup> | $\theta_{JC}$ <sup>3</sup> | Unit |

|---------|---------|----------------------------|--------------------------|--------------------------|----------------------------|----------------------------|------|

|         | BC-49-8 | 66.8                       | 1.7                      | 45.1                     | 45.9                       | 53.1                       | °C/W |

<sup>1</sup>  $\theta_{JA}$ 、 $\Psi_{JT}$ 、 $\Psi_{JB}$ は、JEDEC の自然対流環境下で、16 個のサーマル・ピアを配した JEDEC 2S2P テスト PCB を用いてモデル化したものです。

<sup>2</sup>  $\theta_{JB}$ は、JEDEC に準拠したジャンクションから基板への環境下で、16 個のサーマル・ピアを配した JEDEC 2S2P テスト PCB を用いてモデル化したものです。

<sup>3</sup>  $\theta_{JC}$ は、無限ヒート・シンクをパッケージ表面に直接取り付け、JEDEC 1S テスト PCB を用いてモデル化したものです。

## 静電放電 (ESD) 定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帶電デバイス・モデル (FICDM)。

## AD4081 の ESD 定格

表 5. AD4081、49 ボール CSP\_BGA

| ESD Model                                                                             | Withstand Threshold (V) | Class |

|---------------------------------------------------------------------------------------|-------------------------|-------|

| HBM (Pin E1, Pin E2, Pin D1, and Pin D2 (IN-, AUXIN-, IN+, and AUXIN+, respectively)) | 1000                    | 1B    |

| HBM (All other pins)                                                                  | 1500                    | 1C    |

| FICDM                                                                                 | 750                     | 2B    |

## ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

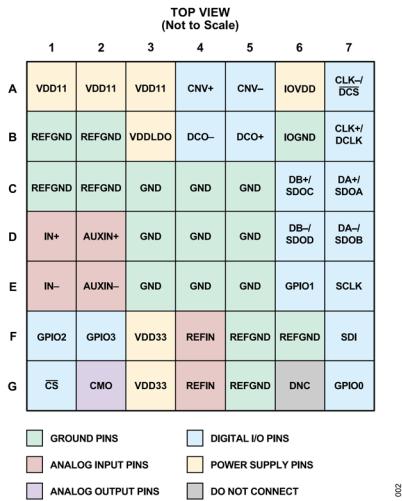

## ピン配置およびピン機能の説明

図 2. ピン配置

表 6. ピン機能の説明

| ピン番号                       | 記号         | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                                                                                                                                      |

|----------------------------|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2, A3                 | VDD11      | P                | 1.1V ADC コア電源。これらの電源ピンは、GND への 4 つの 470nF コンデンサによって内部でデカップリングされています。<br>VDDLDO (B3) に給電されると、内部 LDO 電圧レギュレータが、これらのピンで必要な 1.1V を生成します。VDDLDO が 1.4V を超えると、電圧レギュレータの電源が自動的にオンになります。<br>VDDLDO を切断したままにしておく場合は、必要な 1.1V を必ず、外部電源からこれらのピンに供給する必要があります。                                                                       |

| A4, A5                     | CNV+, CNV- | DI               | 変換開始入力。このピン・ペアは変換制御入力として機能します。変換信号の立上がりエッジで変換が開始されます。<br>これらの入力は、デフォルトで CMOS (相補型金属酸化膜半導体) モードに設定されています。このモードでは、CNV-を IOGND に接続し、変換信号を CNV+に印加します。LVDS データ・インターフェース・モードでは、変換開始入力を LVDS モードに任意に設定できます。この場合、変換信号は CNV+と CNV-に別々に適用され、外部 100Ω 終端抵抗を必ず、これらのピンの間に配置します。詳細については <a href="#">ADC 変換コントロール</a> のセクションを参照してください。 |

| A6                         | IOVDD      | P                | 1.1V デジタル・インターフェース電源レール。この電源は内部で、220nF のコンデンサによって IOGND とデカップリングされています。<br>VDDLDO (B3) に給電されると、内部 LDO 電圧レギュレータがこのピンで必要な 1.1V を生成します。VDDLDO が 1.5V を超えると、電圧レギュレータの電源が自動的にオンになります。<br>VDDLDO を切断したままにしておく場合は、必要な 1.1V を必ず、外部電源（通常はホスト・コントローラ・インターフェース電源）からこのピンに供給する必要があります。                                               |

| A7                         | CLK-/DCS   | DI               | データ・インターフェースのクロック入力 (CLK-) / データ・インターフェースのチップ・セレクト (DCS) 多機能ピン。LVDS データ・インターフェース・モード (デフォルト) では、このピンは差動データ・クロック入力の半分として機能し、このピンと CLK+ピンの間には外部 100Ω 終端抵抗が必要です。<br>SPI データ・インターフェース・モードでは、このピンはチップ・セレクト入力 (データ・インターフェース・チップ・セレクト) として機能します。                                                                               |

| B1, B2, C1, C2, F5, F6, G5 | REFGND     | P                | リファレンス・グラウンド。外部リファレンス・デカップリング・コンデンサを REFIN と REFGND の間に接続します。REFGND は必ず、低インピーダンス経路で GND に接続します。                                                                                                                                                                                                                         |

| B3                         | VDDLDO     | P                | LDO 電源レール入力。<br>この電源レールは内部で、220nF のコンデンサによって GND とデカップリングされています。2 つの 1.1V 内部 LDO 電圧レギュレータには、この入力に 1.5V~2.7V の範囲の電源を接続して給電できます。このピンがオープンである場合、内部レギュレータの電源が自動的にオフになり、VDD11 と IOVDD の両方を仕様の許容範囲内の外部電圧源に接続する必要があります。<br>VDDLDO が電圧源に接続されている場合は、VDD11 も IOVDD も、外部電圧源に接続しないでください。                                            |

## ピン配置およびピン機能の説明

表 6. ピン機能の説明（続き）

| ピン番号                                  | 記号                        | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B4, B5                                | DCO-, DCO+                | DO               | LVDS エコー・クロック出力。<br>LVDS データ・インターフェース・モード（デフォルト）では、このピン・ペアは CLK+と CLK-のバッファリングされた遅延バージョンを出力します。LVDS データ・レーン DA+およびデータ・レーン DA-（および、アクティブの場合、データ・レーン DB+およびデータ・レーン DB-）からのデータ出力は、DCO+および DCO-の立上がりエッジおよび立下がりエッジの両方に合わせてクロック・アウトされます。SPI データ・インターフェース・モード（または LVDS データ・インターフェース・モード中にエコー・クロック・モードがディスエーブルになっている場合）では、これらのピンは未接続のままにしておくことができます。                                  |

| B6                                    | I0GND                     | P                | デジタル・インターフェース電源のグラウンド・リファレンス。このピンは必ず、他のすべての GND ピンと同じグランド・プレーンに接続します。                                                                                                                                                                                                                                                                                                         |

| B7                                    | CLK+/DCLK                 | DI               | データ・インターフェースのクロック入力多機能ピン。<br>LVDS データ・インターフェース・モード（デフォルト）では、このピンは差動データ・クロック入力の半分として機能し、このピンと CLK- ピンの間には外部 100Ω 終端抵抗が必要です。<br>SPI データ・インターフェース・モードでは、このピンにシングルエンドのデータ・クロック信号を印加する必要があります。                                                                                                                                                                                     |

| C3 to C5, D3 to D5,<br>E3 to E5<br>C6 | GND<br>DB+/SDOC           | P<br>DO          | グラウンド。すべてのグラウンド・ピンは必ず、PCB GND プレーンに接続します。<br>データ・インターフェース出力多機能ピン。<br>LVDS データ・インターフェース・モード（デフォルト）では、この出力ピンは DB-と共に、オプションのセカンダリ LVDS データ・レーン B として機能します。未使用の場合は、未接続のままにします。<br>SPI データ・インターフェース・モードでは、このピンはシリアル・データ出力 C (SDOC) として機能します。SDOC は 4 レーン構成でのみ有効です。結果データは、データ・インターフェースのクロック (DCLK) の立下がりエッジで、このピンからシフト出力されます。                                                       |

| C7                                    | DA+/SDOA                  | DO               | このピンを使用しない場合は必ず、未接続のままにします。<br>データ・インターフェース出力多機能ピン。<br>LVDS データ・インターフェース・モード（デフォルト）では、この出力ピンは DA-と共にプライマリ LVDS データ・レーン A として機能します。<br>SPI データ・インターフェース・モードでは、このピンはシリアル・データ出力 A (SDOA) として機能します。SDOA は 4 レーン構成でのみ有効です。結果データは、データ・インターフェースのクロック (DCLK) の立下がりエッジで、このピンからシフト出力されます。<br>このピンを使用しない場合は必ず、未接続のままにします。                                                                |

| D1<br>D2<br>D6                        | IN+<br>AUXIN+<br>DB-/SDOD | AI<br>AI<br>DO   | 正側アナログ差動入力。<br>正側補助アナログ差動入力。<br>データ・インターフェース出力多機能ピン。<br>LVDS データ・インターフェース・モード（デフォルト）では、この出力ピンは DB+と共に、オプションのセカンダリ LVDS データ・レーン B として機能します。未使用の場合は、未接続のままにします。<br>SPI データ・インターフェース・モードでは、このピンはシリアル・データ出力 D (SDOD) として機能します。SDOD は 4 レーン構成でのみ有効です。結果データは、データ・インターフェースのクロック (DCLK) の立下がりエッジで、このピンからシフト出力されます。このピンは、CSが非アクティブのときに 4 レーン SPI モードで使用すると、高インピーダンス状態にならないことに注意してください。 |

| D7                                    | DA-/SDOB                  | DO               | このピンを使用しない場合は必ず、未接続のままにします。<br>データ・インターフェース出力<br>LVDS データ・インターフェース・モード（デフォルト）では、この出力ピンは DA+と共に、プライマリ LVDS データ・レーン A として機能します。未使用の場合は、未接続のままにします。<br>SPI データ・インターフェース・モードでは、このピンはシリアル・データ出力 B (SDOB) として機能します。これは、シングル・レーン・モードで唯一アクティブなシリアル・データ出力です。結果データは、データ・インターフェースのクロック (DCLK) の立下がりエッジで、このピンからシフト出力されます。                                                                 |

## ピン配置およびピン機能の説明

表 6. ピン機能の説明（続き）

| ピン番号   | 記号     | タイプ <sup>1</sup> | 説明                                                                               |

|--------|--------|------------------|----------------------------------------------------------------------------------|

| E1     | IN-    | AI               | 負側アナログ差動入力。                                                                      |

| E2     | AUXIN- | AI               | 負側補助アナログ差動入力。                                                                    |

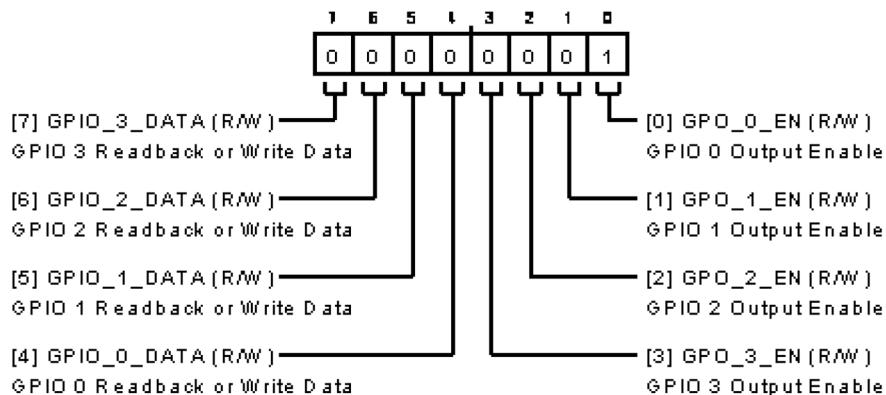

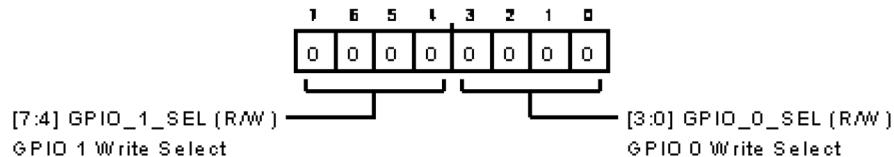

| E6     | GPIO1  | DI/O             | 汎用入出力 1 ピン。                                                                      |

| E7     | SCLK   | DI               | 設定インターフェースのシリアル・データ・クロック。このクロック入力は、デバイス・コンフィギュレーション・メモリとの間でデータをシフト入出力するために使用します。 |

| F1     | GPIO2  | DI/O             | 汎用入出力 2 ピン。                                                                      |

| F2     | GPIO3  | DI/O             | 汎用入出力 3 ピン。                                                                      |

| F3, G3 | VDD33  | P                | 3.3V 電源レール入力。これらの電源ピンは内部で、470nF のコンデンサによって GND とデカッピングされています。                    |

| F4, G4 | REFIN  | AI               | 3.0V リファレンス電圧入力。                                                                 |

| F7     | SDI    | DI               | シリアル・データ入力。設定データは、シリアル・データ・クロック SCLK の立上がりエッジで、この入力にシフト入力されます。                   |

| G1     | CS     | DI               | 設定インターフェースのチップ・セレクト入力（アクティブ・ロー）。CS入力は、設定 SPI を介してシリアル・データ転送をフレーム化します。            |

| G2     | CMO    | AO               | コモンモード電圧 ( $V_{CM}$ ) 出力。                                                        |

| G6     | DNC    | DNC              | 接続しないでください。                                                                      |

| G7     | GPIO0  | DI/O             | 汎用入出力 0 ピン。デフォルトでは設定 SPI SDO データとして設定されています。                                     |

<sup>1</sup> AI はアナログ入力、AO はアナログ出力、DI はデジタル入力、DI/O はデジタル入出力、DO はデジタル出力、P は電源です。

## 代表的な性能特性

図 3. 高速フーリエ変換 (FFT)

20MSPS、 $f_{IN} = 1\text{kHz}$ 、 $-0.5\text{d BFS}$

図 4. FFT

20MSPS、 $f_{IN} = 1\text{MHz}$ 、 $-1.0\text{d BFS}$

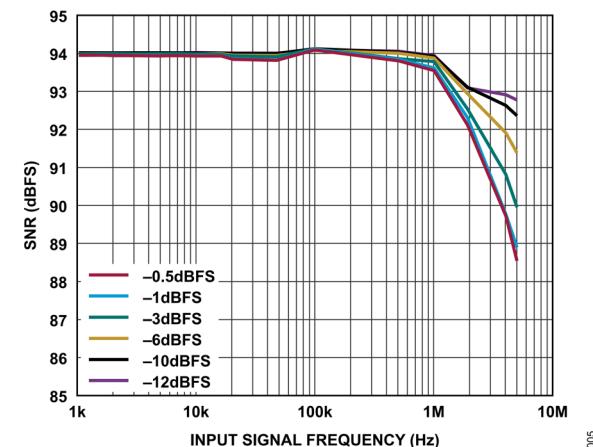

図 5. SN 比と入力信号周波数の関係（振幅 =  $-0.5\text{d BFS}$ 、 $-1\text{d BFS}$ 、 $-3\text{d BFS}$ 、 $-6\text{d BFS}$ 、 $-10\text{d BFS}$ 、 $-12\text{d BFS}$ ）

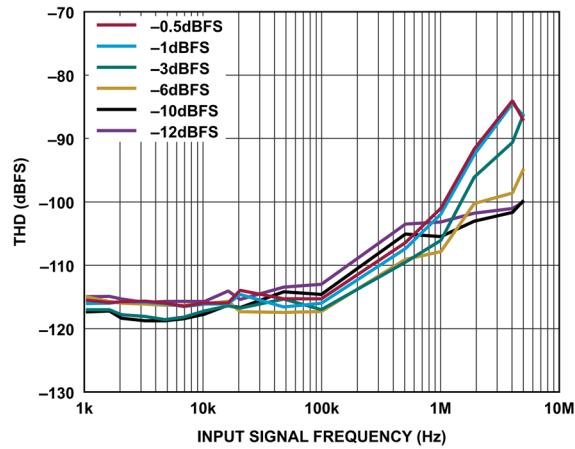

図 6. THD と入力信号周波数の関係（振幅 =  $-0.5\text{d BFS}$ 、 $-1\text{d BFS}$ 、 $-3\text{d BFS}$ 、 $-6\text{d BFS}$ 、 $-10\text{d BFS}$ 、 $-12\text{d BFS}$ ）

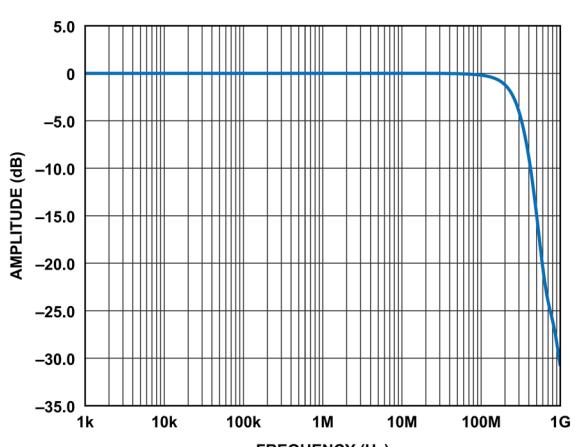

図 7. 20MSPS 時のアナログ入力小信号サンプリング帯域幅

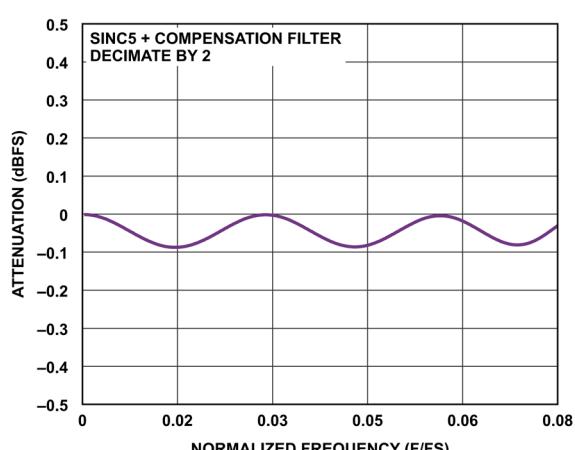

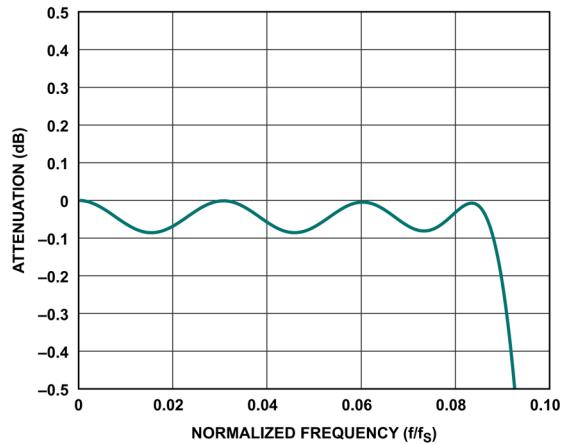

図 8. sinc5 + 補償フィルタ、バス・バンドの平坦性

## 代表的な性能特性

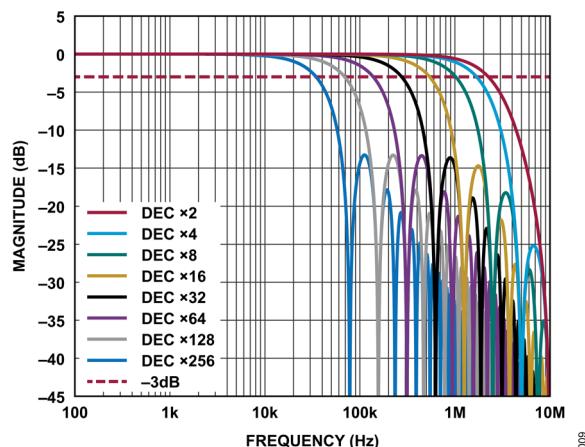

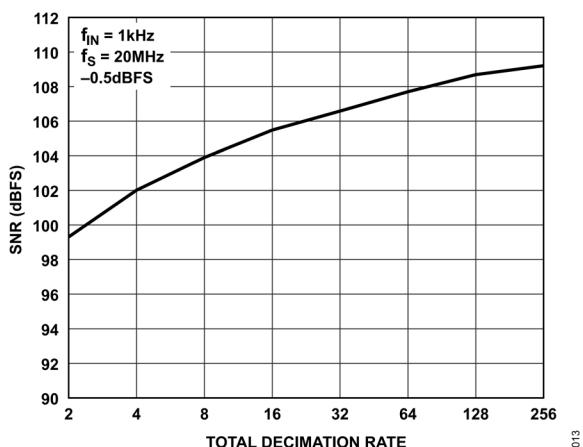

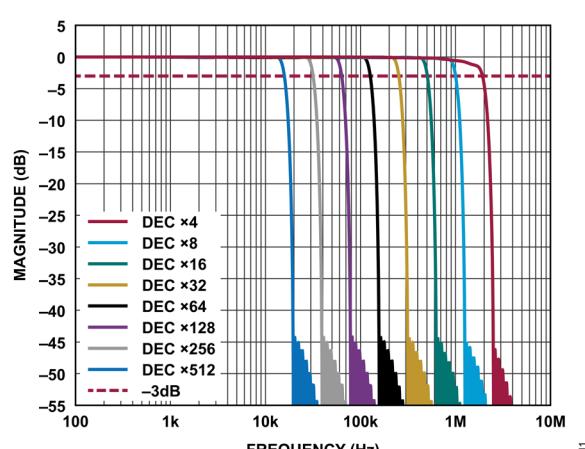

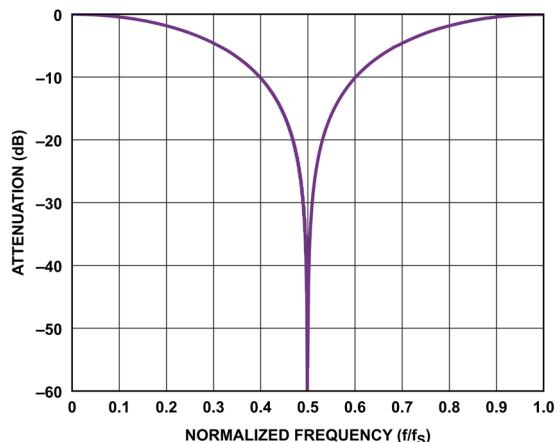

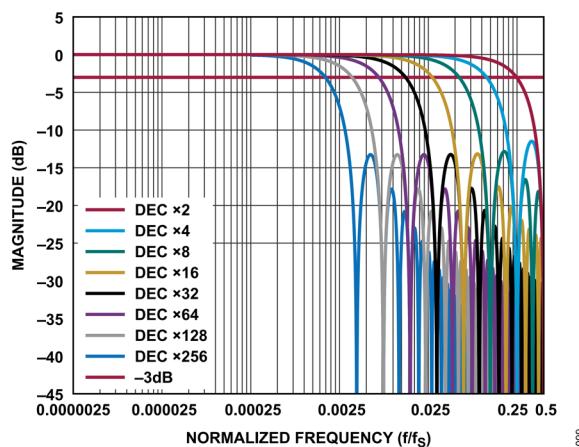

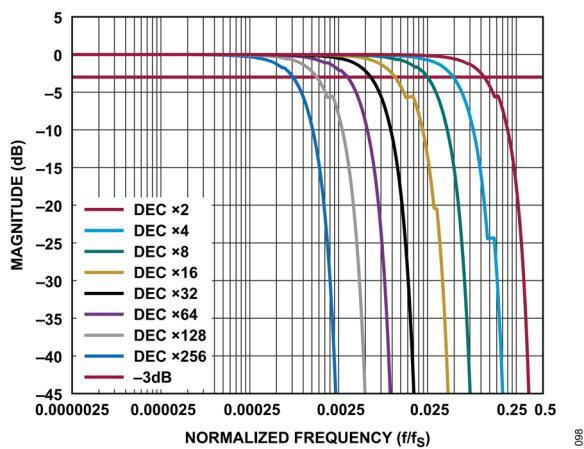

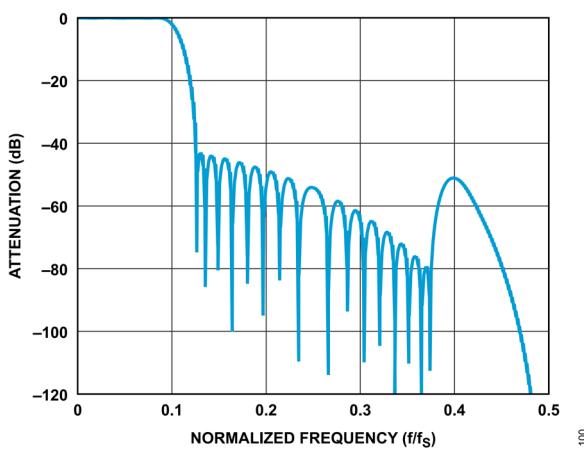

図 9. sinc1 フィルタ応答、

$f_s = 20\text{MHz}$  (DEC  $\times$ はデシメーション率)

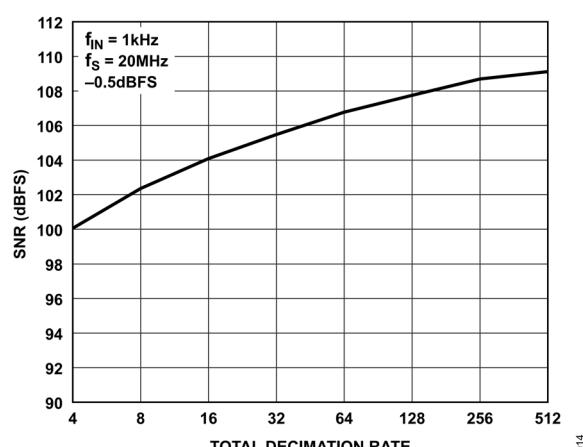

図 12. SNR と合計デシメーション率の関係、sinc1

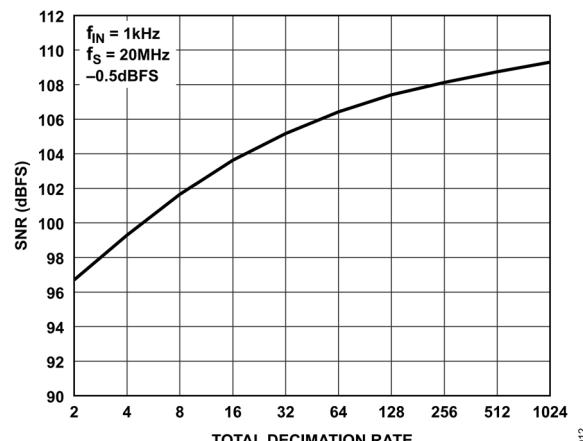

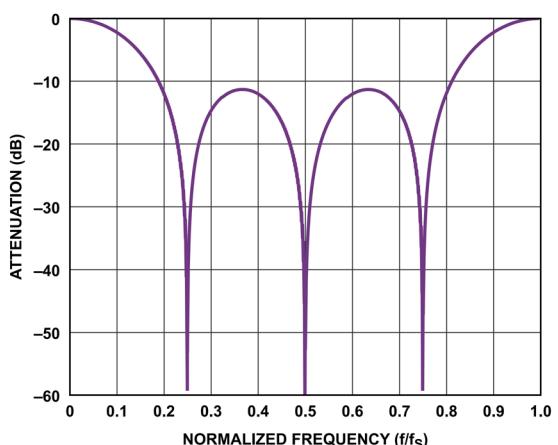

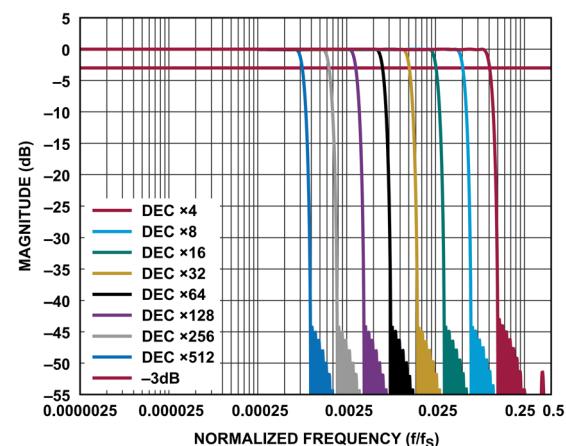

図 10. sinc5 フィルタ応答、 $f_s = 20\text{MHz}$

図 13. SNR と合計デシメーション率の関係、sinc5

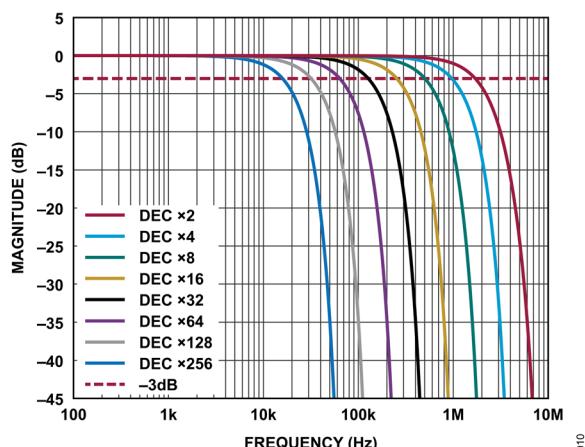

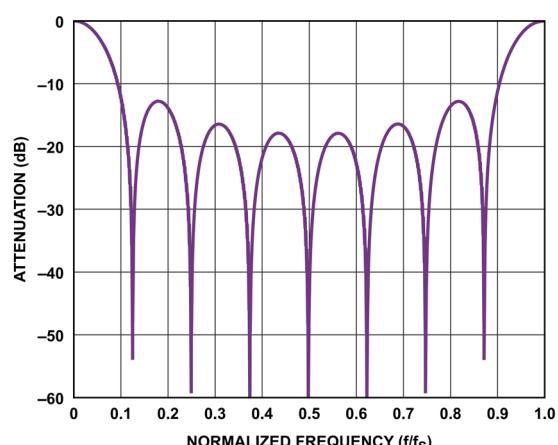

図 11. sinc5 + 補償 フィルタ応答、 $f_s = 20\text{MHz}$

図 14. SNR と合計デシメーション率の関係、sinc5 + 補償

## 代表的な性能特性

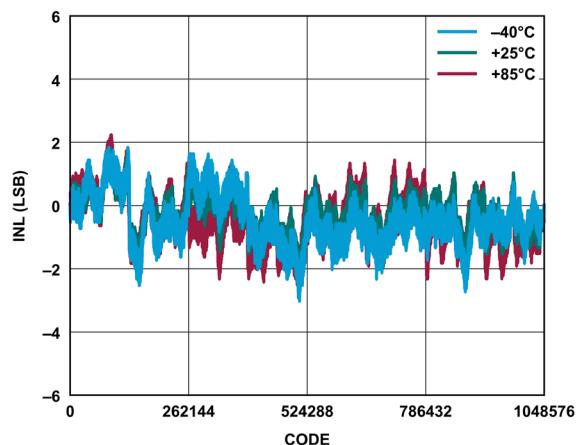

図 15. 様々な温度での INL とコードの関係、20MSPS

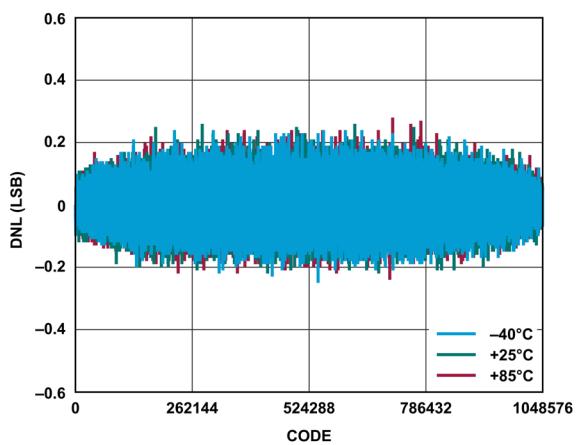

図 16. 様々な温度での DNL とコードの関係、20MSPS

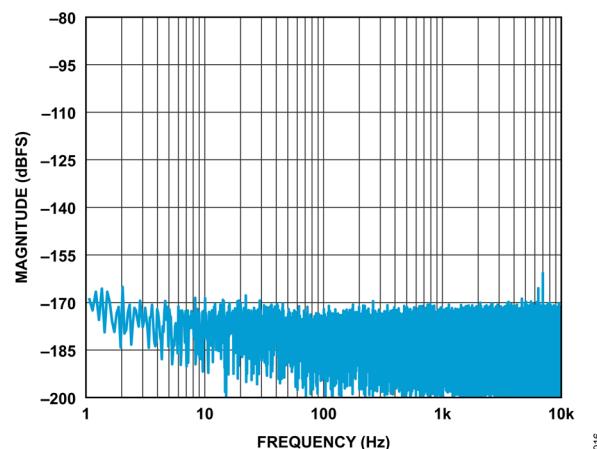

図 17. 低周波ノイズ、入力を短絡

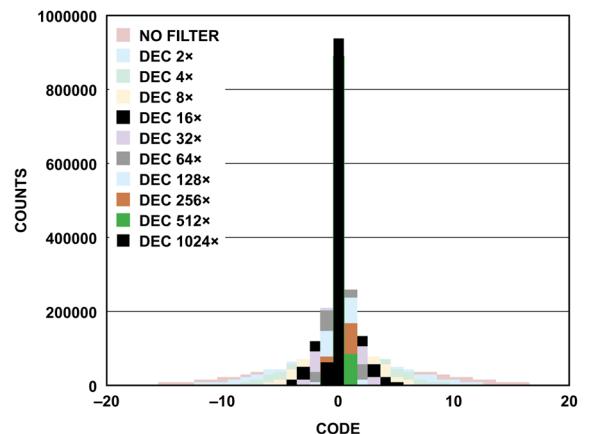

図 18. コードのヒストグラム、sinc1、フィルタなし、デシメーション率 2、4~1024

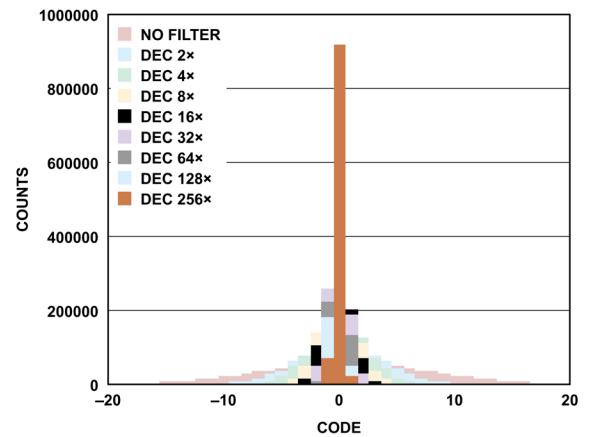

図 19. コードのヒストグラム、sinc5、フィルタなし、デシメーション率 2、4~256

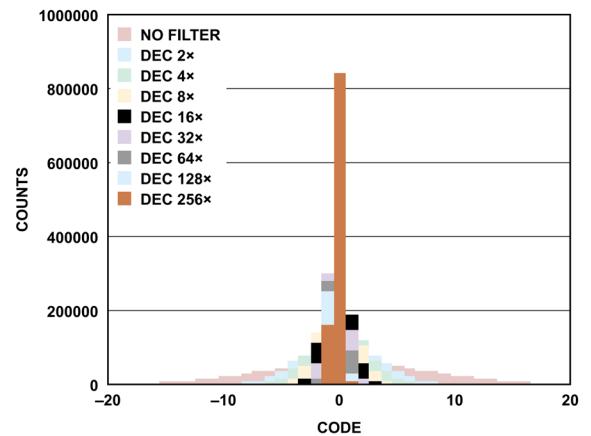

図 20. コードのヒストグラム、sinc5 + 補償、フィルタなし、デシメーション率 2、4~512

## 代表的な性能特性

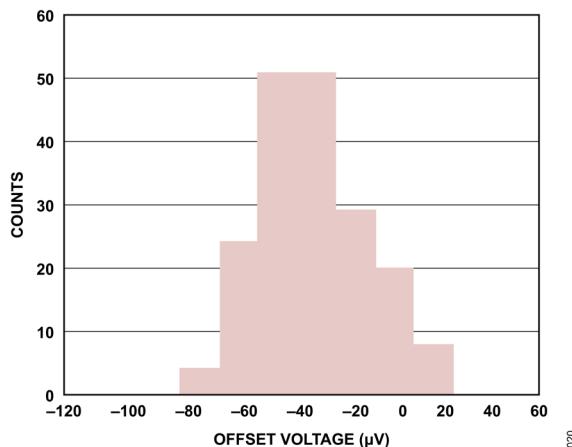

図 21. オフセット電圧のヒストグラム

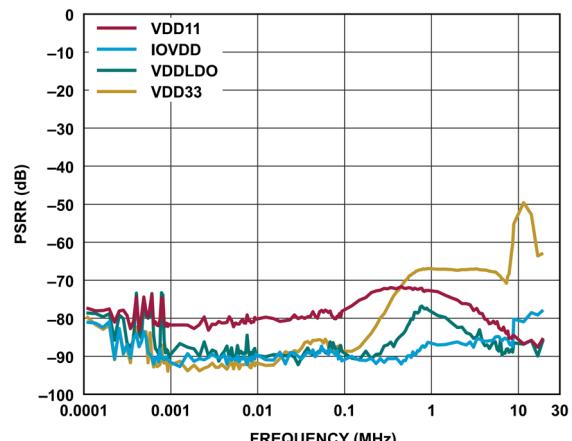

図 24. 電源電圧変動除去比（PSRR）と周波数の関係

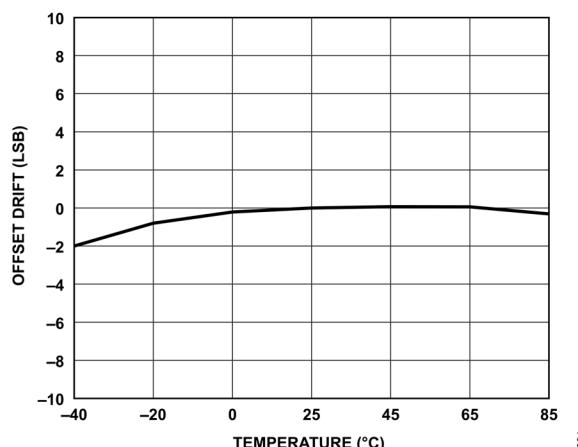

図 22. オフセット・ドリフトと温度の関係

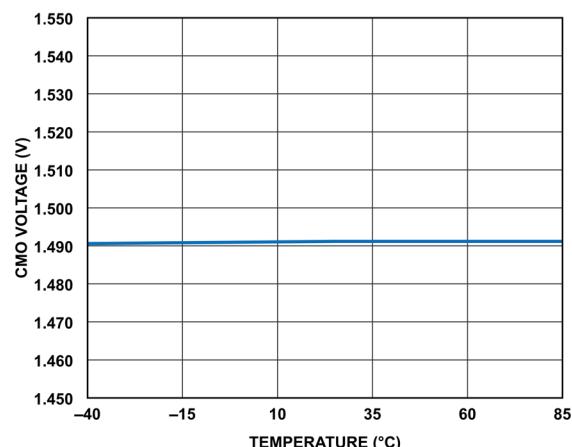

図 25. CMO 電圧と温度の関係

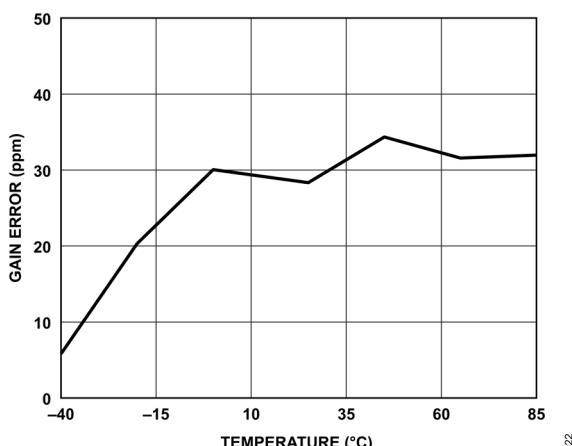

図 23. ゲイン誤差と温度の関係

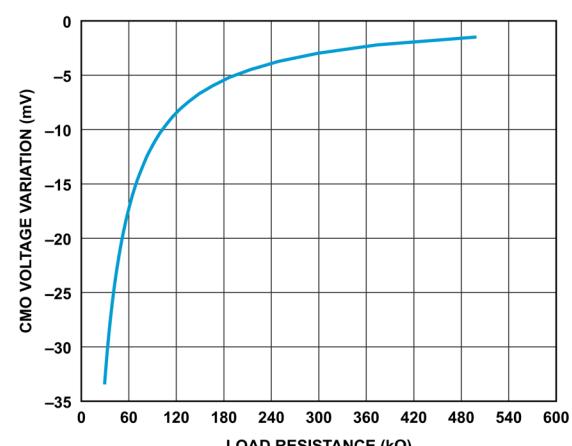

図 26. CMO 電圧変動と負荷抵抗の関係

## 代表的な性能特性

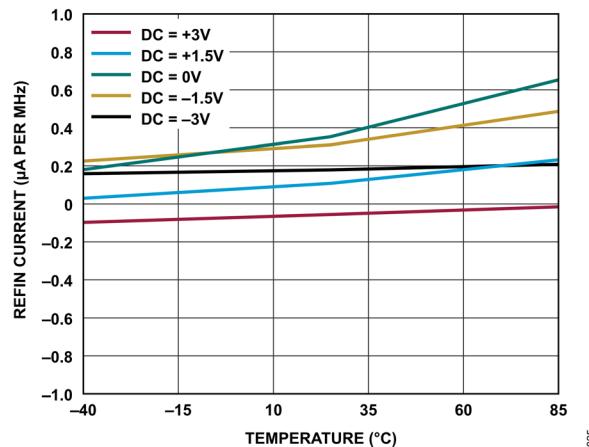

図 27. ダイナミック REFIN 電流と温度の関係

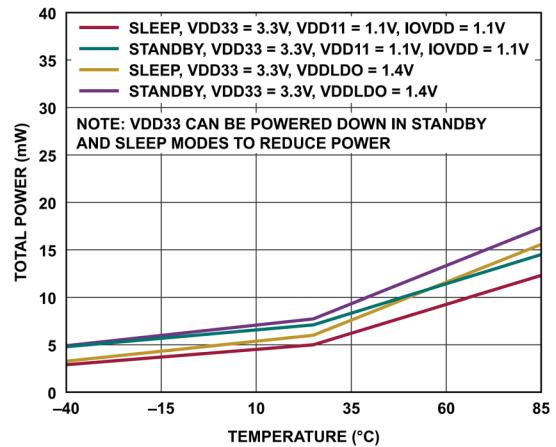

図 30. スリープ・モードおよびスタンバイ・モードでの総電力と温度の関係

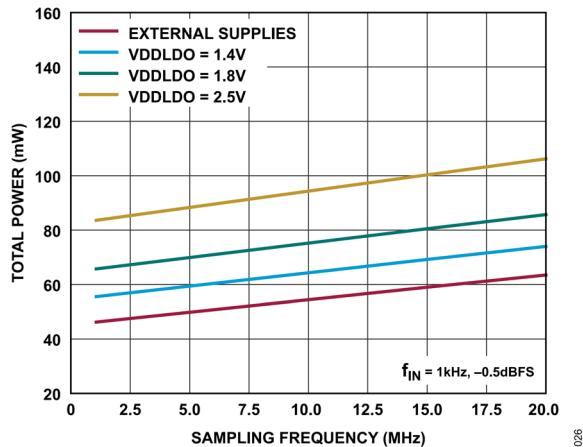

図 28. 総電力とサンプリング周波数の関係

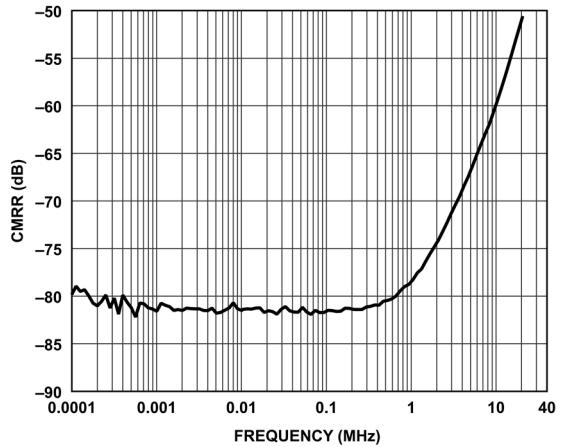

図 31. AC 同相モード除去比 (CMRR) と入力周波数の関係

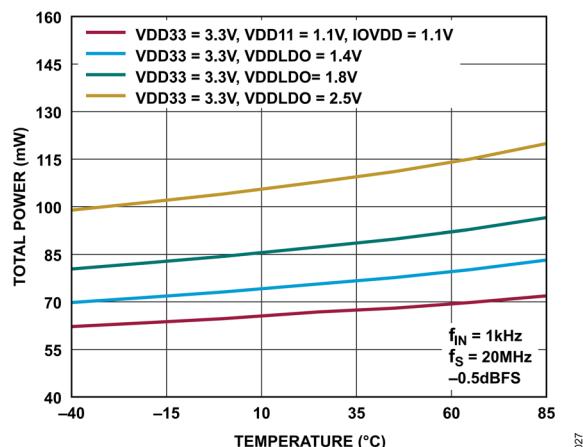

図 29. 20MSPS での総電力と温度の関係

## 用語の定義

### 積分非直線性誤差 (INL)

点の間に引かれた線からの各出力コードの偏差を指します。負側フルスケール・リファレンスは、最初のコード遷移の $\frac{1}{2}$ LSB 前に相当する入力レベルとして定義されます。正側フルスケール・リファレンスは、最後のコード遷移を $1\frac{1}{2}$ LSB 超えた入力レベルとして定義されます。偏差は、各コードの中央から直線までの距離として測定されます。

### 微分非直線性誤差 (DNL)

理想的な ADC では、コード遷移は 1 LSB 間隔で発生します。DNL は、理想的なコード幅からの任意のコードの最大偏差を表す尺度です。DNL はノー・ミッシング・コードが確保される分解能で仕様規定されます。

### ゼロ誤差

ゼロ誤差は、理想的なミッドスケール電圧 (0V) と、ミッドスケール出力コード (0LSB) が出力される印加電圧との差です。

### ゲイン誤差

ゲイン誤差は、ADC 伝達特性の傾きと理想的なコンバータの傾きとの差として仕様規定されます。理想的なデータ・コンバータでは、最初のコード遷移 (100...00 から 100...01 へ) は、公称の負側フルスケール入力 (20 ビットで $\pm 3.0V$  の範囲に対して $-2.999997V$ ) よりも $\frac{1}{2}$ LSB 多く発生し、最後のコード遷移 (011...10 から 011...11 へ) は、公称の正側フルスケール入力 (20 ビットで $\pm 3.0V$  の範囲に対して $+2.999991V$ ) よりも $1\frac{1}{2}$ LSB 少なく発生します。

### SN 比 (SNR)

SNR は、実効値ボルトで測定された基本信号振幅と、高調波および DC 成分を除くナイキスト帯域幅 ( $f < f_s/2$ ) 内の他のすべてのスペクトル成分の二乗和の平方根の比の計算値です。SNR の計算値は対数スケールに変換され、デシベル (dB) で表されます。

### 信号ノイズ + 歪み (SINAD) 比

SINAD は、実効値ボルトで測定された基本信号振幅と、高調波成分を含むが DC 成分を除くナイキスト帯域幅 ( $f < f_s/2$ ) 内の他のすべてのスペクトル成分の二乗和の平方根の比の計算値です。SINAD の計算値は対数スケールに変換され、デシベル (dB) で表されます。

### 全高調波歪み (THD)

THD は、フルスケール入力信号の実効値振幅に対する、最初の 5 つの高調波成分の振幅の実効値総和の比で、デシベル (dB) で表されます。

### スプリアスフリー・ダイナミック・レンジ (SFDR)

SFDR は、入力信号の実効値振幅とピーク・スプリアス信号振幅の比で、デシベル (dB) で表されます。

### 相互変調歪み

2 つの周波数  $f_A$  と  $f_B$  の正弦波からなる入力では、非直線性を持つ任意のアクティブ・デバイスは、 $m \times f_A$  と  $n \times f_B$  ( $m, n = 0, 1, 2, 3$  など) の和および差の周波数で歪み積を生成します。相互変調歪み項とは  $m$  も  $n$  も 0 ではない項です。例えば、2 次項には  $(f_A + f_B)$  と  $(f_A - f_B)$  があり、3 次項には  $(2f_A + f_B)$  、 $(2f_A - f_B)$  、 $(f_A + 2f_B)$  、および  $(f_A - 2f_B)$  があります。

AD4081 は、入力帯域幅の上限に近い 2 つの入力周波数を用いてテストされます。この場合、通常、2 次項は元の正弦波の周波数から遠く離れ、3 次項は入力周波数に近くなります。そのため、2 次項と 3 次項は別々に仕様規定されます。相互変調歪みの計算は THD 仕様に従います。この歪みは、基本波の和の実効値振幅に対する個々の歪み積の実効値総和の比で、デシベルで表されます。

### 電源電圧変動除去比 (PSRR)

PSRR は、周波数に対する、仕様規定された電源レールの変動に対する ADC の感度を表す尺度です。PSRR は、電源に結合された摂動信号の実効値振幅に対する実効値ボルト単位の出力コードの変化の観測値の比として計算されます。結果の比はデシベル (dB) で表されます。

## 動作原理

### 製品の概要

AD4081 は、高速、低ノイズ、低歪み、Easy Drive 機能を備えた 20 ビット逐次比較レジスタ (SAR) A/D コンバータ (ADC) です。本デバイスは、最大 20MSPS の変換レートと 77.50ns の結果出力レイテンシを実現します。パラメトリック性能、帯域幅、およびスループットにより、本製品は様々な高速のデータ・アクイジション・アプリケーションに最適です。AD4081 製品設計での革新により、データ・アクイジション・シグナル・チェーンの設計における複雑さの低減とコンポーネントの柔軟性の両方が実現されます。

コンバータ・アーキテクチャにより、全変換期間  $t_{CONV}$  にわたって入力信号の連続アクイジションが可能になり、仕様規定された分解能にセトリングするために必要な入力信号調整帯域幅が低減します。

この構造では、スイッチド・キャパシタ SAR 入力に代表的な充電キックバックに関連する非直線入力電流を低減する回路を組み込んでいます。

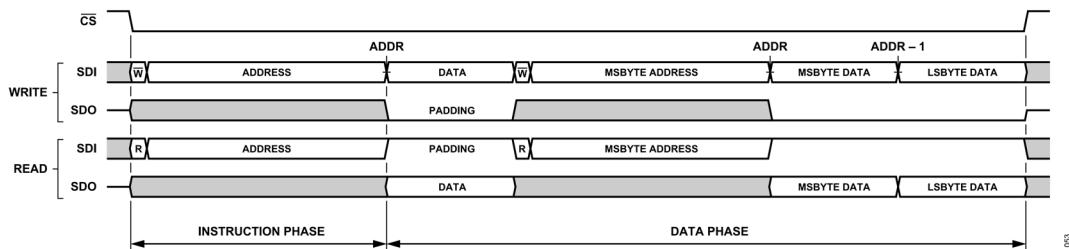

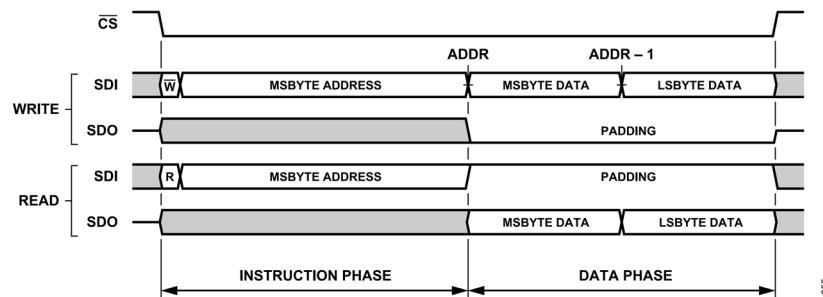

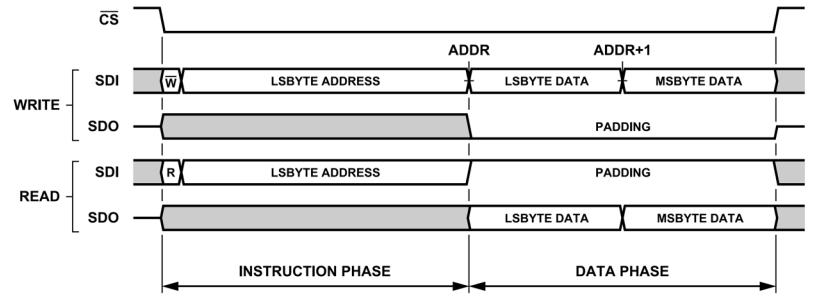

変換結果へのアクセスは、最大 200MHz のクロック・レートで動作するマルチレーン LVDS ポート、または最大 50MHz のクロック・レートで動作するマルチ出力 SPI のいずれかを介して行われます。

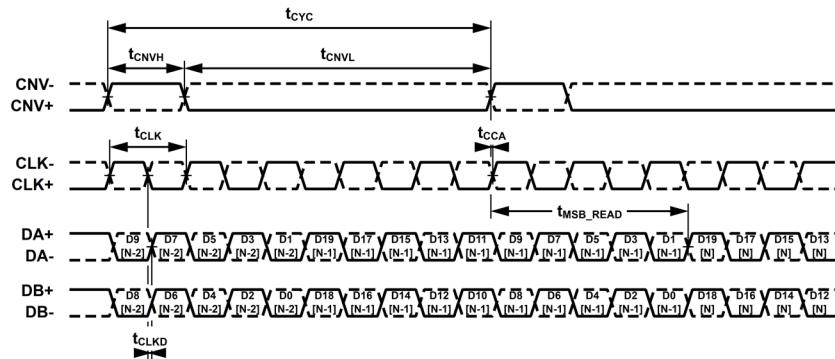

LVDS インターフェースは、1.2V～2.5V の差動信号規格と互換性があります。スループットを最大化するために、CNV+エッジと CLK+立上がりエッジが同期している限り、変換期間の全体にわたって前の変換結果の読み出しができます。LVDS インターフェースの詳細については、[LVDS データ・インターフェースの構成](#)のセクションを参照してください。

シングル・レーンまたはクワッド・レーン SPI データ・インターフェースは、CMOS レベルのインターフェースにも使用できます。このインターフェースは、設定すると、オンチップ FIFO に格納されている変換結果にアクセスするために使用されます。FIFO 動作については、[結果 FIFO](#) のセクションで説明します。

### コンバータの動作

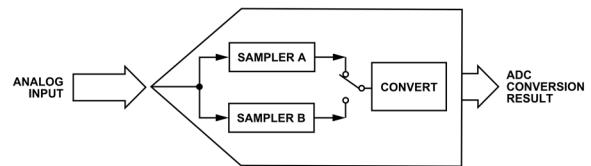

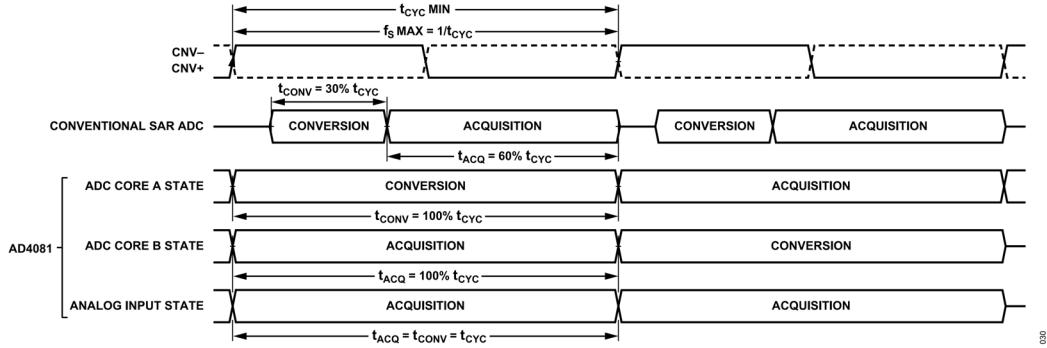

従来の SAR ADC は一般的に、アナログ入力ピンからアナログ入力電圧が取得されるアクイジション・フェーズと、それに続いて変換開始信号によって開始される変換フェーズの 2 つのフェーズで動作します。変換フェーズでは、サンプリングされたアナログ入力電圧がデジタル変換結果に変換されます。単一の ADC では、これは一般的に、1 つのサンプリング回路からの電圧の変換によって行われます。AD4081 の場合、図 32 はこのコンバータのユニークな特徴を詳細に示しています。アナログ入力は 2 つのサンプリング回路に接続され、入力はそれぞれの回路によって順番にサンプリングされます。ユーザにとって、これは追加の制御または設定が不要になり、したがって、使用法が完全に平明になります。

図 32. AD4081 SAR ADC の簡略表示

AD4081 コンバータは、一方のサンプラーから他方のサンプラーへとシームレスにシーケンスを前後させます。つまり、一方のサンプラーはアクイジション・モードになり、同時に他方のサンプラーでサンプリングされた電圧の変換が行われます。図 33 は、AD4081 タイミングが従来の SAR ADC に対して対比されることを示しており、ここで、逐次変換とアクイジション・フェーズとの間の切り替えは、入力信号のアクイジションおよびセトリングのための時間量を減少させます。サンプリング・レートが増加するにつれて（したがって、サイクル時間が減少するにつれて）、特に AD4081 によって提供されるより高いレベルの精度に対して、セトリングを可能にするためにより長いアクイジション・タイムを維持することが重要です。ドライバとノイズの帯域幅を削減するメリットの詳細については、[Easy Drive アナログ入力](#) のセクションを参照してください。

図 33. 従来の SAR と比較した変換サイクル

## 動作原理

### 伝達関数

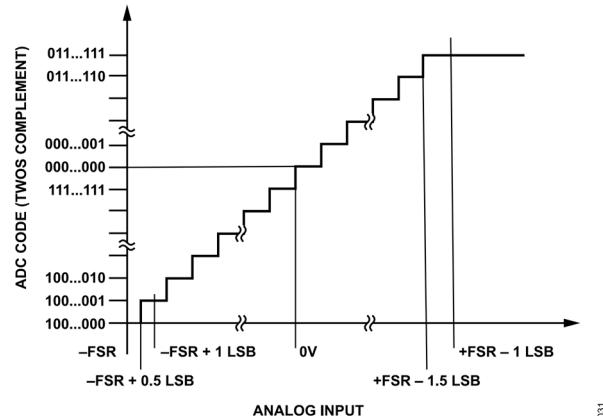

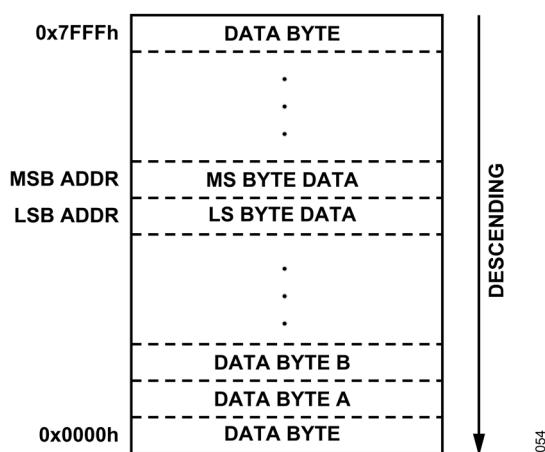

AD4081 は  $2 \times V_{REFIN}$  のフルスケール差動電圧を  $2^{20}$  のレベルにデジタル化し、 $V_{REFIN} = 3.0V$  の場合に LSB サイズは  $5.72\mu V$  になります。20 ビットでの 1LSB は約 0.95ppm になります。

表 7 に、入力電圧と差動出力コードの対応関係を示します。

図 34. 差動出力コードに対する ADC の理想的な伝達関数

(FSR はフルスケール範囲)

表 7. 入力電圧と出力コードの対応関係

| Description      | Analog Input Voltage Difference ( $IN+ - IN-$ , Volts) | Digital Output Code (Twos Complement, Hex) |

|------------------|--------------------------------------------------------|--------------------------------------------|

| FS - 1 LSB       | $+V_{REFIN} \times (1 - 1/2^{19})$                     | 0x7FFF                                     |

| Midscale + 1 LSB | $+V_{REFIN}/2^{19}$                                    | 0x0001                                     |

| Midscale         | 0                                                      | 0x0000                                     |

| Midscale - 1 LSB | $-V_{REFIN}/2^{19}$                                    | 0xFFFF                                     |

| -FS + 1 LSB      | $-V_{REFIN} \times (1 - 1/2^{19})$                     | 0x8001                                     |

| -FS              | $-V_{REFIN}$                                           | 0x8000                                     |

### Easy Drive アナログ入力

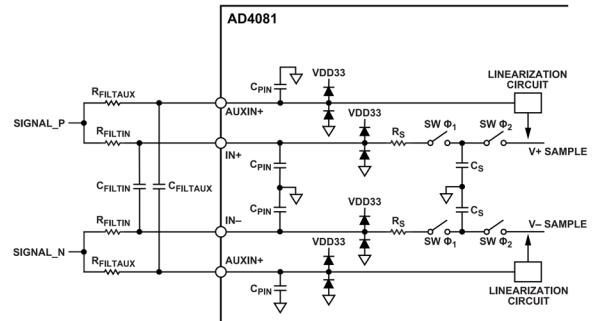

AD4081 信号入力は、完全差動入力ペア ( $IN+$  と  $IN-$ ) で構成され、それぞれが入力サンプリング・ネットワーク (直列抵抗  $R_S$  とサンプリング・コンデンサ  $C_S$ ) に接続され、サンプリング・ネットワーク直線化回路にリファレンスを提供する補助入力ペア ( $AUXIN+$  と  $AUXIN-$ ) で構成されます。図 35 に、アナログ入力の等価回路モデルを示します。

図 35. アナログ入力の等価回路モデル

このモデルでは、入力サンプリング・ネットワークを簡素化して、アクイジョン・モードの ADC のために 2 つの理想的なスイッチ、 $R_S$  および  $C_S$  で構成されました。代表値で、 $C_S$  は  $23.5\text{pF}$ 、 $R_S$  は  $26\Omega$  です。

ピン接続に関連する寄生容量  $C_{PIN}$  は、ピンとデバイスのグラウンド端子 (GND) 間のシャント・コンデンサとしてモデル化されます。この容量には、物理インターフェース、パッケージ基板内の配線、およびデバイス入力保護回路から形成される寄生容量が含まれます。 $C_{PIN}$  の代表値は  $4.5\text{pF}$  です。AD4081 の入力保護回路は、GND および VDD33 電源レールへのダイオード・クランプとしてモデル化されています。

$R_{FILTIN}$  および  $C_{FILTIN}$  からと、 $R_{FILTAUX}$  および  $C_{FILTAUX}$  から構成された外部ローパス・フィルタ (LPF) は、それぞれプライマリ経路と補助経路の帯域制限フィルタです。

$R_{FILTIN}$  と  $C_{FILTIN}$  で構成されたフィルタは、アナログ入力信号経路に单極フィルタを附加するため、アンチエイリアス・フィルタと呼ばれることがよくあります。ただし、 $C_{FILTIN}$  の機能はより複雑なため、慎重に検討してください。SAR を介する変換には、図 35 において  $C_S$  で表される内部コンデンサからの電圧のサンプリングが含まれ、これは一般的に、時間軸上の 2 つのフェーズ、 $\phi_1$  と  $\phi_2$  で動作します。第 1 フェーズ中に、 $\phi_1$  スイッチは閉じられ、 $\phi_2$  スイッチは開かれ、サンプリング・コンデンサ ( $C_S$ ) は、 $IN+$  および  $IN-$  に存在するアナログ入力電圧に充電されます。第 2 フェーズ中に、 $\phi_1$  スイッチは開かれ、 $\phi_2$  は閉じられ、ADC が電圧を  $C_S$  に変換します。

これ以外に短時間のフェーズが存在し、変換の完了後に  $C_S$  の電荷がリセットされます。このプロセスは、新たな ADC 変換ごとに繰り返されます。各変換サイクルでスイッチが閉じることにより、ADC アナログ入力ピンから  $C_S$  へ電荷が転送され、アナログ入力ピンに需要が生じます。入力ピンに印加された電圧が、内部 ADC 活動によって乱されないようにして、最高の精度で電圧変換できるようにすることが重要です。新しい変換が行われるたびに、入力に外乱すなわちキックが発生します。

## 動作原理

ADC 変換速度が速いほど、これらのキックの発生頻度は高くなります。ADC ドライバを用いると、各サンプリング・インスタンスでのキックによって乱された入力電圧が、次のサンプルが取得される前に、必要な ADC 分解能に完全にセトリングされます。ADC ドライバ・アンプには必ず、各サンプルに対して時間内に電圧をセトリングさせるために十分に広い出力帯域幅が必要です。これにより、必要とされる電圧精度（または ADC 分解能）のセトリングに十分な時間を確保するには、シグナル・チェーン設計上の制約が生じます。このため、高速な ADC には、広い帯域幅のドライバが必要になります。高分解能 ADC では、高分解能を得るために低いシグナル・チェーン・ノイズが必要です。帯域幅が広ければ、シグナル・チェーンを通って ADC に入るノイズが増加する可能性があり、従来の SAR ADC に対しては重要なシグナル・チェーンの設計上の課題となる可能性があります。ただし、AD4081 には、シグナル・チェーン設計のこれらの側面を簡素化する Easy Drive の独自の特長がいくつかあります。

このような AD4081 の特長の 1 つは、連続的な信号アクイジションです。この独自の設計により、 $t_{AQC}$  は ADC の  $t_{CYC}$  と等しくなり、その結果、AD4081 は各 ADC 変換の全期間にわたって信号アクイジション・モードになります。入力電圧には、次の変換の前に入力電圧をセトリングさせるために  $t_{CYC}$  変換時間の 100% を費やすことができますが、従来の ADC では、この時間の 60% でセトリングさせる必要があります。セトリング時間が長くなると、ドライバに必要な帯域幅が小さくなり、一般に、ドライバの所要電力が低くなります。更に、外部フィルタ ( $RFILTIN$  と  $CFILTIN$ ) は、ドライバが入力電圧をセトリングさせるのに十分な帯域幅を持つように設計する必要があるため、セトリング時間が長くなるとカットオフが低くなります。この低いカットオフのために、より多くのシグナル・チェーン・ノイズを、これらの外部フィルタを用いて入力でフィルタリングできます。

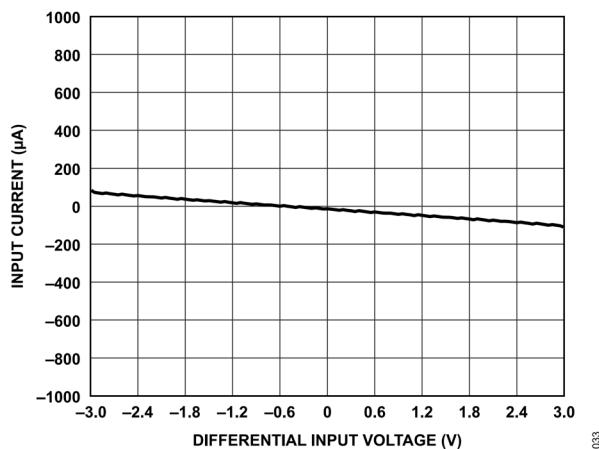

Easy Drive のもう 1 つの特長は、高度に直線化されたアナログ入力電流です。この特長により、AD4081 は、ドライバ・アンプへの負荷を軽減し、非直線入力電流が与えられたときに発生するおそれのあるドライバからの潜在的な歪みを低減します。**図 36** に、差動信号ペア ( $IN+$  および  $IN-$ ) と補助入力 ( $AUXIN+$  および  $AUXIN-$ ) の両方への代表的な入力電流を示します。

図 36. 代表値入力電流と差動入力電圧の関係

外部入力フィルタの設計では、要求される分解能に対してどのような大きさの時定数 ( $K$ ) が必要かを計算するのが通常です。

$n$  ビットのコンバータでは、 $1\text{ppm} = 2^n/1000000$  として  $1\text{ppm}$  を計算できます。必要な設定値分解能の自然対数から時定数を計算するには、例えば、20 ビット ( $n = 20$ ) の分解能の  $1\text{ppm}$  以内にセトリングしたい場合は、 $1\text{ppm}$  は  $1.048576 \text{ LSB}$ （あるいは  $2^n/1000000$ ）に相当し、以下の式で計算されます。

$$K = \ln(2^n/1\text{ppm})$$

$$K = \ln(2^n/1.048576\text{LSB}) = 13.82 \text{ time constants} \quad (1)$$

アクイジション・タイムが ADC 変換サイクルのわずか 60% である従来の ADC の場合には、[コンバータの動作](#) のセクションで説明したように、セトリングに利用できる時間が少なくなります。このような 20MSPS での ADC サンプリングに対して、ドライバは、 $50\text{ns} \times 0.6$  すなわち  $30\text{ns}$  内で安定しなければならず、 $1\text{ppm}$  内での入力電圧のセトリングも、 $30\text{ns} \div K = 2.171\text{ns}$  の時定数タウ ( $\tau$ ) または  $1/(2 \times \pi \times \tau) = 73\text{MHz}$  の帯域幅が必要になります。

ただし、AD4081 の Easy Drive 機能を使用すると、変換サイクルの 100% のアクイジション・タイムが得られ、20 ビット分解能の  $1\text{ppm}$  内にセトリングするための時定数は 13.86 のみであるということになります。しかし、AD4081 の低いアナログ入力電流およびドライバへのキックバックを低減する内部方法（サンプリング・インスタンスにおいてアナログ入力から内部サンプリング・コンデンサへ電荷が移動するときの）により、必要な時定数の数が 9.5% 減少します。したがって、20 ビット・セトリングの例では、必要な時定数の数 ( $K$ ) は、セトリングまたは歪みに影響を与えることなく、13.82 から 12.51 に減少します。

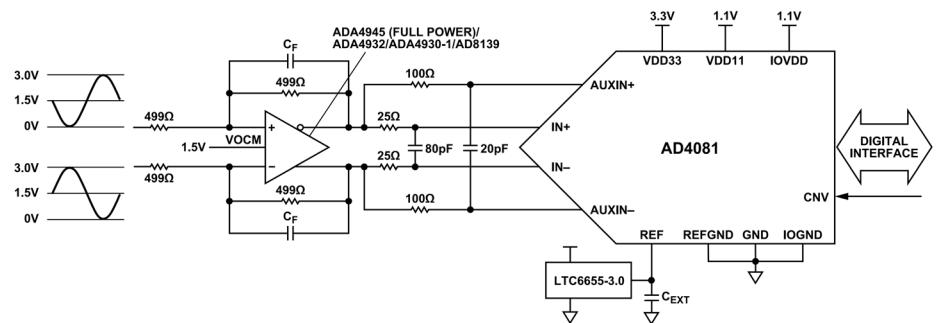

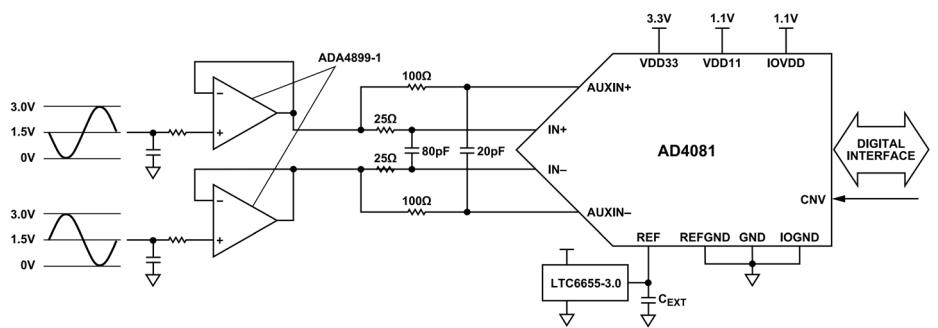

これらの Easy Drive 機能により、セトリングに必要なドライバの帯域幅が大幅に低減します。例えば、20MSPS では、 $1\text{ppm}$  以内の入力電圧のセトリングに、 $50\text{ns} \div K = 3.997\text{ns}$  の時定数タウ ( $\tau$ )、または  $1/(2 \times \pi \times \tau) = 40\text{MHz}$  の帯域幅が必要です。必要とされる帯域幅におけるこの顕著な減少により、より電力が低く帯域幅が低いドライバを使用することができ、ドライバやシグナル・チェーンのノイズをより多く除去できる低い帯域幅の入力フィルタの設計が可能になります。**表 8** は、いくつかのユース・ケース条件の例で、AD4081 で使用するいくつかのフィルタ値を示しています。

**図 35** に見られるように、Easy Drive のもう 1 つの特長は、補助信号入力経路です。この経路は、アナログ入力信号を内部直線化ブロックに供給し、このブロックは、サンプリングされた電圧に補正信号を供給します。**表 8** に推奨値を示します。補助入力のフィルタはアナログ入力と同じ帯域幅に設定され、 $RFILTAUX$  は  $RFILTIN$  の 4 倍に設定する必要があります。推奨されるフィルタ構成は、差動  $CFILTIN$  コンデンサを使用することです。したがって、 $\tau = RFILTIN \times 2 \times CFILTIN$  として各部品の値を計算します。

なお、 $RFILTIN$  の最小値は  $15\Omega$  でなければならず、 $RFILTAUX$  は最小  $5\Omega$  から  $4 \times RFILTIN$  まで設定可能です。

## 動作原理

表 8. 推奨される入力フィルタ設定

| $f_s$ (MSPS) | Target Accuracy (Bit) | Required Bandwidth (MHz) | $R_{FILTIN}$ ( $\Omega$ ) | $C_{FILTIN}$ (pF) | $R_{FILTAUX}$ ( $\Omega$ ) | $C_{FILTAUX}$ (pF) |

|--------------|-----------------------|--------------------------|---------------------------|-------------------|----------------------------|--------------------|

| 20           | 20                    | 40                       | 25                        | 82                | 100                        | 20                 |

| 20           | 18                    | 36                       | 25                        | 82                | 100                        | 20                 |

| 10           | 20                    | 20                       | 25                        | 100               | 100                        | 40                 |

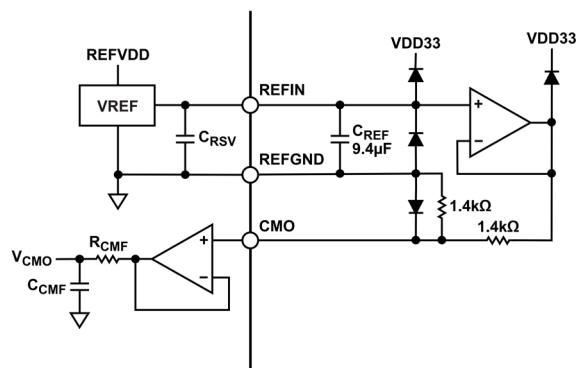

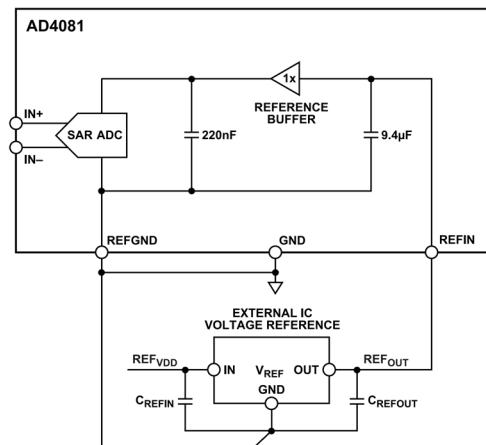

## リファレンス・バッファとコモンモード出力

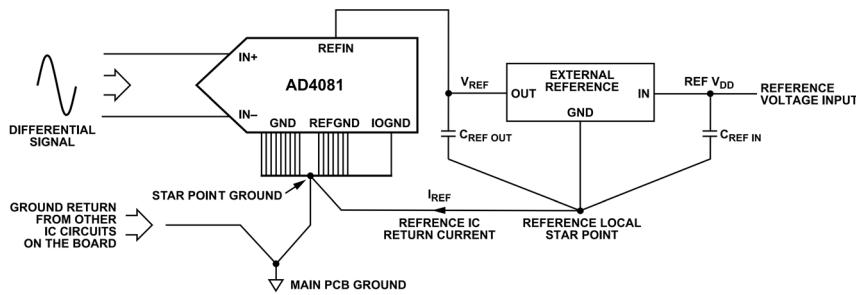

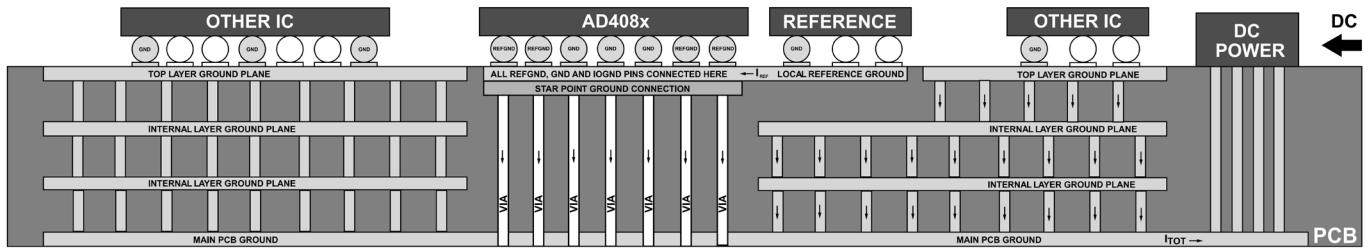

AD4081 は、リファレンス入力ピン (REFIN) に電荷貯蔵器コンデンサ ( $C_{REF}$ ) と低ドリフトのリファレンス・バッファを内蔵しているため、専用の外付け部品が不要になり、複数の AD4081 デバイスで 1 つの電圧リファレンスを共有できます。

集積コンデンサ ( $C_{REF}$ ) は  $9.4\mu F \pm 20\%$  の容量を持ち、市販の多層高誘電体 (X6S) セラミック・コンデンサで構成されます。 $C_{REF}$  は、データ・コンバータの一次電荷貯蔵器として機能します。 $C_{REF}$  などのパッケージ内蔵部品は、ソリューション全体の面積を最小限に抑え、部品の選択などの要因によって発生する潜在的なパフォーマンス・エラーを軽減し、配置や配線の課題を低減し、一般に、適切な設計が初めて得られるまでのエンジニアリング作業を削減します。

必要に応じて、REFIN ピンと REFGND ピンの間に追加の外部コンデンサ ( $C_{RSV}$ ) を配置して、充電容量とノイズ除去を改善することができます。すべての精密回路と同様に、外部リファレンス・コンデンサの配置は、PCB の同じ側のデバイス・ピンにできるだけ近づける必要があります。コンデンサとデバイス・ピンの間の配線は必ず、各配線経路における直列インピーダンスが最小になるようにします。

図 37. REFIN および CMO 内部等価回路と代表的な応用例

AD4081 は内部で  $V_{REFIN}$  の  $1/2$  のコモンモード・リファレンス電圧を生成し、CMO ピンから出力します。CMO 出力電圧の絶対誤差は、 $\pm 20mV$  以下になるように確保されています。CMO 出力は、AD4081 入力を駆動するアナログ・フロントエンド・ステージのコモンモード出力電圧を設定するために使用され、AD4081 のコモンモード入力条件が満たされていることを確認します。CMO 出力は必ず、図 37 に示すように、総出力ノイズを制限するために RC LPF でフィルタリングする必要があります ( $R_{CMF}$  と  $C_{CMF}$  を参照)。

出力は、リファレンス・バッファ出力に接続された抵抗分圧器を用いて生成されます。CMO ピンの出力インピーダンスは通常  $700\Omega$  です。CMO ピンの駆動能力は限られているため、外部負荷は必ず、慎重に検討して、過度の起動時間や絶対誤差を避ける必要があります。CMO 出力は、AD4081 を駆動する完全差動アンプの高インピーダンスのコモンモード入力に直接接続できます。ただし、先行するノイズ制限フィルタの充電時間が、アプリケーションに必要な起動時間に影響を与えないことが前提です。一般に、次のような場合に CMO バッファリングを検討します。

- ▶ AD4081 の VDD33 電源レールは、頻繁に電源が再投入されます。

- ▶ 短い始動セトリング時間が必要になります。

- ▶ CMO の外部負荷が  $30\mu A$  を超える場合 ( $R_L < 45k\Omega$ )。代表的な負荷レギュレーションについては、図 26 を参照してください。

## 電源

AD4081 の電源要件は、3.3V アナログ回路ドメイン (VDD33)、1.1V コア電源 (VDD11)、デジタル・インターフェース用の1.1V ドメイン (IOVDD) を含む、少なくとも 3 つの電源ドメインに分配されています。オプションの 4 番目の電源レール (VDDLDO) を用いて、1.1V コア (VDD11) およびインターフェース (IOVDD) レールに内部で給電するために使用される 2 つの内蔵電圧レギュレータに電力を供給できます。これら 2 つのレギュレータの各電源は、ソフトウェアによって独立してオフにできます。内部電圧レギュレータを使用する場合の詳細および設計上の考慮事項については、内部安定化電源の構成のセクションを参照してください。一方、内部レギュレータを使用しないアプリケーションの詳細については、外部生成化電源の構成のセクションを参照してください。

VDD33 電源レールの電力は、外部電源から供給する必要があります、電源シーケンスのセクションの説明に従って、1.1V 電源レールに給電した後にのみ供給する必要があります。

## 動作原理

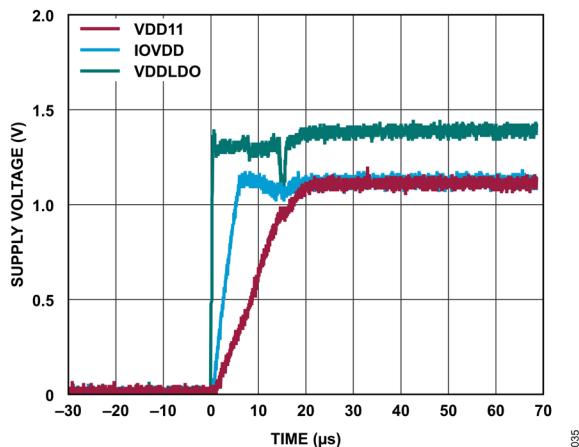

図 38. 代表的なレギュレータの起動トランジエント、コンバータがアイドリング

すべての電源領域は、多層高誘電体セラミック・コンデンサ(X6S)を用いて内部でデカッピングされているため、外部デカッピング・コンデンサが不要になります。ただし、同じ電源を共有する設計内の他の部品のバルク・デカッピング要件を理解するために、注意が必要です。AD4081 の内蔵電源デカッピング・コンデンサを、表 6 と表 9 に示します。

表 9. 内蔵電源デカッピングのまとめ

| Supply Pin | Nominal Value (μF) | Tolerance (%) | Return Path |

|------------|--------------------|---------------|-------------|

| VDD33      | 0.47               | ±10           | GND         |

| VDDLDO     | 0.22               | ±10           | GND         |

| VDD11      | 1.88 (4× 0.47)     | ±10           | GND         |

| IOVDD      | 0.22               | ±10           | LOGND       |

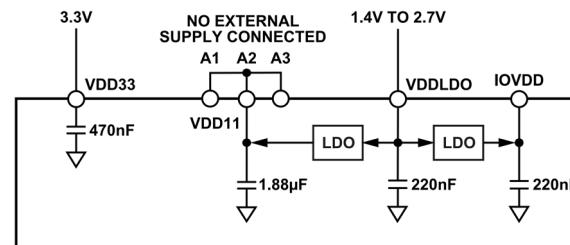

## 内部安定化電源の構成

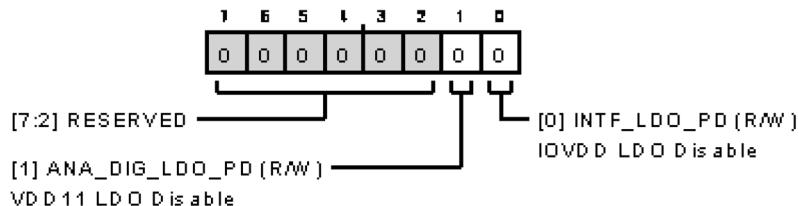

AD4081 には 2 つの内部 LDO レギュレータが含まれており、1 つは 1.1V VDD11 電源レールを生成し、もう 1 つは 1.1V IOVDD 電源レールを内部生成します。AD4081 レジスタの電源投入またはリセット時に、1.4V から 2.7V の範囲の外部電圧源が VDDLDO ピンに印加されると、両方のレギュレータが自動的に電源投入されます。レギュレータは、AD4081 の内部負荷要件を満たすように設計されているため、外部負荷の使用は不可です。省電力動作モードのセクションで説明するように、IOVDD は両方の省電力モードでディスエーブルになることに注意してください。

図 39 に、内部レギュレータを使用する場合に必要な接続を示します。図 39 に示すように、VDD11 ピン (A1, A2, A3) はまとめて短絡する必要があります。PCB のデバイス側の太いパターーンまたは多角形を用いて、物理的設計でこの接続を実装し、配線インピーダンスを最小限に抑えることを推奨します。VDD33 レールには、外部 3.3V 電源が供給されます。この電源は、省電力モードを使用しているときに取り外すことができます。この電源が取り外されると、アナログ回路のみがリセット状態に保持され、設定レジスタの内容は影響を受けません。各電源レールに適用可能な入力電圧の許容差については、表 1 を参照してください。

図 39. 内部安定化 (1.1V) 電源の構成

内部安定化電源の構成は、外部レギュレータを排除する能力に有利な面積が制約された用途での使用に理想的です。ただし、この構成では、内部電源レギュレーションにより消費電力が増加することに注意してください。

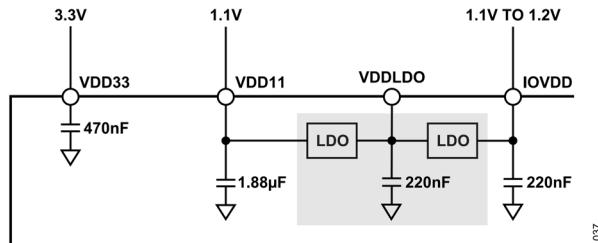

## 外部生成化電源の構成

外部生成化電源を使用するシステムでは、VDDLDO は未接続のままにしておく必要があります。VDDLDO が接続されていない場合、VDD11 に電力を供給する内部 LDO と IOVDD に電力を供給する内部 LDO の両方が自動的にディスエーブルになります。VDD11 は外部生成 1.1V 電源レールに接続する必要があります。IOVDD は外部生成 1.1V~1.2V 電源レールに接続する必要があります。VDD11 が存在しない場合、デバイスはパワーオン・リセット (POR) 状態に保持され、電源が再確立された後、すべての AD4081 レジスタはデフォルト状態にリセットされることに留意してください。POR 回路の詳細については、パワーオン・リセット (POR) モニタのセクションを参照してください。

## 動作原理

VDD33 レールには、外部 3.3V 電源が供給されます。VDD33 電源を取り外して電力を更に削減できます（省電力動作モードのセクションを参照）。アナログ回路のみがリセット状態に保持され、レジスタの内容は影響を受けません。各電源レールに適用可能な入力電圧の許容差については、表 1 を参照してください。

図 40 の例に示されるように、外部電圧源は、VDD11 および IOVDD ピンに印加されます。

図 40. 外部電圧源の構成

## パワーオン・リセット (POR) モニタ

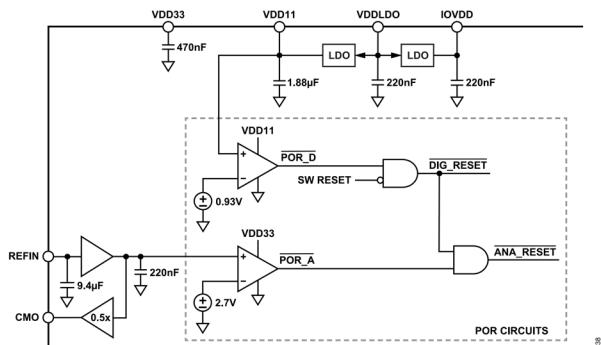

AD4081 電源モニタリング回路は、電源の状態が仕様規定された動作限界を超えると、コンバータ機能を抑制し、コンフィギュレーション・メモリをリセットします。この機能により、各デバイスが電源投入後に確定的な状態になることが確保されます。電源投入機能は、2 つの独立した電圧モニタで構成されています。最初のモニタはコアの 1.1V 電源を測定し、2 番目のモニタはリファレンス入力ピン (REFIN) の電圧を測定します。各モニタには、図 41 に示すように、アナログおよびデジタル・ブロック・リセットのデカップリングに使用される独自のコンペレータ出力があります。

図 41. POR 回路の簡略図

コア VDD (1.1V) 電源モニタは VDD11 電源電圧を 0.93V のリセット・スレッショルドと比較します。電源電圧がこのスレッショルドより低くなると、リセット信号 POR\_D がアサートされます。デジタル論理リセット信号 DIG\_RESET は、POR\_D 信号と SPI ソフトウェア・リセット機能の補数の論理組み合わせ（論理積）として定義されます。POR\_D 信号 (VDD11 < 0.93V) または SW RESET 信号のいずれかがアサートされると、内部デジタル回路はリセット状態に保持されます。クリアすると、設定レジスタの内容が工場出荷時のデフォルト設定値に復元されます。

リファレンス・モニタは REFIN の入力電圧を 2.7V のプリセット・スレッショルドと比較します。図 41 に図示するように、リファレンス・モニタ回路の電源は VDD33 電源から供給されます。しかし、リファレンス電圧が 2.6V を下回ると、デバイスは変換結果のデータの出力を停止することに注意することが重要です。変換プロセスを再開するためには、リファレンス電圧を 2.87V より高くすることが必要です。モニタ回路の正常な動作のためには、リファレンス電源をイネーブルする前に、規定の許容範囲である  $3.3V \pm 5\%$  の VDD33 電源を AD4081 に供給する必要があります。デバイスが規定の電源条件で動作している前提で、リファレンス電圧が 2.7V より低くなると、内部リセット信号の POR\_A がアサートされます。POR\_A 信号と DIG\_RESET 信号の組み合わせ（論理積）によってアナログ信号ブロックのリセット (ANA\_RESET) が発生し、ADC コア、ADC タイマー、リファレンス・バッファなどに作用します。このリセット信号がアサートされると、アナログ・ブロックが非アクティブ状態になり、コンバータの機能がディスエーブルされます。このイベントは、デバイス・ステータス・レジスタ (アドレス 0x14) の POR\_ANA\_FLAG ビットの値 1 で示されます。イベント検出の状態は、ロジック 1 が POR\_ANA\_FLAG ビットに書き込まれて検出状態がクリアされるまで持続します。

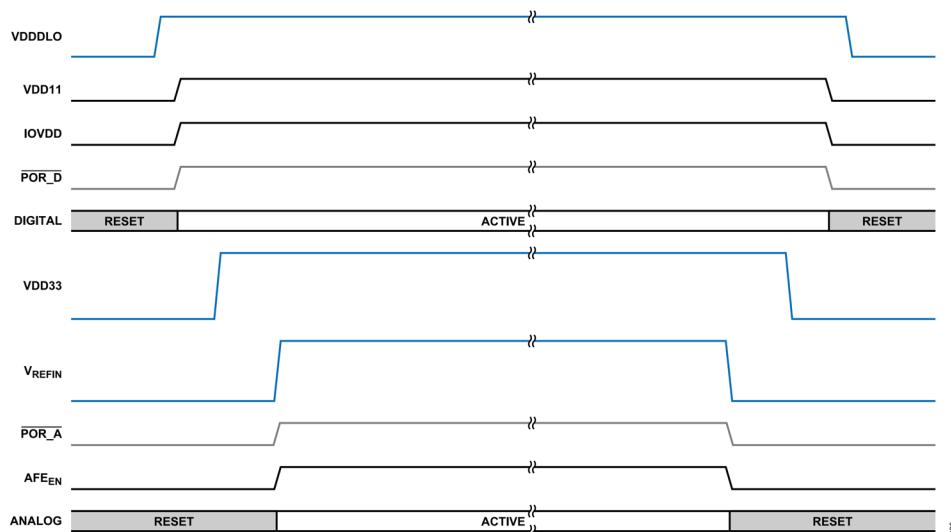

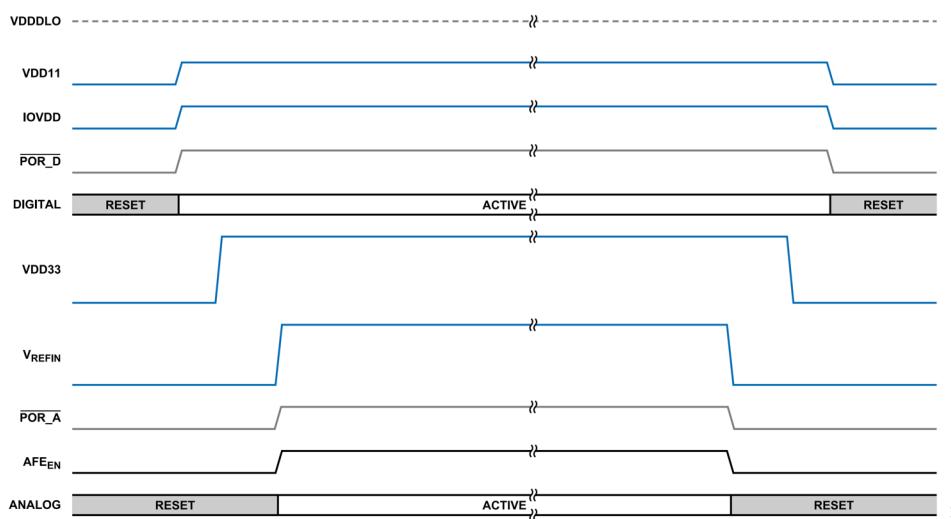

## 電源シーケンス

表 10 は、1.1V 電源レール (IOVDD および VDD11) の内部および外部生成の推奨電源シーケンスを示しています。両方の方法を図 42 と図 43 に示しており、REFIN 電圧を含め、AD4081 に供給すべき電源を青で示しています。いずれの場合も、AD4081 では、電源を電圧の昇順で供給する必要があります。また、アナログ入力 (IN+ および IN-) およびリファレンス入力 (REFIN) には、VDD33 電源と同時に、またはその直後に電圧が印加されるように設計する必要があります。パワーアップ時に REFIN リファレンス電圧が供給されなければ、ADC の出力に ADC 変換が出来ず、REFIN 電圧が供給されるまではその状態が続きます。データ・インターフェース・テスト機能のセクションに記載のテスト・パターンは、パワーアップ時に電圧リファレンスが供給されない前述の場合には動作しないことに注意してください。ただし、リファレンス電圧がパワーアップ時に供給された後に停止された場合には、テスト・パターンは動作し、正しいデータを出力します。パワーオン・リセット (POR) モニタのセクションで説明したように、リファレンス入力ピンの電圧は、VDD33 が仕様規定された電源の許容範囲内にある場合にのみ適用して、望ましくない動作を回避する必要があります。したがって、選択された電圧リファレンスがイネーブル・ピンを提供しない場合、VDD33 の後に電源が投入されるように、リファレンス回路を設計することを強く推奨します。リセットまたはパワーオン・リセットの後には、デバイスにアクセスするまでに 300μs が必要です。これはデバイスの初期化手順の完了を待つためです。この条件が満たされなければ、INTERFACE\_STATUS\_A (0x11) の NOT\_READY\_ERR ビットがアサートされます。

設定 SPI 入力、CS、SCLK、および SDI は、VDD33 電源レールへのクランプで保護され、入力は IOVDD より大きく振れることができます。このアーキテクチャ上の決定の結果として、VDD33 が IOVDD - 0.3V より大きくなるまで、SPI 入力をグラウンドに駆動するか、あるいはフローティング状態のままにしておく必要があります。あるいは、VDD33 電源は、ADP199 のよ

## 動作原理

うな、電源が IOVDD – 0.3V 未満のときにスイッチが開くように構成された直列電源スイッチを用いてデバイスに接続することができ、デジタル入力を経由する VDD33 までの寄生電流経路が排除されます。

表 10. 推奨電源シーケンス

| 1.1 V Supplies (IOVDD and VDD11) Source | Supply Sequence       |

|-----------------------------------------|-----------------------|

| Internally Generated                    | 1. VDDLD0<br>2. VDD33 |

表 10. 推奨電源シーケンス（続き）

| 1.1 V Supplies (IOVDD and VDD11) Source | Supply Sequence                                                                                                                 |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Externally Generated                    | 3. Digital inputs<br>4. Input drive, reference<br>1. IOVDD, VDD11<br>2. VDD33<br>3. Digital inputs<br>4. Input drive, reference |

アプリケーション回路の電源を切断するには、表 10 に示す電源投入シーケンスを逆にする必要があります。

図 42. 電源シーケンス、内部生成化 IOVDD、VDD11

図 43. 電源シーケンス、外部生成化 IOVDD、VDD11

## 動作原理

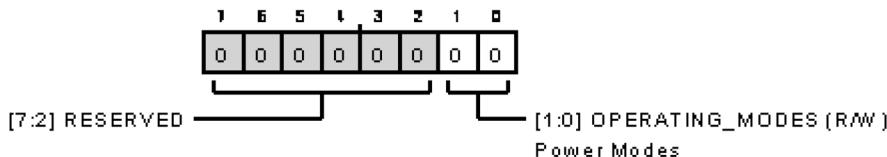

### 省電力動作モード

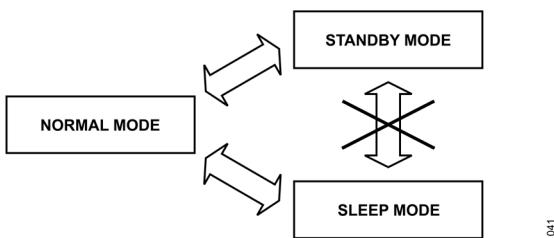

AD4081 の動作モードは、デバイス設定レジスタの OPERATING\_MODES ビットによって制御されます（[デバイス設定レジスタ](#)のセクションを参照、アドレス（0x02））。電源投入時およびリセット後のデフォルトは、ノーマル・モード（OPERATING\_MODES = 00）です。表 11 は、すべての動作モードを説明し、図 44 は、これらのモード間で許容される遷移を示します。2 つの省電力モード（スタンバイ・モードとスリープ・モード）間の直接の遷移は不可であることに注意してください。

電力モードを設定する前に、すべての変換とデータ・インターフェースのクロッキングを停止することが重要です。

スタンバイ・モードまたはスリープ・モードの場合は、VDD33 電源を取り外して消費電力を削減できます。いずれかの省電力モードを終了するには、SPI 設定インターフェース・コマンドを発行する前にこの電源を再確立する必要があります。

図 44. 動作モードの遷移

ノーマル・モードから 2 つの省電力モードのいずれかに遷移するには、デバイス設定レジスタの OPERATING\_MODES ビットに必要な値を書き込みます（[デバイス設定レジスタ](#)のセクションを参照）。SPI 設定インターフェースの動作は省電力モードの影響を受けないため（[SPI 設定インターフェース](#)のセクションを参照）、ウェイクアップ（つまり、ノーマル・モードへの遷移）も同様の方法で実行されます。通常の変換に迅速に戻りたい場合には、電力を節約するためにスタンバイ・モードを選択できます。スリープ・モードは、ノーマル・モードへの復帰に時間がかかる低電力状態です。スタンバイ・モードとスリープ・モードはいずれも、結果 FIFO（[結果 FIFO](#) のセクションを参照）と併用すると特に便利です。これにより、選択された省電力モードにある間に、以前に保存された変換データに FIFO からアクセスできます。

スタンバイ・モードとスリープ・モードのどちらでも、消費電力を削減するために内部 IOVDD LDO レギュレータの電源が切れます。ユーザが外部から IOVDD を供給していない場合、すべての IOVDD ドメイン入力および出力がディスエーブルになります（すべての GPIOx およびすべての LVDS データ・インターフェース（LVDS データ・インターフェースのセクションを参照）および SPI データ・インターフェース（SPI データ・インターフェースのセクションを参照）の信号がディスエーブルになります）。この特定の状態では、AD4081 SPI 設定に書き込んで、デバイス設定レジスタ（[デバイス設定レジスタ](#)のセクションを参照）の OPERATING\_MODES ビットへの書き込みによってノーマル・モードに戻るコマンドを発行でき、あるいは、ソフトウェア・リセット（[ソフトウェア・リセット](#) のセクションを参照）を発行できます。GPIOx がディスエーブルになっているため、SPI 設定インターフェース・バス上で読み出しがアクティビティを実行することはできません。

IOVDD が外部から供給され、デバイスがスタンバイ・モードまたはスリープ・モードになると、LVDS データ・インターフェースはディスエーブルになります。ただし、すべての GPIOx、SPI データ・インターフェース、および SPI 設定インターフェース・ピンはイネーブルのままで影響を受けません。仕様規定された範囲内で IOVDD に外部から電力が供給されている間、結果 FIFO に格納されている以前に取得されたデータは、スタンバイ・モードまたはスリープ・モードのいずれかでアクセスできます。

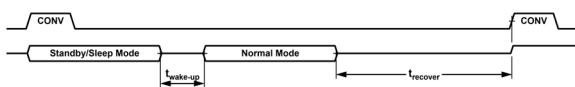

表 11 は、各モードに関連するウェイクアップ時間も示しています。スリープ・モードからのウェイクアップ時間は、スタンバイ・モードの場合よりも大幅に長くなります。これは、内部リファレンス・バッファとコモンモード・バッファが再びイネーブルになり、内部コンデンサに電荷を補充するための時間が必要になるためです。ノーマル・モードに戻るときは、最初の変換開始パルスを印加する前に、仕様規定されたウェイクアップ時間を満たす必要があります。この仕様規定時間は、選択された省電力モードを終了する SPI コマンドがデバイス設定レジスタ（[デバイス設定レジスタ](#)のセクションを参照）に書き込まれてから OPERATING\_MODES ビットが更新されるまでにかかる時間です。

省電力動作モードのいずれかで消費電力を最小限にするためには、ADC データ・インターフェース設定 B レジスタの LVDS\_SELF\_CLK\_MODE（[データ・インターフェース設定 B レジスタ](#)のセクションを参照）をイネーブルして、LVDS DCO トランスマッタをパワーダウンします。

表 11. 省電力動作モード

| 動作モード   | OPERATING_MODES ビット値 | 説明         | 影響                                                                                                                                                                                                                                                                                  | ウェイクアップ時間（ノーマル・モードまでの最大時間） |

|---------|----------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Normal  | 0b00                 | 通常動作モード    | 通常動作。                                                                                                                                                                                                                                                                               | Not applicable             |

| Standby | 0b10                 | スタンバイ動作モード | 内部 IOVDD LDO レギュレータがディスエーブルです。<br>IOVDD が外部から供給されていない場合、すべての GPIOx およびすべての LVDS データ・インターフェースおよび SPI データ・インターフェース信号がディスエーブルになります。SPI 設定インターフェースの場合のみ、デバイス設定レジスタ（ <a href="#">デバイス設定レジスタ</a> のセクションを参照）とインターフェース設定 A レジスタ（ <a href="#">インターフェース設定 A レジスタ</a> のセクションを参照）への書き込みが許可されます。 | 100μs                      |

## 動作原理

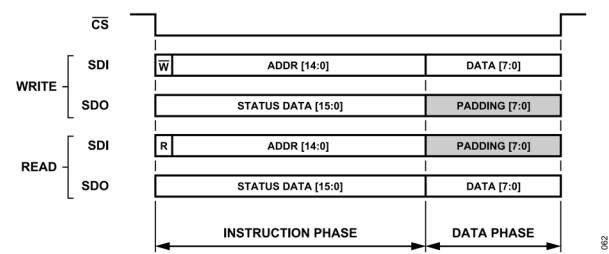

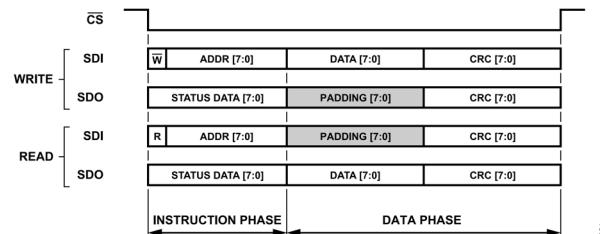

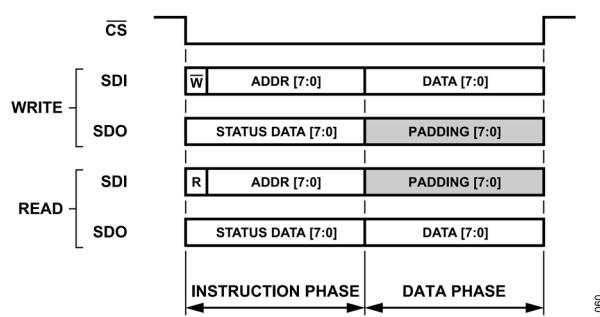

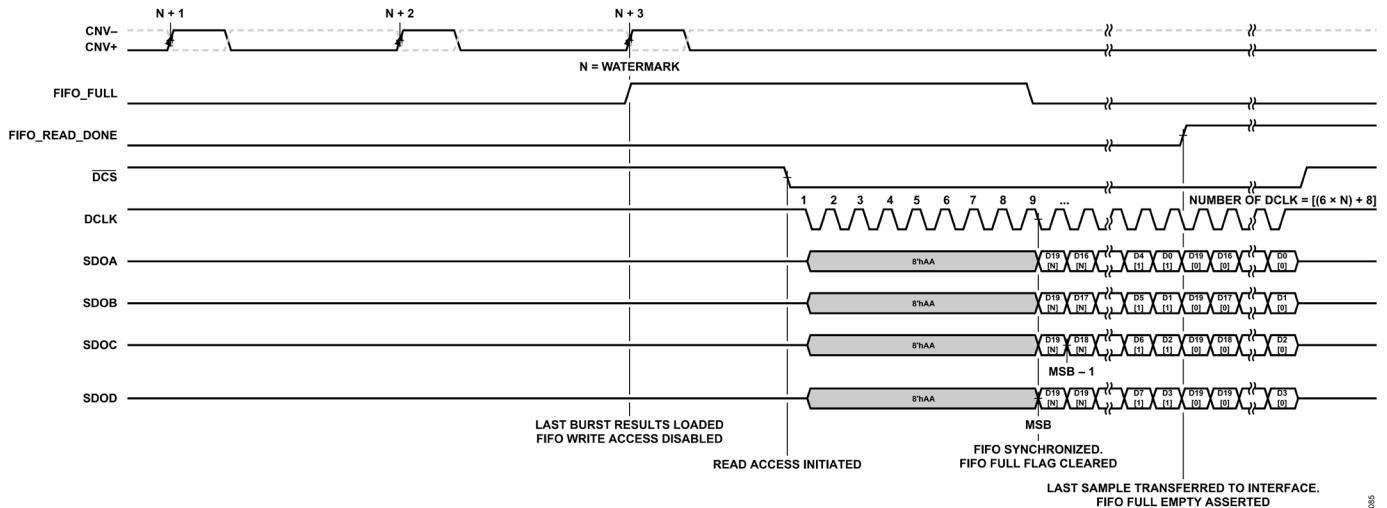

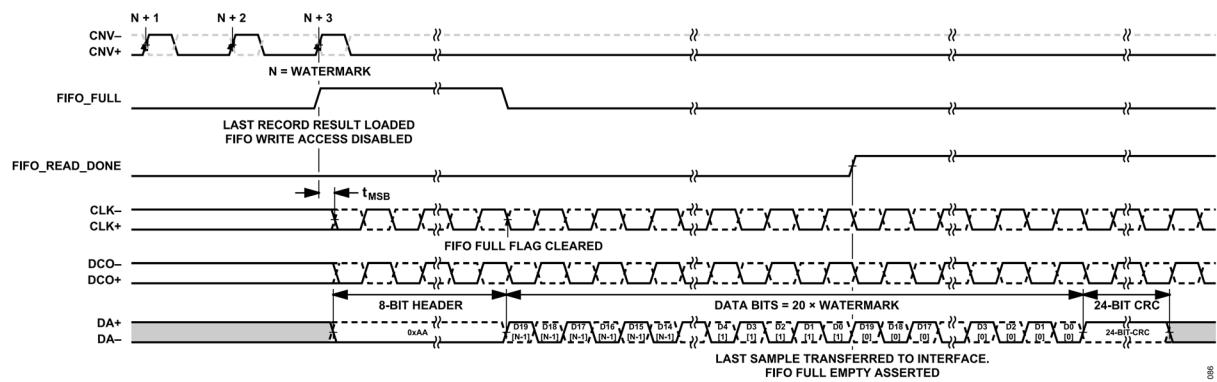

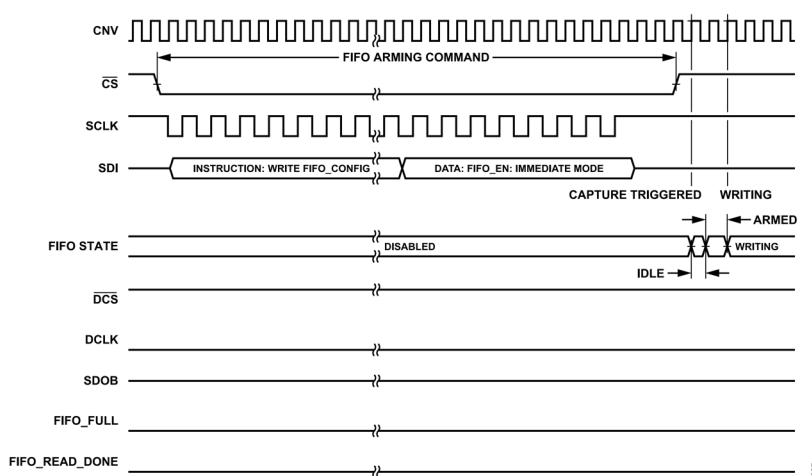

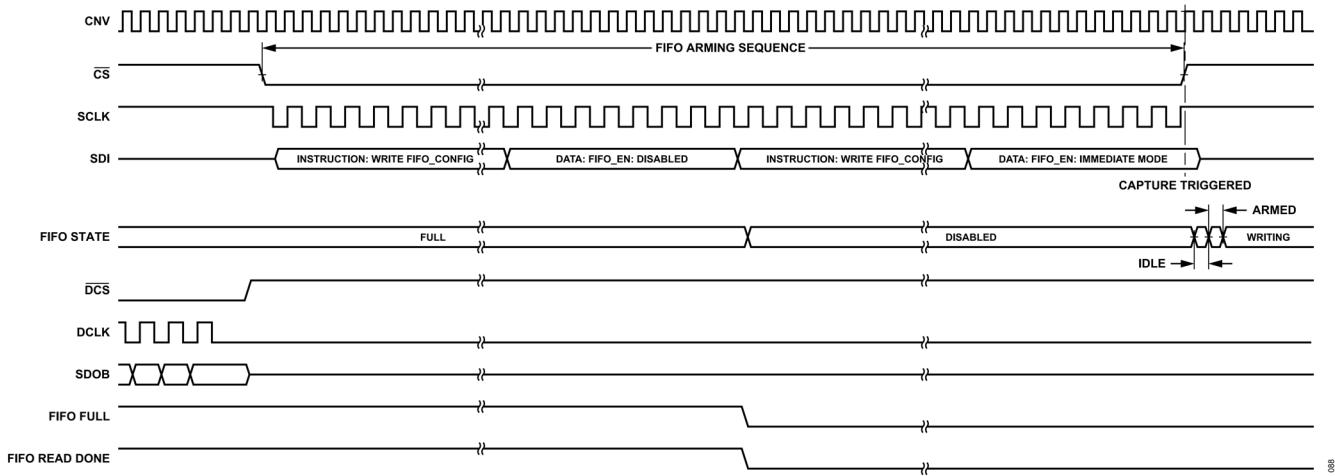

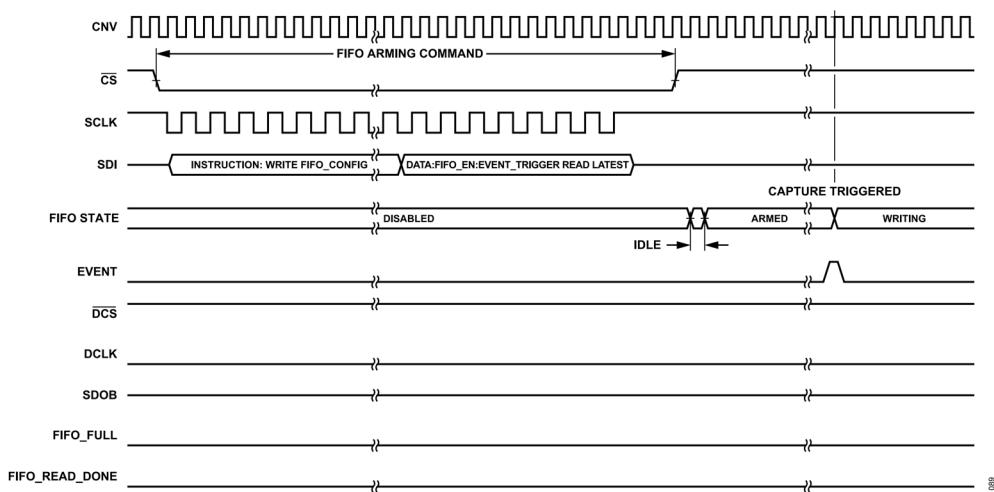

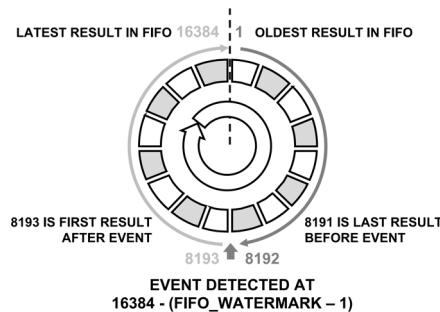

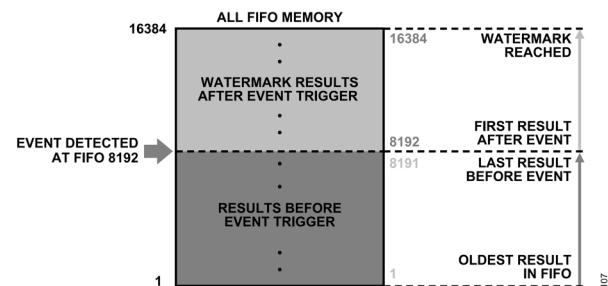

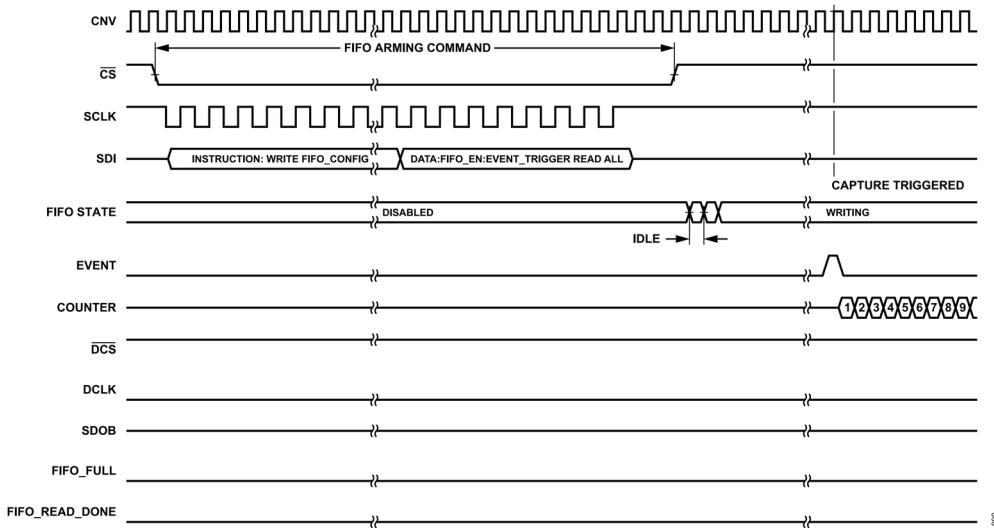

表 11. 省電力動作モード（続き）