## I3C インターフェースを備えた小型低消費電力の 12 ビット Easy Drive SAR ADC

### 特長

- ▶ 小 footprint で高性能

- ▶ INL :  $\pm 0.1$ LSB (最大値)

- ▶ S/N 比 : 73.8dB ( $V_{REF} = 3.3V$ )

- ▶ 1 変換あたり  $1.35nJ$

- ▶ サンプル・モードで  $405\mu W/300kSPS$

- ▶ 自律モードで  $370\mu W/1MSPS$  または  $112\mu W/300kSPS$

- ▶ スタンバイ消費電力 :  $4.1\mu W$

- ▶ 汎用的なシグナル・コンディショニング機能を搭載

- ▶ Easy Drive 機能により小型で低消費電力の AFE 設計を実現

- ▶ 差動およびシングルエンドのシグナル・チェーンに対応

- ▶ 広い同相入力範囲

- ▶ デジタル・ホストの活動と消費電力を最小限に抑制

- ▶ ウィンドウ・コンパレータと割込み生成による自律的なサンプリング

- ▶ パースト・サンプリング対応の平均化フィルタ

- ▶ 関連デバイスとパワーサイクリングを同期

- ▶ 1.8V~3.3V ロジックに対応した 2 線式 I3C インターフェース

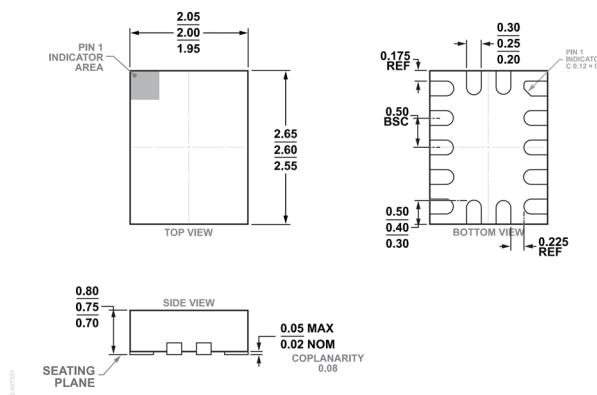

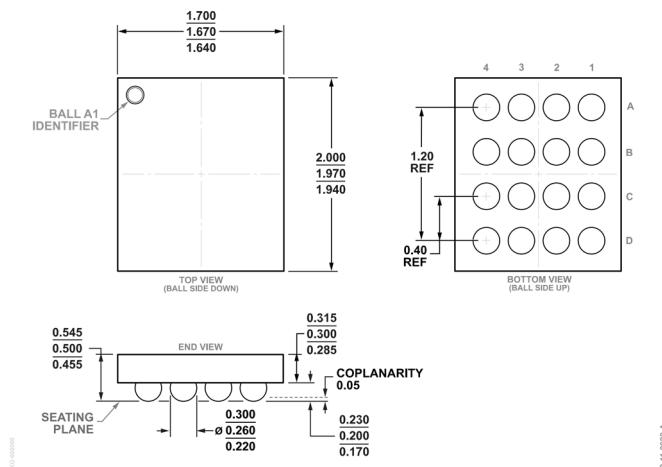

- ▶ 2.00mm × 2.6mm LFCSP および 1.67mm × 1.97mm WLCSP

- ▶ 広い動作温度範囲 :  $-40^{\circ}C \sim +125^{\circ}C$

### アプリケーション

- ▶ バッテリ駆動のデータ・アクイジション

- ▶ バイタル・サインの監視

- ▶ 生物学的分析および化学的分析

- ▶ 地質および地震のセンシング

- ▶ モーション・コントロールおよびロボット制御

### 概要

AD4060 は、逐次比較レジスタ (SAR) を内蔵した汎用的な 12 ビットのアナログ・デジタル・コンバータ (ADC) であり、精度を損なうことなく低電力かつ高密度のデータ・アクイジションが可能です。この ADC は、性能と電力効率の独自のバランスに加えて、システムが直面するニーズに合わせて高分解能モードと低電力モードをスムーズに切り替える、新たな機能を備えています。AD4060 は、バッテリ駆動の小型データ・アクイジションやエッジ・センシングのアプリケーションに最適です。

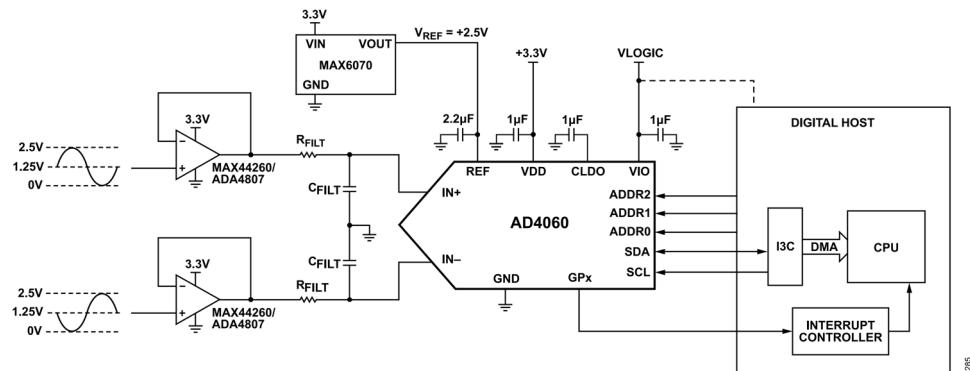

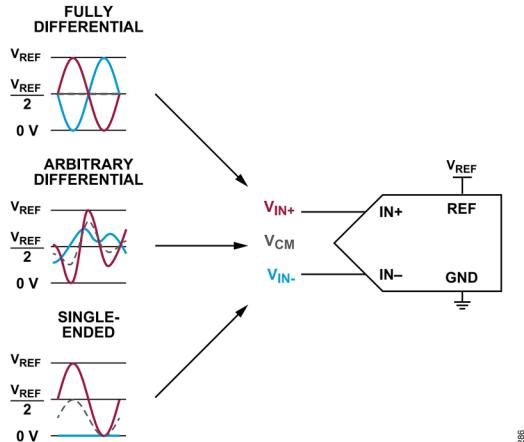

Easy Drive 機能により、高効率のアナログ・フロントエンド (AFE) 設計が可能です。小容量のサンプリング・コンデンサー ( $3.4pF$ ) で入力インピーダンスを高く保つことにより、SAR ADC で通常必要とされる消費電力の大きい高帯域幅アンプへの依存度を減らします。入力同相電圧範囲が広いので、本質的に、差動およびシングルエンド両方の信号に対応できます。

AD4060 は、パワーダウン・モードおよび割込み駆動型ファームウェアを備えたマイクロコントローラにも対応しています。自律モードでは、デジタル・ホストがスリープ状態の間に範囲外のイベントを検出できます。パースト平均化モードでは要求に応じて高分解能の計測を行う一方で、ホスト・プロセッサの演算負荷を軽減します。自己同期型デバイス・イネーブル信号 (DEV\_EN) は、AFE デバイスのパワーサイクリングを ADC のサンプリング・タイミングに同期させて、システムの消費電力を最適化すると共に、電源投入時のセッティング誤差によるアーチファクトを最小限に抑えます。AD4060 は、更なる省電力のために、電圧リファレンスのパワーサイクリングや ADC の電圧リファレンス ( $V_{REF}$ ) として電源を使用することもできます。

デバイス設定と ADC のデータ・リードバックは、信頼性の高い 2 線式 I3C インターフェースを通じて行われ、すべてのデータ転送に巡回冗長検査 (CRC) が適用されます。AD4060 は小型の 14 ピン・リード・フレーム・チップ・スケール (LFCSP) パッケージと 16 ボール・ウェハ・レベル・チップ・スケール (WLCSP) パッケージで提供され、広い温度範囲で動作するので広範なアプリケーションに使用することができます。

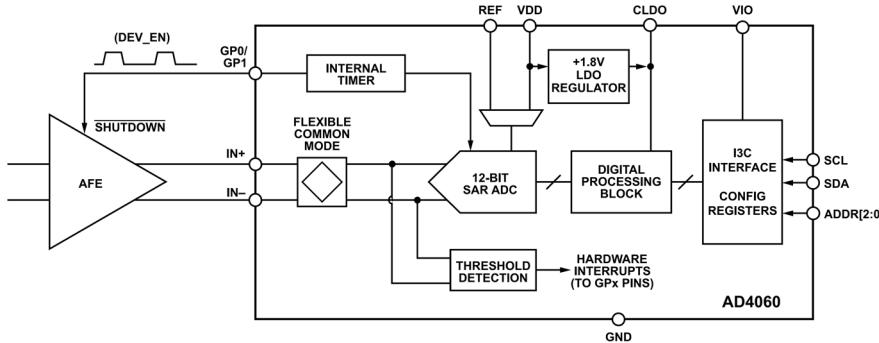

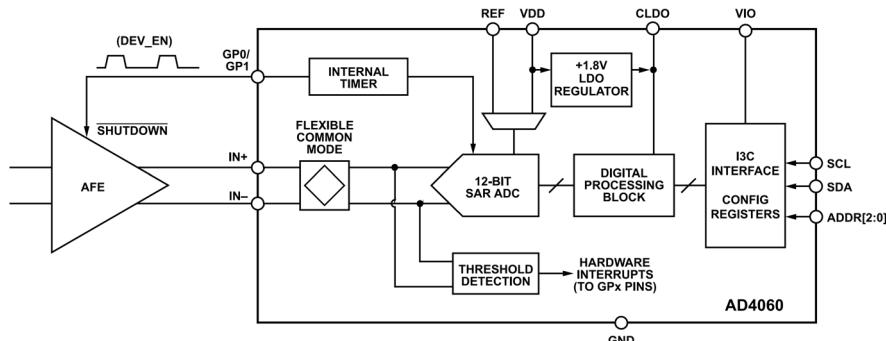

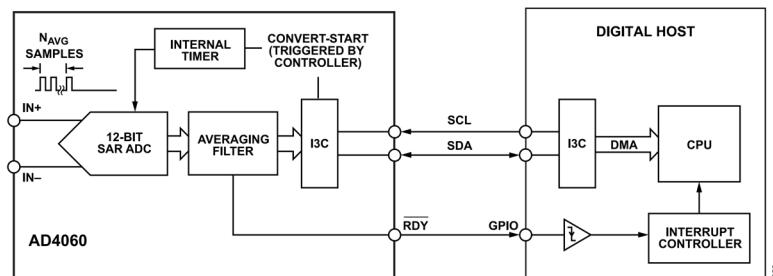

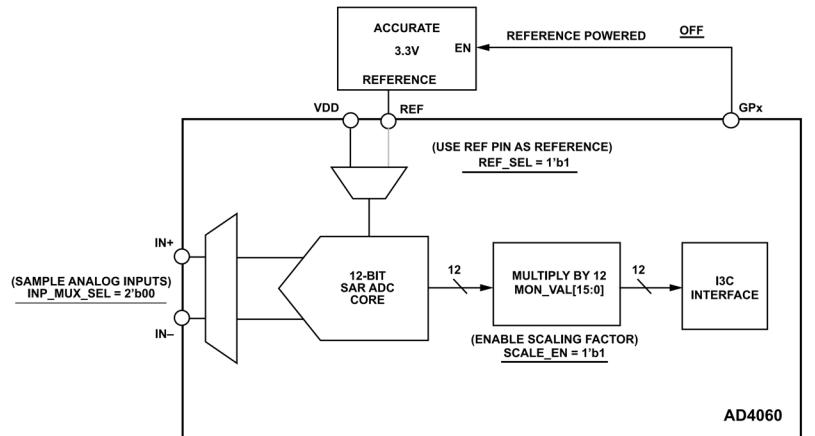

### 機能ブロック図

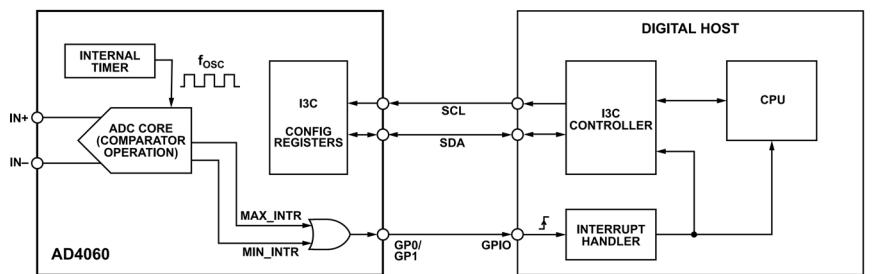

図 1. 機能ブロック図

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

Rev. 0

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                            |    |                            |    |

|----------------------------|----|----------------------------|----|

| 特長                         | 1  | VDD 消費電力                   | 52 |

| アプリケーション                   | 1  | シリアル・インターフェースの出力データレートの計算  | 54 |

| 概要                         | 1  | レイアウトに関する推奨事項              | 55 |

| 機能ブロック図                    | 1  | AD4060 のレジスタの概要            | 56 |

| 仕様                         | 4  | レジスタの詳細                    | 57 |

| タイミング仕様                    | 7  | インターフェース設定 A レジスタ          | 57 |

| 絶対最大定格                     | 10 | インターフェース設定 B レジスタ          | 57 |

| 熱抵抗                        | 10 | デバイス設定レジスタ                 | 57 |

| 静電放電 (ESD) 定格              | 10 | デバイス・タイプ・レジスタ              | 58 |

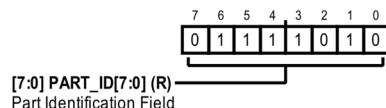

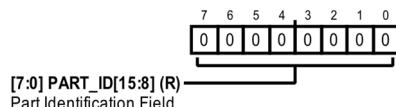

| ESD に関する注意                 | 10 | 製品 ID (LSByte) レジスタ        | 58 |

| ピン配置およびピン機能の説明             | 11 | 製品 ID (MSByte) レジスタ        | 58 |

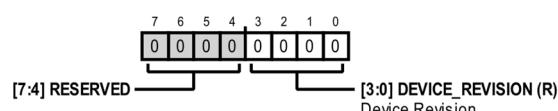

| 代表的な性能特性                   | 13 | デバイス・グレード・レジスタ             | 58 |

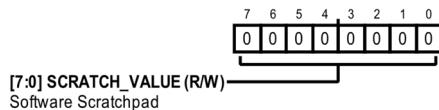

| 用語の定義                      | 18 | スクラッチ・パッド・レジスタ             | 58 |

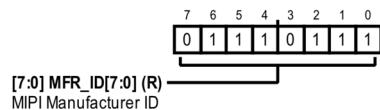

| 動作原理                       | 19 | MIPI メーカーID (下位バイト) レジスタ   | 59 |

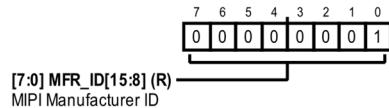

| 概要                         | 19 | MIPI メーカーID (上位バイト) レジスタ   | 59 |

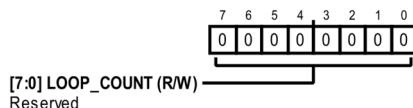

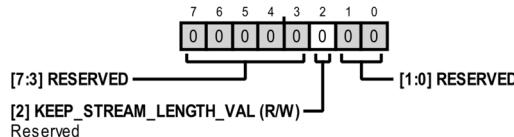

| コンバータの動作                   | 19 | 予約済みレジスタ                   | 59 |

| アナログ入力                     | 21 | 予約済みレジスタ                   | 60 |

| 電圧リファレンス                   | 21 | インターフェース設定 C レジスタ          | 60 |

| デジタル処理機能                   | 22 | インターフェース・ステータス・レジスタ        | 60 |

| 内蔵タイマー                     | 23 | ADC 動作モード設定レジスタ            | 61 |

| 電源                         | 23 | ADC セットアップ設定レジスタ           | 61 |

| コンパレータの動作                  | 23 | 平均化フィルタ設定レジスタ              | 62 |

| 割込み信号および制御信号               | 25 | 汎用ピン設定レジスタ                 | 62 |

| 動作モード                      | 28 | 割込み設定レジスタ                  | 63 |

| サンプル・モード                   | 29 | タイマー設定レジスタ                 | 64 |

| バースト平均化モード                 | 31 | 最大閾値設定レジスタ                 | 65 |

| 自律モード                      | 33 | 最小閾値設定レジスタ                 | 65 |

| スリープ・モード                   | 35 | 最大閾値ヒステリシス・レジスタ            | 65 |

| シリアル・インターフェース              | 36 | 最小閾値ヒステリシス・レジスタ            | 65 |

| ダイナミック・アドレシング              | 36 | MON_VAL スケーリング・レジスタ        | 66 |

| レジスタ・アドレス・ポインタ             | 37 | インターフェース・エラーIBI イネーブル・レジスタ | 66 |

| レジスタへの書込み                  | 37 | ADC IBI イネーブル・レジスタ         | 66 |

| レジスタの読み出し                  | 38 | ヒューズ CRC レジスタ              | 67 |

| レジスタ・アクセス CRC              | 39 | デバイス・ステータス・レジスタ            | 67 |

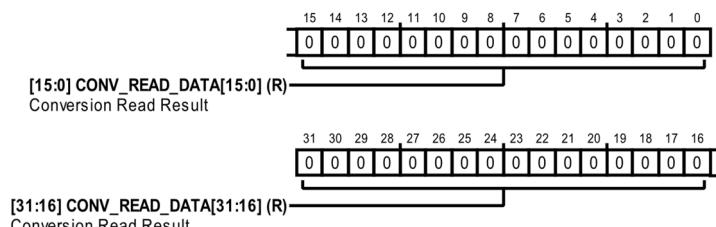

| CONV_READ レジスタ             | 40 | 最大割込みサンプル・レジスタ             | 68 |

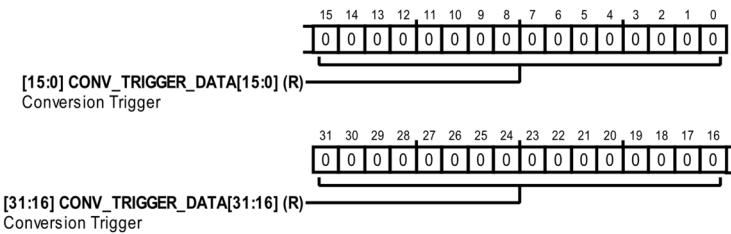

| CONV_TRIGGER レジスタ          | 41 | 最小割込みサンプル・レジスタ             | 68 |

| データ・フェーズの 9 番目の SDA ビット    | 42 | ターゲット・アドレス・レジスタ            | 68 |

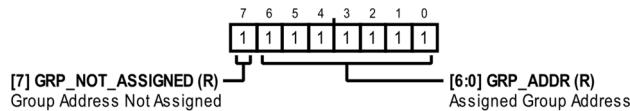

| コモン・コマンド・コード (CCC)         | 42 | グループ・アドレス・レジスタ             | 68 |

| デバイスのリセット                  | 45 | IBI ステータス・レジスタ             | 69 |

| アプリケーション情報                 | 47 | 変換読み出し結果レジスタ               | 69 |

| 代表的なアプリケーション図              | 47 | 変換トリガ・レジスタ                 | 70 |

| アナログ・フロントエンドの設計            | 48 | 外形寸法                       | 71 |

| リファレンス回路設計                 | 50 | オーダー・ガイド                   | 71 |

| アンプのシャットダウンと ADC サンプリングの同期 | 50 | 評価用ボード                     | 71 |

| リファレンスのシャットダウンを利用した高精度の達成  | 51 |                            |    |

## 目次

### 改訂履歴

7/2025—Revision 0: Initial Version

## 仕様

特に指定のない限り、VDD = 2.3V~3.6V、V<sub>REF</sub> = 2.3V~3.6V、VIO = 1.71V~3.6V、リファレンス容量 (C<sub>REF</sub>) = 2.2μF、最大規定サンプル・レート (f<sub>S</sub>) での動作。特に指定のない限り、他の機能はすべてデフォルト設定、最小値および最大値は T<sub>A</sub> = -40°C~+125°C における値、代表値は T<sub>A</sub> = +25°C における値。

表 1. 仕様

| Parameter                                                       | Test Conditions/Comments                                              | Min               | Typ    | Max               | Unit    |

|-----------------------------------------------------------------|-----------------------------------------------------------------------|-------------------|--------|-------------------|---------|

| RESOLUTION                                                      |                                                                       |                   |        |                   |         |

| ADC Resolution                                                  |                                                                       | 12                |        |                   | Bits    |

| Averaging Filter Resolution                                     | Burst averaging mode                                                  | 14                |        |                   | Bits    |

| Comparator Mode Resolution                                      | Autonomous modes                                                      | 12                |        |                   | Bits    |

| SAMPLING DYNAMICS                                               |                                                                       |                   |        |                   |         |

| Sampling Rate (f <sub>S</sub> ) <sup>1</sup>                    |                                                                       |                   | 2      |                   | MSPS    |

| Aperture Delay                                                  |                                                                       | 0.3               |        |                   | ns      |

| ANALOG INPUT                                                    |                                                                       |                   |        |                   |         |

| Input Voltage (V <sub>IN</sub> ) Range <sup>2</sup>             | V <sub>IN</sub> = V <sub>IN+</sub> - V <sub>IN-</sub>                 |                   |        |                   |         |

|                                                                 | Differential mode                                                     | -V <sub>REF</sub> |        | +V <sub>REF</sub> | V       |

|                                                                 | Single-ended mode                                                     | 0                 |        | +V <sub>REF</sub> | V       |

| Absolute Input Voltage <sup>2</sup>                             | V <sub>IN+</sub> , V <sub>IN-</sub>                                   | -0.1              |        | VDD + 0.1         | V       |

| Common-Mode Input Voltage (V <sub>CM</sub> ) Range <sup>3</sup> | V <sub>CM</sub> = (V <sub>IN+</sub> + V <sub>IN-</sub> )/2            | -0.1              |        | VDD + 0.1         | V       |

| Analog Input Leakage Current                                    | IN+, IN-                                                              |                   | 6      |                   | nA      |

| Sampling Capacitance (C <sub>IN</sub> )                         |                                                                       |                   | 3.4    |                   | pF      |

| Analog Input Capacitance <sup>4</sup>                           | IN+, IN-                                                              |                   |        |                   |         |

| Track Phase                                                     |                                                                       |                   | 5.4    |                   | pF      |

| Hold Phase                                                      |                                                                       |                   | 2.0    |                   | pF      |

| DC ACCURACY                                                     | V <sub>REF</sub> = 3.3 V                                              |                   |        |                   |         |

| No Missing Codes                                                |                                                                       | 12                |        |                   | Bits    |

| Transition Noise                                                | Sample mode (no averaging)                                            |                   |        |                   |         |

|                                                                 | Differential mode                                                     |                   | 0.08   |                   | LSB rms |

|                                                                 | Single-ended mode                                                     |                   | 0.16   |                   | LSB rms |

| Integral Nonlinearity (INL)                                     |                                                                       | -0.1              | ±0.03  | +0.1              | LSB     |

| Differential Nonlinearity (DNL) <sup>5</sup>                    |                                                                       | -0.1              | ±0.03  | +0.1              | LSB     |

| Zero Error                                                      |                                                                       | -900              | ±75    | +900              | μV      |

| Zero-Error Drift                                                |                                                                       |                   | ±0.05  |                   | ppm/°C  |

| Gain Error                                                      |                                                                       | -0.06             | ±0.002 | +0.06             | %FS     |

| Gain Error Drift                                                |                                                                       |                   | ±0.2   |                   | ppm/°C  |

| Total Unadjusted Error (TUE) <sup>6</sup>                       |                                                                       | -600              | ±20    | +600              | ppm     |

| Autonomous Mode TUE <sup>7</sup>                                |                                                                       |                   | ±7     |                   | mV      |

| REFERENCE                                                       |                                                                       |                   |        |                   |         |

| V <sub>REF</sub> Input Range                                    |                                                                       | 2.3               |        | VDD               | V       |

| REF Standby Current                                             | V <sub>REF</sub> = 3.3V                                               |                   | 8      |                   | nA      |

| REF Average Input Current <sup>8</sup>                          | V <sub>REF</sub> = 3.3V, f <sub>S</sub> = 300kSPS                     |                   | 9      | 10                | μA      |

| AC PERFORMANCE                                                  | V <sub>REF</sub> = 3.3V                                               |                   |        |                   |         |

| Total RMS Noise                                                 | Sample mode (no averaging)                                            |                   | 476    |                   | μVrms   |

| Signal-to-Noise Ratio (SNR)                                     | V <sub>IN</sub> = -0.5dBFS, input frequency (f <sub>IN</sub> ) = 1kHz |                   |        |                   |         |

| Differential Mode                                               | Sample mode (no averaging)                                            |                   | 73.8   |                   | dB      |

| Single-Ended Mode                                               | Sample mode (no averaging)                                            |                   | 73.5   |                   | dB      |

| Total Harmonic Distortion (THD)                                 | V <sub>IN</sub> = -0.5dBFS, f <sub>IN</sub> = 1kHz, sample mode       | -105              | -90    |                   | dB      |

## 仕様

表 1. 仕様 (続き)

| Parameter                                  | Test Conditions/Comments                                          | Min                  | Typ | Max                  | Unit          |

|--------------------------------------------|-------------------------------------------------------------------|----------------------|-----|----------------------|---------------|

| Signal-to-Noise and Distortion (SINAD)     | $V_{IN} = -0.5\text{dBFS}$ , $f_{IN} = 1\text{kHz}$ , sample mode |                      |     |                      |               |

| Differential Mode                          |                                                                   | 73.8                 |     |                      | dB            |

| Single-Ended Mode                          |                                                                   | 73.5                 |     |                      | dB            |

| -3dB Input Bandwidth                       |                                                                   | 200                  |     |                      | MHz           |

| DIGITAL INPUTS                             |                                                                   |                      |     |                      |               |

| Input Low Voltage ( $V_{IL}$ )             |                                                                   | $-0.1 \times V_{IO}$ |     | $+0.3 \times V_{IO}$ | V             |

| Input High Voltage ( $V_{IH}$ )            |                                                                   | $0.7 \times V_{IO}$  |     | $1.1 \times V_{IO}$  | V             |

| Input Low Current ( $I_{IL}$ )             |                                                                   | -1                   |     | +1                   | $\mu\text{A}$ |

| Input High Current ( $I_{IH}$ )            |                                                                   | -1                   |     | +1                   | $\mu\text{A}$ |

| Digital Input Capacitance                  |                                                                   | 3                    |     |                      | pF            |

| DIGITAL OUTPUTS                            |                                                                   |                      |     |                      |               |

| Output Low Voltage ( $V_{OL}$ )            |                                                                   |                      |     |                      |               |

| SDA                                        | Digital output current = +3mA                                     |                      | 0.3 |                      | V             |

| GP0, GP1                                   | Digital output current = +500 $\mu\text{A}$                       |                      | 0.3 |                      | V             |

| Output High Voltage ( $V_{OH}$ )           |                                                                   |                      |     |                      |               |

| SDA <sup>9</sup>                           | Digital output current = -3mA                                     | $V_{IO} - 0.3$       |     |                      | V             |

| GP0, GP1                                   | Digital output current = -500 $\mu\text{A}$                       | $V_{IO} - 0.3$       |     |                      | V             |

| Digital Output Short-Circuit Current       | $V_{IO} = 3.3\text{V}$                                            |                      |     |                      |               |

| Sourcing                                   | Logic high shorted to 0V                                          |                      | 48  |                      | mA            |

| Sinking                                    | Logic low shorted to 3.3V                                         |                      | 38  |                      | mA            |

| POWER REQUIREMENTS                         |                                                                   |                      |     |                      |               |

| VDD                                        |                                                                   | 2.3                  |     | 3.6                  | V             |

| VIO                                        |                                                                   | 1.71                 |     | 3.6                  | V             |

| POWER SUPPLY CURRENT                       | $V_{DD} = 3.3\text{V}$                                            |                      |     |                      |               |

| Sleep Mode Current                         | $f_S = 0\text{SPS}$                                               |                      |     |                      |               |

| VDD                                        |                                                                   |                      | 10  |                      | nA            |

| VIO                                        | $V_{IO} = 1.8\text{V}$                                            |                      | 20  |                      | nA            |

|                                            | $V_{IO} = 3.3\text{V}$                                            |                      | 120 |                      | nA            |

| Standby Current                            | $f_S = 0\text{SPS}$                                               |                      |     |                      |               |

| VDD                                        |                                                                   |                      | 990 |                      | nA            |

| VIO                                        | $V_{IO} = 1.8\text{V}$                                            |                      | 50  |                      | nA            |

|                                            | $V_{IO} = 3.3\text{V}$                                            |                      | 260 |                      | nA            |

| VDD Active Supply Current <sup>10</sup>    |                                                                   |                      |     |                      |               |

| Sample Mode                                | $f_S = 10\text{kSPS}$                                             | 4                    |     |                      | $\mu\text{A}$ |

|                                            | $f_S = 300\text{kSPS}$                                            | 120                  | 160 |                      | $\mu\text{A}$ |

| Autonomous Modes                           | $f_S = 10\text{kSPS}$                                             | 1.12                 |     |                      | $\mu\text{A}$ |

|                                            | $f_S = 300\text{kSPS}$                                            | 34                   |     |                      | $\mu\text{A}$ |

|                                            | $f_S = 1\text{MSPS}$                                              | 112                  |     |                      | $\mu\text{A}$ |

|                                            | $f_S = 2\text{MSPS}$                                              | 224                  | 300 |                      | $\mu\text{A}$ |

| POWER DISSIPATION                          | $V_{DD} = V_{IO} = 3.3\text{V}$                                   |                      |     |                      |               |

| Sleep Mode Power Dissipation               | $f_S = 0\text{SPS}$                                               | 430                  |     |                      | nW            |

| Standby Power Dissipation                  | $f_S = 0\text{SPS}$                                               | 4.1                  |     |                      | $\mu\text{W}$ |

| VDD Energy per Conversion                  |                                                                   | 1.35                 |     |                      | nJ            |

| VDD Active Power Dissipation <sup>10</sup> |                                                                   |                      |     |                      |               |

## 仕様

表 1. 仕様 (続き)

| Parameter   | Test Conditions/Comments | Min | Typ  | Max | Unit          |

|-------------|--------------------------|-----|------|-----|---------------|

| Sample Mode | $f_S = 10\text{kSPS}$    |     | 13.6 |     | $\mu\text{W}$ |

|             | $f_S = 300\text{kSPS}$   |     | 405  | 528 | $\mu\text{W}$ |

|             | $f_S = 10\text{kSPS}$    | 3.7 |      |     | $\mu\text{W}$ |

|             | $f_S = 300\text{kSPS}$   |     | 112  |     | $\mu\text{W}$ |

|             | $f_S = 1\text{MSPS}$     |     | 370  |     | $\mu\text{W}$ |

|             | $f_S = 2\text{MSPS}$     | 740 |      | 990 | $\mu\text{W}$ |

<sup>1</sup>サンプリング・レートは、AD4060 ADC の最大サンプル・レート能力の仕様です。出力データレートは、シリアル・インターフェースで毎秒送信できる ADC サンプルの数であり、I3C インターフェースのタイミング仕様によって異なります。サンプル・モードでは、I3C インターフェースによって AD4060 の出力データレートが制限されるので、データレートは 2MSPS を下回ります。バースト平均化モードおよび自律モードでは、出力データレートの条件が緩和されるので、AD4060 の ADC コアは最大 2MSPS で動作できます。AD4060 の I3C 出力データレートを動作モードごとに推定するためのガイドラインについては、[シリアル・インターフェースの出力データレートの計算](#)のセクションを参照してください。

<sup>2</sup>  $V_{IN+}$  と  $V_{IN-}$  は、それぞれ IN+ ピンと IN- ピンの電圧を表しています。AD4060 は、 $V_{IN+}$  と  $V_{IN-}$  の差分をサンプリングして変換します。

<sup>3</sup> AD4060 の同相入力電圧範囲の詳細な説明については、[広い入力同相電圧範囲](#)のセクションを参照してください。

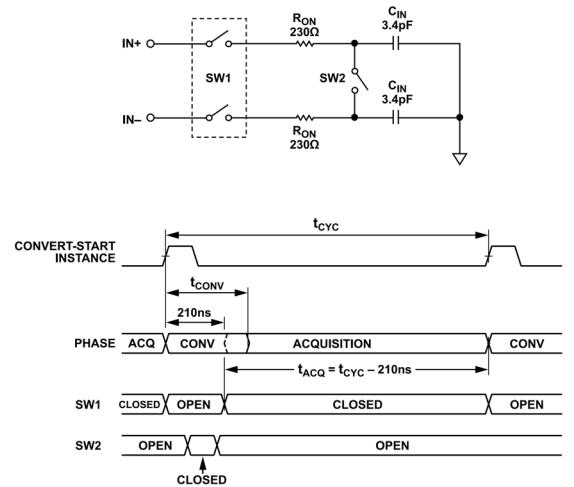

<sup>4</sup> トランク・フェーズでの総入力容量は、 $C_{IN}$  とピン容量の合計になります。ホールド・フェーズでは  $C_{IN}$  が入力から遮断されるので、入力容量はピン容量のみになります。[図 40](#) を参照してください。

<sup>5</sup> DNL の最小仕様および最大仕様は設計により確保されています。

<sup>6</sup> TUE (総合未調整誤差) は、どのデバイスでも、全入力範囲にわたる理想的な DC 伝達関数からの最大のずれと定義されています。TUE には、各デバイスのゼロ誤差、ゲイン誤差、INL 誤差を組み合わせた影響が含まれています。

<sup>7</sup> 自律モードにおける TUE はコンパレータの動作に適用されます。[コンパレータの動作](#)および[自律モード](#)の各セクションを参照してください。

<sup>8</sup> 平均 REF 入力電流は、 $f_S$  に伴って線形に変化します ([図 23](#) を参照)。

<sup>9</sup> ブッシュプル動作の場合に限ります。

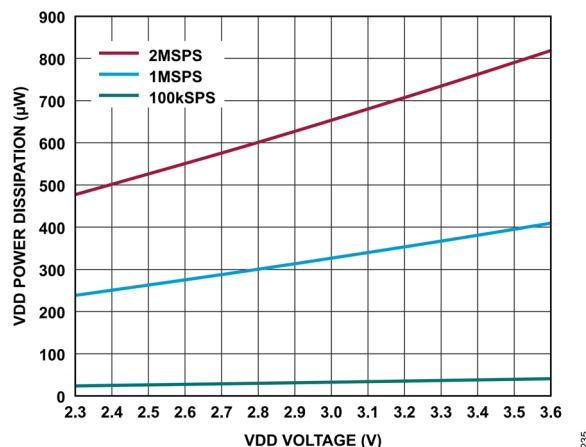

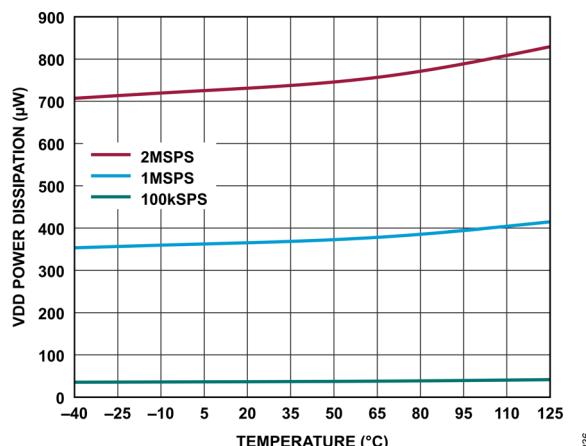

<sup>10</sup> VDD の電源電流と消費電力は、 $f_S$  に伴って線形に変化します ([VDD 消費電力](#)のセクション、[図 26](#)、および[図 29](#) を参照)。

## 仕様

## タイミング仕様

VDD = V<sub>REF</sub> = 2.3V~3.6V、VIO = 1.71V~3.6V、I<sub>3C</sub> バス容量 (C<sub>BUS</sub>) = 50pF、他の全機能はデフォルト設定。特に指定のない限り、最小値および最大値は T<sub>A</sub> = -40°C~+125°C における値、代表値は T<sub>A</sub> = +25°C における値。

表 2. ADC パラメータ

| Parameter <sup>1</sup>                | Symbol            | Min    | Typ              | Max  | Unit |

|---------------------------------------|-------------------|--------|------------------|------|------|

| Sampling Rate <sup>2</sup>            | f <sub>s</sub>    |        |                  | 2    | MSPS |

| Sample Period <sup>2</sup>            | t <sub>CYC</sub>  | 500    |                  |      | ns   |

| Conversion Time                       | t <sub>CONV</sub> |        | 270              | 320  | ns   |

| Acquisition Time <sup>34</sup>        | t <sub>ACQ</sub>  |        |                  |      |      |

| f <sub>s</sub> = 2MSPS                |                   | 290    | 327              |      | ns   |

| f <sub>s</sub> = 300kSPS              |                   | 3123.3 | 3160.3           |      | ns   |

| Internal Timer Frequency <sup>5</sup> | f <sub>osc</sub>  | -15%   | f <sub>osc</sub> | +15% | ns   |

<sup>1</sup> t<sub>CONV</sub> の仕様は製品テストで確認されています。この表の他のタイミング仕様は、すべて特性評価および設計により確保されています。

<sup>2</sup> サンプリング・レートは、AD4060 ADC の最大サンプル・レート能力の仕様です。出力データレートは、シリアル・インターフェースで毎秒送信できる ADC サンプルの数であり、I<sub>3C</sub> インターフェースのタイミング仕様によって異なります。サンプル・モードでは I<sub>3C</sub> インターフェースによって AD4060 の出力データレートが制限されるので、データレートは 2MSPS を下回ります。バースト平均化モードおよび自律モードでは、出力データレートの条件が緩和されるため、AD4060 の ADC コアは最大 2MSPS で動作できます。AD4060 の I<sub>3C</sub> 出力データレートを動作モードごとに推定するためのガイドラインについては、[シリアル・インターフェースの出力データレートの計算](#)のセクションを参照してください。

<sup>3</sup> t<sub>ACQ</sub> の仕様値は、入力サンプリング容量が所定のサンプル・レートにおいて入力電圧を取り込むのに利用できる時間です。t<sub>ACQ</sub> の仕様値は、ADC がトラック・フェーズで消費する時間に相当します。t<sub>ACQ</sub> の仕様値はサンプル・レートに反比例します。そのため、t<sub>ACQ</sub> の仕様値は、サンプル・レートが減少するにつれて増加します。任意のサンプル周期レートにおける t<sub>ACQ</sub> の最小仕様値は次式で得られます。

$$t_{ACQ} = t_{CYC} - 210 \text{ ns} \quad (1)$$

<sup>4</sup> DEV\_EN 信号を使用してアナログ・フロントエンドをパワーサイクリングしている間のアクイジション・タイムの説明については、[デバイス・イネーブル信号](#)のセクションを参照してください。

<sup>5</sup> バースト平均化モードおよび自律モードでは、内蔵タイマーでサンプリング周波数が設定されます。AD4060 は、最大 f<sub>osc</sub> の仕様で動作が確保されています。公称サンプリング周波数オプションについては表 52 を参照してください。

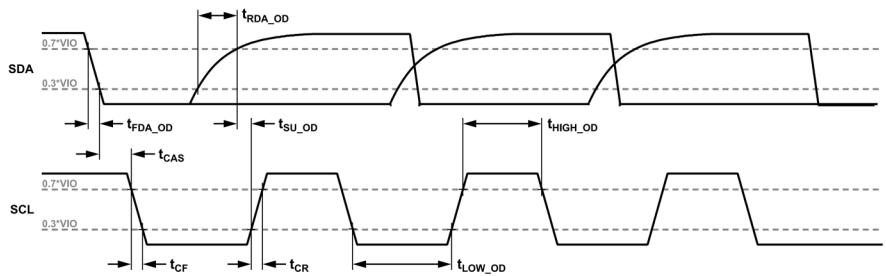

表 3. オープン・ドレイン・パラメータ

| Parameter <sup>1</sup>  | Symbol               | Min  | Typ | Max | Unit |

|-------------------------|----------------------|------|-----|-----|------|

| SCL Low Time            | t <sub>LOW_OD</sub>  | 200  |     |     | ns   |

| SCL High Time           | t <sub>HIGH_OD</sub> | 32   |     |     | ns   |

| SDA Fall Time           | t <sub>FDA_OD</sub>  |      | 4.2 |     | ns   |

| SDA Rise Time           | t <sub>RDA_OD</sub>  |      | 120 |     | ns   |

| SDA Data Setup Time     | t <sub>SU_OD</sub>   | 1.5  |     |     | ns   |

| Clock After Start Time  | t <sub>CAS</sub>     | 38.4 |     |     | ns   |

| Clock Before Stop Time  | t <sub>CBP</sub>     | 19.2 |     |     | ns   |

| Bus Available Condition | t <sub>AVAL</sub>    | 1    |     |     | μs   |

<sup>1</sup> t<sub>LOW\_OD</sub>、t<sub>HIGH\_OD</sub>、t<sub>CAS</sub>、t<sub>CBP</sub> の仕様は製品テストで確認されています。この表の他のタイミング仕様は、すべて特性評価および設計により確保されています。

## 仕様

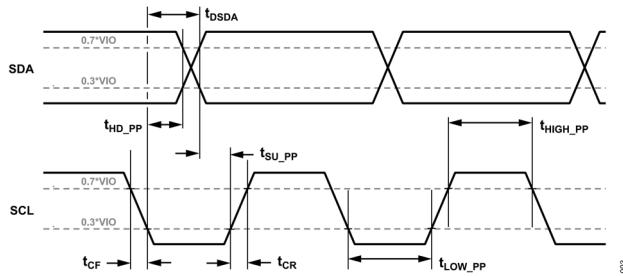

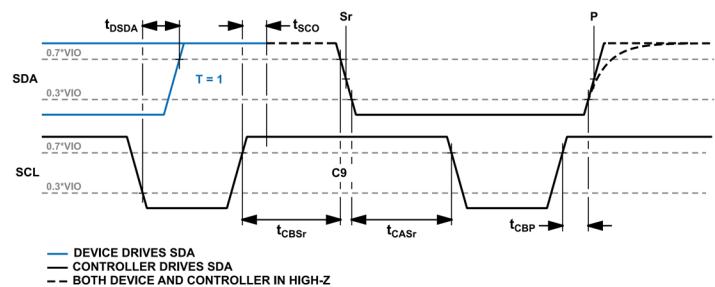

表 4. プッシュプル・パラメータ

| Parameter <sup>1</sup>                              | Symbol       | Min  | Typ  | Max  | Unit |

|-----------------------------------------------------|--------------|------|------|------|------|

| SCL Clock Frequency                                 | $f_{SCL}$    | 0.01 | 12.5 | 12.9 | MHz  |

| SCL Clock Low Time                                  | $t_{LOW}$    | 24   |      |      | ns   |

| SCL Clock High Time                                 | $t_{HIGH}$   | 24   |      |      | ns   |

| SDA Data Out Hold Time                              | $t_{HD\_PP}$ | 10   |      |      | ns   |

| SDA Data Valid Delay                                | $t_{DSDA}$   |      | 34   |      | ns   |

| Time Delay to Switch from Push-Pull to High-Z State | $t_{SCO}$    |      | 12   |      | ns   |

| SDA Data In Setup Time                              | $t_{SU\_PP}$ | 1.5  |      |      | ns   |

| Clock Before Repeated Start                         | $t_{CASr}$   | 19.2 |      |      | ns   |

| Clock After Repeated Start                          | $t_{CBSr}$   | 19.2 |      |      | ns   |

<sup>1</sup>  $t_{LOW}$ 、 $t_{HIGH}$ 、 $t_{CASr}$ 、 $t_{CBSr}$ の仕様は製品テストで確認されています。この表の他のタイミング仕様は、すべて特性評価および設計により確保されています。

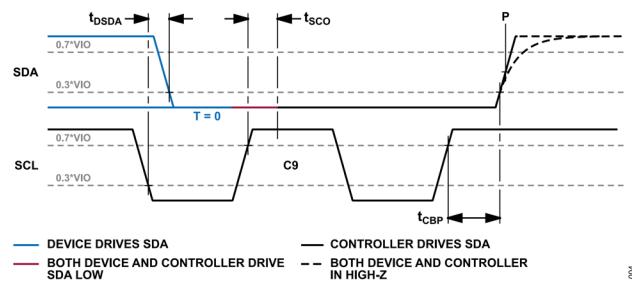

表 5. デバイス固有のパラメータ／その他のパラメータ

| Parameter                        | Symbol                    | Min | Typ | Max | Unit |

|----------------------------------|---------------------------|-----|-----|-----|------|

| Time Between Stop and Start      | $t_{BUF}$                 | 38  |     |     | ns   |

| IBI Delay <sup>1</sup>           | $t_{IBI\_ISSUE}$          |     | 28  |     | μs   |

| Reset Delay for Fuse Reload      | $t_{RESET\_FUSE\_RELOAD}$ | 5   |     |     | ns   |

| Reset Delay for Peripheral Reset | $t_{RESET\_PERIPHERAL}$   | 60  |     |     | ns   |

<sup>1</sup> IBI イベントが発生してから、IBI イベントが発生したことを示すために AD4060 が SDA をローにするまでの時間。

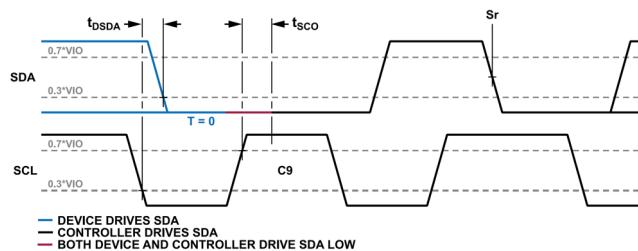

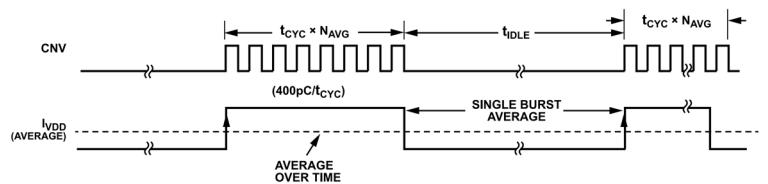

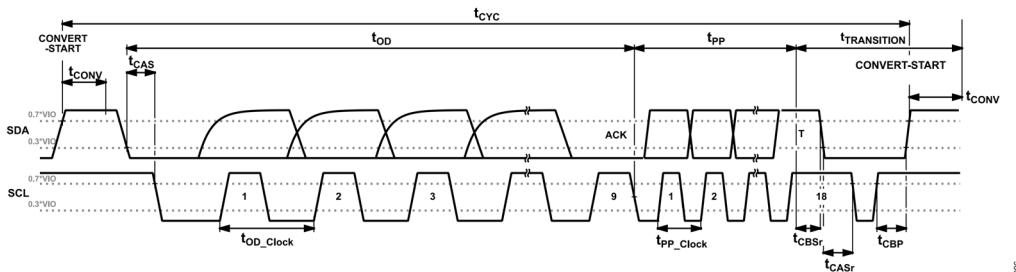

## タイミング図

図 2. オープン・ドレイン・パラメータ

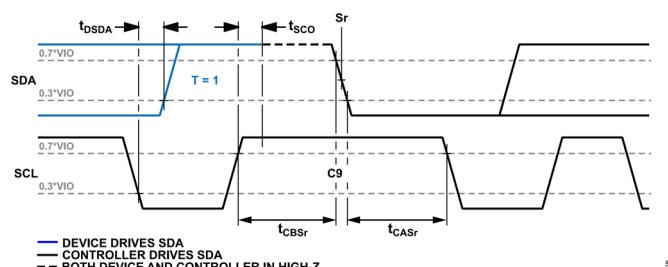

図 3. プッシュプル・パラメータ

## 仕様

図 4. AD4060 が読み出しを終了してコントローラがストップを生成するときの T ビット

図 5. AD4060 が読み出しを終了してコントローラが反復スタートを生成するときの T ビット

図 6. AD4060 とコントローラがメッセージの読み出し続行について合意するときの T ビット

図 7. コントローラが反復スタートとストップにより読み出しを終了するときの T ビット

図 8. コントローラが反復スタートとその後の転送を介して読み出しを終了するときの T ビット

## 絶対最大定格

表 6. 絶対最大定格

| Parameter                                 | Rating              |

|-------------------------------------------|---------------------|

| Analog Inputs<br>IN+, IN-, and REF to GND | -0.3V to VDD + 0.3V |

| Supply Voltages<br>VDD and VIO to GND     | -0.3V to +3.96V     |

| CLDO to GND                               | -0.3V to +2.1V      |

| Digital Inputs to GND                     | -0.3V to VIO + 0.3V |

| Digital Outputs to GND                    | -0.3V to VIO + 0.3V |

| Temperature<br>Storage                    | -55°C to +150°C     |

| Operating $T_J$ Range                     | -40°C to +125°C     |

| Maximum Reflow (Package Body)             | 260°C               |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意を払う必要があります。

表 7. 热抵抗

| Package Type <sup>1</sup> | $\theta_{JA}$ <sup>2</sup> | $\theta_{JC}$ <sup>3</sup> | Unit |

|---------------------------|----------------------------|----------------------------|------|

| CP-14-7                   | 73.9                       | 52.3                       | °C/W |

| CB-16-26                  | 49.6                       | 0.6                        | °C/W |

<sup>1</sup> テスト条件 1: 热抵抗のシミュレーション値は、2S2P JEDEC PCB の使用によって決定します。

<sup>2</sup>  $\theta_{JA}$  は、1 立方フィートの密封容器内で測定された、自然対流下におけるジャンクションと周囲温度の間の熱抵抗です。

<sup>3</sup>  $\theta_{JC}$  は、ジャンクションとケースの間の熱抵抗です。

## 静電放電 (ESD) 定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帶電デバイス・モデル (FICDM)。

## AD4060 の ESD 定格

表 8. AD4060、14 ピン LFCSP および 16 ポール WLCSP

| ESD Model | Withstand Threshold (kV) | Class |

|-----------|--------------------------|-------|

| HBM       | 4                        | 3A    |

| FICDM     | 1.25                     | C3    |

## ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

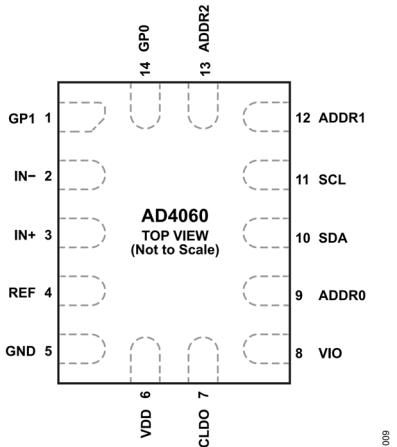

## ピン配置およびピン機能の説明

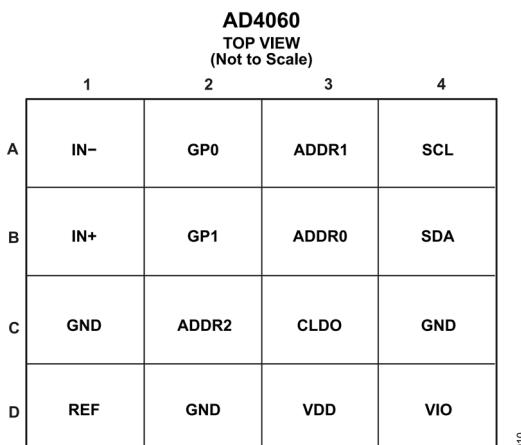

図 9. AD4060 LFCSP のピン配置

図 10. AD4060 WLCSP のピン配置

表 9. AD4060 LFCSP および WLCSP のピン機能の説明

| LFCSP の<br>ピン番号 | WLCSP の<br>ピン番号 | 記号    | タイプ   | 説明                                                                                                                          |

|-----------------|-----------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 1               | B2              | GP1   | DO    | 汎用出力 1。GP1 ピンは、複数のデバイス割込み信号として設定可能なデジタル出力です。割込み信号および制御信号のセクションを参照してください。                                                    |

| 2               | A1              | IN-   | AI    | 負のアナログ入力。アナログ入力のセクションを参照してください。                                                                                             |

| 3               | B1              | IN+   | AI    | 正のアナログ入力。アナログ入力のセクションを参照してください。                                                                                             |

| 4               | D1              | REF   | AI    | リファレンス入力。REF ピンは 2.2 $\mu$ F のコンデンサで GND からデカッピングします。電圧リファレンスのセクションを参照してください。                                               |

| 5               | C1, C4, D2      | GND   | P     | 電源グラウンド。                                                                                                                    |

| 6               | D3              | VDD   | P     | アナログ電源。VDD ピンは 1 $\mu$ F のコンデンサで GND からデカッピングします。VDD ピンは、CLDO ピンの電源電圧を提供する+1.8V の内部 LDO レギュレータへの入力にもなります。電源のセクションを参照してください。 |

| 7               | C3              | CLDO  | P     | ADC コアの電源。CLDO ピンには、+1.8V の内部低ドロップアウト (LDO) レギュレータから電源が供給されます。CLDO ピンは 1 $\mu$ F のコンデンサで GND からデカッピングします。電源のセクションを参照してください。 |

| 8               | D4              | VIO   | P     | ロジック電源。VIO ピンでは、デジタル入力およびデジタル出力のロジック電圧レベルを設定します。VIO ピンは 1 $\mu$ F のコンデンサで GND からデカッピングします。電源のセクションを参照してください。                |

| 9               | B3              | ADDR0 | DI    | アドレス 0 入力。パーティ・インスタンスのビット[0]を 48 ビットの暫定 ID に設定します。表 19 を参照してください <sup>1</sup> 。                                             |

| 10              | B4              | SDA   | DI/DO | シリアル・データ I/O                                                                                                                |

| 11              | A4              | SCL   | DI    | シリアル・データ・クロック入力。                                                                                                            |

## ピン配置およびピン機能の説明

表 9. AD4060 LFCSP および WLCSP のピン機能の説明（続き）

| LFCSP の<br>ピン番号 | WLCSP の<br>ピン番号 | 記号    | タイプ | 説明                                                                                                |

|-----------------|-----------------|-------|-----|---------------------------------------------------------------------------------------------------|

| 12              | A3              | ADDR1 | DI  | アドレス 1 入力。パーツ・インスタンスのビット[1]を 48 ビットの暫定 ID に設定します。 <a href="#">表 19</a> を参照してください <sup>1</sup> 。   |

| 13              | C2              | ADDR2 | DI  | アドレス 2 入力。パーツ・インスタンスのビット[2]を 48 ビットの暫定 ID に設定します。 <a href="#">表 19</a> を参照してください <sup>1</sup> 。   |

| 14              | A2              | GP0   | DO  | 汎用出力 0。GP0 ピンは、複数のデバイス制御信号または割込み信号として設定可能なデジタル出力です。 <a href="#">割込み信号および制御信号</a> のセクションを参照してください。 |

<sup>1</sup> ADDR[2:0] ピンは最大 8 個の固有パーツ・インスタンス値を割当て可能なので、1 つの I<sup>2</sup>C バス上で最大 8 個の AD4060 デバイスをサポートできます。

## 代表的な性能特性

特に指定のない限り、VDD = 3.3V、VREF = 3.3V、VIO = 3.3V、CREF = 2.2μF、最大 fs、TA = 25°C で、全ての機能はデフォルト設定。

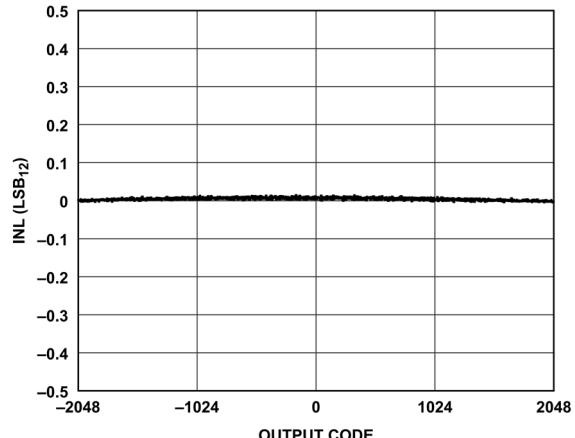

図 11. INL と出力コードの関係

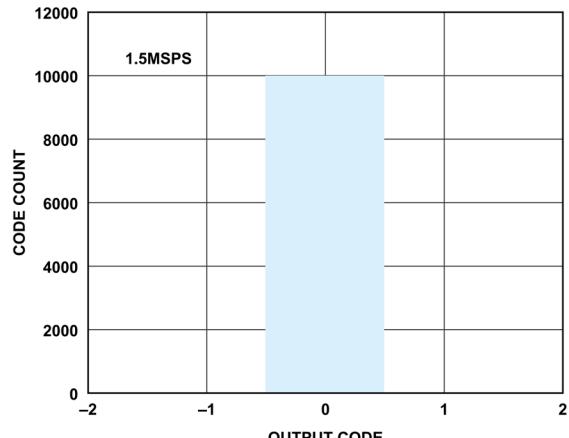

図 14. ヒストグラム、サンプル・モード（平均化なし）

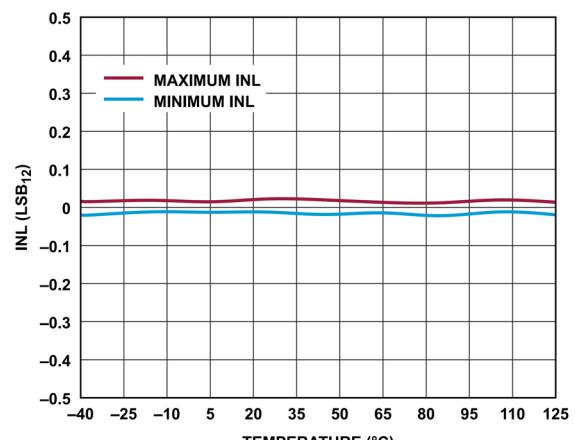

図 12. INL と温度の関係

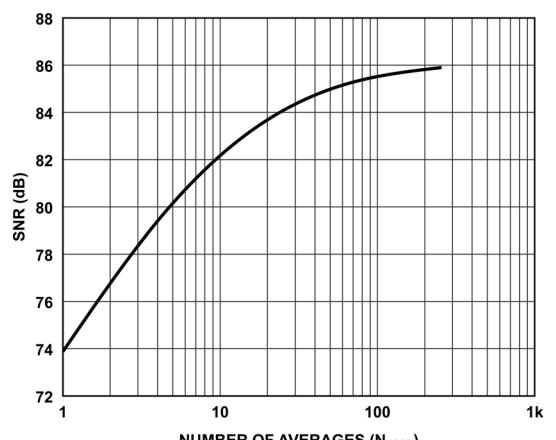

図 15. S/N 比と平均化回数の関係

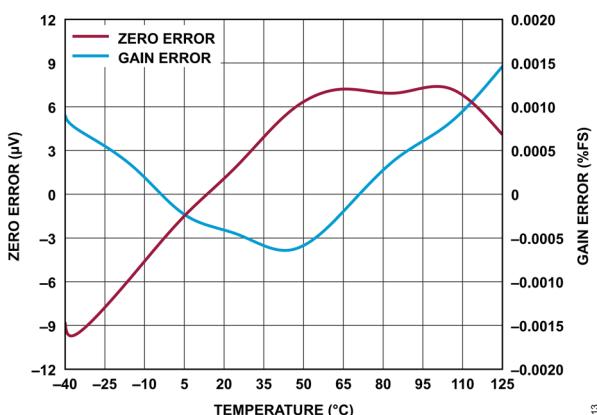

図 13. ゼロ誤差およびゲイン誤差と温度の関係

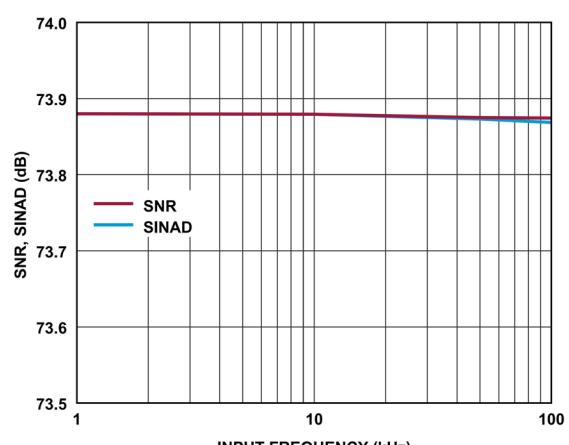

図 16. S/N 比、SINAD と入力周波数の関係

## 代表的な性能特性

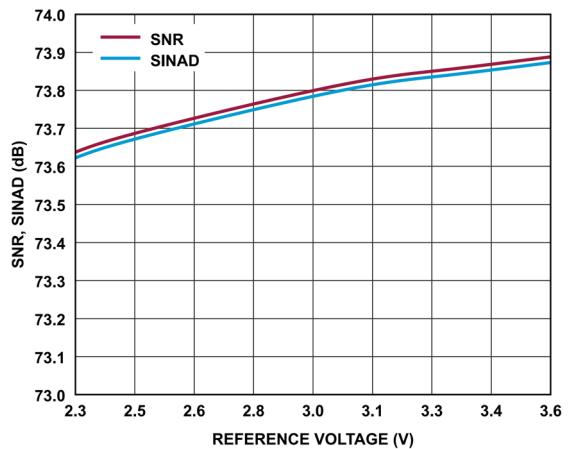

図 17. S/N 比および SINAD とリファレンス電圧の関係

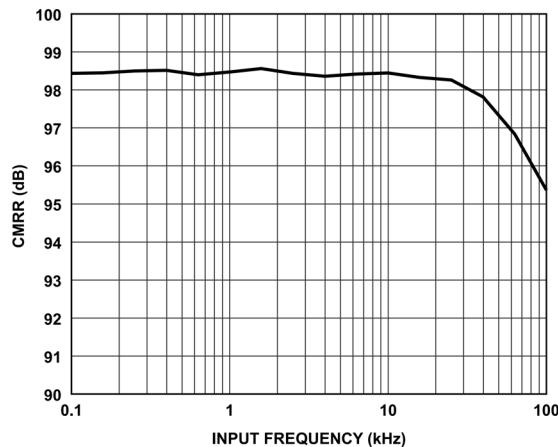

図 20. 同相モード除去比 (CMRR) と入力周波数の関係

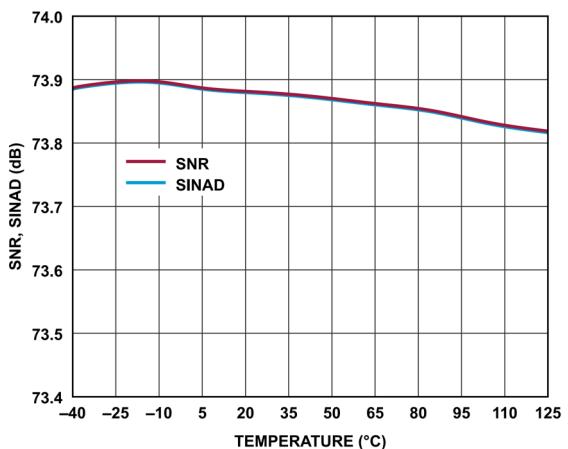

図 18. S/N 比および SINAD と温度の関係

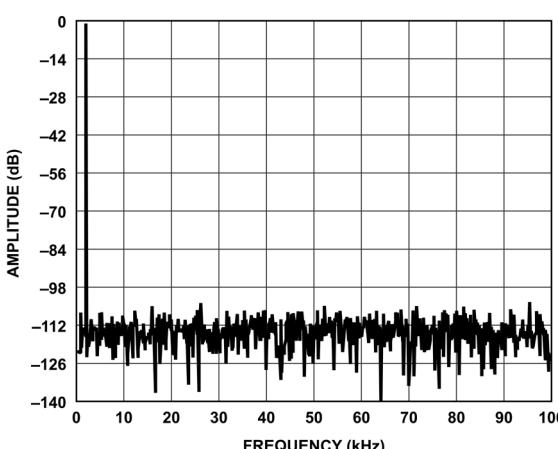

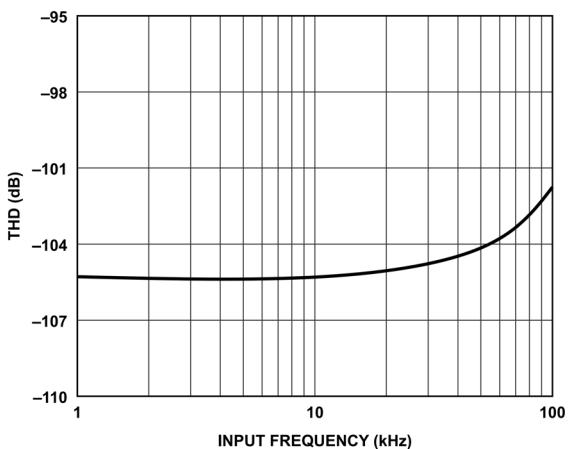

図 21. 高速フーリエ変換 (FFT) 、 $f_s = 200\text{kSPS}$ 、 $f_{IN} = 1\text{kHz}$ 図 19. THD と入力周波数の関係、 $V_{IN} = -1\text{dBFS}$

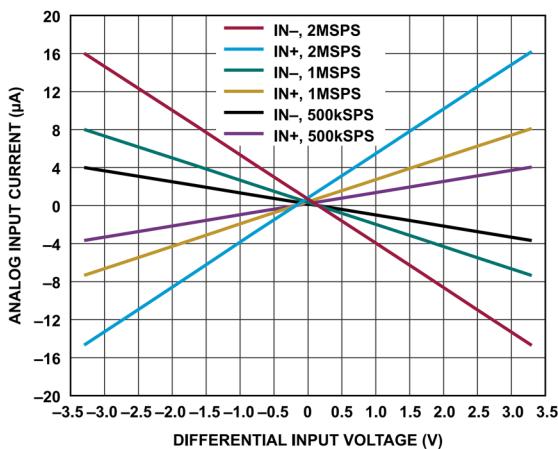

図 22. アナログ入力電流と差動入力電圧の関係

## 代表的な性能特性

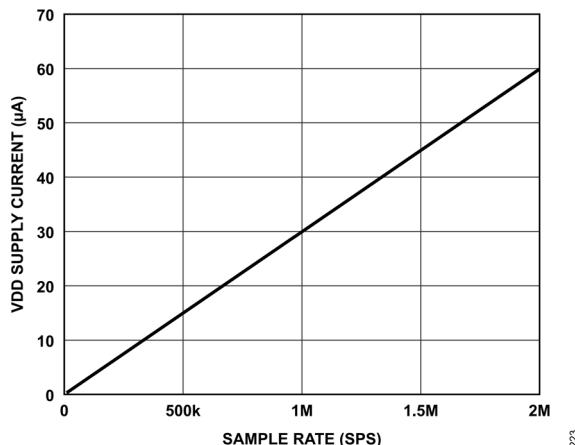

図 23. リファレンス入力電流とサンプル・レートの関係

図 26. VDD 電源電流とサンプル・レートの関係

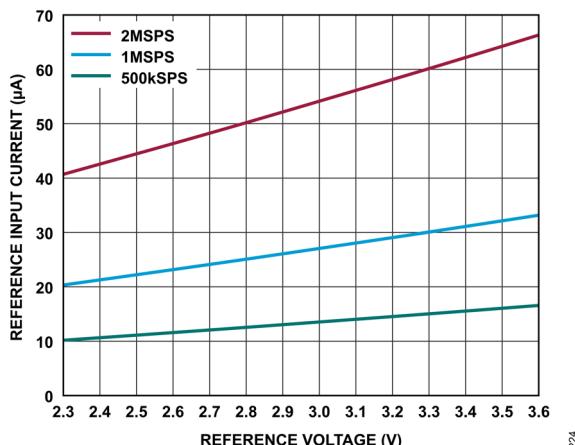

図 24. リファレンス入力電流とリファレンス電圧の関係

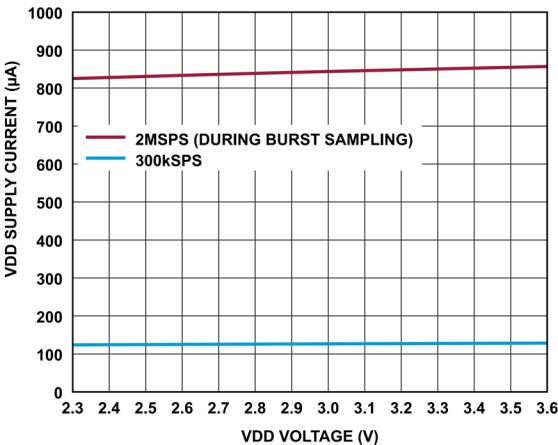

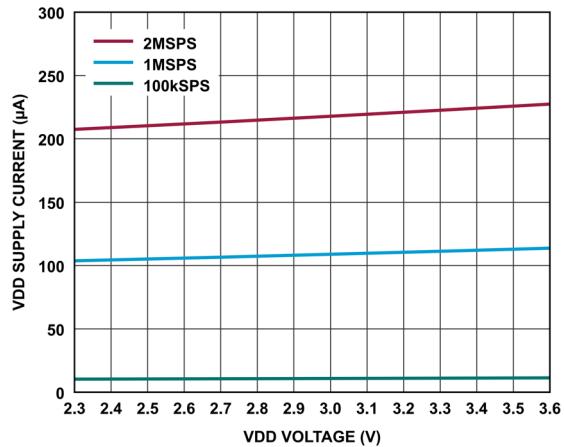

図 27. VDD 電源電流と VDD 電圧の関係

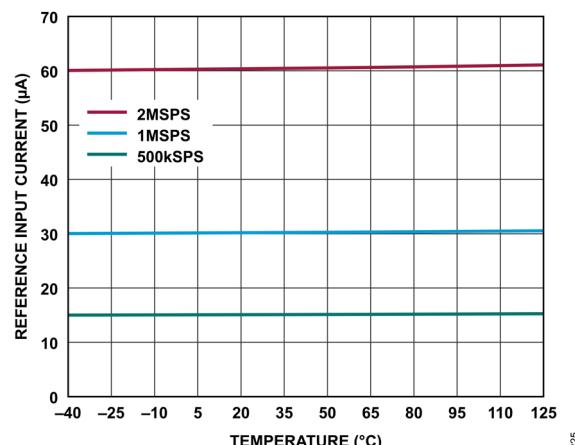

図 25. リファレンス入力電流と温度の関係

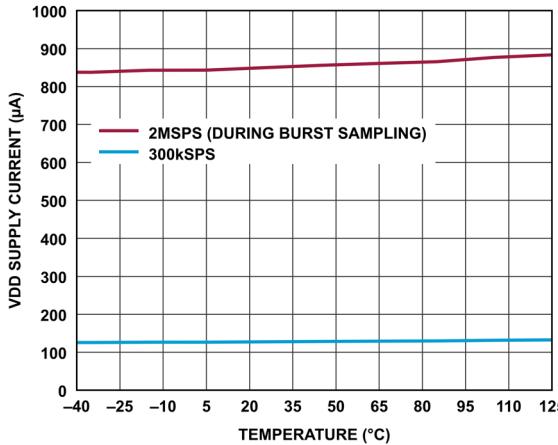

図 28. VDD 電源電流と温度の関係

## 代表的な性能特性

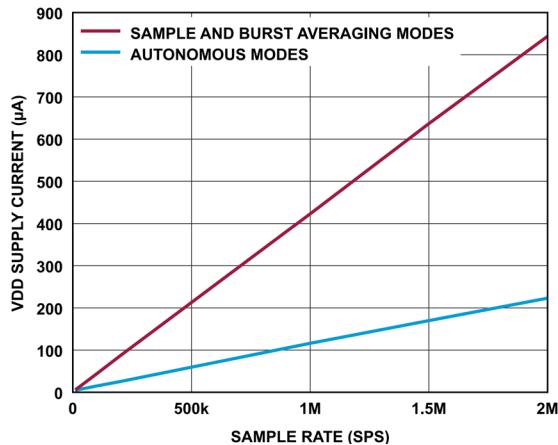

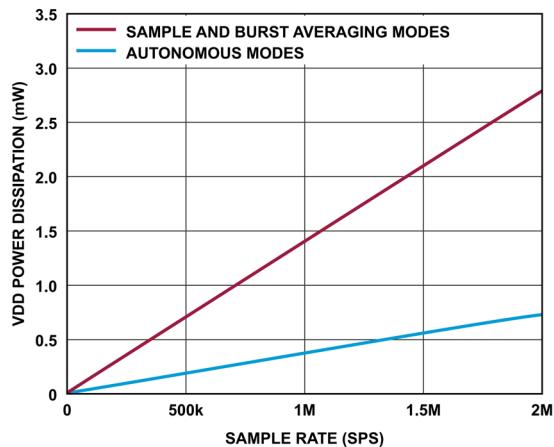

図 29. VDD 消費電力とサンプル・レートの関係

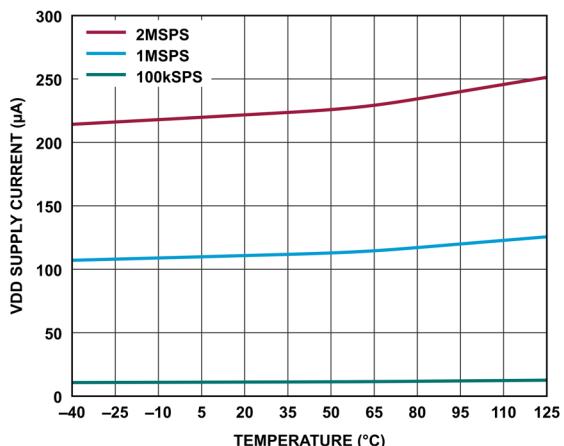

図 32. VDD 電源電流と VDD 電圧の関係（自律モード）

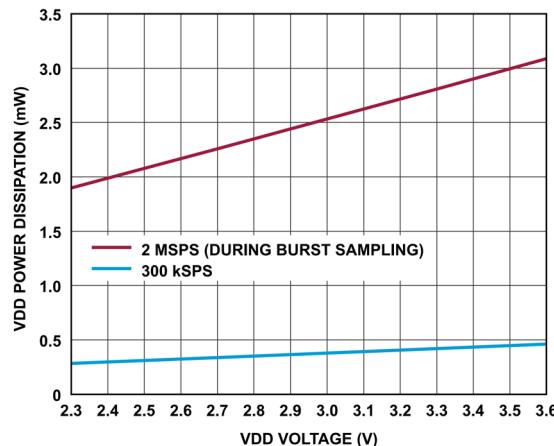

図 30. VDD 消費電力と VDD 電圧の関係

図 33. VDD 電源電流と温度の関係（自律モード）

図 31. VDD 消費電力と温度の関係

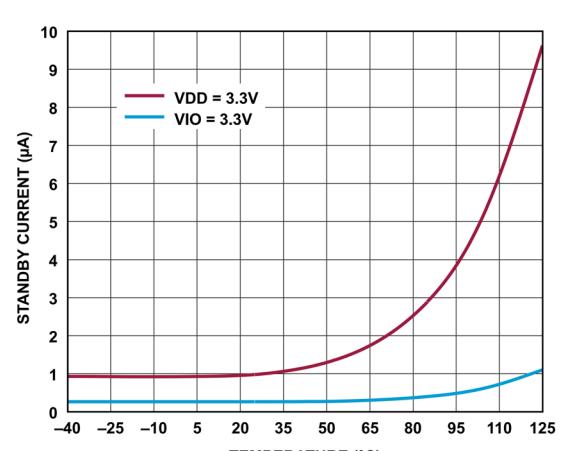

図 34. スタンバイ電流と温度の関係

## 代表的な性能特性

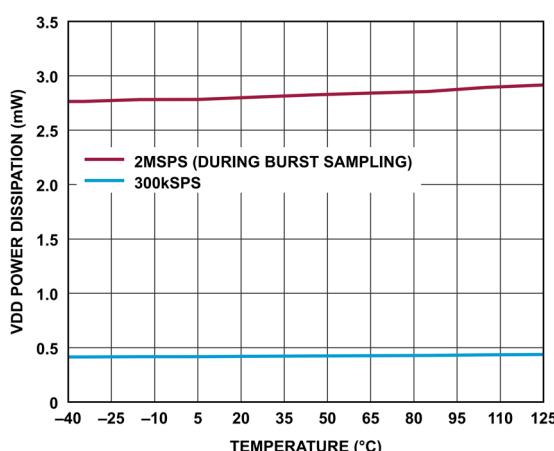

図 35. VDD 消費電力と VDD 電圧の関係（自律モード）

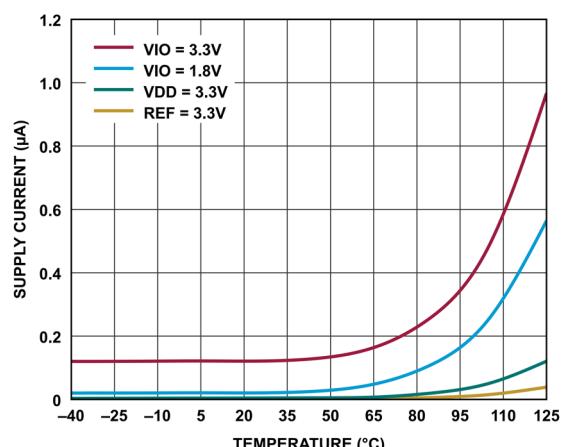

図 37. 電源電流（スリープ・モード）と温度の関係

図 36. VDD 消費電力と温度の関係（自律モード）

## 用語の定義

### 積分非直線性 (INL) 誤差

INL は、負のフルスケールから正のフルスケールまで引かれた直線からの個々のコードのずれを表します。負のフルスケールとして使用される点は、最初のコード遷移点の  $\frac{1}{2}$ LSB 手前に位置します。正のフルスケールは、最後のコード遷移点を  $1\frac{1}{2}$ LSB 上回ったレベルとして定義されます。それは各コードの中心から真の直線までの距離として測定されます。

### 微分非直線性 (DNL) 誤差

理想的な ADC では、コード遷移は 1LSB ごとに生じます。DNL とは、この理想値からの最大偏差のことです。DNL はノード・ミス・コードが確保される分解能で仕様規定されます。

### ゼロ誤差 (ZE)

ゼロ誤差は、理想的なミッドスケール電圧 (0V) とミッドスケール出力コード (0LSB) を生成する実際の電圧との差分です。

### ゲイン誤差 (GE)

最初の遷移 (100…00 から 100…01) は負の公称フルスケールより  $\frac{1}{2}$ LSB 上のレベルで発生します。最後の遷移 (011…10 から 011…11) は、公称フルスケールより  $1\frac{1}{2}$ LSB 下のアナログ電圧で発生します。ゲイン誤差とは、最後の遷移の実際のレベルと最初の遷移の実際のレベルとの差が、理論値レベルの差とどれだけ異なるかを示すものです。

### 総合未調整誤差 (TUE)

TUE は、最も厳しい条件で測定された、全入力範囲にわたる理想的な ADC 伝達関数からのずれであり、フルスケールに対する ppm 単位で規定されます。TUE には、どのデバイスでもゼロ誤差、ゲイン誤差、INL 誤差を組み合わせた影響が含まれています。

### ダイナミック・レンジ (DR)

ダイナミック・レンジは、測定したノイズの合計実効値電圧に対するフルスケール・サイン波の実効値電圧の比率です。ダイナミック・レンジの値はデシベル単位で表されます。ダイナミック・レンジは、全てのノイズ源および DNL アーチファクトを含むように、-60dBFS の信号で測定されます。

### スプリアスフリー・ダイナミック・レンジ (SFDR)

SFDR は、フルスケール入力信号の実効値振幅とピーク・スプリアス信号との差分であり、デシベル (dB) 単位で表されます。

### S/N 比 (SNR)

S/N 比は、ナイキスト周波数未満のすべてのスペクトル成分（高調波と DC を除く）の実効値の総和に対する、フルスケール・サイン波の実効値電圧の比率です。S/N 比の値はデシベル単位で表されます。

### 全高調波歪み (THD)

THD は、フルスケール入力信号の実効値に対する最初の 5 個の高調波成分の実効値総和の比で、単位はデシベルです。

### 信号ノノイズ + 歪み (SINAD) 比

SINAD は、ナイキスト周波数未満の全てのスペクトル成分（高調波成分を含むが DC は除く）の実効値の総和に対する、フルスケール・サイン波の実効値電圧の比率です。SINAD の値はデシベル単位で表されます。

### 有効ビット数 (ENOB)

ENOB は、サイン波入力による分解能の測定値です。ENOB と SINAD の関係は次式で表されます：

$$ENOB = (SINAD \text{ dB} - 1.76) / 6.02.$$

ENOB の単位はビットです。

### 同相モード除去比 (CMRR)

CMRR は、周波数  $f$  の入力同相電圧に印加された-1dBFS のサイン波の電力に対する、ADC 出力における周波数  $f$  の電力の比率です。

$$CMRR(dB) = 10 \times \log(P_{ADC\_IN}/P_{ADC\_OUT})$$

ここで、

$P_{ADC\_IN}$  は、入力に印加された周波数  $f$  の同相電力です。

$P_{ADC\_OUT}$  は、ADC 出力における周波数  $f$  の電力です。

### アパーーチャ遅延

アパーーチャ遅延は、CNV 入力の立上がりエッジから、入力信号が変換のためにホールドされるまでの時間です。

## 動作原理

28

図 38. AD4060 の機能ブロック図

## 概要

AD4060 は、小型で超低消費電力の 12 ビット Easy Drive SAR ADC です。AD4060 の機能セットは、AFE の設計上の制約を緩和し、デジタル・ホストのオーバーヘッドを最小限に抑えることで、低消費電力の高精度計測システムの設計を容易にします。入力容量が小さく、同相入力範囲が広いため、互換性のある AFE コンポーネントの選択肢が広がり、よりシンプルで低消費電力のシグナル・チェーン・ソリューションが可能になります。ブロック平均化フィルタはノイズを低減するとともに、ホスト・プロセッサの演算負荷を軽減します。内蔵のタイマー・ブロックは、自律モニタリング・モード、バースト・サンプリングを可能にするほか、デバイスのパワーサイクリングを ADC のサンプリング・タイミングに同期させて実行できるようにします。また、様々なハードウェア割込みにより、ユーザ定義のイベント間にデジタル・ホストがスリープ状態に入ることが可能です。

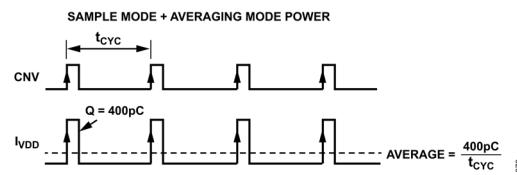

AD4060 は性能と電力効率に関して独自のバランスを提供し、1 回の変換当たりわずか 1.35nJ のエネルギー消費で S/N 比は 73.8dB、INL は  $\pm 0.1$  LSB を確保しています。3.3V 単電源を使用した場合の AD4060 の消費電力は、2MSPS で 2.7mW に過ぎません。AD4060 の消費電力は、サンプル・レートに伴って線形に変化します（図 29 を参照）。変換を行わないスタンバイ時の消費電力は 4.1 $\mu$ W です。スタンバイ電力を更に低減するスリープ・モードも利用可能で、長時間のアイドル動作では消費電力が 430nW まで減少します。

AD4060 は、デバイス設定および ADC データ・リードバックに使用する CRC 機能を備えた 2 線式 I3C を搭載しています。I3C は 1.8V~3.3V のロジック・レベルに対応しています。

AD4060 には複数の動作モードがあり、それぞれ高精度計測または電力効率の高い信号モニタリングに最適化されています。動作原理のセクションは AD4060 の機能ブロックについて説明しており、動作モードのセクションは各動作モードでの機能ブロックの利用方法について説明しています。また、シリアル・インターフェースのセクションは設定レジスタおよび ADC データにアクセスするための I3C プロトコルについて、AD4060 のレジスタの概要のセクションは設定レジスタについて説明しています。

## コンバータの動作

AD4060 は、アクイジション・フェーズと変換フェーズの 2 つのフェーズで動作します。アクイジション・フェーズでは、内部のトラック&ホールド回路が各入力ピン (IN+ と IN-) に接続され、各ピンの電圧を個別に取り込みます。AD4060 は、CONV\_READ レジスタまたは CONV\_TRIGGER レジスタが変換を開始するまで、アクイジション・フェーズのままになります。変換フェーズの開始時に、トラック&ホールド回路は取り込んだアナログ入力信号をサンプリングし、対応する 12 ビットのデジタル・コードを SAR ADC コアが生成します。変換フェーズは、12 ビットの変換結果が得られると終了します。これは、tCONV 仕様として ADC タイミング仕様に示されています。AD4060 のアクイジション・フェーズと変換フェーズは、アクイジション・タイム (tACQ) を最大化するために重なり合っています。

サンプル・モードとバースト平均化モードでは、CONV\_READ または CONV\_TRIGGER レジスタへのアクセスによって変換が開始されます（詳細については、レジスタ・アドレス・ポインタ、CONV\_READ レジスタ、および CONV\_TRIGGER レジスタのセクションを参照）。

AD4060 は内蔵発振器で変換開始をトリガする複数のモードで動作し、その中には自律モードも含まれます。関連する各動作モードに関する特定の ADC タイミング情報については、動作モードのセクションを参照してください。

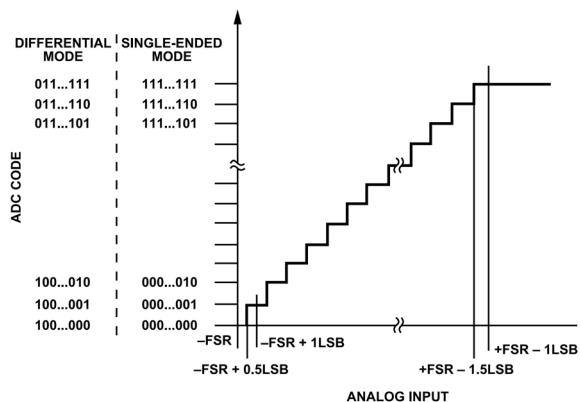

## 伝達関数

図 39 に、AD4060 SAR ADC コアの理想的な伝達関数を示します。AD4060 は、サンプリングした IN+ と IN- の電圧差を、フルスケール範囲 (FSR) に対する比として 12 ビットのデジタル・コードにエンコードします。1LSB の単位は、ADC が分解できる最小の離散電圧ステップを意味しており、これは V<sub>REF</sub> 電圧の閏数です。バースト平均化モードでは、ブロック平均化フィルタが複数の 12 ビット・サンプルの平均を取って、1 つの 14 ビット・コードにします。表 10 と表 11 は、入力電圧とデジタル出力コードの対応をまとめたものです。

## 動作原理

変換後、ADC データは CONV\_READ レジスタと CONV\_TRIGGER レジスタに保存されます。CONV\_READ と CONV\_TRIGGER へのアクセスは、I3C インターフェースを通して 8 ビット・セグメントで行われます（詳細については [CONV\\_READ レジスタ](#) および [CONV\\_TRIGGER レジスタ](#) のセクションを参照）。

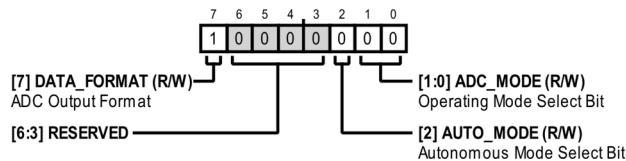

[広い入力同相電圧範囲](#) のセクションに示すように、AD4060 は任意の入力同相電圧に対応しているため、本質的に差分型およびシングルエンド型の両方の信号に対応できます。AD4060 は、2 の補数（符号付き）およびストレート・バイナリ（符号なし）の両方の形式に対応しており、差動信号またはシングルエンド信号を全 12 ビットの ADC 伝達関数に対応付けます。ADC\_MODES レジスタの DATA\_FORMAT ビットを使い、表 10 および表 11 に示す差動モードおよびシングルエンド・モードの伝達関数のいずれかを選択します。

239

図 39. ADC の理想的な伝達関数

表 10. ADC 入力電圧と出力コードの対応関係（サンプル・モード）

| Description      | Differential Mode             |                     | Single-Ended Mode            |                     |

|------------------|-------------------------------|---------------------|------------------------------|---------------------|

|                  | $V_{IN}$                      | Digital Output Code | $V_{IN}$                     | Digital Output Code |

| FSR - 1 LSB      | $(2047/2048) \times V_{REF}$  | 0x7FF               | $(4095/4096) \times V_{REF}$ | 0xFFFF              |

| ...              | ...                           | ...                 | ...                          | ...                 |

| Midscale + 1 LSB | $(1/2048) \times V_{REF}$     | 0x001               | $(2049/4096) \times V_{REF}$ | 0x801               |

| Midscale         | 0 V                           | 0x000               | $(1/2) \times V_{REF}$       | 0x800               |

| Midscale - 1 LSB | $-(1/2048) \times V_{REF}$    | 0xFFFF              | $(2047/4096) \times V_{REF}$ | 0x7FF               |

| ...              | ...                           | ...                 | ...                          | ...                 |

| -FSR + 1 LSB     | $(-2047/2048) \times V_{REF}$ | 0x801               | $(1/2048) \times V_{REF}$    | 0x001               |

| -FSR             | $-V_{REF}$                    | 0x800               | 0 V                          | 0x000               |

表 11. ADC 入力電圧と出力コードの対応関係（バースト平均化モード）

| Description      | Differential Mode             |                     | Single-Ended Mode              |                     |

|------------------|-------------------------------|---------------------|--------------------------------|---------------------|

|                  | $V_{IN}$                      | Digital Output Code | $V_{IN}$                       | Digital Output Code |

| FSR - 1 LSB      | $(8191/8192) \times V_{REF}$  | 0x1FFF              | $(16383/16384) \times V_{REF}$ | 0x3FFF              |

| ...              | ...                           | ...                 | ...                            | ...                 |

| Midscale + 1 LSB | $(1/8192) \times V_{REF}$     | 0x0001              | $(8193/16384) \times V_{REF}$  | 0x2001              |

| Midscale         | 0 V                           | 0x0000              | $(1/2) \times V_{REF}$         | 0x2000              |

| Midscale - 1 LSB | $(-1/8192) \times V_{REF}$    | 0xFFFF              | $(8191/16384) \times V_{REF}$  | 0x1FFF              |

| ...              | ...                           | ...                 | ...                            | ...                 |

| -FSR + 1 LSB     | $(-8191/8192) \times V_{REF}$ | 0x2001              | $(1/16384) \times V_{REF}$     | 0x0001              |

| -FSR             | $-V_{REF}$                    | 0x2000              | 0 V                            | 0x0000              |

## 動作原理

### アナログ入力

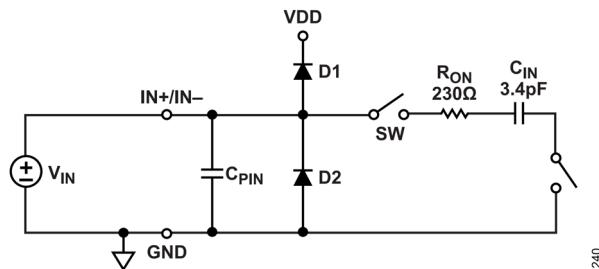

図 40. 等価アナログ入力回路

図 40 は、AD4060 のアナログ入力 (IN+ と IN-) の等価回路を示しています。アナログ入力は、スイッチング容量性負荷としてモデル化されています。アクイジション・フェーズでは、サンプリング・スイッチ (SW) が、 $230\Omega$  のスイッチ・オン抵抗 ( $R_{ON}$ ) を介して、各入力ピンと  $3.4\text{pF}$  のサンプリング・コンデンサ ( $C_{IN}$ ) を直列に接続します。変換フェーズでは、SW を切り離して、サンプリング・コンデンサに保持された IN+ ピンおよび IN- ピンの電圧をサンプリングします。D1 および D2 は、IN+ ピンおよび IN- ピンからそれぞれ VDD 電源および GND につながる ESD ダイオードを表しています。 $C_{PIN}$  は GND に対する各入力ピンのピン容量を表しており、通常は  $2\text{pF}$  です。

AD4060 のアナログ入力の実効負荷特性に関する詳細については、[AD4060 の等価アナログ入力モデル](#) のセクションを参照してください。

### Easy Drive 機能

AD4060 の Easy Drive 対応アナログ入力は、高速、低ノイズ、高出力の特別な ADC ドライバ・アンプへの依存度をできるだけ抑えることで、小型で低消費電力の高精度シグナル・チェーンを実現できるように設計されています。小型のサンプリング・コンデンサは SAR ADC に特有のトランジエント電流グリッチを最小限に抑え、長いアクイジション・フェーズは高サンプル・レートであっても最大限のセトリング・タイムを確保します。RC キックバック・フィルタでは、小型のコンデンサと大きな抵抗を使用して、アンプの安定性に関する懸念を軽減し、小型の受動部品（例えば、0201 NP0/C0G コンデンサ）を使用できるようにします。これらの Easy Drive 機能により、セトリング誤差を招くことなく高出力インピーダンスのフロントエンド回路と AD4060 を接続できるので、低消費電力アンプやセンサーとの互換性が向上します（[アナログ・フロントエンドの設計](#) のセクションを参照）。

AD4060 は LTspice のコンポーネント・ライブラリに含まれており、多様な関連アンプとの協調シミュレーションに対応しています。LTspice モデルは、システム・ノイズおよびセトリング精度のシミュレーションのために、入力換算ノイズ・スペクトル密度および入力遷移負荷をエミュレートします。

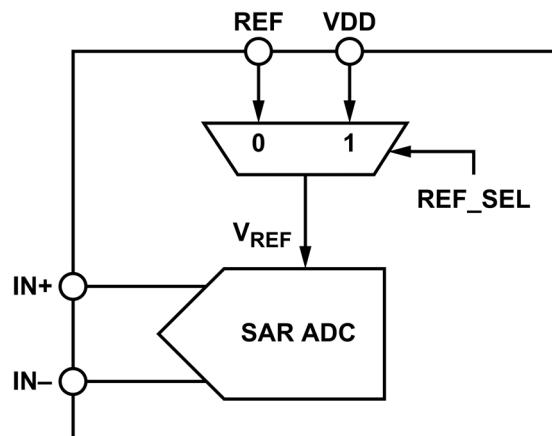

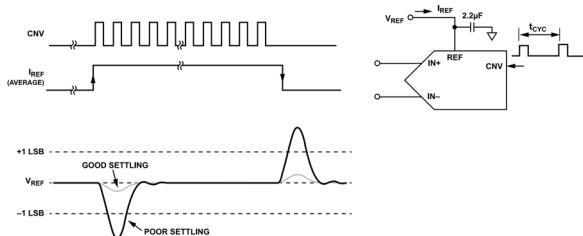

### 電圧リファレンス

$V_{REF}$  電圧は ADC の FSR を設定します（[伝達関数](#) のセクションを参照）。AD4060 の  $V_{REF}$  範囲は  $2.3\text{V} \sim VDD$  で、VDD 電源電圧の最大値は  $3.6\text{V}$  です（[表 1](#) を参照）。

$V_{REF}$  電圧は、ADC 出力コードを決定する SAR ビット・トライアル中にポーリングされます。ビット・トライアル中、SAR コアには過渡的な電荷が流れます。SAR ビット・トライアル中に  $V_{REF}$  電圧を確実に安定させるには、 $2.2\mu\text{F}$  のデカッピング・コンデンサをできるだけ REF ピンの近くに配置します。使用するデカッピング・コンデンサの値が小さくなると（例えば、 $1\mu\text{F}$ ）、わずかに性能が低下する可能性があります。AD4060 を使って電圧リファレンスを組み合わせるための詳しい推奨事項については、[リファレンス回路設計](#) のセクションを参照してください。

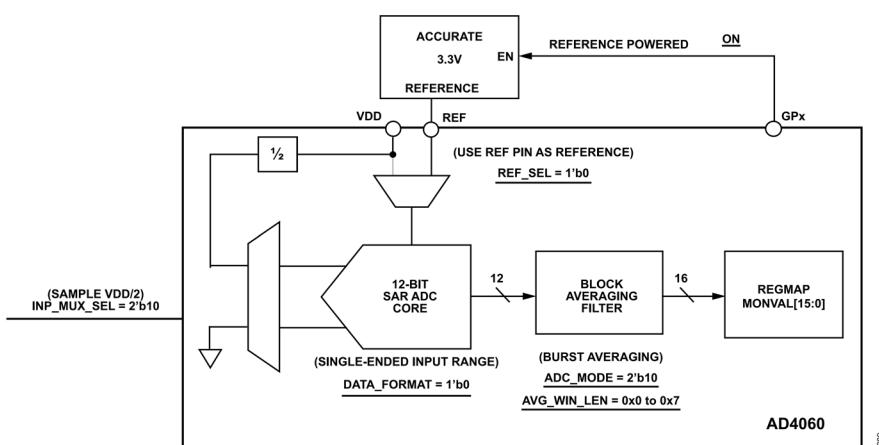

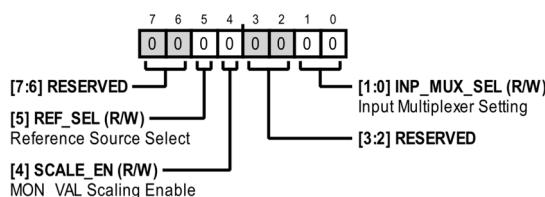

### リファレンス選択モード

AD4060 の  $V_{REF}$  電圧は、REF 入力ピンまたは VDD 電源ピンから供給できます。デフォルトでは、REF ピンが  $V_{REF}$  ソースとして機能します。この設定は、[表 1](#) に示す性能仕様の達成を目的としたモードです。精度が重要ではない低消費電力の計測に対応したり、システムが長期間にわたり電圧リファレンスをパワーサイクリングしてシステム電力を節約できるようにしたりするために、VDD 電源電圧は選択が可能です。 $V_{REF}$  ソースの選択は、ADC\_CONFIG レジスタの REF\_SEL ビットで制御します（[表 48](#) を参照）。

AD4060 には自動ゲイン・スケーリング機能が搭載されています。この場合、ADC コアは VDD 電源電圧に対する比として REF 電圧をサンプリングし、適切なゲイン・スケーリング値を MON\_VAL レジスタに格納して、VDD を  $V_{REF}$  ソースとして使用しても REF の場合と同じ ADC 伝達関数になるようにします。これにより、システムは電圧リファレンス回路を長期間にわたりパワーダウンしても、同程度の性能レベルを保つことができます。自動ゲイン・スケーリング機能の詳細については、[リファレンスのシャットダウンを利用した高精度の達成](#) のセクションを参照してください。

図 41. リファレンス・ソースの選択

## 動作原理

### デジタル処理機能

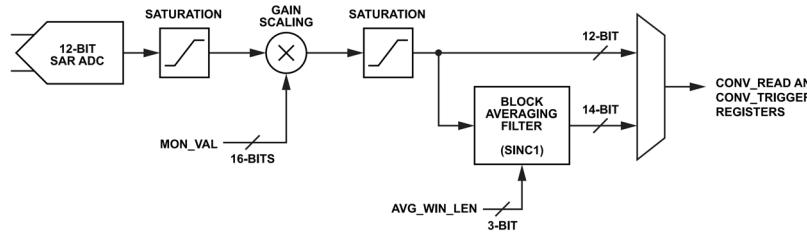

図 42. AD4060 のデジタル処理機能

AD4060 には、デジタル・ホスト・プロセッサの演算負荷を軽減するために ADC データに適用できる複数のデータ処理機能が搭載されています。図 42 は利用可能なデータ処理機能のブロック図です。各ブロックの機能および構成については、以下のセクションで詳細に説明します。なお、これらのデジタル処理機能は自律モードでは使用されません。

### ゲイン・スケーリング

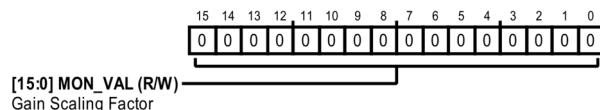

ゲイン・スケーリング機能では、符号なし 16 ビットのデジタル・ゲイン係数を 12 ビットの ADC 結果に適用します。ゲイン・スケーリングは、システム・ゲイン誤差を補正するために適用できます。ゲイン・スケーリング係数は、以下の式に従って、MON\_VAL スケーリング・レジスタ内にある MON\_VAL ビット・フィールドで設定されます。

$$Code_{OUT} = Code_{IN} \times (MON\_VAL / 0x8000) \quad (2)$$

ここで、MON\_VAL は 0x0000 から 0xFFFF の範囲であり、0～1.99997 の実効ゲイン範囲に相当します。

ゲイン・スケーリングは、VDD 電源を V<sub>REF</sub> ソースとして使用する場合に、ADC 伝達関数のスケーリングにも使用できます（リファレンス選択モードのセクションを参照）。AD4060 は、VDD 電源電圧と REF 入力電圧の比を計測し、伝達関数が同じになるように MON\_VAL レジスタの値を自動的に調整するよう設定できます。外部電圧リファレンス回路は、システムの消費電力を削減するためにパワーダウンさせることができます。

詳細については、リファレンスのシャットダウンを利用した高精度の達成のセクションを参照してください。

なお、ゲインをサンプルに適用すると、Code<sub>OUT</sub>（式 2）が 12 ビットのフルスケールを超えた場合、数値が飽和する可能性があります（フルスケール飽和のセクションを参照）。ゲイン・スケーリング・ブロックの出力が飽和しないように、MON\_VAL ビット・フィールドは必ず適切な値に設定してください。

ゲイン・スケーリングはデフォルトでディスエーブルされており、ADC\_CONFIG レジスタの SCALE\_EN ビット・フィールドを 1 に設定するとイネーブルされます（表 48 を参照）。

### フルスケール飽和

変換結果は、サンプリングされたアナログ入力電圧が表 1 に示す入力範囲の制限仕様を超えた場合、（データ処理の前に）デジタル的に飽和します。AD4060 には、ADC コアとゲイン・スケーリング・ブロックのデジタル出力コードが最大値または最小値に達したことを検出する飽和ブロックが、それぞれ ADC コアの出力とゲイン・スケーリング・ブロックの出力に設けられています。

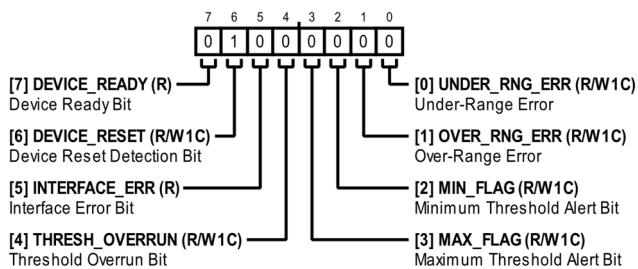

いずれかの飽和ブロックが最大値に飽和したコードまたは最小値に飽和したコードを検出すると、DEVICE\_STATUS レジスタの OVER\_RNG\_ERR および UNDER\_RNG\_ERR のフラグが設定されます。差動モードでは、12 ビットの結果が 0x7FF で最大値に、0x800 で最小値に飽和します。シングルエンド・モードでは、12 ビットの結果が 0xFFFF で最大値に、0x000 で最小値に飽和します（差動モードおよびシングルエンド・モードの説明は伝達関数のセクションを参照）。

ブロック平均化フィルタを使用してフィルタ入力データに飽和がないことを確認する場合は、OVER\_RNG\_ERR および UNDER\_RNG\_ERR のフラグを周期的にポーリングできます。OVER\_RNG\_ERR および UNDER\_RNG\_ERR のフラグは 1 を書き込むことでクリアするビットなので、デジタル・ホストがポーリングできるまでその状態を保持します。

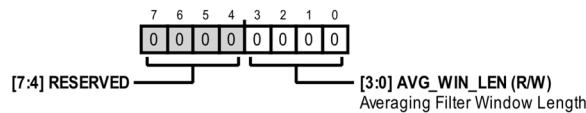

### ブロック平均化フィルタ

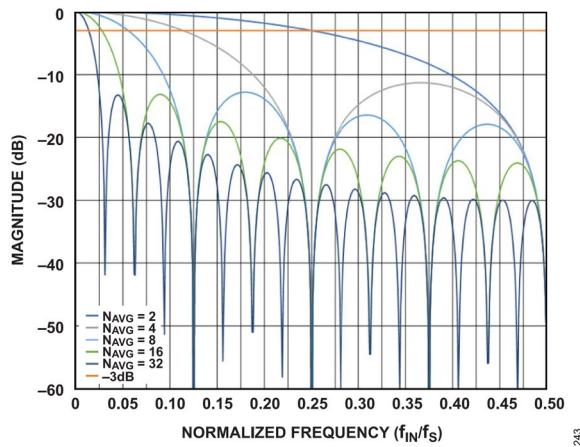

AD4060 には、平均化比率 (N<sub>AVG</sub>) を 2～256 にプログラムできるブロック平均化フィルタが搭載されています。ブロック平均化フィルタは、デバイスがバースト平均化モードのときに自動的にイネーブルされます。ブロック平均化フィルタは、SINC1 周波数応答を示します。図 43 は、N<sub>AVG</sub> が 2、4、8、16、32 の場合の平均化フィルタの周波数応答を示しています。

ブロック平均化フィルタをイネーブルすると、14 ビットの平均結果を生成する前に、12 ビットの ADC 結果のブロックが蓄積されます。N<sub>AVG</sub> は、平均化された結果ごとの ADC サンプルの数を指します。ブロック平均化フィルタは、N<sub>AVG</sub> 個のサンプルのブロックをそれぞれ処理した後にリセット（クリア）されます。N<sub>AVG</sub> 設定は、以下の式を使用して、AVG\_CONFIG レジスタの AVG\_WIN\_LEN ビット・フィールドで設定されます（表 49 を参照）。

$$N_{AVG} = 2^{AVG\_WIN\_LEN + 1} \quad (3)$$

## 動作原理

図 43. ブロック平均化フィルタの周波数応答例

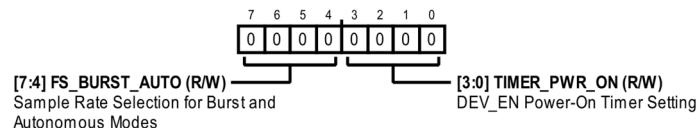

## 内蔵タイマー

AD4060 は、バースト平均化モードと両方の自律モード（モニター・モードとトリガ・モード）で ADC サンプリング・クロックを生成するためのタイマーを内蔵しています。これらのモードにおけるサンプリング周波数は TIMER\_CONFIG レジスタの FS\_BURST\_AUTO ビット・フィールドで設定され、2MSPS～111SPS の範囲になります。AD4060 で提供されるすべての公称サンプリング・クロック周波数 (fosc) については、[レジスタの詳細](#)のセクションの表 52 を参照してください。これらのモードにおける実際のサンプリング周波数は、fosc の ±15% の範囲内となるようサポートされています（[タイミング仕様](#)のセクションを参照）。

内蔵タイマーは、DEV\_EN 信号の遅延も制御します（[デバイス・イネーブル信号](#)のセクションを参照）。tPWR\_ON 遅延は TIMER\_PWR\_ON ビット・フィールドで設定され、これも TIMER\_CONFIG レジスタに含まれています。tPWR\_ON の設定範囲は 0.5μs から 9000μs までです。すべての公称 tPWR\_ON 遅延オプションについては、[レジスタの詳細](#)のセクションの表 52 を参照してください。

モニター・モードでは、閾値が検出されても内蔵サンプリング・クロックはディスエーブルされず、MAX/MIN 閾値割込みビット・フィールドと信号のアサート後でもデバイスはサンプリングを続行します。詳細については[モニター・モード](#)のセクションを参照してください。

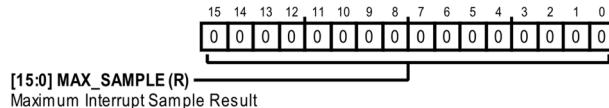

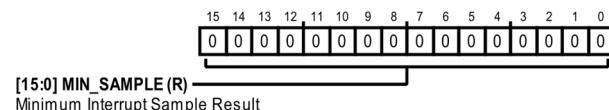

トリガ・モードでは、閾値が検出されても内蔵サンプリング・クロックはディスエーブルされません。同時に、ADC がイネーブルされて N ビット変換が行われ、MAX\_SAMPLE、MIN\_SAMPLE、MAX\_THRESH\_INTR、MIN\_THRESH\_INTR、および THRESH\_OVERRUN ビット・フィールド/レジスタの内容が更新されます。詳細については[トリガ・モード](#)のセクションを参照してください。

## 電源

AD4060 には次の 3 つのパワー・ドメインがあり、その範囲は表 1 に記載されています。

- ▶ VDD はアナログ電源レールです。

- ▶ CLDO は+1.8V の ADC コア電源レールであり、内蔵の+1.8V LDO レギュレータにより生成されます。

- ▶ VIO は、デジタル・インターフェース用のロジック電源レールです。

VDD 電源と VIO 電源は外部から供給する必要があります。CLDO 電源は、VDD レールをソースとする内蔵の+1.8V LDO レギュレータにより内部で生成されます。VDD 電源電流は ADC のサンプリング・レートに依存します。これは、VDD 電源電流が内部 LDO レギュレータを経由して SAR ADC コアに供給されるためです（[VDD 消費電力](#)のセクションを参照）。スリープ・モードでは内部 LDO レギュレータがパワーダウンし、VDD スタンバイ電流が 10nA まで減少します（表 1 および[スリープ・モード](#)のセクションを参照）。

AD4060 に電源シーケンシングは不要です。VDD 電源と VIO 電源の最小許容立ち上がり時間は 100μs です。デバイス・リセットは、VDD 電源および VIO 電源が安定した後に行なうことを推奨します（[パワーオン・リセット](#)のセクションを参照）。

VDD、CLDO、VIO の各ピンは、それぞれ 1μF のコンデンサで GND からデカッピングすることを推奨します。VDD を V<sub>REF</sub> ソースとして選択した場合（[リファレンス選択モード](#)のセクションを参照）、または VDD および REF の各ピンを共通の外部ソースで駆動する場合は、VDD および REF を共通の 2.2μF のコンデンサでデカッピングすることを推奨します。

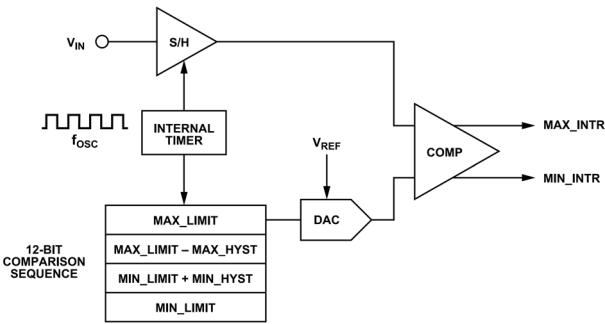

## コンパレータの動作

AD4060 の ADC コアは、閾値の自律的な検出およびモニタリングのために、低消費電力の 12 ビット・ウインドウ・コンパレータ・モードを備えています。図 44 は、自律モードで使用されるウインドウ・コンパレータの簡略化された回路図です。

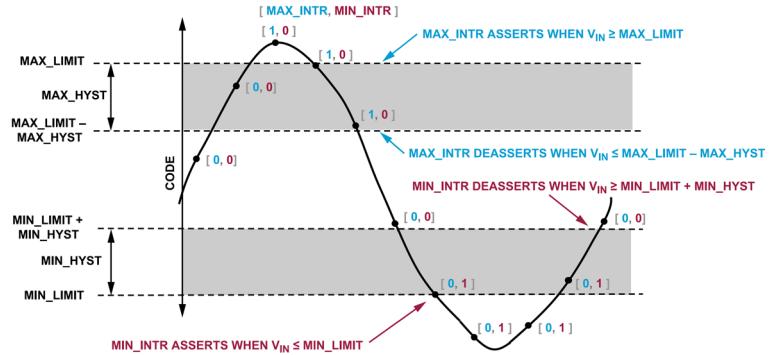

AD4060 には、[自律モード](#)のセクションに示すように、2 つの自律サンプリング・モードがあります。これらの自律モードのいずれかがイネーブルされると ADC はコンパレータ・モードに入り、内蔵タイマーがサンプリング・クロックとして機能します（[内蔵タイマー](#)のセクションを参照）。コンパレータは、ユーザがプログラム可能な 4 つの閾値領域との一連の比較を各サンプルに対して順次行い、信号がこれらの領域に入ったときに、アラート・フラグとハードウェア割込みを生成します。

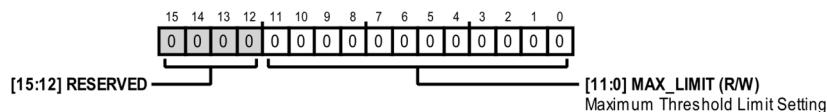

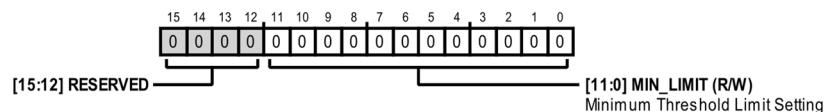

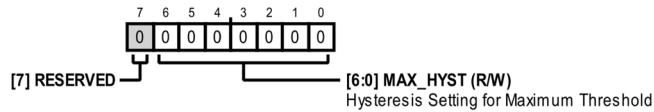

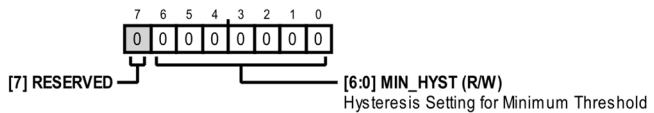

図 45 は、最大および最小の閾値で設定された範囲外の領域を示しています。最大および最小の閾値は、MAX\_LIMIT および MIN\_LIMIT の各ビット・フィールドを通じて、ユーザがプログラム可能です。MAX\_LIMIT および MIN\_LIMIT の各フィールドは、12 ビットのコンパレータ分解能のため、それぞれ 12 ビット幅です。最大および最小の閾値には、MAX\_HYST および MIN\_HYST の各フィールドでそれぞれ設定される個別のヒステリシス設定もあり、これにより、アラート信号を自動でクリアするための別の閾値が定められます。詳細については、[自律モード](#)のセクションを参照してください。

MAX\_LIMIT および MIN\_LIMIT の各フィールドのデータ形式は、選択された入力範囲モードに一致しています（[伝達関数](#)のセクションを参照）。MAX\_LIMIT および MIN\_LIMIT の各フィールドは、差動モードでは 2 の補数で表され（DATA\_FORMAT = 1'b1）、シングルエンド・モードではストレート・バイナリで表されます（DATA\_FORMAT = 1'b0）。MAX\_HYST および MIN\_HYST の各フィールドは、入力モードの設定に関係なく、常にストレート・バイナリです。

コンパレータは、レジスタ・マップに 2 つのアラート信号と自動でクリアされない 2 つのアラート・ビットを備えています。MAX\_INTR および MIN\_INTR の各信号は、それぞれ最大および最小の閾値イベント用アラート信号です。MAX\_INTR および MIN\_INTR の各信号は、GP0 ピンおよび GP1 ピンのいずれかまたは両方にルーティングできます（[割込み信号および制御信号](#)

## 動作原理

のセクションを参照)。MAX\_FLAG および MIN\_FLAG の各ビットはステイッキー・ビットで、1 を書き込むことで DEVICE\_STATUS レジスタのビットをクリアします。DEVICE\_STATUS レジスタには、コンパレータが MAX\_FLAG または MIN\_FLAG のビットをクリアされる前に設定しようとした場合に、その都度設定される閾値超過ビット (THRESH\_OVERRUN) も含まれています。

MAX\_IBI と MIN\_IBI がイネーブルされている場合は、最大閾値イベントによって MAX\_IBI が、最小閾値イベントによって MIN\_IBI がトリガされます。詳細については [インバンド割込み](#) のセクションを参照してください。

図 44. 自律モード・ウィンドウ・コンパレータの簡略化された回路図

図 45. 閾値イベント領域

## 動作原理

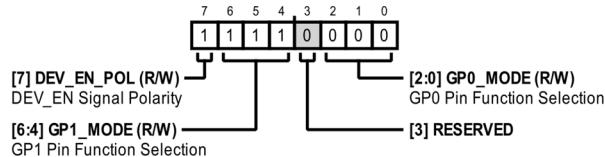

### 割込み信号および制御信号

AD4060 は、ADC サンプリングに対するアナログ・フロントエンド処理とデジタル・バックエンド処理を同期させるために、複数のデジタル信号を生成します。これらの信号は、GP\_CONFIG レジスタの GP0\_MODE および GP1\_MODE の各フィールドを使って、それぞれの汎用ピン (GP0 と GP1) に割り当てることができます。以下のセクションでは、AD4060 の各デジタル信号の機能とタイミングについて詳しく説明します。

表 12 および表 50 は、GPx\_MODE ビット・フィールドの各設定に対応する GPx 信号の割り当てを示しています。

表 12. GP0 および GP1 の信号割り当て制御

| GPx_MODE Setting | GP0 Signal Assignment     | GP1 Signal Assignment |

|------------------|---------------------------|-----------------------|

| 3'h0             | Disabled/high-Z (default) | Disabled/high-Z       |

| 3'h1             | GP0_INTR                  | GP1_INTR              |

| 3'h2             | RDY                       | RDY                   |

| 3'h3             | DEV_EN                    | DEV_EN                |

| 3'h4             | Invalid                   | Invalid               |

| 3'h5             | Logic low                 | Logic low             |

| 3'h6             | Logic high                | Logic high            |

| 3'h7             | Invalid                   | DEV_RDY (default)     |

### インバンド割込み

AD4060 は、特定のイベントに反応する MIPI I3C 仕様のインバンド割込み (IBI) 機能を備えています。IBI イベントがトリガされると、AD4060 はデジタル・ホストに割込み要求を送ります。AD4060 は、I3C ターゲット・デバイスが I3C バス経由で IBI を送信する際の規格と規則を定めた I3C 仕様に準拠しています。

MIPI I3C 仕様のセクション 5.1.3.2.2 によると、ターゲット・デバイスが IBI の送信を開始するには、I3C バスが使用可能な状態になっていなければなりません (表 5 の tIBI\_ISSUE を参照)。IBI をイネーブルするときは、各 I3C フレームの前にプロードキャスト・アドレス 0x7E を置き、AD4060 がその TGT\_ADDR を設定して IBI 要求を開始できるようにすることを推奨します。

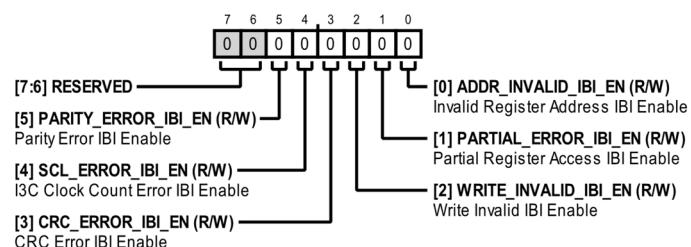

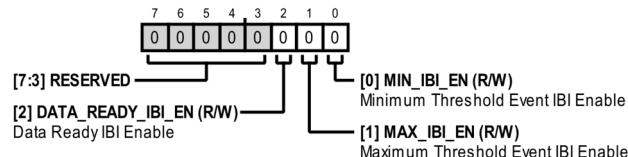

IBI は ENEC CCC を使ってイネーブルし、DISEC CCC を使ってディスエーブルできます (詳細についてはコモン・コマンド・コード (CCC) のセクションを参照)。表 13 に、AD4060 の IBI 一覧、そのトリガ条件、およびイネーブル・ビットを示します。それぞれの IBI は個別にイネーブルまたはディスエーブルできます (詳細についてはインターフェース・エラー IBI イネーブル・レジスタのセクションと ADC IBI イネーブル・レジスタのセクションを参照)。

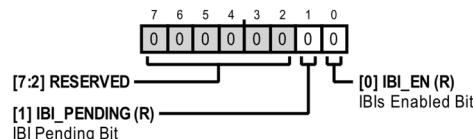

IBI\_STATUS レジスタの IBI\_PENDING ビット・フィールドは、AD4060 に保留中の IBI があるかどうかを示します。IBI は、コントローラが IBI 要求を処理するまで保留のままになります。MIPI I3C 仕様のセクション 5.1.6.2 には、コントローラがターゲット・デバイスの IBI 要求を処理する方法の概要が示されています。IBI\_STATUS レジスタの IBI\_EN ビット・フィールドは、現在 IBI がイネーブルされているかディスエーブルされているかを示します (詳細については IBI ステータス・レジスタのセクションを参照)。

MAX\_IBI は MAX 閾値イベントが発生したことを示します。これは、入力信号値が、MAX\_LIMIT レジスタに保存された制限値を超えたことを意味します。

MIN\_IBI は MIN 閾値イベントが発生したことを示します。これは、入力信号値が、MIN\_LIMIT レジスタに保存された制限値を下回ったことを意味します。

DATA\_READY\_IBI は、CONV\_TRIGGER レジスタから新しい ADC データを読み出せる状態になったことを示すために定義されたものです。DATA\_READY\_IBI は、サンプル・モードとバースト平均化モードの両方で 1 回の変換またはバースト変換が終了し、コントローラが I3C バスを介してデータを読み出せる状態になったときに、変換終了イベントによってトリガされます。

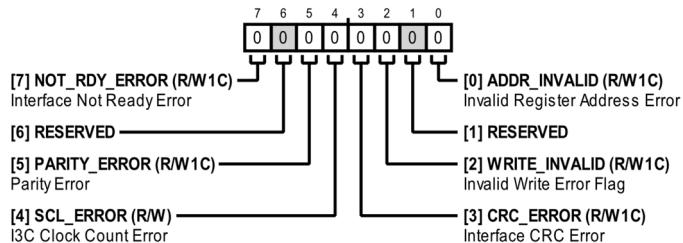

INTERFACE\_ERROR\_IBI は、I3C バス・インターフェースにエラーが生じたときに生成されます。この IBI は、パリティ・エラー、SCL エラー、CRC エラー、書き込み無効エラー、アドレス無効エラーを含め、イネーブルされた何らかのインターフェース・エラー・ソースによってトリガできます。

表 13. IBI トリガとイネーブル・ビット

| IBI                 | IBI Trigger                                                                            | IBI Enable Bit                                                                                            |

|---------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| MAX_IBI             | MAX Threshold Event                                                                    | MAX_IBI_EN                                                                                                |

| MIN_IBI             | MIN Threshold Event                                                                    | MIN_IBI_EN                                                                                                |

| DATA_READY_IBI      | End of Conversion/ Data Valid<br>(Address Pointer → CONV_TRIGGER)                      | DATA_READY_IBI_EN                                                                                         |

| INTERFACE_ERROR_IBI | Parity Error<br>SCL Error<br>CRC Error<br>Write Invalid Error<br>Address Invalid Error | PARTY_ERROR_IBI_EN<br>SCL_ERROR_IBI_EN<br>CRC_ERROR_IBI_EN<br>WRITE_INVALID_IBI_EN<br>ADDR_INVALID_IBI_EN |

### 必須データ・バイト

ターゲット・デバイスによって生成された IBI をコントローラが読み出すと、AD4060 は MIPI I3C 仕様の定義に従い、I3C バスを介して必須データ・バイト (MDB) を送信します。MDB は、割込みグループ識別子フィールド (MDB[7:5]) と特定グループ識別子フィールド (MDB[4:0]) を通じて、どのタイプの IBI が生成されたかを示します。

I3C バス上でインターフェース・エラーが検出されると、INTERFACE\_ERR がアサートされます。インターフェース・エラーが発生した場合、ユーザは INTERFACE\_STATUS レジスタをチェックして、そのエラーに対応する具体的なフィールドを見つける必要があります。INTERFACE\_ERR は、ユーザがレジスタ書き込みを通じて 1 を書き込むとクリアされます。

入力信号が MAX\_LIMIT を超えると MAX\_THRESH\_INTR がアサートされます。

入力信号が MIN\_LIMIT を下回ると MIN\_THRESH\_INTR がアサートされます。

MAX\_THRESH\_INTR と MIN\_THRESH\_INTR はステッキー・ビットです。つまり、このビットが 1 に設定されると、入力信号が MAX\_HYST レジスタと MIN\_HYST レジスタによって設定

## 動作原理

された規定範囲内に復帰したとしても、自動的にクリアされることはありません。これらのビットは、レジスタ書き込みを通じてユーザが 1 を書き込むことでクリアされます（詳細については[自律モード](#)のセクションを参照）。

MAX\_THRESH\_INTR および MIN\_THRESH\_INTR のビット・フィールドは、GP1 ピンまたは GPO ピンにオプションで出力される MAX\_INTR および MIN\_INTR 信号と混同しないように注意が必要です。MAX\_INTR と MIN\_INTR は、入力電圧が MAX\_HYST レジスタと MIN\_HYST レジスタによって定義された範囲内に戻ると、自動的にクリアされます。

表 14. 必須データ・バイト - 割込みグループ識別子フィールド

| IBI                    | Interrupt Group Identified Field                              | MDB[7:5]         |

|------------------------|---------------------------------------------------------------|------------------|

| MAX_IBI (Monitor Mode) | User Defined                                                  | 3'b000           |

| MIN_IBI (Monitor Mode) | User Defined                                                  | 3'b000           |

| MAX_IBI (Trigger Mode) | Pending Read Notification <sup>1</sup>                        | 3'b101           |

| MIN_IBI (Trigger Mode) | Pending Read Notification                                     | 3'b101           |

| DATA_READY_IBI         | Pending Read Notification                                     | 3'b101           |

| INTERFACE_ERROR_IBI    | Either User Defined or Pending Read Notification <sup>2</sup> | 3'b000 or 3'b101 |

<sup>1</sup> MIPI I3C仕様のセクション 5.1.6.2.2 には、ターゲット・デバイスが読み出し保留通知と共に IBI 要求と MDB を送信したときの、コントローラの役割が記載されています。

<sup>2</sup> INTERFACE\_ERROR\_IBI は ADC の動作モードとは無関係に発生する可能性があり、この IBI はその時々でどちらかの割込みグループ識別子コードを示します。したがって、インターフェース・エラー・フラグ (MDB[3]) が 1 に設定された場合は（表 15 を参照）保留中の読み出しを無効なものとして扱い、インターフェース・エラーがクリアされるまで ADC データを読み出さないようにする必要があります。

表 15. 必須データ・バイト - 特定割込み識別子フィールド

| MDB[4] | MDB[3]        | MDB[2] | MDB[1]          | MDB[0]          |

|--------|---------------|--------|-----------------|-----------------|

| 1'b1   | INTERFACE_ERR | 1'b0   | MAX_THRESH_INTR | MIN_THRESH_INTR |

## 静的ロジック出力

AD4060 の GPO および GP1 デジタル出力は、静的なロジック・ローまたはロジック・ハイ・レベルに設定できます。この機能により、デジタル・ホストは AD4060 経由で外部デバイスのロジック設定を制御できるようになり、必要な GPIO リソースを削減します。ロジック出力電圧の仕様および対応する負荷電流条件は、表 1 の  $V_{OL}$  および  $V_{OH}$  で定められています。

## データ・レディ信号

データ・レディ信号 ( $\overline{RDY}$ ) は、新しい ADC データが I3C インターフェース経由で読み出す準備ができたことを示す、アクティブ・ローの割込み信号です。

何らかの形でデバイスをリセットした後は、常に  $\overline{RDY}$  がハイになります。  $\overline{RDY}$  は、ADDR\_PTR が CONV\_READ レジスタと CONV\_TRIGGER レジスタ以外のアドレスをポイントしているときもハイになります。

ADDR\_PTR が CONV\_READ または CONV\_TRIGGER をポイントしているときは、変換スタート時に  $\overline{RDY}$  がハイになり、新しい変換結果が読み出し可能な状態になるとハイからローに遷移します。サンプル・モードでは、変換フェーズ終了時に  $\overline{RDY}$  がローになり、新しい 12 ビットの結果が使用できる状態になったことを示します（サンプル・モードのタイミング図を参照）。バースト平均化モードでは、 $\overline{RDY}$  は  $N_{AVG}$  回の変換後にローになり、新しい 14 ビットの平均結果が利用可能になったことを示します（バースト平均化モードのタイミング図を参照）。

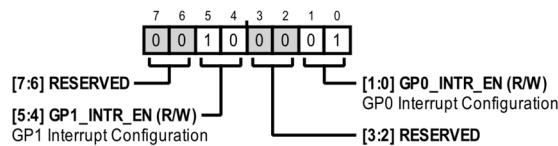

## 閾値アラート信号

コンパレータの閾値アラート信号 MAX\_INTR および MIN\_INTR は、GPO\_INTR および GP1\_INTR の各信号を介して GPO ピンまたは GP1 ピンにルーティングできます（[自律モード](#)のセクションを参照）。GPx\_INTR 信号のいずれかは、MAX\_INTR 信号、MIN\_INTR 信号、またはその両方の論理和に割り当てることができます、最小値および最大値と交差する際に個別のハードウェア割込みを駆動するか、単一の割込みにまとめるかを柔軟に選択できます。デフォルトでは、MAX\_INTR が GP1\_INTR に、MIN\_INTR が GPO\_INTR に割り当てられます。

アラート信号の GPx ピンへのマッピングは、INTR\_CONFIG レジスタの GPO\_INTR\_EN および GP1\_INTR\_EN の各ビット・フィールドによって制御されます（表 16 および表 51 を参照）。

表 16. GPx\_INTR の設定

| GPx_INTR_EN Setting | GPx_INTR Signal Assignment |

|---------------------|----------------------------|

| 2'h0                | Neither interrupt          |

| 2'h1                | MIN_INTR                   |

| 2'h2                | MAX_INTR                   |

| 2'h3                | (MAX_INTR) OR (MIN_INTR)   |

## デバイス・レディ信号

デバイス・レディ信号 (DEV\_RDY) は、AD4060 が電源投入またはリセットのルーチンを完了し、シリアル・インターフェース通信を受け付ける準備ができたことを示すアクティブ・ハイの信号です。DEV\_RDY 信号は電源投入またはリセット後に GP1 ピンにルーティングされるので、デジタル・ホストは、AD4060 がアクティブであるかどうかを知るためにこの信号をモニターできます。DEV\_RDY 信号のタイミング図については、[デバイスのリセット](#)のセクションを参照してください。

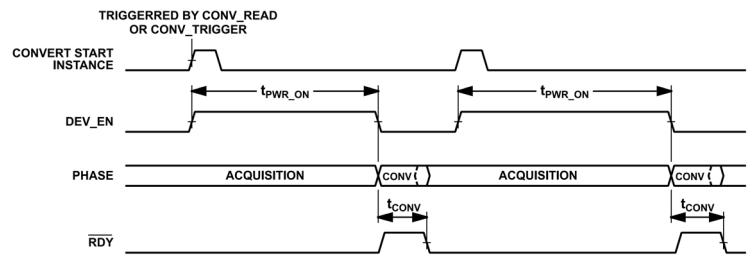

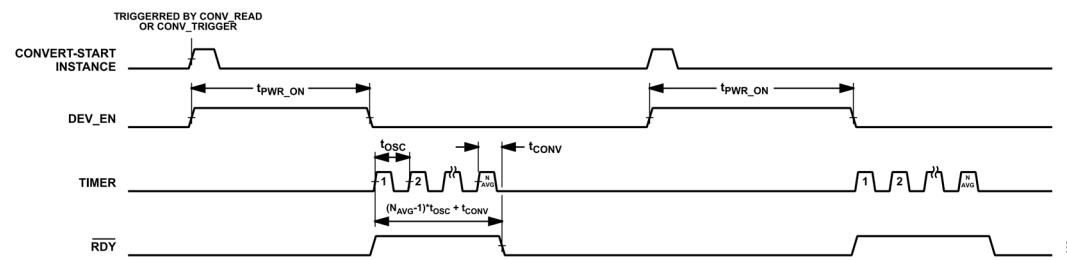

## デバイス・イネーブル信号

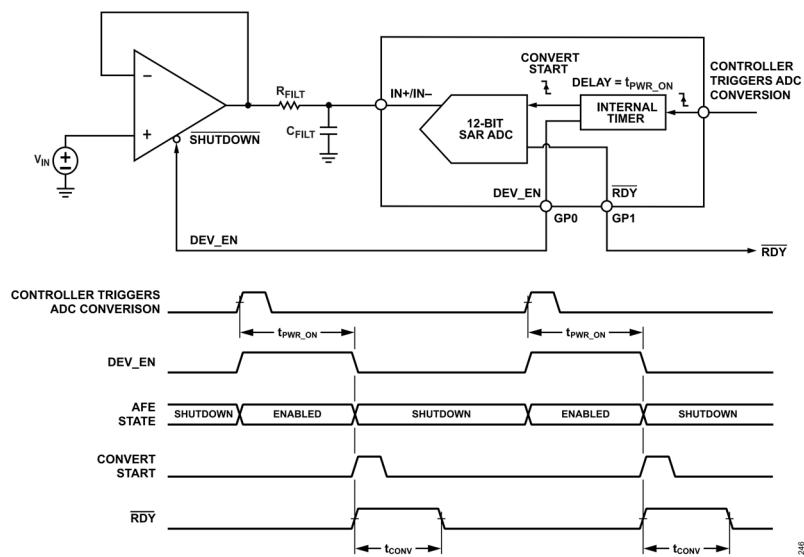

AD4060 は、DEV\_EN と呼ばれる、シグナル・チェーンのパワー・サイクリング制御信号を使用します。DEV\_EN 信号は、シグナル・チェーン・デバイス（アンプ、センサー、電圧リファレンスなど）のイネーブル状態およびパワーダウン状態を ADC のサンプリング・タイミングと同期させ、システムの消費電力を最適化すると共に、パワーオン遅延によるサンプリング・エラーを最小限に抑えます。図 46 は、DEV\_EN 信号を利用してサンプル間でアンプをパワーダウンさせる代表的なアプリケーション回路です。

## 動作原理

DEV\_EN 信号がイネーブルされると、内蔵タイマーは、ADC 変換スタートの立上がりエッジでトリガされるワンショット・タイマーとして機能します。タイマー遅延 ( $t_{PWR\_ON}$ ) は、ADC のサンプリング・タイミングの前にアンプの電源をオンにしている時間を制御し、接続されるデバイスの特定の起動セトリング時間仕様に合うようにプログラムできます。レジスタの詳細のセクションに示す表 52 は、TIMER\_PWR\_ON ビット・フィールドで利用可能な公称  $t_{PWR\_ON}$  設定を示しています。

DEV\_EN 信号は、GP0 または GP1 のデジタル出力に割り当てることでイネーブルされます（表 12 を参照）。DEV\_EN 信号は、GP\_CONFIG レジスタの DEV\_EN\_POL ビット・フィールドでアクティブ・ハイまたはアクティブ・ローに設定できます（表 50 を参照）。DEV\_EN はデフォルトでアクティブ・ハイです。

図 51 と図 55 に、ADC の変換スタートを基準とした DEV\_EN 信号と ADC サンプリングのタイミング図を示します。

CONV\_READ レジスタを使って ADC の変換をトリガする場合は、読み出しコマンドの最後にあるストップ（P）の SDA 立上がりエッジで変換が開始されます（CONV\_READ レジスタのセクションを参照）。この変換スタート時に DEV\_EN 信号がアサートされます。CONV\_TRIGGER レジスタを使って ADC の変換をトリガする場合は、書き込みコマンドの最後にあるストップ（P）の SDA 立上がりエッジで変換が開始されます（CONV\_TRIGGER レジスタのセクションを参照）。この変換スタート時に DEV\_EN 信号がアサートされます。

サンプル・モードでは、変換が完了するごとに DEV\_EN がデアサートされます。バースト平均化モードでは、DEV\_EN はサンプル・バーストの最後の変換が完了するまでアサートされたままでです。DEV\_EN は、自律モードには対応していません。

図 46. DEV\_EN 信号を用いた代表的なアプリケーション回路

## 動作モード

表 18 に、AD4060 の機能モードの概要を示します。各モードの ADC およびシリアル・インターフェースの機能は、次のセクションに記載されています。

パワーアップ後とデバイス・リセット後の AD4060 の ADC コードはアイドル状態になります。動作モードは、表 18 に示すように設定レジスタを介して選択されます。レジスタの書き込みおよび読み出しに関する I<sub>C</sub> プロトコルは、[レジスタの読み出し](#)および[レジスタへの書き込み](#)のセクションで説明します。

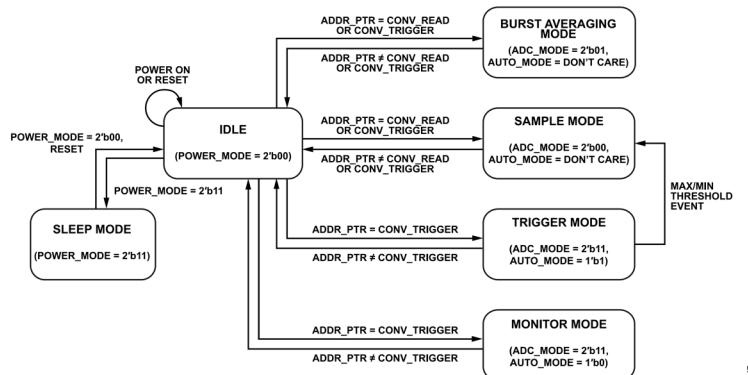

図 47 に、AD4060 の動作モード選択をステート・マシン図として示します。

表 17 は、各機能モードで ADC データを読み出すための推奨アドレス・ポインタ設定です。

表 18. AD4060 の機能モード

| Mode                 | ADC_MODE   | AUTO_MODE  | POWER_MODE |

|----------------------|------------|------------|------------|

| Sample Mode          | 2'b00      | Don't care | 2'b00      |

| Burst Averaging Mode | 2'b01      | Don't care | 2'b00      |

| Monitor Mode         | 2'b11      | 1'b0       | 2'b00      |

| Trigger Mode         | 2'b11      | 1'b1       | 2'b00      |

| Sleep Mode           | Don't care | Don't care | 2'b11      |

図 47. AD4060 のステート・マシン図

表 17. アドレス・ポインタの推奨値

| Mode                 | Conversion Register | Recommended Address Pointer Value |

|----------------------|---------------------|-----------------------------------|

| Sample Mode          | CONV_READ           | 0x51                              |

|                      | CONV_TRIGGER        | 0x57                              |

| Burst Averaging Mode | CONV_READ           | 0x51                              |

|                      | CONV_TRIGGER        | 0x57                              |

| Monitor Mode         | CONV_TRIGGER        | 0x57                              |

|                      | CONV_TRIGGER        | 0x57                              |

## 動作モード

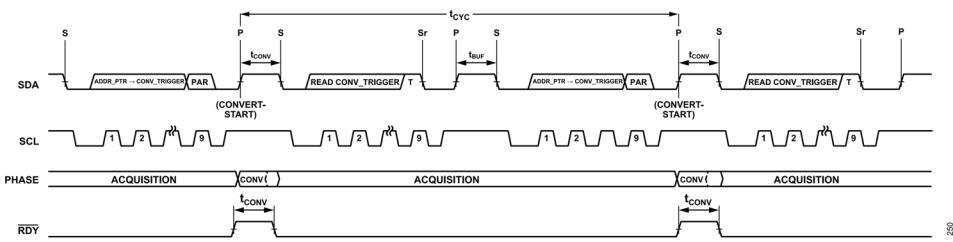

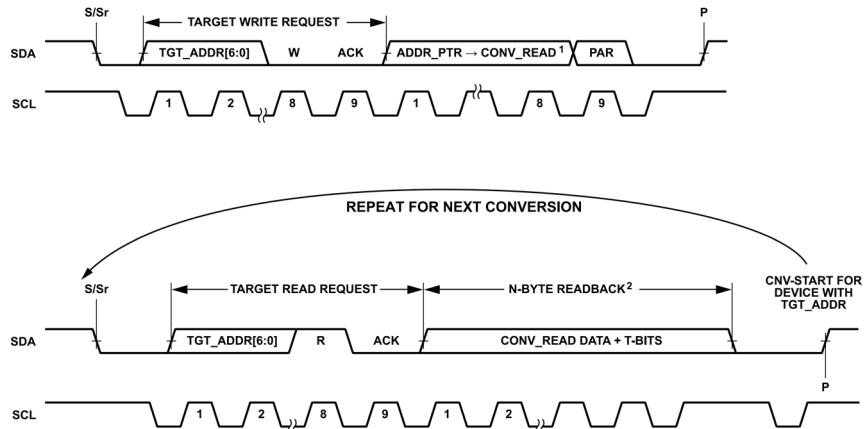

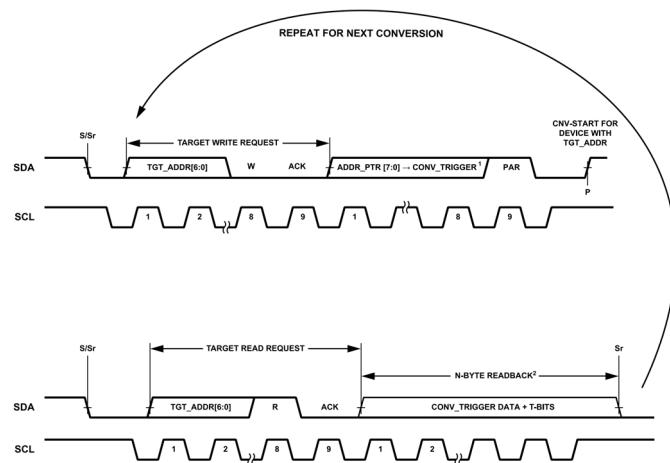

## サンプル・モード

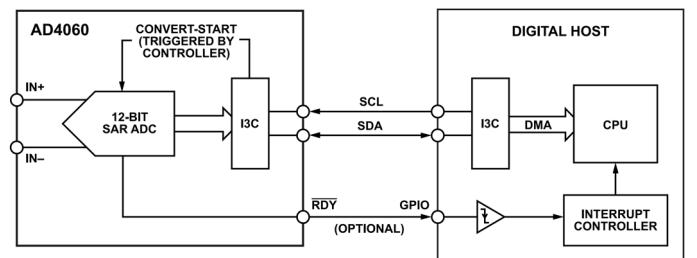

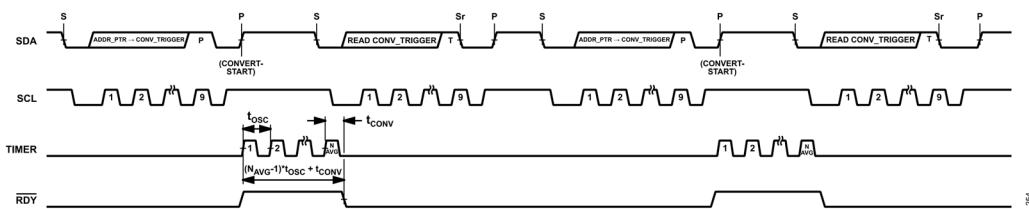

サンプル・モードでは、変換スタートによって 1 回の変換がトリガれます。変換終了時には AD4060 が 12 ビットの結果を生成し、コントローラ・デバイスは I3C バスを介してその結果を読み出します。サンプル・モードを選択する設定レジスタの設定値を表 18 に示します。図 48 は、AD4060 のデジタル・インターフェースの代表的な接続図です。

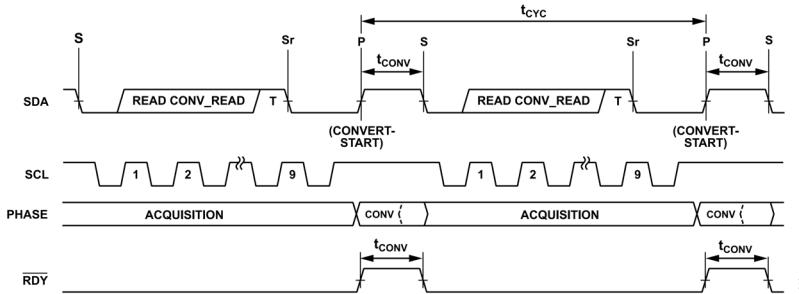

CONV\_READ レジスタ使用時のサンプル・モードにおけるインターフェース・タイミング図を図 49 に、同じく CONV\_TRIGGER 使用時のタイミング図を図 50 に示します。 $t_{CONV}$  の仕様は、変換スタートから変換終了までの遅延時間値を決定します。コントローラは、最大  $t_{CONV}$  遅延が経過するのを待ってから、I3C バス経由で結果を読み出す必要があります。RDY 信号は、I3C 読出しを ADC のサンプリング・フェーズに同期するオプションのハードウェア割込みとして機能します（データ・レディ信号のセクションを参照）。

CONV\_READ レジスタから読み出しを行って ADC 変換をトリガする場合、それぞれの変換結果は、I3C バスを介した変換後の読み出し時に出力されます（CONV\_READ レジスタのセクションを参照）。CONV\_TRIGGER レジスタを使って ADC 変換をトリガする場合は、それぞれの変換後にレジスタから変換結果を読み出す必要があります。そうしないと、前の変換で得られた結果が次の書き込み（および変換スタート）によって上書きされてしまします（CONV\_TRIGGER レジスタのセクションを参照）。

最も効率的なリードバックを行うには、CONV\_READ レジスタと CONV\_TRIGGER レジスタの下位 16 ビットをサンプル・モードで読み出すことを推奨します。サンプル・モードでのリードバック時の推奨 ADDR\_PTR 設定については表 17 を参照してください。

サンプル・モードでは、最大サンプリング・レート ( $f_s$ ) が I3C バスの出力データレートによって制限されますが、その程度は出力データ長と I3C バス特性によって異なります。最速の出力データレートは、図 63 に示すように、CONV\_READ レジスタから繰り返し読み出しを行うことによって得られます。特定動作条件下で実現可能な最大  $f_s$  の推定に関する詳細については、シリアル・インターフェースの出力データレートの計算のセクションを参照してください。

DEV\_EN 信号がイネーブルされると、変換の開始は、変換スタートのトリガから  $t_{PWR\_ON}$ （プログラム可能な遅延時間）だけ遅延されます。DEV\_EN 信号を使用する場合の具体的なタイミングの詳細については、デバイス・イネーブル信号のセクションと図 51 を参照してください。

DATA\_READY\_IBI をイネーブルした場合、この IBI は CONV\_TRIGGER レジスタの変換終了時に生成されて、コントローラが CONV\_TRIGGER レジスタから ADC データを読み出せる状態になったことを示します（詳細についてはインバンド割込みのセクションを参照）。

図 48. サンプル・モードの例示的接続図

図 49. CONV\_READ 使用時のサンプル・モードのタイミング図

## 動作モード

図 50. CONV\_TRIGGER 使用時のサンプル・モードのタイミング図

図 51. DEV\_EN がイネーブルされたサンプル・モードのタイミング

## 動作モード

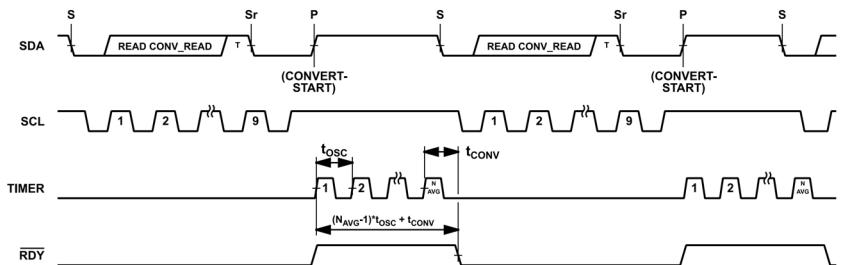

## バースト平均化モード

バースト平均化モードでは、変換スタートが内蔵タイマーをトリガしてバースト変換を実行し、平均化フィルタが結果を蓄積して14ビットの平均値を求めます。表18に、バースト平均化モードを選択するための設定レジスタの設定を示します。図52はAD4060デジタル・インターフェースの代表的な接続図です。

CONV\_READレジスタ使用時のバースト平均化モードにおけるインターフェース・タイミング図を図53に、同じくCONV\_TRIGGER使用時のタイミング図を図54に示します。ADCのサンプリング周期( $t_{cyc}$ )は内蔵タイマーの周波数( $f_{osc}$ )で設定され、バースト当たりのサンプル数は平均化比率( $N_{AVG}$ )で設定されます。表52に $f_{osc}$ のオプションを示します。平均化フィルタは、**ブロック平均化フィルタ**のセクションに示すように、2~256の平均化比率に対応しており、AVG\_WIN\_LENビット・フィールドで設定されます。

コントローラは、平均化された結果が読み出しが可能な状態になるまで待ってから、I3Cバス経由でその結果を読み出す必要があります。RDY信号は、I3Cデータ読み出しをADCのサンプリング・フェーズに同期するオプションのハードウェア割込みとして機能します(データ・レディ信号のセクションを参照)。

変換スタートのトリガからデータ・レディまでの合計遅延は、次式で得られます。

$$\frac{(N_{AVG}-1)}{f_{osc}} + t_{CONV} \quad (4)$$

最も効率的なリードバックを行うには、CONV\_READレジスタとCONV\_TRIGGERレジスタの下位16ビットをバースト平均化モードで読み出すことを推奨します。バースト平均化モードでのリードバックのための推奨ADDR\_PTR設定については、表17を参照してください。

DEV\_EN信号がイネーブルされると、バースト変換の開始は、変換スタートのトリガから $t_{PWR\_ON}$ (プログラム可能な遅延時間)だけ延期されます。DEV\_EN信号は、サンプル・バーストの終了までアサートされたままであります。DEV\_EN信号を使用する場合の具体的なタイミングの詳細については、**デバイス・イネーブル信号**のセクションと図55を参照してください。

DATA\_READY\_IBIをイネーブルした場合、このIBIはCONV\_TRIGGERレジスタの変換終了時に生成されて、コントローラがCONV\_TRIGGERレジスタからADCデータを読み出せる状態になったことを示します(詳細については**インバンド割込み**のセクションを参照)。

図52. バースト平均化モードの例示的接続図

図53. CONV\_READ 使用時のバースト平均化モードのタイミング図

図54. CONV\_TRIGGER 使用時のバースト平均化モードのタイミング図

## 動作モード

図 55. **DEV\_EN** がイネーブルされたバースト平均化モードのタイミング

## 動作モード

### 自律モード

自律モードでは、AD4060が入力信号を自律的にモニターして、範囲外のイベントを検出できるようになります。自律モードは、非自律モードより消費電力が低いのが特徴です。これは、[コンパレータの動作](#)のセクションに示すように、ADC コアが低消費電力コンパレータ・モードに入るからです（各モードの消費電力仕様については表 1 を参照）。

AD4060には、モニター・モードおよびトリガ・モードという2つの自律モードがあります。以下のセクションでは両方の自律モードについて説明します。いずれかの自律モードが選択されると、ADC コアはウィンドウ・コンパレータとして機能し、[コンパレータの動作](#)のセクションに示すように、ADC サンプリング・クロックは内蔵タイマーによって駆動されます。サンプリング・クロック周波数は、TIMER\_CONFIG レジスタの FS\_BURST\_AUTO ビット・フィールドで設定されます（表 52 を参照）。

コンパレータは、以下に示す 4 つのサンプル&比較動作を繰り返しシーケンスで実行します。各動作の実行には 1 つのサンプル期間を要するので、シーケンス全体の時間は次に示す 4 つのサンプル期間になります。

1.  $V_{IN} \geq MAX\_LIMIT$

2.  $V_{IN} \leq MAX\_LIMIT - MAX\_HYST$

3.  $V_{IN} \geq MIN\_LIMIT + MIN\_HYST$

4.  $V_{IN} \leq MIN\_LIMIT$

コンパレータは、最大および最小の閾値イベント（それぞれ MAX\_INTR および MIN\_INTR）用の 2 つのハードウェア・アラート信号を備えています。これらの信号は、[閾値アラート信号](#)のセクションに示すように、GPO0 ピンまたは GP1 ピン、あるいはその両方に割り当てることができます。図 58 は、これらのアラート信号をハードウェア割込みとして使用するマイクロコントローラの典型的な接続図を示しています。

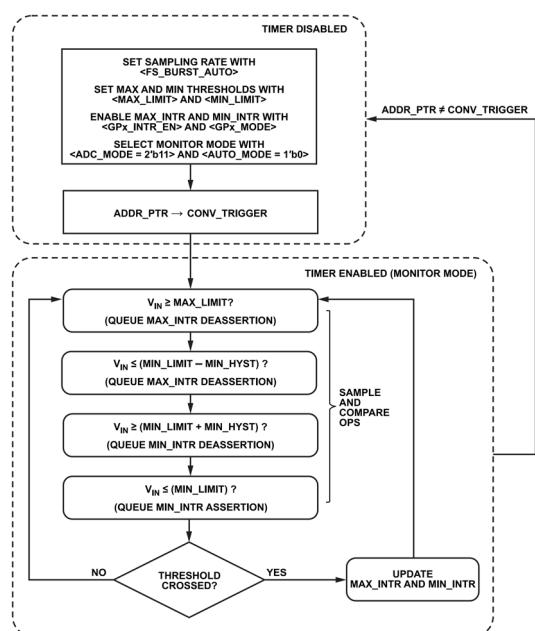

### モニター・モード

モニター・モードに入るための ADC\_MODE ビット・フィールドと AUTO\_MODE ビット・フィールドの設定を表 18 に示します。ADC\_MODE ビットと AUTO\_MODE ビットの設定後に ADDR\_PTR を CONV\_TRIGGER に設定すれば内蔵タイマーがイネーブルされ、AD4060 はウィンドウ・コンパレータとして自律的に機能し始めます。AD4060 は、コントローラが ADDR\_PTR を CONV\_TRIGGER から他の値に変更するまで自律モードで動作し続けます（図 47 を参照）。モニター・モードは、ユーザがプログラム可能なヒステリシス設定を利用し、入力信号が範囲内に戻ったときに MAX\_INTR および MIN\_INTR の各信号を自動でクリアします（図 45 を参照）。

図 56 は、モニター・モードにおけるレジスタ設定、比較シーケンス動作、閾値を超えた後のハードウェア割込みとアラート・フラグの動作に関するフローチャートです。

最大閾値または最小閾値を超えたことが検出された場合は、MAX\_INTR 信号または MIN\_INTR 信号がそれぞれアサートされます。内蔵タイマーはサンプリング・クロックの生成を継続し、サンプリングされた入力信号が MAX\_HYST および MIN\_HYST の各ビット・フィールドで設定された境界内に戻ったときに、MAX\_INTR 信号または MIN\_INTR 信号がそれぞれデアサートされます。

MAX\_FLAG ビットまたは MIN\_FLAG ビットも、MAX\_INTR または MIN\_INTR がそれぞれアサートされるとアサートされます。MAX\_FLAG および MIN\_FLAG は自動でクリアされないため、信号が範囲内に戻っても自動でクリアされることはありません。モニター・モードの終了後は、再びモニター・モードに戻る前に MAX\_FLAG ビットと MIN\_FLAG ビットをリセットすることを推奨します。

図 56. モニター・モードのフローチャート

## 動作モード

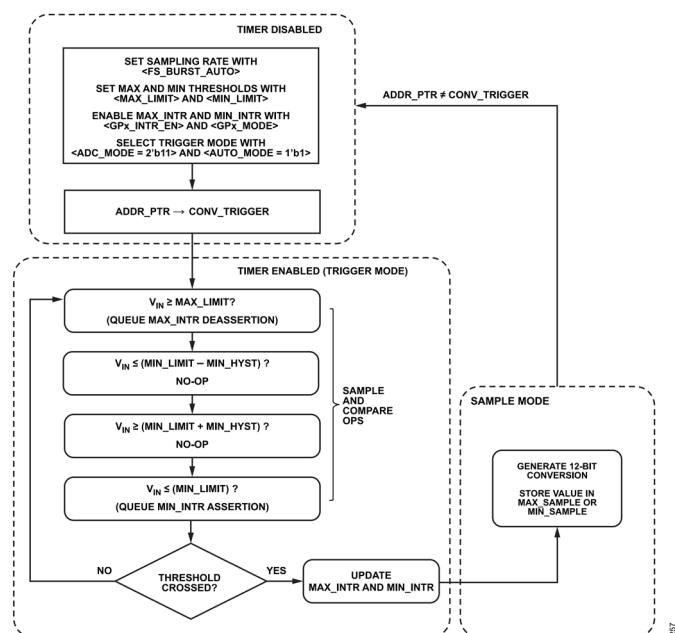

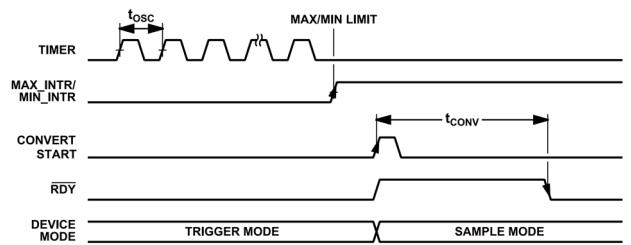

## トリガ・モード

トリガ・モードに入るための ADC\_MODE ビット・フィールドと AUTO\_MODE ビット・フィールドの設定を表 18 に示します。ADC\_MODE ビットと AUTO\_MODE ビットの設定後に ADDR\_PTR を CONV\_TRIGGER に設定すれば内蔵タイマーがイネーブルされ、AD4060 はウインドウ・コンパレータとして自律的に機能し始めます。トリガ・モードでは、閾値を超えたことがトリガとなって、AD4060 は入力信号の 12 ビット変換とサンプル・モードへの遷移を自律的に実行します。I2C バスで MAX または MIN IBI を送る場合は、対応するアラート信号とステータス・ビットがアサートされます。これによりコントローラは、設定モードで MAX\_SAMPLE\_REG または MIN\_SAMPLE\_REG レジスタから 12 ビットの結果を読み出すことができます。

図 57 は、トリガ・モードにおけるレジスタ設定、比較シーケンス動作、および閾値を超えた後のハードウェア割込みとアラート・フラグの動作に関するフローチャートです。

最大値または最小値を超えたことが検出された場合は、MAX\_INTR 信号または MIN\_INTR 信号がそれぞれアサートされます。内蔵タイマーはディスエーブルされて自律的なサンプリング

は停止し、ADC コアが起動して入力信号を変換します。図 59 は、トリガ・モードにおける閾値検出および ADC サンプリングのタイミング図です。閾値イベントの発生後、ファームウェアは、サンプル・モードで AD4060 の動作を続けて更に変換を実行するか、ADDR\_PTR を CONV\_TRIGGER レジスタとは異なる値に設定してサンプル・モードを終了し、アラート・レジスタを読み出すことができます。MAX\_INTR 信号と MIN\_INTR 信号は、ADDR\_PTR が CONV\_TRIGGER と異なる値に更新されるまで、その状態を維持します。

なお、サンプル・モードに遷移した後、レジスタ・マップ内の ADC\_MODE ビット・フィールドは内部で 2'h0 に上書きされるため、2'h3 に再度上書きして自律モードに入直す必要があります。

MAX\_FLAG ビットまたは MIN\_FLAG ビットも、MAX\_INTR または MIN\_INTR がそれぞれアサートされるとアサートされます。MAX\_FLAG および MIN\_FLAG は自動でクリアされないビットのため、ホストがレジスタを書き込んで 1'b1 に設定するまでクリアされません。MAX\_FLAG ビットと MIN\_FLAG ビットは、自律モードに戻る前にリセットすることを推奨します。

## 動作モード

## 自律モードの概略図

図 58. 自律モードの例示的接続図

図 59. トリガ・モードのタイミング図

## スリープ・モード

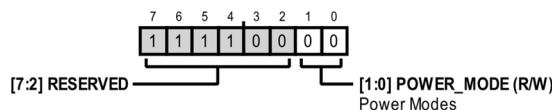

スリープ・モードでは、AD4060はデジタル・インターフェース以外のすべての機能ブロックをパワーダウンし、長いアイドル時間で 430nW という超低消費電力を実現します（表 1 を参照）。DEVICE\_CONFIG レジスタの POWER\_MODE ビット・フィールドを 2'h3 に設定して、AD4060をスリープ・モードに遷移させてください。

スリープ・モード中は内部 LDO レギュレータがパワーダウンして、+1.8V の CLDO 電源の供給を停止します。この機能により、

ADC コアとその他の機能ブロックの大部分がパワーダウンします。デジタル・インターフェースはアクティブのままなので、デジタル・ホストは POWER\_MODE ビット・フィールドを 2'h0 に書き換えてスリープ・モードを終了し、デバイスを起動させます。デバイスは、スリープ・モードを終了すると設定モードに移ります。設定レジスタの状態は維持されているため、デジタル・ホストは、スリープ・モード終了後にデバイス設定を再設定する必要がありません。

## シリアル・インターフェース

AD4060のデジタル・インターフェースには、シリアル・データ転送用の2線式I3Cインターフェースと、2つの汎用デジタル出力GP0とGP1が含まれています。I3Cインターフェースは、主にAD4060設定レジスタの読み出しと書き込み、およびADC結果の読み出しに使用します。動作モードのセクションでは、I3Cの機能およびプロトコルを動作モードごとに説明しています。

AD4060は、このデータシートでも頻繁に引用されているMIPI I3C v1.1に定めるI3C仕様に準拠しています。MIPI I3C仕様のセクション4.2.2には、I3Cターゲット・デバイスの役割についての概要が示されています。AD4060はSDR専用ターゲットであり、HDRモードはサポートしていません。AD4060は、コモン・コマンド・コード(CCC)のセクションに示すコモン・コマンド・コード(CCC)と、インバンド割込み(IBI)をサポートしています。AD4060はホットジョイン機能をサポートしておらず、I3Cコントローラ・デバイスとして使用することはできませんまた、I2Cコントローラとの互換性もありません。

SDAおよびSCLのオープン・ドレイン・プルアップ要件に関するガイダンスについては、MIPI仕様のセクション5.1.3.1を参照してください。

SDAデータはSCLの立上がりエッジで読み出され、SCLの立下がりエッジで更新されます。

AD4060はレジスタの読み出しと書き込みのためのCRC機能を備えており、信頼性の高いデータ転送を実現します(詳細についてはレジスタ・アクセスCRCのセクションを参照)。ADCデータは、ダイレクト・メモリ・アクセス(DMA)など、マイクロコントローラ内蔵メモリの転送動作との互換性を最大限に高めるために、バイト単位の整数倍形式になっています。

インターフェースのロジック・レベルは、仕様に記載されているようにVIO電源電圧で設定されます。AD4060は、1.8V、2.5V、および3.3Vのロジック・システムをサポートしています。

表19. AD4060の48ビット暫定ID定義

| PID <sup>1</sup> Bit Field Name | PID Bit Field Offset | Value                                                | Description                                                                                                                                                       |

|---------------------------------|----------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIPI Manufacturer ID (MID)      | PID[47:33]           | 15'h0177                                             | ADI MIPI assigned vendor ID.                                                                                                                                      |

| PID Type Selector               | PID[32]              | 1'b0                                                 | Vendor fixed value.                                                                                                                                               |

| Part ID                         | PID[31:16]           | 16'h007A                                             | ADI product ID.                                                                                                                                                   |

| Instance ID                     | PID[15:12]           | PID[15] = 1'b0<br>PID[14:12] = [ADDR2, ADDR1, ADDR0] | Allows pin-strap selection of up to eight unique device instances. (See the <a href="#">Pin Configuration and Function Descriptions</a> section for more detail.) |

| Vendor-Defined                  | PID[11:0]            | PID[11:8] = 4'b0<br>PID[7:0] = DCR[7:0]              | Device revision number.<br>Device characteristics register (DCR) byte. See the <a href="#">Register Details</a> section for more detail.                          |

<sup>1</sup> ベンダーごとに固定。

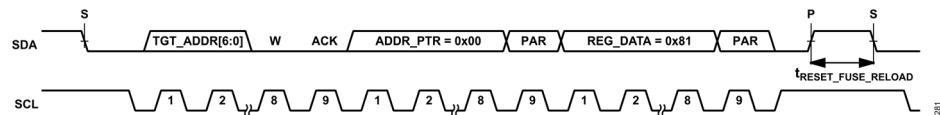

## ダイナミック・アドレシング

AD4060には、I3Cコントローラによって固有のダイナミック・アドレス(TGT\_ADDR)が指定されます。それぞれのスタートや反復スタート後、AD4060は最初のバイトをそのTGT\_ADDRと比較して、アドレスが指定されたかどうかを判定します。

デバイス・リセット後、コントローラは、バスを介してロードキャストENTDAA CCCを送り、ダイナミック・アドレス割当て(Dynamic Address Assignment: DAA)モードに入ることをすべてのターゲット・デバイスに示すことによって、I3Cバスの初期化前にDAA手順を開始する必要があります(詳細についてはコモン・コマンド・コード(CCC)のセクションを参照)。

DAAルーチンにおいて、AD4060(およびバス上にあるその他すべてのI3Cターゲット)は固有の48ビット暫定ID(PID)をコントローラへ送ります。AD4060の48ビットPIDの内容を表19に示します。コントローラはその後、バス上にあるそれぞれのターゲット・デバイスに固有の7ビット・ダイナミック・アドレスを割り当てます(DAA手順の詳細は、MIPI I3C仕様のセクション5.1.4に記載されています)。

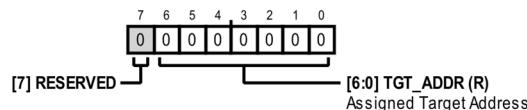

TGT\_ADDRは、割当て後にTGT\_ADDR\_REGに保存されます。

AD4060には、ADDR0、ADDR1、ADDR2と呼ばれる3つのアドレス・ロジック入力があります(表19を参照)。ADDRxピンには最大8個の固有PIDを割り当てることができるので、アドレス競合を起こすことなく1つのI3Cバスに最大8個のAD4060デバイスを接続できます。

AD4060はグループ・アドレシングをサポートしているので、I3Cコントローラは複数のデバイスに同時に書き込みを行うことができます。例えば、グループ・アドレシングは、CONV\_TRIGGERレジスタを介して複数のAD4060デバイスの同時サンプリングをトリガるために使用できます。グループ・アドレスにはSETGRPA CCCが割り当てられます(SETGRPAのセクションを参照)。

AD4060に静的なI2Cアドレスはありません。

## シリアル・インターフェース

### レジスタ・アドレス・ポインタ

レジスタ・アドレス・ポインタ (ADDR\_PTR) は、読み出しまだ書込み用にアクティブな AD4060 レジスタを選ぶための 1 バイト長スアンドアロン・レジスタです。I3C 読出しコマンドの実行が開始されると、コントローラは、現在 ADDR\_PTR に保存されているレジスタ・アドレスからデータを読み出します。同様に、I3C 書込みが開始されると、コントローラは現在 ADDR\_PTR に保存されているレジスタ・アドレスにデータを書き込みます。ADDR\_PTR レジスタ自体にリードバック用のアドレスを直接指定することはできません。

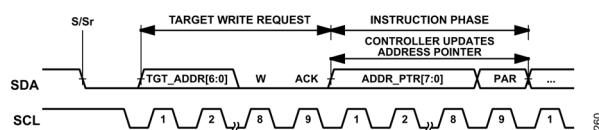

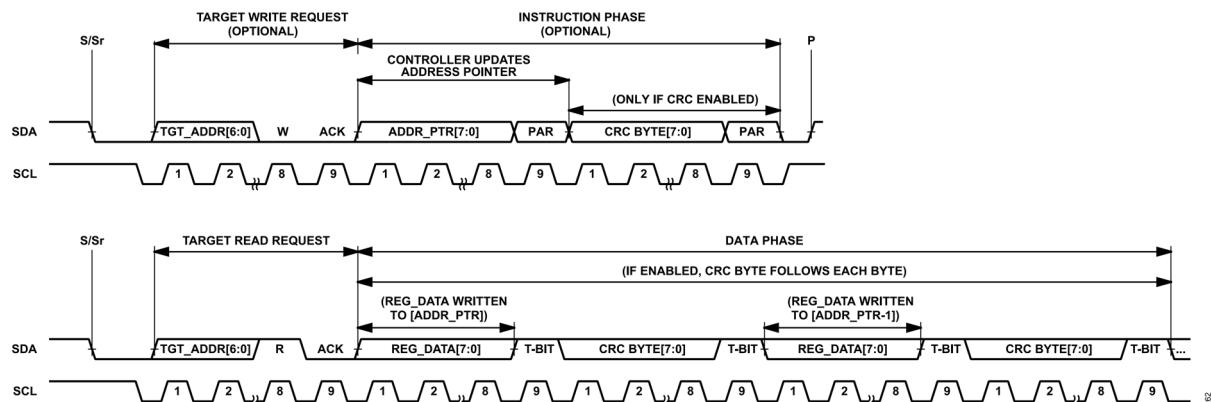

ADDR\_PTR は、I3C 書込みコマンドの命令フェーズで更新されます (図 60 を参照)。ADDR\_PTR は、更新されるまで、あるいはデバイスがリセットされるまで書き込まれた値を保持します。

図 60. アドレス・ポインタの更新

### レジスタへの書込み

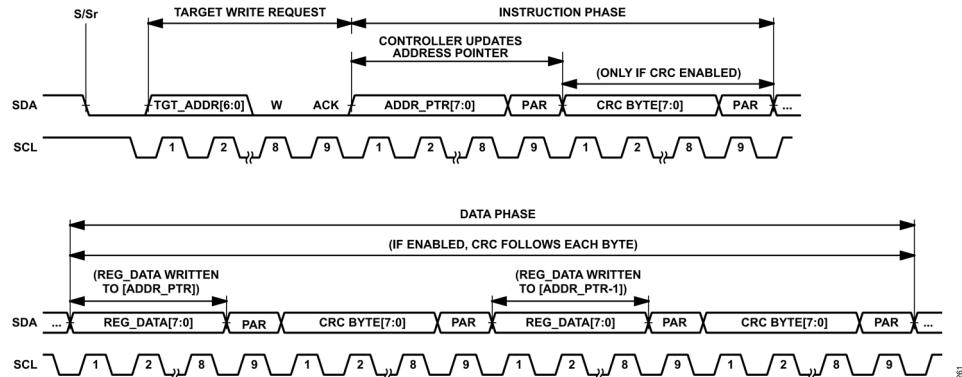

I3C バス上にある AD4060 のレジスタへの書込みプロセスは、3 つの独立したフェーズ、つまりターゲット書込み要求フェーズ、命令フェーズ、およびデータ・フェーズで構成されます。

図 61 に AD4060 のレジスタ書込みシーケンスを示します。

ターゲット書込み要求フェーズでは、RnW ビット = 0 の状態でデバイスのダイナミック・ターゲット・アドレスまたはグループ・アドレスと共にスタート (S) または反復スタート (Sr) を送ることによって、コントローラがレジスタへの書込みを開始します。デバイスは、SDA をローにして ACK を送ることによりアクノリッジを返します。コントローラがグループ・アドレスを介して複数の AD4060 デバイスのアドレスを指定する場合、その後のレジスタ書込みデータは、I3C バス上にあるすべての AD4060 デバイスに適用されます。

命令フェーズでは、コントローラが ADDR\_PTR を更新します。CRC がイネーブルされている場合、ADDR\_PTR には CRC バイトが含まれます。ADDR\_PTR バイトと CRC バイトには、共にそれぞれのパリティ・ビットが含まれています (データ・フェーズの 9 番目の SDA ビットのセクションを参照)。

データ・フェーズでは、コントローラが、連続するアドレスのレジスタへの書込みデータを 1 バイトずつ送信します (CRC がイネーブルされている場合は CRC も送信)。最初のデータ・バイト (と CRC) は、アドレス = <ADDR\_PTR> のレジスタ内にあるデータに対応しています。その後に続くそれぞれのデータ・バイト (と CRC) は、<ADDR\_PTR> の後の次にアドレス値の小さいレジスタに対応しており、以下同様の要領で送信が繰り返されます。

書込みフレームは、コントローラが反復スタート (Sr) またはストップ (P) を開始すると終了します。

図 61. AD4060 のレジスタ書込みシーケンス

## シリアル・インターフェース

### レジスタの読み出し

I<sup>2</sup>C バス上にある AD4060 のレジスタの読み出しプロセスは、3 つの独立したフェーズ、つまり ADDR\_PTR 更新のための書込み、ターゲット読み出し要求フェーズ、およびデータ・フェーズで構成されます。

図 62 に、AD4060 のレジスタ読み出しシーケンスを示します。

ADDR\_PTR は、ターゲット読み出し要求時にどのレジスタをリードバックするかを指定します。ターゲット読み出し要求を送信する前に、ADDR\_PTR を目的のレジスタ・アドレス値に設定してください（レジスタ・アドレス・ポインタのセクションを参照）。

ターゲット書込み要求フェーズでは、RnW ビット = 1 の状態でデバイスの TGT\_ADDR と共にスタート (S) または反復スタート (Sr) を送ることによって、コントローラがレジスタの読み出しを開始します。デバイスは、SDA をローにして ACK を送ることによりアクリシジを返します。

データ・フェーズでは、AD4060 が、連続するアドレスのレジスタからの読み出しはデータを 1 バイトずつ出力します（CRC がイネーブルされている場合は CRC も送信）。最初のデータ・バイト（と CRC）は、アドレス = <ADDR\_PTR> のレジスタ内にあるデータに対応しています。その後に続くそれぞれのデータ・バイト（と CRC）は、<ADDR\_PTR> の後の次にアドレス値の小さいレジスタのデータに対応しており、以下同様の要領で送信が繰り返されます。

読み出しフレームは、コントローラが反復スタート (Sr) を開始すると終了します。それぞれのレジスタ読み出しバイトは T ビットで終了します。レジスタ読み出しの場合は T ビットが常に 1 なので、レジスタ読み出しフレームの終了はコントローラが行います（図 7 と図 8 を参照）。

図 62. AD4060 のレジスタ読み出しシーケンス

## シリアル・インターフェース

### レジスタ・アクセス CRC

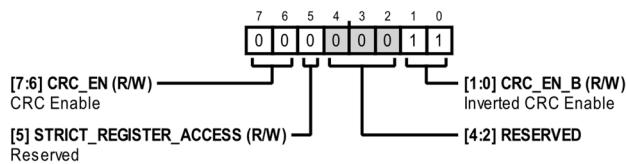

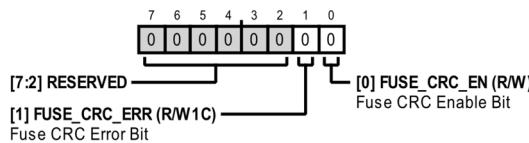

AD4060には、CRC-8に基づくレジスタの読み出しおよび書き込みのエラー・チェック機能がオプションとして含まれており、これには以下の多項式が使われます。

$$x^8 + x^2 + x + 1 \quad (5)$$

CRCは、CRC\_ENおよびCRC\_EN\_Bの各ビット・フィールドをそれぞれ0x1および0x2に設定することでイネーブルされます。CRCをイネーブルすると、レジスタの各データ・バイトの末尾に8ビットのチェックサム・コードが付加されます。チェックサムの値はI3Cバスによる読み出しデータまたは書き込みデータから計算され、これにより、AD4060とコントローラはシリアル通信のエラーを検出することができます。

CRCバイトの送受信は半2重方式で行われ、ある時点で送信できるのはコントローラまたはターゲットのどちらか一方のみです。CRC-8の計算は、SDAがローにスタッキングしているかどうかを検出するために非ゼロ値をシード値とします。各ACKビット後の最初のCRCのシード値は0xA5です。[表20](#)は、設定モードにおけるすべての可能なレジスタ読み出しおよび書き込みトランザクションのデータおよびシード値を要約したものです。

対応するI3Cトランザクションに一致しないチェックサムをAD4060が受け取った場合、そのトランザクションは無効と見な

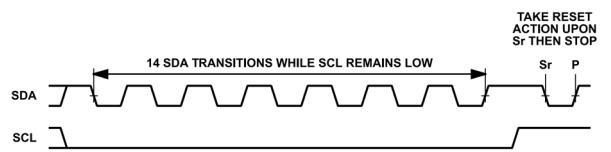

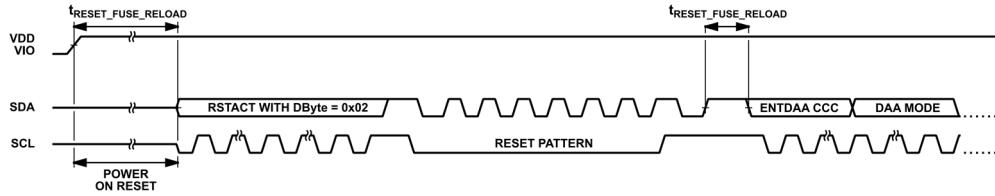

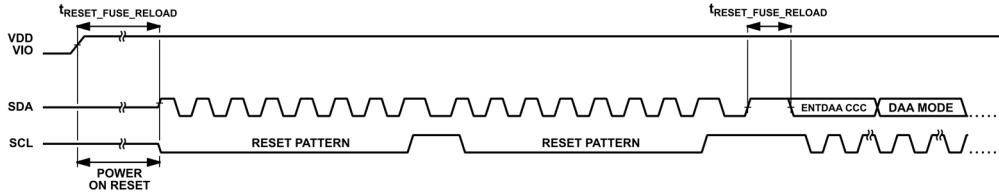

され、INTERFACE\_STATUSレジスタのCRC\_ERRビットが1に設定されます。CRC\_ERRビットは1を書き込むことでクリアするビット(R/W1C)です。CRCをイネーブルした場合は、レジスタが読み出しおよび書き込みを試みるたびにCRC\_ERRビットをチェックすることを推奨します。