## リファレンスと SPI を内蔵した 8 チャンネル 16 ビットの電圧出力 DAC

### 特長

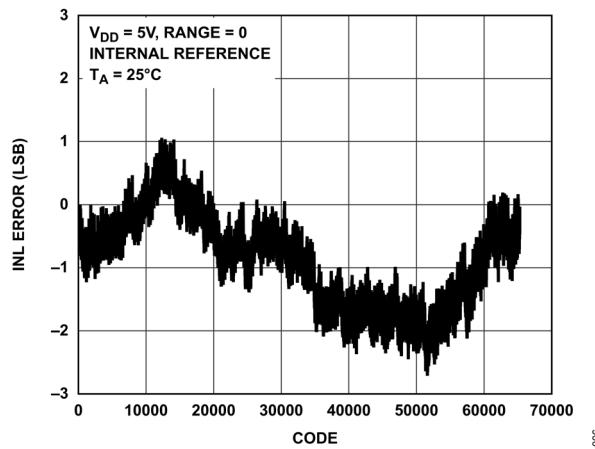

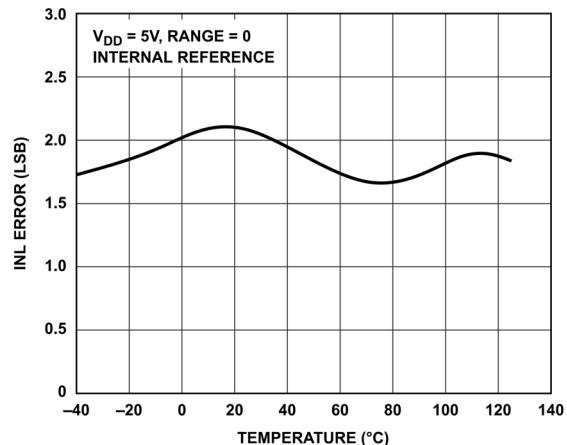

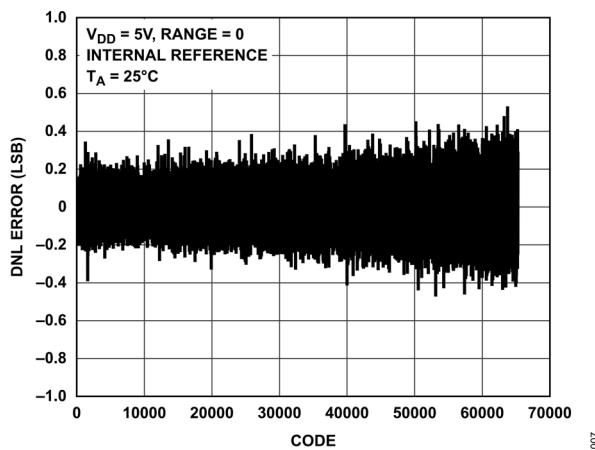

- 16 ビット分解能、 $\pm 3 \text{ LSB}_{16}$  INL、 $\pm 1 \text{ LSB}_{16}$  DNL

- TUE (総合未調整誤差) : FSR の  $\pm 0.22\%$  (最大値)

- オフセット誤差 :  $\pm 1.6 \text{ mV}$  (最大値)

- ゲイン誤差 : FSR の  $\pm 0.26\%$  (最大値)

- 50mA のソース電流を確保

- 超低ヘッドルーム : 20mA 負荷で 25mV

- 内部電圧リファレンス : 2.5V、5ppm/ $^{\circ}\text{C}$  (代表値)

- ノイズ・スペクトル密度 :  $62 \text{ nV}/\sqrt{\text{Hz}}$  (外部リファレンス)

- ノイズ・スペクトル密度 :  $115 \text{ nV}/\sqrt{\text{Hz}}$  (内部リファレンス)

- 出力電圧、電流、およびダイ温度のモニタ

- SPI の書き込みと読み出し : 50MHz

- 電源電圧範囲 : 2.7V~5.5V

- デジタル・インターフェース : 1.2V または 1.8V 互換

- 動作温度範囲 :  $-40^{\circ}\text{C}$ ~ $+125^{\circ}\text{C}$

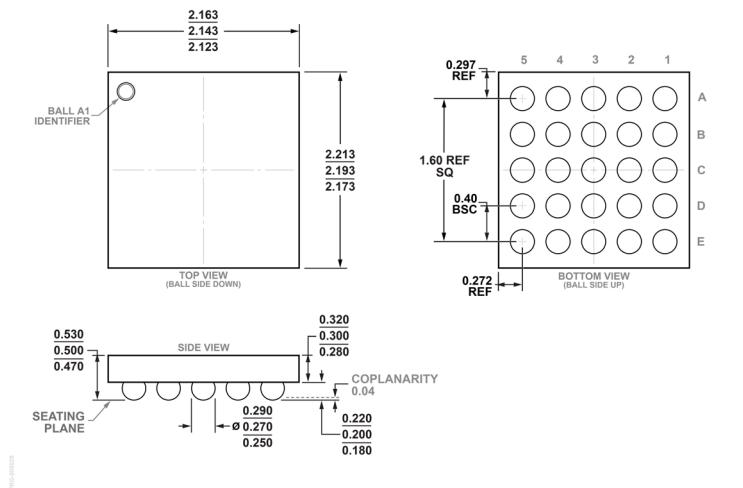

- 小型パッケージ : 2.1mm × 2.2mm、25 ポール WLCSP

### アプリケーション

- 光トランシーバ

- 試験および計測

- 工業用オートメーション

- データ・アクイジション・システム

### 概要

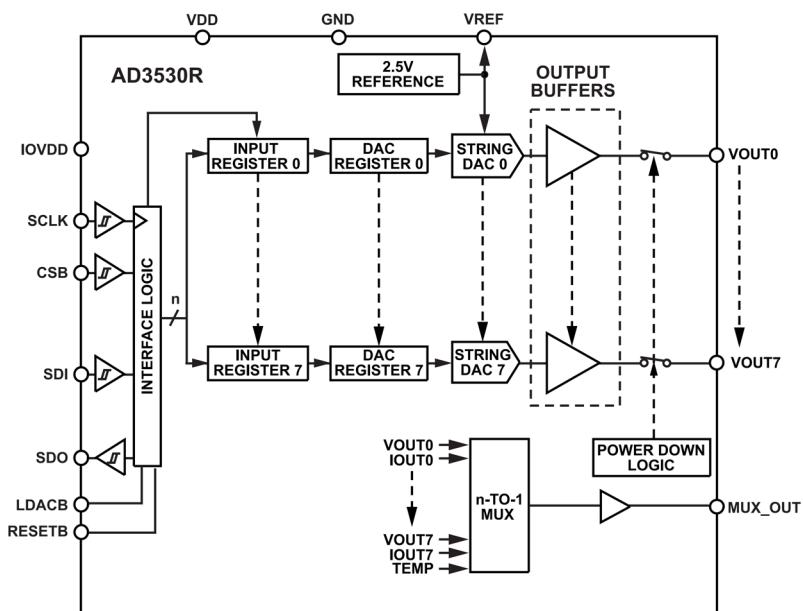

AD3530/AD3530R は、低消費電力、8 チャンネル、16 ビット、バッファ付きの電圧出力 D/A コンバータ (DAC) で、ソフトウェアでプログラム可能なゲイン制御機能を備えており、2.5V のリファレンス電圧に対するフルスケール出力スパンは 2.5V または 5V です。これらのデバイスは 2.7V~5.5V の単電源で動作し、設計によって単調増加性が確保されています。AD3530R は、2.5V、5ppm/ $^{\circ}\text{C}$  の内部リファレンス (デフォルトではディスエーブル) も搭載しています。

これらのデバイスは、出力電圧、電流、内部ダイ温度を監視できるマルチブレクサを内蔵しています。AD3530/AD3530R は、2.1mm × 2.2mm の 25 ポール WLCSP パッケージで提供されます。これらのデバイスにはパワーオン・リセット (POR) 回路が組み込まれており、有効な書き込みが実行されるまでの間、グラウンドとの間の 32k $\Omega$  の抵抗によって DAC の出力を維持します。これらの DAC はパワーダウン・モードも備えており、消費電力を 670 $\mu\text{A}$  (代表値) まで低減します。

シリアル・ペリフェラル・インターフェース (SPI) と MICROWIRE<sup>®</sup> 対応の 4 線式シリアル・インターフェースは、1.08V~1.98V のロジック・レベルと最大 50MHz のクロック・レートで動作します。

表 1. デバイス・ファミリ・リスト

| Channel Count | Interface | Reference         | 16-Bit  |

|---------------|-----------|-------------------|---------|

| 8             | SPI       | Internal/External | AD3530R |

| 8             | SPI       | External          | AD3530  |

### 機能ブロック図

図 1. 機能ブロック図

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

Rev. 0

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                   |    |                          |    |

|-------------------|----|--------------------------|----|

| 特長                | 1  | チップ・タイプ・レジスタ             | 32 |

| アプリケーション          | 1  | 製品 ID 下位レジスタ             | 32 |

| 概要                | 1  | 製品 ID 上位レジスタ             | 32 |

| 機能ブロック図           | 1  | チップ・グレード・レジスタ            | 33 |

| 仕様                | 3  | スクラッチ・パッド・レジスタ           | 33 |

| 電気的特性             | 3  | SPI リビジョン・レジスタ           | 33 |

| AC 特性             | 5  | ベンダ ID 下位レジスタ            | 33 |

| タイミング特性           | 6  | ベンダ ID 上位レジスタ            | 34 |

| 絶対最大定格            | 8  | ストリーム・モード・レジスタ           | 34 |

| 熱抵抗               | 8  | 転送設定レジスタ                 | 34 |

| ESD に関する注意        | 8  | インターフェース設定 C レジスタ        | 35 |

| ピン配置およびピン機能の説明    | 9  | インターフェース・ステータス A レジスタ    | 35 |

| 代表的な性能特性          | 10 | 出力動作モード 0 レジスタ           | 36 |

| 用語の定義             | 19 | 出力動作モード 1 レジスタ           | 36 |

| 動作原理              | 20 | 出力制御 0 レジスタ              | 37 |

| D/A コンバータ         | 20 | リファレンス制御 0 レジスタ          | 37 |

| 電圧リファレンス          | 20 | マルチプレクサ入力選択 0 レジスタ       | 38 |

| 内蔵マルチプレクサ         | 20 | ステータス制御レジスタ              | 39 |

| DAC のコア機能         | 21 | ハードウェア LDAC イネーブル 0 レジスタ | 39 |

| パワーオン・リセット        | 21 | ソフトウェア LDAC イネーブル 0 レジスタ | 40 |

| シリアル・インターフェース     | 22 | DAC レジスタ                 | 41 |

| CRC エラーの検出        | 24 | 複数 DAC レジスタ              | 41 |

| アプリケーション情報        | 25 | 複数 DAC 選択 0 レジスタ         | 41 |

| 電源の推奨事項           | 25 | ソフトウェア LDAC トリガ 0 レジスタ   | 42 |

| レイアウトのガイドライン      | 25 | 複数入力レジスタ                 | 43 |

| ヘッドルームとフットルーム     | 25 | 複数入力選択 0 レジスタ            | 43 |

| DAC の更新           | 25 | ソフトウェア LDAC トリガ 0 レジスタ   | 44 |

| レジスタの一覧           | 29 | 入力レジスタ                   | 44 |

| レジスタの詳細           | 31 | 外形寸法                     | 45 |

| インターフェース設定 A レジスタ | 31 | オーダー・ガイド                 | 45 |

| インターフェース設定 B レジスタ | 31 | 評価用ボード                   | 45 |

| デバイス設定レジスタ        | 32 |                          |    |

## 改訂履歴

1/2025—Revision 0: Initial Version

## 仕様

## 電気的特性

VDD = 2.7V~5.5V、IOVDD = 1.08V~1.98V、VREF = 2.5V (内部または外部) 、負荷抵抗 ( $R_L$ ) = 2k $\Omega$ 、負荷容量 ( $C_L$ ) = 200pF。特に指定のない限り、すべての仕様は  $T_J = -40^{\circ}\text{C}$ ~ $+125^{\circ}\text{C}$  における値で、代表値は  $T_A = 25^{\circ}\text{C}$  での値。

表 2. 電気的特性

| Parameter                              | Min  | Typ     | Max        | Unit                           | Test Conditions/Comments                                                                                                               |

|----------------------------------------|------|---------|------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>        |      |         |            |                                |                                                                                                                                        |

| Resolution                             | 16   |         |            | Bits                           |                                                                                                                                        |

| Integral Nonlinearity Error (INL)      |      | $\pm 3$ | $\pm 10$   | LSB                            | Range = 0 to VREF                                                                                                                      |

|                                        |      | $\pm 3$ | $\pm 10$   | LSB                            | Range = 0 to $2 \times$ VREF                                                                                                           |

| Differential Nonlinearity Error (DNL)  |      | $\pm 1$ | $\pm 1$    | LSB                            | Range = 0 to VREF and guaranteed monotonic                                                                                             |

|                                        |      | $\pm 1$ | $\pm 1$    | LSB                            | Range = 0 to $2 \times$ VREF and guaranteed monotonic                                                                                  |

| Zero-Code Error                        |      | +0.22   | $\pm 1$    | mV                             | Range = 0 to VREF or range = 0 to $2 \times$ VREF                                                                                      |

| Offset Error                           |      | -0.16   | $\pm 1.5$  | mV                             | Range = 0 to VREF                                                                                                                      |

|                                        |      | -0.23   | $\pm 1.6$  | mV                             | Range = 0 to $2 \times$ VREF                                                                                                           |

| Full-Scale Error                       |      | -0.05   | $\pm 0.26$ | % of FSR                       | Range = 0 to VREF                                                                                                                      |

|                                        |      | -0.06   | $\pm 0.18$ | % of FSR                       | Range = 0 to $2 \times$ VREF                                                                                                           |

| Gain Error                             |      | -0.05   | $\pm 0.26$ | % of FSR                       | Range = 0 to VREF                                                                                                                      |

|                                        |      | -0.06   | $\pm 0.18$ | % of FSR                       | Range = 0 to $2 \times$ VREF                                                                                                           |

| Total Unadjusted Error (TUE)           |      | -0.04   | $\pm 0.22$ | % of FSR                       | Range = 0 to VREF                                                                                                                      |

|                                        |      | -0.04   | $\pm 0.16$ | % of FSR                       | Range = 0 to $2 \times$ VREF                                                                                                           |

| Zero-Code Error Drift                  |      |         | $\pm 1.3$  | $\mu\text{V}/^{\circ}\text{C}$ | Range = 0 to VREF or range = 0 to $2 \times$ VREF                                                                                      |

| Offset Error Drift                     |      |         | $\pm 1.3$  | $\mu\text{V}/^{\circ}\text{C}$ | Range = 0 to VREF or range = 0 to $2 \times$ VREF                                                                                      |

| Full-Scale Error Drift                 |      |         | $\pm 200$  | ppm/ $^{\circ}\text{C}$        | Range = 0 to VREF or range = 0 to $2 \times$ VREF                                                                                      |

| Gain Error Drift                       |      |         | $\pm 40$   | ppm/ $^{\circ}\text{C}$        | Range = 0 to VREF or range = 0 to $2 \times$ VREF                                                                                      |

| DC Power Supply Rejection Ratio (PSRR) | 0.03 |         |            | mV/V                           | DAC code = midscale and supply voltage ( $V_{DD}$ ) = 5V $\pm$ 10%                                                                     |

| DC Crosstalk                           |      | $\pm 3$ |            | $\mu\text{V}$                  | Due to single channel, full-scale output change, internal reference, and range = 0 to VREF                                             |

|                                        |      |         | $\pm 0.6$  | $\mu\text{V}/\text{mA}$        | Due to load current change, external reference, and range = 0 to $2 \times$ VREF                                                       |

|                                        |      |         | $\pm 6$    | $\mu\text{V}$                  | Due to powering down (per channel), internal reference, and range = 0 to VREF                                                          |

| OUTPUT CHARACTERISTICS                 |      |         |            |                                |                                                                                                                                        |

| Output Power-Up State                  |      | 32      |            | $\text{k}\Omega$               | Pull-down resistance                                                                                                                   |

| Output Voltage Range                   | 0    |         | 2.5        | V                              | Range = 0 to VREF, internal reference, and VDD > VREF                                                                                  |

|                                        | 0    |         | 5          | V                              | Range = 0 to $2 \times$ VREF, internal reference, and VDD > $2 \times$ VREF                                                            |

| Maximum Capacitive Load                |      | 2       |            | nF                             | $R_L = \infty$                                                                                                                         |

|                                        |      | 5       |            | nF                             | $R_L = 1\text{k}\Omega$                                                                                                                |

| Load Regulation                        |      | 75      |            | $\mu\text{V}/\text{mA}$        | $V_{DD} = 5\text{V} \pm 10\%$ , DAC code = midscale, and $-30\text{mA} \leq \text{output current } (I_{\text{OUT}}) \leq +30\text{mA}$ |

|                                        |      | 75      |            | $\mu\text{V}/\text{mA}$        | $V_{DD} = 3\text{V} \pm 10\%$ , DAC code = midscale, and $-20\text{mA} \leq I_{\text{OUT}} \leq +20\text{mA}$                          |

| Short-Circuit Current <sup>2</sup>     | 50   |         |            | mA                             | Sourcing                                                                                                                               |

|                                        | 40   |         |            | mA                             | Sinking                                                                                                                                |

| Headroom                               | 40   | 25      |            | mV                             | Source current = 20mA                                                                                                                  |

| Footroom                               | 90   | 50      |            | mV                             | Sink current = 20mA                                                                                                                    |

| Load Impedance at Rails                |      | 1.25    |            | $\Omega$                       | VDD, sourcing                                                                                                                          |

|                                        |      | 2.5     |            | $\Omega$                       | GND, sinking                                                                                                                           |

| Power-Up Time                          |      | 5       |            | $\mu\text{s}$                  | Exiting power-down mode and $V_{DD} = 5\text{V}$                                                                                       |

## 仕様

表 2. 電気的特性 (続き)

| Parameter                                                       | Min         | Typ         | Max        | Unit   | Test Conditions/Comments                                                           |

|-----------------------------------------------------------------|-------------|-------------|------------|--------|------------------------------------------------------------------------------------|

| REFERENCE INPUT                                                 |             |             |            |        |                                                                                    |

| Reference Input Current                                         |             | 375         |            | μA     | $V_{REF} = V_{DD} = 5.5V$ and range = 0 to VREF                                    |

|                                                                 |             | 750         |            | μA     | $V_{REF} = V_{DD} = 5.5V$ and range = 0 to $2 \times V_{REF}$                      |

| Reference Input Range                                           | 1           |             | $V_{DD}$   | V      | Range = 0 to VREF                                                                  |

|                                                                 | 1           |             | $V_{DD}/2$ | V      | Range = 0 to $2 \times V_{REF}$                                                    |

| Reference Input Impedance                                       |             | 15.0        |            | kΩ     | Range = 0 to VREF                                                                  |

|                                                                 |             | 7.5         |            | kΩ     | Range = 0 to $2 \times V_{REF}$                                                    |

| REFERENCE OUTPUT                                                |             |             |            |        |                                                                                    |

| Output voltage ( $V_{OUT}$ )                                    | 2.4975      |             | 2.5025     | V      | $T_J = 25^{\circ}C$                                                                |

| Voltage Reference Temperature Coefficient ( $TC$ ) <sup>3</sup> |             | 5           | 15         | ppm/°C | WLCSP                                                                              |

|                                                                 |             | 5           | 10         | ppm/°C | WLCSP; $T_J = 25^{\circ}C$ to $+125^{\circ}C$                                      |

| Output Impedance                                                |             | 0.06        |            | Ω      |                                                                                    |

| Output Voltage Noise                                            |             | 25          |            | μV p-p | 0.1Hz to 10Hz                                                                      |

| Output Voltage Noise Density                                    |             | 96          |            | nV/√Hz | At $T_A, f = 10kHz, C_L = 10nF$ , and range = 0 to VREF or 0 to $2 \times V_{REF}$ |

| Maximum Capacitive Load                                         |             | 0.5         |            | nF     |                                                                                    |

| Load Regulation Sourcing                                        |             | 60          |            | μV/mA  | At ambient temperature                                                             |

| Output Current Load Capability                                  |             | 5           |            | mA     | Sourcing                                                                           |

|                                                                 |             | 100         |            | μA     | Sinking                                                                            |

| Line Regulation                                                 |             | 10          |            | μV/V   | At ambient temperature                                                             |

| Long-Term Stability Drift                                       |             | 55          |            | ppm    | After 1000 hours at $25^{\circ}C$                                                  |

| Thermal Hysteresis                                              |             | 125         |            | ppm    | First cycle                                                                        |

|                                                                 |             | 25          |            | ppm    | Additional cycles                                                                  |

| INTEGRATED MULTIPLEXER                                          |             |             |            |        |                                                                                    |

| Buffer Output Current                                           |             | ±10         |            | mA     |                                                                                    |

| Buffer Output Impedance                                         |             | 0.9         |            | Ω      |                                                                                    |

| Buffer Offset                                                   |             | 10          |            | mV     |                                                                                    |

| Maximum Capacitive Load                                         |             | 470         |            | pF     |                                                                                    |

| Multiplexer (Mux) Switching Glitch <sup>4</sup>                 |             | 0.5         |            | mV     |                                                                                    |

| LOGIC INPUTS                                                    |             |             |            |        |                                                                                    |

| Input Current                                                   |             | ±1          |            | μA     | Per pin                                                                            |

| Input Low Voltage ( $V_{IL}$ )                                  |             | 0.3 × IOVDD |            | V      |                                                                                    |

| Input High Voltage ( $V_{IH}$ )                                 | 0.7 × IOVDD |             |            | V      |                                                                                    |

| Input Capacitance                                               |             | 2           |            | pF     |                                                                                    |

| LOGIC OUTPUT (SDO)                                              |             |             |            |        |                                                                                    |

| Output Low Voltage ( $V_{OL}$ )                                 |             | 0.4         |            | V      | Sink current ( $I_{SINK}$ ) = $200\mu A$                                           |

| Output High Voltage ( $V_{OH}$ )                                | IOVDD - 0.4 |             |            | V      | Source current ( $I_{SOURCE}$ ) = $200\mu A$                                       |

| Floating State Output Capacitance                               |             | 2           |            | pF     |                                                                                    |

| POWER REQUIREMENTS                                              |             |             |            |        |                                                                                    |

| IOVDD                                                           | 1.08        |             | 1.98       | V      |                                                                                    |

| IOVDD Pin Current ( $I_{IOVDD}$ )                               |             | 16          |            | μA     |                                                                                    |

| VDD                                                             | 2.7         |             | 5.5        | V      | Range = 0 to VREF                                                                  |

|                                                                 | VREF + 1.5  |             | 5.5        | V      | Range = 0 to $2 \times V_{REF}$                                                    |

| VDD Current ( $I_{VDD}$ )                                       |             |             |            |        | $V_{IH} = V_{DD}, V_{IL} = GND$ , and $V_{DD} = 2.7V$ to $5.5V$                    |

| Normal Operation <sup>5</sup>                                   | 2.8         | 3.4         |            | mA     | External reference                                                                 |

|                                                                 | 3.85        | 4.3         |            | mA     | Internal reference                                                                 |

## 仕様

表 2. 電気的特性（続き）

| Parameter                                                                      | Min  | Typ  | Max | Unit               | Test Conditions/Comments |

|--------------------------------------------------------------------------------|------|------|-----|--------------------|--------------------------|

| 1k $\Omega$ to GND, 7.7k $\Omega$ to GND, and 32k $\Omega$ to GND <sup>6</sup> | 0.67 | 0.85 | mA  | External reference |                          |

|                                                                                | 1.45 | 1.7  | mA  | Internal reference |                          |

<sup>1</sup> 特に指定のない限り、DC 仕様は出力無負荷でテスト。直線性は、256～65279 の縮小コード範囲を使って計算。

<sup>2</sup> このデバイスは、一時的過負荷状態でデバイスを保護することを目的とした電流制限機能を内蔵しています。電流制限限時にはジャンクション温度の限度を超える可能性があります。仕様規定された最大動作ジャンクション温度を超えての動作は、デバイスの信頼性を損なう可能性があります。

<sup>3</sup> 電圧リファレンスの温度係数はボックス法に従って計算します。詳細については、用語の定義のセクションを参照してください。

<sup>4</sup> MUX\_OUT\_SELECT (SEL) を通じて異なるチャンネルをモニタしているときに、VOUTn チャンネルに現れるピーク電圧グリッチ。

<sup>5</sup> インターフェースは非アクティブ。すべてのチャンネルは動作モード 0 で、出力が無負荷の状態。

<sup>6</sup> インターフェースは非アクティブ。すべてのチャンネルは動作モード 1、2、または 3。

## AC 特性

特に指定のない限り、VDD = 2.7V～5.5V、1.08V  $\leq$  IOVDD  $\leq$  1.98V、VREF = 2.5V（外部）、RL = 2k $\Omega$ ～GND、CL = 200pF、すべての仕様は TJ = -40°C～+125°C における値で、代表値は TA = 25°C での値。

表 3. AC 特性

| Parameter                                    | Min  | Typ | Max | Unit           | Test Condition/Comments                                                                                                               |

|----------------------------------------------|------|-----|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| OUTPUT VOLTAGE SETTLING TIME                 | 5    | 12  |     | $\mu$ s        | 1/4 to 3/4 scale settling to $\pm 2$ LSB                                                                                              |

| SLEW RATE                                    | 1.1  |     |     | V/ $\mu$ s     |                                                                                                                                       |

| DIGITAL-TO-ANALOG GLITCH IMPULSE             | 1    |     |     | nV-sec         | 1 LSB change around major carry, internal reference, and range = 0 to VREF                                                            |

| DIGITAL FEEDTHROUGH                          | 0.05 |     |     | nV-sec         | Internal reference                                                                                                                    |

| CROSSTALK <sup>1</sup>                       | 0.08 |     |     | nV-sec         | Internal reference                                                                                                                    |

|                                              | -0.4 |     |     | nV-sec         | Internal reference and range = 0 to VREF                                                                                              |

|                                              | -0.7 |     |     | nV-sec         | Internal reference and range = 0 to 2 $\times$ VREF                                                                                   |

| DAC-to-DAC                                   | -0.7 |     |     | nV-sec         | Internal reference and range = 0 to 2 $\times$ VREF                                                                                   |

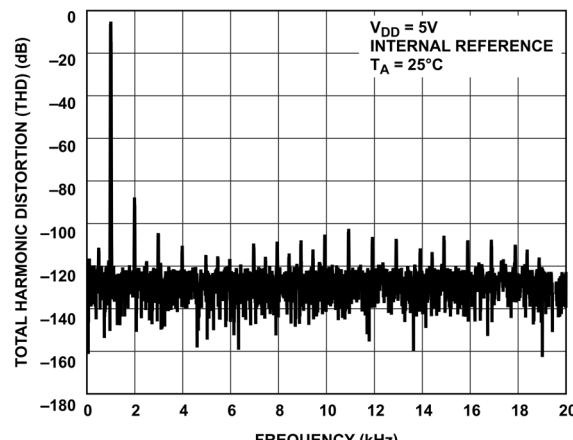

| TOTAL HARMONIC DISTORTION (THD) <sup>2</sup> | -93  |     |     | dB             | At TA, bandwidth = 20kHz, VDD = 5V, output frequency (f <sub>OUT</sub> ) = 1kHz, internal reference, and range = 0 to 2 $\times$ VREF |

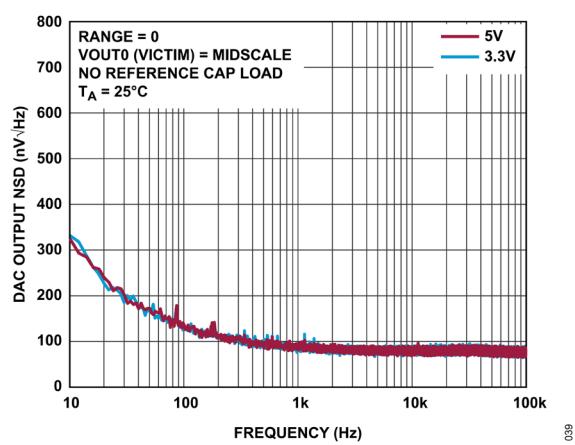

| OUTPUT NOISE SPECTRAL DENSITY                | 62   |     |     | nV/ $\sqrt$ Hz | DAC code = midscale, 10kHz, range = 0 to 2 $\times$ VREF, and external reference                                                      |

|                                              | 115  |     |     | nV/ $\sqrt$ Hz | DAC code = midscale, 10kHz, range = 0 to 2 $\times$ VREF, and internal reference                                                      |

| OUTPUT NOISE                                 | 14   |     |     | $\mu$ V p-p    | 0.1Hz to 10Hz and range = 0 to VREF                                                                                                   |

| SIGNAL-TO-NOISE RATIO (SNR)                  | 92   |     |     | dB             | At TA = 25°C, bandwidth = 20kHz, VDD = 5V, f <sub>OUT</sub> = 1kHz, and internal reference                                            |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)           | 84   |     |     | dB             | At TA = 25°C, bandwidth = 20kHz, VDD = 5V, f <sub>OUT</sub> = 1kHz, and internal reference                                            |

| SIGNAL-TO-NOISE-AND-DISTORTION RATIO (SINAD) | 90   |     |     | dB             | At TA = 25°C, bandwidth = 20kHz, VDD = 5V, f <sub>OUT</sub> = 1kHz, internal reference, and range = 0 to 2 $\times$ VREF              |

<sup>1</sup> 用語の定義のセクションを参照してください。特に指定のない限り、内部リファレンスとレンジ = 0～VREF で測定。

<sup>2</sup> デジタル的に生成した 1kHz のサイン波 (f<sub>OUT</sub>)。

## 仕様

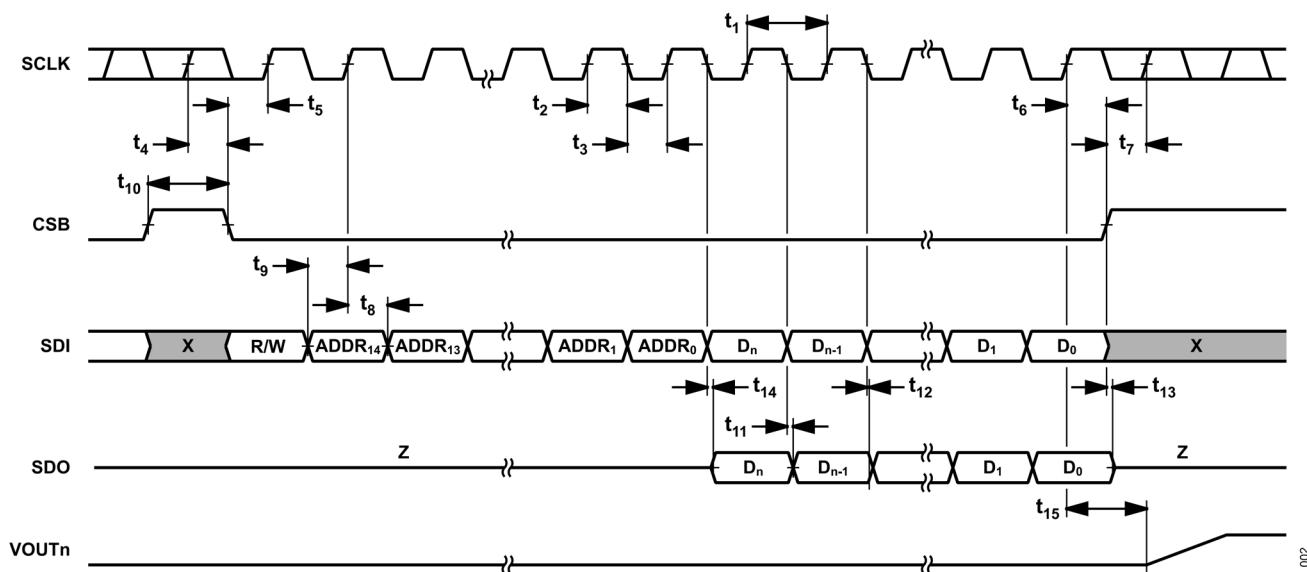

## タイミング特性

すべての入力信号は立上がり時間 ( $t_R$ ) = 立下り時間 ( $t_F$ ) = 1ns/V (V<sub>DD</sub>の 10%~90%) で仕様規定され、電圧レベル(V<sub>INL</sub> + V<sub>INH</sub>)/2 からの時間。V<sub>DD</sub> = 2.7V~5.5V、1.08V ≤ IOVDD ≤ 1.98V、および V<sub>REF</sub> = 2.5V。特に指定のない限り、すべての仕様は T<sub>J</sub> = -40°C~+125°C での値。

表 4. SPI インターフェースのタイミング仕様

| Parameter       | Description                                             | Min             | Typ               | Max | Unit |

|-----------------|---------------------------------------------------------|-----------------|-------------------|-----|------|

| t <sub>1</sub>  | SCLK cycle time                                         | 20              |                   |     | ns   |

|                 |                                                         | 80 <sup>1</sup> |                   |     |      |

| t <sub>2</sub>  | SCLK high time                                          |                 | t <sub>1</sub> /2 |     | ns   |

| t <sub>3</sub>  | SCLK low time                                           |                 | t <sub>1</sub> /2 |     | ns   |

| t <sub>4</sub>  | SCLK rising edge to CSB falling edge                    | 10              |                   |     | ns   |

| t <sub>5</sub>  | CSB falling edge to SCLK rising edge setup time         | 7               |                   |     | ns   |

| t <sub>6</sub>  | SCLK rising edge to CSB rising edge                     | 4               |                   |     | ns   |

| t <sub>7</sub>  | CSB rising edge to SCLK rising edge                     | 6               |                   |     | ns   |

| t <sub>8</sub>  | Data hold time                                          | 2               |                   |     | ns   |

| t <sub>9</sub>  | Data setup time                                         | 5               |                   |     | ns   |

| t <sub>10</sub> | CSB high time (single, combined, or all channel update) | 10              |                   |     | ns   |

| t <sub>11</sub> | SCLK falling edge to SDO data available                 |                 | 9                 |     | ns   |

| t <sub>12</sub> | SCLK falling edge to SDO data remains valid             |                 | 10                |     | ns   |

| t <sub>13</sub> | CSB rising edge to SDO disabled                         |                 | 9                 |     | ns   |

| t <sub>14</sub> | SCLK falling edge to SDO enabled                        |                 | 10                |     | ns   |

| t <sub>15</sub> | Last SCLK rising edge to VOUT transition start          |                 | 3                 |     | μs   |

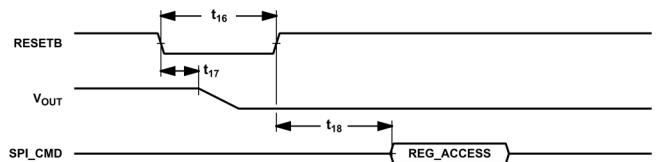

| t <sub>16</sub> | RESETB pulse width                                      |                 | 2.5               |     | μs   |

| t <sub>17</sub> | RESETB falling edge to VOUT transition                  |                 | 3                 |     | μs   |

| t <sub>18</sub> | RESETB rising edge to SPI transaction begin             |                 | 150               |     | ns   |

<sup>1</sup>ストリーム・モード機能だけに適用。

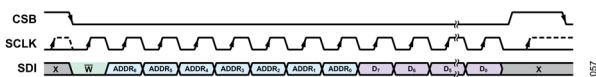

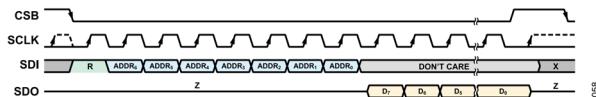

図 2. シリアル読み出し動作と書き込み動作

## 仕様

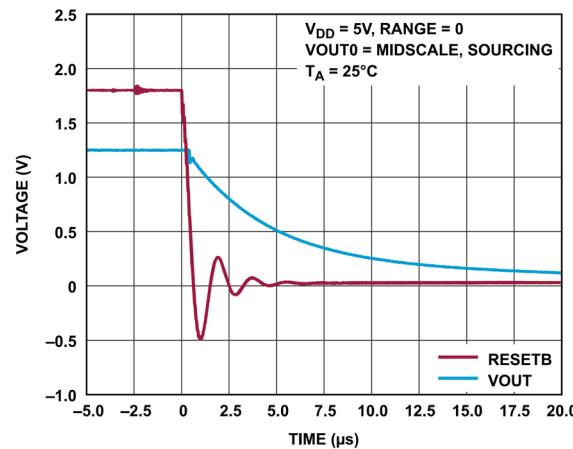

図 3. リセット・タイミング

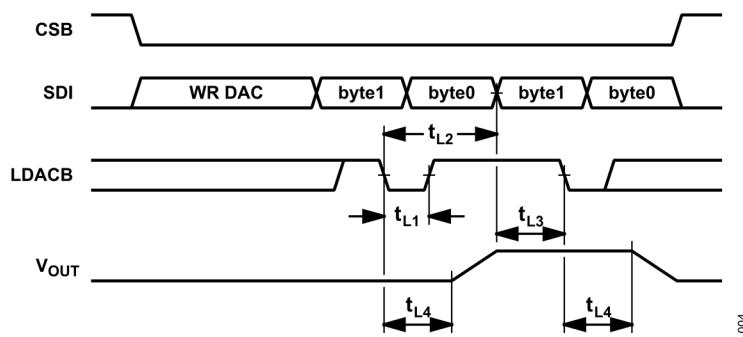

表 5. LDAC のタイミング仕様

| Parameter | Description                                    | Min | Typ | Max | Unit |

|-----------|------------------------------------------------|-----|-----|-----|------|

| $t_{L1}$  | LDACB pulse width (For both CSB==1 and CSB==0) | 120 |     |     | ns   |

| $t_{L2}$  | LDACB falling edge to SPI DAC update.          | 640 |     |     | ns   |

| $t_{L3}$  | SPI DAC update to LDACB negative edge.         | 640 |     |     | ns   |

| $t_{L4}$  | LDACB falling edge to VOUT transition          |     | 1.3 |     | μs   |

図 4. LDAC のタイミング

## 絶対最大定格

表 6. 絶対最大定格

| Parameter                                              | Rating                |

|--------------------------------------------------------|-----------------------|

| VDD to GND                                             | -0.3V to +6.5V        |

| IOVDD to GND                                           | -0.3V to +2.1V        |

| VOUTn to GND                                           | -0.3V to VDD + 0.3V   |

| VREF <sup>1</sup> to GND                               | -0.3V to VDD + 0.3V   |

| Digital Input Voltage to GND                           | -0.3V to IOVDD + 0.3V |

| Temperature                                            |                       |

| Operating Junction Temperature Range                   | -40°C to +125°C       |

| Storage Temperature Range                              | -65°C to +150°C       |

| Absolute Maximum Junction Temperature                  | 150°C                 |

| Reflow Soldering Peak Temperature, Pb-Free (J-STD-020) | 260°C                 |

<sup>1</sup> リファレンス入力ピンとして設定。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上のデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意を払う必要があります。

$\theta_{JA}$  は 1 立方フィートの密閉容器内で測定された自然対流時の周囲とジャンクション間の熱抵抗、 $\theta_{JB}$  はジャンクションとボード間の熱抵抗、 $\theta_{JC}$  はジャンクションとケース間の熱抵抗、 $\psi_{JT}$  はジャンクションと上面間の熱特性評価パラメータ、 $\psi_{JB}$  はジャンクションとボードの間の熱特性値です。

表 7. 热抵抗

| Package Type          | $\theta_{JA}$ | $\theta_{JB}$ | $\theta_{JC}$ | $\psi_{JT}$ | $\psi_{JB}$ | Unit |

|-----------------------|---------------|---------------|---------------|-------------|-------------|------|

| CB-25-11 <sup>1</sup> | 43.71         | 9.64          | 4.75          | 4.42        | 9.64        | °C/W |

<sup>1</sup> 4 個のサーマル・ビアを持つ JEDEC 2S2P ボードを使用した自然空冷（空気流 0m/sec）の場合のシミュレーション値。

## ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能の説明

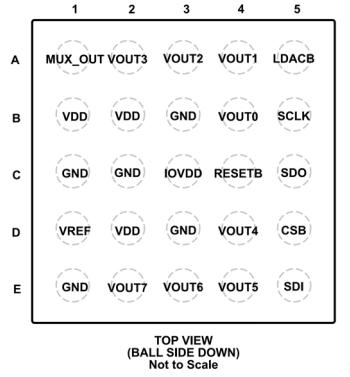

図 5. WLCSP のピン配置

表 8. ピン機能の説明

| ピン番号               | 記号      | タイプ <sup>1</sup> | 説明                                                                                                                   |

|--------------------|---------|------------------|----------------------------------------------------------------------------------------------------------------------|

| A1                 | MUX_OUT | AO               | アナログ・マルチプレクサ。MUX_OUT ピンは、選択したチャンネルの内部ダイ温度、出力電圧、および出力電流をモニタするために使用します。                                                |

| B1, B2, D2         | VDD     | S                | 電源入力。AD3530/AD3530R は 2.7V~5.5V で動作します。VDD 電源は、10μF のコンデンサと 0.1μF のコンデンサを並列にして GND に接続することによりデカップリングします。             |

| C3                 | IOVDD   | DI               | デジタル電源。IOVDD ピンの電圧仕様は表 2 のセクションに規定されています。                                                                            |

| B3, C1, C2, D3, E1 | GND     | S                | デバイスのすべての回路のグラウンド基準ポイント。                                                                                             |

| D1                 | VREF    | AI/O             | リファレンス出力電圧。内部リファレンスを使用する場合、これはリファレンス出力ピンになります。デフォルトでは、VREF はリファレンス入力です。                                              |

| E2                 | VOUT7   | AO               | DAC 7 からのアナログ出力電圧。出力アンプはレール to レールで動作します。                                                                            |

| E3                 | VOUT6   | AO               | DAC 6 からのアナログ出力電圧。出力アンプはレール to レールで動作します。                                                                            |

| E4                 | VOUT5   | AO               | DAC 5 からのアナログ出力電圧。出力アンプはレール to レールで動作します。                                                                            |

| D4                 | VOUT4   | AO               | DAC 4 からのアナログ出力電圧。出力アンプはレール to レールで動作します。                                                                            |

| E5                 | SDI     | DI               | シリアル・データ入力。ロジック入力。デバイスに書き込むデータを提供し、SCLK の立上がりエッジに合わせてレジスタに入力されます。                                                    |

| D5                 | CSB     | DI               | アクティブ・ローの制御入力。これは、入力データに対するフレーム同期化信号です。                                                                              |

| C4                 | RESETB  | DI               | 非同期リセット・ピン。立上がりエッジで動作するアクティブ・ローのロジック入力です。詳細については、 <a href="#">ハードウェア・リセット</a> のセクションを参照してください。                       |

| C5                 | SDO     | DO               | シリアル・データ出力。ロジック出力。リードバック動作を行うと、この出力ピンにシリアル・データ・ストリームとしてデータが供給されます。データは SCLK の立上がりエッジでクロック出力され、SCLK の立上がりエッジで有効になります。 |

| B5                 | SCLK    | DI               | シリアル・クロック入力。書込み動作と読み出し動作のために最大 50MHz のレートでデータを転送します。                                                                 |

| A5                 | LDACB   | DI               | 非同期ロード DAC ピン。立上がりエッジで動作するアクティブ・ローのロジック入力です。詳細については、 <a href="#">ハードウェア LDAC</a> のセクションを参照してください。                    |

| B4                 | VOUT0   | AO               | DAC 0 からのアナログ出力電圧。出力アンプはレール to レールで動作します。                                                                            |

| A4                 | VOUT1   | AO               | DAC 1 からのアナログ出力電圧。出力アンプはレール to レールで動作します。                                                                            |

| A3                 | VOUT2   | AO               | DAC 2 からのアナログ出力電圧。出力アンプはレール to レールで動作します。                                                                            |

| A2                 | VOUT3   | AO               | DAC 3 からのアナログ出力電圧。出力アンプはレール to レールで動作します。                                                                            |

<sup>1</sup> AO はアナログ出力ピン、AI/O はアナログ入力または出力ピン、S は電源ピン、DI はデジタル入力ピン、DO はデジタル入力ピンです。

## 代表的な性能特性

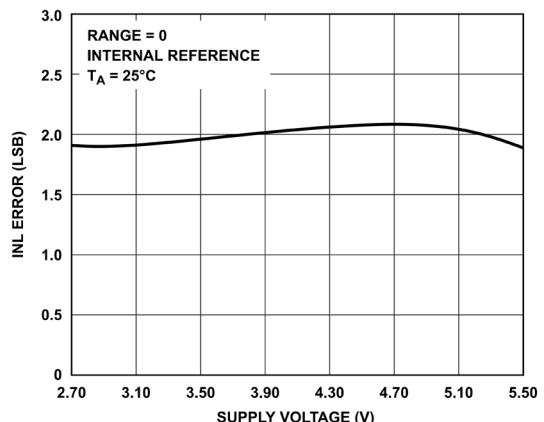

図 6. INL 誤差とコードの関係

図 9. INL 誤差と温度の関係

図 7. DNL 誤差とコードの関係

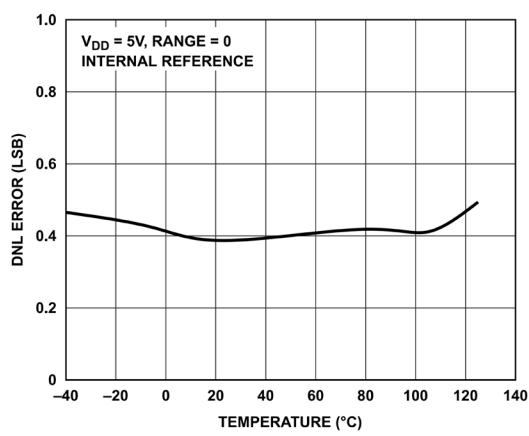

図 10. DNL 誤差と温度の関係

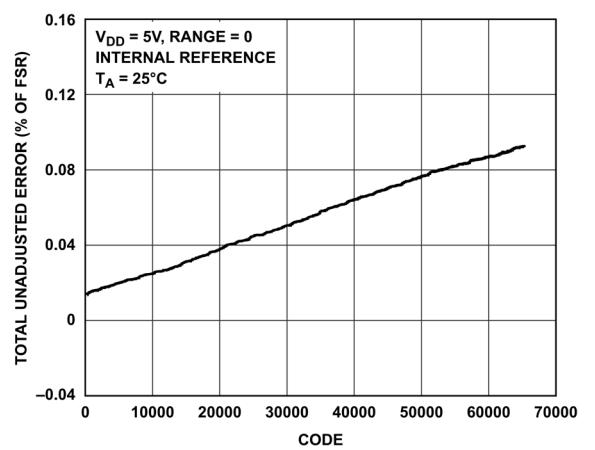

図 8. TUE とコードの関係

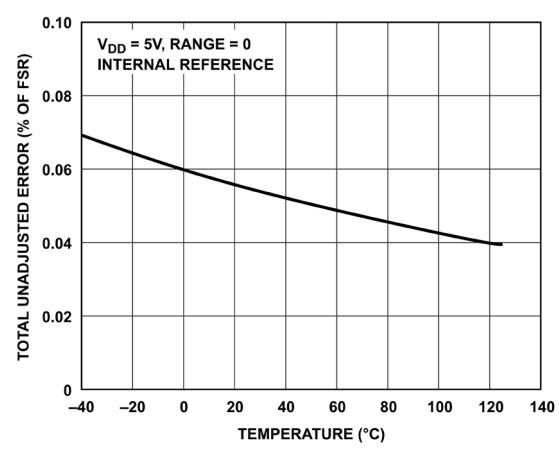

図 11. TUE と温度の関係

## 代表的な性能特性

図 12. INL 誤差と電源電圧の関係

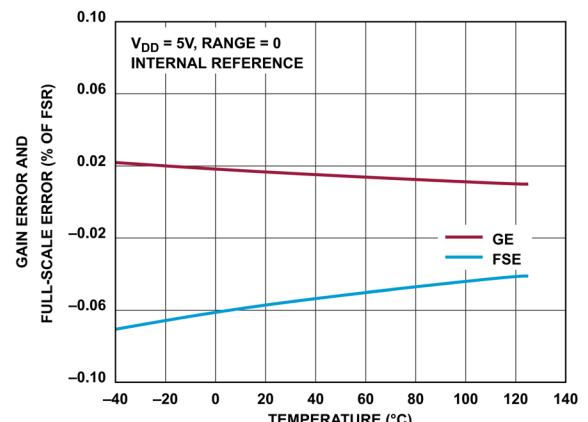

図 15. ゲイン誤差およびフルスケール誤差と温度の関係

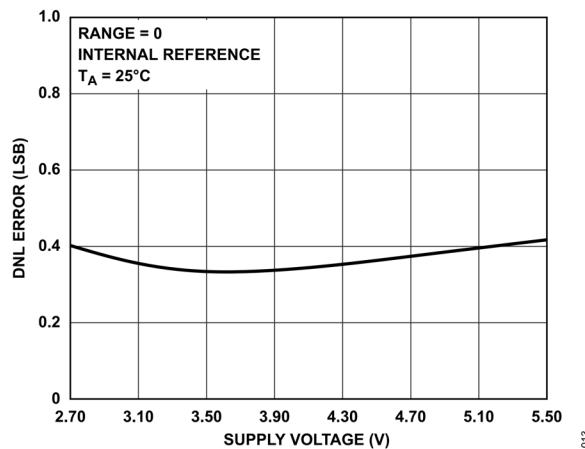

図 13. DNL 誤差と電源電圧の関係

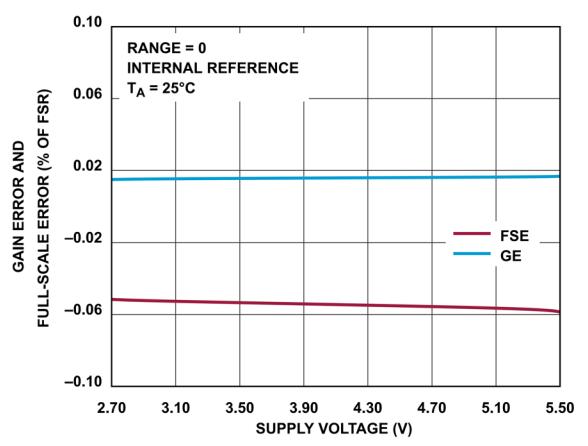

図 16. ゲイン誤差およびフルスケール誤差と電源電圧の関係

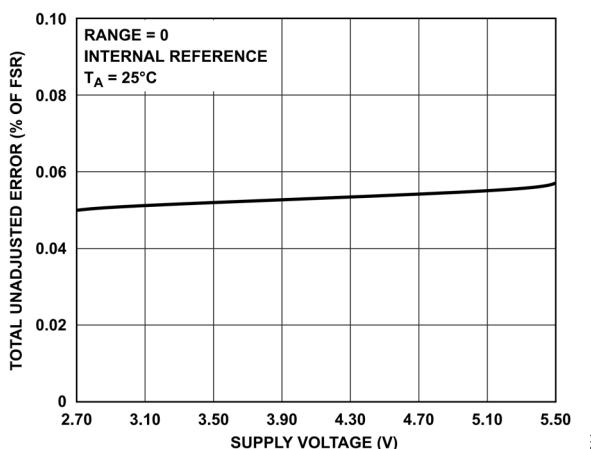

図 14. TUE と電源電圧の関係

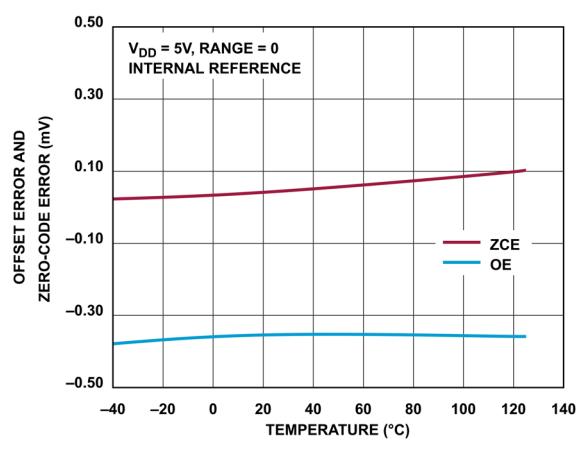

図 17. オフセット誤差およびゼロコード誤差と温度の関係

## 代表的な性能特性

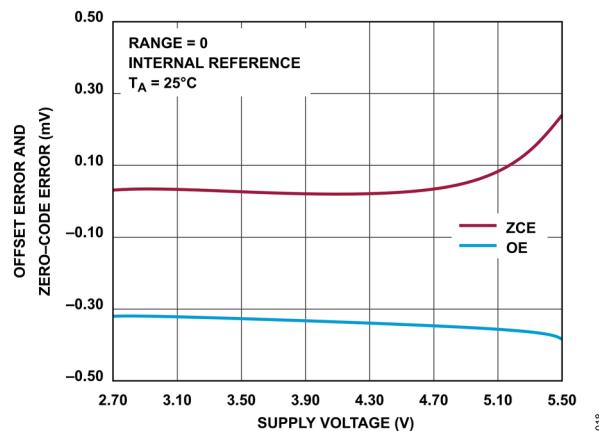

図 18. オフセット誤差およびゼロコード誤差と電源電圧の関係

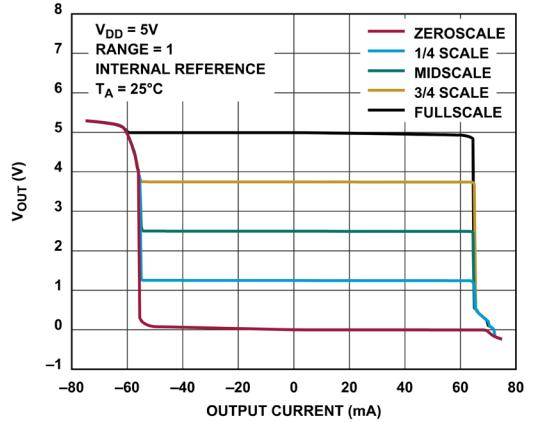

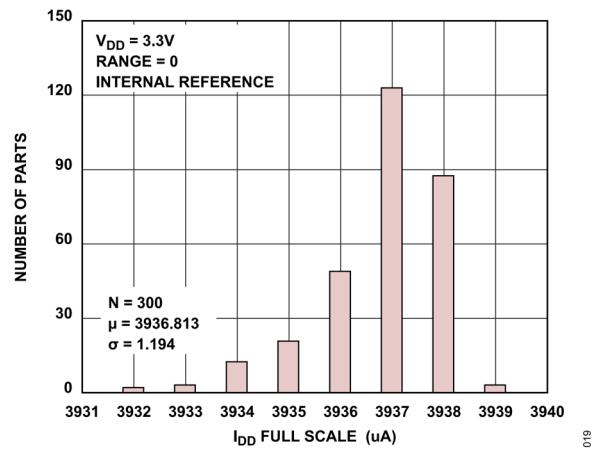

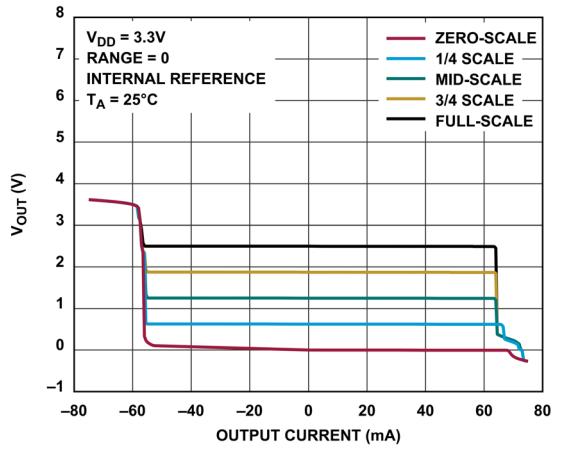

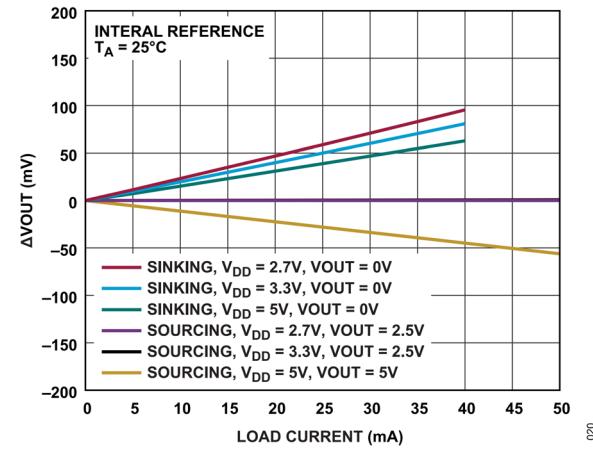

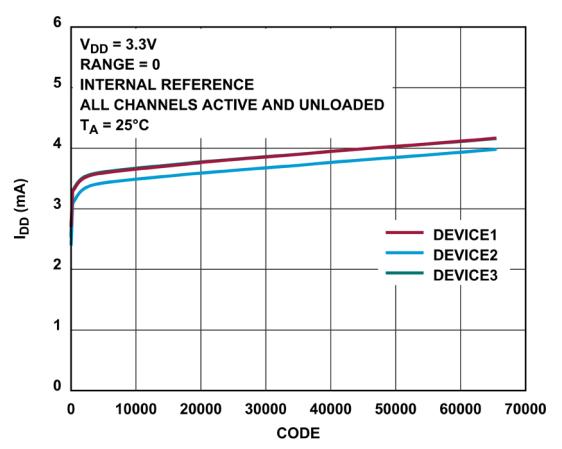

図 21.  $V_{DD} = 5V$  でのソース能力とシンク能力図 19. 内部リファレンス使用時の電源電流 ( $I_{DD}$ ) ヒストグラム図 22.  $V_{DD} = 3.3V$  でのソース能力とシンク能力図 20. ヘッドルームおよびフットルーム ( $\Delta V_{OUT}$ ) と負荷電流の関係図 23.  $I_{DD}$  とコードの関係

## 代表的な性能特性

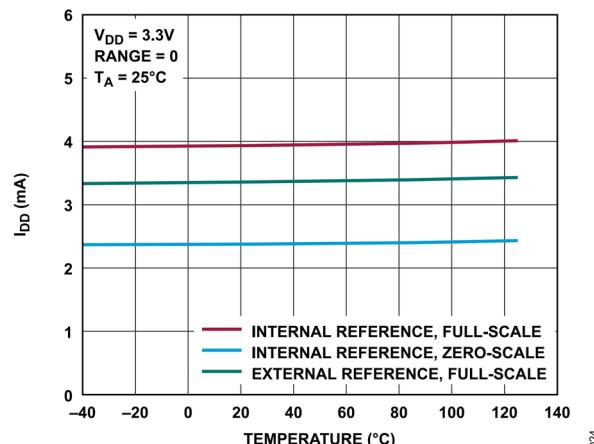

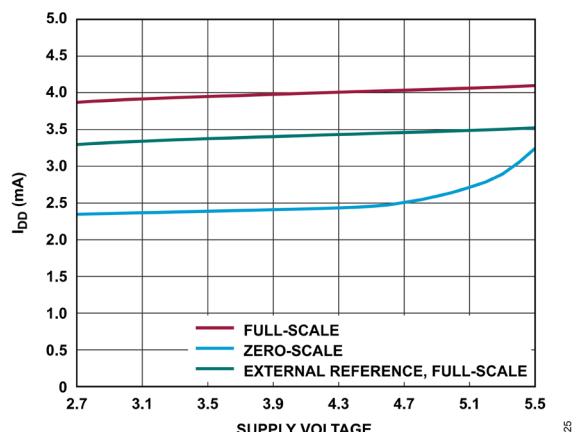

図 24.  $I_{DD}$  と温度の関係

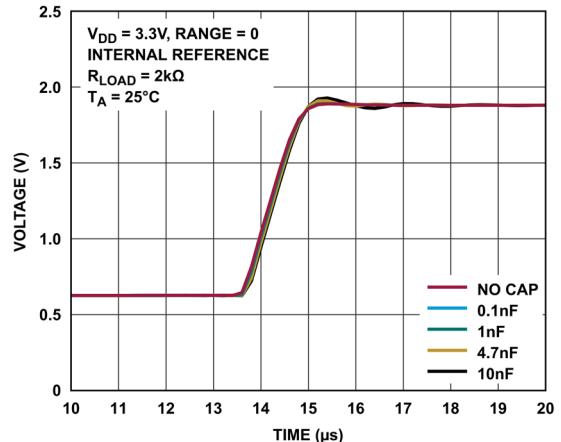

図 27. 異なる容量性負荷でのセッティング時間

図 25.  $I_{DD}$  と電源電圧の関係

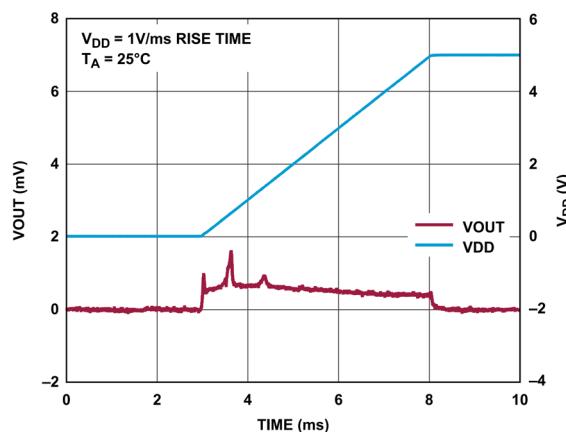

図 28. パワーオン・リセット時のスリーステート出力

図 26. セッティング時間

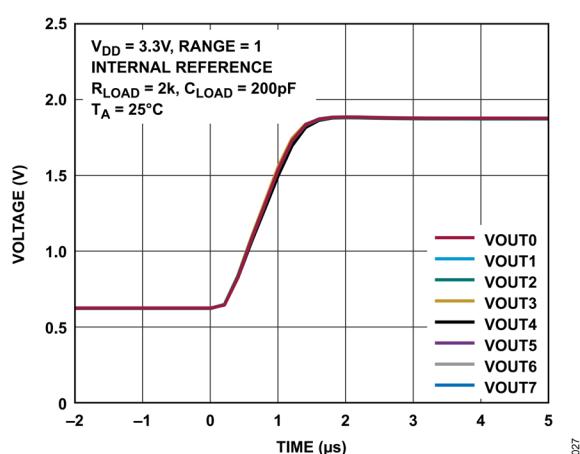

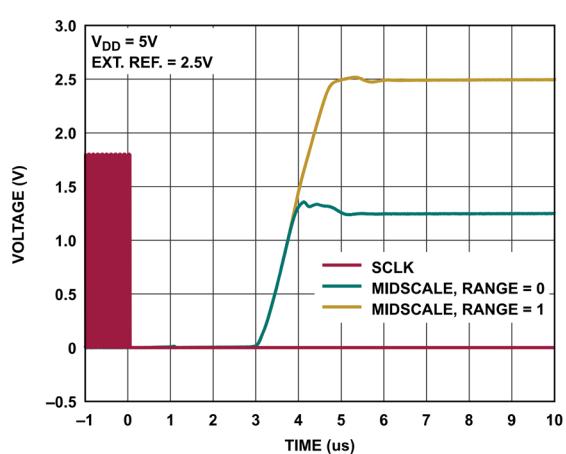

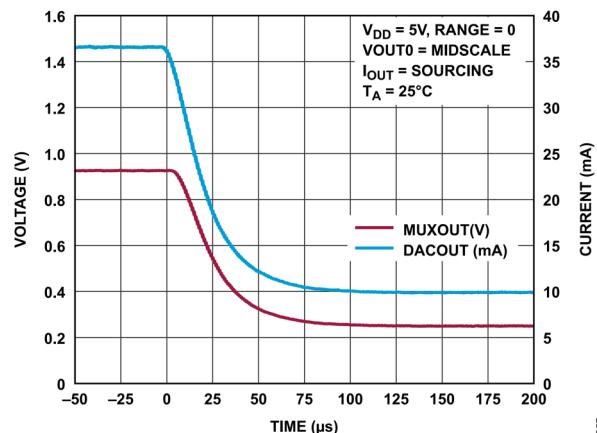

図 29. パワーダウン終了時のミッドスケール出力

## 代表的な性能特性

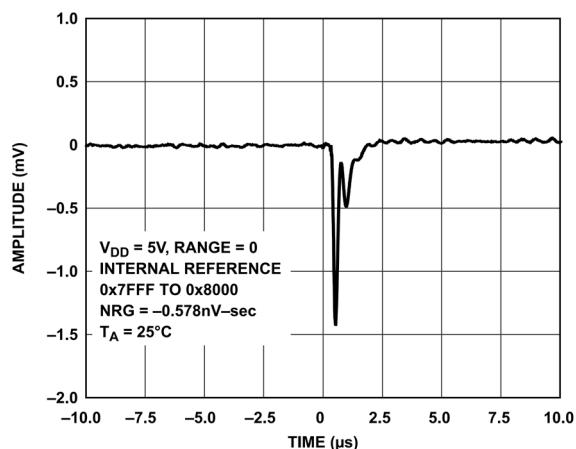

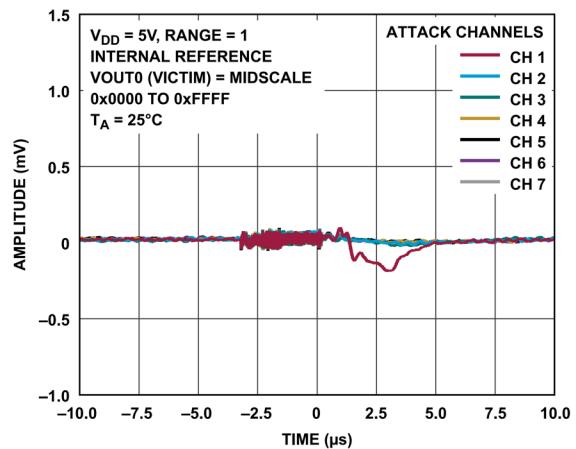

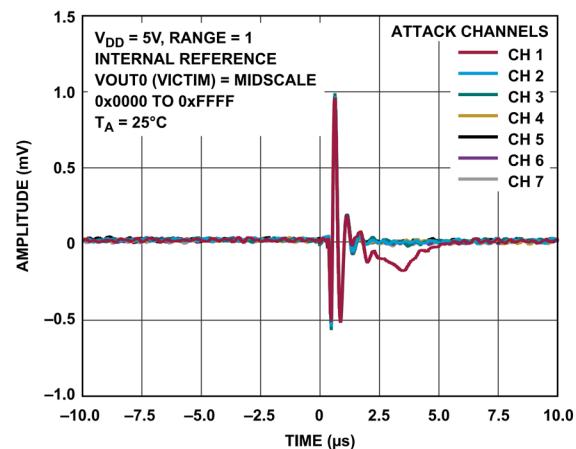

図 30. デジタル／アナログ・グリッヂ・インパルス、5V

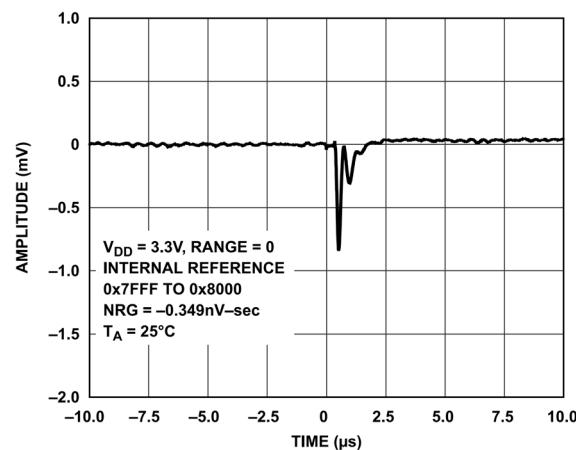

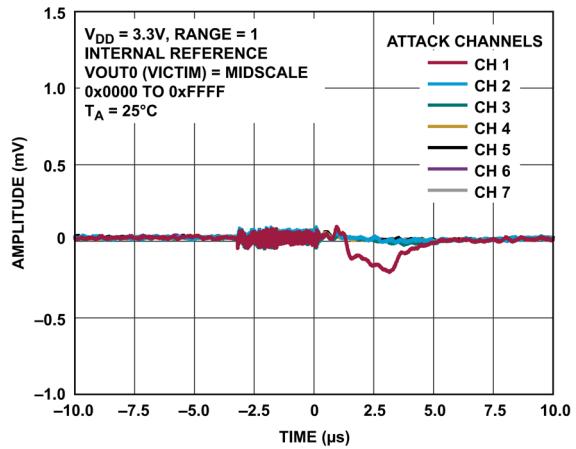

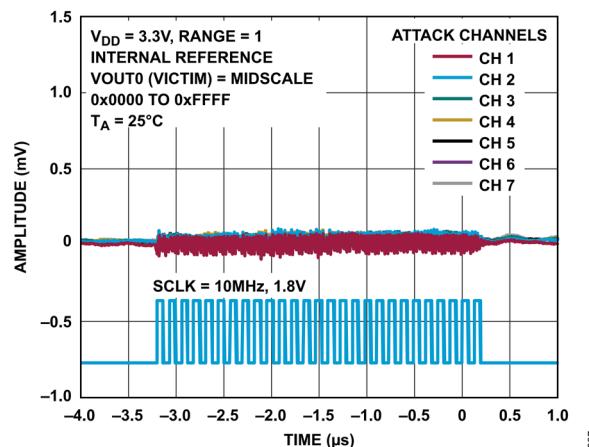

図 31. デジタル／アナログ・グリッヂ・インパルス、3.3V

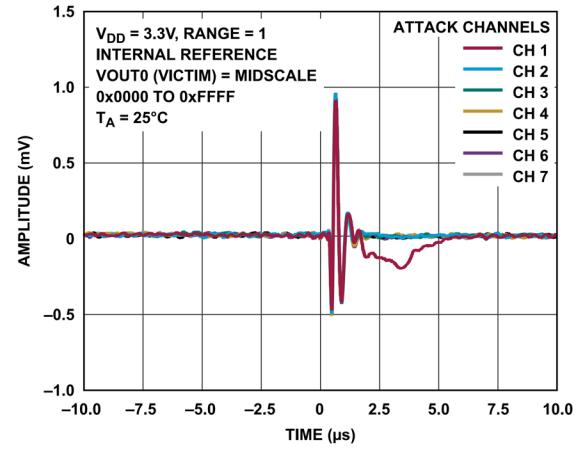

図 33. アナログ・クロストーク、3.3V

図 34. DAC 間クロストーク、5V

図 32. アナログ・クロストーク、5V

図 35. DAC 間クロストーク、3.3V

## 代表的な性能特性

図 36. デジタル・フィードスルー

図 39. 1kHz での THD

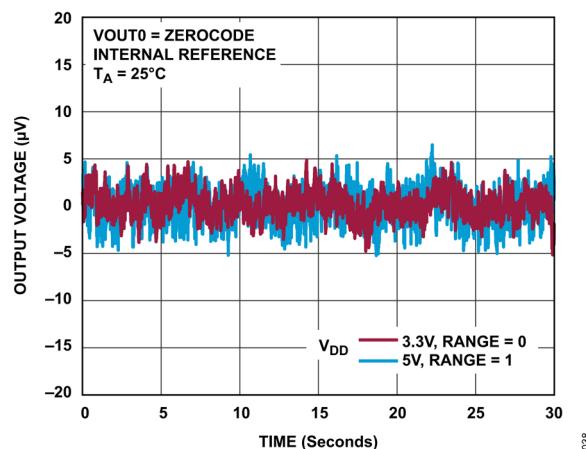

図 37. 0.1Hz~10Hz での出力ノイズ

図 40. ハードウェア・リセット

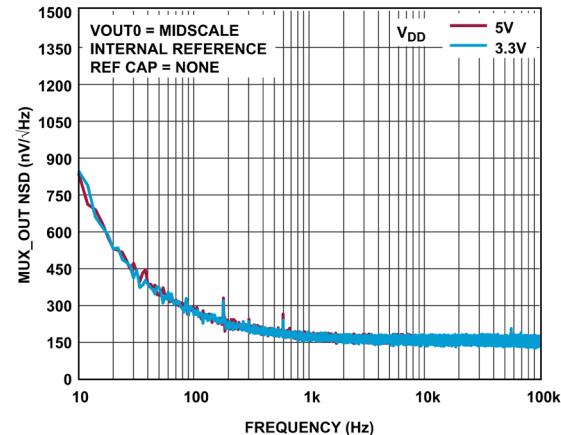

図 38. ノイズ・スペクトル密度 (NSD)

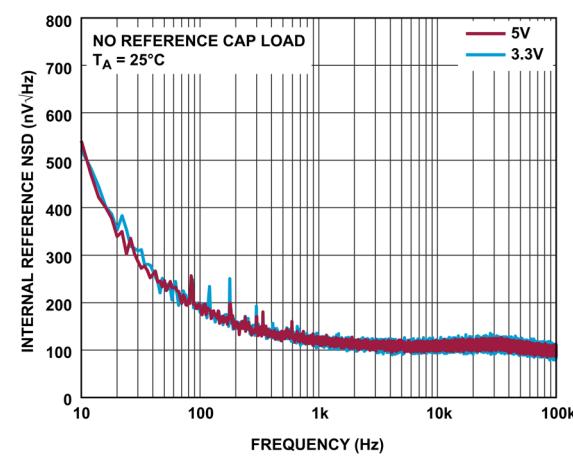

図 41. 内部リファレンス NSD と周波数の関係

## 代表的な性能特性

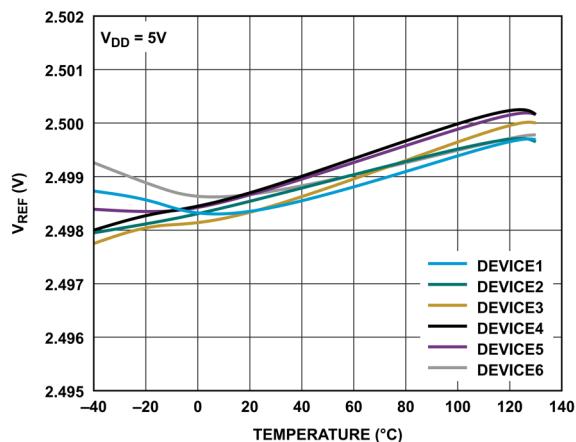

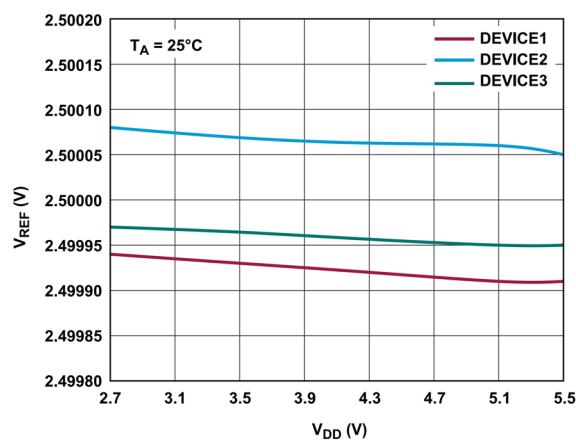

図 42. VREF と温度の関係

043

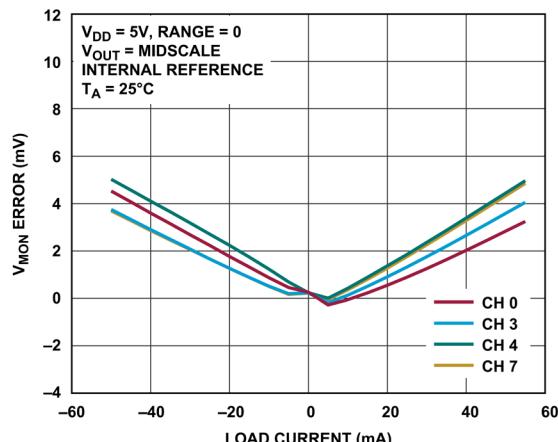

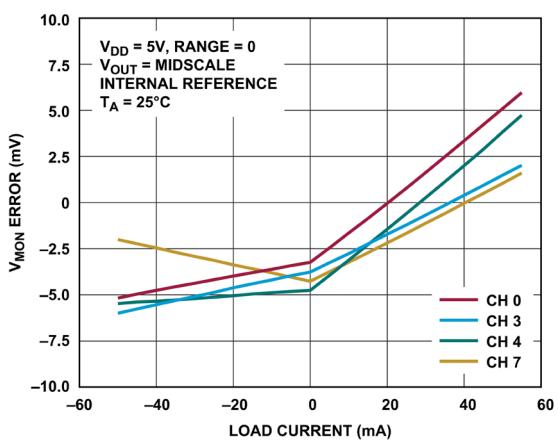

図 45. MUX\_OUT 誤差と出力電流の関係、5V

046

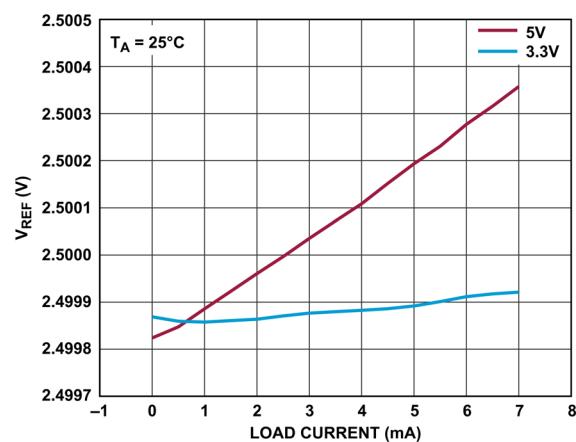

図 43. VREF と負荷電流の関係

044

図 46. MUX\_OUT 誤差と出力電圧の関係、5V

047

図 44. VREF と VDD の関係

045

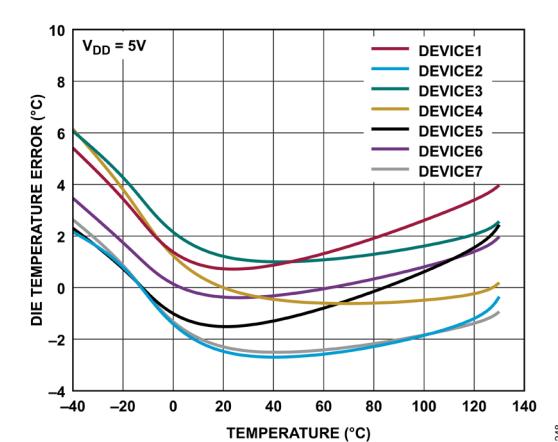

図 47. MUX\_OUT 誤差と内部ダイ温度の関係

048

## 代表的な性能特性

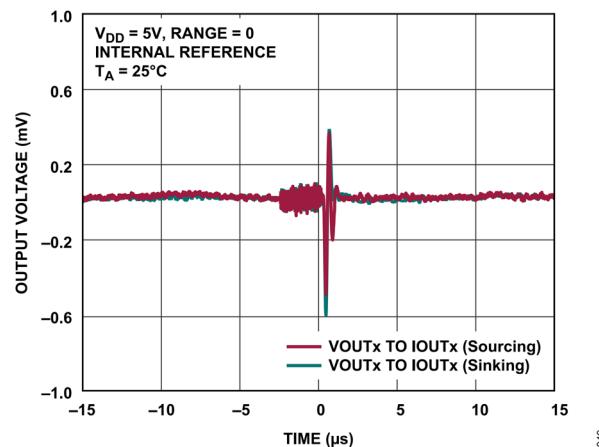

図 48. MUX\_OUT から VOUTx へのグリッチ

図 51. MUX\_OUT NSD

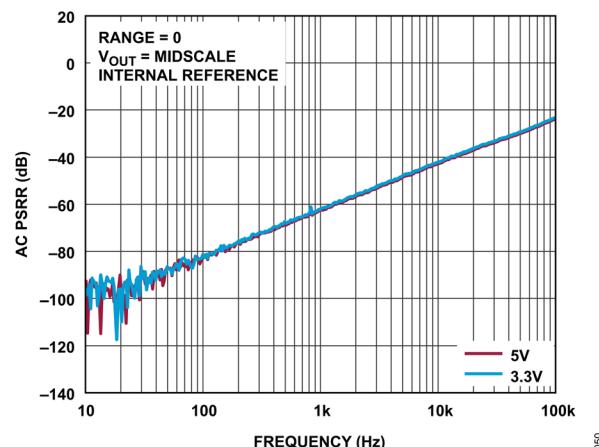

図 49. VOUT AC PSRR と周波数の関係

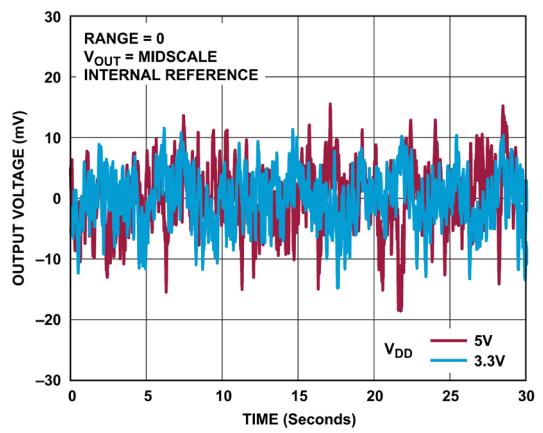

図 52. MUX\_OUT の 0.1Hz～10Hz (1/f) ノイズ

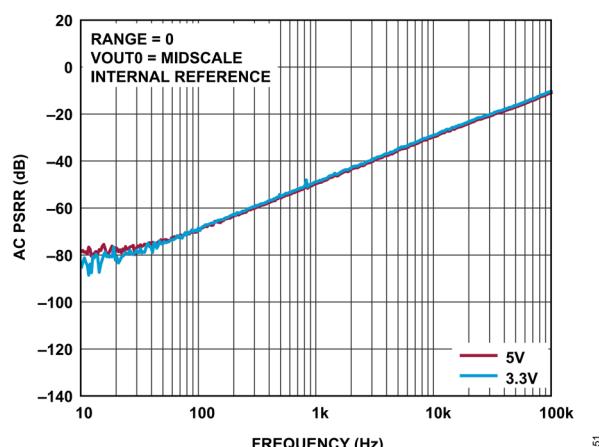

図 50. MUX\_OUT AC PSRR と周波数の関係

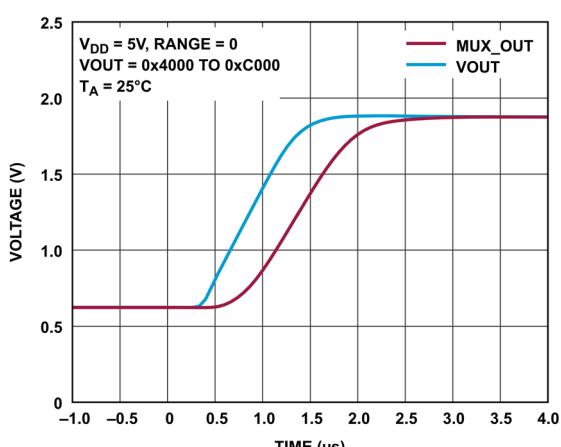

図 53. MUX\_OUT と出力電圧 トランジェントの関係、立上がり

## 代表的な性能特性

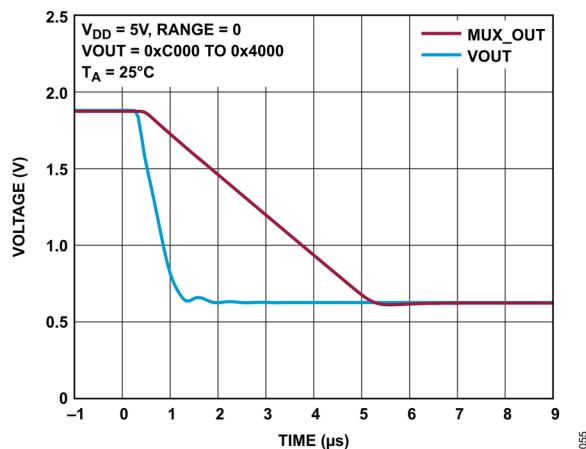

図 54. MUX\_OUT と出力電圧トランジエントの関係、立下がり

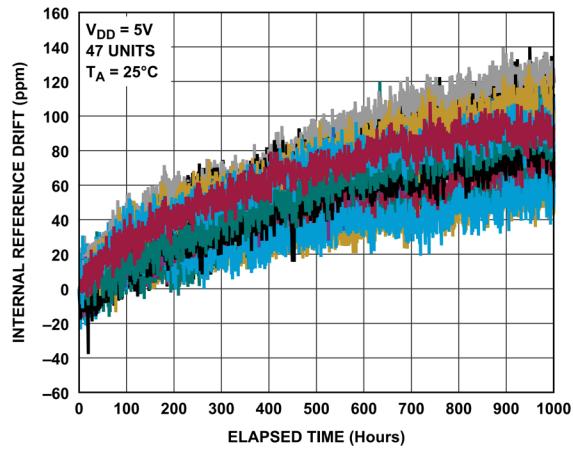

図 57. リファレンスの長期ドリフト

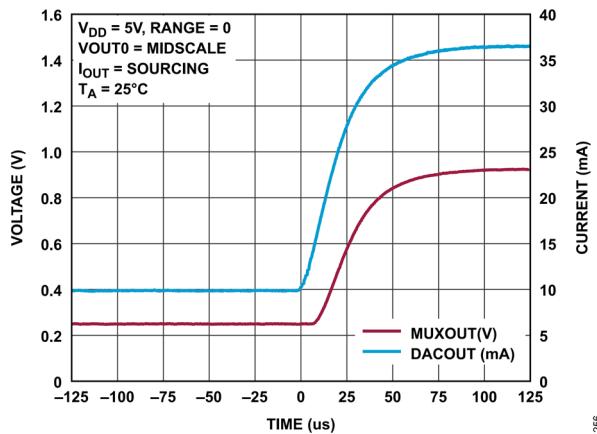

図 55. MUX\_OUT と出力電流トランジエントの関係、立上がり

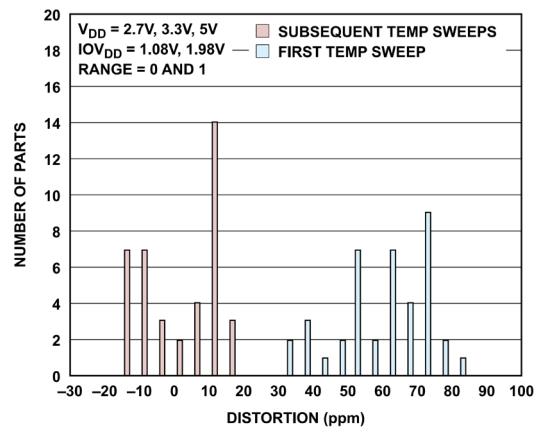

図 58. リファレンスの熱ヒステリシス

図 56. MUX\_OUT と出力電流トランジエントの関係、立下がり

## 用語の定義

### 相対精度または積分非直線性 (INL)

DACの場合、相対精度すなわち積分非直線性は、DAC伝達関数の上下両端を結ぶ直線からの最大偏差 (LSB単位で表示) を表します。

### 微分非直線性誤差 (DNL)

微分非直線性 (DNL) は、隣接する 2 つのコードの間での測定された変化と理論的な 1LSB 変化との差を表します。

### オフセット誤差

オフセット誤差は、伝達関数の直線領域での  $V_{OUT}$  (実測値) と  $V_{OUT}$  (理論) の差を表し、mV で表示されます。オフセット誤差は、コード 256 を DAC レジスタにロードして測定します。これは負または正の値となります。

### オフセット誤差ドリフト

オフセット誤差ドリフトは、温度変化に伴うオフセットの相対的变化を測定したもので、単位は ppm/ $^{\circ}$ C です。所定温度での合計オフセットは、次式で表されます。

$$\text{Deviation at } T = \text{Deviation at } 25^{\circ}\text{C}$$

$$+ \frac{TC \times (T - 25) \times V_{RANGE}}{10^6}$$

### フルスケール/ゼロスケール誤差

これらの誤差は、25 $^{\circ}$ C におけるフルスケールおよびゼロスケールでの理想値からの偏差を表します。フルスケール・レンジ (FSR) に対するパーセンテージで表されます。

### フルスケール/ゼロスケール誤差ドリフト

これらのパラメータは、理想的なゼロスケール電圧とフルスケール電圧を基準としたゼロスケール電圧とフルスケール電圧の変動を、温度の関数として表したもので。単位は ppm/ $^{\circ}$ C です。合計偏差の温度変化は、オフセット誤差ドリフトと同じ式を使って計算します。

### DC PSRR および AC PSRR

PSRR は、DAC 出力に対する電源電圧変化の影響を表します。PSRR は、DAC のミッドスケール出力での、 $V_{OUT}$  変化の電源電圧変化に対する比です。DC PSRR の測定単位は mV/V で、VDD の変化は  $\pm 10\%$  です。これに対し AC PSRR の測定単位は dB で、VDD には  $\pm 200\text{mVp-p}$  の AC 掃引信号が注入されます。

### 出力電圧のセトリング時間

出力電圧セトリング時間は、所定のステップ変化に対して、DAC の出力が指定されたレベルに安定するまでに要する時間です。

### デジタル/アナログ・グリッチ・インパルス

デジタル/アナログ・グリッチ・インパルスは、DAC レジスタ内の入力コードが変化したときに、アナログ出力に混入するインパルスを表します。通常  $\text{nV} \times \text{sec}$  で表すグリッチの面積として規定され、デジタル入力コードが 1LSB だけ変化したときに測定されます。

### デジタル・フィードスルー

デジタル・フィードスルーは、DAC 出力の更新が行われていないときに、DAC のデジタル入力から DAC のアナログ出力に注入されるインパルスを表します。 $\text{nV} \times \text{sec}$  で規定され、データ・バス上でのフルスケールのコード変化時、すなわち全ビット 0 から全ビット 1 への変化時、または全ビット 1 から全ビット 0 への変化時に測定されます。

### 出力ノイズ・スペクトル密度

ノイズ・スペクトル密度は、内部で発生するランダム・ノイズを測定したものです。ノイズの測定はミッドスケール・コードのロード時に DAC 出力で行い、中心周波数は 10kHz に設定されます。測定単位は  $\text{nV}/\sqrt{\text{Hz}}$  です。

### 全高調波歪み (THD)

THD は、理想的な正弦波と、DAC を使って減衰した正弦波との偏差を表します。DAC に対してリファレンスとして正弦波を使ったときに、DAC 出力に現われる高調波が THD になります。単位は dB です。

### 電圧リファレンス温度係数 (TC)

電圧リファレンス TC は、温度変化に伴うリファレンス出力電圧の変化を表します。電圧リファレンス TC はボックス法を使って計算します。この方法では、次のように、ppm/ $^{\circ}$ C 単位で表される所定の温度範囲でのリファレンス出力の最大変化として TC を定義しています。

$$TC = \left( \frac{V_{REF\_MAX} - V_{REF\_MIN}}{V_{REF\_NOM} \times TEMP\_RANGE} \right) \times 10^6 \quad (1)$$

ここで、

$V_{REF\_MAX}$  は全温度範囲で測定した最大リファレンス出力、

$V_{REF\_MIN}$  は全温度範囲で測定した最小リファレンス出力、

$V_{REF\_NOM}$  は 2.5V の公称リファレンス電圧、

$TEMP\_RANGE$  は仕様規定された温度範囲、 $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  です。

### DC クロストーク

1 つの DAC 出力での変化に起因する別の DAC の出力レベルの DC 変化です。ミッドスケールに維持した 1 つの DAC をモニタしながら、別の DAC 上でのフルスケール出力変化（または、ソフト・パワーダウンおよびパワー・アップ）を使って測定されます。単位は  $\mu\text{V}$  です。負荷電流変化に起因する DC クロストークでは、ある DAC の負荷電流の変化がミッドスケールに維持された別の DAC へ与える影響を測定します。単位は  $\mu\text{V}/\text{mA}$  です。

## 動作原理

### D/A コンバータ

AD3530/AD3530R は低消費電力、8 チャンネル、16 ビットの電圧出力 DAC で、2.7V~5.5V のアナログ電源電圧と 1.08V~1.98V のデジタル電源電圧で動作します。AD3530/AD3530R は 5ppm/°C の 2.5V オンチップ・リファレンスを備えています。

AD3530/AD3530R には、標準 SPI との互換性を備えた汎用性の高い 4 線式シリアル・インターフェースが組み込まれています。詳細については [シリアル・インターフェース](#) のセクションを参照してください。

### DAC チャンネル

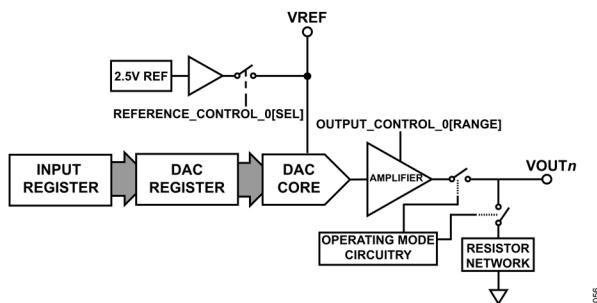

AD3530/AD3530R は、50mA の電流ソースと 40mA の電流シンクが可能な、8 つのバッファ付き電圧出力 DAC チャンネルを備えています。DAC チャンネルの簡略化したブロック図を [図 59](#) に示します。

出力アンプはその出力にレール to レール電圧を生成して、 $OUTPUT\_CONTROL\_0(RANGE) = 0$  で  $0 \sim VREF$  ( $VDD > VREF$ ) 、または  $OUTPUT\_CONTROL\_0(RANGE) = 1$  で  $0 \sim 2 \times VREF$  ( $VDD > 2 \times VREF$ ) の理想的な出力範囲を提供します。適切な出力範囲と  $VDD$  の選択時には、出力電流によって決定されるヘッドルーム電圧とフットルーム電圧も考慮する必要があります。200pF と並列にして GND に接続した  $2k\Omega$  の負荷を駆動する場合の出力スルー・レートは  $1.1V/\mu s$  で、 $\frac{1}{4}$  から  $\frac{3}{4}$  へのセッティング時間は  $5\mu s$  です。

図 59. DAC チャンネルのブロック図

### 伝達関数

デジタル入力コードから理想的な出力電圧への変換は次式により行われます。

$$V_{OUTn} = V_{REF} \times \frac{D}{2^N} \times G$$

ここで、

$V_{OUTn}$  は選択した DAC チャンネル  $n$  の出力電圧です。

$V_{REF}$  は  $VREF$  ピンの電圧で、これはデフォルトでは入力です。内部リファレンスをオンにすると、これは 2.5V に等しくなります。

$D$  は、DAC レジスタにロードされるストレート・バイナリ・コードの 10 進値です (AD3530/AD3530R では  $0 \sim 65535$ )。

$N$  はビット数で表した DAC の分解能です。

$G$  は出力アンプのゲインで、 $OUTPUT\_CONTROL\_0(RANGE) = 0$  の場合は  $G = 1$  (デフォルト) 、 $OUTPUT\_CONTROL\_0(RANGE) = 1$  の場合は  $G = 2$  です。

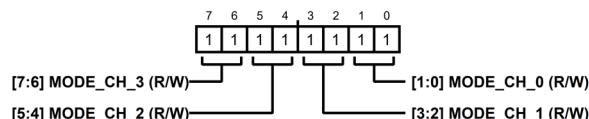

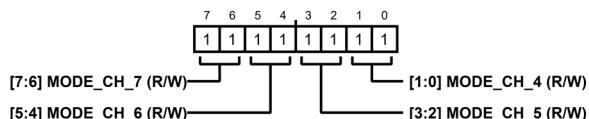

### 動作モード

表 9 に示すように、AD3530/AD3530R の各チャネルには 4 つの動作モードがあります。これらの動作モードは、[出力動作モード 0 レジスタ](#) と [出力動作モード 1 レジスタ](#) の  $MODE\_CH_n[1:0]$  を介してソフトウェアでプログラムできます。パワーアップ時またはパワーオン・リセット後は、デフォルトで動作モード 3 がセットされます。その場合は出力アンプがパワーダウンされ、 $VOUTn$  ピンから GND への実効抵抗は  $32k\Omega$  となります。

表 9. AD3530/AD3530R の動作モード

| Operating Modes | Output State          | MODE_CH_n[1] | MODE_CH_n[0] |

|-----------------|-----------------------|--------------|--------------|

| 0               | Normal operation      | 0            | 0            |

| 1               | $1k\Omega$ to GND     | 0            | 1            |

| 2               | $7.7k\Omega$ to GND   | 1            | 0            |

| 3               | $32k\Omega$ (default) | 1            | 1            |

モード 1、モード 2、またはモード 3 に入っても、他のレジスタの設定や、それらのレジスタの読み出し能力および書き込み能力に影響はありません。入力レジスタや DAC レジスタは依然として更新可能ですが、DAC 出力ピンには反映されません。

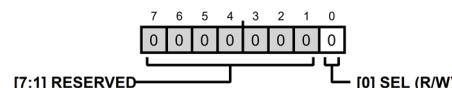

### 電圧リファレンス

AD3530R はオンチップ、バッファ付き、2.5V、5ppm/°C のリファレンスを備えており、 $VREF$  ピンに出力することができます。このピンは、最大  $+5mA$  の電流を外部負荷にソースできます。

デフォルトでは、パワーアップ時とパワーオン・リセット後は  $VREF$  ピンが入力ピンとして設定されるので、外部リファレンス電圧を使用する必要があります。内部リファレンスは、 $REFERENCE\_CONTROL\_0(SEL) = 1$  に設定することによってインエーブルできます。詳細は、[リファレンス制御 0 レジスタ](#) のセクションを参照してください。

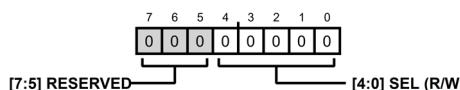

### 内蔵マルチプレクサ

AD3530/AD3530R は 27:1 のマルチプレクサを内蔵しており、選択したチャンネルの出力電圧または出力電流を表す電圧、もしくはデバイスの内部ダイ温度を表す電圧を  $MUX\_OUT$  ピンに出力できます。モニタ・ポイントは、[マルチプレクサ入力選択 0 レジスタ](#) の  $SEL$  ビットを設定することによって指定できます。無効な  $MUX\_OUT\_SELECT (SEL)$  の書き込みは無視され、 $MUX\_OUT\_SELECT (SEL)$  の値は変更されません。

電圧出力モニタを選択した場合の内蔵マルチプレクサの伝達関数は、下に示す式で与えられます。 $VREF$  の電圧出力は、 $OUTPUT\_CONTROL\_0 (RANGE)$  の値に関わらず、モニタする DAC チャンネルのフルスケール・レンジを表します。

$OUTPUT\_CONTROL\_0(RANGE) = 0$  の場合、

$$V_{MEAS} = MUX\_OUT \quad (2)$$

$OUTPUT\_CONTROL\_0(RANGE) = 1$  の場合、

$$V_{MEAS} = MUX\_OUT \times 2 \quad (3)$$

## 動作原理

ここで、

$V_{MEAS}$  は、選択したチャンネルの測定電圧出力、

$MUX\_OUT$  は  $MUX\_OUT$  ピンの電圧出力 (V) です。

電流出力モニタを使用する場合の伝達関数を下に示します。

$$I_{MEAS} = MUX\_OUT \times 40 \text{ mA/V} \quad (4)$$

ここで、

$I_{MEAS}$  は選択チャンネルの測定電流出力、 $MUX\_OUT$  は  $MUX\_OUT$  ピンの電圧出力 (V) です。

$MUX\_OUT\_SELECT$  (SEL) を  $0x19$  に設定することにより、 $MUX\_OUT$  ピンを通じて内部ダイ温度をモニタすることもできます。内部リファレンスをイネーブルして測定温度を導くために使用する伝達関数は、次式で与えられます。

$$T_{MEAS} = \frac{MUX\_OUT - 0.44}{0.0016 \text{ V/}^{\circ}\text{C}} \quad (5)$$

ここで、

$T_{MEAS}$  は測定内部ダイ温度 ( $^{\circ}\text{C}$ ) 、

$MUX\_OUT$  は  $MUX\_OUT$  ピンの電圧 (V) です

内蔵マルチプレクサは、 $\pm 5\text{mA}$  の電流を供給できるバッファ付き出力を備えています。 $VOUT_n$  のモニタリング誤差は代表値で $\pm 5\text{mV}$ 、 $IOUT_n$  のモニタリング誤差は $\pm 2\text{mA}$  です (ここで  $n$  はチャンネル番号)。

## DAC のコア機能

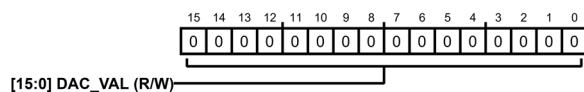

図 59 に示すように、各 DAC チャンネルには専用の **入力レジスタ** と **DAC レジスタ** があります。どちらのレジスタにも、シリアル・インターフェースを通じてアクセスできます。DAC レジスタは DAC の出力電圧に相当するデジタル・コードを保存し、入力レジスタは、DAC レジスタにデータを渡す前の一時的なステージング・レジスタとして動作します。LDAC 機能を使用すると、入力レジスタが保持するデータを使い、1 つ以上の DAC レジスタを並列で更新できます。

DAC レジスタには直接書き込みが可能ですが。この場合は対応する出力が直ちに更新され、ハードウェア LDAC やソフトウェア LDAC は必要ありません。DAC レジスタに直接書き込みを行っても、入力レジスタに保存されたデータには影響しません。

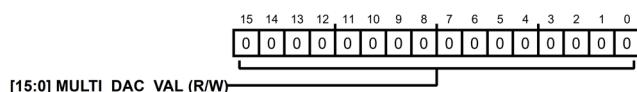

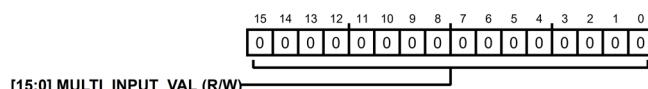

**MULTI\_INPUT\_CH** レジスタに書き込みを行うと、1 回の書き込み動作で 1 つ以上の入力レジスタを更新することができます。**MULTI\_INPUT\_SEL\_0** レジスタは、複数入力レジスタに書き込まれたデータを使って、どの入力レジスタを更新するかを決定します。詳細は **複数入力選択 0 レジスタ** のセクションを参照してください。

同様に、**MULTI\_DAC\_CH** レジスタに書き込みを行うと、1 回の書き込み動作で 1 つ以上の DAC レジスタを更新できます。**MULTI\_DAC\_INPUT\_SEL\_0** は、複数 DAC レジスタに書き込まれたデータを使って、どの DAC レジスタを更新するかを決定します。詳細は **複数 DAC 選択 0 レジスタ** のセクションを参照してください。

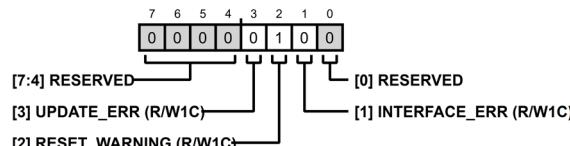

DAC が確実に更新されるようにするには、DAC レジスタの更新が  $640\text{ns}$  ごとに 1 回だけ行われるようにする必要があります。表 5 の  $t_{L2}$  と  $t_{L3}$  を参照してください。DAC の更新書き込みに失敗した場合はエラー・フラグもアサートされます。これは **ステータス制御レジスタ** の **UPDATE\_ERR** ビットを読み出すことによってチェックできます。

## LDAC 機能

LDAC 機能は、選択入力レジスタの内容を複数の対応 DAC レジスタへ転送することによって、1 つ以上の  $VOUT$  ピンを同時に更新するために使われます。LDAC 機能は、LDACB ピンを通じてハードウェアで実行するか、**SW\_LDAC\_TRIG\_A** レジスタまたは **SW\_LDAC\_TRIG\_B** レジスタを通じてソフトウェアで実行することができます。ハードウェア LDAC もソフトウェア LDAC も機能は同じです。

### ハードウェア LDAC

AD3530/AD3530R には、立下がりエッジで動作するアクティブ・ローの LDACB ピンがあります。LDACB 信号がローになると、選択された入力レジスタの内容が対応 DAC レジスタに転送されます。デバイスへの書き込み時に LDACB がローに保持されている場合、入力レジスタはトランスペアレントな存在となり、入力レジスタへの書き込みが行われると同時に、入力レジスタの内容を使って DAC レジスタが更新されます。LDACB がハイに保持されているときは、DAC の出力に影響を及ぼすことなく、任意の入力レジスタに DAC コードを書き込むことができます。図 4 を参照してください。

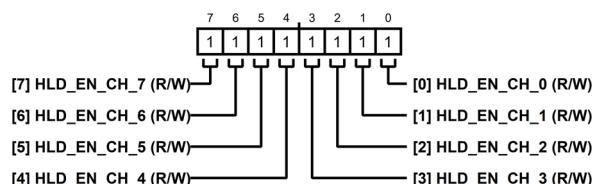

**ハードウェア LDAC イネーブル 0 レジスタ** は、LDACB がアクティブなときまたはアサートされたときに、対応する入力レジスタからどの DAC チャンネルを更新するかを決定するために使われます。デフォルトではすべての DAC チャンネルが選択されて、**HLD\_EN\_CH\_n** ビットフィールドに 1 が格納されます。**HLD\_EN\_CH\_n** ビットフィールドを 0 に設定すると、ターゲット DAC チャンネルのハードウェア LDAC 機能がディスエーブルされます。

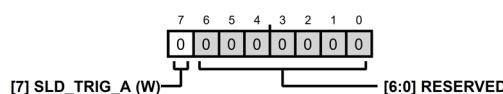

### ソフトウェア LDAC

ソフトウェア LDAC 機能は LDACB の立下がりエッジと同じ働きをします。これは、**ソフトウェア LDAC トリガ 0 レジスタ** の **SLD\_TRIG\_A** ビット、または **ソフトウェア LDAC トリガ 0 レジスタ** の **SLD\_TRIG\_B** ビットに 1 を書き込むことによって、選択された入力レジスタと DAC レジスタの間でシリアル・インターフェースによる内容の転送を開始する方法を提供します。

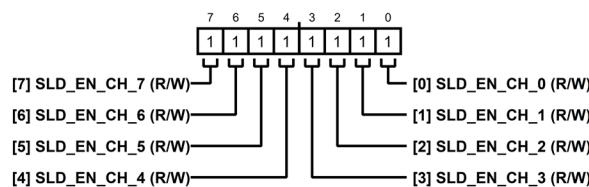

**ソフトウェア LDAC イネーブル 0 レジスタ** は、ソフトウェア LDAC の実行時に、対応する入力レジスタからどの DAC チャンネルを更新するかを決定するために使われます。デフォルトではすべての DAC チャンネルが選択されて、**SLD\_EN\_CH\_n** ビットフィールドに 1 が格納されます。**SLD\_EN\_CH\_n** ビットフィールドを 0 に設定すると、ターゲット DAC チャンネルのソフトウェア LDAC 機能がディスエーブルされます。

### パワーオン・リセット

パワーアップ時は、すべての DAC チャンネルの入力データ・レジスタと DAC データ・レジスタにゼロ・コードがロードされます。その一方で、POR 回路が、そのチャンネルの出力動作モードが変わるまで DAC 出力アンプをパワーダウンします (**動作モード** のセクションのモード 3 を参照)。すべてのレジスタはデフォルト値にリセットされます。

## 動作原理

### ハードウェア・リセット

RESETB は、立下がりエッジで動作するアクティブ・ローの信号です。RESETB をアサートするとデバイスは POR 状態になります。RESETB がアサートされると、すべての SPI トランザクションと LDACB パルスが無視されて、SDO 出力は高インピーダンス状態になります。

RESETB がデアサートされると、デジタル・コアが初期化されて、すべての DAC レジスタがデフォルト値にリセットされます。デジタル・コアの初期化手順は、何らかの SPI トランザクションを開始する約 150ns 前に終わらせる必要があります。

### ソフトウェア・リセット

INTERFACE\_CONFIG\_A レジスタの SW\_RESET ビットと RESET\_SW ビットをセットすることにより、シリアル・インターフェースを使ってデバイスをリセットできます。ソフトウェア・リセットを正常にトリガするには、両方のビットフィールドを同じデータ・フェーズで書き込む必要があります。ソフトウェア・リセット・トランザクション後は、POR シーケンスとデジタル・コアの初期化が実行されて、INTERFACE\_CONFIG\_A レジスタを除くすべての DAC レジスタがデフォルト値にリセットされます。その後の SPI トランザクションは、ソフト・リセット・トランザクションにおける最後の SCLK の後、約 150ns が経過するまで開始できません。詳細については [タイミング特性](#) のセクションを参照してください。

### シリアル・インターフェース

AD3530/AD3530R は、標準 SPI、QSPI、MICROWIRE の各インターフェース規格、およびほとんどのデジタル・シグナル・プロセッサ (DSP) に対応できる、4 線式シリアル・インターフェース (CSB、SCLK、SDI、および SDO) を使用しています。図 2 に代表的な書き込みシーケンスのタイミング図を示します。データのサンプリングは、クロックの立上がりエッジで AD3530/AD3530R が行います。これは SPI モード 0、またはモード 3 に対応します。

デフォルトでは、[インターフェース設定 B レジスタ](#) の SHORT\_INSTRUCTION ビットを設定することによって 15 ビット・アドレス指定がイネーブルされますが、0x80 未満のメモリ位置では 7 ビット・アドレス指定を選択できます。

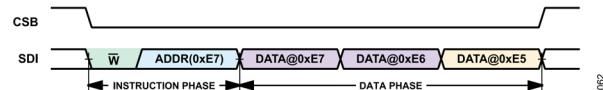

図 60. 標準 SPI の書き込み

図 61. 標準 SPI の読み出し

### SPI フレーム同期

SPI トランザクション時は CSB ピンがデータをフレーム化します。CSB の立下がりエッジによってデジタル・インターフェースがイネーブルされ、SPI トランザクションが開始されます。それぞれの SPI トランザクションは、少なくとも 1 つずつの命令

フェーズとデータ・フェーズによって構成されます。いずれの SPI トランザクションでも、データは MSB ファーストに揃えられます。SPI トランザクション時に CSB をデアサートすると、データ転送の一部または全部が終了し、デジタル・インターフェースがディスエーブルされます。1 つ以上のレジスタへの書き込み後に CSB がデアサートされると (ハイ・レベルに戻ると)、完了したレジスタへの書き込みまたは読み出しが行われますが、一部しか書き込まれなかつたレジスタの書き込みや読み出しが中止されます。図 60 と図 61 に、SPI インターフェースを介したレジスタの読み出しと書き込みの詳細なタイミング図を示します。

### 命令フェーズ

各 SPI フレームは命令フェーズで始まります。命令フェーズは、SPI トランザクションを開始する CSB の立下がりエッジの直後に始まります。命令フェーズは、読み出し/書き込みビット (R/W) と、それに続くレジスタ・アドレス・ワードで構成されます。R/W をローにセットすると書き込み命令が始まり、R/W をハイにセットすると読み込み命令が始まります。レジスタ・アドレス・ワードはアクセス先のレジスタ・アドレスを指定します。レジスタ・アドレスのデフォルトのワード長は 15 ビットです。必要な場合は、INTERFACE\_CONFIG\_B レジスタの SHORT\_INSTRUCTION ビットで 7 ビット・アドレス指定をイネーブルします。詳細は [インターフェース設定 B レジスタ](#) のセクションを参照してください。

### データ・フェーズ

図 62 および図 63 に示すように、データ・フェーズは命令フェーズの直後に置かれます。データ・フェーズには、1 個のシングルバイト・レジスタ、1 個のマルチバイト・レジスタ、または複数個のレジスタのデータを含めることができます。

SPI 書込みトランザクションのデータ・フェーズに更新対象レジスタのデータ・バイトの一部しか含まれない場合、レジスタの内容は更新されず、INTERFACE\_STATUS\_A (CLOCK\_COUNT\_ERR) がセットされます。

### マルチバイト・レジスタ

AD3530/AD3530R は、1 バイト・レジスタに加えて、隣接するアドレスに 2 バイトのデータを保存するレジスタも備えています。このレジスタはマルチバイト・レジスタと呼ばれます。マルチバイト・レジスタへの書き込み時は、1 回の SPI トランザクションですべてのバイトにアクセスする必要があります。このため、INTERFACE\_CONFIG\_C (STRICT\_REGISTER\_ACCESS) は読み出し専用で、1 に設定されます。マルチバイト・レジスタへの書き込みトランザクションは、データ・フェーズの 16 番目の SCLK エッジの後に実行されます。

マルチバイト・レジスタのアドレスは、常に INTERFACE\_CONFIG\_A (ADDR\_ASCENSTION) によって決まります。降順アドレス指定の場合、データ・フェーズで最初にアクセスするバイトはマルチバイト・レジスタの最上位バイトでなければならず、後続のバイトは次の下位アドレスのデータに対応します。昇順アドレス指定の場合、データ・フェーズで最初にアクセスするバイトはマルチバイト・レジスタの最下位バイトでなければならず、後続のバイトは次の上位アドレスのデータに対応します。

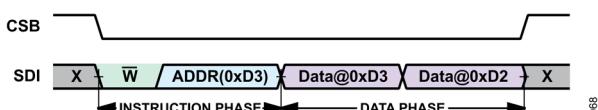

## 動作原理

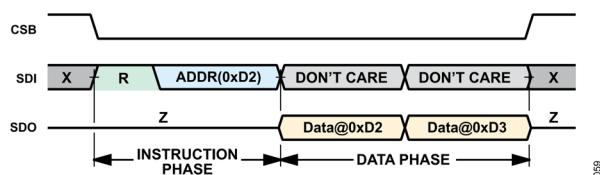

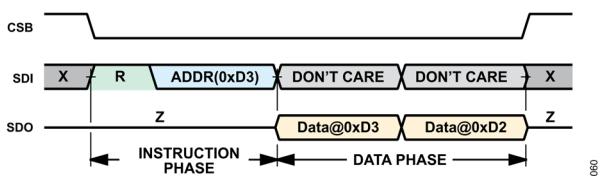

例えば、DAC\_CH0 レジスタは 2 バイト長で、その最下位バイトのアドレスは 0xD2、最上位バイトのアドレスは 0xD3 です。このレジスタの読み出しトランザクションを、図 62 (昇順アドレス指定) と図 63 (降順アドレス指定) に示します。

アドレス方向は、INTERFACE\_CONFIG\_A (ADDR\_ASCENSION) で選択します。このビットを 0 に設定すると、バイトにアクセスするごとにアドレスがデクリメントします。このビットを 1 に設定すると、バイトにアクセスするごとにアドレスがインクリメントします。マルチバイト・レジスタへの SPI 書込みトランザクションをバイトごとに行おうとした場合、デバイスのレジスタの内容は更新されず、INTERFACE\_STATUS\_A (REGISTER\_PARTIAL\_ACCESS\_ERR) がセットされます。

このデバイスは以下のマルチバイト・レジスタを内蔵しています： DAC\_CHn、Input\_CHn、MULTI\_DAC\_CH、および MULTI\_INPUT\_CH。

図 62. 昇順アドレス指定によるマルチバイト読み出し

図 63. 降順アドレス指定によるマルチバイト読み出し

## 单一命令モード

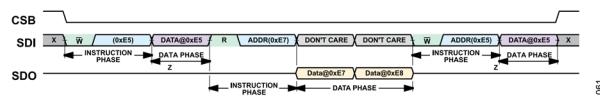

INTERFACE\_CONFIG\_B (SINGLE\_INST) を 1 に設定すると、ストリーミング・モードがディスエーブルされて单一命令モードがイネーブルされます。单一命令モードでは、データ・フェーズは単一レジスタのデータで構成され、CSB がローのままであっても、各データ・フェーズの後には新しい命令フェーズを続ける必要があります。单一命令モードでは、デジタル・ホストは 1 つの SPI フレーム内の隣接しないアドレスのレジスタに対して迅速に読み出しと書き込みを行えます (図 64 を参照)。これに対し、ストリーミング・モードでは、新たな命令フェーズを開始するために CSB パルスをハイにすることなく、隣接レジスタに対する読み出しまたは書き込みを行うことができます。

図 64. 単一命令モード

单一命令モードでマルチバイト・レジスタにアクセスするときは、データ・フェーズに 2 バイトすべて、または 16SCLK サイクルが含まれている必要があります。レジスタ・アドレスの順番は、INTERFACE\_CONFIG\_A (ADDR\_ASCENSION) によって決まります。

## ストリーミング・モード

INTERFACE\_CONFIG\_B (SINGLE\_INST) ビットを 0 に設定すると、单一命令モードがディスエーブルされてストリーミング・モードがイネーブルされます。ストリーミング・モードでは、アドレスが隣接する複数のレジスタに 1 つの命令フェーズとデータ・フェーズでアクセスできるため、メモリの隣接領域に効率的にアクセスできます (例えば、デバイスの初期設定時)。ストリーミング・モードはデフォルトで選択されています。

ストリーミング・モードの場合、各 SPI フレームは 1 つの命令フェーズで構成され、後続のデータ・フェーズにはアドレスが隣接する複数のレジスタのデータが含まれます。開始レジスタのアドレスは命令フェーズにおいてデジタル・ホストが指定し、データの各バイトへのアクセスが行われた後、このアドレスは、自動的にインクリメントまたはデクリメント (アドレス方向の設定による) します。そのため、データ・フェーズは複数バイト長となることがあります。読み出しまたは書き込みデータの連続するバイトはそれぞれ、次の最上位アドレス (昇順アドレス方向の場合) または最下位アドレス (降順アドレス方向の場合) に対応します。

ストリーミング・モードで昇順アドレスによりマルチバイト・レジスタへ書き込みを行う場合は、命令フェーズでレジスタの LSB アドレスを指定し、データ・フェーズで LSB から順にデータを提供する必要があります。ストリーミング・モードで降順アドレスによりマルチバイト・レジスタに書き込みを行う場合は、命令フェーズでレジスタの最上位バイトからアドレス指定を開始し、データ・フェーズで最上位バイトから順にデータを提供する必要があります。

ストリーミング・モードで降順アドレスによりマルチバイト・レジスタから読み出しを行うときは、MSB から順にデータをリード・バックします。ストリーミング・モードで昇順アドレスによりマルチバイト・レジスタから読み出しを行うときは、 LSB から順にデータをリード・バックします。

図 65. ストリーミング・モードの SPI 転送

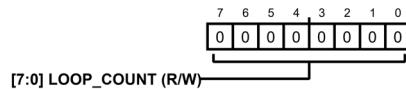

STREAM\_MODE レジスタを用いることで、連続するレジスタのセットを指定してデータ・フェーズでループ・スルーを行うことができます。ルーピングにより、デジタル・ホストは一連のレジスタとの間で可能な限り効率的に読み出しまたは書き込みを繰り返すことができます。

アドレス方向が降順に設定されている場合、アドレスは 0x00 に達するまでデクリメントします。その後のバイト・アクセスでは、アドレスは使用可能な最大のバイト・アドレス値 (0xF9) に設定されます。

アドレス方向が昇順に設定されている場合、アドレスは使用可能な最大のバイト・アドレス値 (0xF9) に達するまでインクリメントします。その後のバイト・アクセスでは、アドレスは 0x00 にリセットされます。

STREAM\_MODE が 0 以外の値に設定されている場合はルーピングがイネーブルされ、バイト・アドレスが命令フェーズでの指定アドレスにリセットされる前に单一データ・フェーズでのアクセス対象となるバイト数は、STREAM\_MODE の値によって設定されます。

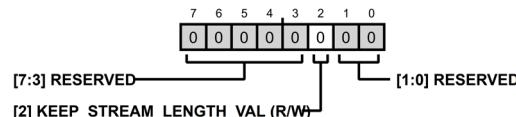

## 動作原理

STREAM\_MODE (LOOP\_COUNT) レジスタの値は、維持するか、フレーム・トランザクションの完了時（つまり CSB がハイになったとき）にデフォルト値 0 に戻すことができます。STREAM\_MODE レジスタの動作は TRANSFER\_CONFIG (KEEP\_STREAM\_LENGTH\_VAL) によって制御されます。

図 66. LOOP\_COUNT = 2 でループングをイネーブル

STREAM\_MODE 使用時は、[DAC のコア機能](#)のセクションに述べた DAC の更新タイミングに留意してください。

## CRC エラーの検出

AD3530/AD3530R DAC は、デジタル・ホストと DAC (ターゲット) 間における SPI トランザクションのエラーを検出するための光学的巡回冗長検査 (CRC) 機能を備えています。CRC エラー検出はデフォルトではディスエーブルされています。CRC エラー検出を用いることで、SPI のホストとターゲットは、ビット転送エラーを高い信頼度で検出できます。CRC アルゴリズムでは、シード値と多項式除算を使用して CRC コードを生成します。コントローラとターゲットの双方で個別に CRC コードを計算し、転送されたデータの有効性を判定します。

この DAC は、次の多項式からなる CRC-8 標準を使用します。

$$x^8 + x^2 + x + 1 \quad (6)$$

CRC エラー検出をイネーブルするには、INTERFACE\_CONFIG\_C レジスタの CRC\_EN ビットと CRC\_EN\_B ビットを用います。CRC\_EN の値が更新されるのは、同じレジスタ書込み命令で CRC\_EN\_B が CRC\_EN の反転値に設定されている場合のみです。そのため、CRC をイネーブルするには、CRC\_EN を 0b01 に設定すると共に、同じ書込みトランザクションで CRC\_EN\_B を 0b10 に設定する必要があります。

CRC をディスエーブルするには、CRC\_EN を 0b00 に設定すると共に、同じ書込みトランザクションで CRC\_EN\_B を 0b11 に設定します。

2 つの別々のフィールドに反転した値を書き込むことで、CRC が誤ってイネーブルされる可能性を低減できます。CSB は書き込みのイネーブル/ディスエーブル後にハイ・レベルにする必要があります。最初の CRC コードは、レジスタの書き込み/読み出しどの後、CRC をイネーブルするレジスタ書込みトランザクションの直後に含める必要があります。CRC をディスエーブルするレジスタ書込みトランザクションでは、SDI に関する CRC コードも含まれていなければなりませんが、その後に続くトランザクションに CRC コードを含める必要はありません。

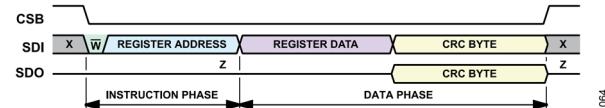

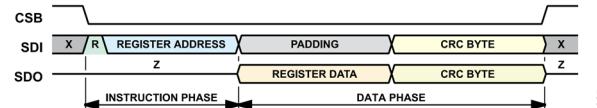

図 67 と図 68 は、デジタル・ホストまたは DAC がデータを検証するために、それぞれ書き込み時または読み出し時に CRC コードがどのように付加されるのかを示しています。レジスタ書込みの場合、式 6 に示す計算を使ってデジタル・ホストが CRC を生成する必要があります。レジスタ読み出しの場合、ホストは DAC によってチェックされる正しい CRC バイトを送信する必要があります。送信データの最初のバイトは CRC 計算に使われます。したがって、値を 0x00 とすることを推奨します。同じ読み出しトランザクションで、DAC はデジタル・ホストが検証するための CRC コードを供給します。

CRC エラー検出をイネーブルしてマルチバイト・レジスタにアクセスする場合、CRC コードはレジスタ・データの全バイトの後に配置されます。CRC エラー検出がイネーブルされている場合、DAC は、SDI のレジスタ・データの最後で有効な CRC コードを受け取るまで、レジスタ書込みトランザクションに応答してレジスタ内容を更新することはありません。CRC コードが無効であったり、デジタル・ホストが CRC コードを送信できなかったりした場合、AD3530/AD3530R はレジスタの内容を更新せず、INTERFACE\_STATUS\_A レジスタの CRC\_ERR フラグをセットします。CRC\_ERR フラグは 1 が書き込まれるとクリアされます (W1C)。また、書き込みによるクリアを有効にするには正しい CRC が必要です。

CRC コードの計算で使用するシード値とその送信方法を、单一命令モードおよびストリーミング・モードの両方について表 14 に示します。单一命令モードを使用する場合、SPI フレーム内のどの CRC コードもシード値として 0xA5 を用い、アドレス 0x0000 で縮退故障状態が発生するのを防止します。

ストリーミング・モードを使用する場合、SPI フレームの最初の CRC コードもシード値として 0xA5 を用いますが、同じフレーム内の後続の CRC コードの計算には、SPI トランザクションでアクセスするレジスタ・アドレスの LSB をシード値として用います。

図 67. CRC をイネーブルした SPI 書込み

図 68. CRC をイネーブルした SPI 読出し

## アプリケーション情報

### 電源の推奨事項

AD3530/AD3530R に電源シーケンスに関する制限はありません。出力は、正しいレジスタ設定が完了するまで、既知のプルダウン抵抗によって POR 状態に維持されます。

AD3530/AD3530R 使用時は、各電源に  $10\mu\text{F}$  と  $0.1\mu\text{F}$  のコンデンサを並列に接続することによって、十分な電源バイパスを確保する必要があります。これらのコンデンサは、パッケージのできるだけ近くに配置してください（デバイスに直接取り付けるのが理想）。これに対し、VREF ピンに使用する最大容量性負荷は、表 2 に示すように  $0.5\text{nF}$  です。 $10\mu\text{F}$  のコンデンサはタンタルのビーズ型を使います。 $0.1\mu\text{F}$  と  $0.5\text{nF}$  のコンデンサには、等価直列抵抗 (ESR) と等価直列インダクタンス (ESL) が小さいものを使用する必要があります。一般的なセラミック・コンデンサは、高い周波数ではグラウンドへの低インピーダンス経路を提供することで、内部ロジックの切り替えによる過渡電流に対応します。

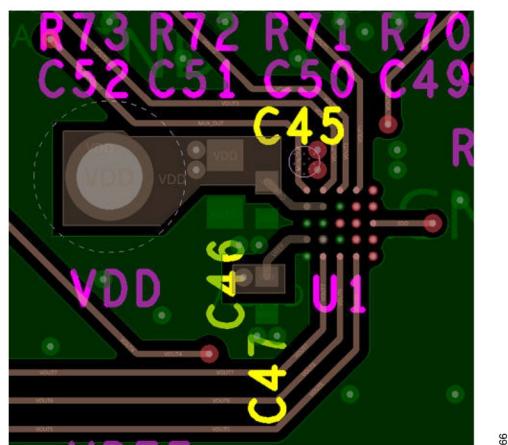

### レイアウトのガイドライン

AD3530/AD3530R のピンは、最適なレイアウトを実現しやすいように配置されています。レイアウトの一例を図 69 に示します。ほとんどの高速デジタル・ラインは、チップの 1 つの辺に配置され、各 DAC のアナログ機能部は他の 3 つの辺に対称に配置されています。このレイアウトは、デジタル・ラインをアナログ機能部から直線的に配置できるようになっています。

図 69. 評価用ボードのレイアウト

AD3530/AD3530R から最大限の性能を引き出すための、PCB 設計に関するいくつかの推奨事項を以下に示します。

- 電源ラインのパターンをできるだけ大きくして低インピーダンス経路を確保し、電源ラインのグリッチによる影響を減らすようにします。

- 低インピーダンスのアナログ・グランド・プレーンとスター型接地方式の使用を推奨します。接地抵抗を最小限に抑えるために、グラウンド層には切れ目を作らないようにしてください。

- クロックなどの高速スイッチング・デジタル信号をボード上の他の部分からシールドするには、デジタル・グラウンドを使用します。

- 可能であれば、デジタル信号とアナログ信号を交差させないでください。パターンがボードの反対面で公差する場合は、アナログ配線とデジタル配線の角度を  $45^\circ$  または  $90^\circ$  として、ボードのフィードスルーが小さくなるようにします。

- デバイス周辺のクロック・レートが最大  $50\text{MHz}$  程度の場合は、ソース I/O ピンの近くに直列抵抗を追加することを推奨します。一般的には  $22\Omega$ ~ $100\Omega$  の値が使われます。この値は、高速の信号遷移によって生じるリンギングと反射を減らすことによって、信号の完全性を向上させる助けとなります。

### ヘッドルームとフットルーム

ヘッドルームとフットルームとは、指定された出力負荷電流に対する DAC の電源電圧と意図する出力電圧の差のことを言います。電源電圧のヘッドルームまたはフットルームが不十分な場合、DAC の内蔵出力アンプの通過素子は、理想スイッチではなく抵抗のような動作を示します。このため、負荷電流が増加すると出力電圧が低下するという結果を招きます。

AD3530/AD3530R の必要ヘッドルームは代表値で  $25\text{mV}/20\text{mA}$ 、フットルームは  $50\text{mV}/20\text{mA}$  という非常に低い値となっています。代表的な特性を図 20 に示します。電圧降下特性は一般に直線的なので、負荷電流にヘッドルーム/フットルーム仕様を乗じることによって計算できます。例えば、電源が  $5\text{V}$  で DAC 出力の設定も  $5\text{V}$  だとします。DAC が負荷に対して  $30\text{mA}$  の電流ソースを開始したとすると、DAC の出力電圧は約  $4.963\text{V}$  です。

フットルームの例を考えると、DAC 出力が  $30\text{mA}$  の電流をシンクしている場合、出力電圧はグラウンド電位基準で  $75\text{mV}$  となります。

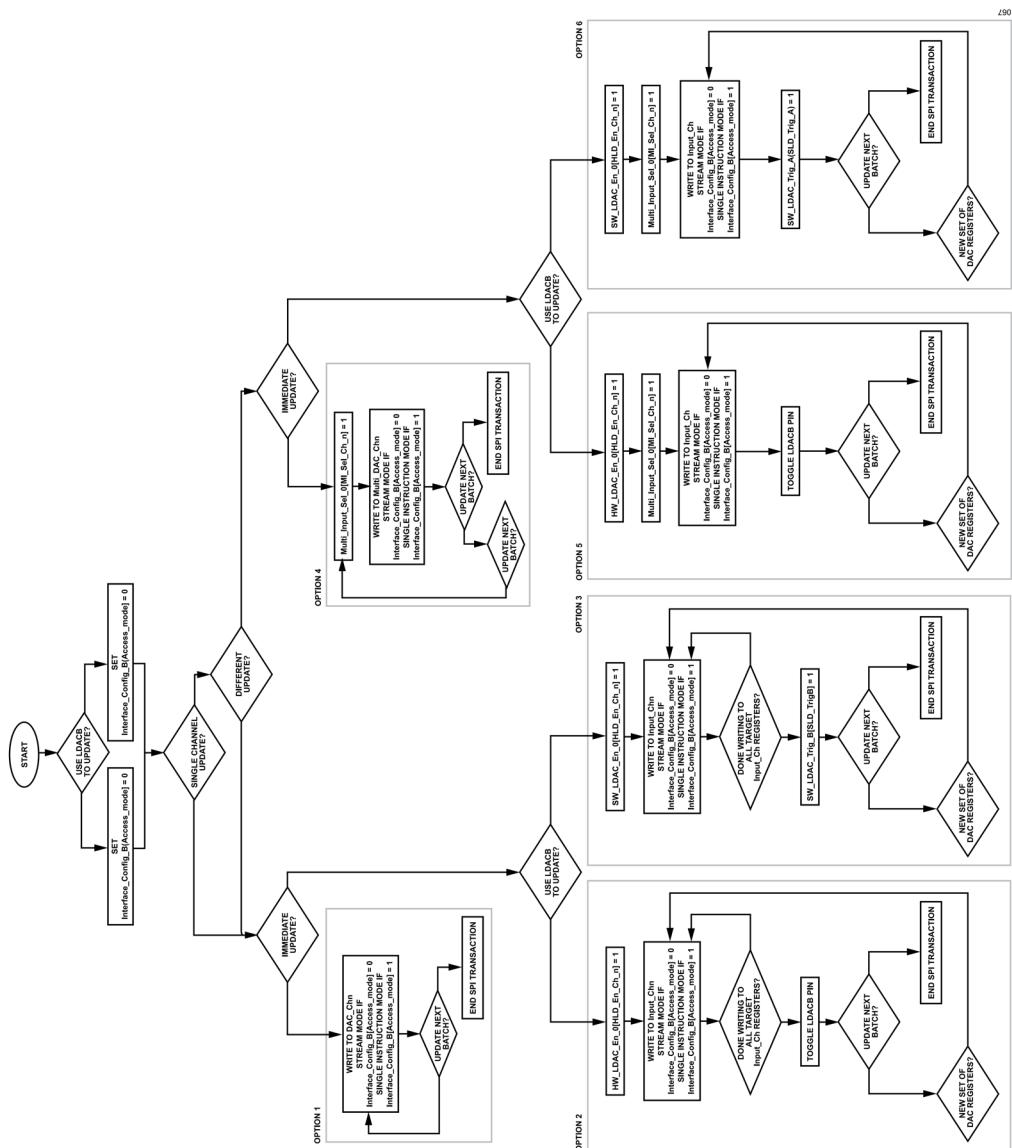

### DAC の更新

DAC\_CHn レジスタ（つまり VOUTn）を更新する方法は複数あります。図 70 は、単一チャンネルの更新と複数チャンネルの更新、類似データと固有データ、LDAC のモードなど、いくつかの要素を考慮しながら DAC\_CHn レジスタを更新するためのオプションを示すフロー・ローチャートです。

## アプリケーション情報

図 70. DAC 更新フローチャート

オプション 1 (直接更新、固有データ、LDAC なし、

单一および複数チャンネル)

オプション 1 では、16 ビットのデータをすべて書き込んだ後で、DAC\_CHn レジスタを直接更新できます。LDAC は必要ありません。

オプション 1 は、单一命令モードまたはストリーム・モードで、单一チャンネル更新と複数チャンネル更新の両方に使用できます。

図 71. オプション 1 の例：

DAC\_CH0 レジスタへの書き込み - 単一命令モード、降順アドレス

单一命令は降順アドレス指定モードを選択して送信されます。命令フェーズで複数バイト・レジスタの上位アドレスが呼び出され (0xD4、DAC\_CH0 レジスタ、2 個の 8 ビット・データが後続)、最後の SCLK の後で直ちに出力が更新されます。

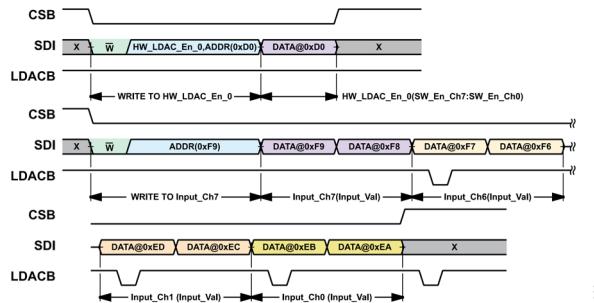

## オプション 2 (間接更新、固有データ、ハードウェア LDAC、单一および複数チャンネル)

オプション 2 では、ハードウェア LDAC を通じて DAC\_CHn レジスタの更新タイミングを INPUT\_CHn レジスタから制御できます。

单一命令モードまたはストリーム・モードで、单一チャンネル更新と複数チャンネル更新の両方に使用できます。

## アプリケーション情報

図 72. オプション 2 の例：Input\_Ch7～Input\_Ch0 レジスタへの書込み - ハードウェア LDAC をイネーブル、ストリーム・モード、降順アドレス

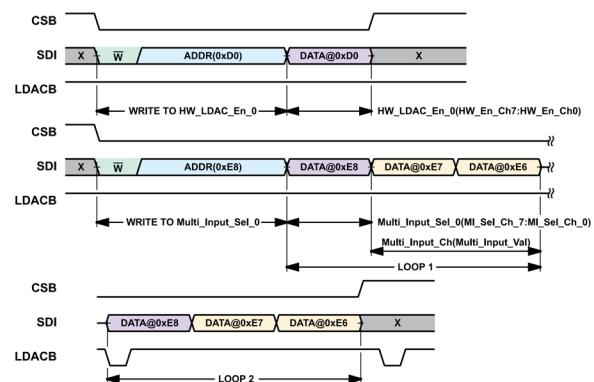

HW\_LDAC\_EN\_0 レジスタへの書込みのために単一命令が送信され、選択されたチャンネルのハードウェア LDAC をイネーブルします。次いでデフォルトの降順アドレス指定でストリーム・モードが開始され、INPUT\_CH7 から INPUT\_CH0 への順番で書込みが行われます。DAC レジスタと DAC 出力を更新するストリームが終了すると、LDACB がアサートされます（正しい LDACB タイミングが守られた場合）。

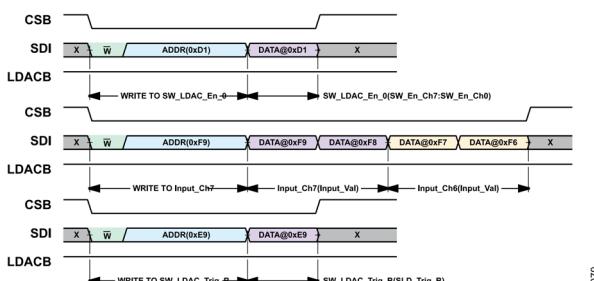

### オプション 3 (間接更新、固有データ、ソフトウェア LDAC、単一および複数チャンネル)

オプション 3 では、ソフトウェア LDAC を通じて、DAC\_CHn レジスタの更新タイミングを INPUT\_CHn レジスタから制御できます。

このオプションは、単一命令モードおよびストリーム・モードで、单一チャンネル更新と複数チャンネル更新の両方に使用できます。

図 73. オプション 3 の例：INPUT\_CH7 および INPUT\_CH6 レジスタへの書込み - ソフトウェア LDAC、ストリーム・モード、降順アドレス

ハードウェア LDAC ではなくソフトウェア LDAC 機能を使用する点を除いて、オプション 2 と同じです。SW\_LDAC\_EN\_0 レジスタは、ソフトウェア LDAC コマンドをどのチャンネルに適用するかを決定します。DAC レジスタと DAC 出力は、SW LDAC コマンドの最終 SCLK 後に書き込まれた入力データによって更新されます。

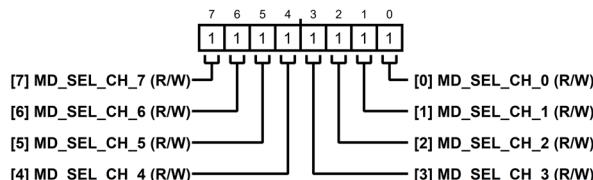

### オプション 4 (直接更新、同一データ、LDAC なし、複数チャンネル)

オプション 4 では、同じデータを持つ MULTI\_DAC\_SEL\_0 (MD\_SEL\_CH\_n) ビットフィールドによって確認された複数の DAC\_CHn レジスタを、直接同時に更新できます。データは MULTI\_DAC\_CH レジスタに格納され、16 ビットのデータをすべて書き込んだ後に更新が開始されます。LDAC は必要ありません。

オプション 4 は、単一命令モードおよびストリーム・モードでの複数チャンネル更新に最適です。

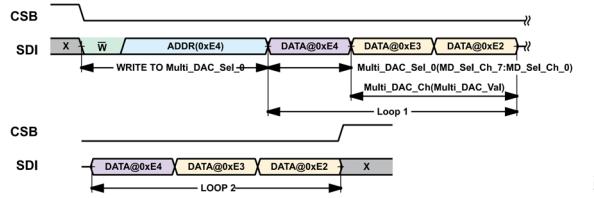

図 74. オプション 4 の例：MULTI\_DAC\_CHn レジスタへの書き込み - ストリーム・モード (ループ)、降順アドレス

MULTI\_DAC\_SEL\_0 レジスタに書込み命令が送信されて、選択されたチャンネルの複数 DAC 機能をイネーブルします。ストリーム・モードで降順アドレスがイネーブルされている場合、コマンドの次には、隣接するマルチバイト・レジスタ 0xE3 (および 0xE2) MULTI\_DAC\_CH のデータが続きます。STREAM\_MODE (LOOP\_COUNT) が 0x3 に設定されているとすると、これに続くデータ・ストリームは開始アドレス 0xE4 にループ・バックして、CSB がデアサートされるまで同じプロセスを繰り返します。

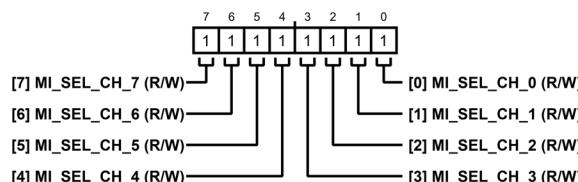

### オプション 5 (間接更新、同一データ、ハードウェア LDAC、複数チャンネル)

オプション 5 では、同じデータを持つ MULTI\_INPUT\_SEL\_0 (MI\_SEL\_CH\_n) ビットフィールドと HW\_LDAC\_EN\_0 (HLD\_EN\_CH\_n) ビットフィールドによって確認された、複数の DAC\_CHn レジスタの更新タイミングを制御することができます。データは MULTI\_INPUT\_CH レジスタに格納され、有効な LDACB パルスを供給することによって更新が開始されます。

オプション 5 は、単一命令モードおよびストリーム・モードでの複数チャンネル更新に最適です。

図 75. オプション 5 の例：MULTI\_INPUT\_CH レジスタへの書き込み - ハードウェア LDAC、ストリーム・モード (ループ)、昇順アドレス

オプション 5 は、MULTI\_INPUT\_SEL\_0 レジスタと MULTI\_INPUT\_CH レジスタを使用して複数の DAC チャンネルの入力レジスタの選択と更新を行いますが、この点を除けばオプション 2 と同じです。DAC レジスタと DAC 出力を更新する各ループが終了すると、LDACB がアサートされます（正しい LDAC が守られた場合）。

## アプリケーション情報

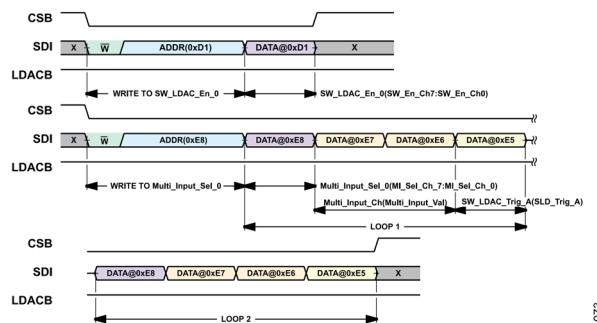

### オプション 6 (間接更新、同一データ、ソフトウェア LDAC、複数チャンネル)

オプション 6 では、同じデータを持つ MULTI\_INPUT\_SEL\_0 (MI\_SEL\_CH\_n) ビットフィールドと SW\_LDAC\_EN\_0 (SLD\_EN\_CH\_n) ビットフィールドによって確認された複数の DAC\_CHn レジスタを、直接同時に更新できます。データは MULTI\_INPUT\_CH レジスタに格納され、ソフトウェア LDAC によって更新が開始されます。

オプション 6 は、单一命令モードおよびストリーム・モードでの複数チャンネル更新に最適です。

073

図 76. オプション 6 の例 : MULTI\_INPUT\_CH レジスタへの書き込み -

ソフトウェア LDAC、ストリーム・モード (ループ) 、

昇順アドレス

オプション 6 は、ハードウェア LDAC 機能ではなくソフトウェア LDAC 機能を使用する点を除いてオプション 5 と同じです。SW\_LDAC\_EN\_0 レジスタは、ソフトウェア LDAC コマンドをどのチャンネルに適用するかを決定します。

## レジスタの一覧

表 10. AD3530/AD3530R のレジスター一覧

| Reg               | Name                         | Bits   | Bit 7              | Bit 6                  | Bit 5             | Bit 4            | Bit 3                  | Bit 2                      | Bit 1           | Bit 0        | Reset | RW  |

|-------------------|------------------------------|--------|--------------------|------------------------|-------------------|------------------|------------------------|----------------------------|-----------------|--------------|-------|-----|

| 0x00              | INTERFACE_CONFIG_A           | [7:0]  | SW_RESET           | RESERVED               | ADDR_ASCENSION    | SDO_ENABLE       |                        | RESERVED                   | RESET_SW        | 0x10         |       | R/W |

| 0x01              | INTERFACE_CONFIG_B           | [7:0]  | SINGLE_INSTRUCTION |                        | RESERVED          |                  | SHORT_INSTRUCTION      |                            | RESERVED        | 0x00         |       | R/W |

| 0x02              | DEVICE_CONFIG                | [7:0]  |                    | RESERVED               |                   |                  |                        |                            | OPERATING_MODES | 0x00         |       | R/W |

| 0x03              | CHIP_TYPE                    | [7:0]  |                    | RESERVED               |                   |                  |                        |                            | CHIP_TYPE       | 0x08         | R     |     |

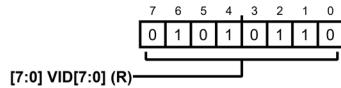

| 0x04              | PRODUCT_ID_L                 | [7:0]  |                    |                        | PRODUCT_ID[7:0]   |                  |                        |                            |                 | 0x01         | R     |     |

| 0x05              | PRODUCT_ID_H                 | [7:0]  |                    |                        |                   | PRODUCT_ID[15:8] |                        |                            |                 | 0x00         | R     |     |

| 0x06              | CHIP_GRADE                   | [7:0]  |                    | GRADE                  |                   |                  |                        | DEVICE_REVISION            |                 | 0x01         | R     |     |

| 0x0A              | SCRATCH_PAD                  | [7:0]  |                    |                        | SCRATCH_PAD       |                  |                        |                            |                 | 0x00         | R/W   |     |

| 0x0B              | SPI_REVISION                 | [7:0]  | SPI_TYPE           |                        |                   | VERSION          |                        |                            |                 | 0x84         | R     |     |

| 0x0C              | VENDOR_L                     | [7:0]  |                    |                        | VID[7:0]          |                  |                        |                            |                 | 0x56         | R     |     |

| 0x0D              | VENDOR_H                     | [7:0]  |                    |                        | VID[15:8]         |                  |                        |                            |                 | 0x04         | R     |     |

| 0x0E              | STREAM_MODE                  | [7:0]  |                    |                        | LOOP_COUNT        |                  |                        |                            |                 | 0x00         | R/W   |     |

| 0x0F              | TRANSFER_CONFIG              | [7:0]  |                    | RESERVED               |                   |                  | KEEP_STREAM_LENGTH_VAL |                            | RESERVED        | 0x00         | R/W   |     |

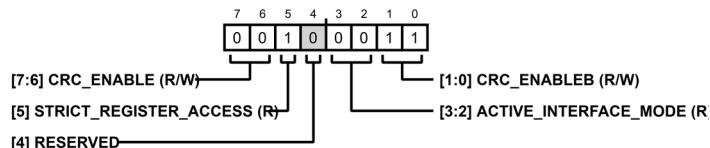

| 0x10              | INTERFACE_CONFIG_C           | [7:0]  | CRC_ENABLE         | STRICT_REGISTER_ACCESS |                   | RESERVED         | ACTIVE_INTERFACE_MODE  |                            | CRC_ENABLEB     | 0x23         | R/W   |     |

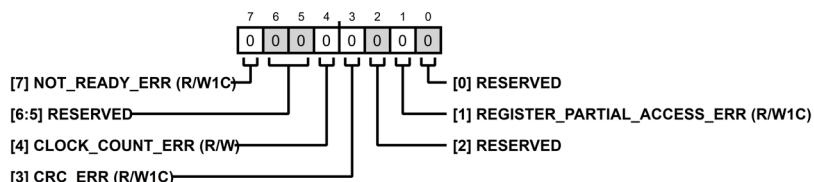

| 0x11              | INTERFACE_STATUS_A           | [7:0]  | NOT_READ_ERR       | RESERVED               | CLOCK_COUNTER_ERR | CRC_ERR          | RESERVED               | REGISTER_PARTIAL_ACCESS_ER | RESERVED        | 0x00         | R/W   |     |

| 0x20              | OUTPUT_OPERATING_MODE_0      | [7:0]  | MODE_CH_3          | MODE_CH_2              |                   | MODE_CH_1        |                        | MODE_CH_0                  |                 | 0xFF         | R/W   |     |

| 0x21              | OUTPUT_OPERATING_MODE_1      | [7:0]  | MODE_CH_7          | MODE_CH_6              |                   | MODE_CH_5        |                        | MODE_CH_4                  |                 | 0xFF         | R/W   |     |

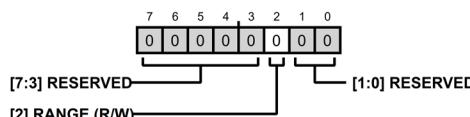

| 0x2A              | OUTPUT_CONTROL_ROL_0         | [7:0]  |                    | RESERVED               |                   |                  | RANGE                  |                            | RESERVED        | 0x00         | R/W   |     |

| 0x3C              | REFERENCE_CONTROL_0          | [7:0]  |                    | RESERVED               |                   | RESERVED         |                        | SEL                        |                 | 0x00         | R/W   |     |

| 0x93              | MUX_OUT_SELECT_0             | [7:0]  | RESERVED           |                        |                   | SEL              |                        |                            |                 | 0x00         | R/W   |     |

| 0xC2              | STATUS_CONTROL               | [7:0]  | RESERVED           |                        | UPDATE_ERROR      | RESET_WAITING    | INTERFACE_ERR          | RESERVED                   |                 | 0x04         | R/W   |     |

| 0xD0              | HW_LDAC_EN_0                 | [7:0]  | HLD_EN_C_H_7       | HLD_EN_C_H_6           | HLD_EN_C_H_5      | HLD_EN_C_H_4     | HLD_EN_C_H_3           | HLD_EN_C_H_2               | HLD_EN_C_H_1    | HLD_EN_C_H_0 | 0xFF  | R/W |

| 0xD1              | SW_LDAC_EN_0                 | [7:0]  | SLD_EN_C_H_7       | SLD_EN_C_H_6           | SLD_EN_C_H_5      | SLD_EN_C_H_4     | SLD_EN_C_H_3           | SLD_EN_C_H_2               | SLD_EN_C_H_1    | SLD_EN_C_H_0 | 0xFF  | R/W |

| 0xD3              | TO DAC_CHn by 2 <sup>1</sup> | [15:8] |                    | DAC_VAL[15:8]          |                   |                  |                        |                            |                 |              |       |     |

| 0xE1              |                              | [7:0]  |                    | DAC_VAL[7:0]           |                   |                  |                        |                            |                 | 0x0000       | R/W   |     |

| 0xE3 <sup>1</sup> | MULTI_DAC_CH                 | [15:8] |                    | MULTI_DAC_VAL[15:8]    |                   |                  |                        |                            |                 | 0x0000       | R/W   |     |

|                   |                              | [7:0]  |                    | MULTI_DAC_VAL[7:0]     |                   |                  |                        |                            |                 |              |       |     |

| 0xE4              | MULTI_DAC_SELECT_0           | [7:0]  | MD_SEL_C_H_7       | MD_SEL_C_H_6           | MD_SEL_C_H_5      | MD_SEL_C_H_4     | MD_SEL_C_H_3           | MD_SEL_C_H_2               | MD_SEL_C_H_1    | MD_SEL_C_H_0 | 0xFF  | R/W |

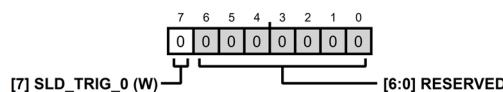

| 0xE5              | SW_LDAC_TRIG_0               | [7:0]  | SLD_TRIG_0         |                        | RESERVED          |                  |                        |                            |                 | 0x00         | R/W   |     |

## レジスタの一覧

表 10. AD3530/AD3530R のレジスター一覧 (続き)

| Reg                                     | Name              | Bits   | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Reset  | RW   |     |

|-----------------------------------------|-------------------|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--------|------|-----|

| 0xE7 <sup>1</sup>                       | MULTI_INPUT_CH    | [15:8] |             |             |             |             |             |             |             |             | 0x0000 | R/W  |     |

|                                         |                   | [7:0]  |             |             |             |             |             |             |             |             |        |      |     |

| 0xE8                                    | MULTI_INPUT_SEL_0 | [7:0]  | MI_SEL_CH_7 | MI_SEL_CH_6 | MI_SEL_CH_5 | MI_SEL_CH_4 | MI_SEL_CH_3 | MI_SEL_CH_2 | MI_SEL_CH_1 | MI_SEL_CH_0 | 0xFF   | R/W  |     |

| 0xE9                                    | SW_LDAC_TRIG_0    | [7:0]  | SLD_TRIG_0  | RESERVED    |             |             |             |             |             |             |        | 0x00 | R/W |

| 0xEB<br>to<br>0xF9<br>by 2 <sup>1</sup> | INPUT_CHn         | [15:8] |             |             |             |             |             |             |             |             | 0x0000 | R/W  |     |

|                                         |                   | [7:0]  |             |             |             |             |             |             |             |             |        |      |     |

<sup>1</sup> 詳細については[マルチバイト・レジスタ](#)のセクションを参照してください。

## レジスタの詳細

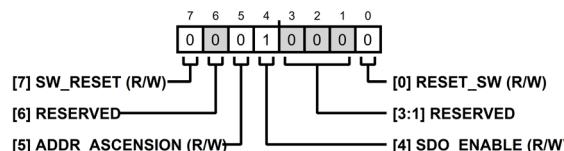

### インターフェース設定 A レジスタ

アドレス : 0x00、リセット : 0x10、レジスタ名 : INTERFACE\_CONFIG\_A

インターフェースの設定値。

表 11. INTERFACE\_CONFIG\_A のビットの説明

| ビット   | ビット名           | 説明                                                                                                                        | リセット | アクセス |

|-------|----------------|---------------------------------------------------------------------------------------------------------------------------|------|------|

| 7     | SW_RESET       | 2つのSW_RESETビットの1つ目。このビットはこのレジスタの2か所にあります。デバイスのソフトウェア・リセットをトリガするには、両方の場所に同時に書き込む必要があります。このレジスタを除くすべてのレジスタがデフォルト値にリセットされます。 | 0x0  | R/W  |

| 6     | RESERVED       | 予約済み。                                                                                                                     | 0x0  | R    |

| 5     | ADDR_ASCENSION | シーケンシャルなアドレス指定動作を決定。<br>0:ストリーミング時にアドレスを1だけデクリメントします。<br>1:ストリーミング時にアドレスを1だけインクリメントします。                                   | 0x0  | R/W  |

| 4     | SDO_ENABLE     | SDOピンをイネーブル。<br>0:SDOピンをディスエーブル。<br>1:SDOピンをイネーブル。                                                                        | 0x1  | R/W  |

| [3:1] | RESERVED       | 予約済み。                                                                                                                     | 0x0  | R    |

| 0     | RESET_SW       | 2つのSW_RESETビットの2つ目。このビットはこのレジスタの2か所にあります。デバイスのソフトウェア・リセットをトリガするには、両方の場所に同時に書き込む必要があります。このレジスタを除くすべてのレジスタがデフォルト値にリセットされます。 | 0x0  | R/W  |

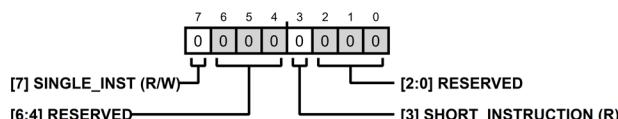

### インターフェース設定 B レジスタ

アドレス : 0x01、リセット : 0x00、レジスタ名 : INTERFACE\_CONFIG\_B

追加のインターフェース設定値。

表 12. INTERFACE\_CONFIG\_B のビットの説明

| ビット   | ビット名              | 説明                                                                                                                           | リセット | アクセス |

|-------|-------------------|------------------------------------------------------------------------------------------------------------------------------|------|------|

| 7     | SINGLE_INST       | ストリーム・モードまたは単一命令モードを選択します。<br>0:ストリーミング・モードがイネーブルになります。連続するデータ・バイトを受信するごとに、アドレスがインクリメント／デクリメントされます。<br>1:単一命令モードがイネーブルになります。 | 0x0  | R/W  |

| [6:4] | RESERVED          | 予約済み。                                                                                                                        | 0x0  | R    |

| 3     | SHORT_INSTRUCTION | 命令フェーズのアドレスを7ビットまたは15ビットに設定します。<br>0:15ビットのアドレス指定。<br>1:7ビットのアドレス指定。                                                         | 0x0  | R/W  |

| [2:0] | RESERVED          | 予約済み。                                                                                                                        | 0x0  | R    |

## レジスタの詳細

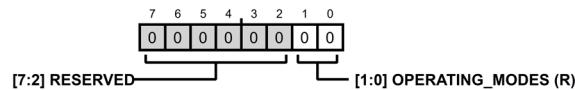

### デバイス設定レジスタ

アドレス : 0x02、リセット : 0x00、レジスタ名 : DEVICE\_CONFIG

表 13. DEVICE\_CONFIG のビットの説明

| ビット   | ビット名            | 説明                                                    | リセット | アクセス |

|-------|-----------------|-------------------------------------------------------|------|------|

| [7:2] | RESERVED        | 予約済み。                                                 | 0x0  | R    |

| [1:0] | OPERATING_MODES | 動作モード。読み出し専用です。<br>00 : 通常動作モード。<br>11 : シャットダウン・モード。 | 0x0  | R    |

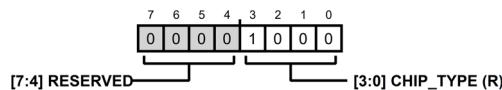

### チップ・タイプ・レジスタ

アドレス : 0x03、リセット : 0x08、レジスタ名 : CHIP\_TYPE

チップ・タイプは、対象のデバイスが属するアナログ・デバイセズ製品ファミリを識別するために用います。目的の製品を一意に特定するには、製品 ID と併せて使用する必要があります。

表 14. CHIP\_TYPE のビットの説明

| ビット   | ビット名      | 説明       | リセット | アクセス |

|-------|-----------|----------|------|------|

| [7:4] | RESERVED  | 予約済み。    | 0x0  | R    |

| [3:0] | CHIP_TYPE | 高精度 DAC。 | 0x8  | R    |

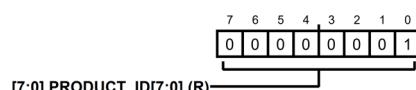

### 製品 ID 下位レジスタ

アドレス : 0x04、リセット : 0x01、レジスタ名 : PRODUCT\_ID\_L

製品 ID の下位バイト。

表 15. PRODUCT\_ID\_L のビットの説明

| ビット   | ビット名            | 説明                                                                 | リセット | アクセス |

|-------|-----------------|--------------------------------------------------------------------|------|------|

| [7:0] | PRODUCT_ID[7:0] | これはデバイスのチップ・タイプ／ファミリです。製品を特定するには、製品 ID と CHIP_TYPE を両方使用する必要があります。 | 0x1  | R    |

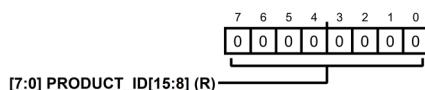

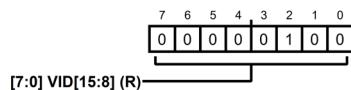

### 製品 ID 上位レジスタ

アドレス : 0x05、リセット : 0x00、レジスタ名 : PRODUCT\_ID\_H

製品 ID の上位バイト。

## レジスタの詳細

表 16. PRODUCT\_ID\_H のビットの説明

| ビット   | ビット名             | 説明                                                            | リセット | アクセス |

|-------|------------------|---------------------------------------------------------------|------|------|

| [7:0] | PRODUCT_ID[15:8] | デバイスのチップ・タイプ／ファミリ。製品を特定するには、製品 ID と CHIP_TYPE を両方使用する必要があります。 | 0x0  | R    |

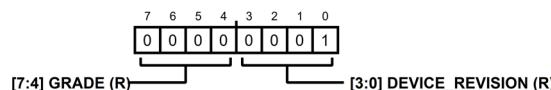

## チップ・グレード・レジスタ

アドレス : 0x06、リセット : 0x01、レジスタ名 : CHIP\_GRADE

製品のバリエーションとデバイスのリビジョンを識別します。

表 17. CHIP\_GRADE のビットの説明

| ビット   | ビット名            | 説明                 | リセット | アクセス |

|-------|-----------------|--------------------|------|------|

| [7:4] | GRADE           | デバイスの性能グレード。       | 0x0  | R    |

| [3:0] | DEVICE_REVISION | デバイスのハードウェア・リビジョン。 | 0x1  | R    |

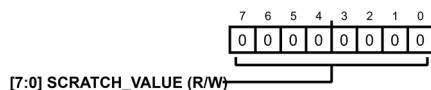

## スクラッチ・パッド・レジスタ

アドレス : 0x0A、リセット : 0x00、レジスタ名 : SCRATCH\_PAD

書き込みや読み出しのテストに使用できます。

表 18. SCRATCH\_PAD のビットの説明

| ビット   | ビット名          | 説明                                                          | リセット | アクセス |

|-------|---------------|-------------------------------------------------------------|------|------|

| [7:0] | SCRATCH_VALUE | ソフトウェア・スクラッチパッド。ソフトウェアは、デバイスに副次的な作用を及ぼすことなく、この場所で読み書きができます。 | 0x0  | R/W  |

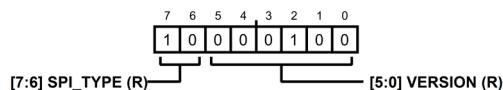

## SPI リビジョン・レジスタ

アドレス : 0x0B、リセット : 0x84、レジスタ名 : SPI\_REVISION

SPI インターフェース・リビジョンを示します。

表 19. SPI\_REVISION のビットの説明

| ビット   | ビット名     | 説明                | リセット | アクセス |