EVALUATION KIT

AVAILABLE

# 25Vスパン、800mAデバイス電源(DPS)

MAX9959

## 概要

MAX9959は、自動試験装置(ATE)やその他の計測器に共通するデバイス電源(DPS)の主要機能をすべて備えています。MAX9959は小型で高水準の集積度と卓越した柔軟性を備えているため、大量のデバイス電源が必要なマルチサイトシステムに最適で経済的です。

MAX9959は、出力電圧および最大/最低(最小の正または最大の負)電圧または電流を個別に設定可能な複数の入力制御電圧を備えています。MAX9959は、負荷電流が2つの設定制限値の間にある場合は電圧源になり、設定電流制限値に達した場合は高精度の電流ソース/シンクに安全に遷移します。出力は、外部から設定された各レベル間に負および正出力電圧値を制限する個別に調整可能な電圧クランプを2つ備えています。

MAX9959は25Vにわたって電圧をソースし、最大 $\pm 800\text{mA}$ の電流をソースすることができます。このDPSは、これより大きい電流をソース/シンクするために外付けバッファに対応しています。複数のMAX9959を共有負荷に対して並列接続構成が可能であり、より柔軟に出力電流を増大することができます。

MAX9959は、広範囲の負荷状態にわたる動作が特長です。設定機能を通じて、セトリング時間、オーバーシュート/アンダーシュート、および安定性を最適化することができます。内蔵の設定可能な範囲変更グリッチ制御回路によって、範囲遷移時の出力グリッチが最小限に抑制されます。

MAX9959は、800mAの負荷において1mVの負荷レギュレーションを提供します。

MAX9959Dは、RCOMFとSENSEの間に300k $\Omega$ の検出抵抗( $R_{FS}$ )を内蔵しています。MAX9959Fはこの検出抵抗を搭載していません。両方のデバイスとも、上面に放熱用のエクスポートドパッド付きの100ピンTQFPパッケージで提供されます。

## アプリケーション

メモリテスタ

VLSIテスタ

オンチップシステムテスタ

産業用システム

構造テスタ

## 特長

- ◆ 25Vスパンの出力電圧

- ◆ プログラマブルな電流および電圧コンプライアンス

- ◆ プログラマブルな電流範囲

- $\pm 200\mu\text{A}$

- $\pm 2\text{mA}$

- $\pm 20\text{mA}$

- $\pm 800\text{mA}$

- ◆ 負荷レギュレーション：1mV (800mAにおいて)

- ◆ 外付けバッファのサポートによって電流増大に対応

- ◆ 複数の並列デバイスによって電流増大に対応

- ◆ プログラマブルな利得によって幅広いDACに対応

- ◆ 被測定物(DUT)のグランド検出

- ◆ プログラマブルな補償によって幅広い負荷を実現

- ◆ Go/No-Goコンパレータ内蔵

- ◆ IDDQテストモード

- ◆ 範囲変更グリッチの制御

- ◆ 小型(14mm x 14mm)パッケージ

- ◆ 3線式シリアルインターフェース

- ◆ サーマル警告フラグおよびサーマルシャットダウン

## 型番

| PART          | TEMP RANGE   | PIN-PACKAGE                   | PKG CODE |

|---------------|--------------|-------------------------------|----------|

| MAX9959DCCQ   | 0°C to +70°C | 100 TQFP-EPR-IDP <sup>†</sup> | C100E-8R |

| MAX9959DCCQ+* | 0°C to +70°C | 100 TQFP-EPR-IDP <sup>†</sup> | C100E-8R |

| MAX9959FCCQ*  | 0°C to +70°C | 100 TQFP-EPR-IDP <sup>†</sup> | C100E-8R |

| MAX9959FCCQ+* | 0°C to +70°C | 100 TQFP-EPR-IDP <sup>†</sup> | C100E-8R |

\*開発中。入手性についてはお問い合わせください。

+は鉛(Pb)フリーパッケージ/RoHS準拠パッケージを表します。

<sup>†</sup>EPR = エクスポートドパッド。上面ダイパッド。

ピン配置はデータシートの最後に記載されています。

Maxim Integrated Products 1

本データシートは日本語翻訳であり、相違及び誤りのある可能性があります。設計の際は英語版データシートを参照してください。

価格、納期、発注情報についてはMaxim Direct (0120-551056)にお問い合わせいただくか、Maximのウェブサイト ([japan.maxim-ic.com](http://japan.maxim-ic.com))をご覧ください。

# 25Vスパン、800mAデバイス電源(DPS)

**MAX9959**

## ABSOLUTE MAXIMUM RATINGS

|                                          |                                                      |

|------------------------------------------|------------------------------------------------------|

| V <sub>CC</sub> to V <sub>EE</sub> ..... | +30V                                                 |

| V <sub>CC</sub> to AGND .....            | +20V                                                 |

| V <sub>EE</sub> to AGND .....            | -15V                                                 |

| V <sub>L</sub> to DGND .....             | +6V                                                  |

| AGND to DGND .....                       | -0.5V to +0.5V                                       |

| Digital Inputs .....                     | -0.3V to (V <sub>L</sub> + 0.3V)                     |

| All Other Pins .....                     | (V <sub>EE</sub> - 0.3V) to (V <sub>CC</sub> + 0.3V) |

|                                                                                                                            |                 |

|----------------------------------------------------------------------------------------------------------------------------|-----------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>100-Pin TQFP-EPR-IDP (derated at 166.7mW/°C<br>above +70°C) ..... | 13.33W          |

| Junction Temperature .....                                                                                                 | +150°C          |

| Storage Temperature Range .....                                                                                            | -65°C to +150°C |

| Lead Temperature (soldering, 10s) .....                                                                                    | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +12V, V<sub>EE</sub> = -12V, V<sub>L</sub> = +3.3V, T<sub>J</sub> = +30°C to +100°C. Typical values are at T<sub>J</sub> = +30°C, unless otherwise specified.) (Notes 1, 2)

| PARAMETER                              | SYMBOL               | CONDITIONS                                                                                                                       | MIN                   | TYP                   | MAX   | UNITS  |

|----------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-------|--------|

| <b>VOLTAGE OUTPUT</b>                  |                      |                                                                                                                                  |                       |                       |       |        |

| Output Voltage Range                   | V <sub>DUT</sub>     | DUT current below 10% of FSR current                                                                                             | V <sub>EE</sub> + 2.5 | V <sub>CC</sub> - 2.5 |       | V      |

|                                        |                      | DUT current = +800mA, range A (Note 2)                                                                                           | 0                     | +7                    |       |        |

|                                        |                      | DUT current = -800mA, range A (Note 2)                                                                                           | -7                    | 0                     |       |        |

|                                        |                      | DUT current at full scale (I <sub>DUT</sub> = 200μA, 2mA, 20mA, or 200mA)                                                        | V <sub>EE</sub> + 5   | V <sub>CC</sub> - 5   |       |        |

| Output Offset                          | V <sub>OS</sub>      | V <sub>IN</sub> = 0, I <sub>OUT</sub> = 0 (no load), gain = +1                                                                   |                       |                       | ±25   | mV     |

| Output-Voltage Temperature Coefficient | V <sub>OSTC</sub>    |                                                                                                                                  |                       | ±50                   |       | μV/°C  |

| Voltage Gain Error                     | V <sub>GE</sub>      | Gain = +1                                                                                                                        |                       | ±1.25                 |       | %      |

|                                        |                      | Gain = +2                                                                                                                        |                       | ±1.25                 |       |        |

|                                        |                      | Gain = +6                                                                                                                        |                       | ±1.25                 |       |        |

|                                        |                      | Gain = -1                                                                                                                        |                       | ±1.25                 |       |        |

|                                        |                      | Gain = -2                                                                                                                        |                       | ±1.25                 |       |        |

|                                        |                      | Gain = -6                                                                                                                        |                       | ±1.25                 |       |        |

| Voltage-Gain Temperature Coefficient   | V <sub>GETC</sub>    |                                                                                                                                  |                       | ±5                    |       | ppm/°C |

| Linearity Error                        | V <sub>LER</sub>     | Gain and offset errors calibrated out; I <sub>OUT</sub> = 0 for ranges A, C, and D; ±20mA for range B; gain = +1 (Notes 3, 4, 5) |                       |                       | ±0.02 | %FSR   |

| Off-State Leakage Current              | HIZFLK               | R <sub>COMF</sub> = (V <sub>CC</sub> - 2.5V) to (V <sub>EE</sub> + 2.5V)                                                         | -10                   | +10                   |       | nA     |

| Force-to-Sense Resistor                | R <sub>FS</sub>      | "D" option only                                                                                                                  |                       | 300                   |       | kΩ     |

| <b>DUT GROUND SENSE</b>                |                      |                                                                                                                                  |                       |                       |       |        |

| Voltage Range                          | ΔV <sub>DUTGND</sub> | V <sub>DUTGSNS</sub> - V <sub>AGND</sub>                                                                                         | ±500                  | ±700                  |       | mV     |

| <b>LOAD REGULATION (Note 6)</b>        |                      |                                                                                                                                  |                       |                       |       |        |

| Voltage                                | ΔV <sub>DUT</sub>    | Range A, gain = +1, V <sub>IN</sub> = (V <sub>CC</sub> - 5V) to (V <sub>EE</sub> + 5V), ±800mA current load step (Note 5)        |                       | ±1                    | ±7    | mV     |

# 25Vスパン、800mAデバイス電源(DPS)

MAX9959

## DC ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = +12V$ ,  $V_{EE} = -12V$ ,  $V_L = +3.3V$ ,  $T_J = +30^{\circ}C$  to  $+100^{\circ}C$ . Typical values are at  $T_J = +30^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                                                         | SYMBOL              | CONDITIONS                                                                                                                                | MIN       | TYP       | MAX        | UNITS            |

|-------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------------|------------------|

| <b>CURRENT OUTPUT</b>                                             |                     |                                                                                                                                           |           |           |            |                  |

| Output Current Range                                              | I <sub>DUT</sub>    | Range D, $R_D = 5000\Omega$                                                                                                               |           | $\pm 200$ |            | $\mu A$          |

|                                                                   |                     | Range C, $R_C = 500\Omega$                                                                                                                |           | $\pm 2$   |            | mA               |

|                                                                   |                     | Range B, $R_B = 50\Omega$                                                                                                                 |           | $\pm 20$  |            |                  |

|                                                                   |                     | Range A, $R_A = 1.25\Omega$                                                                                                               |           | $\pm 800$ |            |                  |

| Input Voltage Range Corresponding to the Full-Scale Force Current | V <sub>INI</sub>    | IOSI = AGND                                                                                                                               | -4        | +4        |            | V                |

|                                                                   |                     | IOSI = AGND + 4V                                                                                                                          | 0         | +8        |            |                  |

| Current-Sense-Amp Offset Voltage Input                            | V <sub>IOSI</sub>   | Relative to AGND                                                                                                                          | -0.2      | +4.4      |            | V                |

| Output Current Offset                                             | I <sub>OS</sub>     | R <sub>COMF</sub> = 0 (Note 4)                                                                                                            |           | $\pm 0.1$ | $\pm 0.5$  | %FSR             |

| Force-Current Offset Temperature Coefficient                      | I <sub>OSTC</sub>   |                                                                                                                                           |           | $\pm 20$  |            | ppm/ $^{\circ}C$ |

| Gain Error                                                        | I <sub>GE</sub>     | R <sub>COMF</sub> = 0, I <sub>OUT</sub> = $\pm FSR$                                                                                       |           |           | $\pm 1.0$  | %                |

| Forced-Current Gain Temperature Coefficient                       | I <sub>GETC</sub>   |                                                                                                                                           |           | $\pm 20$  |            | ppm/ $^{\circ}C$ |

| Output Over Current-Limit Range (Note 4)                          | I <sub>OCL</sub>    | Range D, I <sub>OUT</sub> = $\pm 200\mu A$                                                                                                | $\pm 135$ | $\pm 147$ | $\pm 158$  | %FSR             |

|                                                                   |                     | Range C, I <sub>OUT</sub> = $\pm 2mA$                                                                                                     | $\pm 135$ | $\pm 147$ | $\pm 158$  |                  |

|                                                                   |                     | Range B, I <sub>OUT</sub> = $\pm 20mA$                                                                                                    | $\pm 135$ | $\pm 147$ | $\pm 158$  |                  |

|                                                                   |                     | Range A, I <sub>OUT</sub> = $\pm 800mA$                                                                                                   | $\pm 125$ | $\pm 138$ | $\pm 150$  |                  |

| Linearity Error                                                   | I <sub>LER</sub>    | Gain, offset, and CMR errors calibrated out; V <sub>IOSI</sub> = -0.2V and +4.4V; ranges B, C, and D (Notes 4, 5, 7)                      |           |           | $\pm 0.02$ | %FSR             |

| Rejection of Output Error Due to Common-Mode Load Voltage         | CMROER              | Range D, I <sub>OUT</sub> = 0, V <sub>RCOMF</sub> = (V <sub>EE</sub> + 2.5V) and (V <sub>CC</sub> - 2.5V), measured across R <sub>D</sub> | 0.001     | 0.005     |            | %FSR/V           |

| <b>CURRENT MONITOR</b>                                            |                     |                                                                                                                                           |           |           |            |                  |

| Measured Current Range                                            | I <sub>DUTM</sub>   | Range D                                                                                                                                   |           | $\pm 200$ |            | $\mu A$          |

|                                                                   |                     | Range C                                                                                                                                   |           | $\pm 2$   |            | mA               |

|                                                                   |                     | Range B                                                                                                                                   |           | $\pm 20$  |            |                  |

|                                                                   |                     | Range A                                                                                                                                   |           | $\pm 800$ |            |                  |

| Current-Sense-Amp Voltage Range                                   | V <sub>ISENSE</sub> | IOSI = AGND                                                                                                                               | -4        | +4        |            | V                |

|                                                                   |                     | IOSI = AGND + 4V                                                                                                                          | 0         | +8        |            |                  |

| Current-Sense-Amp Offset Voltage Input                            | V <sub>IOSI</sub>   | Relative to AGND                                                                                                                          | -0.2      | +4.4      |            | V                |

| Current-Sense-Amp Offset                                          | I <sub>MOS</sub>    | R <sub>COMF</sub> = 0 (Note 4)                                                                                                            |           | $\pm 0.1$ | $\pm 0.5$  | %FSR             |

| Measured-Current Offset Temperature Coefficient                   | I <sub>MOSTC</sub>  |                                                                                                                                           |           | $\pm 20$  |            | ppm/ $^{\circ}C$ |

| Gain Error                                                        | I <sub>MGE</sub>    | R <sub>COMF</sub> = 0, I <sub>OUT</sub> = $\pm FSR$                                                                                       |           |           | $\pm 1$    | %                |

# 25Vスパン、800mAデバイス電源(DPS)

**MAX9959**

## DC ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = +12V$ ,  $V_{EE} = -12V$ ,  $V_L = +3.3V$ ,  $T_J = +30^{\circ}C$  to  $+100^{\circ}C$ . Typical values are at  $T_J = +30^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                                                 | SYMBOL               | CONDITIONS                                                                                                          | MIN            | TYP                           | MAX   | UNITS             |

|-----------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|-------|-------------------|

| Measured-Current Gain Temperature Coefficient             | $I_{MGETC}$          |                                                                                                                     |                | $\pm 20$                      |       | ppm/ $^{\circ}C$  |

| Linearity Error                                           | $I_{MLER}$           | Gain, offset, and CMR errors calibrated out; $V_{IOSI} = -0.2V$ and $+4.4V$ , range B (Notes 4, 5)                  |                | $\pm 0.02$                    |       | %FSR              |

| Rejection of Output Error Due to Common-Mode Load Voltage | $CMR_{MOER}$         | Range D, $I_{OUT} = 0$ , $V_{RCOMF} = (V_{EE} + 2.5V)$ and $(V_{CC} - 2.5V)$                                        |                | 0.001                         | 0.005 | %FSR/V            |

| <b>VOLTAGE MONITOR</b>                                    |                      |                                                                                                                     |                |                               |       |                   |

| Measured Output Voltage Range                             | $V_{DUTM}$           | Gain = +1, $V_{IOSV} = AGND$                                                                                        | $V_{EE} + 2.5$ | $V_{CC} - 2.5$                |       | V                 |

| Voltage-Sense-Amp Offset Voltage Input                    | $V_{IOSV}$           | Relative to AGND                                                                                                    | -0.2           | $+4.4$                        |       | V                 |

| Voltage-Sense-Amp Offset                                  | $V_{DUTMOS}$         | Gain = +1                                                                                                           |                | $\pm 25$                      |       | mV                |

| Measured Voltage Offset Temperature Coefficient           | $V_{DUTMOSTC}$       |                                                                                                                     |                | $\pm 10$                      |       | $\mu V/^{\circ}C$ |

| Voltage-Sense-Amp Gain Error                              | $V_{DUTGE}$          | Gain = +1                                                                                                           |                | $\pm 1$                       | %     |                   |

|                                                           |                      | Gain = +1/2                                                                                                         |                | $\pm 1$                       |       |                   |

|                                                           |                      | Gain = +1/6                                                                                                         |                | $\pm 1$                       |       |                   |

| Measured-Voltage Gain Temperature Coefficient             | $V_{DUTGETC}$        |                                                                                                                     |                | $\pm 10$                      |       | ppm/ $^{\circ}C$  |

| Linearity Error                                           | $V_{DUTLER}$         | Gain and offset errors calibrated out, $V_{IOSV} = -0.2V$ and $+4.4V$ , $I_{OUT} = 0$ , gain = +1, range B (Note 4) |                | $\pm 0.02$                    |       | %FSR              |

| <b>VOLTAGE/CURRENT CLAMPS (Note 8)</b>                    |                      |                                                                                                                     |                |                               |       |                   |

| Input Control Voltage                                     | $V_{CLLO}, V_{CLHI}$ |                                                                                                                     | $V_{EE} + 2.3$ | $V_{CC} - 2.3$                |       | V                 |

| Voltage Clamp Range (Note 9)                              | $V_{CRNG}$           | DPS output current $\leq 10\%$ of FSR                                                                               | $V_{EE} + 2.5$ | $V_{CC} - 2.5$                | V     |                   |

|                                                           |                      | DPS output current at FSR                                                                                           | $V_{EE} + 5$   | $V_{CC} - 5$                  |       |                   |

| Voltage Clamp Gain                                        | $V_{CGAIN}$          |                                                                                                                     |                | +1                            |       | V/V               |

| Voltage Clamp Accuracy                                    | $VC_{ERR}$           | Range A to D, $I_{OUT} = \pm FSR$ (Notes 2, 9)                                                                      |                | $\pm 200$                     |       | mV                |

| Current Clamp Range                                       | $IC_{RNG}$           | (Note 10)                                                                                                           |                | $V_{IOSI} \pm 1.5 \times FSR$ |       | V                 |

| Current Clamp Gain                                        | $IC_{GAIN}$          |                                                                                                                     |                | 4                             |       | V/FSR             |

| Current Clamp Accuracy                                    | $IC_{ERR}$           | Range A, $V_{OUT} = \pm FSR$ , $I_{OUT} = \pm FSR$ (Notes 2, 10)                                                    |                | $\pm 0.15$                    | %FSR  |                   |

|                                                           |                      | Range B to D, $V_{OUT} = \pm FSR$ , gain and offset errors calibrated out (Note 10)                                 |                | $\pm 0.05$                    |       |                   |

| <b>COMPARATOR INPUTS</b>                                  |                      |                                                                                                                     |                |                               |       |                   |

| Input Voltage Range                                       | $CMP_{IRG}$          |                                                                                                                     | $V_{EE} + 3.5$ | $V_{CC} - 3.5$                |       | V                 |

| Input Offset Voltage                                      | $CMP_{IOS}$          | $V_{ITHHI} = V_{ITHLO} = 0$                                                                                         |                | $\pm 30$                      |       | mV                |

# 25Vスパン、800mAデバイス電源(DPS)

MAX9959

## DC ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = +12V$ ,  $V_{EE} = -12V$ ,  $V_L = +3.3V$ ,  $T_J = +30^{\circ}C$  to  $+100^{\circ}C$ . Typical values are at  $T_J = +30^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                            | SYMBOL            | CONDITIONS                                                         | MIN          | TYP              | MAX | UNITS          |

|--------------------------------------|-------------------|--------------------------------------------------------------------|--------------|------------------|-----|----------------|

| <b>COMPARATOR OUTPUTS</b>            |                   |                                                                    |              |                  |     |                |

| Output High Voltage                  | CMPOH             | $V_L = 2.375V$ to $3.3V$ , $R_{PULLUP} = 1k\Omega$                 | $V_L - 0.2$  |                  |     | V              |

| Output Low Voltage                   | CMPOL             | $V_L = 2.375V$ to $3.3V$ , $R_{PULLUP} = 1k\Omega$                 |              | 0.4              |     | V              |

| High-Impedance State Leakage Current | CMPOLK            |                                                                    |              | $\pm 5$          |     | nA             |

| High-Impedance Output Capacitance    | CMPOC             |                                                                    |              | 1                |     | pF             |

| <b>ANALOG INPUTS</b>                 |                   |                                                                    |              |                  |     |                |

| Input Current                        | $I_{IN}$          |                                                                    |              | $\pm 5$          |     | nA             |

| Input Capacitance                    | $C_{IN}$          |                                                                    |              | 4                |     | pF             |

| <b>DIGITAL INPUTS</b>                |                   |                                                                    |              |                  |     |                |

| Input High Voltage                   | $V_{IH}$          |                                                                    |              | $V_{THR} + 0.15$ |     | V              |

| Input Low Voltage                    | $V_{IL}$          |                                                                    |              | $V_{THR} - 0.15$ |     | V              |

| VTHR Input Range                     | $V_{THR}$         |                                                                    | 0.5          | $V_L - 0.5$      |     | V              |

| Input Current                        | $I_{IN}$          |                                                                    |              | $\pm 25$         |     | $\mu A$        |

| Input Capacitance                    | $C_{IN}$          |                                                                    |              | 4                |     | pF             |

| <b>DIGITAL OUTPUTS</b>               |                   |                                                                    |              |                  |     |                |

| Output High Voltage                  | $V_{OH}$          | $V_L = 2.375V$ to $3.3V$ , relative to DGND,<br>$I_{OUT} = +1.0mA$ | $V_L - 0.25$ |                  |     | V              |

| Output Low Voltage                   | $V_{OL}$          | $V_L = 2.375V$ to $3.3V$ , relative to DGND,<br>$I_{OUT} = -1.0mA$ |              | 0.2              |     | V              |

| <b>TEMPERATURE SENSOR</b>            |                   |                                                                    |              |                  |     |                |

| Analog Output Offset                 | $V_{TSNSO}$       | $T_J = +28^{\circ}C$                                               |              | 3.01             |     | V              |

| Analog Output Gain                   | $V_{TSNSG}$       |                                                                    |              | 10               |     | $mV/^{\circ}C$ |

| Digital Output Temperature Threshold | $T_{TSNSR}$       | (Note 11)                                                          |              | +130             |     | $^{\circ}C$    |

| Thermal-Shutdown Temperature         | $T_{SDN}$         |                                                                    |              | +140             |     | $^{\circ}C$    |

| <b>POWER SUPPLY</b>                  |                   |                                                                    |              |                  |     |                |

| Positive Supply                      | $V_{CC}$          | (Note 12)                                                          | 12           | 18               |     | V              |

| Negative Supply                      | $V_{EE}$          | (Note 12)                                                          | -15          | -12              |     | V              |

| Total Supply Voltage                 | $V_{CC} - V_{EE}$ |                                                                    |              | +30              |     | V              |

| Logic Supply                         | $V_L$             |                                                                    | +2.375       | +3.300           |     | V              |

| Positive Supply Current              | $I_{CC}$          | No load                                                            | 20           | 22               |     | $mA$           |

| Negative Supply Current              | $I_{EE}$          | No load                                                            | 19           | 21               |     | $mA$           |

| Analog Ground Current                | $I_{AGND}$        | No load                                                            | 0.8          | 1.0              |     | $mA$           |

| Logic Supply Current                 | $I_L$             | No load, all digital inputs at DGND                                | 7.0          | 9.0              |     | $mA$           |

| Digital Ground Current               | $I_{DGND}$        | No load, all digital inputs at DGND                                | 7.0          | 9.0              |     | $mA$           |

| Power-Supply Rejection Ratio         | PSRR              | Each supply varied individually from min to max, $V_{DUT} = 5.0V$  | 80           |                  |     | dB             |

# 25Vスパン、800mAデバイス電源(DPS)

## AC ELECTRICAL CHARACTERISTICS

( $V_{CC} = +12V$ ,  $V_{EE} = -12V$ ,  $V_L = +3.3V$ ,  $C_{C1} = 350pF$ ,  $C_L = 100pF$ ,  $C_{MEAS} = 100pF$ ,  $C_{IMEAS} = 100pF$ ,  $T_J = +30^{\circ}C$  to  $+100^{\circ}C$ . Typical values are at  $T_J = +35^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                                                                                               | SYMBOL              | CONDITIONS                                                                                                | MIN | TYP  | MAX | UNITS |

|---------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| <b>FORCE VOLTAGE (Notes 13, 14)</b>                                                                     |                     |                                                                                                           |     |      |     |       |

| Settling Time                                                                                           | FVST                | Range D = $\pm 200\mu A$ , $R_L = 35k\Omega$ to AGND                                                      | 30  |      |     | μs    |

|                                                                                                         |                     | Range C = $\pm 2mA$ , $R_L = 3.5k\Omega$ to AGND                                                          | 20  |      |     |       |

|                                                                                                         |                     | Range B = $\pm 20mA$ , $R_L = 350\Omega$ to AGND                                                          | 30  | 50   |     |       |

|                                                                                                         |                     | Range A = $\pm 800mA$ , $R_L = 8.75\Omega$ to AGND                                                        | 25  |      |     |       |

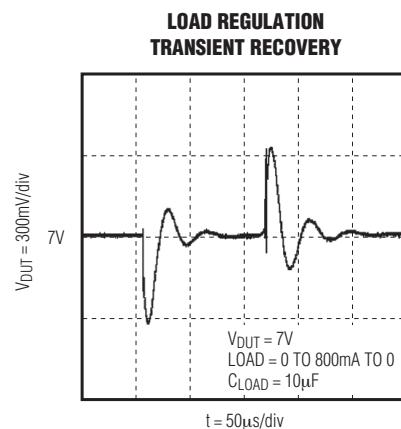

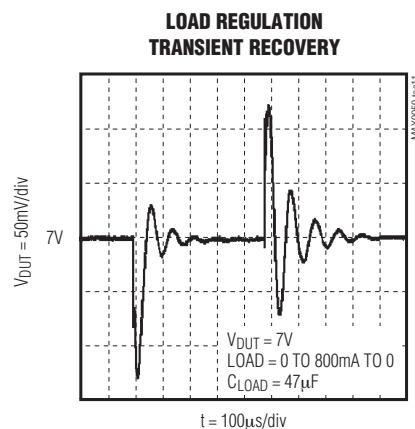

| <b>LOAD REGULATION SETTLING TIME (Note 14)</b>                                                          |                     |                                                                                                           |     |      |     |       |

| Settling Time                                                                                           | LRST                | Range A, $V_{IN} = \pm 7V$ , $R_L = 8.75\Omega$ switched between open circuit to AGND, $C_L = 10\mu F$    | 100 |      |     | μs    |

| <b>FORCE VOLTAGE/MEASURE CURRENT (Notes 13, 14, 15)</b>                                                 |                     |                                                                                                           |     |      |     |       |

| Settling Time                                                                                           | FVMIST              | Range D = $\pm 200\mu A$ , $R_L = 35k\Omega$ to AGND                                                      | 50  |      |     | μs    |

|                                                                                                         |                     | Range C = $\pm 2mA$ , $R_L = 3.5k\Omega$ to AGND                                                          | 20  |      |     |       |

|                                                                                                         |                     | Range B = $\pm 20mA$ , $R_L = 350\Omega$ to AGND                                                          | 25  | 50   |     |       |

|                                                                                                         |                     | Range A = $\pm 800mA$ , $R_L = 8.75\Omega$ to AGND                                                        | 35  |      |     |       |

| <b>FORCE CURRENT (Notes 13, 14)</b>                                                                     |                     |                                                                                                           |     |      |     |       |

| Settling Time                                                                                           | FI <sub>ST</sub>    | Range D = $\pm 200\mu A$ , $R_L = 35k\Omega$ to AGND                                                      | 100 |      |     | μs    |

|                                                                                                         |                     | Range C = $\pm 2mA$ , $R_L = 3.5k\Omega$ to AGND                                                          | 35  |      |     |       |

|                                                                                                         |                     | Range B = $\pm 20mA$ , $R_L = 350\Omega$ to AGND                                                          | 25  | 50   |     |       |

|                                                                                                         |                     | Range A = $\pm 800mA$ , $R_L = 8.75\Omega$ to AGND                                                        | 20  |      |     |       |

| <b>FORCE CURRENT/MEASURE VOLTAGE (Notes 13, 14, 15)</b>                                                 |                     |                                                                                                           |     |      |     |       |

| Settling Time                                                                                           | FIMV <sub>ST</sub>  | Range D = $\pm 200\mu A$ , $R_L = 35k\Omega$ to AGND                                                      | 100 |      |     | μs    |

|                                                                                                         |                     | Range C = $\pm 2mA$ , $R_L = 3.5k\Omega$ to AGND                                                          | 35  |      |     |       |

|                                                                                                         |                     | Range B = $\pm 20mA$ , $R_L = 350\Omega$ to AGND                                                          | 25  | 50   |     |       |

|                                                                                                         |                     | Range A = $\pm 800mA$ , $R_L = 8.75\Omega$ to AGND                                                        | 40  |      |     |       |

| <b>FORCE OUTPUT</b>                                                                                     |                     |                                                                                                           |     |      |     |       |

| Output Slew Rate                                                                                        | FO <sub>SLEW</sub>  | $C_L = 0$ (Note 16)                                                                                       | 0.7 | 2.1  |     | V/μs  |

| Stable Load Capacitance Range                                                                           | FO <sub>SLC</sub>   | (Notes 17, 18)                                                                                            |     | 1000 |     | μF    |

| Output Overshoot                                                                                        | FO <sub>OOSHT</sub> | $C_L < 20\mu F$ , $CB1 = 3nF$                                                                             | 0   |      |     | %     |

| <b>MEASURE OUTPUT</b>                                                                                   |                     |                                                                                                           |     |      |     |       |

| Stable Load Capacitance Range                                                                           | MO <sub>SLC</sub>   | (Note 17)                                                                                                 |     | 1000 |     | pF    |

| <b>COMPARATORS (<math>C_{ILIMHI/LIMLO} = 20pF</math>, <math>R_{PULLUP} = 1k\Omega</math>) (Note 19)</b> |                     |                                                                                                           |     |      |     |       |

| Propagation Delay                                                                                       | CMP <sub>PD</sub>   | 100mV overdrive, 1V <sub>P-P</sub> , measured from input threshold zero crossing to 50% of output voltage | 100 |      |     | ns    |

| Rise Time                                                                                               | CMP <sub>TR</sub>   | 20% to 80%                                                                                                | 80  |      |     | ns    |

| Fall Time                                                                                               | CMP <sub>TF</sub>   | 20% to 80%                                                                                                | 5   |      |     | ns    |

| Disable True to High Impedance                                                                          | CMP <sub>HIZT</sub> | Measured from 50% of digital input voltage to 10% of output voltage                                       | 100 |      |     | ns    |

| Disable False to Active                                                                                 | CMP <sub>HIZF</sub> | Measured from 50% of digital input voltage to 90% of output voltage                                       | 100 |      |     | ns    |

## AC ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = +12V$ ,  $V_{EE} = -12V$ ,  $V_L = +3.3V$ ,  $C_{C1} = 350pF$ ,  $C_L = 100pF$ ,  $C_{MEAS} = 100pF$ ,  $C_{IMEAS} = 100pF$ ,  $T_J = +30^{\circ}C$  to  $+100^{\circ}C$ . Typical values are at  $T_J = +35^{\circ}C$ , unless otherwise specified.) (Notes 1, 2)

| PARAMETER                                                                                                    | SYMBOL            | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------------------------------------------------------------|-------------------|------------|-----|-----|-----|-------|

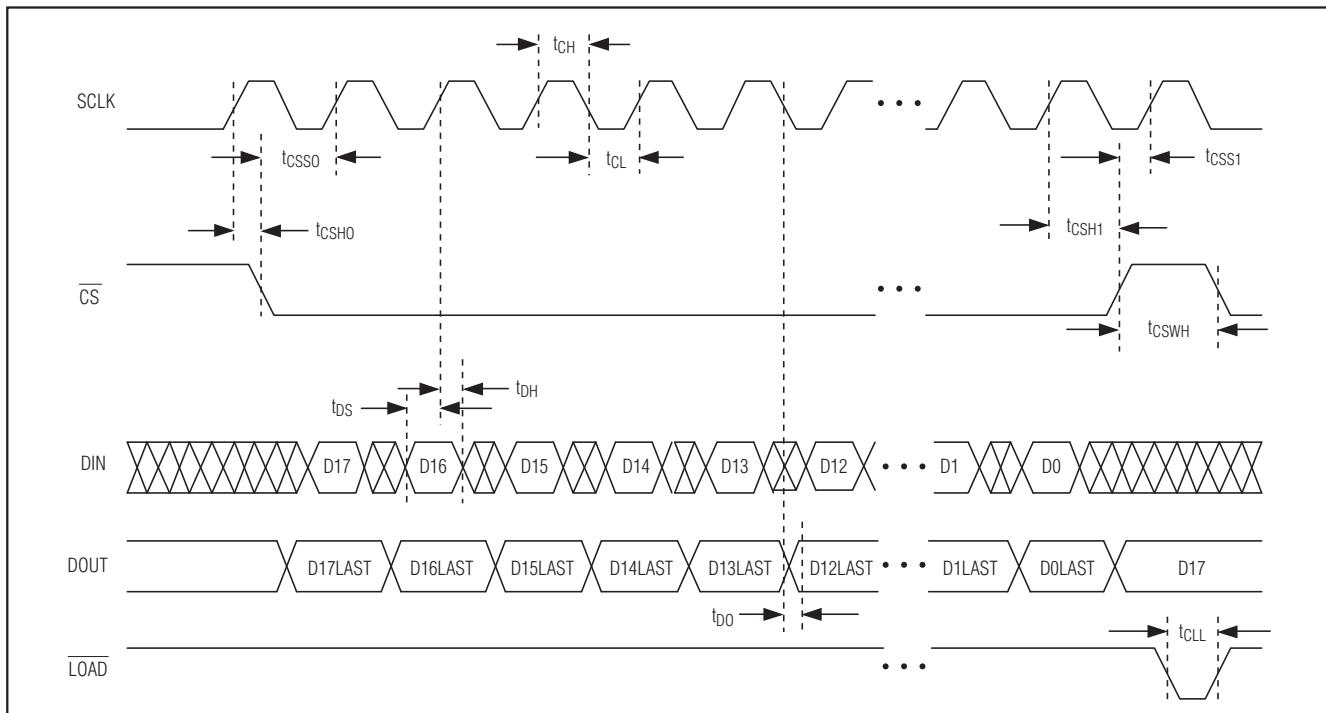

| <b>SERIAL PORT TIMING CHARACTERISTICS (<math>V_L = 3.0V</math>, <math>C_{DOUT} = 10pF</math>) (Figure 4)</b> |                   |            |     |     |     |       |

| Serial Clock Frequency                                                                                       | f <sub>SCLK</sub> |            |     |     | 20  | MHz   |

| SCLK Pulse-Width High                                                                                        | t <sub>CH</sub>   |            |     | 12  |     | ns    |

| SCLK Pulse-Width Low                                                                                         | t <sub>CL</sub>   |            |     | 12  |     | ns    |

| SCLK Fall to DOUT Valid                                                                                      | t <sub>DO</sub>   |            |     |     | 25  | ns    |

| CS Low to SCLK High Setup                                                                                    | t <sub>CS0</sub>  |            | 10  |     |     | ns    |

| SCLK High to CS High Hold                                                                                    | t <sub>CSH1</sub> |            | 22  |     |     | ns    |

| SCLK High to CS Low Hold                                                                                     | t <sub>CSH0</sub> | (Note 17)  | 0   |     |     | ns    |

| CS High to SCLK High Setup                                                                                   | t <sub>CS1</sub>  |            | 5   |     |     | ns    |

| DIN to SCLK High Setup                                                                                       | t <sub>DS</sub>   |            | 10  |     |     | ns    |

| DIN to SCLK High Hold                                                                                        | t <sub>DH</sub>   |            | 0   |     |     | ns    |

| CS Pulse-Width High                                                                                          | t <sub>CSWH</sub> |            | 10  |     |     | ns    |

| CS Pulse-Width Low                                                                                           | t <sub>CSWL</sub> |            | 10  |     |     | ns    |

| LOAD Pulse-Width Low                                                                                         | t <sub>CLL</sub>  |            | 20  |     |     | ns    |

| Power-On Reset                                                                                               | POR               |            |     |     | 50  | μs    |

**Note 1:** All minimum and maximum test limits are 100% production tested at  $T_J = +35^{\circ}C \pm 15^{\circ}C$  at nominal supplies. Specifications over the full operating temperature range are guaranteed by design and characterization.

**Note 2:** Exercise care not to exceed the maximum power dissipation specifications listed in the *Absolute Maximum Ratings* section. With drive current of  $\pm 800mA$  limit DPS operation to two quadrants (i.e., when sourcing current limit  $V_{DUT}$  to below +7V, when sinking current limit  $V_{DUT}$  to above -7V). With drive current below  $\pm 800mA$  and four-quadrant operation, limit DPS power dissipation to below the allowed maximum.

**Note 3:** VIN swept to achieve an output voltage of ( $V_{EE} + 2.5V$ ) to ( $V_{CC} - 2.5V$ ), with  $I_{OUT} = 0$ .

**Note 4:** Parameters expressed in terms of %FSR (percent of full-scale range) are as a percent of the end-point-to-end-point range.

**Note 5:** Case must be maintained to within  $\pm 5^{\circ}C$  for linearity specifications to apply.

**Note 6:** Load regulation is defined at a single programmed output voltage (force voltage mode), independent of linearity specification, with a 0 to 100% current step.

**Note 7:** To maintain linearity, keep the clamps at least 700mV away from VR<sub>COMF</sub>.

**Note 8:** In the force-current and force-voltage modes, the reference-clamping voltage CLH must be greater than 0V, and CLL must be less than 0V. For high clamping accuracy, CLH-CLL is > 1V. To maintain 0.02% force-voltage linearity when the programmable current clamps are enabled, two conditions must be met: 1) CLH and CLL must be set 12.5% FSR higher than the forced current and 2) CLH and CLL must be set such that CLH is  $\geq 1.6V + IOSI$  and CLL is  $\leq -1.6V + IOSI$  (e.g., if driving  $\pm 1mA$  in the 2mA range, the current clamps must be set to a minimum of  $\pm 1.5mA$ , or CLH = 3V, CLL = -3V, and IOSI = 0V).

**Note 9:** DPS in force current mode.

**Note 10:** DPS in force voltage mode.

**Note 11:** The temperature threshold may vary up to  $\pm 10^{\circ}C$  from the specified threshold.

**Note 12:** The device operates properly within absolute specifications, for varying supply voltages with equally varying output voltage settings.

**Note 13:** Settling times are for a full-scale voltage or current step. FV<sub>S</sub>T measured from VIN to V<sub>DUT</sub>, FV<sub>M</sub>IST from VIN to IMEAS, FI<sub>S</sub>T from VIN to V<sub>DUT</sub>, and FIMV<sub>S</sub>T from VIN to V<sub>MEAS</sub>.

**Note 14:** Settling times are to 0.1% of FSR.

**Note 15:** The actual settling time of the measure path (sense input to measure output) is less than 1μs. However, the RC time constant of the sense resistor and the load capacitance causes a longer overall settling time of V<sub>DUT</sub>. This settling time is a function of the current range resistor.

**Note 16:** Slew rate is measured from the 20% to 80% points.

**Note 17:** Guaranteed by design and characterization.

**Note 18:** Range A.

**Note 19:** The propagation delay time is measured by holding the current constant, and transitioning ITHHI or ITHLO.

# 25Vスパン、800mAデバイス電源(DPS)

MAX9959

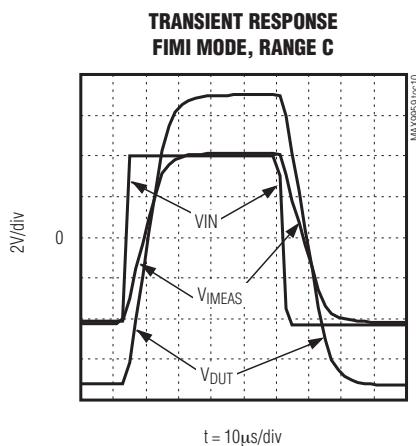

## 標準動作特性

( $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

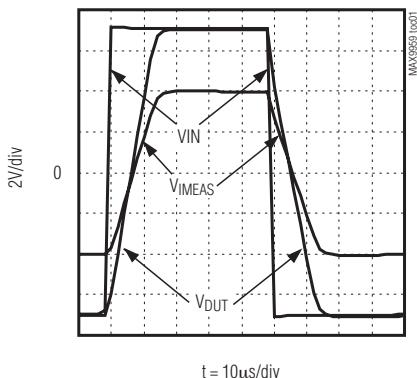

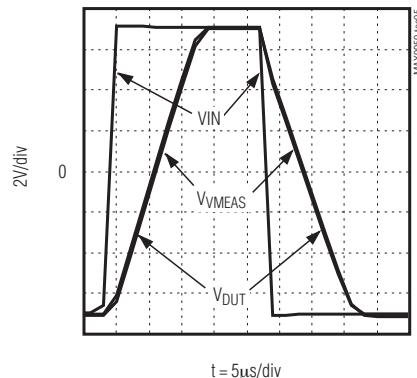

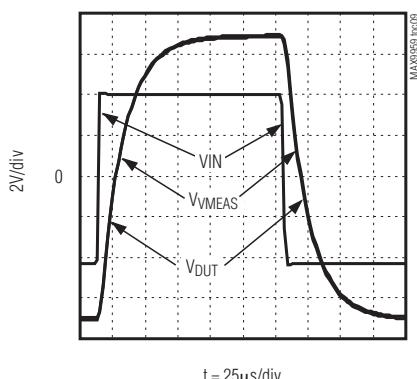

TRANSIENT RESPONSE

FVMI MODE, RANGE A

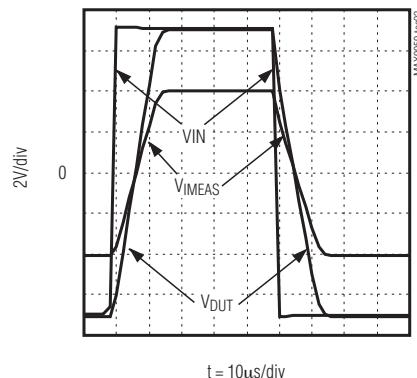

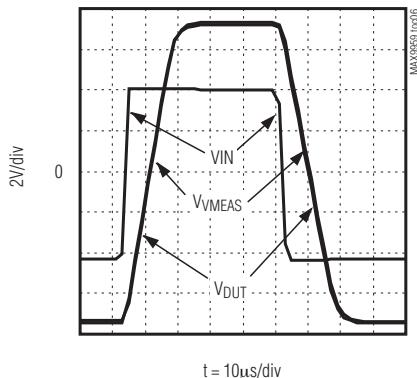

TRANSIENT RESPONSE

FVMI MODE, RANGE B

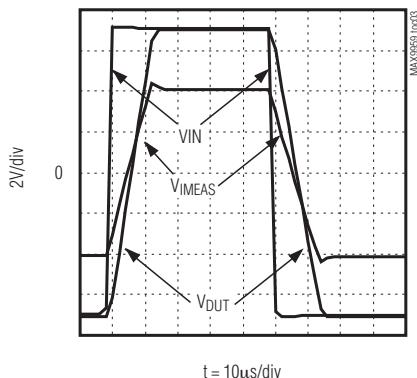

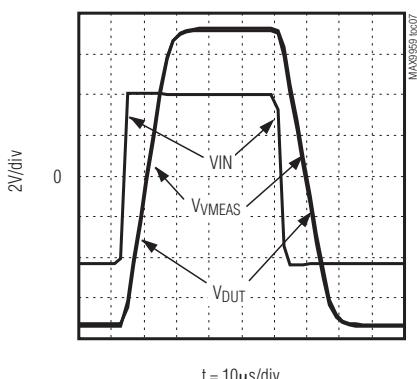

TRANSIENT RESPONSE

FVMI MODE, RANGE C

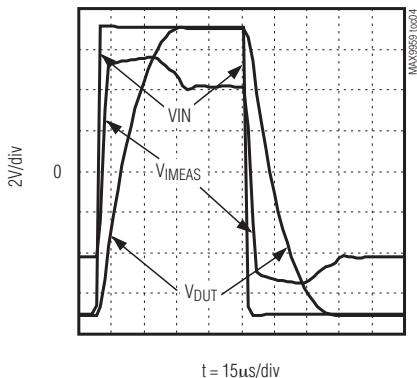

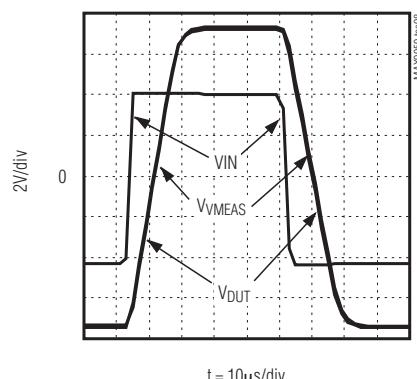

TRANSIENT RESPONSE

FVMI MODE, RANGE D

TRANSIENT RESPONSE

FVMV MODE, RANGE C

TRANSIENT RESPONSE

FIMV MODE, RANGE A

TRANSIENT RESPONSE

FIMV MODE, RANGE B

TRANSIENT RESPONSE

FIMV MODE, RANGE C

TRANSIENT RESPONSE

FIMV MODE, RANGE D

# 25Vスパン、800mAデバイス電源(DPS)

## 標準動作特性(続き)

( $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

# 25Vスパン、800mAデバイス電源(DPS)

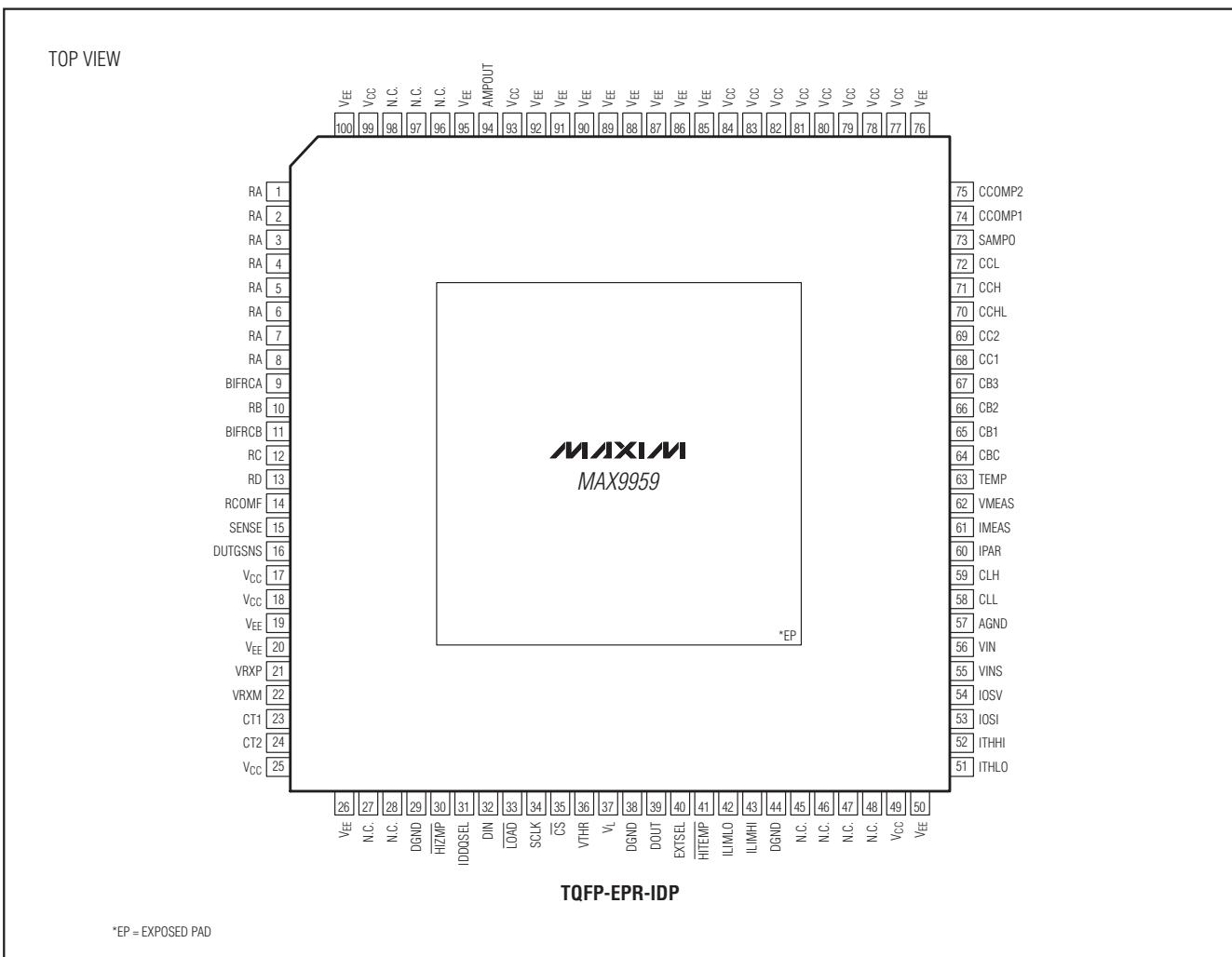

## 端子説明

| 端子                                    | 名称      | 機能                                                                              |

|---------------------------------------|---------|---------------------------------------------------------------------------------|

| 1–8                                   | RA      | 範囲Aの出力。範囲設定抵抗に互いに接続します。                                                         |

| 9                                     | BIFRCA  | 正電流検出アンプ入力。範囲Aで使用され、範囲設定抵抗にケルビン接続します。                                           |

| 10                                    | RB      | 範囲Bの出力。範囲設定抵抗に接続します。                                                            |

| 11                                    | BIFRCB  | 正電流検出アンプ入力。範囲Bで使用され、範囲設定抵抗にケルビン接続します。                                           |

| 12                                    | RC      | 範囲Cの出力。範囲設定抵抗に接続します。                                                            |

| 13                                    | RD      | 範囲Dの出力。範囲設定抵抗に接続します。                                                            |

| 14                                    | RCOMF   | 検出抵抗のケルビン接続。DUTに接続される検出抵抗用のケルビン接続。RCOMFは、電流検出用のフィードバックポイントです。                   |

| 15                                    | SENSE   | 検出入力。DUTへのケルビン接続。FVMIのフィードバック信号とFIMVの測定信号を供給します。                                |

| 16                                    | DUTGSNS | DUTのグランド検出。電圧印加モードでAGNDとDUTGND間のエラーを検出し、出力電圧を調整して、DUTGNDに対してDUTでの任意の電圧降下を実現します。 |

| 17, 18, 25, 49,<br>77–84, 93, 99      | VCC     | 正アナログ電源                                                                         |

| 19, 20, 26, 50, 76,<br>85–92, 95, 100 | VEE     | 負アナログ電源                                                                         |

| 21                                    | VRXP    | 正電流検出アンプ入力。外部範囲で使用され、範囲設定抵抗にケルビン接続します。                                          |

| 22                                    | VRXM    | 負電流検出アンプ入力。外部範囲で使用され、範囲設定抵抗にケルビン接続します。                                          |

| 23                                    | CT1     | 範囲変更グリッチ制御コンデンサ接続部。オプションのコンデンサをCT1とDGNDの間に接続します。                                |

| 24                                    | CT2     | 範囲変更グリッチ制御コンデンサ接続部。オプションのコンデンサをCT2とDGNDの間に接続します。                                |

| 27, 28, 45–48,<br>96, 97, 98          | N.C.    | 接続なし。これらの端子とは接続しません。                                                            |

| 29, 38, 44                            | DGND    | デジタルグランド                                                                        |

| 30                                    | HIZMP   | ハイインピーダンス制御入力。この端子で電流および電圧測定出力をハイインピーダンス状態にします。                                 |

| 31                                    | IDDQSEL | IDDQテストの選択。FVモードでは、設定した電流範囲と最小電流範囲の範囲Dを切り替えます。                                  |

| 32                                    | DIN     | データ入力。シリアルインタフェースのデータ入力                                                         |

| 33                                    | LOAD    | データロード入力。 $\overline{\text{LOAD}}$ の立下りエッジで、データを入力レジスタからDPSのレジスタに転送します。         |

| 34                                    | SCLK    | シリアルクロック入力。シリアルインタフェースクロック                                                      |

| 35                                    | CS      | チップ選択入力                                                                         |

| 36                                    | VTHR    | スレッショルド電圧入力。全デジタル入力の入力ロジックスレッショルドレベルを設定します。未接続の場合は、デフォルトで $V_L$ の1/2になります。      |

| 37                                    | $V_L$   | ロジック電源                                                                          |

# 25Vスパン、800mAデバイス電源(DPS)

## 端子説明(続き)

| 端子 | 名称     | 機能                                                                                                     |

|----|--------|--------------------------------------------------------------------------------------------------------|

| 39 | DOUT   | データ出力。シリアルインターフェースのデータ出力                                                                               |

| 40 | EXTSEL | 外部選択出力。外部範囲を選択します。                                                                                     |

| 41 | HITEMP | 高温インジケータ出力。ダイ温度が指定した安全動作温度を上回ると、オープンコレクタ出力はローになります。                                                    |

| 42 | ILIMLO | 下限電流制限出力。検出された電流が下限スレッショルド電流設定値ITHLOを下回ると、オープンコレクタ出力はハイインピーダンスになります。                                   |

| 43 | ILIMHI | 上限電流制限出力。検出された電流が上限スレッショルド電流設定値ITHHIを上回ると、オープンコレクタ出力はハイインピーダンスになります。                                   |

| 51 | ITHLO  | 下限電流制限入力。検出電流コンパレータの下限スレッショルドを設定する電圧入力                                                                 |

| 52 | ITHHI  | 上限電流制限入力。検出電流コンパレータの上限スレッショルドを設定する電圧入力                                                                 |

| 53 | IOSI   | 電流検出オフセット電圧入力。FIまたはMIモードにおける電流検出アンプのオフセット電圧を設定する電圧入力                                                   |

| 54 | IOSV   | オフセット電圧測定入力。電圧測定アンプのオフセット電圧を設定する電圧入力                                                                   |

| 55 | VINS   | 印加電流入力。FIスレーブモードにおける印加電流を設定する電圧入力                                                                      |

| 56 | VIN    | 印加電流/電圧入力。FIモードにおける印加電流、またはFVモードにおける印加電圧を設定する電圧入力                                                      |

| 57 | AGND   | アナロググランド                                                                                               |

| 58 | CLL    | コンプライアンス下限入力。下側の電圧/電流コンプライアンスを設定する電圧入力                                                                 |

| 59 | CLH    | コンプライアンス上限入力。上側の電圧/電流コンプライアンスを設定する電圧入力                                                                 |

| 60 | IPAR   | 電流制御比例電圧出力。IPARは、DUT電流に比例する電圧を出力します。これを使って他の並列DPSをスレーブ接続し、出力電流を増大します。                                  |

| 61 | IMEAS  | 電流制御比例電圧出力。IMEASは、DUT電流に比例する電圧を出力します。HIZMPがローにされると、ハイインピーダンスになります。                                     |

| 62 | VMEAS  | 電圧制御比例電圧出力。VMEASは、SENSEにおける電圧の1倍、1/2倍、または1/6倍に相当する電圧を出力します。HIZMPがローに強制されると、ハイインピーダンスになります。             |

| 63 | TEMP   | 温度モニタ出力。TEMPは、10mV/Kのダイ温度に比例する電圧を出力します。                                                                |

| 64 | CBC    | CBの共通接続部。バイパスコンテンサ接続部CB1、CB2、およびCB3の共通ポイント                                                             |

| 65 | CB1    | バイパスコンテンサ1。補償コンテンサ1の接続部                                                                                |

| 66 | CB2    | バイパスコンテンサ2。補償コンテンサ2の接続部                                                                                |

| 67 | CB3    | バイパスコンテンサ3。補償コンテンサ3の接続部                                                                                |

| 68 | CC1    | メイン補償コンテンサ。補償コンテンサの接続部1                                                                                |

| 69 | CC2    | メイン補償コンテンサ。補償コンテンサの接続部2                                                                                |

| 70 | CCHL   | クランプ補償コンテンサの共通接続部。CCLおよびCCHの共通接続部                                                                      |

| 71 | CCH    | 上側クランプ補償コンテンサ。上側電圧クランプ補償コンテンサ接続部                                                                       |

| 72 | CCL    | 下側クランプ補償コンテンサ。下側電圧クランプ補償コンテンサ接続部                                                                       |

| 73 | SAMPO  | リード補償コンテンサの共通接続部。CCOMP1およびCCOMP2の共通接続部                                                                 |

| 74 | CCOMP1 | 補償コンテンサ1。リード補償コンテンサ1の接続部                                                                               |

| 75 | CCOMP2 | 補償コンテンサ2。リード補償コンテンサ2の接続部                                                                               |

| 94 | AMPOUT | メインアンプ出力。外部範囲モード時に外付けバッファを駆動します。                                                                       |

| —  | EP     | エクスポートドパッド。 $V_{EE}$ に内部接続されています。放熱特性を最大限に高めるために大きめの $V_{EE}$ 電源プレーンまたはヒートシンクに接続してください。電気的な接続点ではありません。 |

# 25Vスパン、800mAデバイス電源(DPS)

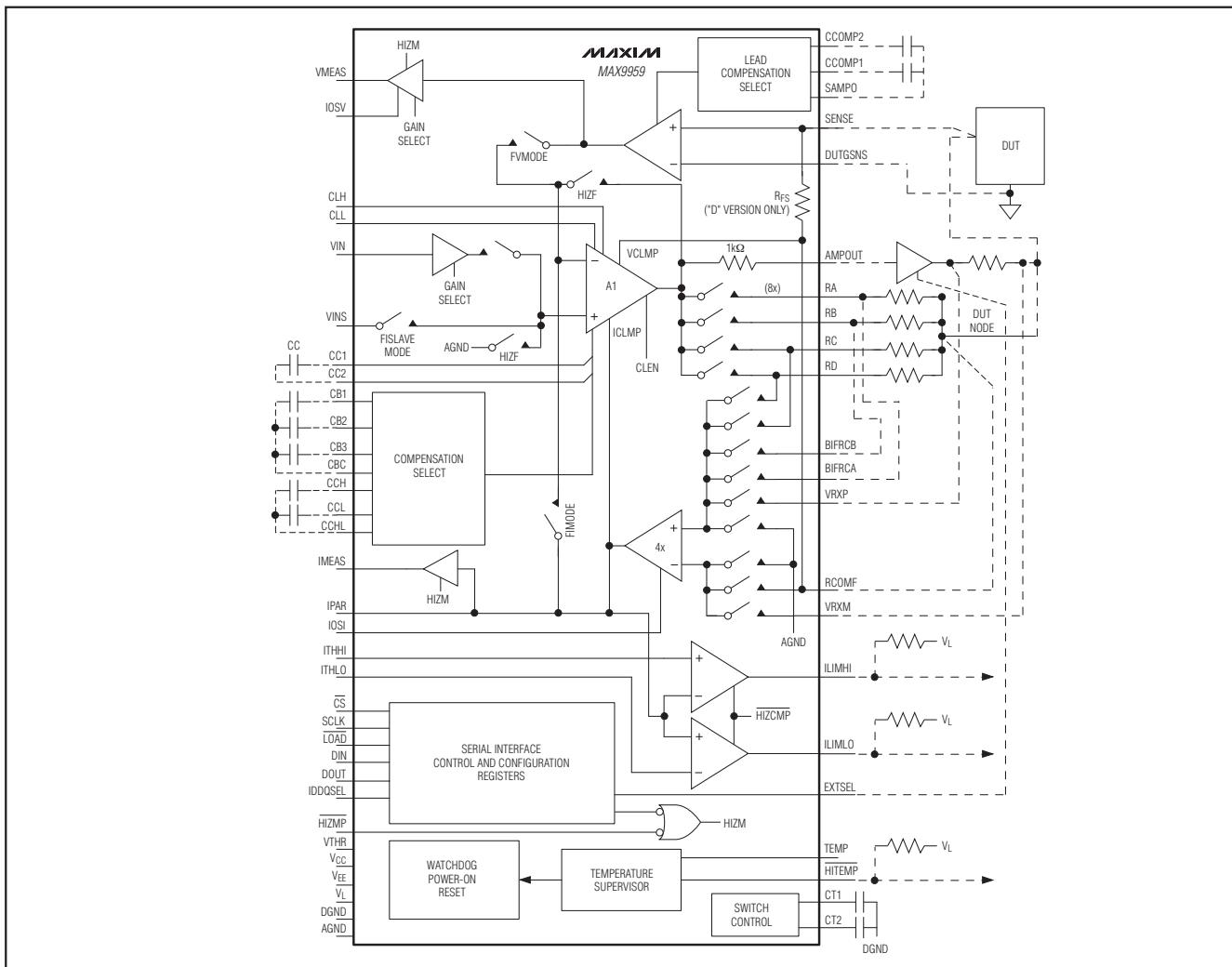

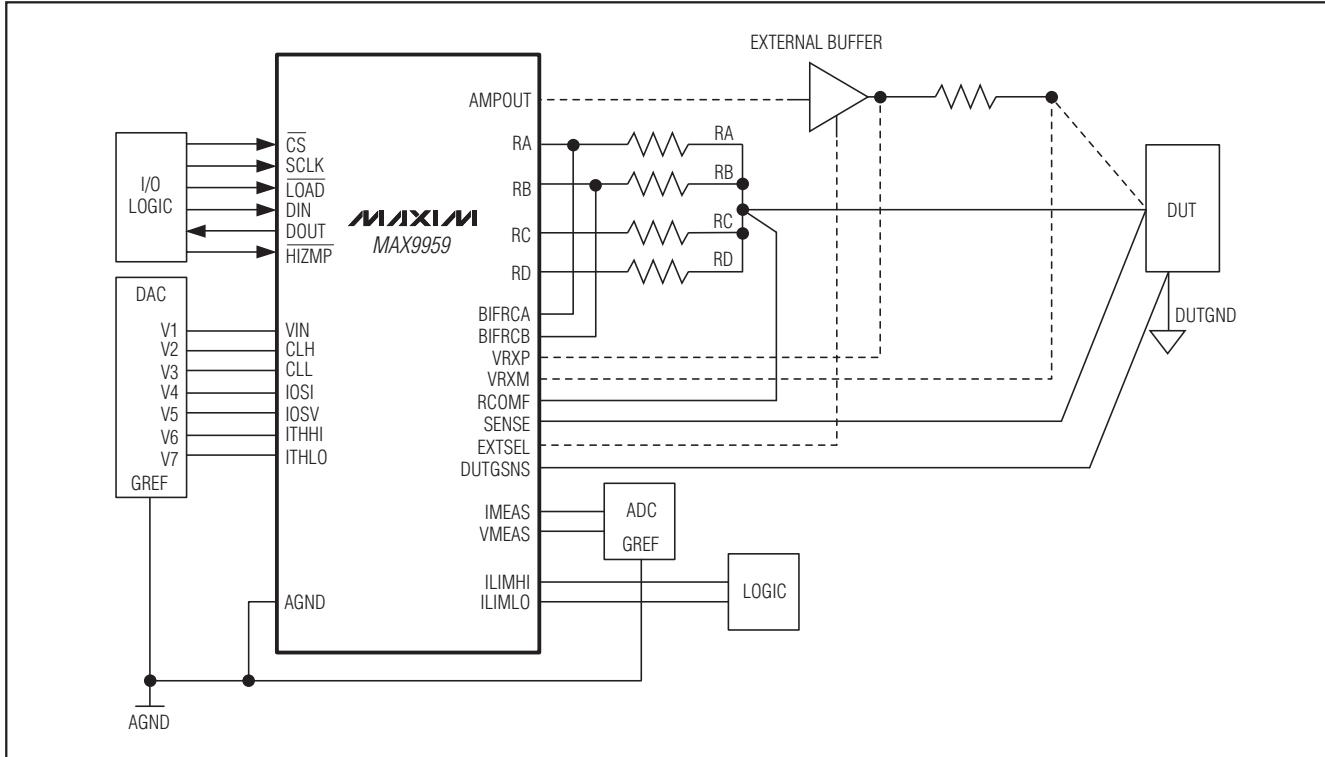

図1. ファンクションダイアグラム

## 詳細

デバイス電源(DPS)のMAX9959は、負荷電流が2つの設定制限値の間にある場合は電圧源になり、設定電流制限値に達した場合は高精度の電流ソース/シンクに安全に遷移します。この電源は、出力電圧、最大電圧(電流)および最低(最小の正または最大の負)電圧(電流)を個別に設定可能な電圧制御入力を備え、最大±800mAの電流で25Vの範囲にわたって電圧をソースすることができます。±200mA以下の電流の場合は、MAX9959は全4象限の動作を行います。これより大きい電流のソース/シンク用に外付けバッファの追加をサポートし、複数のMAX9959を共有負荷に並列接続することが可能なため、より柔軟に総電流能力を増大することができます。さらに、出力は、外部設定の制限値に負および正出力電圧/電流を制限する個別に調整可能なクランプを2つ備えています。このデバイスは、電圧/電流測定出力、Go/No-Goテスト用のウインドウコンパレータ、温度

モニタ、高温警告フラグ、および高温シャットダウンを備えています。

MAX9959Dは、RCOMFとSENSEの間に300kΩの検出抵抗R<sub>F5</sub>を内蔵しています。MAX9959Fはこの検出抵抗を内蔵していません。

## アナログ信号の極性

電圧印加モードでは出力電圧(図1「ファンクションダイアグラム」のSENSE/RCOMF)は入力制御電圧に比例し、シリアルインターフェースを通じて制御される3つの+/-利得設定値のいずれか1つを選択して出力電圧を設定します。

電流印加モードでは、出力電流は入力制御電圧に比例し、次式に従います。

$$I_{OUT} = \frac{V_{IN}}{4R_{SENSE}}$$

正電流は、DPSのMAX9959からの電流フローとして定義されます。

ハイインピーダンスマードでは、出力RA、RB、RC、およびRDはハイインピーダンスになります。

## 電流検出アンプオフセット

### 電圧入力

電流検出アンプは、図1のRA、RB、RC、およびRDに接続された出力抵抗の電圧を監視します。電流検出オフセット電圧入力IOSIは、電流検出アンプにオフセットをもたらします。IOSIがAGNDに対してゼロの場合は、+/-のフルスケール出力電流に対応する電流検出アンプの標準の出力電圧範囲は-4V～+4Vです。IOSIに印加された電圧は、この出力電圧にそのまま加えられます。例えば、+4VがIOSIに印加された場合は、+/-フルスケール電流に対応する電圧範囲は電源レイルが許可する範囲内で0V～+8Vになります。

## 電圧検出測定アンプオフセット

### 電圧入力

電圧検出測定アンプは、MAX9959の出力電圧を監視します。測定オフセット電圧入力IOSVは、電圧測定アンプにオフセットをもたらします。IOSVに印加された電圧は、この出力電圧にそのまま加えられます。

## 外部モードのサポート

MAX9959は、デバイスが供給可能な最大範囲を上回る(または最小電流範囲を下回る)電流範囲を供給する外付けアンプを駆動する回路を内蔵しています。電圧出力AMPOUTが外付けアンプの入力に供給されると、デジタル出力EXTSELはハイになり、外付けアンプを作動させます。フィードバック入力VRXPおよびVRXMは、外付けアンプの電流検出抵抗の両端に接続されています。図1に示すように接続されたとして、外付けアンプが非選択時(EXTSEL = ロー)の場合には、その出力はハイインピーダンスでなければなりません。

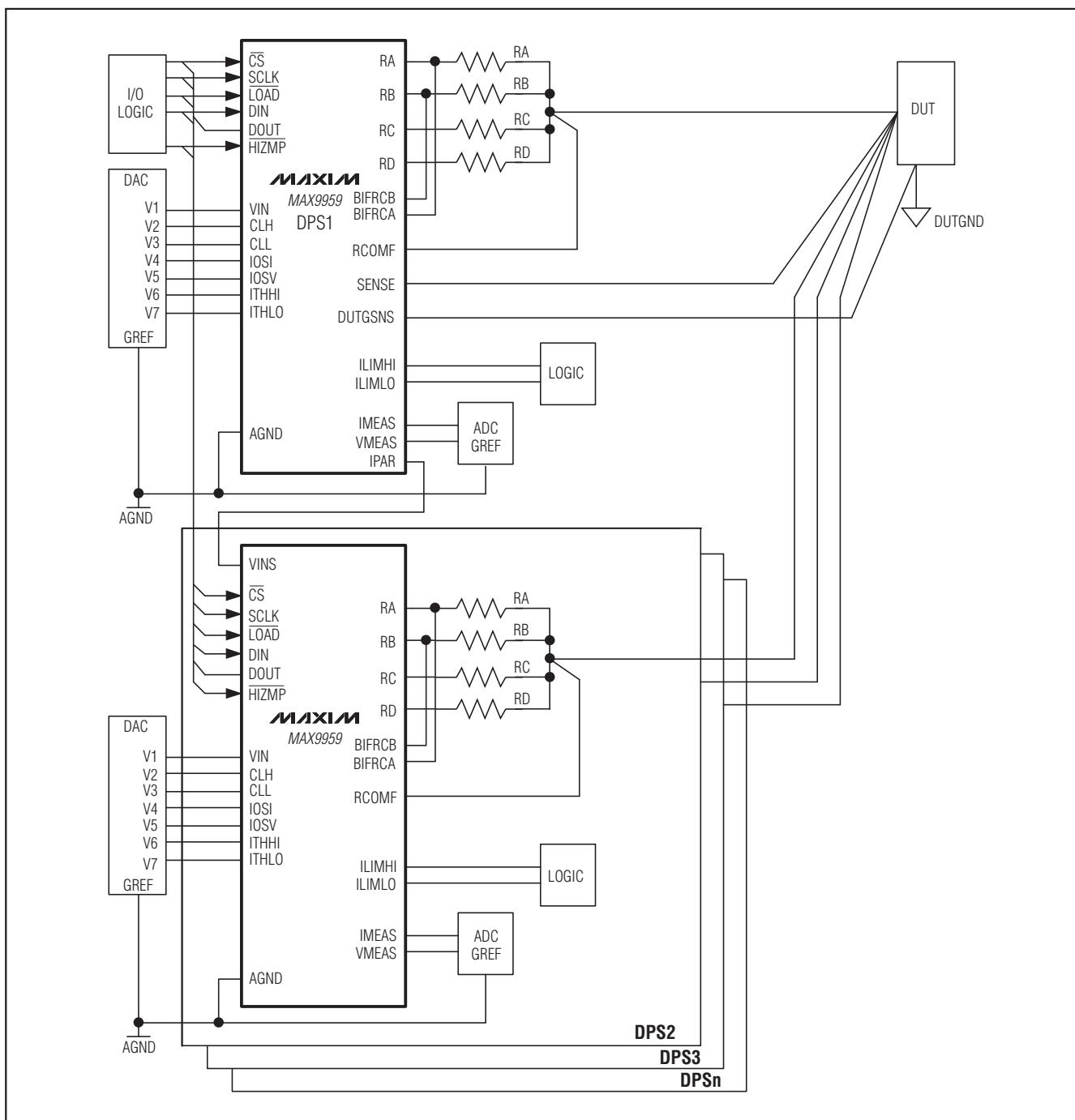

## 並列DPS動作

MAX9959は複数のデバイスを並列接続して、利用可能なDUT駆動電流を増大させることができます。DPSのうち1つはマスター構成(FVモード)とする必要があり、並列デバイスはスレーブ構成(FIスレーブモード)とする必要があります。マスターとスレーブの接続はIPAR出力とVINS入力を利用します。IPARはDUT電流に比例する電圧を出力し、VINSは比例する印加電流/電圧入力を提供します。MAX9959は最大16個まで並列接続することができます。

## 電圧クランプ

FIモード時に、プログラマブルな内蔵電圧クランプは出力電圧を設定値に制限します。入力CLHおよびCLLを使って、クランプ電圧制限値を設定します。クランプは最大±800mAを処理し、SENSEの電圧と無関係にRCOMFの電圧によってトリガれます。シリアル制御ワード内のクランプイネーブルビットCLENによって、電圧クランプをイネーブルします。

## 電流制限

プログラマブルおよびデフォルトの電流制限をFIおよびFVモードにおいて出力で利用することができます。プログラマブルな電流コンプライアンスがイネーブルの場合は、DPS出力電流は電流範囲ごとに設定された設定値に制限されます。電流制限がディセーブルされていると、DPS出力電流は、範囲B、C、およびDに対して選択された電流範囲のデフォルト値、147% FSR (typ)に制限されます。FIおよびFV状態で範囲Aにおいては、DPS出力電流は138% FSR (typ)に制限されます。それぞれ選択された範囲内にある電流の場合は、FV出力は定電圧源として動作します。デフォルトまたは設定電流コンプライアンス制限値に達した場合は、DPSは定電流モードに遷移します。

## 電流制限フラグ

MAX9959は、ユーザ設定の制限値内で電流をフラグ設定することができます。これによって、実稼働環境において迅速なGo/No-Goテストが可能になります。ウインドウコンパレータは負荷電流を連続的に監視し、負荷電流を入力ITHHIおよびITHLOと比較します。コンパレータ出力はオープンコレクタであり、シリアルインターフェースを通じてハイインピーダンスにすることができます。

## 測定アンプハイインピーダンスマード

測定出力VMEASおよびIMEASをロジック入力HIZMPまたはシリアルインタフェースビットHIZMSを使って、ハイインピーダンス状態にすることができます。このため、他のDPS測定出力によって測定出力をバス状にすることができます。

## グランドおよびDUTグランド検出

2つのグランド接続、AGND (アナロググランド)およびDGND (デジタルグランド)はともに局所的なグランドです。これらのグランドをプリント基板(PCB)上で互いに接続します。DUTのグランド検出入力DUTGSNSによって、電圧印加モードでDUTに関する検出が可能になります。

# 25Vスパン、800mAデバイス電源(DPS)

## 短絡保護

RA、RB、RC、RD、AMPOUT、およびSENSEは、各電圧間(電源レールも含む)の短絡に対する耐性を備えています。

## 温度センサおよび温度過昇保護

MAX9959は、TEMPにおいて $10\text{mV/K}$ (または $10\text{mV/}^{\circ}\text{C}$ )のダイ温度に比例する電圧を出力し、公称出力電圧は $343\text{K}$ ( $+70^{\circ}\text{C}$ )で $3.43\text{V}$ です。ダイ温度が $+120^{\circ}\text{C}$ ～ $+140^{\circ}\text{C}$ の範囲に入ると、オープンコレクタ出力HITEMPはローになります。ダイ温度が $+140^{\circ}\text{C}$ を超えると、温度センサはパワーオンリセットを発行し、DPSをハイインピーダンス状態に移行させます。温度で始動したリセット後に温度が低下しても、DPSは元の動作状態に復帰しません。再設定が必要です。

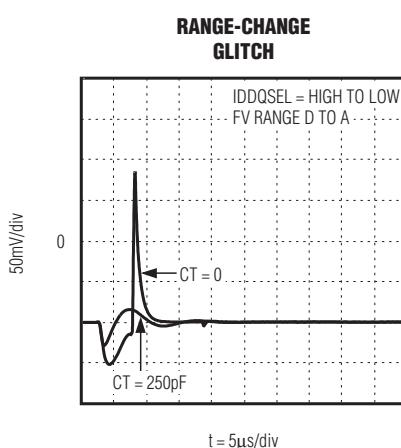

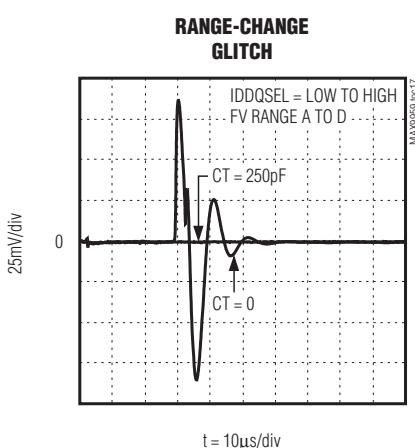

## モードおよび範囲変更トランジエント

MAX9959ではグリッヂを最小化する対策として、出力グリッヂを抑制する内蔵クランプとマイクビフォアブレークスイッチングを採用しています。範囲変更の間に発生するグリッヂを最小限に抑制するために、隣接する範囲(RAからRB、RDからRCなど)間で変更します。進行中の範囲変更動作が完了するまで、別の範囲に切り替えないでください。マイクビフォアブレーク方式のほかに、接続部CT1およびCT2が、範囲変更スイッチに対するゲート駆動のエッジレートを制御するオプションのコンデンサ用に用意されています。 $150\text{pF}$ の2個のコンデンサはそれぞれ、グリッヂ制御時間と範囲変更遷移時間との間で適度なバランスを実現します。

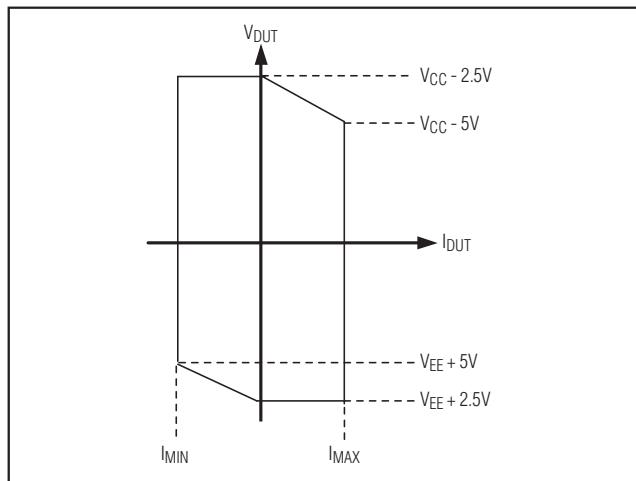

## DUT電圧振幅 対 DUT電流/電源電圧

MAX9959が供給可能なDUTの電圧は、以下の2つの主要要素と2つのその他要素によって制限されます。

- 1) アンプや他の内蔵回路に必要な各電源レールから $2.5\text{V}$ のオーバヘッド

- 2) 検出抵抗と検出抵抗に直列な内蔵回路の電圧降下。最大電流では、これらを合わせた電圧降下は $2.5\text{V}$ であり、抵抗では $1\text{V}$ 、スイッチでは $1.5\text{V}$ です。オーバヘッド要件とともに、この電圧が全電圧ではありません。これら2つの影響が重複しています。図2を参照してください。

- 3) システム電源電圧の変動

- 4) 被測定物のグランド電位とAGND間の変動

項目3と項目4の影響を無視した場合のDPSの出力能力が図2に示されています。

図2. 出力スイング

図2は、DUT電流がゼロの場合、DUT電圧は( $V_{EE} + 2.5\text{V}$ )から( $V_{CC} - 2.5\text{V}$ )にスイングすることを示しています。正のDUT電流の場合は、最大電圧は、最大電流において( $V_{CC} - 5\text{V}$ )に達するまで直線的に下降します。同様に負のDUT電流の場合は、負の電圧振幅は、( $V_{EE} + 5\text{V}$ )に達するまで直線的に減少します。

DPSが $\pm 200\text{mA}$ 以上の出力電流を供給している場合は、DPSの損失電力はパッケージの電力制限値以下に制限する必要があります([Absolute Maximum Ratings (絶対最大定格)]および[Note 2(注2)]を参照)。例えば、DPSが範囲Aで $\pm 800\text{mA}$ を供給している場合は、 $V_{CC}$ 電源は $+12\text{V}$ を、 $V_{EE}$ は $-12\text{V}$ を超えないようにしてください。DPSが電流をソースしている場合は、DUTのノードをゼロボルト以下に駆動しないでください。DPSが電流をシンクしている場合は、DUTのノードをゼロボルト以上に駆動しないでください(2象限動作)。 $\pm 800\text{mA}$ 以下で動作する場合は、DPSの消費電力に応じて4象限動作が可能な場合があります。消費電力については、電源電圧の変動と、被測定物のグランドおよびDPS AGND間の電位差を考慮する必要があります(上記の項目3および4)。

最大出力電圧範囲は電源電圧に比例するため、電源電圧が公称値から低下すると比例して範囲が縮小します。また最大出力電圧範囲は、DUTのグランドとアナロググランド間( $DUTGSNS - AGND$ )の電位差によっても縮小します。なお、これらの制限内で印加DUT電圧は、DUTのグランドに入力制御電圧を加えた値に等しくなります。同様に、電圧測定時には測定電圧はDUT電圧とDUTグランド間の電位差に等しくなります。

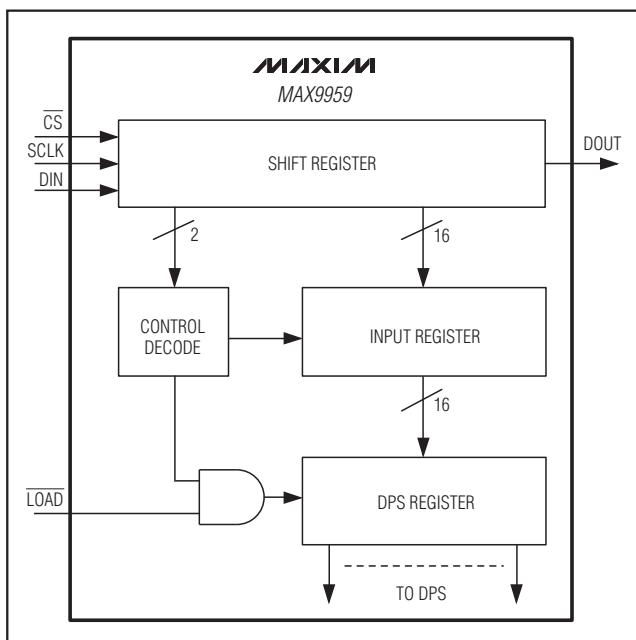

## 設定および制御

MAX9959の設定はシリアルインターフェースと専用のロジック制御入力HIZMP、LOAD、およびIDQSELを通じて行われます。

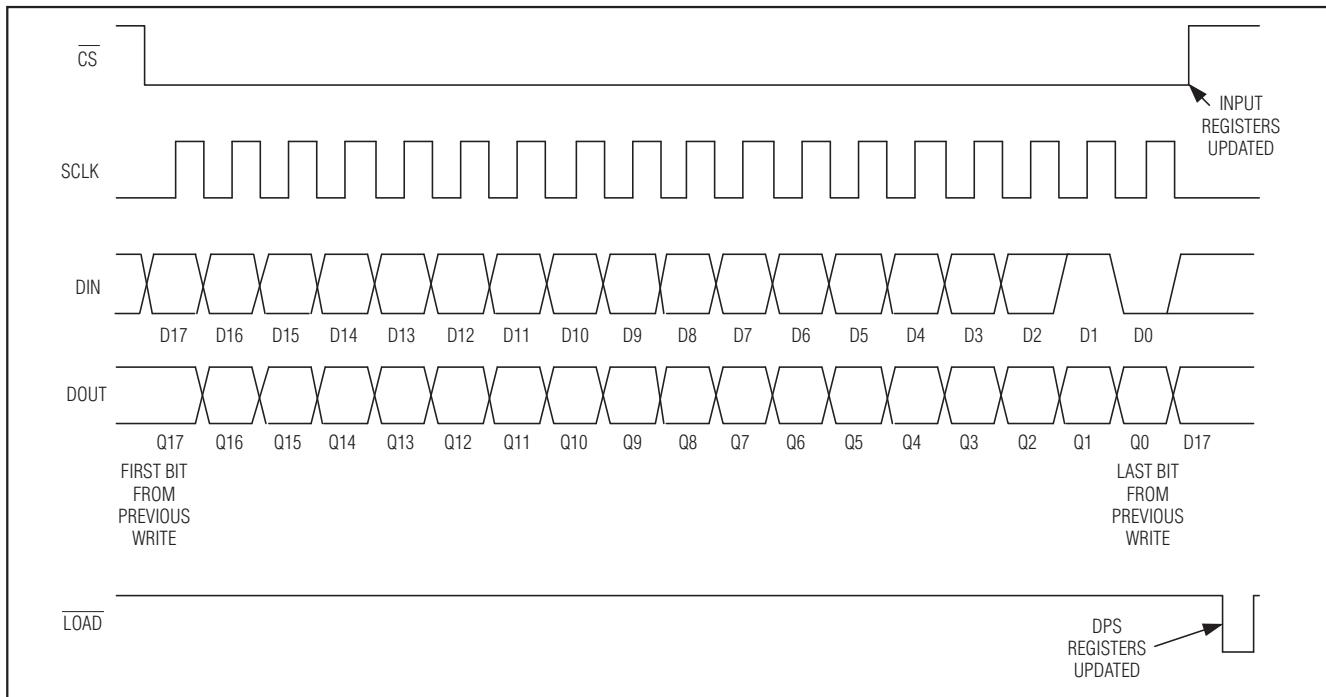

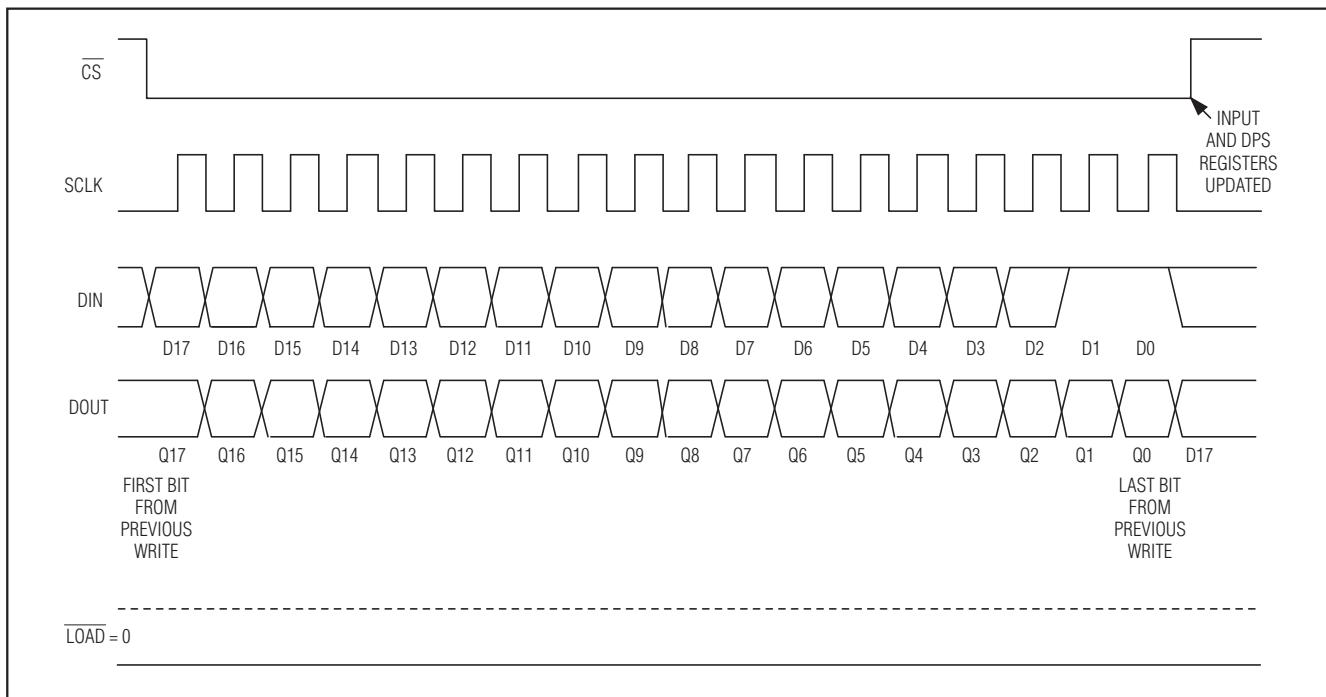

シリアルインターフェースは、シフトレジスタ、入力レジスタ、およびDPSレジスタを備えています(図3)。シリアルデータは、データがDPSレジスタに達するまでDPSにいかに影響を与えません。DPSレジスタへのデータフローは、2ビットの制御ビット(A0およびC0)およびロジック入力LOADを通じて制御されます。LOADによって、データは入力レジスタからDPSレジスタに非同期で転送されます。データが入力レジスタにラッチされている時にLOADがローに維持されると、データはDPSレジスタにいかに(透過的に)転送されます。これによって、シリアルポートのデータ通信の終了と同期するか、またはシリアルポート通信と非同期でDPSの状態を変更することができます。LOADを通じた非同期更新によって、デイジーチェーン接続された複数のDPSデバイスの同時更新が容易になります。

### DPSデータ制御ビット

18ビットワードによってMAX9959を設定します。表1は、18ビット制御ワード構造を概説しています。

### シリアルインターフェースデータフロー制御ビット

ビット0および1(C0およびA0)は、シフトレジスタから入力/DPSレジスタへのデータ転送の有無と方法を指定します。CSがハイになると、表2に示される指定アクションが実行されます(図5および6)。

図3. DPSシリアルポートブロックダイアグラム

A0 = C0 = 0 (NOP)の場合は、モードや動作を変更せずに、データはシフトレジスタを経由してDOUTに転送されます。これが役立つのは、デバイスをデイジーチェーン接続し、デバイスの運用データの一部や全部を変更せずに、運用データを数々のデバイスを経由して特定デバイスに転送する場合です。デイジーチェーン接続された複数のデバイスを同時に更新するには、A0 = 1およびC0 = 0で更新対象のデバイスの入力レジスタをロードし、CSがハイになった後にLOADを作動させます(図5)。また、CSがハイの間にLOADがローに維持されている場合は、入力レジスタにラッチされたデータはC0の状態とは無関係にDPSレジスタにラッチされます。

表1. データ制御ビットおよびビット順序

| DATA BIT | NAME   | FUNCTION                           |

|----------|--------|------------------------------------|

| 17       | FMODE  | Mode Select                        |

| 16       | G2     | Gain and Polarity Select           |

| 15       | G1     |                                    |

| 14       | G0     |                                    |

| 13       | RS2    |                                    |

| 12       | RS1    | Range Select                       |

| 11       | RS0    |                                    |

| 10       | CLEN   | Clamp Enable                       |

| 9        | RESERV | Reserved. Set this bit to zero.    |

| 8        | HIZFRC | Force High-Impedance Select        |

| 7        | HIZMS  | Measure High-Impedance Select      |

| 6        | HIZCMP | Comparator High-Impedance Select   |

| 5        | LCOMP1 | Compensation Select                |

| 4        | LCOMPO |                                    |

| 3        | BCOMP1 |                                    |

| 2        | BCOMP0 |                                    |

| 1        | A0     | Serial Interface Data Flow Control |

| 0        | C0     |                                    |

表2. シリアルインターフェースデータフロー制御ビット

| DATA BITS | OPERATION |                                                          |

|-----------|-----------|----------------------------------------------------------|

|           | A0 (D1)   | C0 (D0)                                                  |

| 0         | 0         | NOP: Input and DPS registers remain unchanged            |

| 0         | 1         | Load DPS register from input register                    |

| 1         | 0         | Load input register from shift register                  |

| 1         | 1         | Load input register and DPS register from shift register |

# 25Vスパン、800mAデバイス電源(DPS)

## チップの選択による「クイックロード」

MAX9959の標準動作中に入力レジスタからDPSレジスタにデータをラッチするには、付加的なコマンドやLOADを使用する必要があります。もう1つの「近道」はCSをローにし、最低限のCSのローバルス幅規格を満たし、同時クロック動作を伴わずにCSをハイに戻すことです。入力レジスタ内のデータは、CSの立上りエッジでDPSレジスタにラッチされます。

## プログラマブルなアナログモード

### 電流範囲の選択

制御ワード(RS0、RS1、およびRS2)のビットD11～D13は、FI(電流印加)モードまたはMI(電流測定)モードのいずれかのフルスケール電流範囲を制御します。電流モニタ抵抗の公称値および電流範囲を表3に示しています。

**表3. 範囲選択ビットおよび検出抵抗公称値**

| DATA BITS |           |           | RANGE    | MAXIMUM CURRENT | NOMINAL SENSE RESISTOR VALUE (Ω) |

|-----------|-----------|-----------|----------|-----------------|----------------------------------|

| RS2 (D13) | RS1 (D12) | RS0 (D11) |          |                 |                                  |

| 0         | 0         | 0         | D        | ±200μA          | 5000                             |

| 0         | 0         | 1         | C        | ±2mA            | 500                              |

| 0         | 1         | 0         | B        | ±20mA           | 50                               |

| 0         | 1         | 1         | A        | ±800mA          | 1.25                             |

| 1         | X         | X         | External | —               | —                                |

X = 任意

### VINおよび電圧測定、可変利得アンプの選択

制御ワード(G0、G1、およびG2)のビットD14～D16は、可変利得アンプ(VGA)の利得と極性を制御します。これらのビットは測定アンプの利得も制御するため、FVMVモード時に1:1の入力から出力への電圧伝達関数が可能です。設定値は表4に詳述されています。

**表4. VGA利得および極性選択ビット**

| DATA BITS* |          |          | VIN VGA | MEASURE VOLTAGE VGA |

|------------|----------|----------|---------|---------------------|

| G2 (D16)   | G1 (D15) | G0 (D14) |         |                     |

| 0          | 0        | 0        | +1      | +1                  |

| 0          | 0        | 1        | +2      | +1/2                |

| 0          | 1        | 0        | +6      | +1/6                |

| 1          | 0        | 0        | -1      | +1                  |

| 1          | 0        | 1        | -2      | +1/2                |

| 1          | 1        | 0        | -6      | +1/6                |

\*011および111は使用されていません。

## モードの選択

制御ワード(HIZFRCおよびFMODE)のビットD8およびD17によって、表5に示すMAX9959の動作モードを選択します。FMODEによってDPSが電圧または電流を印加するかを選択します。HIZFRCは、ドライバアンプをハイインピーダンス状態にするか、またはVINSをアンプへの入力として選択するかどうかを設定します(FIスレーブモード)。

**表5. DPSモード選択ビット**

| DATA BITS   |             | DPS MODE       | AMP INPUT | OUTPUTS RA, RB, RC, AND RD |

|-------------|-------------|----------------|-----------|----------------------------|

| HIZFRC (D8) | FMODE (D17) |                |           |                            |

| 0           | 0           | High Impedance | AGND      | High Impedance             |

| 0           | 1           | FI Slave       | VINS      | Current                    |

| 1           | 0           | FV             | VIN       | Voltage                    |

| 1           | 1           | FI             | VIN       | Current                    |

FVおよびFIモードでは、IMEASおよびVMEAS出力はDUT検出電圧または電流の測定を行い、従来の電圧印加/電流測定(FVMI)モードや電流印加/電圧測定(FIMV)モードを超えた柔軟な動作モードを実現します。サポートするモードには以下があります。

FVMI： 電圧印加/電流測定

FIMV： 電流印加/電圧測定

FVMV： 電圧印加/電圧測定

FIMI： 電流印加/電流測定

FNMV： 印加なし/電圧測定

FVまたはFIモードでは、印加電圧または印加電流の制御用にVINが選択されます。FIスレーブモードでは、VINSが選択されます。このため、外部リレーを使わずにマスターDPSをスレーブに接続することができます。

## デジタルインターフェース動作

3線式SPI™/QSPI™/MICROWIRE™対応シリアルインターフェースは、MAX9959のコマンドおよび制御用に使用されます。このシリアルインターフェースは、最高20MHzまでのクロック速度で動作します。また、いくつかのロジック入力は特別機能を制御し、シリアルインターフェース制御データと連携する場合や、このデータを無効にする場合があります。

SPIおよびQSPIは、Motorola, Inc.の商標です。

MICROWIREはNational Semiconductor Corp.の商標です。

### ロジック入力および共用制御機能

測定出力ハイインピーダンス状態の制御は、HIZMSビット(D7)とロジック入力HIZMPの間で共用されます。入力シフトレジスタから2個の内部制御レジスタ、入力およびDPSまでのデータ転送動作は、制御ワードのA0/C0ビットとロジック入力LOADの間で共用されます(「設定および制御」の項を参照)。

### デジタル入力

デジタル入力のSCLK、DIN、CS、LOAD、HIZMP、およびIDQSELは、ノイズを軽減し、光アイソレータとの整合性を確保するためにヒステリシスを備えています。デジタル入力の電圧スレッショルドレベルはVTHRで設定され、VTHRが未接続状態の場合はデフォルトで $V_L$ の1/2になります。

### デジタル出力(DOUT)

入力データレジスタがいっぱいの場合は、データは先入れ先出し方式でDOUTに出力されるため、複数デバイスをデイジーチェーン接続することができます。DOUTのデータは、デイジーチェーン接続された機器当り18サイクルのクロック分の遅延を持ってDINに従います。デジタル出力は入力クロックの立下りエッジで出力されるため、デイジーチェーン接続されたデバイスは同じクロック信号を使用することができます。

### シリアルポートのタイミング

シリアルポートのタイミングは、タイミング図4、図5、および図6と、「AC Electrical Characteristics (AC電気的特性)」表のシリアルポートのタイミング特性の項に詳述されています。

図4. シリアルインタフェースのタイミング

# 25Vスパン、800mAデバイス電源(DPS)

MAX9959

図5. DPSレジスタの非同期ロード時のシリアルインタフェースタイミング

図6. DPSレジスタの同期ロード時のシリアルインタフェースタイミング

## アプリケーション情報

### エクスポートドパッド

EPは非接続または $V_{EE}$ に接続し、グランドには接続しないでください。

### リード補償コンデンサの選択

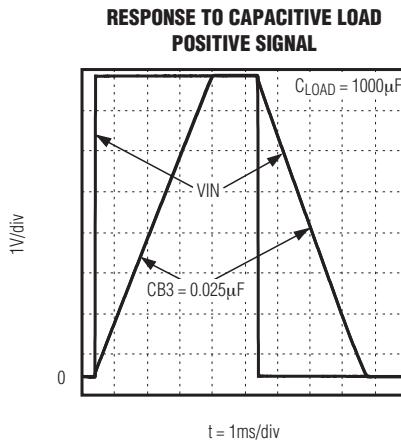

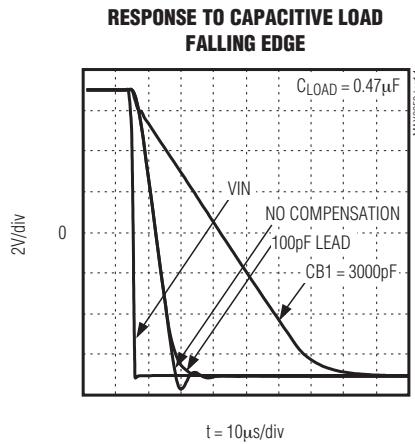

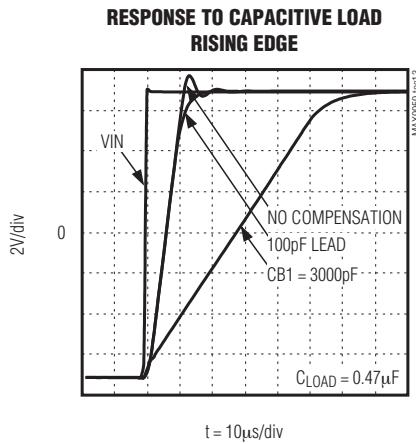

MAX9959は、大きく変動する負荷容量を駆動することができます。負荷容量が増えるに従って、DPSの出力

がオーバーシュートする傾向があります。これに対処するためにリード補償コンデンサ回路接続部が用意され、それにシリアルインターフェースを通じて制御可能な専用内蔵スイッチが装備されています(図1)。この回路は、コンデンサを組み合わせて、セトリング時間対オーバーシュートなどの特定のニーズに対応させることができます。制御ビットD5およびD4 (LCOMP1およびLCOMP0)は、表6に示すように補償コンデンサ接続を設定します。

**表6. リード補償コンデンサの選択**

| DATA BITS   |             | COMPENSATION CAPACITOR SELECT | MINIMUM CAPACITOR VALUE (pF) | MAXIMUM CAPACITOR VALUE (pF) |

|-------------|-------------|-------------------------------|------------------------------|------------------------------|

| LCOMP1 (D5) | LCOMP0 (D4) |                               |                              |                              |

| 0           | 0           | None                          | —                            | —                            |

| 0           | 1           | CCOMP1                        | 27                           | 330                          |

| 1           | 0           | CCOMP2                        | 27                           | 330                          |

| 1           | 1           | CCOMP1 and CCOMP2             | 27 each                      | 330 each                     |

### バイパス補償コンデンサの選択

リード補償のほかに、DPSはバイパス補償も実装しています、このバイパス補償は重い容量性負荷の状態時に必要になる場合があります。FVまたはFIに選択されたモードに応じて、制御ビットD3およびD2 (BCOMP1およびBCOMP0)は各種コンデンサを選択します。

FIモードでは、表7に示されるように、3個のバイパスコンデンサ(CB1、CB2、およびCB3)のいずれか1つが選択されるか、またはどれも選択されません。表8は、各種負荷状態に対応したCB1、CB2、およびCB3の推奨コンデンサ値を示しています。

**表7. FVモードにおけるバイパスコンデンサの選択**

| DATA BITS   |             | BYPASS CAPACITOR SELECT |

|-------------|-------------|-------------------------|

| BCOMP1 (D3) | BCOMP0 (D2) |                         |

| 0           | 0           | None                    |

| 0           | 1           | CB1                     |

| 1           | 0           | CB2                     |

| 1           | 1           | CB3                     |

**表8. CB1、CB2、およびCB3の推奨値**

| RANGE | LOAD        |             |              |               |                |                 |                  |

|-------|-------------|-------------|--------------|---------------|----------------|-----------------|------------------|

|       | $\geq 1nF$  | $\geq 10nF$ | $\geq 100nF$ | $\geq 1\mu F$ | $\geq 10\mu F$ | $\geq 100\mu F$ | $\leq 1000\mu F$ |

| A     | —           | —           | CB1 = 2.7nF  | CB1 = 2.7nF   | CB2 = 10nF     | CB3 = 22nF      | CB3 = 22nF       |

| B     | —           | —           | CB1 = 2.7nF  | CB1 = 2.7nF   | CB2 = 10nF     | CB3 = 22nF      | —                |

| C     | —           | CB1 = 2.7nF | CB1 = 2.7nF  | CB2 = 10nF    | CB3 = 22nF     | —               | —                |

| D     | CB1 = 2.7nF | CB1 = 2.7nF | CB2 = 10nF   | CB3 = 22nF    | —              | —               | —                |

FIモードでは、バイパスコンデンサ(CCH/CCL)の組合せが選択されるか、またはどのコンデンサも選択されません(表9)。表10は、各種負荷状態に対応したCCHおよびCCLの推奨コンデンサ値を示しています。これらの補償コンデンサは、重負荷駆動時に電圧クランプ回路の安定性を向上します。

**表9. FIモード電圧クランプ補償コンデンサの選択**

| DATA BITS   |             | FORCE-CURRENT MODE COMPENSATION CAPACITOR SELECT |

|-------------|-------------|--------------------------------------------------|

| BCOMP1 (D3) | BCOMP0 (D2) |                                                  |

| 0           | 0           | None                                             |

| X           | 1           | CCL/CCH                                          |

| 1           | X           | CCL/CCH                                          |

X = 任意

# 25Vスパン、800mAデバイス電源(DPS)

表10. CCHおよびCCLの推奨値(CCH = CCL)

| RANGE | LOAD                |                   |                    |                     |                     |                      |                       |                        |

|-------|---------------------|-------------------|--------------------|---------------------|---------------------|----------------------|-----------------------|------------------------|

|       | $\geq 100\text{pF}$ | $\geq 1\text{nF}$ | $\geq 10\text{nF}$ | $\geq 100\text{nF}$ | $\geq 1\mu\text{F}$ | $\geq 10\mu\text{F}$ | $\geq 100\mu\text{F}$ | $\leq 1000\mu\text{F}$ |

| A     | —                   | —                 | —                  | 4.7nF               | 4.7nF               | 4.7nF                | 4.7nF                 | 4.7nF                  |

| B     | —                   | —                 | 4.7nF              | 4.7nF               | 4.7nF               | 4.7nF                | 4.7nF                 | —                      |

| C     | —                   | 4.7nF             | 4.7nF              | 4.7nF               | 4.7nF               | 4.7nF                | —                     | —                      |

| D     | 4.7nF               | 4.7nF             | 4.7nF              | 4.7nF               | 4.7nF               | —                    | —                     | —                      |

## 測定出力ハイインピーダンス制御

HIZMS制御ビット(D7)またはデジタル入力HIZMPの2つの方法のどちらかを使って、測定出力を低リークのハイインピーダンス状態に移行します。これらの2つの制御は、表11に示すように論理的にAND接続されています。デジタル入力HIZMPによって、シリアルインターフェースを使用せずに複数のDPSの測定出力を多重化することができます。

表11. 測定出力ハイインピーダンス制御

| DATA BIT HIZMS (D7) | DIGITAL INPUT HIZMP | MEASURE OUTPUT (VMEAS, IMEAS) MODE |

|---------------------|---------------------|------------------------------------|

| 1                   | 1                   | Measure Output Enabled             |