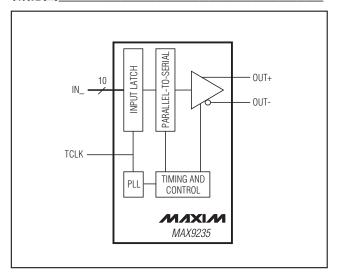

# 10ビットLVDSシリアライザ

MAX9235シリアライザは10ビット幅のパラレル LVCMOS/LVTTLデータを高速のシリアル、低電圧差動 信号(LVDS)のデータストリームに変換します。このシリ アライザはシリアル出力を受信してそれを元の10ビット 幅のパラレルデータに変換するMAX9206などのデシリ アライザと対にして使用されるのが普通です。

MAX9235はPCBトレースまたは対より線ケーブルに よって最高400Mbpsの速度でシリアルデータを伝送し ます。クロックはシリアルデータストリームの中から再 生されるため、パラレルバスの場合に存在するクロックと データ間、およびデータ間のスキューは、排除されます。 シリアライザのMAX9235は外付け部品や制御信号なし

に16MHz~40MHzのシステムクロックにロックするこ とができます。シリアライザの出力は、このデバイスが ローカルシステムクロックに完全にロックされるまでは ハイインピーダンスを維持します。

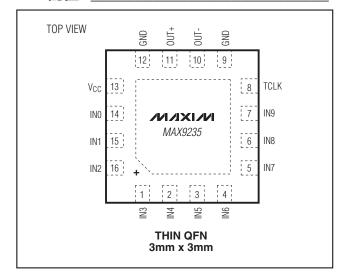

MAX9235は+3.3Vの単一電源で動作し、-40℃~ +105℃で動作が保証され16ピンのTQFN (3mm x 3mm) パッケージで提供されます。

# アプリケーション

車線逸脱警報システム リアビューカメラ 監視カメラ 製造ラインの監視

- ◆ 単方向リンク用に最適なスタンドアロンシリアライザ (SERDESと比較して)

- ◆ デシリアライザの再同期用のフレーミングビットに よってシステム割込みなしに活線挿入が可能

- ◆ ポイント間アプリケーション仕様のLVDSシリアル出力

- ◆ 広いリファレンスクロック入力範囲 16MHz~40MHz

- ◆ 31mAの低電源電流

- ◆ 10ビットパラレルLVCMOS/LVTTLインタフェース

- ♦ ペイロードデータレート:最高400Mbps

- ◆ 小型16ピンTQFN (3mm x 3mm)パッケージ

#### 型番

| PART        | PIN-        | REF CLOCK   | PKG     |  |

|-------------|-------------|-------------|---------|--|

|             | PACKAGE     | RANGE (MHz) | CODE    |  |

| MAX9235ETE+ | 16 TQFN-EP* | 16 to 40    | TI633-5 |  |

+は鉛フリーパッケージを示します。

注:このデバイスは-40℃~+105℃の温度範囲での動作が保証 されています。

\*EP =エクスポーズドパッド。

ピン配置と機能図はデータシートの最後に記載されています。

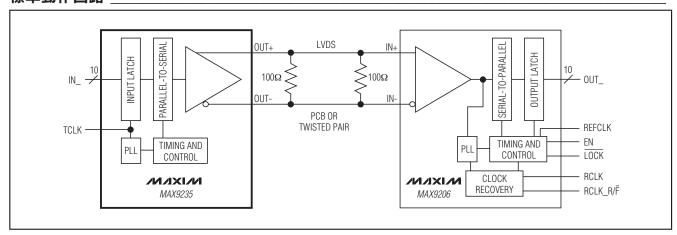

#### 標準動作回路

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +4.0V IN_, TCLK to GND0.3V to (V <sub>CC</sub> + 0.3V) | Storage Temperature Range65°C to +150°C Junction Temperature                                                                                                                         |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT+, OUT- to GND0.3V to +4.0V Output Short-Circuit Duration                         | Operating Temperature Range40°C to +105°C Lead Temperature (soldering, 10s)+300°C ESD Protection (Human Body Model, OUT+, OUT-)±8kV ESD Protection (Human Body Model, IN_, TCLK)±2kV |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 50\Omega \pm 1\%, C_L = 10 \text{pF}, T_A = -40 ^{\circ}\text{C} \text{ to } +105 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Notes 1, 2, 3)

| PARAMETER                                                        | SYMBOL           | CON                                                | MIN                                    | TYP   | MAX   | UNITS           |      |  |

|------------------------------------------------------------------|------------------|----------------------------------------------------|----------------------------------------|-------|-------|-----------------|------|--|

| LVCMOS/LVTLL LOGIC INPUTS                                        | (INO TO INS      | , EN, TCLK)                                        |                                        |       |       |                 | •    |  |

| High-Level Input Voltage                                         | V <sub>IH</sub>  |                                                    |                                        | 2.0   |       | V <sub>CC</sub> | V    |  |

| Low-Level Input Voltage                                          | VIL              |                                                    |                                        | GND   |       | 0.8             | V    |  |

| Input Current                                                    | I <sub>IN</sub>  | V <sub>IN</sub> _ = 0 or V <sub>CC</sub>           | V <sub>IN</sub> = 0 or V <sub>CC</sub> |       |       |                 | μΑ   |  |

| LVDS OUTPUTS (OUT+, OUT-)                                        |                  |                                                    |                                        | •     |       |                 |      |  |

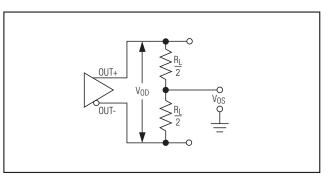

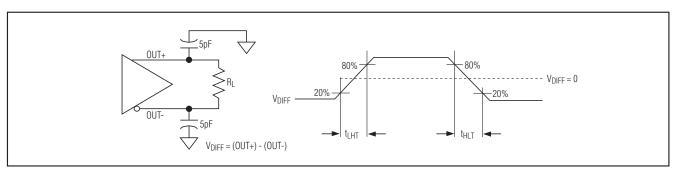

| Differential Output Voltage                                      | Von              | Figure 1                                           | $R_L = 100\Omega$                      | 600   | 735   | 950             | mV   |  |

|                                                                  | V <sub>OD</sub>  | Figure 1                                           | $R_L = 50\Omega$                       | 250   | 370   | 470             |      |  |

| Change in V <sub>OD</sub> Between<br>Complementary Output States | ΔV <sub>OD</sub> | Figure 1                                           |                                        | 1     | 35    | mV              |      |  |

| 0 0                                                              |                  | F                                                  | $R_L = 100\Omega$                      | 1.025 | 1.265 | 1.375           |      |  |

| Output Offset Voltage                                            | Vos              | Figure 1                                           | $R_L = 50\Omega$                       | 1.125 | 1.265 | 1.375           | \ \  |  |

| Change in VOS Between<br>Complementary Output States             | ΔV <sub>OS</sub> | Figure 1                                           |                                        |       | 3     | 35              | mV   |  |

| Output Short-Circuit Current                                     | los              | OUT+ or OUT- = 0,<br>IN0 to IN9 = EN = high        |                                        |       | -13   | -15             | mA   |  |

| Power-Off Output Current                                         | lox              | V <sub>CC</sub> = 0, OUT+ or OUT- = 0 or 3.6V      |                                        | -10   |       | +10             | μΑ   |  |

| POWER SUPPLY                                                     |                  |                                                    |                                        | •     |       |                 |      |  |

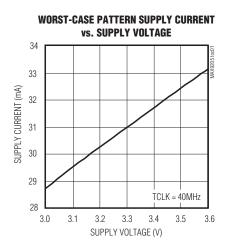

| Supply Current                                                   | Icc              | $R_L = 100\Omega$ or $50\Omega$ worst-case pattern | 16MHz                                  |       | 22    | 35              | - mA |  |

|                                                                  | 100              | (Figures 2, 4)                                     | 40MHz                                  |       | 31    | 45              | IIIA |  |

\_\_ /N/IXI/M

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 50\Omega \pm 1\%, C_L = 5 \text{pF}, T_A = -40 ^{\circ}\text{C} \text{ to } +105 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Notes 2, 4)

| PARAMETER                                 | SYMBOL                    | CONDITIONS |                  |      | MIN                        | TYP                   | MAX                         | UNITS       |  |  |

|-------------------------------------------|---------------------------|------------|------------------|------|----------------------------|-----------------------|-----------------------------|-------------|--|--|

| TRANSMIT CLOCK (TCLK) TIMING REQUIREMENTS |                           |            |                  |      |                            |                       |                             |             |  |  |

| TCLK Center Frequency                     | fTCCF                     |            |                  |      | 16                         |                       | 40                          | MHz         |  |  |

| TCLK Frequency Variation                  | TCFV                      |            |                  |      | -200                       |                       | +200                        | ppm         |  |  |

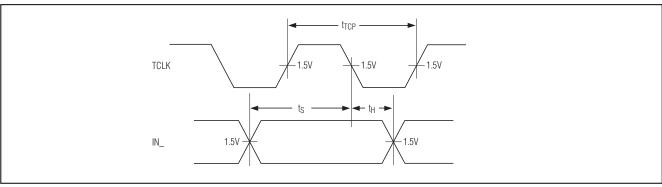

| TCLK Period                               | tTCP                      |            |                  |      | 25                         |                       | 62.5                        | ns          |  |  |

| TCLK Duty Cycle                           | TCDC                      |            |                  |      | 40                         |                       | 60                          | %           |  |  |

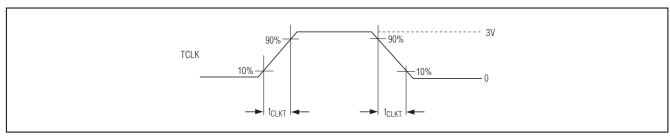

| TCLK Input Transition Time                | tCLKT                     | Figure 3   |                  |      |                            | 3                     | 6                           | ns          |  |  |

| TCLK Input Jitter                         | tJIT                      |            |                  |      |                            |                       | 150                         | ps<br>(RMS) |  |  |

| SWITCHING CHARACTERISTIC                  | SWITCHING CHARACTERISTICS |            |                  |      |                            |                       |                             |             |  |  |

| Low-to-High Transition Time               | t <del></del>             | Figure 4   | R <sub>L</sub> = | 100Ω |                            | 370                   | 500                         | ps          |  |  |

| Low-to-riigh Transition Time              | tLHT                      | rigure 4   | R <sub>L</sub> = | 50Ω  |                            | 350                   | 500                         |             |  |  |

| High-to-Low Transition Time               | thlt                      | Figure 4   | R <sub>L</sub> = | 100Ω |                            | 370                   | 500                         | ps          |  |  |

| Tilgii-to-Low Transition Tillie           | ЧLI                       | Figure 4   | R <sub>L</sub> = | 50Ω  |                            | 350                   | 500                         | μδ          |  |  |

| IN_ Setup to TCLK                         | ts                        | Figure 5   |                  |      | 1                          |                       |                             | ns          |  |  |

| IN_ Hold from TCLK                        | tH                        | Figure 5   |                  |      | 3                          |                       |                             | ns          |  |  |

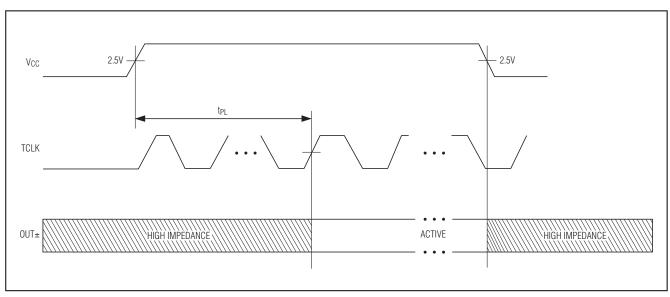

| PLL Lock Time                             | t <sub>PL</sub>           | Figure 6   |                  |      | 2048 x<br>t <sub>TCP</sub> |                       | 2049 x<br>t <sub>TCP</sub>  | ns          |  |  |

| Bus LVDS Bit Width                        | t <sub>BIT</sub>          |            |                  |      |                            | t <sub>TCP</sub> / 12 |                             | ns          |  |  |

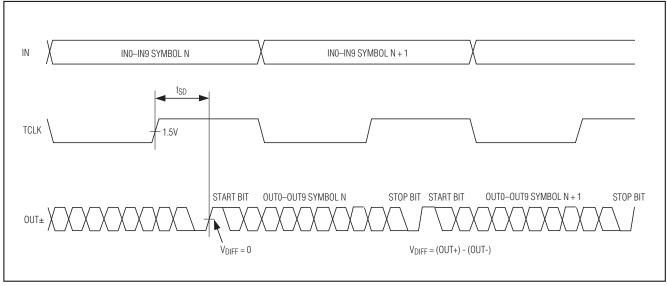

| Serializer Delay                          | tsD                       | Figure 7   |                  |      | t <sub>TCP</sub> /6        |                       | (t <sub>TCP</sub> /6)<br>+5 | ns          |  |  |

Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>OD</sub>, ΔV<sub>OD</sub>, and V<sub>OS</sub>.

**Note 2:** C<sub>L</sub> includes scope probe and test jig capacitance.

**Note 3:** Parameters 100% tested at  $T_A = +25^{\circ}$ C. Limits over operating temperature range guaranteed by design and characterization.

**Note 4:** AC parameters are guaranteed by design and characterization.

図2. ワーストケースのI<sub>CC</sub>テストパターン

図3. 入力クロック遷移時間要件

図4. 出力負荷と遷移時間

図5. データ入力のセットアップ時間とホールド時間

図6. PLLロック時間

図7. シリアライザ遅延

NIXIN

# 標準動作特性

(V<sub>CC</sub> = +3.3V, R<sub>L</sub> = 50 $\Omega$ , C<sub>L</sub> = 5pF, T<sub>A</sub> = +25°C, unless otherwise noted.)

| 端子              | 名称                        | 機能                                                                                                              |

|-----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1–7, 14, 15, 16 | IN3-IN9, IN0,<br>IN1, IN2 | LVCMOS/LVTTLデータ入力データはTCLKの立上りエッジによって10ビットラッチにロードされます。各入力は内部でグランドにプルダウンされています。                                   |

| 8               | TCLK                      | LVCMOS/LVTTLによるリファレンスクロック入力16MHz~40MHzのクロックを受け取ります。TCLKはPLLに対する周波数リファレンスを提供し、その立上りエッジで入力ラッチにパラレルデータをストローブ入力します。 |

| 9, 12           | GND                       | グランド                                                                                                            |

| 10              | OUT-                      | LVDS差動出力の反転バス                                                                                                   |

| 11              | OUT+                      | LVDS差動出力の非反転バス                                                                                                  |

| 13              | Vcc                       | 電源入力。 $0.1 \mu F$ のコンデンサと $0.001 \mu F$ のコンデンサでグランドにバイパスしてください。 $0.001 \mu F$ のコンデンサは $V_{CC}$ の近くに配置してください。    |

| _               | EP                        | エクスポーズドパッド。EPをグランドに半田付けすると、熱放散が改善されます。                                                                          |

#### 詳細

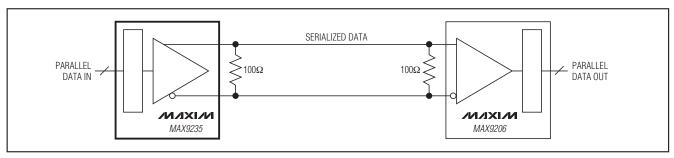

10ビットシリアライザのMAX9235は100Mbps~400Mbpsの速度で標準の対より線ペアケーブルまたはPCBトレースの差動媒体でデータを伝送します。インタフェースは単一または二重終端のポイント間とすることができます。二重終端のポイント間インタフェースはインタフェースの両端に100 $\Omega$ の終端抵抗を用いるため、結果として50 $\Omega$ の負荷となります。データ伝送を完結するためには、シリアライザにはMAX9206のようなデシリアライザが必要です。

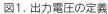

ハイ状態のスタートビットとロー状態のストップビットが内部で追加されて、10ビットのパラレルデータのフレームが構成されて、シリアルデータストリームの遷移が確実に行われます。したがつて、12個のシリアルビットが各10ビットのパラレル入力に対して伝送されます。MAX9235は16MHz~40MHzのリファレンスクロックを受け取り、192Mbps (12ビット×16MHz)~480Mbps (12ビット×40MHz)のシリアルデータレートを作り出します。入力データからは10ビットのみであるため、実際のスループットはTCLK周波数の10倍です。

データを伝送するために、シリアライザのシーケンスには2つのモードがあります。初期化モードとデータ伝送モードです。

#### 初期化モード

$V_{CC}$ が印加されたとき、出力はハイインピーダンスに保持され、内部回路は内蔵の電源オンリセット回路によってディセーブルになっています。 $V_{CC}$ が2.35Vに達すると、PLLは内部のリファレンスクロックへのロックを開始します。リファレンスクロックのTCLKはシステムから与えられます。シリアライザはTCLKの2049サイクル以内にロックされます。いったん、ロックされると、シリアライザはデータ送信の準備状態になっています。

#### データ伝送モード

初期化の後、INO~IN9の入力データはTCLK入力によって シリアライザにクロック同期入力されます。データは TCLKの立上りエッジでストローブ入力されます。

スタートビットのハイとストップビットのローによって 10ビットデータのフレームが構成され、シリアルデータ ストリームの中に埋め込まれたクロックエッジの働きを します。シリアル速度はデータと追加されたビットに TCLK周波数を乗算した値になります。例えば、TCLKが 40MHzとすると、シリアル速度は40 x 12 (10 + 2 ビット) = 480Mbpsとなります。入力データは10ビット のみであるため、ペイロード速度は40 x 10 = 400Mbps です。

#### ハイインピーダンス状態

シリアライザの出力端子(OUT+とOUT-)はV<sub>CC</sub>が最初に 印加され、PLLが内部リファレンスクロックにロック しようとしているときはハイインピーダンスのままです。 シリアライザがハイインピーダンスになると、デシリア ライザはPLLロックを喪失し、データ転送を再開する ためには位相ロックを再確立する必要があります。 これは、最低1フレームの間、すべてゼロを送信する ことで行われます。

### アプリケーション情報」

#### 電源バイパス

$V_{CC}$ を高周波用表面実装セラミック $0.1\mu$ Fおよび $0.001\mu$ Fのコンデンサを並列接続して可能な限りデバイスに近づけ、小さい値の方を $V_{CC}$ の近くに実装してバイパスしてください。

#### 差動配線と終端

インピーダンスが制御された媒体を使用し、媒体の特性インピーダンスで伝送ラインの両端で終端してください。ポイント間リンクの片端に1個の終端をすることは通常、許容することができる性能を提供します。MAX9235の出力レベルは二重終端されたポイント間のアプリケーションに対して規定されています。1個の100Ω終端では出力振幅が大きくなります。

リボンまたは単純な同軸ケーブルのような不平衡ケーブルの使用は避けてください。対より線ペアなどの並行型ケーブルは優れた品質を提供し、相殺効果のためにEMIの発生が少ない傾向があります。平衡型ケーブルはコモンモードのノイズを拾い易く、これは差動レシーバで排除されます。

反射が起こらないようにして、両差動配線を近づけて 配置してノイズをコモンモードとして結合させてくだ さい。トレースの電気長をマッチさせると、スキュー が小さくなります。スキューが過度になると、磁界の 相殺が悪化する結果となります。

差動出力信号は相互に近づけて配線し、その外部磁界を相殺させてください。差動インピーダンスに不連続が生じないように差動トレース間の距離を一定にしてください。90°の曲がりを避け、ビアを最小化してさらに不連続が生じないようにしてください。

#### トポロジ

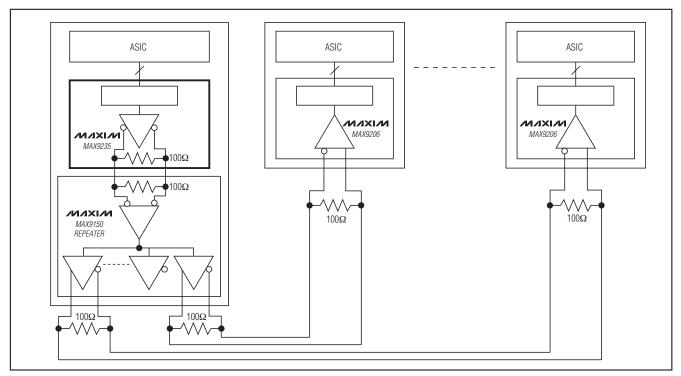

MAX9235はポイント間またはブロードキャスト構成で動作させることができます。

ケーブルまたはPCBトレースの特性インピーダンスで各端を終端したポイント間接続を図8に示します。シリアライザから見た総合負荷は $50\Omega$ です。二重終端の方が通常は単一の $100\Omega$ 終端に比べて反射が減ります。デシリアライザで単 $-100\Omega$ の終端とすることは可能であり、差動信号振幅が大きくなります。

ポイント間ブロードキャスト構成が図9に示されています。 ジッタの小さいMAX9150の10ポートリピータがシリア ライザ出力を再生して10個の二重終端したポイント間 リンクで伝送するために使われています。 リピータを使うと、10組のシリアライザとデシリアライザ接続に比べて9個のシリアライザが不要になります。 リピータのジッタがシリアライザとデシリアライザの タイミングマージンから削減されるため、ジッタの 小さいリピータがほとんどの高データレートのアプリケーションにとって不可欠です。

#### ボードレイアウト

LVDSアプリケーションでは、電源、グランド、および 入出力信号を分離可能な4層のPCBを推奨します。 LVTTL/LVCMOSとLVDS信号を相互に分離してLVDS ラインへの結合を避けてください。

図8. 二重終端したポイント間通信

図9. MAX9150リピータを使用したポイント間ブロードキャスト

# 機能図

# ピン配置

チップ情報

PROCESS: CMOS

MIXIM

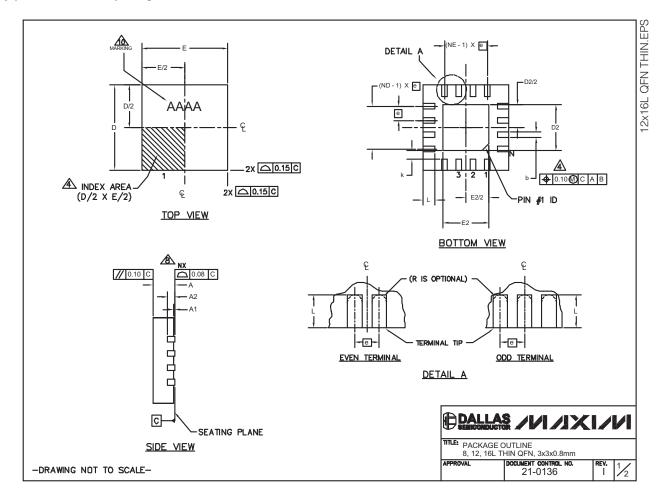

#### パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、japan.maxim-ic.com/packagesをご参照下さい。)

### パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、 japan.maxim-ic.com/packagesをご参照下さい。)

| PKG  | 8L 3x3 |         |      | 1     | 2L 3x3    |      | 16L 3x3        |           |      |  |

|------|--------|---------|------|-------|-----------|------|----------------|-----------|------|--|

| REF. | MIN.   | NOM.    | MAX. | MIN.  | NOM.      | MAX. | MIN.           | NOM.      | MAX. |  |

| Α    | 0.70   | 0.75    | 0.80 | 0.70  | 0.75      | 0.80 | 0.70           | 0.75      | 0.80 |  |

| b    | 0.25   | 0.30    | 0.35 | 0.20  | 0.25      | 0.30 | 0.20           | 0.25      | 0.30 |  |

| D    | 2.90   | 3.00    | 3.10 | 2.90  | 3.00      | 3.10 | 2.90           | 3.00      | 3.10 |  |

| Е    | 2.90   | 3.00    | 3.10 | 2.90  | 3.00      | 3.10 | 2.90           | 3.00      | 3.10 |  |

| е    | 0      | .65 BSC | ).   | 0     | 0.50 BSC. |      |                | 0.50 BSC. |      |  |

| L    | 0.35   | 0.55    | 0.75 | 0.45  | 0.55      | 0.65 | 0.30 0.40 0.50 |           | 0.50 |  |

| N    |        | 8       |      | 12 16 |           |      |                |           |      |  |

| ND   |        | 2       |      |       | 3         |      |                | 4         |      |  |

| NE   |        | 2       |      |       | 3         |      | 4              |           |      |  |

| A1   | 0      | 0.02    | 0.05 | 0     | 0.02      | 0.05 | 0              | 0.02      | 0.05 |  |

| A2   | 0      | .20 RE  | F    | 0     | 0.20 REF  |      | 0.20 REF       |           |      |  |

| k    | 0.25   | -       | -    | 0.25  | -         | -    | 0.25           | -         | -    |  |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |             |        |  |

|------------------------|------|------|------|------|------|------|-------------|--------|--|

| PKG.                   | D2   |      |      | E2   |      |      | PIN ID      | JEDEC  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. | PINID       | JEDEC  |  |

| TQ833-1                | 0.25 | 0.70 | 1.25 | 0.25 | 0.70 | 1.25 | 0.35 x 45°  | WEEC   |  |

| T1233-1                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |

| T1233-3                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |

| T1233-4                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |

| T1633-2                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| T1633F-3               | 0.65 | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |

| T1633FH-3              | 0.65 | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |

| T1633-4                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| T1633-5                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

#### NOTES:

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- N IS THE TOTAL NUMBER OF TERMINALS.

- 4 THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- \land DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.20 mm AND 0.25 mm FROM TERMINAL TIP.

- $\stackrel{lack}{ ext{6.}}$  ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- ▲ COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220 REVISION C.

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 12. WARPAGE NOT TO EXCEED 0.10mm.

DALLAS /VI/IXI/VI

PACKAGE OUTLINE 8, 12, 16L THIN QFN, 3x3x0.8mm

21-0136

-DRAWING NOT TO SCALE-

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。 マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600