# 低コスト、7ns、 低電力電圧コンパレータ

## 概要

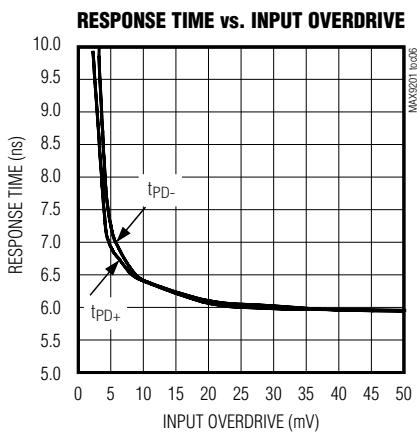

MAX9201/MAX9202/MAX9203は、能動的内部プルアップ付のTTLロジック出力を備えた高速、低電力、クワッド/デュアル/シングルコンパレータです。伝播遅延が短いため(オーバドライブが5mVの時に7ns typ)、これらのデバイスは高速A/Dコンバータ及びサンプリング回路、ラインレシーバ、V/Fコンバータ及びその他多くのデータ弁別、信号復元アプリケーションに最適です。

全てのコンパレータは、独立したアナログ電源とデジタル電源で駆動することも、単一の電源電圧を両方に使用することもできます。アナログ入力同相範囲は負電源電圧を含んでいるため、単一電源で駆動されている場合でもグランド検出が可能です。MAX9201/MAX9202/MAX9203の消費電力は、コンパレータ当り僅か9mW(+5V電源)です。

MAX9202/MAX9203はTTLコンパチブル入力付の出力ラッチを備えています。ラッチ入力がローに駆動されると、コンパレータ出力状態が保持されます。MAX9201はラッチを除いてMAX9202/MAX9203と同じ機能を持っています。

MAX9201/MAX9202/MAX9203は、MAX901/MAX902/MAX903の低電力低成本アップグレード製品となっており、電力を50%節約すると共にパッケージが小さくなっています。

## アプリケーション

|            |              |

|------------|--------------|

| 高速A/Dコンバータ | スレッシュルドディテクタ |

| 高速V/Fコンバータ | 入力トリガ回路      |

| ラインレシーバ    | 高速データサンプリング  |

| 高速信号矩形化/復元 | PWM回路        |

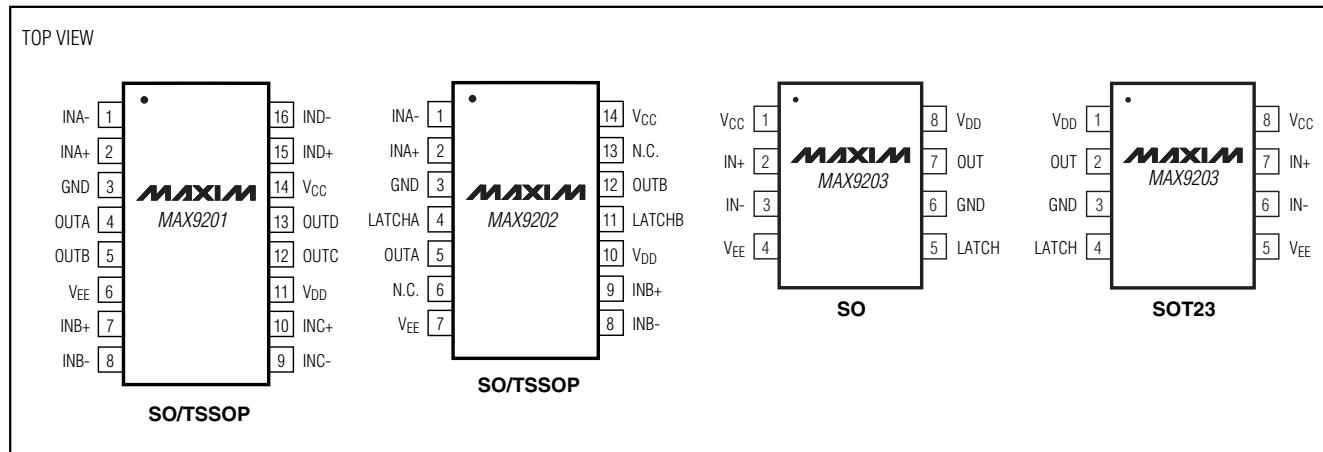

## ピン配置

# 低成本、7ns、 低電力電圧コンパレータ

## ABSOLUTE MAXIMUM RATINGS

|                                                                                     |                                   |

|-------------------------------------------------------------------------------------|-----------------------------------|

| Analog Supply Voltage (V <sub>CC</sub> - V <sub>EE</sub> )                          | +12V                              |

| Digital Supply Voltage (V <sub>DD</sub> )                                           | +7V                               |

| Differential Input Voltage.....(V <sub>EE</sub> - 0.3V) to (V <sub>CC</sub> + 0.3V) |                                   |

| Common Mode Input Voltage .....(V <sub>EE</sub> - 0.3V) to (V <sub>CC</sub> + 0.3V) |                                   |

| Latch Input Voltage<br>(MAX9202/MAX9203 only)                                       | -0.3V to (V <sub>DD</sub> + 0.3V) |

| Output Short-Circuit Duration                                                       | Continuous                        |

| To GND                                                                              | Continuous                        |

| To V <sub>DD</sub>                                                                  | 1min                              |

Continuous Power Dissipation (T<sub>A</sub> = +70°C)

|                                             |                      |

|---------------------------------------------|----------------------|

| 8-Pin SOT23-8 (derate 9.1mW/°C above +70°C) | ...727mW/°C          |

| 8-Pin SO (derate 5.9mW/°C above +70°C)      | ....471mW/°C         |

| 14-Pin TSSOP (derate 9.1mW/°C above +70°C)  | ....727mW/°C         |

| 14-Pin SO (derate 8.3mW/°C above +70°C)     | ....667mW/°C         |

| 16-Pin TSSOP (derate 9.4mW/°C above +70°C)  | ....755mW/°C         |

| 16-Pin SO (derate 8.7mW/°C above +70°C)     | ....696mW/°C         |

| Operating Temperature Range                 | .....-45°C to +85°C  |

| Junction Temperature                        | .....+150°C          |

| Storage Temperature Range                   | .....-65°C to +150°C |

| Lead Temperature (soldering, 10s)           | .....+300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +5V, V<sub>EE</sub> = -5V, V<sub>DD</sub> = +5V, GND = 0, V<sub>CM</sub> = 0, LATCH\_ = logic high, T<sub>A</sub> = -40°C to +85°C. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                          | SYMBOL                            | CONDITIONS                                                                |                     | MIN                   | TYP  | MAX                    | UNITS |

|------------------------------------|-----------------------------------|---------------------------------------------------------------------------|---------------------|-----------------------|------|------------------------|-------|

| Analog Supply Voltage Range        | V <sub>CC</sub> - V <sub>EE</sub> | Referenced to V <sub>EE</sub>                                             |                     | 4.75                  | 10.5 |                        | V     |

| Digital Supply Voltage Range       | V <sub>DD</sub>                   | Referenced to GND                                                         |                     | 4.75                  | 5.25 |                        | V     |

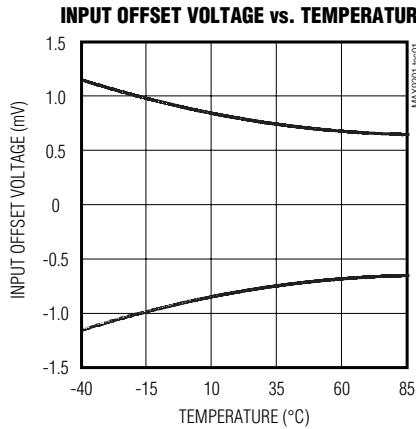

| Input Offset Voltage               | V <sub>OS</sub>                   | V <sub>CM</sub> = 0,<br>V <sub>OUT</sub> = 1.4V                           | TA = +25°C          |                       | 1    | 4                      | mV    |

|                                    |                                   |                                                                           | TA = -40°C to +85°C |                       |      | 7.5                    |       |

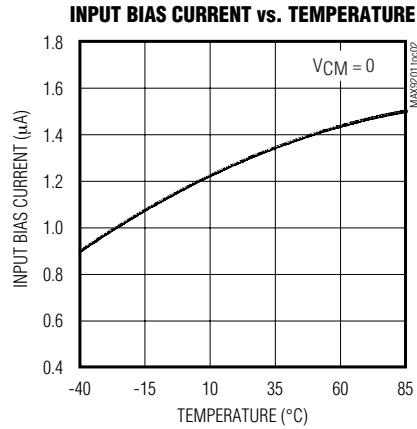

| Input Bias Current                 | I <sub>B</sub>                    | I <sub>IN+</sub> or I <sub>IN-</sub>                                      | TA = +25°C          |                       | 1.25 | 5                      | μA    |

|                                    |                                   |                                                                           | TA = -40°C to +85°C |                       |      | 7.0                    |       |

| Input Offset Current               | I <sub>OS</sub>                   | V <sub>CM</sub> = 0,<br>V <sub>OUT</sub> = 1.4V                           | TA = +25°C          |                       | 50   | 250                    | nA    |

|                                    |                                   |                                                                           | TA = -40°C to +85°C |                       |      | 450                    |       |

| Common-Mode Input Voltage Range    | V <sub>CM</sub>                   | Note 2                                                                    |                     | V <sub>EE</sub> - 0.1 |      | V <sub>CC</sub> - 2.25 | V     |

| Common-Mode Rejection Ratio        | CMRR                              | -5.1V < V <sub>CM</sub> < +2.75V<br>V <sub>OUT</sub> = 1.4V               | TA = +25°C          |                       | 50   | 150                    | μV/V  |

|                                    |                                   |                                                                           | TA = -40°C to +85°C |                       |      | 250                    |       |

| Power-Supply Rejection Ratio       | PSRR                              | Note 3                                                                    | TA = +25°C          |                       | 50   | 150                    | μV/V  |

|                                    |                                   |                                                                           | TA = -40°C to +85°C |                       |      | 250                    |       |

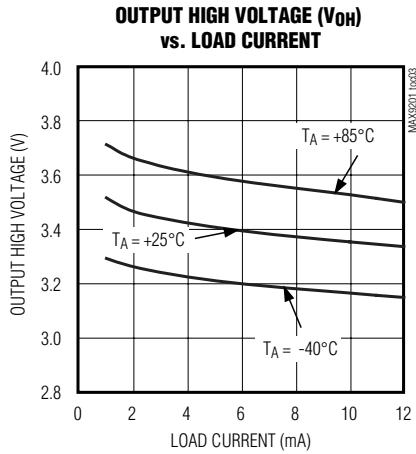

| Output High Voltage                | V <sub>OH</sub>                   | (V <sub>IN+</sub> - V <sub>IN-</sub> ) > 250mV, I <sub>SOURCE</sub> = 1mA |                     | 3.0                   | 3.5  |                        | V     |

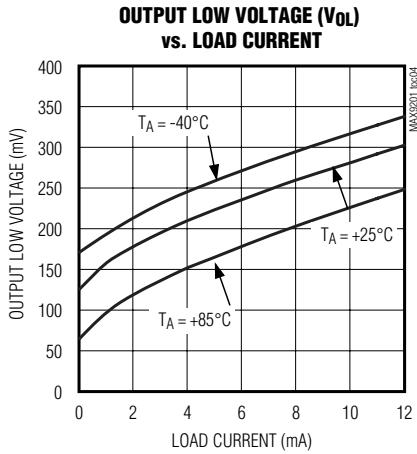

| Output Low Voltage                 | V <sub>OL</sub>                   | (V <sub>IN+</sub> - V <sub>IN-</sub> ) < -250mV, I <sub>SINK</sub> = 8mA  |                     |                       | 0.25 | 0.4                    | V     |

| Latch Input Threshold Voltage High | V <sub>LH</sub>                   | Note 4                                                                    |                     |                       | 1.4  | 2                      | V     |

| Latch Input Threshold Voltage Low  | V <sub>LL</sub>                   | Note 4                                                                    |                     | 0.8                   | 1.4  |                        | V     |

| Latch Input Current High           | I <sub>LH</sub>                   | V <sub>LH</sub> = 3.0V, Note 4                                            |                     |                       | 0.5  | 3                      | μA    |

| Latch Input Current Low            | I <sub>LL</sub>                   | V <sub>LL</sub> = 0.3V, Note 4                                            |                     |                       | 0.5  | 3                      | μA    |

| Input Capacitance                  | C <sub>IN</sub>                   |                                                                           |                     |                       | 4    |                        | pF    |

| Differential Input Impedance       | R <sub>IND</sub>                  |                                                                           |                     |                       | 5    |                        | MΩ    |

| Common-Mode Input Impedance        | R <sub>INCM</sub>                 |                                                                           |                     |                       | 5.5  |                        | MΩ    |

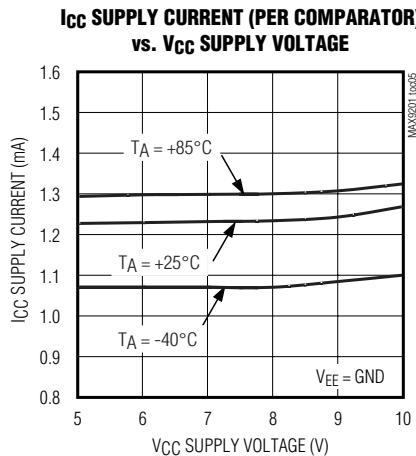

| Positive Analog Supply Current     | I <sub>CC</sub>                   | Note 5                                                                    | MAX9201             |                       | 4.7  | 7                      | mA    |

|                                    |                                   |                                                                           | MAX9202             |                       | 2.5  | 4.0                    |       |

|                                    |                                   |                                                                           | MAX9203             |                       | 1.3  | 2                      |       |

# 低コスト、7ns、 低電力電圧コンパレータ

MAX9201/MAX9202/MAX9203

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = +5V$ ,  $V_{EE} = -5V$ ,  $V_{DD} = +5V$ ,  $GND = 0$ ,  $V_{CM} = 0$ ,  $LATCH_-$  = logic high,  $T_A = -40^\circ C$  to  $+85^\circ C$ . Typical values are at  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 1)

| PARAMETER                      | SYMBOL   | CONDITIONS                                 |         | MIN | TYP | MAX | UNITS |

|--------------------------------|----------|--------------------------------------------|---------|-----|-----|-----|-------|

| Negative Analog Supply Current | $I_{EE}$ | Note 5                                     | MAX9201 |     | 3.4 | 5.0 | mA    |

|                                |          |                                            | MAX9202 |     | 1.8 | 3.0 |       |

|                                |          |                                            | MAX9203 |     | 1.0 | 1.6 |       |

| Digital Supply Current         | $I_{DD}$ | Note 5                                     | MAX9201 |     | 2   | 3.0 | mA    |

|                                |          |                                            | MAX9202 |     | 1   | 1.5 |       |

|                                |          |                                            | MAX9203 |     | 0.5 | 0.8 |       |

| Power Dissipation              | $P_D$    | $V_{CC} = V_{DD} = +5V$ ,<br>$V_{EE} = 0V$ | MAX9201 |     | 33  | 44  | mW    |

|                                |          |                                            | MAX9202 |     | 17  | 24  |       |

|                                |          |                                            | MAX9203 |     | 9   | 13  |       |

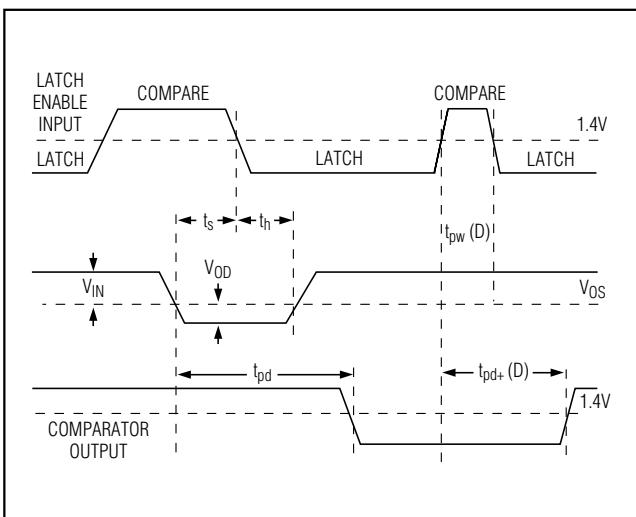

## TIMING CHARACTERISTICS

( $V_{CC} = +5V$ ,  $V_{EE} = -5V$ ,  $V_{DD} = +5V$ ,  $GND = 0$ ,  $V_{CM} = 0$ ,  $LATCH_-$  = logic high,  $T_A = -40^\circ C$  to  $+85^\circ C$ . Typical values are at  $T_A = +25^\circ C$ , unless otherwise noted.) (Notes 1, 6)

| PARAMETER                                   | SYMBOL          | CONDITIONS                                            |                                      | MIN | TYP | MAX | UNITS |

|---------------------------------------------|-----------------|-------------------------------------------------------|--------------------------------------|-----|-----|-----|-------|

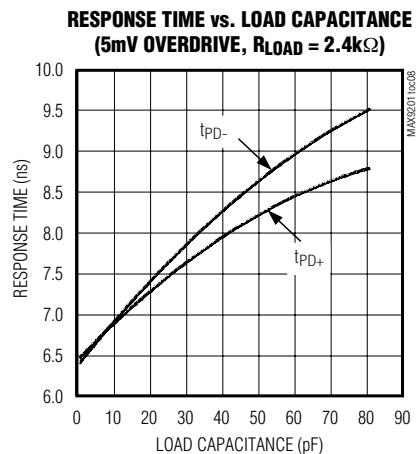

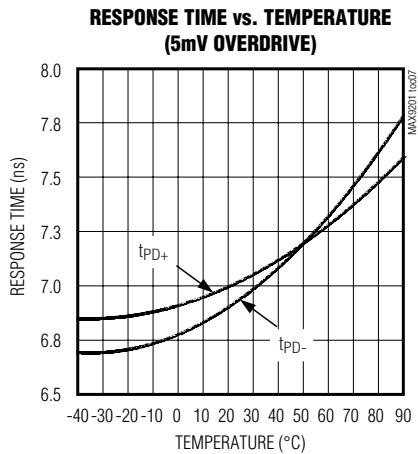

| Input-to-Output High Response Time          | $t_{PD+}$       | $V_{OD} = 5mV$ ,<br>$C_L = 15pF$ ,<br>$I_{OUT} = 2mA$ | $T_A = +25^\circ C$                  |     | 7   | 9   | ns    |

|                                             |                 |                                                       | $T_A = -40^\circ C$ to $+85^\circ C$ |     |     | 12  |       |

| Input-to-Output Low Response Time           | $t_{PD-}$       | $V_{OD} = 5mV$ ,<br>$C_L = 15pF$ ,<br>$I_{OUT} = 2mA$ | $T_A = +25^\circ C$                  |     | 7   | 9   | ns    |

|                                             |                 |                                                       | $T_A = -40^\circ C$ to $+85^\circ C$ |     |     | 12  |       |

| Rise Time                                   | $t_R$           | $C_L = 15pF$ ,<br>$I_{OUT} = 2mA$                     | $T_A = +25^\circ C$                  |     | 2.0 |     | ns    |

| Fall Time                                   | $t_F$           | $C_L = 15pF$ ,<br>$I_{OUT} = 2mA$                     | $T_A = +25^\circ C$                  |     | 1.0 |     | ns    |

| Difference in Response Time Between Outputs | $\Delta t_{PD}$ | Note 7                                                | $T_A = +25^\circ C$                  |     | 0.5 | 1.5 | ns    |

|                                             |                 |                                                       | $T_A = -40^\circ C$ to $+85^\circ C$ |     |     | 2.5 |       |

| Latch Disable to Output High Delay          | $t_{PD+(D)}$    | Note 4                                                |                                      |     | 10  |     | ns    |

| Latch Disable to Output Low Delay           | $t_{PD-(D)}$    | Note 4                                                |                                      |     | 10  |     | ns    |

| Minimum Setup Time                          | $t_S$           | Note 4                                                |                                      |     | 2   |     | ns    |

| Minimum Hold Time                           | $t_N$           | Note 4                                                |                                      |     | 1   |     | ns    |

| Minimum Latch Disable Pulse Width           | $t_{PW(D)}$     | Note 4                                                |                                      |     | 8   |     | ns    |

**Note 1:** All devices are 100% production tested at  $T_A = +25^\circ C$ . All temperature limits are guaranteed by design.

**Note 2:** Inferred by CMRR test.

**Note 3:** Tested for  $+4.75V < V_{CC} < +5.25V$ , and  $-5.25V < V_{EE} < -4.75V$  with  $V_{DD} = +5V$ , although permissible analog power-supply range is  $4.75V < V_{CC} < +10.5V$  for single supply operation with  $V_{EE}$  grounded.

**Note 4:** Specification does not apply to MAX9201.

**Note 5:**  $I_{CC}$  tested for  $4.75V < V_{CC} < +10.5V$  with  $V_{EE}$  grounded.  $I_{EE}$  tested for  $-5.25V < V_{EE} < -4.75V$  with  $V_{CC} = +5V$ .  $I_{DD}$  tested for  $+4.75V < V_{DD} < +5.25V$  with all comparator outputs low, worst-case condition.

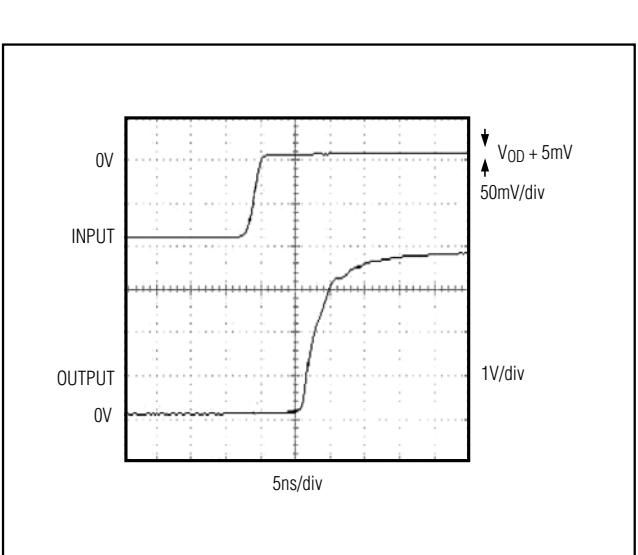

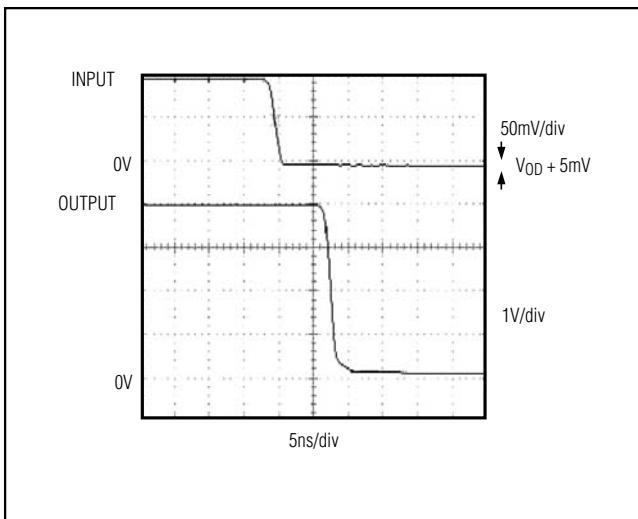

**Note 6:** Guaranteed by design. Times are for 100mV step inputs (see propagation delay characteristics in Figures 2 and 3)

**Note 7:** Maximum difference in propagation delay between two comparators in the MAX9201/MAX9202.

# 低成本、7ns、 低電力電圧コンパレータ

## 標準動作特性

( $V_{CC} = +5V$ ,  $V_{EE} = -5V$ ,  $V_{DD} = +5V$ , GND = 0,  $V_{CM} = 0$ , LATCH\_ = logic high,  $V_{OUT} = 1.4V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# 低成本、7ns、 低電力電圧コンパレータ

MAX9201/MAX9202/MAX9203

## 標準動作特性(続き)

( $V_{CC} = +5V$ ,  $V_{EE} = -5V$ ,  $V_{DD} = +5V$ ,  $GND = 0$ ,  $V_{CM} = 0$ ,  $LATCH\_ = \text{logic high}$ ,  $V_{OUT} = 1.4V$ ,  $T_A = +25^\circ\text{C}$ , unless otherwise noted.)

## 端子説明

### MAX9201

| 端子              | 名称              | 機能                   |

|-----------------|-----------------|----------------------|

| 1, 8, 9,<br>16  | IN_-            | 負入力(チャネルA、B、C、D)     |

| 2, 7, 10,<br>15 | IN_+            | 正入力(チャネルA、B、C、D)     |

| 3               | GND             | グランド                 |

| 4, 5, 12,<br>13 | OUT_-           | 出力(チャネルA、B、C、D)      |

| 6               | V <sub>EE</sub> | 負アナログ電源及び<br>サブストレート |

| 11              | V <sub>DD</sub> | 正デジタル電源              |

| 14              | V <sub>CC</sub> | 正アナログ電源              |

### MAX9202

| 端子    | 名称              | 機能                   |

|-------|-----------------|----------------------|

| 1, 8  | IN_-            | 負入力(チャネルA、B)         |

| 2, 9  | IN_+            | 正入力(チャネルA、B)         |

| 3     | GND             | グランド                 |

| 4, 11 | LATCH_-         | ラッチ入力(チャネルA、B)       |

| 5, 12 | OUT_-           | 出力(チャネルA、B)          |

| 6, 13 | N.C.            | 無接続                  |

| 7     | V <sub>EE</sub> | 負アナログ電源及び<br>サブストレート |

| 10    | V <sub>DD</sub> | 正デジタル電源              |

| 14    | V <sub>CC</sub> | 正アナログ電源              |

# 低成本、7ns、 低電力電圧コンパレータ

## 端子説明(続き)

### MAX9203

| 端子 |     | 名称              | 機能               |

|----|-----|-----------------|------------------|

| SO | SOT |                 |                  |

| 1  | 8   | V <sub>CC</sub> | 正アナログ電源          |

| 2  | 7   | IN+             | 正入力              |

| 3  | 6   | IN-             | 負入力              |

| 4  | 5   | V <sub>EE</sub> | 負アナログ電源及びサブストレート |

| 5  | 4   | LATCH           | ラッチ入力            |

| 6  | 3   | GND             | グランド             |

| 7  | 2   | OUT             | 出力               |

| 8  | 1   | V <sub>DD</sub> | 正デジタル電源          |

## アプリケーション情報

### 回路レイアウト

MAX9201/MAX9202/MAX9203は伝達関数の利得帯域幅が大きいため、高速能力をフルに活かすためには特別な注意が必要です。良好な低インダクタンスグランドプレーンを持つプリント回路基板が必須です。全てのデカップリングコンデンサ(小型100nFセラミックタイプが好適です)を電源ピンのできるだけ近くに取付けて下さい。アナログV<sub>CC</sub>とデジタルV<sub>DD</sub>のデカップリングコンデンサは別々にすることを推奨します。デカップリング及び終端処理部品の帯域幅には特に注意して下さい。コンパレータの周囲の望ましくない寄生フィードバックを避けるためには、入力と出力のリードを短く

することが必須です。ソケットを使わずに、デバイスを直接プリント基板にハンダ付けして下さい。

### 入力スルーレートの要求条件

全ての高速コンパレータに共通することですが、MAX9201/MAX9202/MAX9203は利得帯域幅積が大きいために入力がリニア領域をよぎる時に発振の問題が生じがちです。出力波形に発振や段差のないクリーンな出力スイッチングを実現するには、入力が最小スルーレート条件(0.5V/s typ)を満たしている必要があります。発振は主に基板レイアウト及びソースインピーダンスと浮遊入力容量のカップリングしたものの関数です。レイアウトが悪かつたりソースインピーダンスが大きかつたりすると、デバイスは発振しやすくなり、最小スルーレート条件が増加します。アプリケーションによっては、出力と正入力の間に正フィードバックを印加すると良い場合があります。これにより、出力は遷移領域を正常に通過しますが、入力端子から見たスレッショルドにヒステリシスがかかります。

### TTL出力及びラッチ入力

コンパレータのTTL出力段は、低電力ショットキTTLをファンアウト4で駆動するように最適化されています。ラッチがロジックハイレベルに接続されると、コンパレータはトランスペアレントになり、入力端子の変化に直ちに応答します。ラッチがTTLローレベルに接続されていると、コンパレータの出力はラッチコマンドが印加された瞬間に(同じ状態に)ラッチして、その後の入力変化には応答しなくなります。MAX9201にはラッチはありません。

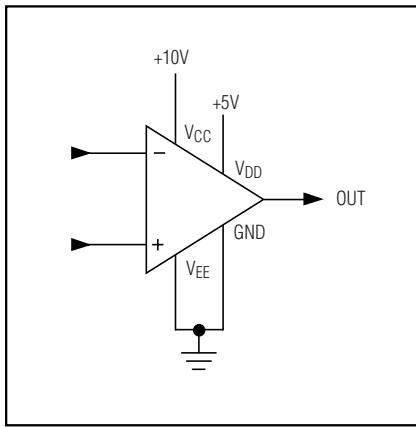

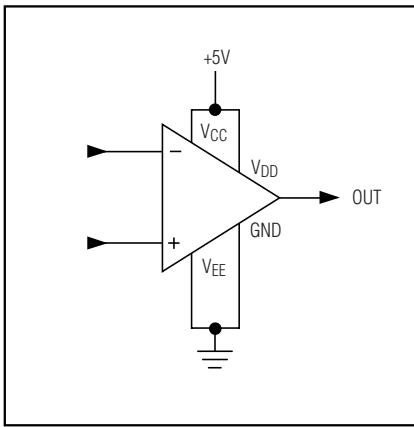

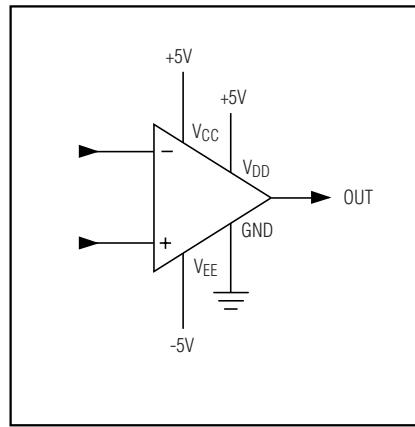

## 標準電源接続法

図1a. 別個のアナログ電源、

共通グランド

図1b. +5V単一電源、

共通グランド

図1c. スプリット±5V電源、

別々のグランド

# 低成本、7ns、 低電力電圧コンパレータ

MAX9201/9202/9203

## 電源

MAX9201/MAX9202/MAX9203は、アナログ電源とデジタル電源を別々にすることも、+5V単一電源で駆動することもできます。アナログ電源は単一電源動作の場合は $V_{EE}$ を接地して+5V～+10Vの範囲が可能です(図1a及び1b)。スプリット±5V電源(図1c)も可能です。 $V_{DD}$ デジタル電源は常に+5Vを必要とします。高速混合信号アプリケーションにおいて共通グランドを共有している場合、ノイズの大きなデジタル環境がアナログ入力信号に悪影響を与えることがあります。電源が別々になっている場合、MAX9201/MAX9202/MAX9203はアナロググランド( $V_{EE}$ )とデジタルグランド(GND)を別々にすることによってアナログ信号とデジタル信号を分離します。

## 用語の定義

|           |                                                                                      |

|-----------|--------------------------------------------------------------------------------------|

| $V_{OS}$  | 入力オフセット電圧：出力においてTTLロジックスレッショルド(+1.4V)を得るために2つの入力端子間に印加される電圧。                         |

| $V_{IN}$  | 入力電圧パルス振幅：通常、コンパレータ仕様では100mVに設定されます。                                                 |

| $V_{OD}$  | 入力電圧オーバードライブ：通常、コンパレータでは5mV、極性は $V_{IN}$ と反対に設定されます。                                 |

| $t_{pd+}$ | 入力から出力ハイへの遅延：入力信号が入力オフセット電圧をよぎつてから出力のローからハイへの遷移のTTLロジックスレッショルド(+1.4V)までとして測定される伝播遅延。 |

図2. MAX9201/MAX9202/MAX9203の

ダイアグラム

$t_{pd-}$

入力から出力ローへの遅延。入力信号が入力オフセット電圧をよぎつてから出力のハイからローへの遷移のTTLロジックスレッショルド(+1.4V)までとして測定される伝播遅延。

$t_{pd+(D)}$  ラッチディセーブルから出力ハイへの遅延：

ラッチ信号がローからハイへの遷移においてTTLロジックスレッショルド(+1.4V)をよぎつてから、出力のローからハイへの遷移においてTTLロジックスレッショルド(+1.4V)をよぎるまでとして測定される伝播遅延。

$t_{pd-(D)}$  ラッチディセーブルから出力ローへの遅延：

ラッチ信号がローからハイへの遷移においてTTLロジックスレッショルド(+1.4V)をよぎつてから、出力のハイからローへの遷移においてTTLロジックスレッショルド(+1.4V)をよぎるまでとして測定される伝播遅延。

$t_s$

最小セットアップ時間：入力信号が取込まれて出力でホールドされるために、ラッチ信号の負遷移以前に入力信号の変化が存在していなければならぬ最小時間。

$t_h$

最小ホールド時間：入力信号が取込まれて出力でホールドされるために、ラッチ信号の負遷移以後に入力信号が不变のまま維持されなければならない最小時間。

$t_{pw(D)}$

最小ラッチディセーブルパルス幅：入力信号の変化を取込んでホールドするためにラッチ信号がハイでなければならない最小時間。

図3. 5mVのオーバードライブに対する $t_{PD+}$ の応答時間

# 低成本、7ns、 低電力電圧コンパレータ

図4. 5mVのオーバードライブに対する $t_{PD-}$ の応答時間

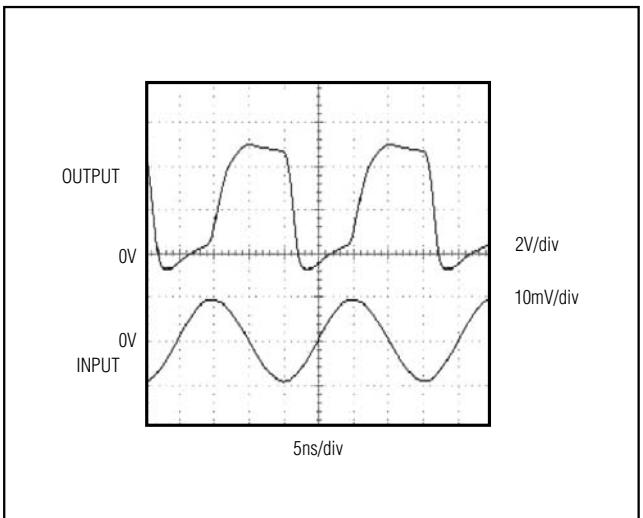

図5. 応答時間セットアップ

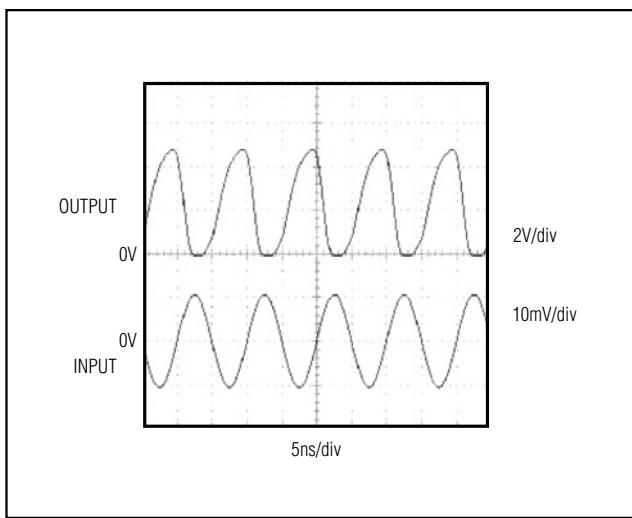

図6. 50MHzサイン波への応答

図7. 100MHzサイン波への応答

## チップ情報

MAX9201 TRANSISTOR COUNT: 348

MAX9202 TRANSISTOR COUNT: 176

MAX9203 TRANSISTOR COUNT: 116

PROCESS: Bipolar

**マキシム・ジャパン株式会社**

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。

8 **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

© 2005 Maxim Integrated Products

**MAXIM** is a registered trademark of Maxim Integrated Products, Inc.