## MAX9150評価キット

**Evaluates: MAX9150**

### 概要

MAX9150評価キット(EVキット)は、MAX9150 400Mbps、10ポート低電圧差動信号(LVDS)リピータの評価作業を容易にする完全実装済み、試験済みの回路基板です。MAX9150はLVDS信号を受け付けて、その信号を10個の出力にリピートします。出力レベルはダブル終端バス(差動バスの両端に $100\Omega$ 、全体で $50\Omega$ )に対してLVDSとなります。本EVキットは2個の独立した回路を備えており、その各々がMAX9150 リピータを持っています。これらの回路は、様々な媒体を使ってリンクすることも、独立にテストすることもできます。出力はSMAコネクタ又はカテゴリー5のツイストワイペアを通じてサンプリングすることができます。本EVキットの2個の回路の動作には+3.3V電源が必要です。

### 部品メーカー

| SUPPLIER | PHONE        | FAX          |

|----------|--------------|--------------|

| AVX      | 803-946-0690 | 803-626-3123 |

| Kemet    | 864-963-6300 | 864-963-6521 |

| TDK      | 847-803-6100 | 847-803-6296 |

注：上記の部品メーカーに問い合わせをするときは

MAX9150を使用していることを伝えてください。

### 部品リスト

| DESIGNATION                                     | QTY | DESCRIPTION                                                                               |

|-------------------------------------------------|-----|-------------------------------------------------------------------------------------------|

| C1, C11                                         | 2   | 10 $\mu$ F, 10V tantalum capacitors (B)<br>AVX TAJB106M010 or<br>Kemet T494B106K010AS     |

| C2, C5, C6,<br>C12, C15, C16                    | 6   | 0.1 $\mu$ F, 16V X7R ceramic<br>capacitors (0603)<br>TDK C1608X7R1C104KT or<br>equivalent |

| C3, C4, C13,<br>C14                             | 4   | 0.01 $\mu$ F, 50V X7R ceramic<br>capacitors (0603)<br>TDK C1608X7RH103KT or<br>equivalent |

| R1, R2, R21,<br>R22, R31, R32,<br>R34, R37, R40 | 9   | 49.9 $\Omega \pm 1\%$ resistors (0402)                                                    |

### 特長

- ◆ 2個の独立したリピータ回路

- ◆ LVDS信号によるリンクテスト

- ◆ 様々な媒体のテストをサポート

- SMAコネクタ付の同軸ケーブル

- ツイストワイペア

- プリント基板トレース

- ◆ 独立した電源により、同相モードのテストが可能

- ◆ 低電圧、低電力動作

- ◆ 完全実装済み、試験済み

### 型番

| PART         | TEMP. RANGE  | IC PACKAGE |

|--------------|--------------|------------|

| MAX9150EVKIT | 0°C to +70°C | 28 TSSOP   |

|                                        |    |                                       |

|----------------------------------------|----|---------------------------------------|

| R11-R20, R33,<br>R35, R36,<br>R38, R39 | 15 | 100 $\Omega \pm 1\%$ resistors (0402) |

| R41, R42, R43                          | 0  | Not installed (0805)                  |

| U1, U2                                 | 2  | MAX9150EUI (28-pin TSSOP)             |

| INA1, INB1,<br>INA2, INB2              | 4  | SMA PC-mount edge connectors          |

| OUTA1, OUTB1,<br>OUTA2, OUTB2          | 4  | SMA PC-mount connectors               |

| JU1, JU18                              | 2  | 3-pin headers                         |

| JU12-JU17,<br>JU21-JU25                | 11 | 2-pin headers                         |

| None                                   | 4  | Shunts (JU1, JU16, JU17, JU18)        |

| None                                   | 1  | MAX9150 PC board                      |

| None                                   | 1  | MAX9150 data sheet                    |

| None                                   | 1  | MAX9150 EV kit data sheet             |

Maxim Integrated Products 1

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

無料サンプル及び最新版データシートの入手には、マキシムのホームページをご利用ください。<http://japan.maxim-ic.com>

# MAX9150評価キット

## 推奨機器

- DC電源:

+3.3V±0.3V、200mA

+3.3V±0.3V、200mA

- LVDS信号入力用のパルス発生器

(例えばHP 8131A)

- オシロスコープ(例えばTektronix 11801C)

## クイックスタート

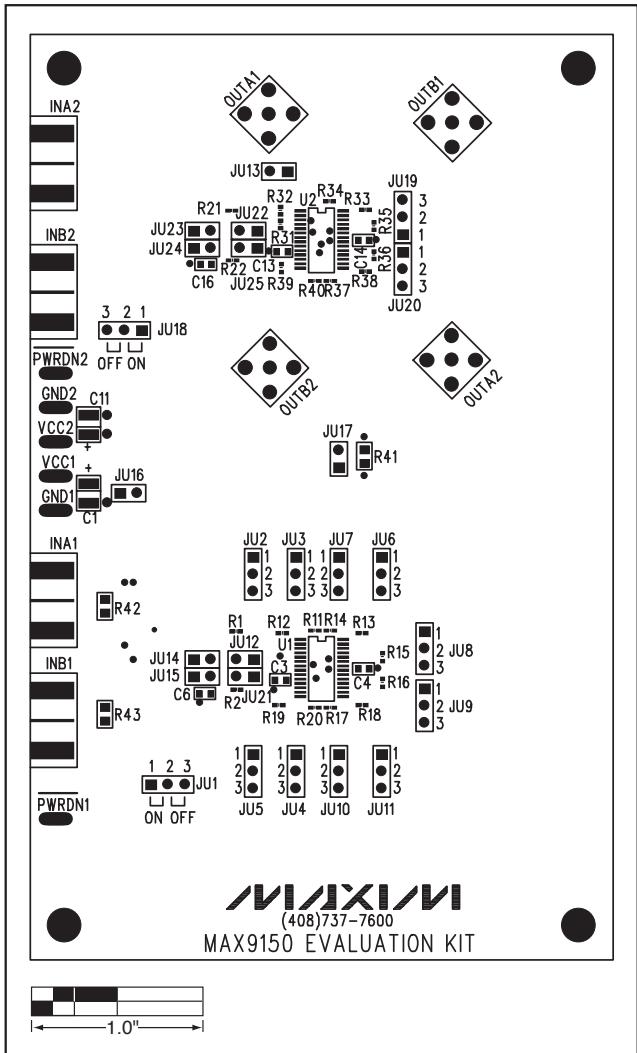

MAX9150EVキットは完全実装済み、出荷試験済みの表面実装基板です。本EVキットには2個のテスト回路が実装されています。回路1は出荷時、基板の下半分に位置し、カテゴリー5ケーブルの接続用に最適化されています。回路2は基板の上半分に位置し、直接プローブ、カテゴリー5及び同軸ケーブル接続用に設定されています。

### 回路1(下側回路)

以下の手順で回路1の動作を試して下さい。全ての接続が完了するまで、電源を投入したり、パルス発生器をイネーブルしたりしないで下さい。

- 1つの+3.3V電源をVCC1に接続します。この電源のグランド端子をGND1に接続します。

- LVDS信号を発生するようにパルス発生器を設定します(これには、パルス発生器から非反転及び反転信号出力が必要です)。公称LVDS出力を得るには、1.375Vと1.025Vの間を遷移時間約1nsで遷移する2個の相補的なシングルエンド信号を設定して下さい。遷移時間は100ps以内にマッチングする必要があります。

- ジャンパJU16にシャントを取付けます。

- パルス発生器からの信号を回路1の入力に接続します(非反転信号をSMAコネクタINA1、反転信号をSMAコネクタINB1に接続します)。

- オシロスコープをLVDS信号入力用に設定します。

- オシロスコーププローブを使ってJU2～JU11の出力信号を確認することができます。コネクタJU2～JU11において、ピン1は非反転出力、ピン2は反転出力です。ピン3はグランド接続です。

- 電源を投入します。

- パルス発生器をイネーブルします。

- ジャンパJU1のピン1と2の間にシャントを接続し、MAX9150 (U1)をイネーブルします。

- 出力信号を評価します。

## 回路2(上側回路)

以下の手順で回路2の動作を試して下さい。全ての接続が完了するまで、電源を投入したり、パルス発生器をイネーブルしたりしないで下さい。

- 1つの+3.3V電源をVCC2に接続します。この電源のグランド端子をGND2に接続します。

- LVDS信号を発生するようにパルス発生器を設定します(これには、パルス発生器から非反転及び反転信号出力が必要です)。公称LVDS出力を得るには、1.375Vと1.025Vの間を遷移時間約1nsで遷移する2個の相補的なシングルエンド信号を設定して下さい。遷移時間は100ps以内にマッチングする必要があります。

- パルス発生器からの信号を回路2の入力に接続します(非反転信号をSMAコネクタINA2、反転信号をSMAコネクタINB2に接続します)。

- オシロスコープをLVDS信号入力用に設定します。

- 以下のコネクタで、オシロスコープをLVDS出力信号に接続します。

- 同軸ケーブルで信号を評価するには、SMAコネクタOUTA1(非反転)及びOUTB1(反転)又はOUTA2(非反転)及びOUTB2(反転)に接続します。全負荷50Ω(ドライバ出力の100Ω終端、R33又はR38を含む)とするために特性インピーダンス50Ωの同軸ケーブルを使用し、先端で100Ωの抵抗で終端して下さい。

- JU19とJU20において、オシロスコーププローブを使って出力信号を確認することができます。JU19の場合、ピン2が非反転信号、ピン1が反転信号です。JU20の場合、P1が非反転信号、ピン2が反転信号です。JU19とJU20のピン3はグランド接続です。

- 差動プローブで評価するには、プローブをJU13の両端に接続します。

- 電源を投入します。

- パルス発生器をイネーブルします。

- ジャンパJU18のピン1と2の間にシャントを接続することにより、MAX9150 (U2)をイネーブルします。

- 出力信号を評価します。

## 詳細

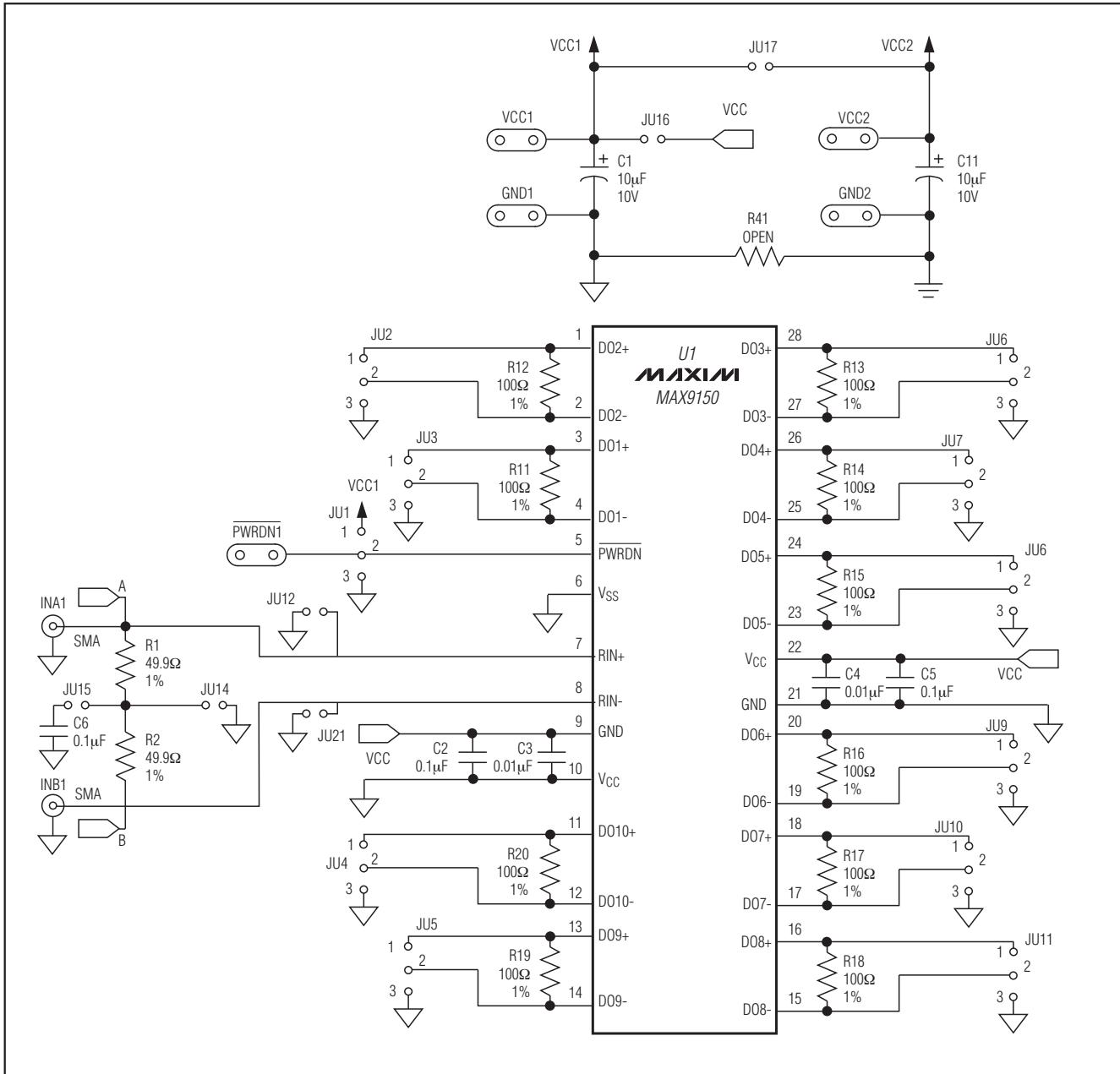

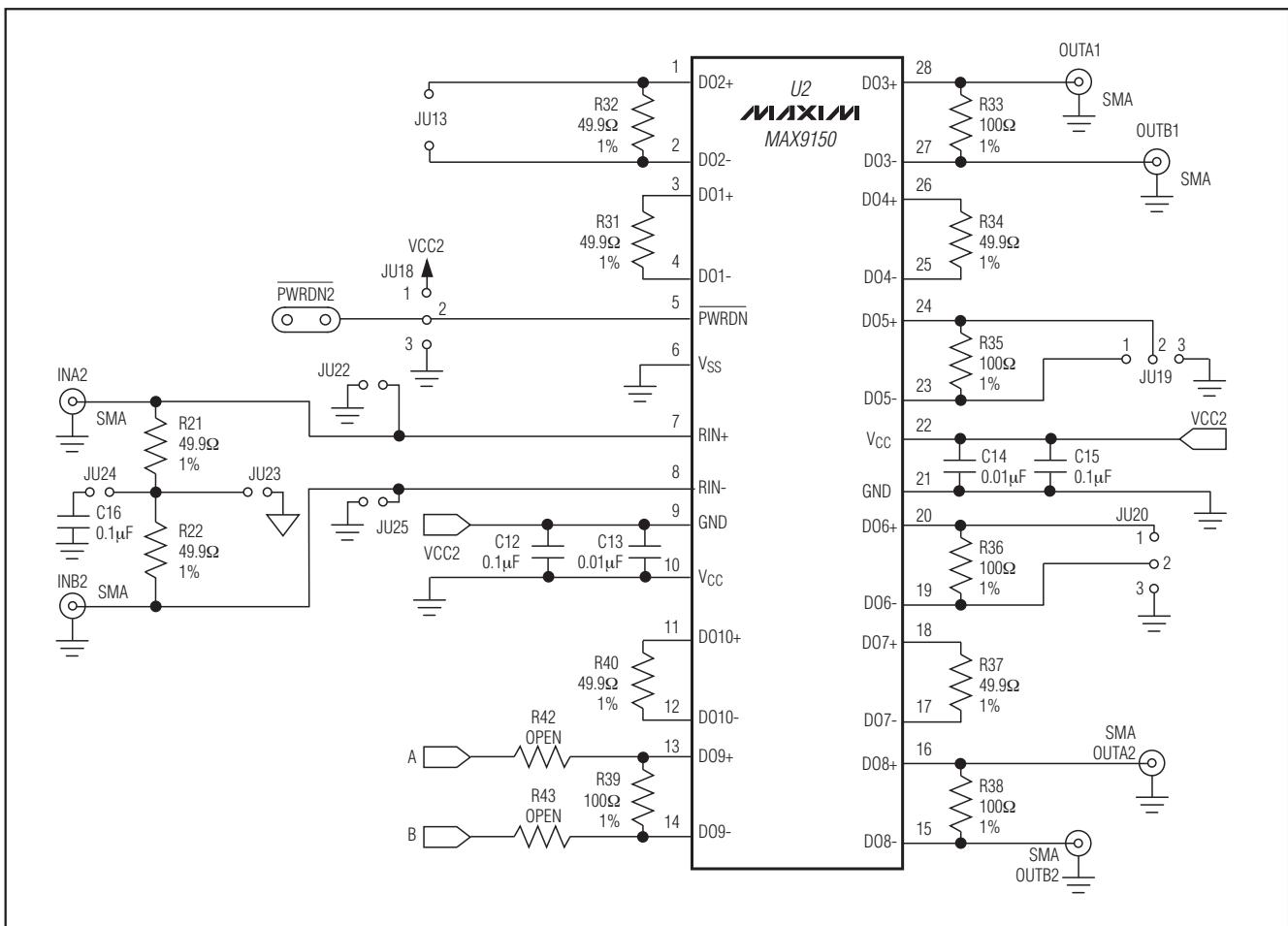

MAX9150EV キットはMAX9150 LVDSリピータの評価作業を容易にする完全実装済み、試験済みの回路基板です。MAX9150はLVDS入力を受け付け、最大400Mbpsの速度でそれを10個の出力ポートにリピートします。本EVキットは2個の独立した回路を備えており、その各々がMAX9150リピータを備えています。一方の回路は基板の上側(回路2、図2)に位置し、他方は基板の下側(回路1、図1)に位置します。これら2個の回路は一方の回路の出力信号を他方の回路の入力に接続することによって連結することができます。個々の出力はSMAコネクタ付の同軸ケーブル又はインピーダンス100Ωのツイストワイヤペアを通じて測定することができます。

## 電源

MAX9150EVキットは、独立に動作可能な2個の別々の回路を備えており、その各々が専用の電源とグランドプレーンを備えています。電源とグランドプレーンが独立であるため、グランドシフトその他の同相モード効果に対する回路の応答が測定可能になります。各回路は200mAを供給できる+3.3V電源を必要とします。本基板をコモングランドのドライバ/レシーバモードで評価する場合は、+3.3V単一電源(400mA)で動作させることができます。「ドライバ/レシーバ回路」の項を参照して下さい。

## 入力信号

MAX9150はLVDS入力を受け付けます。差動ハイスレッショルドは+100mVで、差動ロースレッショルドは-100mVです。回路2の入力コネクタはINA2(非反転)及びINB2(反転)という名前のSMAコネクタです。回路1の入力コネクタはINA1(非反転)及びINB1(反転)という名前のSMAコネクタです。

入力信号はジャンパJU22とJU25の間(回路2)又はジャンパJU12とJU21の間(回路1)に取付けられた差動信号プローブで監視することができます。ジャンパJU24又はJU15にシャントを取付けると、同相AC信号が除去されて差動信号の安定性が増加します。

回路2の動作時にシングルエンド入力信号を監視するには、JU23にシャントを取り付けて、ジャンパJU22又はジャンパJU25の両端に信号プローブを取り付けて下さい。同様に、回路1の動作時にはJU14にシャントを取り付けて、ジャンパJU12又はJU21においてシングルエンド入力信号を監視して下さい。ジャンパの設定については表1を参照して下さい。

## 出力信号

MAX9150の入力は1つのLVDS信号を受け付け、それをLVDSドライバ付の10個の出力ポートでリピートします。各ドライバの出力信号は非反転及び反転信号から成っています。回路2では、様々な異なるコネクタを通じて5個のドライバにアクセスすることができます

**表1. ジャンパ設定**

| JUMPER     | STATUS | PIN CONNECTION                                                                            | EV KIT OPERATION                                                                         |

|------------|--------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| JU1        | 1 & 2  | PWRDN to VCC1.                                                                            | U1 is enabled.                                                                           |

|            | 2 & 3  | PWRDN to GND1.                                                                            | U1 is disabled.                                                                          |

| JU14, JU23 | Closed | INA1, INB1, INA2, and INB2 SMA connectors are terminated to ground with a 49.9Ω resistor. | U1 and U2 inputs are terminated for single-ended input signals.                          |

|            | Open   | None.                                                                                     | U1 and U2 receivers are terminated with 100Ω for an LVDS signal.                         |

| JU15, JU24 | Closed | INA1, INB1, INA2, and INB2 SMA connectors are connected to a common-mode bypass network.  | Provides common-mode bypass to the input signal.                                         |

|            | Open   | None.                                                                                     | Differential termination only.                                                           |

| JU16       | Open   | VCC not connected.                                                                        | U1 is not connected to the power source.                                                 |

|            | Closed | VCC to VCC1.                                                                              | Power is supplied to U1.                                                                 |

| JU17       | Closed | VCC1 and VCC2 power planes are connected together.                                        | Operable with one power supply (a short is required at R41 pads to connect the grounds). |

|            | Open   | VCC1 and VCC2 power planes are isolated.                                                  | Circuit 1 and circuit 2 require separate power supplies.                                 |

| JU18       | 1 & 2  | PWRDN to VCC2.                                                                            | U2 is enabled.                                                                           |

|            | 2 & 3  | PWRDN to GND2.                                                                            | U2 is disabled.                                                                          |

# MAX9150評価キット

(4個のドライバは50Ω抵抗で終端処理されており、1つは回路1のレシーバに接続することができます)。利用可能な5個のドライバのうち、2個はSMAコネクタに接続し、2個はシールド付のツイストワイヤペアに接続可能で、5番目のドライバは差動信号プローブで監視することができます。出力信号、対応するドライバ及び必要な接続タイプについては表2を参照して下さい。

回路1の10個のドライバは、シールド付ツイストペアケーブルによってコネクタJU2～JU11においてアクセスすることができます。コネクタJU2～JU11のピン1は非反転信号、ピン2は反転信号、ピン3はケーブルのシールドをグランドに接続するために使用できます。

## ドライバ/レシーバ回路

回路2のドライバは回路1のレシーバを駆動するために使用することができます。このモードでは、2個の回路の電源及びグランドプレーンを連結して基板全体を単一電源で駆動することができます。この連結モードでは400mAの電源を使用して下さい。2個の電源と2個のグランドプレーンを連結するには、ジャンパJU17の両端にシャントを取り付け、R41パッドの両端に短絡又は値の小さな(< 1Ω)抵抗をハンダ付けして下さい。

回路1のレシーバを駆動するには、回路1のSMA入力コネクタ(INA1/INB1)に差動出力信号ペア(OUTA1/OUTB1、OUTA2/OUTB2、JU19又はJU20)を接続して下さい。非反転及び反転出力及び入力のマッピングについては表2を参照して下さい。本基板をドライバ/レシーバモードで動作させるもう1つの方法は、回路2のドライバのプリント基板トレースを回路1のレシーバにプリッジすることです。プリント基板トレースの接続をプリッジするには、R42とR43パッドの両端をハンダで短絡して下さい。**注記**: 回路1が回路2からLVDS信号を受信している時にはJU14にシャントがないこと

**表2. 回路2の出力信号及び接続**

| DRIVER | NONINVERTING SIGNAL | INVERTING SIGNAL | CONNECTOR                                  |

|--------|---------------------|------------------|--------------------------------------------|

| 1      | OUTA1               | OUTB1            | SMA connector                              |

| 2*     | Pin 2, JU19         | Pin 1, JU19      | Plated through holes for twisted-wire pair |

| 3*     | Pin 1, JU20         | Pin 2, JU20      | Plated through holes for twisted-wire pair |

| 4      | OUTA2               | OUTB2            | SMA connector                              |

| 5      | JU13                | JU13             | Differential signal probe pins             |

\*ピン3を使ってシールドをグランドに接続することができます。

を確認して下さい。これはLVDSドライバをオーバロードしないためです。

## MAX9150のイネーブル/ディセーブル

MAX9150はPWRDNピンにロジックハイを印加することによってイネーブルされ、ロジックローによってディセーブルされます。MAX9150EVキットにおいて、これは回路2の場合はJU18、回路1の場合はJU1を設定することによって実現できます。それぞれの回路をイネーブルするには、ジャンパのピン1と2の間にシャントを取付けて下さい。ディセーブルするには、ジャンパのピン2と3の間にシャントを取付けて下さい。ジャンパ設定については表1を参照して下さい。これらの回路はCMOSロジック信号をPWRDN1パッド又はPWRDN2パッドに印加することによってもイネーブル/ディセーブルすることができます。**注記**: CMOSロジック信号がPWRDN1又はPWRDN2パッドに接続されている場合、それとのジャンパにシャントが取付けられていないことを確認して下さい。

## 終端処理及びレイアウト

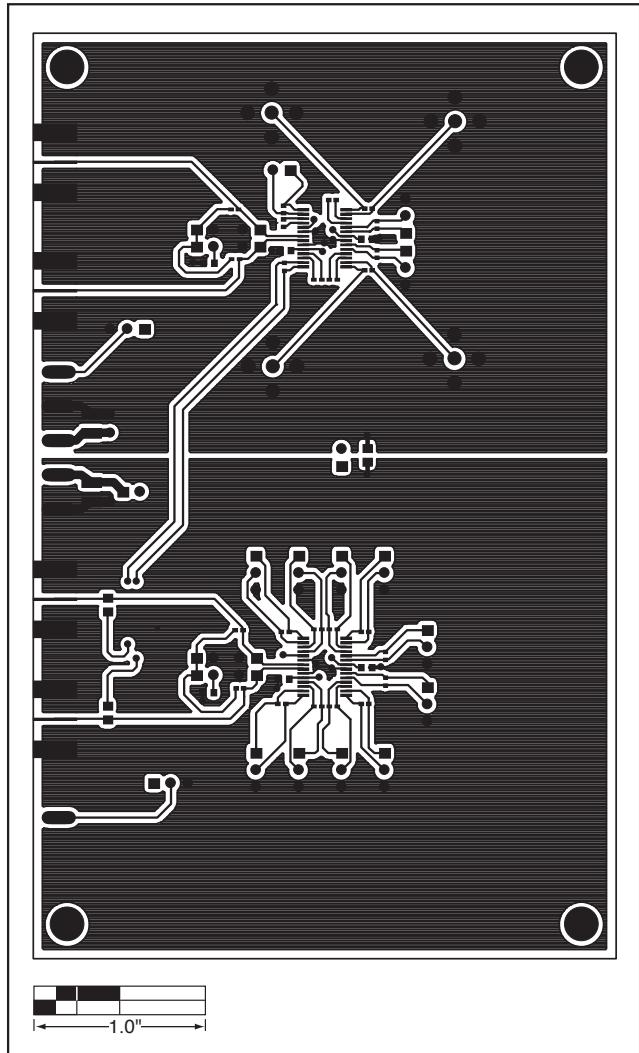

全ての信号ラインは50Ωのインピーダンスが調整されたトレースです。JU13を除く全ての差動出力信号トレースは100Ω抵抗で終端処理されています(JU13は50Ω抵抗で終端処理されています)。各差動出力ペアはトレースの長さが同じになるように配置されており、長さの差の最大値は13ミル(0.33mm)です。ノイズによる干渉を最小限にするため、本EVキットは4層基板になっています。ツイストワイヤペアをテストする時は、ワイヤの遠い方の端で100Ω抵抗を使って終端処理して下さい。

図1. MAX9150EVキットの回路図(回路1)

## Evaluates: MAX9150

図2. MAX9150EVキットの回路図(回路2)

# MAX9150評価キット

**Evaluates: MAX9150**

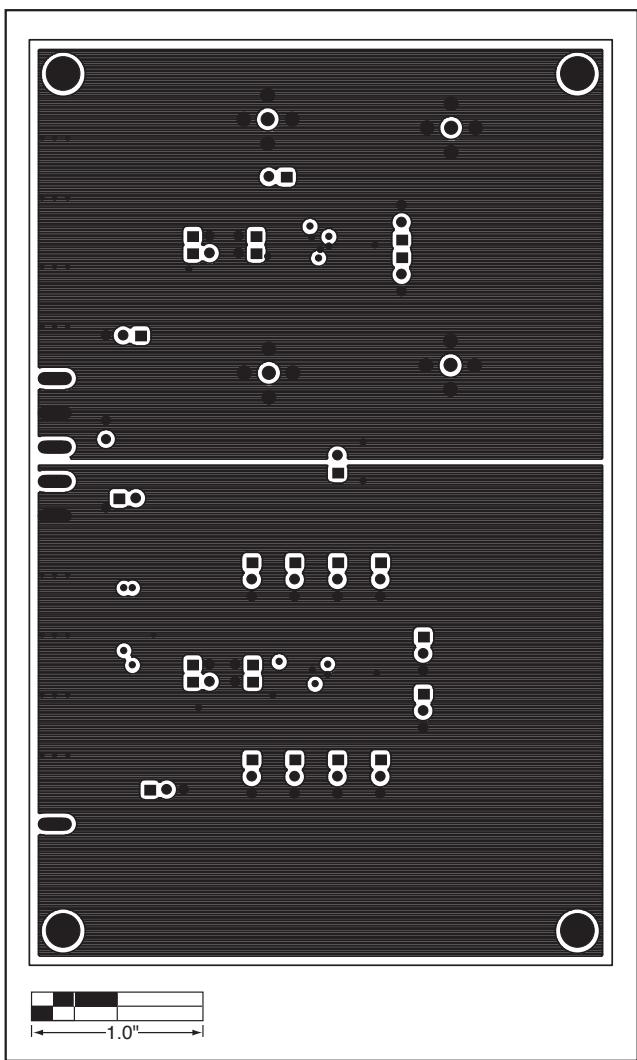

図3. MAX9150EVキットの部品配置図(部品面側)

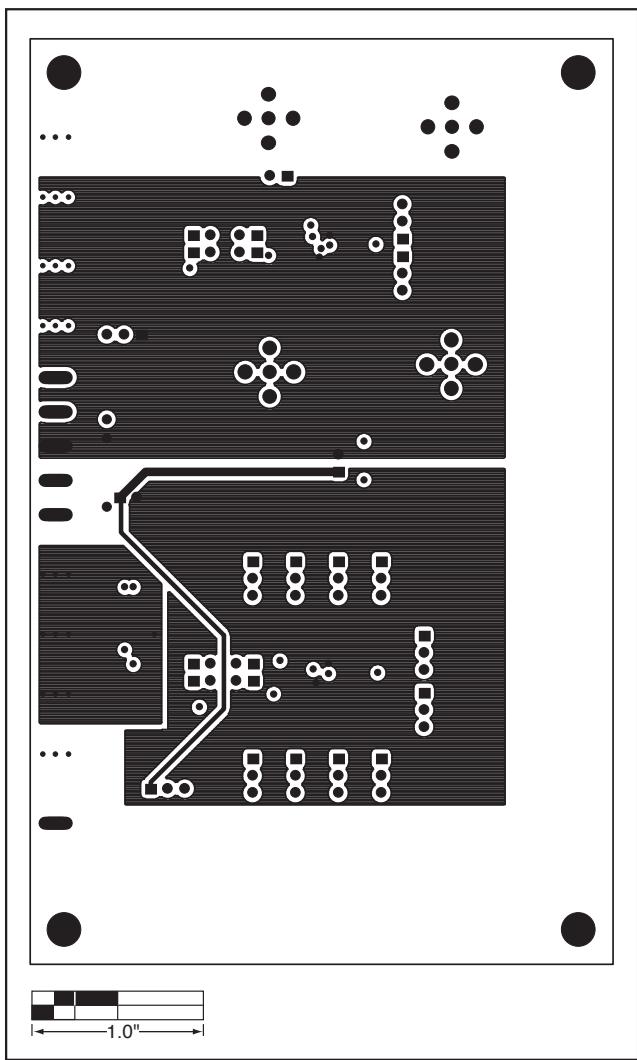

図4. MAX9150EVキットのプリント基板レイアウト

(部品面側)

# MAX9150評価キット

**Evaluates: MAX9150**

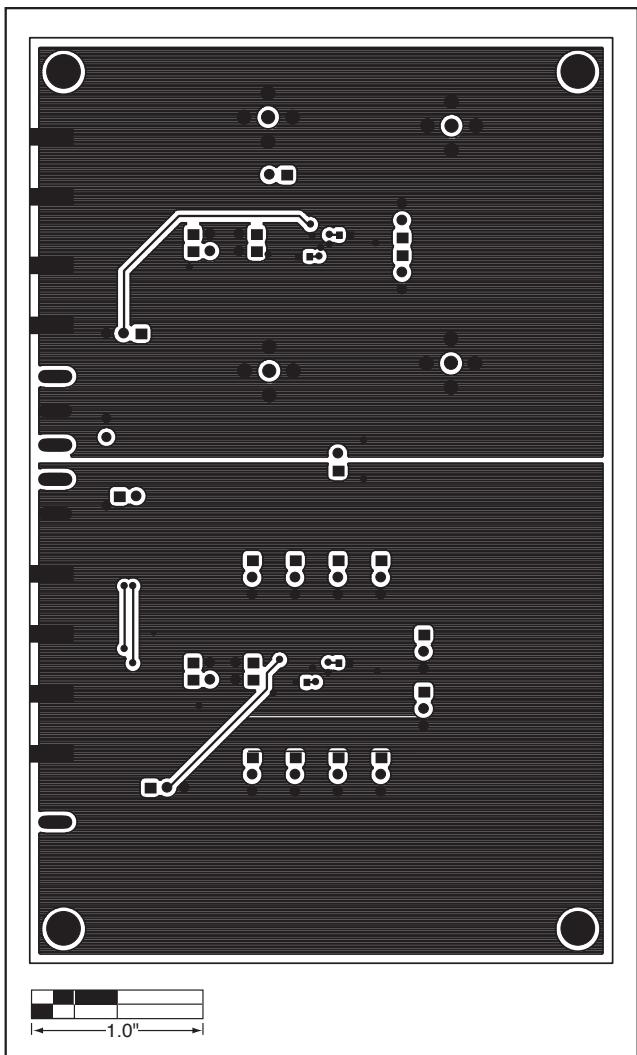

図5. MAX9150EVキットのプリント基板レイアウト

(グランドプレーン)

図6. MAX9150EVキットのプリント基板レイアウト

(電源プレーン)

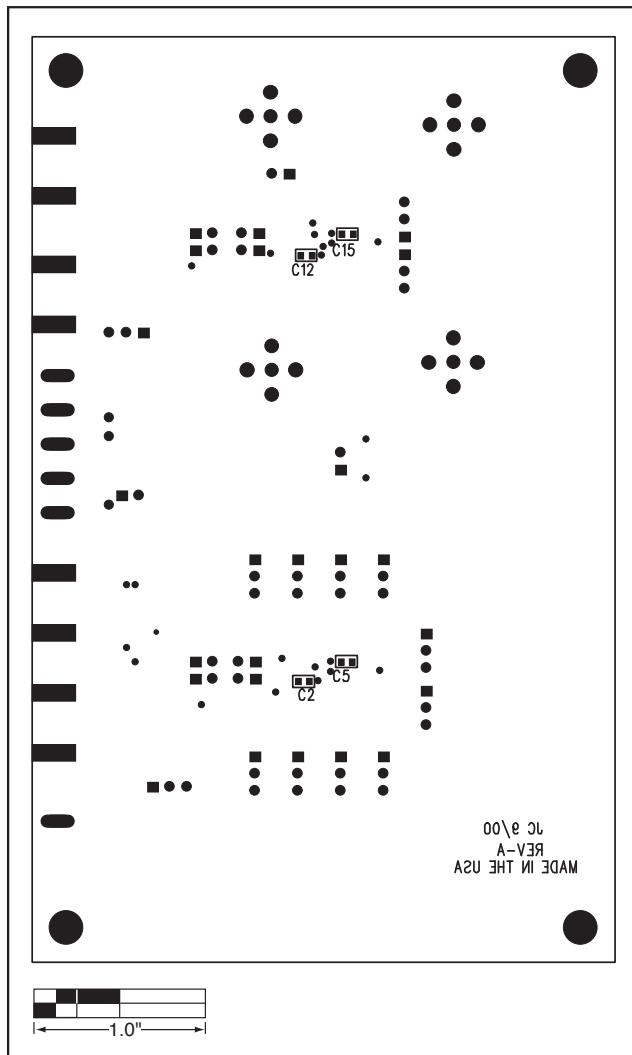

図7. MAX9150EVキットのプリント基板レイアウト

(ハンダ面側)

図8. MAX9150EVキットの部品配置図(ハンダ面側)

**マキシム・ジャパン株式会社**

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。

マキシムは隨時予告なく回路及び仕様を変更する権利を留保します。